## KEY FRONT-END CIRCUITS IN MILLIMETER-WAVE SILICON-BASED WIRELESS TRANSMITTERS FOR PHASED-ARRAY APPLICATIONS

A Dissertation Presented to The Academic Faculty

by

Tso-Wei Li

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2020

COPYRIGHT© 2020 BY TSO-WEI LI

## KEY FRONT-END CIRCUITS IN MILLIMETER-WAVE SILICON-BASED WIRELESS TRANSMITTERS FOR PHASED-ARRAY APPLICATIONS

#### Approved by:

Dr. Hua Wang, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Gee-Kung Chang School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Farrokh Ayazi School of Electrical and Computer Engineering Georgia Institute of Technology Dr. John D Cressler School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hossein Miri Lavasani Department of Electrical, Computer and Systems Engineering Case Western Reserve University

Date Approved: December 3, 2020

## **ACKNOWLEDGEMENTS**

I want to thank my advisor, Dr. Hua Wang, for providing feedback and brainstorm throughout my works in my Ph.D. career. It is also my pleasure to join one of the best labs in the RF/millimeter-wave integrated circuit field in the world, including cutting-edge equipment and intelligent people. I truly appreciate my family for their unlimited support; I cannot obtain my Ph.D. degree without them.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                   | iv        |

|--------------------------------------------------------------------|-----------|

| LIST OF TABLES                                                     | vii       |

| LIST OF FIGURES                                                    | viii      |

| SUMMARY                                                            | XIV       |

| CHAPTER 1. INTRODUCTION                                            | 1         |

| CHAPTER 2. HARMONICALLY-TUNED PA OPERATION                         | 7         |

| 2.1 Introduction                                                   | 7         |

| 2.1.1 Conventional Class-F PA operation                            | 7         |

| 2.1.2 Conventional Class-F-1 PA operation                          | 9         |

| 2.1.3 Continuous-mode Class-F and Class-F-1 PA                     | 12        |

| 2.1.4 Proposed Continuous-mode PA Output Network                   | 15        |

| 2.2.1 Continuous-Mode Class-F-1 PA Output Network                  | 15        |

| 2.2.2 Continuous-mode Hybrid Class-F/F-1 PA Output Network         | 20        |

| 2.1.5 Continuous-Mode Harmonically-Tuned PA Implementation         | 25        |

| 2.3.1 Design 1: A Two-Stage Continuous-mode Class-F-1 PA           | 25        |

| 2.3.2 Design 2: A One-Stage Continuous-mode Class-F/F-1 PA         | 25        |

| 2.3.3 Design 3: A Two-Stage Continuous-mode Class-F/F-1 PA         | 26        |

| 2.1.6 Measurement Results                                          | 28        |

| 2.1.7 Chapter Summary                                              | 40        |

| CHAPTER 3. A POWER AMPLIFIER WITH NMOS/PMOS NONLINEAITY            |           |

| CANCELLATION SCHEME                                                | 41        |

| 3.1 Introduction                                                   | 41        |

| 3.2 MOSFET AM-AM and AM-PM Distortion Analysis                     | 44        |

| 3.3 Proposed NMOS/PMOS AM-PM Nonlinearity Cancellation Scheme      | 51        |

| 3.3.1 Concept of doubly NMOS/PMOS nonlinearity cancellation scheme | 51        |

| 3.3.2 PA output network NMOS/PMOS Linearity Improvement Scheme     | 53        |

| 3.3.3 Series-Parallel DAT Output Power Combiner                    | 53        |

|                                                                    | <b>56</b> |

| 3.4 PA Implementation 3.5 Measurement Results                      | 58        |

| 3.6 Chapter Summary                                                | 68        |

| 5.0 Chapter Summary                                                | UO        |

| CHAPTER 4. A MILLIMETER-WAVE FULLY INTEGRATED PASSIVE              |           |

| REFLECTION-TYPE PHASE SHIFTER WITH                                 |           |

| TRANSFORMER-BASED MULTI-RESONANCE LOADS FO                         | R         |

| 360° PHASE SHIFTING                                                | 69        |

| 4.1 Introduction                                                   | 69        |

| 4.2 Reported RTPS Topologies                                       | 69        |

| 4.3 RTPS Design Challenge                                          | 71        |

| 4.4 I        | Reflective Load Designs in RTPS                            | 71  |

|--------------|------------------------------------------------------------|-----|

| 4.4.1        | Capacitive load (CL)                                       | 73  |

| 4.4.2        | Series L-C resonant load (SLC)                             | 75  |

| 4.4.3        | Parallel L-C Resonant Load (PLC)                           | 77  |

| 4.4.4        | CLC $\pi$ -resonator load with one tunable capacitor       | 79  |

| 4.4.5        | CLC $\pi$ -resonator load with two tunable capacitors      | 82  |

| 4.4.6        | Transformer-based multi-resonance reflective load          | 87  |

| <b>4.5</b> T | <b>Transformer-based 90° Coupler Design</b>                | 93  |

| 4.6          | Circuit Implementation and Simulation of the Proposed RTPS | 96  |

| 4.7 N        | Aeasurement Results                                        | 101 |

| 4.8          | Chapter Summary                                            | 109 |

| <b>4.9</b> A | appendix                                                   | 109 |

| 4.9.1        | Capacitive load (CL)                                       | 110 |

| 4.9.2        | Series L-C resonant load (SLC)                             | 112 |

| 4.9.3        | Parallel L-C resonant load (PLC)                           | 113 |

| 4.9.4        | CLC $\pi$ -resonant load with one-side capacitive tuning)  | 116 |

| 4.9.5        | CLC $\pi$ -resonant load with two-side capacitive tuning   | 116 |

| 4.9.6        | Transformer-based multi-resonance reflective load          | 118 |

| REFER        | ENCES                                                      | 122 |

# LIST OF TABLES

| Table 2.1 | – PA Load Impedance Behaviors for Different Operations                                                                                          | 14  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 | - CW Performance Comparison with State-of-the art Silicon-based Mm-Wave Power Amplifier at Related Frequency                                    | 39  |

| Table 2.3 | <ul> <li>Modulation Performance Comparison With State-of-the art</li> <li>Silicon-based Mm-Wave Power Amplifier at Related Frequency</li> </ul> | 40  |

| Table 3.1 | <ul> <li>CW Performance Comparison with The State-Of-The-Art<br/>Silicon-Based Mm-Wav E PA at Related Frequency</li> </ul>                      | 67  |

| Table 3.2 | <ul> <li>Modulation Comparison with The State-Of-The-Art Silicon-<br/>Based Mm-Wave PA at Related Frequency</li> </ul>                          | 68  |

| Table 4.1 | <ul> <li>Comparison table of maximum phase shift for different reflective<br/>loads in an RTPS</li> </ul>                                       | 93  |

| Table 4.2 | Performance comparison of reported fully integrated RTPS designs in silicon                                                                     | 108 |

## LIST OF FIGURES

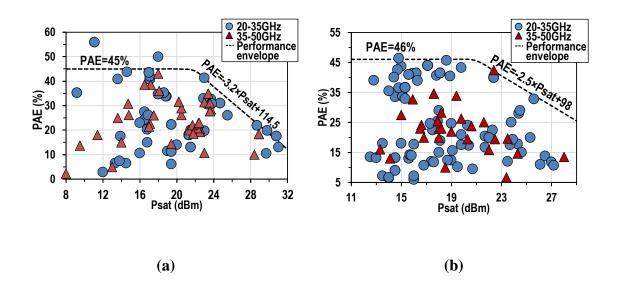

| Figure 1.1 | <ul> <li>PAE comparison with state-of-the-art mm-Wave silicon-based PAs in (a) SiGe and (b) CMOS process (20-50 GHz) [26].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| Figure 1.2 | <ul> <li>Average Efficiency vs Average Output Power for SiGe and CMOS</li> <li>PAs in modulation with 64QAM (20-50 GHz) [26].</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   | 6  |  |  |

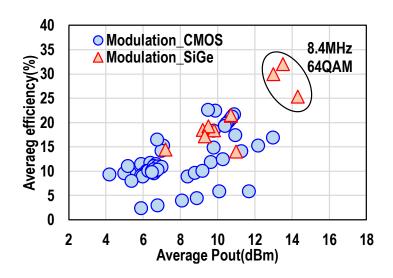

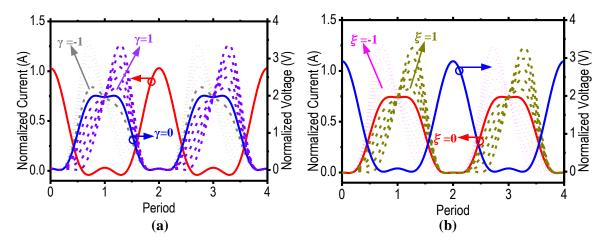

| Figure 2.1 | <ul> <li>Theoretical current and voltage waveforms composed of the<br/>fundamental, 2nd- and 3rd-harmonics for (a) conventional/continuous-<br/>mode Class-F and (b) conventional/continuous-mode Class-F-1<br/>operations.</li> </ul>                                                                                                                                                                                                                                                                                                     | 8  |  |  |

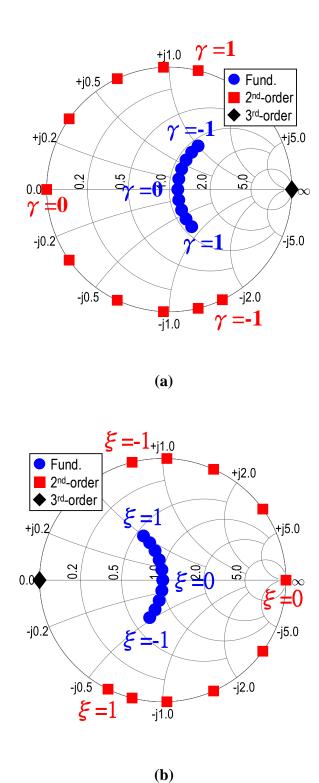

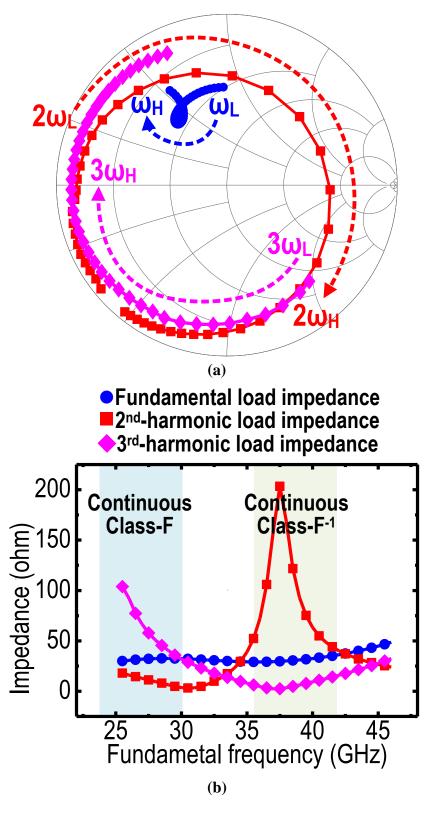

| Figure 2.2 | <ul> <li>Fundamental, 2nd- and 3rd-harmonic load impedances for (a) continuous-mode Class-F and (b) continuous-mode Class-F-1 PA operations.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    | 11 |  |  |

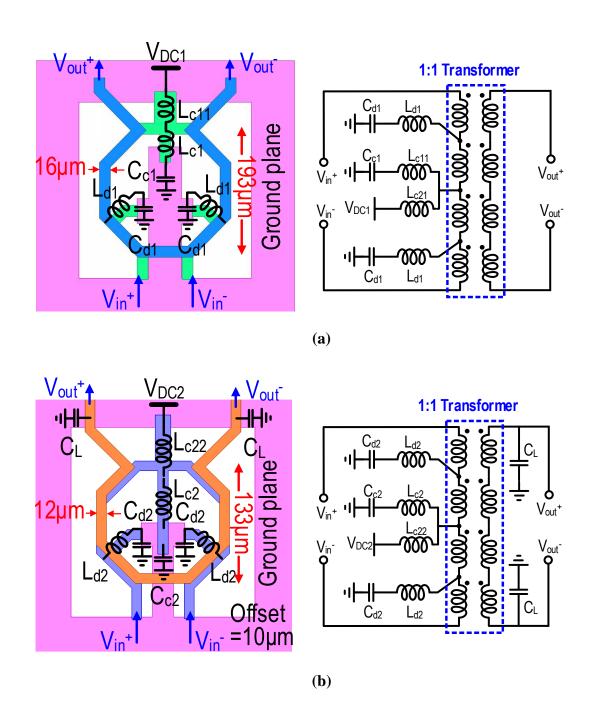

| Figure 2.3 | – EM and schematic of (a) continuous-mode Class-F-1 PA and (b) continuous-mode hybrid Class-F/-F-1 PA.                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |  |  |

| Figure 2.4 | – Simplified of (a) differential-mode and (b) common-mode half circuits of the continuous-mode Class-F-1 PA output network at (c) the fundamental frequency (d) the 3rd-harmonic of lower band, and (e) the 2nd-harmonic frequencies, respectively.                                                                                                                                                                                                                                                                                        | 18 |  |  |

| Figure 2.5 | – Trajectories of the half-circuit load impedance at fundamental, 2nd-and 3rd-order harmonic frequencies (characteristic impedance Z0 = $50\Omega$ ).                                                                                                                                                                                                                                                                                                                                                                                      | 19 |  |  |

| Figure 2.6 | – Simplified half circuits of the (a) differential-mode, (b) common-mode of the continuous-mode hybrid Class-F/F-1 PA output network at (c) the fundamental frequency ( $\omega L \le \omega \le \omega H$ ) and (d) the fundamental equivalent circuit, (e) the 3rd-order harmonic of lower band ( $\omega = 3\omega L$ ), (f) the 3rd-order harmonic of higher band ( $\omega = 3\omega H$ ), (g) the 2nd-order harmonic of lower band ( $\omega = 2\omega L$ ), and (h) the 2nd-order harmonic of higher band ( $\omega = 2\omega H$ ). | 23 |  |  |

| Figure 2.7 | – (a) Trajectories of half-circuit load impedance at fundamental, 2nd-and 3rd-order harmonic frequencies (Z0 =50 $\Omega$ ), and (b) impedance response.                                                                                                                                                                                                                                                                                                                                                                                   | 24 |  |  |

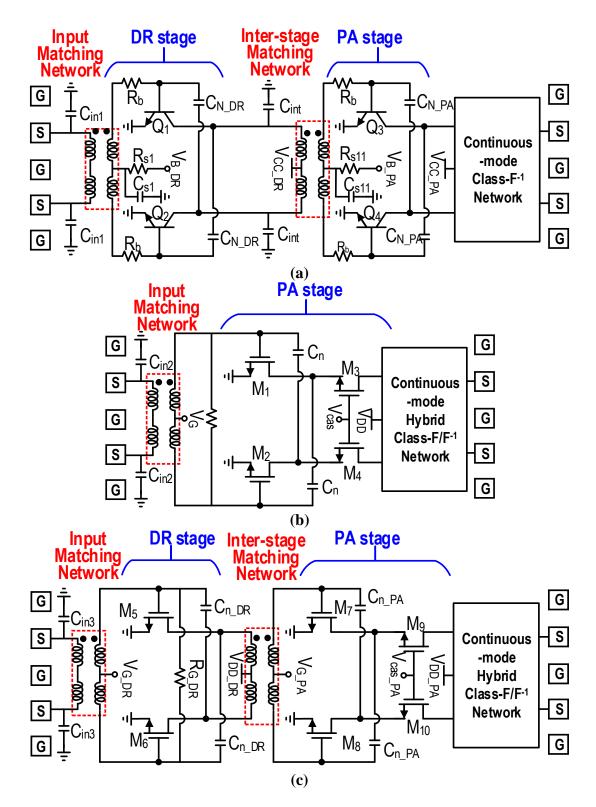

| Figure 2.8 | – Schematic of (a) two-stage continuous-mode Class-F-1 PA, (b) one-and (c) two-stage continuous-mode hybrid Class-F/F-1 PAs.                                                                                                                                                                                                                                                                                                                                                                                                               | 27 |  |  |

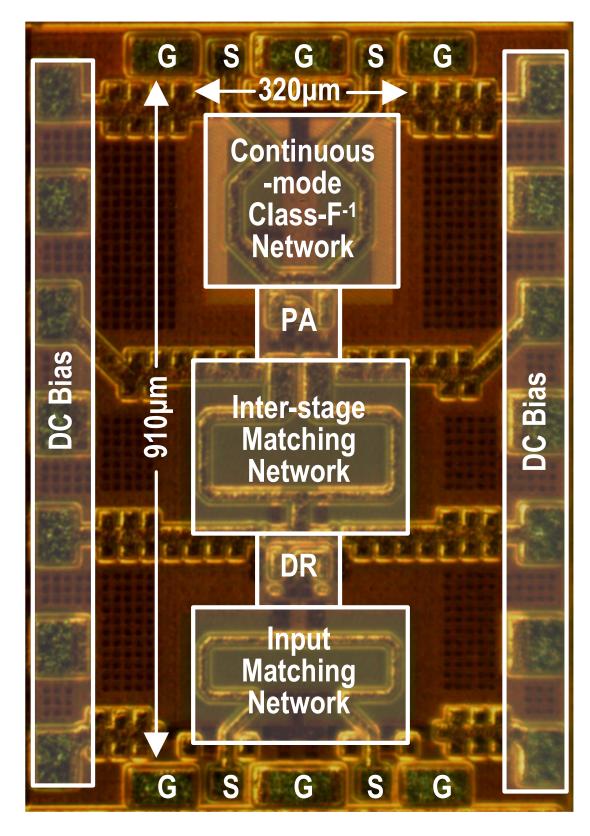

| Figure 2.9 | - Chin microphotograph of two-stage continuous-mode Class-F-1 PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29 |  |  |

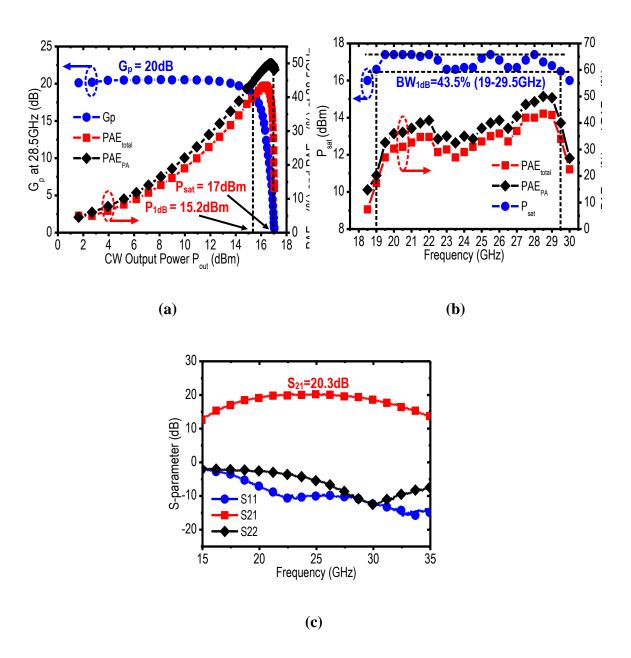

| Figure 2.10 | - (a) measured CW large-signal performance at 28.5 GHz, (b) measured CW large-signal performance vs. frequency and (c) measured small-signal S-parameter of two-stage continuous-mode Class-F-1 PA. |    |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| Figure 2.11 | - (a) 64-QAM constellation, (b) 256-QAM constellation, (c) 64-QAM spectrum and (d) 256-QAM spectrum at fcarrier of 28.5 GHz of Design 3.                                                            |    |  |  |  |  |

| Figure 2.12 | <ul> <li>Chip microphotograph of one-stage continuous-mode hybrid Class-F/F-1 PA.</li> </ul>                                                                                                        |    |  |  |  |  |

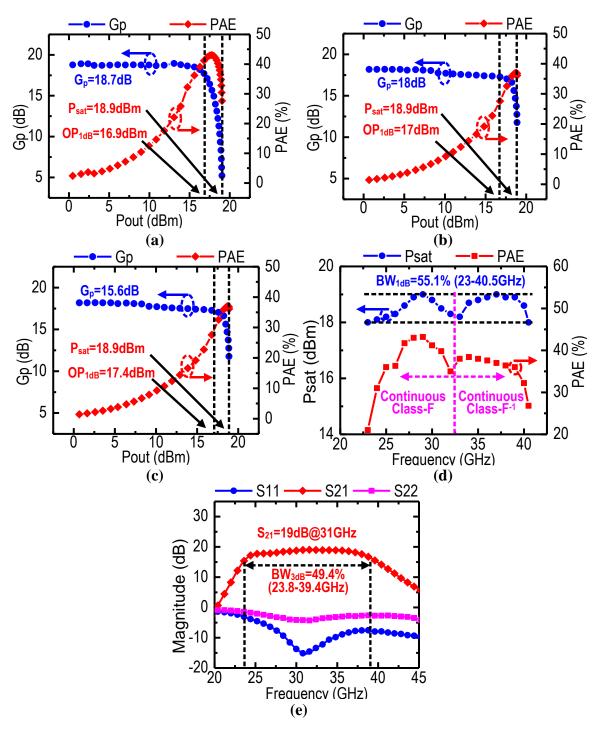

| Figure 2.13 | One-stage continuous-mode hybrid Class-F/F-1 PA CW large-signal measurement at (a) 28 GHz, (b) 37 GHz and (c) 39 GHz, (d) Psat/PAE vs. frequency, and (e) small-signal S-parameter.                 |    |  |  |  |  |

| Figure 2.14 | <ul> <li>Chip microphotograph of two-stage continuous-mode hybrid Class-F/F-1 PA.</li> </ul>                                                                                                        | 36 |  |  |  |  |

| Figure 2.15 | - Two-stage continuous-mode hybrid Class-F/F-1 PA CW large-signal measurement at (a) 28 GHz, (b) 37 GHz and (c) 39 GHz, (d) Psat/PAE vs. frequency, and (e) small-signal S-parameter.               | 37 |  |  |  |  |

| Figure 2.16 | <ul> <li>Two-stage continuous-mode hybrid Class-F/F-1 PA modulation<br/>measurement results (0.5 GSym/s) at (a) 24 GHz, (b) 28 GHz, (c) 37<br/>GHz, (d) 39 GHz respectively.</li> </ul>             | 38 |  |  |  |  |

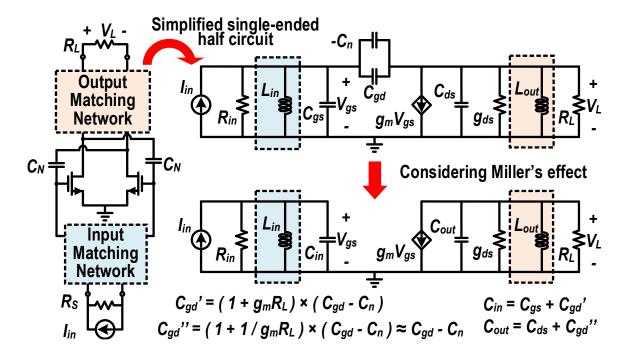

| Figure 3.1  | – A neutralized PA and its simplified single-ended half circuit.                                                                                                                                    | 49 |  |  |  |  |

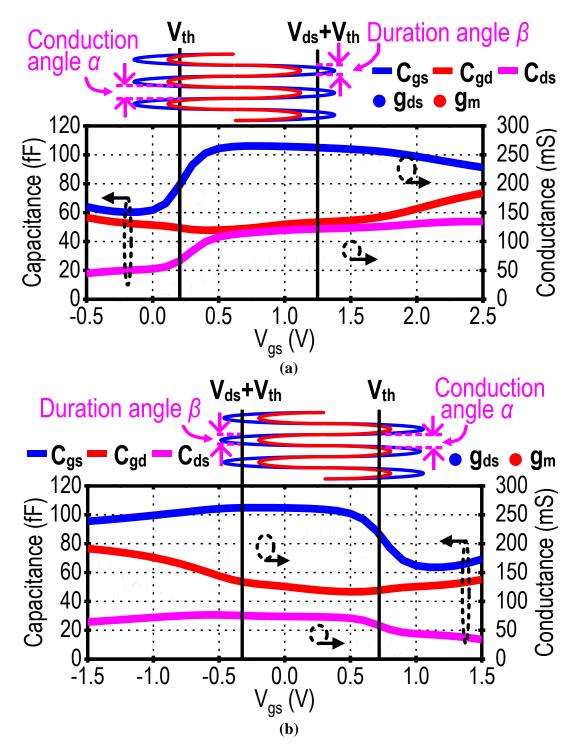

| Figure 3.2  | – The extracted gate-to-source Cgs, gate-to-drain Cgd and drain-to-source <i>Cds</i> , and transconductance gm and drain-to-source conductance <i>gds</i> in (a) NMOS and (b) PMOS transistor.      | 50 |  |  |  |  |

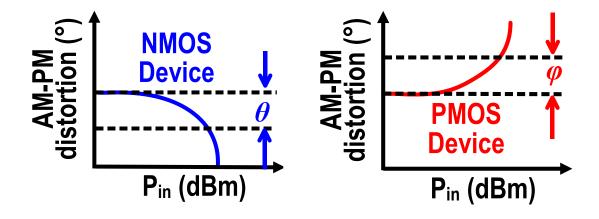

| Figure 3.3  | - The AM-PM behaviors of NMOS and PMOS PAs.                                                                                                                                                         | 51 |  |  |  |  |

| Figure 3.4  | <ul> <li>The concept of the proposed doubly nonlinearity cancellation<br/>scheme.</li> </ul>                                                                                                        | 52 |  |  |  |  |

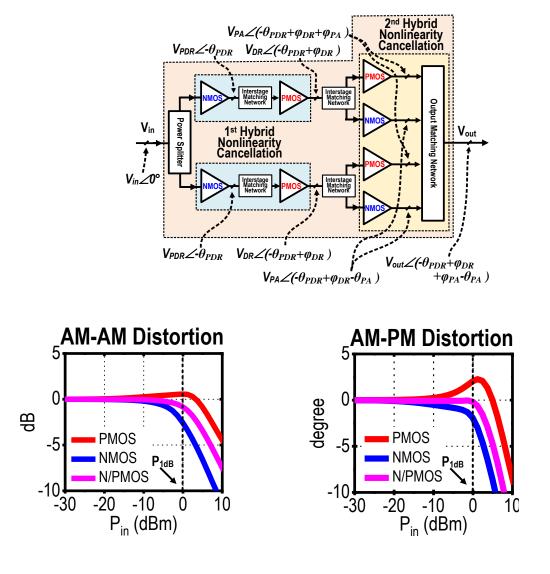

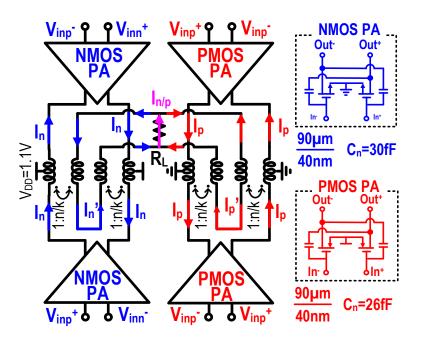

| Figure 3.5  | – The schematic of the hybrid NMOS/PMOS nonlinearity cancellation scheme.                                                                                                                           | 54 |  |  |  |  |

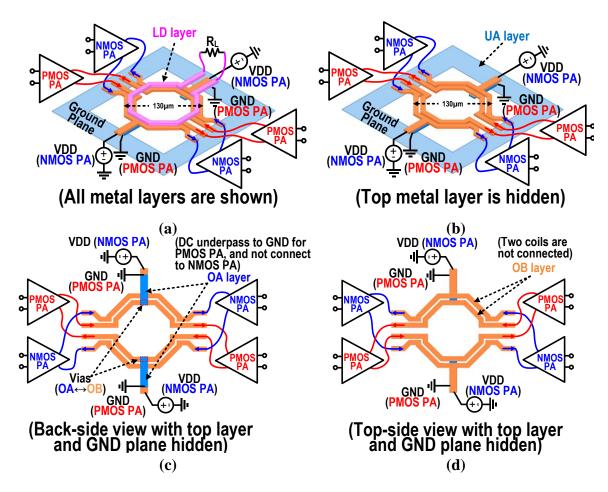

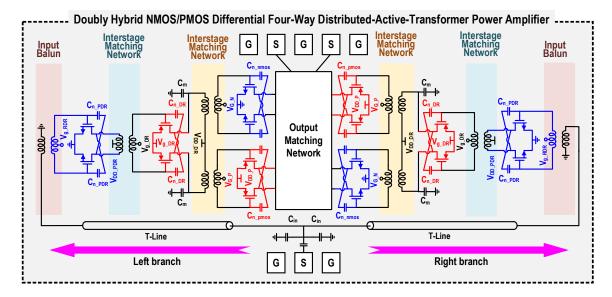

| Figure 3.6  | <ul> <li>The 3D EM model of the hybrid NMOS/PMOS nonlinearity<br/>cancellation PA with 4-way series-parallel DAT.</li> </ul>                                                                        |    |  |  |  |  |

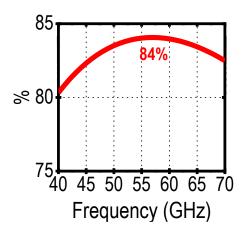

| Figure 3.7  | <ul> <li>The simulated passive efficiency of the proposed series-parallel<br/>DAT.</li> </ul>                                                                                                       | 55 |  |  |  |  |

| Figure 3.8  | – The schematic of the proposed PA.                                                                                                                                                                                                                                                                                                                                                                 | 57 |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

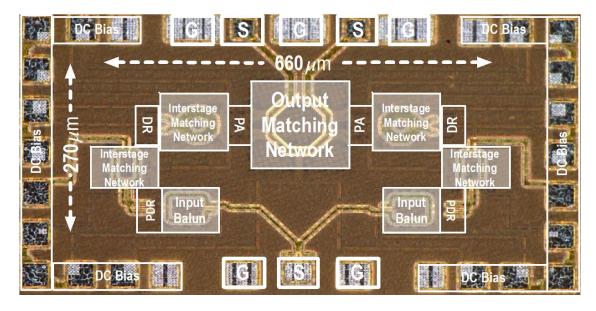

| Figure 3.9  | - The chip microphotographic.                                                                                                                                                                                                                                                                                                                                                                       | 57 |  |  |  |  |

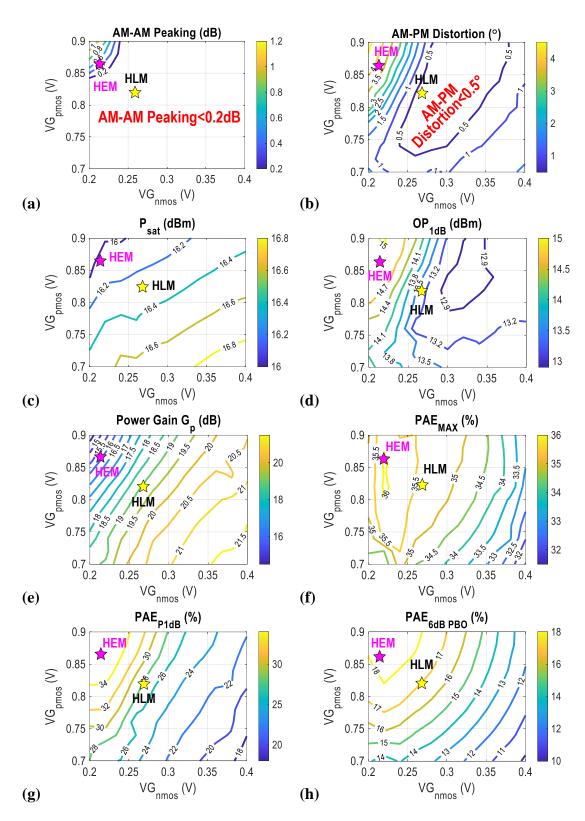

| Figure 3.10 | <ul> <li>Measured CW performance vs. the gate voltages, e.g., (a)AM-AM distortion, (b) AM-PM distortion, (c) Psat, (d) OP1dB (e) Gp, (f) PAEmax, (g) PAEP1dB, and (h) PAE6dB_PBO</li> </ul>                                                                                                                                                                                                         |    |  |  |  |  |

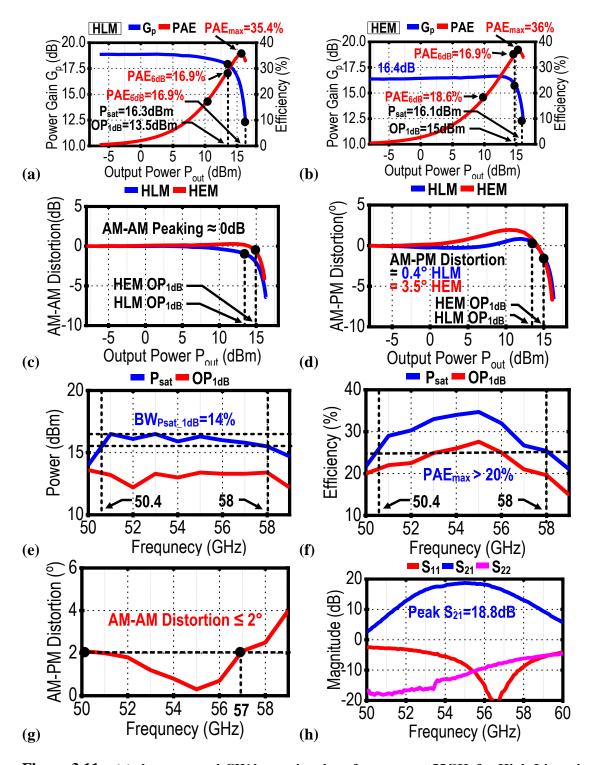

| Figure 3.11 | – (a) the measured CW large-signal performance at 55GHzfor High-Linearity-Mode (HLM), (b) the measured CW large-signal performance at 55GHz for High-Efficiency-Mode (HEM), (c) the AM-AM distortion, (d) the AM-PM distortion, (f) the delivery power, (g) the efficiency and (h) The S-parameters.                                                                                                | 62 |  |  |  |  |

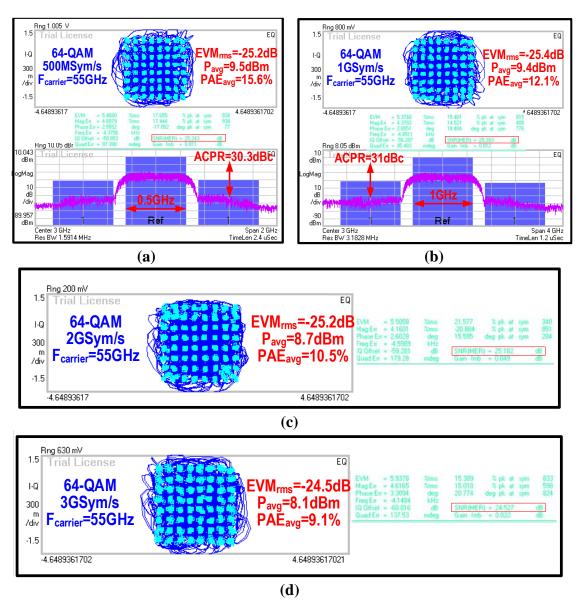

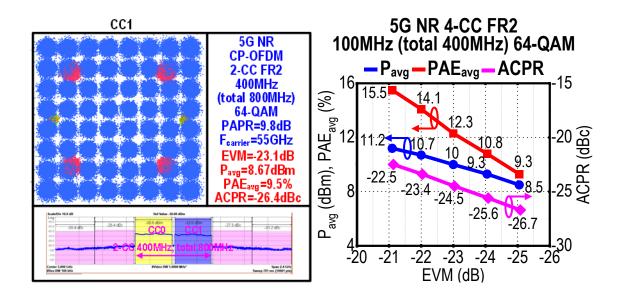

| Figure 3.12 | – The 5G NR 64-QAM CP-OFDM modulation results with 1-CC FR2 400MHz.                                                                                                                                                                                                                                                                                                                                 | 63 |  |  |  |  |

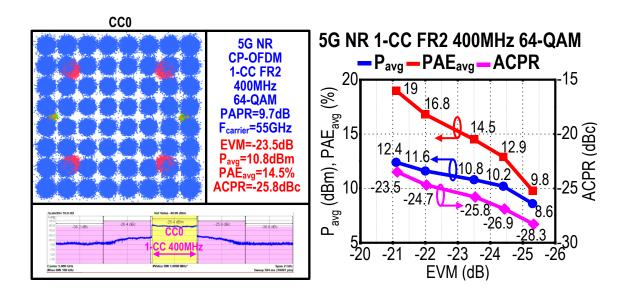

| Figure 3.13 | - The 5G NR 64-QAM CP-OFDM modulation results with 1-CC FR2 400MHz.                                                                                                                                                                                                                                                                                                                                 | 64 |  |  |  |  |

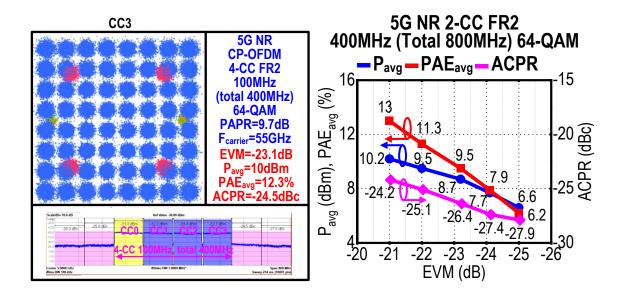

| Figure 3.14 | $^{\rm -}$ The 5G NR 64-QAM CP-OFDM modulation results with 2-CC FR2 400MHz.                                                                                                                                                                                                                                                                                                                        | 64 |  |  |  |  |

| Figure 3.15 | <ul> <li>The 5G NR 64-QAM CP-OFDM modulation results with 4-CC FR2 100MHz.</li> </ul>                                                                                                                                                                                                                                                                                                               | 65 |  |  |  |  |

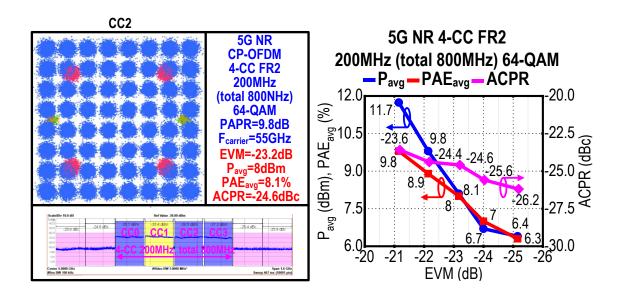

| Figure 3.16 | <ul> <li>The 5G NR 64-QAM CP-OFDM modulation results with 4-CC FR2 200MHz.</li> </ul>                                                                                                                                                                                                                                                                                                               | 65 |  |  |  |  |

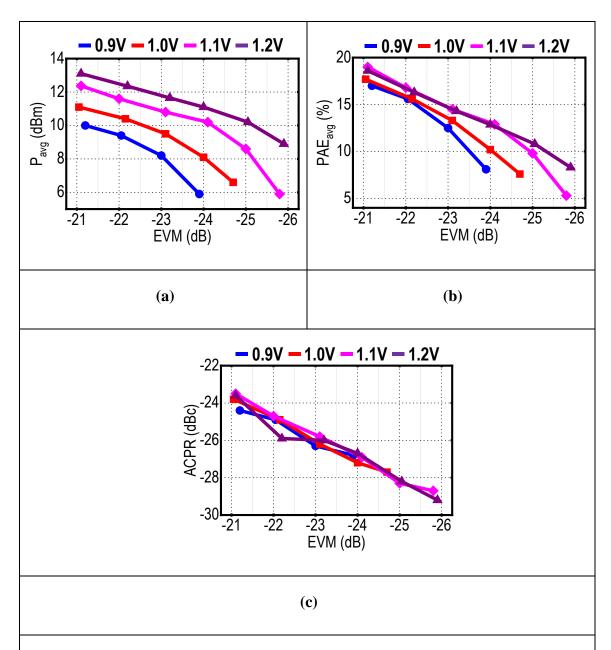

| Figure 3.17 | – The measured 5G NR 64-QAM CP-OFDM 1-CC FR2 400MHz modulation results, e.g., (a) Pavg, (b) PAEavg and (c) ACPR with various VDD values (VDD = 0.9, 1.1, 1.1 and 1.2 V).                                                                                                                                                                                                                            | 66 |  |  |  |  |

| Figure 4.1  | – A single-ended reflection-type phase shifter (RTPS).                                                                                                                                                                                                                                                                                                                                              | 73 |  |  |  |  |

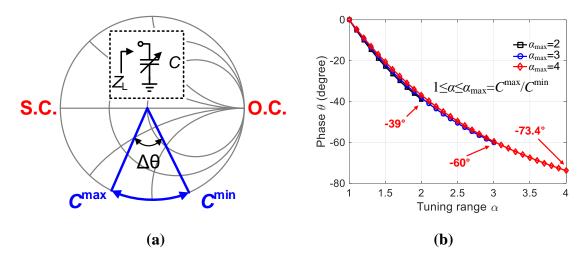

| Figure 4.2  | – (a) The load impedance tuning range for a lossless capacitive load (CL) by tuning C, and (b) the simulated phase shifting range as the capacitor load tuning range $\alpha$ varies from 1 to its maximum value for different $\alpha$ max (e.g., $\alpha$ max=2, 3, or 4). Assume that the optimum Cmin value, i.e., $C^{min}=1/(\sqrt{\alpha_{max}}Z_0\omega_0)$ is used in this CL RTPS design. | 75 |  |  |  |  |

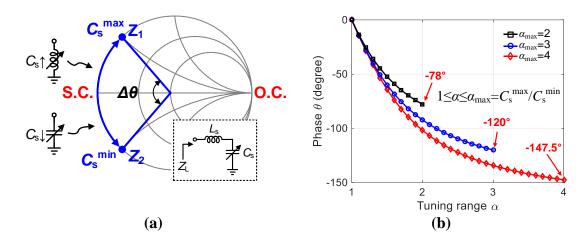

| Figure 4.3  | – (a) The load impedance trajectory for a lossless parallel L-C load (PLC) by tuning Cp, and (b) the simulated phase shifting range for different maximum capacitor tuning range αmax=Cpmax/Cpmin, e.g., αmax=2, 3, or 4. Assume the optimum Cpmin and Lp values are used in this PLC RTPS design.                                                                                                  | 77 |  |  |  |  |

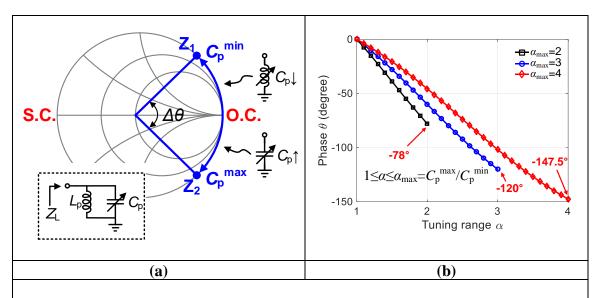

| Figure 4.4  | – (a) The load impedance trajectory for a lossless parallel L-C load (PLC) by tuning Cp, and (b) the simulated phase shifting range for different maximum capacitor tuning range $\alpha$ max=Cpmax/Cpmin, e.g., $\alpha$ max=2, 3, or 4. Assume the optimum Cpmin and Lp values are used in this PLC RTPS design.                                                                                              | 79 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.5  | – The load impedance tuning range for a lossless CLC $\pi$ -resonator load with one tunable capacitor (CLC-1).                                                                                                                                                                                                                                                                                                  | 81 |

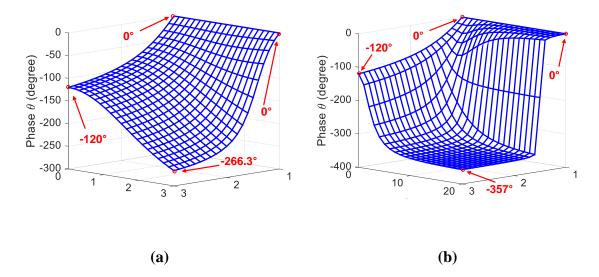

| Figure 4.6  | – The simulated CLC-1 phase shifting range versus the capacitor tuning α and capacitor ratio β (i.e., $\beta$ =C3/C2min) for a lossless CLC-1 RTPS load. The phase shifting range is referenced to zero for α =1, i.e., no capacitive tuning. It covers (a) $0 \le \beta \le 3$ and (b) $0 \le \beta \le 20$ .                                                                                                  | 82 |

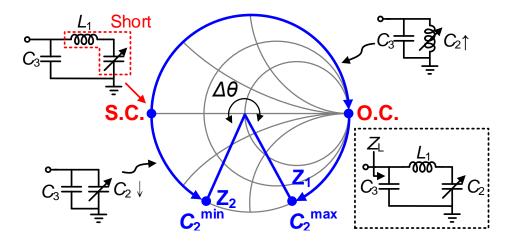

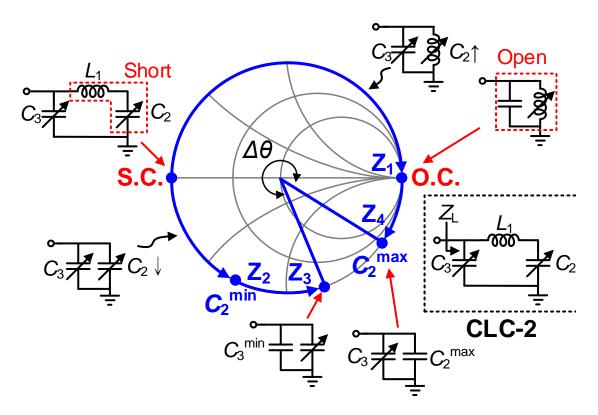

| Figure 4.7  | – The load impedance tuning range for a lossless CLC $\pi$ -resonator load with two tunable capacitors (CLC-2).                                                                                                                                                                                                                                                                                                 | 85 |

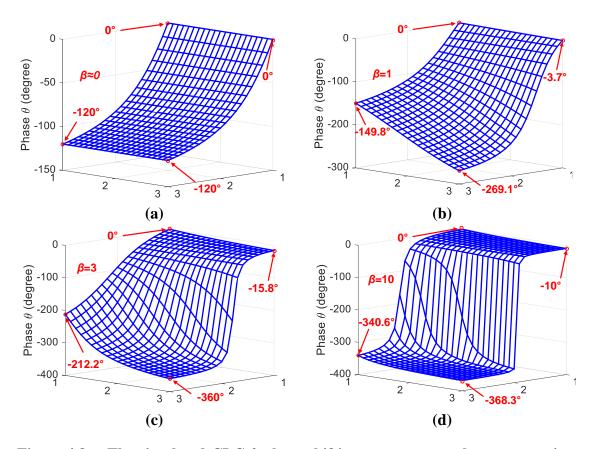

| Figure 4.8  | – The simulated CLC-2 phase shifting range versus the two capacitor tuning $\alpha 2$ and $\alpha 3$ at different capacitor ratios $\beta$ (i.e., $\beta$ =C3min/C2min) for a lossless CLC-2 RTPS load with (a) $\beta$ =0, (b) $\beta$ =1, (c) $\beta$ =3, and (d) $\beta$ =10. The $\alpha$ max is 3 and the $\Delta\theta$ is referenced to zero for $\alpha 2$ = $\alpha 3$ =1, i.e., no capacitive tuning. | 86 |

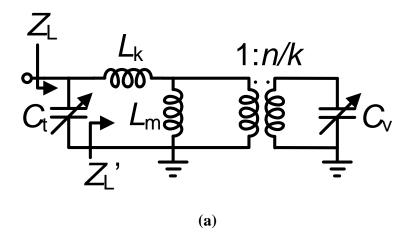

| Figure 4.9  | <ul> <li>The proposed transformer multi-resonance load in an RTPS with (a) single-ended schematic and (b) simplified schematic.</li> </ul>                                                                                                                                                                                                                                                                      | 91 |

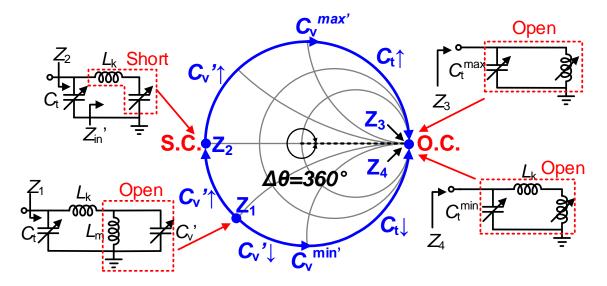

| Figure 4.10 | - The load impedance tuning range for the proposed transformer-based multi-resonance load by varying both Ct and Cv'. All the passive components are assumed to be lossless for simplicity.                                                                                                                                                                                                                     | 92 |

| Figure 4.11 | – The simulated phase shift of our proposed transformer-based multi-resonance load by independently varying Cv and Ct with a maximum capacitive tuning range $\alpha tmax = \alpha vmax = 3$ . (a) Ctmin is obtained from equation (24), and (b) Ctmin is 1.5 times of the value obtained from equation (24).                                                                                                   | 92 |

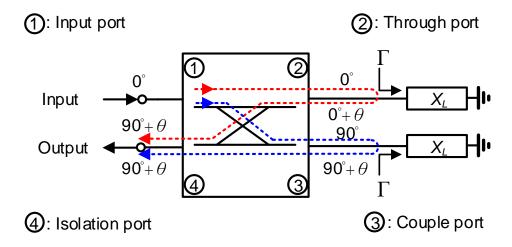

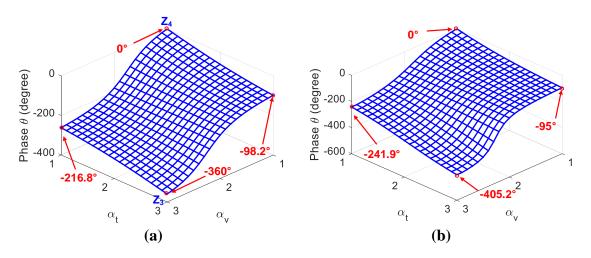

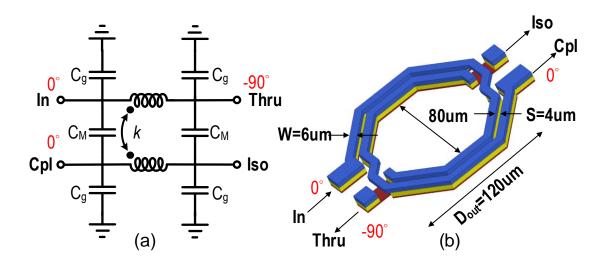

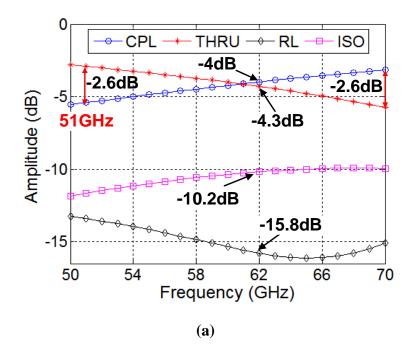

| Figure 4.12 | $-$ A transformer-based $90^\circ$ coupler with (a) the schematic and (b) 3D EM model in the proof-of-concept 60GHz RTPS design.                                                                                                                                                                                                                                                                                | 94 |

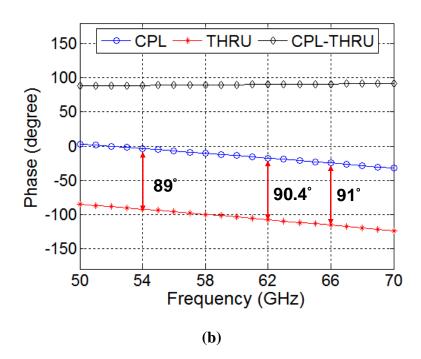

| Figure 4.13 | <ul> <li>(a) Simulated amplitudes for the Thru, Cpl, and Iso ports and the return loss at the In port.</li> <li>(b) Simulated phases for the Thru and Cpl ports.</li> </ul>                                                                                                                                                                                                                                     | 95 |

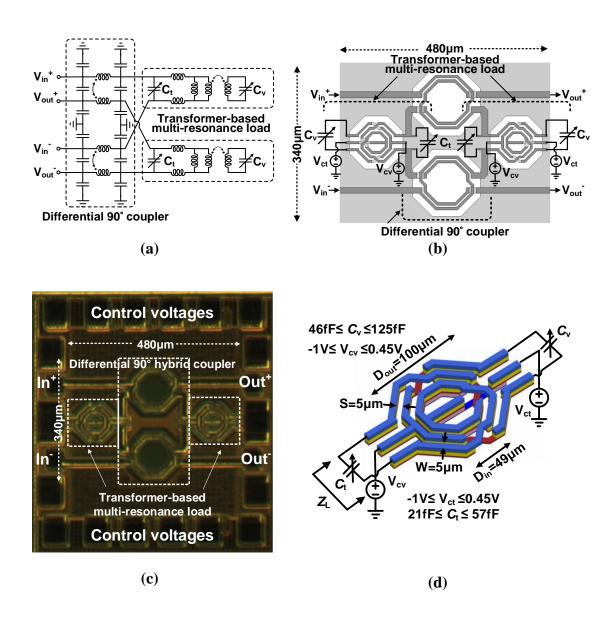

| Figure 4.14 | - Our proposed RTPS design with (a) the schematic, (b) the layout and EM model, (c) the chip microphotograph, and (d) the EM model of the proposed load.                                                                                                                                                                                                                                                        | 98 |

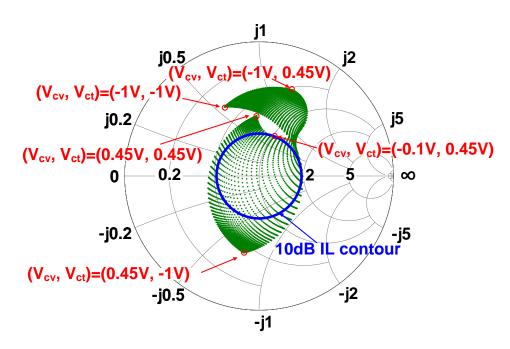

| Figure 4.15 | 5 – The simulated complex IL at 62GHz for the proposed transformer-based RTPS. The simulation includes 3D EM modeling of the passive structures and device parasitic extraction.                                                                              |     |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

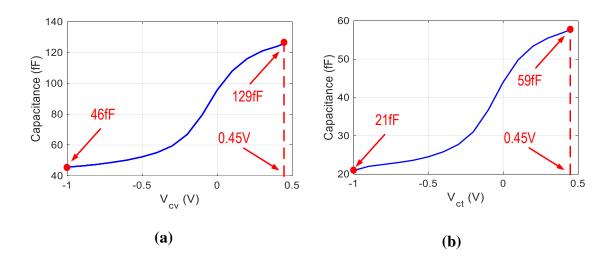

| Figure 4.16 | <ul> <li>The simulated capacitance vs. the control voltage of (a) Vcv and (b)</li> <li>Vct.</li> </ul>                                                                                                                                                        | 99  |  |  |  |

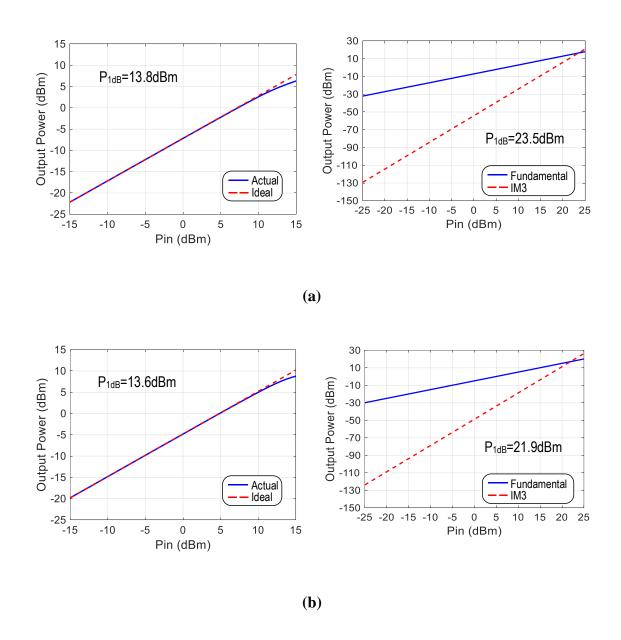

| Figure 4.17 | - The simulated P1dB and IIP3 with (a) Vcv=0.45V and Vct=0.45V Vcv=0.45V and Vct=0.45V, and (b) Vcv=-1V and Vct=-1V.                                                                                                                                          |     |  |  |  |

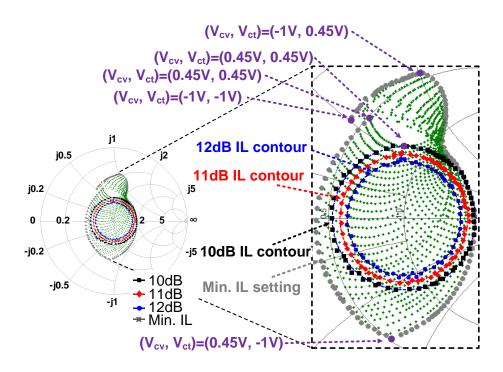

| Figure 4.18 | <ul> <li>Measured RTPS complex IL at 62GHz for the test chip 1. Minimum IL and constant IL contours (10dB, 11dB, and 12dB) are highlighted.</li> </ul>                                                                                                        |     |  |  |  |

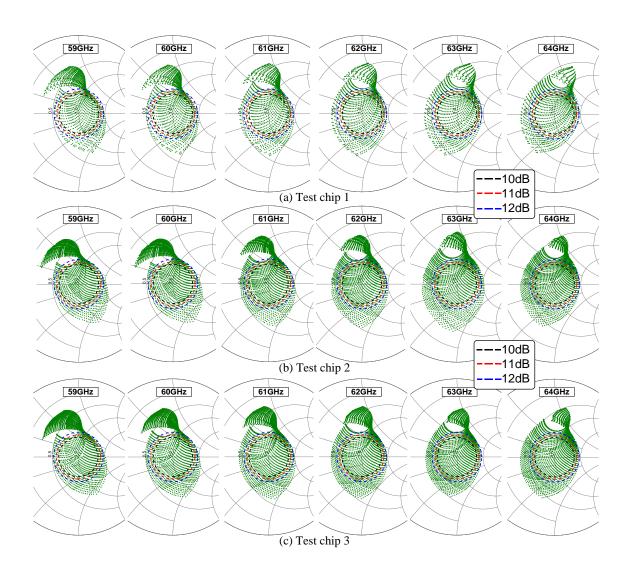

| Figure 4.19 | 19 — Measured complex IL of three independent RTPS test chips at<br>different frequencies. The constant IL contours (IL=10/11/12dB) are<br>highlighted.                                                                                                       |     |  |  |  |

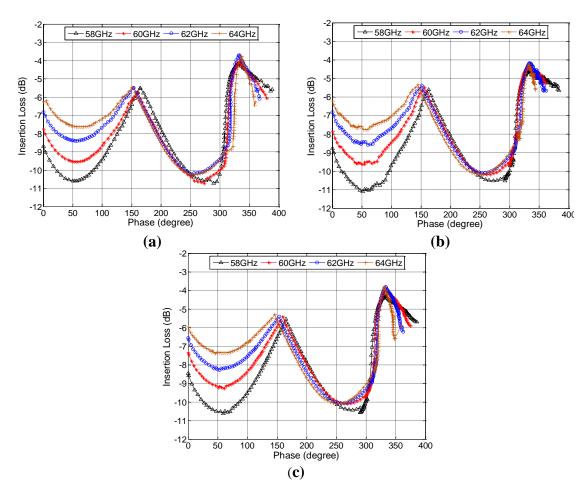

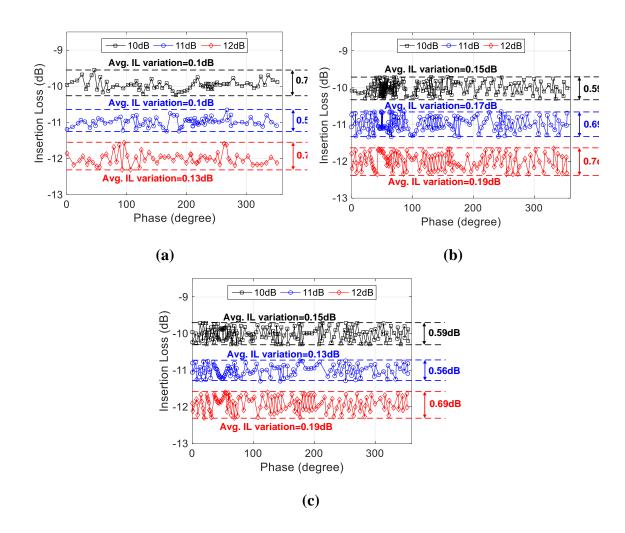

| Figure 4.20 | - Measured RTPS minimum IL vs. phase shift settings at various frequencies for 3 test chips, e.g., (a) Test chip 1, (b)Test chip 2 and (c)Test chip 3.                                                                                                        | 105 |  |  |  |

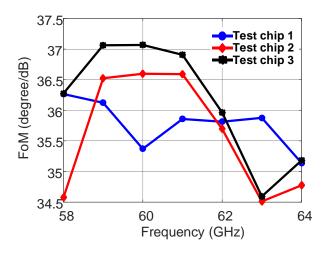

| Figure 4.21 | - FoM vs. frequency for our RTPS at different frequencies.                                                                                                                                                                                                    | 105 |  |  |  |

| Figure 4.22 | – Measured IL variation vs. 360° phase shifts for different constant IL contours (10, 11 and 12dB) at 62GHz for 3 test chips, e.g., (a) Test chip 1, (b)Test chip 2 and (c)Test chip 3.                                                                       | 106 |  |  |  |

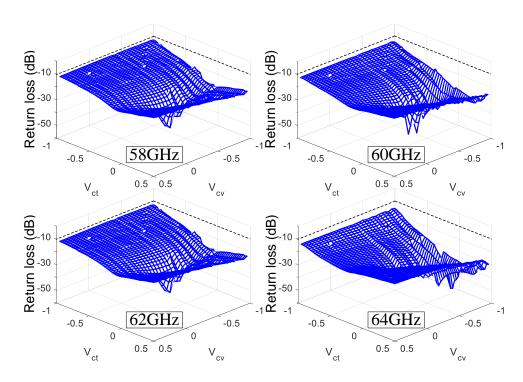

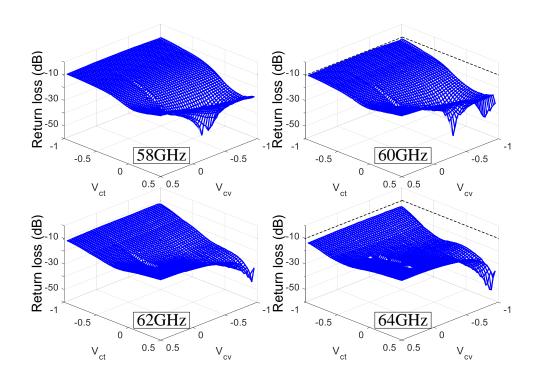

| Figure 4.23 | <ul> <li>Measured return loss vs. 2 independent control voltages (i.e., Vcv and Vct) of three independent RTPS chip samples at 58, 60, 62 and 64GHz for Test chip 1.</li> </ul>                                                                               | 107 |  |  |  |

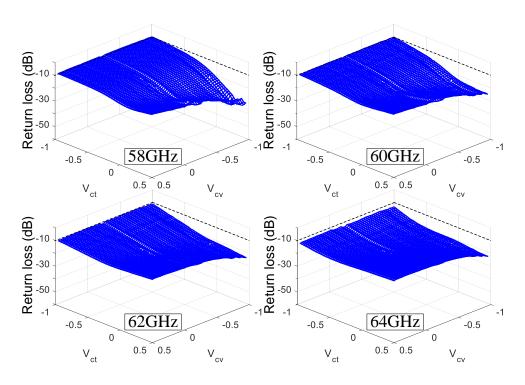

| Figure 4.24 | <ul> <li>Measured return loss vs. 2 independent control voltages (i.e., Vcv and Vct) of three independent RTPS chip samples at 58, 60, 62 and 64GHz for Test chip 2.</li> </ul>                                                                               | 107 |  |  |  |

| Figure 4.25 | <ul> <li>Measured return loss vs. 2 independent control voltages (i.e., Vcv and Vct) of three independent RTPS chip samples at 58, 60, 62 and 64GHz for Test chip 3.</li> </ul>                                                                               | 108 |  |  |  |

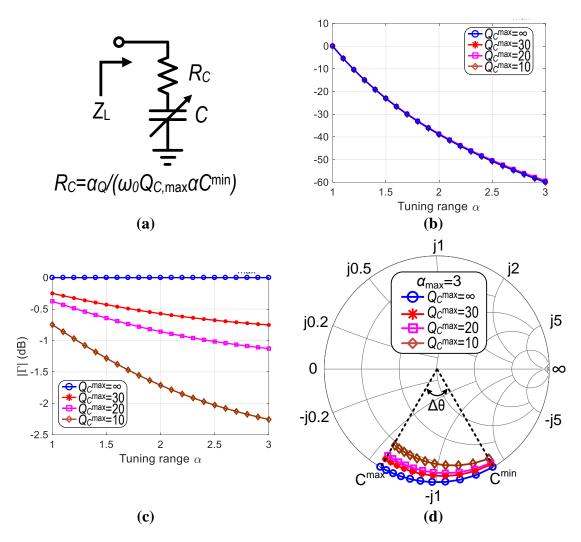

| Figure 4.26 | – (a) A lossy CL model, (b) the maximum phase shift $\Delta\theta$ max vs. $\alpha$ , (c) the load reflection coefficient $ \Gamma $ vs. $\alpha$ , and (d) the load impedance trajectory with different QCmax.                                               | 111 |  |  |  |

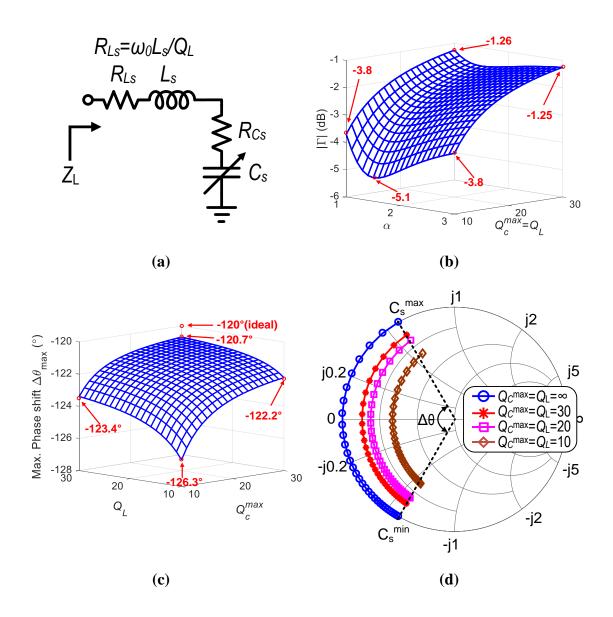

| Figure 4.27 | – (a) A lossy SLC model, (b) the load reflection coefficient $ \Gamma $ as $\alpha$ varies from 1 to $\alpha$ max, (c) the $\Delta\theta$ max versus different quality factors, and (d) the load impedance trajectory on Smith chart with the different QCmax | 113 |  |  |  |

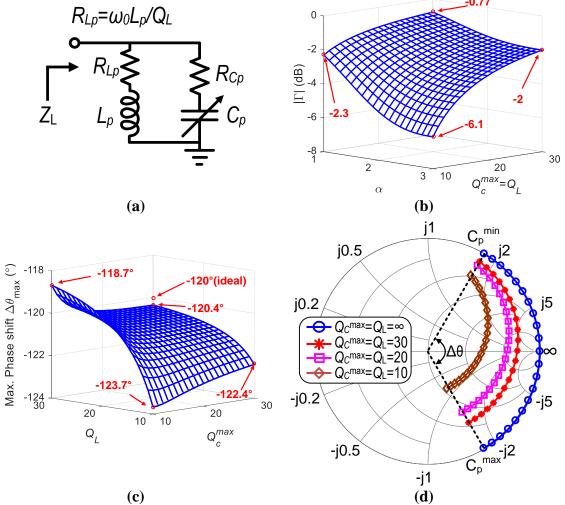

- Figure 4.28 (a) A lossy PLC model, (b) the load reflection coefficient  $|\Gamma|$  as  $\alpha$  115 varies from 1 to  $\alpha$ max, (c) the  $\Delta\theta$ max versus different quality factors, and (d) the load impedance trajectory on Smith chart with the different  $OC^{max}$ .

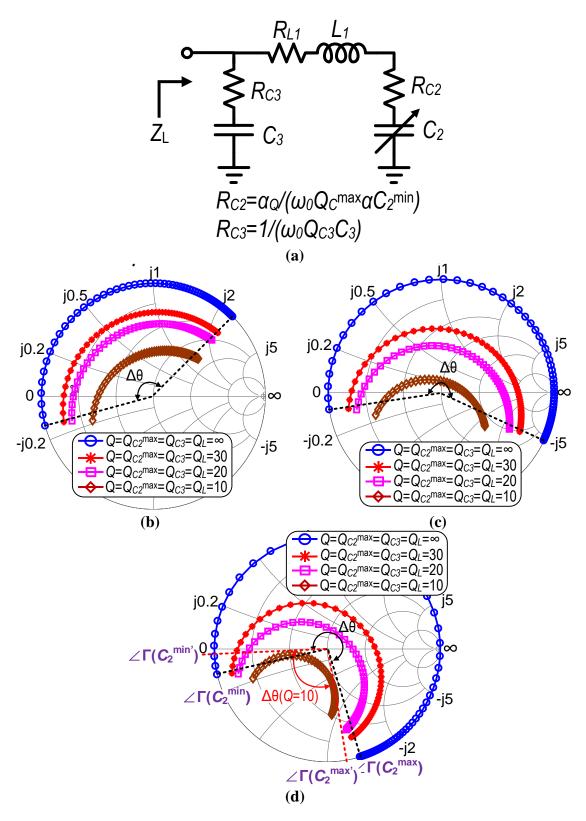

- Figure 4.29 (a) A lossy CLC-1 model, (b) the load impedance trajectory on Smith 117 chart with different quality factors for  $\alpha$ max=3 and  $\beta$ =1, (c)  $\beta$ =2 and (d)  $\beta$ =3.

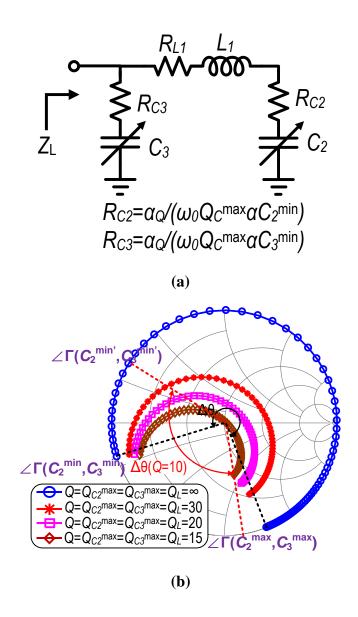

- Figure 4.30 (a) A lossy CLC-2 model and (b) the lossy CLC-2 load impedance 118 trajectory on Smith chart with the different quality factors for  $\alpha$ max=3 and  $\beta$ =1.

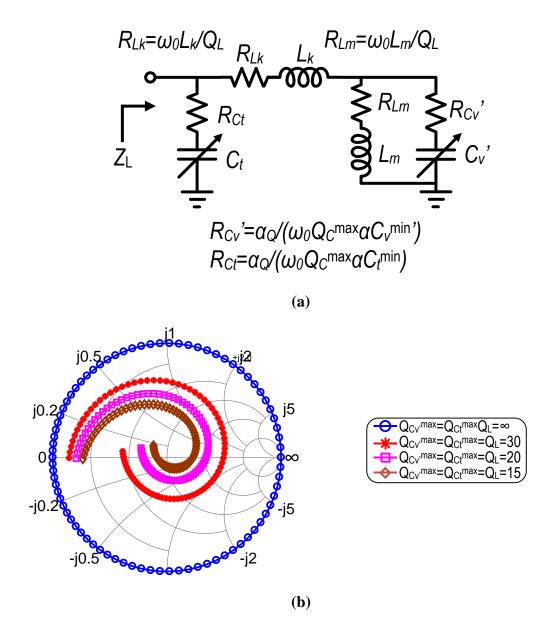

- Figure 4.31 (a) A lossy proposed transformer-based multi-resonance reflective 119 model and (b) the load impedance trajectory on Smith chart with the different quality factors for αmax=3.

#### **SUMMARY**

Millimeter-wave (mm-Wave) phased arrays have been widely used in numerous wireless systems to perform beam forming and spatial filtering that can enhance the equivalent isotropically radiated power (EIRP) for the transmitter (TX). As well as it can minimize the interferences and further increase signal-to-noise ratio (SNR) for the receiver (RX). Regarding the existing phased-array architectures, an mm-Wave transmitter includes several building blocks to perform the desired delivered power and phases for wireless communication.

Power amplifier (PA) is the most important building block. It needs to offer several advantages, e.g., high efficiency, broadband operation and high linearity. With the recent escalation of interest in 5G wireless communication technologies, mm-Wave transceivers at the 5G frequency bands (e.g., 28 GHz, 37 GHz, 39 GHz, and 60 GHz) have become an important topic in both academia and industry. Thus, PA design is a critical obstacle due to the challenges associated with implementing wideband, highly efficient and highly linear PAs at mm-Wave frequencies. However, there exists several fundamental challenges for mm-Wave PA in silicon due to the lower transistor cut-off frequency ( $f_{max}$ ) compared to compound III-V processes, lower breakdown voltage and lossy silicon substrate, which causes high design complexity and difficulty. In this dissertation, we present several PA design innovations to address the aforementioned challenges.

Additionally, phase shifter (PS) also plays a key role in a phased-array system, since it governs the beam forming quality and steering capabilities. A high-performance phase

shifter should achieve a low insertion loss, a wide phase shifting range, dense phase shift angles, and good input/output matching.

For PA design, first, an mm-Wave continuous-mode harmonically-tuned PA is proposed to provide an instantaneously broadband operation, high PA efficiency and an ultra-compact size at 28.5GHz. Based on the harmonically-tuned technique, a continuous-mode Class-F<sup>-1</sup> PA can be realized and present a power-added efficiency and saturated power (P<sub>sat</sub>). Moreover, we combine both continuous-mode Class-F and Class-F<sup>-1</sup> PA operation to realize a continuous-mode hybrid Class-F/F<sup>-1</sup> PA to provide a broader operation bandwidth and also maintain high PA efficiency. Importantly, these continuous-mode harmonically-tuned operation delivers output power and drain efficiency equivalent to that of the standard narrow band Class-F and Class-F<sup>-1</sup> PA operations.

Secondly, an mm-Wave PA with a power combiner-type N-/P-MOS amplitude-to-phase (AM-PM) distortion cancellation scheme is proposed to provide a <1° AM-PM distortion and maintain high PAE at V-band range. Although multiple AM-PM distortion cancellation schemes have been reported, they usually require additional elements or circuits. However, elements or circuits induce extra losses to downgrade the PA performance even they maintain high PA linearity. Our proposed technique not only improve PA linearity but provide high PAE.

For phase shifter design, we present an mm-Wave fully differential transformer-based passive reflection-type phase shifter (RTPS) capable of performing full span 360° continuous phase shift from 58 to 64 GHz. It consists of two transformer-based 90° couplers and two transformer-based multi-resonance reflective loads to provide 360° phase

shift with low loss and ultra-compact chip size. Our proof-of-concept design is implemented in a standard 130-nm BiCMOS process with a core area of 480μm×340μm. It achieves a wide phase shifting range of 367° and a low insertion loss IL (3.7dB<|IL|<10.2dB) at62 GHz and maintains a full span 360° phase shifting range from58 to 64 GHz. Moreover, it supports360° phase shifting with a constant IL, i.e., |IL|=10, 11, 12 dB, at an IL variation of less than 0.74 dB at 62 GHz. To the best of our knowledge, this design achieves a first-ever full span 360° phase shifting (up to 367°),the lowest IL, the smallest IL variation, and the best figure-of-merit of 37.1°/dB among reported 60 GHz fully integrated RTPS in silicon.

#### CHAPTER 1. INTRODUCTION

With the rapid growth of the fifth generation (5G) communication, multiple non-contiguous millimeter-wave (mm-Wave) frequency bands (e.g., 24, 28, 37 and 39 GHz) are being allocated in different countries and regions. For example, the 5G frequency spectrums are allocated as, 27.5-28.35 GHz and 37-40 GHz (USA), 24.25-27.5 GHz and 31.8-33.4 GHz (Europe), and 24.25-27.5 GHz and 37-42.5 GHz (China). The frequency bands will extend to V-band (40-75 GHz) or even higher in the future. An ultra-broadband mm-Wave TX that can cover all these potential 5G bands will enable frequency diversity and international roaming as well as supporting wideband Multiple-Input-Multiple-Output (MIMO) wireless technology with ultra-compact elements by eliminating the need for assembling several single-band TXs. Thus, regarding future commercial the 5G products, it can release design difficulty and save manufacture cost significantly for targeting multiple frequency bands.

PA plays a crucial role in TX for mobile devices since it consumes a majority of the DC power, shortening usage/standby times and transmitting ranges. Thus, the efficiency of a mm-Wave PA is the key metric to perform. Additionally, 5G mm-Wave systems are expected to support wideband spectrum-efficient complex modulation schemes (e.g., 64- and 256-QAM) to achieve Gb/s link throughput revolution. These complex modulation schemes, however, often come with high-density constellations that demand stringent linearity to provide higher spectral efficiency, i.e. large-signal AM-AM and AM-PM distortion, on the PAs. Thus, the 5G communication system can support large and fragmented spectrum, dynamic spectrum access, and short packet transmissions with

loose synchronization requirements. Therefore, in order to support future wideband MIMOs, desired mm-Wave silicon-based PA solutions should offer wide carrier bandwidth for multiple the future 5G frequency bands, high efficiency for longer usage/standby times, high linearity for complex modulation schemes, sufficient output power for required transmitting ranges, and compact size for cost reduction simultaneously [1]-[25].

Figure 1.1 shows continuous-wave (CW) performance comparisons with reported mm-Wave PAs in SiGe and CMOS process from 20 GHz to 50 GHz. According to [26], both SiGe and CMOS PAs exhibit upper performance envelopes for peak PAE vs. P<sub>sat</sub>, showing "device limited regime" in the low/medium P<sub>sat</sub> region determined by the intrinsic power device efficiency and "circuit/combiner limited regime" in the medium/high P<sub>sat</sub> region governed by the combiner efficiency. Thus, these upper performance envelopes are big challenges for PA designers.

Figure 1.2 shows the plot of average PAE (PAE<sub>avg</sub>) vs average output power ( $P_{avg}$ ) for SiGe and CMOS PA in modulation with 64QAM from 20 GHz to 50 GHz. There are two major groups of  $P_{avg}$ , e.g.,  $P_{avg}$ =5-7dBm with PAE<sub>avg</sub>=~10% and  $P_{avg}$ =9-11dBm PAE<sub>avg</sub>=~10-20% respectively. Note that this plot does not distinguish modulation speeds (i.e., data-rate or symbol-rate) of the reported PA designs. For future 5G wireless communication, the proposed data-rate is at least 0.8 Gb/s at mm-Wave frequency bands.

Basic linear PAs, e.g., Class-A and Class-AB PAs, offer design simplicity and good linearity [27]-[31]. However, their simple "all-short" output harmonic terminations fundamentally limit the peak efficiency. On other hand, mm-Wave time-domain switching

PAs, e.g., Class-E PAs, show high peak efficiency but limited linearity [27][28][32]-[34]. They cannot support complex modulations without major digital pre-distortion (DPD) computation, while DPD at Gb/s usually requires substantial power and complexity for future 5G communication. To solve this classic efficiency-linearity challenge, there are multiple reported advanced PA architectures, such as Doherty PAs [7][31] and Outphasing PAs [2][27]. They can boost the back-off efficiency and maintain high linearity for mm-Wave 5G applications. However, the former often requires large area, while the latter also demand extensive DPD to increase design and implementation complexity.

According to the reported PA design recently, a promising alternative solution is the overdriven linear PAs with harmonically-tuned impedance terminations to address the classic efficiency-linearity challenge. Multiple recent designs show that Class-AB, Class-J, Class-F and inverse Class-F (Class-F<sup>-1</sup>) harmonically-tuned terminations on linear PAs can boost their peak efficiency and still preserve high linearity. The reported harmonicallytuned terminations usually consist manifold L-C resonant tanks to provide the desired harmonic impedances. However, these designs either have limited bandwidth due to narrowband harmonic terminations, require area-consuming passive networks, constraining their use in broadband MIMO systems, or increase design and implementation complexity [35]-[39]. To address these PA issues, we present continuous-mode harmonically-tuned PA to achieve wide bandwidth, high efficiency and compact formfactor together, offering future 5G PA solutions. Moreover, we proposed a V-band PA employing our NMOS/PMOS AM-PM distortion cancellation technique to further improve the linearity. Also, this PA design includes a series-parallel distributed-active transformer (DAT), performing low loss and proving the PA optimal load.

The applications of mm-Wave phased array systems include ultra-high data-rate transmission, emerging 5G communication, and radar and imaging systems [127]-[141]. Phase shifters (PS) play a key role in a phased array system, since it governs the beam forming quality and steering capabilities. A high-performance phase shifter should achieve a low insertion loss (IL), a wide phase shifting range, dense phase shift angles, and good input/output matching. We present a millimeter-wave fully differential transformer-based passive reflection-type phase shifter (RTPS) capable of performing full span 360° continuous phase shift from 58GHz to 64GHz.

Taking full advantages of the increasing transistor speed, my Ph.D. research focuses on exploring new silicon-based PA topologies and circuit techniques to achieve state-of-the-art performance for various emerging applications at mm-Wave. Through my Ph.D. career at Georgia Tech GEMS Lab, I did research on the design challenges in mm-Wave PA, and devoted my research efforts in implementing energy efficient, broadband and high linearity using advanced silicon technologies. The major contributions of my dissertation are listed below.

- We propose a mm-Wave silicon-based harmonically-tuned PA designs by using continuous-mode Class-F<sup>-1</sup> and continuous-mode hybrid Class-F/F<sup>-1</sup> PA operations at 5G bands.

- We propose a mm-Wave silicon-based V-band PA with the proposed N-/P-MOS AM-PM distortion cancellation scheme to achieve <1° AM-PM distortion and PAE of 35%.

- 3. We propose a millimeter-wave fully differential transformer-based passive

reflection-type phase shifter which performs full span 360° continuous phase shift from 58GHz to 64GHz with low insertion loss or constant insertion loss.

The remainder of this dissertation is organized as follows.

In this dissertation, the design details of the mm-Wave silicon-based harmonically-tuned Continuous-mode PA designs are discussed in Chapter 2. The proposed power-combining-based NMOS/PMOS AM-PM distortion cancellation scheme are demonstrated in Chapter 3. Later, Chapter 4 shows the design and implementation of the proposed RTPS. Finally, Chapter 5 summarizes this dissertation.

Figure 1.1 - PAE comparison with state-of-the-art mm-Wave silicon-based PAs in (a) SiGe and (b) CMOS process (20-50 GHz) [26].

Figure 1.2 – Average Efficiency vs Average Output Power for SiGe and CMOS PAs in modulation with 64QAM (20-50 GHz) [26].

#### CHAPTER 2. HARMONICALLY-TUNED PA OPERATION

The basic continuous-mode PA operation and our proposed continuous-mode harmonically-tuned are discussed in this chapter. The implementation and measurement results are also presented.

#### 2.1. Introduction

The device output voltage and current waveforms are essential for optimizing the device-level PA performance, e.g., output power, efficiency, or linearity. A harmonically-tuned PA with finite harmonic terminations (e.g., only the fundamental, 2nd-, and 3rd-order harmonics) is designed to achieve high efficiency by loading the proper terminations at its fundamental and harmonic frequencies. In the time domain, proper harmonic terminations shape the voltage and current waveforms on the power transistor drain/collector terminal to minimize the overlap between the current and voltage, boosting the efficiency. In practice, higher order harmonics (>3rd-order) provide limited contributions and are difficult to generate and terminate [40]-[46].

#### 2.1.1. Conventional Class-F PA operation

The conventional Class-F PA output network provides high impedance terminations at odd harmonics and low impedance terminations at even harmonics [40]. Thus, the voltage waveform  $v_F$  on drain/collector terminal behaves as a square waveform and can be expressed (including DC-/1<sup>st</sup>-/3<sup>rd</sup>-term) as

$$v_F(\theta) = V_{DC} - v_{F1}\cos\theta + v_{F3}\cos3\theta, \tag{2-1}$$

$$v_{F1}/V_{DC} = 2/\sqrt{3}, v_{F3}/V_{DC} = 1/3\sqrt{3},$$

where  $V_{DC}$  represents the dc supply voltage, and  $V_{F,1}$  and  $V_{F,3}$  are the voltage swing at fundamental and 3<sup>rd</sup>-harmonic frequencies respectively. Furthermore, the device current behaves as a half-sine waveform (including DC/1<sup>st</sup>/2<sup>nd</sup> term) as

$$i_F(\theta) = I_{DC} + i_{F,1} \cos \theta + i_{F,2} \cos 2\theta,$$

(2-2)

$i_{F,1}/I_{DC} = \pi/2, i_{F,2}/I_{DC} = 2/3,$

where  $I_{DC}$  is the DC current, and  $I_{F,1}$  and  $I_{F,2}$  are the current swing at fundamental and  $2^{\text{nd}}$ -harmonic frequencies, respectively. The normalized time-domain current and voltage waveforms are shown in Figure 2.1 (i.e., the blue solid line represents the voltage and the red solid line represents current).

Figure 2.1 – Theoretical current and voltage waveforms composed of the fundamental, 2nd- and 3rd-harmonics for (a) conventional/continuous-mode Class-F and (b) conventional/continuous-mode Class-F<sup>-1</sup> operations.

## 2.1.2. Conventional Class-F<sup>-1</sup> PA operation

The conventional Class-F<sup>-1</sup> PA is a dual of the Class-F PA by exchanging the current and voltage waveforms. Namely, the conventional Class-F<sup>-1</sup> PA generates a half-sinusoidal voltage waveform and a square current waveform with high impedance for even order harmonic output impedance and low impedance for odd order harmonic output impedance. The voltage waveform  $v_{IF}$  can be written as

$$v_{IF}(\theta) = V_{DC} + v_{IF,1} \cos \theta + v_{IF,2} \cos 2\theta,$$

(2-3)

$$v_{IF,1}/V_{DC} = \sqrt{2}, v_{IF,2}/V_{DC} = 1/2,$$

where  $V_{IF,1}$  and  $V_{IF,2}$  are the voltage swing at fundamental and 3<sup>rd</sup>-order harmonic frequencies, respectively. Thus, the current on a transistor behaves as a square waveform and it can be expressed as

$$i_{IF}(\theta) = I_{DC} - i_{IF,1}\cos\theta + i_{IF,3}\cos3\theta \tag{2-4}$$

$$i_{IF,1}/I_{DC} = 1.162, i_{IF,3}/I_{DC} = 0.162,$$

where  $I_{IF,1}$  and  $I_{IF,3}$  are the current swing at fundamental and 3<sup>rd</sup>-order harmonic frequencies, respectively [44]. The normalized time-domain current and voltage waveforms are shown in Figure 2.1(b) (i.e., the blue solid line represents voltage and the red solid line represents current respectively).

Moreover, the PA efficiency  $\eta$ , (i.e., drain efficiency for MOSFET and collector for Bipolar) can be expressed as,

$$\eta = \frac{P_{delivery}}{P_{DC}} = \frac{1}{2} \left( \frac{v_{F,1} \text{ or } v_{IF,1}}{V_{DD}} \right) \left( \frac{i_{F,1} \text{ or } i_{IF,1}}{I_{DC}} \right) = \eta_{\text{max}} \left( 1 - \frac{V_k}{V_{DC}} \right), \tag{2-5}$$

where  $\eta_{\text{max}}$  represents the maximum PA efficiency,  $V_k$  is the knee voltage which represents a minimum limit on the swing across the transistor. An ideal Class-F PA with fundamental,  $2^{\text{nd}}$ -and  $3^{\text{rd}}$ - harmonics can achieve an  $\eta_{\text{max}}$  of 90.6 % while a Class F<sup>-1</sup> PA can achieve an  $\eta_{\text{max}}$  of 81.6 %, respectively [27]. To maintain high PA efficiency, conventional Class-F and Class-F<sup>-1</sup> PA output networks need to provide multiple accurate harmonic impedance terminations, resulting in narrow carrier bandwidths [27][37][38].

Figure 2.2 – Fundamental, 2nd- and 3rd-harmonic load impedances for (a) continuous-mode Class-F and (b) continuous-mode Class-F-1 PA operations.

## 2.1.3. Continuous-mode Class-F and Class-F-1 PA

Continuous-mode harmonically tuned PAs generalize the optimum harmonic termination conditions and thus substantially expand the carrier frequency range. In reference [41], the author introduces a continuous-mode PA, alleviating the precise harmonic requirements of the conventional ones by offering multiple impedance terminations that can be dynamically distributed over the desired operation bandwidth, while preserving the desired output power and efficiency. Given by [41], for the continuous-mode Class-F PA operation, the voltage waveform in (2-1) is extended by multiplying an additional defining term, shown as

$$v_{CF}(\theta) = (V_{DC} - v_{F1}\cos\theta + v_{F3}\cos3\theta) \times (1 - \gamma\sin\theta). \tag{2-6}$$

The first bracket of (2-6) is the voltage waveform formulation for the conventional Class-F as expressed in (2-1) with  $\gamma$ =0. The last bracket in (6) is a defining term  $(1-\gamma\sin\theta)$  that performs a new design space. Thus, the parameter  $\gamma$  varies between -1 and 1 (i.e., -1 $\leq \gamma \leq 1$ ), forming a family of voltage waveforms that provide multiple solutions Figure 2.2(a), gray dot lines for  $\gamma$ <0 and purple dash lines for  $\gamma$ >0) to maintain constant power and efficiency. As result, each value of corresponding to the particular PA output fundamental,  $2^{\text{nd}}$ - and  $3^{\text{rd}}$ -order harmonic impedances can be expressed as [44],

$$Z_{CF,1} = R_{opt} \frac{2}{\sqrt{3}} + j\gamma R_{opt}, Z_{CF,2} = jR_{opt} \frac{7\sqrt{3}\pi}{24} \gamma, Z_{CF,3} = \infty,$$

(2-7)

where  $R_{opt}$  is the optimum impedance of the standard Class-B operation with all harmonics short-circuited. The impedance trajectories can be presented on the Smith chart (Figure 2.2a).

On other hand, for the continuous-mode Class-F<sup>-1</sup> PA operation, the current waveform in (2-2) can be also extended by multiplying an additional defining term, expressed as

$$i_{CIF}(\theta) = (I_{DC} - i_{IF,1}\cos\theta + i_{IF,3}\cos3\theta) \times (1 - \xi\sin\theta). \tag{8}$$

The first bracket of (2-8) is the conventional voltage waveform formulation for the conventional Class-F<sup>-1</sup> operation as expressed in (2-2) with  $\xi$ =0. The last bracket of (2-8) is also a defining term  $(1-\xi\sin\theta)$ , offering a new design space. The parameter  $\xi$  varies between -1 and 1 (i.e., -1 $\leq$  $\xi$  $\leq$ 1), forming a family of current waveforms that provide multiple solutions Figure 2.2(b), magenta dot lines for  $\xi$ <0 and dark-yellow dash lines for  $\xi$ >0) to maintain constant delivery power and efficiency. Each value of corresponding to the continuous-mode PA output fundamental, 2<sup>nd</sup>-order and 3<sup>rd</sup>-order harmonic impedances can be expressed as the following [44],

$$Y_{CIF,1} = G_{opt} \sqrt{2} i_{IF,1} + j G_{opt} \sqrt{2} i_{DC} \xi, \tag{9}$$

$$Y_{CIF,2} = jG_{opt} 2(i_{IF,1} + i_{IF,3})\xi, Y_{CIF,3} = \infty,$$

where  $G_{opt}$  (=1/ $R_{opt}$ ) is as the optimum admittance. The impedance trajectories can be shown on the Smith chart (Figure 2.2b). These continuous-mode PA operations can be realized over the desired operation bandwidth by applying the required harmonic

impedances for the different  $\gamma$  or  $\xi$  values. Additionally, these continuous-mode PAs can deliver output power and efficiency almost equivalent to that of the conventional PAs [41]- [44].

The PA load impeance (e.g.,  $Z_L$ ) behaviours for different PA operation are summarized in Table II. It is obvious that the coninuoious-mode PA operation (i.e.,  $\gamma \neq 0$  and  $\xi \neq 0$ .) causes fundamental impedance (e.g., Capacitive/Inductive or Inductive/Capacitive) and  $2^{nd}$ -harmonic impedance (e.g., Inductive/Capacitive or Capacitive/Inductive) out of phase. The  $3^{rd}$ -harmonic impedances stay high or low.

**Table 2.1 – PA Load Impedance Behaviors for Different Operations**

| Operation            |             | Fundamental<br>Impedance              |                         | 2 <sup>nd</sup> harmonic<br>Impedance |                         | 3 <sup>rd</sup> harmonic<br>Impedance |         |

|----------------------|-------------|---------------------------------------|-------------------------|---------------------------------------|-------------------------|---------------------------------------|---------|

|                      |             | $ Z_L $                               | $Z_{L}$                 | $ Z_L $                               | $Z_{L}$                 | $ Z_L $                               | $Z_{L}$ |

| Class-F              | <b>γ</b> =0 | $R_{opt,F}$                           | 0                       | Low                                   | 0                       | High                                  | 0       |

| Class-F-1            | ξ=0         | $R_{opt,IF}$                          | 0                       | High                                  | 0                       | Low                                   | 0       |

| Continuous-Class-F   | γ>0<br>γ<0  | $R_{\text{opt,F}}$ $R_{\text{opt,F}}$ | Capacitive<br>Inductive | Low<br>Low                            | Inductive<br>Capacitive | High                                  | either  |

| Continuous-Class-F-1 | ξ>0<br>ξ<0  | $R_{opt,IF}$ $R_{opt,IF}$             | Inductive<br>Capacitive | High<br>High                          | Capacitive Inductive    | Low                                   | either  |

#### 2.1.4. Proposed Continuous-mode PA Output Network

Most existing continuous-mode and harmonically-tuned PA output networks require multiple passive components and transmission lines for multi-resonance tuning, inevitably increasing the network complexity, losses, and size. Our PA output network exploits and uses parasitic elements in one on-chip transformer to achieve continuous-mode harmonic tuning at both differentials- and common-mode with substantial network simplification and area-saving (Figure 2.3).

#### 2.2.1. Continuous-Mode Class-F<sup>-1</sup> PA Output Network

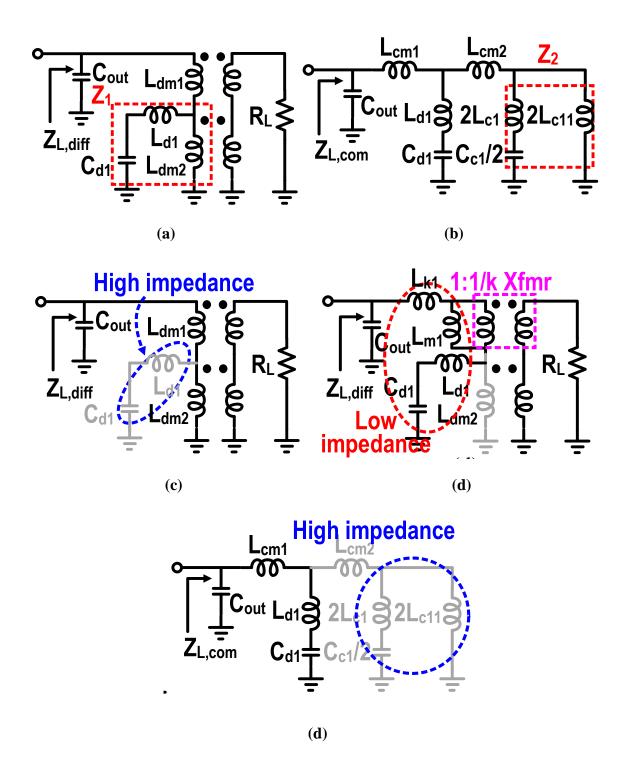

The proposed differential continuous-mode Class-F<sup>-1</sup> PA output network is as shown in Figure 2.3(a). It consists of one 1:1 transformer and three harmonic tuning capacitors ( $2\times C_{d1}$  and  $C_{c1}$ ). This structure utilizes two symmetrically embedded branches  $L_{d1}$  inside the transformer for the  $3^{rd}$ -order harmonic impedance tuning in differential-mode, and two extended branches  $L_{c1}$  and  $L_{c11}$  for the  $2^{nd}$ -order harmonic impedance tuning in common-mode respectively. Figure 2.4 shows the simplified differential and common-mode half-circuits at the fundamental,  $2^{nd}$ - and  $3^{rd}$ -order harmonic frequencies respectively.  $L_{dm1}/L_{cm1}$  and  $L_{dm2}/L_{cm2}$  are the differential/common-mode half-circuit inductances of the transformer, and the output leads are absorbed into the transformer secondary coil (Figure 2.4a-b). Moreover,  $L_{m1}$  and  $L_{k1}$  are the magnetizing and leakage inductances of the transformer in the differential-mode half-circuit (Figure 2.4d).

In the differential mode, the center-tap of the transformer is virtual ground, so  $L_{c1}/L_{c11}$  and  $C_{c1}$  do not affect the fundamental and  $3^{rd}$ -order harmonic impedances.  $C_{d1}$ - $L_{d1}$ - $L_{dm2}$

form a multi-resonance tank  $Z_1$  with high-frequency resonance. At the fundamental frequency, the series network  $C_{d1}$ - $L_{d1}$  behaves like a small capacitor, resulting in a high impedance to the transformer. Thus, the transformer performs matching with the PA output capacitance  $C_{out}$  and provides the desired fundamental load impedance to the PA (Figure 2.4c). At the  $3^{rd}$ -order harmonic frequency,  $C_{d1}$ - $L_{d1}$  is slightly below its series resonance, which shorts out  $L_{dm2}$  and forms a series resonance of  $C_{d1}$ - $L_{d1}$ - $L_{m1}$ - $L_{k1}$  to provide a desired low impedance. In the common-mode half-circuit, the network of  $C_{c1}/2$ ,  $2 \times L_{c1}$ , and  $2 \times L_{c11}$  forms a multi-resonance tank  $Z_2$  (Figure 2.4b). At the  $2^{nd}$ -order harmonic frequency,  $Z_2$  provides a high impedance, resulting in the remaining series tank of  $C_{d1}$ - $L_{d1}$  as a capacitor. Thus, the  $2^{nd}$ -order harmonic impedance is dominated by  $C_{out}$ ,  $L_{cm1}$  and the effective capacitance due to series  $C_{d1}$ - $L_{d1}$ , which achieve desired  $2^{nd}$ -order harmonic impedance (Figure 2.4e).

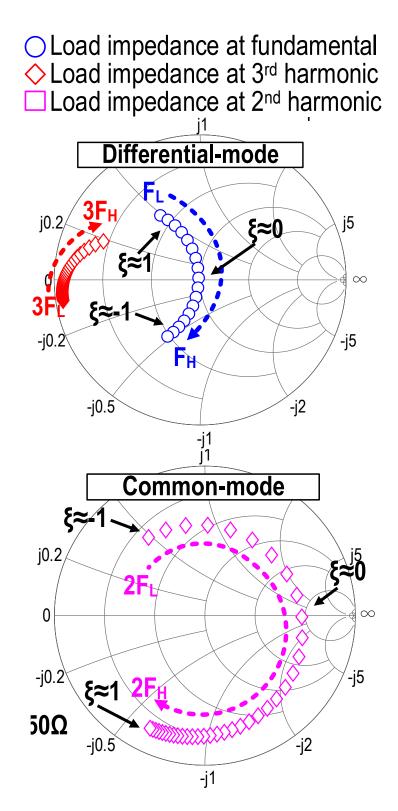

The trajectories of half-circuit load impedance at fundamental,  $2^{nd}$ - and  $3^{rd}$ -order harmonics with the PA output capacitance  $C_{out}$  are shown on the Smith Chart in Figure 2.5. The fundamental load impedance is mostly inductive for lower frequency  $(0 \le \xi \le 1)$  and capacitive for higher frequency  $(-1 \le \xi \le 0)$ , and vice versa for the  $2^{nd}$ -order harmonic impedance. The fundamental and the  $2^{nd}$ -order harmonic impedances of the upper operation bandwidth follow the constant conductance circles, while the  $3^{rd}$ -order-harmonic impedance is kept low. These aspects verify that the PA achieves continuous-mode Class- $F^{-1}$  harmonic terminations for its fundamental,  $2^{nd}$ -, and  $3^{rd}$ -order impedances [41]-[44].

Figure 2.3 - EM and schematic of (a) continuous-mode Class-F<sup>-1</sup> PA and (b) continuous-mode hybrid Class-F/-F<sup>-1</sup> PA.

Figure 2.4 – Simplified of (a) differential-mode and (b) common-mode half circuits of the continuous-mode Class- $F^{-1}$ PA output network at (c) the fundamental frequency (d) the 3rd-harmonic of lower band, and (e) the 2nd-harmonic frequencies, respectively.

Figure 2.5 – Trajectories of the half-circuit load impedance at fundamental,  $2^{nd}$ - and  $3^{rd}$ -order harmonic frequencies (characteristic impedance  $Z_0$  =50 $\Omega$ ).

## 2.2.2. Continuous-mode Hybrid Class-F/F-1 PA Output Network

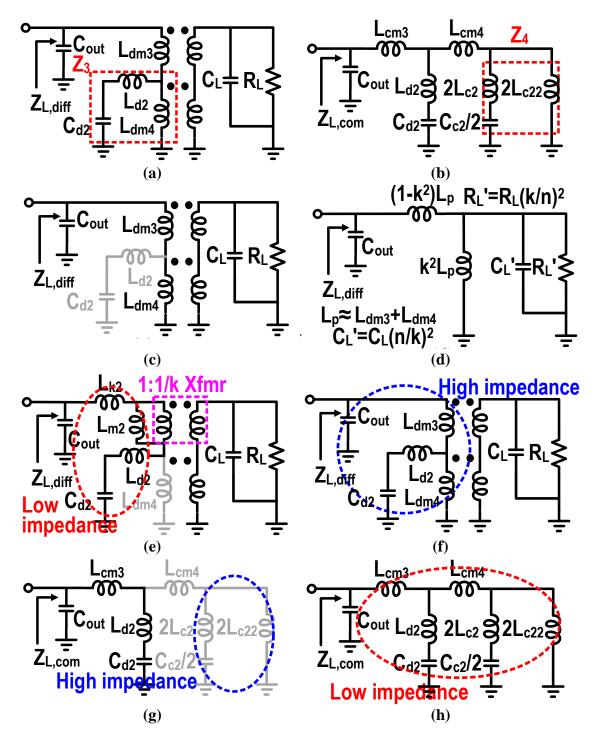

This continuous-mode hybrid Class-F/F<sup>-1</sup> PA output network combines continuous-mode hybrid Class-F and F<sup>-1</sup> PA operations together to further extend the bandwidth. Compared to the continuous-mode Class-F<sup>-1</sup> PA output network, the two matching capacitors (i.e.,  $2\times C_L$ ) can facilitate the fundamental operation bandwidth extension, and the longer branches  $L_{c2}$  can provide a larger inductance for  $2^{nd}$ -order harmonic impedance, as shown in Figure 2.3(b). It also consists of one 1:1 transformer, three harmonic tuning capacitors (i.e.,  $2\times C_{d2}$  and  $C_{c2}$ ), and two matching capacitors (i.e.,  $2\times C_L$ ) to realize hybrid Class-F and Class-F<sup>-1</sup> operations at the lower ( $\omega_L$ ) and higher frequency ( $\omega_H$ ) bands, respectively, as shown in Figure 2.3(b). The PA output harmonic termination network is explained in Figure 2.6(a)-(h). Here,  $L_{dm3}/L_{cm3}$  and  $L_{dm4}/L_{cm4}$  represent the differential-/common-mode half-circuit inductances of the transformer, and the output leads are absorbed into the secondary coil.  $C_{d2}$ - $L_{d2}$ - $L_{dm4}$  forms a multi-resonance tank  $Z_3$  (Figure 2.6a). In the common-mode half-circuit, the network of  $C_{c2}$ /2,  $2\times L_{c2}$ , and  $2\times L_{c22}$  forms a multi-resonance tank  $Z_4$  (Figure 2.6b).

At fundamental operation frequencies ( $\omega_L \le \omega \le \omega_H$ ), the series network  $C_{d2}$ - $L_{d2}$  behaves as a small capacitor (Figure 2.6c) to provide a high impedance. So, this high impedance branch can be ignored. Thus,  $Z_{L,diff}$  can be converted to a simplified model as shown in Figure 2.6(d).  $k^2 \times L_p$  and  $(1-k^2) \times L_p$  are the magnetization and leakage inductances respectively of the transformer in the half-circuit differential-mode (Figure 2.6d). The equivalent inductance  $L_p$  is roughly equal to  $L_{dm3}$  and  $L_{dm4}$ . Thus, Figure 2.6(d) forms the

matching network with the PA output capacitance C<sub>out</sub> and provides PA the desired fundamental load impedance.

At the  $3^{rd}$ -order harmonic of the higher band ( $\omega$ =3 $\omega_H$ ), the series network  $C_{d2}$ -L $_{d2}$  impedance is slightly below its series resonance, which shorts out L $_{dm4}$  and forms a series resonance of  $C_{d2}$ -L $_{d2}$ -L $_{m3}$ -L $_{k2}$  to offer a low load impedance (Figure 2.6e). In this case, L $_{m2}$  and L $_{k2}$  represent the magnetization and leakage inductances of coil L $_{dm3}$  of the transformer in the half-circuit differential-mode. Also, at the  $3^{rd}$ -order harmonic of the lower band ( $\omega$ =3 $\omega_L$ ), Z $_{L,diff}$  sees a high impedance by L $_{dm3}$  and Z $_3$  in parallel with  $C_{out}$ . At the 2 $^{nd}$ -order harmonic of the higher band ( $\omega$ =2 $\omega_H$ ), Z $_4$  provides a high impedance, while the remaining  $C_{d2}$ -L $_{d2}$  series tank behaves as a capacitor (Figure 2.6g). Therefore, the 2 $^{nd}$ -order harmonic impedance Z $_{L,com}$  is dominated by  $C_{out}$ , L $_{cm3}$  and the effective capacitance due to series  $C_{d2}$ -L $_{d2}$  branch, achieving the desired continuous-mode 2 $^{nd}$ -order harmonic impedance.

Additionally, at the  $2^{nd}$ -order harmonic of the lower band ( $\omega$ = $2\omega_L$ ),  $Z_2$  becomes inductive. Moreover, the series network  $C_{d2}$ - $L_{d2}$  remains capacitive. Therefore,  $Z_{L,com}$  can present a low overall impedance. The trajectories of the half-circuit load impedance at fundamental,  $2^{nd}$ - and  $3^{rd}$ -order harmonics with the absorbed PA output capacitance  $C_{out}$  are shown on the Smith Chart in Figure 2.7(a).

The fundamental load impedance  $(\omega_L \le \omega \le \omega_H)$  is inductive, while the  $2^{nd}$ -order harmonic load impedances  $(\omega = 2\omega_L)$  or  $\omega = 2\omega_H$  are capacitive and provide  $-1 \le \gamma < 0$  for continuous-mode class-F PA operation and  $-1 \le \xi < 0$  for continuous-mode Class-F<sup>-1</sup> PA operation, respectively. Compared with the fundamental, the  $3^{rd}$ -oder harmonic load impedance is low for lower band  $(\omega = 3\omega_L)$  while it is high for higher band  $(\omega = 3\omega_H)$ . The

load impedance trajectories demonstrate the continuous-mode hybrid Class-F/F<sup>-1</sup> PA. The impedance responses of each harmonic over frequency are shown in Figure 2.7(b).

The design procedure of the PA output network is starting from building a  $4^{th}$ -order matching network using passive lumped elements (e.g., inductors and capacitors) at fundamental frequency, like Figure 2.6(d). The designed values of the passive lumped elements are depended on the load-pull simulation. For the harmonic-thing, the importance is that the required lumped inductors and capacitors are necessary arranged properly in the differential and common modes to realize the  $2^{nd}$ - and  $3^{rd}$ -order harmonic impedance terminations for the continuous-mode operation, respectively. Here, the values of the inductors and capacitors are determined by the continuous-mode design equations, as discussed in Section II. Then, a transformer with the routing traces and pads (i.e., GSGSG pads) is to replace the lumped elements. As a result, the transformer needs to be well optimized and simulated to determine the inductances and capacitances (e.g.,  $C_{c1}$ ,  $C_{c2}$ ,  $C_{d1}$ ,  $C_{d2}$ ,  $C_{d1}$ ,  $C_{d2}$ ,  $C_{d1}$ ,  $C_{d2}$ ,  $C_{d1}$ ,  $C_{d2}$ , and so on).

Figure 2.6 – Simplified half circuits of the (a) differential-mode, (b) common-mode of the continuous-mode hybrid Class-F/F<sup>-1</sup> PA output network at (c) the fundamental frequency ( $\omega_L \le \omega \le \omega_H$ ) and (d) the fundamental equivalent circuit, (e) the 3<sup>rd</sup>-order harmonic of lower band ( $\omega = 3\omega_L$ ), (f) the 3<sup>rd</sup>-order harmonic of higher band ( $\omega = 3\omega_H$ ), (g) the 2<sup>nd</sup>-order harmonic of lower band ( $\omega = 2\omega_L$ ), and (h) the 2<sup>nd</sup>-order harmonic of higher band ( $\omega = 2\omega_H$ ).

Figure 2.7 – (a) Trajectories of half-circuit load impedance at fundamental,  $2^{nd}$ -and  $3^{rd}$ -order harmonic frequencies ( $Z_0 = 50\Omega$ ), and (b) impedance response.

### 2.1.5. Continuous-Mode Harmonically-Tuned PA Implementation

## 2.3.1. Design 1: A Two-Stage Continuous-mode Class-F<sup>-1</sup> PA

Figure 2.8(a) shows the schematic of the two-stage continuous-mode Class-F<sup>-1</sup>PA design. It is composed of a driver (DR) stage and a PA stage followed by the proposed differential transformer-based harmonically-tuned PA output network, implemented in GlobalFoundries 0.13 µm SiGe BiCMOS process. The transformer-based harmonicallytuned PA output network has been fully analyzed in the previous section. The transistor size of DR (i.e.,  $Q_1$  and  $Q_2$ ) is 21  $\mu$ m/120 nm and the transistor size of PA (i.e.,  $Q_3$  and  $Q_4$ ) is 32  $\mu$ m/120 nm, respectively. Two series input resistors R<sub>b</sub> are 10  $\Omega$  for both DR and PA stages to improve stability. Both PA and DR stages utilize neutralization capacitors  $(C_{N DR}=30 \text{ fF} \text{ and } C_{N PA}=40 \text{ fF})$  to improve power gain, reverse isolation and stability. The input and inter-stage matching networks are realized by two 1-to-1 transformers respectively, and two input capacitors (C<sub>in1</sub>=128 fF) and two inter-stage capacitors (C<sub>int</sub>=55 fF). The DR stage is biased (V<sub>B</sub> DR) at 0.84 V and DC supply voltage (V<sub>CC</sub> DR) is 0.9 V, and the PA stage is biased (V<sub>B PA</sub>) at 0.83 V and DC supply voltage (V<sub>CC PA</sub>) is 1.9 V, respectively. To enhance PA linearity, a harmonic trap network (i.e.,  $R_{s1}=R_{s11}=25~\Omega$  and  $C_{s1}=C_{s11}=200$  fF) is added at the PA input to provide a low 2<sup>nd</sup>-order harmonic source impedance. The DC and peak current of the PA stage are 16 mA and 48 mA, respectively.

## 2.3.2. Design 2: A One-Stage Continuous-mode Class-F/F<sup>-1</sup> PA

Figure 2.8(b) shows the schematic of the one-stage differential hybrid continuous-mode Class-F/F<sup>-1</sup> PA design. It is composed of only the PA stage followed by the proposed differential transformer-based PA output network, implemented in a Globalfoundries 45nm

CMOS SOI process. The PA is realized using a cascode topology with identical sizes  $(W/L=6\times30~\mu\text{m}/40~\text{nm})$  for  $M_1$ ,  $M_2$ ,  $M_3$ , and  $M_4$  that are biased at  $V_G=0.3~\text{V}$ ,  $V_{cas}=1.3~\text{V}$ , and  $V_{DD}=2~\text{V}$ . The capacitive neutralization scheme  $(C_n=55~\text{fF})$  is used for the bottom transistor pair  $(M_1/M_2)$ . The input matching network is composed of a 1:1 transformer with parallel capacitors  $C_{in}=160~\text{fF}$  and a parallel resistor  $R_g=170~\Omega$ . The DC and peak current of the PA stage is 24 mA and 65/70/68~mA at 28/37/39~GHz, respectively.

### 2.3.3. Design 3: A Two-Stage Continuous-mode Class-F/F<sup>-1</sup> PA

Figure 2.8(c) shows the schematic of the two-stage differential hybrid continuous-mode Class-F/F<sup>-1</sup> PA design, consisting of a DR stage and a PA stage. This design is an extended version of the one-stage differential hybrid continuous-mode Class-F/F<sup>-1</sup> PA. Thus, both designs cooperate the identical continuous-mode hybrid Class-F/F<sup>-1</sup> PA output networks. The DR stage is realized using a CS topology with identical sizes (W/L=6×30  $\mu$ m/40 nm) for M<sub>5</sub> and M<sub>6</sub>. It is biased at V<sub>G\_DR</sub>=0.32 V, and V<sub>DD\_DR</sub>=0.8 V. In addition, the PA stage is also realized using a cascode topology with identical sizes (W/L=6×30  $\mu$ m/40 nm) for M<sub>7</sub>, M<sub>8</sub>, M<sub>9</sub>, and M<sub>10</sub> that are biased at V<sub>G\_PA</sub>=0.32 V, V<sub>cas\_PA</sub>=1.4 V, and V<sub>DD\_PA</sub>=2 V. The neutralization capacitors (C<sub>n\_DR</sub>) for DR stage are 55 fF and the neutralization capacitors (C<sub>n\_PA</sub>) for PA stage are 55 fF, respectively. The input and interstage matching networks of this two-stage PA design are also realized by two 1:1 transformer, and two input capacitors (C<sub>in2</sub>=140 fF). The DC and peak current of the PA stage is 25 mA and 70/80/87 mA at 28/37/39 GHz, respectively.

Figure 2.8 – Schematic of (a) two-stage continuous-mode Class-F<sup>-1</sup> PA, (b) one- and (c) two-stage continuous-mode hybrid Class-F/F<sup>-1</sup> PAs.

#### 2.1.6. Measurement Results

## 2.4.1. Design 1: A Two-Stage Continuous-Mode Class-F-1 PA

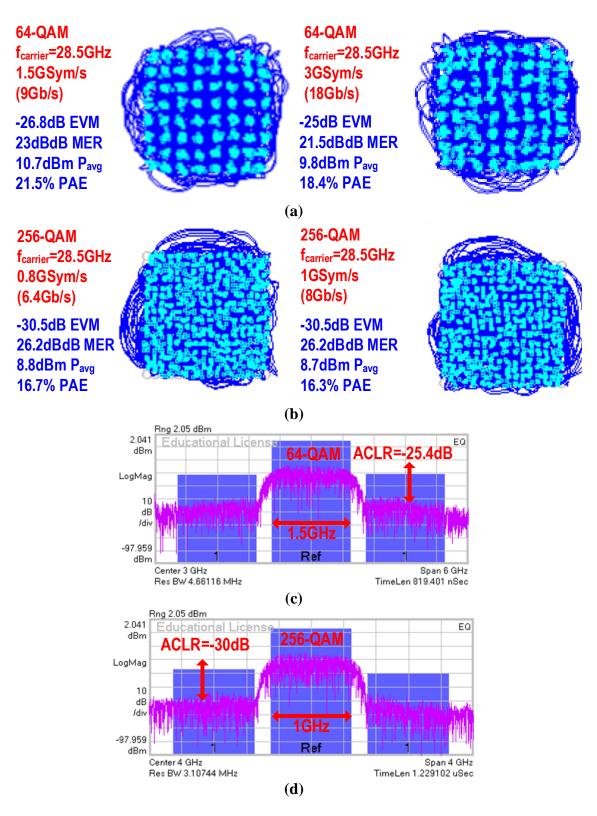

The first PA design occupies a 0.91×0.32 mm<sup>2</sup> core area excluding pads (Figure 2.9a). All designs are measured by direct probing. The CW large-signal and small-signal S-parameter measurements are shown in Figure 2.10. At 28.5 GHz, this PA achieves P<sub>sat</sub> of 17 dBm and P<sub>1dB</sub> of 15.2 dBm, the power gain (G<sub>p</sub>) of 20 dB and peak PAE (PAE<sub>max</sub>) of 43.5 % (Figure 2.10a). Figure 2.10(c) shows 20.3 dB of peak S<sub>21</sub> for the measured smallsignal S-parament. The measured P<sub>sat</sub> is from 16.4 to 17.4 dBm from 19 to 29.5 GHz, achieving a 43.3 % P<sub>sat</sub> 1-dB (BW<sub>1dB</sub>) bandwidth (Figure 2.10b). The measured PAE includes the loss of the DR stage, PA stage and the output network. This PA is first measured using 64-QAM signals at 1.5 GSym/s (9 Gb/s) and 3 GSym/s (18 Gb/s) at the carrier frequency (f<sub>carrier</sub>) of 28.5 GHz (Figure 2.11a). Without DPD, the measured EVM is below <-25 dB for all data rates. At 3 GSym/s, the EVM is -25 dB with average output power (P<sub>avg</sub>) of 9.8 dBm and average PAE (PAE<sub>avg</sub>) of 18.4 %. Next, this PA is measured using 256-QAM signals at 0.8 GSym/s (6.4 Gb/s) and 1GSym/s (8 Gb/s) at f<sub>carrier</sub> of 28.5 GHz (Figure 2.11b). The EVM is kept below -30 dB for all data rates. At 1 GSym/s, the EVM is -30 dB with P<sub>avg</sub> of 8.7 dBm and PAE<sub>avg</sub> of 16.3 %. Noted that the roll-off factor  $(\alpha)$  of the raised-cosine shaped filter is 0.35, the same setting as the following modulation measurements.

Figure 2.9 – Chip microphotograph of two-stage continuous-mode Class-F-1 PA

Figure 2.10 - (a) measured CW large-signal performance at 28.5 GHz, (b) measured CW large-signal performance vs. frequency and (c) measured small-signal S-parameter of two-stage continuous-mode Class-F-1 PA.

Figure 2.11 – (a) 64-QAM constellation, (b) 256-QAM constellation, (c) 64-QAM spectrum and (d) 256-QAM spectrum at f<sub>carrier</sub> of 28.5 GHz of Design 3.

## 2.4.2. Design 2: A One-Stage Continuous-mode Class-F/F<sup>-1</sup> PA

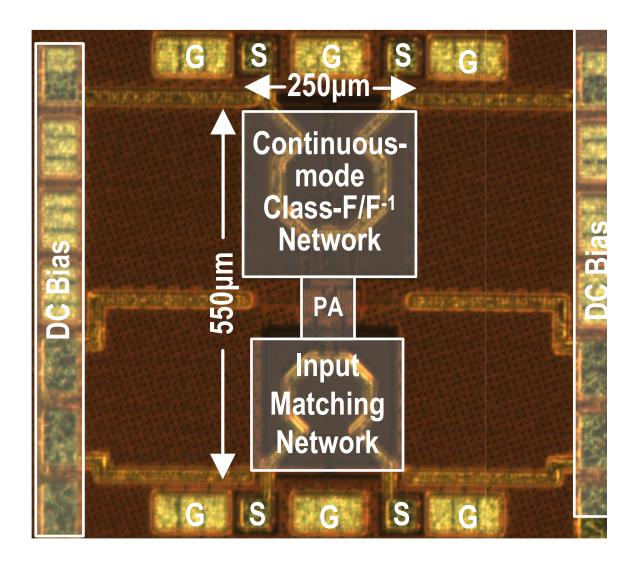

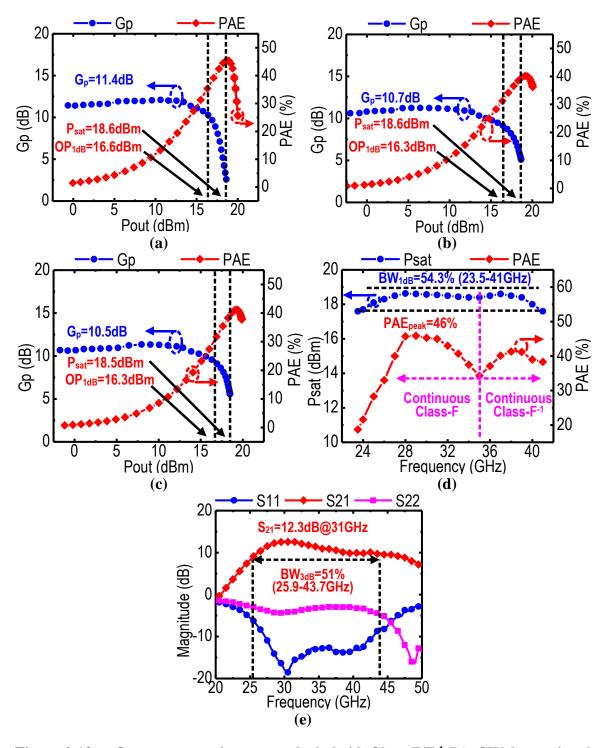

The second PA design occupies a  $0.55\times0.25~\text{mm}^2$  core area, as shown in Figure 2.12. Figure 2.13 shows the measured CW large-signal performance at 28, 37 and 39 GHz respectively. At 28 GHz, this proposed PA design achieves  $P_{\text{sat}}$  of 18.6 dBm,  $PAE_{\text{max}}$  of 45.7 % and  $G_p$  of 11.4 dB. At 37 GHz, the PA demonstrates  $P_{\text{sat}}$  of 18.6 dBm,  $PAE_{\text{max}}$  of 40.2 % and  $G_p$  of 10.7 dB. At 39 GHz, the PA achieves  $P_{\text{sat}}$  of 18.5 dBm,  $PAE_{\text{max}}$  of 41.2 % and  $G_p$  of 10.5 dB. This PA achieves high efficiency (i.e.,  $PAE_{\text{max}} \ge 40$  %) and delivers almost constant  $P_{\text{sat}}$  at all the potential 5G bands (28/37/39 GHz). The  $P_{\text{sat}}$  1-dB bandwidth is 54.3 % from 23.5 GHz to 41 GHz and the peak PAE is 46 % at 29 GHz, as shown in Figure 2.13(c). Also, it maintains over 30 % PAE from 25.5 GHz to 41 GHz (46.6 %). Figure 2.13(d) also demonstrates that the Class-F mode operates around 28 GHz, while Class-F-1 mode operates around 38 GHz. A mode transition is clearly shown around 35 GHz, which matches our analysis in Section III. In Figure 2.13(e), the measured small-signal S-parameter shows that 3-dB bandwidth is 51 % (25.9-43.7 GHz.)

Figure 2.12 – Chip microphotograph of one-stage continuous-mode hybrid Class-F/F<sup>-1</sup> PA.

Figure 2.13 – One-stage continuous-mode hybrid Class- $F/F^{-1}$  PA CW large-signal measurement at (a) 28 GHz, (b) 37 GHz and (c) 39 GHz, (d) Psat/PAE vs. frequency, and (e) small-signal S-parameter.

## 2.4.3. Design 3: A Two-Stage Continuous-mode Class-F/-F<sup>-1</sup> PA

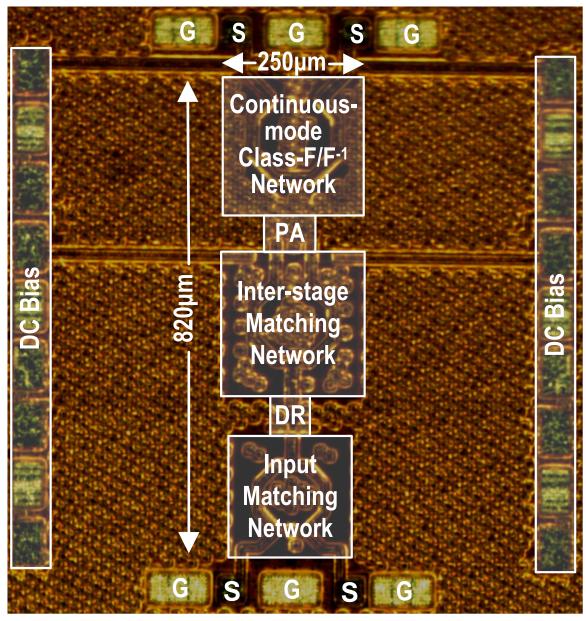

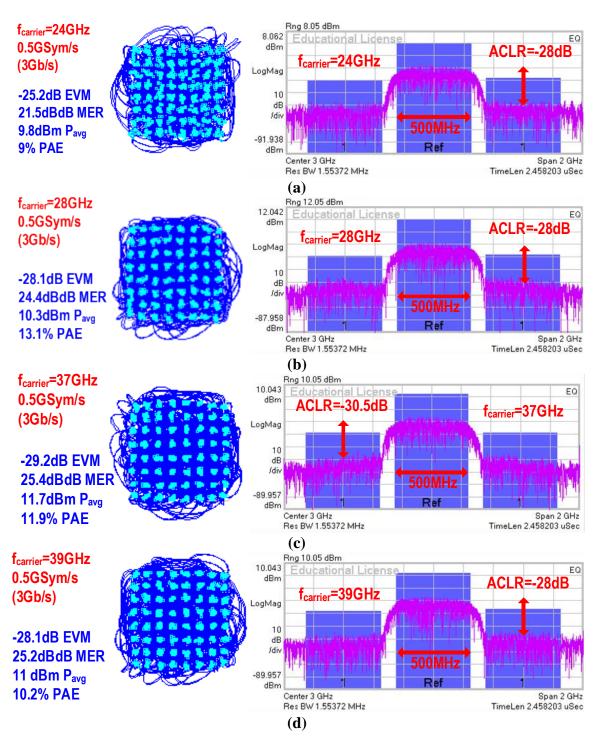

The third PA design occupies a  $0.82 \times 0.25$  mm<sup>2</sup> core area, as shown in Figure 2.14. Figure 2.15 shows the measured CW large-signal performance at 28, 37 and 39 GHz. At 28 GHz, this PA achieves P<sub>sat</sub> of 18.9 dBm, PAE<sub>max</sub> of 43.2 % and G<sub>p</sub> of 18.7 dB. At 37 GHz, the PA demonstrates P<sub>sat</sub> of 18.9dBm, PAE<sub>max</sub> of 37 % and Gp of 18 dB. At 39 GHz, the PA achieves P<sub>sat</sub> of 18.9 dBm, PAE<sub>max</sub> of 36 % and G<sub>p</sub> of 15.6 dB. The measured CW large-signal performance vs. frequency is shown in Figure 2.15(d). The P<sub>sat</sub> 1-dB bandwidth is 55.1 % from 23 GHz to 40.5 GHz. This design maintains over 30 % PAE from 24 GHz to 40 GHz (50 %). A mode transition is clearly shown around 33 GHz. The measured small-signal S-parameter shows 3-dB bandwidth is 49.4 % from 23.8 GHz to 39.4 GHz (Figure 2.15d). This PA is measured using 64-QAM signals at 0.5 GSym/s (3 Gb/s) at f<sub>carrier</sub> of 24 GHz, 28 GHz, 37 GHz and 39 GHz respectively (Figure 2.16). Without DPD, the measured EVM is below <-25 dB. At  $f_{carrier}$  of 24 GHz,  $P_{avg}$  of 9.8 dBm and PAE of 9 %. At f<sub>carrier</sub> of 28 GHz, P<sub>avg</sub> is 10.3 dBm and PAE<sub>avg</sub> is 13.1 %. At f<sub>carrier</sub> of 37 GHz, Pavg is 11.7 dBm and PAEavg is 11.9 %. At f<sub>carrier</sub> of 39 GHz, Pavg is 11 dBm and PAEavg is 10.2 %. This PA design satisfies the stringent linearity requirement for future 5G bands (28/37/39 GHz). The large-signal and modulation comparisons with other PAs are listed in Table 2-1 and Table 2-2, respectively.

Figure 2.14 – Chip microphotograph of two-stage continuous-mode hybrid Class- $F/F^{-1}$  PA.

Figure 2.15 – Two-stage continuous-mode hybrid Class-F/F<sup>-1</sup> PA CW large-signal measurement at (a) 28 GHz, (b) 37 GHz and (c) 39 GHz, (d) Psat/PAE vs. frequency, and (e) small-signal S-parameter.

Figure 2.16 – Two-stage continuous-mode hybrid Class-F/F<sup>-1</sup> PA modulation measurement results (0.5 GSym/s) at (a) 24 GHz, (b) 28 GHz, (c) 37 GHz, (d) 39 GHz respectively.

Table 2.2 – CW Performance Comparison with State-of-the art Silicon-based Mm-Wave Power Amplifier at Related Frequency

|                   | P <sub>sat</sub> 1-dB<br>Freq.<br>(GHz) | P <sub>sat</sub> 1dB<br>BW (%) | Operation<br>Freq. (GHz) | P <sub>sat</sub> (dBm) | PAE <sub>max</sub> (%) | Gain<br>(dB)         | OP1dB<br>(dBm)       | VDD<br>(V) | Process             | Topology                                             | Size<br>(mm²) |

|-------------------|-----------------------------------------|--------------------------------|--------------------------|------------------------|------------------------|----------------------|----------------------|------------|---------------------|------------------------------------------------------|---------------|

| Design 1          | 19-29.5                                 | 43.3                           | 28.5                     | 17                     | 43.5                   | 20                   | 15.2                 | 1.9        | 130nm<br>SiGe       | 2-stg. Continuous Class-F-1                          | 0.29          |