# Contrôleurs reconfigurables ultra-faible consommation pour les réseaux de capteurs sans fil

Vivek Tovinakere Dwarakanath

## ▶ To cite this version:

Vivek Tovinakere Dwarakanath. Contrôleurs reconfigurables ultra-faible consommation pour les réseaux de capteurs sans fil. Autre. Université Rennes 1, 2013. Français. <NNT : 2013REN1S018>. <tel-00859921>

## HAL Id: tel-00859921 https://tel.archives-ouvertes.fr/tel-00859921

Submitted on 9 Sep 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour la grade de

## DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention : Traitement du Signal et Télécommunications

École Doctorale : MATISSE

présentée par

## Vivek TOVINAKERE DWARAKANATH

preparée à l'unite recherche : IRISA - UMR 6074

Institut de Recherche en Informatique et Systèmes Aléatoires - CAIRN

École Nationale Supérieure des Sciences Appliquées et de Technologie

Contrôleurs reconfigurables ultra-faible consommation pour les nœuds de réseaux

de capteurs sans fil

Ultra-Low Power Reconfigurable Architectures for Controllers in Wireless Sensor Network Nodes Composition du jury :

Ian O'CONNOR Professeur, INL Ecole Centrale de Lyon / Examinateur

**Jean-Philippe DIGUET** Directeur de Recherche, CNRS, LAB-STICC Université de Bretagne Sud / Examinateur

**Patrick GIRARD** Directeur de Recherche, CNRS, LIRMM Université de Montpellier / Rapporteur

Marc BELLEVILLE Directeur de Recherche, CEA, LETI Minatec, Grenoble / Rapporteur

**Olivier SENTIEYS** Directeur de Recherche, INRIA Lannion / Directeur de thèse

**Steven DERRIEN** Professeur, Université de Rennes 1 Rennes / Co-directeur de thèse

# Résumé

Les réseaux de capteurs sans fil représentent une convergence de trois aspects des systèmes intégrés pour le traitement de l'information, à savoir la perception de l'environnement, le traitement de données et leur communication par radio. Un nœud du réseau de capteurs sans fil peut avoir besoin de traiter dans ses unités de calcul les signaux de plusieurs types de capteurs. Sur l'aspect des communications sans fil, un nœud peut avoir à effectuer différentes de tâches liées à la transmission de l'information et à adapter les protocoles de communication. Un nœud lui-même peut donc avoir à changer son rôle de façon dynamique et doit donc inclure des tâches complexes de contrôle pour la gestion de ses ressources. Tous ces facteurs font que la flexibilité est un sujet primordial dans la conception de nœuds de réseaux de capteurs sans fil, en plus bien sur de l'énergie consommée. Les architectures reconfigurables, comme les FPGA qui utilisent des blocs logiques configurables et des réseaux d'interconnexion programmables ont été proposés pour répondre aux besoins de flexibilité. Ils sont milleurs en termes de coûts non récurrents par rapport à des circuits intégrés spécialisés (ASIC). Toutefois, le matériel flexible de ces processeurs reconfigurables n'est pas une solution alternative à la grande efficacité énergétique des circuits ASIC - la contrainte primordiale pour les nœuds des réseaux de capteurs sans fil.

Dans cette thèse, des contrôleurs flexibles de consommation ultra-faible pour les nœuds réseaux de capteurs sans fil basés sur des micro-tâches reconfigurables sont étudiées. Une micro-tâche est principalement une unité de contrôle numérique incluant une machine d'états finis (FSM) et un chemin de données assemblant des unités arithmétiques et logiques, des mémoires et des périphériques d'entrées-sorties. Pour introduire de la flexibilité dans les micro-tâches, des machines d'états finis flexibles et évolutives, et des additionneurs reconfigurables à précision variable sont considérés au prix d'une légère augmentation de la surface du matériel. De plus, un fonctionnement à ultra-faible consommation est recherché grâce à l'utilisation des techniques de *power gating* pour réduire la puissance statique. Il est bien connu que, dans les circuits CMOS nanométriques, l'augmentation de la densité de puissance statique dépasse de loin l'impact de la surface de Silicium en raison de la très forte intégration.

Le power qating (PG) comme technique de faible consommation est considéré aux niveaux architecture et circuit pour les machines d'état finis et les éléments du chemin de données. Une étude approfondie des problèmes liés à la conception et à la modélisation des circuits utilisant la technique de *power gating* est réalisée en suivant une approche ascendante. Des modèles au niveau porte pour l'estimation des paramètres de conception des circuits PG sont tout d'abord dérivés. Ensuite, les additionneurs et machines d'états finis reconfigurables proposées pour les micro-tâches sont étudiés pour tirer partie de l'efficacité des possibilités des techniques PG. Dans les additionneurs, la reconfigurabilité est utilisée pour faire varier dynamiquement la précision de l'opération et des économies significative d'énergie sont obtenues en éteignant les blocs logiques inutilisés. Pour les machines d'états finis reconfigurables, des architectures avec différents degrés de flexibilité et de complexité sont proposées. La technique PG au niveau de la lookup table (LUT) est proposée pour atteindre des réductions de puissance statique significatives. Différentes structures transverses et de rétroaction des machines d'états finis sont exploitées pour réduire les interconnexions programmables. Enfin, les modèles proposés sont appliqués à analyser l'économie d'énergie (ou de puissance) réalisée dans les contrôleurs et les chemins de données en raison de l'utilisation conjointe de la reconfiguration et du PG. Les micro-tâches reconfigurables proposées sont positionnées par rapport à

des microcontrôleurs de faible puissance et des micro-tâches câblées en tenant compte de différents paramètres.

# Abstract

Wireless sensor networks (WSNs) represent a convergence of three aspects of evolutionary integrated systems for information processing *viz.*, sensing, computation and communications. A node in the wireless sensor network may need to process signals from different types of sensors in their sensing and computational units. On the communications side, a node may have to perform different transceiver tasks to adapt wireless communication protocols. A node itself may have to change its roles dynamically. Hence the controller in a node is required to execute different control tasks to manage its resources. All these factors imply that flexibility is of key concern in the design of WSN nodes. Reconfigurable hardware such as FPGAs that use configurable logic blocks and programmable interconnection networks have been proposed to address the need for flexibility. They also offer efficiency in terms of non-recurring engineering (NRE) costs compared to ASIC-based designs. However flexible hardware of reconfigurable processors are not energy efficient unlike dedicated circuits - a key constraint for WSN nodes.

In this thesis, ultra-low power flexible controllers for WSN nodes based on reconfigurable microtasks are explored. A microtask is essentially a digital control unit in a node with a finite state machine (FSM) and a datapath consisting of arithmetic-logic unit, memories and input/output interfaces. To introduce flexibility in microtasks, reconfigurable FSMs and adders are considered at the expense of hardware area. Scalable architectures for reconfigurable FSMs along with variable precision adders in the datapath are proposed in this work for flexible controllers based on a microtask model. Further, it is sought to achieve ultra-low power operation using power gating. It is well known that in nanoscale CMOS circuits, the increase in static power density as a cost far exceeds the impact of area due to increased logic integration.

Power gating as a low power technique is considered at architecture and circuit levels for FSM and datapath elements of microtasks. It involves an extensive study of design issues in power gating and modeling of design parameters of a power-gated circuit. A bottom-up approach is taken: gate level models for estimation of key design parameters of power-gated circuits are derived first. Next, reconfigurable adders and FSMs proposed for microtasks are studied at gate level for power gating opportunities. In adders, reconfigurability is used for dynamically varying the precision of operation and hence examined for potential energy savings by power gating unused logic. For reconfigurable FSMs, scalable architectures with varying degrees of flexibility and complexity are presented. Power gating at the level of lookup table (LUT) logic is proposed to achieve aggressive leakage power and energy reduction. The feedback and feedforward structures of a FSM are exploited to reduce programmable interconnections. Finally the proposed models are applied to analyze energy (or power) savings in the logic clusters of FSMs and adders in datapath due to power gating. The position of reconfigurable microtasks in the design space of controllers relative to a low power microcontroller and hardwired microtasks is discussed using different metrics.

# Contents

| R  | ésum   | é                                                                              | i        |

|----|--------|--------------------------------------------------------------------------------|----------|

| A  | bstra  | let                                                                            | iii      |

| Li | ist of | Figures                                                                        | ix       |

| Li | ist of | Tables x                                                                       | iii      |

| 0  | Rés    | umé étendu                                                                     | 1        |

|    | 0.1    | Nœuds d'un réseau de capteurs                                                  | 1        |

|    |        | 0.1.1 Espace de conception de contrôleurs flexibles pour les nœuds de          |          |

|    |        | capteurs                                                                       | 2        |

|    |        | 0.1.2 Contrôleurs reconfigurables à faible consommation $\ldots \ldots \ldots$ | 4        |

|    | 0.2    | Modèles pour les circuits à coupure d'alimentation                             | 5        |

|    |        | 0.2.1 Circuit et opération équivalents d'un circuit à coupure d'alimentation   | 5        |

|    |        | 0.2.2 Temps et énergie de réveil                                               | 7        |

|    | 0.3    | Additionneur faible consommation à précision variable                          | 8        |

|    | 0.4    |                                                                                | 10       |

|    |        |                                                                                | 10       |

|    | 0 5    | 1                                                                              | 12       |

|    | 0.5    |                                                                                | 12       |

|    | 0.6    |                                                                                | 13       |

|    |        |                                                                                | 14<br>14 |

|    |        | 0.0.2 Le cout de la flexibilité                                                | 14       |

| 1  | Intr   | roduction                                                                      | 17       |

|    | 1.1    | Overview of Low Power Design                                                   | 18       |

|    |        | 1.1.1 Sources of Power and Energy Constraints                                  | 18       |

|    |        | 1.1.2 Energy Consumption in CMOS Circuits                                      | 19       |

|    |        | *                                                                              | 20       |

|    |        |                                                                                | 21       |

|    | 1.2    |                                                                                | 21       |

|    |        |                                                                                | 21       |

|    |        |                                                                                | 22       |

|    | 1.3    |                                                                                | 23       |

|    | 1.4    |                                                                                | 24       |

|    | 1.5    | Organization of the Thesis                                                     | 25       |

| <b>2</b> | Cor | trollers for Wireless Sensor Network Nodes                | <b>27</b> |

|----------|-----|-----------------------------------------------------------|-----------|

|          | 2.1 | Introduction                                              | 27        |

|          | 2.2 | Wireless Sensor Network Nodes                             | 27        |

|          | 2.3 | Controllers for WSN Nodes                                 | 29        |

|          | 2.4 | Reconfigurable Microtasks                                 | 32        |

|          | 2.5 | Embedded FPGA                                             | 34        |

|          |     | 2.5.1 Resource Utilization                                | 35        |

|          |     | 2.5.2 Power Estimation                                    | 38        |

|          |     | 2.5.2.1 Model for Optimistic Power Estimation             | 39        |

|          |     | 2.5.2.2 Results                                           | 42        |

|          |     | 2.5.3 Observations on Embedded FPGA                       | 43        |

|          | 2.6 | Low Power Reconfigurable Hardware                         | 44        |

|          | 2.7 | Conclusion                                                | 45        |

| 3        | Des | ign Considerations in Power-Gated Circuits                | 47        |

|          | 3.1 | Introduction                                              | 47        |

|          | 3.2 | Leakage Currents in MOS Devices                           |           |

|          | 3.3 | Power Gating                                              |           |

|          |     | 3.3.1 Sleep Devices and Power Gating Networks             |           |

|          |     | 3.3.2 Design Parameters                                   |           |

|          |     | 3.3.3 Power-Gating Example                                |           |

|          | 3.4 | Models for Estimation of Wakeup Time and Wakeup Energy    |           |

|          |     | 3.4.1 Power-Gated Circuit Operation                       |           |

|          |     | 3.4.2 Power-Gated Logic Cluster Model                     |           |

|          |     | 3.4.3 Virtual-Vdd Model                                   |           |

|          |     | 3.4.3.1 Determination of Steady-State Virtual-Vdd Voltage | 60        |

|          |     | 3.4.3.2 Wakeup Time Estimation                            |           |

|          |     | 3.4.3.3 Sleep Mode Virtual-Vdd Model                      | 62        |

|          |     | 3.4.3.4 Determination of $R_{lin}$                        | 64        |

|          |     | 3.4.3.5 Heuristics for $I_0, I_1$ and $R_{sp}$            | 65        |

|          |     | 3.4.4 Experimental Results                                | 66        |

|          |     | 3.4.5 Wakeup Energy Estimation                            | 69        |

|          |     | 3.4.6 Logic Clustering for Wakeup Scheduling              | 70        |

|          |     | 3.4.7 Logic Clustering for Wakeup Energy Control          | 71        |

|          | 3.5 | Conclusion                                                | 71        |

| 4        | Var | iable Precision Arithmetic Units for Low Power            | 73        |

|          | 4.1 | Introduction                                              | 73        |

|          | 4.2 | Variable Precision Arithmetic Units: A Review             | 73        |

|          |     | 4.2.1 Low Power Optimizations                             | 74        |

|          | 4.3 | Logic Clustering Method and Energy Savings                | 76        |

|          |     | 4.3.1 Logic Clustering                                    | 76        |

|          |     | 4.3.2 Energy Savings in Active Mode                       | 77        |

|          | 4.4 | Logic Clustering in Arithmetic Circuits                   | 78        |

|          |     | 4.4.1 Parallel-Prefix Trees                               | 78        |

|          |     | 4.4.2 Partial Products in Multiplier                      | 79        |

|          | 4.5 | Power-Gated Reconfigurable Circuits                       | 80        |

| Bi | bliog        | graphy        |                                                                  | 125   |

|----|--------------|---------------|------------------------------------------------------------------|-------|

| Pι | ıblica       | ations        |                                                                  | 123   |

|    |              | 6.4.2         | Circuit-Level Optimizations                                      |       |

|    |              | 6.4.1         | Power Efficient Reconfiguration Mechanisms                       |       |

|    | 6.4          |               | e Work                                                           |       |

|    | 6.3          |               | f Flexibility                                                    |       |

|    | 6.2          |               | y Efficiency                                                     |       |

|    | 6.1          |               | iew                                                              | . 117 |

| 6  | Con          | clusio        | ns and Perspectives                                              | 117   |

|    | 5.8          |               | ision                                                            |       |

|    | 5.7          |               | Sequential Circuits                                              |       |

|    | 5.6          | Cost o        | f Area                                                           | . 112 |

|    |              | 5.5.6         | Effects of Wakeup Overheads and Performance-Power Trade-offs     | . 110 |

|    |              | 5.5.5         | Sources of Errors in Power Estimation                            | . 110 |

|    |              | 5.5.4         | Experimental Setup and Validation                                | . 108 |

|    |              | 5.5.3         | An Analysis of Power Estimation                                  | . 106 |

|    |              | 3.3. <b>H</b> | Cells                                                            |       |

|    |              | 5.5.2         | Static Power in State Register, Configuration Bits and Isolation |       |

|    | 0.0          | 5.5.1         | Characterization of LUTs, Input Selector and Decoders            |       |

|    | 5.5          |               | Estimation in Reconfigurable FSMs                                |       |

|    |              | 5.4.3         | Overall Architecture                                             |       |

|    |              | 5.4.2         | Input Selector-Decoder Design and Overheads                      |       |

|    |              | 5.4.1         | Motivation                                                       |       |

|    | 5.4          |               | ed Reconfigurability in FSMs                                     |       |

|    |              | 5.3.5         | Observations on Power-Gated Architectures                        |       |

|    |              | 5.3.4         | Power Gating Opportunities                                       |       |

|    |              | 5.3.3         | Configuration Bits for Reconfiguration                           |       |

|    |              | 5.3.2         | Output Functions                                                 |       |

|    | 0.0          | 5.3.1         | Next-State Functions                                             |       |

|    | 5.3          |               | ectures Optimized for Reconfigurable FSMs                        |       |

|    | $5.1 \\ 5.2$ |               | figurable Finite State Machines                                  |       |

| J  | 5.1          |               | uction                                                           |       |

| 5  | Low          |               | r Reconfigurable Finite State Machines                           | 89    |

|    | 4.7          | Conclu        | asion                                                            | . 86  |

|    |              | 4.6.4         | Energy Savings Example                                           | . 86  |

|    |              | 4.6.3         | Reducing Simulation Time                                         | . 84  |

|    |              | 4.6.2         | Results                                                          | . 83  |

|    |              | 4.6.1         | Experimental Setup                                               | . 81  |

|    | 4.6          | Power         | Estimation and Analysis                                          | . 81  |

|    |              | 4.5.2         | Power Gating in Multipliers                                      | . 80  |

|    |              | 4.5.1         | Variable-Precision Adders                                        | . 80  |

# List of Figures

| 1    | Un réseau de capteurs typique.                                                 | 2  |

|------|--------------------------------------------------------------------------------|----|

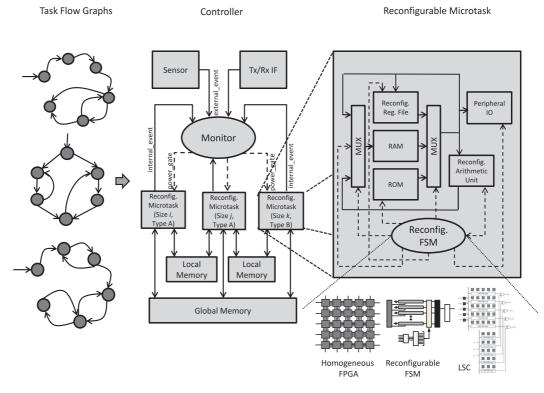

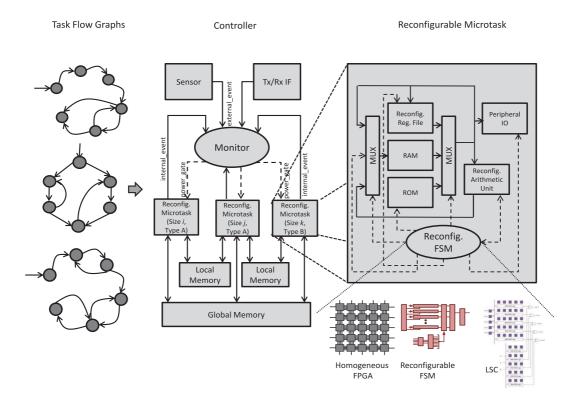

| 2    | Un graphe de micro-tâches et la vue système de l'architecture générée par      |    |

|      | le flot de conception proposé dans [1].                                        | 3  |

| 3    | Structure d'un CLB et d'un CB dans le eFPGA.                                   | 4  |

| 4    | Vue système de la matrice du eFPGA et un élément de celle-ci contenant         |    |

|      | les canaux de routage et la matrice d'interconnexions programmables            | 4  |

| 5    | Structure d'un contrôleur flexible pour micro-tâche reconfigurable.            | 5  |

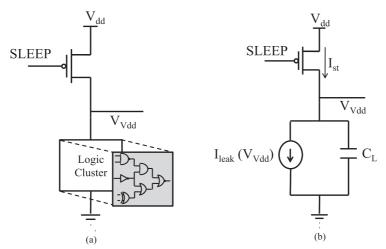

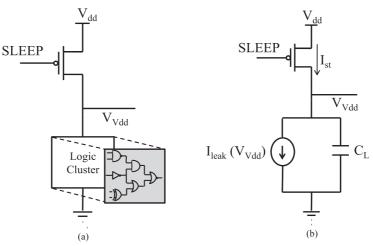

| 6    | (a) Cluster logique à coupure d'alimentation. (b) Circuit équivalent.          | 6  |

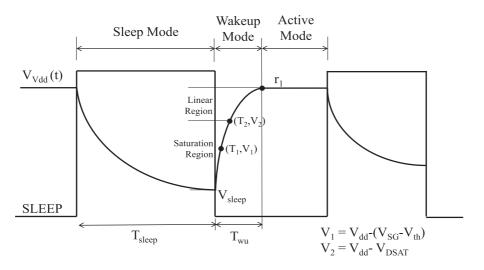

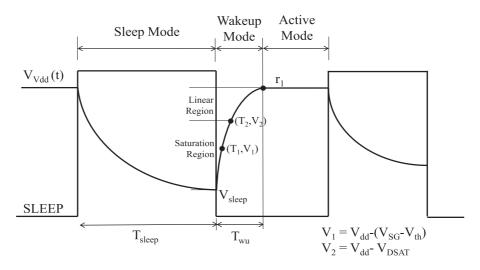

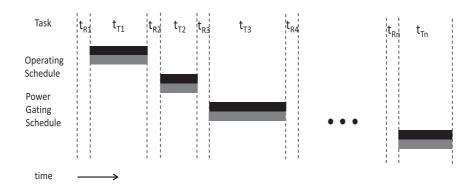

| 7    | Un chronogramme temporel typique et les différents modes d'opérations          |    |

|      | dans un cycle typique de <i>power gating</i>                                   | 6  |

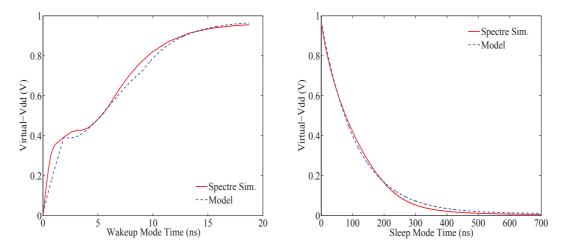

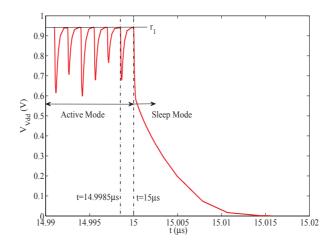

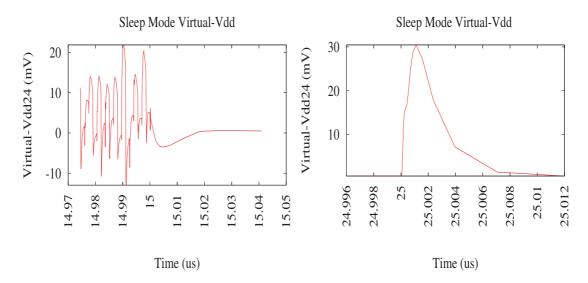

| 8    | Virtual-Vdd en modes réveil et veille (W=1.2 $\mu$ m) pour le benchmark c7552. | 8  |

| 9    | Additionneur reconfigurable à coupure d'alimentation.                          | 9  |

| 10   | Modèle architectural de FSM reconfigurable, tel qu'il a été utilisé pour la    |    |

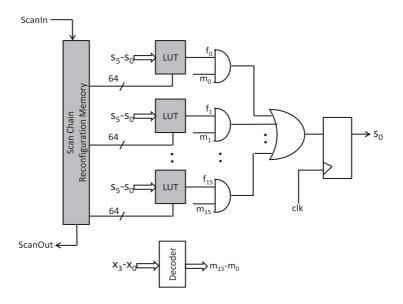

|      | validation expérimentale                                                       | 11 |

| 1.1  | A typical wireless sensor network node                                         | 22 |

| 1.2  | A generalized task flow graph and system level view of generated archi-        |    |

|      | tecture as proposed in [1]                                                     | 23 |

| 2.1  | Functional representation of a wireless sensor network                         | 28 |

| 2.2  | Structure of a microtask (as proposed in [1])                                  | 31 |

| 2.3  | Structure of flexible controller with reconfigurable microtasks                | 33 |

| 2.4  | Configurable Logic Block (CLB) structure in eFPGA.                             | 34 |

| 2.5  | Configuration Bit (CB) in eFPGA.                                               | 34 |

| 2.6  | Top level view of eFPGA.                                                       | 35 |

| 2.7  | An array element of eFPGA with routing channels and interconnection            |    |

|      | network                                                                        | 36 |

| 2.8  | Switch box in eFPGA.                                                           | 36 |

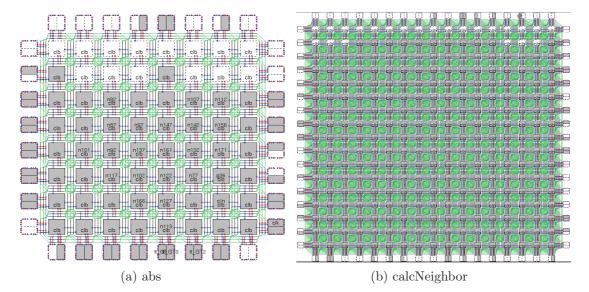

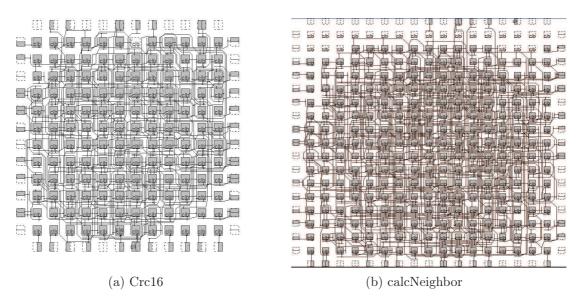

| 2.9  | Interconnection network complexities in mappings of two FSMs                   | 37 |

| 2.10 | Compact placement and routing in mappings of two FSMs                          | 40 |

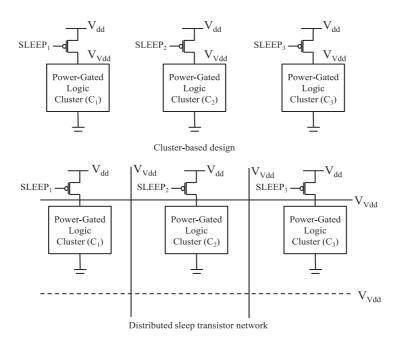

| 3.1  | Cluster-based power gating and distributed sleep transistor network            | 50 |

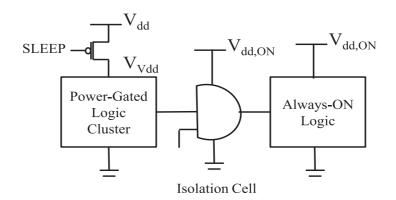

| 3.2  | A power-gated logic cluster with header type of sleep transistor and iso-      |    |

|      | lation cell.                                                                   | 51 |

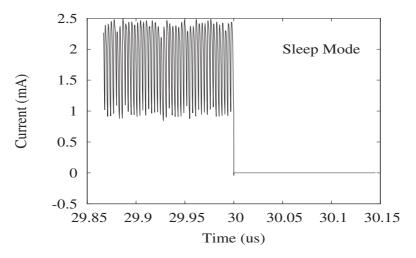

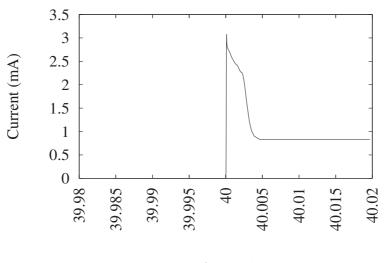

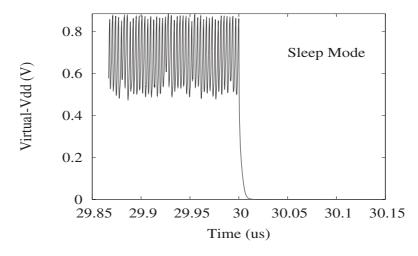

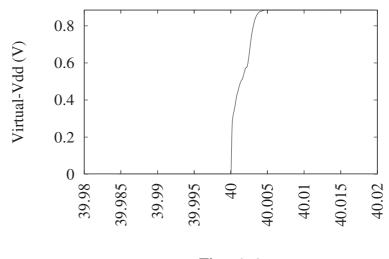

| 3.3  | Active mode and sleep mode current in power-gated c6288 (W=12 $\mu m).$        | 54 |

| 3.4  | Wakeup mode current in power-gated c6288 (W=12 $\mu$ m) $\ldots$               | 54 |

| 3.5  | Active mode and sleep mode Virtual-Vdd in power-gated c6288 (W=12 $\mu m).$    | 55 |

| 3.6  | Wakeup mode Virtual-Vdd in power-gated c6288 (W= $12\mu$ m)                    | 55 |

| 3.7   | (a) Power-gated logic cluster of header type. (b) Equivalent circuit of logic cluster                                                             | 57       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.8   | Typical timing instants and modes of operation in a power gating cycle.                                                                           | 57       |

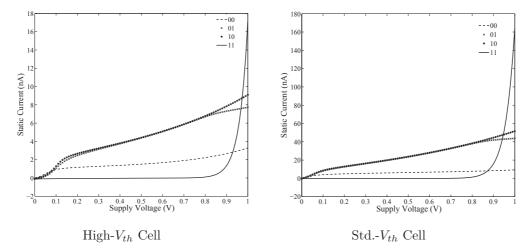

| 3.9   | Static current profile of a 2-input NAND gate of high- $V_{th}$ and std $V_{th}$                                                                  |          |

|       | devices for all input patterns.                                                                                                                   | 58       |

|       | Virtual-Vdd in active and sleep modes                                                                                                             | 64       |

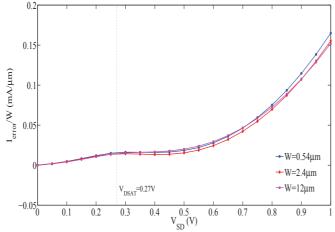

|       | $I_{error}/W$ vs. $V_{sd}$ for 65nm PMOS transistors                                                                                              | 66       |

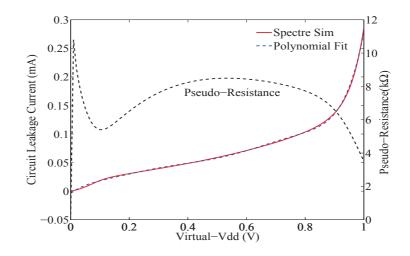

|       | Leakage current and pseudo-resistance profile in c6288                                                                                            | 67       |

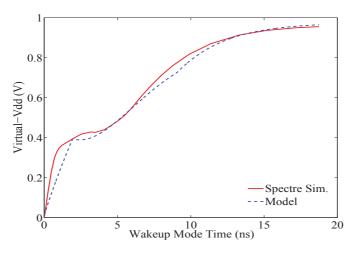

|       | Virtual-Vdd in wakeup mode (W= $1.2\mu$ m) in c7552                                                                                               | 68       |

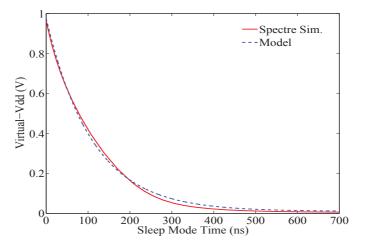

| 3.14  | Virtual-Vdd in sleep mode (W=1.2 $\mu$ m) in c7552                                                                                                | 68       |

| 4.1   | Typical flow for design of variable-precision power-gated arithmetic circuits.                                                                    | 75       |

| 4.2   | Parallel-prefix tree structure for carry generation in BK adder.                                                                                  | 79       |

| 4.3   | Parallel-prefix tree structure for carry generation in KS adder                                                                                   | 79       |

| 4.4   | Partial product structure in a binary multiplier clustered for variable pre-                                                                      |          |

|       | cision and power gating.                                                                                                                          | 80       |

| 4.5   | Power-gated reconfigurable adder                                                                                                                  | 81       |

| 4.6   | Power-gated reconfigurable multiplier.                                                                                                            | 82       |

| 4.7   | Current drawn by power-gated KS adder (16-bit precision).                                                                                         | 84       |

| 4.8   | Virtual-Vdd of $C_{N_4}$ in power-gated KS adder (16-bit precision)                                                                               | 85<br>85 |

| 4.9   | Virtual-Vdd of $C_{N_2}$ in power-gated KS adder (16-bit precision)                                                                               | 85       |

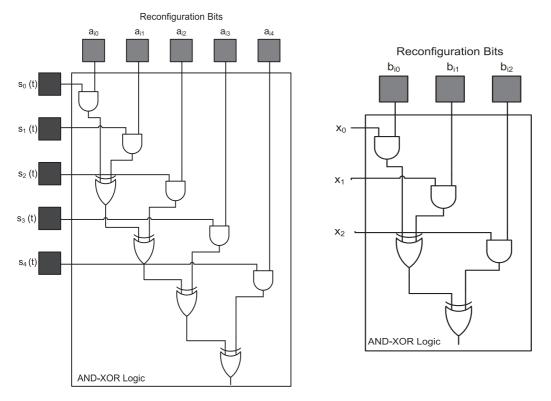

| 5.1   | Microtasks with reconfigurable FSMs.                                                                                                              | 90       |

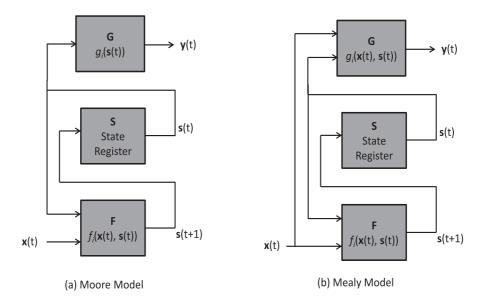

| 5.2   | Moore and Mealy models of finite state machines                                                                                                   | 91       |

| 5.3   | Next-state function realization for one state-register bit ( $N = 6, n =$                                                                         |          |

|       | $4, K = 6). \ldots \ldots$ | 93       |

| 5.4   | Output function realization in Moore type FSM (Case 2. $N = 6, m = 10, K = 6$ ).                                                                  | 94       |

| 5.5   | Output function realization in Mealy type FSM $(N = 6, m = 1, K = 6)$ .                                                                           | 95       |

| 5.6   | Scan chain reconfiguration memory of LUTs                                                                                                         | 96       |

| 5.7   | Power gating opportunity for active mode energy savings in a reconfig-                                                                            |          |

|       | urable FSM                                                                                                                                        | 97       |

| 5.8   | Power gating opportunity for aggressive active mode energy savings in a                                                                           |          |

|       | reconfigurable FSM.                                                                                                                               | 98       |

| 5.9   | Power gating opportunity for aggressive active mode energy savings in                                                                             |          |

| F 10  | reconfigurable FSM output logic.                                                                                                                  | 99       |

|       | Input selector-decoder logic to select minterms of dependent inputs                                                                               | 102      |

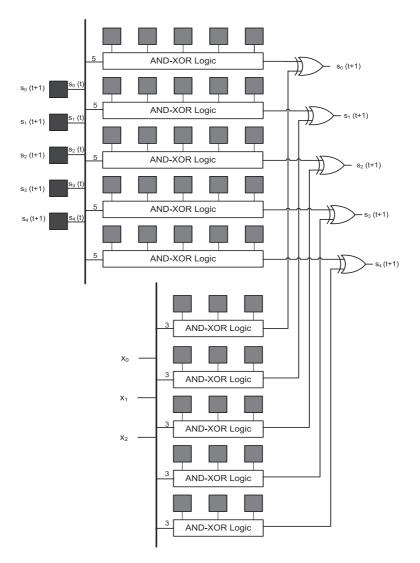

| 5.11  | Schematic diagram of the overall architecture of scalable power-gated re-<br>configurable FSM.                                                    | 102      |

| 5 1 2 | An architectural module of overall power-gated reconfigurable FSM used                                                                            | 103      |

| 0.12  | in experimental validation.                                                                                                                       | 109      |

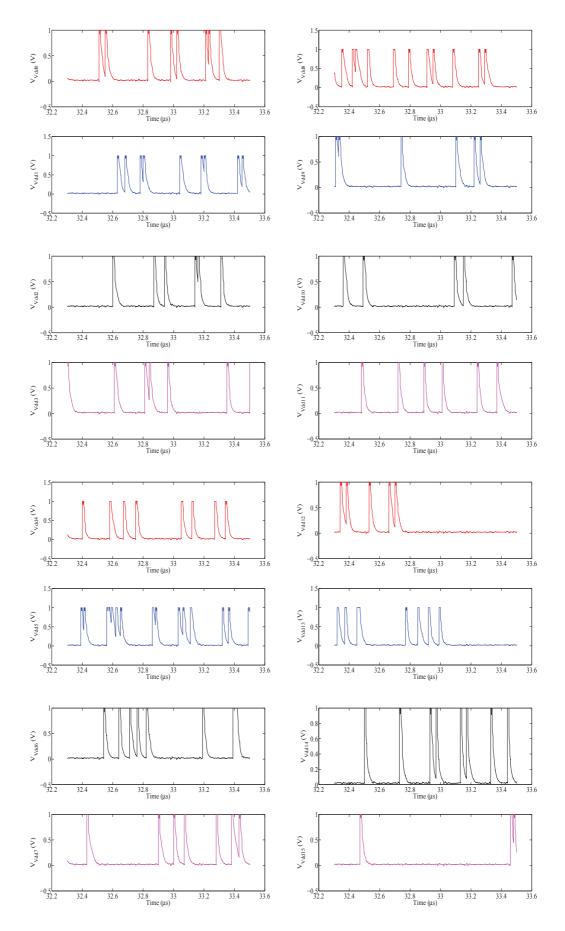

| 5.13  | Snapshot of Virtual- $V_{dd}$ nodes of 16 LUT logic clusters from SPICE sim-                                                                      | 200      |

|       | ulations for random input data at 100 MHz.                                                                                                        | 111      |

| 5.14  | Basic logic structures to evaluate partial matrix multiplications in Eq. (5.23).                                                                  |          |

| 5.15  | Schematic for next-state function in a linear sequential circuit                                                                                  | 115      |

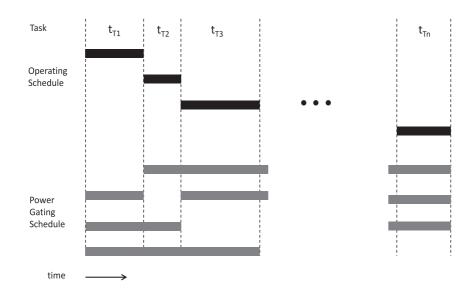

| 61    | Openating and power gating schedules for hardwined microtash-                                                                                     |          |

| 6.1   | Operating and power gating schedules for hardwired microtasks as pro-<br>posed in [1]                                                             | 120      |

6.2 Operating and power gating schedules for reconfigurable microtask. . . . 120

# List of Tables

| 1          | Consommation de puissance (mW) pour cinq FSM issues de SenseBench<br>synthétisées sur un eFPGA.                                                  | 4          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2          | Consommation de puissance pour des additionneurs BK et KS sans coupure d'alimentation.                                                           | 9          |

| 3          | Consommation de puissance pour des additionneurs reconfigurables BK et KS avec coupure d'alimentation.                                           | 9          |

| 4          | Puissance et énergie moyennes par opération pour des FSM implantées<br>sur une architecture à base de <i>power gating</i>                        | 12         |

| 5<br>6     | Coût en énergie par instruction pour trois réalisation de contrôleurs<br>Comparaison des coûts en surface des FSM spécialisées par rapport aux   | 14         |

| 0.1        | FSM reconfigurables (pour une chemin de données sur 16 bits)                                                                                     | 15         |

| 2.1        | Resource utilization $N_{CLB}$ , minimum channel width (MCW) and average interconnection length $(L_{av})$ required for FSMs on eFPGA-like array | 37         |

| 2.2        | Important eFPGA parameters as obtained from physical design. (Esti-<br>mates due to 'Family B' low power registers are in parenthesis.)          | 42         |

| 2.3        | Resource utilization, power and energy estimation for routable FSMs on eFPGA.                                                                    | 42         |

| 2.4        | Total power for routable FSMs on eFPGA. (Static power of unused array elements is not considered.)                                               | 43         |

| 2.5        | Resource utilization, power and energy estimation for FSMs on 7-channel scaled eFPGA.                                                            | 43         |

| 2.6        | Total power for FSMs on 7-channel scaled eFPGA.                                                                                                  | 43         |

| 3.1        | Leakage current density in nanoscale PMOS transistors.                                                                                           | 48         |

| 3.2<br>3.3 | Power consumption in ungated and power-gated array multiplier (c6288).<br>Linear region resistance of PMOS transistors.                          | $54 \\ 65$ |

| 3.4        | Maximum Virtual-Vdd after wakeup in ISCAS85 benchmark circuits with HVT cells.                                                                   | 68         |

| 3.5        | Wakeup time in ISCAS85 benchmark circuits with HVT cells                                                                                         | 69         |

| 3.6        | Maximum Virtual-Vdd after wakeup in ISCAS85 benchmark circuits with SVT cells                                                                    | 69         |

| 3.7        | Wakeup time in ISCAS85 benchmark circuits with SVT cells                                                                                         | 69         |

| 3.8        | Average relative errors in estimation of maximum $V_{Vdd}$ and wakeup time<br>in ISCAS85 benchmark circuits.                                     | 70         |

| 3.9        | Average relative error in estimation of wakeup energy in ISCAS85 benchmark circuits.                                                             | 70         |

| 4.1  | On-Off schedule for operation of different adders in the power-gated re-<br>configurable adder                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2  | Area overhead in power-gated reconfigurable adders over non-reconfigurable adders. 82                                                                    |

| 4.3  | Power consumption in non-reconfigurable/non-power gated BK and KS adders                                                                                 |

| 4.4  | Power consumption in power-gated reconfigurable BK and KS adders 83                                                                                      |

| 4.5  | Maximum Virtual- $V_{dd}$ in active mode operation of BK and KS adders 84                                                                                |

| 4.6  | Comparison of power estimation results between SPICE simulations and<br>models in 32-bit KS adder                                                        |

| 5.1  | Number of LUTs required for next-state function for full reconfigurability. 95                                                                           |

| 5.2  | Number of configuration bits                                                                                                                             |

| 5.3  | Limited reconfigurability examples                                                                                                                       |

| 5.4  | K-LUT parameters for power estimation $(K=4, K=6)$                                                                                                       |

| 5.5  | Area, leakage power consumption $(P_{leak})$ , switching energy $(E_{sw})$ and critical Path $(t_d)$ comparisons against decoders of different sizes 106 |

| 5.6  | Input selector-decoder logic                                                                                                                             |

| 5.7  | Parameter level specifications of FSMs                                                                                                                   |

| 5.8  | Static power in power-gated FSM architecture with limited reconfigura-                                                                                   |

|      | bility $(N = 7, n_I = 3, m = 23)$                                                                                                                        |

| 5.9  | Static power in power-gated FSM architecture with limited reconfigura-                                                                                   |

|      | bility $(N = 7, n_I = 4, m = 23)$                                                                                                                        |

| 5.10 | Dynamic energy estimation in power-gated reconfigurable FSM architecture108                                                                              |

| 5.11 | Total average power and energy per operation for FSMs on power-gated                                                                                     |

|      | architecture                                                                                                                                             |

| 5.12 | Area of power-gated reconfigurable FSM                                                                                                                   |

| 5.13 | Resources required for LSC and its area and static power estimates $115$                                                                                 |

| 6.1  | Equivalent energy per instruction in three realizations of node controllers. 119                                                                         |

| 6.2  | Comparison of areas of 16-bit hardwired and reconfigurable microtasks 119                                                                                |

## Chapitre 0

# Résumé étendu

### 0.1 Nœuds d'un réseau de capteurs

Les réseaux de capteurs (WSN) sont une infrastructure composée d'un large nombre de systèmes embarqués, appelés des nœuds, capables de capter des signaux physiques, de calculer et de communiquer entre eux au sein d'un réseau à la topologie variable. Ce type de fonctionnalité d'un WSN aboutit à un grand nombre d'applications potentielles [2, 3] telles que le monitoring de paramètres environnementaux, la surveillance dans un contexte de sécurité, la surveillance de santé personnelle [4], la gestion de trafic de véhicules, la gestion d'énergie dans les bâtiments, etc. Typiquement, un nœud peut contrôler d'autres nœuds, capter de l'information, transmettre, relayer ou recevoir des informations. Par conséquent, un nœud doit pouvoir changer son rôle dynamiquement au cours du temps, ce qui implique que leur omniprésence requiert de la flexibilité, tout en satisfaisant des contraintes fortes d'énergie et de performance.

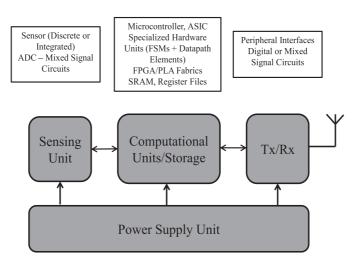

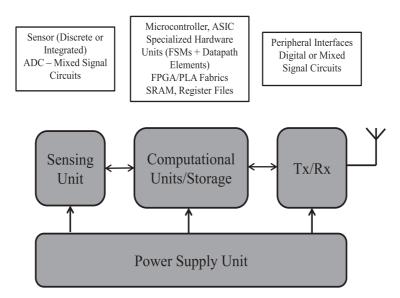

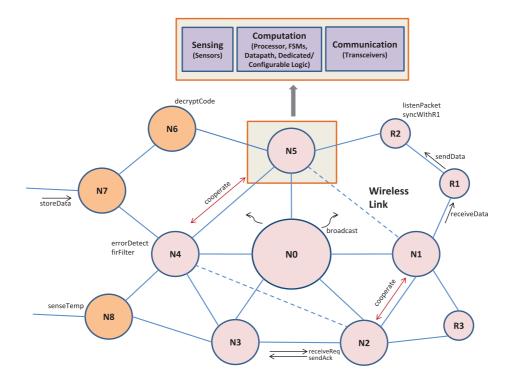

L'architecture typique d'un nœud de capteur, comme le montre la Fig. 1, est composée des capteurs et de leur interface, d'une unité de calcul et de contrôle et d'un émetteur/récepteur radio-fréquence. En plus de ces trois unités, une alimentation électrique incluant une unité de gestion de la puissance est requise. La technologie la plus utilisée pour la réalisation matérielle de ces nœuds est la technologie de circuit intégré CMOS *(complementary metal-oxide-semiconductor)*. Cette intégration d'un large nombre de transistors MOS apporte de nombreux challenges et compromis entre puissance consommée, performance, taille du circuit intégré et coût du produit final. Une étude critique des relations entre la fonctionnalité des nœuds de WSN, leurs contraintes énergétiques et leurs méthodes de conception, est nécessaire pour explorer correctement l'espace de conception des solutions matérielles efficaces en énergie.

Tandis que les réseaux de capteurs évoluent rapidement, leur spectre d'applications évolue encore plus vite. Les unités de calcul traitent des signaux issus de plus en plus de types de capteurs. Les unités de communications doivent s'adapter aux évolutions

FIGURE 1: Un réseau de capteurs typique.

rapides des protocoles sans fil. Ceci implique donc de plus en plus de tâches diverses de contrôle et aussi que la flexibilité est en enjeu essentiel pour les unités de contrôle assurant le gestion des nœuds.

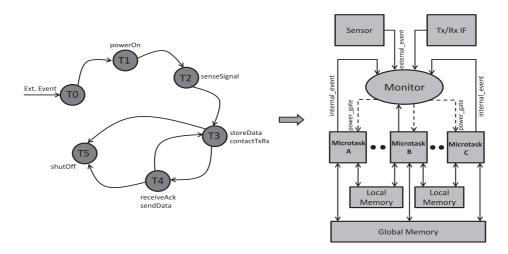

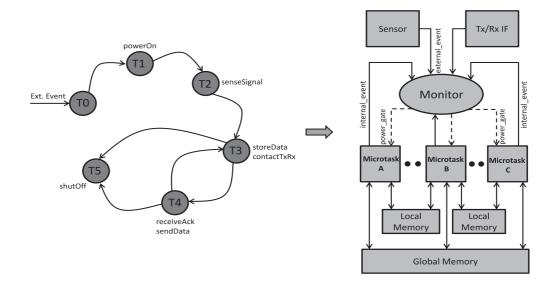

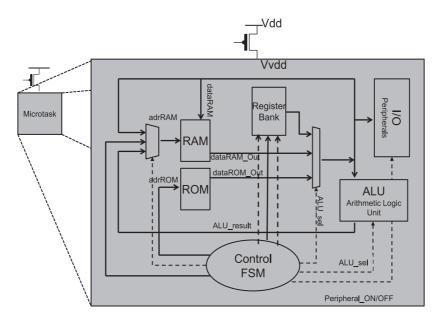

Un flot de conception complet assurant la synthèse depuis une spécification système de contrôleurs de nœuds d'un réseau de capteurs a été proposé dans [1]. Dans cette approche les parties calcul et contrôle d'un nœud de capteur sont constituées d'un ensemble de micro-tâches matérielles qui sont activées selon un principe événementiel, chacune étant dédiée à une tâche spécifique du système comme par exemple le relevé de paramètres, la couche MAC, le routage ou le traitement des données. Le flot prend en entrée une spécification de haut niveau du graphe flot de tâches associant le langage C et un langage spécifiquement conçu pour ce domaine. Il génère automatiquement la description architecturale de ces micro-tâches sous la forme de blocs matériels spécialisés, constitués d'une machine à états finis (FSM) et de chemin de données (datapath), associés à une gestion système des tâches et des mémoires pour une exécution de l'ensemble du contrôle du nœud, comme le montre la Fig. 2. L'architecture est de plus optimisée en énergie, en particulier lors des périodes d'inactivité, grâce à l'utilisation des techniques de power gating. Même si le flot de conception permet un prototype rapide, le matériel généré est cependant spécifique au code synthétisé et la flexibilité est donc extrêmement limitée.

# 0.1.1 Espace de conception de contrôleurs flexibles pour les nœuds de capteurs

La fonction primaire d'un contrôleur de nœuds de capteurs est de gérer des ressources matérielles incluant des chemins de données de calcul, des horloges, des interruptions, des générateurs d'événements, des mémoires, des périphériques, des gestionnaires d'alimentation et des gestionnaires globaux. Il a été estimé que jusqu'à 25% de la consommation

FIGURE 2: Un graphe de micro-tâches et la vue système de l'architecture générée par le flot de conception proposé dans [1].

globale d'un nœud est due au contrôle. Grâce à leur flexibilité, les micro-contrôleurs sont une cible privilégiée pour cette tâche, comme le montre à l'évidence leur utilisation dans de nombreuses plateformes [5, 6, 7]. Un large spectre de techniques de réduction de la consommation d'énergie allant de la coupure d'horloge *(clock gating)* à la conception sous le seuil en passant par la coupure d'alimentation *(power gating)*, [8, 9, 10] a été utilisé dans ce type de micro-contrôleurs. Cependant, ces cibles sont encore loin d'être des solutions optimales dans nombre d'applications, du fait que l'exécution séquentielle des différentes étapes du contrôle implique une forte consommation de la logique du processeur.

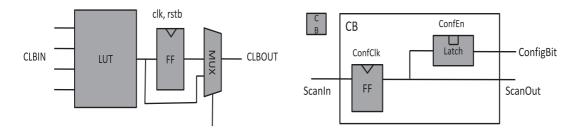

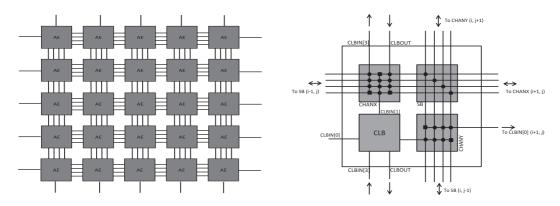

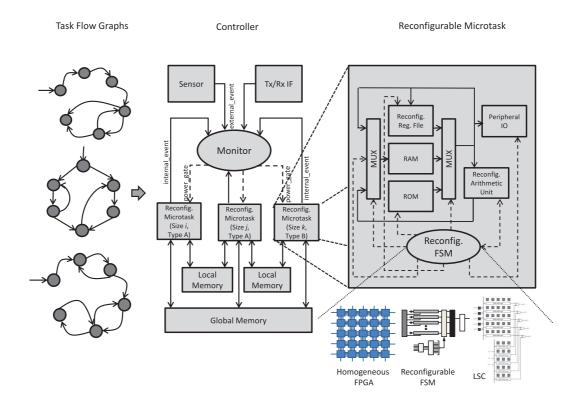

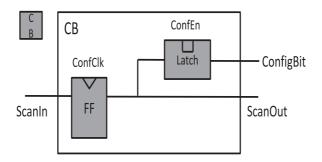

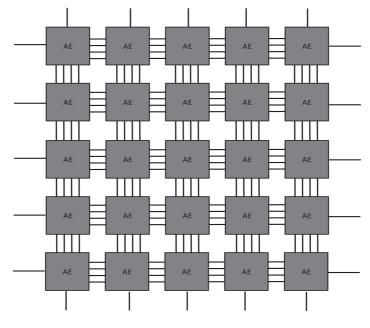

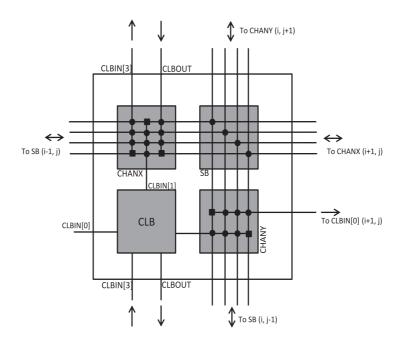

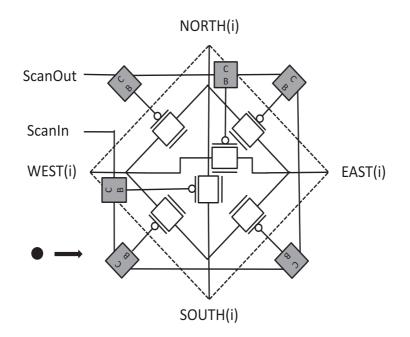

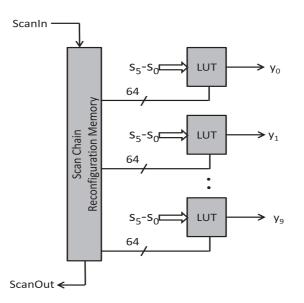

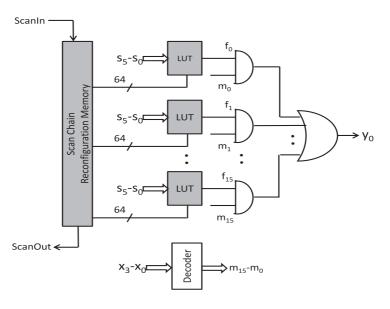

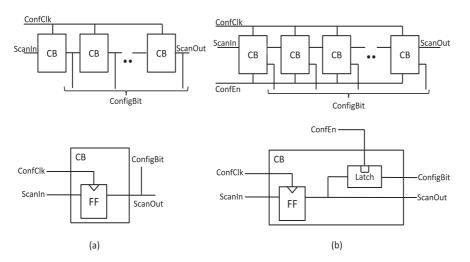

Dans les contrôleurs de WSN qui nécessitent de supporter de multiples graphes de tâches, les processeurs reconfigurables offrent à la fois use grande flexibilité et une réduction des coûts de prototype et de production par comparaison aux solutions ASIC. Une architecture reconfigurable communément utilisée, et nommée Embedded FPGA (eFPGA) dans ce travail, est une fabrique homogène contenant de nombreux blocs logiques configurables (CLB) associés à un réseau d'interconnexions programmable permettant de connecter les différents CLB entrée eux [11, 12]. Un CLB est constitué d'une table de correspondance (lookup table) à K entrées (K-LUT), de bits de configuration (CB) et d'une bascule que l'on peut ajouter pour mémoriser la sortie sur un cycle d'horloge. Une LUT est un ensemble de  $2^{K}$  éléments mémoire sur un bit qui content la table de vérité d'une fonction décodée par les K variables d'entrées. Le CLB d'une LUT à 4 entrées et le bit de configuration utilisé dans un élément mémoire sont représentés à la Fig. 3. Une vue complète de la matrice du eFPGA et son élément de base sont quant à eux montrés Fig. 4. Une estimation de la consommation de puissance pour cinq FSM issues du benchmark SenseBench [13] implémentées dans une technologie CMOS 65nm est donnée dans le tableau 1. La puissance consommée est comparable à celle d'un micro-contrôleur faible

consommation [1] et, clairement, le matériel flexible des architectures reconfigurables de type FPGA n'est pas aussi efficace en énergie que les circuits dédiés, ce qui pose un problème pour les contraintes énergétiques requises par les applications des WSN.

FIGURE 3: Structure d'un CLB et d'un CB dans le eFPGA.

FIGURE 4: Vue système de la matrice du eFPGA et un élément de celle-ci contenant les canaux de routage et la matrice d'interconnexions programmables.

| eFPGA       | Total Power of FSM (mW)    |                             |  |  |  |

|-------------|----------------------------|-----------------------------|--|--|--|

| erroa       | $f_{clk} = 20 \text{ MHz}$ | $f_{clk} = 100 \text{ MHz}$ |  |  |  |

| abs         | 0.79                       | 1.93                        |  |  |  |

| Crc8        | 1.39                       | 3.32                        |  |  |  |

| receiveData | 1.58                       | 3.74                        |  |  |  |

| Crc16       | 2.70                       | 6.77                        |  |  |  |

| firBasic    | 4.71                       | 13.29                       |  |  |  |

TABLE 1: Consommation de puissance (mW) pour cinq FSM issues de SenseBench synthétisées sur un eFPGA.

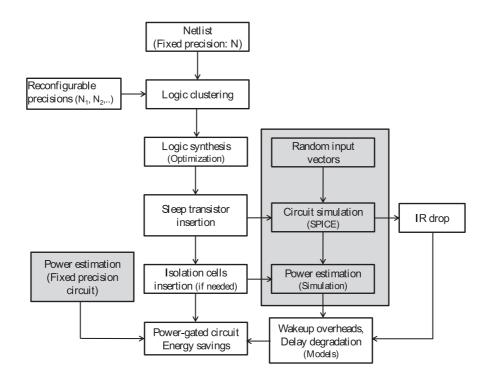

#### 0.1.2 Contrôleurs reconfigurables à faible consommation

Dans cette thèse, des unités arithmétiques à précision variable pour les chemins de données et des architectures modulables pour des FSM reconfigurables à très fable consommation sont explorées comme cible matériel pour des micro-tâches flexibles. La coupure d'alimentation est utilisée comme technique de réduction d'énergie aux niveaux circuit et architecture pour les FSM et les chemins de données des micro-tâches telles que décrits dans [1]. Ceci implique une étude extensive des problèmes liés à la conception d'un circuit utilisant la coupure d'alimentation. Des modèles au niveau porte pour l'estimation des paramètres clés des circuits à coupure d'alimentation sont tout d'abord dérivés. Ensuite, deux blocs matériels de micro-tâches, c'est-à-dire un additionneur et une machine d'états, sont optimisés en termes de consommation d'énergie. Dans les deux cas, la reconfigurabilité est considérée comme élément clé pour une conception matérielle flexible. Tandis que dans les additionneurs la reconfiguration est utilisée pour faire varier dynamiquement la précision, dans les FSM reconfigurables, des architectures modulaires avec plusieurs degrés de complexité et de flexibilité sont proposées. Finalement, les modèles sont appliqués pour analyser différents paramètres de conception dans la logique des FSM et des additionneurs utilisant le *power-gating*.

FIGURE 5: Structure d'un contrôleur flexible pour micro-tâche reconfigurable.

### 0.2 Modèles pour les circuits à coupure d'alimentation

## 0.2.1 Circuit et opération équivalents d'un circuit à coupure d'alimentation

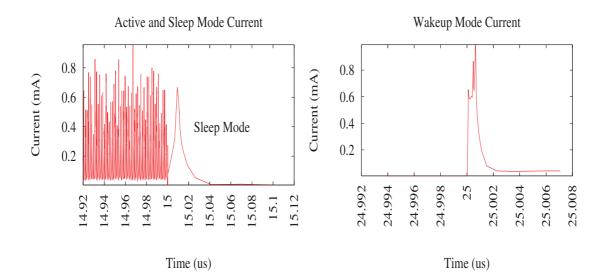

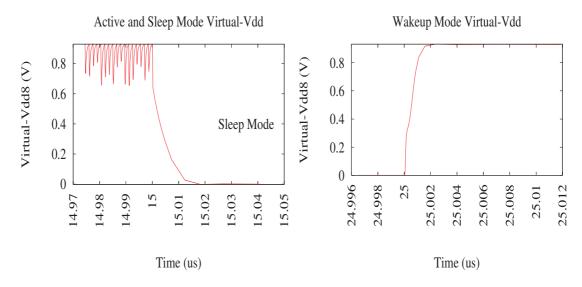

Tandis que les transistors MOSFET voient leur dimension se réduire en dessous de 100nm, une augmentation exponentielle du courant de fuite est observée à cause de la réduction de la tension de seuil  $(V_{th})$  opérée pour maintenir la commande grille à des valeurs correctes [14]. Une structure de *power-gating* coupe la tension d'alimentation des transistors MOS d'une cellule logique de façon à ce que les courants de fuite soient réduits de façon significative pendant les phases de repos. Un exemple de circuit de coupure d'alimentation est donné à la Fig. 6. Il est constitué d'un transistor PMOS ayant une tension de seuil  $V_{th}$  haute, connecté entre le rail d'alimentation  $V_{dd}$  et le nœud de tension d'alimentation virtuelle  $V_{Vdd}$  du bloc logique. Un bloc logique est ici un ensemble de portes logiques dont la tension d'alimentation sera coupée par ce transistor de mise en veille, dont la grille est connectée à un signal de contrôle SLEEP pour commander le bloc entre les états on et off. Un circuit à coupure d'alimentation opère donc dans trois modes : actif, veille et réveil dans un cycle typique de power gating, comme indiqué Fig. 7.

FIGURE 6: (a) Cluster logique à coupure d'alimentation. (b) Circuit équivalent.

FIGURE 7: Un chronogramme temporel typique et les différents modes d'opérations dans un cycle typique de *power gating*.

#### 0.2.2 Temps et énergie de réveil

Dans ce travail, nous avons proposé de dériver les profils des courants de fuite pour un circuit complet en utilisant une approche basée sur des approximations polynomiales. Soit un bloc logique à coupure d'alimentation composé de cellules logiques standards issues d'une bibliothèque, le courant statique total pour  $n(S_i, j)$  occurrences de chaque cellule  $S_i$  est

$$I_{leak} = \sum_{i=0}^{P-1} \sum_{j=0}^{R_i-1} n(S_i, j) I_{leak}(S_i, j)$$

où  $I_{leak}(S_i, j) = \sum_{k=0}^{N} b_k(S_i, j) V_{Vdd}^k$  est use approximation polynomiale obtenue à partir de simulations au niveau transistor plus précises, P et  $R_i$  sont le nombre de types de cellules et le nombre de combinaisons potentielles de la cellule  $S_i$  respectivement. La capacité totale du bloc logique est obtenue comme la somme des capacités de toutes les entrées des cellulose standards qui le constituent  $C_L = \sum_{i=0}^{P-1} \sum_{j=0}^{R_i-1} n(S_i, j) C_{ij}$ . La résolution des équations

$$\frac{dV_{Vdd}}{dt} = -\frac{1}{\tau} \sum_{i=0}^{N} c_i V_{Vdd}^i$$

$\operatorname{et}$

$$\frac{dV_{Vdd}}{dt} = -\frac{1}{\tau} (V_{Vdd} - r_1)(V_{Vdd} - r_2)$$

avec  $\tau = R_{lin}C_L$ ,  $c_i = f_i(V_{dd}, R_{lin}, b_i, V_{th})$ , ainsi que d'autres heuristiques pour le courant dans la région de saturation, aboutissent à une expression pour  $V_{Vdd}(t)$  (avec un comportement comme montré sur la Fig. 8) à partir de laquelle le temps de réveil peut être déterminé comme  $T_{wu} = T_{(V_{Vdd}=r_1)}$  en prenant l'hypothèse que  $V_{Vdd} = V_{sleep}$  à t = 0.  $R_{lin}$  et  $r_1$  représentent ici la résistance du transistor de mise en veille en région linéaire et l'état de  $V_{Vdd}$  au début du mode actif, respectivement. De plus, les gains en énergie dans le bloc logique avec power gating par rapport à celui sans coupure d'alimentation sont donnés par

$$E_s = V_{dd}I_{leak}(V_{dd})T_{sleep} - \int_0^{T_{sleep}} V_{Vdd}I_{leak}(V_{Vdd})dt.$$

Le surcoût en énergie dû au réveil peut être estimé en sommant les  $N_{wu}$  intervalles sur la courbe  $I_{st}(t)$  de taille  $\Delta t$  in  $[0, T_{wu}]$  selon

$$E_{wu} \approx V_{dd} \sum_{i=0}^{N_{wu}-1} I_{st_i} \Delta t$$

où  $I_{st}(t)$  est le courant dans le transistor de mise en veille. Ainsi, plusieurs paramètres de conception sont obtenus depuis des caractérisations polynomiales simples du courant

statique dépendant de la tension d'alimentation dans des portes logiques. Des résultats expérimentaux montrent que les temps de réveil et l'énergie de réveil sont estimés avec une erreur moyenne de 16% et 13% respectivement par rapport à des simulations SPICE sur des circuits issus des benchmark ISCAS85.

FIGURE 8: Virtual-Vdd en modes réveil et veille (W= $1.2\mu$ m) pour le benchmark c7552.

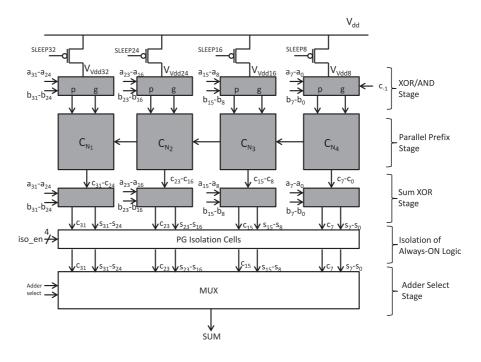

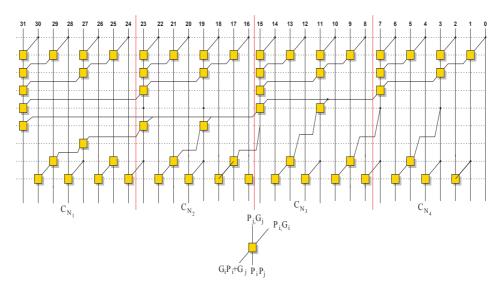

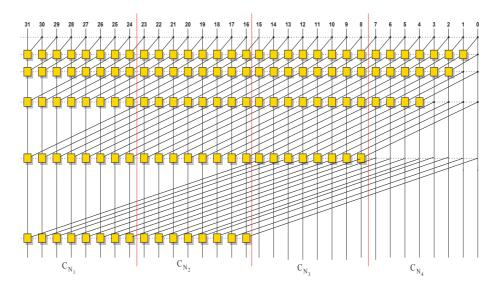

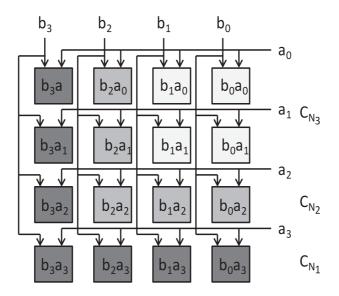

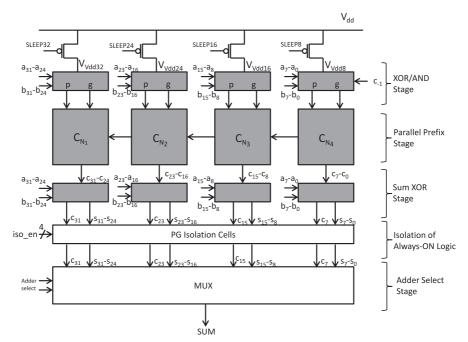

### 0.3 Additionneur faible consommation à précision variable

Les circuits arithmétiques ayant des tailles d'entrée fixes sont des sources de gaspillage d'énergie lorsque des données de précision plus faibles doivent être calculées pendant de longues périodes de temps. Sachant que ces opérateurs arithmétiques sont des structures denses mais régulières pouvant être implémentées avec des tailles de mots et du parallélisme à des granularités diverses, ils pourraient être configurés pour des précisions plus faibles conjointement avec une suppression des courants de fuite inutiles dans les portes logiques inutilisées. Les additionneurs sont utilisés dans la logique d'adressage et de séquencement (boucles) des microprocesseurs tandis que les multiplieurs font partie intégrante des chemins de données de calcul. Dans ce travail nous nous sommes concentrés sur les additionneurs comme composant des chemins de données intégrés aux micro-tâches matérielles de [1]. Une approche générale est considérée pour partitionner la logique d'un additionneur d'une taille donnée en différents blocs logiques supportant des précisions intermédiaires, et en appliquant des coupures d'alimentation pour éteindre les blocs inutilisés en fonction de la précision considérée. La méthode est utilisée sur deux additionneurs à préfix parallèle de Brent-Kung (BK) [15] et de Kogge-Stones (KS) [16]. Deux additionneurs 32 bits pouvant être configurés comme des additionneurs 8 bits, 16 bits ou 32 bits, sont décrits. Une comparaison de leur puissance consommée avec celle de l'additionneur 32 bits non flexible montre des potentiels de réduction de la puissance

par un facteur all ant de 8 à 13 pour des augmentations en surface de 15% et 9.2% respectivement.

FIGURE 9: Additionneur reconfigurable à coupure d'alimentation.

| Function             | $I_{max,ac}$ (mA) |      | $P_{active}$ | $_{,av}(\mu W)$ | $P_{idle,av}(\mu W)$ |      |  |

|----------------------|-------------------|------|--------------|-----------------|----------------------|------|--|

| 1 unction            | BK                | KS   | BK           | KS              | BK                   | KS   |  |

| addition sur 32 bits | 4.92              | 4.61 | 222.3        | 240.7           | 55.5                 | 62.9 |  |

| addition sur 24 bits | 4.22              | 3.86 | 185.2        | 200.6           | 55.8                 | 62.8 |  |

| addition sur 16 bis  | 2.92              | 2.63 | 142.6        | 152.8           | 55.4                 | 62.3 |  |

| addition sur 8 bits  | 1.80              | 1.59 | 102.4        | 104.8           | 55.1                 | 61.9 |  |

TABLE 2: Consommation de puissance pour des additionneurs BK et KS sans coupure d'alimentation.

| Adder                |      | (A)  | $P_{acti}$ $(\mu)$ | we,av<br>W) | $P_{idl}$ $(\mu)$ |      | $P_{slee}$ $(\mu V)$ |     |

|----------------------|------|------|--------------------|-------------|-------------------|------|----------------------|-----|

|                      | BK   | KS   | BK                 | KS          | BK                | KS   | BK                   | KS  |

| additionneur 32 bits | 1.91 | 2.02 | 223.8              | 286.2       | 60.5              | 81.7 | 8.6                  | 8.7 |

| additionneur 24 bits | 1.52 | 1.56 | 171.8              | 218.9       | 47.7              | 62.5 | 7.8                  | 8.2 |

| additionneur 16 bits | 1.17 | 1.09 | 118.3              | 139.5       | 34.8              | 40.1 | 7.3                  | 7.6 |

| additionneur 8 bits  | 0.73 | 0.75 | 65.1               | 66.1        | 20.9              | 20.7 | 6.8                  | 7.0 |

TABLE 3: Consommation de puissance pour des additionneurs reconfigurables BK etKS avec coupure d'alimentation.

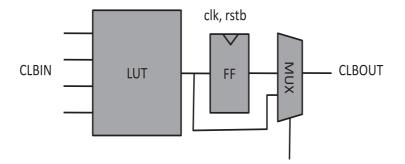

### 0.4 Machines à états reconfigurable avec *power-gating*

La mise en œuvre de machines à états (Finite State Machine) consiste en deux blocs combinatoires notés  $\mathbf{F}$  et  $\mathbf{G}$  ainsi qu'un ensemble d'éléments de mémorisation (registres)  $\mathbf{S}$  synchronisés sur un signal d'horloge. La valeur des n entrées de la machine à états à un instant t est représentée par le vecteur  $\mathbf{x}(t) = [x_0(t), x_1(t), ..., x_{n-1}(t)]$ , la valeur des msorties de cette machine à états par  $\mathbf{y}(t) = [y_0(t), y_1(t), ..., y_{m-1}(t)]$ . Enfin, la valeur des N bits du registre d'états est noté  $\mathbf{s}(t) = [s_0(t), s_1(t), ..., s_{N-1}(t)]$ . Soit  $f_i$  une fonction booléenne dans  $\mathbf{F}$  et  $g_j$  une fonction booléenne dans  $\mathbf{G}$ .

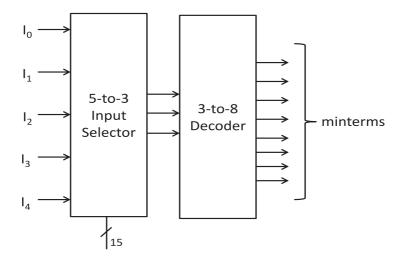

L'ensemble de fonctions de transition  $s_i(t + 1)$  et de commande  $y_j$  représentées par  $s_i(t+1) = f_i(\mathbf{x}(t), \mathbf{s}(t)), i = 0, 1, ..., N-1$  et  $y_j(t) = g_j(\mathbf{s}(t)), j = 0, 1, ..., m-1$  décrivent une FSM de Moore [17] tandis que celles représentées pas  $s_i(t + 1) = f_i(\mathbf{x}(t), \mathbf{s}(t)), i = 0, 1, ..., N-1$  and  $y_j(t) = g_j(\mathbf{x}(t), \mathbf{s}(t)), j = 0, 1, ..., m-1$  représentent des FSM de Mealy [18]. La réécriture de la fonction de transition en utilisant sa décomposition de Shannon nous permet d'obtenir  $s_i(t+1) = \sum_{k=0}^{2^{(n+N-K)}-1} m_k f_i(n(m_k), ..., s_{N-1})_k$  avec K correspondant au nombre de variables dont dépend  $f_i(.)_k$  après cette décomposition. Le minterm généré par les n+N-K premières variables d'entrées de la séquence  $x_i, ..., s_i(t+1)$  s'écrit  $m_k$ , par exemple  $m_1 = x'_{n+N-K-1}x'_{n+N-K-2}...x_0$ . Le vecteur motif binaire correspondant au minterm  $m_k$  est représenté par  $n(m_k)$ , par exemple on aura  $n(m_1) = 000...01$ . Pour un  $f_i$  donné, la fonction peut-être réalisée comme un assemblage de porte logiques, cependant si l'on souhaite permettre la reconfigurabilité, il est nécessaire de réaliser  $f_i(.)_k$  comme une LUT (Look-Up-Table ou mémoire tabulée) qui pourra être reconfigurée en fonction de la machine à état à implanter.

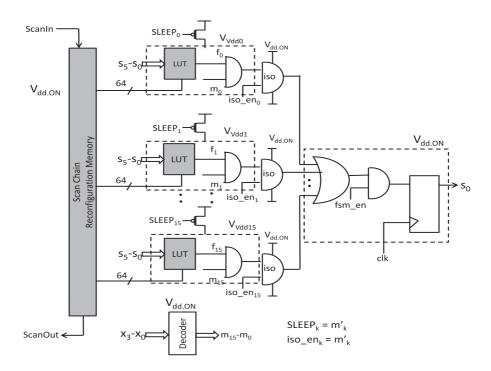

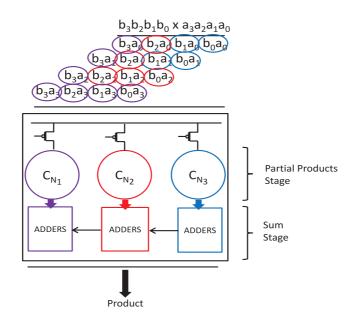

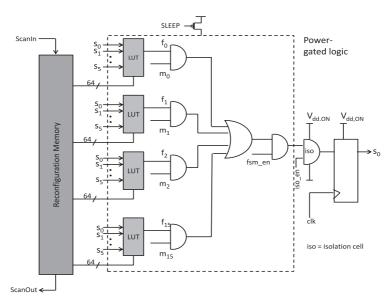

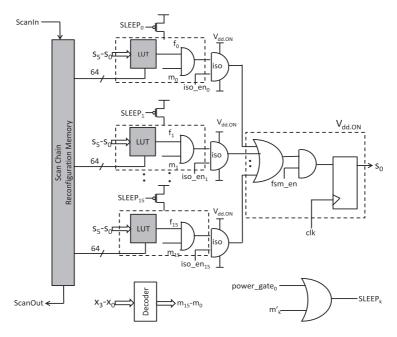

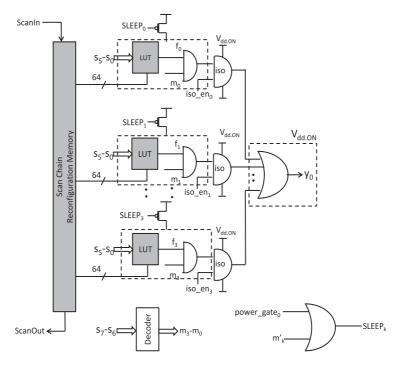

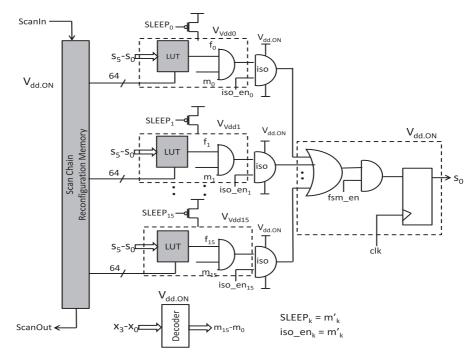

#### 0.4.1 Utilisation de la technique de coupure d'alimentation

Les possibilités de *power gating* sont utilisées comme illustré dans la figure Fig. 10, qui est dérivée de la décomposition de Shannon d'une fonction de transition à un niveau de granularité de type LUT combiné à un ensemble de porte AND.

Le réseau de transistors de coupure nécessite autant de signaux de contrôle que de LUT. L'opération de *power gating* peut-être expliquée comme suit. Quand la FSM reconfigurable est configurée en une FSM spécifique, son fonctionnement dépend d'un sous ensemble de ses entrées qui varie en général assez peu dans le temps, de ce fait, suivant les valeurs de ces entrées, tous les *minterms* s'évaluent à 0. Il est également possible que certaines entrées n'interviennent pas dans l'équation logique définissant certains bits du registre d'état, là encore les *minterm* correspondant s'évaluent à 0.

Il donc possible d'exploiter ces propriétés afin de couper l'alimentation de certaines LUT même lorsque la FSM est active, tant que le *minterm* qui leur est associé ne change pas de valeur (sa valeur dépendant elle même des entrées de la FSM). Ces sorties de

FIGURE 10: Modèle architectural de FSM reconfigurable, tel qu'il a été utilisé pour la validation expérimentale.

décodage peuvent fonctionner comme des signaux de contrôle qui serviront à couper l'alimentation de ces LUT évitant ainsi le recours à un contrôleur externe. Cette technique de *power gating* induit un coût plus important en termes de surface du fait de l'utilisation de cellules d'isolation [19] mais aussi en termes de réactivité (délais et dissipation énergétique causés par les phases de réveil [20]. Il est important d'indiquer que des technique similaires (opérant à des niveaux de granularité divers) peuvent être utilisées pour les fonctions de sortie.

Pour des architectures basées sur une granularité de power gating au niveau LUT, telles que proposées plus haut, on peut remarquer qu'à un instant donné, il n'y a qu'une seule LUT par bit d'état (ou de sortie) en mode actif, les autres pouvant être mises en veille. En d'autres termes, la consommation électrique à un instant donné ne dépend que de ces N + m LUT, ceci indépendamment du coût (en nombre de LUT) de la FSM qui varie (dans le cas conservatif) comme une fonction exponentielle du nombre d'entrées, d'états et de sorties. Il faut néanmoins également comptabiliser les sources de dissipation énergétiques liées aux bits de configuration et aux cellules d'isolation.

Il faut également remarquer que pour chaque changement de l'entrée du décodeur, le *minterm* actif change également, et par conséquent, tous les *minterms* actifs peuvent être désactivés (par *power gating*). Par conséquent, un changement des valeurs en entrée induit des surcoûts en termes de temps de réaction et d'énergie causés par la phase de réveil correspondant à l'activation d'un *minterm*. Des gains en dissipation énergétique seront toutefois possibles lorsque la fréquence de fonctionnement de la FSM est peu élevée. De

plus, pour les FSM dont le nombre d'états et de sorties est inférieur au seuil maximum de l'architecture proposée, les LUT inutilisées peuvent également être désactivées par *power gating*.

#### 0.4.2 Estimation de puissance

Une estimation de la consommation électrique pour un ensemble de machines à états utilisant la technique proposée est fournie dans le tableau 4. Les résultats ont été obtenus à partir de simulations SPICE. Une comparaison avec les estimations de puissance et d'énergie pour des FSM implantées sur un eFPGA indiquent une amélioration de la consommation électrique pour les FSM de taille importante en faveur de notre approche.

|             | Puissance d                | issipée (mW)                | Energie par opération (pJ) |                             |  |

|-------------|----------------------------|-----------------------------|----------------------------|-----------------------------|--|

|             | $f_{clk} = 20 \text{ MHz}$ | $f_{clk} = 100 \text{ MHz}$ | $f_{clk} = 20 \text{ MHz}$ | $f_{clk} = 100 \text{ MHz}$ |  |

| abs         | 0.35                       | 0.75                        | 17.76                      | $7.54 \ (7.92)^{a}$         |  |

| Crc8        | 0.51                       | 1.13                        | 25.46                      | 11.30(11.45)                |  |

| receiveData | 0.64                       | 1.46                        | 32.23                      | 14.56(14.54)                |  |

| Crc16       | 0.59                       | 1.32                        | 29.38                      | 13.21 (13.22)               |  |

| firBasic    | 0.63                       | 1.41                        | 31.31                      | 14.14 (14.10)               |  |

<sup>a</sup>Estimation extrapolée à partir de simulations SPICE

TABLE 4: Puissance et énergie moyennes par opération pour des FSM implantées sur une architecture à base de *power gating*.

## 0.5 Contributions

Les contributions de ce travail sont résumées ci-dessous.

- 1. Nous avons proposé un modèle semi-empirique pour estimer le temps de réveil pour des clusters logiques exploitant la coupure d'alimentation *power gating*. Étant donnée une description de circuit au niveau porte et une caractérisation compacte de son organisation en termes de portes logiques et de transistors de coupure, notre approche permet d'estimer très rapidement le temps de réveil de chaque bloc avec un taux d'erreur avoisinant les 16%. Elle permet donc d'obtenir des estimations précises tout en évitant de recourir à des simulations au niveau transistor, bien trop longues pour pouvoir être utilisées.

- 2. La puissance statique d'un bloc logique quelconque peut-être estimée avec une précision de 3% en utilisant un modèle analytique par approximation polynomiale du courant statique au niveau porte. Par ailleurs, d'autres paramètres clés des circuits exploitant le *power gating*, à savoir la valeur de la tension d'alimentation en régime permanent en mode actif et veille, le coût en énergie des phases de réveil ainsi que les gains globaux s'obtiennent directement à partir de ce modèle ou à

l'aide de simples extensions. Ces modèles, lorsque utilisés ensemble, peuvent servir en tant qu'outils d'estimation rapide qui pourront servir à guider le reste du flot de conception.

- 3. Nous proposons une approche de partitionnement appliquée à l'exploitation du power gating pour des circuits arithmétiques denses et réguliers (p. ex. : additionneurs ou multiplieurs). Notre approche permet leur utilisation comme des opérateurs à précision variable. Nos résultats indiquent que des gains en consommation allant jusqu'à 30% peuvent être obtenus. Nous avons également utilisé la possibilité de déterminer un seuil de précision au dessus duquel il est possible de réduire la puissance dynamique. Celui ci peut ensuite aider à la dérivation d'un ordonnancement du signal de coupure d'alimentation en vue d'obtenir une consommation minimale.

- 4. Nous avons proposé un modèle extensible d'architecture reconfigurable pour la mise en œuvre de FSM. Ce modèle se base sur la décomposition de Shannon des fonctions de transition et de décodage. Nous avons identifié des possibilités de réduire significativement la puissance statique dissipée (en mode actif) grâce a l'utilisation du *power gating* directement au niveau de la couche de reconfiguration. Ce modèle permet d'obtenir un niveau de consommation électrique intermédiaire entre une approche complètement programmable à base de micro-contrôleur et une approche complètement dédiée à base de micro-tâches matérielles spécialisées. Notre modèle d'architecture est donc une alternative intéressante combinant flexibilité et efficacité énergétique.

## 0.6 Conclusion

Dans ce travail, nous avons proposé l'utilisation d'architectures reconfigurables exploitant la technique de *power gating*, afin d'offrir une approche flexible à la mise en œuvre de nœuds de réseaux de capteurs basés sur le principe de micro-tâche matérielle. Nous avons exploité les propriétés structurelles des automates à mettre en œuvre afin de réduire le coût en interconnexion et la logique de sélection à un niveau minimal tout en garantissant un bon passage à l'échelle pour des machines à états plus complexes. Nous avons également proposé des modèles pour l'estimation rapide des surcoût liés aux temps de réveil ainsi que pour d'autres paramètres importants pour une conception au niveau porte logique exploitant les coupures d'alimentation. Nous avons ainsi montré que le délai de réveil est un élément clé qui contribue grandement dans le bilan énergétique global (en mode actif) des FSM reconfigurables à base de *power gating*. Enfin, nous discutons l'efficacité énergétique de notre approche en la mettant en regard du surcoût en surface induit par l'utilisation d'une forme de reconfiguration.

#### 0.6.1 Efficacité énergétique

Une bonne métrique permettant d'évaluer l'efficacité énergétique des différentes réalisations est l'énergie moyenne dissipée par instruction. Le tableau 5 évalue cette métrique pour différentes tâches et stratégies de réalisation matérielle utilisées dans ce travail. Ainsi, l'énergie équivalente par instruction pour une micro-tâche  $E_{eff}$  s'obtient par

$$E_{eff} = \frac{E_{task}}{N_{inst}} \tag{1}$$

où l'énergie par tâche  $E_{task}$  est obtenue selon

$$E_{task} = N_{states} E_{op,MT}.$$

(2)

et où  $N_{states}$  est le nombre d'opérations (ou transitions d'états de la FSM) nécessaires à l'exécution de la tâche et  $E_{op,MT}$  correspond à l'énergie moyenne par opération d'un micro-tâche.

Les résultats du tableau indiquent que l'efficacité énergétique de l'approche à base de micro-tâches reconfigurables se situe entre celle d'une approche à base de micro-contrôleur programmable très faible consommation et celle à base de micro-tâches spécialisées, ce qui était l'objectif à l'origine de ces travaux.

|             | Energie équivalente par instruction (pJ/Inst.) |           |                                     |           |                          |           |  |

|-------------|------------------------------------------------|-----------|-------------------------------------|-----------|--------------------------|-----------|--|

| Micro-tâche | openMSP430 $[1]^a$                             |           | Micro-tâche                         |           | Micro-tâche              |           |  |

| where-tache |                                                |           | $\operatorname{Reconfigurable}^{b}$ |           | Câblée 16 bits $[1]^{a}$ |           |  |

|             | Ninst                                          | $E_{eff}$ | $N_{states}$                        | $E_{eff}$ | $N_{states}$             | $E_{eff}$ |  |

| Crc8        | 30                                             | 163       | 71                                  | 31.60     | 71                       | 8.1       |  |

| receiveData | 66                                             | 230       | 332                                 | 83.53     | 332                      | 15.7      |  |

| Crc16       | 27                                             | 170       | 73                                  | 41.27     | 73                       | 9.3       |  |

| firBasic    | 58                                             | 179       | 168                                 | 46.90     | 168                      | 26.1      |  |

<sup>a</sup>130nm, @16MHz

$^{b}65\mathrm{nm},$  multiple  $V_{th}$  cells, @100MHz, 16×16 register file, no SRAM  $^{c}65\mathrm{nm},$  std.- $V_{th}$  cells

TABLE 5: Coût en énergie par instruction pour trois réalisation de contrôleurs.

#### 0.6.2 Le coût de la flexibilité

Un revers important de la flexibilité est le surcoût en surface comparé à une approche à base de micro-tâches spécialisées. En se basant sur les résultats de Pasha et al. [1], il peut être montré que le surcoût en surface d'une micro-tâche reconfigurable est jusqu'à 19 fois plus élevé que sa version spécialisée, comme indiqué Table 6. Ce surcoût en surface doit-être envisagé sous deux angles différents. Dans ce travail, les architectures proposées garantissent que toute FSM satisfaisant certaines contraintes (en terme de nombre d'états, de commandes, etc.) pourra être implantée sur une micro-tache reconfigurable. Ce n'est pas le cas d'approches basées sur un eFPGA ou sur micro-tâches spécialisées.

| Microtask   | Spécialisées             | Reconfigurable        | eFPGA $(\mu m^2)$ | openMSP-       |

|-------------|--------------------------|-----------------------|-------------------|----------------|

|             | Microtask $[1](\mu m^2)$ | Microtask $(\mu m^2)$ | (217  CLBs)       | $430(\mu m^2)$ |

| Crc8        | 3097                     | 140522.2              | 1076871           | 22141          |

| receiveData | 2858                     |                       |                   |                |

| Crc16       | 3102                     |                       |                   |                |

| firBasic    | 7164                     |                       |                   |                |

TABLE 6: Comparaison des coûts en surface des FSM spécialisées par rapport aux FSMreconfigurables (pour une chemin de données sur 16 bits).

De plus, le nombre de micro-tâches dans une plateforme pour nœud de réseau de capteurs peut varier et aller jusqu'à 40 ou 50. La coût en surface correspondant à une telle implémentation est donc significatif, et est susceptible de dépasser celui d'une approche à base de micro-tâches reconfigurables. En principe, une unique micro-tâche reconfigurable peut-être utilisée en lieu et place d'un ensemble de micro-tâches spécialisées en utilisant une forme de multiplexage temporel. Le contrôleur du nœud nécessite encore dans ce cas un moniteur système pour assurer la reconfiguration et le contrôle global de la plateforme.

## Chapter 1

# Introduction

Convergence of computing and communications has led to development of new portable, handheld, battery-powered products for multimedia and wireless applications. A testimony to this fact is the advent of smartphones which, in association with advanced wireless communication networks, are able to deliver comprehensive user experience of nearly anywhere, anytime telephony and multimedia applications. The onboard software driving these embedded systems process multimedia content requiring intensive computations. Other consumer electronic products based on such a convergence include tablets, portable computers and wireless peripheral devices.

Another class of applications that has gained importance are broadly based on what are referred to as Wireless Sensor Networks (WSNs). The fundamental unit of a WSN is called a node. Typically, but not necessarily, nodes have an additional function of sensing along with computing and communications [21]. Such an integration of functions leads to several applications [2, 3] - weather monitoring, surveillance for security, personal health care, vehicular traffic management, energy efficient buildings, etc. An anticipated evolution of mobile devices into WSN nodes would merge the two sets of applications into one (e.g., 'Cloud Health Care' [4]). A characteristic feature of WSNs is the possibility of using a large number of nodes in a number of untethered ways. For example, a node can be a controller of other nodes, a communicating agent with sensing, a transmitter, repeater, or a receiver. They may be configured to operate in different network topologies. Further, nodes may change their behaviour dynamically over time. The ubiquity of nodes requires that they offer flexibility while also satisfying power and performance constraints.

Wireless Sensor Network nodes have been realized on various technological platforms. One of the most common technologies used in WSN nodes has been the complementary metal-oxide-semiconductor (CMOS) integrated circuit (IC) technology as is also the case with a large number of electronic systems in the last fifty years. A key driver behind the success of CMOS circuits has been the continuous scaling of devices to nanoscale dimensions and consequent high density of device integration. The predictability of scaling has been captured by Moore's 'law' [22] which states that the integration density of MOS transistors doubles approximately every two years. The International Technology Roadmap for Semiconductors (ITRS) [23] had indicated downscaling of physical gate length of MOS transistors from 65nm in the year 2002 to 22nm in 2012. The technological feasibility of integrating a very large number of MOS devices has brought about challenges in identifying trade-offs in power consumption, performance, sizes of integrated circuits and cost of final products. A critical study of interrelationships between functional convergence in WSN nodes, energy requirements and design automation is necessary to explore the design space for energy efficient solutions.