# Nouvelles Topologies des diviseurs de puissance, balun et déphaseurs en bandes RF et millimétiques, apport des lignes à ondes lentes

François Burdin

## ► To cite this version:

François Burdin. Nouvelles Topologies des diviseurs de puissance, balun et déphaseurs en bandes RF et millimétiques, apport des lignes à ondes lentes. Autre. Université Grenoble Alpes, 2013. Français. <NNT : 2013GRENT018>. <tel-00903675>

# HAL Id: tel-00903675 https://tel.archives-ouvertes.fr/tel-00903675

Submitted on 12 Nov 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano-Électronique et Nano-Technologies

Arrêté ministériel : 7 août 2006

Présentée par

# François BURDIN

Thèse dirigée par **Philippe FERRARI** et codirigée par **Florence PODEVIN**

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal

# Nouvelles topologies de diviseurs de puissance, baluns et déphaseurs en bandes RF et millimétriques, apport des lignes à ondes lentes

Thèse soutenue publiquement le **16 Juillet 2013**, devant le jury composé de :

M. Christophe GAQUIERE

Professeur des universités, Lille, Président

M. Roberto SORRENTINO

Professeur des universités, Pérouse (Italie), Rapporteur

M. Eric KERHERVE

Professeur des universités, Bordeaux, Rapporteur

M. Daniel GLORIA

Ingénieur STMicroelectronics, Crolles, Membre

M. Tibor BERCELI

Professeur des universités, Budapest (Hongrie), Invité

M. Philippe FERRARI

Professeur des universités, Grenoble, Directeur de thèse

Mme. Florence PODEVIN

Maître de conférences, Grenoble, Co-encadrant de thèse

# Résumé

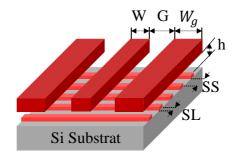

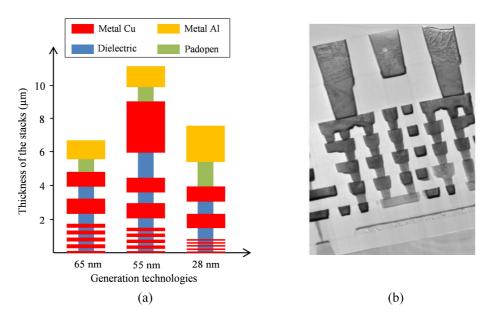

L'objectif de cette thèse a été premièrement de réaliser des dispositifs passifs intégrés à base de lignes à onde lentes nommées S-CPW (pour « Slow-wave CoPlanar Waveguide ») aux fréquences millimétriques. Plusieurs technologies CMOS ou BiCMOS ont été utilisées: CMOS 65 nm et 28 nm ainsi que BiCMOS 55 nm.

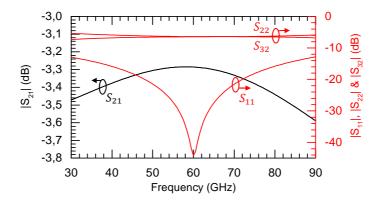

Deux baluns, le premier basé sur une topologie de rat-race et le second basé sur un diviseur de puissance de Wilkinson modifié, ainsi qu'un inverseur de phase, ont été réalisés et mesurés dans la technologie CMOS 65 nm. Les résultats expérimentaux obtenus se situent à l'état de l'art en termes de performances électriques. Un coupler hybride et un diviseur de puissance avec des sorties en phase sans isolation ont été conçus en technologie CMOS 28 nm. Les simulations montrent de très bonnes performances pour des dispositifs compacts. Les circuits sont en cours de fabrication et pourront très bientôt être caractérisés. Ensuite, une nouvelle topologie de diviseurs de puissance, avec sorties en phase et isolé a été développée, offrant une grande flexibilité et compacité en comparaison des diviseurs de puissance traditionnels. Cette topologie est parfaitement adaptée pour les technologies silicium. Comme preuve de concept, deux diviseurs de puissance avec des caractéristiques différentes ont été réalisés en technologie PCB microruban à la fréquence de 2.45 GHz. Un composent a été conçu à 60 GHz en technologie BiCMOS 55 nm utilisant des lignes S-CPW. Les simulations prouvent que le dispositif est faibles pertes, adapté et isolé. Les circuits sont également en cours de fabrication. Enfin, deux topologies de « reflection type phase shifter » ont été développées, la première dans la bande RF et la seconde aux fréquences millimétrique. Pour la bande RF, le déphasage atteint plus de 360° avec une figure de mérite très élevée en comparaison avec l'état de l'art. En ce qui concerne le déphaseur dans la bande millimétrique, la simulation montre un déphasage de 341° avec également une figure de mérite élevée.

**Mots-clés** : Ligne à ondes lentes S-CPW, facteur de qualité, technologies CMOS, balun, rat-race, inverseur de phase, diviseur de puissance, coupleur hybride, déphaseur, bande millimétrique, bande RF, figure de mérite, miniaturisation.

## Title

New topologies of power dividers, baluns and phase shifters in RF and millimetrewave bands, based on microstrip lines and slow-wave coplanar waveguides technologies.

## Abstract

The first purpose of this work was the use of slow-wave coplanar waveguides (S-CPW) to achieve various passive components with the aim to show their great potential and interest at millimetre-waves. Several CMOS or BiCMOS technologies were used: CMOS 65 nm and 28 nm, and BiCMOS 55 nm.

Two baluns, one based on a rat-race topology and the other based on a modified Wilkinson power divider, and a phase inverter, were achieved and measured in a 65 nm CMOS technology. State-of-the-art results were achieved. A branch-line coupler and an in phase power divider without isolation were designed in a 28 nm CMOS technology. Really good performances are expected for these compact devices being yet under fabrication. Then, a new topology of in phase and isolated power divider was developed, leading to more flexibility and compactness, well suited to millimetre-wave frequencies. Two power dividers with different characteristics were realized in a PCB technology at 2.45 GHz by using microstrip lines, as a proof-of-concept. After that, a power divider was designed at the working frequency of 60 GHz in the 55 nm BiCMOS technology with S-CPWs. The simulation results showed a low loss, full-matched and isolated component, which is also under fabrication and will be characterized as soon as possible. Finally, two new topologies of reflection type phase shifters were presented, one for the RF band and one for the millimetre-wave one. For the one in RF band, the phase shift can reach more than 360° with a great figure-of-merit as compared to the state-of-the-art. Concerning the phase shifter in the millimetre-wave band, the simulation results show a phase shift of 341° with also a high figure-of-merit.

**Key words** : Slow-wave CPW, quality factor, CMOS technologies, balun, rat-race, phase inverter, power divider, branch-line coupler, reflection type phase shifter, millimetre-wave band, RF band, figure-of-merit, miniaturization.

# Remerciements

Je souhaite tout d'abord remercier Monsieur Christophe Gaquière, professeur à l'université de Lille, qui me fait l'honneur de présider le jury, ainsi que Messieurs Eric Kerhervé, professeur à l'université de Bordeaux et Roberto Sorrentino, professeur à l'université de Pérouse pour avoir accepté d'être rapporteurs de cette thèse.

Merci à Daniel GLORIA qui a accepté d'être examinateur au cours de la soutenance ainsi que pour la mise à disposition en toute confiance des technologies de STMicroelectronics. Sa collaboration a été essentielle pour mon travail de thèse. Un grand merci au Professeur Tibor BERCELI de l'université de Budapest, qui m'a fait l'honneur d'assister à cette thèse. Budapest... cette ville qui représente tant de choses pour moi.

Ma rencontre avec Philippe FERRARI à l'IUT en 2006 allait sans le savoir être déterminante pour ma carrière. Après m'avoir accepté en stage à l'IMEP-LAHC lors de ma deuxième année à l'ENSERG en 2009, une année après Philippe m'a très gentiment proposé cette thèse. Ses qualités professionnelles, sa pédagogie et son optimisme ont fait que l'idée de travailler avec lui a été le facteur dominant pour accepter ce projet. Florence PODEVIN a parfaitement complété mon encadrement, avec sa gentillesse et sa générosité. Malgré ses contraintes, Florence a toujours été disponible et m'a toujours aidé pour avancer au mieux dans mon travail. Philippe et Florence m'ont toujours fait confiance, j'avais donc une réelle volonté de ne pas les décevoir. Cette confiance était pour moi une source de motivation aussi importante que la réussite de ma thèse. Je pense avoir eu des encadrants exceptionnels, ceux que tout thésard rêve d'avoir, et j'en ai conscience. C'est pour cela que je leurs en suis extrêmement reconnaissant. Merci Philippe. Merci Florence.

Je suis également reconnaissant à Nicolas CORRAO pour les mesures des dispositifs intégrés et s'être déplacé à Chambéry avec moi, à Benjamin BLAMPEY pour toute la partie de-embedding, à Alejandro NIEMBRO pour la réalisation et mesure des antennes et à Alexandre CHAGOYA pour son aide sur les design Kits. Il y a aussi ceux que j'ai côtoyés ou avec lesquels j'ai travaillé pendant ces trois années, merci à Anne-Laure, Xiaolan, Jean-Michel, Estelle, Jean-Daniel, Farid, José, Pierre et bien sûr Manu le chambreur numéro un... Toutes ces personnes m'ont apporté bien plus qu'elles ne le pensent et je les remercie. Je pense également à Zyad, mon premier et unique stagiaire, toujours souriant et amical, qui a donc accepté d'être mon cobaye, à son insu... Je pense que nous avons fait une belle équipe et lui souhaite plein de bonheur pour la suite.

Un grand merci à tous les doctorants qui se sont succédés au bureau A440. J'ai pu y rencontrer Fabien, Zine, Florent et bien sûr Inès et Alex qui ont apportés une dimension internationale très agréable. Une grande complicité s'était installée entre nous et c'est avec regret que je les quitte. Merci à notre voisin de bureau, Tan-Phu, qui pensait toujours à nous pour partager ses friandises.

Il m'est impossible de ne pas citer mes amis de l'ERG avec qui j'ai passé mes trois plus belles années d'études. Je pense à Armand, Nico, Tyty, Ousmane et Polo, notre groupe des admis sur titre, mais aussi à Minot, Youyou (dit « Binôme ») et Richard Président. Merci pour votre aide, pour toutes ces soirées, ces sorties, ces foots... et je m'excuse de n'avoir pu passer plus de temps avec vous ces trois dernières années. Il y a eu bien sûr cette coloc Magic, avec les Trois Mousquetaires, période qui restera inoubliable.

Il y a aussi des gens que j'ai rencontrés et qui sont devenus plus que des amis. Je tiens à remercier Vlad, avec qui j'ai passé tant de temps. C'était toujours un plaisir de faire du design pour me trouver dans la même salle que lui. Merci aussi à Francesco et Paolo, à leur année à l'IMEP-LAHC qui est passée beaucoup trop vite. Notre périple en Italie, les Châteaux de la Loire avec Ana et toutes ces sorties ensemble...que de souvenirs.

Un très grand merci à mes parents qui ont toujours acceptés mes choix, m'ont soutenus et m'ont fait confiance. Je n'oublie pas mon frère Nico à qui je souhaite la réussite et tout le bonheur du monde.

Enfin, je remercie la personne qui a partagé avec moi cette aventure et qui a toujours été à mes côtés depuis trois ans et demi. Merci Elena, pour ta gentillesse et ta compréhension, je ne te remercierai jamais assez pour les sacrifices que tu as faits en me suivant en France. Un grand merci à ta famille qui m'accueille toujours comme un Tsar lors de nos visites à Saint Pétersbourg.

# TABLE OF CONTENTS

| INTRODUCTION                                         |    |

|------------------------------------------------------|----|

| CHAPTER I : POWER DIVIDERS/COMBINERS AND REFLEC      |    |

| TYPE PHASE SHIFTER PRESENTATION                      | 17 |

| I.1 PLANAR DIVIDERS/COMBINERS                        |    |

| I.1.1 Overview                                       |    |

| I.1.2 Wilkinson power divider/combiner               |    |

| I.1.2.1 Presentation                                 |    |

| I.1.2.2 Evolution                                    |    |

| I.1.2.3 Striking applications                        |    |

| I.1.3 Branch-line coupler                            |    |

| 1.1.3.1 Presentation                                 |    |

| I.1.3.2 Evolution                                    |    |

| I.1.3.3 Striking applications                        |    |

| I.1.4 Rat race coupler                               | 24 |

| I.1.4.1 Presentation                                 |    |

| I.1.4.2 Evolution                                    |    |

| I.1.4.3 Application                                  |    |

| I.2 REFLECTION TYPE PHASE SHIFTER                    |    |

| I.2.1 Principle and theory                           |    |

| I.2.1.1 Insertion loss                               |    |

| I.2.1.2 Relative phase shift                         |    |

| I.2.1.3 Practical example with non-ideal varactor    |    |

| I.2.1.4 Conclusion                                   |    |

| I.2.2 Modified reflective load                       |    |

| I.2.2.1 Serial inductance                            |    |

| I.2.2.2 State-of-the-art at RF frequencies           |    |

| I.2.3 Branch-line coupler substitution               |    |

| I.2.4 Applications                                   |    |

| I.2.5 State-of-the-art review                        |    |

| I.3 MINIATURIZATION TECHNIQUES                       |    |

| I.3.1 Shunt-stub-based artificial transmission lines |    |

| I.3.2 Meander and Fractals                           |    |

| I.3.3 Phase inverter                                 |    |

| I.3.4 Capacitor loading                                                                       | 38 |

|-----------------------------------------------------------------------------------------------|----|

| I.3.5 Stepped-impedance                                                                       | 38 |

| I.3.6 Slow-wave transmissions lines                                                           | 38 |

| I.4 STATE-OF-THE-ART IN MILLIMETRE-WAVES                                                      | 41 |

| I.4.1 Power divider with in phase outputs                                                     | 41 |

| I.4.2 Power divider with quadrature outputs                                                   | 42 |

| I.4.3 Power divider with out-of-phase outputs                                                 | 43 |

| I.4.4 Phase shifter                                                                           | 44 |

| I.5 CONCLUSION                                                                                | 45 |

| CHAPTER II : S-CPW APPLICATIONS                                                               | 47 |

| II.1 SIMULATION TOOL                                                                          | 47 |

| II.2 CALIBRATION & DE-EMBEDDING                                                               | 48 |

| II.2.1 Two port devices                                                                       | 48 |

| II.2.1.1 Transmission Line                                                                    | 48 |

| II.2.1.2 Devices                                                                              | 49 |

| II.2.2 Four port devices                                                                      | 50 |

| II.3 STACKS                                                                                   | 54 |

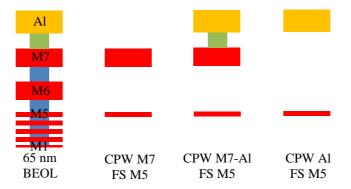

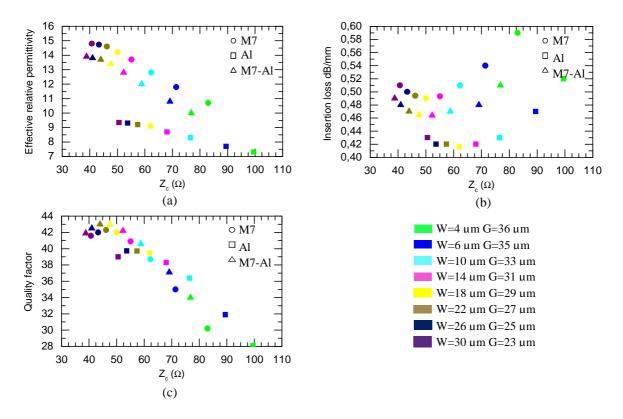

| II.4 SIMULATED AND MEASURED TRANSMISSIONS LINES                                               | 54 |

| II.4.1 Study of the quality factor of the S-CPW in the 65 nm CMOS technology                  | 55 |

| II.4.2 Transmission lines in the 65 nm CMOS technology: measurement versus simulation results |    |

| II.4.2.1 Microstrip                                                                           |    |

| II.4.2.2 S-CPW                                                                                |    |

| II.4.2.3 Results synthesis                                                                    | 59 |

| II.4.3 Transmission lines in the 28 nm CMOS technology: simulation results                    | 59 |

| II.4.4 Transmission lines in the 55 nm BiCMOS technology: simulation results                  | 60 |

| II.5 PHASE INVERTER                                                                           | 61 |

| II.6 BALUNS                                                                                   | 62 |

| II.6.1 Rat-race coupler balun                                                                 | 62 |

| II.6.1.1 Design and layout                                                                    | 63 |

| II.6.1.2 Simulation versus measurement results                                                |    |

| II.6.1.3 Further improvements                                                                 |    |

| II.6.2 Power divider balun                                                                    | 66 |

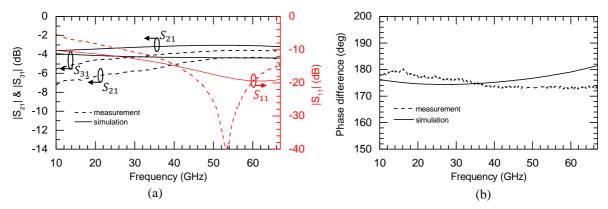

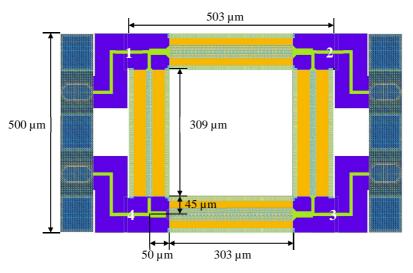

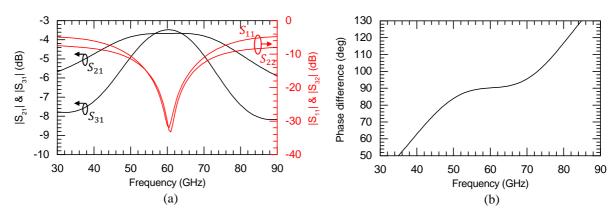

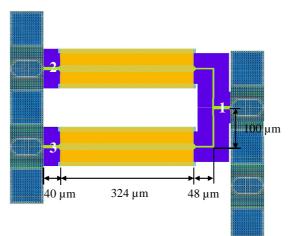

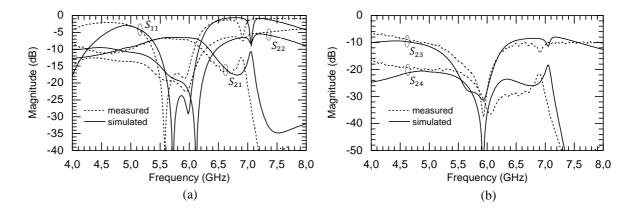

| II.6.2.1 Simulation versus measurement results                                                  | 67 |

|-------------------------------------------------------------------------------------------------|----|

| II.6.2.2 Further improvements                                                                   | 68 |

| II.6.3 Comparison with the state-of-the-art                                                     | 68 |

| II.7 BRANCH-LINE COUPLER                                                                        | 69 |

| II.8 POWER DIVIDER                                                                              | 70 |

| II.9 CONCLUSION                                                                                 | 72 |

| CHAPTER III : NEW TYPE OF POWER DIVIDER BASED ON A                                              |    |

| WILKINSON POWER DIVIDER/COMBINER FOR                                                            |    |

| MILLIMETRE-WAVE FREQUENCIES APPLICATIONS                                                        | 74 |

| III.1 ISSUES FOR WILKINSON POWER DIVIDERS IN SILICON TECHNOLOGY                                 | 75 |

| III.1.1 Isolation resistance                                                                    | 75 |

| III.1.2 Characteristic impedance flexibility                                                    | 75 |

| III.1.3 State-of-the-art of the solutions                                                       | 76 |

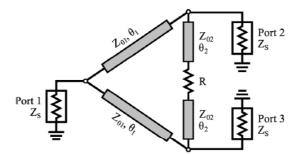

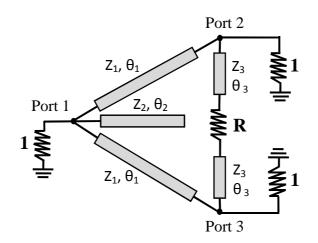

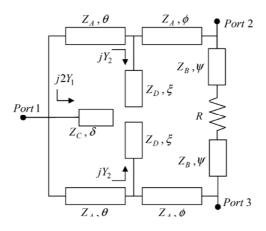

| III.2 STUDY OF A NEW SOLUTION                                                                   | 77 |

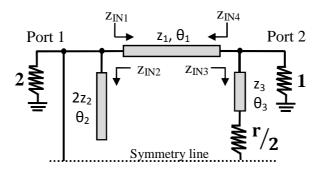

| III.2.1 Topology presentation                                                                   | 77 |

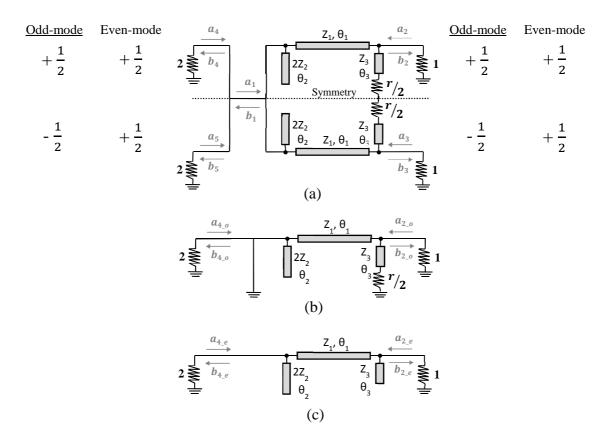

| III.2.2 Theory and design equations                                                             | 77 |

| III.2.2.1 Even-mode analysis                                                                    | 78 |

| III.2.2.2 Odd-mode analysis                                                                     | 80 |

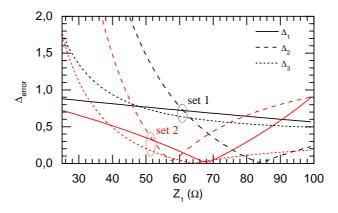

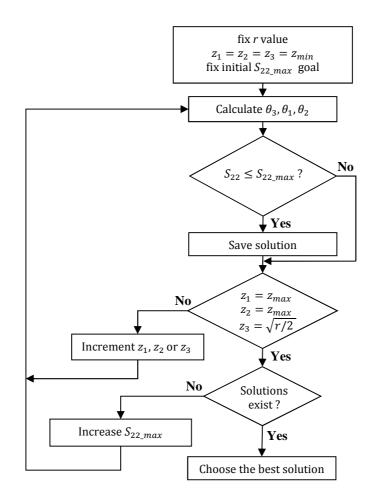

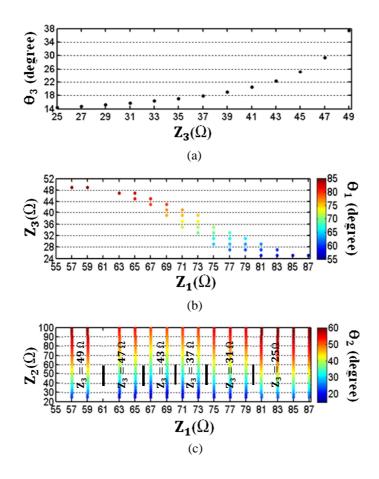

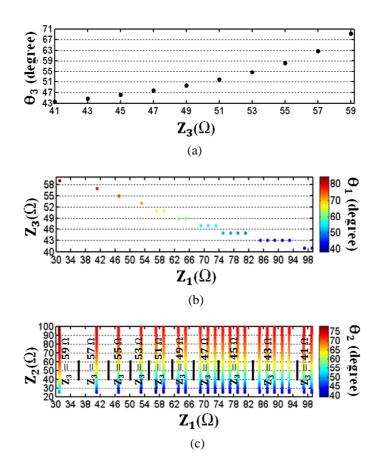

| III.2.3 Design procedure                                                                        | 81 |

| III.2.3.1 Demonstration of the good matching and isolation according to the value of $S_{22}$ . |    |

| III.2.3.2 Procedure for finding solutions                                                       | 85 |

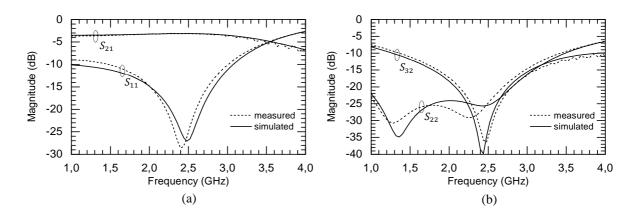

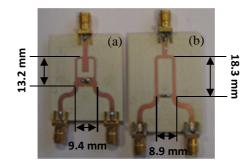

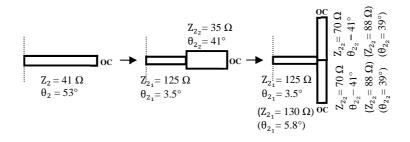

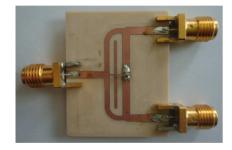

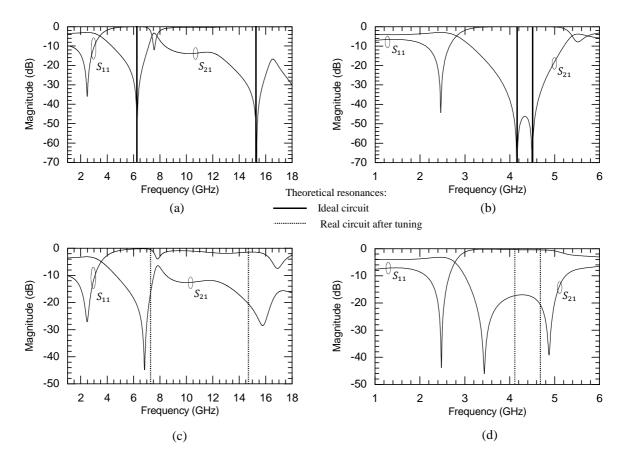

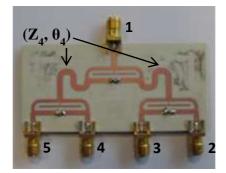

| III.3 CIRCUITS DESIGN AND EXPERIMENTAL RESULTS                                                  | 87 |

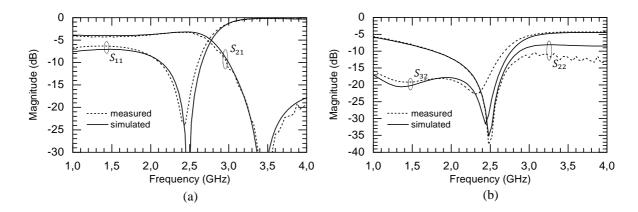

| III.3.1 Power Divider with $R = 105 \Omega$                                                     | 87 |

| III.3.2 Power Divider with $R = 150 \Omega$                                                     | 90 |

| III.4 HARMONICS SUPPRESSION                                                                     | 92 |

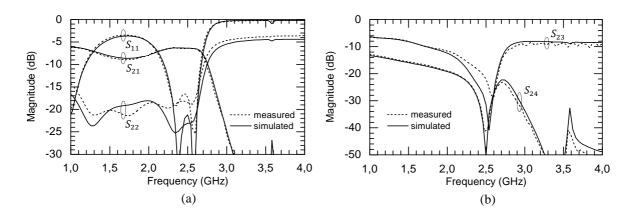

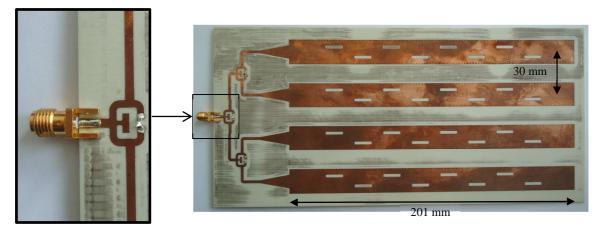

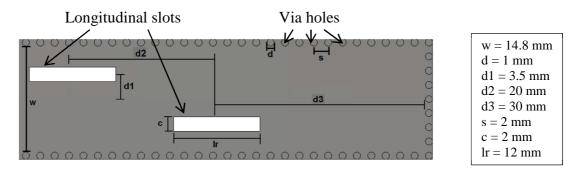

| III.5 ANTENNAS ARRAY FEEDING NETWORK APPLICATION                                                | 95 |

| III.5.1 2.45 GHz working frequency                                                              | 95 |

| III.5.2 5.8 GHz working frequency                                                               | 96 |

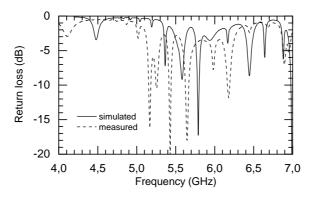

| III.5.2.1 1:4 feeding network                                                                   | 96 |

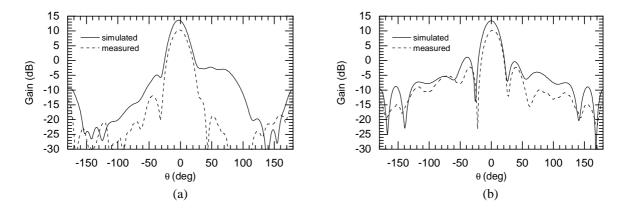

| III.5.2.2 1:4 feeding circuit with antennas                                                     | 97 |

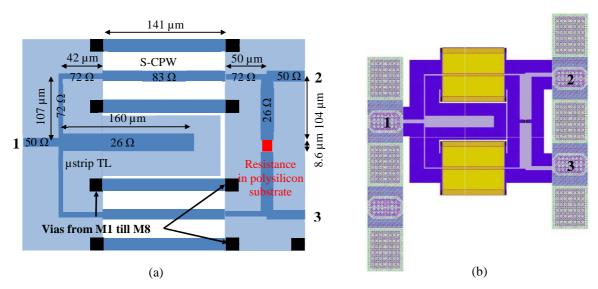

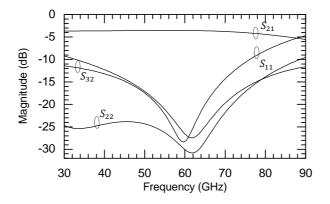

| III.6 MILLIMETRE-WAVE APPLICATION                                                               | 98 |

| III.6.1 Design and simulation                                                                   | 99 |

| III.6.2 Sensitivity to the resistance value101                                          |

|-----------------------------------------------------------------------------------------|

| III.7 CONCLUSION                                                                        |

| CHAPTER IV : NEW TOPOLOGIES OF REFLECTION TYPE PHASE                                    |

| SHIFTER FOR HIGH FIGURE OF MERIT                                                        |

| SIIII TEK FOR IIIGH FIGURE OF MERIT                                                     |

| IV.1 STUDY OF THE TOPOLOGIES                                                            |

| IV.1.1 Reflection load with one varactor104                                             |

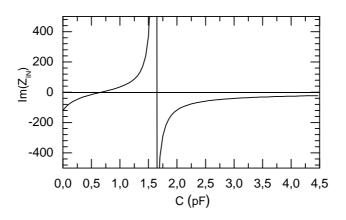

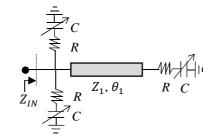

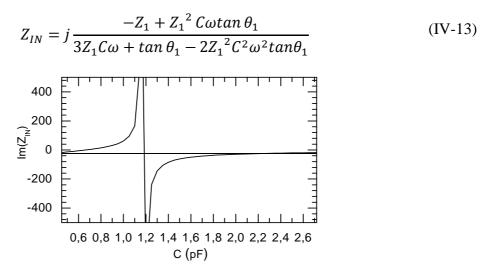

| IV.1.2 Reflection load with two varactors108                                            |

| IV.1.3 Reflection load with three varactors                                             |

| IV.2 DESIGN PROCEDURE                                                                   |

| IV.3 CIRCUITS DESIGN AND EXPERIMENTAL RESULTS IN PCB 112                                |

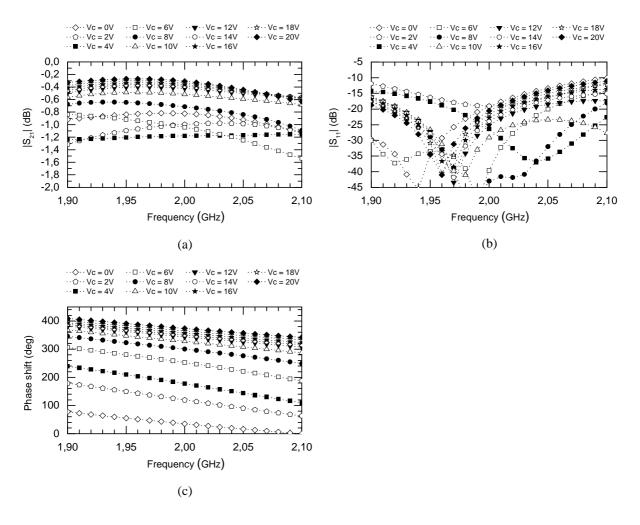

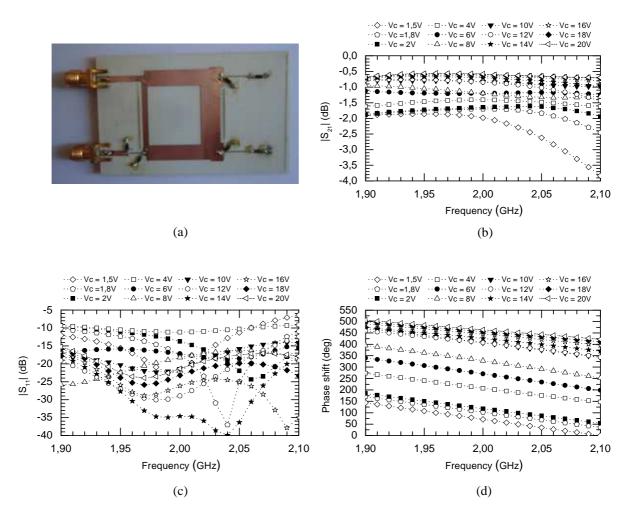

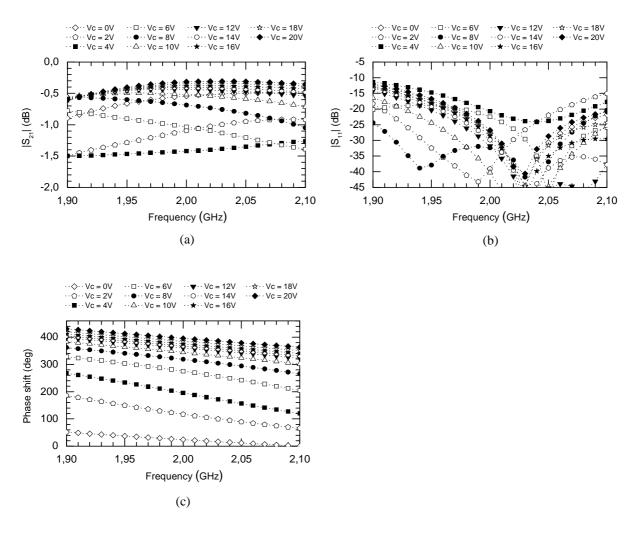

| IV.3.1 Reflection load with one varactor113                                             |

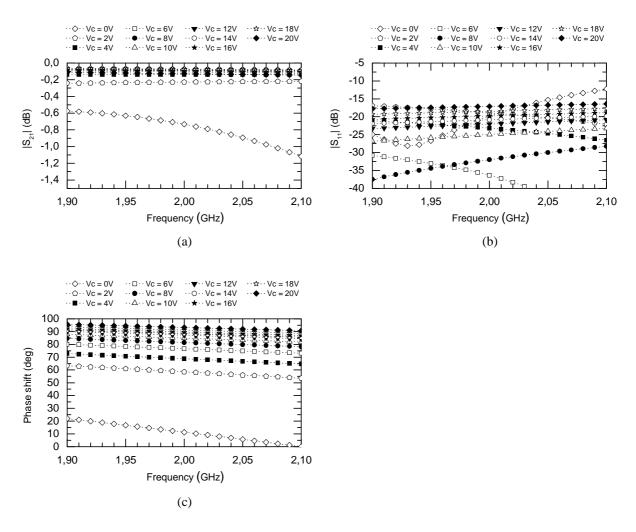

| IV.3.2 RTPS with reflection load with two varactors cascaded with a II-type             |

| phase shifter                                                                           |

| IV.3.2.1 Choice of the RTPS115<br>IV.3.2.2 Optimization of the П-type phase shifter116  |

| IV.3.2.2 Optimization of the RTPS with the П-type phase shifter                         |

| IV.3.2.4 Measurement results                                                            |

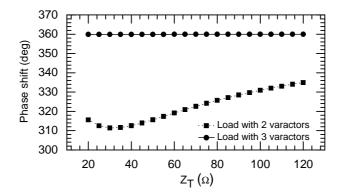

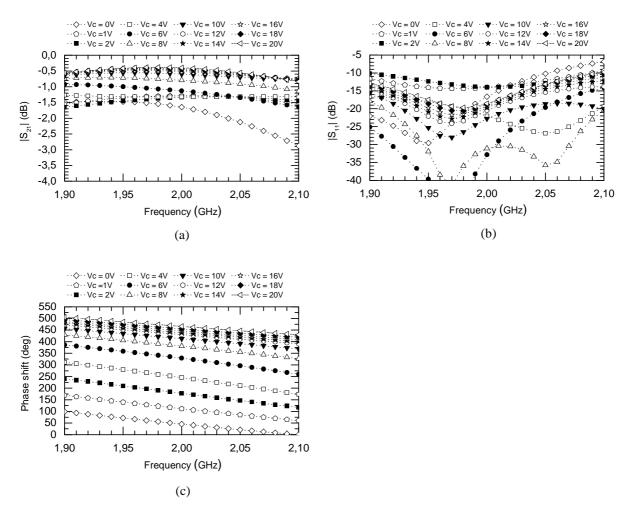

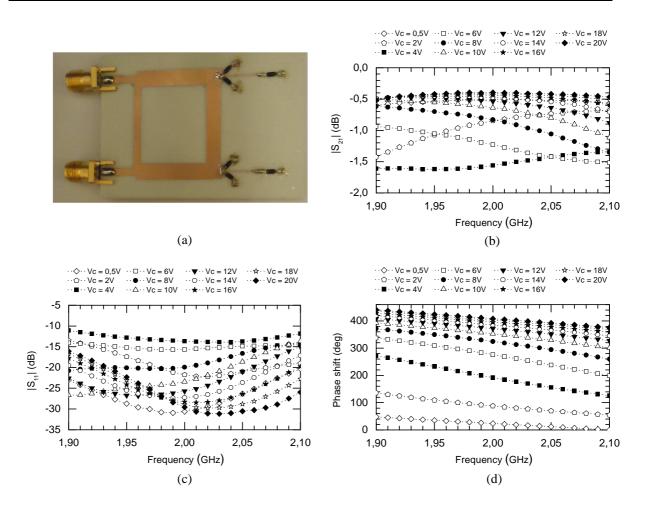

| IV.3.3 Reflection load with three varactors                                             |

| IV.3.4 Results synthesis                                                                |

| 1v.5.4 Results synthesis                                                                |

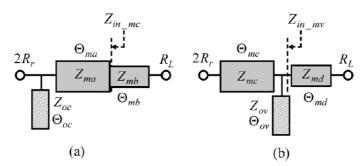

| IV.4 RTPS IN INTEGRATED TECHNOLOGY                                                      |

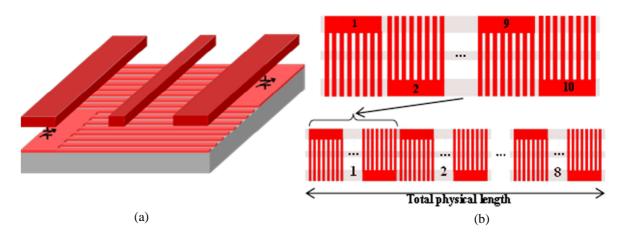

| IV.4.1 Topology of the reflection load based on a distributed loaded line phase shifter |

| IV.4.2 Layout and simulation of the RTPS                                                |

| IV.4.2 RTPS, loaded line phase shifter alone and state-of-the-art comparison            |

| 1 v.4.5 K11 5, loaded line phase sinter alone and state-or-the-art comparison           |

| IV.5 PERSPECTIVES                                                                       |

| IV.6 CONCLUSION                                                                         |

| CONCLUSION129                                                                           |

| APPENDIX-A131                                                                           |

| APPENDIX-B133                                                                           |

| REFERENCES135                                                                           |

| PUBLICATIONS143                                                                         |

# Introduction

Nowadays, 21st century, progress and innovation in science and technology are jawdropping. Wave propagation is directly impacted by the technology developments in several domains and applications. More particularly, millimetre-waves have concentrated much and much interest since more than ten years. Two main advantages, as compared to radio frequencies (RF, a few GHz), make millimetre-waves attractive today, (i) the wide bandwidth and (ii) the antennas small size. In current systems, the bandwidth is more or less proportional to the working frequency; except for the particular case of Ultra-Wide-Band dedicated to short range low data-rate communications, the relative bandwidth is limited to a maximum of 10 to 15 %. Hence, for a given relative bandwidth, increasing the working frequency increases the bandwidth. The antennas size is also a key issue. It is obvious that smaller antennas lead to smaller systems, but the main interest stays the possibility to achieve large antennas arrays allowing focused beams, which is mandatory in order to address consumption issues for autonomous systems. Antennas arrays also enable to carry out beam-steering and/or beam-forming systems by using phased antenna arrays. In a more general point of view, millimetre-waves antenna arrays lead to an improved efficiency, as compared to RF systems, for the same area of the antenna system.

High-data-rate communications, radars, security, and medical applications are concerned by the development of millimetre-wave systems. In order to ensure data rates greater than a few Gbit/s, the most suitable solution has been to operate in the millimetrewaves. In the vicinity of 60 GHz, in particular, a common 5 GHz band between 59 and 64 GHz was defined for unlicensed use in the countries where the consumer electronic market was the most developed. This spectrum is an attractive option for very high data rate wireless local area networks (WLANs) or wireless personal area networks (WPAN). Moreover, this millimetre-waves radiation is capable of penetrating clothing while being partially reflected by human skin. As the reflection pattern of metals, but also plastics, ceramics and liquids are readily detectable for radiation at these frequencies, millimetrewaves imagers have been considered as a superior alternative as compared to traditional metal detectors. Hence, the security domain constitutes one of the major areas for millimetre-waves imaging systems. The frequencies better suited to this use are 35, 94, 140, and 220 GHz, which correspond to the atmospheric propagation windows, e.g. to the minima observed in terms of atmospheric attenuation. In the past, 94 GHz systems were usually adopted, but higher frequencies, leading to even better spatial resolutions, are under study. Recently, significant technological advances in the automotive industry have taken place for improving vehicles safety. The radar system can detect and track objects in the frequency domain triggering a driver warning of an imminent collision and initiate electronic stability control intervention. For long range radar there is a certain international consensus regarding the 76-77 GHz band whereas for short range such as anti-collision and

handheld radars for parking assistance, pre-crash sensing, obstacle avoidance and blind spot detection the working frequency was fixed to 79 GHz. Here again, high spatial resolution is required and obviously the smallest antennas as possible.

All these millimetre-waves applications are commonly recognized to belong to and to lead to a smart society because they will facilitate the communications between people, inside or outside homes and offices, and from building to building (backhauling), avoiding heavy civil engineering infrastructure. They will also increase safety in transports, with improvement of traffic and parking. Nonetheless, they will also be sustainable because they will not consume much power, will have a small area and high performances level.

CMOS and BiCMOS technologies are addressed to fabricate low cost millimetrewave devices. Indeed traditional monolithic microwave integrated circuits (MMICs) with Gallium Arsenide (GaAs) can provide high-performance millimetre-waves devices due to the higher electron mobility of GaAs, higher breakdown voltage, and good insulating properties. However, GaAs technology is expensive even in mass production, which results in systems with prohibitive costs for consumer applications. This is why CMOS/BiCMOS technologies are preferred for mass production.

Such applications convey high innovation. They will also permit a large part of the microelectronic industry in developed countries to pursue its activities.

As discussed above, for some applications beam-steering systems are required either to achieve specific functions (e.g. radars) or to improve point-to-point transmissions efficiency. The beam-steering approach gives spatial agility, locating and concentrating the emitted/received energy in the direction of the receiver/emitter. This allows a longer communication range and an improvement of the system capability, leading to a more secure communication, and also to the detection of mobile blind spots. In that case, the system will quickly establish a new communication path, using for example, beams that reflect off the walls. It is a significant technological challenge to achieve such goal in a compact, cost-effective and energy-efficient solution. Mechanical beam-steering has been used with the advantage of a wide field of view and no signal processing requirement; but its manufacturing complexity, size, weight and scanning rate are not appropriate for lowcost consumer applications. Nowadays, few techniques have been developed for beamsteering. It can be performed by changing the phase of the local oscillator at the millimetrewave mixers level but high power consumption is induced because one mixer is necessary for each antenna element of the antenna array. Other realizations have shown monolithic millimetre-waves antenna array front-ends, with digitally processed phase shifting for each antenna. Here again, the main drawback of such approach is linked to its very high power consumption, which is not compatible with mobile applications where autonomy is mandatory. The phase shifting in the millimetre-waves path would ensure low power consumption. The system could be very simple, with simple power splitters feeding phase shifters controlling each antenna of the antenna array. The key issue is then to improve the devices performance while decreasing their surface area in order to decrease the fabrication costs. A great challenge!

To improve the performances and reduce the area of the passive components needed in the millimetre-waves range, slow wave transmissions lines have proved to be good candidates and particularly the slow-wave coplanar waveguides (S-CPWs). It has been shown in [1] and [2] that the phase constant ( $\beta$ ) increases while keeping the same attenuation constant ( $\alpha$ ) than a classical microstrip transmission line, leading to a quality factor (Q) defined as:

$$Q = \frac{\beta}{2\alpha}$$

about two to three times higher than the classical transmission line. With such transmission lines not only performances can be improved but also the compactness of the devices.

The performances of the integrated tunable devices are usually related to the tuning elements used to vary the phase. The utilization of varactors induces high insertion loss level because of the low quality factor of the varactors, particularly at millimetre-wave frequencies. Until no varactors with better performances are achieved, all the tunable topologies developed at RF frequencies have to be studied again in order to reduce the insertion loss or should be modified in order to substitute the varactors. Ferrites could be used for this purpose but they suffer from high cost and lead to large size components. Liquid crystal (LC) appears to be a promising tunable dielectric, since its losses decrease with frequency. Thus, it is ideally suited for high performance millimetre-waves applications. At these frequencies, LC features low dielectric losses and continuous tunability. The main drawback of LC-based devices is the response time (tenths of ms) and the length of the devices due to a low tunability of the dielectric constant of about 25 %. BST material is a good candidate at RF frequencies, but suffers from high dielectric losses at millimetre-waves. Finally, microelectromechanical systems (MEMS) have the potential to be inexpensive, low loss, with high quality phase-shifting capability. However, all the above technologies are not compatible with CMOS unless performing a post-process. Hence, in parallel of the study of these hybrid solutions, it is still important to continue to study fully integrated solutions and try to develop high-quality factor tunable elements.

The purpose of my thesis work was thus to explore the possibilities to use S-CPWs in order to achieve high-performance passive devices at millimetre-waves. Power dividers, baluns and phase shifters were realized in CMOS or BiCMOS technologies. Efforts were carried out towards the study of new topologies in order to improve both performance and compactness. Some devices were first realized at RF in a PCB technology as a proof-of-concept, but also for some of them because their development at RF frequencies was interesting for RF systems.

In the first chapter, the principle of planar dividers/combiners with their most important striking evolutions and applications in the RF range are given. Baluns are considered as an application of certain power divider type devices. Then, the reflection type phase shifter topology is explored. The common miniaturization techniques for all the presented components are also listed. Finally, the state-of-the-art, at millimetre-waves, for phase shifters and power dividers is developed.

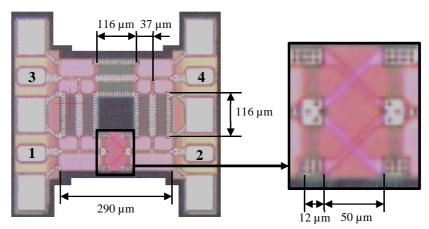

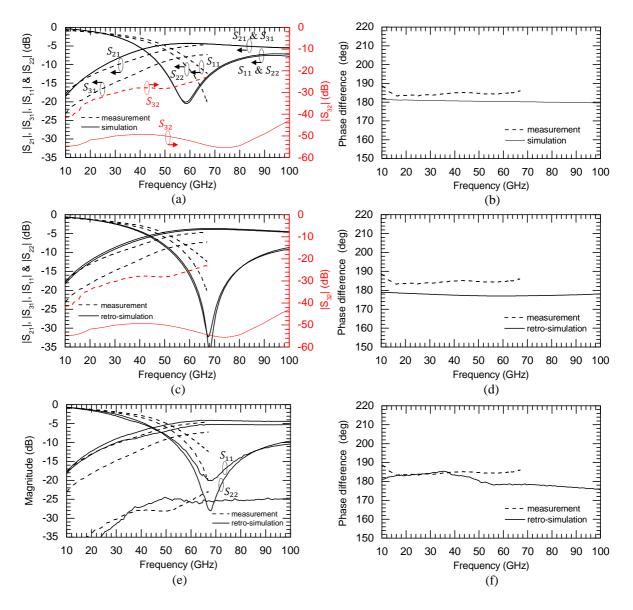

In the second chapter, in order to highlight the great interest of slow-wave coplanar waveguides at millimetre-waves, baluns achieved by the use of power dividers and a wideband phase inverter were designed in the 65 nm CMOS technology and measured. Also, power dividers with in phase (modified Wilkinson power divider) and in quadrature (branch-line coupler) were designed in the 28 nm CMOS technology.

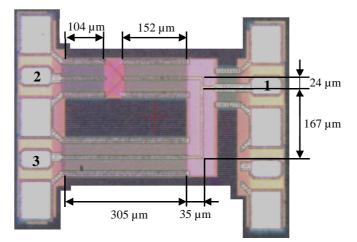

The third chapter presents a new topology of in phase power divider, which is compact and flexible, perfectly adapted to millimetre-waves. Two power dividers and two antennas array feeding circuits were realized in PCB technology, as a proof-of-concept, and then characterized. Next, the simulation results of such a power divider with slow-wave coplanar waveguides designed in the 55 nm BiCMOS technology are given.

Finally, the last chapter describes a new topology of reflection type phase shifter (RTPS) in RF with a high figure-of-merit as compared to the state-of-the-art. This topology is based on lumped varactors together with transmission lines as a reflexion load and was achieved after a careful study of the most suitable topologies and a new optimization procedure. A second solution of reflection type phase shifter was developed for millimetre-waves in the 55 nm BiCMOS technology. As a reflexion load, a slow-wave coplanar waveguide loaded with distributed capacitive switches is used. This phase shifter was achieved thanks to the development of a new switched capacitor showing improved quality factor as compared to the varactors available in the design kit. Designs carried out showed that high performance reflection type phase shifters could be realized thanks to this new topology.

# Chapter I : Power dividers/combiners and Reflection Type Phase Shifter presentation

With the fast development of multifunctional technologies and the need for miniaturization in wireless communication systems, compact microwave components and circuits—especially microwave integrated circuits with system-level performance—have become increasingly popular. Those considerations stay available whatever the considered frequency range and topology, i.e. radio frequency (RF) in advanced PCB technologies, or millimetre-waves (mmW) compatible with CMOS and 3D integration techniques.

Among the large number of microwave integrated passive circuits, power dividers and phase shifters are fundamental, powerful and necessary, device building blocks. For wireless communication purpose, they are full part of the front-end transceiver. They can also be used independently to make analog active circuits more performing: power amplifiers or local oscillators are common example.

In this chapter, after a brief overview of the already existing solutions in terms of planar dividers/combiners, we will remind the principle of the commonly used components with their most important evolution and recent applications in the RF range. In a second time, solutions for phase shifting will be explored, focusing on the theory of the Reflection Type Phase Shifting, the most appropriate technique to combine high phase shifting and port matching in the meantime. Various topologies are compared and explained. Then, we will list, illustrate and comment miniaturization techniques; most of which are similarly used to miniaturize both components: power dividers and phase shifters. Finally, we will draw the state-of-the-art, at millimetre-waves, for phase shifters, power dividers, and baluns (one application among many of power dividers).

## I.1 Planar dividers/combiners

Power dividers are usually considered to be a family of devices. They can be found in many applications, including power division and combination, modulation and demodulation, balanced mixing, balun for power amplification, Butler matrices, and feeding network of antenna arrays, among others. A reciprocal divider can provide an equal or unequal power split between two or more channels. Thanks to reciprocity, and assuming that input signals to be combined should be coherent and of equal magnitudes, this circuit may also be employed to combine a number of oscillators or amplifiers towards a single port.

The major parameters used to define and compare the dividers/combiners in RF and microwave integrated circuits are bandwidth, power division, relative phase difference,

phase and magnitude imbalance, insertion loss, matching or return loss, isolation, number of inputs/outputs, integration level and cost. The performances concerning these parameters have been improved over time, either developing new topologies or with the help of more advanced techniques and methodologies. Consequently, more than one hundred different types of dividers/combiners have been developed over the past four decades.

### I.1.1 Overview

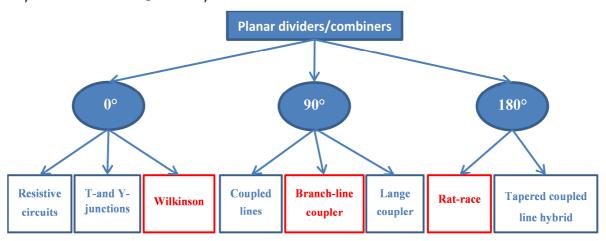

Dividers/combiners can be classified according to numerous characteristics. The most common ways are: distributed, lumped-element, or combination of both, number of ports, equal or unequal power division, fixed or tunable power division, bandwidth and relative phase difference. Hereby this is the last criterion which is chosen as a parameter so that the graph in Figure I.1 shows the main planar dividers/combiners classified according to the relative phase difference. Outputs can be in phase ( $\Delta_{\varphi} = 0^{\circ}$ ), in quadrature ( $\Delta_{\varphi} = 90^{\circ}$ ) or out-of-phase ( $\Delta_{\varphi} = 180^{\circ}$ ).

Figure I.1: Main types of planar dividers/combiners

This study concentrates on the Wilkinson power divider/combiner, the branch-line coupler and the rat-race. They are the three mostly used dividers/combiners among the ones of their phase difference category.

### I.1.2 Wilkinson power divider/combiner

#### I.1.2.1 Presentation

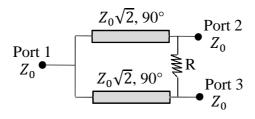

The lossless Wilkinson divider/combiner developed in 1960 [3], shown in Figure I.2, is composed of two quarter wave transmission lines (TLs), of characteristic impedance  $Z_0\sqrt{2}$ , with  $Z_0$  being the ports impedance. It is a really efficient component in terms of matching and isolation. Indeed, it can be matched at all ports simultaneously, while keeping isolation, thanks to a unique lossy element *R* connected between the two output ports. The branch between the output ports is named isolation branch. Theoretically, the resistance *R*

equates  $2 \times Z_0$ . However, this resistance limits the ability to combine any signals of higher power than that developed in the isolation branch, which is usually rated for several watts.

Figure I.2 : Wilkinson power divider

Because of the quarter wave TLs, its relative bandwidth under 20 dB of return loss is limited to 20 %. For the applications requiring broadband one possibility consists to cascade the dividers. Obviously, not only the bandwidth increases but the insertion loss and the complexity of the device as well. The real divider characteristics deviate from the ideal ones, due to manufacture tolerances, losses, discontinuities, mismatching of the terminations, as well as the physical quality of the resistance. The influence of these different factors on the parameters of the divider was examined by Paral and Moynihan in 1965 [4]. The ideal [*S*] matrix has the following form:

$$[S] = \frac{-j}{\sqrt{2}} \begin{bmatrix} 0 & 1 & 1\\ 1 & 0 & 0\\ 1 & 0 & 0 \end{bmatrix}$$

(I-1)

#### I.1.2.2 Evolution

The first modified Wilkinson divider/combiner with unequal power-split ratio was presented in [4] (see Figure I.3 and equations (I-2)). The electrical lengths of the four TLs are 90° at the working frequency. The properties of full-matching and isolation at the working frequency are observed.

Figure I.3 : Wilkinson power divider with arbitrary power division

$$\frac{POWER \ AT \ PORT \ 4}{POWER \ AT \ PORT \ 5} = \frac{1}{K^2} \qquad R = Z_0 \frac{1+K^2}{K}$$

$$Z_{02} = Z_0 \sqrt{K(1+K^2)} \qquad Z_{04} = Z_0 \sqrt{K} \qquad (I-2)$$

$$Z_{03} = Z_0 \sqrt{\frac{1+K^2}{K^3}} \qquad Z_{05} = \frac{Z_0}{\sqrt{K}}$$

However, when the power dividing ratio is higher than 3 ( $K^2 > 3$ ), TLs with very high characteristic impedances are required. Some popular TLs with potentially very high characteristic impedances, such as microstrip or CPW, become too narrow to be realized practically. The high characteristic impedance can be realised by using a meander-shaped defected ground structure (DGS) [5]. Nevertheless, the increase of impedance in such a manner is limited. The rectangular-shaped defected ground structure is also effective for the realisation of high characteristic impedances [6]. In [7] the high characteristic impedances for a 5:1 unequal power divider were realized by suing offset doubled-sided parallel-strip lines (DSPSL). DSPSL-to-microstrip transitions have to be employed at the three ports, which inevitably introduces additional insertion loss and increases the circuit size. The grooved substrate microstrip method could be used to realize high characteristic impedance as in [8]. But this grooved substrate microstrip is difficult to be fabricated, compared to traditional microstrip. In [9] the high characteristic impedance TLs were replaced by Tshaped structures, in order to decrease the characteristic impedances towards more suitable values. In the case of the 4:1 unequal divider designed, the highest characteristic impedance was 97  $\Omega$  and the lowest 43  $\Omega$  instead of 158  $\Omega$  and 35  $\Omega$  for the conventional unequal divider.

#### I.1.2.3 Striking applications

#### I.1.2.3.a Feeding network

The Wilkinson power divider is the basic device for many applications. In [10] and [11], it was used as a feeding circuit for antenna arrays beam forming. In [10] one power divider feeds two antennas and used stepped-impedance open-circuited radial stubs to achieve good operation within a ultra-wide band. In [11] two power dividers in parallel were connected at the outputs of a first one to feed an array of four antennas as shown in Figure I.4. Phase shifters between the Wilkinson power dividers and the antennas enable beam-steering. In both cases, the measured input reflection coefficient ( $S_{11}$ ) is below -10 dB, in the band 4-14 GHz for [10] and 1.8-2.1 GHz for [11], respectively.

Figure I.4 : Electronic passive vertical beam scanning with Wilkinson dividers and phase shifters.

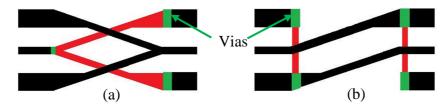

#### I.1.2.3.b Balun

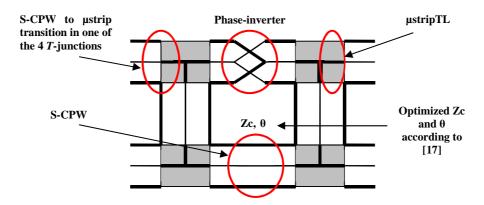

If a phase inverter is placed in series with one of the two quarter wave TLs of the Wilkinson power divider, as in Figure I.5, the 180° relative phase difference obtained between the two output ports makes its use as a balun possible. The output ports of the modified Wilkinson power divider stay close to each other. We will see soon this is a great advantage comparing to the rat-race balun. However, the resistance *R*, mandatory for isolation and output matching, must be removed. Indeed, the 180° relative phase difference between the outputs would create a permanent flowing current through the resistance and would increase considerably the losses. When removing this resistance, isolation and output ports matching are degraded in such a way that the component cannot be used anymore as a combiner. Nevertheless, it is still remarkably suitable for differential power amplification. This device, performed at the IMEP-LAHC, is totally novel. It has been designed and measured in a 65 nm CMOS technology and will be described in detail in chapter II. It is not referenced herein since the final version is an optimised case of Figure I.5.

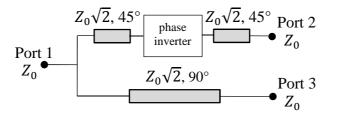

Figure I.5 : Modified Wilkinson divider with phase inverter for balun application.

### I.1.3 Branch-line coupler

#### I.1.3.1 Presentation

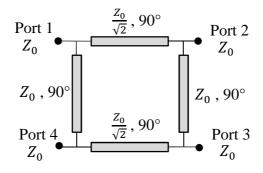

The branch-line coupler or 90° hybrid coupler is a particular case of a directional coupler. It is a four ports network where coupling factor is -3 dB and phase relationship between the output ports is 90°. The ideal coupler is lossless and matched at all ports. Compared to the Wilkinson power divider, it does not need any resistance for ports matching, but requires a fourth port. The branch-line coupler is composed by four quarter wave TLs of characteristic impedances  $Z_0$  for the vertical TLs and  $Z_0/\sqrt{2}$  for the horizontal ones in a  $Z_0$  system as shown in Figure I.6. Incident power at port 1 separates between port 2 (the through port) and port 3 (the coupled port), but no power flows through port 4 (the isolated port). Similarly, incident power at port 2 will couple to ports 1 and 4, but not 3. Thus, ports 1 and 4 are decoupled, as are ports 2 and 3. The fraction of power coupled from port 1 to port 3, named coupling (C), is given by (I-3). The leakage of power from port 1 to port 4 is given by (I-4) and is named isolation (I). To conclude, the directivity (D), which is the ratio of the power delivered to the coupled port and the isolated port is defined as D = I - C (dB) or by (I-5).

Coupling =

$$C = -10\log \frac{P_3}{P_1} = -10\log |S_{31}|^2$$

(I-3)

Isolation =

$$I = -10\log \frac{P_4}{P_1} = -10\log |S_{41}|^2$$

(I-4)

Directivity =

$$D = -10\log \frac{P_4}{P_3} = -10\log |S_{43}|^2$$

(I-5)

Figure I.6 : Branch-line coupler

The bandwidth of this device is about 10-20 %. As for the Wilkinson power divider, by cascading dividers, the bandwidth is enlarged, leading unfortunately to an increase of the insertion loss and the complexity of the device. Scattering parameters demonstration is available in [12]. The ideal [*S*] matrix has the following form:

$$[S] = \frac{-1}{\sqrt{2}} \begin{bmatrix} 0 & j & 1 & 0 \\ j & 0 & 0 & 1 \\ 1 & 0 & 0 & j \\ 0 & 1 & j & 0 \end{bmatrix}$$

(I-6)

#### I.1.3.2 Evolution

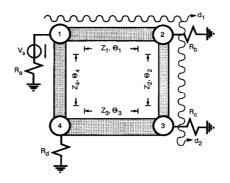

When the output ports of the hybrid coupler are connected to impedances different from  $Z_0$ , an additional matching network is needed. To avoid the need for a supplementary network, [13] presented a device with both arbitrary termination impedances and arbitrary power division. By referring to the nomenclature in Figure I.7, the ratio of the scattering parameters  $|S_{11}|$  to  $|S_{31}|$  is that of  $d_1$  to  $d_2$ . The electrical TL lengths  $\theta_1$ ,  $\theta_2$ ,  $\theta_3$ , and  $\theta_4$  are all  $\lambda/4$  at the centre frequency, and the characteristic impedances  $Z_1$ ,  $Z_2$ ,  $Z_3$  and  $Z_4$  in Figure I.7 are expressed as:

$$Z_{1} = \sqrt{\frac{d_{1}^{2}}{d_{1}^{2} + d_{2}^{2}}} \sqrt{R_{a}R_{b}} \qquad Z_{2} = \frac{d_{1}}{d_{2}} \sqrt{R_{b}R_{c}}$$

$$Z_{3} = \sqrt{\frac{d_{1}^{2}}{d_{1}^{2} + d_{2}^{2}}} \sqrt{R_{c}R_{d}} \qquad Z_{4} = \frac{d_{1}}{d_{2}} \sqrt{R_{d}R_{a}}$$

(I-7)

where  $R_a$ ,  $R_b$ ,  $R_c$ , and  $R_d$  are the real impedances termination. For both  $d_1 = d_2$  and  $R_a = R_b = R_c = R_d$ , the results are similar to a conventional 3 dB branch-line hybrid.

Figure I.7 : Branch-line coupler with both arbitrary termination impedances and arbitrary power division

#### I.1.3.3 Striking applications

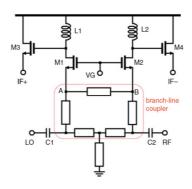

#### I.1.3.3.a Coupling for frequency mixing

Mixers are frequency translation devices. Thanks to a local oscillator (LO), they allow the signal conversion from a high frequency (RF) to a lower intermediate frequency (IF or baseband), and inversely. In down-conversions, hybrids as well as rat-races may be used as functional passives to bring the RF and LO signals towards the non-linear active component. In [14], a 138 GHz down-conversion mixer with a branch-line coupler was developed. It was based on a 90 nm CMOS technology. As shown in Figure I.8 the branch-line coupler converts the separated RF and LO input signals into two RF-LO combined signals, which were injected into M1 and M2 that basically operate as independent mixers and generate the IF signals. Although at 138 GHz a quarter wavelength line, equivalent to one edge of the coupler, becomes shorter than 300  $\mu$ m on silicon substrates, the size is still reduced with specific techniques such as capacitive open-stub loading (non-visible here). This miniaturization technique will be explained with more details further in this chapter.

Figure I.8 : Down-conversion mixer with branch-line coupler

#### I.1.3.3.b Reflection Type Phase Shifting

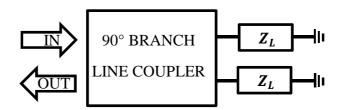

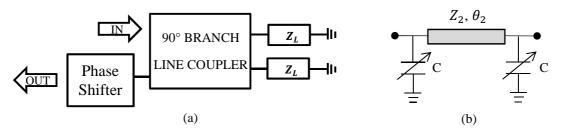

When connecting the output ports 2 and 3 of a branch-line coupler by two identical reflective loads, a reflection type device is obtained between ports 1 and 4. If  $\Gamma$  is the reflection coefficient at ports 2 or 3, the phase shift between ports 1 and 4 is equal to the phase of  $\Gamma$  plus 90°; such device is so called Reflection Type Phase Shifter (RTPS). Figure I.9 shows the block diagram of a typical RTPS with the impedance value of the reflective

loads denoted as  $Z_L$ . If  $Z_L$  is purely reactive, there is no power lost in the reflective loads so that the whole power is coupled to the output. The main advantage of this configuration is that input and output impedance matching is preserved, whatever the phase shifting is, as long as the coupler is terminated with identical reflective loads. Any load which can provide an impedance mismatch can produce reflections. However, to get better performance, which means high phase shifting with low loss, different kinds of modified loads were compared. In chapter IV, devices with optimised loads are achieved and measured in a PCB technology with state-of-the-art performances. Simulations in a CMOS technology show excellent performances, to be confirmed soon by measurements.

Figure I.9: Block diagram of a RTPS

#### I.1.4 Rat race coupler

#### **I.1.4.1 Presentation**

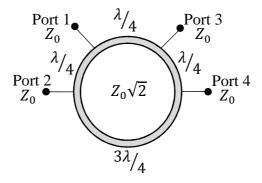

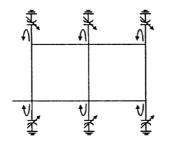

The rat-race coupler or hybrid ring directional coupler is a lossless reciprocal four ports network. The conventional circuit is schematized in Figure I.10. It comprises three 90° branches and one 270° branch. The characteristic impedance of the ring branches should be  $\sqrt{2}$  times the characteristic impedance of the ports terminations with the purpose of impedance matching at all ports.

Figure I.10 : Rat-race coupler

Historically, the first hybrid ring was described by Tyrrel in 1947 [15]. As a power divider, the rat-race coupler can be used for in-phase operation and  $180^{\circ}$  out-of-phase operation. However some of the components described herein are much more suitable and compact for in phase power division. Consequently, the rat race coupler is mainly used for  $180^{\circ}$  out-of-phase. For this application, a signal injected at port 2 divides evenly between ports 1 and 4 with  $180^{\circ}$  phase difference, meanwhile port 3 keeps isolated. As a power

combiner, signals are simultaneously injected in phase at ports 2 and 3, summing at port 1, and subtracting at port 4. Consequently, ports 1 and 4 are referred to as  $\Sigma$  and  $\Delta$ , respectively. By contrast, if signals injected at ports 2 and 3 have a 180° phase shift, sum and difference result inversely at ports 1 and 4. The bandwidth of this device is less than 25 %; improvement can be obtained by the addition of a fifth port. Scattering parameters demonstration is available in [12]. The [S] matrix has the following form:

$$[S] = \frac{-j}{\sqrt{2}} \begin{bmatrix} 0 & 1 & 1 & 0 \\ 1 & 0 & 0 & -1 \\ 1 & 0 & 0 & 1 \\ 0 & -1 & 1 & 0 \end{bmatrix}$$

(I-8)

#### I.1.4.2 Evolution

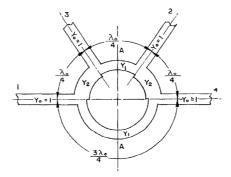

In 1961, [16] gave the design equations of a rat-race coupler with any degree of coupling. These equations are detailed in (I-9) with  $Y_1$  and  $Y_2$  the normalized admittances and  $a_i$  and  $b_i$  the incident and reflected waves at port *i*, respectively, as in Figure I.11.

Figure I.11 : Rat-race with any degree of coupling

$$Y_{1}^{2} + Y_{2}^{2} = 1$$

$$\frac{b_{3}}{b_{4}} = -\frac{Y_{2}}{Y_{1}}$$

$$\frac{b_{1}}{b_{2}} = \frac{Y_{2}}{Y_{1}}$$

(I-9)

In 2007, Mandal and Sanyal proved that there is more than one solution in terms of electrical lengths and characteristic impedances to bring to a lossless, isolated and full-matched component. Indeed, in [17] it is shown that an infinite number of solutions exist for coupler design at a given frequency. For all the solutions, characteristic impedances are less than the conventional  $Z_0\sqrt{2}$ . Theoretically, the characteristic impedance of the ring can be chosen between 0 and 70.7  $\Omega$  in a 50  $\Omega$  system. For each value, two ring electrical lengths are addressable, one giving a total ring electrical length higher than 1.5  $\lambda$  and one lower. The drawback is the bandwidth strengthening further and further with the decrease of the total electrical length.

#### I.1.4.3 Application

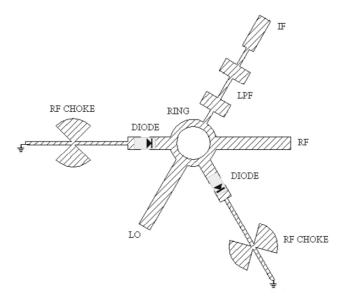

The main application of the rat race coupler is the balun function, used for instance in balanced mixers as in [18]. The single balanced mixer gets use of a microstrip rat race hybrid and two GaAs Schottky diodes, in the configuration given in Figure I.12. The LO and RF signals are mixed in these diodes and are isolated by the rat-race. The IF port is isolated from both the RF port and the LO port by the low-pass filter. The RF chokes provide a tuning mechanism and prevent the RF signal from leaking into ground. Measurement results show that conversion loss is less than 13.5 dB from 90 GHz to 97 GHz. Such mixer can be widely used in communication and radar systems in the mmW range.

Figure I.12 : Configuration of the rat-race balanced mixer [18].

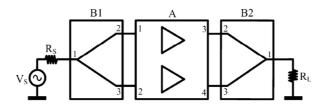

Another application of the rat race as a balun is the differential measurement as presented in [19]. The purpose is to measure the gain and noise performances of differential amplifiers by using single-ended measurements. Ideally, the input balun B1 shown in Figure I.13, equally splits the signal along two 180° out-of-phase branches. The behaviour of the output balun B2 is equivalent, although combining the output signals from the amplifiers A. Baluns to characterize a differential amplifier allow the use of conventional two ports measurement equipment.

Figure I.13: Measurement procedure of a differential amplifier using baluns.

## I.2 Reflection Type Phase Shifter

#### I.2.1 Principle and theory

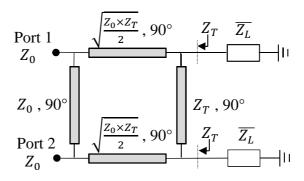

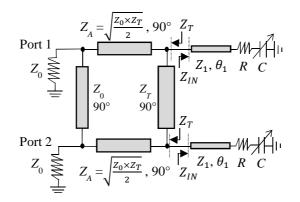

The first Reflection Type Phase Shifter (RTPS) was proposed in 1960 by Hardin *et al.* [20]. The RTPS is composed by the branch-line coupler given in Figure I.7 with equal power split loaded by two identical varactors as in Figure I.14. The usual input and isolation ports of the branch-line coupler alone, ports 1 and 2 in Figure I.14, have a port impedance of  $Z_0$ , whereas the usual through and coupled ports have a port impedance of  $Z_T$ . The input signal is divided into two parts. Each part is reflected by a reflective load, to finally combine at the last port.

Figure I.14 : RTPS loaded by varactors

The calculation of the transmission parameter  $S_{21}$  with the *S* matrix of the branchline coupler loaded by the variable impedances  $\overline{Z_L}$  easily brings to:

$$S_{21} = j\bar{\Gamma} \tag{I-10}$$

with  $\overline{\Gamma}$  the reflection coefficient between the outputs of the branch-line and the loads defined as:

$$\bar{\Gamma} = \frac{\overline{Z_L} - Z_T}{\overline{Z_L} + Z_T} \tag{I-11}$$

Considering the load  $\overline{Z_L}$  as an ideal varactor  $1/jC\omega$ , the magnitude of the transmission parameter  $S_{21}$  is 1, which means that all the power is transmitted, while the phase depends on the reflection coefficient  $\overline{\Gamma}$  and so, on the load  $\overline{Z_L}$ . The principle of the RTPS is demonstrated. Intentionally, the two following sub-parts which detail the theoretical equations for loss and phase shift are not referenced. To our best of knowledge, the analysis throughout the literature was not enabling to enlighten the compromise between minimized losses and maximized phase shift. The following demonstrations are thus totally novel.

#### I.2.1.1 Insertion loss

In practice the load is not ideal and leads to losses. To represent losses, a resistance R representing the loss was connected in series with  $1/jC\omega$ .  $\overline{Z_L}$  can be written as:

$$\overline{Z_L} = R + \frac{1}{jC\omega} = R \frac{1 + j/Q}{j/Q} = R(1 - jQ)$$

(I-12)

with Q (I-13) the quality factor of the varactor.

$$Q = \frac{1}{R \cdot C \cdot \omega} \tag{I-13}$$

Under these conditions, the reflection coefficient  $\overline{\Gamma}$  is:

$$\bar{\Gamma} = \frac{\overline{Z_L} - Z_T}{\overline{Z_L} + Z_T} = \frac{R(1 - jQ) - Z_T}{R(1 - jQ) + Z_T} = \frac{1 - \frac{Z_T}{R} - jQ}{1 + \frac{Z_T}{R} - jQ} = \frac{1 - \kappa - jQ}{1 + \kappa - jQ}$$

(I-14)

with  $\kappa = \frac{Z_T}{R}$ .

The magnitude of  $S_{21}$  is thus given by:

$$|\overline{S_{21}}| = |\overline{\Gamma}| = \sqrt{\frac{\left(1 - \frac{Z_T}{R}\right)^2 + Q^2}{\left(1 + \frac{Z_T}{R}\right)^2 + Q^2}} = \sqrt{\frac{(1 - \kappa)^2 + Q^2}{(1 + \kappa)^2 + Q^2}} = \sqrt{\frac{1 + \left(\frac{1 - \kappa}{Q}\right)^2}{1 + \left(\frac{1 + \kappa}{Q}\right)^2}}$$

(I-15)

According to (I-15),  $\kappa$  has to be much greater or much lower than 1 to get  $|\overline{S_{21}}|$  close to 1 and so to reduce the insertion loss. If  $Z_T = Z_0$  (for the conventional branch-line coupler), since  $Z_0$  and R are both fixed values, this condition cannot be met for lossy varactors with the simple configuration given in Figure I.14. Looking at  $\kappa = \frac{Z_T}{R}$ , it is straightforward that by increasing  $Z_T$ , the condition  $\kappa \gg 1$  is roughly met and therefore the insertion loss is reduced. In accordance with the formulas given in (I-7),  $Z_T$  may take any desired value while the branch-line coupler given in Figure I.14 would keep equal split and matched ports 1 and 2.

#### I.2.1.2 Relative phase shift

According to (I-10) and (I-14) the phase of the transmission parameter  $S_{21}$  of the RTPS is:

$$\varphi_{S_{21}} = \frac{\pi}{2} + Arg(\bar{\Gamma}) = \frac{\pi}{2} + Arg\left(\frac{1-\kappa-jQ}{1+\kappa-jQ}\right)$$

$$= \frac{\pi}{2} + ArcTan(-Q/(1-\kappa)) + ArcTan(Q/(1+\kappa))$$

(I-16)

Among the two possible solutions for minimizing the insertion loss, the only one leading to a variable phase according to Q and so to C, is a  $\kappa$  much greater than 1. Indeed, with  $\kappa \gg 1$ :

$$\varphi_{S_{21}} \approx \frac{\pi}{2} + 2 \cdot ArcTan(Q/\kappa) = \frac{\pi}{2} + 2 \cdot ArcTan\left(\frac{1}{Z_{\rm T} \cdot C \cdot \omega}\right) \tag{I-17}$$

We named  $C_{min}$  and  $C_{max}$  the minimum and maximum values of the varactor. The relative phase shift calculated as  $\varphi_{S_{21}(Cmin)} - \varphi_{S_{21}(Cmax)}$  is:

$$\Delta \varphi \approx 2. \left[ ArcTan\left(\frac{1}{Z_T \cdot C_{min} \cdot \omega}\right) - ArcTan\left(\frac{1}{Z_T \cdot C_{max} \cdot \omega}\right) \right]$$

(I-18)

Theoretically, if the condition  $\kappa \gg 1$  is checked and if the varactor varies between 0 and  $+\infty$ ,  $\Delta \varphi$  could reach 180° without insertion loss. However, varactors have a limited range so that only a maximum relative phase shift may be reached corresponding to a fixed value of  $Z_T$ . The equation (I-18) is derived according to  $Z_T$  and fixed equal with 0 in order to find the value of  $Z_T$  leading to the maximal  $\Delta \varphi$ . The obtained equation is given in (I-19), and is consequently the condition to respect to get the maximal  $\Delta \varphi$ , considering that  $\kappa \gg 1$ .

$$1 = \frac{\sqrt{\frac{1}{C_{min}.C_{max}.\omega^2}}}{Z_T}$$

(I-19)

To reduce the insertion loss,  $Z_T$  has to be as high as possible whilst to get the highest relative phase shift the equation (I-19) has to be verified. For a given varactor, two different criteria have to be met by only one variable. In consequence, it is not possible to benefit simultaneously from the lowest loss with the highest relative phase shift. A compromise between these two characteristics has to be found. The next part illustrates this case with a practical example.

#### I.2.1.3 Practical example with non-ideal varactor

Let's choose a varactor with a capacitor value *C* in the range [1-5] pF with a parasitic resistance *R* of 2  $\Omega$  at 2 GHz. According to (I-19)  $Z_T$  has to be fixed to 35.6  $\Omega$  to get the maximal relative phase shift. Table I.1 sums up the calculated performances of two RTPS realized with ideal hybrid couplers, taking into account only the parasitic resistance *R* of the load. For one RTPS  $Z_T = 35.6 \Omega$ , chosen to get the maximal relative phase shift, and for the other one  $Z_T = 100 \Omega$ , chosen as high as possible to respect  $\kappa \gg 1$  while taking into account standard technology limitation.

| Ζ <sub>τ</sub><br>(Ω) | к    | Approximate $\Delta_{\varphi}$ according to (I-18) (°) | Exact $\Delta_{arphi}$ according to (I-16) (°) | Max. insertion loss<br>according to (I-15)<br>(dB) | FoM<br>(°/dB) |  |

|-----------------------|------|--------------------------------------------------------|------------------------------------------------|----------------------------------------------------|---------------|--|

| 35.6                  | 17,8 | 80.57                                                  | 83.53                                          | 0.81                                               | 75.3          |  |

| 100                   | 50   | 58.79                                                  | 58.94                                          | 0.34                                               | 92.1          |  |

Table I.1 : RTPS performances with simple capacitive reflective load.

The figure-of-merit (FoM) of a phase shifter is defined as the relative phase shift over the maximum insertion loss. It would not be accurate to calculate the FoM only taking into account the loss due to R, if we consider that these circuits were fabricated on a

dielectric substrate with  $\tan \delta = 0.0027$ , the insertion loss added by the branch-line coupler is estimated to about 0.3 dB. So the FoMs presented here take also into account the insertion loss induce by the branch-line coupler.

With  $Z_T = 35.6 \Omega$ , the relative phase shift is about 83° with 0.81 dB of insertion loss leading to a FoM of 75.3 °/dB. As expected, with  $Z_T = 100 \Omega$  the insertion loss is lower with 0.34 dB but the relative phase shift as well with 59°. The FoM is higher with 92.1 °/dB. We can notify that the criteria  $\kappa \gg 1$  is respected in both cases, because the error between the approximate  $\Delta \varphi$  and the exact one is less than 4 %.

#### I.2.1.4 Conclusion

The ideal RTPS is lossless and has a phase controlled by the loads connected at the branch-line output ports. Due to the limited range and the parasitic resistance of the varying loads, the performances of the phase shifter are getting worse. With the flexible output port impedance of the branch-line coupler, it is possible to find different values than the classical 50  $\Omega$  in such a way that performances can be improved. It will be a compromise between the relative phase shift and the loss level. However, in this configuration the maximum relative phase shift stays modest and not high enough for some applications. In order to get more degrees of freedom than the only  $Z_T$  for better performances and compromise, networks may be placed between the output ports of the branch-line coupler and the varactors. As we have seen, the purpose is to get a value of  $Z_T$  different from R, so the added network can be called a mismatching network.

### I.2.2 Modified reflective load

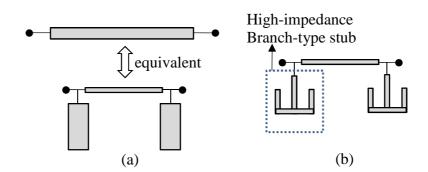

#### I.2.2.1 Serial inductance

A modified reflective load can be designed with one, two or even more varactors depending on the targeted phase shift. As a general rule, the more varactors, higher the phase shift. The simplest modified reflective load used as a mismatching network is a series inductance with the varactor, also named series-resonating load. We will first explain the advantages of this widely used reflective load before presenting mismatching networks with or without inductance, but of higher complexity.

If the reflective load consists in a fixed inductance L in series with an ideal varactor C as in Figure I.15, the reflective load becomes:

$$Z_L = jL\omega + \frac{1}{jC\omega} \tag{I-20}$$

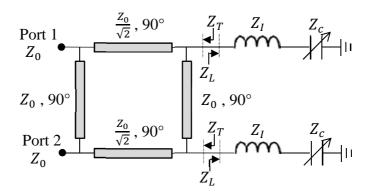

Figure I.15 : RTPS with inductive load.

The minimum and maximum values of  $Z_L$  are reached for the extreme values of the variable C. For this study, C and L are ideal, e.g. without loss, and C can reach any value in the  $[0;+\infty]$  range.

For

$$C = 0$$

:  $Z_L = jL\omega - j\infty = -j\infty$  (*L* has no influence)

For  $C = +\infty$ :  $Z_L = jL\omega + \frac{1}{+j\infty} = jL\omega$  if  $L = +\infty$ ,  $Z_L = +j\infty$

So  $\Delta \varphi = 2$ .  $\left[ArcTan\left(\frac{-j\infty}{Z_0}\right) - ArcTan\left(\frac{+j\infty}{Z_0}\right)\right] = 2.(90 + 90) = 360^{\circ}$ .

When adding a series inductance the maximum relative phase shift increases up to  $360^{\circ}$  as long as its value tends to be  $+\infty$ . In practice the value of *C* and *L* are limited. Hence the relative phase shift is much lower, so that a compromise should be found between phase shift and insertion loss. This is shown in the state-of-the-art.

#### I.2.2.2 State-of-the-art at RF frequencies

#### I.2.2.2.a Reflective load with lumped inductance and one varactor

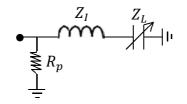

With an lumped inductance in series with a capacitor, a relative phase shift of 97° with 1.5 dB of maximum insertion loss was measured at 2 GHz in [21]. The varactor range value is [1.4-8] pF with a parasitic resistance of 2  $\Omega$ . The insertion loss variation for the 97° is 0.4 dB. The relative phase shift is much below the 360° theoretical maximum one calculated above. This is due to the limited range of values of the varactor and the finite inductance value. Moreover, there is a compromise to make between the insertion loss and the insertion loss variation. The outputs ports impedance  $Z_T$  of the branch line coupler is 50  $\Omega$ , leading to an impedance transforming ratio  $r_Z = Z_0/Z_T = 1$ . Still in [21], another RTPS with the same reflective load was measured, but with  $Z_T = 12.5 \Omega$ , e.g.  $r_Z = 4$ . In that condition the relative phase shift is now 240° with 3.8 dB of maximum insertion loss and an insertion loss variation of 2.2 dB. In counterpart of the increase of almost 150 % of the relative phase shift, both the maximum insertion loss and the insertion loss variation for 2.2 dB. In counterpart of the insertion loss variation parallel with the load, as shown in Figure I.16.

Figure I.16 : Reflective load proposed in [21].

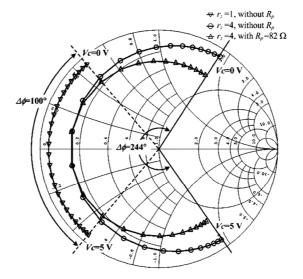

This resistance smoothes the loss at its maximum value but does not modify the relative phase shift. Indeed, concerning the device with  $R_P$ , the maximal insertion loss is still 3.8 dB but the variation of this characteristic dwindles as low as 0.1 dB. The return loss is better than 20 dB. Figure I.17 shows the measured reflection coefficient of the three presented RTPSs at 2 GHz.

Figure I.17 : Reflection coefficient of the three types of reflective load at 2 GHz.

These results confirmed that it is not possible yet to get a relative phase shift of  $360^{\circ}$  with only one varactor in series with an inductance, due to their limited range. Other variable reflective loads have been enfaced with several varactors in order to increase  $\Delta \varphi$ . Some of them include a series inductance.

#### I.2.2.2.b Reflective load with lumped inductance and several varactors

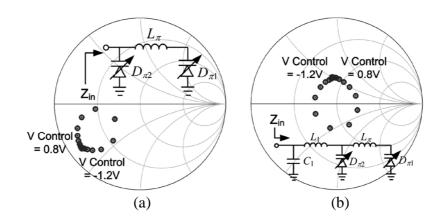

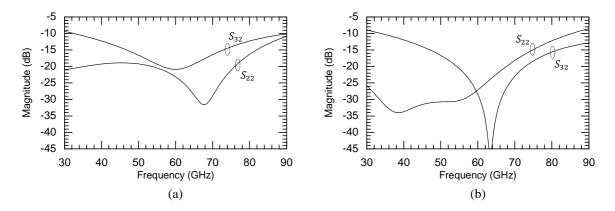

In [22], a varactor was added before the reflective load previously presented in Figure I.15, leading to a  $\Pi$ -shape as described in Figure I.18(a). The simulation Figure I.18(a) shows that the impedance variation of  $Z_{IN}$  is not centred anymore on the Smith chart real axis. Consequently the relative phase shift is really small. Therefore, an impedance transformation was added. On the Smith chart in Figure I.18(b), it can be seen that the simulated relative phase shift becomes higher than 360° with the impedance transformation.

Figure I.18 : Simulated Impedance trajectory on the Smith chart. (a) П-shape load without impedance transformation. (b) П-shape load with impedance transformation.

This RTPS was implemented in a 0.18  $\mu$ m CMOS technology at 2.45 GHz. The two varactors have a capacitance range of [0.52-1.4] pF and [1.9-5.4] pF, resulting in a measured relative phase shift of 340° with a maximum insertion loss of 12.6 dB and a loss variation of 4 dB. With this topology the simulated relative phase shift shown that 360° can be reached but the measurement result was limited to 341°.

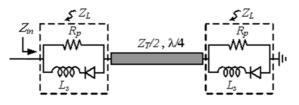

In [23], the reflection loads are composed by two inductances in series with varactors, interconnected by a quarter-wavelength TL, as shown in Figure I.19.

Figure I.19 : Reflective load proposed in [23].

Here again the resistance  $R_p$  was used to smooth the insertion loss, and  $r_Z$  was modified and fixed to 1.25. The measured maximum relative phase shift is 407° and the insertion loss is 4.6 dB at 2 GHz with a variation of 0.4 dB. The phase shifter was realized with silicon varactors of a [1.4-8] pF capacitance range and an average 2  $\Omega$  resistance.

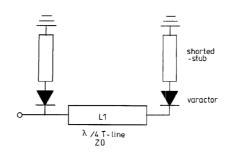

#### I.2.2.2.c Reflective load without lumped inductance

It is also possible to get  $360^{\circ}$  of relative phase shift with a reflective load without inductance. The reflective load suggested in Figure I.20 by [24] consists in two shorted transmission-line stubs connected in series with the varactors. Those two parallel arms are interconnected with a quarter-wave TL. It increases both the total amount and the linearity of the phase shift. The phase shifter showed a total phase shift of  $380^{\circ}$  and a maximum insertion loss of 5.3 dB with a variation of 1.6 dB at 10 GHz. The high insertion loss is mainly due to the GaAs beam-lead varactor diodes which exhibit a 5.5  $\Omega$  parasitic resistance.

Figure I.20 : Reflective load proposed in [24].

In [25], 6 varactors were used in each reflective load.  $Z_L$  is shown in Figure I.21. Each one of the seven TL is 50- $\Omega$  quarter-wavelength arms with a varactor diode at every node. All the varactors are similar, with a [0.2-1.1] pF capacitance range. The relative phase shift is really high with 500°. The maximum insertion loss is 3.5 dB with 2.5 dB of variation. The main drawbacks of this topology are the big area needed due to the numerous quarter-wavelength TLs and the cost with the use of 12 varactors for one RTPS.

Figure I.21 : Reflective load proposed in [25].

## I.2.3 Branch-line coupler substitution

The above literature review showed that all of the papers that dealt with the RTPS assumed by default that the coupler, which is the backbone of the phase shifter, is a branchline coupler. However, the Lange coupler or quarter-wavelength coupled lines coupler can be used instead, particularly in order to increase the bandwidth. The RTPS presented in [26] consists in a CPW Lange coupler with 3-dB coupling and, as a reflective termination, a combination of two interdigital capacitors in series with an inductor. The relative phase shift is 95° at 2.5 GHz with a 96 % relative bandwidth determined for an input return loss better than 10 dB, whereas it is about 10-15 % for a RTPS using a branch-line coupler.

[27] shows that a RTPS can be designed using less than one tenth of a wavelength coupled structure if the mode impedances of that structure are chosen properly. At 2.2 GHz, the relative phase shift is  $373^{\circ}$  with a bandwidth of 36 % under 10 dB of input return loss. To achieve the maximum possible phase range across the required bandwidth, the odd-mode impedance of the short coupled structure needs to be around 10  $\Omega$ , whereas the even-mode impedance needs to be around 200  $\Omega$ . Thus, the optimized short-section design requires higher even-mode impedance and lower odd-mode impedance than the values needed in the traditional design method. To realize such extreme impedances, slotted

ground plane was used, which results in a reduction in the even-mode capacitor and, thus, an increase in the even-mode impedance. Concerning the requirement for a range of low odd-impedance values, it can be achieved by connecting a chip capacitor between the middle points of the coupled lines. This capacitor has no effect on the even-mode circuit. However, it increases the equivalent odd-mode capacitor of the coupled structure and thus decreases the odd-mode impedance.

## **I.2.4 Applications**

Phase shifters are used to adjust transmission phase in a system; they can be fixed digital phase shifters or analogue variable types. They are key elements in phased arrays, especially tunable phase shifters. They can be used to perform adaptive beam-forming or beam-steering; they enable multi-beam operation and are also used in phase-modulation communication systems. Recently, the demand for phased array systems operating at millimetre-wave bands has increased owing to the applications of security, imaging, radars (automotive), military surveillance and satellite communication. The RTPS is praised as a low control complexity device (only one control voltage), owing good stability against temperature changes and low sensitivity to process tolerances. Nevertheless, its main advantage stays the independency between ports matching and phase tunability thanks to the recourse of a four-port coupler which leads to design simplicity and high electrical performance.

| Ref. | Freq.<br>(GHz) | Phase<br>shift<br>(°) | Average<br>insertion<br>loss<br>(dB) | Insertion<br>loss<br>variation<br>(dB) | Varactor<br>range<br>(pF) | Parasitic<br>resistance<br>(Ω) | Lumpe d<br>inductance | Return<br>loss<br>(dB) | 10 dB<br>return loss<br>bandwidth<br>(%) | Max.<br>insertion<br>loss in the<br>BW<br>(dB) | Nb. of<br>varactors | Type of<br>RTPS  | FoM<br>(°/dB) |

|------|----------------|-----------------------|--------------------------------------|----------------------------------------|---------------------------|--------------------------------|-----------------------|------------------------|------------------------------------------|------------------------------------------------|---------------------|------------------|---------------|

| [21] | 2              | 237                   | 3.75                                 | ±0.05                                  | 1.4 - 8                   | 2                              | Yes<br>(2.7 nH)       | -21                    | >10                                      | >4.6                                           | 2                   | Branch-<br>line  | 62.4          |

| [23] | 2              | 407                   | 4.4                                  | ±0.1 for<br>360°<br>±0.2 for<br>407°   | 1.4 - 8                   | 2                              | Yes<br>(-)            | -20                    | >10                                      | >5.8                                           | 4                   | Branch-<br>line  | 88.5          |

| [24] | 10             | 380                   | 4.5                                  | ±0.7                                   | 0.16 - 2.9                | 5.5                            | No                    | -10                    | -                                        | -                                              | 4                   | Branch-<br>line  | 73.1          |

| [25] | 2.05           | 500                   | 2.2                                  | ±1.25                                  | 0.2 - 1.1                 | 2                              | No                    | -12                    | >10                                      | >3.5                                           | 12                  | Branch-<br>line  | 142.9         |

| [26] | 2.5            | 95                    | 1.6                                  | ±0.4                                   | 1.35-4.2                  | <1                             | Yes<br>(2.2 nH)       | -15                    | 96                                       | 3.8                                            | 4                   | Lange<br>coupler | 47.5          |

| [27] | 2.2            | 373                   | 2.5                                  | ±0.75                                  | 0.6-4.8                   | 2                              | Yes<br>(1.7 nH)       | -13                    | 36                                       | 4                                              | 2                   | Lange<br>coupler | 116.6         |

### I.2.5 State-of-the-art review

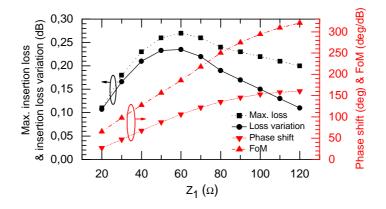

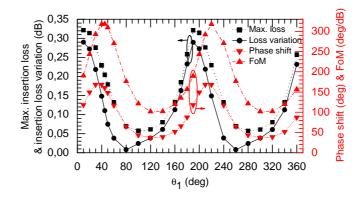

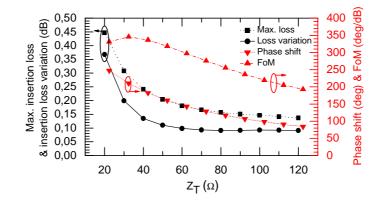

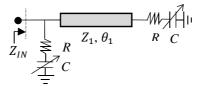

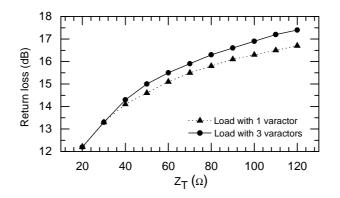

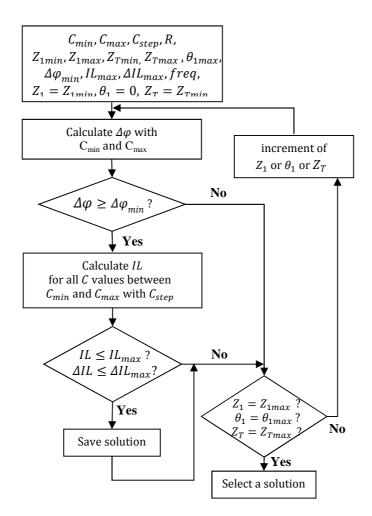

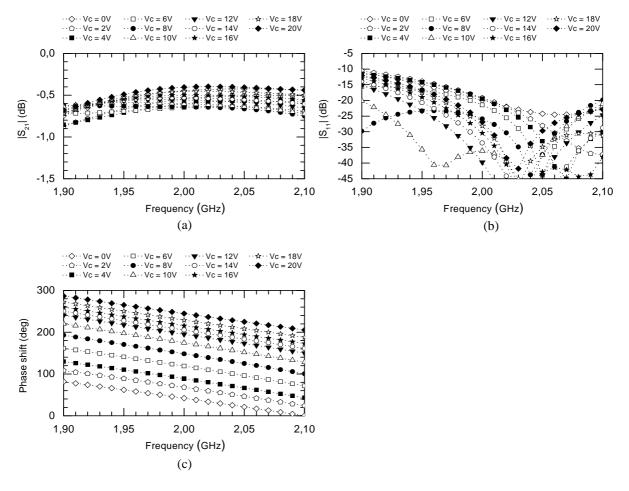

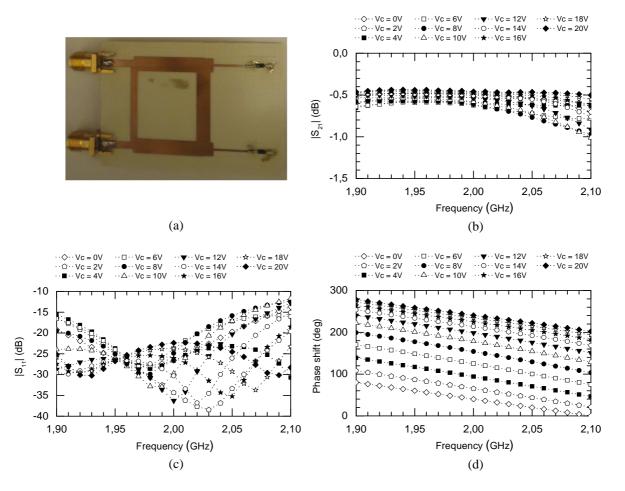

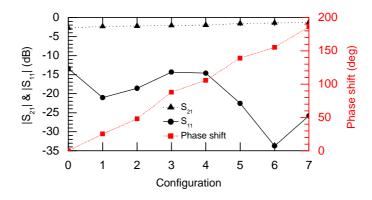

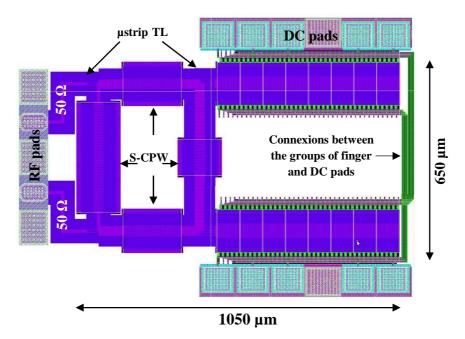

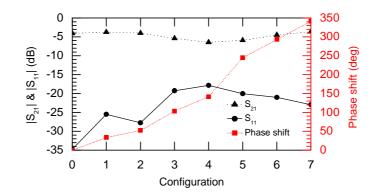

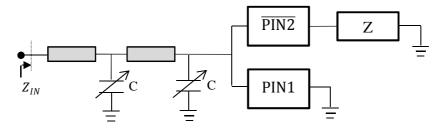

Table I.2 : State-of-the-art of the RTPS in PCB technology.