# SINGLE EVENT TRANSIENT AND TOTAL IONIZING DOSE EFFECTS ON III-V MOSFETs FOR SUB-10 NM NODE CMOS

By

Kai Ni

# Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

# DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

December, 2016

Nashville, Tennessee

Approved:

Ronald D. Schrimpf, Ph.D. Daniel M. Fleetwood, Ph.D. Robert A. Reed, Ph.D. Michael L. Alles, Ph.D. Sokrates T. Pantelides, Ph.D.

#### ACKNOWLEDGEMENTS

Looking back at my Ph.D. study, this dissertation would lose its luster without expressing my appreciations to many people for their help and encouragement. First, I would thank my advisor, Professor Ron Schrimpf, for his tremendous support and guidance through my Ph.D. study. He offers me opportunities that lead to experience I will cherish all my life. I am also grateful for his constructive and insightful advices which give me great encouragement in choosing my career path. From him, I not only learn how to conduct scientific research, I also indebted to him for his philosophy towards research and life.

I would thank Professor Dan Fleetwood for his continuous support and guidance in my research. His breadth and depth of knowledge give me great inspiration. His photographic memory absolutely impresses me. He sets a good example for me in how to be a good scientist. I would also thank Professor Robert Reed for guiding me into single event effects and laser. The discussions with him have always been reassuring. I would also thank Professor Michael Alles for all the valuable and constructive discussions on the research direction and sharing me his experience. I would also thank Professor Sokrates Pantelides for serving on my committee and financially supporting me in learning semiconductor fabrication. I also enjoy the "Condensed matter physics" course and all the little interesting stories.

I am also grateful for our partners at MIT, Jianqiang Lin, Alon Vardi, Xiaowei Cai, and Professor Jesús del Alamo, for providing us test devices. They have always been successful in designing state-of-the-art devices and very helpful in customizing the test devices for us. I would also thank Professor del Alamo for his rigorous scientific attitude in editing my papers, which greatly benefits me. I would also thank for Shufeng Ren from Yale, Ling Dong, Jingyun Zhang, and Professor Peide D. Ye from Purdue for providing me test samples. They have always been responsive and helpful.

Special thanks have to be given to Enxia Zhang for her endless support during my experiments and in choosing my research direction. She is always there to help me whenever I have troubles during my research. Without her, my Ph.D. study would be much more difficult. I would also thank Bo Choi for tutoring me semiconductor fabrication hand by hand. His self-styled and selfconsistent philosophy towards life and research greatly impresses me. I would also thank Andrew L. Sternberg for his efforts in the laser test. He has done an excellent job in helping me perform my experiments. I would also thank Geert Eneman and Eddy Simone for three months' happy life in IMEC, Leuven. It is my great pleasure to work with these smart people. They have always encouraged me and made me confident in my work. I am absolutely impressed by the vast amount of publications Eddy has made. I will remember all the happy walks after lunch for the rest of my life. I would also thank Nadine Collaert and Anda Mocuta for their trust and opportunities.

I am also grateful for my fellow graduate students in the Radiation Effects and Reliability group and a few students outside the group. Specially, I would thank Xuan Zhang, Nick Hooten, Geoff Bennett, Guoxing Duan, Jin Chen, Isaak Samsel, Xiao Shen, and Yevgeniy Puzyrev for helping me quickly engaged in the experiments and insightful discussions. It is also my great pleasure to have Chundong Liang, Yanran Chen, Rong Jiang, Pan Wang, Huiqi Gong, Pengfei Wang, Simeng Zhao, and Peng Wang in the lab and I will cherish all the happy discussions.

In the last but not the least, I would thank my wife Zhi Zheng for her discussion, support and love, which make my life more colorful and enjoyable. I would also thank my mom and my sister for their endless love and support.

# LIST OF TABLES

| Table 1.1. Electron effective mass and energy separations for different valleys of different          |

|-------------------------------------------------------------------------------------------------------|

| materials [24]                                                                                        |

| Table 1.2. Ionized charge per unit length for an ion having a LET of 1MeV•cm <sup>2</sup> /mg [75] 13 |

| Table 2.1. Details of heavy ions used to test GaAs surface channel MOSFETs                            |

| Table 3.1. Details of ions used in experiment                                                         |

| Table 4.1. Materials parameters and carrier generation mechanism at two different wavelengths         |

|                                                                                                       |

| Table 6.1. Charge collection characteristics of the III-V MOSFETs with different architectures        |

|                                                                                                       |

# LIST OF FIGURES

| 40 years of microprocessor trend data [1]                                                    |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Trend in state-of-the-art high performance (HP) CMOS transistor innovation.                  |  |  |  |  |  |  |  |

| Transformative changes in materials (high-k dielectric, Ge, III-V channel) and the           |  |  |  |  |  |  |  |

| transistor architecture (3D, Tunnel FET) being implemented and explored to maintain          |  |  |  |  |  |  |  |

| historical rate of performance, density and power scaling [3]                                |  |  |  |  |  |  |  |

| 1.3 (a) Electron and hole mobility of group III-V compound semiconductors. Electron          |  |  |  |  |  |  |  |

| mobility is marked red and hole mobility is in blue. The arrow indicates the increase of     |  |  |  |  |  |  |  |

| biaxial compressive strain. (b) Electron injection velocity in III-V materials [15] 4        |  |  |  |  |  |  |  |

| Schematic diagram illustrating physical processes in MOS system after ionizing               |  |  |  |  |  |  |  |

| radiation [51]                                                                               |  |  |  |  |  |  |  |

| (A) Charge generation and collection processes in a reverse biased pn junction and (B)       |  |  |  |  |  |  |  |

| the resultant current transient caused by the passage of a high-energy ion [54]              |  |  |  |  |  |  |  |

| Neutron-induced critical charges for SRAM devices at different technology nodes.             |  |  |  |  |  |  |  |

| Minimum critical charge refers to the minimum value of all state nodes and state             |  |  |  |  |  |  |  |

| transitions [59]9                                                                            |  |  |  |  |  |  |  |

| Threshold voltage shift as a function of irradiation dose for (a) InGaAs planar quantum-     |  |  |  |  |  |  |  |

| well MOSFETs [69] and (b) InGaAs FinFET and nanowire GAA MOSFETs [70] 11                     |  |  |  |  |  |  |  |

| SEU cross section vs. LET for GaAs MESFET based DCFL latch circuit [76]12                    |  |  |  |  |  |  |  |

| Current path for gate to drain charge collection in a SRAM cell [79] 14                      |  |  |  |  |  |  |  |

| . Schematic diagram illustrating (a) the bipolar gain and (b) channel-modulation charge      |  |  |  |  |  |  |  |

| enhancement mechanisms that contribute to the charge collection processes of GaAs            |  |  |  |  |  |  |  |

| FETs [73]                                                                                    |  |  |  |  |  |  |  |

| . Schematic of an ion hitting the gate edge of a GaAs MESFET device and the charge           |  |  |  |  |  |  |  |

| collection efficiency/effective collection length along the transistor width direction [91]. |  |  |  |  |  |  |  |

| The efficiency is normalized to the maximum efficiency                                       |  |  |  |  |  |  |  |

| . Proposed hardening techniques. (a) Buried p layer under the active region and (b) low-     |  |  |  |  |  |  |  |

| temperature GaAs buffer layer                                                                |  |  |  |  |  |  |  |

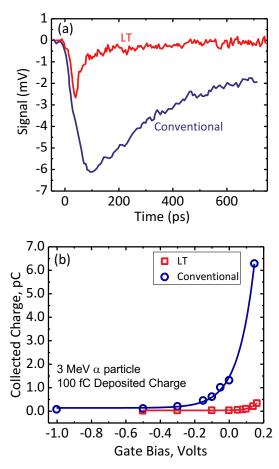

| (a) Charge collection transients and (b) collected charge measured for n-channel HFET        |  |  |  |  |  |  |  |

| devices with and without LT GaAs buffer layer exposed to 3 MeV $\alpha$ particle irradiation |  |  |  |  |  |  |  |

| [100]                                                                                        |  |  |  |  |  |  |  |

|                                                                                              |  |  |  |  |  |  |  |

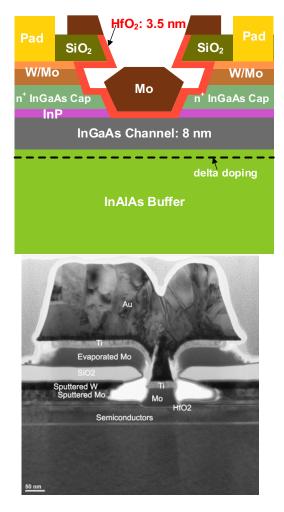

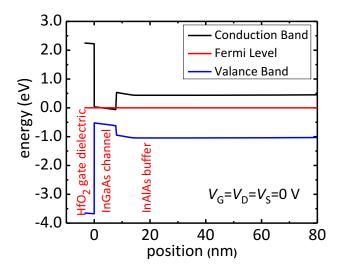

| Fig. 2.1.                            | (a) Schematic cross section of the device with $L_G = 4 \ \mu m$ and TEM picture of the gate                                                                                                                                                                                                                                                                                                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | stack; (b) band diagram along a vertical cutline through the gate oxide at $V_G=V_D=V_S=0$                                                                                                                                                                                                                                                                                                       |

|                                      | V. The band diagram is generated from Sentaurus TCAD simulation                                                                                                                                                                                                                                                                                                                                  |

| Fig. 2.2.                            | Measured and simulated $I_D$ - $V_G$ transfer characteristics. $V_D = 50$ mV during                                                                                                                                                                                                                                                                                                              |

|                                      | measurement. Simulation is done with Sentaurus TCAD tools                                                                                                                                                                                                                                                                                                                                        |

| Fig. 2.3.                            | Device model used in 2D TCAD simulation. Here the drain is in the negative x direction                                                                                                                                                                                                                                                                                                           |

|                                      | and source is in the positive x direction. The red arrow indicates the strike location, $x =$                                                                                                                                                                                                                                                                                                    |

|                                      | -6 µm. For the simulation, Sentaurus TCAD tools are used                                                                                                                                                                                                                                                                                                                                         |

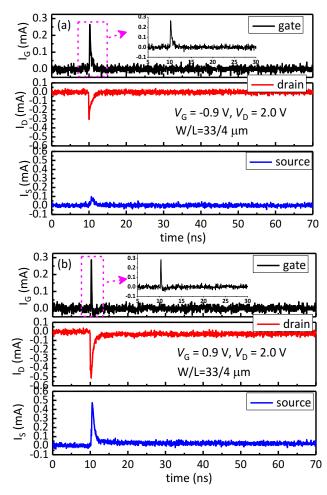

| Fig. 2.4.                            | Representative transients under oxygen ion irradiation at (a) OFF, $V_G = -0.9 V$ ; (b) ON                                                                                                                                                                                                                                                                                                       |

|                                      | bias conditions; $V_G = 0.9 V$ for a device with $L_G = 4 \mu m$ . For this device, $V_{TH} = 0.4 V$ .                                                                                                                                                                                                                                                                                           |

|                                      | The inset of the figure shows the zoom into the magenta box region                                                                                                                                                                                                                                                                                                                               |

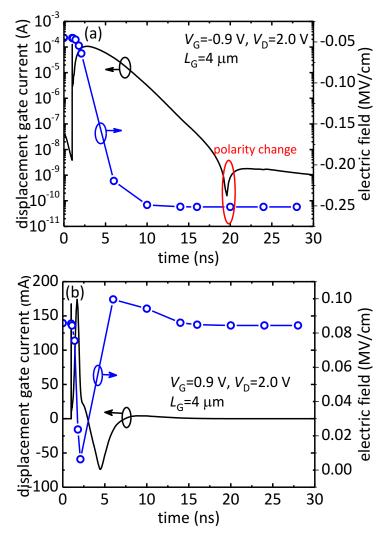

| Fig. 2.5.                            | Displacement gate current and electric field in $La_2O_3$ as a function of time at (a) $V_G$ = -                                                                                                                                                                                                                                                                                                 |

|                                      | $0.9 \text{ V}$ ; (b) $V_G = 0.9 \text{ V}$                                                                                                                                                                                                                                                                                                                                                      |

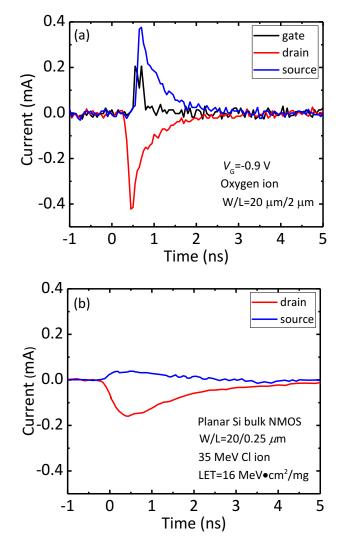

| Fig. 2.6.                            | Current transients for (a) GaAs surface channel MOSFET with W/L=20/2 $\mu m$ due to                                                                                                                                                                                                                                                                                                              |

|                                      | oxygen ion irradiation and (b) planar Si bulk NMOS with W/L=20/0.25 $\mu m$ due to Cl                                                                                                                                                                                                                                                                                                            |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                      | ion irradiation [124]                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 2.7.                            | ion irradiation [124]                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 2.7.                            |                                                                                                                                                                                                                                                                                                                                                                                                  |

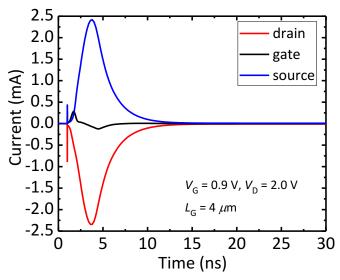

| Fig. 2.7.<br>Fig. 2.8.               | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu m$ . The                                                                                                                                                                                                                                                                              |

| C                                    | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu m$ . The current is scaled by the width of 33 $\mu m$                                                                                                                                                                                                                                 |

| C                                    | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu m$ . The current is scaled by the width of 33 $\mu m$                                                                                                                                                                                                                                 |

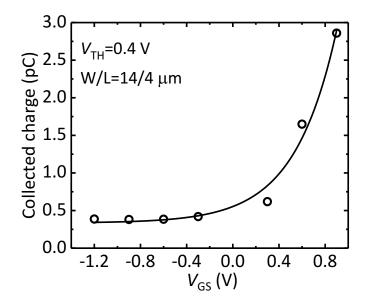

| Fig. 2.8.                            | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu m$ . The current is scaled by the width of 33 $\mu m$ . 28<br>Drain collected charge as a function of gate bias under oxygen ion irradiation. $V_D = 2 \text{ V}$ during irradiation. 29                                                                                              |

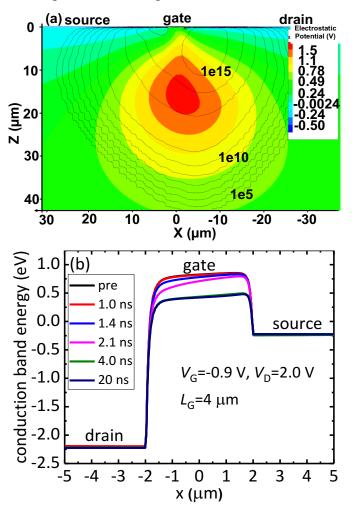

| Fig. 2.8.                            | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu m$ . The current is scaled by the width of 33 $\mu m$ . 28<br>Drain collected charge as a function of gate bias under oxygen ion irradiation. $V_D = 2 \text{ V}$ during irradiation. 29<br>(a) The color map shows the electrostatic potential difference and the contour plot shows |

| Fig. 2.8.                            | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.               | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.               | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.<br>Fig. 2.10. | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.<br>Fig. 2.10. | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.<br>Fig. 2.10. | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

| Fig. 2.8.<br>Fig. 2.9.<br>Fig. 2.10. | Simulated current transients at $V_G = 0.9 \text{ V}$ , $V_D = 2.0 \text{ V}$ when striking at $x = -6 \mu \text{m}$ . The current is scaled by the width of 33 $\mu \text{m}$                                                                                                                                                                                                                   |

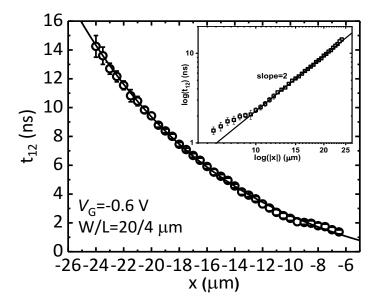

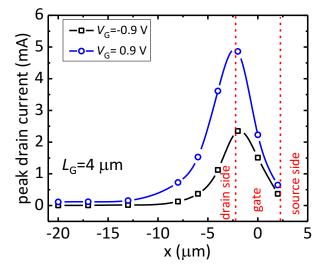

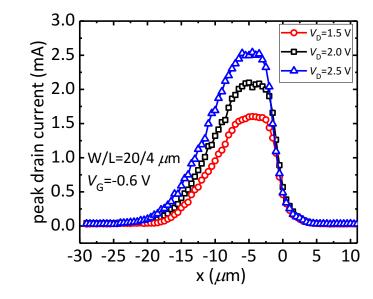

Fig. 2.16. Simulated peak drain current along a horizontal cut line at two different gate biases. 37

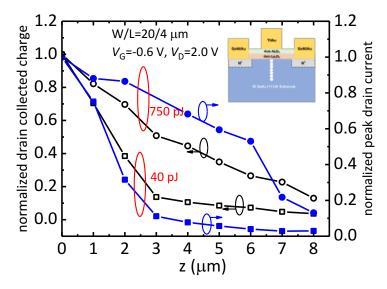

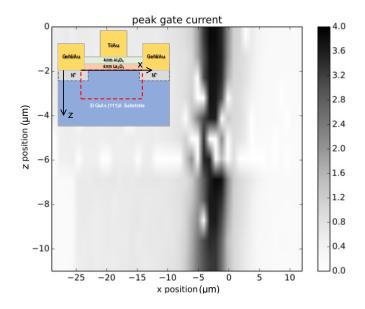

- Fig. 2.19. Peak gate current under the XZ area scan. The origin of the XZ plane is at the center of the gate and the front surface of the device. For this scan,  $V_G = -0.6 \text{ V}$ ,  $V_D = 2.0 \text{ V}$ ,  $V_{TH} = 0.3 \text{ V}$ . Laser pulse energy is 0.75 nJ. The white block in the center of the figure is due to loss of the data during experiment. The red box in the inset shows the scan area... 39

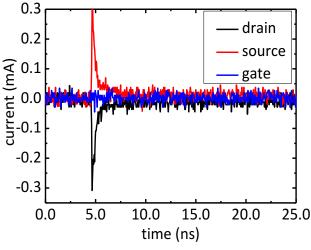

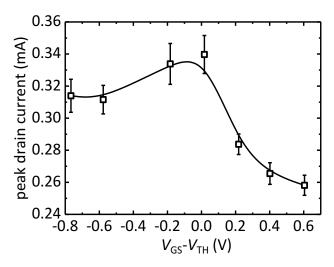

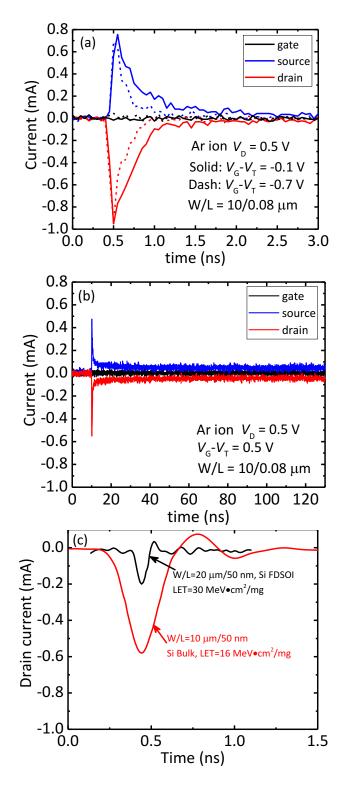

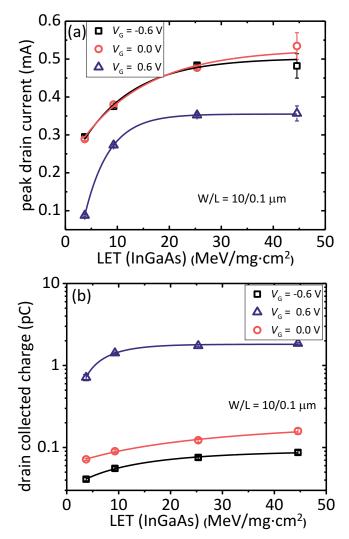

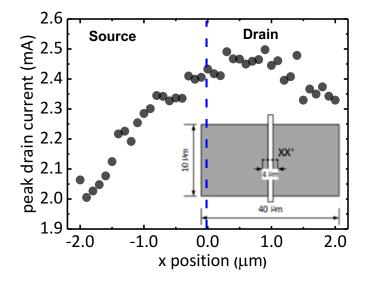

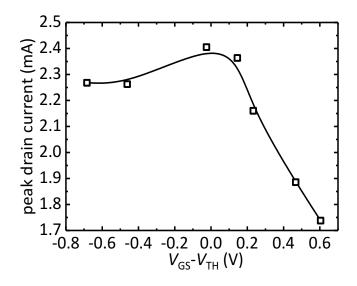

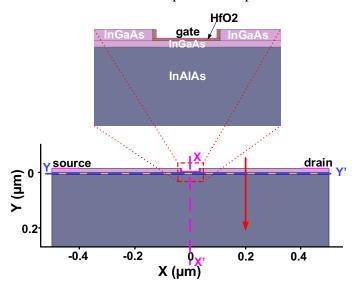

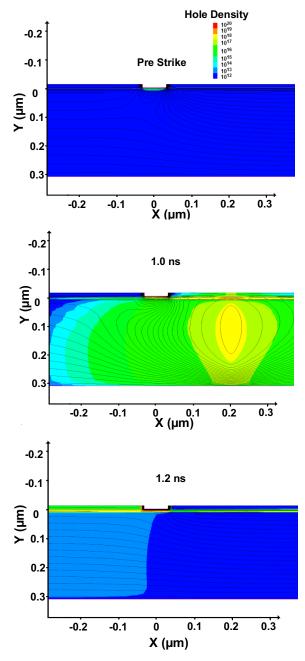

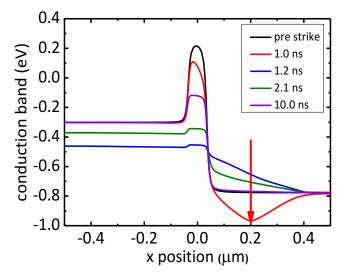

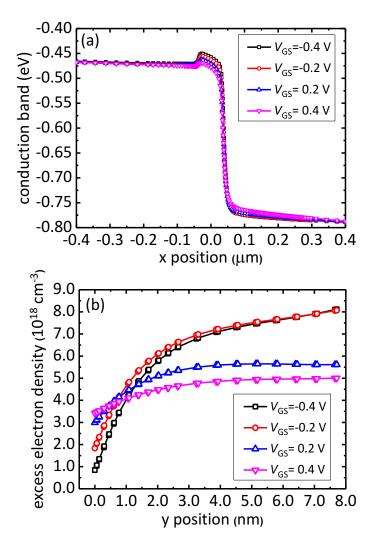

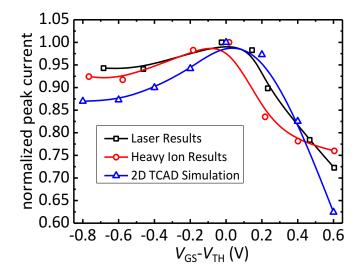

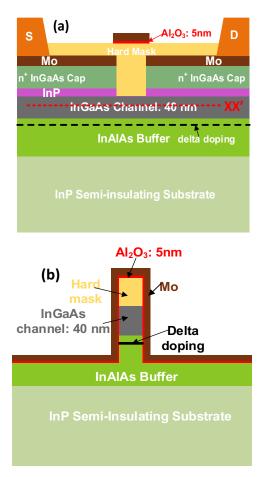

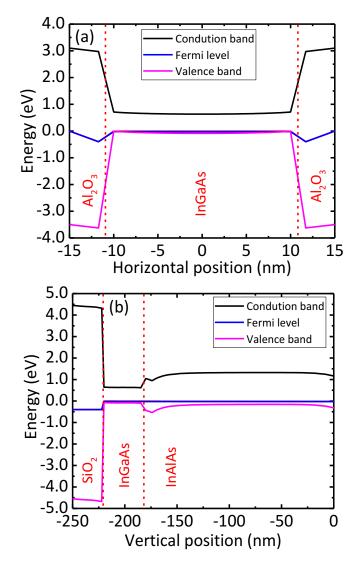

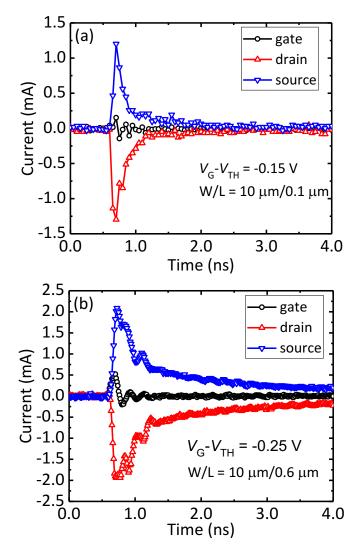

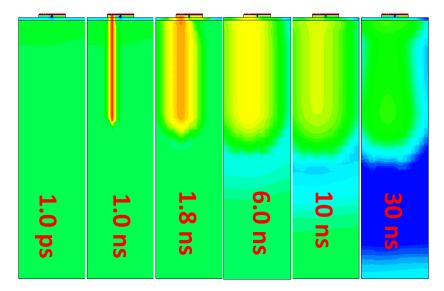

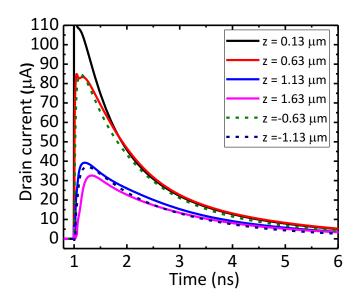

Fig. 3.4. Current transient for a device biased at  $V_{GS}-V_{TH} = -0.2$  V,  $V_{DS} = 0.5$  V with source Peak drain current vs. gate bias of at  $V_{DS} = 0.5$  V. The average flux is  $1 \times 10^8$ Fig. 3.5. particles/s•cm<sup>2</sup>. The error bars indicate the standard error of the mean. W/L=10  $\mu$ m/0.07 Transients due to Ar ion strike for device biased at (a)  $V_G = -0.6$  V and  $V_G = 0.0$  V, and Fig. 3.6. (b)  $V_G = 0.6 \text{ V}$ .  $V_T = 0.1 \text{ V}$ . (c) Drain current transients of Si FDSOI with size of W/L=20 µm/50 nm and body thickness of 11 nm, exposed to 808 MeV Kr ion with LET=30 MeV•cm<sup>2</sup>/mg [131] and Si planar bulk device with size of W/L=10  $\mu$ m/50 nm exposed (a) Peak drain current and (b) drain collected charge as a function of LET. Each data Fig. 3.7. point represents an average of 100 transients recorded. The error bar represents the standard deviation of the mean. The drain collected charge is obtained by integrating the drain current transients within a time window of 30 ns. This is to restrict the tail current Fig. 3.8. Peak drain current along the line scan XX' at bias  $V_{GS}$ - $V_{TH}$ =0 V,  $V_{DS}$ =0.5 V. The laser pulse energy is around 0.55 pJ. The source side has a negative x coordinate while the Fig. 3.9. Drain peak current vs. gate bias at  $V_{DS}=0.5$  V (each data point is taken as the average of Fig. 3.10. Device model that is used in the 2D TCAD simulation (red arrow indicates the center of strike location). Synopsys Sentaurus TCAD tools are used here for simulation. ...... 51 Fig. 3.11. Hole density and electrical potential plotted at 1.0 ps (pre-strike), 1.0 ns and 1.2 ns. The hole density is shown as color map and the electrical potential is shown as the equipotential line. The device is biased at  $V_{GS}$ - $V_{TH}$ =-0.2 V,  $V_{DS}$ =0.5 V. Only the region Fig. 3.12. Conduction band along the horizontal cut,YY', shown in Fig. 3.10, at different time. Fig. 3.13. (a) Conduction band along the horizontal cut YY' in the channel layer and (b) Electron density along the vertical cut XX' under different gate biases at 1.2 ns (200 ps after the

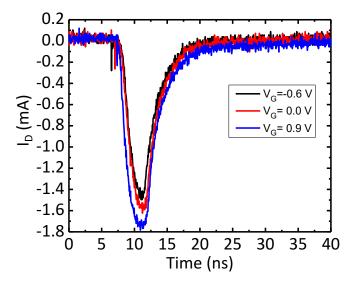

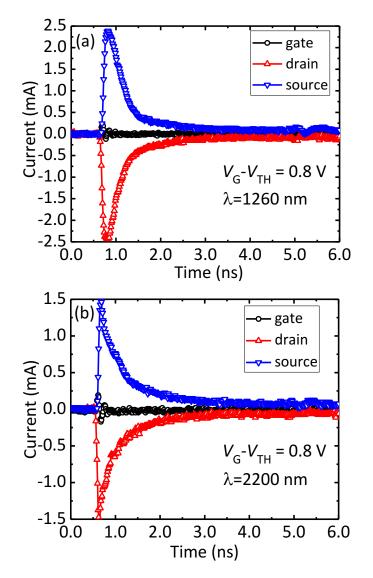

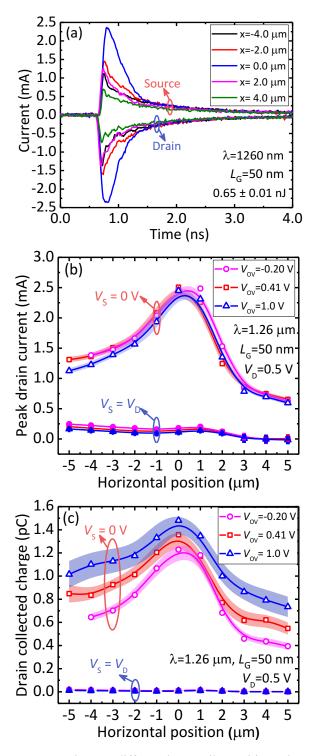

- Fig. 4.4. Typical transients captured by (a) Tektronix TDS6124C oscilloscope and (b) Teledyne Lecroy LabMaster 10-36Zi-A oscilloscope. The strike point is at the center of the device, on top of the gate. The laser wavelength used is 1260 nm. Peak currents differ as a result of different laser energies. V<sub>D</sub>=0.5 V.

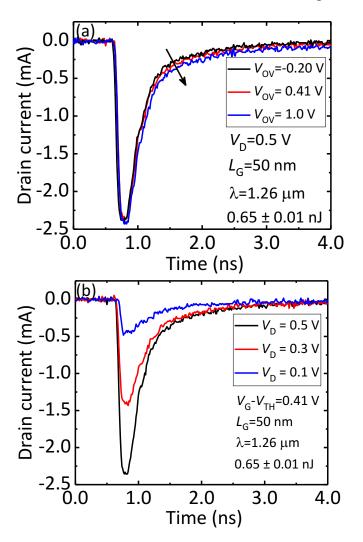

- Fig. 4.6. Drain current transients at different (a) gate bias, and (b) drain bias. The laser strike is at the center of the gate. W<sub>FIN</sub>=20 nm.

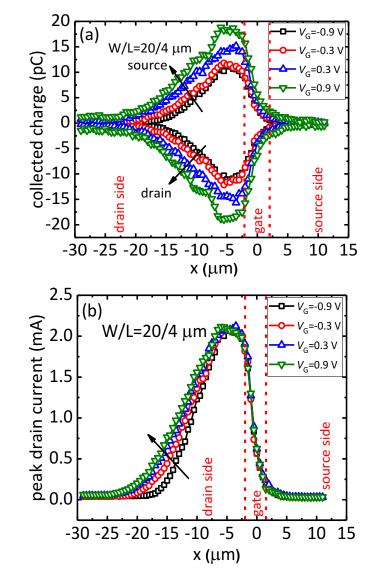

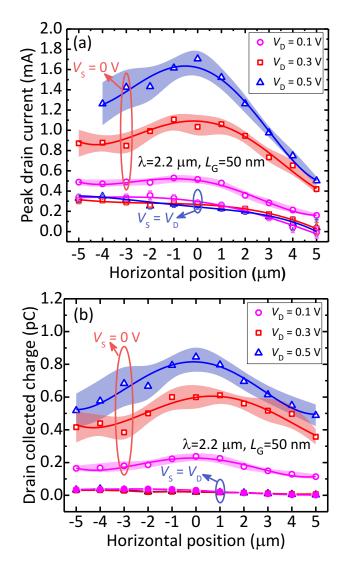

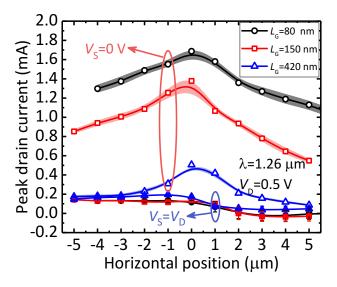

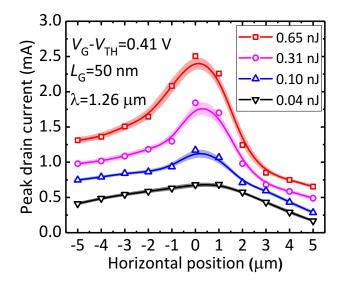

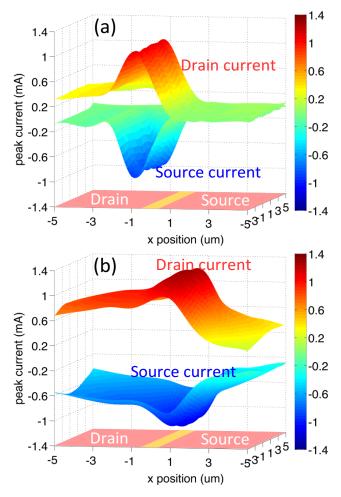

- Fig. 4.7. (a) Source and drain current transients at different laser strike positions along a line scan.

(b) and (c) show the peak drain current and drain collected charge, respectively, along a line scan at different gate biases. Here the center of the gate is taken as x=0 μm. The negative x coordinate represents the drain side and the positive x coordinate represents the source side. The laser wavelength λ=1260 nm. The shadow in (b) and (c) represents

the standard deviation among the 50 transients recorded at each position.  $W_{FIN}=20$  nm.

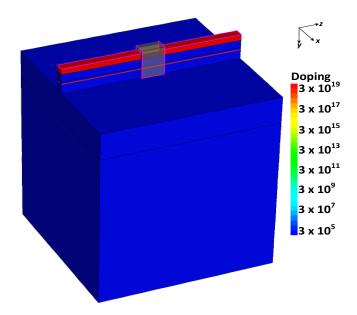

- Fig. 4.12. 3D TCAD model of InGaAs double-gate FinFET device. L<sub>G</sub>=50 nm, W<sub>FIN</sub>=20 nm... 72

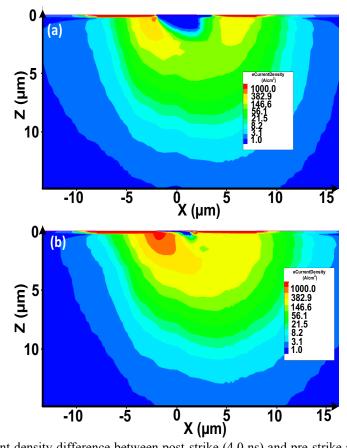

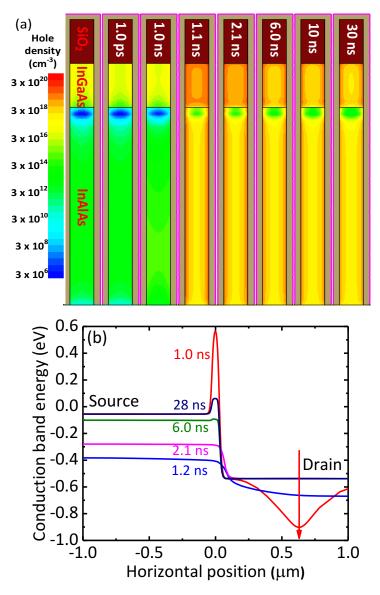

- Fig. 4.14. (a) Hole density inside the fin structure at different times. Shown is a cut plane of the device at z=0 μm, the center of the gate. There are three layers in the fin structure, the top SiO<sub>2</sub>, the middle InGaAs channel and the bottom InAlAs buffer. (b) Conduction band along a horizontal cut line, XX' shown in Fig. 4.1 (a), from source to drain. V<sub>G</sub>=-0.6 V, V<sub>D</sub>=0.5 V, V<sub>S</sub>=0 V. The red arrow indicates the location of charge injection. 74

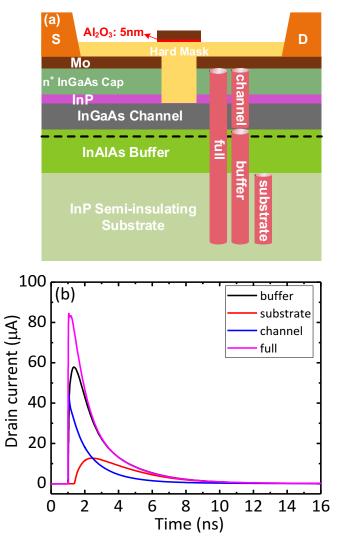

- Fig. 4.15. (a) Different charge injection volumes in the simulation. (b) Drain current transients as a function of time for these areas. Here 'full' represents charge injection from the top surface of the device and extends 8 μm, 'channel' represents charge injection in the channel layer only, 'buffer' represents charge injection starting from the buffer layer and extending 7.9 μm, and 'substrate' represents charge injection starting from the substrate. The charge injection profiles in the other three conditions are just segments

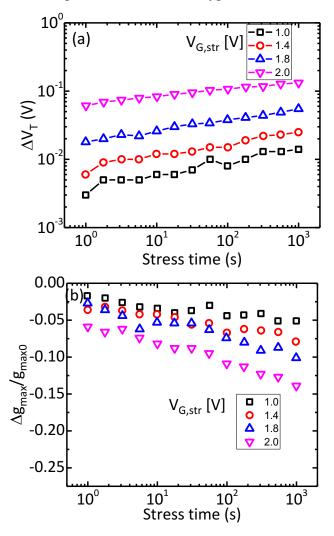

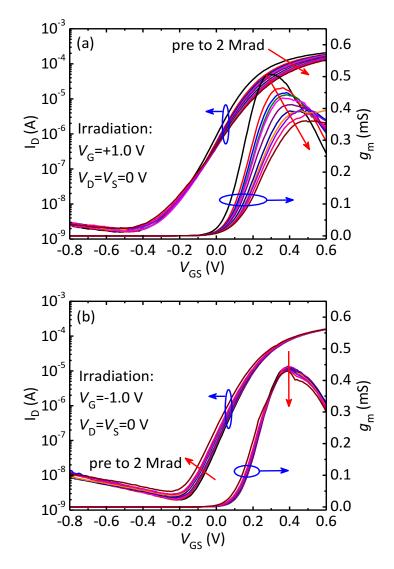

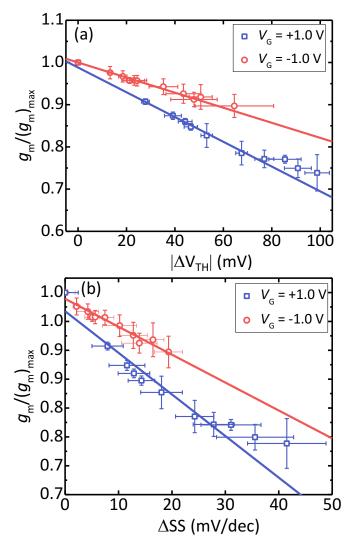

- Fig. 5.4. Subthreshold swing (left) and normalized peak transconductance (right) as a function of irradiation dose and annealing time for (a)  $V_{GS} = +1.0$  V and (b)  $V_{GS} = -1.0$  V. The normalization is based on the pre-irradiation peak transconductance. The error bars represent standard deviations among different devices tested. Measurements are made with  $V_{DS} = 50$  mV. All the tested devices have dimensions of W/L = 10  $\mu$ m/2  $\mu$ m.... 82

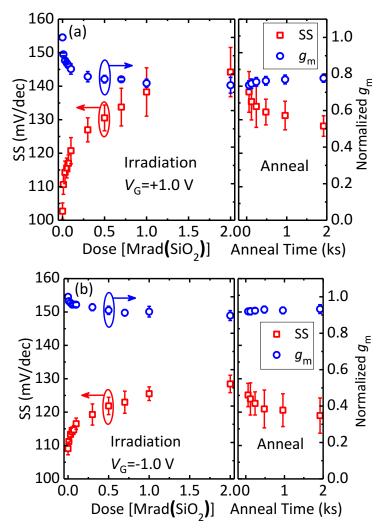

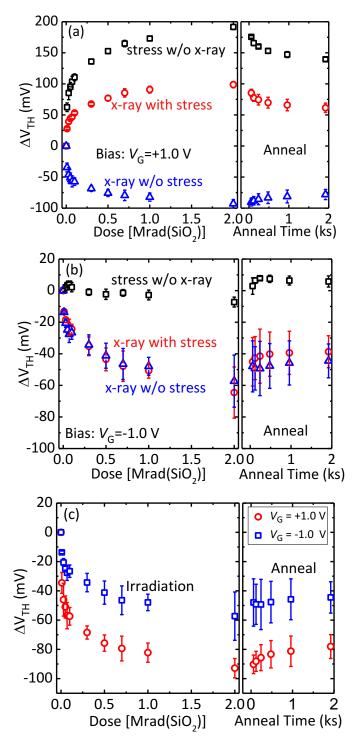

- Fig. 5.6. Threshold voltage as a function of irradiation dose and annealing time for irradiation, bias only, and bias-stress-adjusted irradiation conditions for (a)  $V_{GS} = +1.0$  V and (b)  $V_{GS} = -1.0$  V during irradiation; (c) threshold voltage shift as a function of dose and annealing time for bias-stress-adjusted irradiation at two bias conditions. The error bars represent the standard deviations among different devices tested. Measurements are

made with  $V_{DS} = 50$  mV. All the tested devices have dimensions of W/L = 10  $\mu$ m/2  $\mu$ m.

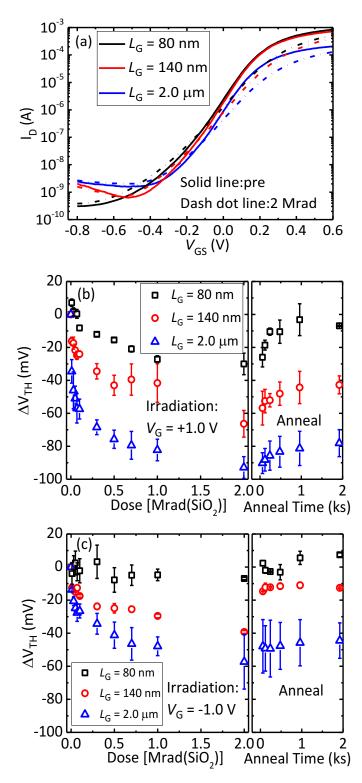

- Fig. 5.9. (a) I<sub>D</sub> versus V<sub>GS</sub> before and after 2 Mrad(SiO<sub>2</sub>) irradiation for devices with different gate lengths. During irradiation, V<sub>GS</sub> = +1.0 V. The bias-stress-adjusted TID-induced threshold voltage shift is shown as a function of dose and anneal time for different gate lengths for bias at (b) V<sub>GS</sub> = +1.0 V, and (c) V<sub>GS</sub> = -1.0 V. The error bars represent standard deviations among different devices tested. Measurements are made with V<sub>DS</sub> = 50 mV.

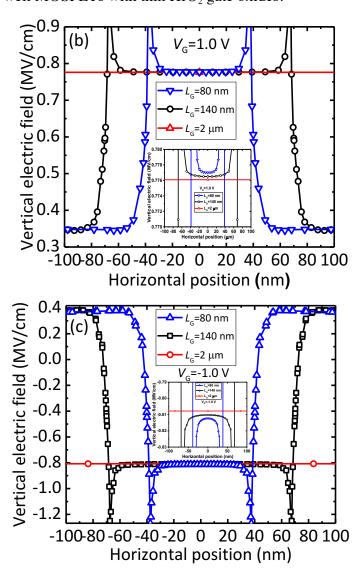

Fig. 5.10. (a) and (b) show the vertical electric field in the gate oxide along a horizontal cut line

# TABLE OF CONTENTS

| ACKNO    | WLEDGEMENTSii                                                 |

|----------|---------------------------------------------------------------|

| LIST OF  | F TABLESiv                                                    |

| LIST OF  | F FIGURES v                                                   |

| Chapter  |                                                               |

| 1. Intro | oduction1                                                     |

| 1.1.     | III-V MOSFET                                                  |

| 1.2.     | Radiation Effects Overview                                    |

| 1.2      | 1. Total Ionizing Dose Effects Introduction                   |

| 1.2      |                                                               |

| 1.3.     | Radiation Effects in III-V Materials and Devices10            |

| 1.3      | 1. Total Ionizing Dose Effects in III-V FETs: An Overview     |

| 1.3      | 2. Single Event Effects in III-V FETs: An Overview            |

| 1.4.     | Overview of Dissertation                                      |

| 2. Cha   | rge Collection Mechanisms in GaAs MOSFETs21                   |

| 2.1.     | Introduction                                                  |

| 2.2.     | Device Description                                            |

| 2.3.     | Experimental and Simulation Details                           |

| 2.4.     | Results and Discussion                                        |

| 2.4      | 1. Broadbeam Heavy Ion Results                                |

| 2.4      | 2. TPA Laser Results                                          |

| 2.5.     | Conclusion                                                    |

| 3. Sing  | gle Event Transient Response of InGaAs Quantum-Well MOSFETs41 |

| 3.1.     | Introduction                                                  |

| 3.2.     | Device Description                                            |

| 3.3.     | Experimental Details                                          |

| 3.4.     | Results and Discussions                                       |

| 3.4      | 1. Heavy Ion Results                                          |

| 3.4      | .2.    | TPA Laser Results                                                       | 50  |

|----------|--------|-------------------------------------------------------------------------|-----|

| 3.4      | .3.    | 2D TCAD Simulation Results                                              | 51  |

| 3.5.     | Con    | clusion                                                                 | 56  |

| 1 I.a.d  |        | dia Change Collection Machanisms in InCoAs EinEETs Using Useh Speed     |     |

|          |        | nding Charge Collection Mechanisms in InGaAs FinFETs Using High-Speed   |     |

| Pulsed-I |        | Transient Testing with Tunable Wavelength                               |     |

| 4.1.     | Intro  | oduction                                                                | 57  |

| 4.2.     | Dev    | ice Description                                                         | 58  |

| 4.3.     | Exp    | erimental Setup                                                         | 60  |

| 4.4.     | Res    | ults and Discussions                                                    | 62  |

| 4.4      | .1.    | System Validation                                                       | 62  |

| 4.4      | .2.    | Charge collection in InGaAs FinFETs                                     | 64  |

| 4.4      | .3.    | TCAD Simulations                                                        | 72  |

| 4.5.     | Con    | clusion                                                                 | 76  |

| 5. Gate  | - Rias | and Geometry Dependence of Total-Ionizing-Dose Effects in InGaAs Quantu | ım  |

|          |        | Ts                                                                      |     |

| 5.1.     |        | oduction                                                                |     |

| 5.2.     |        |                                                                         |     |

|          |        | ice Description and Experimental Setup                                  |     |

| 5.3.     |        | ults and Discussions                                                    |     |

| 5.4.     | Con    | clusion                                                                 | 89  |

| 6. Con   | clusic | ons and Future Work                                                     | 91  |

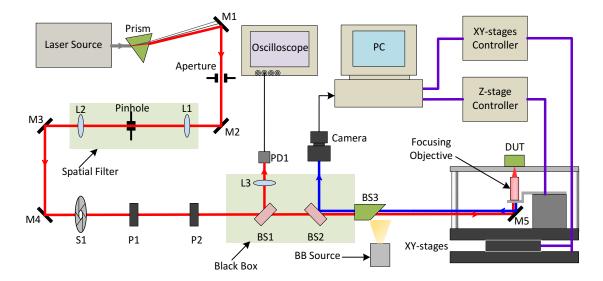

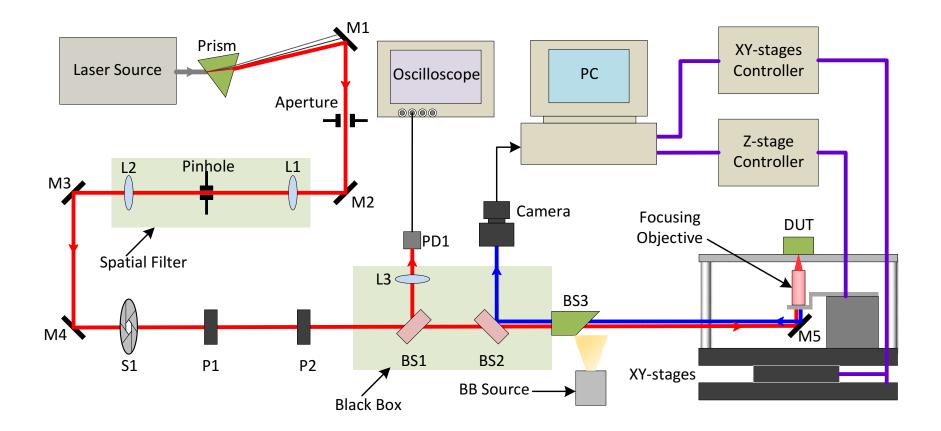

| Appendi  | xA.    | Tunable Wavelength Laser System                                         | 94  |

| Intr     | oduct  | ion                                                                     | 94  |

| Sys      | tem (  | Components                                                              | 94  |

| -        |        | -                                                                       |     |

|          |        | TCAD Scripts                                                            |     |

|          |        | ion                                                                     |     |

|          |        | FinFET SRAM mixed-circuit simulation                                    |     |

| InC      | iaAs I | FinFET                                                                  | 102 |

| REFERI   | ENCE   | S                                                                       | 110 |

## **Chapter 1. Introduction**

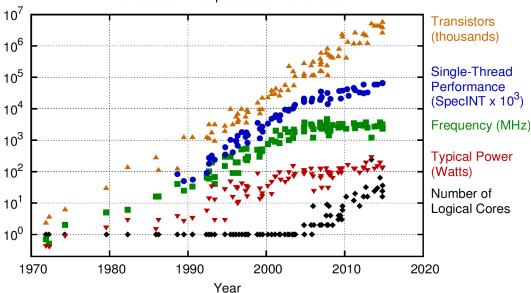

Ever since the invention of the transistor, the semiconductor industry has seen tremendous progress by following Moore's law, which states that the number of transistors per integrated circuit doubles approximately every 24 months. For example, Fig. 1.1 shows that the transistor count in microprocessors has been increasing for over 40 years [1]. The key to sustain Moore's law is the miniaturization of single transistors. However, conventional scaling has hit a power wall, so that it is now limited by the power consumption [2]. Therefore, low power and high performance logic devices are currently actively investigated to maintain the scaling trends.

40 Years of Microprocessor Trend Data

Fig. 1.1. 40 years of microprocessor trend data [1].

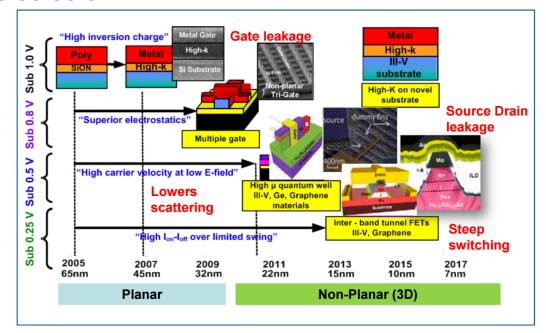

However, it is becoming more and more challenging to continue transistor scaling. Technology innovations are necessary to extend Moore's law. Several transformative changes have been implemented and explored to maintain the scaling, as shown in Fig. 1.2 [3]. For example, strain engineering was first introduced in the 90 nm node to increase both electron and hole mobility [4], [5]. Metal-gate/high- $\kappa$  gate stacks were introduced in the 45 nm node to reduce the gate leakage and eliminate poly-silicon depletion [6], [7]. The most dramatic change was the transition from planar transistor to FinFET technology in the 22 nm node for combating short channel effects [8], [9], [10]. However, as scaling continues, current techniques are reaching their limits and new technologies are needed. Some of the leading candidates for sub-10 nm nodes are alternative

channel materials which have superior transport properties. Currently III-V/Ge materials are promising NMOS/PMOS channel materials due to their high carrier mobility and injection velocity [11], [12], [13], [14].

Fig. 1.2. Trend in state-of-the-art high performance (HP) CMOS transistor innovation. Transformative changes in materials (high-k dielectric, Ge, III-V channel) and the transistor architecture (3D, Tunnel FET) being implemented and explored to maintain historical rate of performance, density and power scaling [3].

## 1.1. III-V MOSFET

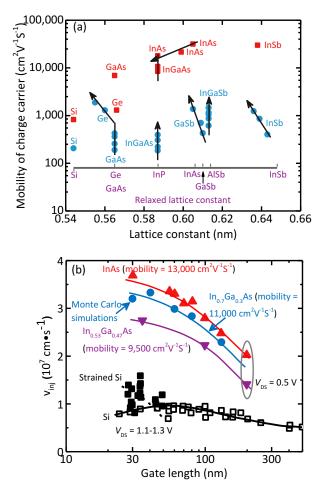

The low field carrier mobilities of typical semiconductor materials are shown in Fig. 1.3(a) [15]. The electron mobility in III-V materials, especially InGaAs, is about 10x higher than Si. This is due to the low effective mass of electrons in InGaAs compared with Si. Similarly, the hole mobility in Ge is significantly higher than Si. As a result, heterogeneous integration of InGaAs and Ge as channel materials on silicon substrates is under consideration for the next generation logic devices [11], [12], [13].

For sub-10 nm technology, transistors are operating in the quasi-ballistic region, where the electrons traveling from source to drain experience no or few scattering events [16]. In this circumstance, low field mobility is no longer a physically meaningful parameter. Instead, the injection velocity  $v_{inj}$  at the 'virtual source', where the conduction band barrier is the highest, is the right parameter to characterize the transport properties [17]. The transistor ballistic current can be expressed as [18]:

$$I_{D} = Q_{i} v_{inj} \frac{1 - \mathcal{F}_{1/2}(\eta_{F2}) / \mathcal{F}_{1/2}(\eta_{F1})}{1 + \mathcal{F}_{0}(\eta_{F2}) / \mathcal{F}_{0}(\eta_{F1})}$$

(1.1)

where  $Q_i$  is the charge density at the top of conduction band and  $\mathcal{F}_i$  is the Fermi-Dirac integral of order *i*. The other parameters are defined as:

$$v_{inj} = \sqrt{\frac{2k_BT}{\pi m^*}} \frac{\mathcal{F}_{1/2}(\eta_{F1})}{\mathcal{F}_0(\eta_{F1})}$$

$$\eta_{F1} = \frac{E_{FS} - \varepsilon_S}{k_BT}$$

$$\eta_{F2} = \frac{E_{FD} - \varepsilon_D}{k_BT}$$

$$Q_i = C_g \left( V_G - V_T \right)$$

(1.2)

This model shows that the smaller the effective mass, the higher the injection velocity. Fig. 1.3(b) shows the injection velocity of InGaAs of different composition compared with silicon obtained from experiments and simulations. The injection velocity in InGaAs is at least 2x higher than that in strained Si. Therefore, it can be concluded that InGaAs has better transport properties than Si for ballistic transport.

There have been concerns over the low effective mass of InGaAs, which results in a low density of states (DOS), known as the 'density of states bottleneck' [19]. This is because the DOS is given by:

$$2D: DOS = \frac{m^*}{\pi\hbar^2}$$

$$3D: DOS = \frac{1}{2\pi^2} \left(\frac{2m^*}{\hbar^2}\right)^{3/2} \sqrt{E - E_C}$$

(1.3)

Smaller effective mass, such as that in InGaAs, will lead to smaller density of states. For extremely scaled device with thin gate dielectrics, the gate capacitance is dominated by the quantum capacitance, not the insulator capacitance [20], [21]. The quantum capacitance includes two components, one due to the finite DOS  $C_{DOS}$ , and the other one due to the finite distance between the charge centroid and the interface  $C_{cent}$ . Both terms are proportional to the effective mass [20], [21]. The low gate capacitance corresponds to low carrier densities at a certain gate voltage. Therefore, the performance of III-V MOSFETs needs to be studied carefully, considering both mobility and DOS together.

Fig. 1.3 (a) Electron and hole mobility of group III-V compound semiconductors. Electron mobility is marked red and hole mobility is in blue. The arrow indicates the increase of biaxial compressive strain. (b) Electron injection velocity in III-V materials [15].

However, studies have shown that the strong non-parabolicity of the band structure of InGaAs boosts the carrier concentration effectively compared with the simple parabolic approximation [19]. Moreover, techniques, such as use of (111) surface orientation to take advantage of large outof-plane quantization mass and low in-plane transport mass of the L valley, have been proposed to overcome the DOS bottleneck [22], [23]. Table 1.1 shows the effective mass at different energy valleys for some typical semiconductor materials [24]. For all the III-V materials listed, the L valley is close to the  $\Gamma$  valley and the transverse effective mass is also very small, close to the  $\Gamma$  valley effective mass, suggesting superior transport properties. In addition, the longitudinal effective mass of the L valley is large. By proper design of the quantum well channel, the  $\Gamma$  valley and L valley will be almost at the same energy level so that both valleys participate in the carrier transport, which can boost the density of states and increase drive current. Taking all these effects into consideration, III-V MOSFETs still outperform Si, as shown in various simulation studies [25], [26].

|                                          | Γ valley  |           | X valle   | ey                 |           | L valle   | y                  |

|------------------------------------------|-----------|-----------|-----------|--------------------|-----------|-----------|--------------------|

| material                                 | $m^*/m_o$ | $m_l/m_o$ | $m_t/m_o$ | $E_X$ - $E_\Gamma$ | $m_l/m_o$ | $m_t/m_o$ | $E_L$ - $E_\Gamma$ |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 0.045     | 1.29      | 0.19      | 0.83 eV            | 1.23      | 0.062     | 0.47 eV            |

| InAs                                     | 0.026     | 1.13      | 0.16      | 0.87 eV            | 0.65      | 0.05      | 0.57 eV            |

| GaAs                                     | 0.067     | 1.30      | 0.22      | 0.47 eV            | 1.90      | 0.075     | 0.28 eV            |

| Si                                       | -         | 0.92      | 0.19      | negative           | -         | -         | -                  |

Table 1.1. Electron effective mass and energy separations for different valleys of different materials [24].

The initial attempt to fabricate III-V MOSFETs started in 1965 [27]. It was quickly realized that a low-defect thermo-dynamically stable gate dielectric was the key to III-V MOSFETs. Unlike the nearly perfect interface between Si and SiO<sub>2</sub>, there are no ideal native oxides for III-V materials. The oxides are not stable, generally leaky and have low dielectric breakdown strength [28]. These highly defective states will pin the Fermi-level, which prevents the formation of an inversion layer. Since then, there are decades of research on suitable dielectrics for III-V MOSFETs. But limited success has been achieved until in-situ molecular beam epitaxy (MBE) deposition of Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>) as a gate dielectric [29] and ex-situ atomic layer deposition (ALD) of high  $\kappa$  dielectric on III-V materials were discovered [30]. Since the ALD process was used to deposit high  $\kappa$  dielectric materials on Si in commercial technology and record-high performance III-V MOSFETs were reported [31], [32], the ALD process is now most widely used.

In parallel with the surface channel III-V MOSFET development, quantum-well III-V MOSFETs, which use an InGaAs or InAs channel sandwiched between barriers, were also heavily investigated [14], [33]-[39]. Because of the good interface between the channel and barrier, the interface-related scattering is eliminated, which boosts the carrier mobility. With this structure, record high performance III-V MOSFETs were reported [40].

To control the short channel effects in the sub-10 nm node, multi-gate architecture is necessary to enhance the gate control over the channel [12], [41]. In accordance with this, multi-gate III-V MOSFETs are developed. For example, InGaAs FinFETs have been demonstrated in [42], [43], [44]. In addition, InGaAs gate-all-around nanowire transistors have also been demonstrated through both top-down and bottom-up fabrication methods [45]-[49]. To fully understand the

radiation effects in III-V MOSFETs, different device architectures are investigated, including surface channel, quantum-well channel, and FinFET.

# **1.2. Radiation Effects Overview**

For space applications, devices or ICs have to withstand radiation exposure. The radiation comes from high energy particles, including protons, electrons, solar heavy ions, and galactic cosmic rays [50]. Radiation can have different effects on devices or ICs. In this thesis, two kinds of effects, total ionizing dose (TID) effects and single event effects (SEE), are studied.

## **1.2.1.** Total Ionizing Dose Effects Introduction

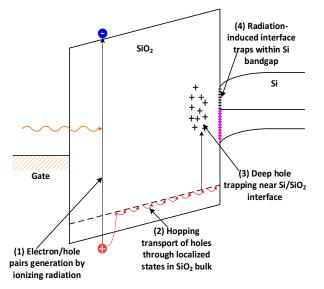

Total ionizing dose (TID) effects refer to parametric degradation and possible functional failures in electronic devices caused by the cumulative effects of ionizing radiation [51]. Usually insulators are the most sensitive parts in MOS systems. Fig. 1.4 shows the physical processes that happen in MOS systems following ionizing radiation [51]. When radiation passes through an oxide, electron/hole pairs are created by the deposited energy. Electrons are quickly swept out of the oxide due to high mobility, while holes surviving from initial recombination remain in the oxide. The fractional yield of holes is dependent on the electric field and the generated electron/hole pair densities [51]. The remaining holes are trapped in oxide defects or transported to the oxide/semiconductor interface through hopping. Some of the holes are trapped close to the interface. Protons are liberated during hole transport and further move to the interface and create interface traps. The oxide traps and interface traps cause reliability issues.

Fig. 1.4. Schematic diagram illustrating physical processes in MOS system after ionizing radiation [51].

The charges trapped in the gate oxide will cause threshold voltage shifts. The positive charge reduces threshold voltage while the negative charge increases threshold voltage. The relationship is given by:

$$\Delta V_{TH} = -\frac{Q_i}{C_{ox}} - \frac{1}{\varepsilon_{ox}} \int_0^{x_o} x \cdot \rho_{ox}(x) dx$$

(1.4)

where  $Q_i$  is the interface charge,  $\rho_{ox}$  is the volumetric oxide charge density,  $x_o$  is the oxide thickness and  $\varepsilon_{ox}$  is the oxide dielectric constant.

For relatively thick oxides, the threshold-voltage shift caused by trapped holes in the oxide is described by:

$$\Delta V_{ot} \propto x_o^2 \tag{1.5}$$

This square law dependence is due to the capacitance of the gate oxide on the one hand, as illustrated in (1.4), and the number of generated electron/hole pairs [52]. This suggests that TID effects on gate oxides are becoming less significant for advanced technology nodes with the CMOS scaling. The gate oxide thickness is now approximately 1.0 nm, which is too thin to cause noticeable TID effects. Instead, the thick oxides in the device structure, for example the shallow trench isolation (STI) and the buried oxide in the silicon-on-insulator (SOI), cause reliability problems, for example leakage current increases [52].

# 1.2.2. Single Event Effects Introduction

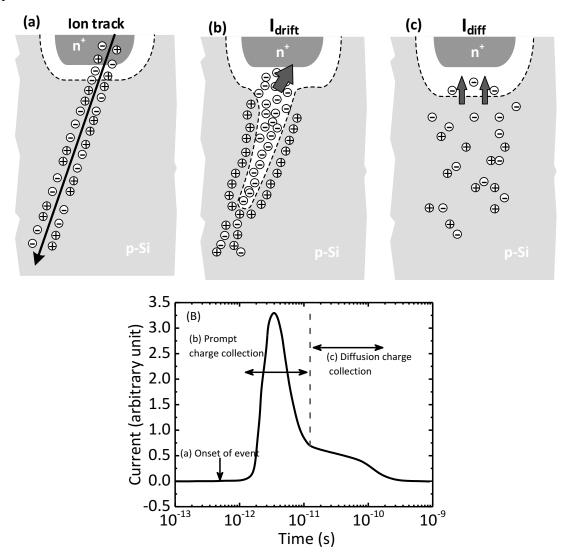

SEE refers to events caused by high energy particles (protons, neutrons, electrons, heavy ions, etc.) hitting sensitive regions of a device or circuit [53]. When a particle hits a device, it may cause nondestructive effects such as single event upset (SEU) in a memory cell where the memory cell flips [54] or potentially destructive effects such as single event latchup (SEL) where parasitic pnpn junctions are triggered and form a low resistance path between the power supply and ground [55]. The physical origin of all these phenomena comes from the charge deposition by high energy particles through either direct ionization or indirect ionization, and then charge collection through carrier transport in the device [53]. Fig. 1.5 (A) shows the charge deposition by the ion and subsequent charge collection by drift and diffusion [54]. For example, for a reverse-biased pn junction, which is usually the most sensitive region in a device due to the high electric field, particle-induced electron/hole pairs in the depletion region are separated and collected efficiently by the terminal, known as drift collection.

For those carriers generated close to the depletion region, they can diffuse back to the depletion region, where they are collected by the drift process. This process is known as the diffusion process since the carriers generated outside the high-field region diffuse to the depletion region. The charge collection processes are extensively investigated through TCAD simulations [56], [57]. A representative current pulse, shown in Fig. 1.5 (B), illustrates a prompt drift and a slow diffusion component.

Fig. 1.5. (A) Charge generation and collection processes in a reverse biased pn junction and (B) the resultant current transient caused by the passage of a high-energy ion [54].

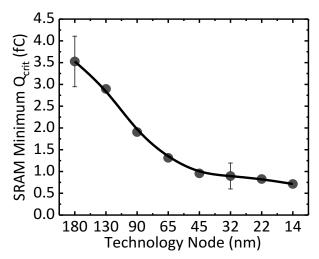

Different from the impact of scaling on TID effects, devices/ICs are more sensitive to SEE effects due to scaling. This is because the node capacitance and supply voltage decrease, which lead to the reduction of critical charge [59], [60]. The critical charge is defined as a threshold above

which soft errors occur when the collected charge is over the threshold. The soft error rate (SER) is approximately represented as [59], [60],

$$SER \propto A_{diff} \exp\left(-\frac{Q_{crit}}{Q_{coll}}\right)$$

(1.6)

where  $A_{diff}$  is the diffusion area and on average decreases 2x every technology generation as illustrated in Moore's law,  $Q_{crit}$  is the critical charge, and  $Q_{coll}$  is the collected charge. The critical charge  $Q_{crit}$  of SRAM cell for different Intel technology nodes is shown in Fig. 1.6 [59]. It shows that the  $Q_{crit}$  decreases 30% in older technology and 15% in more advanced technologies (starting from 45 nm). The decrease of  $Q_{crit}$  leads to enhanced soft error rate when it is considered independently of other factors, such as changes in the size of the transistors.

Fig. 1.6. Neutron-induced critical charges for SRAM devices at different technology nodes. Minimum critical charge refers to the minimum value of all state nodes and state transitions [59].

The overall impact of scaling on SER depends on all three factors in Eq. (1.6). For example, with the introduction of FinFET technology, the SER of a single SRAM cell decreases significantly [59]. This is because the  $Q_{coll}$  significantly decreases due to the smaller geometrical footprint of the FinFET while the  $Q_{crit}$  remains almost the same. In addition, different circuits have different dependence on scaling. For example, SRAM/latch SER decreases with scaling while the combinational logic SER exponentially increases [61]. Since III-V MOSFETs are expected to continue the scaling, it is necessary to understand the SEE effects in these devices.

To understand the device vulnerability to SEE, and further to harden the device or IC against SEE, it is very important to understand the charge collection processes, especially for new

technologies that are very different from traditional Si technology. Usually new technologies have new charge collection mechanisms. For example, CMOS scaling makes the transistor inside a well more sensitive to SEE due to the bipolar amplification mechanism caused by slow holes staying in the well, which reduces the source to substrate barrier [58]. Similar effects are also observed in silicon on insulator (SOI) technology [62]. Thus, understanding the charge collection processes in emerging III-V MOSFETs with different structures, such as surface channel, quantum-well channel, and FinFET, is important and can provide insights for their applications in radiation environments.

# **1.3. Radiation Effects in III-V Materials and Devices**

Since the early search for suitable dielectrics on III-V materials was not successful, other types of field effect transistors that did not need an insulator were developed, such as junction gate field-effect transistors (JFETs) [63], metal-semiconductor field effect transistors (MESFETs) in 1966 [64], and high electron mobility transistor (HEMTs) in 1980 [65]. Applications of these devices included early digital IC and RF/Microwave ICs for communication [66]. Radiation effects on these devices have been investigated thoroughly from the 1970s to the 1990s because of the strong motivation of applying them in space due to their high speed and high performance [67]. Since the emergence of III-V MOSFETs, several radiation studies have also been performed [68], [69], [70], [71]. In this section, the radiation effects in III-V materials and devices are reviewed.

# 1.3.1. Total Ionizing Dose Effects in III-V FETs: An Overview

In early III-V FETs, including JFETs, MESFETs, and HEMTs, there is no gate dielectric in the device. This makes these devices hard against TID effects. This is because the gate oxide is usually the most critical in determining TID response since it causes charge trapping when exposed to ionizing irradiation. Therefore, for III-V FETs without gate insulators, TID effects on the threshold voltage are not a concern [72].

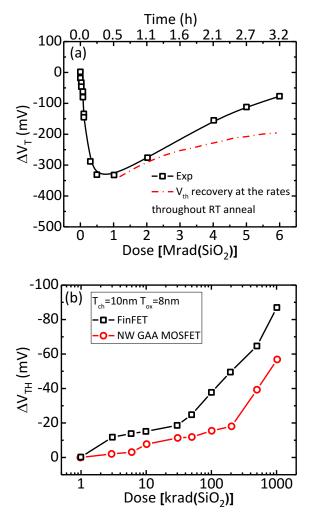

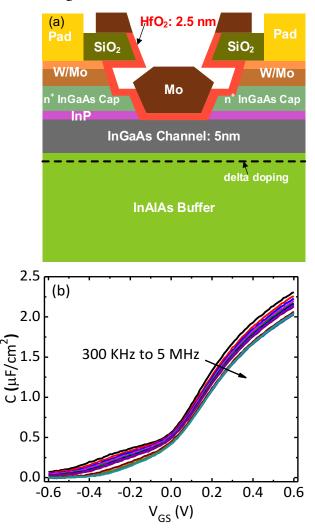

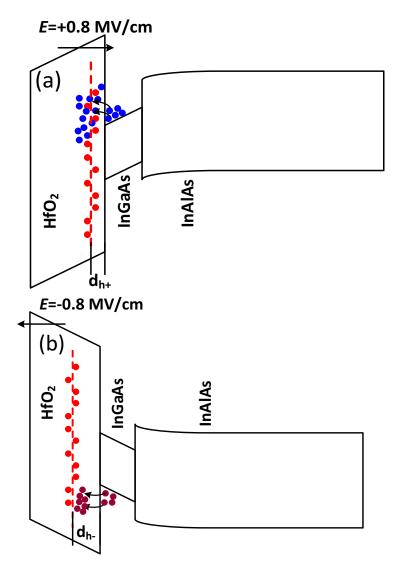

With the advent of III-V MOSFETs, TID effects have been studied in AlGaN/GaN MOS-HEMTs [68], InGaAs quantum-well MOSFETs [69], and InGaAs nanowire gate-all-around (GAA) MOSFETs [70]. Fig. 1.7 (a) and (b) show the threshold voltage shift as a function of irradiation dose for InGaAs quantum-well MOSFETs and GAA MOSFETs, respectively. The threshold voltage shifts about -0.35 V and shows interesting turn-around behavior for the quantum-well MOSFET, which has an equivalent oxide thickness (EOT) of 7.5 nm. However, for multi-gate architectures, the threshold voltage shift is much smaller, less than -0.1 V, as presented in Fig. 1.7 (b). Moreover, the GAA structure shows smaller threshold voltage shift than the FinFET device. This is because the electrons are closer to the surface in FinFETs than GAA devices, which leads to higher electric field in the oxide in FinFET [70]. The large electric field means high hole yield, and hence higher hole trapping [51]. These studies show an interesting device architecture dependence of TID effects. However, all these studies focus on thick gate oxide, around 8 nm, which is impractical for advanced technology nodes. Therefore, it is necessary to study the TID response with more relevant gate oxides.

Fig. 1.7.Threshold voltage shift as a function of irradiation dose for (a) InGaAs planar quantum-well MOSFETs [69] and (b) InGaAs FinFET and nanowire GAA MOSFETs [70].

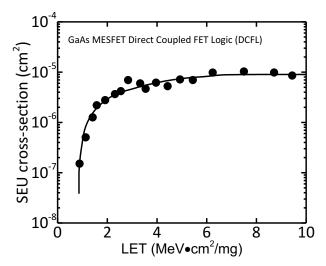

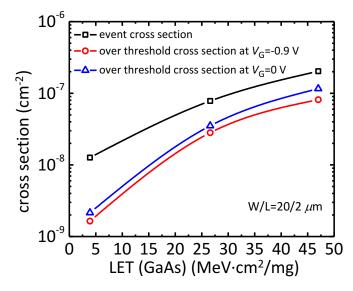

# 1.3.2. Single Event Effects in III-V FETs: An Overview

Since the early III-V FETs are found to be hard against TID effects, most of the research efforts have been directed toward understanding SEE in III-V FETs [67], [72]-[75]. It is found that III-V FETs are more sensitive to SEE compared with Si FETs, due to material property and device architecture differences. For example, Fig. 1.8 shows a typical cross section vs. LET for a GaAs MESFET-based direct coupled FET logic (DCFL) latch [76]. The threshold LET is low, less than 1 MeV•cm<sup>2</sup>/mg and the saturation cross section is much higher than the sensitive area of the latch, suggesting enhancement effects in these devices and circuits. These two factors imply that III-V FETs may be relatively sensitive to SEE. In this section, the SEE in III-V FETs are briefly overviewed and the sensitivity is explained through the charge deposition, non-insulating gate, charge enhancement mechanisms, and semi-insulating substrate, which could provide insights into the SEE in III-V MOSFETs.

Fig. 1.8. SEU cross section vs. LET for GaAs MESFET based DCFL latch circuit [76].

#### 1.3.2.1. Charge Deposition in III-V Materials

To understand the SEE vulnerability of III-V FETs, it is important to understand the charge deposition in III-V materials. The ionizing energy loss by an ion to the target material is characterized by linear energy transfer (*LET*), which is a measure of energy transfer per unit length of the material. It is defined as energy loss per unit length divided by the material density

$$LET = \frac{dE}{dx} \frac{1}{\rho}$$

(1.7)

To calculate the number of electron-hole pairs generated by an ion, another important parameter is the creation energy  $\varepsilon_I$ [77], which is the energy required to create an electron-hole pair. Then the number of electron-hole pairs generated per unit length is

$$LET\left(\frac{ehp}{\mu m}\right) = LET\left(\frac{MeV \cdot cm^2}{mg}\right) \div \varepsilon_I\left(\frac{eV}{ehp}\right) \times \rho\left(\frac{g}{cm^3}\right)$$

(1.8)

where the unit of each parameter is shown in the parentheses. So for a given material, there is a conversion factor from *LET* in units of  $MeV \bullet cm^2/mg$  to *LET* in units of  $ehp/\mu m$ . Table 1.2 lists the conversion factor,  $\varepsilon_l$ , and  $\rho$ . Also listed in column four is the ionized charge per unit length for an ion having *LET* of 1  $MeV \bullet cm^2/mg$ .

From the results, it could be concluded that the higher the creation energy and the smaller the mass density, the smaller the generated electron-hole pair density. Even though GaAs has higher creation energy than Si, the higher density of GaAs causes 70% more carriers generated compared with Si for the same LET. The situation is even worse for In<sub>0.53</sub>Ga<sub>0.47</sub>As, which has lower creation energy and higher density than GaAs. The charge generated in In<sub>0.53</sub>Ga<sub>0.47</sub>As is 3x that in Si. So for III-V FETs, such as GaAs MESFETs or InGaAs MOSFETs, more charge will be generated by an ion compared with Si FETs if the ion penetrates the same thickness of Si and III-V materials and has the same LET in the materials.

| Target<br>Semiconductor                  | €I (eV) | Density<br>(g/cm <sup>3</sup> ) | <i>fC/μm</i> for an <i>LET</i> =1<br><i>MeV</i> •cm <sup>2</sup> /mg | Divide <i>LET</i> by X for <i>pC/µm</i> deposited |

|------------------------------------------|---------|---------------------------------|----------------------------------------------------------------------|---------------------------------------------------|

| Si                                       | 3.6     | 2.32                            | 10.4                                                                 | 97                                                |

| GaAs                                     | 4.8     | 5.32                            | 17.8                                                                 | 56                                                |

| InP                                      | 4.5     | 4.81                            | 17.1                                                                 | 58                                                |

| InAs                                     | 1.8     | 5.68                            | 50.5                                                                 | 20                                                |

| In <sub>0.53</sub> Ga <sub>0.47</sub> As | 2.9     | 5.49                            | 30.3                                                                 | 33                                                |

| $In_{0.52}Al_{0.48}As$                   | 4.6     | 4.74                            | 16.5                                                                 | 61                                                |

| SiC                                      | 8.7     | 3.21                            | 5.9                                                                  | 169                                               |

| GaN                                      | 10.3    | 6.11                            | 9.5                                                                  | 105                                               |

Table 1.2. Ionized charge per unit length for an ion having a LET of 1MeV•cm<sup>2</sup>/mg [75]

#### **1.3.2.2.Non-insulating Gates**

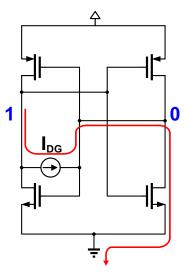

For III-V FETs that have wide application, most of them have non-insulating gates, such as the pn depletion region used in JFETs, the Schottky barrier used in MESFETs, and the barrier layer in high electron mobility transistors (HEMTs) to isolate the gate from the channel. These devices are robust against TID-induced degradation, however, the high field in the depletion region under the gate or low barrier layer will cause radiation-generated carriers to be collected in the gate, causing gate transients [78]. The gate transient-induced upset is a new upset mechanism, different from the traditional drain transient-induced upset. Fig. 1.9 shows the current path for gate to drain current transients [79]. This can discharge the stored charge on the left side and cause the upset of the SRAM cell.

Fig. 1.9. Current path for gate to drain charge collection in a SRAM cell [79].

Different from SEUs in CMOS technology, gate transient-induced SEU is a new upset mechanism and has a lower critical charge compared with the traditional upset mechanism [80]. Besides, it is found that the gate transient biases the device and causes additional drain current [73], [81]. Furthermore, it is observed that traditional hardening techniques, such as decoupling feedback resistors, used in CMOS technology will store the collected charges in the gate node, making the circuit more susceptible to single events [67], [80]. Therefore, the non-insulating gate represents a tradeoff between TID and SEE effects.

# 1.3.2.3. Charge Enhancement

Another reason why III-V FETs are vulnerable to SEE is charge enhancement, which means that the charge collected at a node, usually the drain node, is higher than that deposited by an ion

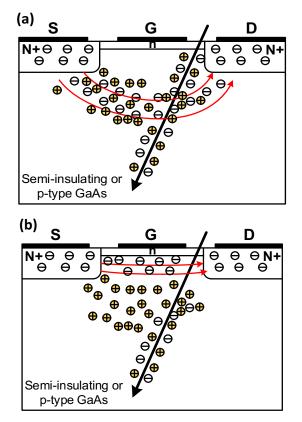

[82], [83]. Charge enhancement has been observed in all different kinds of III-V FETs when exposed to ions, lasers, and e-beams, such as GaAs MESFETs [82], [83], AlGaAs/GaAs HEMTs [84], InAs HEMTs [86], InGaAs HEMTs [86], etc. The main mechanisms are illustrated in Fig. 1.10 for GaAs MESFETs [73]. The enhancement mechanisms are very similar in other types of III-V FETs.

During an ion strike, a high density of electron hole pairs is generated along the ion track. Due to highly asymmetric carrier motilities in III-V materials (electron mobility is at least 10x hole mobility), electrons are quickly collected, while the holes remain in the device, perturbing the local potential. Fig. 1.10(a) shows the parasitic bipolar mechanism. The holes in the substrate near the source reduce the potential barrier from source to substrate, causing electron injection from source to substrate, which are further collected by the drain. Fig. 1.10(b) shows the channel modulation, or backgating mechanism. The holes in the substrate act like a floating back gate and modulate the channel conductivity, causing current flow between source and drain.

Fig. 1.10 Schematic diagram illustrating (a) the bipolar gain and (b) channel-modulation charge enhancement mechanisms that contribute to the charge collection processes of GaAs FETs [73].

The charge enhancement mechanisms contribute most of the charge collected and are the main

reason why III-V FETs are relatively vulnerable to SEE. Charge enhancement factors are typically less than 5 [83]-[89], but factors up to 60 also have been reported [74]. Therefore, the collected excess charge makes III-V FET SEU performance a serious concern for applications in radiation environments.

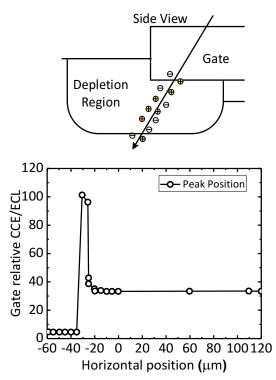

# 1.3.2.4. Semi-insulating Substrate

High resistivity semi-insulating substrates are widely used in III-V FET technology because they are ideal for isolation between transistors and also eliminate additional isolation structures. These substrates are usually made through a compensation mechanism, where the high density deep donor native defect, EL2, related to the As antisite, compensates shallow acceptors [90]. The depletion region in the semi-insulating substrate will be much larger than that in a p-type substrate. Therefore, the sensitive volume of III-V FETs on a semi-insulating substrate is very large. One related effect is the gate-edge effect [91]. At the gate edge, the gate is directly in contact with the semi-insulating substrate, creating a large depletion region underneath the gate, as shown in Fig. 1.11. The charge collection efficiency has a peak around the gate edge, about 3X of the active region of the device.

Fig. 1.11. Schematic of an ion hitting the gate edge of a GaAs MESFET device and the charge collection efficiency/effective collection length along the transistor width direction [91]. The efficiency is normalized to the maximum efficiency.

The other phenomenon related to semi-insulating substrates are the long-term transients after irradiation [92]-[96]. Recovery time on the order of 1s is observed in all kinds of devices after irradiation. It is ascribed to charge trapping in deep traps in the substrate and its subsequent thermal release. Negatively-charged traps deplete the channel and decrease the channel current, while positively-charged traps increase the channel current. Further studies show that a buried p-layer under the active region could effectively shield the channel from the charges in the substrate, and reduce the long-term transients significantly [95].

## **1.3.2.5.** Transistor Hardening Techniques

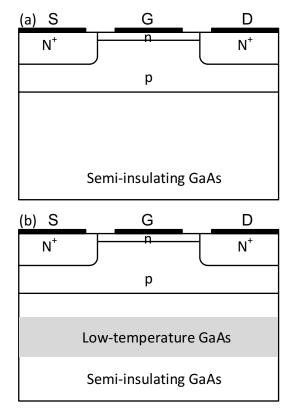

Several transistor-level hardening techniques have been proposed against SEE and they have achieved various degrees of success. The idea behind hardening is to reduce the gain enhancement mechanisms. For example, a buried p layer under the active region, as shown in Fig. 1.12 (a), increases the source to substrate barrier and could reduce the charge collection [97]. It does not eliminate the charge enhancement completely, however.

Fig. 1.12.Proposed hardening techniques. (a) Buried p layer under the active region and (b) low-temperature GaAs buffer layer.

Another effective hardening method is to reduce the hole lifetime in the substrate so that

generated holes quickly recombine before they can induce source to drain current flow [98]-[100]. A low temperature (LT) GaAs buffer layer inserted between the substrate and the active layer, as shown in Fig. 1.12 (b), could effectively reduce carrier lifetime, even down to 150 fs [73]. The LT GaAs buffer layer is grown at around 200 °C to 350 °C in an As-rich environment via molecular beam epitaxy (MBE). It contains high densities of As antisites and Ga vacancies, which increase the electron/hole trapping and recombination significantly. The generated holes are quickly recombined, so the charge enhancement is largely eliminated. Fig. 1.13 (a) and (b) show the comparison between HFETs with and without an LT buffer layer in terms of charge collection transients and collected charge, respectively, when exposed to  $\alpha$  particles [100]. It is clear that the LT buffer layer effectively reduces the transients and collected charge.

Fig. 1.13 (a) Charge collection transients and (b) collected charge measured for n-channel HFET devices with and without LT GaAs buffer layer exposed to 3 MeV  $\alpha$  particle irradiation [100].

The aforementioned factors which lead to sensitivity of III-V FETs to SEE may or may not apply for III-V MOSFETs, depending on the device materials and architectures. The charge

deposition and charge enhancement are likely to be effective in III-V MOSFETs, since the III-V materials are present in the device. However, the effects related to non-insulating gates will disappear due to the gate insulator in III-V MOSFETs. The issues with semi-insulating substrates are complicated. For the early demonstration of III-V MOSFETs, semi-insulating GaAs or InP substrates are used. The aforementioned issues will likely be present in these substrates. However, III-V MOSFETs will eventually be integrated on Si substrates [15], [101], [102], [103]. Whether substrate-related issues exist needs further investigation. In this dissertation, these effects are discussed in III-V MOSFETs.

# **1.4. Overview of Dissertation**

This Ph.D. dissertation focuses on the characterization and understanding of radiation effects in emerging III-V MOSFETs with different architectures, such as surface channel, quantum-well channel, and FinFET. This dissertation is organized as follows:

- Chapter 1 introduces the background and motivation of this work. The history and advantages of III-V nMOSFETs are discussed. Moreover, the radiation effects in III-V FETs are overviewed.

- Chapter 2 describes the transient characterization and charge collection mechanisms in GaAs surface channel MOSFETs. Similar experiments are performed as those in Chapter 2. Comparisons of charge collection mechanisms are made between surface channel and quantum-well channel devices.

- Chapter 3 describes the single event transients in InGaAs quantum-well MOSFETs induced by heavy ion and two-photon-absorption (TPA) laser irradiation. Technology computer aided design (TCAD) simulations are applied to understand the charge collection mechanisms.

- 4. Chapter 4 studies the charge collection mechanisms in InGaAs FinFET devices through tunable wavelength laser irradiation and TCAD simulation. The new laser setup allows charge injection into channel layer and new insights can be obtained.

- 5. Chapter 5 investigates the gate bias and geometry dependence of TID effect in InGaAs quantum-well MOSFETs. Combined electrical stress and X-ray experiments are designed to understand the TID effects in these devices.

- 6. The last chapter is the conclusion of the dissertation and future work is described that is interesting and worth further investigation.

The appendix includes the tunable wavelength laser setup and several TCAD scripts that I developed during my Ph.D.

#### Chapter 2. Charge Collection Mechanisms in GaAs MOSFETs

# 2.1. Introduction

Charge collection mechanisms are investigated in surface channel GaAs MOSFETs under broadbeam heavy ion irradiation and pulsed two-photon-absorption laser irradiation. The large barrier between the gate dielectric and GaAs eliminates gate conduction current, but there is significant gate displacement current. Charge enhancement occurs because radiation-generated holes accumulate in the substrate, which increases the local electrostatic potential. The increased potential enhances the source-to-drain current, resulting in excess collected charge. The collected charge increases significantly with gate bias, due to the long tails of the charge waveforms that occur for higher gate bias. The collected charge increases with increasing drain bias.

# 2.2. Device Description

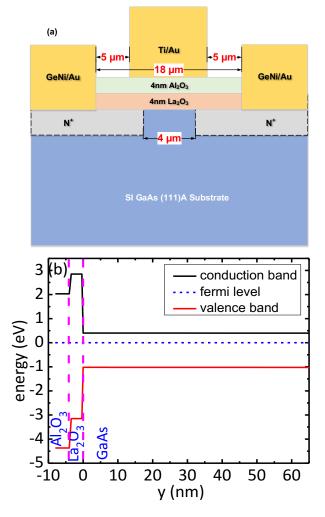

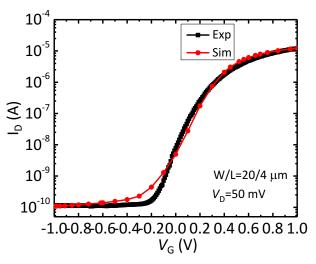

The devices under test are surface channel GaAs nMOSFETs with gate lengths of 2 and 4  $\mu$ m; the schematic cross-section is shown in Fig. 2.1(a). Also shown is the TEM picture around the gate stack. The gate dielectric is composed of 4 nm of single crystalline La<sub>2</sub>O<sub>3</sub> grown on top of a 350  $\mu$ m thick semi-insulating (SI) GaAs substrate by atomic layer epitaxy (ALE), with 4 nm of Al<sub>2</sub>O<sub>3</sub> on top of the La<sub>2</sub>O<sub>3</sub> for protection. The distance between electrodes varies with the gate length and is given for devices with  $L_G = 4 \mu$ m in Fig. 1(a). The detailed process information is found in [116]. The band diagrams along a vertical cutline through the gate oxide at zero bias applied to all terminals are shown in Fig. 2.1(b). The electron and hole quasi-Fermi levels are the same in this case because zero bias is applied to all terminals. The conduction band and valence band offsets between La<sub>2</sub>O<sub>3</sub> and GaAs are 2.4 eV and 2.1 eV, respectively [117].

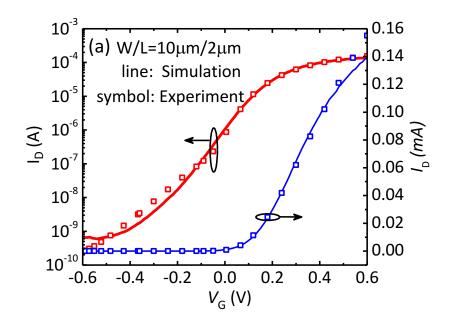

The  $I_{\rm D}$ - $V_{\rm G}$  transfer characteristic is shown in Fig. 2.2. The experimental data and simulation data agree well. To simulate the semi-insulating GaAs substrate, carbon acceptor doping and deep donor traps are included [118]. Devices with gate lengths of 2  $\mu$ m and 4  $\mu$ m and gate widths of 20  $\mu$ m and 33  $\mu$ m were tested (W/L = 20/4, 20/2, and 33/4). For both heavy ion experiments and laser experiments, at least three devices were tested. For transient capture, all the devices are mounted in custom milled high-speed packages [107]. For the laser experiments, the backsides of the DUTs were polished before mounting in high-speed packages.

Fig. 2.1. (a) Schematic cross section of the device with  $L_G = 4 \,\mu$ m; (b) band diagram along a vertical cutline through the gate oxide at  $V_G = V_D = V_S = 0$  V. The band diagram is generated from Sentaurus TCAD simulation.

Fig. 2.2. Measured and simulated  $I_{D}-V_{G}$  transfer characteristics.  $V_{D} = 50$  mV during measurement. Simulation is done with Sentaurus TCAD tools.

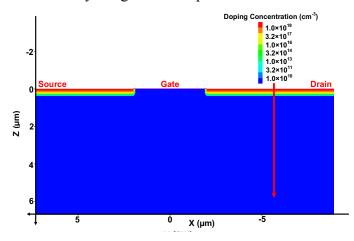

2D TCAD simulations, performed with Sentaurus TCAD tools, were used to understand the charge collection process during heavy ion strikes. The models used include drift and diffusion transport, inversion and accumulation layer mobility models, and electron velocity saturation models [119]. In addition, the SRH, radiative and Auger recombination models are used. Events produced by oxygen ions are simulated. The center of the strike is at 1.0 ns, and the strike center is at  $x = -6 \mu m$ , as shown in Fig. 2.3. The radius of the strike is 50 nm. During the simulation,  $V_D = 2.0 V$  and  $V_G$  was varied to study the gate bias dependence.

Fig. 2.3. Device model used in 2D TCAD simulation. Here the drain is in the negative x direction and source is in the positive x direction. The red arrow indicates the strike location,  $x = -6 \mu m$ . For the simulation, Sentaurus TCAD tools are used.

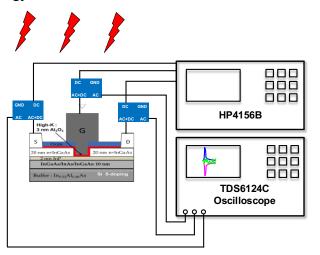

#### 2.3. Experimental and Simulation Details

Broadbeam heavy ion irradiation was performed using 14.3 *MeV* oxygen ions in Vanderbilt's Pelletron electrostatic accelerator. *LET* of Oxygen ion in GaAs is 4.3  $MeV \cdot cm^2/mg$ . The range is 7.5 µm. The experimental setup is the same as that shown in Fig. 3.3. TPA laser irradiation was performed at Vanderbilt University. All devices were irradiated from the backside by high peak power femtosecond laser pulses. A similar experimental setup is used as described in section 3.3. The laser photon energy is 0.98 eV, which is less than the GaAs band gap of 1.42 eV. As a result, the carriers are generated primarily through two-photon absorption [109].

Quantitative understanding of TPA laser experiments is challenging and remains an active area of research [120]. In this chapter, TPA laser experiments are used to map the sensitive areas of the devices by scanning the laser beam across the active areas with varying gate and drain biases. The transients were captured using a Tektronix TDS6124C oscilloscope with 12 GHz front-end bandwidth and 20 GS/s sampling rate. Each oscilloscope channel has 50  $\Omega$  input impedance, which

is used to convert the transient current to a measurable voltage. During these tests, the source was grounded and the gate bias and the drain bias were varied. A semiconductor parameter analyzer, HP 4156B, supplied the dc biases through Picosecond Model 5542 bias tees with 50 GHz bandwidth.

# 2.4. Results and Discussion

# 2.4.1. Broadbeam Heavy Ion Results

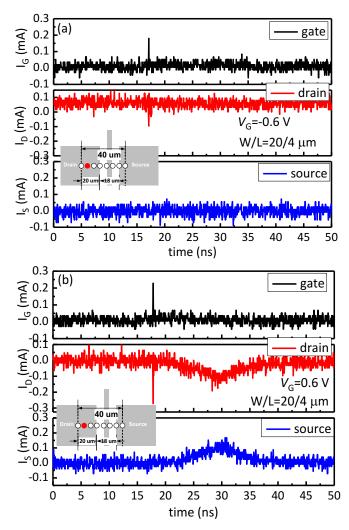

Fig. 2.4 (a) and (b) show the transients for a device with  $L_G = 4 \mu m$  for OFF and ON gate biases under oxygen ion irradiation. For all transients, the DC current is filtered out and only AC current transients are shown. Under both bias conditions, there are strong gate transients. Positive and negative gate transients correspond to charging and discharging of the gate capacitance, respectively.

Fig. 2.4. Representative transients under oxygen ion irradiation at (a) OFF,  $V_G = -0.9$  V; (b) ON bias conditions;  $V_G = 0.9$  V for a device with  $L_G = 4 \ \mu$ m. For this device,  $V_{TH} = 0.4$  V. The inset of the figure shows the zoom into the magenta box region.

After an initial positive transient, the gate current polarity changes for devices biased in the ON state (see inset in the top panel of Fig. 2.4 (b)), which is a strong indication of displacement current through the gate dielectric [121], [122]. This polarity change is not observed for devices in the OFF state (see inset of Fig. 2.4 (a)). If there is any negative gate current in the OFF state, it is obscured by the oscilloscope noise.

Fig. 2.5. Displacement gate current and electric field in La<sub>2</sub>O<sub>3</sub> as a function of time at (a)  $V_G = -0.9$  V; (b)  $V_G = 0.9$  V.

Fig. 2.5 (a) and (b) show the simulated gate displacement current and electric field in the La<sub>2</sub>O<sub>3</sub> as functions of time at  $V_G = -0.9$  V and  $V_G = 0.9$  V, respectively. The gate transient at  $V_G = -0.9$  V is displayed on a log scale to show the polarity change more clearly. When the device is biased in the OFF state, there is a large initial positive gate transient, followed by a polarity change. The electric field in the gate dielectric increases up to 20 ns, and after that it slowly decreases. The moment the electric field reaches a peak is when the gate transient changes polarity. The negative

gate current is orders of magnitude smaller than the positive peak gate current, which explains why only positive gate transients are observed in Fig. 2.5 (a). The negative portion of the gate transient is small and likely obscured by the instrument noise.