### Assessing and Detecting Malicious Hardware in Integrated Circuits

By

### Trey Reece

Dissertation Submitted to the Faculty of the Graduate School of Vanderbilt University in partial fulfillment of the requirements

for the degree of

### DOCTOR OF PHILOSOPHY

in

Electrical Engineering

December, 2014 Nashville, TN

### Approved:

William H. Robinson, Ph.D. Bharat L. Bhuva, Ph.D. Gabor Karsai, Ph.D. Thomas D. Loveless, Ph.D. Bradley A. Malin, Ph.D.

### Assessing and Detecting Malicious Hardware in Integrated Circuits

### Trey Reece

### Dissertation under the direction of Professor William H. Robinson

System security often focuses on the software, causing hardware security to be overlooked. Such oversight allows for attacks that can completely undermine the use of hardware as the root of trust. During the design of an integrated circuit, there are several opportunities for adversaries to make malicious modifications or insertions to a design. These attacks, known as hardware Trojans, can have catastrophic effects on a circuit if left undetected. This dissertation addresses Trojan impact, and proposes two low-cost detection methods for hardware Trojans inserted at different points in the production pipeline, namely: (1) Trojans hidden within third-party intellectual property (IP) licensed from a vendor, and (2) Trojans inserted during the fabrication steps taking place at external fabrication plants.

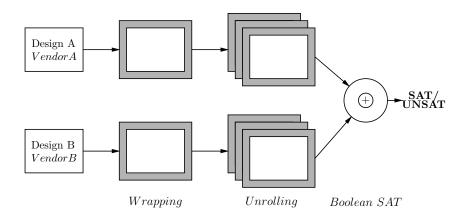

Determining whether third-party IP does only its intended function and nothing else is a major challenge. Through comparison of two similar but untrusted designs using design unrolling and Boolean satisfiability, functional differences can be identified for all possible input combinations within a window of time. This technique was tested on multiple Trojan benchmarks and demonstrated effective and accurate detectability.

Process variation poses the greatest obstacle to detecting Trojans in chips. In order to detect Trojans inserted during fabrication, a digital model is created. This model can then be trained using the fabricated chip to account for different parameters, such as process variation. The parameters of the trained model can be used to identify suspicious areas of the chip. Furthermore, this process does not require expensive test equipment, nor does it require a costly golden, trusted chip for comparison.

### Acknowledgements

First, I would like to thank my family for their continued support. It's been a long trek, and they never stopped believing in me. This dissertation would not be what it is now without their constant help. I would also like to thank my advisor, Dr. William H. Robinson, for putting up with me over the years. His steadfast support has been critical in finishing this work, and for me in finishing my degree. Further thanks go to Katy Clark, for all of her help with proofreading and editing. Special thanks is also deserved for Dr. Bharat Bhuva, who has given me a huge amount of assistance ever since I darkened his door as an undergraduate. I also thank those in the JPAC group for their support and friendship. Finally, I would like to thank the National Science Foundation for financial support in performing my research.

### TABLE OF CONTENTS

| ACK          | NOWLEDGEMENTS                                                  |    |      |  |  |  |   |   |  |  | iii             |

|--------------|----------------------------------------------------------------|----|------|--|--|--|---|---|--|--|-----------------|

| LIST         | OF FIGURES                                                     |    |      |  |  |  |   |   |  |  | vii             |

| LIST         | OF TABLES                                                      |    |      |  |  |  |   |   |  |  | ix              |

| LIST         | OF ABBREVIATIONS                                               |    |      |  |  |  | • |   |  |  | X               |

| 1            | Introduction                                                   |    | <br> |  |  |  |   |   |  |  | 1               |

| 1.1<br>1.2   | Research Contributions                                         |    |      |  |  |  |   |   |  |  | $\frac{2}{3}$   |

| 2            | Risk Management                                                |    |      |  |  |  |   |   |  |  | 5               |

| 2.1          | What can we Trust?                                             |    |      |  |  |  |   |   |  |  | 6               |

|              | Out-of-House                                                   |    |      |  |  |  |   |   |  |  | 6<br>8          |

| 2.2.1        | Verification                                                   |    |      |  |  |  |   |   |  |  | 8 9             |

| 2.2.3        | State Machines or Finite State Automata<br>Design Verification |    |      |  |  |  |   |   |  |  | 11<br>11        |

| 3            | Hardware Trojans                                               |    |      |  |  |  | • |   |  |  | 15              |

| 3.1<br>3.2   | Background and Risk                                            |    |      |  |  |  |   |   |  |  | 15<br>16        |

| 3.3<br>3.3.1 | Taxonomy                                                       |    |      |  |  |  |   |   |  |  | 17<br>19        |

|              | Effect/Payload                                                 |    |      |  |  |  |   |   |  |  | 20<br>20        |

|              | $\begin{array}{cccccccccccccccccccccccccccccccccccc$           |    |      |  |  |  |   |   |  |  | $\frac{20}{21}$ |

| 4            | Production of Integrated Circuits                              |    |      |  |  |  |   | • |  |  | 22              |

| 4.1<br>4.1.1 | Specification                                                  |    |      |  |  |  |   |   |  |  | $\frac{22}{23}$ |

| 4.2          | Design                                                         |    |      |  |  |  |   |   |  |  | $\frac{24}{24}$ |

| 4.2.2        | Electronic Design Automation (EDA) Too<br>Cell Library         | ls |      |  |  |  |   |   |  |  | 26<br>26        |

| 4.2.4        | Device and Component Models                                    |    |      |  |  |  |   |   |  |  | 26<br>26        |

| 4.3   | Fabrication                                                                  |

|-------|------------------------------------------------------------------------------|

| 4.3.1 | Masking                                                                      |

|       | Fabrication                                                                  |

|       | Wafer Probe                                                                  |

|       | Dice & Package                                                               |

| 4.4   | Testing                                                                      |

|       | Test Equipment                                                               |

|       |                                                                              |

| 5     | Securing Production                                                          |

| 5.1   | Specification                                                                |

|       | 1                                                                            |

| 5.2   | Design                                                                       |

| 5.2.1 | Third-Party IP                                                               |

|       | Tools                                                                        |

| 5.2.3 | Cell Libraries and Models                                                    |

| 5.2.4 | Hardware Description Languages                                               |

| 5.3   | Fabrication                                                                  |

| 5.3.1 | Confounding Factors                                                          |

|       | Side-Channel Measurements                                                    |

|       | Current/Power analysis                                                       |

|       | Timing/Delay Analysis                                                        |

|       | Circuit Trust through Hardening                                              |

|       | Circuit Trust through Obfuscation                                            |

| 5.4   | 9                                                                            |

|       |                                                                              |

| 5.5   | Summary                                                                      |

| 6     | Detection of Hardware Trojans in Third-Party Intellectual Property using Un- |

| U     | trusted Modules                                                              |

|       | trusted Modules                                                              |

| 6.1   | Design Comparison                                                            |

|       | Wrapping                                                                     |

|       | Unrolling                                                                    |

|       | Boolean Satisfiability                                                       |

|       | v                                                                            |

| 0.1.4 |                                                                              |

|       | Evaluating Trustworthiness with Design Comparison                            |

|       | False Positives                                                              |

|       | False Negatives                                                              |

| 6.3   | Experimental Methodology                                                     |

| 6.3.1 | Wrapping                                                                     |

| 6.3.2 | Unrolling Tools                                                              |

| 6.3.3 | Boolean Satisfiability                                                       |

| 6.4   | Testing and Results                                                          |

| 6.4.1 | RS-232 Universal Asynchronous Receiver/Transmitter                           |

|       | PIC16F84 8-bit Microcontroller                                               |

|       | Wishbone Conmax IP Core                                                      |

|       | ISCAS '89 Benchmarks                                                         |

|       | Limitations                                                                  |

|       | Summary                                                                      |

| ().() | Duiiiiiai V                                                                  |

| 7     | Assessment of Trojan Impact on Host Circuitry                          |

|-------|------------------------------------------------------------------------|

| 7.1   | Benchmark Analysis                                                     |

| 7.1.1 | Benchmark Suite Composition                                            |

| 7.1.2 | Methodology                                                            |

| 7.2   | Impact Within a Design                                                 |

| 7.3   | Impact Across Different Designs                                        |

| 7.3.1 | Impact on Area                                                         |

| 7.3.2 | Impact on Power                                                        |

| 7.3.3 | Limitations                                                            |

| 7.4   | Summary                                                                |

| 8     | Identifying Malicious Hardware through Software Parameter Modelling 76 |

| 8.1   | Testing Process                                                        |

| 8.1.1 | Process Variation                                                      |

| 8.1.2 | Representing a Trojan Circuit                                          |

| 8.1.3 | Training                                                               |

| 8.1.4 | Algorithm                                                              |

| 8.2   | Results                                                                |

| 8.2.1 | Limitations                                                            |

| 8.3   | Summary                                                                |

| 9     | Summary                                                                |

| 9.1   | Detection in third-party IP                                            |

| 9.2   | Assessment of Trojan impacts on area and power                         |

| 9.3   | Identification of Trojans in fabricated chips                          |

| 9.4   | Opportunities for Future Work                                          |

| REF   | ERENCES                                                                |

# List of Figures

| 2-1 | Levels of system abstraction for integrated circuits, classified into hardware (HW) stages and software (SW) stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | E.         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16<br>18   |

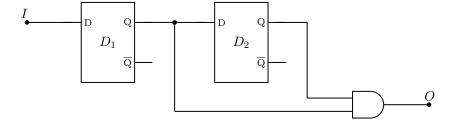

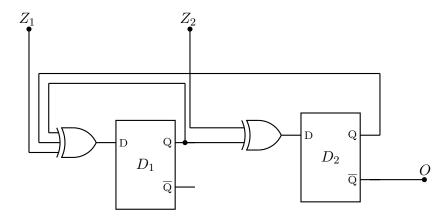

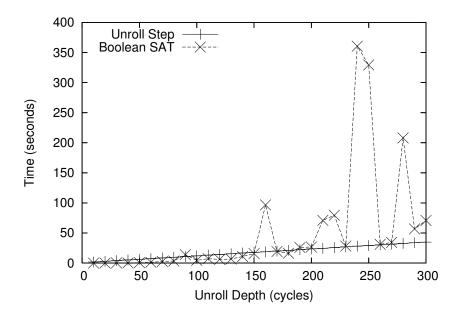

|     | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>46   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47         |

| 6-4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48         |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56         |

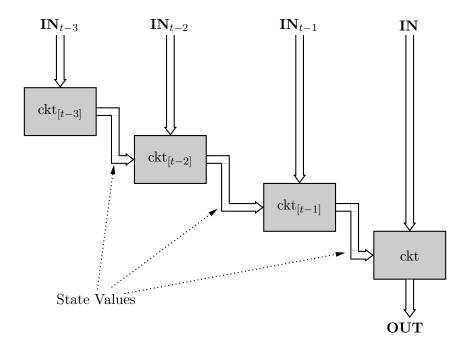

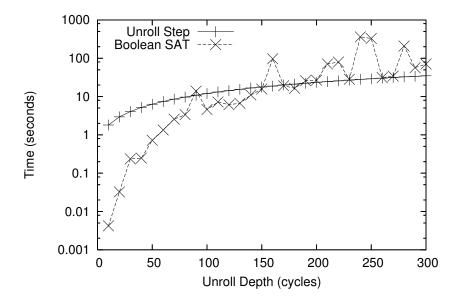

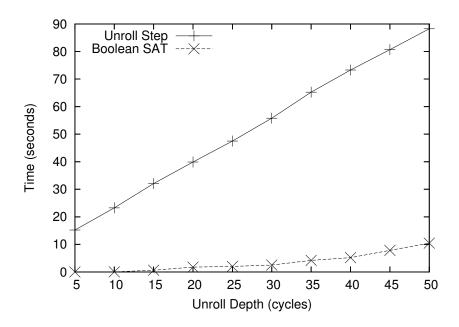

|     | Time to perform Design Comparison on RS232 UART circuit on a logarithmic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57         |

| 6-7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58         |

|     | , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65         |

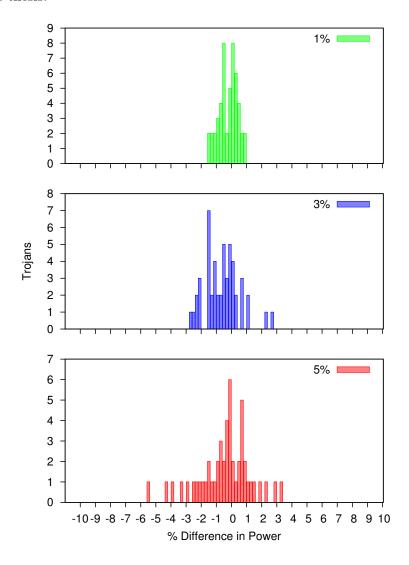

| 7-2 | Change in percent power due to data leak Trojans in AES cryptographic circuits. Calculated on the 32-nm, 45-nm, and 90-nm standard cell libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66         |

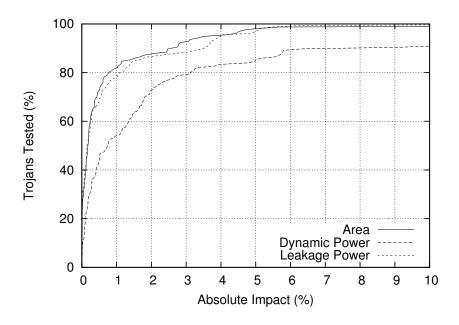

| 7-3 | Cumulative distribution of absolute impacts on area, dynamic power consumption, and leakage power on all benchmark circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67         |

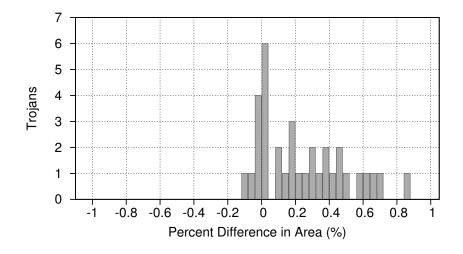

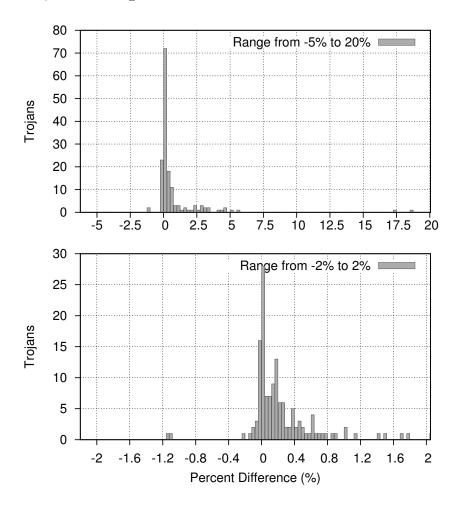

| 7-4 | Change in percent area over all tested Trojans. Calculated across the 32-nm, 45-nm, and 90-nm standard cell libraries. The bottom is a zoomed-in version of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •          |

|     | the top plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68         |

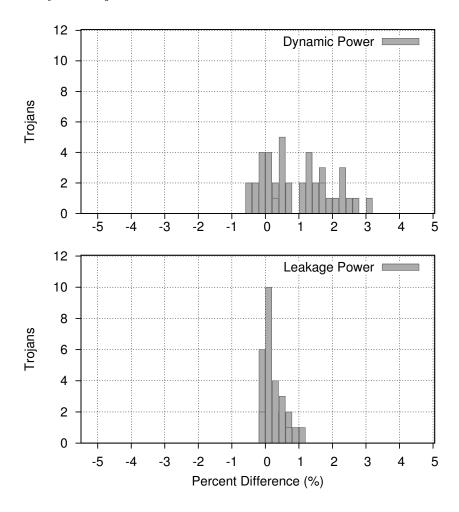

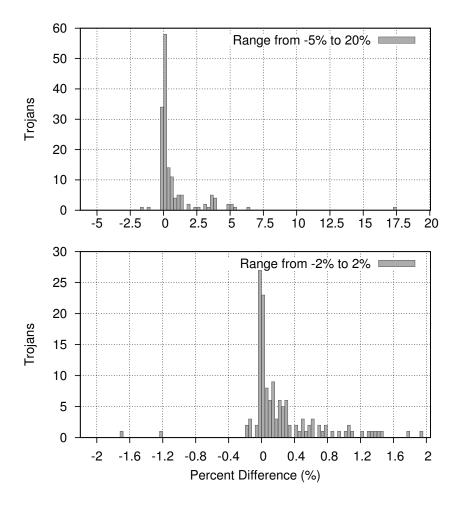

| 7-5 | Change in leakage power consumption over all tested Trojans. Calculated on the 32-nm, 45-nm, and 90-nm standard cell libraries. The bottom is a zoomed-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

|     | version of the top plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>7</b> 0 |

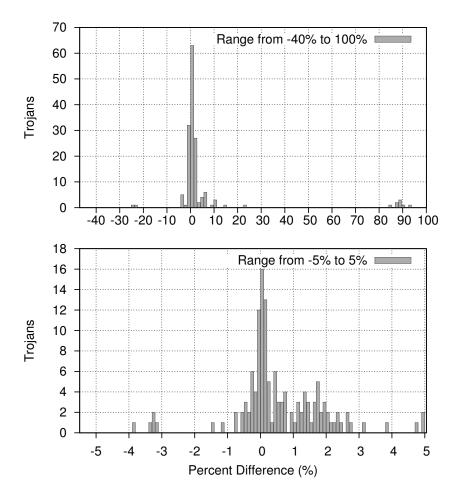

| 7-6 | Change in dynamic power consumption over all tested Trojans. Calculated on the 32-nm, 45-nm, and 90-nm standard cell libraries. The bottom is a zoomed-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

|     | version of the top plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71         |

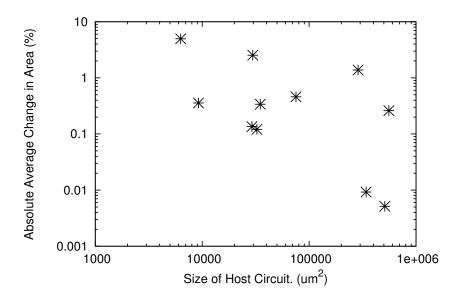

| 7-7 | Average absolute change in area due to Trojans compared to the size of the host circuit when synthesized to the 32-nm standard cell library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>7</b> 2 |

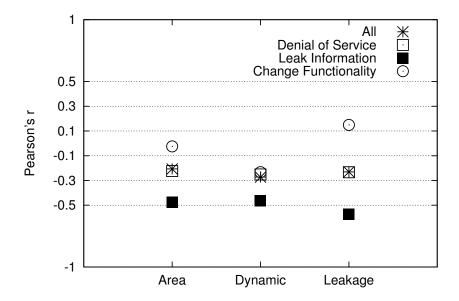

| 7-8 | Pearson product-moment correlation coefficient relating Trojan impact on percent area, dynamic power, and leakage power to the size of the modified circuit when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73         |

|     | of minimum of the ordinary and the management of the control of th | . 0        |

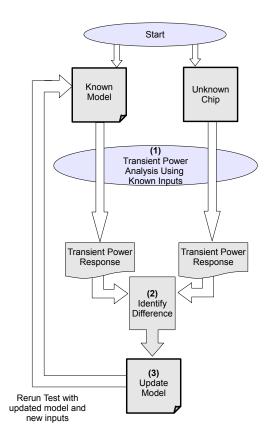

| 8-1 | Overview of model matching process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77         |

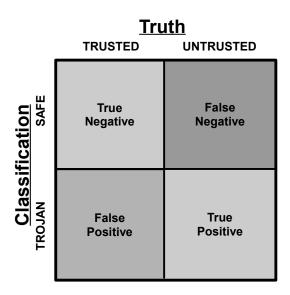

| 8-2 | Classification of unknown chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78         |

| 8-3 | Impact observed testing 50 circuits with randomly distributed variation within each circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80         |

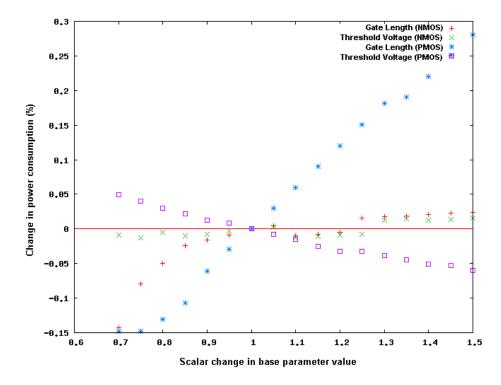

| 8-4 | Percent  | change   | in pov | ver o | ${ m consumption}$ | of | transistor | dependent   | upon | change | in |    |

|-----|----------|----------|--------|-------|--------------------|----|------------|-------------|------|--------|----|----|

|     | threshol | d voltag | e and  | gate  | e length of Pl     | ΜO | S and NM   | OS transist | ors  |        |    | 82 |

## List of Tables

| 4-1 | 2011 Top-10 Semiconductor Foundries [1]                                     | 28 |

|-----|-----------------------------------------------------------------------------|----|

| 6-1 | Size of base benchmark circuits when synthesized to the OSU 45-nm Standard  |    |

|     | Cell Library using Cadence RTL Compiler                                     | 54 |

| 6-2 | Cost in time to run test over different benchmark circuits (seconds)        | 54 |

| 7-1 | Average impact on area for each host circuit                                | 69 |

| 7-2 | Average impact on area for each Trojan classification                       | 69 |

| 7-3 | Average impact on dynamic power for each host circuit                       | 72 |

| 8-1 | Measured Trojan impacts on transient power consumption and p-value for one- |    |

|     | tailed t-test                                                               | 87 |

## List of Abbreviations

**AES** Advanced Encryption Standard

**ALU** Arithmetic Logic Unit

ATPG Automated Test Pattern Generation

**DFT** Design for Test

**EDA** Electronic Design Automation

FPGA Field Programmable Gate Array

**HDL** Hardware Description Language

IC Integrated Circuit

IP Intellectual Property

JTAG Joint Test Action Group

MISR Multiple-Input Signal Register

NMOS n-type Metal-Oxide-Semiconductor

**PMOS** p-type Metal-Oxide-Semiconductor

**SMV** Symbolic Model Verifier

TMR Triple Modular Redundancy

**UART** Universal Asynchronous Retriever/Transmitter

VHDL VHSIC Hardware Description Language

### Chapter 1

### Introduction

The continued advancement of modern integrated circuits has played a significant part in technological advancements over the past few decades. Unfortunately, as technology advances, opportunities to abuse or subvert this technology also become available. To most designers, one of the advantages to implementing a design in hardware instead of as a software implementation is the secure nature of hardware. The assumption that hardware is secure while software can be attacked, is prevalent. Unfortunately, this is a false assumption, created due to a lack of security awareness with increasingly complicated circuits [2].

Modern integrated circuits can be incredibly complicated, incorporating billions of transistors, and making use of resources from hundreds of sources. Many of these external resources can probably be trusted, such as the Cadence or Synopsys tool suites as they are the standard tools used for chip design. Unfortunately, other external resources cannot, and most likely should not, be trusted. There is no guarantee that a design sent overseas for fabrication will not have malicious changes in the final chip. It is important to identify threats and possible risks, and determine what is trustworthy and what threats need to be mitigated.

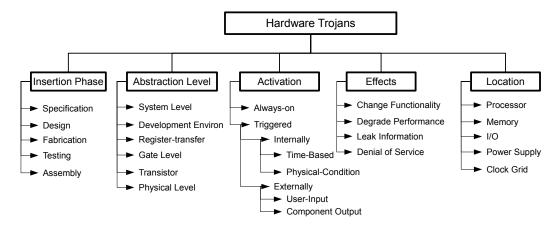

An unaddressed threat represents a possible vector for an adversary to insert an attack into a fabricated chip. Such attacks, dubbed "hardware Trojans", can have a wide variety of payloads for an even wider variety of malicious purposes [3]. For instance, an attacker could easily modify a cryptographic circuit to leak a key, set a critical circuit to self-destruct on a specific signal, or even covertly monitor and control a microcontroller remotely [4]. As long as the circuit appears to operate correctly under test conditions, such an attack would likely remain unnoticed.

While there are many points during production during which an adversary could influ-

ence a circuit, the possible damage that can be inflicted is maximized during the design and fabrication stages. Prior to the design stage, most malicious input would be limited to intentional sabotage of the overall design. Similarly, after the fabrication stage the attacker would generally need to rely on either intentional sabotage, or physically swapping the fabricated design with a subverted chip. However, during the design and fabrication stages, the damage is much more subtle.

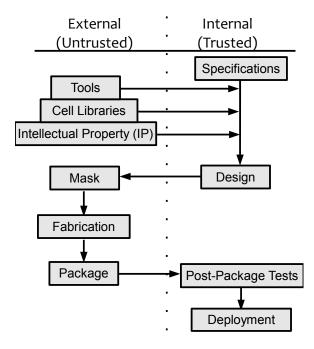

During the design stage, an adversary could hide malicious functionality inside of a third-party design block, masking it as an Intellectual Property (IP) watermark. Such functionality would remain in the circuit even after fabrication, and could be a veritable landmine whenever an attacker needed to call upon it. During the fabrication stage, an attacker at a fabrication plant could have free reign to modify the circuit, and the original designer would likely never know. The only certain way to identify such an attack would be to tear the fabricated chip apart with destructive imaging techniques, and digitally compare the designs. While such reverse engineering may be effective at finding Trojans, despite the small size of modern fabrication technologies [5], this process is much too expensive for a chip that most likely does not have a hidden Trojan. Taking the costs into account, very few Trojans will be identified by imaging techniques. Effective methods that provide a more cost-effective alternative must be provided.

### 1.1 Research Contributions

The contributions of this research can be summarized as follows:

- Development and testing of a technique to identify Trojans hidden within third-party intellectual property This technique samples IP blocks from multiple vendors and uses them as validating circuits for each other. This aids designers in preventing inclusion of malicious functionality in both licensed and unlicensed third-party design blocks.

- Assessment of the impact of malicious modifications on fabricated chips in terms of area and power consumption. The primary benefit from this re-

search comes from the characterization of what amount of impact can arise from a Trojan, and therefore how small of an impact must be detectable for counter-Trojan techniques.

• A functional modelling method for identifying Trojans hidden within fabricated circuits without need of a physical golden copy. This method revolves around adapting a known model of a circuit to match power and timing responses for an unknown physical circuit. This adapted model can then be examined after testing to identify signs of possible Trojan circuitry hidden in the unknown circuit. This allows chip designers to identify suspicious chips in a lot even without access to known safe copies of chips, or "golden" chips.

### 1.2 Organization of Dissertation

The dissertation is organized as follows:

The first portion of the dissertation, covering Chapters 2 through 5, covers key background information regarding malicious hardware and existing research on the topics.

- Chapter 2 describes the definitions with which risk and trust are measured and verified.

- Chapter 3 describes the background of hardware Trojans, and provides details for their structure and classification.

- Chapter 4 describes the process from the conception of a specification of an integrated circuit (IC) to the testing of the fabricated design, and identifies many possible attack vectors during this process.

- Chapter 5 explains how many of the threatened steps during production can be secured.

The second portion of this dissertation, covering chapters 6 through 9, describe the research performed, and techniques developed in this dissertation.

• Chapter 6 describes the technique developed within this dissertation to identify Trojan functionality hidden within third-party intellectual property, and its results.

- Chapter 7 reports the research and results in exploring the impact of Trojan functionality on host circuitry in terms of area and power.

- Chapter 8 describes the modelling technique developed in order to identify Trojans hidden within fabricated circuitry during the fabrication process.

- Finally, Chapter 9 summarizes this work, and provides extensions for future study.

### Chapter 2

## Risk Management

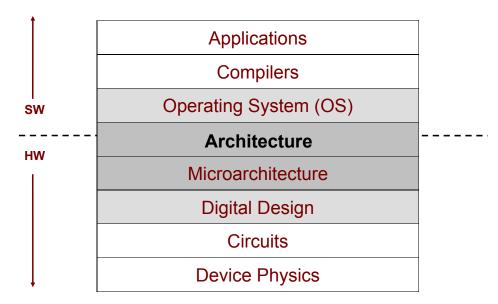

One of the prevailing assumptions in the area of security is the false belief that hardware implementations are secure. Due to the sheer number of attacks implemented through software, a mistaken belief has arisen that attacks will only come through software. While it is certainly true that the vast majority of attacks on a design might be through software, this does not preclude the possibility that an attack will also be implemented inside the hardware. In a complex design, many assumptions are made about the security of each step, and at each abstraction level. Everything at higher abstraction levels is built with the assumption that the lower abstraction levels operate securely (see Figure 2-1). If an operating system is secure, but operating on a compromised digital design, then can we call this implementation secure? Is it even possible to build a secure implementation upon an insecure base?

Figure 2-1: Levels of system abstraction for integrated circuits, classified into hardware (HW) stages and software (SW) stages.

### 2.1 What can we Trust?

When determining the security of a design, the first step is to identify clearly what types of steps can be trusted, and what types cannot. This determination might change depending upon types of circuits and their implementations, but for this dissertation, one easy rule will be implemented: in-house work can be trusted, while out-of-house work cannot.

### 2.1.1 In-House

A simplifying assumption made for the purpose of this work is that that all in-house work can be considered "trusted". The point of this assumption is to clearly define attack vectors in order to most effectively block possible attacks. This allows a designer to guarantee that every possible step in a design is covered from attacks. Under no circumstances does this mean that there are no security leaks, attempted sabotage, theft, or other problems within an organization. In fact, many organizations are rife with this type of in-house threat. However, there are many effective methods to resolve these threats that can be put into place [6]. It is difficult to secretly sabotage a design if all changes to a digital design are tracked and logged, with significant oversight on all changes. To put it simply: in-house work has its own process of verification that acts completely separately from other types of verification.

#### 2.1.2 Out-of-House

We further assume that all work performed outside of an organization is suspect. Any production step in which a design is modified by, or in the care of, an outside source can represent a possible vector for an attack. For each step, it is important to identify what attacks might be made by a third party during this opportunity, and determine methods of either preventing or identifying such attacks. For example, a medical device company designing a pacemaker might license a wireless controller block from a vendor marketing third-party intellectual property (IP). It could be disastrous if this controller had malicious functionality hidden by the designer. In such a situation, it is critical to identify the risk posed by incorporating this untrusted block in a design.

Another important aspect of the environment to note is that each step represents a different type of risk, which needs to be assessed by the designer. In the previous example of a pacemaker, there is a high level of risk for the design due to the disastrous effects of their device failing. There would be less need to incorporate such strict security for a wireless controller in a car alarm, as the cost of failure is lower. Failing car-alarms are much less likely to cause death than failing pacemakers.

### 2.1.2.1 Vulnerabilities in the Supply Chain

One reason that out-of-house resources are assumed untrusted in this dissertation, regardless of what is purported to be supplied, is because tracking the source of an external resource can be long and convoluted. This has been a significant issue with defense contractors in the past few years, with regards to actual physical chips purchased from reputable vendors or resellers.

Consider several examples. First, a fiasco involving the United States Navy was made public in 2010, when a company called VisionTech was charged with selling over 59,000 microchips which contained hidden kill-switch functionality [7]. This functionality would allow an attacker to remotely disable whatever was running on these chips, including missiles, communication equipment, and other military vehicles. For years, this company had been importing counterfeit chips from China and marketing them to defense companies as military grade microchips. The list of these companies includes BAE systems, which provides Identification Friend-or-Foe (IFF) systems to the US Navy, and Raytheon Missile systems, for incorporation on F-16 fighter planes.

Second, unfortunately VisionTech is not the only reseller to buy cheap microchips from overseas and sell them domestically. Another similar example of corruption in the supply-chain transpired in 2005 when United Aircraft and Electronics, a company in which the operator sold false certification of aircraft parts, and was sentenced to 188 months in prison [8].

Third, an example from 2002 is the case of United Space Alliance, a company which bid and received a \$24 million contract with NASA to supply military grade 8086 microprocessors for use with the space-shuttle computers. This company then proceeded to purchase

used computers through eBay and pull commercial-grade 8086 processors from the motherboards [8]. Commercial-grade chips would almost certainly have difficulties operating in the adverse environments required by the space shuttle computers.

Unless it is possible to completely track the life of a resource, that resource should be considered suspect. Since verification of an external resource is generally a simpler task than a full forensic investigation of the history of a resource, verification is the preferred method of determining whether something can be considered trusted.

### 2.2 How do we Trust?

Although one can make the argument that something can be made 100% trustworthy by simply doing everything in-house, this is not an option for most organizations. One of the primary reasons for outsourcing individual steps in a production path is to save time and money. If avoiding outsourcing causes a design to become too expensive to compete on an open market, then there is little point in creating the design.

What is necessary in this case is a method of taking an untrusted input, be it a circuit, a digital design, or a cell library, and verify that this untrusted input has no hidden malicious functionality. Depending on the untrusted step, this process will be different.

#### 2.2.1 Verification

The first step when exploring the problem of verification is to explicitly define what is meant by the word 'verification'. For some groups, verification of a design means the manual or logical proof that a design functions as intended for all possible inputs and states. This is often used with digital designs when it is possible to form a mathematical proof. However, according to Godefroid [9]:

• To verify means to mathematically prove that a system meets its correctness requirements. Verification is thus the tool that enables the designer to be confident that the formal description of the system he/she has obtained does indeed satisfy the problem requirements.

Under this definition, only when every possible input situation is proven to act as intended, the system is verified. However, when dealing with something other than a computer system or a simulated design, such a mathematical proof can become impossible. This also can happen as the designs grow in size and complexity. In many cases, it is useful to consider an alternate version of verification:

• as a means to test and show that the design works well enough and will act as intended through all expected situations.

Even though both of these definitions of verification have the same general purpose, the actual process involved with each type of verification varies significantly. This difference is predominantly due to problem known as the state explosion dilemma, which is reviewed below.

### 2.2.2 The State Explosion Dilemma

Most modern designs are too complicated to allow for exhaustive testing of every possible input. This is due to the rate at which the number of possible tests increase. For instance, a simple circuit with no internal states and four inputs has a total of  $2^4$ , or 16 possible patterns to test. If the number of inputs were to be increased to 10, there would be  $2^{10}$ , or 1024 possible test patterns. This increase is exponential, growing increasingly quickly with each additional input. To make matters worse, most modern designs are not stateless; they incorporate possible internal states affecting the response for each input. During an exhaustive test, each state would need to be tested with every possible input. The total number of test patterns can be explained with the relation  $2^{(n+m)}$  where n is the number of input bits, and m is the number of state bits (i.e., flip-flops or latches in a circuit). As such, the work necessary for a comprehensive test increases exponentially with a linear increase in the size of a problem. This quickly becomes too large to test practically, even for small circuits. For example, a circuit containing 20 inputs and 60 state bits would require over  $1.21 \times 10^{24}$  tests if every possible state were to be tested. At 2.4 GHz with one test per cycle. this would take almost 16 million years to finish. Even if this work were to be parallelized and split among thousands of processors, it would still take years. Clearly, another method of verifying the validity of a design is necessary.

### 2.2.2.1 Addressing the problem