# SINGLE-EVENT-TRANSIENT EFFECTS IN SUB-70 NM BULK AND SOI FINFETS

By

Farah El Mamouni

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

August, 2012

Nashville, Tennessee

Approved:

Ronald D. Schrimpf

Robert A. Reed

Michael L. Alles

Daniel M. Fleetwood

Sokrates Pantelides

Copyright © 2012 by Farah El Mamouni

All Rights Reserved

То

Ahmed El Mamouni

## ACKNOWLEDGMENT

I would like to thank the HiREV Program and DTRA's Basic Research Program for financially supporting this work.

I would like to thank my advisor, Dr. Ronald D. Schrimpf for being a wonderful professor, a good friend, and an outstanding mentor. I thank him for his great contribution to improving my technical skills as well as assisting my personality to blossom.

I would like to thank Dr. Robert A. Reed, for helping me dive in the sea of single event effects. His guidance during testing trips and group meetings was priceless.

I would like to thank Dr. Alles and Dr. Fleetwood for their invaluable discussions.

I would like to thank Dr. Dale McMorrow, Dr. Steve Buchner and Dr. Jeffery Warner for their help and support performing my laser experiments at NRL. I would like to thank Dr. Gyorgy Vizkelethy for his patience and assistance to successfully accomplish the heavy ion experiments at SNL.

I would like to thank Dr Kenneth Galloway for helping out getting our first set of sub-130 nm imec bulk FinFETs. I would like to thank Dimitri Linten and Dr Eddy Simoen and Dr Cor Claeys for providing us with our second set of sub-70 nm imec bulk and SOI FinFETs.

I would like to thank Dr. Enxia Zhang for her help preparing my high-speed packages. I thank her and Michael King for performing my heavy ion experiments when needed. I would like to thank Andrew Sternberg and Nick Pate for helping me with my Python scripts. Finally I thank all of the RER group students and staff for the interesting and fun discussions we had in the lab.

I would like to thank my first professor, first cheerleader and the first one who believed in me, my father, Ahmed El Mamouni. I love you dad...

I would like to thank my mother Nabila for her unconditional love, my brother Anass for setting a terrific example, my sister Fadoua for telling me once "just do it, I am with you!" my brother Jassim for his endless encouragements, and my beautiful little sister Hajar for her crazy and genuine love.

I would like to thank my dear husband Nausher Ahmed for his growing love, continuous support and hilarious friendship.

I would like to thank my mother in law Aziza and my sister in law Awatef for their continuous prayers and emotional support.

## TABLE OF CONTENTS

| ACKNOWLEDGMENT  | iv |

|-----------------|----|

|                 |    |

| LIST OF FIGURES | ix |

|                 |    |

| Chapter         |    |

| I. INTRODUC                                                                                                                                                      | CTION                                       | 1              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------|

| 1.1. Thesis object                                                                                                                                               | ive                                         | 1              |

| 1.2. Introduction.                                                                                                                                               |                                             | 2              |

| 1.3. Introduction t                                                                                                                                              | to non-planar technology                    | 4              |

| 1.3.1. Limits of pl                                                                                                                                              | lanar technology                            | 4              |

| 1.3.1.1. Shor                                                                                                                                                    | t channel effects                           | 5              |

| 1.3.2. Non-plan                                                                                                                                                  | nar technology                              | 7              |

| 1.3.2.2. FinF                                                                                                                                                    | ET technology<br>ET operation<br>ET scaling |                |

|                                                                                                                                                                  |                                             |                |

|                                                                                                                                                                  | SINGLE EVENT EFFECTS ON ELECTRONIC          |                |

|                                                                                                                                                                  |                                             | 11             |

| 2.1. Single Event                                                                                                                                                |                                             |                |

| 2.1. Single Event<br>2.1.1. Definition.                                                                                                                          | Effects (SEEs)                              | 11<br>11<br>11 |

| <ul><li>2.1. Single Event</li><li>2.1.1. Definition</li><li>2.1.2. History</li></ul>                                                                             | Effects (SEEs)                              |                |

| <ul> <li>2.1. Single Event</li> <li>2.1.1. Definition</li> <li>2.1.2. History</li> <li>2.1.3. Charge g</li> <li>2.1.3.1. Ion/s</li> <li>2.1.3.2. Char</li> </ul> | Effects (SEEs)                              |                |

| 2.1.4.1.             | Drift collection                                         |    |

|----------------------|----------------------------------------------------------|----|

| 2.1.4.2.<br>2.1.4.3. | Funneling<br>Diffusion collection                        |    |

| 2.1.4.3.             | Bipolar amplification                                    |    |

| 2.1.4.5.             | Shunt collection                                         |    |

| 2.2. Device          | response to single event effects (SEEs)                  |    |

| 2.2.1. Sin           | gle-Event Effects in Planar MOSFETs                      |    |

| 2.2.1.1.             | Bulk Planar MOSFETs                                      |    |

| 2.2.1.2.             | SOI Planar MOSFETs                                       | 25 |

| 2.2.1.3.             | Summary                                                  |    |

| 2.2.2. Sin           | gle-Event Effects in FinFETs                             |    |

| III. DEVIC           | CE AND EXPERIMENTAL DETAILS                              |    |

| 3.1. Measur          | ement techniques                                         |    |

| 3.1.1. Las           | ser source, Naval Research Laboratory (NRL)              |    |

| 3.1.1.1.             | Single photon absorption (SPA)                           |    |

| 3.1.1.2.             |                                                          |    |

| 3.1.2. Hea           | avy ion source                                           |    |

| 3.1.2.1.             | IBICC                                                    |    |

| 3.1.2.2.             | TRIBICC                                                  |    |

| 3.1.2.3.             | High speed packages                                      |    |

| 3.2. Devices         | 5                                                        | 39 |

|                      | R INDUCED CURRENT TRANSIENTS IN SUB-130 nm BUL<br>INFETS |    |

| 4.1. Bulk Fi         | nFETs                                                    | 41 |

| 4.1.1. Devie         | ce and experimental details                              | 41 |

| 4.1.2. Cu            | rrent transients in the drain region                     |    |

| 4.1.2.1.             | Charge collection                                        |    |

| 4.1.2.2.             | Charge collection mechanisms                             |    |

| 4.1.3. Cu            | rrent transients in the fins region                      |    |

| 4.2. Bulk vs         | s. SOI FinFETs                                           | 50 |

| 4.2.1. Dev           | vice and experimental details                            | 50 |

| 4.2.2. Laser         | r induced current transients in bulk and SOI FinFETs     |    |

| 4.2.3. Las           | ser energy dependence of the charge collection           |    |

| 4.2.4. Laser energy dependence of the FWHMs                                                                                                                                           | 55 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2.5. Drain bias dependence of the charge collection                                                                                                                                 | 56 |

| V. HEAVY-ION-INDUCED CHARGE COLLECTION IN SUB-70 NM BU<br>AND SOI FINFETS                                                                                                             |    |

| 5.1. Device and experimental details                                                                                                                                                  |    |

| 5.2. Charge collection in bulk FinFETs                                                                                                                                                |    |

| 5.2. Charge collected in SOI FinFETs                                                                                                                                                  | 65 |

| 5.2.1. IBICC experimental results                                                                                                                                                     |    |

| 5.2.2. TCAD simulation results                                                                                                                                                        | 69 |

| 5.3. Current transients in bulk FinFETs                                                                                                                                               | 73 |

| VI. CHARGE COLLECTION MECHANISMS IN FINFETS WITH REDUC<br>DRAIN REGION AREAS                                                                                                          |    |

| 6.1. Charge collection in FinFETs with saddle contacts                                                                                                                                | 76 |

| 6.1.1. Bulk FinFETs                                                                                                                                                                   | 77 |

| <ul><li>6.1.1.1. Sensitive area of bulk FinFETs with saddle contacts</li><li>6.1.1.2. Current transients in bulk FinFETs with saddle contacts</li></ul>                               |    |

| 6.1.2. SOI FinFETs                                                                                                                                                                    | 80 |

| <ul><li>6.1.2.1. Substrate-bias-dependence of the transient response of SOI Fi with saddle contacts</li><li>6.1.2.2. Current transients in SOI FinFETs with saddle contacts</li></ul> | 80 |

| 6.2. Transient shunt effect in FinFETs with saddle contacts                                                                                                                           | 84 |

| 6.2.1. Bulk FinFETs with saddle contacts                                                                                                                                              | 84 |

| 6.2.2. SOI FinFETs with saddle contacts                                                                                                                                               | 87 |

| 6.3. Drain bias dependence of the shunt effect in FinFETs with saddle contacts                                                                                                        | 88 |

| 6.3.1. Bulk FinFETs with saddle contacts                                                                                                                                              | 88 |

| 6.3.2. SOI FinFETs with saddle contacts                                                                                                                                               | 90 |

| VII. CONCLUSION                                                                                                                                                                       |    |

| REFERENCES                                                                                                                                                                            | 96 |

# LIST OF FIGURES

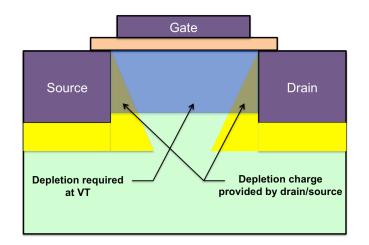

| Figure 1: Depletion required at the threshold voltage $(V_T)$ in the channel region and the depletion charge provided by drain/source regions in a planar MOSFET transistor [10]5                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

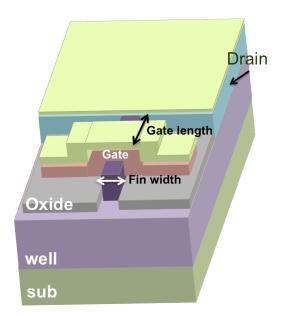

| Figure 2: Physical structure of a FinFET device [12]7                                                                                                                                                                                                                                                                                                          |

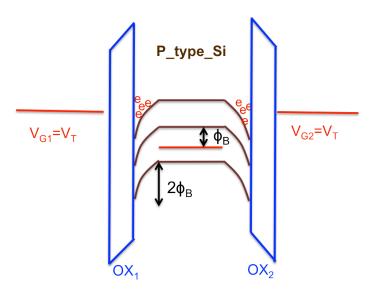

| Figure 3: Energy band diagram in the fin at the threshold voltage of an n-channel FinFET device                                                                                                                                                                                                                                                                |

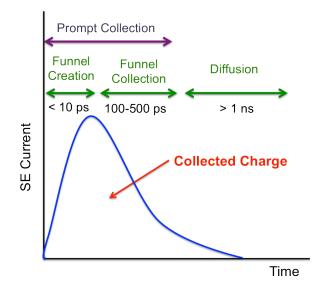

| Figure 4: Shape of a representative single event pulse measured at a struck p-n junction [24]                                                                                                                                                                                                                                                                  |

| Figure 5: Charge collection in the depletion region in a p-n junction [24]                                                                                                                                                                                                                                                                                     |

| Figure 6: The figure shows the progress of funneling from the plasma track creation (on the left) to the funnel build up (on the right) [24]                                                                                                                                                                                                                   |

| Figure 7: Diagram of a multilayer structure exhibiting shunt effect [24][48]21                                                                                                                                                                                                                                                                                 |

| Figure 8: Drain and source transient currents induced by a 35 MeV Cl ion beam in a 0.25 $\mu$ m bulk planar NMOS transistor. The transistor is biased in the OFF state (V <sub>D</sub> =1V) and in the transmission gate configurations [43]                                                                                                                   |

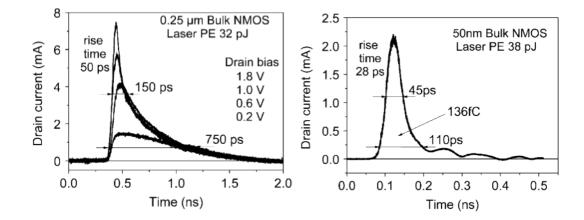

| Figure 9: a). Transient drain currents induced by pulsed laser irradiation in a 0.25 $\mu$ m NMOS transistor. The transistor is OFF biased and the drain voltage is: 1.8 V, 1 V, 0.6 V, 0.2 V. b). Transient drain currents induced by pulsed laser irradiation in a 50 nm bulk NMOS transistors. The transistor is OFF biased with a drain voltage of 1V [50] |

| Figure 10: Drain current transients induced by a pulsed laser irradiation in a 0.25 $\mu$ m technology partially depleted SOI transistor. The device is OFF biased. The drain is biased at different voltages: 1.8, 1.0, 0.6 and 0.2 V [50]. This device was processed with a 400 nm BOX thickness and 100 nm silicon film thickness                           |

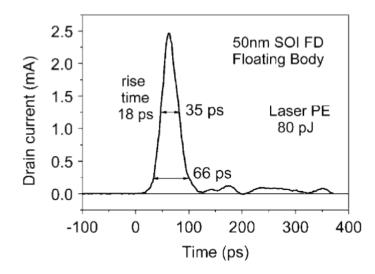

| Figure 11: Drain current transients recorded in a 50 nm gate length FD SOI MOSFET irradiated with a pulsed laser energy of 80 pJ [50]. This device is processed with an 11 nm silicon film and 100 nm BOX thickness                                                                                                                                            |

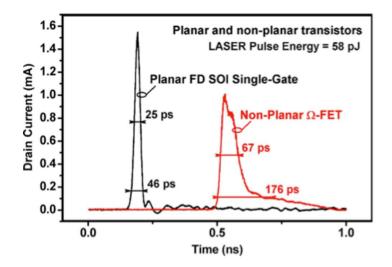

| Figure 12: Transient drain current induced by a pulsed laser irradiation in a planar FD SOI MOSFET with a gate length of 50 nm and a floating body and in a non-planar                                                                                                                                                                                         |

| FinFET device with a gate length of 60 nm . The silicon film thickness is: 8 nm and 25 in of the FD SOI devices and the non-planar devices, respectively [55]                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

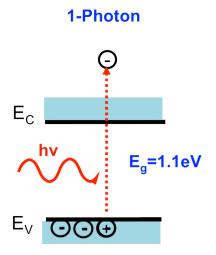

| Figure 13: Energy band diagram for silicon illustrating the single photon absorption. hv is the energy of the incident photon                                                                                                                                                             |

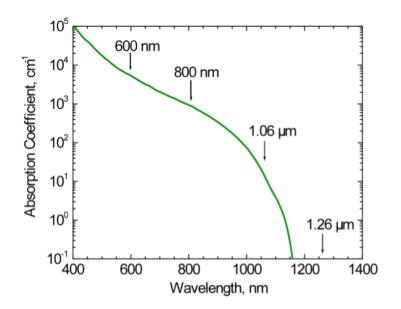

| Figure 14: Absorption coefficient as a function of the wavelength for silicon [58]                                                                                                                                                                                                        |

| Figure 15: Energy band diagram for silicon illustrating the two-photon absorption34                                                                                                                                                                                                       |

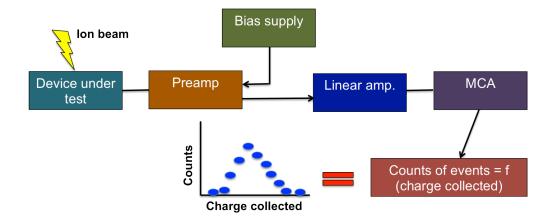

| Figure 16: Representative diagram of the experimental set up of IBICC technique [62-<br>63]                                                                                                                                                                                               |

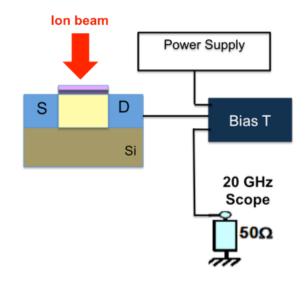

| Figure 17: Schematic diagram of the experimental setup used to record current transients in bulk and SOI FinFETs. A 20 GHz TDS6124C scope with 50-ohm impedance was used to visualize and record the transients                                                                           |

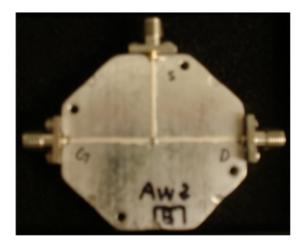

| Figure 18: Alumina high-speed package (40 GHz)                                                                                                                                                                                                                                            |

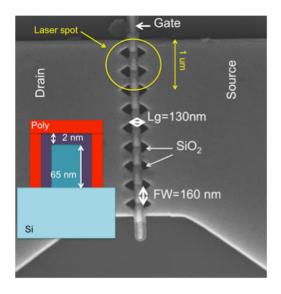

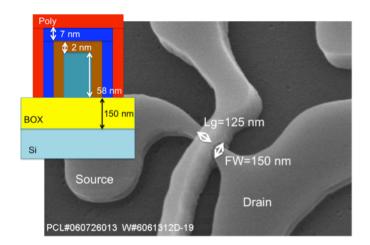

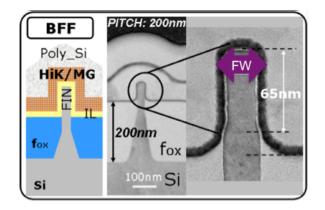

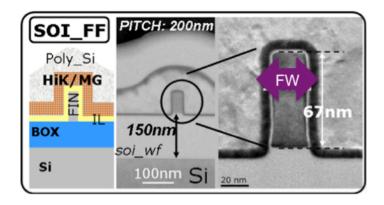

| Figure 19: SEM picture of a 10-fins bulk FinFET. The figure shows the fin width (FW) and the gate length (Lg) parameters. The inset shows the cross section of the bulk FinFET corresponding to one fin [12]                                                                              |

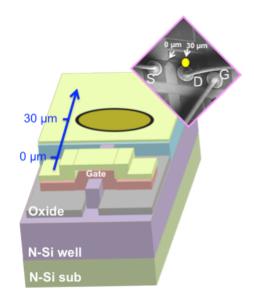

| Figure 20: Physical structure of the FinFET showing the location of the laser spot in the fin and up to 30 $\mu$ m away from the fin. Inset: SEM picture of the whole bulk FinFET structure including the gate drain and source terminals. Figures are not to scale [12]44                |

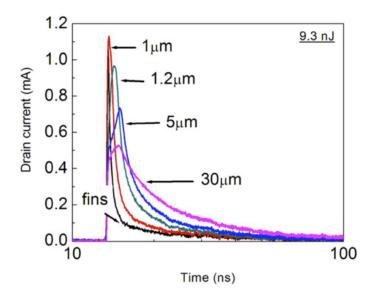

| Figure 21: Representative semi log current transients recorded in the fins ( $x = 0-\mu m$ ) and up to 30- $\mu m$ underneath the drain away from the fins [12]                                                                                                                           |

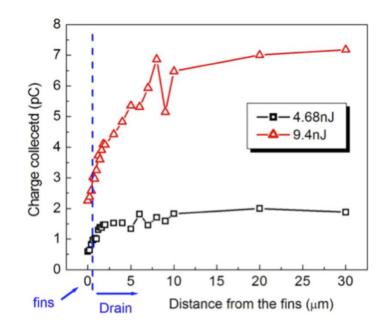

| Figure 22: Charge collected (pC) as a function of x-position from the fins (x = 0 $\mu$ m) to 30 $\mu$ m toward the drain region (the blue arrows) as illustrated in Fig. 20 for different laser energies [12]                                                                            |

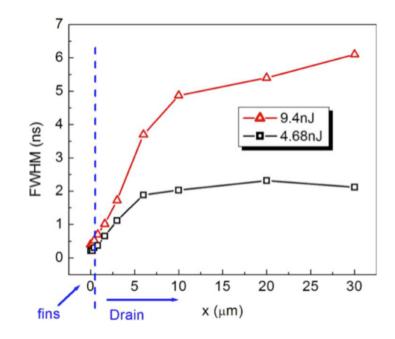

| Figure 23: Full width at half maximum (FWHM) (ns) as a function of the distance x ( $\mu$ m) for two laser energies: 4.68 nJ and 9.4 nJ. At x = 0 $\mu$ m, the laser is focused in the fins [12]                                                                                          |

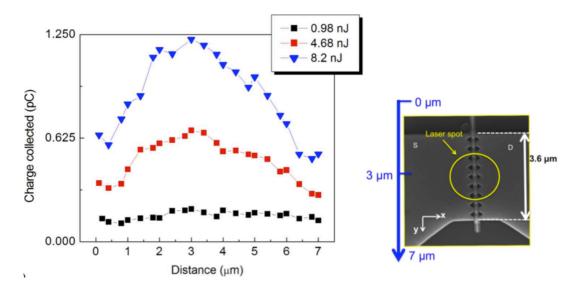

| Figure 24: (a) Charge collected (pC) as a function of the distance y ( $\mu$ m) traversed by the laser for 3 different laser energies, 0.98-nJ, 4.68-nJ and 8.2-nJ. (b). SEM picture of the fins region, showing distance traversed by the laser across the fins in the y-direction [12]. |

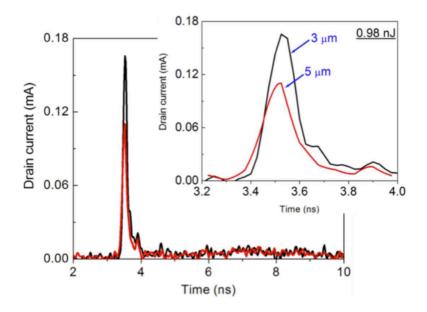

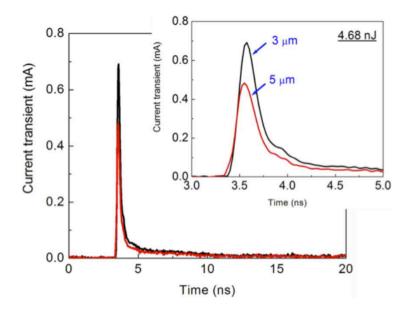

| Figure 25: Current transients captured in the fins at distances: $3 \mu m$ and $5 \mu m$ (cf. Fig. 22(b)) for laser energy of 0.89 nJ [12]                                                                                                                                                |

| Figure 26: Current transients captured in the fins at distances: $3 \mu m$ and $5 \mu m$ (cf. Fig. 6(b)) for a laser energy of 4.68 nJ [12]                                                                                                                                               |

| Figure 27: SEM picture of a single-fin SOI FinFET. The figure shows the fin width (FW) and the gate length ( $L_g$ ) parameters. The inset shows the cross section of the FD SOI FinFET [66]                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

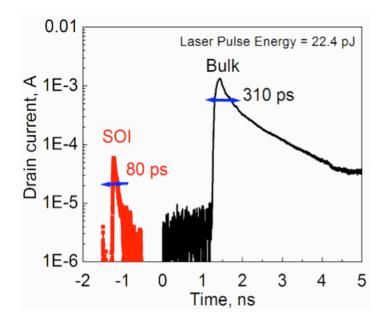

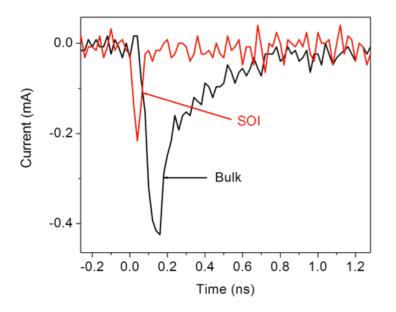

| Figure 28: Semi log drain current transients generated by the pulsed laser in both SOI and bulk FinFETs. The laser energy is 22.4 pJ. A voltage of -0.6 V was applied to both samples during irradiation. The full width at half maximum (FWHM) is illustrated for both devices on the figure [66] |

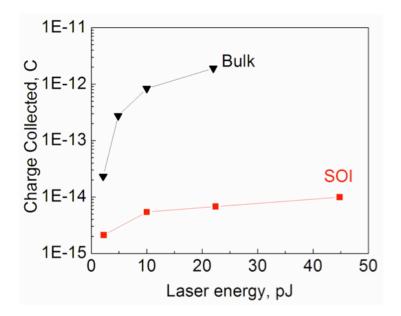

| Figure 29: Semi log curves showing charge collected (C) for bulk (triangles) and SOI (squares) FinFETs as a function of laser energy [66]                                                                                                                                                          |

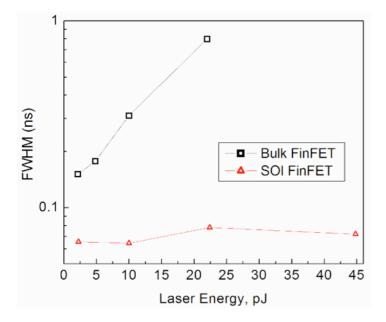

| Figure 30: Semi log plot showing FWHM as a function of laser energy for bulk (empty squares) and SOI FinFETs (empty triangles) [66]                                                                                                                                                                |

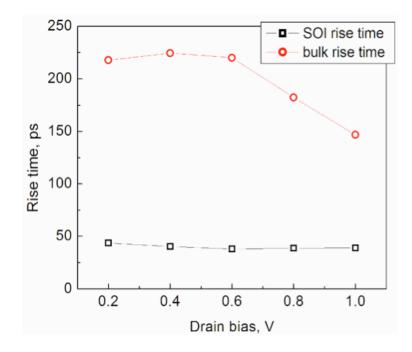

| Figure 31: Rise time in ps for bulk and SOI bulk FinFETs current transients for different drain biases [66]                                                                                                                                                                                        |

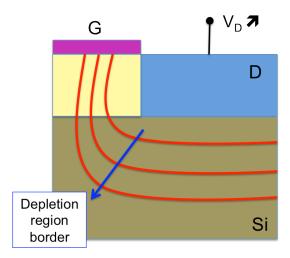

| Figure 32: Schematic diagram of the (2D) cross section of the drain-substrate region in the bulk FinFET [66]                                                                                                                                                                                       |

| Figure 33: SEM picture of the cross section of bulk FinFET is shown on the right. On the left is illustrated the schematic cross sections [69]. The well doping is $\sim 10^{17}$ cm <sup>-3</sup>                                                                                                 |

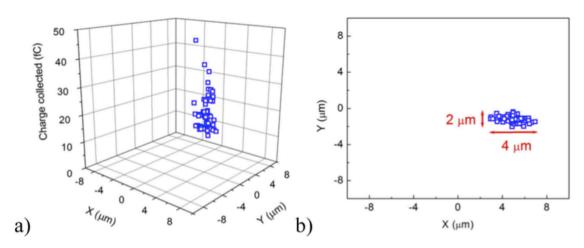

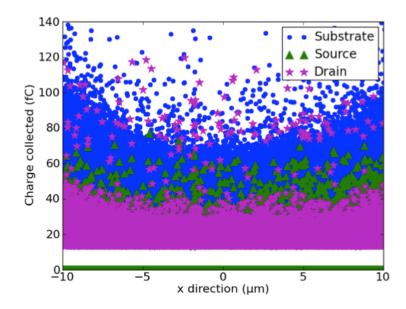

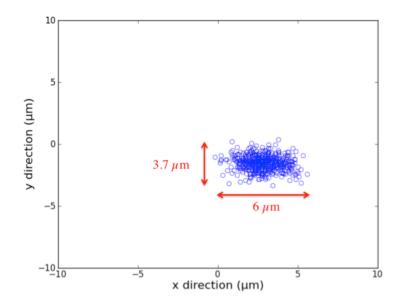

| Figure 34: (a) Charge collected in the drain terminal of a bulk FinFET with a 5 nm fin width and a gate length of 70 nm. (b) Projection of the charge-collected values on the (x, y) plan defining the sensitive area of the tested structure [12]                                                 |

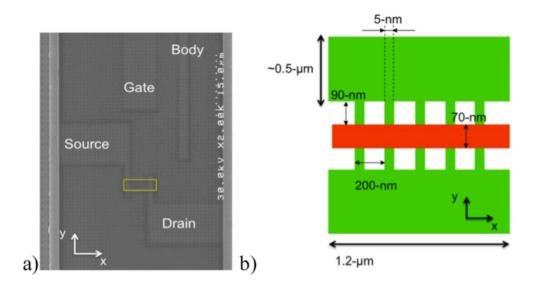

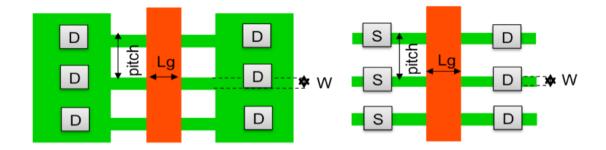

| Figure 35: (a) SEM picture showing the location of the FinFET device on the die. (b) Top layout view of a FinFET device with 5-fins. All tested devices have the same parameters illustrated on the layout unless otherwise mentioned [12]                                                         |

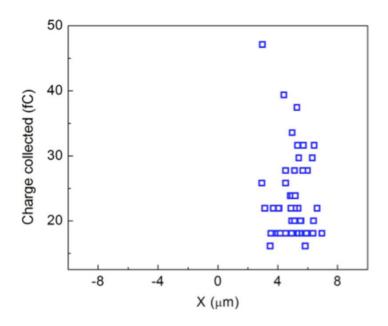

| Figure 36: Projected values of the charge collected (fC) shown in Fig. 2(a) on the x-axis $(\mu m)$ [12]                                                                                                                                                                                           |

| Figure 37: Pictures of the cell layout and an SEM of a FinFET based SRAM cell built in imec [69]                                                                                                                                                                                                   |

| Figure 38: SEM picture of the cross section of SOI FinFET is shown on the right. On the left is illustrated the schematic cross sections [69]                                                                                                                                                      |

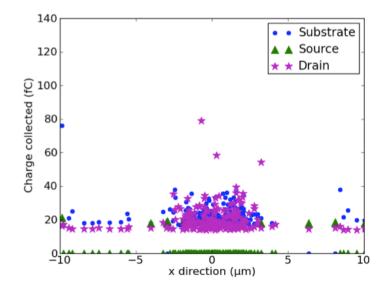

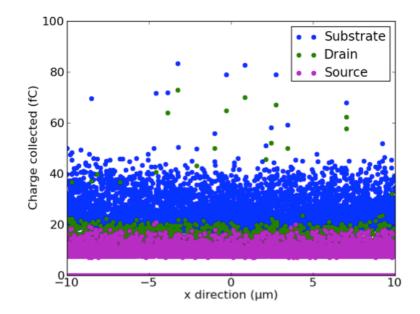

| Figure 39: Values of charge collected (fC) along the x-axis (along the gate) in the substrate (circles) source (triangles) and drain (stars) terminals. The SOI FinFET was biased in the off state configuration with a grounded substrate [73]                                                    |

| Figure 40: Values of charge collected (fC) along the x-axis (along the gate) in the substrate (circles) source (triangles) and drain (stars) terminals. The SOI FinFET was biased in the off state configuration with a substrate bias of -4V [73]67                                               |

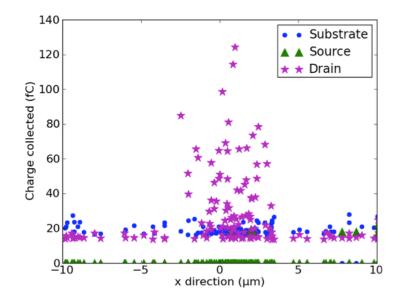

| Figure 41: Values of the charge collected (fC) along the x-axis (along the gate) in the substrate source and drain terminals. The SOI FinFET was biased in the off state configuration with a substrate bias of +4V [73]                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

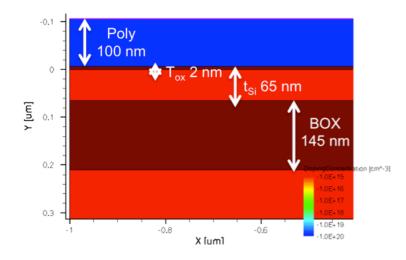

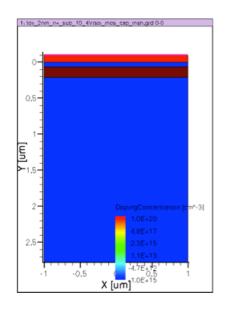

| Figure 42: Enlarged view of the schematic cross section of the SOI MOS capacitor simulated using TCAD                                                                                                                                                                                                                                                 |

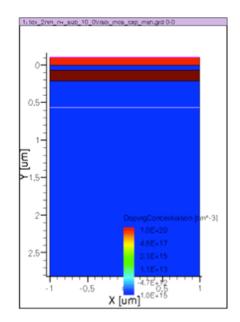

| Figure 43: Cross section of the SOI MOS capacitor with a grounded substrate. The white line in the substrate illustrates the oxide/substrate depletion region                                                                                                                                                                                         |

| Figure 44: Cross section of the SOI MOS capacitor with a substrate voltage of -4 V. The white line in the substrate illustrates the oxide/substrate depletion region                                                                                                                                                                                  |

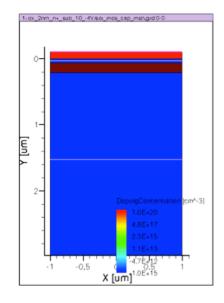

| Figure 45: Cross section of the SOI MOS capacitor with a substrate voltage of +4 V. The absence of the white line in the substrate demonstrates the absence of the depletion region                                                                                                                                                                   |

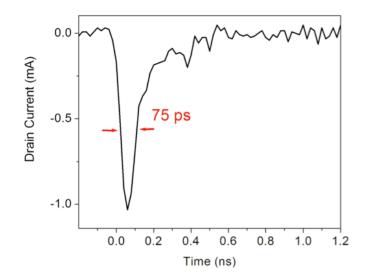

| Figure 46: Current transient collected in the drain terminal of a bulk FinFET biased in the off state with a drain bias of 0.6 V. The FinFET has 5 fins, each fin is 20 nm wide and 70 nm long                                                                                                                                                        |

| Figure 47: a). Top layout view of FinFETs with common drain contact (dumbbell contact). b) Top layout view of FinFETs with multiple drain contacts (saddle contact). FinFETs with dumbbell and saddle contacts have different number of fins [73]75                                                                                                   |

| Figure 48: (x, y) locations of the transient events recorded in a bulk FinFET with saddle contact                                                                                                                                                                                                                                                     |

| Figure 49: The solid (black) transient curve was recorded in a FinFET ( $W_{f}/L=20/70$ ) with dumbbell contacts. The dashed (red) transient was recorded in a FinFET ( $W_{f}/L=20/60$ ) with saddle contacts [73]                                                                                                                                   |

| Figure 50: Projected values of charge collected (fC) along the x-axis (along the gate) in the substrate source and drain terminals. The SOI FinFET was biased in the off state configuration with a bias substrate of -5V                                                                                                                             |

| Figure 51: Current transients recorded in bulk and SOI FinFETs with saddle contacts.<br>Both devices have 10 fins; each fin is 20 nm wide and 60 nm long. Both devices were<br>biased in the off state configuration with a drain bias of 1 V. The body of the SOI FinFET<br>was left floating                                                        |

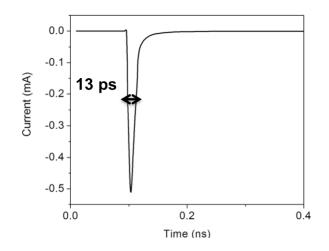

| Figure 52: Simulated drain current transient in an SOI FinFET. A FWHM of 13 ps is obtained                                                                                                                                                                                                                                                            |

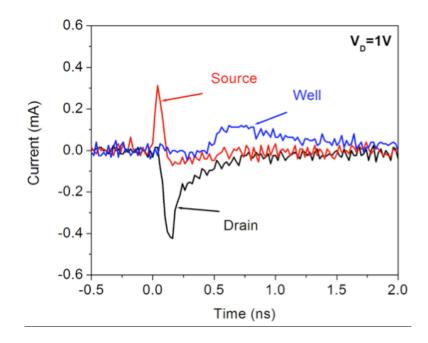

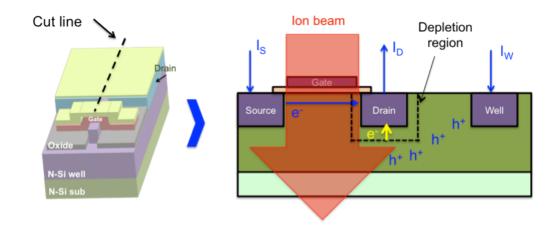

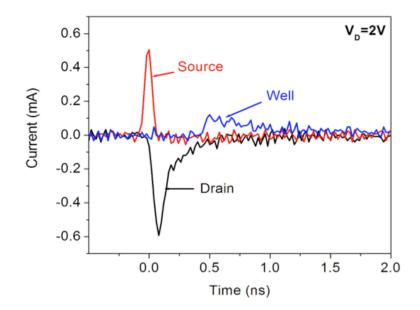

| Figure 53: Current transients recorded in the drain (black), in the source (red), and in the well (blue) of a bulk FinFET with saddle contacts. The FinFET has a gate length of 60 nm, a fin width of 20 nm and 10 fins in parallel. The FinFET was irradiated in the OFF state configuration, with $V_D = 1$ V and all other terminals grounded [73] |

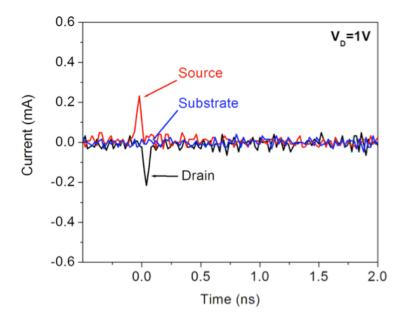

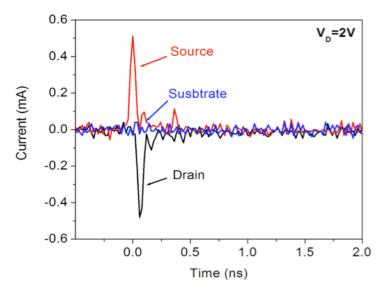

Figure 57: Current transients recorded in the drain (black), in the source (red), and in the well (blue) of an SOI FinFET with saddle contacts. The FinFET has a gate length of 60 nm, a fin width of 20 nm and 10 fins in parallel. The FinFET was irradiated in the OFF state configuration, with  $V_D = 2$  V and all other terminals grounded [73]......90

#### CHAPTER I

## INTRODUCTION

#### 1.1. Thesis objective

After fourteen years of research and investigations by engineers in the university and industry communities, FinFET devices are finally ready to use in products [1-2]. FinFET technologies have been demonstrated to outperform planar technologies for high speed, low power and high performance applications, while maintaining the shrinking trends of microelectronics (beyond 32 nm) for at least the next two to three technology generations. These promising findings were enough for leading chip manufacturers like Intel to announce their plans to mass-produce FinFETs in the near future [3-4]. However, the device response in extreme environments (i.e., space) is still not well understood. Exploring the behavior of FinFETs in such environments is also important for the aerospace and medical industries, where unhardened commercial off the shelf (COTS) electronics are used.

The objective of this work is to explore the transient electrical behavior of FinFET devices in both bulk and SOI technologies in radiation-rich environments through laser and heavy ion testing. A further objective of this work is to contribute to improving the performance of FinFET devices, in particular in harsh environments. Indeed, the new results obtained in this work identify the physical regions in the devices that are most sensitive to radiation effects and how they affect the radiation response. The findings will help

engineers to design new generations of FinFET devices with higher tolerance to radiation effects.

#### 1.2. Introduction

Technology scaling enhances the impact of short channel effects on the electrical behavior of integrated devices and circuits. As a consequence, the gate control over the body in MOSFET devices must be increased. FinFET technology is one of the leading solutions to satisfy the need for excellent control of the gate over the potential in the body. These structures can be mass produced with minor changes to the fabrication processes used for planar technology. Initial radiation effects investigations on FinFETs were focused on total ionizing dose effects [5-8], which resulted in a number of journal and conference publications. Single-event effects (SEEs) in FinFETs, however, are not as well understood. With Intel and other leading manufacturers bringing FinFET technology to the marketplace, investigating and analyzing SEEs in FinFET devices is quickly becoming an important priority. The test structures and state of the art FinFETs investigated in this work were provided by manufacturers working to refine their product for higher SEE tolerance, which illustrates the industry's interest in understanding these effects.

In this work we investigate single-event transient (SET) effects in bulk and SOI Fin-FETs through topside and backside laser and heavy ion irradiations. SETs are voltage spikes that can propagate in circuits and may cause a memory cell to flip its state from 0 to 1 or visa versa. Laser testing is an alternative to ion irradiation to reproduce SEEs in devices and circuits. Later in this chapter, we briefly introduce the FinFET technology after explaining the limits and constraints of planar technology. In the second chapter, we review the basics of SEEs in electronic devices. The fundamentals of the charge generation and charge collection processes are explained in detail. In this chapter we investigate the different mechanisms that have been demonstrated to play key roles in the charge collection in MOSFET systems.

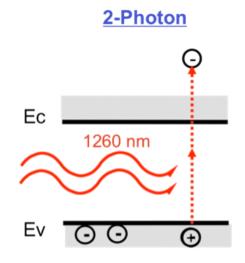

In the third chapter, we explain the experimental techniques used for evaluating Fin-FET devices. Moreover, we describe the tested FinFET device details. We describe the concepts of the single photon absorption (SPA) and two photon absorption (TPA) techniques. We also provide a basic description of the operation of both the ion beam induced charge collection (IBICC) and time resolved ion beam induced charge collection (TRIBICC) techniques. These techniques are used in this work to analyze the transient response of FinFET devices.

In the fourth chapter, we report results from sub-130 nm bulk and SOI FinFET test structures obtained using both SPA and TPA laser testing techniques at the Naval Research Laboratory (NRL). TPA results show that the drain region in bulk FinFET dominates the charge collection response of these structures, masking the intrinsic contribution of the fins. SPA results on bulk and SOI FinFETs demonstrate a significantly higher tolerance of SOI devices to SEEs, thanks to the buried oxide (BOX) layer that reduces their collection volume to the fins.

In the fifth chapter, the IBICC technique is used to investigate the heavy-ion-induced charge collection in sub-70 nm bulk and SOI FinFETs. Like the test structures considered in chapter four, these FinFETs have a sensitive area that maps reasonably well to the drain region. The transient response of the SOI FinFETs is affected by charge motion in the substrate beneath the buried oxide when the substrate is negatively biased.

In the sixth chapter, we investigate the single event response of bulk and SOI Fin-FETs with reduced (more realistic) drain areas. This study is of crucial significance since practical bulk FinFETs have similar drain region design. This chapter also illustrates the impact of this work on today's FinFET technology. We first compare the transient response of FinFETs with conventional drain regions (dumbbell contact) and FinFETs with reduced drain regions (saddle contact). I explain the different mechanisms contributing to charge collection and charge enhancement in bulk and SOI FinFETs with saddle contacts. The bulk vs. SOI comparison demonstrates higher tolerance to SEEs of SOI FinFETs in comparison to their bulk counterparts.

Finally, I conclude in the seventh chapter by discussing the significance and applications of this work.

#### 1.3. Introduction to non-planar technology

#### 1.3.1. *Limits of planar technology*

Intel co-founder Gordon Moore observed that the number of transistors in an integrated circuit roughly doubles every 2-3 years [9]. This observation has been remarkably accurate over the past five decades. In order to keep pace with Moore's law, the MOSFETs' dimensions were reduced by half every 3 years. The channel lengths of the first commercial MOSFETs were greater than 20  $\mu$ m [10]. Currently, semiconductor manufacturers are announcing the production of transistors with gate lengths of 20 nm on a regular basis [3-4]. Transistors with short gate lengths are vulnerable to undesirable short channel effects [10], which present some of the most important limits to planar MOSFET scaling.

#### 1.3.1.1. Short channel effects

Short channel effects refer to modification of ideal electrostatic gate-controlled behavior, introducing two-dimensional effects in the channel region. One of the most obvious manifestations is the threshold voltage reduction when increasing the drain voltage. This decrease in the threshold voltage is the result of the combined effects of: source/drain charge sharing, drain-induced barrier lowering (DIBL), and punch-through [10].

Source/drain charge sharing: In short channel MOSFETs, parts of the drain and source space charge regions contribute to the substrate depletion region (underneath the gate oxide). Fig. 1 illustrates the depletion required at the threshold voltage (V<sub>T</sub>) and the depletion charge provided by drain/source regions in a planar MOSFET transistor [10]. The contributions of the source/drain depletion regions to the channel depletion result in reducing the required gate voltage to deplete this region, decreasing the threshold voltage of the transistor.

Figure 1: Depletion required at the threshold voltage  $(V_T)$  in the channel region and the depletion charge provided by drain/source regions in a planar MOSFET transistor [10].

- Drain induced barrier lowering: Increasing the drain voltage in a short channel MOSFET can significantly modulate the surface potential in the channel region of the transistor. Indeed, the surface potential increase in the channel lowers the source barrier to electron injection into the channel. DIBL reduces the threshold voltage at high drain biases.

- Punch-through: As in the DIBL case, high drain bias lowers the source-substrate barrier in a short channel transistor. However, the punch-through conduction takes place in the silicon bulk. The drain depletion region expands deep in the substrate, where the doping is low, and reaches the source depletion region, creating a parasitic conductive path from source to drain.

The gate oxide thickness is another challenging limit to MOSFET scaling [11]. Transistors with gate oxides (SiO<sub>2</sub>) of thicknesses lower than 2 nm are being manufactured. It has been reported that devices with gate oxides 2 nm thick exhibit leakage current of ~0.1  $A/cm^2$  at 1.2 V [11]. This might not be a threat to general MOSFET applications but it is considered to be problematic for very low power applications [11]. This result raises concerns when extrapolated to the future.

Several techniques can be adopted to circumvent these scaling limits. However, one approach that takes care of most of these constraining factors is modifying the physical structure of MOSFET transistors from planar to 3D technology.

#### 1.3.2.1. FinFET technology

In an unceasing attempt to increase current drive, control short-channel effects, improve the speed and minimize the power dissipation in devices and circuits, MOS transistors have developed from planar single gate MOS devices into three-dimensional devices with multiple common gate regions. Fig. 2 illustrates the physical structure of a FinFET transistor [12].

Figure 2: Physical structure of a FinFET device [12].

Fig. 2 shows that the gate and the poly-silicon wrap around a thin slice of silicon, also known as a 'fin', and the current flows along the top and side surfaces of the fin. The fin's dimensions play a key role in defining the operation of the device. Wider fin structures behave more like planar devices. In narrower fin devices, the additional lateral gates provide excellent control over the potential in the body by the gates. This significantly miti-

gates the short channel effects. Moreover, the lateral gates allow further scaling of the transistor with a relatively thicker gate oxide in comparison to that of a planar structure. This reduces the gate tunneling leakage current and improves the drive current of the FinFET device. Owing to its superior electrostatic scalability and better gate control over the channel [13], FinFET technology is one of the main candidates to continue CMOS scaling below the 22-nm node [3]. In fact, Intel Corporation announced in 2011 that the company is moving to volume production of bulk FinFET-based integrated circuits [14]. Engineers from Intel Corporation announced that an increase in performance of about 37%, versus their own 32 nm planar transistors, could be achieved using bulk FinFETbased chips, with an increase in process cost of only 2 to 3%. This makes bulk FinFETs good candidates for volume production, offering a cost advantage over SOI FinFETs, which require an increase of process cost of almost 10%. The additional fabrication step where the buried oxide layer (BOX) is added to the SOI wafer increases the process cost for SOI FinFETs. The BOX layer in SOI FinFETs isolates the fins from the substrate region.

#### 1.3.2.2. FinFET operation

It is expected that in the future FinFETs may have undoped fins to mitigate random doping fluctuations, which can produce significant device-to-device variations (i.e., in the threshold voltage) [15]. The threshold voltage in undoped FinFETs will be controlled by the gate metal work function. However, until good quality gate metals are available, Fin-FETs with polysilicon and doped fins are being investigated.

Fig. 3 illustrates the energy band diagram in the fin of an n-channel FinFET biased at the threshold voltage. A hard mask is usually built on top of the fin to protect it from the different etching steps. This is why the top oxide is usually not used as a gate. FinFETs with a functional top gate are called tri-gate devices. The process of turning ON a FinFET device is similar to that of a planar device. However, in FinFET devices both lateral gates are turned ON, generating current flow along both the gate/silicon surfaces as shown in Fig. 3.

Figure 3: Energy band diagram in the fin at the threshold voltage of an n-channel FinFET device.

Moreover, thanks to the vertical geometry of FinFETs, their overall gate capacitance is greater than that of planar devices for the same consumed area and with the same gate oxide thickness. Equation (1) expresses the threshold voltage of a FinFET device (cf. Fig. 3). The number 2 in the denominator of the third term in the threshold voltage equation below correspond to the two lateral gates:

$$V_T = V_{FB} + 2\phi_B + \frac{Q_{DEP}}{2C_{OX}} \tag{1}$$

where  $V_{FB}$  is the flat band voltage,  $\Phi_B$  is the silicon bulk potential (kT ln(p/n<sub>i</sub>)),  $Q_{DEP}$  is the depletion (fixed) charge per unit area in the depleted fin, and  $C_{OX}$  is the oxide capacitance per unit area of one gate.

#### 1.3.2.3. FinFET scaling

In the last decade, CMOS technology experienced striking progress toward scaling of planar processes. Increasing short channel effects and leakage current formed formidable obstacles to continue scaling of planar technologies down to 10 nm [16]. Thanks to its quasi-planar architecture and relatively simple fabrication, research laboratories and industries have elected FinFET technology as a possible alternative to planar technologies. Intel is using bulk FinFETs for its 22 nm "Ivy Bridge" processor. Bulk FinFETs have shown better performance than their planar counterparts. However, bulk FinFET performance is still "mid-way" between planar and highly scaled SOI FinFETs. Indeed, due to their higher junction capacitance and lower mobilities due to the well doping, the present generation of bulk FinFETs is less likely to outperform SOI FinFETs for applications that require strong analog performance, for instance [17]. The transient radiation response of bulk FinFETs is still not well understood. In this thesis, we evaluate the transient response of sub-130 nm bulk and SOI FinFETs as well as state of the art bulk FinFETs with different designs. FinFETs on SOI substrates are examined as well and compared to their bulk counterparts.

In the next chapter we review the basics of radiation effects on electronic devices, in particular, single event effects (SEEs).

#### CHAPTER II

# BASICS OF SINGLE EVENT EFFECTS ON ELECTRONIC DEVICES

The proper functioning of electronic equipment in radiation-rich environments may be limited by their vulnerability to single-event effects (SEEs). This can result in erroneous data, system shutdown, or even catastrophic failure.

#### 2.1. Single Event Effects (SEEs)

#### 2.1.1. Definition

An electronic system may stop functioning when a heavy ion passes through a sensitive node. This disturbance of the system is called a single-event effect. These effects can be either destructive or non-destructive. In this thesis we focus on one of the nondestructive single-event effects, the single event transient (SET). SETs are sudden voltage spikes that occur after the passage of a heavy ion through an electronic structure. These spikes can be propagated in a circuit and cause single event upsets (SEUs). SEUs occur in memory cells when a state '1' flips to the state '0' or vice versa.

#### 2.1.2. *History*

Single-event upsets were observed in laboratories in the 1970's [18]. However, the first data relative to in-flight anomaly was reported by Binder in 1975 [18-19]. Four events were recorded during periods of low sun activity over 17 years of operational use of the satellite [19]. It has been demonstrated that cosmic ray interactions can change the state of digital circuits [19]. Critical transistors in JK flip flop circuits were shown to collect enough charge to turn on and/or off after a cosmic ray passes through a sensitive node, changing the cell's state [18-19]. The charge generated by the high-energy cosmic ray charged the emitter-base capacitance of the critical bipolar transistors in this technology to the turn on voltage, modulating the operation of the flip flop circuit and modifying its state.

SEUs were first discovered in dynamic random access memories (RAMs) and charge coupled devices (CCDs) in 1978 [20]. d-RAMs store every bit of data in a separate capacitor where the accumulated charge (~ 1.5 million electrons in 3  $\mu$ m technology d-RAM parts [20-21]) is detected by a sensitive amplifier [22]. CCDs are memory devices where isolated potential wells store charge with typical amounts between 180k and 50k electrons per bit in 3  $\mu$ m technology CCD devices [20-21][23]. RAMs and CCDs exhibited the upset of the stored data after the passage of ionizing radiation through the memory structures [14]. SEUs were caused by alpha particles that emanate from the packaging material surrounding the electronic structures. Packaging materials like glass and ceramic contain trace amounts of radioactive elements like Uranium and Thorium that decay, producing heavily ionizing alpha particles with energies ranging from 3.95 MeV to over 9 MeV [14]. The charge generated by the alpha particles modulates the

charge state of the storing nodes, reversing their states and producing upsets, which are also called soft errors. Unlike hard errors such as those caused by gate oxide break down, soft errors are not permanent and are easily recovered by outside control [24]. The amount of charge that differentiates between the 0 and 1 states is called the "critical charge". It has been demonstrated that the critical charge is one of the dominant factors in determining the soft error rate in devices [14].

Very energetic particles (protons, helium and heavy ions with energies of up to  $10^{19}$ eV [20]) originating from space (cosmic rays, solar wind...) can cross the magnetic field protecting the earth and reach the atmosphere, where secondary particles (charged or/and uncharged) may be generated. These particles (photons, electrons, protons, neutrons, muons and pions [25-26]) can affect electronic systems on the ground. SEUs due to cosmic rays were first reported on earth in 1979 [20]. Dynamic RAMs and CCD circuits were found to be sensitive to high-energy cosmic particles at sea level, with the highest soft fail rates recorded in the CCD devices due to their lower stored charge [20]. A total rate of  $\sim 7$  soft errors per 10<sup>6</sup> hours was obtained in the 64k RAM circuit, with 87% of these events due to the alpha particles. On the other hand, a total rate of  $\sim 600$  soft errors per 10<sup>6</sup> hours was recorded in the 64k CCD devices. Protons and muons may generate charge that is higher than the critical charge of the CCDs through direct ionization, resulting in considerable rates of soft errors in these structures (up to 330 errors per  $10^6$  hours) [20]. A muon is a fundamental or unitary particle like an electron but with a heavier mass ( $\sim 200$  $m_{a}$ ) and a negative charge [27]. Muons are the most ubiquitous charged particles at sea level [28]. Moreover, CCDs may exhibit significant soft error rates (100 per 10<sup>6</sup> hours) due to neutron interactions [20]. Neutrons are uncharged particles that interact with the

nucleus, producing electron-hole pairs through heavy nucleus recoils [20]. The next paragraph will summarize the ion-semiconductor interactions as a function of their mechanisms.

#### 2.1.3. Charge generation

#### 2.1.3.1. Ion/semiconductor interactions

The passage of an energetic particle through a semiconductor material creates electron-hole pairs. The electron-hole pairs are generated via different mechanisms.

- <u>Rutherford or Coulomb scattering</u> relies upon electronic forces. The incident charged particle (protons, ions, or electrons) interacts with free (in the conduction band) and bound electrons in the lattice, producing electron-hole pairs through Coulomb attraction and/or repulsion. Incident protons with energies lower than 100 keV ionize the target atoms, producing free carriers along its track.

- When the incident particles are more energetic (protons, neutrons, and electrons with energies higher than 10 MeV [29], 6 MeV [30] and 150 keV [31] respectively), <u>ion-nuclei</u> interactions dominate. Energetic protons and neutrons are more likely to interact with an atomic nucleus since its volume is 8000 times that of an electron. An elastic collision can displace an atom from its original position in the lattice. The recoiled atom acts as a heavy ion in the lattice, producing electron-hole pairs along its track through ionization. The relocated atom's vacancy modifies the local lattice potential, generating displacement damage [31]. The energy received by the displaced atom can also be transferred to the lattice in the form of phonons (heat).

Spallation is an inelastic nuclear reaction that takes place when a high-energy (≥ 50 MeV) incident particle (proton, neutron...) interacts with the nucleus of the target atom [32]. The spallation reaction is inelastic since the incident particle loses some of its energy to the collision. The incident particle's energy needs to exceed the interaction energy of the nucleons in the atomic nucleus target so that the fragmentation of this later is possible [32]. The nucleus ejects secondary particles that ionize neighboring atoms, producing electron-hole pairs.

#### 2.1.3.2. Charge generation

In general, the incident particle loses energy through Coulomb scattering. The rate of the transferred energy to the material is often called linear energy transfer (LET) [24]:

$$LET = \frac{1}{\rho} \frac{dE}{dx}, MeV \, cm^2 / mg \tag{1}$$

where  $\rho$  is the material density. Knowing the density of the target material, the amount of charge created along the path is calculated using the equation above when the LET is constant. The incident particle eventually loses all of its energy to the target material when the material thickness is larger than the penetration depth of the incident ion. The energy loss per distance is maximal at the Bragg peak [33]. This characteristic is often used in medicine to locate the exact position in the body that will receive the maximum amount of deposited energy for disease treatments. The distance travelled by the incident ion is called the range of the ion. It depends on the energy, the atomic number of the ion, and the nature of the target material.

#### 2.1.3.3. <u>Electron-hole recombination</u>

An important mechanism takes place right after the carriers' generation process: electron-hole recombination, which is also called "initial recombination" at these short times [34]. Models for two limiting cases have analytically quantified the recombination process: when the electron/hole pairs are close together (columnar model [35]) and when they are far apart (geminate model [36]). The distance distinguishing between the two cases is the thermalization radius. This distance corresponds to the space between an electron-hole pair after generation once this pair reaches thermal equilibrium [37][38]. In the columnar model, charge is distributed along the incident ion's path, forming a column or a cylinder. This charge is highly dense, so that recombination between electrons and holes inside the column is possible [34]. On the other hand, the distance separating the generated electron-hole pair in the geminate model is larger than the thermalization distance in silicon. Recombination between the generated electron and hole of the same pair dominates [34] [38]. Recombination rate in the geminate model is much smaller than that in the columnar model. The charge profile along the incident ion's track defines the most convenient recombination model to be used. The charge profile depends on the nature and the energy of the incident particle [38].

#### 2.1.4. Charge collection

Most of the generated electron-hole pairs in a bulk semiconductor region tend to recombine in the absence of an electric field [24-38]. However, when this charge is deposited in or in the neighborhood of a p-n junction, the charge is collected in the depletion region of the p-n junction, producing a measurable transient photocurrent [24]. The charge collection in IC junctions takes place via several mechanisms that will be explained in detail in the following paragraphs.

Fig. 4 shows a typical time-dependent current at a struck p-n junction. The integral of the illustrated pulse represents the charge collected ( $Q_{coll}$ ) in the junction. The figure shows that the rise and the fall times are controlled by different charge collection mechanisms. The drift and the funnel mechanisms govern the fast component of the illustrated transient, which lasts up to a few hundred picoseconds. The drift and funnel mechanisms are explained in more detail in the next sections. The slow component or the tail of the transient is a result of the carriers collected from outside the depletion region of the p-n junction (via diffusion).

Figure 4: Shape of a representative single event pulse measured at a struck p-n junction [24].

Fig. 4 summarizes the basic mechanisms governing charge collection in a p-n junction. However, additional processes affect the charge collection, depending on the type of the device and the nature of the incident particle. For instance, the parasitic bipolar npn (or pnp) structure in SOI technologies, which has been demonstrated to play a key role in enhancing the collected charge in these structures, is explained later in this section [39].

#### 2.1.4.1. Drift collection

In the presence of an electric field E, the generated electrons and holes due to the incident particle move in opposite directions.

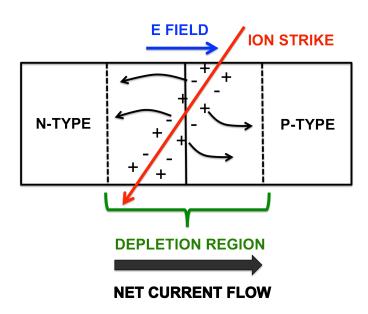

Figure 5: Charge collection in the depletion region in a p-n junction [24].

Fig. 5 shows the depletion region in a reverse-biased p-n junction after the passage of an ion. Electrons move toward the n-type region (positively biased) and holes proceed to the p-type region (negatively biased). The charge flow leads to photocurrent generation or a current pulse that can be measured at the diode terminals. Since the carrier's motion is controlled by an electric field, this mechanism is called drift collection.

#### 2.1.4.2. Funneling

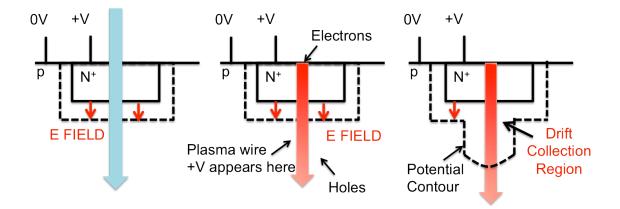

The generated carrier track can distort the original depletion region in a reverse biased p-n junction [24] [40-41]. In fact, the created carrier track can temporarily screen the depletion region. This stretches the resistance along the track, extending the voltage drop outside the original depletion region as shown in Fig. 6. This results in carrier collection outside the depletion region, which increases the amount of collected charge in the p-n diode.

Figure 6: The figure shows the progress of funneling from the plasma track creation (on the left) to the funnel build up (on the right) [24].

While drift collection takes a few picoseconds, the funneling process takes a few hundred picoseconds to proceed [24].

#### 2.1.4.3. Diffusion collection

Carriers that are generated in the substrate, close to the depletion region or the funnel (distorted depletion region), can diffuse and get collected in the biased (positively or negatively) region of the p-n junction. The current that results from this process occurs at a later time compared to the field-assisted collection process discussed above. In general, the contribution of diffusion to the charge collection process is observed as a tail in the current pulse. This tail can extend over a few nanoseconds [24]. In the late seventies (1979) charge diffusion was assumed to be the dominant soft failure mechanism in devices [42].

#### 2.1.4.4. Bipolar amplification

Bipolar amplification is an inherent characteristic of SOI devices [43]. It is also a direct consequence of the floating body effects in SOI structures. The parasitic npn transistor in an n-channel partially depleted SOI MOSFET (or pnp transistor in a p-channel PD SOI MOSFET) can turn on after the passage of a heavy ion [39][44-45]. While the generated minority electrons quickly leave the body [39], the majority carriers (holes) are confined in the body [39]. The holes that escape recombination in the body of an n-channel SOI device forward bias the source/body junction, triggering the injection of electrons from the source to the body, where they are collected by the drain terminal. This is called the bipolar mechanism. This effect can drastically amplify the collected charge, dominating the SEE response of partially-depleted SOI technologies [39][46]. Fully depleted SOI technologies have been demonstrated to be vulnerable to bipolar amplification as well [47]. However the charge amplification in these latter technologies is less significant than that in their partially-depleted counterparts [47] thanks to their mitigated floating-body effects assured by the higher control of the gate over the potential in the body. The bipolar phenomenon is mitigated in highly-doped silicon films, which decreases the lifetime and the mobility of carriers in the silicon. Bulk devices have been demonstrated to be subject to bipolar amplification as well [43]. This amplification effect is enhanced for low-doped substrate bulk devices.

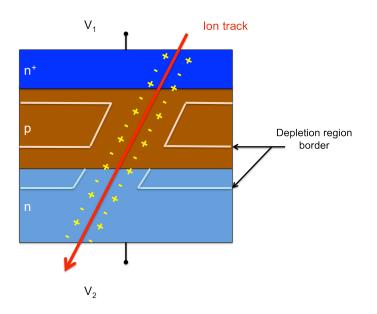

#### 2.1.4.5. Shunt collection

Plotted in Fig. 7 is a schematic diagram of a multilayer structure exhibiting a distinctive phenomenon that is becoming critically important for modern dense integrated devices [24]. The ion track in Fig. 7 is penetrating two proximate junctions. Thanks to its high carrier density, the ion track plasma can form a conductive path between the two n regions in Fig. 7. The conductive path acts as a wire carrying charge that was generated due to the heavy ion and additional charge that may originate outside the npn structure as well [24]. This collection mechanism is called the "shunt" effect [24][48-49].

Figure 7: Diagram of a multilayer structure exhibiting shunt effect [24][48].

The results presented in this thesis demonstrate that shunt collection plays a key role in explaining the charge collection mechanism in bulk and SOI FinFETs.

#### 2.2. Device response to single event effects (SEEs)

The critical dimensions of MOS field effect transistors have dramatically decreased since the 70's [50]. The transistor's gate length has dropped from 10  $\mu$ m in the 1970's [50] to 22 nm [3-4] for current technologies. The decrease of device dimensions enhances the IC's vulnerability to single-event effects. In the first part of this section, we review SEEs on planar bulk and SOI MOSFETs. The second part reviews the published data related to SEEs on FinFETs.

#### 2.2.1. Single-Event Effects in Planar MOSFETs

#### 2.2.1.1. Bulk Planar MOSFETs

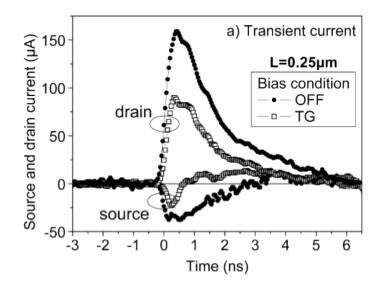

Illustrated in Fig. 8 are the recorded current transients in the drain and the source terminals of a bulk planar transistor fabricated in 0.25  $\mu$ m technology irradiated with a 35 MeV Cl ion beam. The sample is biased in either the off state (V<sub>D</sub> = 1 V) or the transmission gate bias (V<sub>D</sub> = V<sub>S</sub> = 1 V) configuration. The shape of the drain transient in Fig. 8 is comparable to that shown in Fig. 4, with two main charge collection mechanisms: drift collection and diffusion collection.

Figure 8: Drain and source transient currents induced by a 35 MeV Cl ion beam in a 0.25  $\mu$ m bulk planar NMOS transistor. The transistor is biased in the OFF state (V<sub>D</sub>=1V) and in the transmission gate configurations [43].

The drain transients in Fig. 8 exhibit long tails (~ 4 ns), highlighting the diffusion phenomenon of carriers from the substrate, which dominates the charge collection process in these bulk planar devices. Fig. 8 shows that the bulk samples exhibit negative current transients in the source terminal for both OFF state and transmission gate bias configurations, with the largest transients obtained for the OFF state configuration. This suggests a conduction path between the drain and the source terminals [43]. Charge collection in bulk devices may be affected by minor bipolar amplification in low-doped substrate bulk structures. After the passage of a heavy ion through the sample, the source-substrate junction is forward biased due to the extra holes in the body. Electrons are injected from the source to the body and are collected by the drain due to the positive drain voltage. The bipolar amplification [43] is more significant in the off-state bias configuration as illustrated in Fig. 8, where the largest negative source transients are obtained. The

bipolar effect is less significant in the TG bias configuration since the source, like the drain, is collecting electrons due to the applied positive bias ( $V_s = 1 \text{ V}$ ).

Figure 9: a). Transient drain currents induced by pulsed laser irradiation in a  $0.25 \,\mu m$  NMOS transistor. The transistor is OFF biased and the drain voltage is: 1.8 V, 1 V, 0.6 V, 0.2 V. b). Transient drain currents induced by pulsed laser irradiation in a 50 nm bulk NMOS transistors. The transistor is OFF biased with a drain voltage of 1V [50].

Illustrated in Fig. 9 are the drain current transients recorded in irradiated 0.25  $\mu$ m and 50 nm bulk NMOS transistors. Both samples were irradiated with comparable laser energies (32 pJ and 38 pJ). In contrary to large bulk NMOSFETs, current transients recorded in smaller devices have smaller pulse amplitudes, widths, and tails [50]. It has been shown that scaled devices can be more prone to bipolar amplification than their large (1  $\mu$ m) counterparts [43]. However, the sophisticated doping profiles used in some of the newer technologies appear to reduce this amplification effect significantly [50]. Moreover, the heavy well doping of the scaled devices results in less diffusion collection, as shown in Fig. 9, due to the reduced lifetime of the generated carriers. On the other hand, higher rates of single and multiple bit upsets were observed in some highly integrated technologies, which suggests a need to review the diffusion contribution to charge collec-

tion in highly scaled technologies [51-52]. In fact, higher doping profiles induce more complex charge diffusion mechanisms with respect to proximate sensitive regions [51-52].

# 2.2.1.2. SOI Planar MOSFETs

In an SOI MOSFET, the thickness of the silicon film determines the physics of the device operation. When the silicon film thickness  $(t_{si})$  in the channel is larger than the maximum depletion width  $(x_{dmax})$ , where  $x_{dmax}$  is expressed by equation (2), the device is considered to be partially-depleted (PD) [53].

$$x_{dmax} = \sqrt{\frac{4\varepsilon_{si}\phi_F}{qN_a}},\tag{2}$$

where  $\varepsilon_{si}$  is the silicon permittivity,  $\phi_F$  is the Fermi potential or silicon bulk potential,  $N_a$  is the silicon film doping per unit volume and q is the elementary charge [53].

On the other hand, When  $t_{si}$  is lower than  $x_{dmax}$ , the silicon film is completely depleted and the device is considered to be fully depleted (FD). The fully-depleted technology mitigates the floating body effects usually observed in partially-depleted SOI technologies.

The buried oxide in SOI transistors isolates the active region of the device from the substrate, reducing the collection volume. This significantly decreases SOI devices' sensitivity to single event effects in comparison to their bulk counterparts. Illustrated in Fig. 10 are current transients recorded in PD SOI MOSFETs fabricated in a 0.25  $\mu$ m technology.

Figure 10: Drain current transients induced by a pulsed laser irradiation in a  $0.25 \,\mu$ m technology partially depleted SOI transistor. The device is OFF biased. The drain is biased at different voltages: 1.8, 1.0, 0.6 and 0.2 V [50]. This device was processed with a 400 nm BOX thickness and 100 nm silicon film thickness.

The current transients in Fig. 10 exhibit significantly shorter tails than the ones observed in bulk NMOSFETs with the same gate length, as shown in Fig. 9a. This results in notably smaller amounts of charge collected in SOI devices than their bulk counterparts.

Fig. 11 illustrates the current transients obtained in a FD SOI device with a 50 nm gate length and 11 nm silicon film thickness [50]. The current transient is very short, with a FWHM of 35 ps and a width of only 66 ps. The absence of the tail in the 50 nm FD SOI device confirms the minimal contribution of floating body effects previously observed in partially depleted device (cf. Fig. 10). The small dimensions of this device reduce the to-tal collected charge (~ 200 fC) in comparison to bulk devices.

Figure 11: Drain current transients recorded in a 50 nm gate length FD SOI MOSFET irradiated with a pulsed laser energy of 80 pJ [50]. This device is processed with an 11 nm silicon film and 100 nm BOX thickness.

It is noteworthy that partially-depleted SOI MOSFETs with gate lengths of 50 nm have been shown to collect greater amounts of charge than similar devices with 0.25  $\mu$ m gate lengths [50] due to bipolar amplification, enhanced by floating body effects. It has been reported that OFF biased partially depleted SOI NMOSFETs can collect as much as 40 times more charge than that deposited by the incident ion [43].

# 2.2.1.3. <u>Summary</u>

Bulk planar devices are more sensitive to SEEs than their SOI counterparts due to their bigger collection volume. Diffusion-related charge collection in bulk planar devices results in long tails in the transients. The high doping in the wells of scaled planar bulk devices significantly reduces the amount of collected charge. Smaller transients with short tails are recorded in SOI devices. Scaled FD SOI devices are less sensitive to SEEs than their bulk counterparts, with no diffusion signatures in the transients, thanks to their small collection volumes. Partially depleted SOI NMOSFETs can be very sensitive to bipolar effects when the doping is not optimized.

# 2.2.2. Single-Event Effects in FinFETs

FinFET technology is relatively new. A fair amount of work related to total ionizing dose (TID) effects on FinFETs devices has been done. SOI FinFETs with wide fin widths behave like planar devices [6]. The vertical coupling between the front and the back gates overpowers the lateral gate coupling [5]. Wide fin devices can be very vulnerable to the effects of trapped charge in the BOX [5], which can induce effects that are very similar to those usually observed in planar SOI devices like the "high state current" phenomenon [5][54]. On the other hand, narrow fin SOI devices have shown higher tolerance to TID effects thanks to their excellent control of the lateral gate over the electrostatic potential in the body [5-7]. The isolation oxide in bulk FinFETs appears to significantly affect the TID response of some narrow fin bulk FinFETs [8]. The trapped charge in the shallow trench isolation (STI) oxides modulates the potential in the body, making narrow-fin Fin-FETs more sensitive to total dose effects [8]. Very limited work related to the transient response of FinFET devices has been reported.

Plotted in Fig. 12 are drain current transients in a planar FD SOI MOSFET (black curve) and in a non-planar SOI FinFET device (red curve). The planar FD SOI device has a gate length of 50 nm and a silicon thickness of 8 nm [55]. The gamma shaped SOI Fin-FET has a gate length of 60 nm, a fin width of 50 nm and a 25 nm tall fin [55]. The BOX layer in both technologies is 100 nm. In contrast to the fast transients recorded in the pla-

nar FD SOI devices, slower transients with longer tails are obtained in the FinFET [55]. This results in greater amount of collected charge in the FinFET.

Figure 12: Transient drain current induced by a pulsed laser irradiation in a planar FD SOI MOSFET with a gate length of 50 nm and a floating body and in a non-planar FinFET device with a gate length of 60 nm. The silicon film thickness is: 8 nm and 25 in of the FD SOI devices and the non-planar devices, respectively [55].

It has been demonstrated that the obtained transient response is not intrinsic to the Fin-FET geometry, but is due to characteristics of these samples [55]. The drain-to-body access length in the FinFETs induces the slow shape of the obtained transients [55]. The generated carriers in the body take more time to reach the drain terminal in the FinFETs, resulting in the long tails. In fact, with the same values of drain-to-body access distance, the transients obtained in the FinFETs and the FD SOI devices are very similar [55]. Fin-FETs used in previous work were test structures fabricated in technologies that are in the process of being improved in order to reach the level of development of planar FD technologies. New results of the transient response of state-of-the-art bulk and SOI FinFETs are presented and investigated in detail in this thesis.

### CHAPTER III

# DEVICE AND EXPERIMENTAL DETAILS

In order to study the SEE response of electronic devices, samples are irradiated in several accelerator facilities equipped with different beams. Depending on the structure and on the sensitivity of the studied structure, samples are evaluated using ion and laser beams with different energies. These testing facilities allow device behavior in space to be predicted in reduced times compared to actual applications. In this chapter we present the details of the testing facilities and the measurement techniques, along with the details about the FinFETs used in this work.

3.1. Measurement techniques

#### 3.1.1. Laser source, Naval Research Laboratory (NRL)

Laser testing is frequently used as a surrogate test for ion irradiation to simulate single event effects (SEEs) in microelectronic devices. Laser testing provides the spatial information and the temporal details of the charge collected, which are necessary to identify the sensitive nodes and the mechanisms involved in charge collection [56]. Moreover, laser facilities are less expensive and easy to access in comparison to their ion beam counterparts. This makes laser testing a good approach for SEE investigation.

#### 3.1.1.1. <u>Single photon absorption (SPA)</u>

The single-photon absorption (SPA) pulsed laser technique originates from the optical above band gap excitation of carriers in a semiconductor material.

Figure 13: Energy band diagram for silicon illustrating the single photon absorption. hv is the energy of the incident photon.

Fig. 13 shows the process of exciting an electron from the valence band into the conduction band in silicon. For example, a 1.97 eV photon excites an electron, which jumps to the conduction band leaving a hole behind in the valence band [55]. The energy of 1.97 eV corresponds to the wavelength of 630 nm used at NRL. The energy is calculated from the equation:

$$E = \frac{hc}{\lambda},$$

(3)

where h is Planck's constant,  $\lambda$  is the photon wavelength (630 nm at NRL) and c is the speed of light (3 × 10<sup>8</sup> m.s<sup>-1</sup>) [57].

The SPA technique injects a well-known amount of charge in a precise location (x, y) at a specific time. Each photon is absorbed to create an electron-hole pair, hence the sin-

gle photon absorption nomenclature. It is also called linear regime absorption. Carrier generation in the SPA process is primarily governed by Beer's law [58]:

$$I(z) = I_0 \exp(-\alpha z) \tag{4}$$

where  $I_0$  is the intensity of the incident laser beam,  $\alpha$  is the linear absorption coefficient of the material target, and z is the depth of the laser penetration. The equation describes an exponential reduction in the laser intensity as it propagates into the target material (device).

Figure 14: Absorption coefficient as a function of the wavelength for silicon [58].

Fig. 14 illustrates the absorption coefficient as a function of the laser wavelength for silicon. For a 630 nm wavelength, the silicon absorption coefficient is ~  $4 \times 10^3$  cm<sup>-1</sup> [59]. The absorption coefficient of the laser through a material is equal to the reciprocal of the optical penetration ( $\alpha = 1/e$ , where e is the penetration depth) [60]. Light with a wave-

length of 630 nm can penetrate a distance of ~ 3  $\mu$ m in the silicon. The penetration depth value can be varied (up to 10  $\mu$ m ranges have been successfully achieved in silicon [58]) by choosing the wavelength of the laser. The SPA laser beam is typically focused at the surface of the device under test.

Also, in contrast to ions, optical pulses cannot pass through metal layers. This can be a limit to laser techniques for SEE applications, since the amount of generated charge is directly related to the amount of incident light. The metal layers on top of the sensitive nodes can modulate the amount of charge collected by the device. The topside SPA technique is useful for structures that are not covered by metal. However regions with metal overlayers, in particular advanced structures with multiple metal layers, can still be investigated using the back side two photon absorption technique as explained in the next paragraph.