#### RICE UNIVERSITY

#### Performance Analysis for Parallel Programs

From Multicore to Petascale

by

#### Nathan Russell Tallent

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

#### Doctor of Philosophy

APPROVED, THESIS COMMITTEE:

John Mellor-Crummey, Chair

Professor of Computer Science and Electrical & Computer Engineering

Vivek Sarkar

E.D. Butcher Professor of Computer Science and Electrical & Computer Engineering

Peter Varman

Professor of Electrical & Computer Engineering and Computer Science

Robert Fowler

Chief Domain Scientist, High Performance Computing, Renaissance Computing Institute

HOUSTON, TEXAS

**MARCH 2010**

UMI Number: 3421196

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 3421196

Copyright 2010 by ProQuest LLC.

All rights reserved. This edition of the work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### Abstract

# Performance Analysis for Parallel Programs From Multicore to Petascale

by

#### Nathan Russell Tallent

Cutting-edge science and engineering applications require petascale computing. Petascale computing platforms are characterized by both extreme parallelism (systems of hundreds of thousands to millions of cores) and hybrid parallelism (nodes with multicore chips). Consequently, to effectively use petascale resources, applications must exploit concurrency at both the node and system level — a difficult problem. The challenge of developing scalable petascale applications is only partially aided by existing languages and compilers. As a result, manual performance tuning is often necessary to identify and resolve poor parallel and serial efficiency.

Our thesis is that it is possible to achieve unique, accurate, and actionable insight into the performance of fully optimized parallel programs by measuring them with asynchronous-sampling-based call path profiles; attributing the resulting binary-level measurements to source code structure; analyzing measurements on-the-fly and postmortem to highlight performance inefficiencies; and presenting the resulting context-sensitive metrics in three complementary views. To support this thesis, we have developed several techniques for identifying performance problems in fully optimized serial, multithreaded and petascale programs. First, we describe how to attribute very precise (instruction-level) measurements to source-level static and dynamic contexts in fully optimized applications — all for an average run-time overhead of a few percent. We then generalize this work with the development of logical call path

profiling and apply it to work-stealing-based applications. Second, we describe techniques for pinpointing and quantifying parallel inefficiencies such as parallel idleness, parallel overhead and lock contention in multithreaded executions. Third, we show how to diagnose scalability bottlenecks in petascale applications by scaling our our measurement, analysis and presentation tools to support large-scale executions. Finally, we provide a coherent framework for these techniques by sketching a unique and comprehensive performance analysis methodology. This work forms the basis of Rice University's HPCTOOLKIT performance tools.

#### Acknowledgments

This dissertation represents more than just my past few years of Computer Science graduate study. Seemingly by accident, I became involved in the early stages of the HPCToolkit performance tools project (née HPCView), inaugurated by John Mellor-Crummey. Consequently, before beginning any work toward this dissertation, I had helped build most of what became the proto HPCToolkit.

Nevertheless, I must highlight this dissertation's profound debt to others. The most generous share of credit goes to my advisor, John Mellor-Crummey, whose guidance and insight inform and infuse this work. I must also acknowledge several additional collaborators (in alphabetical order):

- Laksono Adhianto, who is the primary implementer of HPCTOOLKIT's presentation tool, hpcviewer.

- Mike Fagan, who contributed to Chapter 3's on-the-fly binary analysis for unwinding call stacks and whose continual questions uncover weaknesses in our thinking.

- Mark Krentel, whose efforts and commitment to correctness have vastly improved HPCTOOLKIT's ability to dynamically and statically monitor processes and threads.

- Allan Porterfield, who helped develop Chapter 6's blame shifting.

Additionally, I am grateful to (in chapter order):

- Chapter 3: Mark Charney and Robert Cohn of Intel who assisted with XED2 [38].

- Chapter 6: Robert Fowler for focusing our attention on MADNESS; Robert Harrison for helping us with his MADNESS code; and William Scherer for

reminding us of Bacon's prior work on dual-representation locks and pointing out the similarity to STM contention managers.

Chapter 7: Anshu Dubey and Chris Daley of the FLASH team; and Peter Lichtner, Glenn Hammond and other members of the PFLOTRAN team. Both teams graciously provided us with a copy of their respective code, configuration advice, and a test problem of interest.

Finally, I would like to acknowledge Robert Fowler, who was deeply involved with HPCTOOLKIT while at Rice; Gabriel Marin, who was part of the original HPC-TOOLKIT team; Nathan Froyd, who worked on an early version of what is now HPC-TOOLKIT's measurement tool; and Cristian Coarfa, who first explored the scalability analysis technique used in Chapter 7.

\* \* \*

Development of the HPCTOOLKIT performance tools would not have been possible without without

- support from the Department of Energy's Office of Science under cooperative agreements DE-FC02-07ER25800 and DE-FC02-06ER25762;

- equipment purchased in part with funds from NSF Grant CNS-0421109;

- resources at the Argonne Leadership Computing Facility at Argonne National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under contract DE-AC02-06CH11357;

- resources at the National Center for Computational Sciences at Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S.

Department of Energy under Contract No. DE-AC05-00OR22725.

\* \* \*

While academic supervision and financial support are necessary for dissertation research, they are not sufficient. To my parents, who lived like sojourners for their children; and to my grandfather Jack, who wanted to see this day: this dissertation is dedicated to you. To my wife, two sons and baby: we let the wind sweep away the world's wisdom and, despite a shoestring budget and some competition between midnight baby sitting and midnight paper writing, have been the happier for it. And finally, would science be possible without a starting point?

For all knowledge proceeds from faith of whatever kind. You lean on God, you proceed from your own ego, or you hold fast to your ideal. The person who does not believe does not exist. At the very least, one who had nothing standing immediately firm before him could not find a point for his thinking to even begin. And how could someone whose thinking lacked a starting point ever investigate something *scientifically*?

Abraham Kuyper, October 20, 1880. [24, p. 486]

### Contents

| 1 | Intr              | roduction                                                   |          |

|---|-------------------|-------------------------------------------------------------|----------|

| 2 | AN                | Methodology for Performance Analysis                        |          |

|   | 2.1               | Introduction                                                |          |

|   | 2.2               | Principles of Performance Analysis                          | 1        |

|   | 2.3               | From Principles to Practical Methods                        | 1        |

|   |                   | 2.3.1 Measurement                                           | 1        |

|   |                   | 2.3.2 Attribution                                           | 2        |

|   |                   | 2.3.3 Analysis                                              | 2        |

|   |                   | 2.3.4 Presentation                                          | 2        |

|   | 2.4               | Related Work                                                | 3        |

|   | $\frac{2.4}{2.5}$ | Discussion                                                  | 3        |

|   | 2.0               | Discussion                                                  | J        |

| 3 | Mea               | asurement & Attribution: Fully Optimized Applications       | 3        |

|   | 3.1               | Introduction                                                | 3        |

|   | 3.2               | Binary Analysis for Call Path Profiling                     | 4        |

|   |                   | 3.2.1 Inferring Procedure Bounds                            | 4        |

|   |                   | 3.2.2 Computing Unwind Recipes                              | 5        |

|   |                   | 3.2.3 Evaluation                                            | 5        |

|   | 3.3               | Binary Analysis for Source-Level Attribution                | 6        |

|   |                   | 3.3.1 Recovering the Procedure Hierarchy                    | 6        |

|   |                   | 3.3.2 Recovering Alien Contexts                             | 6        |

|   |                   | 3.3.3 Recovering Loop Nests                                 | 6        |

|   |                   | 3.3.4 Normalization                                         | 7        |

|   |                   | 3.3.5 Summary                                               | 7        |

|   | 3.4               | Putting It All Together                                     | 7        |

|   |                   | 3.4.1 MOAB                                                  | 7        |

|   |                   | 3.4.2 S3D                                                   | 7        |

|   | 3.5               | Related Work                                                | 7        |

|   | 3.6               | Discussion                                                  | 7        |

| 4 | ъл.               | announced to Attail action. I amine 1 Call Dath Description | S        |

| 4 |                   | asurement & Attribution: Logical Call Path Profiling        | <b>8</b> |

|   | 4.1               | Introduction                                                |          |

|   | 4.2               | The Challenges of Work Stealing                             | 8        |

|   | 4.3               | Logical Call Path Profiles                                  | 8        |

|   |                   | 4.3.1 Logical Call Paths                                    | 8        |

|   |                   | 432 Representing Logical Call Path Profiles                 | O        |

|   | 4.4 | Obtaining Logical Call Path Profiles                       | 93   |

|---|-----|------------------------------------------------------------|------|

|   |     | 4.4.1 Logical Stack Unwinding                              | 94   |

|   |     | 4.4.2 Thread Creation Contexts                             | 95   |

|   |     | 4.4.3 An API for Logical Unwinding                         | 95   |

|   | 4.5 | Logical Call Path Profiles of Cilk Executions              | 98   |

|   | 4.6 | Related Work                                               | 100  |

|   | 4.7 | Discussion                                                 | 101  |

| 5 | Ana | ysis of Multithreaded Executions: Work Stealing 1          | .03  |

|   | 5.1 |                                                            | 103  |

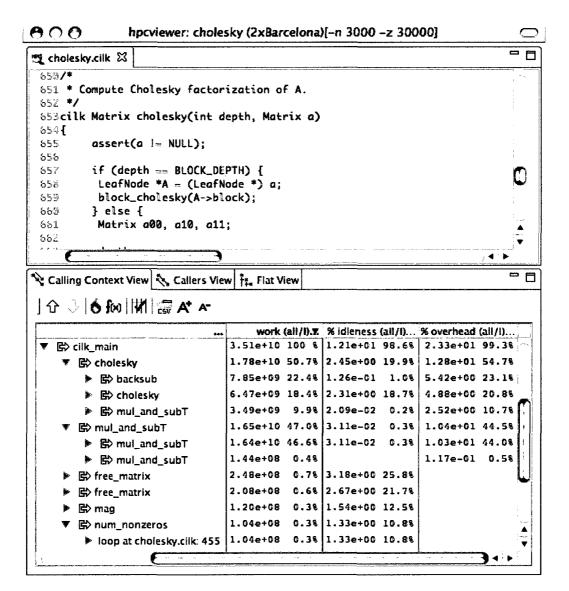

|   | 5.2 | Pinpointing Parallel Bottlenecks                           | 105  |

|   |     | 5.2.1 Quantifying Insufficient Parallelism                 | 105  |

|   |     | 5.2.2 Quantifying Parallelization Overhead                 | 108  |

|   |     | 5.2.3 Analyzing Efficiency                                 | 110  |

|   | 5.3 | Measurement and Analysis of Cilk Executions                | 111  |

|   |     | 5.3.1 Parallel Work and Idleness                           | 112  |

|   |     | 5.3.2 Parallel Overhead                                    | 112  |

|   |     | 5.3.3 Case Study                                           | 115  |

|   | 5.4 | Related Work                                               | l 19 |

|   | 5.5 | Discussion                                                 | 122  |

| 6 | Ana | ysis of Multithreaded Executions: Lock Contention 1        | 23   |

|   | 6.1 |                                                            | 123  |

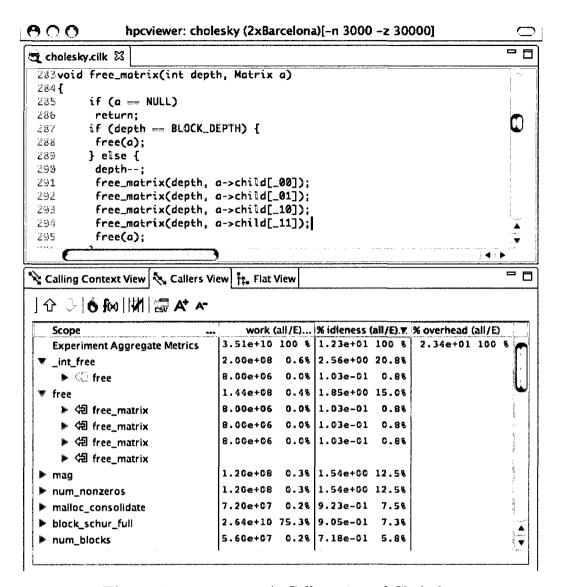

|   | 6.2 | Attributing Idleness to its Calling Context                | 125  |

|   |     | 6.2.1 A Straightforward Strategy                           | 125  |

|   |     |                                                            | 127  |

|   |     | 6.2.3 Evaluation                                           | 127  |

|   | 6.3 | Blaming Idleness on Lock-holders                           | 129  |

|   |     |                                                            | 129  |

|   |     | 6.3.2 Making It Practical                                  | 131  |

|   |     | 6.3.3 Evaluation                                           | 133  |

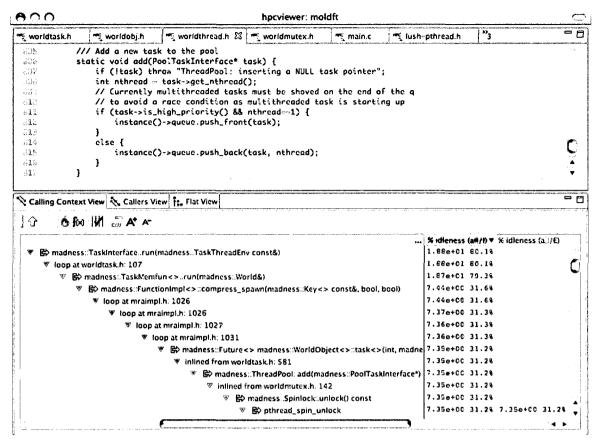

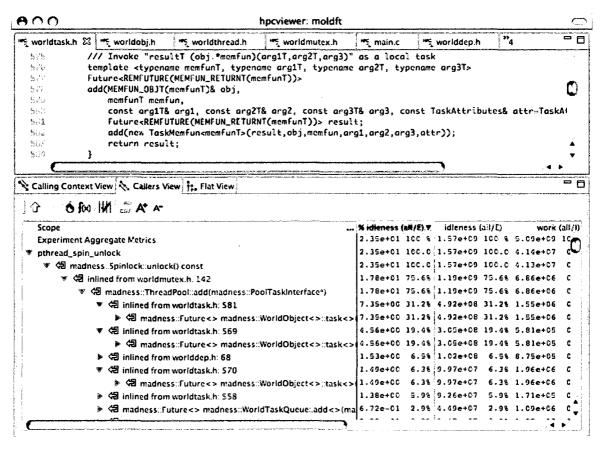

|   | 6.4 | Communicating Blame Directly to Lock-holders               | 134  |

|   |     | 6.4.1 Blame Shifting: A Distributed and Precise Strategy 1 | 134  |

|   |     | 6.4.2 Blame Shifting in Action                             | 136  |

|   |     | 6.4.3 Dual-representation Locks                            | .39  |

|   |     | 6.4.4 Blocking (Sleep-waiting)                             | 45   |

|   |     | 6.4.5 Hints for Developers                                 | 46   |

|   | 6.5 |                                                            | 47   |

|   |     | 6.5.1 MADNESS                                              | 47   |

|   |     | 6.5.2 UTS                                                  | .53  |

|   |     | 6.5.3 SSCA #2                                              | .54  |

|   | 6.6 | Related Work                                               | .54  |

|   | 6.7 | Discussion                                                 | .57  |

| 7            |       | alysis & Presentation of Petascale Executions              | 160               |

|--------------|-------|------------------------------------------------------------|-------------------|

|              | 7.1   | Introduction                                               | 160               |

|              | 7.2   | Scalable Measurement, Analysis and Presentation            | 166               |

|              |       | 7.2.1 Pinpointing Scaling Losses Using Call Path Profiling | 166               |

|              |       | 7.2.2 Analyzing & Presenting Large-Scale Executions        | 169               |

|              |       | 7.2.3 Scalably Computing Metrics                           | 171               |

|              |       | 7.2.4 Scalably Presenting Call Path Profiles               | 177               |

|              | 7.3   | Application Studies                                        | 194               |

|              |       | 7.3.1 PFLOTRAN                                             | 196               |

|              |       | 7.3.2 FLASH                                                | 209               |

|              |       | 7.3.3 MILC                                                 | 215               |

|              | 7.4   | Related Work                                               | 219               |

|              | 7.5   | Discussion                                                 | 221               |

| 8            | Con   | nclusions                                                  | 224               |

| Aı           | ppen  | dices                                                      | 234               |

| A            | The   | eory of Sampling-Based Measurement                         | 234               |

|              |       | A Sampling-based Measurement Strategy                      | 235               |

|              | 11.1  | A.1.1 Instruction-based sampling                           | 237               |

|              |       | A.1.2 Event-based sampling                                 | 238               |

|              |       | A.1.3 Practical considerations                             | 239               |

|              | A.2   |                                                            | $\frac{233}{241}$ |

|              | Π.Δ   | A.2.1 Error bounds for $\hat{Y}_c$                         | 241 $242$         |

|              |       | A.2.1 Error bounds for $Y_c$                               | 244               |

|              |       | ů ů                                                        | $\frac{244}{246}$ |

|              |       | A.2.3 Choosing sampling periods                            | 240               |

| $\mathbf{B}$ | Effic | ciently Representing Logical CCTs                          | <b>249</b>        |

|              | B.1   | Terminology                                                | 250               |

|              | B.2   | Sharing Within Bichords                                    | 251               |

|              | B.3   | Implementation                                             | 253               |

| $\mathbf{C}$ | Defi  | initions of Atomic Primitives                              | 256               |

# List of Figures

| 2.1          | Overview of HPCToolkit tool's workflow                                                      | 16         |

|--------------|---------------------------------------------------------------------------------------------|------------|

| 2.2          | An asynchronous-sampling-based call path profiler                                           | 20         |

| 2.3          | hpcviewer's Calling Context view of scaling losses (cycles)                                 | 26         |

| 2.4          | hpcviewer's Callers view of scaling losses (cycles)                                         | 27         |

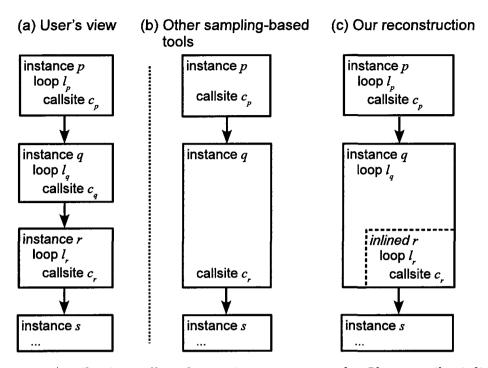

| 3.1          | Attributing call path metrics to source code                                                | 43         |

| 3.2          | Comparing hpcrun's and Intel PTU's overhead and unwind failures on                          | <u>.</u> . |

|              | SPEC CPU2006                                                                                | 54         |

| 3.3          | Representing program structure with a mapping between object code and source-code structure | 60         |

| 3.4          |                                                                                             | 62         |

| $3.4 \\ 3.5$ | Example of typical line map information                                                     | 64         |

| 3.6          | Bounding procedure end lines                                                                | 66         |

| 3.7          | Detecting incorrect loop placement via nesting cycles while recovering                      | 00         |

|              | program structure                                                                           | 70         |

| 3.8          | Correcting nesting cycles while recovering program structure                                | 71         |

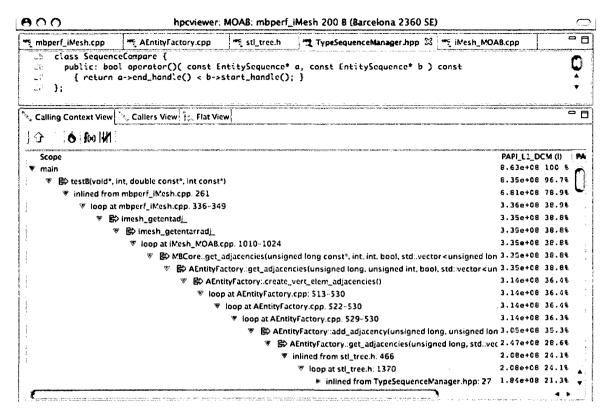

| 3.9          | hpcviewer's Calling Context view showing call paths overlayed with                          |            |

|              | static program structure for MOAB (C++)                                                     | 74         |

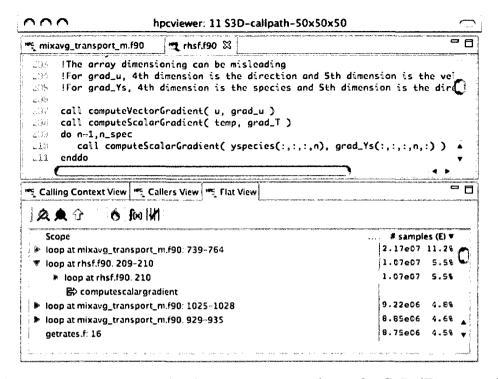

| 3.10         | hpcviewer's Flat view exposing loops for S3D (Fortran 90)                                   | 76         |

| 4.1          | Example of Cilk's simplicity and expressiveness                                             | 85         |

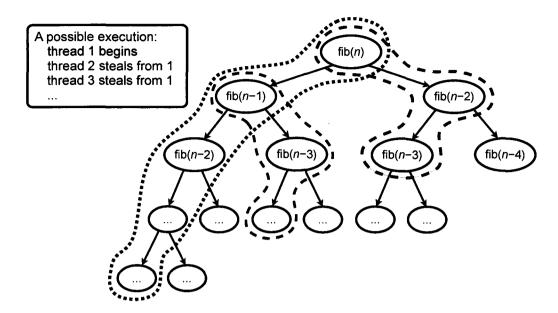

| 4.2          | Scheduling work via work stealing.                                                          | 86         |

| 4.3          | An asynchronous-sampling-based call path profiler                                           | 87         |

| 4.4          | A case for logical call path profiling                                                      | 88         |

| 4.5          | The logical call path for a typical Cilk worker thread                                      | 100        |

| 5.1          | Using parallel idleness and overhead to determine if the given applica-                     |            |

| 0.1          | tion and input are effectively parallel on $n$ cores                                        | 110        |

| 5.2          | Fragment of a Cilk program for computing Fibonacci numbers and                              |            |

| J            | compiled C code for that fragment                                                           | 114        |

| 5.3          | hpcviewer's Calling Context view of Cholesky                                                | 116        |

| 5.4          | hpcviewer's Callers view of Cholesky                                                        | 118        |

| 6.1          | hpcviewer's Calling Context view of MADNESS's moldft                                        | 149        |

| 6.2          | hpcviewer's Callers view of MADNESS's moldft                                                | 151        |

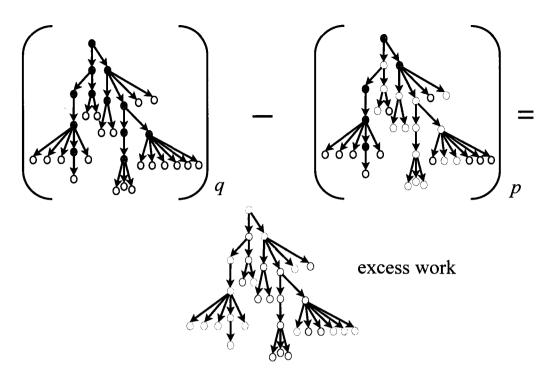

| 7.1          | A pictorial representation of differencing call path profiles to pinpoint                   |            |

|              | (weak) scaling bottlenecks                                                                  | 168        |

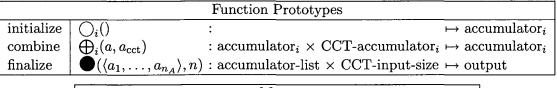

| 7.2          | Function prototypes for an incrementally computed metric                                    | 172        |

| 7.3  | Computing sum, mean, minimum and maximum incrementally                 | 174 |

|------|------------------------------------------------------------------------|-----|

| 7.4  | Computing standard deviation incrementally                             | 175 |

| 7.5  | Comparing different definitions for exclusive Calling Context metrics. | 179 |

| 7.6  | Example showing that it is, in general, impossible to compute derived  |     |

|      | metric values given finalized derived metric values                    | 184 |

| 7.7  | Computing metrics incrementally for a Flat or Callers view             | 190 |

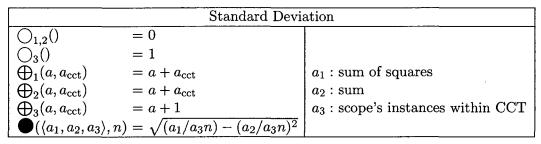

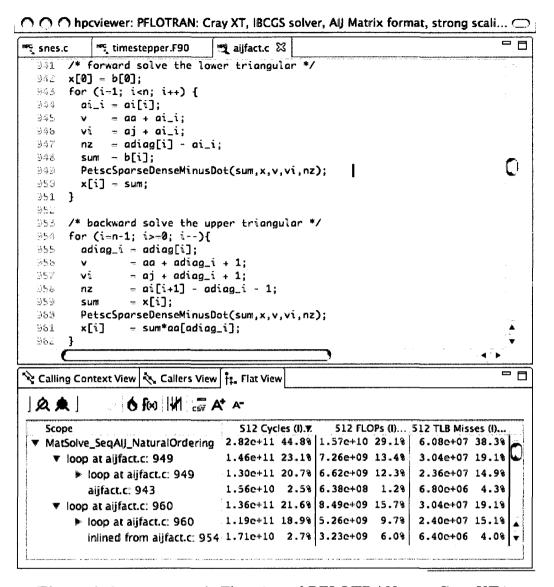

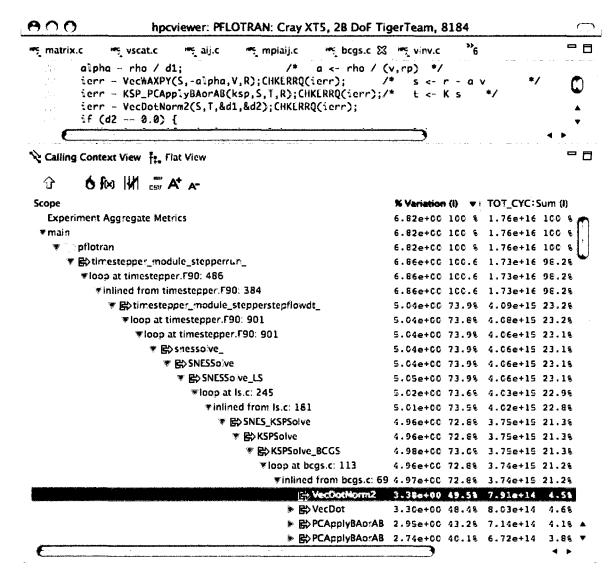

| 7.8  | hpcviewer's Calling Context view of PFLOTRAN on a Cray XT4             | 197 |

| 7.9  | hpcviewer's Flat view of PFLOTRAN on a Cray XT4                        | 199 |

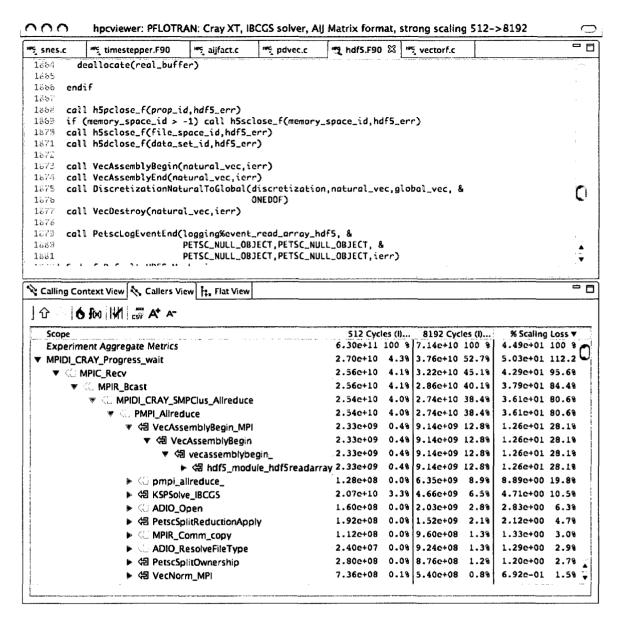

| 7.10 | hpcviewer's Callers view of scaling losses for PFLOTRAN on a Cray      |     |

|      | XT4                                                                    | 200 |

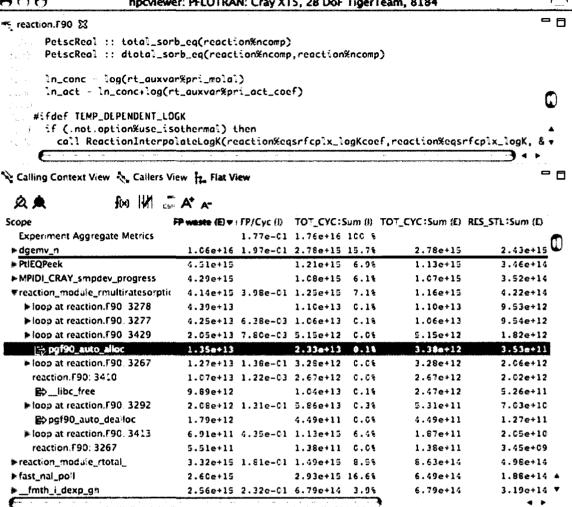

| 7.11 | hpcviewer's Flat view of floating point efficiency for PFLOTRAN on     |     |

|      | a Cray XT5                                                             | 203 |

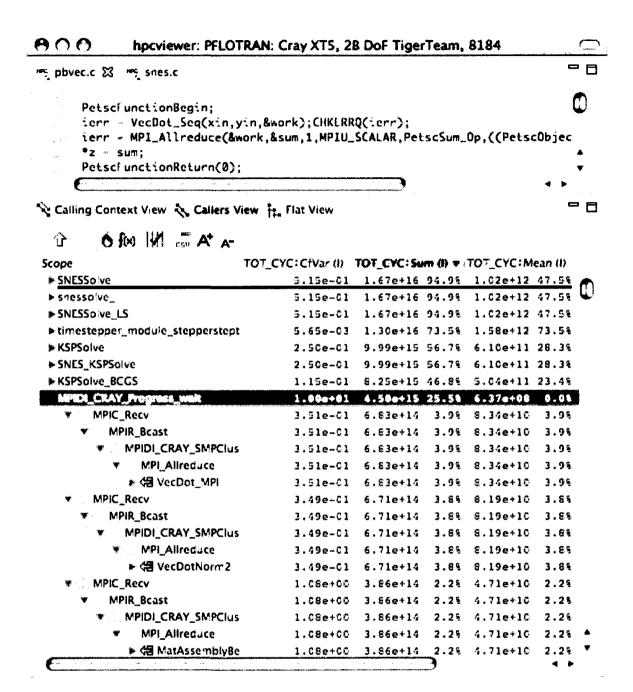

| 7.12 | hpcviewer's Callers view of variance within PFLOTRAN on a Cray         |     |

|      | XT5                                                                    | 205 |

| 7.13 | hpcviewer's Calling Context view of PFLOTRAN's variability on a        |     |

|      | Cray XT5                                                               | 208 |

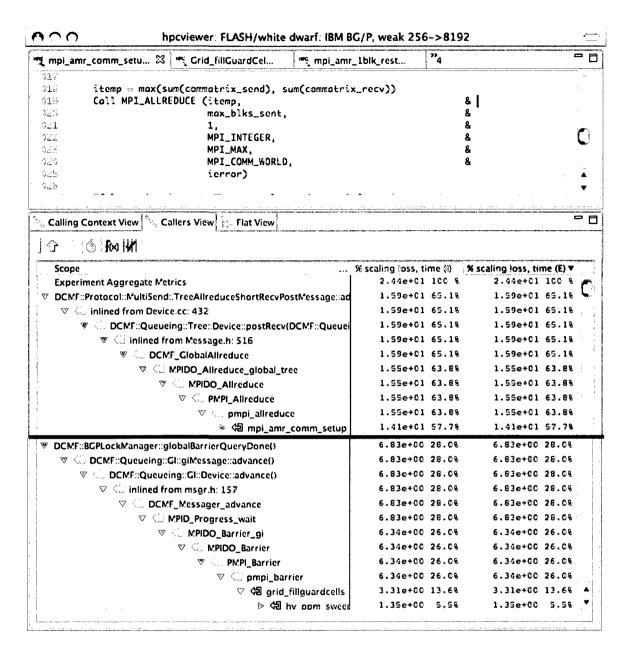

| 7.14 | hpcviewer's Callers view of scaling losses (wallclock) for FLASH on    |     |

|      | an IBM BG/P                                                            | 211 |

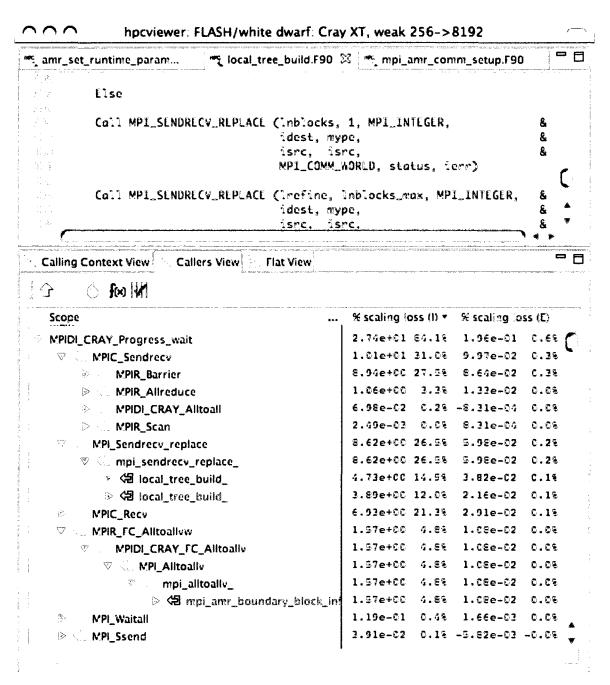

| 7.15 | hpcviewer's Callers view of scaling losses (cycles) for FLASH on a     |     |

|      | Cray XT4                                                               | 213 |

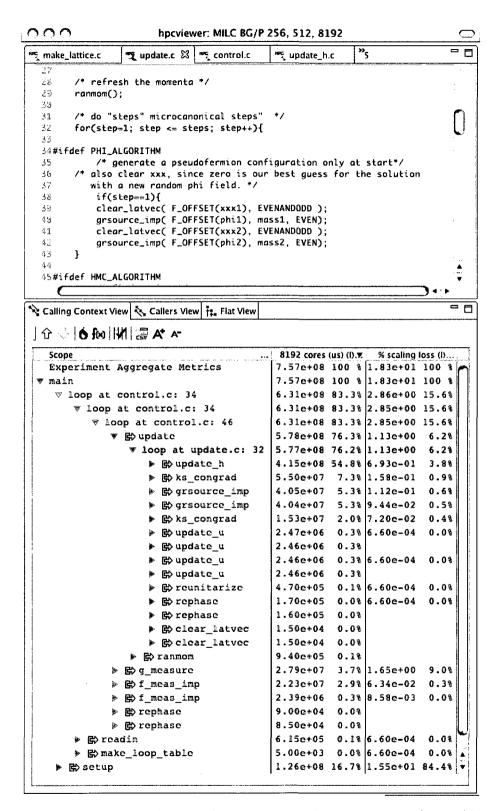

| 7.16 | hpcviewer's Calling Context view of scaling losses (cycles) for MILC   |     |

|      | on a BG/P.                                                             | 216 |

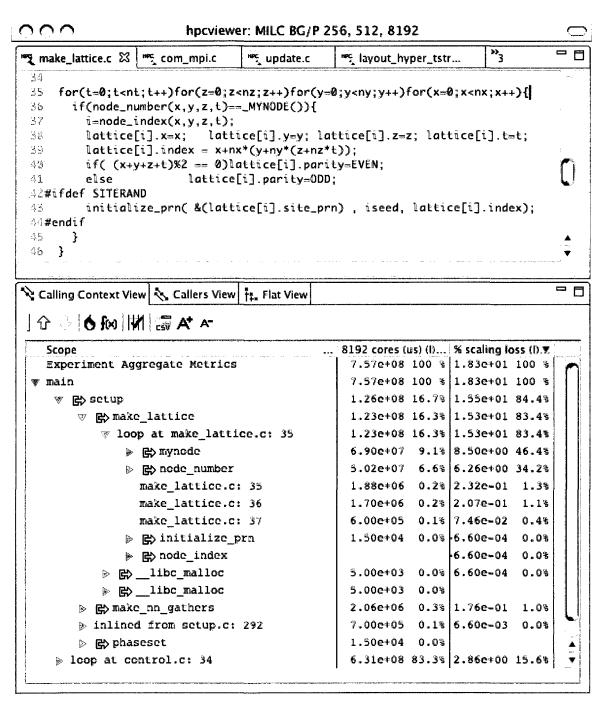

| 7.17 | A closer look at scaling losses for MILC on a BG/P                     | 217 |

|      |                                                                        |     |

| A.1  | A systematic sample                                                    | 242 |

|      |                                                                        |     |

# List of Algorithms

| 3.1 | backtrace: Use on-the-fly binary analysis to unwind call stacks from fully optimized code | 47  |

|-----|-------------------------------------------------------------------------------------------|-----|

| 3.2 | recover-program-structure: Recover static source code structure from an                   |     |

|     | application binary.                                                                       | 69  |

| 3.3 | determine-context: Determine the static context of a loop or statement.                   | 69  |

| 4.1 | logical-backtrace: Perform a logical unwind                                               | 97  |

| 6.1 | blame-suspects: On sampling a working thread, compute that thread's                       |     |

|     | blame for the execution's idleness based on associated suspects                           | 133 |

| 6.2 | demand-mon-lock: The protocol for converting a native lock into an out-                   |     |

|     | of-band lock in demand-driven fashion                                                     | 140 |

| 6.3 | lock-mon-lock: Lock a dual-representation lock                                            | 141 |

| 6.4 | trylock-mon-lock: Trylock on a dual-representation lock                                   | 143 |

| 6.5 | unlock-mon-lock: Unlock a dual-representation lock                                        | 145 |

| 7.1 | incrementally-compute-metrics: Incrementally compute derived metrics                      |     |

|     | in parallel                                                                               | 173 |

| 7.2 | make-flat-view: Given a Calling Context view with non-finalized derived                   |     |

|     | metric values, make a Flat view                                                           | 187 |

| 7.3 | make-callers-view: Given a Calling Context view with non-finalized de-                    |     |

|     | rived metric values, make a Callers view                                                  | 191 |

### Chapter 1

### Introduction

High performance computers have become enormously complex. Today's largest systems consist of tens of thousands of nodes and current plans call for a hundred thousand. Nodes themselves are equipped with one or more multicore microprocessors. Often these processor cores support additional levels of parallelism, such as hardware threads, short vector operations and pipelined execution of multiple instructions. Microprocessor-based nodes rely on deep multi-level memory hierarchies for managing latency and improving data bandwidth to processor cores. Subsystems for interprocessor communication and parallel I/O add to the overall complexity of these platforms. Recently, accelerators such as graphics chips and other co-processors have started to become more common on nodes. As the complexity of high performance computing (HPC) systems has grown, the complexity of applications has grown as well. Multi-scale and multi-physics applications are increasingly common, as are coupled applications.

Because HPC computing resources are limited and therefore precious, achieving top performance on leading-edge systems is critical. Unfortunately, existing compilers and other automatic techniques often fail to achieve top performance. The inability to harness such machines efficiently limits their ability to tackle the largest problems of interest. As a result, there is an urgent need for effective and scalable tools that can pinpoint a variety of performance and scalability bottlenecks in complex applications.

Our thesis is that it is possible to achieve unique, accurate, and actionable insight into the performance of fully optimized parallel programs by (1) measuring them with asynchronous-sampling-based call path profiles; (2) attributing the resulting binary-level measurements to source code structure; (3) analyzing measurements on-the-fly and post-mortem to highlight performance inefficiencies; and (4) presenting the resulting context-sensitive metrics in three complementary views. By actionable insight, we refer to insight into an application's performance that justifies concrete actions, such as determining how to resolve a performance bottleneck or deciding that there are no significant and worthwhile opportunities for performance improvement. By program performance, we refer to characterizing the performance of a particular execution. This is in contrast to constructing analytical models of a program that can be used for performance prediction on different inputs or architectures. Although we only focus on obtaining performance insight from a particular execution, it is often the case that fixing a bottleneck in a representative execution improves performance on different inputs and architectures.

To support this thesis, we have developed several techniques for identifying performance problems in fully optimized serial, multithreaded and petascale programs and have shown how these techniques form a coherent methodology. This work forms the basis of Rice University's HPCTOOLKIT performance tools [119].

Methodology. To lay a foundation for our work, Chapter 2 sketches a performance analysis methodology. This methodology is based on a set of complementary principles that, while not novel in themselves, form a coherent synthesis that is greater than the constituent parts. Our methodology is accurate, because it assiduously avoids systematic measurement error (such as that introduced by instrumentation); scalable, because it can be used to effectively analyze the performance of a single

thread or a large parallel execution; and *actionable*, because it associates insightful performance metrics (such as parallel inefficiency, scalability loss or memory bandwidth consumed) with important source code abstractions (such as loops) in their full dynamic calling contexts [1,95,96,138].

Measurement & Attribution. Chapters 3 and 4 present the measurement and attribution technology that serves as a foundation for the analysis techniques described in later chapters. In particular, we describe how to attribute very precise measurements to source-level static and dynamic contexts in fully optimized applications — all for an average run-time overhead of a few percent [141].

Modern programs frequently employ sophisticated modular designs. As a result, performance problems cannot be identified from metrics attributed to procedures in isolation; understanding code performance requires information about a procedure's calling context. Performance tools that attribute performance metrics to their full calling context are called call path profilers [67]. Current strategies for attributing calling-context-sensitive performance at the source level for fully optimized applications either compromise measurement accuracy, remain too close to the binary, or require custom compilers. Many tools measure using instrumentation, i.e., special instructions inserted directly into an application. Tools based on general instrumentation incur large overheads — often factors of at least two — that compromise accuracy. To avoid large overheads, we use asynchronous sampling. Sampling-based call path profilers must be able to unwind a program thread's call stack and then attribute the result back to source code. Existing sampling-based call path profilers are unable to reliably do this for fully optimized applications.

To understand the performance of fully optimized modular code, Chapter 3 describes two novel binary analysis techniques for asynchronous-sampling-based call

path profilers: (1) on-the-fly analysis of optimized machine code to enable minimally intrusive measurements qualified by their full dynamic calling contexts; and (2) postmortem analysis of optimized machine code and its debugging sections to recover its program structure and reconstruct a mapping back to its source code [141]. By combining the recovered static program structure with dynamic calling context information, HPCTOOLKIT can accurately attribute performance metrics to procedures, loops, and inlined instances of procedures in their full calling contexts.

Over the past decade, high-level multithreaded programming models such as Cilk [58] have emerged to simplify the development of multithreaded programs. These programming models raise the level of abstraction of parallel programming by partitioning the problem into two parts: the programmer is responsible for expressing the logical concurrency in a program and a run-time system is responsible for partitioning and mapping parallel work efficiently onto a pool of threads for execution.

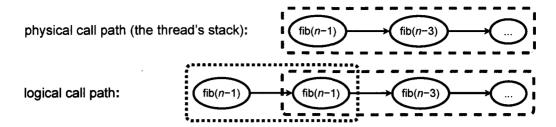

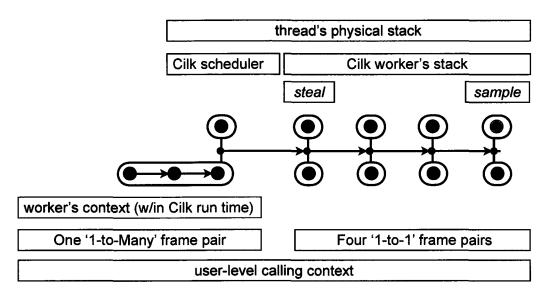

To apply our work on call path profiling to parallel programming models such as Cilk, Chapter 4 generalizes the notion of call path profiling to logical call path profiling [140,142]. For many high-level programming models, using call path profiling to associate costs with the context in which they are incurred is not as simple as it sounds. Standard call path profiling assumes a thread's call stack can be used as a proxy for the full source-level calling context of a particular point in its execution. However, for applications written in Cilk, which uses a work-stealing scheduler to partition and map work onto a thread pool, the stack of native procedure frames active within a thread represents only a suffix of the calling context. Moreover, Cilk's work-stealing scheduler causes calling contexts to become separated in space and time as procedure frames migrate between threads as work is distributed (stolen). As a result, a standard call path profile of a Cilk execution shows fragments of call paths mapped to each of the threads in the scheduler's thread pool. In contrast, a logical call path

profile attributes arbitrary performance metrics to source-level contexts for a Cilk application, even in the presence of work distribution (stealing). Accomplishing this requires bridging the gap between the expression of logical concurrency in a program and its realization at run time as the program's work is dynamically partitioned and scheduled onto a pool of threads. A later chapter uses these results to attribute metrics that reflect parallel inefficiency to source-level calling contexts in Cilk.

Analysis of Multithreaded Executions. Chapters 5 and 6 focus on performance analysis of multithreaded executions. Understanding why the performance of a multithreaded program does not improve linearly with the number of cores in a shared-memory multicore node is increasingly important. For instance, nodes on the Department of Energy's 'leadership class' machines currently contain 4-12 cores and nodes on less-balanced large-scale systems will soon contain scores of threaded cores. To address these issues, we developed techniques for pinpointing and quantifying parallel inefficiencies in work-stealing-based and lock-based multithreaded applications.

To understand the performance of work-stealing-based programs, Chapter 5 develops techniques for quantifying parallel idleness and overhead and pinpointing them to their logical calling context [140,142]. Parallel idleness occurs when threads are stalled and unable to work, whereas parallel overhead occurs when a thread performs miscellaneous work other than the user's computation. These metrics enable one to identify areas of an application where concurrency should be increased (to reduce idleness), decreased (to reduce overhead), or where the present parallelization is hopeless (where idleness and overhead are both high). By basing our techniques on asynchronous sampling, we can measure and attribute parallel idleness for minimal overhead (< 5%). By using a combination of compiler support and post-mortem binary analysis, we can measure parallel overhead without any measurement cost be-

yond normal profiling. These techniques apply broadly to high-level programming models such as Cilk and OpenMP. Our results provide unique insight into the performance of complex modular code where existing techniques fail.

Although higher-level parallel programming models are attractive, most multithreaded codes use locks to coordinate access to shared data. Indeed, fine-grain locking remains the gold standard for performance. In addition, locks are used to implement higher-level abstractions such as software transactional memory [50]. The chief cause of parallel inefficiency in lock-based programs is lock contention. Being able to quantify and attribute lock contention is important for understanding how to improve a multithreaded program's scalability.

Chapter 6 proposes and evaluates three strategies for gaining insight into performance losses due to lock contention [144]. First, we consider using a straightforward strategy based on call path profiling to attribute idle time and show that it fails to yield insight into lock contention. Second, we consider an approach that builds on the strategy of Chapter 5 for analyzing idleness in work stealing computations; we show that this strategy does not work well for understanding lock contention. Finally, we propose a new technique for measurement and analysis of lock contention that uses data associated with locks to blame lock holders for the idleness of spinning threads. Our approach incurs less than 5% overhead for a non-trivial execution of a quantum chemistry code that makes extensive use of locking (65M distinct locks, a maximum of 340K live locks, and an average of 30K lock acquisitions per second per thread) and attributes lock contention to its full static and dynamic calling contexts. Our strategy is distributed and should scale well to systems with larger core counts.

Analysis & Presentation of Petascale Executions. Finally, Chapter 7 focuses on the performance analysis and presentation of petascale executions. The first petas-

cale systems became available in 2009. To compute at the petaflop level — a thousand trillion floating point operations per second — petascale systems have hundreds of thousands of processor cores. Because of the challenge of using petascale computing platforms effectively, there is an acute need for application scientists to resolve scaling bottlenecks. To help address these issues, we develop new features for HPC-TOOLKIT to support the low-overhead (1-2%) collection of precise measurements on emerging petascale platforms [2, 56, 143]. Additionally, we show how to scalably analyze and present data from large-scale runs, including how to scalably compute a large set of derived metrics in parallel. With these new features, we show how to use HPCTOOLKIT's call path sampling to pinpoint and quantify both scaling and node performance bottlenecks. By applying this method to several emerging petascale applications on the Cray XT and IBM BlueGene/P platforms, HPCTOOLKIT identifies specific source lines — in their full calling context — associated with performance bottlenecks in these codes. This information is exactly what application developers need to know to improve their applications to take full advantage of the power of petascale systems.

\* \* \*

The principal goal of performance analysis is to determine if a production application has any performance bottlenecks and, if so, to provide actionable insight into what should be done next. This at least involves highlighting, within source code, bottlenecks that are both profitable and worthwhile to resolve. However, achieving such actionable insight is difficult. Since performance measurement typically occurs within a program's execution space, the very act of measuring disturbs a program's execution. Consequently, there is a natural tension between measurement precision and accuracy: the more precise measurements are, the more difficult to obtain ac-

curacy. Yet, both precise and accurate measurements are usually prerequisites for actionable insight into program performance.

As a result, one of the principal focuses of this thesis has been the design and implementation of techniques for providing accurate fine-grain measurements of production applications running at scale. For measurements to be accurate, performance tools must avoid introducing measurement error, including error from overhead. For tools to be useful on production applications, they cannot significantly increase execution time by inducing large overhead. HPCTOOLKIT is able to attribute precise measurements — statements in their full static and dynamic calling context — with low, controllable overhead and high accuracy.

A second overriding theme has been constructing insightful metrics from these accurate fine-grain measurements. We have accomplished this in two ways. First, we have highlighted sources of inefficiency in a program rather than where it spends its time. Second, we have developed ways to blame sections of source code for causing inefficient computation rather than reporting where that inefficiency is manifested.

# Chapter 2

# A Methodology for Performance Analysis

#### 2.1 Introduction

In this chapter, we sketch HPCTOOLKIT's unique and comprehensive methodology for analyzing the performance of parallel programs [1,95,96,138]. The methodology is based on a set of complementary principles that, while not novel in themselves, form a coherent synthesis that is greater than the constituent parts. This methodology is (1) accurate, because it assiduously avoids systematic measurement error (such as that introduced by instrumentation); (2) scalable, because it can be used to effectively analyze the performance of a single thread or a large parallel code; and (3) actionable, because it associates insightful performance metrics (such as parallel inefficiency, scalability loss or memory bandwidth) with important source code abstractions (such as loops) in their full calling context. These emphases have resulted in measurement techniques that incur low overhead, preserve low-level detail, and scale to large systems; metrics that highlight inefficiency rather than simply resource usage; and attribution, analysis and presentation techniques that yield insight by projecting low-level measurements to much higher levels of abstraction.

The methodology we describe is a significant development of prior work with Mellor-Crummey, Fowler and Marin [93] and Froyd [60, 61]. Since this prior work, HPCTOOLKIT's measurement, attribution, analysis, and presentation abilities have been radically advanced and its ability to effectively analyze multithreaded and large-

scale parallel executions is entirely new. Accordingly, we now present a full-orbed methodology for performance analysis of parallel programs. As a companion to our methodology, Appendix A presents an analysis, the first to our knowledge, of statistical sampling as a means of obtaining a thread-based profile.

This chapter is organized as follows. Section 2.2 enumerates several principles of performance analysis and then Section 2.3 applies those principles to form a methodology based on accurate measurement, source-level attribution, effective analysis and insightful presentation. Finally, Section 2.4 discusses related work and Section 2.5 discusses the chapter's main themes.

#### 2.2 Principles of Performance Analysis

The following principles form the basis of our methodology.

#### The goal is actionable insight.

The goal of performance analysis is actionable insight. By actionable insight, we refer to insight into an application's performance that justifies concrete actions such as determining how to resolve a performance bottleneck or deciding that there are no significant and worthwhile opportunities for performance improvement. Although obtaining insight requires accurate and scalable measurement techniques, such techniques are only a means to an end.

One way of stating this principle more concretely is to observe that the role of performance tools is not so much to highlight program hot spots, but to pinpoint and diagnose bottlenecks. For instance, the most important thing to know for a parallel application is whether there are parallel scaling bottlenecks at any architectural level. If both inter-node and intra-node parallelism are good, the next step is to determine

if the application making the most of a processor core. What are the rate-limiting factors for the application? Is there a mismatch between the application's needs and the computing system's capabilities? Finally, when a bottleneck is identified, it is important to know two things about it: What the expected benefit of resolving the bottleneck is and what level of effort will be necessary to do so.

#### Be language independent.

Modern parallel scientific programs, on one hand, often have a numerical core written in some modern dialect of Fortran, but on the other hand, leverage frameworks and communication libraries written in C or C++. For this reason, the ability to analyze multi-lingual programs is essential. To provide language independence, HPCTOOLKIT works directly with application binaries rather than source code.

#### Avoid code instrumentation for measurement.

We define instrumentation to be any addition to a program that is directly and synchronously invoked during the course of normal program execution; it can be contrasted with the indirect execution of an asynchronous signal handler. Although instrumentation can take several forms — source code, compiler-inserted or binary — all forms can distort application performance through a variety of mechanisms [109]. The most common problem with instrumentation is overhead, which distorts measurements. The classic tool Gprof [65], which uses compiler-inserted instrumentation, induced an average overhead of over 100% on the SPEC 2000 integer benchmarks [60]. Intel's VTune [77], which uses static binary instrumentation, claims an average overhead of a factor of eight. Intel's Performance Tuning Utility (PTU) [7] includes a call graph profiler based on Pin's dynamic binary instrumentation [88]; we found that it yielded an average overhead of over 400% on the SPEC 2006 integer benchmarks [141].

Another problem with instrumentation is the trade-off between accuracy and precision. While all measurement approaches must address this trade-off, the problem is particularly acute for instrumentation. For example, tools such as TAU [128] may intentionally refrain from instrumenting certain procedures to avoid large overheads. A common selective instrumentation technique is to ignore small frequently executed procedures. The more this approach reduces overhead, the more it reduces precision. Moreover, the ignored procedures may be just the synchronization library routines that are critical performance bottlenecks.

Tools that rely on source code instrumentation can distort application performance in even more subtle ways. Because instrumentation often has side effects, it interferes with inlining and template optimization [139]; some compiler-based instrumentation also disables compiler optimizations. Additionally, source code instrumentation is fundamentally unable to measure procedures for which source is unavailable, such as from binary-only libraries. This results in blind spots.

To avoid instrumentation's pitfalls, HPCTOOLKIT uses statistical sampling to measure performance. When possible, we prefer using asynchronous signals to generate sample events. However, in some cases an event is fundamentally and synchronously tied to program execution. For example, our analysis of lock contention (Chapter 6) requires intercepting every invocation of lock and unlock — potentially frequent events. To minimize the distorting overhead of instrumentation in these cases, HPCTOOLKIT applies sampling to instrumentation, i.e., it uses very lightweight instrumentation to periodically switch to short periods of heavyweight instrumentation. Another example of a fundamentally synchronous event is an application thread's entry and exit point. HPCTOOLKIT intercepts these entry and exit points to initialize and finalize statistical sampling.

#### Avoid blind spots.

Production applications frequently link against fully optimized and even partially stripped binaries, e.g., math and communication libraries, for which source code is not available. To avoid systematic error, one must measure costs for routines in these libraries. However, fully optimized binaries create challenges for asynchronous-sampling-based call path profiling and hierarchical aggregation of performance measurements. To deftly handle optimized and stripped binaries, HPCToolkit performs several types of binary analysis that are summarized in Sections 2.3.1 and 2.3.2.

#### Context is essential for understanding modular software.

Modern software design emphasizes modularity through layers of functional abstraction, generics and object-orientation. In such programs, it is important to attribute the costs incurred by each procedure to the different contexts in which the procedure is called. The costs incurred for calls to communication primitives (e.g., MPI\_Wait) or for code that results from instantiating C++ data structure templates can vary widely depending upon their calling context. When considering how to implement a set, different choices may be appropriate for different contexts. For instance, a bit vector can be a good implementation where a dense set is needed, but other representations are preferable for sparse sets. Because there are often layered implementations within applications and libraries, it is insufficient either to measure at any one level or to distinguish costs based only upon the immediate caller. For this reason, HPCTOOLKIT supports call path profiling [67] to attribute performance metrics to the full calling contexts in which they are incurred.

Although we focus on calling contexts, it is possible to collect other forms of contextual information. If calling context represents inter-procedural control flow, it is also possible to additionally collect intra-procedural context representing the path of flow within a procedure's control flow graph [53,71]. Yet another piece of context is the value of a state variable or a particular procedure's input. For example, one may wish to distinguish communication calls by message size. Finally, it is possible to distinguish between context *instances* by qualifying all measurements by time, or more generally, by any monotonically increasing resource. This is also known as tracing.

While more contextual information theoretically produces more fine-grained measurement data, this is only true if there is a reasonable balance between accuracy and the desired level of measurement (precision). We have focused on calling context because it is very useful and becuase we have developed highly accurate low-overhead techniques for gathering it. Moreover, we have developed fully post-mortem techniques for fusing static program structure — including loop nests — with dynamic calling contexts. Such information enables HPCTOOLKIT to expose the most important aspect of intra-procedural flow without any measurement overhead.

#### Any one performance measure produces a myopic view.

Measuring time or only one species of event seldom diagnoses a correctable performance problem. One set of metrics may be necessary to identify a problem and another set may be necessary to diagnose its causes. For example, counts of cache misses indicate problems only if both the miss *rate* is high and the latencies of the misses are not hidden. HPCTOOLKIT supports collection, correlation and presentation of multiple metrics.

#### Metrics pinpointing inefficiency are essential for effective analysis.

Typical metrics such as elapsed time are useful for identifying program hot spots. However, tuning a program usually requires a measure *not* of where resources are consumed, but where they are consumed *inefficiently*. For this purpose, derived measures such as the difference between peak and actual performance are far more useful than raw data such as operation counts. HPCTOOLKIT supports the computation of user-defined derived metrics and enables users to rank and sort program scopes using such metrics. In addition, HPCTOOLKIT can compute metrics that blame sections of source code for *causing* inefficient computation rather than simply reporting where that inefficiency is manifested.

#### Performance analysis should be top-down.

It is unreasonable to require users to wade through mountains of data to hunt for evidence of important problems. To make analysis of large programs tractable, performance tools should present measurement data in a hierarchical fashion, prioritize what appear to be important problems, and support a top-down analysis methodology that helps users quickly locate bottlenecks without the need to wade through irrelevant details. HPCTOOLKIT's presentation tool supports hierarchical presentation of performance data according to both static and dynamic contexts, along with ranking and sorting based on metrics.

#### Hierarchical aggregation is vital.

The amount of instruction-level parallelism in processor cores can make it difficult or expensive for hardware counters to precisely attribute particular events to specific instructions. However, even if fine-grain attribution of events is flawed, total event counts within loops or procedures will typically be accurate. Moreover, in most cases, it is the balance of operations within loops that matters — for instance, the ratio between floating point arithmetic and memory operations. HPCTOOLKIT's

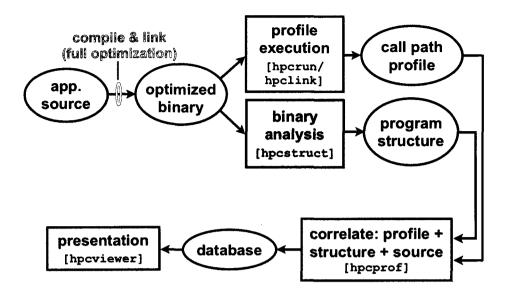

Figure 2.1: Overview of HPCTOOLKIT tool's workflow.

hierarchical attribution and presentation of measurement data deftly addresses this issue; loop-level information available with HPCToolkit is particularly useful.

#### Measurement and analysis must be scalable.

Large parallel systems may have tens of thousands of nodes, each equipped with one or more multicore processors. For performance tools to be useful on these systems, measurement and analysis techniques must scale to tens to hundreds of thousands of threads. HPCToolkit's sampling-based measurements are compact and the data for large-scale executions is not unmanageably large.

### 2.3 From Principles to Practical Methods

From these principles, we have devised a general methodology summarized by the workflow depicted in Figure 2.1. The workflow is organized around four principal capabilities:

- 1. measurement of context-sensitive performance metrics while an application executes;

- 2. binary analysis to recover program structure from application binaries;

- 3. attribution of performance metrics by correlating dynamic performance metrics with static program structure; and

- 4. presentation of performance metrics and associated source code.

To use HPCTOOLKIT to measure and analyze an application's performance, one first compiles and links the application for a production run, using *full* optimization. Second, one launches an application with HPCTOOLKIT's measurement tool, hpcrun, which uses statistical sampling to collect a performance profile. Third, one invokes hpcstruct, HPCTOOLKIT's tool for analyzing an application binary to recover information about files, procedures, loops, and inlined code. Fourth, one uses hpcprof to combine information about an application's structure with dynamic performance measurements to produce a performance database. Finally, one explores a performance database with HPCTOOLKIT's hpcviewer graphical presentation tool.

At this level of detail, much of the HPCTOOLKIT workflow approximates other performance analysis tools, with the most unusual step being binary analysis. However, the high level of the workflow discussion masks several novel aspects of HPC-TOOLKIT's methodology. In the following sections, we (1) sketch how the principles described above inform our methodology and (2) highlight several novel approaches to accurate measurement (Section 2.3.1), source-level attribution (Section 2.3.2), effective analysis (Section 2.3.3) and insightful presentation (Section 2.3.4).

<sup>&</sup>lt;sup>1</sup>For the most detailed attribution of application performance data using HPCTOOLKIT, one should ensure that the compiler includes line map information in the object code it generates. While HPCTOOLKIT does not need this information to function, it can be helpful to users trying to interpret the results. Since compilers can usually provide line map information for fully optimized code, this requirement need not require a special build process.

#### 2.3.1 Measurement

Without accurate performance measurements for fully optimized applications, analysis is unproductive. Consequently, one of our chief concerns has been designing an accurate measurement approach that simultaneously exposes low-level execution details while avoiding systematic measurement error, either through large overheads or through systematic dilation of execution. For this reason, HPCToolkit avoids instrumentation and favors *statistical sampling*.

#### Statistical sampling

Statistical sampling is a method for estimating performance metrics for a whole execution from a sample of that execution. There are two basic technique types for sampling a program's execution: asynchronous and synchronous.

HPCTOOLKIT primarily relies on asynchronous sampling for measurement. Asynchronous sampling uses a recurring event trigger to send signals to the program being profiled. When an event trigger occurs, a signal is sent to the program. A signal handler then records the context where the sample occurred. The recurring nature of the event trigger means that the program counter and context is sampled many times, resulting in a histogram of program contexts. As long as the number of samples collected during execution is sufficiently large (and is not correlated with certain program features), their distribution is expected to approximate the true distribution of the costs that the event triggers are intended to measure.

The second form of statistical sampling is synchronous sampling. Sometimes it is necessary to monitor fundamentally synchronous events such as lock acquisitions. To minimize the overhead typically associated with synchronously monitoring frequently occurring synchronous events, HPCTOOLKIT samples them. In effect, this involves switching between lightweight and heavyweight instrumentation.

#### Event triggers

Different kinds of event triggers measure different aspects of program performance. From the perspective of a program, event triggers can be either asynchronous or synchronous, corresponding to asynchronous and synchronous sampling, respectively. Asynchronous triggers are external to the monitored program and are not initiated by direct program action. HPCToolkit initiates asynchronous samples using either an interval timer or hardware performance counter events. Hardware performance counters enable HPCToolkit to statistically profile events such as cache misses and issue-stall cycles. Synchronous triggers, on the other hand, are generated via direct program action. Examples of interesting events for synchronous profiling are memory allocation, I/O, and inter-process communication. For such events, one might measure bytes allocated, written, or communicated, respectively. Another example of a synchronous trigger is lightweight instrumentation that samples heavyweight instrumentation.

Unless there is a compelling need for a synchronous event trigger, we prefer an asynchronous one. Asynchronous triggers use easily controllable sampling periods, require no direct change to an application, and, assuming the sampling period is not correlated with program behavior, cannot contribute to a blind spot.

#### Maintaining control over parallel applications

To manage profiling of an executable, HPCToolkit intercepts certain process control routines including those used to coordinate thread/process creation and destruction, signal handling, dynamic loading, and MPI initialization. To support measurement of unmodified, dynamically linked, optimized application binaries, HPC-Toolkit uses the library preloading feature of modern dynamic loaders to preload

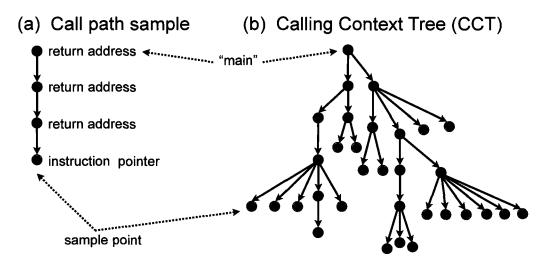

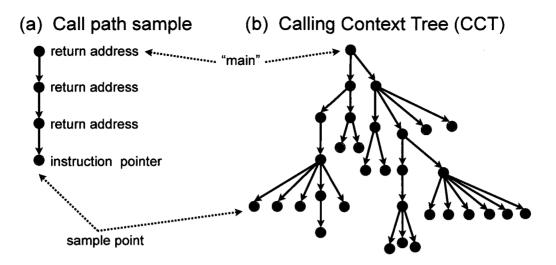

**Figure 2.2:** An asynchronous-sampling-based call path profiler (a) collects a call path for each sample point; and (b) several call paths form a calling context tree.

a profiling library as an application is launched.<sup>2</sup> For statically linked executables, a script arranges to intercept process control routines at link time.<sup>3</sup> In either case, HPCTOOLKIT is able to execute its own code both before and after the intercepted routine executes.

#### Call path profiling

Experience has shown that comprehensive performance analysis of modern modular software requires information about the full calling context in which costs are incurred. The calling context for a sample event is the set of procedure frames active on the call stack at the time the event trigger fires. We refer to the process of monitoring an execution to record the calling contexts in which event triggers fire as call path profiling [67].

When synchronous or asynchronous events occur, hpcrun records the full calling context for each event. A calling context collected by hpcrun is a list of instruction

<sup>&</sup>lt;sup>2</sup>On Linux, see the loader's special environment variable LD\_PRELOAD.

<sup>&</sup>lt;sup>3</sup>On Linux, see the linker's special --wrap option.

pointers, one for each procedure frame active at the time the event occurred; an example is shown in Figure 2.2(a). The last instruction pointer in the list is the program address at which the event occurred. The rest of the list contains the return address for each active procedure frame. Rather than storing the call path independently for each sample event, we represent all of the call paths for events as a calling context tree (CCT) [9]. In a calling context tree, shown in Figure 2.2(b), the path from the root of the tree to a node corresponds to a distinct call path observed during execution; a count at each node in the tree indicates the number of times that the path to that node was sampled.

#### Coping with fully optimized binaries

Collecting a call path profile requires capturing the calling context for each sample event. To capture the calling context for a sample event, hpcrun must be able to unwind the call stack at any point in a program's execution. Obtaining the return address for a procedure frame that does not use a frame pointer is challenging since the frame may dynamically grow (as space is reserved for the caller's registers and local variables; as the frame is extended with calls to alloca; as arguments to called procedures are pushed) and shrink (as space for the aforementioned purposes is deallocated) as the procedure executes. To cope with this situation, we developed a fast, on-the-fly binary analyzer that examines a procedure's machine instructions and computes how to unwind a stack frame for the procedure [141]. For each address in the routine, there must be a recipe for how to unwind. Different recipes may be needed for different intervals of addresses within the routine. Each interval ends in an instruction that changes the state of the procedure's stack frame. Each recipe describes (1) where to find the current frame's return address, (2) how to recover the value of the stack pointer for the caller's frame, and (3) how to recover the value that

the frame pointer register had in the caller's frame. Once we compute unwind recipes for all intervals in a routine, we memoize them for later reuse.

To apply our binary analysis to compute unwind recipes, we must know where each routine begins and ends. When working with applications, one often encounters partially stripped libraries or executables that are missing information about function boundaries. To address this problem, we developed a binary analyzer that infers routine boundaries by noting instructions that are reached by call instructions or instructions following unconditional control transfers (jumps and returns) that are not reachable by conditional control flow.

HPCTOOLKIT's use of binary analysis for call stack unwinding has proven to be very effective, even for fully optimized code. At present, HPCTOOLKIT provides binary analysis for stack unwinding on the x86-64, Power, and MIPS architectures. A detailed study of the x86-64 unwinder on versions of the SPEC CPU2006 benchmarks optimized with several different compilers showed that the unwinder was able to recover the calling context for all but a vanishingly small number of cases [141].

#### Handling dynamic loading

Modern operating systems such as Linux enable programs to load and unload shared libraries at run time, a process known as *dynamic loading*. Dynamic loading presents the possibility that multiple functions may be mapped to the same address at different times during a program's execution. During execution, hpcrun ensures that all measurements are attributed to the proper routine in such cases.

#### 2.3.2 Attribution

To enable effective analysis, measurements of fully optimized programs must be correlated with important source code abstractions. Since HPCTOOLKIT measures

with reference to instructions in executables and shared libraries, for analysis it is necessary to attribute these low-level measurements back to program source. To do this, we need a mapping between a load module's object code and its associated source code. Most load modules contain such mappings in the form of a 'line map.' However, to accurately attribute measurements to interesting source-level structure such as loop nests, it is necessary to have much richer information than can typically be obtained from the line map, which is fundamentally line based. Moreover, the line map for fully optimized programs often contains ambiguities resulting from inlining. Consequently, HPCTOOLKIT's hpcstruct tool constructs such a mapping using a binary analysis technique that we call recovering program structure.

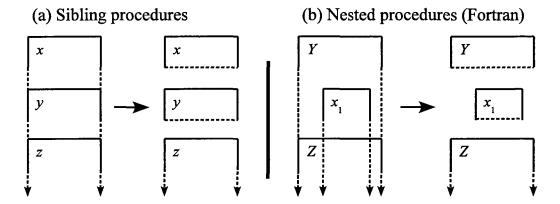

hpcstruct focuses its efforts on recovering procedures and loop nests, the most important elements of source code structure. To recover program structure, hpcstruct (1) parses a load module's machine instructions; (2) reconstructs a control flow graph; and (3) combines line map information with interval analysis on the control flow graph in a way that enables it to identify transformations to procedures such as inlining and account for transformations to loops [141].<sup>4</sup>

Several benefits naturally accrue from this approach. First, HPCTOOLKIT can expose the structure of what is actually executed and assign metrics to it, even if source code is unavailable. For example, hpcstruct's program structure naturally reveals transformations such as loop fusion and scalarized loops implementing Fortran 90 array notation. Similarly, it exposes calls to compiler support routines and wait loops in communication libraries of which one would otherwise be unaware. hpc-run's function discovery heuristics expose distinct logical procedures within stripped binaries.

<sup>&</sup>lt;sup>4</sup>Without line map information, hpcstruct can still identify procedures and loops, but is not able to account for inlining, which can affect loops in the vicinity of inlined code.

#### 2.3.3 Analysis

#### Derived metrics

Identifying performance problems and opportunities for tuning may require synthesizing performance metrics from others. To identify where an algorithm is not effectively using hardware resources, one should compute a metric that reflects *inefficiency* rather than accomplishment; wasted rather than consumed resources. For instance, when tuning a floating-point-intensive scientific code, it is often less useful to know where the majority of the floating-point operations occur than where floating-point performance is low. Knowing where the most cycles are spent doing things other than floating-point computation hints at opportunities for tuning. Such a metric can be directly computed by taking the difference between the cycle count on one hand and, on the other hand, the floating point operations (FLOPs) count divided by a target FLOPs-per-cycle value, and displaying this measure for loops and procedures. Our experiences with using multiple computed metrics such as miss ratios, instruction balance, and 'lost cycles' underscore the power of this approach.

#### Third-party metrics

For multithreaded applications, critical inefficiency occurs when threads idle waiting for work. In contrast to serial code, idleness in one thread is usually caused by another thread. For example, if one thread holds a lock that another thread needs, the latter's execution must be delayed. Or, if threads who are responsible for generating parallel work fail to do so, then other threads will be starved of work. To attribute the idleness in one thread to its cause in another thread, we have developed techniques for efficiently blaming the offending thread for the idleness it causes [140, 144]. We call these metrics third-party because in contrast to first-party metrics, they require

some knowledge of the execution state of other threads and the interactions between those threads.

## Scalably identifying scalability bottlenecks in parallel programs

We have developed scalable versions of hpcprof and hpcviewer for scalably analyzing, attributing and presenting call path profiles from large-scale executions. One novel application of HPCTOOLKIT's call path profiles is to use them to pinpoint and quantify scalability bottlenecks in emerging petascale SPMD parallel executions [143]. In particular, with HPCTOOLKIT's scalable analysis and presentation, it is possible to apply differential profiling [41,92] to compare two whole executions instead of, as with non-scalable techniques, two 'representative' threads. Combining execution-wide call path profiles with program structure information, HPCTOOLKIT can use an excess work metric to quantify scalability losses and attribute them to the full calling context in which these losses occur.

We have also developed techniques for effectively analyzing scalability bottlenecks in multithreaded applications [140, 144]. Using them, HPCTOOLKIT can attribute precise measures of lock contention, parallel idleness, and parallel overhead to *source-level* calling contexts — even for a multithreaded language such as Cilk [58], which uses a work-stealing scheduler.

#### 2.3.4 Presentation

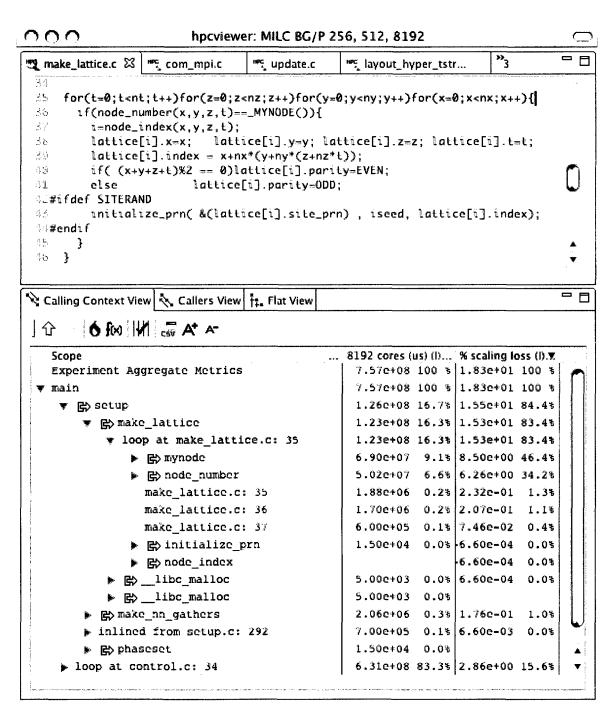

HPCTOOLKIT's presentation tool, hpcviewer, interactively presents context-sensitive performance metrics correlated to program structure (Section 2.3.2) and mapped to a program's source code, if available. Figure 2.3 shows a snapshot of hpcviewer's user interface presenting a call path profile. The user interface is composed of two principal panes. The top pane displays program source code. The bot-

Figure 2.3: hpcviewer's Calling Context view of scaling losses (cycles).

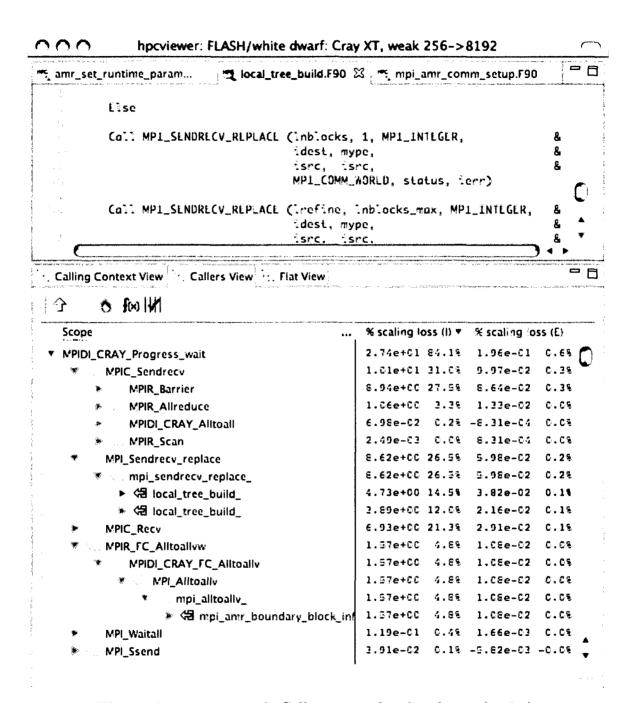

Figure 2.4: hpcviewer's Callers view of scaling losses (cycles).

tom pane associates a table of performance metrics with static or dynamic program structure. hpcviewer provides three different views of performance measurements collected using call path profiling. We briefly describe the three views and their corresponding purposes.

- Calling Context view. Figure 2.3 shows a Calling Context view. This top-down view associates metrics with the full calling context in which they were incurred. Indentation in the lower pane shows dynamic nesting of calls, loops and inlined code. Using this view, one can readily see how much of the application's cost was incurred by a procedure when called from a particular context. If finer detail is of interest, one can explore how the costs incurred by a call in a particular context are divided between the callee itself and the procedures it calls. HPCTOOLKIT distinguishes calling context precisely by individual call sites; this means that if a procedure f contains calls to procedure g in different places, each call represents a separate calling context. The Calling Context view is created by integrating dynamic calling contexts gathered by hpcrun with static program structure (e.g., loops) gathered by hpcstruct. Loops appear explicitly in the call chains shown in Figure 2.3.

- Callers view. This bottom-up view enables one to look upward along call paths. Because the Callers view apportions metrics of a callee on behalf of its caller, this view is particularly useful for understanding the performance of software components or procedures that are called in more than one context. For instance, a message-passing program may call MPI\_Wait in many different calling contexts. The cost of any particular call will depend upon its context. Serialization or load imbalance may cause long waits in some calling contexts

but not others. Figure 2.4 shows hpcviewer presenting a Callers view of a call path profile.

When several levels of the Callers view are expanded, saying that the Callers view apportions metrics of a callee on behalf of its caller can be ambiguous: what is the caller and what is the callee? To resolve this ambiguity we can say that the Callers view apportions the metrics of a particular procedure in its various calling contexts on behalf of that context's caller. Alternatively but equivalently, the Callers view apportions the metrics of a particular procedure on behalf of its various calling contexts. For example, notice that the highlighted line in Figure 2.4 shows a (partially collapsed) callers chain ending with local\_tree\_build that is four levels deep. The metrics at local\_tree\_build are actually formed by attributing the metrics at the chain's root (MPIDI\_CRAY\_Progress\_wait) up its call chain to local\_tree\_build.

• Flat view. This view organizes performance data according to an application's static structure. That is, all costs incurred by a procedure, in any calling context, are aggregated together to form the Flat view. This view complements the Calling Context view, in which the costs incurred by a particular procedure are represented separately for each call to the procedure from a different calling context.

hpcviewer can present an arbitrary collection of performance metrics gathered during one or more runs, or compute derived metrics expressed as formulae with existing metrics as terms.

For any given scope in these three views, hpcviewer computes both *inclusive* and *exclusive* metric values. For the moment, consider the Calling Context view. Inclusive metrics reflect costs for the entire subtree rooted at that scope. Exclusive metrics are

of two flavors, depending on the scope. For a procedure, exclusive metrics reflect all costs within that procedure but excluding callees. In other words, for a procedure, costs are exclusive with respect to dynamic call chains. For all other scopes, exclusive metrics reflect costs for the scope itself; i.e., costs are exclusive with respect to static structure. The Callers and Flat views contain inclusive and exclusive metric values that are relative to the Calling Context view. This means, e.g., that inclusive metrics for a particular scope in the Callers or Flat view are with respect to that scope's subtree in the Calling Context view.

Within a view, a user may order program scopes by sorting them using any performance metric. hpcviewer supports several convenient operations to facilitate analysis: revealing a hot path within the hierarchy below a scope; flattening one or more levels of the static hierarchy, e.g., to facilitate comparison of costs between loops in different procedures; and zooming to focus on a particular scope and its children.

## 2.4 Related Work

Here, we primarily discuss work related to HPCTOOLKIT's measurement methodology. We defer detailed discussion of attribution, analysis and presentation to later chapters.

Tools that permit monitoring of unmodified executables are critical for applications with long build processes or for attaching to an existing production run. Although different performance tools measure the same dimensions of an execution, they may differ with respect to their measurement methodology. These different methodologies determine whether a tool can analyze the performance of unmodified applications. TAU [129], OPARI [102], and Pablo [117], among others, add instrumentation to source code during a program's build process. Gprof relies on