# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

## Energy Efficient Design of an Adaptive Switching Algorithm for the Iterative-MIMO Receiver

Noor Zahrinah Binti Mohd Tadza (Nina)

A thesis submitted for the degree of Doctor of Philosophy. **The University of Edinburgh**.

May 2015

#### **Abstract**

An efficient design dedicated for iterative-multiple-input multiple-output (MIMO) receiver systems is now imperative in our world since data demands are increasing tremendously in wireless networks. This puts a massive burden on the signal processing power especially in small receiver systems where power sources are often shared or limited. This thesis proposes an attractive solution to both the wireless signal processing and the architectural implementation design sides of the problem. A novel algorithm, dubbed the Adaptive Switching Algorithm, is proven to not only save more than a third of the energy consumption in the algorithmic design, but is also able to achieve an energy reduction of more than 50% in terms of processing power when the design is mapped onto state-of-the-art programmable hardware. Simulations are based in Matlab<sup>TM</sup> using the Monte Carlo approach, where multiple additive white Gaussian noise (AWGN) and Rayleigh fading channels for both fast and slow fading environments were investigated. The software selects the appropriate detection algorithm depending on the current channel conditions. The design for the hardware is based on the latest field programmable gate arrays (FPGA) hardware from Xilinx<sup>®</sup>, specifically the Virtex-5 and Virtex-7 chipsets. They were chosen during the experimental phase to verify the results in order to examine trends for energy consumption in the proposed algorithm design. Savings come from dynamic allocation of the hardware resources by implementing power minimization techniques depending on the processing requirements of the system. Having demonstrated the feasibility of the algorithm in controlled environments, realistic channel conditions were simulated using spatially correlated MIMO channels to test the algorithm's readiness for real-world deployment. The proposed algorithm is placed in both the MIMO detector and the iterative-decoder blocks of the receiver. When the final full receiver design setup is implemented, it shows that the key to energy saving lies in the fact that both software and hardware components of the Adaptive Switching Algorithm adopt adaptivity in the respective designs. The detector saves energy by selecting suitable detection schemes while the decoder provides adaptivity by limiting the number of decoding iterations, both of which are updated in real-time. The overall receiver can achieve more than 70% energy savings in comparison to state-of-the-art iterative-MIMO receivers and thus it can be concluded that this level of 'intelligence' is an important direction towards a more efficient iterative-MIMO receiver designs in the future.

## **Declaration of Originality**

I hereby declare that the research recorded in this thesis and the thesis itself was composed and originated entirely by myself in the Institute for Digital Communications (IDCOM) of the School of Engineering at The University of Edinburgh.

Noor Zahrinah Binti Mohd Tadza (Nina) May 2015

### Acknowledgements

In the name of Allah, the Most Gracious and the Most Merciful. Alhamdulillah, all praises to Allah for the strength He gave me and for His blessings that enabled me to complete this thesis.

First and foremost, I would like to express my deepest gratitude and indeed it has been and honour and privilege to work closely with both Professor John Thompson and Dr. Dave Laurenson, without whose guidance and (extreme) patience, I would not have completed this PhD thesis. I have been fortunate to have had the joy of learning from their knowledge, experience and expertise. I am extremely grateful to them for bringing me such an interesting problem to study in this past three four years.

I wish to thank my father, Dr. Mohd Tadza, for his constant words of encouragement that gave me the strength to keep going; my mother, Dr. Noor Hasnah, without whose provision and advice, I would not have been be able to endure this arduous journey; my brothers, Dr. Mohd Yuhyi and (soon to be) Dr. Muhammad Afiq for their relentless moral support and company, that kept my mind off the stress this PhD sometimes created. For their love and support, I will always be thankful. Special appreciation and apologies go to Mr. Pepijn De Cuyper for relentlessly editing the thesis for grammatical errors for which I know were plenty.

To my old friends and the new ones I made along this journey, my colleagues or should I say my comrades at IDCOM, I wish to say "thank you" for enduring together in the same battle. Our shared experiences and difficulties have helped me realize that I am not alone in this crusade. I know that one day, we will look back to these days and smile. Thank you goes to the Ministry of Education (MoE), Malaysia for providing me the scholarship to pursue my doctorate, and to Tun Hussein Onn University (UTHM) for supporting my study leave.

## Contents

|   |                                                                           | Declaration of Originality ii            |  |  |  |  |  |

|---|---------------------------------------------------------------------------|------------------------------------------|--|--|--|--|--|

|   |                                                                           | Acknowledgements                         |  |  |  |  |  |

|   |                                                                           | Contents                                 |  |  |  |  |  |

|   |                                                                           | List of Figures                          |  |  |  |  |  |

|   |                                                                           | List of Tables                           |  |  |  |  |  |

|   |                                                                           | Acronyms and Abbreviations               |  |  |  |  |  |

|   |                                                                           | Nomenclature                             |  |  |  |  |  |

|   |                                                                           | Tromonomics                              |  |  |  |  |  |

| 1 | Intr                                                                      | oduction                                 |  |  |  |  |  |

|   | 1.1                                                                       | Motivation of Work                       |  |  |  |  |  |

|   | 1.2                                                                       | Thesis Contributions                     |  |  |  |  |  |

|   | 1.3                                                                       | Thesis Outline                           |  |  |  |  |  |

|   |                                                                           |                                          |  |  |  |  |  |

| 2 | Bacl                                                                      | kground                                  |  |  |  |  |  |

|   | 2.1                                                                       | Chapter Contribution                     |  |  |  |  |  |

|   | 2.2                                                                       | Wireless Communication                   |  |  |  |  |  |

|   |                                                                           | 2.2.1 Iterative-MIMO System Architecture |  |  |  |  |  |

|   |                                                                           | 2.2.2 MIMO Detectors                     |  |  |  |  |  |

|   |                                                                           | 2.2.3 Hard-Output MIMO Detection         |  |  |  |  |  |

|   |                                                                           | 2.2.4 Soft-Output MIMO Detection         |  |  |  |  |  |

|   |                                                                           | 2.2.5 Iterative Decoders                 |  |  |  |  |  |

|   | 2.3                                                                       | Hardware Architecture                    |  |  |  |  |  |

|   |                                                                           | 2.3.1 Power Minimization Techniques      |  |  |  |  |  |

|   | 2.4                                                                       | Chapter Summary                          |  |  |  |  |  |

| 3 | A do                                                                      | ptive Switching Algorithm 4.             |  |  |  |  |  |

| 3 |                                                                           |                                          |  |  |  |  |  |

|   | 3.1                                                                       | · · · · · · · · · · · · · · · · · · ·    |  |  |  |  |  |

|   | 3.2                                                                       |                                          |  |  |  |  |  |

|   | 3.3                                                                       | System Model Description                 |  |  |  |  |  |

|   |                                                                           | 3.3.1 V-BLAST/ZF                         |  |  |  |  |  |

|   | 2.4                                                                       | 3.3.2 FSD                                |  |  |  |  |  |

|   | 3.4                                                                       | Adaptive Switching Algorithm             |  |  |  |  |  |

|   | 3.5                                                                       | Results and Analysis                     |  |  |  |  |  |

|   |                                                                           | 3.5.1 Software Performance               |  |  |  |  |  |

|   |                                                                           | 3.5.2 Hardware Performance               |  |  |  |  |  |

|   |                                                                           | 3.5.3 Rayleigh Fading Performance 65     |  |  |  |  |  |

|   | 3.6                                                                       | Chapter Summary                          |  |  |  |  |  |

| 4 | Design Trends of the Adaptive Switching Algorithm on the FPGA Hardware 69 |                                          |  |  |  |  |  |

| - | 4.1                                                                       | Chapter Contribution                     |  |  |  |  |  |

|   | 4.2                                                                       | Related Work                             |  |  |  |  |  |

|   | 4.3                                                                       | System Model Description                 |  |  |  |  |  |

|   | 4.4                                                                       | System Design Architecture 74            |  |  |  |  |  |

| 6<br>A | 6.1<br>6.2<br>6.3         | 5.4.1<br>Result:<br>5.5.1<br>5.5.2<br>5.5.3<br>Chapte<br>clusions<br>Summ<br>Major | Iterative Turbo Decoding                                           | 09<br>13<br>16<br><b>17</b><br>17                   |

|--------|---------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------|

| 6      | 5.6<br><b>Con</b> 6.1 6.2 | 5.4.1<br>Result:<br>5.5.1<br>5.5.2<br>5.5.3<br>Chapte<br>clusions<br>Summ<br>Major | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09<br>13<br>16<br><b>17</b><br>18 |

| 6      | 5.6<br><b>Con</b><br>6.1  | 5.4.1<br>Result:<br>5.5.1<br>5.5.2<br>5.5.3<br>Chapte<br>clusions<br>Summ          | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09<br>13<br>16                    |

| 6      | 5.6<br><b>Con</b>         | 5.4.1<br>Result<br>5.5.1<br>5.5.2<br>5.5.3<br>Chapte                               | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09<br>13<br>16                    |

| 6      | 5.6                       | 5.4.1<br>Result<br>5.5.1<br>5.5.2<br>5.5.3<br>Chapte                               | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09<br>13                          |

|        |                           | 5.4.1<br>Result<br>5.5.1<br>5.5.2<br>5.5.3                                         | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09<br>13                          |

|        | 5.5                       | 5.4.1<br>Results<br>5.5.1<br>5.5.2                                                 | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09                                |

|        | 5.5                       | 5.4.1<br>Results<br>5.5.1<br>5.5.2                                                 | Iterative Turbo Decoding                                           | 00<br>04<br>04<br>09                                |

|        | 5.5                       | 5.4.1<br>Result<br>5.5.1                                                           | Model Description                                                  | 00<br>04<br>04                                      |

|        | 5.5                       | 5.4.1<br>Result                                                                    | Model Description                                                  | 00<br>04                                            |

|        |                           | 5.4.1                                                                              | Model Description                                                  | 00                                                  |

|        |                           | •                                                                                  | Model Description                                                  |                                                     |

|        | 5.4                       | Systen                                                                             | ·                                                                  |                                                     |

|        | 5.3                       | _                                                                                  | lly Correlated MIMO Channels                                       | 97                                                  |

|        | 5.2                       |                                                                                    |                                                                    | 95                                                  |

|        | 5.1                       | Chapte                                                                             |                                                                    | 95                                                  |

|        | late                      | d Chanı                                                                            | nels                                                               | 95                                                  |

| 5      | Prac                      | ctical Po                                                                          | erformance of the Adaptive Switching Algorithm in Spatially Corre- |                                                     |

|        | 4.8                       | Chapte                                                                             | er Summary                                                         | 92                                                  |

|        |                           | 4.7.4                                                                              | Combination of Power Minimization Techniques                       | 91                                                  |

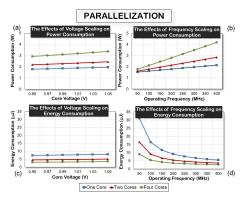

|        |                           | 4.7.3                                                                              | Parallelization                                                    | 88                                                  |

|        |                           | 4.7.2                                                                              | Sleep Mode                                                         | 87                                                  |

|        |                           | 4.7.1                                                                              | DVFS                                                               | 85                                                  |

|        | 4.7                       | Result                                                                             | s and Analysis                                                     | 82                                                  |

|        |                           | 4.6.3                                                                              |                                                                    | 82                                                  |

|        |                           | 4.6.2                                                                              |                                                                    | 81                                                  |

|        |                           | 4.6.1                                                                              | 1                                                                  | 80                                                  |

|        | 4.6                       |                                                                                    |                                                                    | 80                                                  |

|        |                           | 4.5.3                                                                              |                                                                    | 79                                                  |

|        |                           | 4.5.2                                                                              |                                                                    | 78                                                  |

|        | 7.5                       | 4.5.1                                                                              |                                                                    | 70<br>77                                            |

|        | 4.5                       |                                                                                    |                                                                    | 76                                                  |

|        |                           | 4.4.2                                                                              |                                                                    | 74<br>75                                            |

|        |                           | 4.4.1<br>4.4.2                                                                     |                                                                    | 74<br>74                                            |

|        |                           | 1 1 1                                                                              |                                                                    | 74                                                  |

## List of Figures

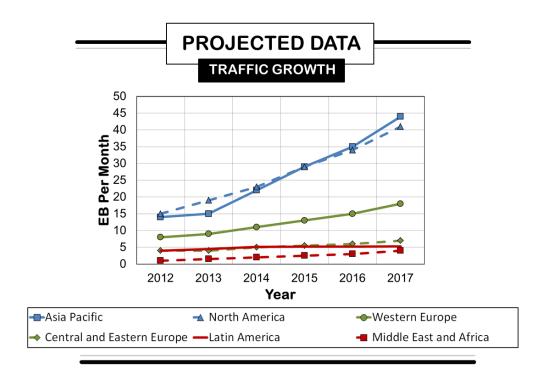

| 1.1  | Projected data traffic growth                                                                                                                             | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

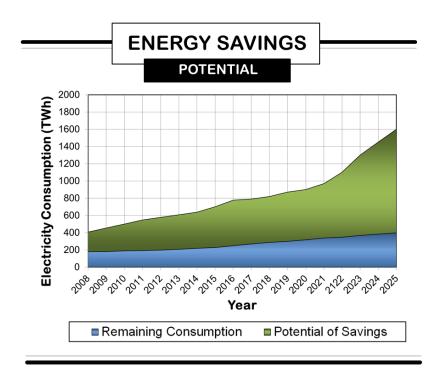

| 1.2  | Potential energy savings trend [1]                                                                                                                        | 4  |

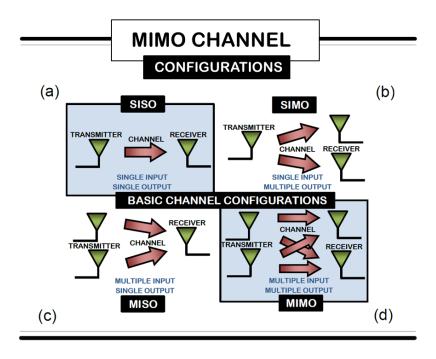

| 2.1  | Channel transmission configurations                                                                                                                       | 11 |

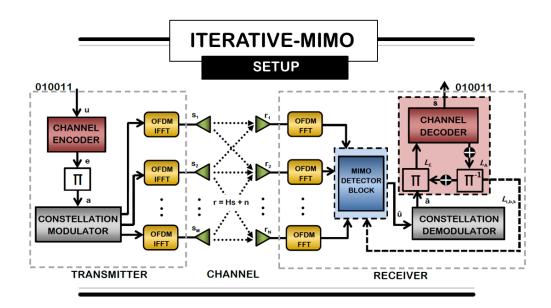

| 2.2  | Iterative-MIMO system channel                                                                                                                             | 12 |

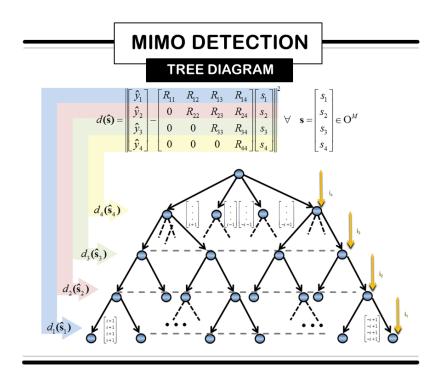

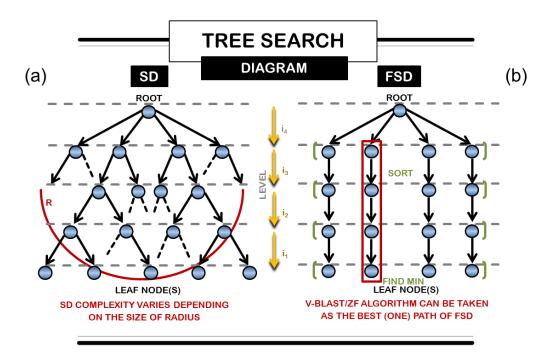

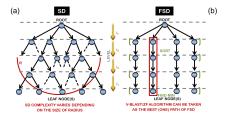

| 2.3  | MIMO detection as a tree diagram for 4-QAM modulation on a $4 \times 4$ MIMO system                                                                       | 15 |

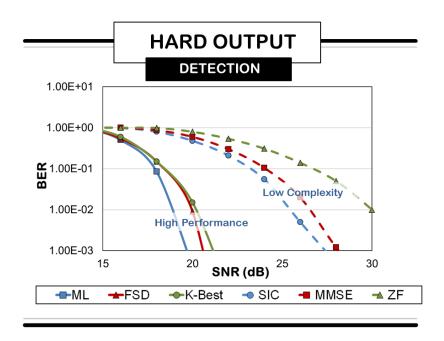

| 2.4  | BER performance comparison high performance and low complexity hard decoding 16-QAM with convolutional coding of $\varphi = 1/2 \dots \dots \dots$        | 23 |

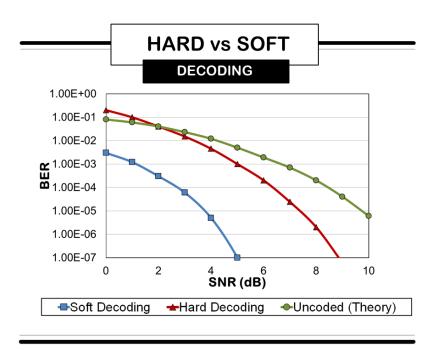

| 2.5  | BER performance comparison between hard and soft decoding BPSK with convolutional coding of $\varphi = 1/2 \dots \dots \dots \dots \dots$                 | 24 |

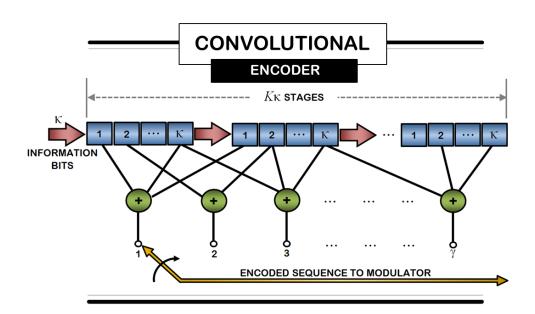

| 2.6  | Convolutional encoder                                                                                                                                     | 27 |

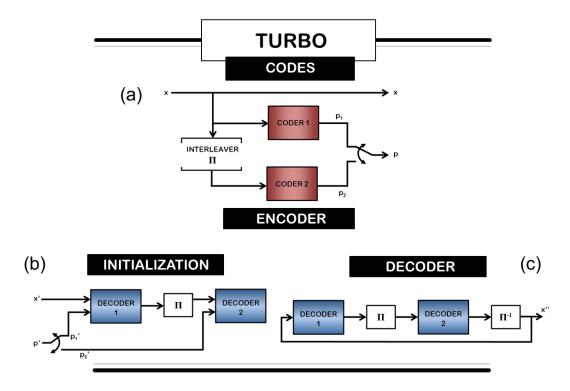

| 2.7  | Innerworking of turbo codes for both (a) for encoder, (b) and (c) for decoder                                                                             | 28 |

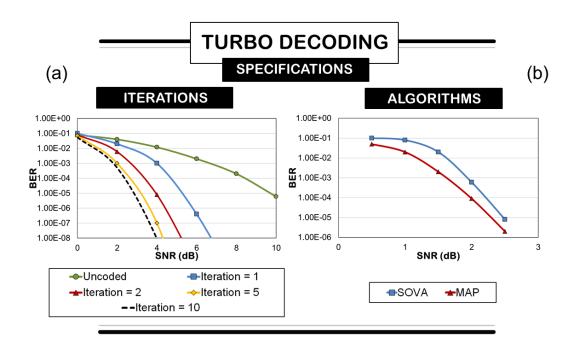

| 2.8  | BER for different specifications of turbo decoding according to (a) the number                                                                            |    |

| • •  | of decoding iterations and (b) different decoding algorithm                                                                                               | 31 |

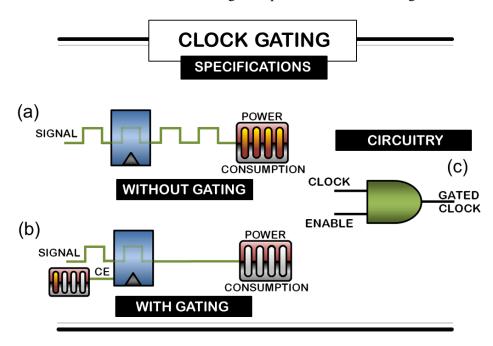

| 2.9  | The inner workings of clock gating where (a) is without clock gating, (b) is                                                                              | 22 |

| 2.10 | with clock gating and (c) is the clock gating circuitry                                                                                                   | 33 |

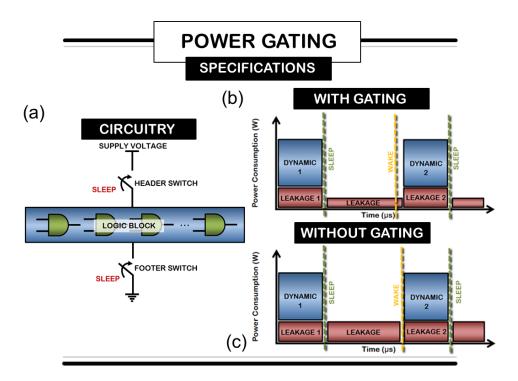

| 2.10 | The inner workings of power gating where (a) is the power gating circuitry, (b) is with clock gating and (c) is without clock gating                      | 35 |

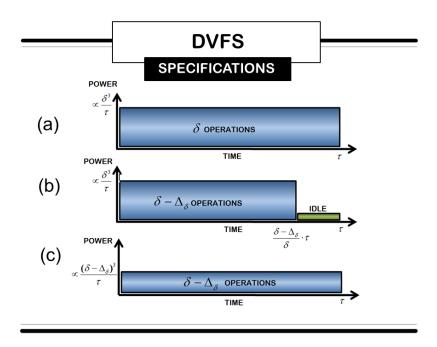

| 2.11 | The inner workings of <i>DVFS</i> where (a) without <i>DVFS</i> , (b) finishing early and                                                                 | 33 |

| 2,11 | (c) finishing just-in-time for dynamic power consumption                                                                                                  | 36 |

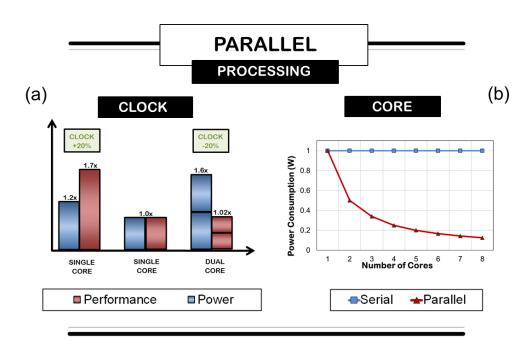

| 2.12 | The inner workings of parallel processing where (a) shows the effect of clocking and (b) the number of cores affecting the performance and power consump- | 30 |

|      | tion on a hardware                                                                                                                                        | 39 |

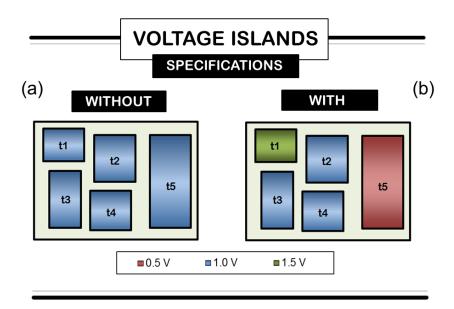

| 2.13 |                                                                                                                                                           | 33 |

| 2.13 | islands                                                                                                                                                   | 40 |

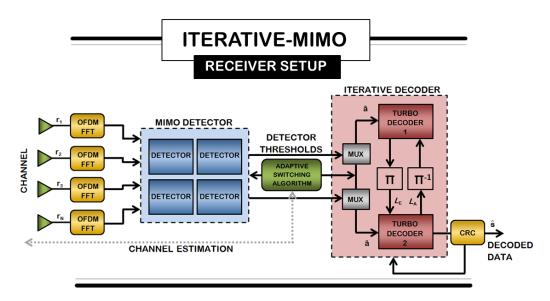

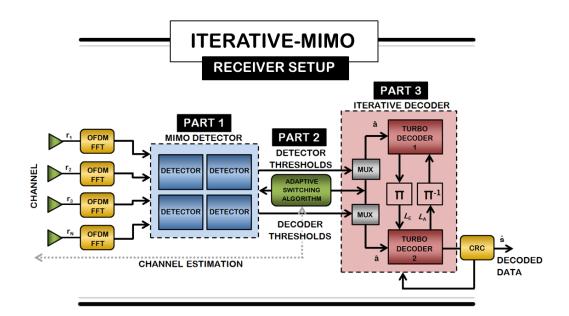

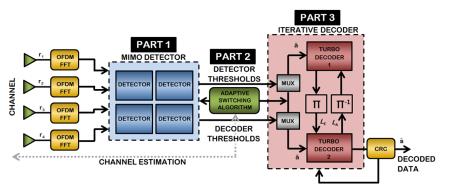

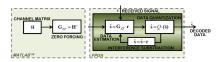

| 3.1  | Iterative-MIMO receiver system                                                                                                                            | 46 |

| 3.2  | Tree structure of (a) SD and (b) FSD and V-BLAST/ZF algorithms                                                                                            | 51 |

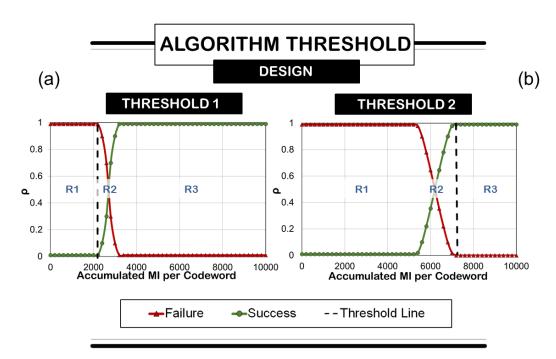

| 3.3  | Probability of receiver successes and failures for a $4 \times 4$ MIMO where (a) for                                                                      |    |

|      | the FSD method and (b) for the V-BLAST/ZF method                                                                                                          | 54 |

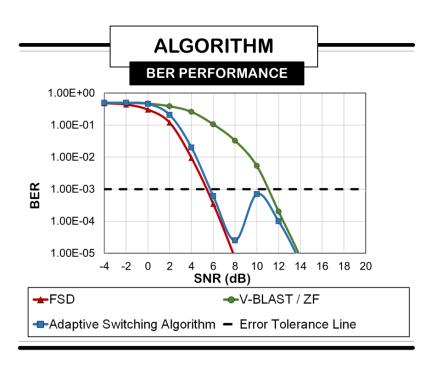

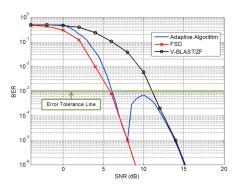

| 3.4  | BER performance of different detectors on a complex $4 \times 4$ MIMO system $$                                                                           | 57 |

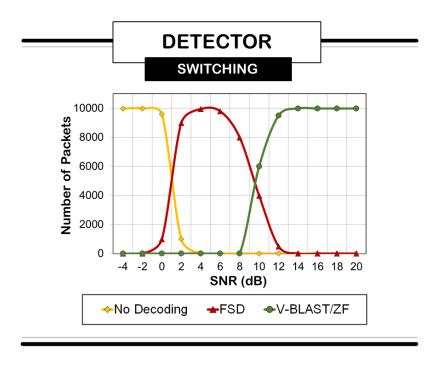

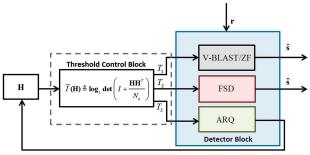

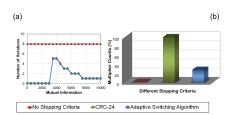

| 3.5  | Detection algorithm switching selection in iterative-MIMO receiver                                                                                        | 58 |

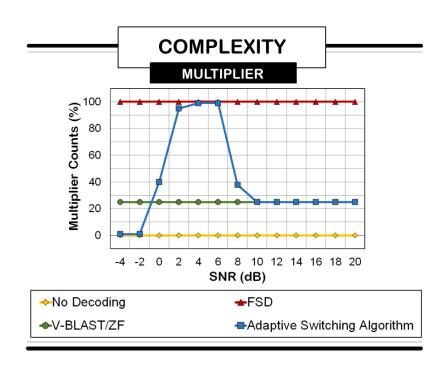

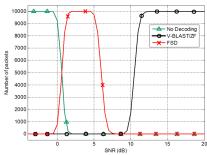

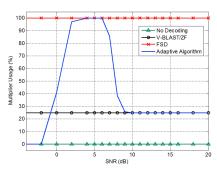

| 3.6  | Complexity measurements of multiplier counts between different MIMO detection schemes                                                                     | 59 |

| 3.7  | Complexity count for simple mechanism of different detection algorithm                                                                                    | 59 |

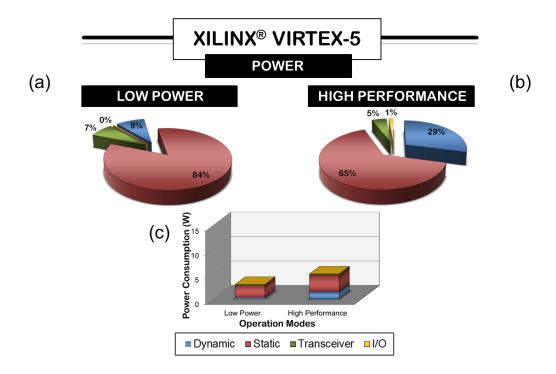

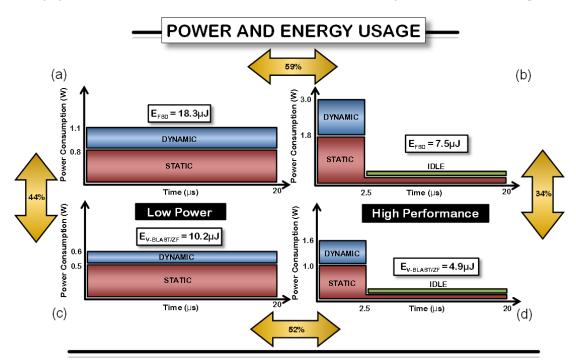

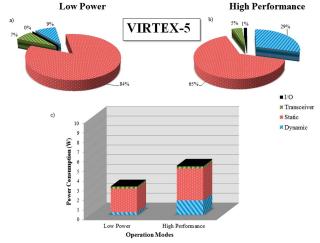

| 3.8  | Total power usage in Xilinx® Virtex-5 hardware design                                                                                                     | 62 |

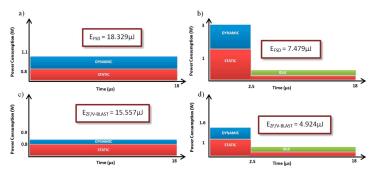

| 3.9  | MIMO detection FSD (a) and (b) in comparison with V-BLAST/ZF (c) and (d)                                                                                  |    |

|      | for "low power" mode and "high performance" mode respectively                                                                                             | 63 |

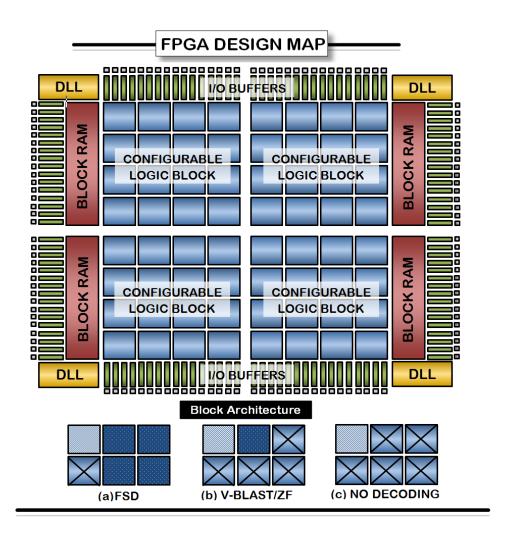

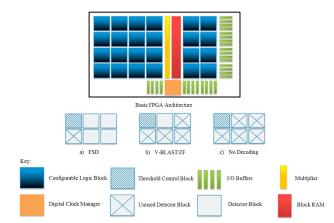

| 3.10 | Total resource allocation of Adaptive Switching Algorithm on a basic FPGA                                                                                 |    |

|      | architecture                                                                                                                                              | 64 |

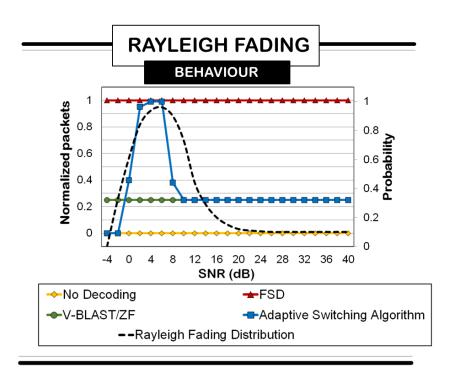

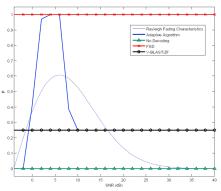

| 3.11       | Detection algorithm behaviours in a Rayleigh fading channel                                                                                                     | 67  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

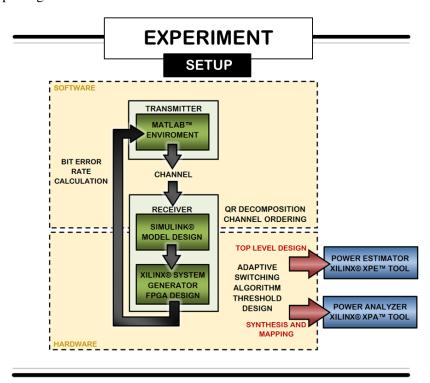

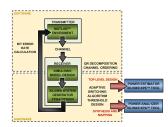

| 4.1        | Flowchart of the software/hardware experimental setup                                                                                                           | 73  |

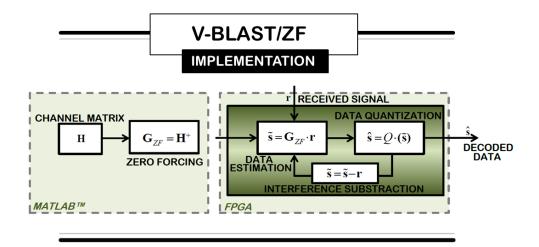

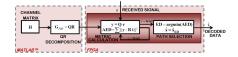

| 4.2        | Breakdown of V-BLAST/ZF FPGA implementation model                                                                                                               | 75  |

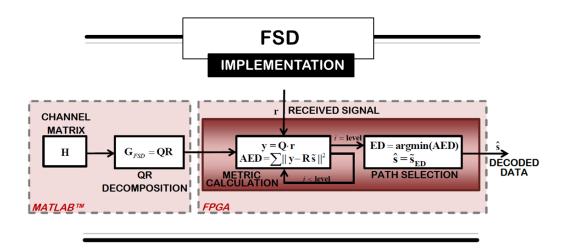

| 4.3        | Breakdown of FSD FPGA implementation model                                                                                                                      | 76  |

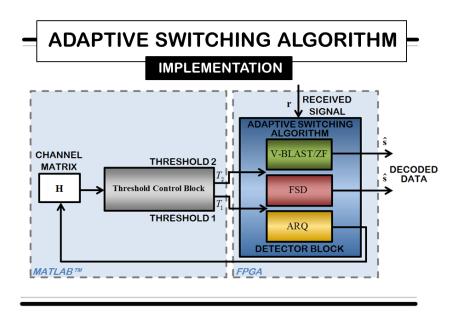

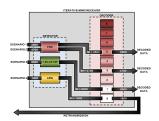

| 4.4        | Breakdown of Adaptive Switching Algorithm FPGA implementation model                                                                                             | 77  |

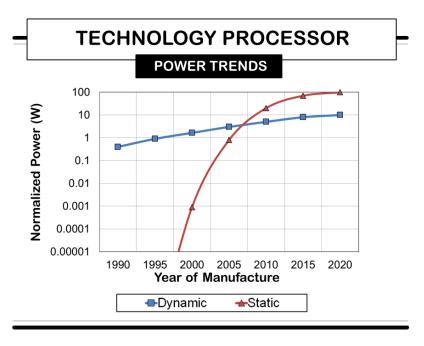

| 4.5        | Dynamic and static power consumption effects on process nodes [117]                                                                                             | 79  |

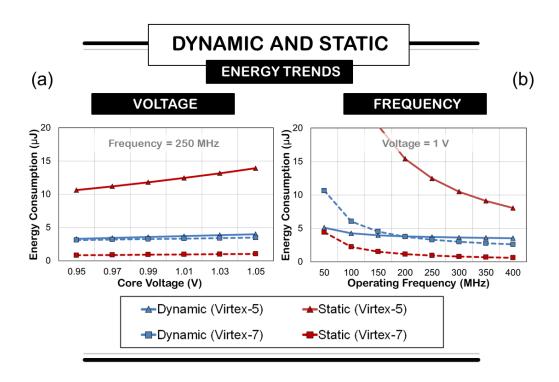

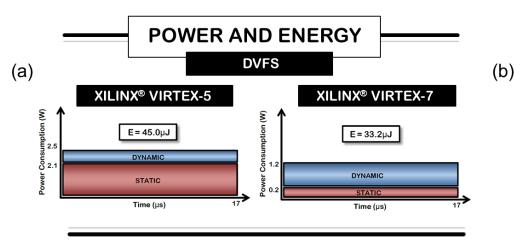

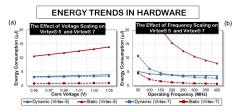

| 4.6        | Energy trends with (a) the voltage applied and (b) the variation of frequencies on the Xilinx® Virtex-5 and Virtex-7 respectively                               | 84  |

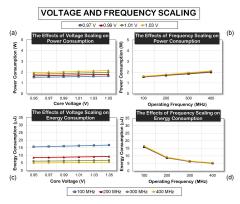

| 4.7        | Power and energy usage for (a) Xilinx® Virtex-5 and (b) Virtex-7 with <i>DVFS</i> applied                                                                       | 85  |

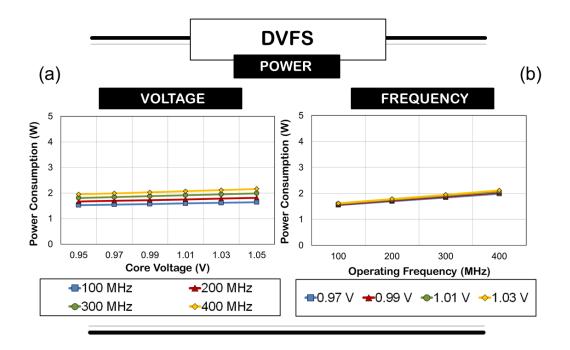

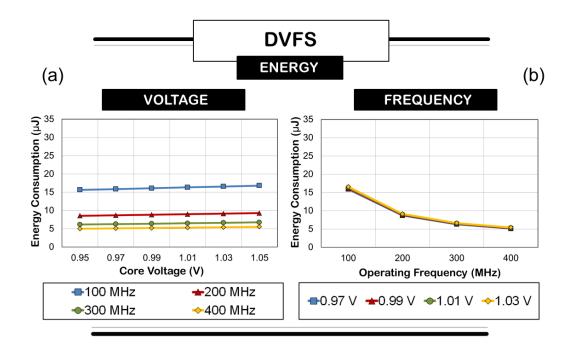

| 4.8        | Scaling effects where (a) is with voltage applied and (b) is with the variation of frequencies respectively for Xilinx® Virtex-7 platform                       | 86  |

| 4.9        | Scaling effects where (a) is with voltage applied and (b) is with the variation of                                                                              |     |

|            | frequencies respectively for Xilinx® Virtex-7 platform                                                                                                          | 87  |

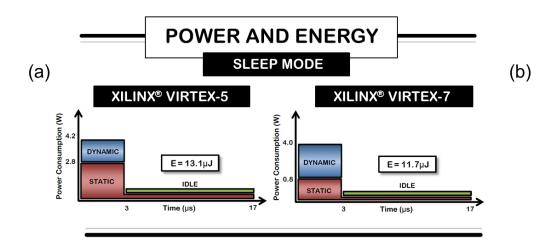

| 4.10       | Power and energy usage for (a) Xilinx <sup>®</sup> Virtex-5 and (b) Virtex-7 with <i>sleep</i>                                                                  |     |

|            | mode utilization                                                                                                                                                | 88  |

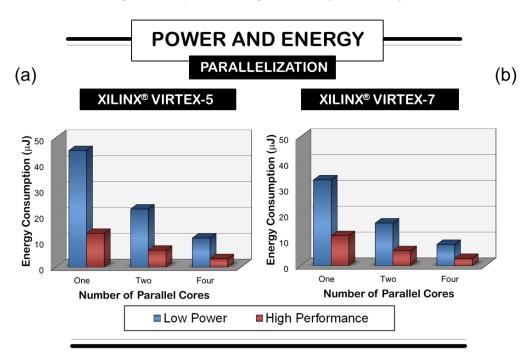

| 4.11       | Energy usage for (a) Xilinx <sup>®</sup> Virtex-5 and (b) Virtex-7 with parallel operations                                                                     | 89  |

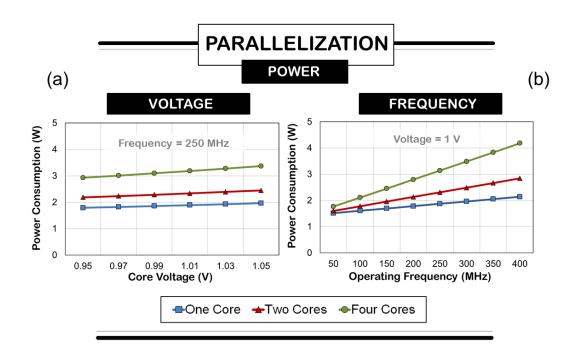

|            | Effects of scaling on power with parallel implementation where (a) with the voltage applied and (b) with the variation of frequencies respectively for Xilinx®  |     |

|            | Virtex-7 platform                                                                                                                                               | 90  |

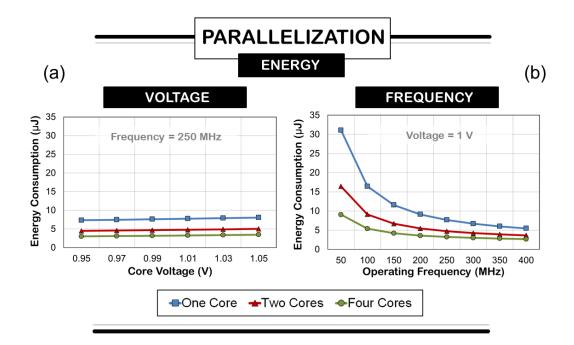

| 4.13       | Effects of scaling on energy with parallel implementation where (a) with the voltage applied and (b) with the variation of frequencies respectively for Xilinx® |     |

|            | Virtex-7 platform                                                                                                                                               | 90  |

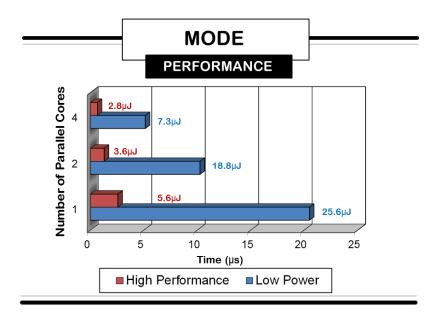

| 4.14       | Comparison of modes on parallel implementation                                                                                                                  | 92  |

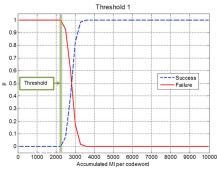

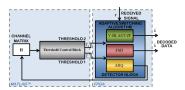

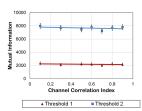

| 5.1<br>5.2 | Iterative-MIMO receiver system under consideration                                                                                                              | 100 |

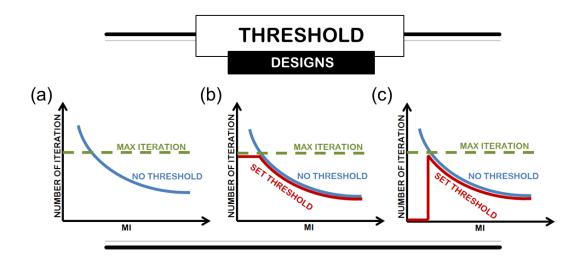

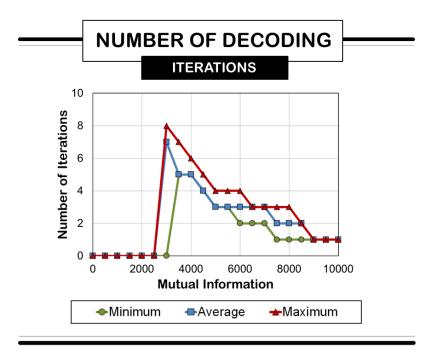

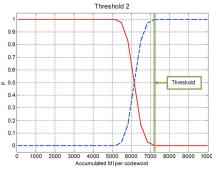

|            | both minimum and maximum thresholds are used                                                                                                                    | 104 |

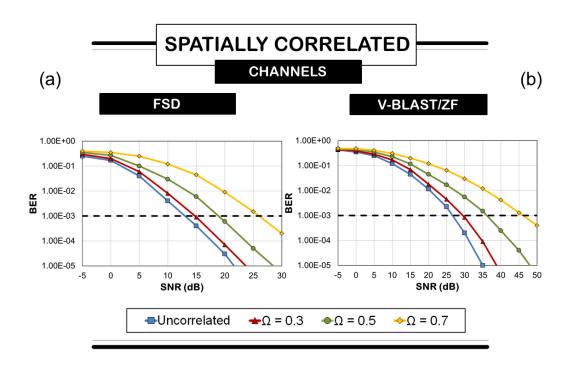

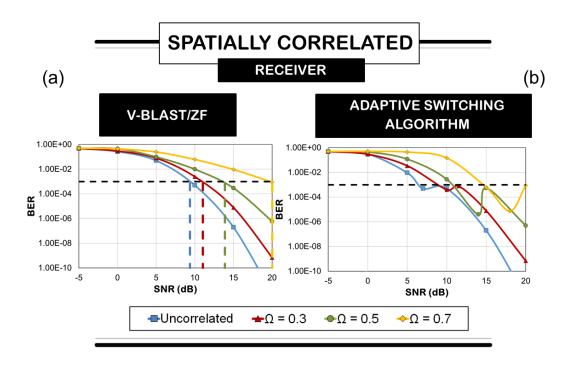

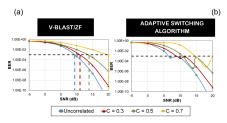

| 5.3        | Comparison of detector performance on spatially correlated channels                                                                                             | 106 |

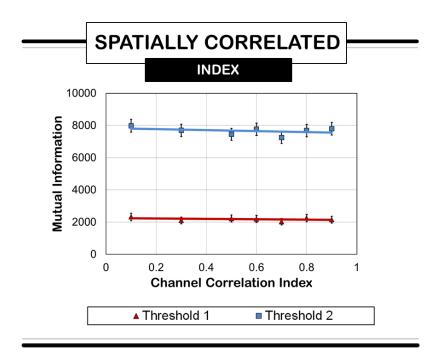

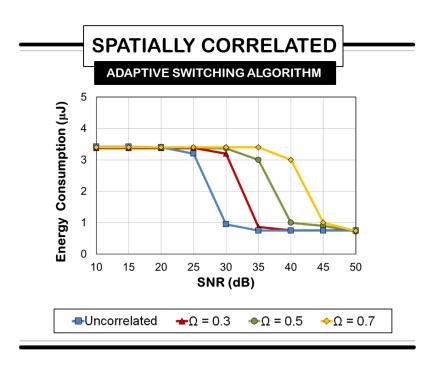

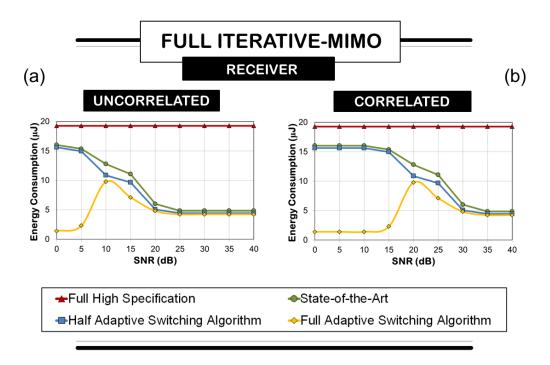

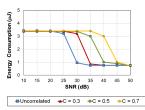

| 5.4        | Comparison of detector energy consumption on spatially correlated channels                                                                                      | 107 |

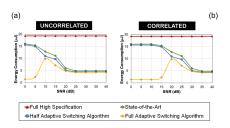

| 5.5        | Energy consumption of the Adaptive Switching Algorithm in spatially corre-                                                                                      |     |

|            | lated channels                                                                                                                                                  | 108 |

| 5.6        | Comparison of detector energy consumption on spatially correlated channels                                                                                      | 110 |

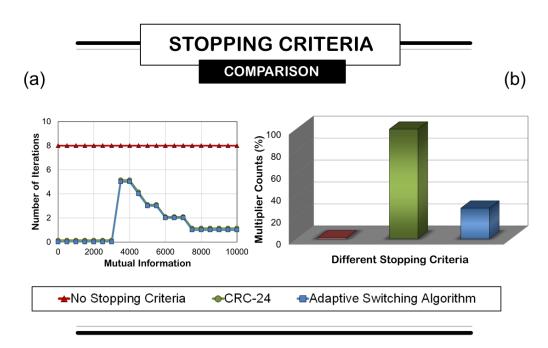

| 5.7        | Comparison of stopping criteria in turbo decoder                                                                                                                | 111 |

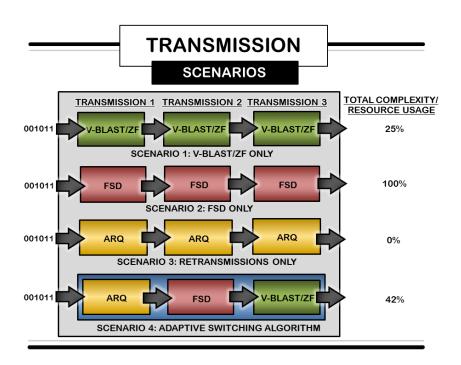

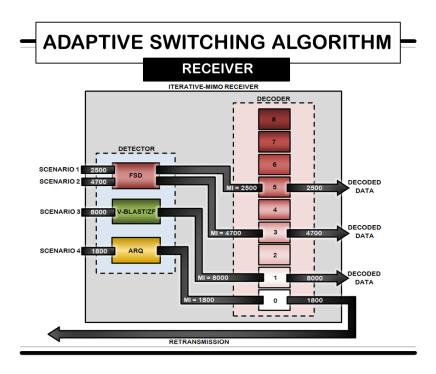

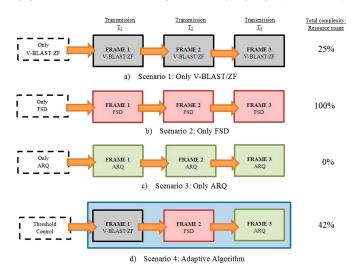

| 5.8        | Different transmission scenarios for Adaptive Switching Algorithm receiver                                                                                      | 113 |

| 5.9        | Performance of turbo decoder in spatially correlated channels                                                                                                   | 115 |

| 5.10       | Full receiver design with Adaptive Switching Algorithm                                                                                                          | 115 |

## List of Tables

| 2.1 | Different algorithm complexity of MIMO detectors measured in kFLOPS            | 22  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.1 | V-BLAST/ZF algorithm                                                           | 50  |

| 3.2 | FSD algorithm                                                                  | 52  |

| 3.3 | Adaptive Switching Algorithm                                                   | 55  |

| 3.4 | Xilinx® Virtex-5 resource utilization for the V-BLAST/ZF and FSD detection     |     |

|     | algorithms                                                                     | 60  |

| 3.5 | Experiment parameters for different detection algorithms                       | 61  |

| 3.6 | Comparison power and energy usage of different detection algorithms on dif-    |     |

|     | ferent channel environment                                                     | 66  |

| 4.1 | Operating parameters for the Xilinx® Virtex-5 and Virtex-7                     | 80  |

| 4.1 | Resource utilization for Adaptive Switching Algorithm                          | 82  |

| 4.2 | Power consumption of Adaptive Switching Algorithm on the Xilinx® Virtex-5      | 02  |

| 4.3 |                                                                                | 83  |

| 4.4 | and Virtex-7                                                                   | 88  |

| 4.4 | The 'low power' and 'high performance' parallel implementations                | 91  |

| 4.3 | The low power and high performance paranel implementations                     | 91  |

| 5.1 | Experimental parameters                                                        | 101 |

| 5.2 | Xilinx® Virtex-7 resource utilization for the V-BLAST/ZF and the FSD detec-    |     |

|     | tion algorithms                                                                | 105 |

| 5.3 | Energy savings of Adaptive Switching Algorithm detector on spatially corre-    |     |

|     | lated channels                                                                 | 108 |

| 5.4 | Complexity breakdown for turbo decoding                                        | 109 |

| 5.5 | Average energy savings of the decoder on Xilinx® Virtex-7                      |     |

| 5.6 | Adaptive Switching Algorithm threshold designs for detector and decoder blocks |     |

|     | of receiver                                                                    | 112 |

| 5.7 | Receiver systems design parameters                                             | 113 |

| 5.8 | Average energy savings of the iterative-MIMO receiver on Xilinx® Virtex-7.     | 116 |

### Acronyms and Abbreviations

AED Accumulated Euclidean Distance

APP A Posteriori Probability

ASIC Application Specific Integrated Circuit

ARQ Automated Repeat ReQuest

AWGN Additive White Gaussian Noise

BICM Bit-Interleaved Coded Modulation

BER Bit-Error-Rate

BPSK Binary Phase-Shift Keying

CE Cross Entropy

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processing Unit

CRC Cyclic Redundancy Code

DSP Digital Signal Processor/Processing

DVFS Dynamic Voltage and Frequency Scaling

EDA Electronic Design Automation

ED Euclidean Distance

EXIT Extrinsic Information Transfer Chart

FER Frame-Error-Rate

FFT Fast Fourier Transform

FLOPS FLoating-point Operations Per Second

FPGA Field-Programmable Gate Array

FSD Fixed Sphere Decoder

GSM Global System for Mobile

HDL Hardware Description Language

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IFFT Inverse Fast Fourier Transform

IID Independent and Identically Distributed

ISE Integrated Software Environment

LLR Log-Likelihood Ratio

LORD Layered ORthogonal Lattice Detector

LTE Long Term Evolution

LTE-A Long Term Evolution Advanced

LUT Look-Up Table

MAP Maximum A Posteriori Probability

ME Mean-Estimation

MI Mutual Information

MIMO Multiple-Input Multiple-Output

MISO Multiple-Input Single-Output

ML Maximum-Likelihood

MMSE Minimum Mean Square Error Estimation

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

OFDM Orthogonal Frequency-Division Multiplexing

PSK Phase-Shift Keying

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase-Shift Keying

SD Sphere Decoding

SIC Successive Interference Cancellation

SIMO Single-Input Multiple-Output SISO Single-Input Single-Output

SNR Signal-to-Noise Ratio

SOCA Smart Candidate Adding Algorithm

SoC System-on-Chip

SOVA Soft-Output Viterbi Algorithm

UMTS Universal Mobile Telecommunications SystemV-BLAST Vertical-Bell Laboratories Layered Space-Time

VCW Valid Code Word Checks

VLSI Very Large Scale Integration Systems

WLAN Wireless Local Area Network

XPA Xilinx® Power Analyzer

XPE Xilinx® Power Estimator

ZF Zero Forcing

## Nomenclature

| ≜                             | Equals to by definition                                             |

|-------------------------------|---------------------------------------------------------------------|

| $\otimes$                     | Kronecker product                                                   |

| $(\cdot)^H$                   | Hermitian transpose operation                                       |

| $(\cdot)^{\mathrm{T}}$        | Conjugate transpose operator                                        |

| β                             | Number of clock cycles per detection                                |

| $\gamma$                      | Number of output of decoder                                         |

| δ                             | Task operation                                                      |

| $\eta$                        | Number of tasks                                                     |

| $\kappa$                      | Number of inputs to decoder                                         |

| $\mu$                         | Complex mean                                                        |

| ξ                             | Number of toggling transistor                                       |

| ho                            | Fading environment                                                  |

| $\sigma^2$                    | Complex AWGN variance                                               |

| au                            | Time                                                                |

| $\omega$                      | Real value correlation coefficient                                  |

| Φ                             | Search sphere radius                                                |

| $\varphi$                     | Code rate                                                           |

| Π                             | Interleaver                                                         |

| Ω                             | Channel correlation index                                           |

| a                             | Encoded and interleaved bits                                        |

| â                             | Demodulated bit vectors                                             |

| A                             | Lower limit of integration                                          |

| b                             | Number of random interleaved coded bits                             |

| b                             | Number of random interleaved coded vectors                          |

| $\mathbb{B}$                  | Set of bit vectors <b>b</b>                                         |

| B                             | Upper limit of integration                                          |

| $\mathbb{C}$                  | Circular symmetric complex Gaussian factor                          |

| C                             | Capacitance of hardware chip                                        |

| $\mathcal{CN}(\mu, \sigma^2)$ | Complex Gaussian distribution with mean $\mu$ and variance $\sigma$ |

- $d_i$  Accumulated Euclidean distance

- $D_i$  Euclidean distance

- e Encoded bits

- $E(\cdot)$  Expected value

- E Energy consumption

- $\mathbf{E}_s$  Energy consumption per symbol bit

- f Clock frequency of a hardware chip

- F Probability density function

- $\mathbf{G}$   $M \times M$  Moore-Penrose pseudoinverse channel matrix of  $\mathbf{H}$

- h Elements of channel matrix **H**

- **H**  $N \times M$  channel matrix

- $\mathbf{H}_w$   $N \times M$  channel matrix unit with  $\mu = 0$  and  $\sigma^2 = 1$

- *i* Iteration number for antenna level

- I  $N \times N$  identity matrix

- $\bar{I}$   $N \times N$  accumulated mutual information

- 3 Imaginary part of a complex number

- j Iteration number for nodes considered in search

- J Throughput of an algorithm in bits per second

- k Number of channel realization in an ordered set  $\S$

- K Constraint length

- K Number of nodes in K-Best considered

- $K_e$  Number of bits per frame

- $K_s$  Number of symbols per frame

- $K_u$  Number of information bits per frame

- $\mathcal{L}$  List of candidates' size in search algorithm

- L Log-likelihood ratio

- $L_A$  A priori log-likelihood bit ratio

- **L**<sub>A</sub> A priori log-likelihood vector ratio

- $L_E$  Extrinsic log-likelihood bit ratio

- $\mathbf{L}_E$  Extrinsic log-likelihood vector ratio

- M Number of transmit antennas

- n Number of nodes in search algorithm

- **n** Additive white circularly symmetric complex Gaussian noise vector

- Number of receive antennas

- $N_0$  Noise power spectral density

- $\mathcal{O}$  QAM constellation of W points

- $p_1$  Output bit from coder 1

- $p_2$  Output bit from coder 2

- P Power consumption

- $Q(\cdot)$  Quantizer argument to the closest point in  $\mathcal{O}^M$

- **Q** Unitary matrix of  $M \times N$

- **r** N-vector of received symbols

- r Receive bit

- **R** Upper triangular matrix of  $M \times N$

- $R_x$  Receiver

- $\mathbf{R}_{Rx}$   $N \times N$  receive spatial correlation matrix

- $\mathbf{R}_{Tx}$   $M \times M$  transmit spatial correlation matrix

- Real part of a complex number

- § Ordered set

- s Transmit bit

- S Total size of search nodes

- $\hat{s}$  Transformation of transmit bit

- **s** *M*-vector of transmitted symbols

- $\hat{\mathbf{s}}$  M-vector of the transformation for the received symbols  $\mathbf{r}$

- Threshold value

- $T_x$  Transmitter

- u Hard data bits

- **û** Detected symbol vectors

- $\mathbf{U}$   $M \times M$  upper triangular matrix

- V Voltage of operating hardware chip

- W Number of QAM constellation points

- **x** General vector description

- y M-vector of decision statistics

- $\hat{y}$  M-vector of estimated statistics

- $\mathcal{Z}$  Subset of  $\mathcal{O}$

## Chapter 1 **Introduction**

Wireless communication has become the fastest growing segment of the communications industry. It has gone through remarkable advancement in the 20th century and along with it, electronic circuit design is also progressing at an exponential rate. Recent innovations in wireless communication technology and computing have led to the current proliferation of devices, each with specific applications, form factor, functionality and battery lifetime. The explosive growth in wireless systems coupled with the proliferation of electronics devices indicate a bright future for wireless networks, both as stand-alone and as a part of a larger networking infrastructure. However, many technical challenges remain in designing robust wireless networks and devices that deliver the performance necessary to support emerging applications. One major challenge materializes in the form of power. With approximately 14 billion electronic devices are connected online; personal ones, such as mobile phones, laptops, set-top boxes, modems, and/or on a larger scale; base stations, wireless hotspots and femtocells, the communication sector has become one power hungry industry. The devices are estimated to waste around US\$ 80 billion each year due to inefficient designs. This trend could lead to an estimated loss of around US\$ 120 billion by the end of 2020 [1]. Therefore, solutions are sought to overcome the current predicament. This introductory chapter provides a brief review of wireless communications and describes the motivation behind the work that has been undertaken, the technical challenges, and finally the possible contributions this work aims to accomplish.

#### 1.1 Motivation of Work

Due to the large number of devices available, just by reconfiguring the design for each individual device chipsets to be more efficient, would have tremendous impact on the global energy usage. With the adoption of best available technologies, chipsets are able to possess a higher degree of software and hardware flexibility to be more efficient in radio systems. It is said that such devices could perform exactly the same tasks while consuming around 65% less power [1]. Therefore, motivation of this work is to tackle the power consumption problem head on starting from each individual device.

There are two sides to the coin, the **wireless communication** side, which deals with the tremendous data demands, and the other, the **computer architecture** side, where a more efficient implementation is sought for better hardware deployment. On the **wireless communication** side, traffic volume according to regions as depicted in Figure 1.1, taken from the report in [1], shows that data demand is increasing over the years. It is predicted that by the end of 2017, with the fastest growing inclination, the data for Asia Pacific will be more than triple, reaching to about 45 exabyte (EB) in just 5 years. In other regions, demands are also rising year by year. The total world demand for data per year amounts to more than 120 EB per month.

Figure 1.1: Projected data traffic growth

In order to cater for this trend in data demand, a significant breakthrough came in the late 1980s when the adaptive use of multiple-input multiple-output (MIMO) antenna systems was proposed. By using multiple antennas at both transmit and receive sides, parallel channels that utilize the same radio spectrum space can be created. MIMO manipulates this to increase the capacity of a channel so more data can be transmitted at one time. While minimizing power usage in these devices in wireless networks is imperative, more priority is given to the receivers since they handle massive computation processing. With billions of devices available, the total power consumption would be massive. Moreover, the receivers are usually limited in power

source where they are operated using a battery, which has a limited lifetime. This brings us to the subject of **computer architecture**. Future wireless receivers aim at supporting a wide variety of wireless communication standards, such as the Long-Term Evolution (LTE), Universal Mobile Telecommunications System (UMTS), wireless local area network (WLAN), and Global System for Mobile (GSM). Key enabling technology for the enormous success of wireless communication is the progress in integrated circuit (IC) technology. It started in the late 1950s with the production of the first metal-oxide-semiconductor field-effect transistors (MOS-FET) and with the idea of complementary metal-oxide-semiconductor (CMOS) circuits [2]. IC follows the trend given by Moore's law, which states that the number of transistors in a dense integrated circuit has doubled approximately every two years. Electronic design automation (EDA) software tools help handle larger and faster chips, fabrication technologies for supporting new technology nodes, and verification strategies for the increased circuit complexity. The progress in CMOS IC technology made it possible to pack more and more transistors onto the same area of silicon. This progress allowed to realize increasingly complex functions on a small piece of silicon. With this, the realization of a fast Fourier transform (FFT), a real-time detection and decoding algorithms, or an entire wireless baseband processor on a single chip became feasible.

Figure 1.2 shows the potential energy savings that can be achieved with growing technology in programming and IC circuitry. It depicts the proportion of savings that can be accomplished to compute a given operation, and that the devices of today do not fully reap these benefits in the designs. By the year 2015, just by implementing power minimization techniques to evoke a more efficient hardware design, 70% of potential energy savings can be gained, and this trend continues to rise up to a point where, in 2025, it is predicted that around 87% of energy usage can be conserved if more efficient designs are implemented in these devices. In order to have a more efficient design, flexible software and hardware implementation are needed for the whole receiver. To achieve this flexibility, the processor circuit and signal processing software need to have certain adaptivity whereby they possess a level of 'intelligence'. In principle, this would allow the exchange between transmission standards and algorithms at boot or even dynamically at run-time. This could be in the form of a system that is able to adapt to the detection algorithm on-the-fly to the current operating scenario according to the requests of the system. Current radio communication devices have incorporated digital signal processing (DSP)-based programmability for some receiver blocks. However, many computationally intensive parts still require dedicated hardware for performance and efficiency reasons. This issue is particularly crucial for MIMO transceivers, where the volume of incoming data is multi-fold, and therefore the energy required to process would be immensely large.

**Figure 1.2:** *Potential energy savings trend* [1]

This aspect of **computer architecture** and the power management schemes have not been fully exploited. Even though the technology exists, several power minimization techniques are not properly optimized on devices that support MIMO. This thesis therefore proposes a more efficient design for a receiver that rivals the state-of-the-art available in the market today. With the combination of both fields of knowledge, another setback to take into account when designing an efficient hardware capable of transmitting large amounts of data is that when a signal propagates through a wireless channel, it experiences random fluctuations in time if the transmitter or receiver is moving, due to changing reflections and attenuations. Thus, the characteristics of the channel appear to change randomly with time, which makes it difficult to design reliable systems with guaranteed performance. This is imperative to keep in mind in order to confirm the applicability of the new design in realistic situations.

In summary, technological advances in the following areas are needed to overcome the challenges this work aims to tackle:

- Algorithmic design for the MIMO detection and decoding algorithms that support efficiency in implementations.

- Hardware design suitable for low-power handheld computer and communication receiver terminals, which can be implemented on current and future communication systems.

- Measurements and models for wireless indoor and outdoor channels in order to verify the design suited for real-life deployment.

Given these requirements, the work draws from many areas of expertise, which includes the area of communications, signal processing, software and hardware design, and power management schemes. Moreover, given the fundamental limitations of the wireless channels and the explosive demand for its utilization, communication between these interdisciplinary groups is necessary to implement the most rudimentary shell for the thesis work.

#### 1.2 Thesis Contributions

The objective of this work is to design an efficient iterative-MIMO receiver fit for current and upcoming wireless communication standards. The main contributions of this work are distributed in three separate chapters. The chapters integrate into one another to culminate in achieving the main objective of the thesis, which is to design an efficient adaptive algorithm that possesses a level of 'intelligence' for iterative-MIMO receivers. Each stage of the work leads to the next logical progression from experimental to design practicality, as detailed below:

- An Adaptive Switching Algorithm that adapts to real-time channel conditions to minimize the power and energy consumption of iterative-MIMO detection systems is proposed. This is realized in the form of a threshold control unit, which selects the minimum complexity detector capable of meeting the desired bit-error-rate (BER) performance. The adaptive algorithm shows promising BER performance on par with the current available detection schemes with lower resource utilization. An evaluation of the new algorithmic design shows convincing dynamic and static power savings compared to baseline detectors.

- Realistic power and energy saving trends of the Adaptive Switching Algorithm are computed for the chosen hardware circuitry. Detailed power and energy analysis and the

assessment of potential benefits of specific power minimization techniques show more promising results compared to the others. The combination of both the algorithmic design and the hardware design adaptivity results in tremendous gains in the overall proposed design.

• The performance of the Adaptive Switching Algorithm in realistic conditions shows significant power and energy savings with slight BER degradation. The proposed algorithm is suitable to be used as a link between the detector and iterative decoder blocks in the receiver, as a stopping criteria tool to help determine the number of decoding iterations needed per transmission. Hardware design implementation for the proposed algorithm maintains the performance of the Adaptive Switching Algorithm total receiver design in spatially correlated channels with a lower hardware utilization complexity to boot.

#### 1.3 Thesis Outline

The thesis is structured into several chapters covering different stages of the work, following a logical flow of information, starting with the development from theoretical concepts and continuing on with the three main contributions of the research; the proposed Adaptive Switching Algorithm, the design performance of the proposed algorithm on hardware and finally, the performance of the hardware design in realistic channel conditions to test its readiness for real world applicability. The structure of each chapter is described below:

Chapter 2 is divided into two parts, viz. the wireless communication and the computer architecture. The wireless communication part explains the total iterative-MIMO systems and provides additional background on the detecting and decoding techniques. For a reader who is familiar with modern wireless communication systems, this part will serve mainly as a refresher as it introduces the concept of MIMO systems that provides the foundation of the research. The computer architecture part presents the different hardware types available and various power minimization techniques labelled as state-of-the-art, each of which promises significant power savings. The combination of the two fields of knowledge provides the comprehensive understanding required as basis for the work described in this thesis.

The proposed novel innovation of the Adaptive Switching Algorithm introduced in **Chapter 3** proves to be suitable for the sole purpose of saving power and energy consumption of the overall receivers in both slow and fast fading environments. The algorithm works by switching between

thresholds pre-calculated between the transmitters and receivers during each transmission in real-time. This novel idea is the first of its kind to produce an 'intelligent' system based on switching from a high to a low complexity detector, exploiting full information of the current channel conditions of a MIMO system. The adaptivity shows that promising savings can be gained in comparison to non-adaptive iterative-MIMO detectors.

Having shown the potential power and energy savings that can be achieved within the receiver design with the proposed algorithmic design of the Adaptive Switching Algorithm, the next stage of work as described in **Chapter 4** extends those findings by incorporating the novel idea of the Adaptive Switching Algorithm onto hardware design, to promote its applicability in implementations as well. With efficient design, the proposed algorithm shows that significant power and energy savings can be gained when different power minimization techniques are utilized. A comprehensive power and energy performance analysis of the Adaptive Switching Algorithm is investigated for the iterative-MIMO systems, with the primary goal of minimizing additional power and energy consumption within the receiver. The work is then extended to examine the potential benefits of several power minimization techniques during the implementation of the Adaptive Switching Algorithm. An in depth investigation shows that power and energy usage can be further optimized when the design for the proposed algorithm is designed on state-of-the-art hardware.

After having demonstrated in the preceding chapters that the Adaptive Switching Algorithm could save significant complexity, power and energy consumption in both algorithmic and hardware design implementation in experimentally controlled conditions, its effectiveness in real-world situations is then verified in **Chapter 5**, whereby the proposed algorithm is executed under spatially correlated channel conditions. The performance of the Adaptive Switching Algorithm in these channel conditions shows that significant energy savings can be gained with slight BER degradation as the correlation between the transmitters and receivers increases. The chapter describes how forwarding the proposed algorithm threshold information to the decoder, which by providing the same necessary information used in the detector as a stopping criteria for the decoder, helps limit the number of iteration(s) required during each transmission. Significant power and energy savings are achieved for the full Adaptive Switching Algorithm receiver in comparison to state-of-the-art hardware, with lower hardware utilization complexity to boot.

The concluding remarks about this work, as presented in Chapter 6, enumerates the major

contributions while identifying the novel aspects and improvements in comparison to other research that has been carried out in the same area. Special attention is also paid to the specific areas that could potentially be studied in future work. An appendix that contains a list of publications originating from this work is attached and included as references throughout the thesis.

## Chapter 2 **Background**

#### 2.1 Chapter Contribution

The work described in this thesis revolves around designing an efficient iterative-MIMO receiver that is suitable for state-of-the-art wireless communication standards. This chapter aims to provide comprehensive knowledge in the areas of wireless communications for software design and computer architecture for the hardware design implementation. The combination of each field of specialization gives the background information required to help the reader in understanding the nature of the work. The chapter begins by introducing the wireless communication system under consideration and the blocks within the iterative-MIMO systems i.e. the detector and the decoder. After a brief description regarding each block, the chapter progresses to the other area of specialization, namely the computer architecture. Several power minimization techniques in hardware are discussed in detail to shed light on the state-of-the-art methods currently available in the market. The chapter concludes by summarizing the chosen methods in this thesis for detecting and decoding and the reason behind them. It also pinpoints the best power minimization techniques to investigate in this study. Both information will lead to better understanding of the upcoming technical chapters.

#### 2.2 Wireless Communication

Wireless communication is the transfer of information between two or more points that are not connected by an electrical conductor. The most common wireless technologies use radio. Figure 2.1 illustrates the different antenna configurations for wireless communication links. Single-input single-output (SISO), shown in Figure 2.1(a) is effectively a standard radio channel. This type of configuration has one transmitter and one receiver. Due to its simplicity, SISO requires no extra processing for manipulating the diversity that may be used. The disadvantage of SISO is that it is vulnerable to interference and fading. Moreover, the throughput is dependent on the channel bandwidth and the signal-to-noise ratio (SNR), which means it is

bounded by Shannon's law. The single-input multiple-output (SIMO) version is depicted in Figure 2.1(b) and the multiple-input single-output (MISO) is shown in Figure 2.1(c). Due to the usage of multiple antennas, there are several advantages that can be gained when compared to their SISO counterpart. SIMO or MISO is able to increase the receive SNR by coherently combining the wireless signals to achieve array gain. Moreover, diversity gain, which can be classified as transmit or received diversity, are used to combat fading. The receive diversity does this by enabling the receiver to receive signals from a number of independent channels. Transmit diversity on the other hand, generates redundant data from the multiple transmitters for the one receiver to choose from. This is when the signal is transmitted over multiple (ideally) independent fading paths in time, frequency, or space. This allows the receiver to select the optimum signal to extract the required data. The advantages of using multiple transmitters are that it creates redundancy in coding and moves processing from the receiver to the transmitter. This is highly beneficial for the receiver. The lower processing requirement, which leads to lower power consumption, will have a positive impact on the size needed for multiple antennas, as well as the cost and battery lifetime. In addition, the usage of multiple antennas exploits the spatial dimension to increase the separation between users by directing signal energy towards the intended user. This is **interference reduction**. Lastly, **spatial multiplexing gain** in the multiple antenna setup provides additional data capacity by utilizing the different paths to increase the data throughput capability [3] [4] [5].

By combining the configurations, MIMO may exploit all the advantages provided by the configurations of others [6], from the aforementioned techniques of **array gain**, **diversity gain**, **spatial multiplexing gain** and **interference reduction**. MIMO, as illustrated in Figure 2.1(d), uses multiple antennas at both the transmitters and receivers. It enables a variety of signal paths to carry the data, choosing separate paths for each antenna to enable multiple signal paths to be used. It is found that the signal can take many paths between a transmitter and a receiver. Additionally, by moving the antennas even by a small distance, the paths used by the signal will change. The variety of paths available occurs as a result of the number of objects that appear to the side or even in the direct path between the transmitter and receiver. By using MIMO, these additional paths provide additional robustness to the radio link by improving the SNR, or by increasing the link data capacity. As a result, it is able to considerably increase the capacity of a given channel by increasing the number of receive and transmit antennas. MIMO increases the throughput of the channel linearly with every pair of antennas added to the system. Moreover, as spectral bandwidth is becoming an ever more valuable commodity for radio

Figure 2.1: Channel transmission configurations

communications systems, MIMO is one of the techniques needed to properly exploit available bandwidth more effectively as well. Hence, depending on the purpose of the MIMO system, an appropriate trade-off needs to be found. Due to the increasing demand of data mentioned in the previous chapter, **spatial multiplexing** provides the capacity to cater for this need. The aim of this work is therefore, to find the right trade-off in a system that incorporates **spatial multiplexing**, between the complexity or power consumption and the system performance.

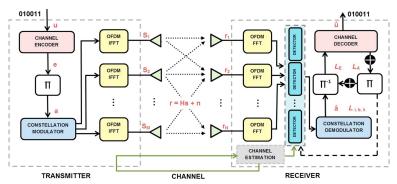

#### 2.2.1 Iterative-MIMO System Architecture

A typical iterative-MIMO architecture is illustrated in Figure 2.2. An in-depth explanation of the full iterative-MIMO system can be found in the next section, however, as an overview, the system can be partitioned into three segments; the **transmitter**, the **channel** and the **receiver**. The **transmitter** is made up of several components. The hard data bits, u, first go through the channel encoder. The channel encoder appends extra data bits to make the data transmission more robust to interferences on the transmission channel. There are many coding schemes available and they can basically be categorized into two major types; linear block codes and convolutional codes. In a typical iterative-MIMO system, the latter is used, specifically the

turbo encoder, where two convolutional codes are used in parallel with some kind of interleaving in between. This gives the encoded e bits, which are interleaved. These are being passed through to the constellation modulator where the bits are mapped onto a digital scheme such as the quadrature amplitude modulation (QAM) or the phase-shift keying (PSK). By representing the transmitted bits a as a complex number and modulating a cosine or sine carrier signal with real ( $\Re$ ) and imaginary ( $\Im$ ) parts respectively, the symbols can be sent with two carriers on the same frequency. Once the symbols are modulated, they are split into several streams depending on the number of transmitters used before being transmitted over a **channel**. The transmission **channel** is essentially a path between two nodes in a network.

Figure 2.2: Iterative-MIMO system channel

Consider a spatial multiplexing MIMO-orthogonal frequency-division multiplexing (OFDM) system with M transmitters, N receivers, and  $M \ge N$ . The channel can be represented by the matrix described in Equation (2.1).

$$\mathbf{r} = \mathbf{H}\mathbf{s} + \mathbf{n} \tag{2.1}$$

where the channel matrix  $\mathbf{H} \in \mathbb{C}^{M \times N}$  with independent elements  $h_{i,j} \sim \mathcal{CN}(\mu, \sigma^2)$ , for  $1 \leq i \leq M$  and  $1 \leq j \leq N$  representing a block fading propagation environment, with  $\mu = 0$  and  $\sigma^2 = 1$ ,  $\mathbf{s} = (s_1, s_2, \dots, s_M)^{\mathrm{T}}$  is the transpose vector of the M-dimensional

transmit symbol vector with  $E[|\mathbf{s}_i|^2] = M^{-1}$ ,  $\mathbf{n}$  is the  $\mathbb{C}^{N\times 1}$  additive independent and identically distributed (i.i.d.) circular symmetric complex Gaussian noise vector normalized so that its covariance matrix is the identity matrix, i.e.  $\mathbf{n} \sim (0, N_0 \mathbf{I}_N)$  of  $h_{i,j} \sim \mathcal{CN}(0, N_0)$  and  $\mathbf{r} = (r_1, r_2, \dots, r_N)^{\mathrm{T}}$  is the transpose N-vector of received symbols. Throughout this thesis, the SNR is defined as the average SNR per receive antenna according to Equation (2.2).

$$SNR = \frac{M\mathbf{E}_s}{N_0} \tag{2.2}$$

where  $\mathbf{E}_s$  is the energy per transmit symbol s. The received symbols,  $\mathbf{r}$ , are then processed by the **receiver**. From Figure 2.2, first, the symbols are multiplexed into a single stream before being detected by the MIMO detector to give  $\hat{\mathbf{u}}$  bit streams.

In the **receiver**, the detection can be solved in many ways. In order to optimally solve the MIMO detection problem, an exhaustive search for the best solutions can be performed over all signal constellations. The number of possible signal constellations increases exponentially with the number of antennas and the number of bits per modulation symbol. Maximum-Likelihood (ML) detection finds the minimum constellation point in Equation (2.1) within the received symbols. It is given by:

$$\hat{\mathbf{s}}_{ML} = \underset{\mathbf{s} \in \mathcal{O}^M}{\operatorname{arg \, min}} \| \mathbf{r} - \mathbf{H} \mathbf{s} \|^2$$

(2.3)

where  $\mathcal{O}$  denotes the constellation size of a specific modulation. The ML detector is optimal and fully exploits all available degree of freedom. Even though ML produces the best BER performance, due to its use of exhaustive search, it can have immense complexity for direct implementation. The complexity grows exponentially with the transmission rate  $\varphi$ , since the detector needs to go through  $2^{\varphi}$  hypotheses for each received vector. For example, for the case of a  $4\times 4$  iterative-MIMO system employing 16-QAM, the detector would need to search a total of  $S=16^4=65,536$  candidates in order to find the correct transmitted vector. For 64-QAM, this number rises to more than  $S=64^4=16,777,216$ . This makes an exhaustive search infeasible for a hardware implementation [7]. As the optimal exhaustive search is far too complex for hardware implementations, many sub-optimal detection algorithms exist with a big range in communications performance and complexity. Several efficient suboptimal detection techniques have therefore been proposed or adapted from the field of multi-user detection.

Even though these techniques are much less computationally demanding than the ML detector, they are often unable to exploit a large part of the available degree of freedom, and thus, their performance tends to be significantly poorer than that of ML detection. However, this trade-off can be made for efficient hardware designs.

Back to Figure 2.2, after the detection, the symbols are then forwarded to the constellation demodulator where the symbols are demapped to get â before going to the turbo decoder, with two constituent decoders working together with deinterleavers in between them. These iterative decoders then produce the hard output for the received symbol bits. Within the **receiver** is where the focus of the work lies. This involves around minimizing power and energy consumption within the iterative-MIMO receiver, particularly, by re-designing the MIMO detector and the iterative decoder parts of the system. The sections below explain different types of detectors and decoders available, and their advantages and disadvantages are highlighted to showcase parts that need to be improved for a better performance in power and/or energy consumption. Finding the right trade-off between communications performance with implementation complexity, and understanding the implications on the whole receiver is one of the major challenges in the design of iterative-MIMO receivers.

#### 2.2.2 MIMO Detectors

MIMO detection algorithms can be seen as a "tree search" problem, as shown in Figure 2.3. This is realized by inverting the channel matrix  $\mathbf{H}$  using the  $\mathbf{Q}\mathbf{R}$ -decomposition to decompose matrix  $\mathbf{H}$  into a unitary matrix  $\mathbf{Q}$  of dimension  $M \times M$  and an upper-triangular matrix  $\mathbf{R}$  of dimension  $M \times N$  according to:

$$\mathbf{H} = \mathbf{Q}\mathbf{R} \tag{2.4}$$

The system model in Equation (2.1) can be left-multiplied by the Hermitian transpose of  $\mathbf{Q}$ , which is the  $\mathbf{Q}^H$ , to give:

$$\hat{\mathbf{y}} \triangleq \mathbf{Q}^H \mathbf{r} = \mathbf{R}\mathbf{s} + \mathbf{n} \tag{2.5}$$

When the problem is visualized as a "tree search", the ML detection rule as given in Equation

(2.3) can be approximated as:

$$\hat{\mathbf{s}}_{ML} \approx \underset{\mathbf{s} \in \mathcal{O}^M}{\operatorname{arg \, min}} \parallel \hat{\mathbf{y}} - \mathbf{R}\mathbf{s} \parallel^2$$

(2.6)

**Figure 2.3:** *MIMO detection as a tree diagram for* 4-QAM *modulation on a*  $4 \times 4$  *MIMO system*

Figure 2.3 depicts the search traversing down level i, looking through j nodes until the solution is found, where the  $\mathcal{O}$  is the number of constellation points in respective modulation scheme. Since  $\mathbf{R}$  is upper-triangular, the minimization in Equation (2.3) corresponds to a "tree search" problem, where the nodes on level i are associated with a partial symbol vector  $\mathbf{s} = [s_i, ..., s_M]^T$  and with a corresponding squared partial Euclidean distance (ED),  $d_i(\mathbf{s})$ . The squared partial ED is given by:

$$d_i(\mathbf{s}_i) = d_{i+1}(\mathbf{s}_{i+1}) + |D_i(\mathbf{s}_i)|^2$$

(2.7)

with i = M, M - 1, ..., 1. The distance increments  $|D_i(\mathbf{s}_i)|^2$  are computed as:

$$|D_i(\mathbf{s}_i)|^2 = |\hat{y}_i - \sum_{j=i}^M R_{ij} s_j|^2$$

(2.8)

Therefore, the squared ED for the ML solution is given as:

$$d_{ML} = \min_{\mathbf{s} \in \mathcal{O}^M} (d_1(\mathbf{s}_1)) \tag{2.9}$$

and the ML solution is the associated  $s_1$ . With this illustration in mind, the task of a MIMO-detector is to find the vector  $s_1$  that leads to the smallest  $d_i$ , i.e. the leaf node with the smallest squared partial ED.

To this end, a vast amount of literature exists that presents algorithms and approximations to process the tree in a clever way in order to find the estimate  $\hat{s}$  with less computational effort than an exhaustive search. The trade-off between the different approaches consists of implementation complexity, BER performance, and throughput.

#### 2.2.3 Hard-Output MIMO Detection

The output of a MIMO detection algorithm is either a hard-output decision (the estimate  $\hat{s}$ ), or an *a posteriori* probability (APP) for each bit of the transmitted symbol vector. The latter helps further improve the performance of a MIMO detector. This soft-output iterative-MIMO detection algorithms were introduced in [8], and will be described in the next section. A hard-output MIMO detector delivers an estimate  $\hat{s}$  of the transmitted symbol vector s. Starting point is the input-output relation as given in Equation (2.1). Several algorithms exist to obtain the estimate  $\hat{s}$ . In general, these are divided into linear detection, successive interference cancellation (SIC) detection, and ML detection methods.

#### 2.2.3.1 Linear Detectors

A linear detector first separates the data streams with a linear filter and then decodes each stream independently. The computational complexity of linear hard-output MIMO detection is small in comparison to other detection schemes. However, the BER performance is significantly worse compared to ML detection. Examples of linear detectors are Zero Forcing (ZF) and minimum

mean square error (MMSE) filters apply an inverse of the channel to the received signal in order to restore the transmitted signal [9]. These linear filters can be implemented at a low complexity, however, their performance is very low as well.

The **ZF** detector inverts the effect of the channel matrix, **H**. The corresponding channel filter matrix  $G_{ZF}$  is given by Equation (2.10).

$$\mathbf{G}_{ZF} = (\mathbf{H}^H \mathbf{H})^{-1} \mathbf{H}^H \tag{2.10}$$

where  $G_{ZF}$  is the Moore-Penrose pseudoinverse of H. Left-multiplying Equation (2.1) with  $G_{ZF}$  yields the ZF estimate of:

$$\hat{\mathbf{y}}_{ZF} = \mathbf{G}_{ZF}\mathbf{r} = \mathbf{s} + \mathbf{G}_{ZF}\mathbf{n} \tag{2.11}$$

to obtain the symbol-vector estimate  $\hat{\mathbf{s}}$ , the equalized noise  $\mathbf{G}_{ZF}\mathbf{n}$  is ignored and each element of  $\hat{\mathbf{y}}_{ZF}$  is mapped to the closest constellation point according to Equation (2.12).

$$\hat{s}_i = [\hat{y}_i]_{\mathcal{O}}, \quad \text{for } i = 1, ..., M$$

(2.12)

The ZF detection removes the co-channel interference and it is the ideal detector when the channel is noiseless, i.e.  $\mathbf{n} = 0$ . However, in a real system, the noise is enhanced and correlated by  $\mathbf{G}_{ZF}$ , which is the main reason for the poor BER performance of ZF detection. This phenomenon is known as noise-enhancement [10].

The **MMSE** detector considers the noise power in the interference cancellation and therefore shows a slightly better performance. It reduces the effect of noise-enhancement by minimizing the total error, including the noise term, according to Equation (2.13).

$$\mathbf{G}_{MMSE} = \underset{\mathbf{G} \in \mathbb{C}^{M \times N}}{\operatorname{arg \, min}} \parallel \mathbf{Gr} - \mathbf{s} \parallel^{2}$$

(2.13)

The MMSE estimator matrix  $G_{MMSE}$  can be computed as in [10] to give Equation (2.14).

$$\mathbf{G}_{MMSE} = (\mathbf{H}^H \mathbf{H} + \frac{M}{\text{SNR}} \mathbf{I}_M)^{-1} \mathbf{H}^H$$

(2.14)

Left multiplication of Equation (2.1) by  $G_{MMSE}$  yields:

$$\hat{\mathbf{y}}_{MMSE} = \mathbf{G}_{MMSE}\mathbf{r} = \sqrt{\frac{N}{\mathbf{E}_s}}\mathbf{s} + \mathbf{G}_{MMSE}\mathbf{n}$$

(2.15)