En vue de l'obtention du

#### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Université Toulouse 3 Paul Sabatier

Présentée et soutenue le jeudi 10 décembre 2015 par :

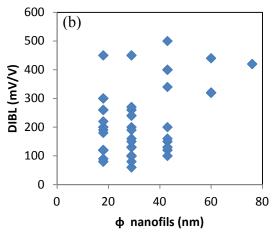

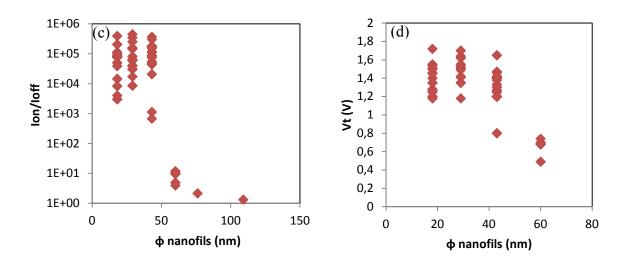

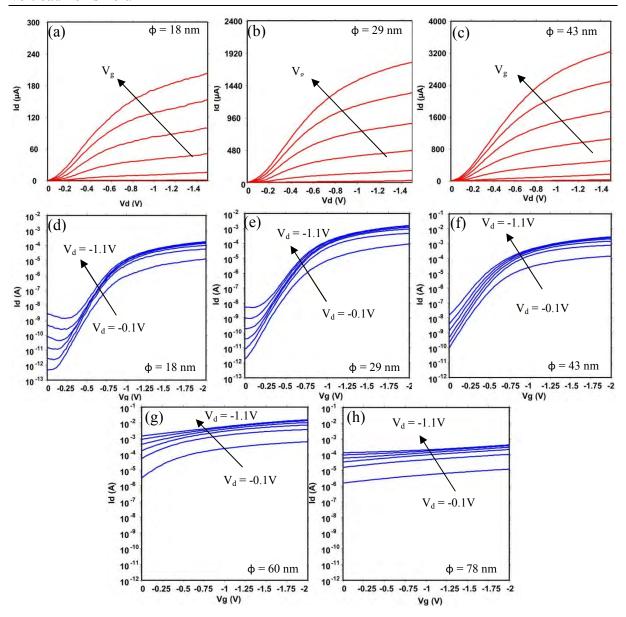

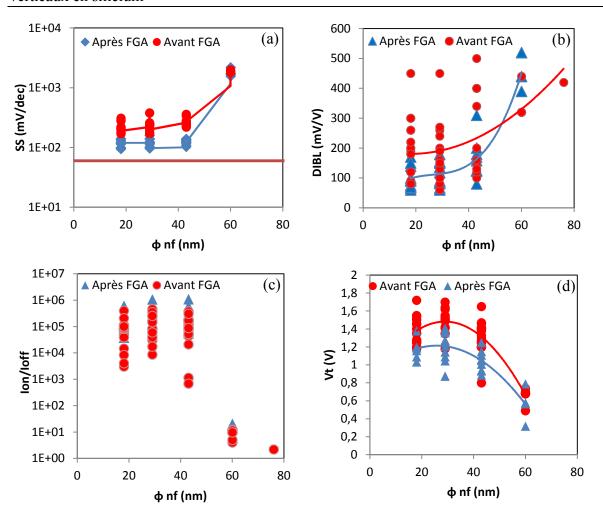

#### Youssouf GUERFI

Réalisation et caractérisation de transistors MOS à base de nanofils verticaux en silicium

#### **JURY**

SYLVAIN BOLLAERT LAURENT PICHON ALAIN CAZARRE BASSEM SALEM Professeur d'Université Professeur d'Université Professeur d'Université Chargé de recherche

Rapporteur Rapporteur Président Examinateur

École doctorale et spécialité :

GEET : Micro et Nanosystèmes

Unité de Recherche:

Laboratoire d'Analyse et d'Architecture des Systèmes (UPR 8001)

Directeur(s) de Thèse:

Guilhem LARRIEU et Filadelfo CRISTIANO

Rapporteurs:

Sylvain BOLLAERT et Laurent PICHON

À la mémoire de mon père, Ahmed GUERFI (1951 – 2002).

À ma mère, tu as toujours su me montrer la voie à prendre, m'encourager et me soutenir. Je te dois tout.

À mes sœurs et mon frère Said, merci pour votre aide et soutien, vous êtes tout pour moi.

À mes oncles, tantes, mes cousins et cousines, ainsi que toute ma grande famille, vous êtes ma fierté.

À mes beaux parents et mes belles sœurs, votre rencontre est un cadeau de la vie.

À Rahim, ton oncle sera toujours là pour toi ainsi que pour tes frères et ta sœur.

Enfin, à ma femme, ta présence à mes côtés m'est vitale, merci pour ta patience, ton soutien indéfectible et tes encouragements.

Je remercie mes responsables de thèse, Guilhem LARRIEU et Filadelfo CRISTIANO de m'avoir donné l'opportunité de faire ma thèse sur un sujet qui m'a tant inspiré. Sans oublier toute l'équipe MPN.

Mes remerciements vont également à Alain Cazarre, professeur d'Université Paul Sabatier et président de mon jury de thèse.

Merci à Laurent PICHON professeur d'université Rennes 1 et Sylvain BOLLAERT professeur d'université Lille 1 d'avoir accepté de rapporter mes travaux de thèse. Merci également à Bassem SALEM, chargé recherche au LTM-CNRS de faire partie de mon jury de thèse en tant qu'examinateur.

Je tiens à exprimer ma profonde gratitude à Franck CARCENAC de m'avoir fait profiter de sa grande expérience et me permettre d'acquérir une expertise dans le domaine de la micro et nanotechnologie. Ta porte a toujours été ouverte pour moi, tu as toujours eu du temps pour répondre à mes questions, me donner une piste et me conseiller, un soutien technique et moral, MERCI! Sans sortir du bureau, je tiens à remercier Jean Baptiste DOUCET et Emmanuelle DARAN pour leur aide et agréables discussions. Voila un bureau très chaleureux.

Je remercie toute l'équipe TEAM, pour leur disponibilité et leur aide pour la réalisation de ces travaux. Notamment, Eric IMBERNON et Jean-Christophe MARROT, Ludovic SALVAGNAC et Pascal DUBREUI, Bernard ROUSSET et Adrian LABORDE.

Merci à tous mes ami(e)s et collègues du LAAS; Moustafa ZERARKA, Hakim TAHIR, Imad et Walid BOURENNANE, Mohamed MATMAT, Fehd BETTAHAR, Fadhila SEKLI, Abdelilah EL KHADIRY, Said HOUMADI, Valentina CASTAGNOLA Amel ALI SLIMANE, Sabeha et Amel ZEDEK, Hajer MAKHLOUFI, Adem et Ahmet LALE, Sami ABADA, Brice ADELIN, et Abdenour AOUINA. Je m'excuse auprès de ceux que j'ai oublié.

Mes remerciements, vont à mes amis des deux rives de la méditerranée, tout d'abord, à Abdelaziz LARGUET, Mohamed IHADDADEN, El Hachemi ADMANE, Noureddine TCHIKOU et Djallel BENSALAH et ainsi ceux qui ont décidé de faire la traversée avec moi pour poursuivre nos études, en l'occurrence Adel SAADI et Djamel TOUBAL MAAMAR.

# Table des matières

| Introduction | générale                                                                  | 10  |

|--------------|---------------------------------------------------------------------------|-----|

| Bibliograp   | ohie                                                                      | 14  |

| Chapitre 1:  | Le MOSFET élément de base de l'industrie semiconducteur                   | 16  |

| Introduction | on                                                                        | 17  |

| 1.1 Le       | MOSFET                                                                    | 19  |

| 1.1.1        | Structure de base et principe de fonctionnement                           | 19  |

| 1.1.2        | Régime de fonctionnement                                                  | 20  |

| 1.2 Me       | étriques du MOSFET                                                        | 21  |

| 1.2.1        | Etat bloqué : faible inversion                                            | 22  |

| 1.2.2        | Etat passant : forte inversion                                            | 23  |

| 1.3 Mi       | niaturisation du MOSFET                                                   | 24  |

| 1.4 Ef       | fets de canaux courts                                                     | 26  |

| 1.4.1        | DIBL et perçage volumique                                                 | 27  |

| 1.4.2        | Effet du champ électrique longitudinal                                    | 28  |

| 1.5 Al       | ternative aux effets canaux courts et amélioration des performances       | des |

| MOSFETs      |                                                                           | 29  |

| 1.5.1        | Résistances séries                                                        | 29  |

| 1.5.2        | Introduction des contraintes dans le canal de conduction                  | 30  |

| 1.5.3        | Matériaux à constante diélectrique élevée (High K) et grille métallique . | 31  |

| 1.5.4        | Silicon On Insulator (SOI) MOSFET                                         | 33  |

| 1.5.5        | Multiples grilles                                                         | 33  |

| 1.6 Tra      | ansistor sans jonction                                                    | 37  |

| 1.7 No       | ouvelles structures : architectures nanofils                              | 39  |

| 1.7.1        | Architecture horizontale                                                  | 40  |

| 1.7.2 Architecture verticale                                          | 46 |

|-----------------------------------------------------------------------|----|

| 1.8 Pourquoi une architecture verticale ?                             | 50 |

| 1.9 Objectif de la thèse                                              | 51 |

| 1.10 Conclusion                                                       | 51 |

| Bibliographie                                                         | 53 |

| Chapitre 2 : Réalisation de réseaux de nanofils verticaux en silicium | 63 |

| Introduction                                                          | 64 |

| 2.1 Réalisation du masque de gravure                                  | 65 |

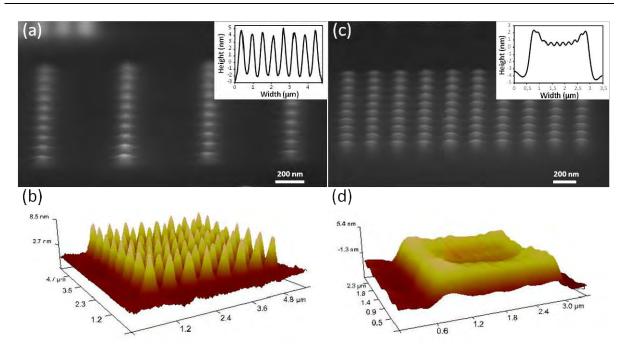

| 2.1.1 Lithographie électronique                                       | 65 |

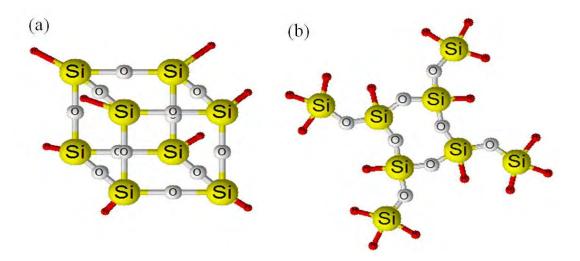

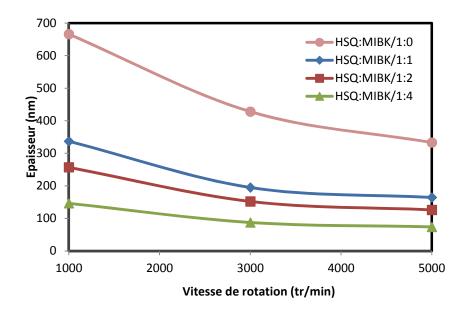

| 2.1.2 Hydrogène SilsesQuioxane (HSQ)                                  | 66 |

| 2.1.3 Exposition de la HSQ à la lithographie électronique             | 66 |

| 2.1.4 Révélation de la HSQ                                            | 69 |

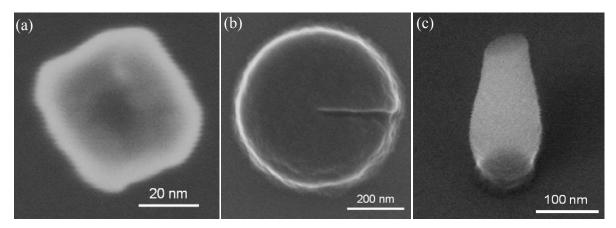

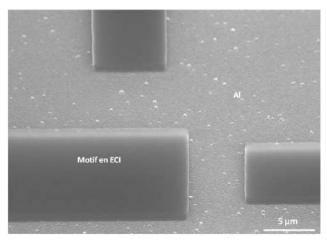

| 2.1.5 Approche classique                                              | 70 |

| 2.1.6 Amélioration de l'anisotropie                                   | 71 |

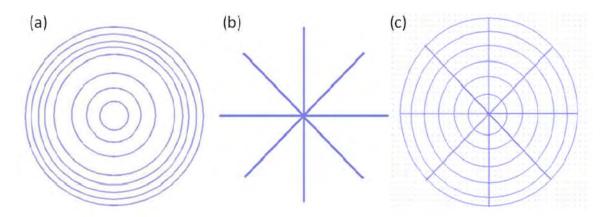

| 2.1.7 Amélioration de la circularité                                  | 72 |

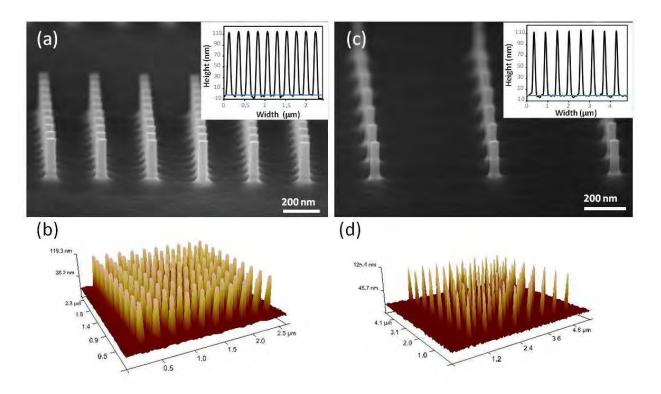

| 2.2 Transfert des nanofils dans le substrat : gravure du silicium     | 77 |

| 2.2.1 Procédé de gravure                                              | 78 |

| 2.2.2 Mécanisme de gravure du silicium par plasma chloré              | 79 |

| 2.2.3 Expérimentation                                                 | 80 |

| 2.2.4 Influence de l'ICP                                              | 81 |

| 2.2.5 Vitesse de gravure et sélectivité                               | 83 |

| 2.3 Amincissement des nanofils                                        | 83 |

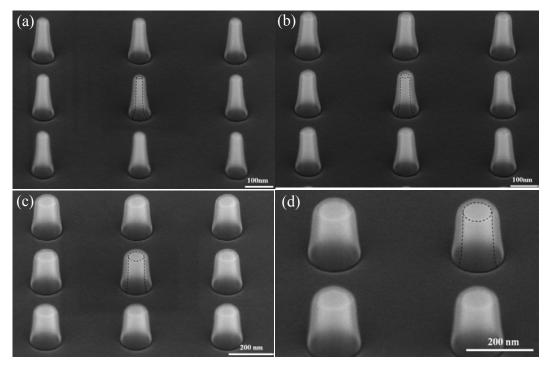

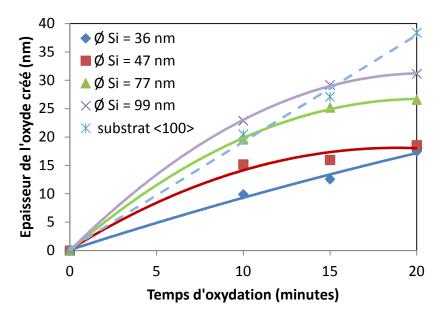

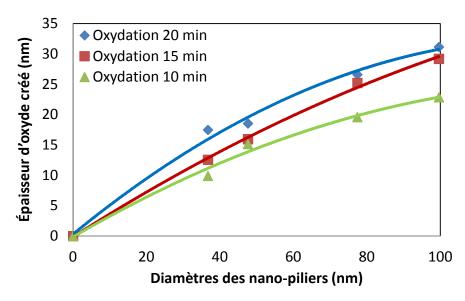

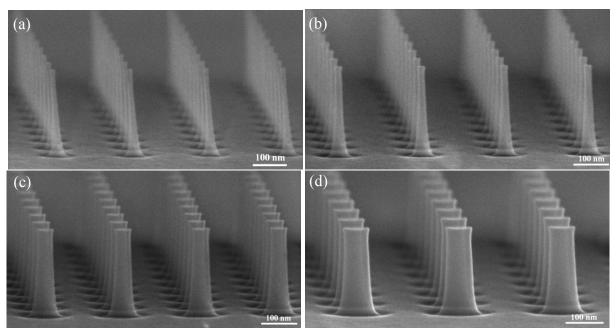

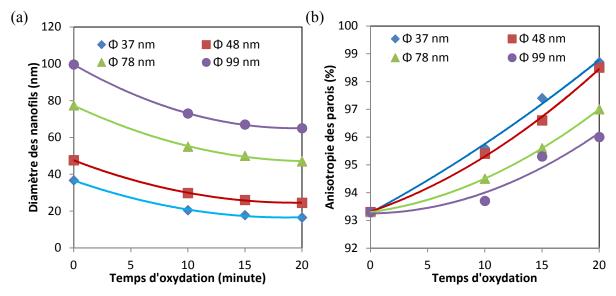

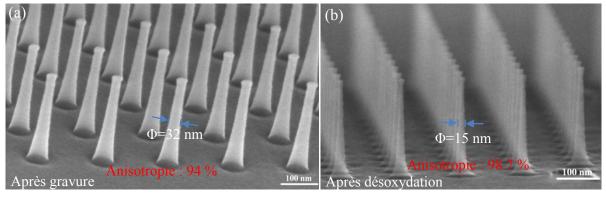

| 2.3.1 Oxydation thermique des réseaux de nanofils en silicium         | 84 |

| 2.3.2 Mécanisme physique d'oxydation retardée                         | 87 |

| 2.3.3 Bilan d'oxydation thermique des réseaux de nanofils             | 89 |

| 2.4 Oxyde de grille                                                   | 91 |

| 2.5 Conclusion                                                        | 91 |

| Biblio       | graphie                                                               | 92          |

|--------------|-----------------------------------------------------------------------|-------------|

| Chapitre     | 3 : Technologie de fabrication de transistors MOS à base de NFV en s  | ilicium 97  |

| Introd       | uction                                                                | 98          |

| 3.1          | Réalisation des contacts source et drain de faible hauteur de barrièr | re Schottky |

| aux trous    | 98                                                                    |             |

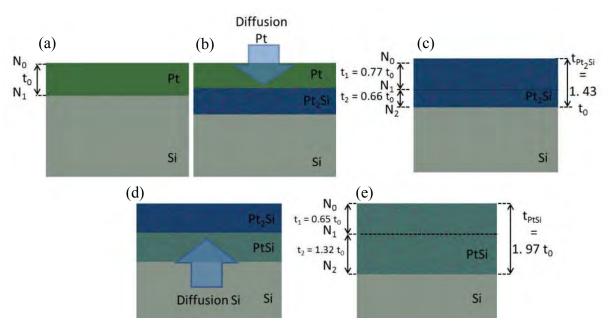

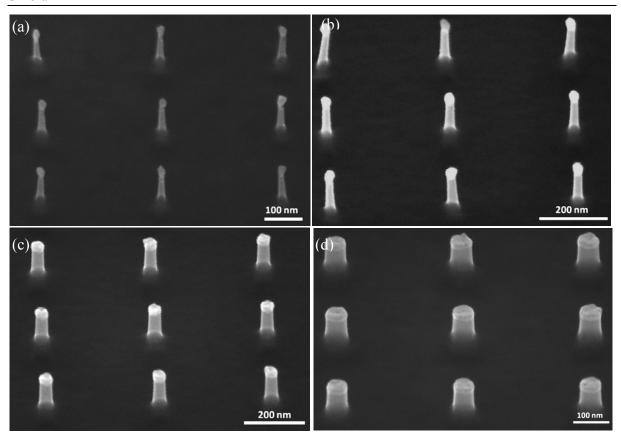

| 3.1.         | 1 Techniques de formation des siliciures                              | 99          |

| 3.1.         | 2 Mécanisme de formation du siliciure de platine (PtSi)               | 99          |

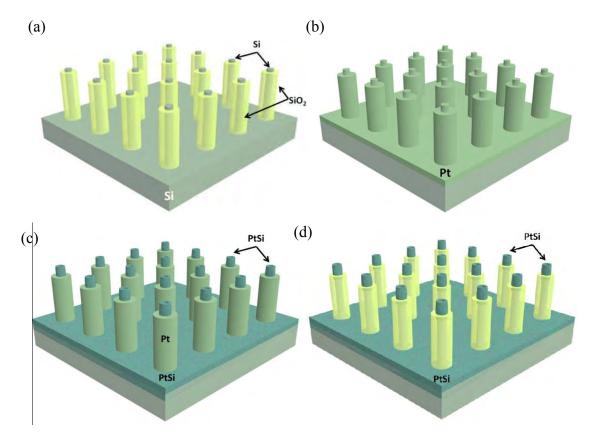

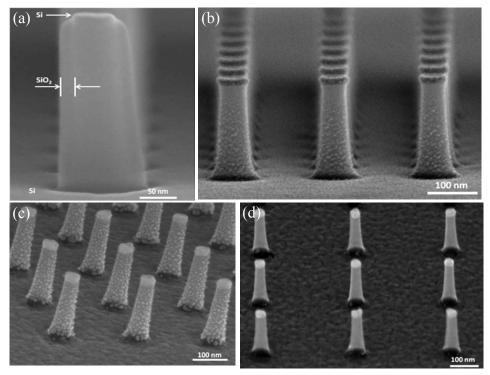

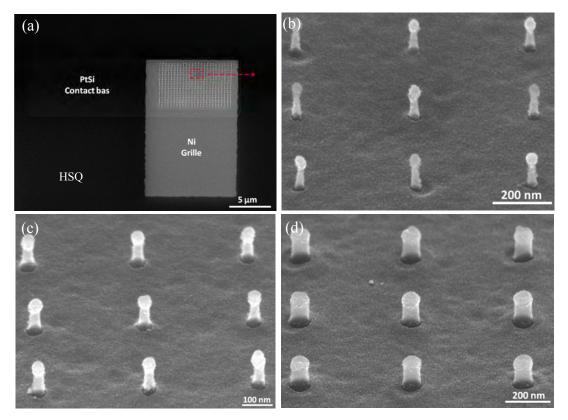

| 3.1.         | Formation du PtSi sur les réseaux NFV en Si                           | 102         |

| 3.1.         | 4 Gravure de l'oxyde de silicium                                      | 103         |

| 3.1.         | 5 Siliciuration de platine sur nanofils                               | 104         |

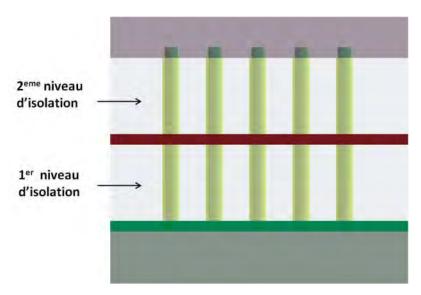

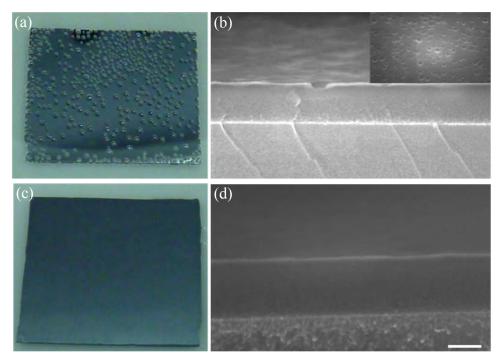

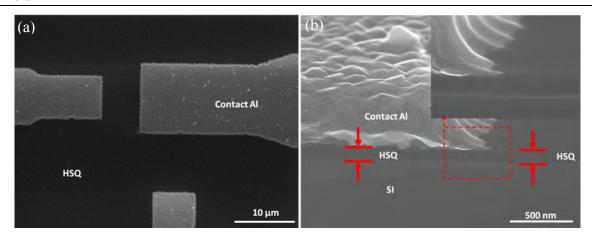

| 3.2          | Réalisation des couches d'isolation                                   | 104         |

| 3.2.         | 1 Matériaux isolants et techniques de planarisation                   | 105         |

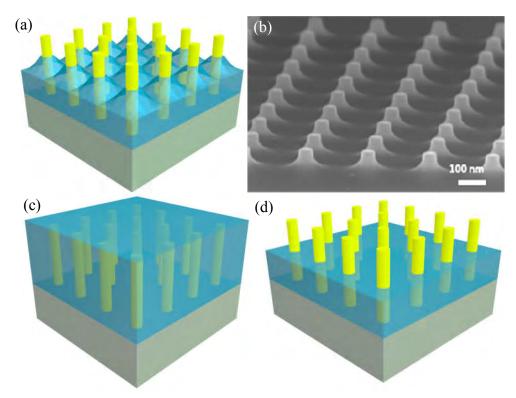

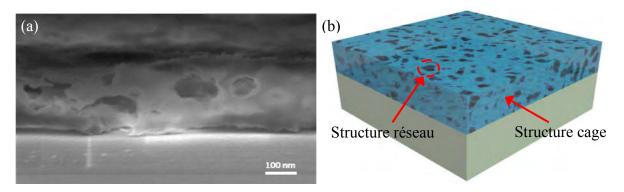

| 3.2.         | 2 Réalisation de la couche d'isolation inférieure                     | 106         |

| 3.2.         | Niveau d'isolation supérieur                                          | 113         |

| 3.3          | Photolithographie                                                     | 115         |

| 3.3.         | Procédé monocouche pour lift off                                      | 116         |

| 3.3.         | 2 Verrous technologiques : incompatibilité développeur résine – H     | SQ 121      |

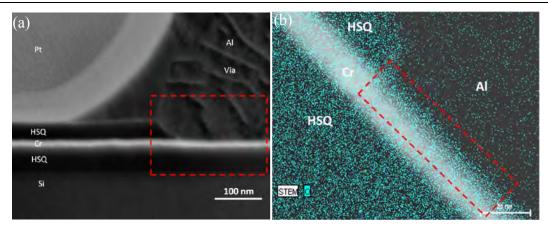

| 3.3.         | 3 Structuration des métaux                                            | 122         |

| 3.3.         | 4 Réalisation du contact de grille.                                   | 123         |

| 3.3.         | 5 Qualité de dépôt                                                    | 124         |

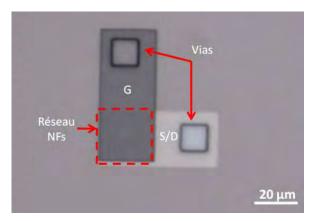

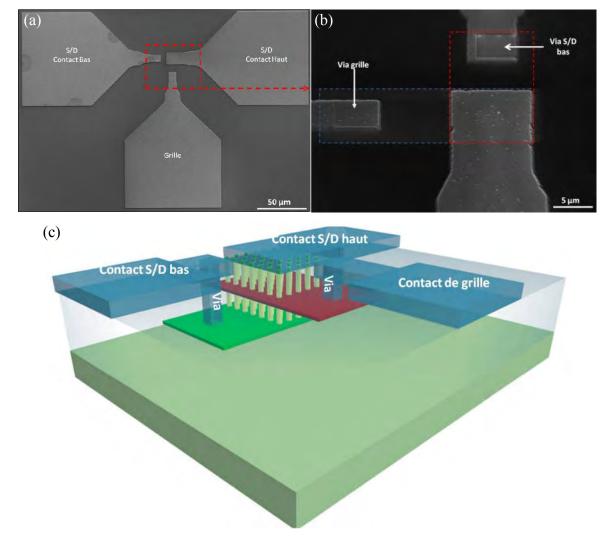

| 3.3.         | 6 Réalisation des vias et plots de contact                            | 126         |

| 3.4          | Conclusion                                                            | 128         |

| Biblio       | graphiegraphie                                                        | 130         |

| Chapitre     | 4 : Caractérisation électrique de transistors MOSFET à base of        | de nanofils |

| verticaux en | Si                                                                    | 133         |

| Introd       | uction                                                                | 134         |

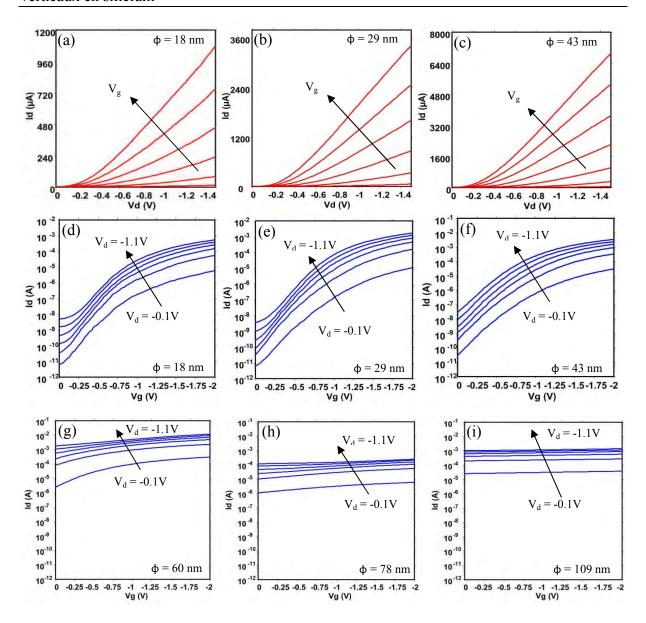

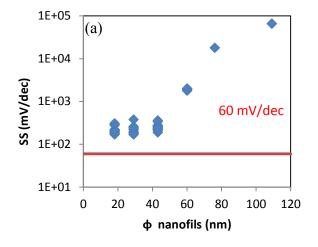

| 4.1          | Caractéristiques des composants                                       | 134         |

| 4.2          | Caractéristiques I(V)                                                 | 134         |

# Table des matières

| 4.3      | Physique du composant                  | 141 |

|----------|----------------------------------------|-----|

| 4.4      | La longueur naturelle                  | 141 |

| 4.5      | La tension de seuil (V <sub>th</sub> ) | 142 |

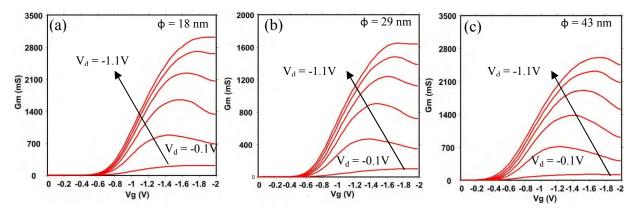

| 4.6      | La transconductance                    | 143 |

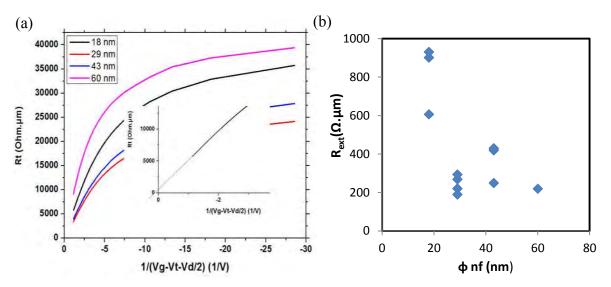

| 4.7      | Extraction des résistances séries.     | 144 |

| 4.8      | Extraction de la mobilité apparente    | 144 |

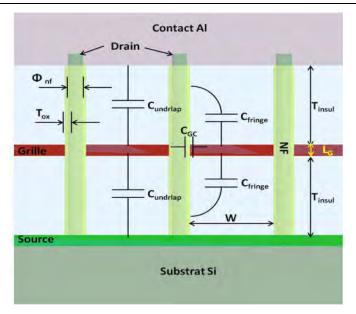

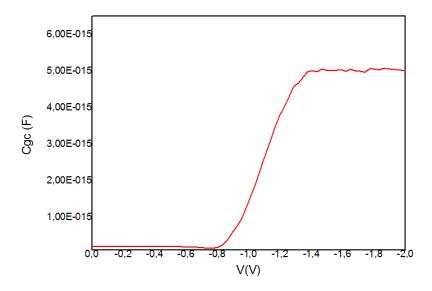

| 4.8      | Evaluation de la capacité de grille    | 145 |

| 4.9      | Inverseurs CMOS                        | 147 |

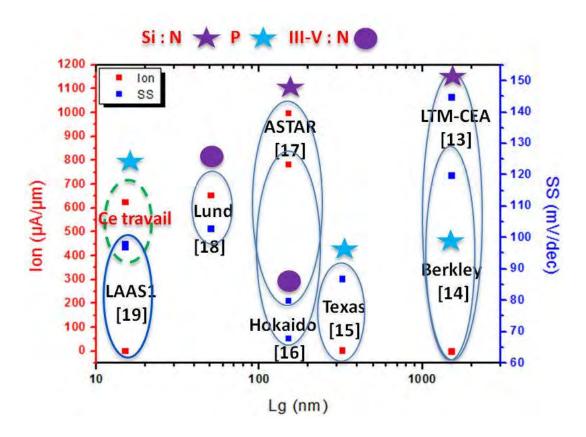

| 4.10     | Etat de l'art                          | 149 |

| 4.11     | Conclusion.                            | 150 |

| Biblio   | ographie                               | 152 |

| Conclus  | sion et perspectives                   | 155 |

| 5.1      | Conclusion générale                    | 156 |

| 5.2      | Perspectives                           | 157 |

| 5.2      | Etudes complémentaires                 | 157 |

| 5.2      | .2 Développements technologiques       | 158 |

| Liste de | s publications et conférences          | 164 |

| 5.3      | Revues internationales                 | 164 |

| 5.4      | Conférences internationales            | 164 |

| 5.5      | Conférences Nationales                 | 165 |

L'innovation dans la conception des circuits intégrés (ICs), nous a permis de jouir de plus de facilité pour accomplir nos taches et activités quotidiennes. Alors que les applications où l'on pouvait retrouver des ICs se cantonnaient strictement aux ordinateurs, de nos jours, elles inondent notre environnement, du smart-phone à la tablette en passant par les objets connectés, dans les voitures, dans le médical jusqu'aux équipements électroménagers. Avec l'arrivée de l'ère de l'internet des objets (internet of thing (IOT)) [1], le besoin de concevoir des circuits intégrés plus performants et intégrant plus de fonctionnalités, est parmi les objectifs principaux des acteurs de l'industrie des semiconducteurs. Le chiffre d'affaire de cette dernière est estimé par World Semiconductor Trade Statistics (WSTS) à 343 milliards de dollars (US) à la fin 2015, soit une augmentation de 2.3 % par rapport à l'année précédente. Les mêmes analystes prédisent un chiffre d'affaire de 365 milliards de dollars (US) en 2017.

La miniaturisation du transistor Métal-Oxyde-Semiconducteur à effet de champs (MOSFET) a été le point de départ de l'évolution des ICs. Considéré comme l'élément de base, ses dimensions ont été réduites afin d'augmenter sa densité dans les ICs, passant de l'échelle micrométrique (d'où l'appellation microélectronique), à la fin des années 50, à l'échelle nanométrique durant la dernière décennie (nanoélectronique). La miniaturisation du MOSFET a été accompagnée par des efforts technologiques afin d'amender le fonctionnement du dispositif face aux challenges de la miniaturisation. En effet, face aux attaques incessantes des effets néfastes de la miniaturisation (canaux courts), le contrôle électrostatique du canal par la grille unique de l'architecture planaire n'était plus possible.

L'avènement des structures tridimensionnelles (3D) au sein de l'industrie des semiconducteurs est de plus en plus central en raison des efforts de miniaturisation des différents

acteurs de l'industrie des semiconducteurs. L'exemple le plus marquant est le basculement de

la technologie MOSFET planaire vers l'architecture FinFET entrepris par Intel en 2011 pour

le nœud technologique 22nm [2] puis suivi par ses principaux concurrents (SAMSUNG,

TSMC, IBM, GlobalFoundries...) pour le nœud technologique 16/14 nm [3][4][5][6] en 2014

lors de la quête continue pour des composants plus petits et plus performants. Les nanofils

sont considérés comme des candidats potentiels pour poursuivre la miniaturisation des

MOSFETs afin d'atteindre les nœuds technologiques 7 ou 5 nm, en raison de leurs

avantageuses géométries ainsi que leurs propriétés physiques et électriques, en particulier, la

possibilité d'implémenter des architectures MOSFET à grille entourant tout le canal de conduction pour un meilleur contrôle électrostatique [7].

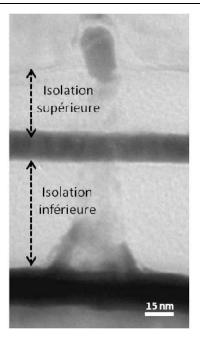

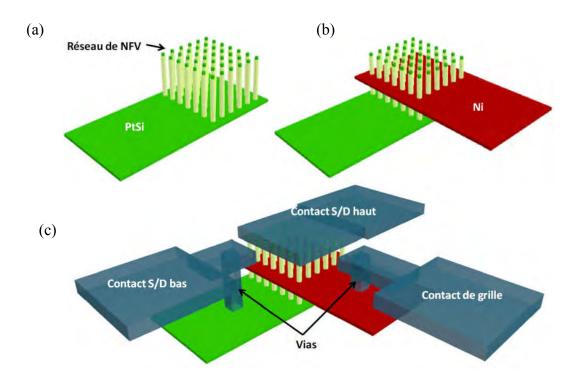

Au cours de cette thèse, nous proposons une architecture MOSFET à base de nanofils verticaux en silicium, comprenant une grille entourant tout le canal de conduction de longueur de 15 nm, implémentée à mi-hauteur d'un nanofil ou d'un réseau de nanofils afin d'atteindre un meilleur contrôle électrostatique limitant les effets canaux courts.

Le premier chapitre de ce manuscrit débute par une introduction à nos travaux, avec l'historique de la création du MOSFET et les débuts de l'industrie des semiconducteurs, précédent la description et le fonctionnement du MOSFET. Les challenges de miniaturisation de ce dernier seront également abordés. Nous traiterons les limitations de l'architecture planaire causées par les effets de canaux courts ainsi que les solutions proposées par la communauté scientifique. Enfin, différents exemples de réalisation d'architecture nanofils seront exposés. Une étude comparative servira de tremplin afin de présenter les tenants et aboutissants de notre architecture MOSFET à base de nanofils verticaux en silicium.

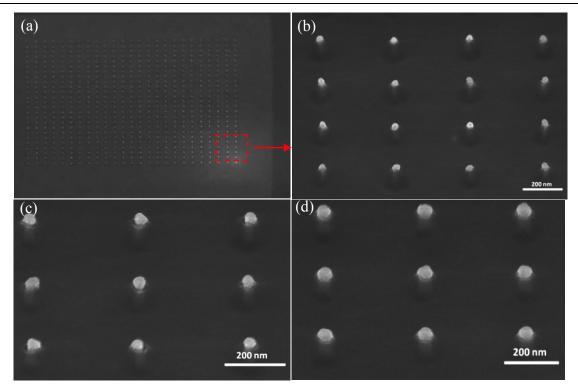

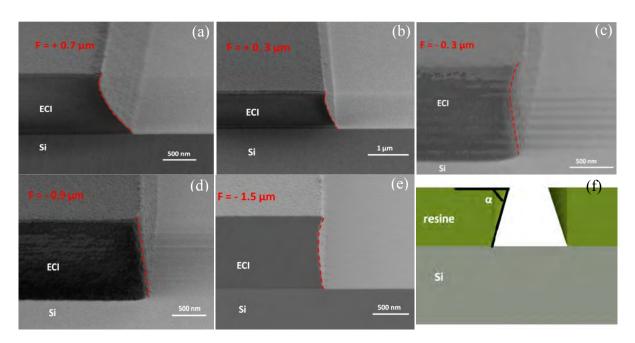

Au cours du deuxième et troisième chapitre, nous détaillerons le procédé de fabrication du dispositif à grand échelle à base de photolithographie standard et lithographie électronique à faible tension d'accélération. Tout d'abord, le procédé de réalisation de nanofils verticaux en silicium sera détaillé au cours du deuxième chapitre. Un procédé descendant consiste en la réalisation d'un masque de gravure par lithographie électronique suivi d'une gravure plasma pour transférer les nanoplots en résine dans le substrat en silicium. Enfin une oxydation sacrificielle est opérée pour réduire le diamètre des nanofils réalisés. Le troisième chapitre détaille le procédé de réalisation du MOSFET sur les nanofils par une ingénierie de couches minces à l'échelle nanométrique qui comporte la réalisation des contacts de source et de drain métalliques à base de siliciure de platine pour la réalisation des contacts Schottky à faible hauteur de barrière. Une technique de planarisation innovante d'une couche fine de diélectrique d'échelle nanométrique servant d'isolation entre les différents terminaux du dispositif sera présentée. Cette technique, permet d'accomplir une parfaite planéité de la couche d'isolation avec une très faible rugosité de surface. Enfin, les différents terminaux ainsi que les vias et les plots de contacts seront réalisés par un procédé de photolithographie standard.

# Introduction générale

Le quatrième et dernier chapitre de cette thèse sera dédié à l'étude des performances électrique du transistor MOS à base de nanofils verticaux en silicium.

Enfin, une conclusion sur les résultats majeurs réalisés au cours de ces travaux de thèse sera proposée suivie par des perspectives pour la poursuite de ces travaux.

## **Bibliographie**

- [1] L. Tan and N. Wang, "Future internet: The Internet of Things," in 2010 3rd International Conference on Advanced Computer Theory and Engineering (ICACTE), 2010, vol. 5, pp. V5–376–V5–380.

- [2] M. Bohr, "The evolution of scaling from the homogeneous era to the heterogeneous era," in *Electron Devices Meeting (IEDM), 2011 IEEE International*, 2011, pp. 1.1.1–1.1.6.

- [3] Y.-H. Chen, W.-M. Chan, W.-C. Wu, H.-J. Liao, K.-H. Pan, J.-J. Liaw, T.-H. Chung, Q. Li, G. H. Chang, C.-Y. Lin, M.-C. Chiang, S.-Y. Wu, S. Natarajan, and J. Chang, "13.5 A 16nm 128Mb SRAM in high- #x03BA; metal-gate FinFET technology with write-assist circuitry for low-VMIN applications," in *Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, 2014 IEEE International, 2014, pp. 238–239.

- [4] S. Natarajan, M. Agostinelli, s. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang, and K. Zhang, "A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 #x00B5;m2 SRAM cell size," in *Electron Devices Meeting (IEDM)*, 2014 IEEE International, 2014, pp. 3.7.1–3.7.3.

- [5] C.-H. Lin, B. Greene, S. Narasimha, J. Cai, A. Bryant, C. Radens, V. Narayanan, B. Linder, H. Ho, A. Aiyar, E. Alptekin, J.-J. An, M. Aquilino, R. Bao, V. Basker, N. Breil, M. Brodsky, W. Chang, L. Clevenger, D. Chidambarrao, C. Christiansen, D. Conklin, C. DeWan, H. Dong, L. Economikos, B. Engel, S. Fang, D. Ferrer, A. Friedman, A. Gabor, F. Guarin, X. Guan, M. Hasanuzzaman, J. Hong, D. Hoyos, B. Jagannathan, S. Jain, S.-J. Jeng, J. Johnson, B. Kannan, Y. Ke, B. Khan, B. Kim, S. Koswatta, A. Kumar, T. Kwon, U. Kwon, L. Lanzerotti, H.-K. Lee, W.-H. Lee, A. Levesque, W. Li, Z. Li, W. Liu, S. Mahajan, K. McStay, H. Nayfeh, W. Nicoll, G. Northrop, A. Ogino, C. Pei, S. Polvino, R. Ramachandran, Z. Ren, R. Robison, I. Saraf, V. Sardesai, S. Saudari, D. Schepis, C. Sheraw, S. Siddiqui, L. Song, K. Stein, C. Tran, H. Utomo, R. Vega, G. Wang, H. Wang, W. Wang, X. Wang, D. Wehelle-Gamage, E. Woodard, Y. Xu, Y. Yang, N. Zhan, K. Zhao, C. Zhu, K. Boyd, E. Engbrecht, K. Henson, E. Kaste, S. Krishnan, E. Maciejewski, H. Shang, N. Zamdmer, R. Divakaruni, J. Rice, S. Stiffler, and P. Agnello, "High performance 14nm SOI FinFET CMOS technology with 0.0174 #x00B5;m2 embedded DRAM and 15 levels of Cu metallization," in Electron Devices Meeting (IEDM), 2014 *IEEE International*, 2014, pp. 3.8.1–3.8.3.

- [6] J. Singh, C. Jerome, A. Wei, R. Miller, B. Arnaud, C. Lili, H. Zang, P. Kasun, P. Manjunatha, S. Biswanath, A. Kumar, S. M. Pandey, N. M. Iyer, A. Mittal, R. Carter, L. Zhao, E. Manfred, and S. Samavedam, "Analog, RF, and ESD device challenges and solutions for 14nm FinFET technology and beyond," in *2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers*, 2014, pp. 1–2.

- [7] K. D. Buddharaju, N. Singh, S. C. Rustagi, S. H. G. Teo, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "Si-nanowire CMOS inverter logic fabricated using gate-all-around (GAA) devices and top-down approach," *Solid-State Electron.*, vol. 52, no. 9, pp. 1312–1317, Sep. 2008.

# Chapitre 1 : Le MOSFET élément de base de l'industrie semiconducteur

#### Introduction

Les premiers pas de l'électronique des solides ont été effectués par Ferdinand Braun en 1874 à travers sa découverte de l'effet de redressement à un point de contact entre un métal et un matériau cristallin, où il remarqua que le courant circulait dans un seul sens. Son invention du redresseur à point de contact à base de sulfure de plomb présentée à Leipzig en 1876, n'a pas trouvé d'application à cette période et est devenue obsolète lorsque le tube à vide a été créé. Le besoin de travailler à des fréquences plus élevées pour les applications radio, sa taille ainsi que sa fiabilité écarta rapidement le tube à vide. A ce moment-là, l'intérêt pour le redresseur à point de contact a refait surface.

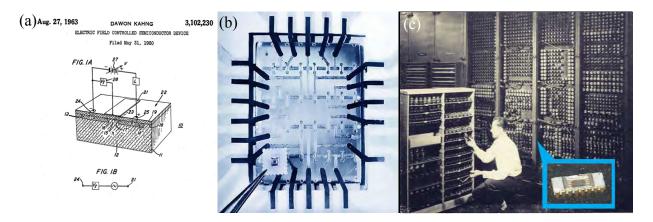

C'est en 1926, par l'invention de Julius Edgard Lilienfeld [1], que le concept de transistor à effet de champ a vu le jour sans pour autant démontrer de preuves d'une réalisation fonctionnelle. En 1936, aux laboratoires Bell, Marvin Kelly constitua un groupe de recherche sur les composants à semiconducteur composé de Shockley, Ohl et Pearson, renforcé par Brattain et Bardeen quelques années plus tard. Leurs recherches se sont focalisées sur le silicium et le germanium. Ohl, travaillant sur le silicium cristallin, inventa la jonction PN en 1946 [2]. Brattain et Bardeen proposèrent le premier transistor en germanium à point de contact [3][4], puis la théorie du transistor bipolaire par Shokley [5][6] suivie par sa première réalisation par Teal et al. [7]. Il faut attendre jusqu'à 1959 où Kahng et Attala proposèrent le premier MOSFET (Metal Oxyde Semiconductor Field Effect Transistor) réalisé avec succès grâce à la maitrise des défauts d'interface qui empêchaient le champ électrique de pénétrer dans le matériau semiconducteur [8] en utilisant le système Si-SiO<sub>2</sub> [9](fig. 1.1(a)).

La communauté industrielle fraichement établie aux alentours de la baie de San Francisco en Californie, a très rapidement reconnu le potentiel du MOSFET à base de silicium, donnant naissance à ce qu'on appelle aujourd'hui la Silicon Valley. Radio Corporation of America (RCA) et Fairchild Semiconductor ont intégré le MOSFET dans leur premier circuit intégré en 1962 [10][11] comme le témoigne la figure 1.1(b) avec un circuit intégré composé de 16 MOSFETs développé par RCA.

Figure 0.1 - (a) Brevet du MOSFET établi par D. Kahng [12], (b) photographie d'un des premiers circuit intégré composé de 16 transistors MOS réalisé par RCA et (c) comparaison entre le microprocesseur Intel 4004 et l'ordinateur ENIAC.

Les composants MOSFETs ont fait leur entrée dans le marché des semiconducteurs en 1964 avec General Microelectronis (GME 1004) et Fairchild Semiconductor (F1 100) avec des MOSFETs de type p pour les applications logiques, et des MOSFETs de type n pour l'amplification des signaux. C'est finalement en 1971 que l'industrie des semiconducteurs a pris son véritable envol grâce au microprocesseur d'Intel 4004 constitué de 2300 MOSFETs avec une longueur de grille de 10 µm fonctionnant à une fréquence maximale de 740 kHz, et réalisant le travail du premier ordinateur ENIAC (Electronic Numerical Integrator Analyser and Computer) développé en 1946 par l'université de Pennsylvanie qui occupait une surface de 160 m² et pesait 30 tonnes (fig. 1.1(c)). 99 % des circuits intégrés produits de nos jours utilisent les MOSFETs comme brique de base. On les retrouve dans les systèmes où l'information est traitée ou mémorisée.

Au cours de ce premier chapitre, nous nous intéresserons au MOSFET comme l'élément précurseur des grandes innovations technologiques des dernières décennies en commençant par sa composition, son mode de fonctionnement ainsi que sa miniaturisation. Les limitations et les challenges auquel la communauté scientifique devrait faire face pour l'amélioration des performances seront adressés, notamment par l'introduction des architectures MOSFET à base de nanofils, la problématique même de cette thèse.

#### 1.1 Le MOSFET

#### 1.1.1 Structure de base et principe de fonctionnement

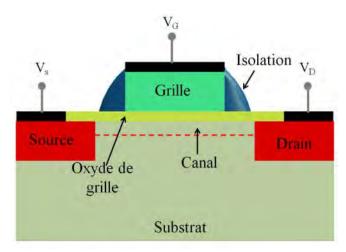

Le MOSFET est traditionnellement représenté comme un interrupteur par les dessinateurs de circuits logiques. En effet, l'électrode appelée «grille», permet de contrôler le courant traversant un canal de conduction établi entre l'électrode de source et l'électrode de drain. Ainsi la grille agit comme électrode de commutation de l'état bloqué à l'état passant et vice versa.

Le canal de conduction est créé en dessous de l'oxyde de grille, entre les deux réservoirs de charges que représentent les régions de source et de drain, grâce à un champ électrique vertical traversant le semiconducteur à travers la capacité MOS (Métal – Oxyde – Semiconducteur), d'où le nom transistor à effet de champ (fig. 1.2).

Figure 0.2 - Structure MOSFET.

Selon le type des porteurs formant le canal de conduction, les MOSFETs se divisent en deux catégories. Lorsque le canal de conduction est formé essentiellement d'électrons, il est dit MOSFET de type n ou NMOS, il est conducteur à l'application d'une tension positive sur la grille. Un MOSFET de type p ou PMOS, quand la conduction est faite par des trous lors de l'application d'une tension négative sur la grille. Pour les deux cas, le dopage du substrat est opposé à la nature du canal et les réservoirs de charges source et drain. Un MOSFET est dit à enrichissement ou Normally Off si le MOSFET est à l'état bloqué à une tension de grille nulle et à l'inverse, il est dit à déplétion ou Normally On si une tension non nulle sur la grille est nécessaire pour passer à l'état bloqué.

#### 1.1.2 Régime de fonctionnement

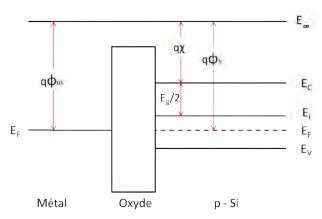

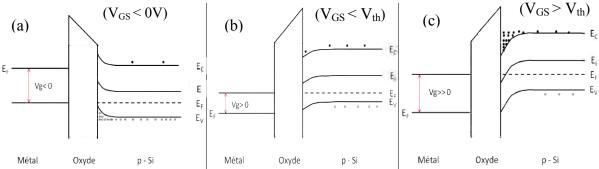

L'application d'une tension sur le contact de grille a une incidence directe sur la nature des porteurs se trouvant à la surface du semiconducteur sous l'influence d'un champ électrique. Pour une meilleure compréhension des différents régimes de fonctionnement du MOSFET, il est important de revoir le diagramme de bande de la structure Métal – Oxyde – Semiconducteur en condition de bandes plates (travail de sortie du métal  $(\Phi_m)$  est égal à celui du semiconducteur  $(\Phi_s)$ , de même pour les énergies de Fermi  $(E_{FM} = E_{FS} = E_F)$ ) (fig. 1.3).

Figure 0.3 : Diagramme d'énergie d'une structure MOS pour un semiconducteur de type p en condition de bandes plates.

avec  $\chi$  et  $E_g$  représentent l'affinité électronique et la bande interdite du semiconducteur,  $E_F$ ,  $E_{\infty}$   $E_C$ ,  $E_V$  et  $E_i$  sont respectivement, le niveau d'énergie de Fermi, de vide, bande de conduction, de valence et le niveau d'énergie intrinsèque du Si. A chaque tension appliquée (positive ou négative) au niveau de la grille, 3 régimes différents existent à la surface du semiconducteur [13] tel que décrit ci-dessous pour le cas d'un NMOS.

#### 1.1.2.1 Régime d'accumulation

Pour une tension  $V_{GS} < 0V$ , on assiste à une courbure des bandes d'énergie vers le haut à l'interface oxyde/semiconducteur. Les trous, considérés comme porteurs majoritaires sont attirés à la surface du semiconducteur, d'où le nom de régime d'accumulation. Le canal de conduction n'étant pas formé, le transistor est bloqué (fig. 1.4(a)).

#### 1.1.2.2 Régime de déplétion

Lorsqu'une tension légèrement positive est appliquée ( $0 < V_{GS} < V_{th}$ ), les bandes d'énergie sont courbées vers le bas. Les trous sont repoussés de la surface créant une zone dépourvue de

porteurs, appelée zone de charge d'espace, constituée uniquement de charges ionisées. C'est le régime de déplétion, le transistor est toujours bloqué (fig. 1.4(b)).

#### 1.1.2.3 Régime d'inversion

A une tension  $V_{GS} > V_{th}$ , les bandes d'énergie se courbent encore plus, les électrons (porteurs minoritaires) sont attirés à la surface du semiconducteur. La densité d'électrons devient plus grande que celle des trous à la surface, c'est le régime d'inversion. Le canal de conduction est formé, l'application d'une tension  $V_{DS} > 0$  V, entraine le passage du courant de la source au drain, le transistor est passant (fig. 1.4(c)).

Figure 0.4 – Diagramme d'énergie d'une structure NMOS en régime (a) d'accumulation (b) déplétion et (c) inversion.

### 1.2 Métriques du MOSFET

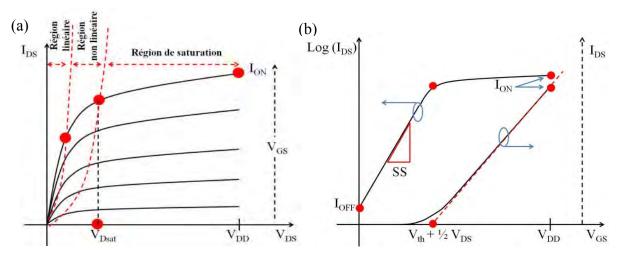

Il existe deux manières distinctes pour représenter les caractéristiques I(V) du MOSFET, la première consiste à tracer le courant de drain  $(I_{DS})$  en fonction de la tension de drain  $(V_{DS})$ , tout en fixant la tension d'entrée  $(V_{GS})$ , c'est la caractéristique de sortie (fig. 1.5(a)). La deuxième est la caractéristique de transfert, c'est-à-dire, on trace le courant de sortie  $I_{DS}$  en fonction de la tension d'entrée  $V_{GS}$  à  $V_{DS}$  constant (fig. 1.5(b)).

Figure 0.5 – Caractéristiques idéales (a) de sortie  $(I_{DS}(V_{DS}))$  et (b) de transfert  $(I_{DS}(V_{GS}))$  d'un MOSFET.

A partir de la caractéristique de sortie et selon la tension de polarisation  $V_{DS}$ , la courbe  $I_{DS}(V_{DS})$  passe par trois régions distinctes, chacune correspond à un régime de fonctionnement du MOSFET. Il est plus facile d'extraire les paramètres principaux du MOSFET à partir de la caractéristique de transfert, comme la tension de seuil  $V_{th}$  ainsi que les courants de conduction  $I_{ON}$  et de fuite  $I_{OFF}$ . Intéressons-nous tout d'abord à l'expression du courant de sortie  $I_{DS}$  du MOSFET.

Le courant en tout point du canal de conduction peut être défini comme :

$$I_d(y) = W \mid Qn(y) \mid v(y)$$

Équation 0-1

où W représente la largeur du canal, Qn et  $\upsilon$  sont respectivement les charges formant le canal et leur vitesse de dérive. La quantité de charges dans le canal est donnée par l'équation suivante :

$$\left| \ Qn(y) \ \right| = \left[ V_G - V_{FB} - \Delta \Phi_i(y) - 2\Phi_B \right] C_{OX} - \sqrt{2\epsilon_S q N_a [\Delta \Phi(y) + 2\Phi_B]} \qquad \qquad \text{\'equation 0-2}$$

avec  $V_{FB}$  la tension de bande plate,  $\Phi_i(y)$ ,  $\Phi_B$ , les potentiels de Fermi,  $\epsilon_s$  la permittivité du silicium et  $N_a$  la concentration des accepteurs. En se mettant en condition d'approximation du canal graduel (Gradual-Channel Approximation), où le champ électrique dépend essentiellement du champ électrique transverse ( $\xi_x$ ) (le champ électrique longitudinal ( $\xi_y$ ) est négligé), la mobilité ( $\mu$ ) devient constante. Par conséquent la vitesse des porteurs dans le canal devient  $\upsilon = \xi \mu$  ( $\xi$  représente le champ électrique). L'expression du courant  $I_d$  devient :

$$I_{DS} = \frac{W\mu_n C_{ox}}{L} \{ (V_G - V_{FB} - 2\Phi_B - V_d/2)Vd - (\frac{2}{3})(\frac{\sqrt{2\epsilon_S q Na}}{\text{Cox}})(V_d + 2\Phi_B)^{3/2} - (2\Phi_B)^{3/2}] \}$$

Équation 0-3

Cox, représente la capacité de grille.

# 1.2.1 Etat bloqué : faible inversion

Le MOSFET n'est pas un inverseur parfait, c'est-à-dire même à des tensions  $V_{GS}$  inférieure à la tension de seuil  $V_{th}$  (régime de déplétion ou faible inversion), un faible courant appelé courant de fuite de nature diffusive, circule. Il est possible d'extraire sa valeur en traçant la caractéristique de transfert en échelle logarithmique, il correspond au courant  $I_{DS}$  à  $V_{GS} = 0$  et  $V_{DS} = V_{DD}$ , il est exprimé comme suit :

$$I_{DS} = \frac{W\mu_n C_{ox}}{L} \left(\frac{KT}{q}\right)^2 exp\left(q\frac{V_{GS} - V_{th}}{SS} \textbf{ln10}\right) \left[1 - exp\left(\frac{-qV_{DS}}{KT}\right)\right]$$

Équation 0-4

SS (pente sous le seuil) est la tension de grille nécessaire pour induire une augmentation du courant de drain d'une décade d'où son unité (mV/décade), il représente également la qualité de transition de l'état bloqué à l'état passant du transistor. Il est défini comme l'inverse de la pente de la caractéristique de sortie en dessous du seuil (fig. 1.4(b)). Son expression est :

$$SS = \left(\frac{\sigma Log I_{DS}}{\sigma V_{GS}}\right)^{-1} = \left(\frac{KT}{q}\right) ln 10$$

Équation 0-5

A T= 300 K et pour un transistor à canal long, SS= 60 mV/dec.

Enfin, la tension de seuil est la tension à appliquer à la grille pour obtenir une forte inversion, elle est exprimée par l'équation suivante :

$$V_{th} = V_{FB} - 2\Phi_{B} - \sqrt{\frac{2\epsilon_{S}qNa(2\Phi_{B})}{C_{ox}}}$$

Équation 0-6

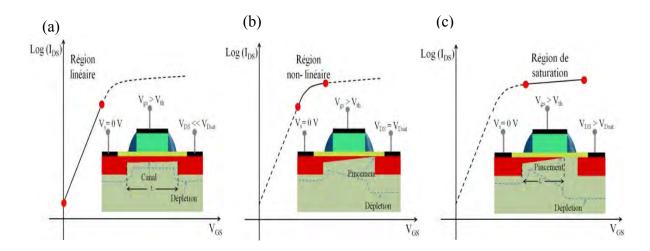

#### 1.2.2 Etat passant: forte inversion

Pour une tension  $V_{GS} > V_{th}$ , le canal de conduction est établi et en appliquant une tension  $V_{DS}$  positive, un courant électrique circule entre la source et le drain. Le canal se comporte comme une résistance et le courant varie proportionnellement avec la tension de drain, c'est la région linéaire (fig. 1.6(a)). L'expression du courant  $I_{DS}$  dans ce cas devient :

$$I_{DS} = \frac{W\mu_n C_{ox}}{L} \left( V_{GS} - V_{th} - \frac{V_{DS}}{2} \right) V_{DS}$$

Équation 0-7

En augmentant la tension  $V_{GS}$ , le courant de drain dévie d'un comportement ohmique et se stabilise (région non linéaire) à cause de la réduction des charges proche de la région de drain (y = L), devenant quasi nulle et induisant le pincement du canal (fig. 1.6 (b)). Cet effet est dû à la présence d'un champ électrique important du côté de la région du drain et l'augmentation de la vitesse des porteurs. Le courant  $I_{DS}$  peut être exprimé par :

$$I_{DS} = \frac{W\mu_n C_{ox}}{L} \left(V_{GS} - V_{th} - \frac{MV_{DS}}{2}\right) V_{DS}$$

Équation 0-8

M est une fonction de concentration des dopants et d'épaisseur d'oxyde, elle est égale à  $1 + \frac{K}{2\sqrt{\Phi}} \text{ avec } K = \sqrt{2\epsilon_S q N_a}/C_{ox}.$

A partir de cette tension  $V_{DS} > V_{Dsat}$ , le courant  $I_{DS}$  reste quasiment constant et le point de pincement tend à s'approcher de la région de source réduisant la longueur de grille de L à L', le MOSFET est en régime de saturation (fig. 1.6 (c)), le courant  $I_{DS}$  devient :

$$I_{DS} = \frac{W\mu_n C_{ox}}{2ML} \left(V_{GS} - V_{th}\right)^2$$

Équation 0-9

Figure 0.6 – Evolution de la caractéristique de sortie d'un MOSFET à canal long en fonction de la tension  $V_{\text{DS}}\boldsymbol{.}$

#### 1.3 Miniaturisation du MOSFET

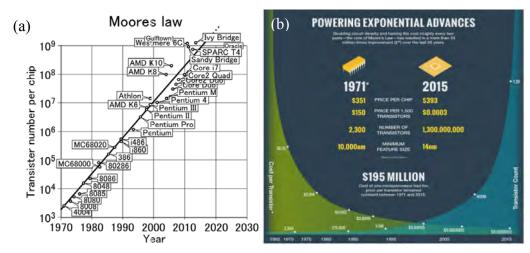

En 1965, Gordon Moore, un des fondateurs d'Intel a prédit que le nombre de transistors par circuit devait doubler tous les deux ans [14]. Cette loi empirique émise par une simple constatation appelée « la loi de Moore » devint la règle fondamentale et la source d'engouement pour la course à la miniaturisation des MOSFETs comme le témoigne la figure 1.7(a). Cette loi datant maintenant de 50 ans est à ce jour encore considérée comme moteur. Cette miniaturisation a permis l'augmentation de la densité des transistors dans les microprocesseurs incluant ainsi plus de fonctionnalités et d'espace de stockage d'information. Un autre paramètre, le coût de production du transistor, a été également le cheval de bataille de l'industrie des semiconducteurs. La figure 1.7(b) exprime l'évolution de l'industrie des semiconducteurs en nombre et coût du MOSFET [15].

Figure 0.7 - Loi de Moore (a) évolution du nombre et (b) du coût du MOSFET depuis 50 ans de miniaturisation.

Grâce à cette miniaturisation, de 1971 (procédé 10 µm) jusqu'à 2015 (procédé 14 nm)[16], les performances ont été améliorées d'un facteur de 3500 fois, avec une meilleure efficacité énergique de 90000 fois, mais surtout, le coût de production d'un transistor a été réduit de plus de 60000 fois [17].

Dennard et al.[18] Ont proposé des règles de miniaturisation en prenant en considération trois variables, il s'agit de la dimension des transistors, la tension de fonctionnement et le dopage. Il définit un facteur de miniaturisation k ou chaque variable varie en fonction de ce facteur. La réduction de ces variables a une incidence directe sur les caractéristiques du transistor et du circuit, qui varient en fonction de ce même facteur. Le tableau 1.1 résume les règles de miniaturisation établies par Dennard.

| Paramètres                                                       | Facteur de miniaturisation |

|------------------------------------------------------------------|----------------------------|

| Dimension du composant (T <sub>ox</sub> , L, W, X <sub>j</sub> ) | 1/K                        |

| Concentration du dopage (N <sub>a</sub> )                        | K                          |

| Tension d'alimentation (V)                                       | 1/k                        |

| Courant (I)                                                      | 1/k                        |

| Capacité (εA/t)                                                  | 1/k                        |

| Délai / circuit (CV/I)                                           | 1/k                        |

| Puissance de dissipation /circuit (VI)                           | 1/k <sup>2</sup>           |

Tableau 1.1 Evolution des paramètres du MOSFET en fonction du facteur de miniaturisation.

Cependant, ces règles de miniaturisation répondent à un cas de figure idéal et ont connu de multiples divergences, à titre d'exemple, le courant sous le seuil ou l'épaisseur de l'oxyde de grille avec des courants de fuite par effet tunnel. Ces effets indésirables de la miniaturisation sont attribués aux effets dits de canaux courts (Short Channel Effect). C'est pourquoi, les paramètres de miniaturisation ne devraient pas forcement avoir le même facteur d'échelle. Brews et al. [19] ont proposé une loi empirique où les MOSFETs gardent les caractéristiques d'un transistor à canal long qui est définie comme suit :

$$L \ge C_1 [x_d t_{ox} (W_S + W_D)^2]^{1/3}$$

Équation 0-10

Où,  $C_1$  est une constante,  $W_S + W_D$  la somme des largeurs de déplétion de source et de drain,  $x_d$  la profondeur des jonctions.

Ces règles de miniaturisation dites traditionnelles, ont été longuement suivies jusqu'en début des années 2000, où le courant de fuite est devenu conséquent en raison des effets de canaux courts.

#### 1.4 Effets de canaux courts

et

Un MOSFET est considéré comme composant à canal court, lorsque les largeurs de déplétion des jonctions de source et de drain  $(x_{dS}, x_{dD})$  sont du même ordre de grandeur que la longueur de grille L, elles sont exprimées par :

$$\begin{split} \mathbf{X}_{dD} &= \sqrt{\frac{2\epsilon_S \left(V_{DS} + \Phi_{Si} + V_{SB}\right)}{qN_a}} & \text{\'equation 0-11} \\ \\ \mathbf{X}_{dS} &= \sqrt{\frac{2\epsilon_S \left(\Phi_{Si} + V_{DB}\right)}{qN_a}} & \text{\'equation 0-12} \end{split}$$

V<sub>SB</sub> et V<sub>DB</sub> sont respectivement la tension source - substrat et la tension drain - substrat [20].

Pour un MOSFET à canal court, la distribution du potentiel dans le canal de conduction est dépendante du champ électrique transverse ( $\xi_x$ , induit par la tension de grille) qui devient également dépendante du champ électrique longitudinal ( $\xi_y$ , induit par la tension de drain). Dans ce cas, la condition d'approximation du canal graduel n'est plus valide et des effets indésirables dits de canaux courts apparaissent. On rassemble sous la nomination d'effet de canaux courts tout phénomène physique modifiant la tension de seuil du MOSFET ou

imposant une limitation au courant de dérive des porteurs du canal de conduction. On retrouve notamment les effets suivants :

#### 1.4.1 DIBL et perçage volumique

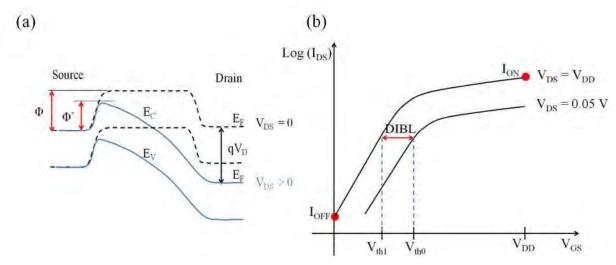

Pour des dispositifs MOSFETs de canal long (L > 1 $\mu$ m) et pour des tensions de grille  $V_{GS}$  <  $V_{th}$ , une barrière de potentiel au niveau source/canal s'oppose au passage du courant. C'est lorsque la tension  $V_{GS}$  >  $V_{th}$ , que le canal se forme et le courant circule de la source au drain, dont l'intensité est modulée par la tension de drain. Cette dernière entraine la réduction de la longueur du canal lorsque la tension de saturation est atteinte, mais sans incidence sur la barrière de potentiel de la source. Cette condition n'est plus respectée dans le cas d'un dispositif dit à canal court, où en augmentant la tension de drain, la zone de charge d'espace au niveau de drain s'étend en direction de la source. Il en résulte une pénétration du champ électrique dans la région de source entrainant l'abaissement de sa barrière de potentiel avec le canal, causant l'injection des porteurs dans le canal même lorsque  $V_{GS}$  <  $V_{th}$  [21][22]. Cet effet est nommé Drain Induced Barrier Lowering (DIBL) (fig. 1.8(a)). Il est fortement modulé par la tension de drain, il caractérise la variation de la tension de seuil du dispositif en fonction de la variation de la tension de drain, comme on peut le constater sur la caractéristique de transfert (fig. 1.8(b)).

Figure 0.8 – (a) Diagramme de bandes d'énergie à  $V_{DS}=0$  V (en pointillés noir) et à  $V_{DS}>0$  (ligne bleue) illustrant l'abaissement de la barrière de potentielle de  $\Phi$  à  $\Phi$ ' (b) Caractéristique de sortie illustrant l'effet du DIBL sur la tension de seuil.

Il est encore plus dramatique lorsque la région de déplétion du drain s'élargit encore jusqu'à rejoindre celle de source ( $x_{dS} + x_{dD} \approx L$ ), (perçage volumique (Punch Through)). En conséquence, la barrière de potentiel au niveau de la source est éliminée et un canal parasite

s'est formé dans le substrat parallèlement au canal de conduction. Les porteurs majoritaires dans la source sont injectés dans la région du canal de déplétion (canal parasite) puis balayés par le champ électrique et récoltés par le drain. Il en résulte un large courant de fuite qui a une forte corrélation avec la tension de drain. Le courant de drain devient dominé par le courant de la région de déplétion, il est exprimé comme :

$$I_{DS} = \frac{9\epsilon_S \mu_n A V_D^2}{8L^3}$$

Équation 0-13

où A représente la surface de section du canal de déplétion [23].

#### 1.4.2 Effet du champ électrique longitudinal

Sachant que le facteur de miniaturisation k n'est pas le même pour tous les paramètres du MOSFET, il a été plus difficile de réduire les tensions de polarisation que les dimensions du MOSFET. Le champ électrique longitudinal devient de plus en plus élevé, ajoutant ainsi sa participation aux effets de canaux courts notamment par la modulation de la mobilité des porteurs dans le canal de conduction, parmi ces effets on retrouve :

#### 1.4.2.1 La saturation de la vitesse des porteurs

Lorsque le champ électrique longitudinal  $\xi_y$  est faible, la vitesse de dérive des porteurs varie linéairement avec le champ électrique. Cependant, lorsque  $\xi_y$  atteint une valeur de  $10^4$  V / cm (cas du silicium), la vélocité de dérive a tendance à augmenter plus lentement, jusqu'à atteindre la saturation à une vitesse de  $10^7$  cm / s lorsque  $\xi_y$  atteint une valeur aux alentours de  $10^5$  V / cm.

#### 1.4.2.2 Distribution de surface

Sachant que le canal d'inversion est créé à la surface du semiconducteur, extrêmement proche de l'interface  $Si-SiO_2$  en raison d'un fort  $\xi_x$ , la vitesse des porteurs est réduite en raison de la distribution de surface (surface scattering). Les porteurs se déplacent avec une grande difficulté sous l'influence du  $\xi_y$  le long du canal de conduction entrainant une grande diminution de la vitesse des porteurs.

#### 1.4.2.3 Porteurs chauds

L'effet du fort champ électrique attribue aux porteurs une grande énergie. Ils sont émis dans l'oxyde de grille à proximité de la région du drain. Cet effet induit la création de pièges ou des défauts à l'interface Si-SiO2 qui causent une variation de la tension de seuil et de la transconductance du MOSFET [24].

#### 1.4.2.4 Ionisation par impact

Cet effet (propre au NMOS) est dû à la présence d'un fort champ électrique au niveau de la jonction p-n formée par le canal et la région de drain. Les porteurs acquièrent une énergie cinétique importante entrainant la création de pairs électrons-trous (e-h) par ionisation par impact, puis la multiplication des pairs (e-h) par avalanche. Les électrons sont attirés par le drain, tandis que les trous sont repoussés dans le substrat formant un courant parasite. L'effet de ce courant est aperçu à travers le transistor npn (bipolaire) parasite, où la jonction p-n formée par la source et le substrat devient polarisée en directe, de sorte que les électrons sont injectés dans le substrat et sont attirés vers le drain [25].

Afin de limiter l'effet de l'augmentation du champ électrique sur les MOSFET à canaux court, il est favorable de réduire le niveau de dopage des régions de source et de drain. Cependant cette réduction entraine une augmentation de la résistance de contact causant la réduction du courant I<sub>ON</sub>. Un compromis a été trouvé par la restructuration des régions de source et drain en deux niveaux de dopage, un caisson fortement dopé identique au précédent puis suivi d'un petit caisson faiblement dopé et adjacent au canal de conduction. Cette structure est appelée drain légèrement dopé ou Lightly Doped Drain (LDD) [26].

# 1.5 Alternative aux effets canaux courts et amélioration des performances des MOSFETs

#### 1.5.1 Résistances séries

Avec la continuité de la miniaturisation des MOSFETs, les résistances du transistor qui incluent la résistance de canal intrinsèque ainsi que les résistances en série parasites associées aux diffusions et aux contacts, n'ont cessé d'augmenter et sont devenues prépondérantes. Elles causent notamment la réduction de l'intensité du courant de conduction I<sub>ON</sub>, mais également la vitesse d'opération des circuits [27]. L'introduction des siliciures a permis de

réduire ces résistances séries grâce à leur faible résistivité (sheet resistance) ainsi qu'une faible résistance de contact. Ils ont été utilisés pour la réalisation des contacts de grille, source et drain ainsi que les interconnexions. Tout d'abord, les siliciures de molybdène (Mo) ont été utilisés pour la réalisation des mémoires DRAM pendant les années 80, puis remplacés par les siliciures de tungstène (W) en raison de sa plus faible résistivité [28]. A chaque nœud technologique, des siliciures de plus faible résistivité et résistance de contact ont été incorporés dans le but de réduire les résistances séries, passant par les siliciures de titane (Ti) [29], les siliciures de cobalt (Co) [30] et les siliciures de nickel (Ni) [28].

#### 1.5.2 Introduction des contraintes dans le canal de conduction

Sous l'emprise d'un fort champ électrique, la vitesse des porteurs dans le canal de conduction est sujet à une forte limitation, jusqu'à saturation. La tendance à la dégradation de la mobilité des trous et des électrons a été constatée depuis plusieurs nœuds technologiques. La mobilité des électrons est passée de 400 cm² / Vs pour le nœud technologique 0.8 µm à 120 cm² / Vs pour celui de 0.13 µm [31].

L'introduction des contraintes dans le canal de conduction dès le nœud technologique 90 nm, a permis d'améliorer les performances des MOSFETs en augmentant le courant de conduction à travers l'augmentation de la mobilité des électrons et des trous [32]. Il est possible d'appliquer des contraintes bi-axiales comme uni-axiales, pour les deux cas de figures, ces dernières causent la distorsion des bandes d'énergie. En finalité, la mobilité effective des porteurs est améliorée à travers la réduction des masses effectives [33]. La mobilité effective est exprimée par la relation suivante :

$$\mu_{eff} = \frac{q \tau}{m^*}$$

Équation 0-14

où  $1/\tau$  représente la fréquence de collision des porteurs tandis que m\* leur masse effective de conduction.

Quand la mobilité des porteurs est dominée par les phonons dans un MOSFET non contraint, l'effet des contraintes est suspecté de supprimer l'influence des phonons de type G d'après Fischetti et al. [34] ou de type F selon Formicone et al. [35] rendant l'interface moins rugueuse, facilitant la diffusion des porteurs [36].

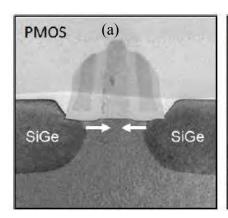

Les contraintes dans les MOSFETs de type p ont été obtenues par le changement des régions de source et de drain par des couches de Si<sub>1-x</sub>Ge<sub>x</sub> (fig. 1.9(a)). L'écart de maille

cristallin entre le SiGe et le Si crée une contrainte compressive longitudinale dans le canal de conduction, améliorant la mobilité des trous. Les contraintes dans le canal des MOSFETs de type n sont obtenues par le dépôt d'une couche de SiN au-dessus du transistor créant une contrainte élastique dans le canal (fig.1.9(b)) [37][38].

Figure 0.9 – Technologie 90 nm d'Intel illustrant l'ingénierie des contraintes (a) source et drain en SiGe pour les PMOSFET et (b) couche de SiN au-dessus des NMOSFET.

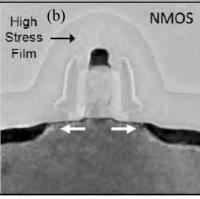

# 1.5.3 Matériaux à constante diélectrique élevée (High K) et grille métallique

L'utilisation du dioxyde de silicium (SiO<sub>2</sub>) comme oxyde de grille pour les dispositifs MOSFET en silicium, représente la clé de réussite de l'intégration de ces derniers au sein de l'industrie des semiconducteurs, notamment grâce à ses bonnes qualités électriques et mécaniques caractérisées par sa faible densité de défauts d'interface, large bande interdite (9 eV) qui lui confère d'excellentes propriétés d'isolation électrique, ainsi qu'une parfaite compatibilité avec les procédés de fabrication des circuits intégrés. Dans la course à la miniaturisation, l'épaisseur du SiO<sub>2</sub> a été réduite avec un facteur de 0.7 à chaque nœud technologique jusqu'au nœud de 130 nm atteignant une épaisseur de 1.5 nm [39], puis une stabilisation à 1.2 nm pour les nœuds technologiques de 90 et 65 nm [32], en raison d'une forte augmentation du courant de fuite à travers la structure MOS. Les porteurs diffusent à travers l'oxyde de grille par effet tunnel, entrainant l'augmentation de la puissance statique et une forte dégradation des performances. Il a été remarqué que le courant de fuite par effet tunnel augmente de manière exponentielle avec la réduction de l'épaisseur du SiO<sub>2</sub> [40], sachant qu'une limite fondamentale de 0.7 nm pour l'épaisseur minimale du SiO<sub>2</sub> à utiliser en dessous de laquelle la bande interdite n'est pas complètement formée [41]. La solution alternative est de remplacer le SiO<sub>2</sub> par des diélectriques avec une forte permittivité dit High K. Grâce à ces matériaux, il est possible de définir un oxyde de grille avec une épaisseur physique plus grande pour la même valeur de capacité obtenue avec le SiO<sub>2</sub> aux épaisseurs ultimes. On définit alors, l'Epaisseur d'Oxyde Equivalent (EOT) qui se réfère à l'épaisseur de diélectrique nécessaire pour produire le même effet que le SiO<sub>2</sub>. Il s'exprime par :

$$EOT = t_{high K} \frac{\varepsilon_{SiO2}}{\varepsilon_{high K}}$$

Équation 0-15

$t_{high~K}$  et  $\epsilon_{high~K}$  sont respectivement l'épaisseur et la permittivité du matériaux à forte permittivité et  $\epsilon_{SiO2}$  permittivité du  $SiO_2$  égale à 3.9. Parmi les matériaux les plus étudiés on retrouve, l' $Al_2O_3$  ( $\epsilon=10$ ),  $HfO_2$  ( $\epsilon=26$ ),  $ZrO_2$  ( $\epsilon=25$ ),  $Ta_2O_3$  ( $\epsilon=25$ ) ainsi que le  $TaO_2$  ( $\epsilon\geq50$ ).

L'intégration des matériaux High K n'est pas sans peine, par exemple lors du dépôt sur le substrat en Si, une couche d'oxyde SiO<sub>x</sub> se forme, augmentant la valeur de l'EOT finale. Il est également nécessaire de surmonter quelques challenges comme la dégradation de la mobilité par les phonons optiques ou le verrouillage du niveau de Fermi (Vt pinning) [42]. C'est pour cela que l'intégration des matériaux High K dans les nouvelles architectures MOSFET a été accompagnée par l'intégration de la grille métallique en remplacement de la grille en polysilicium permettant de contrôler les phonons optiques. Encore, le remplacement de la grille en polysilicium permet de réduire encore la valeur de l'EOT. En effet, la grille en polysilicium induisait l'apparition d'une couche de déplétion au niveau de l'interface polysilicium — SiO<sub>2</sub> entrainant la réduction de la capacité de grille, d'où la nécessité d'introduire des grilles en métal ou siliciures de métaux. Le nœud technologique 45 nm a été marqué par l'introduction de l'HfO<sub>2</sub> comme matériau high K et la grille métallique en replacement à l'oxyde de grille en SiO<sub>2</sub> et la grille en polysilicium respectivement [43] (fig. 1.10).

Figure 0.10 – (a) MOSFET au nœud technologique 45 nm avec une grille métallique et high K diélectrique (b) image TEM montrant l'empilement de grille.

#### 1.5.4 Silicon On Insulator (SOI) MOSFET

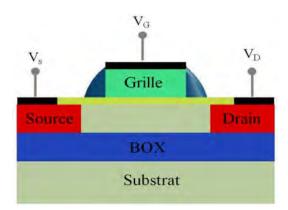

L'augmentation continue du courant de fuite ainsi que la dégradation des performances due aux effets des canaux courts ont conduit à l'évolution d'approches alternatives. Le SOI MOSFET présente une architecture différente que celle du MOSFET planaire, il est constitué d'une fine couche de silicium déposée sur un oxyde dit enterré ou Burried Oxide (BOX). Le canal de conduction est confiné entre l'oxyde de grille et l'oxyde enterré ce qui lui confère un meilleur contrôle électrostatique du potentiel. Lorsque la couche de silicium est relativement épaisse, les régions de déplétion n'atteignent pas le BOX, le SOI MOSFET est dit partiellement déplété ou Partially Depleted SOI (PDSOI), dans le cas contraire le SOI MOSFET est dit complètement déplété ou Fully Depleted SOI (FDSOI). Parmi les avantages que présentent les structures SOI, on trouve la suppression des capacités de jonctions car celles-ci sont séparées du substrat par le BOX (source – substrat et drain – substrat), qui sont remplacées par des capacités d'oxyde beaucoup moins influentes. Egalement, la structure SOI permet l'amélioration du contrôle de la grille sur le canal de conduction (fig.1.11).

Figure 0.11 – Illustration d'une structure SOI MOSFET.

### 1.5.5 Multiples grilles

L'intégration des contraintes pour augmenter la mobilité des porteurs ainsi que les matériaux diélectriques à forte permittivité et la grille métallique ont permis de maitriser les effets de canaux courts. Cependant, ces apports ont tout de même des limites. La réduction continue de la longueur de grille est accompagnée par l'augmentation du champ électrique longitudinal et son influence dans le canal de conduction, qui engendre la perte du contrôle électrostatique de la grille sur le canal de conduction au profit du drain. En effet, le contrôle électrostatique de la grille sur le canal de conduction est obtenu à travers un couplage capacitif entre la grille et la région du canal. Ce contrôle est effectué verticalement tandis que

l'influence du drain sur la région du canal de conduction s'effectue par la propagation des lignes de champ électrique latéralement. D'où l'intérêt de concevoir une grille couvrant plusieurs côtés du canal.

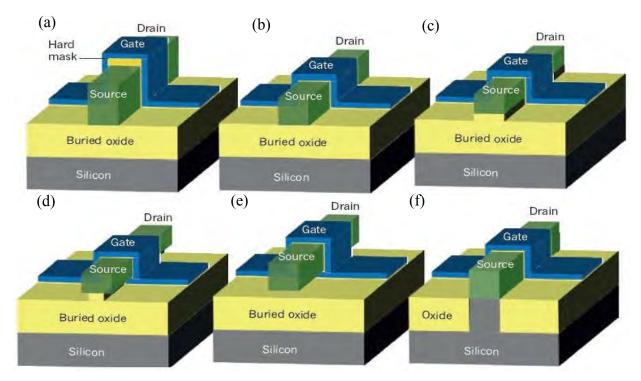

Le premier MOSFET à double grille (DG) proposé par Sekigawa et al.[44], comprenait une deuxième grille située en dessous du canal, prédisant la réduction des effets canaux courts. Plusieurs configurations de dispositifs MOSFET sur bulk ou SOI à multiple grilles ont été proposées (fig. 1.12) où la partie semiconductrice active planaire est remplacée par une ailette (Fin en anglais) sur laquelle différentes options de définition de la grille sont possibles. On retrouve notamment le DG MOSFET (fig. 1.12(a)) ou le contrôle électrostatique est exercé sur les deux cotés latéraux, ou le MOSFET à triple grille, le contrôle électrostatique est exercé sur trois faces du canal (fig. 1.12(b)). Ces deux premiers dispositifs sont dits Fin Field Effect Transistor (FinFET). Lorsque les grilles latérales pénètrent dans le substrat ou légèrement en dessous de l'ailette, nous obtenons respectivement des Π-MOSFET (fig. 1.12(c)) et le Ω-MOSFET (fig. 1.12(d)), leurs appellations sont liées à la forme de la grille. Cette incursion de la grille dans le substrat améliore encore le contrôle électrostatique en induisant une contribution sur la partie inférieure du canal de conduction.

On appelle grille entourante ou Gate All Around (GAA) MOSFET (fig. 1.12(e)), lorsque le canal de conduction est complètement entouré par la grille, où le contrôle électrostatique est maximal, lui conférant une forte maitrise du flux des porteurs dans le canal et la minimalisation des effets canaux courts [45]. La figure 1.12(f) représente un FinFET réalisé sur bulk planaire.

Plusieurs études ont démontré qu'en augmentant le nombre de grilles, une meilleure immunité contre les effets de canaux courts est obtenue ie : faible DIBL, pente sous le seuil avoisinant les 60 mV/dec [46][47][48].

Figure 0.12 – MOSFET à multiple grilles : (a) DG SOI MOSFET (b) triple grille SOI MOSFET (c)  $\Pi$  SOI MOSFET (d)  $\Omega$  SOI MOSFET (e) GAA SOI MOSFET et (f) triple grille bulk MOSFET.

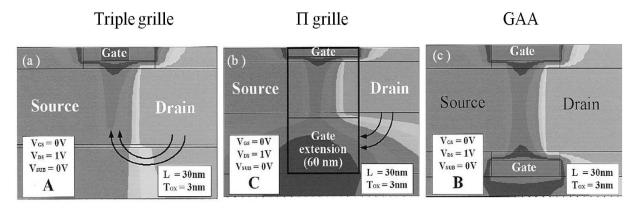

Afin de démontrer l'efficacité du contrôle électrostatique par les dispositifs multiples grilles, Park et al. [46] ont modélisé la distribution des lignes équipotentielles pour des dispositifs à triple grille, Π et GAA MOSFET de longueur de grille de 30 nm. Il a été démontré que même pour un dispositif à triple grille, le canal de conduction subit l'influence des lignes de champ électrique exercées par le drain (fig. 1.13(a)), tandis que l'immunité électrostatique est préservée pour le Π et GAA MOSFET (fig. 1.13 (b, c)). Le contrôle électrostatique est tel pour un MOSFET à grille entourante (GAA) qu'il est possible de réaliser des MOSFETs dont le canal est fortement dopés, appelés également MOSFET sans jonctions [49][50].

Figure 0.13 – Modélisation de la distribution des lignes équipotentielles pour des dispositifs à (a) triple grilles (b) Π et (c) GAA MOSFET [46].

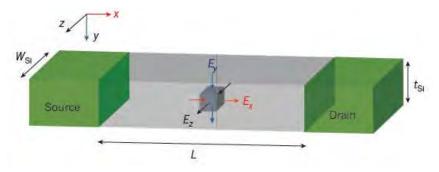

Pour estimer la qualité du contrôle électrostatique de la grille sur le canal de conduction, l'équation de Poisson tridimensionnelle illustre parfaitement la compétition existante entre la grille et le drain pour le contrôle électrostatique du canal :

$$\frac{\sigma\xi}{\sigma x} + \frac{\sigma\xi}{\sigma y} + \frac{\sigma\xi}{\sigma z} = -\frac{\rho}{\epsilon} = constant$$

Équation 0-16

Pour un MOSFET à multiple grilles, le contrôle électrostatique est exercé sur les axes y et z, ce qui entraine une augmentation des termes  $\sigma \xi/\sigma y$  et  $\sigma \xi/\sigma z$  et la diminution du terme  $\sigma \xi/\sigma x$  le long de l'axe x, exercé par le drain (fig.1.14) [45].

Figure 0.14 - Représentation tridimensionnelle du champs électrique dans le canal de conduction [45].

Yan et al. [51] en résolvant l'équation de poisson, ont introduit la longueur naturelle  $\lambda$  (natural length). Elle représente la distance de pénétration des lignes de champ électrique exercée par le drain dans le canal de conduction. En d'autres termes, elle représente la longueur de la région du canal qui est sous le contrôle du drain [52]. Pour un MOSFET à multiple grilles,  $\lambda$  s'exprime par :

$$\lambda_n = \sqrt{\frac{\epsilon_{Si} t_{Si} t_{ox}}{n \epsilon_{ox}} \left(1 + \frac{\epsilon_{ox} t_{Si}}{4 \epsilon_{Si} t_{ox}}\right)}$$

Équation 0-17

où n représente le nombre de grilles,

L'influence du drain sur le contrôle électrostatique du canal est moins effective avec l'augmentation du nombre de grilles ce qui implique que les effets de canaux courts sont mieux maitrisés. Des simulations démontrent qu'un MOSFET est considéré comme libre de toute influence des effets de canaux courts lorsque la longueur de grille effective est supérieure à  $\lambda$  d'au moins 6 fois ( $L_G > 6\lambda$ ) [51]. Suzuki et al. [53] ont proposé un modèle permettant d'estimer la sensibilité des dispositifs MOSFETs à grilles multiples aux effets de canaux courts se basant sur  $\alpha_n$  un facteur de miniaturisation qui s'exprime par :

$$\alpha_{n}=rac{L_{eff}}{2\lambda_{n}}$$

Équation 0-18

Les résultats de simulation, prédisent que pour des effets de canaux courts acceptables, il est nécessaire que la valeur de  $\alpha_n$  soit supérieure à 2.7 pour un DG MOSFET, tandis que pour un GAA MOSFET, une valeur de  $\alpha_n$  égale à 2.3 est suffisante [53] [54].

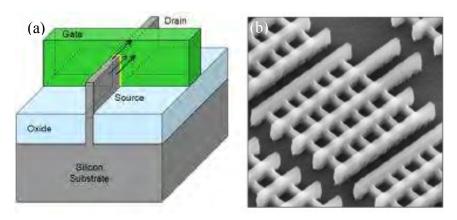

Les MOSFETs à multiple grilles ont fait leur apparition en 2011 au sein de l'industrie des semiconducteurs lorsque Intel a fait un grand saut en passant à l'architecture FinFET à triple grilles pour le nœud technologique 22 nm (fig. 1.15)[54] afin de contrôler les effets de canaux courts et améliorer les performances des MOSFETs. Nous assistons cette année à la deuxième génération des FinFETs pour le nœud technologique 16/14 nm adoptée cette fois par les majeures fonderies de fabrication de MOSFET [55][56][57][58].

Figure 0.15 - "Nœud technologique 22nm à base de "FinFET (a) Illustration (b) Image MEB [32].

Cet intérêt pour les architectures à multiple grilles démontre parfaitement le potentiel de ces dispositifs à surmonter les effets de canaux courts devant la miniaturisation continue des MOSFETs. Toutefois, il est toujours question de contrôle électrostatique de la grille pour les nœuds technologiques suivants, une triple grille suffira-t-elle à exercer un contrôle électrostatique efficace sur le canal de conduction pour des longueurs de grille de plus en plus courtes ? Il est évident que la poursuite de la loi de Moore passe par l'introduction des structures adaptées à une architecture MOSFET à grille entourant tout le canal de conduction (GAA MOSFET).

# 1.6 Transistor sans jonction

La réduction des dimensions des MOSFETs, nécessite la réalisation de jonctions de source et de drain avec un profil de dopage extrêmement abrupt, de telle sorte que la transition d'une zone n à une zone p doit se faire en quelques nanomètres seulement. A cette fin, des techniques extrêmement coûteuses sont employées pour l'activation thermique des dopants qui consistent à réaliser des recuits à des températures assez élevées pendant un très court laps de temps afin de limiter la diffusion des impuretés. Cependant, même avec l'utilisation de recuits ultrarapides, la réalisation de telles jonctions abruptes reste très difficile à réaliser. Colinge et al.[49] ont proposé une architecture MOSFET sans jonction, qui consiste en un ruban de silicium avec un dopage élevé et homogène, c'est-à-dire, sans la nécessité de recourir à de coûteux recuits thermiques ultrarapides pour la réalisation de jonctions abruptes de source et de drain.

Figure 0.16 - MOSFET sans jonction proposé par Colinge et al. [49].

Les transistors sans jonctions (JLT) sont semblables aux transistors fonctionnant en mode d'accumulation (AMT) mais avec la différence que le canal de conduction pour ces derniers est moins dopé que les régions de source et drain (N<sup>+</sup>NN<sup>+</sup>), alors que pour les JLT le dopage est identique pour les 3 terminaux du MOSFET (N<sup>+</sup>N<sup>+</sup>N<sup>+</sup>). Cette différence est fondamentale, car le canal de conduction pour les AMT est formé en surface et est sujet à la rugosité de l'interface oxyde de grille – silicium, tandis que le canal de conduction d'un JLT est formé au centre du ruban de silicium (ou nanofils) et n'est pas sous l'influence du champ électrique perpendiculaire au sens du flux des porteurs.

La figure 1.17 présente le fonctionnement du JLT en fonction de la tension de grille. Le canal de conduction est parfaitement déplété lorsque la tension de grille est inférieure à la tension de seuil (fig. 1.17(a)). Lorsque la tension de grille est égale à la tension de seuil, le canal se forme entre la source et le drain (fig. 1.17(b)) et au fur et à mesure que la tension de grille augmente, le canal s'élargit (fig. 1.17(c)) jusqu'à atteindre la condition de bande plate

(fig.1.17(d)) où le transistor devient comme une résistance, d'où son appellation résistance à grille (gated resistor). A l'inverse des transistors à inversion, la tension de bande plate ( $V_{fb}$ ) est atteinte à une tension de grille supérieure à la tension de seuil.

Figure 0.17 – Variation de la concentration d'électrons dans le canal de conduction d'un transistor sans jonction de type n (a)  $V_g < V_{th}$  le canal est déplété de porteurs (b)  $V_g = V_{th}$  formation du canal de conduction entre la source et le drain (c)  $V_g > V_{th}$  expansion du canal de conduction (d) à condition de bande plate, ie  $V_g = V_{fb} >> V_{th}$  le transistor se comporte comme une simple résistance [49].

Plusieurs équipes de recherches ont proposé des modèles analytiques pour le courant de drain pour les dispositifs JLT [59] [60], cependant, lorsque la condition de bande plate est atteinte, il se comporte comme une simple résistance, il est tout à fait possible d'exprimer le courant d'un JLT par l'équation 1.19 suivante [49] :

où  $N_D$  représente la concentration de dopants,  $W_{si}$  et  $T_{si}$  sont la largeur et épaisseur du film du silicium.

#### 1.7 Nouvelles structures : architectures nanofils

Les nanofils sont des fils qui ont une section de l'ordre de quelques dizaines de nanomètres de diamètre ou de côté et pouvant atteindre quelques nanomètres. Le facteur de forme ou le rapport entre la longueur du nanofil et son diamètre est tellement grand qu'ils sont considérés comme des structures unidimensionnelles. On leur attribue également l'appellation de fils quantiques en raison de leur taille si petite où les effets quantiques ne sont plus négligeables.

La structure nanofils est la structure idéale pour la continuité de la loi de Moore pour la réalisation des dispositifs de plus en plus petits, notamment grâce à son adaptabilité au grille entourant tout le canal de conduction. De plus, des simulations effectuées par Ansari et al.[61] prédisent un bon fonctionnement des MOSFETs à base de nanofils pour une longueur de grille de 3 nm.

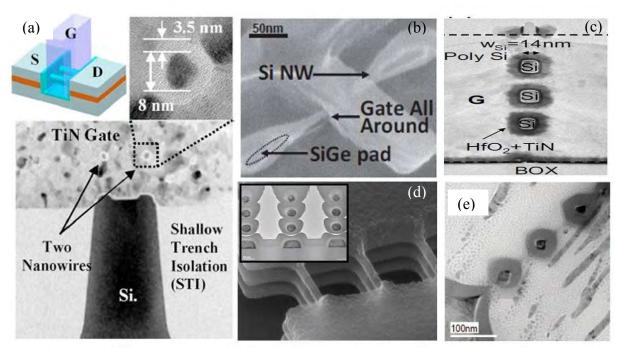

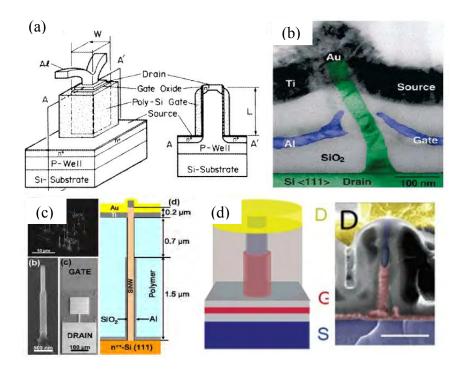

De nombreuses architectures MOSFET à base de nanofils en silicium ont été proposées, il est possible de les classifier selon le mode d'intégration, à savoir horizontal ou vertical.

#### 1.7.1 Architecture horizontale

On peut diviser ce type d'architecture selon l'approche de réalisation, soit ascendante (Bottom-Up) ou descendante (Top-Down). La première consiste à faire croitre des nanofils à partir du substrat tandis que la deuxième approche consiste à réaliser des nanofils par transfert de masque dans le substrat par gravure plasma.

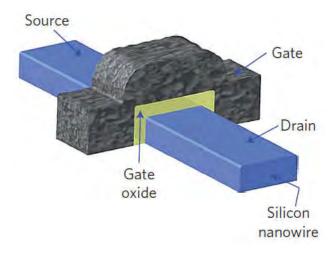

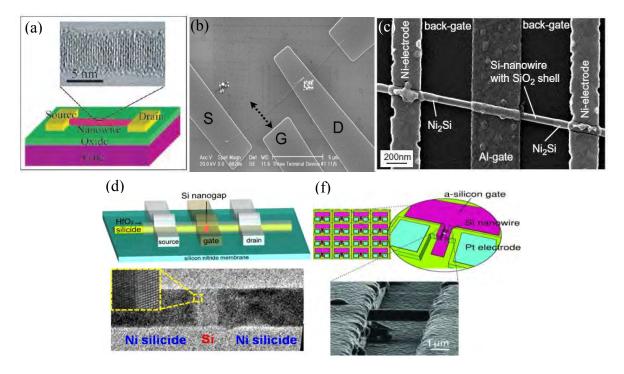

Parmi les premiers travaux sur les dispositifs MOSFET à base de nanofils par approche ascendante, on retrouve les travaux de référence de Cui et al [62], reportant des nanofils synthétisés par méthode Vapeur-Liquide–Solide (VLS) utilisant des nanoparticules d'or comme catalyseurs [63]. Les nanofils de diamètres de 10 à 20 nm ont été cisaillés par sonication puis transférés sur un autre substrat de silicium comprenant un oxyde de 600 nm utilisé comme oxyde de grille. Les contacts de source et de drain en Ti ont été définis sur les deux extrémités du nanofils (fig. 1.18(a)). De la même façon, on retrouve également les travaux de Chung et al.[64], où des nanofils réalisés par VLS ont été reportés sur un substrat avec une grille définie par une électrode au-dessus du nanofils (fig. 1.18(b)). Même si le courant débité n'est pas conséquent, ces études ont démontré la possibilité de concevoir des dispositifs MOSFET à base de nanofils.

L'implémentation de contacts S/D en siliciure de nickel a permis d'améliorer le courant débité ainsi que les caractéristiques sous le seuil (fig. 1.18(c)) [65]. Récemment Tang et al.[66] (fig.1.18(d)) en maitrisant mieux le mécanisme de siliciuration du nickel sur les nanofils, ont proposé une architecture nanofils avec une longueur de grille de 17 nm débitant

un courant maximal de  $890 \mu A/\mu m$ . Oh et al. [67][68] ont démontré la faisabilité de dispositifs MOSFET à base de nanofils suspendus réalisés par la méthode VLS. Après avoir réalisé une tranchée, des particules d'Au ou Ti ont été déposées sur les parois où les nanofils sont réalisés par CVD, jusqu'à atteindre l'autre paroi. L'oxyde de grille est réalisé thermiquement, la grille en polysilicium est définie et les régions de source et de drain sont réalisées sur les deux côtés de la tranchée (fig. 1.18(e)).

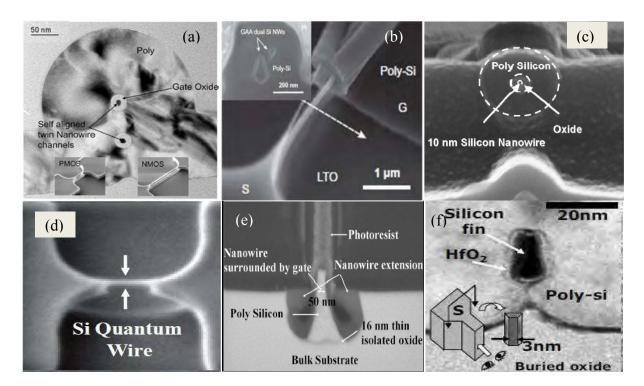

Figure 0.18 - MOSFET à base de nanofils horizontaux par approche ascendante (a) Cui et al [62] (b) Chung et al. [64] (c) Appenzeller et al. [65] (d) Tang et al. [66] et (e) Oh et al. [67].

Malgré les efforts conséquents à valoriser les architectures nanofils réalisées par méthode VLS, celles-ci se caractérisent par un procédé de fabrication très contraignant et inadapté aux techniques VLSI. En commençant par le besoin de synthétiser les nanofils sur un substrat support puis positionner les nanofils par des méthodes telles que la diélectrophorèse [69] sur un autre substrat. La maitrise des dimensions des fils est liée à la taille des catalyseurs métalliques comme l'Au, cependant, considérés comme contaminants, ils dégradent les caractéristiques des MOSFETs.

Les dispositifs MOSFET à base de nanofils horizontaux réalisés selon l'approche descendante sont aussi variés, on retrouve notamment le procédé de réalisation proposé par Rustagi et al. [70] (fig.1.19(a)) et Buddharaju et al. [71] qui consiste par la réalisation d'ailette de très faible largeur par gravure plasma anisotrope à travers un masque de gravure réalisé par procédé photolithographique. Les ailettes sont après soumises à une oxydation thermique

limitée à basse température. Après désoxydation, il en résulte deux nanofils en Si suspendus et superposés de 8 nm de diamètre parfaitement séparés. Ensuite une grille entourant (GAA) en polysilicium et des régions S/D sont réalisées de part et d'autre des nanofils. Ce procédé se distingue par des caractéristiques sous le seuil intéressantes avec un SS quasi idéal (63 mV/dec et 71 mV/dec) ainsi qu'un faible DIBL (50 mV/V et 18 mV/V respectivement pour les p et NMOS). Une variante de ce procédé consiste à réduire les résistances de contact par l'intégration de S/D en siliciure de nickel [72][73], permettant encore l'amélioration du SS et DIBL et l'augmentation du courant I<sub>ON</sub> à 3,74 mA/μm pour les NMOS [74]. Un procédé similaire est proposé par Najmzadeh et al. [75], cependant les nanofils obtenus sont de tailles et de formes aléatoires, altérant la reproductibilité du procédé (fig. 1.19(b)).

On retrouve dans la littérature d'autres dispositifs GAA MOSFET à base de nanofils horizontaux réalisés par une succession du procédé de gravure plasma et d'oxydation limitée à partir d'une ailette de Si (fig. 1.19(c)) par Tian et al. [76] et Wong et al. [77] (fig.1.19(d)) ou à partir de tranchées très rapprochées comme proposé par Song et al. [78] (fig. 1.19(e)). Le dispositif ayant la plus faible longueur de grille (5 nm) a été proposé par Lee et al. [79] au détriment des caractéristiques sous le seuil (fig.1.19(f)).

Figure 0.19 – MOSFET à base de nanofils en Si suspendus proposés par (a) Rustagi [70] (b) [75] (c) Tian et al. [76](d) Wong et al. [77] (e) Song et al. [78] et (f) Lee et al. [79].

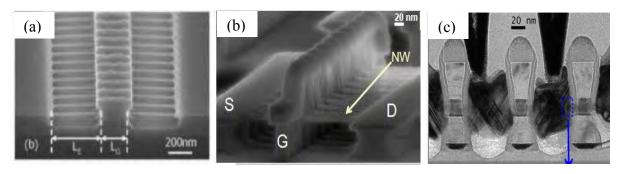

Des dispositifs MOSFET à base de réseaux de nanofils disposés parallèlement ont été proposés par Gunawan et al. [80] (fig. 1.20(a)) ainsi que par Bangsaruntip et al. [81]. Le

procédé de fabrication se base également sur la gravure plasma et l'oxydation limitée. Cependant, la spécificité du procédé de Bangsauntip et al. réside dans l'exposition des ailettes à un recuit thermique sous gaz H<sub>2</sub>. Cette étape permet de réduire les dimensions tout en lissant les formes des ailettes et en arrondissant la section des nanostructures. L'oxydation limitée permet de réduire la taille des nanofils suspendus jusqu'à 5 nm de diamètre (fig. 1.20(b)). Cette architecture démontre l'intégration de nanofils avec un courant de conduction élevé de 3,456 mA/μm et 4,147 mA/μm, respectivement pour N et PMOS. Plus récemment, le même groupe de recherche a optimisé ce procédé pour la réalisation d'une architecture à nanofils suspendus à forte densité pour le nœud technologique 10 nm. Elle intègre plusieurs MOSFETs sur toute la longueur du nanofil en alternant les grilles et les régions S/D réalisées, in situ, par épitaxie [82] (fig. 1.20(c)).

Figure 0.20 -GAA MOSGET à base de réseau de nanofils suspendus (a) Gunawan et al.[80] Bangsaruntip et al. [81] (c) large densité d'intégration pour le nœud technologique 10 nm [82].

Une technique innovante pour la réalisation des nanofils horizontaux a été proposée par plusieurs groupes de recherche à partir d'un empilement de fines couches de Si/SiGe réalisées par épitaxie en se servant du SiGe comme couche sacrificielle. Le principe consiste à transférer l'ailette dans le silicium puis graver le SiGe afin de libérer les nanofils de silicium. Cette méthode a également été proposée par les chercheurs de Samsung pour la réalisation du Twin Si Nanowire GAA MOSFET [83][84][85][86][87][88][89] où des nanofils en Si suspendus de diamètre minimal de 3 nm sont intégrés (fig. 1.21(a)). Une équipe de STMicroelectronics propose également une approche similaire mais utilisant un procédé lithographique 3D à base du diélectrique HSQ [90] (fig. 1.21(b)).

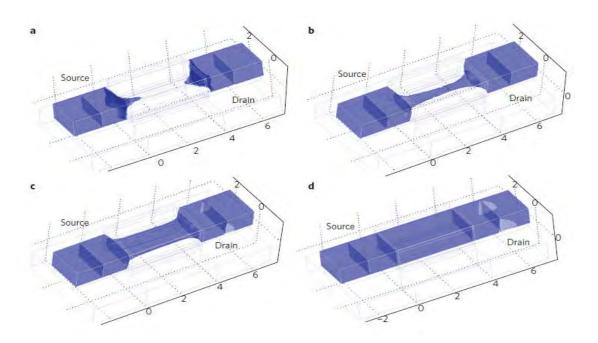

Afin d'augmenter le courant de conduction, des procédés de réalisation d'empilement vertical de nanofils horizontaux par la multiplication des couches épitaxiées de Si/SiGe ont été proposés, comme celui présenté par Dupré et al. [91](fig. 1.21(c)) avec la réalisation de nanofils de section rectangulaire de 70 nm de largeur et 20 nm d'épaisseur, puis de section carré de 20 nm de côté. Dornel et al. [92][93] ont appliqué un recuit thermique sous H<sub>2</sub> afin

d'arrondir la section des nanofils (fig. 1.21(d)). Cette configuration a permis d'obtenir un courant de conduction maximal de 6.5 mA/μm pour les NMOS [94]. D'autres travaux d'empilement de nanofils ont été présentés [95][96] à partir de la gravure du silicium à travers un masque de gravure par procédé de gravure Bosch utilisant le gaz SF6 suivi d'oxydation limitée afin de délimiter les nanofils (fig. 1.21(e)).

Figure 0.21 – (a- b) Procédé utilisant le SiGe comme couche sacrificielle pour la réalisation des nanofils suspendus par Suk et. [86] et Coquand et al. [90] respectivement, (c et d) empilement vertical de nanofils en Si suspendus en utilisant le système Si/SiGe par Dupré et al. [94] et Suk et al. [92] respectivement et (e) empilement vertical de nanofils en Si suspendus obtenus par procédé gravure Bosch et oxydation limitée [95].

Sur la table 1.2, un comparatif de résultats pour les différentes architectures proposées de MOSFET à base de nanofils horizontaux réalisés par approche top- down est proposé.

Tableau 1.2- tableau comparatif de résultats pour les différentes architectures de MOSFET à base de nanofils horizontaux réalisés par approche top down.

| SS<br>(mV/dec) | DIBL<br>(mV/V) | $ m I_{ON}/ m I_{Off}$ | I <sub>ON</sub><br><sub>(</sub> μΑ/μm) | VDD (V) | EOT ou<br>Tox (nm)                    | Empile-<br>ment de<br>grille | Lg (nm)                  | Diamètre<br>(nm) | Section du<br>NF (nm) | Nombre de<br>NF | Type<br>MOSFET |                   |

|----------------|----------------|------------------------|----------------------------------------|---------|---------------------------------------|------------------------------|--------------------------|------------------|-----------------------|-----------------|----------------|-------------------|

| 71             | 18             | >107                   | 862                                    | 1       | 1                                     | SiO <sub>2</sub> /           | 775                      |                  | Circ                  |                 | Z              | Rusta             |

| 63             | 50             |                        | 107                                    | 800     | 1.2                                   | 10                           | SiO <sub>2</sub> /PolySi | 275              | - ∞                   | Circulaire      | 2              | P                 |

| 71             | 13             | $10^{6}$               | 2640                                   | 1       | 2                                     | SiO <sub>2</sub> /<br>TiN    | 30                       | 10               | Circul-<br>aire       | 2               | Z              | Suk<br>[86]       |

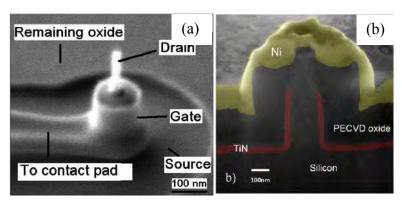

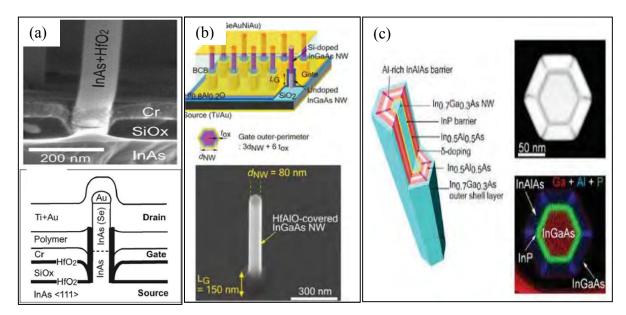

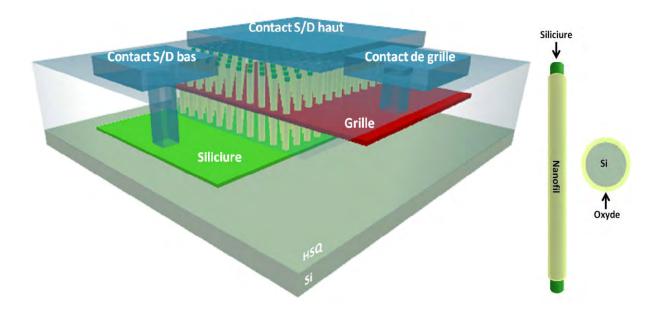

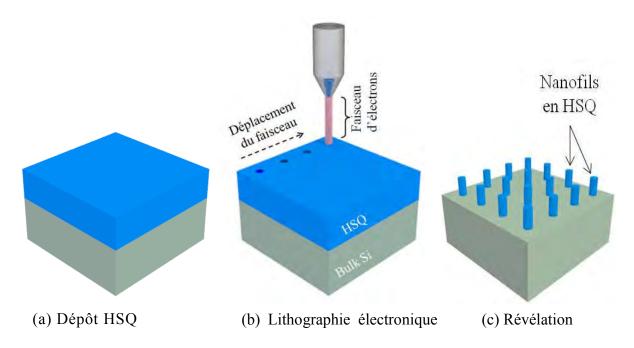

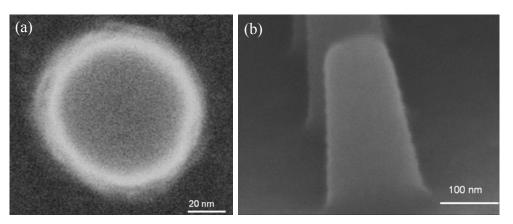

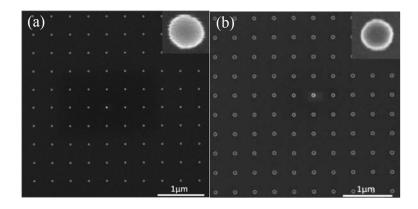

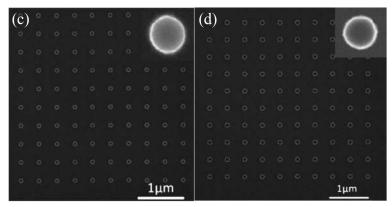

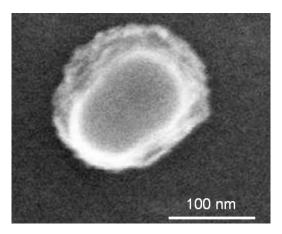

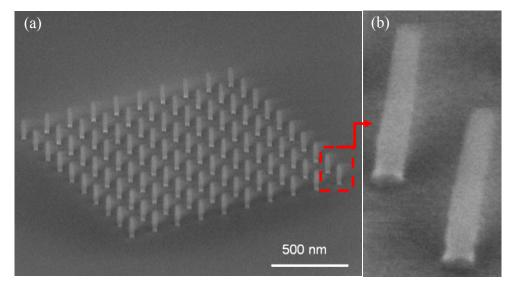

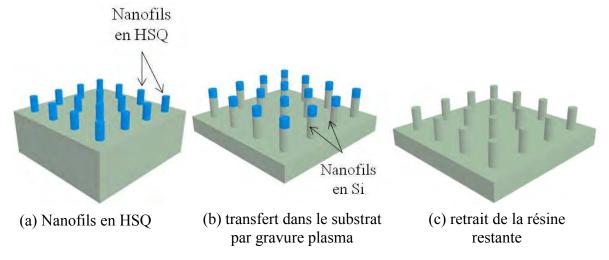

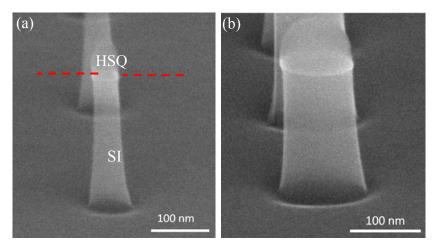

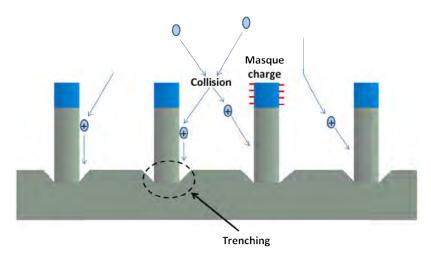

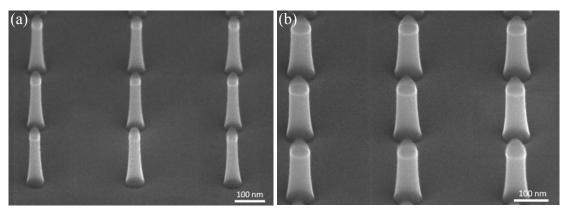

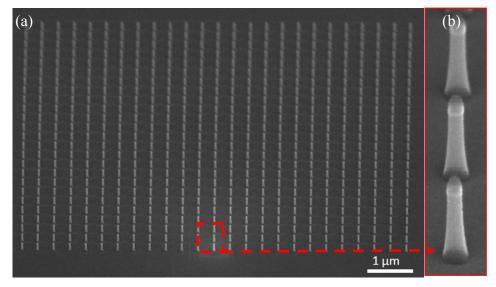

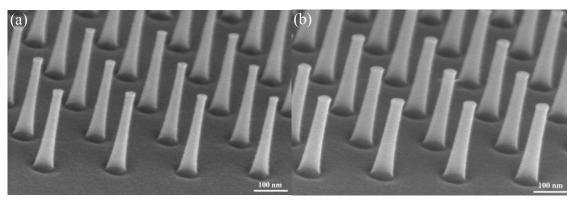

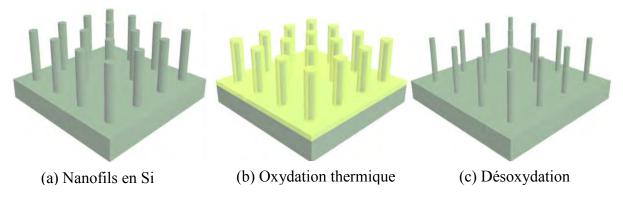

| 72             | 4 - 12         | >108                   | 1039                                   | 1.5     | 5                                     | SiO <sub>2</sub> /<br>PolySi | 120                      | 10               | Circul-<br>aire       | 1               | Z              | Zhuge<br>[97]     |