En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

**Délivré par :** l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier) Cotutelle internationnale avec l'Université de Modena and Reggio Emilia

> Présentée et soutenue le 14/04/2014 par : Alessandro MAGNANI

Circuits CMOS et BiCMOS pour une conversion de fréquence efficace jusqu'aux fréquences millimetriques

FAUSTO FANTINI MATTIA BORGARINO THIERRY PARRA CHRISTOPHE VIALLON ANDREA BONI SYLVAIN BOURDEL JURY Professeur d'Université Professeur d'Université Maître de Conférence Professeur d'Université Professeur d'Université

Président du Jury Directeur de thése Directeur de thése Membre du Jury Rapporteur Rapporteur

#### École doctorale et spécialité :

GEET : Micro-Ondes, Electromagnétisme et Optoélectronique Unité de Recherche : Laboratoire d'analyse et d'architecture des systèmes (LAAS-CNRS) Directeur(s) de Thèse : Prof. Thierry PARRA et Prof. Mattia BORGARINO Rapporteurs : Prof. Andrea BONI et Prof. Sylvain BOURDEL

# THESIS IN CO-TUTELE

## UNIVERSITY OF MODENA AND REGGIO EMILIA

Information and Communications Technology Doctorate School cycle XXVI Director: Prof. Giorgio Matteo VITETTA

and

# UNIVERSITY PAUL SABATIER TOULOUSE III

Ecole Doctorale Génie Electrique, Electronique, Télécommunications

presented by Alessandro MAGNANI

in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY in: Electronics and Telecommunications

## CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

Discussion scheduled for 14 April 2014 Examinators: Prof. Andrea BONI Prof. Sylvain Bourdel Commission: Prof. Mattia BORGARINO Prof. Thierry PARRA Un Prof. Christophe VIALLON Un

**Prof. Fausto FANTINI**

University of Parma INP, Grenoble

University of Modena and Reggio EmiliaAdvisorUniversity UPS ToulouseAdvisorUniversity UPS ToulouseUniversity of Modena and Reggio Emilia

# THESIS IN CO-TUTELE

## Université de Modena and Reggio Emilia

Information and Communications Technology Doctorate School cycle XXVI Director: Prof. Giorgio Matteo VITETTA

and

# Université Paul Sabatier Toulouse III

Ecole Doctorale Génie Electrique, Electronique, Télécommunications

presented by Alessandro MAGNANI

Pour obtenir le grade de

DOCTEUR in: Électronique

## Circuits CMOS et BiCMOS pour une conversion de fréquence efficace jusqu'aux fréquences millimetriques.

Soutenance prévue le 14 Avril 2014 Rapporteurs: Prof. Andrea BONI Prof. Sylvain Bourdel Commission: Prof. Mattia BORGARINO Prof. Thierry PARRA Prof. Christophe VIALLON

**Prof. Fausto FANTINI**

University of Parma INP, Grenoble

University of Modena and Reggio Emilia University UPS Toulouse University UPS Toulouse University of Modena and Reggio Emilia

Directeur de thèse Directeur de thèse

## THESIS IN CO-TUTELA with

## UNIVERSITÀ OF MODENA AND REGGIO EMILIA

Information and Communications Technology Doctorate School cycle XXVI Director: Prof. Giorgio Matteo VITETTA

and

# Università Paul Sabatier Toulouse III

Ecole Doctorale Génie Electrique, Electronique, Télécommunications

presented by Alessandro MAGNANI

per conseguimento del titolo di

## DOTTORE DI RICERCA in: Elettronica e Telecomunicazioni

## Realizzazione in tecnologia CMOS e BiCMOS dei principali blocchi costruttivi utilizzati per realizzare la conversione di frequenza in modo efficiente, utilizzabili fino in banda millimetrica.

Discussione prevista il 14 Aprile 2014 Esaminatori: Prof. Andrea BONI Prof. Sylvain Bourdel Commissione: Prof. Mattia BORGARINO University of Modena and Reggio Emilia University UPS Toulouse **Prof. Thierry PARRA Prof. Christophe VIALLON Prof. Fausto FANTINI**

INP, Grenoble

University of Parma

Relatore Relatore

University UPS Toulouse University of Modena and Reggio Emilia

# Acknowledgments

First of all, I would like to thank my advisor Mattia Borgarino for providing me the opportunity to do this fascinating but challenging experience. He has always assured me a constant support and he has giving me the chance of doing a remarkable experience outside Italy.

Thank you also to the other advisor Thierry Parra for making possible this experience in France and host me again in a dynamic environment in the LAAS.

Then, a special acknowledgement to my co-advisor Christophe Viallon who couldn't appear officially as co-supervisor due to administrative constraints, but has always being supervising and supporting me during these two years that I have spent in the LAAS.

Thanks to Alexandre Rumeau for the support during the circuit measurements and overall for making pleasant the staying in "salle de manip" with the smooth melody of the cryoprober. Thanks also to Xavier Bouquet for his essential support in the assembly of the circuits for testing.

I would like to thank all the people (they are too many to say all the names) that I have met outside and inside the labs, in Toulouse and in Modena, for being with me in the worst and the great moments.

Finally I would like to thanks my family for being at my side even being separated by some hundreds of kilometers.

# Table of Contents

| Chapte<br>2.1<br>2.2 |        | Xu-band Phase Locked Oscillator                                                                    |    |

|----------------------|--------|----------------------------------------------------------------------------------------------------|----|

|                      | Introd | Tu banu i nase noticu Osemator                                                                     | 3  |

| 2.2                  | minuu  | uction                                                                                             | 3  |

|                      | Theore | etical recalls                                                                                     | 5  |

|                      | 2.2.1  | Phase locked loop linear model $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$           | 5  |

|                      | 2.2.2  | Loop filter                                                                                        | 7  |

| 2.3                  | Circui | t design $\ldots$ | 10 |

|                      | 2.3.1  | General architecture                                                                               | 10 |

|                      | 2.3.2  | Employed technology                                                                                | 10 |

|                      | 2.3.3  | Quadrature voltage controlled oscillator                                                           | 11 |

|                      | 2.3.4  | Frequency divider                                                                                  | 12 |

|                      | 2.3.5  | Phase frequency detector                                                                           | 16 |

|                      | 2.3.6  | Charge pump and Loop Filter                                                                        | 17 |

| 2.4                  | Simula | ated performances                                                                                  | 19 |

| 2.5                  | Exper  | imental performances                                                                               | 21 |

|                      | 2.5.1  | Measurements setup                                                                                 | 21 |

|                      | 2.5.2  | Results                                                                                            | 22 |

| 2.6                  | Conclu | usions                                                                                             | 27 |

| Chapte               | r 3 1  | K-band Fundamental Sampling Mixer                                                                  | 29 |

| 3.1                  | Introd | uction                                                                                             | 29 |

| 3.2                  | The fr | equency translation using sampling theory                                                          | 30 |

| 3.3                  | Analy  | tical modeling of sampling mixer                                                                   | 31 |

|                      | 3.3.1  | Simplified electrical network derivation                                                           | 32 |

|                      | 3.3.2  | Time-domain analytic conversion gain calculation                                                   | 34 |

|                      | 3.3.3  | Discussion on the low-pass filter                                                                  | 35 |

|                      | 3.3.4  | Frequency-related analytic conversion gain derivation                                              | 36 |

|                      | 3.3.5  | Discussion on sampling mixer's conversion gain                                                     | 37 |

| 4.4<br>4.5 | 4.3.2<br>4.3.3<br>State-<br>Conclu | 4.3.1.1Conversion gain versus LO power                                                                                        |                                  |

|------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|            | 4.3.3<br>State-                    | 4.3.1.1Conversion gain versus LO power                                                                                        | 64<br>65<br>65<br>67<br>68<br>69 |

|            | 4.3.3                              | 4.3.1.1Conversion gain versus LO power <td>64<br/>65<br/>65<br/>67<br/>68</td>                                                | 64<br>65<br>65<br>67<br>68       |

|            | -                                  | 4.3.1.1Conversion gain versus LO power4.3.1.2Model comparison4.3.1.3Conversion gain versus RF frequency1 dB Compression point | 64<br>65<br>65<br>67             |

|            |                                    | <ul> <li>4.3.1.1 Conversion gain versus LO power</li></ul>                                                                    | 64<br>65<br>65                   |

|            |                                    | <ul><li>4.3.1.1 Conversion gain versus LO power</li></ul>                                                                     | 64<br>65                         |

|            |                                    |                                                                                                                               |                                  |

|            |                                    |                                                                                                                               |                                  |

|            | 4.3.1                              | Conversion Gain                                                                                                               |                                  |

| 4.3        | Chara                              | cterization of the mixer in a sub-sampling operation $\ldots \ldots \ldots$                                                   | 62                               |

|            | 4.2.2                              | Sub-harmonic mixers (SHM)                                                                                                     | 61                               |

|            | 4.2.1                              | Fundamental mixers                                                                                                            | 60                               |

| 4.2        | $60\mathrm{GH}$                    | z mixer state-of-the-art                                                                                                      | 60                               |

| 4.1        | Introd                             | uction                                                                                                                        | 59                               |

| nique      |                                    |                                                                                                                               | 59                               |

| Chapte     | er 4 1                             | Bandwidth Extension to V-band Using Sub-sampling Tech-                                                                        |                                  |

|            | 3.6.7                              | Conclusion and state-of-the-art comparison                                                                                    | 55                               |

|            | 3.6.6                              | Measured bandwidth of the sampling mixer                                                                                      | 55                               |

|            | 3.6.5                              | Noise Figure                                                                                                                  | 53                               |

|            | 3.6.4                              | $1 \mathrm{dB}$ Compression point $\ldots \ldots \ldots$       | 52                               |

|            | 3.6.3                              | Conversion Gain                                                                                                               | 51                               |

|            | 3.6.2                              | K-band rat-race balun                                                                                                         | 50                               |

|            | 3.6.1                              | Description of the test-bench $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                | 48                               |

| 3.6        | Exper                              | imental results                                                                                                               | 48                               |

|            | 3.5.2                              | IF Amplifier                                                                                                                  | 47                               |

|            | 3.5.1                              | Mixing device sizing optimization                                                                                             | 46                               |

| 3.5        | Descri                             | ption of the fundamental sampling mixer                                                                                       | 45                               |

|            | 3.4.4                              | Layout considerations and final simulations                                                                                   | 44                               |

|            | 3.4.3                              | Class-A inverting amplifier                                                                                                   | 42                               |

|            | 3.4.2                              | A pulse-shaping circuit based on Class-C technique                                                                            | 41                               |

|            | 3.4.1                              | d pulse shaping circuit                                                                                                       | 40<br>41                         |

| 3.4        | II ban                             |                                                                                                                               |                                  |

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to II millimeter-Waves.

| Chapte         | A Trapezoidal, triangular and square waves Fourier trans- |    |

|----------------|-----------------------------------------------------------|----|

| form ca        | culation 7                                                | 75 |

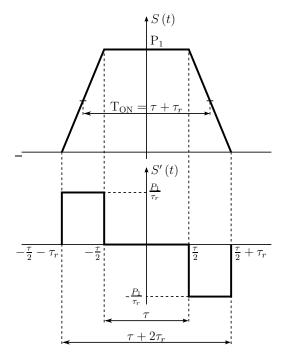

| A.1            | Trapezoidal waveform                                      | 75 |

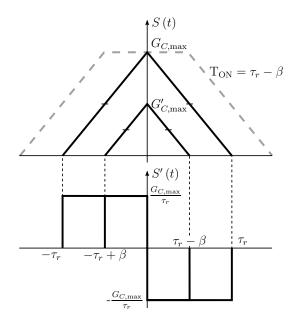

| A.2            | Friangular waveform                                       | 77 |

| A.3            | Square waveform                                           | 79 |

| יוות           |                                                           | 14 |

| Publications 8 |                                                           |    |

III CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

# List of Figures

| 1.1  | Receiver block diagram                                                                         | 2  |  |

|------|------------------------------------------------------------------------------------------------|----|--|

| 2.1  | PLL linar phase-domain model                                                                   | 5  |  |

| 2.2  | Schematic of $2^{nd}$ (a) and $3^{nd}$ -order (b) loop filter                                  |    |  |

| 2.3  | $3^{rd}$ -order overall system magnitude and phase information of open loop gain.              |    |  |

| 2.4  | Phase Locked Oscillator Blocks Diagram.                                                        | 10 |  |

| 2.5  | 130 nm CMOS STM technology (HCMOS9GP)                                                          | 11 |  |

| 2.6  | Schematic of the Quadrature VCO                                                                | 11 |  |

| 2.7  | Schematic of: (a) Master-Slave divide-by-two frequency divider, (b) CML                        |    |  |

|      | latch, (c) CML buffer, (d) Digital divider                                                     | 12 |  |

| 2.8  | Output frequency versus input frequency of the first CML divide-by-                            |    |  |

|      | two frequency divider for several corner cases under worst case parasitic                      |    |  |

|      | extraction                                                                                     | 15 |  |

| 2.9  | Detailed layout of the interface between the QVCO and the frequency                            |    |  |

|      | divider                                                                                        | 16 |  |

| 2.10 | Schematic of the designed PFD                                                                  | 16 |  |

| 2.11 |                                                                                                |    |  |

|      | PFD phase noise performance (b)                                                                | 17 |  |

| 2.12 | Schematic of the designed CP                                                                   | 18 |  |

| 2.13 | Simulated transient PLO behavior                                                               | 19 |  |

| 2.14 | Simulated closed loop phase noise contributions                                                | 20 |  |

| 2.15 | (a) Die microphotograph of the fabricated PLO, (b) test board detail with                      |    |  |

|      | filtering capacitors highlighted                                                               | 21 |  |

| 2.16 | Measured output spectrum (a) and $\text{Div}_Q$ et $\text{Div}_I$ frequency divider output (b) | 23 |  |

| 2.17 | Comparison between measured and simulated phase noise                                          | 23 |  |

| 2.18 | Comparison between the simulated phase noise with $25\mu\mathrm{A}$ and $300\mu\mathrm{A}$     |    |  |

|      | charge pump current; red symbols are DVB-S standard phase noise limits.                        | 25 |  |

| 2.19 | Charge pump current effects on phase noise performances reported with                          |    |  |

|      | LF relative size                                                                               | 25 |  |

|      |                                                                                                |    |  |

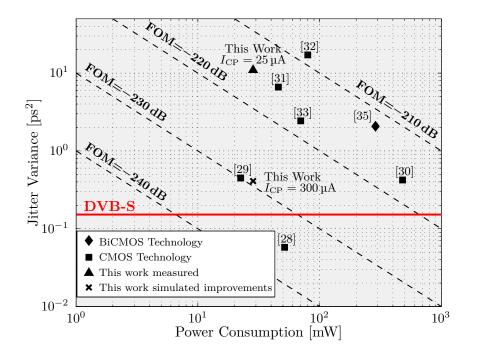

| 2.20 | Jitter and power comparison between the PLO reported in this work and                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | others PLL reported in the literature in term of $FOM_{PLL}$                                                                                      | 28 |

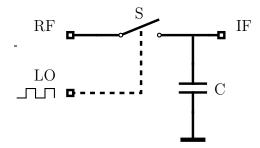

| 3.1  | Simplified model of sampling mixer.                                                                                                               | 30 |

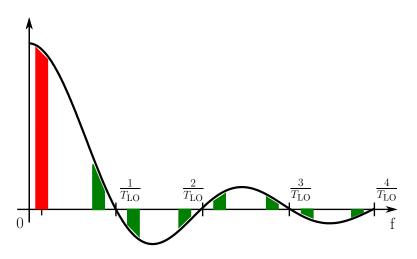

| 3.2  | Spectrum of the IF voltage.                                                                                                                       | 31 |

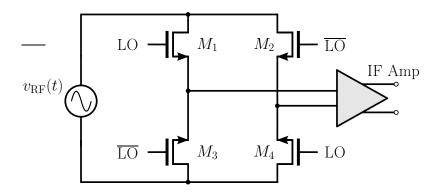

| 3.3  | Schematic of a ring mixer.                                                                                                                        | 31 |

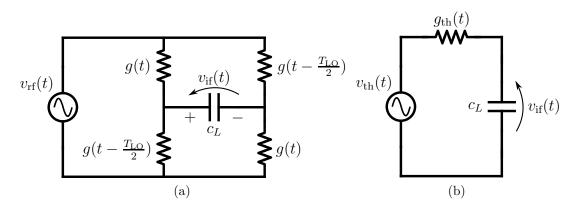

| 3.4  | Equivalent schematic of the mixer (a) and its Thévenin representation                                                                             |    |

|      | from IF balanced output (b)                                                                                                                       | 32 |

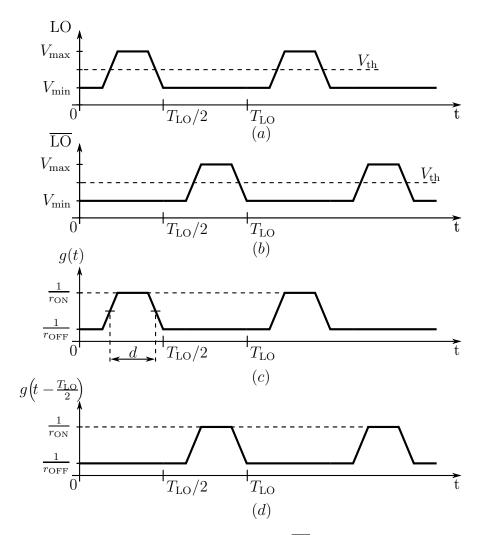

| 3.5  | Waveform of the driven voltage signals LO and $\overline{\text{LO}}$ (a),(b) and the relative                                                     |    |

|      | conductances variation.                                                                                                                           | 33 |

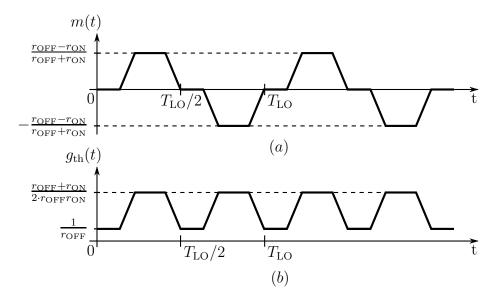

| 3.6  | Waveforms of mixing function $m(t)$ (a), and Thévenin conductance $g_{\rm th}(t)$                                                                 |    |

|      | (b)                                                                                                                                               | 34 |

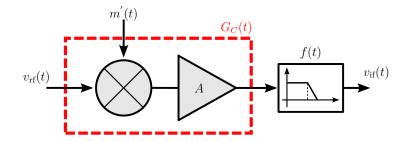

| 3.7  | Equivalent block diagram of the sampling mixer for conversion gain calcu-                                                                         |    |

|      | lation                                                                                                                                            | 35 |

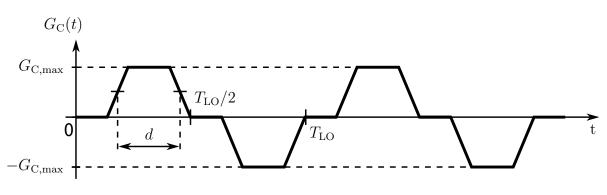

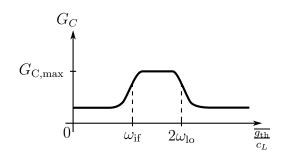

| 3.8  | Conversion gain function waveform.                                                                                                                | 35 |

| 3.9  | Condition on $c_L$ to optimize conversion gain                                                                                                    | 36 |

| 3.10 | Conversion gain with $f_{\rm LO} = 19 \text{GHz}, f_{\rm RF} = 20 \text{GHz}$                                                                     | 37 |

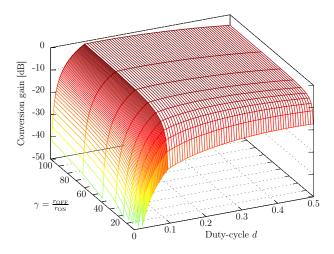

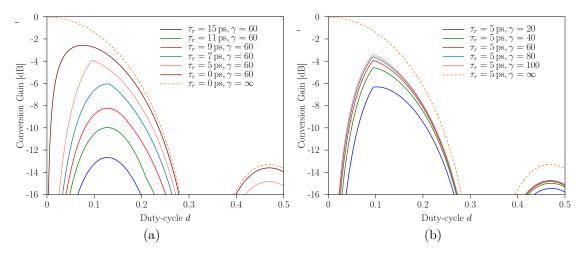

| 3.11 | Calculated conversion gain with $f_{\rm RF} = 39 \text{GHz}$ in (a) and 58 GHz in (b).                                                            |    |

|      | $f_{\rm LO} = 19 \mathrm{GHz}.$                                                                                                                   | 38 |

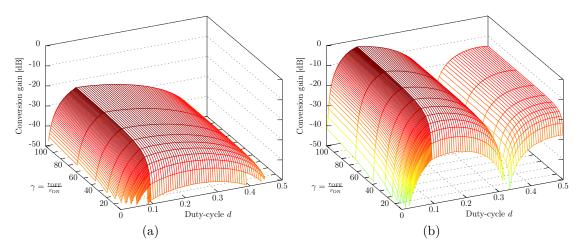

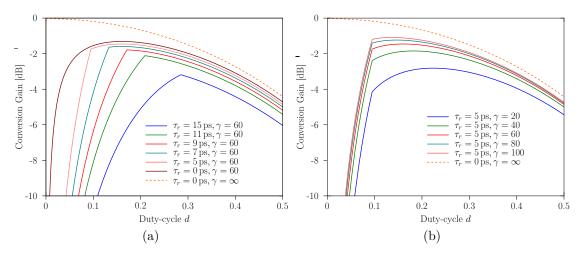

| 3.12 | Estimated conversion gains by the model in "normal condition" ( $f_{\rm LO} =$                                                                    |    |

|      | 19 GHz, $f_{\rm RF} = 20$ GHz) with: (a) different $\tau_r$ values fixing $\gamma = 60$ and (b)                                                   |    |

|      | different $\gamma$ values fixing $\tau_r = 5 \mathrm{ps.} \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                         | 39 |

| 3.13 | Estimated conversion gains by the model in "sub-harmonic condition"                                                                               |    |

|      | $(f_{\rm LO} = 19 {\rm GHz}, f_{\rm RF} = 58 {\rm GHz})$ with: (a) different $\tau_r$ values fixing $\gamma = 60$                                 |    |

|      | and (b) different $\gamma$ values fixing $\tau_r = 5 \text{ ps.} \dots \dots \dots \dots \dots \dots \dots$                                       | 39 |

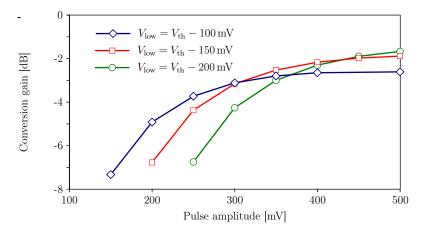

| 3.14 | Different conversion gain obtained by different $25\%$ LO square wave voltage                                                                     |    |

|      | $amplitude. \ldots \ldots$ | 40 |

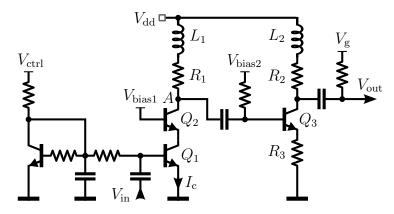

| 3.15 | Schematic of the pulse shaper.                                                                                                                    | 42 |

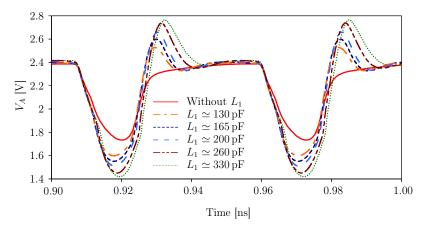

| 3.16 | Simulated waveform at the class-C output with different $L_1$ values com-                                                                         |    |

|      | parison.                                                                                                                                          | 42 |

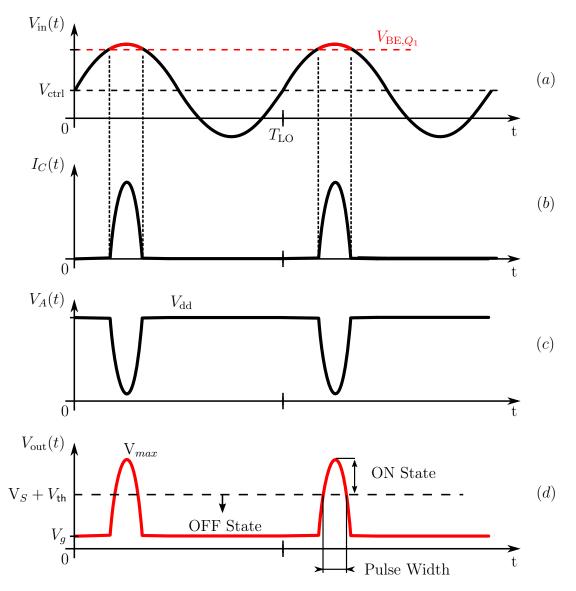

| 3.17 | Pulse waveforms in different points of the pulse shaper: sinusoïdal input                                                                         |    |

|      | voltage (a), class-C current (b), output voltage (c), and output class-A                                                                          |    |

|      | voltage (d)                                                                                                                                       | 43 |

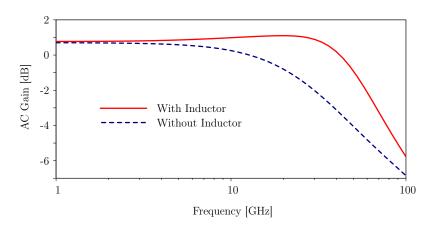

| 3.18 | Simulated AC gain of Class-A amplifier                                                                                                            | 44 |

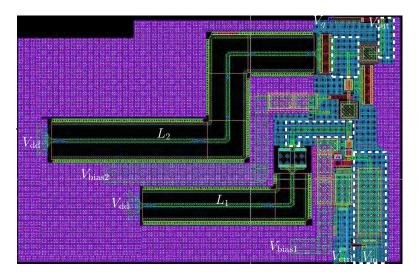

| 3.19 | Pulse shaper layout.                                                                                                                              | 44 |

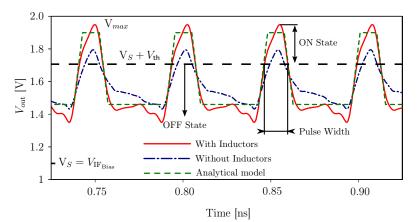

| 3.20 | Simulated output waveform of the pulse shaper at 19 GHz                                                                                           | 45 |

|      |                                                                                                                                                   |    |

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to VI millimeter-Waves.

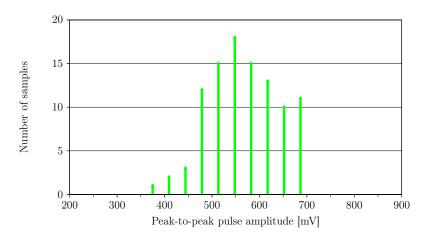

| 3.21 | Monte Carlo simulations representing Peak-to-peak amplitude for 100                |    |

|------|------------------------------------------------------------------------------------|----|

|      | samples.                                                                           | 46 |

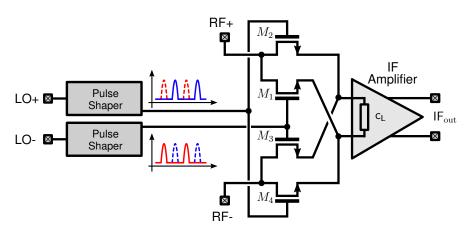

| 3.22 | Block diagram of the fundamental sampling mixer.                                   | 46 |

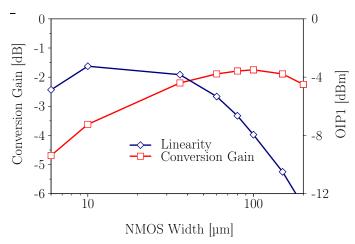

| 3.23 | Conversion gain and linearity variations of the ring mixer versus NMOS             |    |

|      | widths                                                                             | 47 |

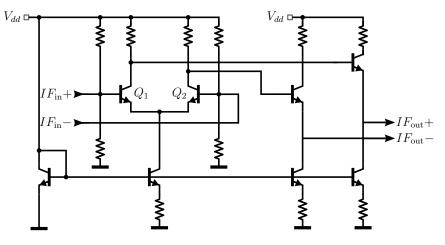

| 3.24 | Schematic of the IF amplifier                                                      | 48 |

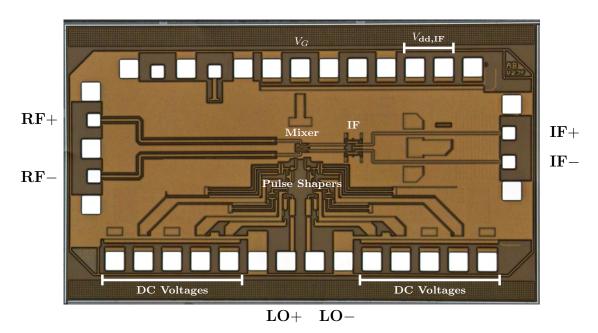

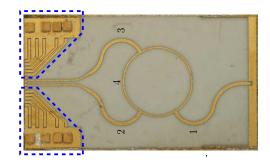

| 3.25 | Die micro-photograph of the fabricated down-converter.                             | 49 |

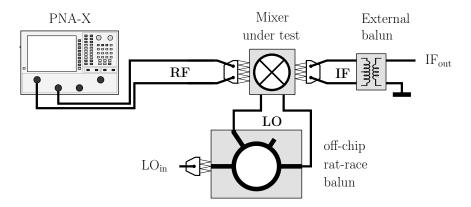

| 3.26 | Test-bench used for mixer characterization                                         | 49 |

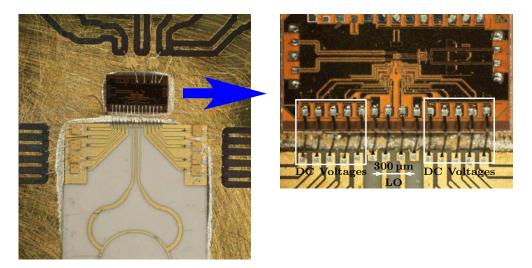

| 3.27 | Balun-die interface with wires bonding and DC-filtering microcapacitors.           | 50 |

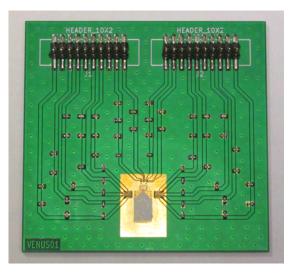

| 3.28 | FR4 test board                                                                     | 51 |

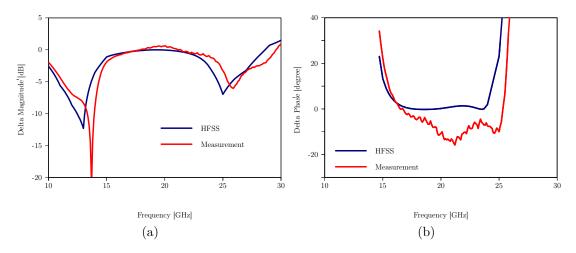

| 3.29 | Simulated and measured S-parameters delta magnitude (a) and delta phase            |    |

|      | (b) of the alumina balun                                                           | 51 |

| 3.30 | Rat-race balun microphotograph                                                     | 52 |

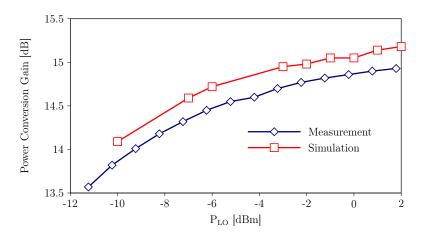

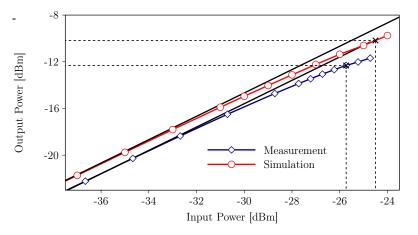

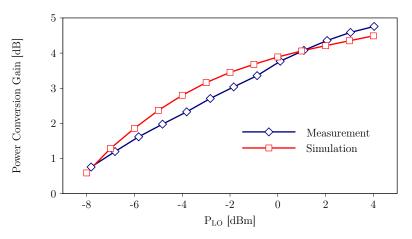

| 3.31 | Measured and simulated conversion gain.                                            | 52 |

| 3.32 | Mixer-only simulated conversion gain.                                              | 53 |

| 3.33 | 1 dB compression point extraction with $f_{RF} = 18.8 \text{GHz}$ and $f_{LO} =$   |    |

|      | 17.8 GHz                                                                           | 53 |

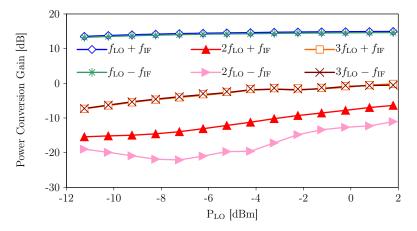

| 3.34 | Measured conversion gains around $2\prod$ and $3\prod$ the LO frequency            | 54 |

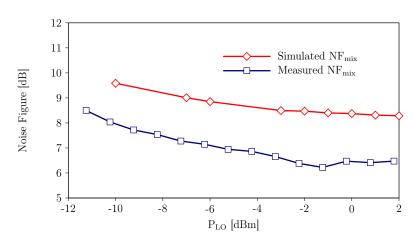

| 3.35 | Simulated and measured noise figure                                                | 54 |

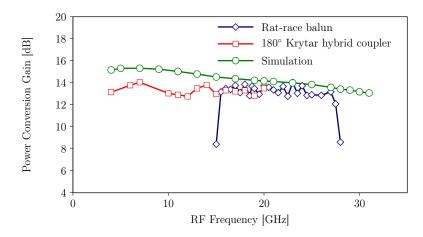

| 3.36 | Simulated and measured bandwidth of the sampling mixer                             | 56 |

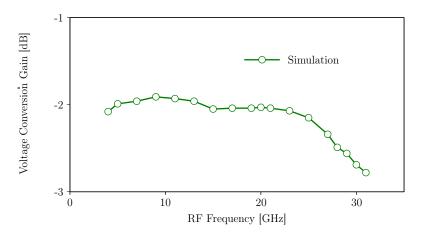

| 3.37 | Simulated voltage conversion gain of the sampling ring mixer                       | 56 |

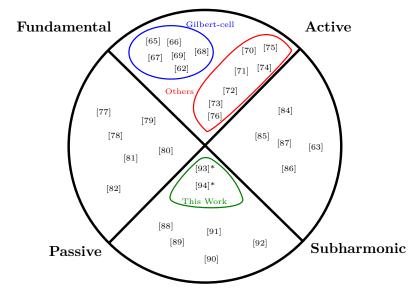

| 4.1  | Different categories of 60 GHz mixers published to date                            | 62 |

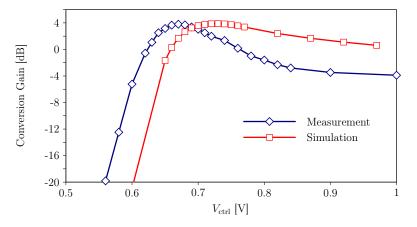

| 4.2  | Simulated and measured conversion gain variations for different values of          |    |

|      | $V_{\rm ctrl}$ for a fixed value of $P_{\rm LO} = 0  {\rm dBm}$ .                  | 63 |

| 4.3  | Simulated conversion gain variations for different values of duty-cycle with       |    |

|      | $P_{\rm LO} = 0 \mathrm{dBm}.$                                                     | 63 |

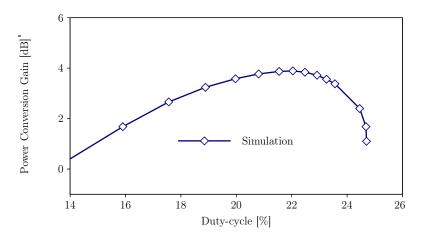

| 4.4  | Measured and simulated power conversion gain of the couple mixer/IF-               |    |

|      | amplifier, at a RF frequency of 58 GHz.                                            | 64 |

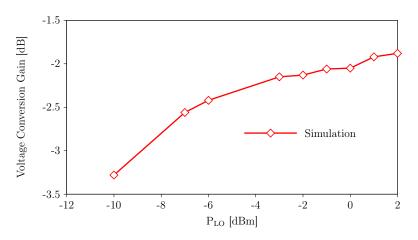

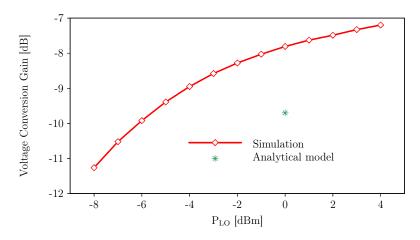

| 4.5  | Mixer-only simulated voltage conversion gain at a RF frequency of $58\mathrm{GHz}$ | 65 |

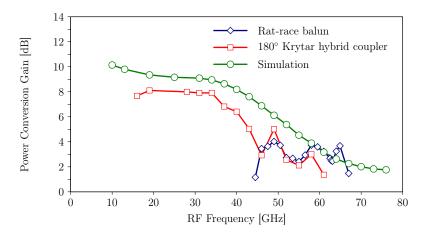

| 4.6  | Simulated and measured power conversion gain for the down-converter,               |    |

|      | LO power is 0dBm                                                                   | 66 |

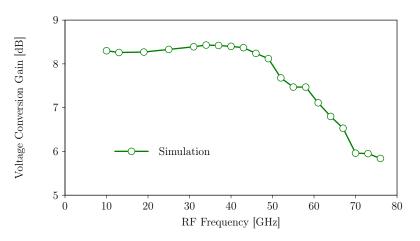

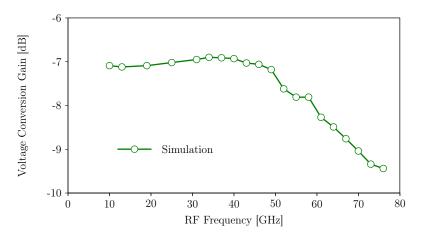

| 4.7  | Simulated voltage conversion gain of the downconverter versus RF fre-              |    |

|      | quency, LO power is 0dBm                                                           | 67 |

| 4.8  | Simulated voltage conversion gain of the single mixer versus RF frequency,         |    |

|      | LO power is 0dBm                                                                   | 67 |

|      |                                                                                    |    |

VII CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

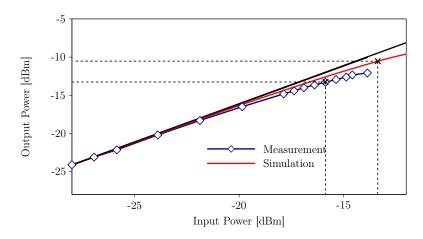

| 4.9  | .9 Measured and simulated output IF power versus input RF power at an            |    |  |

|------|----------------------------------------------------------------------------------|----|--|

|      | input RF frequency of 58 GHz.                                                    | 68 |  |

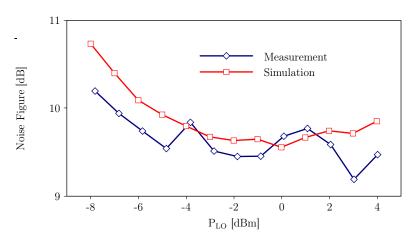

| 4.10 | Simulated and measured down-converter noise figure. Frequencies $58\mathrm{GHz}$ | 68 |  |

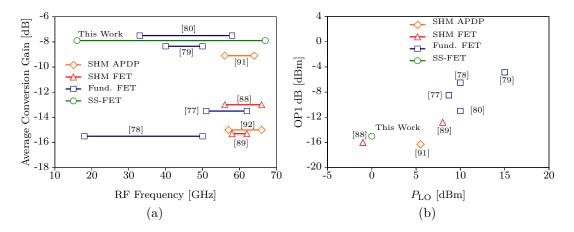

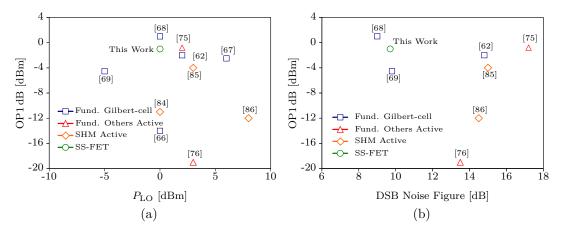

| 4.11 | Comparison of monolithic integrated wideband passive mixers by the               |    |  |

|      | average conversion losses on the RF frequency bandwidth (a) and the              |    |  |

|      | linearity performances versus the applied LO power signal (b)                    | 70 |  |

| 4.12 | Comparison of the passive proposed down-converter with monolithic inte-          |    |  |

|      | grated wideband active mixers by the average conversion gains on the RF          |    |  |

|      | frequency bandwidth.                                                             | 70 |  |

| 4.13 | Comparison of the passive proposed down-converter with monolithic inte-          |    |  |

|      | grated wideband active mixers by the linearity versus both applied LO            |    |  |

|      | power (a) and noise figure (b).                                                  | 71 |  |

| A.1  | Considered trapezoidal waveform $S(t)$ and its derivate $S'(t)$                  | 75 |  |

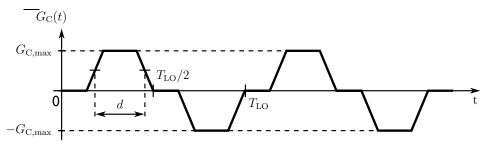

| A.2  | $G_C(t)$ signal                                                                  | 76 |  |

| A.3  | Considered triangular waveform $S(t)$ and its derivate $S'(t)$                   | 78 |  |

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up toVIII millimeter-Waves.

# List of Tables

| Ι   | First stage CML frequency divider transistrors width.                      | 14 |

|-----|----------------------------------------------------------------------------|----|

| Π   | CP transistrors width                                                      | 18 |

| III | In-Band performances comparison with other silicon-based PLL $\ . \ . \ .$ | 24 |

| IV  | Performances comparison summary with other silicon-based PLL               | 26 |

| Ι   | Performances comparison summary with other passive mixers                  | 57 |

| Ι   | Performances comparison summary with other passive mixers                  | 69 |

| II  | Performances comparison summary with other active mixers                   | 72 |

# 1

# **General Introduction**

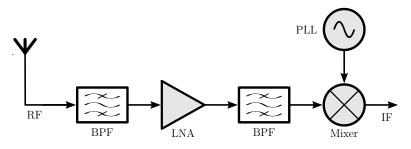

The continuous improvements of SiGe BiCMOS and Si CMOS technologies have made it possible to build low-cost radio receivers up to millimeter-wave frequencies [1]. As well known, the front-end receiver is a building block of primary importance in wireless communication systems. Its main purpose is to recover the high frequency transmitted signal and make it available for the base-band signal processing. A building block diagram of a general front-end receiver architecture is depicted in figure 1.1. The antenna picks up the high frequency signal emitted by a remote transmitter and delivers it to the front-end input. First of all this signal undergoes a low noise amplification performed by the Low Noise Amplifier (LNA). The LNA amplifies the signal amplitude to a large enough value for the following signal conditioning. As a second step, the amplified high frequency signal is pass-band filtered for sake of image frequency rejection and finally it is down-converted by the mixer to an intermediate frequency (IF).

In the case of an homodyne receiver architecture, where the intermediate frequency is the base band, the image rejection filter before the mixer is no more required. The down-conversion mixer is driven by the local oscillator tone (LO), which is generated by a frequency synthesizer, that usually comes in the form of a PLL synthesizer.

The performance of the whole radiofrequency front-end should satisfy the specifications imposed by the addressed telecom standard. Usually this is obtained by a tricky trade-off work carried out through a spreadsheet in the easiest cases or through system level simulations in the hardest ones. In this optimization procedure, the performance of each building block is traded off with the performance of the others. To put the output of the system level optimization into the real world, that is to translate the system level spec of each building block in silicon, it is of primary importance to be able to manage at the best the performance of each building block at physical level, which means to master at the best the circuit in terms of both at schematic and layout level.

In particular, the research activity reported in the present PhD thesis addressed the PLL and down-conversion mixer topics with the idea in mind of investigating the potentialities of the 130 nm silicon technology for applications in the Ku (12-18 GHz) and K (18-27 GHz) frequency band. For the lowest band a bulk pure 130nm CMOS technology by ST Microelectronics has been employed to design a PLL useful for Digital Video Broadcasting Satellite (DVB-S) applications. For the highest band a more sophisticated 130 nm SiGe BiCMOS technology by IBM has been preferred to design a high frequency sampling passive down-converter. The present PhD thesis is organized as in the follows.

Chapter 2 concerns the design of the Ku band PLL. The fabricated prototype is a meaningful breakthrough of the current state-of-the-art, because it is, at the best knowledge, the first CMOS PLL providing evidence that a pure, low-cost, bulk CMOS technology can be addressed for the fabrication of a DVBS synthesizer, where, in the literature, more expensive integrated and/or discrete technologies are employed.

Chapter 3 is devoted to the design of the down-converter. The fabricated prototype outperforms the literature, because it is the first example of high frequency sampling passive down-converter working up to K band frequencies. The chapter therefore highlight the potentialities of this circuit topology well beyond the actual low frequency operating range.

Finally, chapter 4 proofs, thanks to sub-sampling technique applied to the chip realized in the chapter 3, its operating frequency range extension up to millimeter-wave frequencies. The 60 GHz Industrial, Scientific and Medical (ISM) band has been targeted. The work presented in both chapter 3 and 4 was supported under the Région Midi-Pyrénées and French state ELECTRA 2010 funded project WIATIC.

Figure 1.1: Receiver block diagram.

# Ku-band Phase Locked Oscillator

## 2.1 Introduction

Several mass market applications, as for example, Standard and High Definition TeleVision (SDTV and HDTV), interactive multimedia, data content distribution and professional TV applications use a portion of Ku band spectrum reserved for point to point and broadcasting satellite communications. Nowadays, in satellite receivers, the signal is picked up by the dish antenna and then amplified and down-converted by a low noise front-end. This block is frequently built using discrete compound semiconductor High Electron Mobility Transistors (HEMT) and implements Dielectric Resonator Oscillators (DRO), as well. This discrete approach is expensive due to components, assembling operations, and the resonator manual tuning [2]. A silicon-based monolithic integrated receiver offers secure advantages in term of cost and size, especially using an integrated local oscillator. Nevertheless, performance limitations of integrated solutions are still restricting this kind of solutions for penetrating high frequency mass market applications such as Digital Video Broadcasting Satellite (DVB-S) [3]. Some efforts have led to several prototype as a monolithic 0.8 µm bipolar technology Low Noise Block (LNB) by STMicroelectronics [2], and more recently, a 0.25 µm SiGe:C commercially available BiCMOS technology LNB was reported by NXP Semiconductors [3]. Avoiding the use of bipolar transistors is of great interest as well, which is the aim of [4] and [5], presenting a 0.18 µm CMOS LNA/down-conversion mixer chain and a LNB, respectively. In all reported examples, the frequency synthesizer used to generate the local oscillator (LO) signal consists in a Phase Locked Loop (PLL). This kind of implementation requires a programmable frequency divider in the feedback loop. To easier demonstrate the potentiality of a technology for a given application where a local clock and/or a local frequency are required, the use of a Phase Locked Oscillator (PLO) can be then a good alternative because the frequency divider in a PLO exhibits a fixed modulus, making in this way easier the design. The present chapter reports on the design and the characterization of a Ku-band PLO realized with a bulk 130 nm CMOS technology. The operation frequency of the PLO was chosen so that to test its potentiality for both up-link

$(12.9 \div 18.4 \,\mathrm{GHz})$  and down-link  $(10.7 \div 12.75 \,\mathrm{GHz})$  frequency band. Particular attention has been done on phase noise which is the hardest specification to be satisfied. This because the modulations schemes (APSK) adopted in DVB-S standard exhibits a round constellation where excessive rotational errors due to excessive phase noise would produce a burst of error [6]. The PLO can be also used as local oscillator in the architecture of a microwave radiometric front-ends [7]. Several applications in the microwave radiometry field, such as industrial harsh plants, where conventional sensor can not be employed, or automotive safety, require cost and size reductions of the radiometer. For example, in order to keep low the cost, the emitted black-body radiation is usually detected with a low cost printed antenna array [7, 8], which size depends on the operation frequency. Therefore, a PLO working at higher frequency allows a reduction of the antenna size. For a  $8 \times 8$  array patch-antenna with a gain of 25 dB, when the operation frequency moves from X-band to Ku-band, as in the present case, the antenna area shrinks of 2.5 times, from  $10 \times 10$  inch<sup>2</sup> to  $6.3 \times 6.3$  inch<sup>2</sup> [9]. Microwave radiometry is considered also an interesting solution for wild fire detection. In order to minimize the maintenance cost of the batteries, the microwave radiometer collocated in each node of the smart sensor network distributed on the wild area should be energy independent as much as possible, exploiting renewable energy sources, as integrated microphotovoltaic cells or harvesting circuits [10]. Therefore, dissipated power reduction is a further parameter of paramount importance. Using, as in this case, low power technology allows to solve this constraint, making easier to target the energy independence of each node of the smart sensor network. When bias voltage moves from a 3.3 V of a 0.35 µm technology to a 1.2 V of a 130 nm technology, a significant reduction of the dissipated power has to be expected. Therefore, the use of a higher operation frequency and more scaled technology with respect to those reported in [7] allows to address the above discussed advantages of reduction in size and dissipated power. This chapter is organized as follows. After a brief theoretical recall of PLL linear model in 2.2, the PLO architecture and the design of each building block are described in Section 2.3. Simulations resuls and experimental results are summarized in Section 2.4 and Section 2.5 followed by some considerations. Finally conclusions are drawn in Section 2.6.

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 4 millimeter-Waves.

## 2.2 Theoretical recalls

#### 2.2.1 Phase locked loop linear model

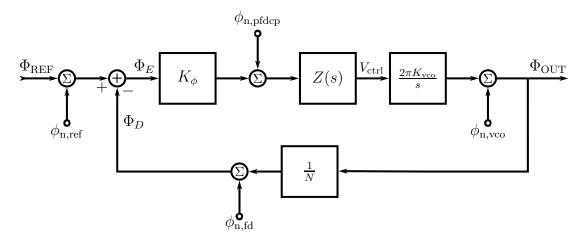

Figure 2.1: PLL linar phase-domain model.

For good loop estimation performances, whole PLL system can be described using a linearized model. For modeling the behavior of the PLL to small perturbations when the PLL is in lock condition, the PLL linear phase-domain model depicted in figure 2.1 can been used as indicated in [11].

As known, the voltage controlled oscillator converts its input voltage to an output signal with a known frequency  $f_{OUT}(t) = K_{VCO} \cdot v_{ctrl}(t)$  where  $K_{VCO}$  is the VCO gain in V · Hz<sup>-1</sup>. Integrating and applying the Laplace transform at this expression, VCO phase-domain characteristic needed in a phase-domain model is obtained

$$\Phi_{OUT}(s) = \mathcal{L}\left\{2\pi \cdot \int K_{VCO} v_{ctrl}(t) \, dt\right\} = \frac{2\pi K_{VCO}}{s} V_{ctrl}(s) \tag{2.1}$$

Given a signal  $v_i(T)$ , a frequency divider will produce an output signal  $v_o(NT)$  where N is the divide ratio. Therefore, the phase transfer characteristic of a divider is

$$\Phi_o = \frac{\Phi_i}{N} \tag{2.2}$$

Divided signal is compared with the reference by the phase frequency detector. The phase difference  $\Phi_E$  is converted in a current signal by the charge pump. The output of the charge pump immediately passes through a low pass filter with Z(s) transfer function that it carry out both current-voltage conversion and high frequencies signal suppression.

<sup>5</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

So, the pulse nature of charge pump output can be ignored and hence the average charge pump current will be take into account [11]. Thus, the transfer characteristic of the combined PFD-CP become

$$\langle i_{\rm cp} \rangle = I_{\rm CP_{max}} \frac{\Phi_{\rm REF} - \Phi_D}{2\pi} = K_\phi \cdot (\Phi_{\rm REF} - \Phi_D)$$

(2.3)

where  $K_{\phi} = I_{\rm CP}/2\pi$  is the PFD-CP characteristic gain.

For PLL noise phenomena study, single noise sources of the PLL components as integrated in the model. Generally, there can be identified two principal noise transfer functions. The noise sources that can be referred back to the input such as PFD-CP, frequency divider, loop filter and reference signal (generically indicated by  $\phi_{n,in}$ ) undergo a low-pass function  $F_{ref}$  whereas the VCO contribution that is referred to the output undergoes a high pass function  $F_{vco}$  [12].

$$F_{\rm ref} = \frac{\Phi_{\rm out}}{\phi_{\rm n,in}} = \frac{\frac{K_{\phi}Z(s)2\pi K_{\rm vco}}{s}}{1 + \frac{K_{\phi}Z(s)2\pi K_{\rm vco}}{Ns}}$$

(2.4)

$$F_{\rm vco} = \frac{\Phi_{\rm out}}{\phi_{\rm n,vco}} = \frac{1}{1 + \frac{K_{\phi}Z(s)2\pi K_{\rm vco}}{Ns}}$$

(2.5)

Defining the open loop gain  $G_{OL}$  as

$$G_{\rm OL}\left(s\right) = \frac{\Phi_I}{\Phi_E} = \frac{K_{\phi} Z\left(s\right)}{N} \frac{2\pi K_{\rm vco}}{s}$$

(2.6)

equations (2.4) and (2.5) become

$$F_{\rm ref} = \frac{NG_{\rm OL}(s)}{1 + G_{\rm OL}(s)} \tag{2.7}$$

$$F_{\rm vco} = \frac{1}{1 + G_{\rm OL}(s)} \tag{2.8}$$

If  $s \to \infty$  ( $\omega \to \infty$ ) because of the VCO's pole the open loop gain  $G_{\rm OL} \to 0$  hence  $F_{\rm vco}$  and  $F_{\rm ref}$  tend to 1 and 0 respectively. Therefore, at higher frequency the noise of the PLL is that of the VCO as expected because the low-pass filter blocks any feedback at high frequency. Instead, if  $\omega \to 0$ , ever for the VCO's pole this time  $G_{\rm OL} \to \infty$  and consequently  $F_{\rm vco} \to 0$  and  $F_{\rm ref} \to 1$ . Otherwise, at low frequency, the VCO noise is lowered by the loop gain and the PLL noise depends by the noise contributions of PFD-CP, frequency divider, loop filter and reference signal. In latter case, further considerations on the VCO noise can be done. Knowing that VCO power spectral density  $S_{\phi_{\rm vco}}$  neglecting

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 6 millimeter-Waves.

flicker noise is directly proportional to  $1/\omega^2$ , filter presence become important. Indeed, if  $Z(s) \propto 1$  (without the filter) the VCO output noise power  $F_{\rm vco}^2 S_{\phi_{\rm vco}}$  is finite and nonzero. However, choosing charge pump topology, Z(s) adding at least one pole hence the VCO output noise power goes to zero [11].

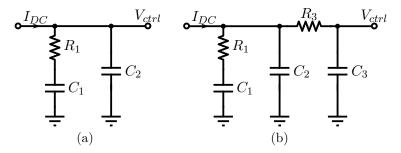

#### 2.2.2 Loop filter

Overal system order depends on the selected loop filter order. The simpler solution is a two poles  $2^{nd}$ -order filter shown in figure 2.2a to build a  $3^{rd}$ -order overall system. It is composed by capacitance-resistance series shunted with a second capacitance. The latter  $C_2$  is recommended to avoid discrete voltage step in the VCO's control voltage node due to instantaneous sudden charge pump output variations, answerable for references spurs. If a stronger spurs suppression is required, another pole should be added using  $3^{rd}$ -order filter shown in figure 2.2b, for a  $4^{th}$ -order overall system. Taking into account the simpler case, the filter transfer function becomes:

$$Z(s) = \left(R_1 + \frac{1}{sC_1}\right) / \frac{1}{sC_2} = \frac{1}{sC_2} \cdot \frac{T_p}{T_z} \cdot \frac{1 + sT_z}{1 + sT_p}$$

(2.9)

where  $T_z = R_1 C_1$  and  $T_p = R_1 C_1 C_2 / (C_1 + C_2)$  are zero and pole time constants respectively.

Substituting the Z(s) expression 2.9 in 2.6 results that

$$G_{\rm OL}\left(s\right) = \frac{K_{\phi} 2\pi K_{\rm VCO}}{sN} \cdot \frac{1}{sC_2} \cdot \frac{T_p}{T_z} \cdot \frac{1+sT_z}{1+sT_p}$$

(2.10)

Figure 2.2: Schematic of  $2^{nd}$  (a) and  $3^{nd}$ -order (b) loop filter.

Since  $s = j\omega$  open loop magnitude and phase expression is equal to:

<sup>7</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

$$|G_{\rm OL}(j\omega)| = \frac{K_{\phi} 2\pi K_{\rm VCO} T_p}{\omega^2 N C_1 T_z} \cdot \frac{\sqrt{1 + (\omega T_z)^2}}{\sqrt{1 + (\omega T_p)^2}}$$

(2.11)

$\underline{/G_{OL}}(j\omega) = 180 + \arctan(\omega T_z) - \arctan(\omega T_p)$ (2.12)

Figure 2.3: 3<sup>rd</sup>-order overall system magnitude and phase information of open loop gain.

whose trend is plotted in 2.3. The two PLL parameters of paramount importance for the design are the bandwidth  $f_{\rm BW}$  and the phase margin PM, highlighted in 2.3. The first is the frequency  $\omega_{\rm BW}$  corresponding to  $|G_{\rm OL}(j\omega)| = 0$  dB while the second is evaluated as the difference between -180° and  $\underline{G}_{\rm OL}(j\omega)$  when the frequency is equal to  $\omega_{\rm BW}$ . In order to ensure stability, the phase margin must be chosen between 30° and 70°: trade off between higher stability and slower loop response time should be considered. Nonetheless it should be no less than 45° and also to reduce peaking in closed-loop gain which produce excess phase noise, the phase margin is typically 60° or more [11].

To find the frequency point for which the phase reaches the maximum (2.12) is derived and forced to 0 to obtain a bandwidth relationship depending on pole and zero value:

$$f_{\rm BW} = \frac{1}{\left(2\pi\sqrt{T_z T_p}\right)} \tag{2.13}$$

In the same wave, putting  $\omega = \omega_{BW} = 2\pi f_{BW}$  in (2.12), equation (2.14) is obtained

$$\tan\left(PM\right) = \frac{\omega_{\rm BW}T_z - \omega_{\rm BW}T_p}{2} \tag{2.14}$$

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 8 millimeter-Waves.

Using equations (2.13) and (2.14) after some mathematical steps reported in [13],  $T_z$ and  $T_p$  expression results become

$$T_p = \frac{\sec\left(PM\right) - \tan\left(PM\right)}{\omega_{\rm BW}} \tag{2.15}$$

$$T_z = \frac{1}{\omega_{\rm BW}^2 T_P} \tag{2.16}$$

Therefore, for both bandwidth and phase margin given and knowing whole block parameters such as  $K_{VCO}$ ,  $K_{\phi}$  and N, the LF components value are obtained using equations (2.17), (2.18) and (2.19)

$$C_1 = C_2 \left(\frac{T_z}{T_p} - 1\right) \tag{2.17}$$

$$C_{2} = \frac{K_{\phi} 2\pi K_{\rm VCO}}{\omega_{\rm BW}^{2} N} \cdot \frac{T_{p}}{T_{z}} \cdot \frac{\sqrt{1 + (\omega_{\rm BW} T_{z})^{2}}}{\sqrt{1 + (\omega_{\rm BW} T_{p})^{2}}}$$

(2.18)

$$R_1 = \frac{T_z}{C_1} \tag{2.19}$$

If a  $3^{rd}$ -order filter is used, the attenuation introduced by the third poles is  $\alpha_{dB} = 20 \log \left[ (2\pi f_{REF} T_{P_3})^2 + 1 \right]$  where  $T_{P_3}$  is the time constant. For good dimensioning, this additional pole must be lower than the reference frequency in order to significantly attenuate the spurs but must be at least five time higher than the loop bandwidth otherwise the loop will almost assuredly become unstable. Recalculating the loop filter component with  $T_{P_3}$  contribution,  $C_1$  and  $R_1$  remain unchanged and  $C_2$  become:

$$C_{2} = \frac{K_{\phi}K_{\rm VCO}}{(\omega_{\rm BC})^{2}N} \cdot \frac{T_{p}}{T_{z}} \cdot \frac{\sqrt{\left[1 + (\omega_{\rm BC}T_{z})^{2}\right]}}{\sqrt{\left[1 + (\omega_{\rm BC}T_{p})^{2}\right]\left[1 + (\omega_{\rm BC}T_{P_{3}})^{2}\right]}}$$

(2.20)

where  $f_{BC}$  is the new open loop unity gain frequency reported in [14]. As regards  $C_3$  and  $R_3$ , they are normally arbitrarily chosen. General thumb rule is taking  $C_3$  ten times smaller than  $C_2$  to avoid  $T_{P_3}$  interaction with primary poles and  $R_3$  must be chosen twice  $R_1$ .

<sup>9</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

## 2.3 Circuit design

## 2.3.1 General architecture

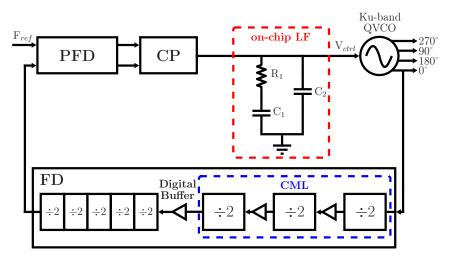

Figure 2.4 depicts the building block diagram of the designed PLO. It is constituted by a Phase Frequency Detector (PFD), a Charge Pump (CP), a second order Loop Filter (LF), a fixed modulus Frequency Divider (FD), and a Quadrature Voltage Controlled Oscillator (QVCO). The frequency division ratio (256) of the frequency divider is set for enabling the generation of Ku-band tone from an external reference frequency  $f_{ref}$  of about 60 MHz. The frequency divider is implemented from eight division-by-two stages. The first three stages are designed using a Current Mode Logic (CML) to achieve high operation frequency. Each CML stage is buffered in order to be able to drive the following divider stage. The division chain is completed with five low power digital frequency dividers realized with transmission gate registers. Because of the QVCO implementation, four output phases are available at PLO outputs. Finally, it is worth noticing that the loop filter is integrated on die for low cost considerations.

Figure 2.4: Phase Locked Oscillator Blocks Diagram.

## 2.3.2 Employed technology

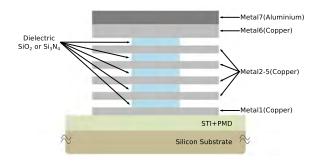

The circuit is designed to fit with the commercial HCMOS9GP technology from STMicroelectronics. It is a triple well bulk CMOS technology with multiple voltage threshold transistors, for low leakage or high speed purposes, featuring an effective gate length of 130 nm. As shown in figure 2.5, the back-end features six copper layers with low-k inter-level dielectric and one aluminium layer on top, as reported in [15], [16], [17]. The

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 10 millimeter-Waves.

bias supply is typically 1.2 V even if the 2.5 V option is also available [16]. For the present design, low leakage, low threshold voltage transistors have been used with a supply voltage of 1.2 V. Several kinds of resistors are also available, as diffusion, salicied or unsalicied poly, and high resistivity poly resistors [18]. MIM capacitors, spiral inductors, and varactors are also available.

Figure 2.5: 130 nm CMOS STM technology (HCMOS9GP).

### 2.3.3 Quadrature voltage controlled oscillator

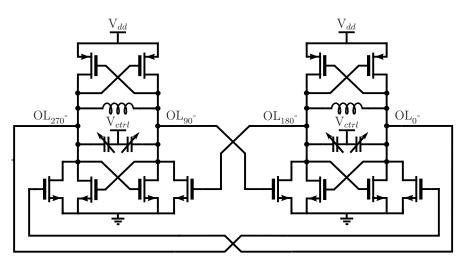

Figure 2.6: Schematic of the Quadrature VCO.

For generating signals in quadrature, the main techniques usually used are poly-phase filters, ring oscillators or frequency dividers. Nevertheless, for the present work targeted application, a solution from two cross-connected symmetric LC VCOs has been preferred because of the LC-oscillators good phase noise performances.

The schematic of the QVCO used in the present design is depicted in figure 2.6 and was previously reported in [19]. Here some features and performances are quickly

<sup>11</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

reminded; more details are available in [19]. The circuit is biased without current mirror to minimize the phase noise, the power consumption, and also to avoid any automatic control circuit. All transistors exhibit the minimum gate length. The width of the PMOS transistors is wide enough to ensure robustness against fabrication tolerances. The octagonal inductor at 15 GHz in the tank exhibits an inductance of about 290 pH and a maximum quality factor of 27. The tuning capability is achieved using two 20 fingers MOS varactors with a minimum gate length of 350 nm. For a carrier frequency  $(f_{carrier})$  of 15 GHz, the dissipated power  $(P_{DC})$  is 11 mW and the measured phase noise  $L(\Delta f)$  is -106 dBc/Hz at a carrier frequency offset  $(\Delta f)$  of 1 MHz.

#### 2.3.4 Frequency divider

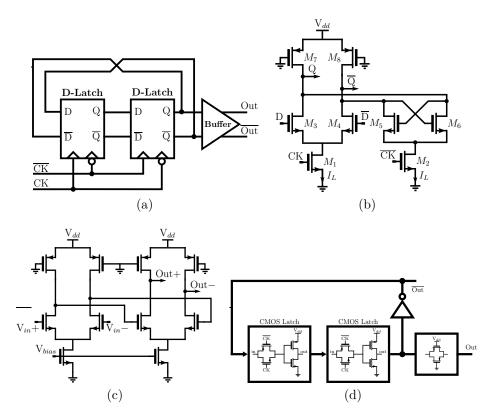

Figure 2.7: Schematic of: (a) Master-Slave divide-by-two frequency divider, (b) CML latch, (c) CML buffer, (d) Digital divider

As previously stated, the frequency divider is composed of eight division stages. Because it operates at high frequencies, each of the first three division-by-two stages is implemented from the CML latch depicted in figure 2.7b. The frequency division is

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 12 millimeter-Waves.

carried out by two latches arranged in a master-slave configuration and closed in feedback, as depicted in figure 2.7a.

The output buffer required for the driving of the following division stage, whose schematic is shown in Figure 2.7c, is designed from CML structures [20], as well. It is worth noticing here that the use of CML structures is well suited since their differential intrinsic topology contributes to reject the common mode noise injected from the supply and the substrate. Once related with PLO performances, this rejection translates into lower jitter and therefore into lower phase noise [21]. In the present work the CML latch, and of course the resulting frequency division CML chain, is inductor-less, using PMOS transistors as loads to minimize the layout area of circuits. Because of the low voltage bias, the traditional tail current bias is removed [22]. The inductor-less solution sounds reasonable, since it can provide a 130 nm CMOS static frequency divider operating up to 45 GHz frequency. Inductors become mandatory when a 130 n meter CMOS frequency divider should target millimeter wave frequencies [23].

Main feature of frequency divider design is the latch transistors sizing, especially for high frequency application. For this reason, several guideline have been followed. As reported in [24], using unstable circuits is necessary for efficient frequency divider design. Therefore, the following necessary and sufficient condition for instability (2.21) must be satisfied

$$g_{m5,6} \cdot R_{out} > 1$$

(2.21)

where  $R_{out}$  is the output latch charge load and  $g_{m5,6}$  is the small signal transconductance of cross-coupled transistors. Circuits that do not satisfy this condition may still function but a larger input clock amplitude is required [24]. Coarse maximum operation frequency  $f_{max}$  could be estimated using the following equation:

$$f_{max} < \frac{1}{2\ln(2)C_{out}R_{out}} \approx \frac{\sqrt{\mu_n C_{ox} \left(\frac{W}{L}\right)_{5,6}}I_L}{2\ln(2)C_{out}}$$

(2.22)

where  $(W/L)_{5,6}$  is the cross-coupled latch section transistor size of  $M_{5,6}$ ,  $I_L$  is the latch current, and  $C_{out}$  the whole capacitance viewed at the output [23]  $(C_{out} \approx C_{gs}^{M_{3,4}} + C_{gs}^{M_{5,6}})$ neglecting  $C_{db}$ . To increase maximum operating frequency both the following solutions are possible:

- 1. increase  $I_L$  by increasing the transistors size. This would mean increase the capacitance  $C_{out}$  and the power dissipation making unattractive this solution.

- 13 CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

2. reducing  $C_{out}$ ; Since drive transistor  $M_{3,4}$  should be large enough to quickly switch the latch output state between the available output swing,  $C_{gs}^{M_{3,4}}$  cannot be much reduced. Therefore, the only way is to decrease  $C_{gs}^{M_{5,6}}$  by decreasing the  $M_{5,6}$ transistors size. This solution involves a transconductance loss directly proportional to  $\sqrt{W_{5,6}}$  which will be compensate increasing  $R_{out}$ . Because of this, too small  $W_{5,6}$  value must be avoided to keep satified equation (2.21)

For leading the next stage, higher output voltage swing  $V_{OS}$  is preferred to minimize  $M_{3,4}$  transistors size. Logic high and low output voltage levels are  $V_{dd}$  and  $V_{dd} - R_{out}I_L$  respectively. Therefore, the output voltage swing equation becomes:

$$V_{OS} = R_{out} \cdot I_L = \frac{I_L}{\sqrt{\mu_n C_{ox} \left(\frac{W}{L}\right)_{7,8} \left(V_{GS} - V_{TH}\right)}}$$

(2.23)

$V_{OS}$  is inversely proportionals to  $\sqrt{W_{7,8}}$ , hence for high output voltage swing  $M_{7,8}$  small transistors sizes are better. The trade-off between instability condition and  $f_{max}$  as indicated in (2.22) should be take into account for the  $R_{out}$ . Finally input transistors  $M_{1,2}$  should be large enough to minimize the voltage drop across the transistor keeping the parasitic capacitances as small as possible [22]. For the most critical first CML stage, the used transistor sizes are reported in Table I.

| Transistors      | Width [µm] |

|------------------|------------|

| $M_{1,2}$        | 10         |

| M <sub>3,4</sub> | 6          |

| $M_{5,6}$        | 1.4        |

| M <sub>7,8</sub> | 10         |

Table I: First stage CML frequency divider transistrors width.

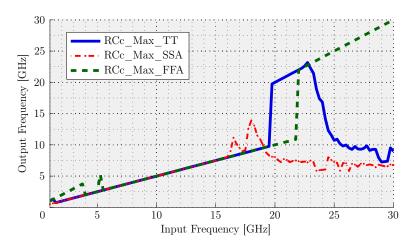

Another paramount design features are good extraction and minimization of parasitics at the interface between the VCO and the frequency divider. Unpredicted and/or too large parasitics can translate into a frequency mismatch between the tuning range of the VCO and the sensitivity range of the frequency divider, making impossible the lock of the PLO. Therefore, a compact and carefully laid out layout of the frequency divider front-end allows the optimization of this interface by minimizing the parasitics. In order to assess the robustness of the circuit against technology dispersions, several post-layout simulations have been carried out under RC parasitic worst case of the VCO/divider interface and for several corner cases for transistors. Figure 2.8 plots the simulated

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 14 millimeter-Waves.

output frequency versus input frequency of the first CML divider stage. A slope of 0.5 certifies the proper operation of this divide-by-two stage. figure 2.8 shows that in the 6 GHz to 16 GHz frequency range, the CML divider stage is able to correctly work not only under the typical corner case (TT) but also under the Slow-Slow (SSA) and the Fast-Fast (FFA) corner cases, i.e. when the transistor transconductance is lower and higher than its typical value, respectively. Note that the frequency range where the circuit correctly works is larger (narrower) than the typical case when the transistors are fast (slow). The SSA case is therefore the most critical one. Similar simulations have been carried out for the other CML stages.

Figure 2.8: Output frequency versus input frequency of the first CML divide-by-two frequency divider for several corner cases under worst case parasitic extraction.

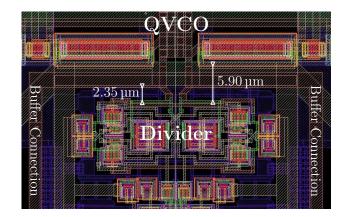

As far as the implementation of the last five division-by-two stages operating at lower frequencies, CMOS latches are used as basic cells for a dynamic solution where the transmission gates sample the input data and synchronize the transparent and opaque states as shown in figure 2.7d. As pointed out in figure 2.4, a digital buffer, simply composed by a cascade of two inverters, connects the CML and low frequency blocks. The whole division chain exhibits a simulated power consumption of about 10.5 mW. The small size of the whole frequency divider (figure 2.9), of  $44 \times 154 \,\mu\text{m}^2$ , is mainly resulting from the inductor-less approach. Because in these conditions the connection between the QVCO output and the frequency divider can be very short (only few microns as pointed out in figure 2.9), RLC parasitic components of the connection are minimized ensuring a good frequency matching of these blocks.

15 CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

Figure 2.9: Detailed layout of the interface between the QVCO and the frequency divider.

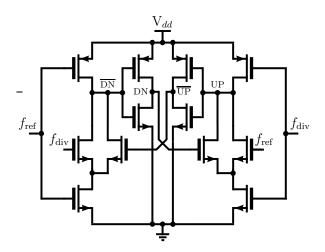

Figure 2.10: Schematic of the designed PFD.

#### 2.3.5 Phase frequency detector

Figure 2.10 shows the schematic of the designed Falling-Edge (FE) PFD [25]. When input signals  $f_{\text{ref}}$  and  $f_{\text{div}}$  are low, UP and DN are low and  $\overline{\text{UP}}$  and  $\overline{\text{DN}}$  are in pre-charge mode. UP and DN go high only when both input signals are high and they go down only in correspondence to  $f_{\text{div}}$  and  $f_{\text{ref}}$  falling-edge, respectively. Phase difference is equal to the width difference between UP and DN signal. When locking condition has been reached, phase difference fall to zero and output signals width are the same. For this reason charge pump current should be matched as much as possible. Thanks to the absence of a reset signal, as more traditional PFD's often require, this configuration is dead zone free as demonstrates the simulated phase characteristic for small differents phase shift shows in figure 2.11b. This property leads to a better phase noise of the PLO.

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 16 millimeter-Waves.

It is worth noticing that the True Single Phase Clock (TSPC) solution is dead zone free as well, but its implementation requires more transistors than the FE solution [25]. As it combines good phase noise and compact layout, the FE solution has been adopted in the present work. Further advantages offered by this structure are low dissipated power and high speed operation. It is worth pointing out that for getting no dead zone and a

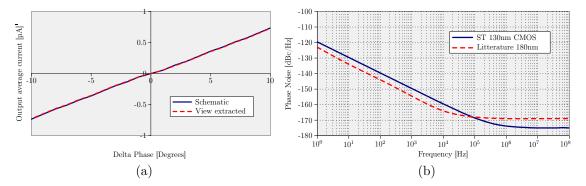

Figure 2.11: Simulated PFD phase characteristic for small differents phase shift (a) and PFD phase noise performance (b).

good linearity of the phase characteristic, the FE PFD should compare signals exhibiting the same duty cycle with a value in the range of 50 % [25], which is the case of the PLO reported in the present chapter. Under these conditions, the simulated phase noise of the designed FE PFD, figure 2.11b is about  $-173.8 \,\mathrm{dBc/Hz}$  at frequency offset of 1 MHz, outperforming the  $-168.8 \,\mathrm{dBc/Hz}$  claimed in [25]. Moreover, it has to be pointed out that the PFD schematic depicted in figure 2.10 exhibits a differential structure. This topology not only makes the PFD robust against common mode noise sources but also provides up and down signals in both true and false forms, so that a differential CP can be driven.

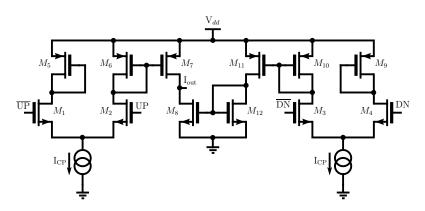

### 2.3.6 Charge pump and Loop Filter

To optimize in-band phase noise performances, CP should be carefully designed. For this, a differential topology whit single ended output is selected for the CP, which is able to improve the common mode noise rejection [21]. The schematic of the designed CP is shown in figure 2.12. As previously highlighted, used PFD need good matched charge pump currents. Nonetheless, output node mismatch between NMOS and PMOS may cause mismatch current. To keep current mismatch as small as possible and hence keep small reference spurs amplitude, following solutions have been observed. Keeping in mind the mobility difference between PMOS and NMOS,  $M_{7,8}$  are sized for transistors

<sup>17</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

Figure 2.12: Schematic of the designed CP.

transconductance matching. Furthermore,  $M_{7,8}$  output resistance  $r_{ds}$  should be as high as possible [12]. Longer devices and small charge pump current  $I_{CP}$  are therefore better.

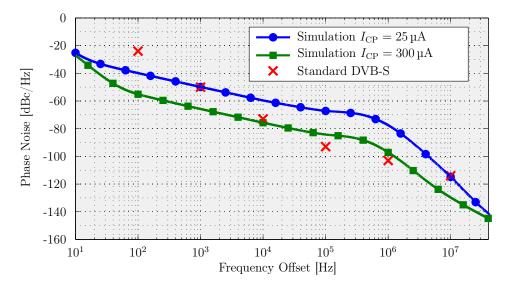

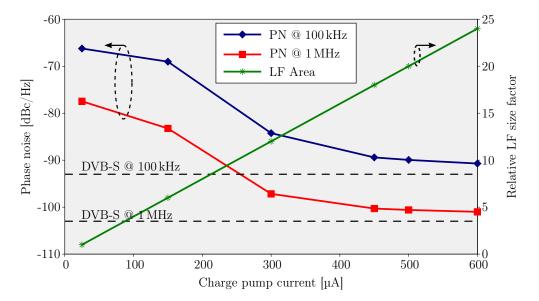

Longer channel transistors are also used in the bias current mirrors to improve the current matching, as much as possible [26]. Finally, as known, the values of capacitance and resistance implemented in the loop filter (see figure 2.4) depend on the desired open loop gain. More precisely, as indicated in section 2.2 the capacitances are directly proportional to  $K_{\varphi} \cdot K_{\text{VCO}}/(\omega_{\text{BW}})^2 \cdot N$ , where  $K_{\varphi}$  is the gain of the CP,  $\omega_{BW}$  the bandwidth of the PLO, and N is the division ratio of the frequency divider. Considering  $K_{\varphi} = I_{CP}/2\pi$ , values of the capacitances are also directly proportional to this current. Hence, the size of the loop filter is kept small by setting  $I_{CP}$  to 25 µA. Table II summarizes the transistor size of the designed CP. This low current value allows a second order loop filter to be designed on chip ( $C_1 = 44 \text{ pF}$ ,  $R_1 = 27.09 \text{ k}\Omega$  and  $C_2 = 3.39 \text{ pF}$ ). The resulting bandwidth and phase margin are 500 kHz and 60 degrees, respectively. To shrink the filter size as much as possible, polysilicon n-well capacitors are used for their higher capacitance-area ratio.

| Transistors                 | W/L                                 |

|-----------------------------|-------------------------------------|

| $M_{5-7}$ and $M_{9-11}$    | $12\mu\mathrm{m}/0.5\mu\mathrm{m}$  |

| $M_{1,2}$ and $M_{3,4}$     | $8\mu\mathrm{m}/0.13\mu\mathrm{m}$  |

| $I_{\rm CP}$ Current Mirror | $12\mu\mathrm{m}/0.6\mu\mathrm{m}$  |

| $M_{8,12}$                  | $8.3\mu\mathrm{m}/1.2\mu\mathrm{m}$ |

Table II: CP transistrors width.

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 18 millimeter-Waves.

## 2.4 Simulated performances

Because of computation time, the simulation of the locking transient of the whole PLL was possible only at schematic level, that is in post-layout simulation were addressed.

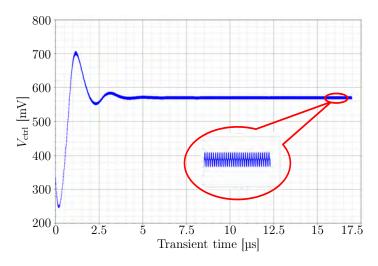

As shown in figure 2.13, the QVCO control voltage  $V_{\text{tune}}$  reaches a steady value often about 5 µs, demonstrating that the PLO feedback loop properly works. A small periodic steady variation was observed, as highlighted in figure 2.13, which is due to the input reference. RCc simulations predict a -15 dBm buffer output tone on 50  $\Omega$  load, overall

Figure 2.13: Simulated transient PLO behavior.

biased with about 86 mA. The PLO output signal picked out before buffers (charged on higher impedance) shows a great peak to peak sinusoidal amplitude of about 950 mV. To perform a phase noise analysis with Cadence<sup>®</sup>, SpectreRF must first find a steady-state solution of the DUT (device under test) with PSS (Periodic Steady State) analysis. If the circuit has a periodic solution, then is possible perform a noise simulation. Nonetheless, the time  $t_c$  required to compute the noise depends on the number of circuit equations describing the DUT ( $N_{\text{circuits}}$  equations) and on the numbers of time points needed to accurately render a single period of the solution ( $N_{\text{time}}$  point), the latter when simulate a PLL with large division ratio could be too higher making simulation impossible in practice [11].

$$t_{\rm c} \propto N_{\rm circuits\_equations} \cdot N_{\rm time\_point}$$

(2.24)

To walk around this problem, linear model based simulation tool described in [13] was used. The tool was developed using MATLAB<sup>®</sup> Graphical User Interface environment to build easier user interface and Simulink<sup>®</sup> models. The tool receives as input whole

<sup>19</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

loop characteristic (such as  $K_{\rm VCO}$ , N,  $I_{\rm CP}$ ,  $B_W$ , PM and  $f_{\rm REF}$ ) and the phase noise contributions for each building block simulated as in PLO lock condition at transistor level. Using these input the tool computes both the open and closed loop responses together with the loop design specification, the zero-pole information, and the phase noise spectra as well [13]. Each simulated buildings box phase noise contribution is reported in figure 2.14, where the noise contribution of the reference signal is also reported (sky-blue curve), as well. From these results, the PFD/CP block can be identified as the main contributor to the PLO overall phase noise. Therefore, if the CP noise contribution will be drastically reduced, the overall PLO performances may respect the stringent DVB-S phase noise standard. This topic will be addressed in the experimental performances section 2.5.

Figure 2.14: Simulated closed loop phase noise contributions.

# CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 20 millimeter-Waves.

# 2.5 Experimental performances

### 2.5.1 Measurements setup

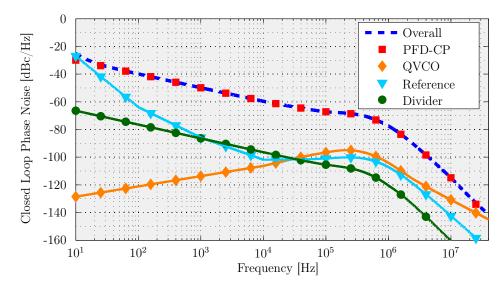

Figure 2.15a shows the microphotograph of the fabricated prototype where each building block of the PLO is highlighted. Note the buffers driving the 50  $\Omega$  load of the external instruments in the higher chip side. The GSGSG pads for the differential RF output  $(OL_{90^\circ}, OL_{270^\circ})$  are also visible on the top of the chip. To keep the circuit as symmetric as possible for the best balanced operation of the QVCO, two dummy buffers are connected on both other RF outputs. These outputs are not available over pads for experimental test simplification. Both pads on the left are implemented for the measurement of the frequency divider output signals ( $\text{Div}_Q$  et  $\text{Div}_I$ ). On the bottom, pads are visible for the reference signal and power supply. The size of the whole chip is 920 × 1010 µm<sup>2</sup>, pad enclosed but the PLO active area without buffers is about 450 × 900 µm<sup>2</sup>, which is quite compact.

Figure 2.15: (a) Die microphotograph of the fabricated PLO, (b) test board detail with filtering capacitors highlighted

For test simplification and quality purpose, the die is mounted on a PCB test board and bias pads as well as the reference low frequency pad are wire-bonded to interconnection lines. High frequency output signals are measured using coplanar micro-probes. Under these conditions, only one differential RF probe is required, and the bias can be correctly

<sup>21</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

filtered with 100 pF microcapacitors located as close as possible to the die and with several smd capacitors with higher capacitance values of 10 and 100 nF placed more distant as indicated in figure 2.15b. The bias voltage is supplied by a TTi Thurlby Thandar Instruments PL330 32V-3A Power Supply Unit. Finally, measurements are carried out inside a Faraday shielding, in order to minimize possible interferences with parasitic signals.

### 2.5.2 Results

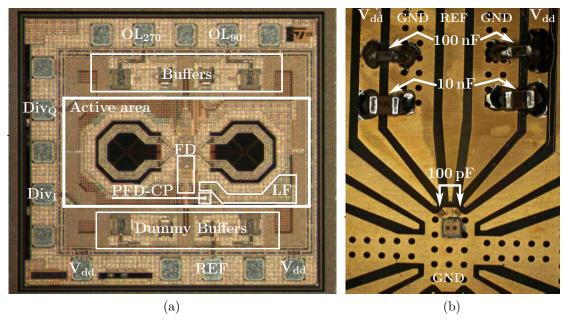

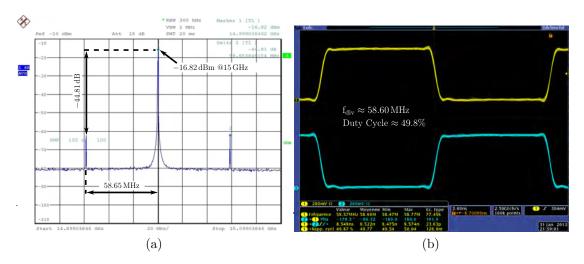

The differential output is applied to the single-ended input of the Rohde&Schwarz FSU67 Spectrum Analyzer by picking up only one signal and closing the other one on a 50  $\Omega$  load. The tuning external reference frequency is obtained from the Marconi instruments 2042 low noise signal generator (10kHz ÷ 5.4GHz). figure 3.4 shows the measured spectrum. By sweeping the external reference frequency, a range of  $f_{carrier}$  from 14.2 GHz to 15.1 GHz is observed, which matches the expected tuning range.

The PLO delivers a power of about  $-16.8 \,\mathrm{dBm}$  on a 50  $\Omega$  load, and it is biased under a current of 23.7 mA from 1.2 V supplied voltage (this bias is not taking into account buffers consumptions which simulated values have been removed from the overall bias of 92 mA). These results are not far from simulated performances reported in 2.4.

The frequency divider output was tested using Tektronix DPO4054 500 MHz 2.5 GS/s digital phosphor oscilloscope connected with  $\text{Div}_Q$  et  $\text{Div}_I$ . Using a 58.6 MHz reference frequency, square waves with about  $f_{div}$  of 58.6 MHz and 50% duty cycle have been measured as shown in figure 2.16b, proof that the frequency divider properly work. Unfortunately, quadrature information could not be obtained because of earlier phase information is lost through frequency divider chains.

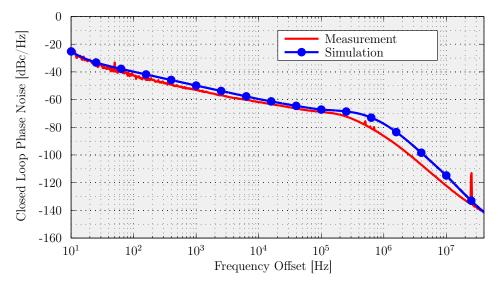

Then, the phase noise is measured using the Agilent Technology signal source analyzer E5052B (10 MHz ÷ 7 GHz) associated with the microwave downconverter E5053A (3 GHz ÷ 26.5 GHz). Figure 2.17 shows the measured phase noise (red curve) for  $f_{carrier} = 15$  GHz into a span  $\Delta f$  from 10 Hz to 40 MHz. For example, the PLO exhibits a phase noise  $L(\Delta f) = -86.3 \,\mathrm{dBc/Hz} @ \Delta f = 1 \,\mathrm{MHz}$  and  $L(\Delta f) = -122.2 \,\mathrm{dBc/Hz} @ \Delta f = 10 \,\mathrm{MHz}$ .

Figure 2.17 shows a very good agreement between measured (red curve) and simulated (dotted blue curve) phase noise, indicating that the phase noise simulation tool correctly works. It is here worth reminding that previous simulations (see section 2.4 gave evidence that the PFD and the CP are the main contributions to the phase noise of the whole PLL. Therefore, in order to discriminate between PFD and CP, the PFD phase noise performance has been investigated using the following Figure-of-Merit for PFD

CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to 22 millimeter-Waves.

Figure 2.16: Measured output spectrum (a) and  $Div_Q$  et  $Div_I$  frequency divider output (b)

Figure 2.17: Comparison between measured and simulated phase noise.

$(FOM_{PFD})$  based on Barenjee model and reported in [27]:

$$FOM_{PFD}(dBc/Hz) = L(\Delta f) - 20\log_{10} N - 10\log_{10} f_s$$

(2.25)

where N is the division ratio of the frequency divider and  $f_s$  the external reference frequency. The computed  $FOM_{PFD}$  are listed in Table III. The  $FOM_{PFD}$  exhibited in the present work is only slightly higher than those claimed in the literature. This result suggests that the PFD is not the circuit to be deeply improved.

Therefore, using  $FOM_{PFD}$ , allows to find the circuit part that must to be enhanced, as

<sup>23</sup> CMOS and BiCMOS Buildings blocks for a microwave efficient frequency conversion, up to millimeter-Waves.

|           | Process       | $f_s [{ m MHz}]$ | N    | Phase Noise<br>[dBc/Hz] | $FOM_{PFD}$<br>[dBc/Hz <sup>2</sup> ] |

|-----------|---------------|------------------|------|-------------------------|---------------------------------------|

| This Work | CMOS 130nm    | 58.6             | 256  | -68.9@100kHz            | -194.7                                |

| [28]      | CMOS 130nm    | 1118.75          | 34   | -85@100kHz              | -205.9                                |

| [29]      | CMOS 130nm    | 78               | 257  | -77@100kHz              | -204.1                                |

| [30]      | CMOS 130nm    | 600              | 32   | -85.6@100kHz            | -203.5                                |

| [31]      | CMOS 130nm    | 45.1             | 1024 | -63@100kHz              | -199.8                                |

| [32]      | CMOS 65nm     | 18               | 1160 | -55@50kHz               | -188.8                                |