# **THÈSE**

En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

### Délivré par :

Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

# Présentée et soutenue par : Giancarlo VINCENZI

le lundi 13 janvier 2014

Titre:

Graphene: FET and Metal Contact Modeling Graphène : modélisation du FET et du contact métallique

### École doctorale et discipline ou spécialité :

ED GEET : Électromagnétisme et Systèmes Haute Fréquence

### Unité de recherche :

Laboratoire d'Analyse et Architecture de Systèmes

### Directeur(s) de Thèse:

Patrick PONS, Fabio COCCETTI

#### Jury:

Thierry PARRA, Président du Jury

Marco FARINA, Rapporteur

George KONSTANTINIDIS, Rapporteur

Patrick PONS, Directeur de Thèse

Fabio COCCETTI, Co-directeur de Thèse

Charlotte TRIPON-CANSELIET, Examinateur

Luca PIERANTONI, Invité

George DELIGEORGIS, Invité

### Abstract

### Doctor of Philosophy

Graphene: FET and metal contact modeling

by Giancarlo Vincenzi

Nine years have passed since the discovery of graphene, all of them dense of research works and publications that, piece by piece, shed more light on the properties of this extraordinary material. With more understanding of its best qualities, a more precise prospect of the applications that would better profit from its use has been defined. High Frequency devices, like mixers and power amplifiers, and Flexible and Transparent electronics are the most promising fields.

In those fields great attention is devoted to two subjects: the downscaling of the dimensions of the graphene transistor, in order to reduce the carriers travel time and attain increasingly larger fractions of ballistic electronic transport; and the optimization of the contact parasitics. Both are highly beneficial to the maximization of the device's RF Figures Of Merit.

In this thesis, Two models have been developed to address such topics: the first served both the quasi-ballistic large-area graphene and graphene nanoribbon transistors. It demonstrated the correlation between ballistic and diffusive electron transport and device length, and extracted the large signal DC currents and transconductances. The second reproduced the high-frequency conduction through graphene and its contact parasitics. The latter also motivated the development and fabrication of a RF test bed on a dedicated plastic technology, enabling the RF characterization of the contact impedance and of the specific interfacial impedance of monolayer CVD graphene.

## Contents

| A  | bstra            | net                                                | ii         |

|----|------------------|----------------------------------------------------|------------|

| Li | st of            | Figures                                            | v          |

| Li | $\mathbf{st}$ of | Tables                                             | vii        |

| 1  | Intr             | $\operatorname{roduction}$                         | 1          |

| •  | 1.1              | Thesis structure                                   | 3          |

| 2  | Lite             | erature Review                                     | 5          |

|    | 2.1              | Graphene Technology                                | 5          |

|    |                  | 2.1.1 Graphene Isolation and synthesis             | 5          |

|    | 2.2              | Graphene Physics                                   | 8          |

|    |                  | 2.2.1 Electronic Bandstructure                     | 8          |

|    |                  | 2.2.2 Consequences of the absence of bandgap       | 9          |

|    | 2.3              | Graphene FET models                                | 11         |

|    |                  | 2.3.1 Physical models                              | 12         |

|    |                  | 2.3.2 Empirical models                             | 14         |

|    | 2.4              | Graphene/metal contact and propagation models      | 15         |

|    |                  | 2.4.1 Physical and Chemical models of the contact  | 16         |

|    |                  | 2.4.2 DC models and measurements                   | 24         |

|    |                  | 2.4.3 RF measurements and models                   | 25         |

|    | 2.5              | Conclusions                                        | 27         |

| 3  | Gra              | phene DC model                                     | 39         |

|    | 3.1              | Motivation                                         | 39         |

|    | 3.2              | Objectives of the study                            | 40         |

|    | 3.3              | Model: Top of the Barrier                          | 40         |

|    |                  | 3.3.1 The Landauer Equation, carriers and contacts | 41         |

|    |                  | 3.3.2 Electrostatics                               | 43         |

|    |                  | 3.3.3 The channel population: closing the loop     | 44         |

|    | 3.4              | Method: Extending the model to GFETs               | 46         |

|    |                  | 3.4.1 Scattering and channel population            | 47         |

|    | 3.5              | Results                                            | 49         |

|    |                  | 3.5.1 GNRFET                                       | 49         |

|    |                  | 3.5.2 GFET                                         | 50         |

|    | 2.6              | Putung month                                       | <b>E</b> 2 |

|   | 3.7  | Conclusions                                                | 53         |  |  |  |

|---|------|------------------------------------------------------------|------------|--|--|--|

| 4 | Gra  | raphene RF model                                           |            |  |  |  |

|   | 4.1  | Motivation                                                 | 57         |  |  |  |

|   | 4.2  | Objectives of the study                                    |            |  |  |  |

|   | 4.3  | Model                                                      |            |  |  |  |

|   | 4.4  | Method                                                     |            |  |  |  |

|   |      | 4.4.1 Technology and design                                |            |  |  |  |

|   |      | 4.4.2 EM model (MoM) and schematic                         |            |  |  |  |

|   | 4.5  | Results                                                    |            |  |  |  |

|   |      | 4.5.1 Performance projection with other graphene materials |            |  |  |  |

|   | 4.6  | Chapter conclusions and future/ongoing work                |            |  |  |  |

|   |      | 3 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                    |            |  |  |  |

| 5 | Plas | stic test beds                                             | 39         |  |  |  |

|   | 5.1  | Motivation                                                 | 39         |  |  |  |

|   | 5.2  | Objectives of the study                                    | 71         |  |  |  |

|   |      | 5.2.1 Design Specifications                                | 71         |  |  |  |

|   | 5.3  | Method                                                     | 72         |  |  |  |

|   |      | 5.3.1 Technology                                           | 72         |  |  |  |

|   |      | 5.3.1.1 Fabrication of CPW on SiO2/HR Silicon              | 73         |  |  |  |

|   |      | 5.3.1.2 Fabrication of CPW on Polymeric substrates         | 73         |  |  |  |

|   |      | 5.3.2 Design                                               | 75         |  |  |  |

|   |      | 5.3.2.1 Modeling                                           | 76         |  |  |  |

|   |      | 5.3.3 Fabricated structures                                | 30         |  |  |  |

|   |      | 5.3.3.1 De-embedding                                       | 36         |  |  |  |

|   | 5.4  | Results: Graphene monolayer, CVD                           | 90         |  |  |  |

|   | 5.5  | Future work                                                | <b>)</b> 1 |  |  |  |

|   | 5.6  | Conclusions                                                | <b>)</b> 2 |  |  |  |

| 6 | Con  | aclusions                                                  | 95         |  |  |  |

|   | 6.1  |                                                            | 96         |  |  |  |

|   |      |                                                            |            |  |  |  |

# List of Figures

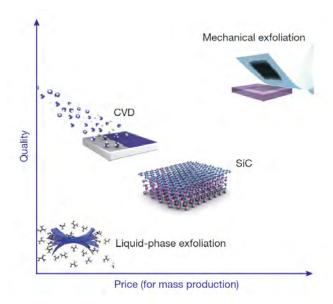

| 2.1  | Quality vs. Cost for graphene production                      | 8  |

|------|---------------------------------------------------------------|----|

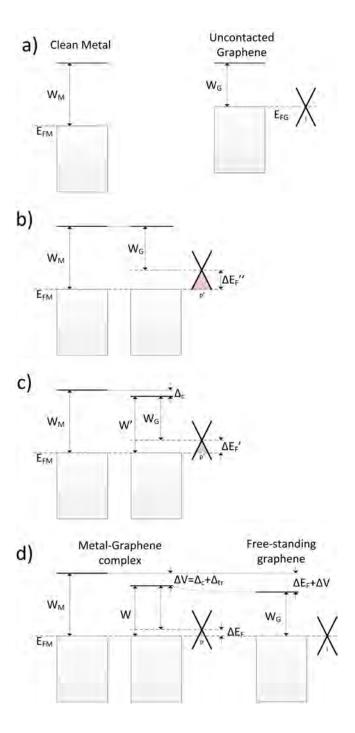

| 2.2  | Work functions of metal and Graphene in contact               | 18 |

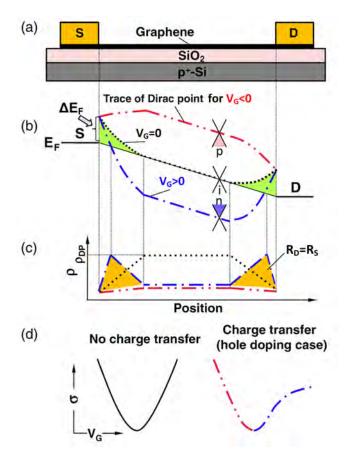

| 2.3  | Potential and resistivity along the channel of a graphene FET | 20 |

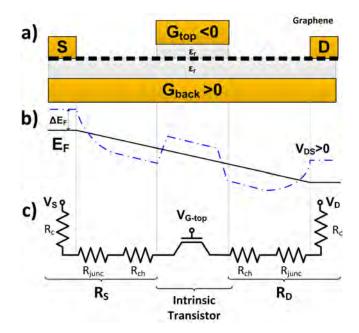

| 2.4  | Access resistance of a double-gate graphene FET               |    |

| 2.5  | TLM circuit                                                   | 24 |

|      |                                                               |    |

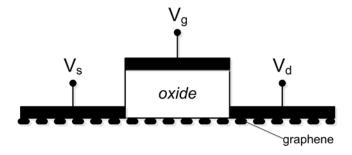

| 3.1  | Cross-section of a graphene FET                               | 41 |

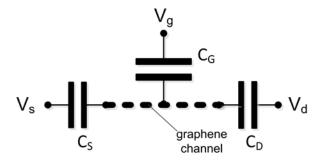

| 3.2  | Electrostatic part of the problem                             | 43 |

| 3.3  | Injection of carriers into the channel                        | 45 |

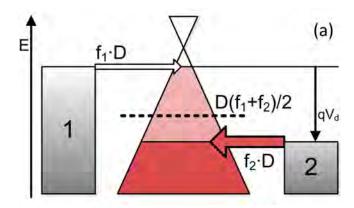

| 3.4  | Quasi-ballistic injection into a nanoscale semiconductor      | 46 |

| 3.5  | Quasi-ballistic injection in graphene                         | 48 |

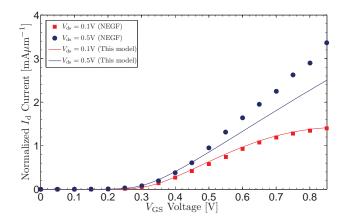

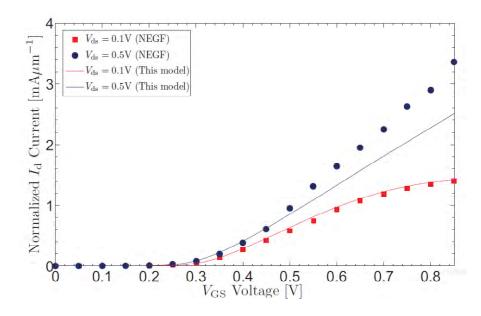

| 3.6  | $I_{d}$ - $V_{gs}$ of FET1                                    | 50 |

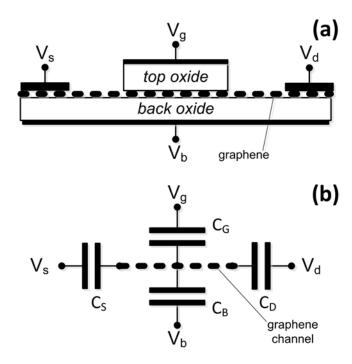

| 3.7  | Structure of FET2                                             | 51 |

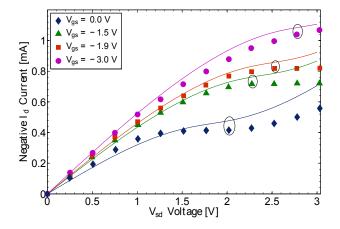

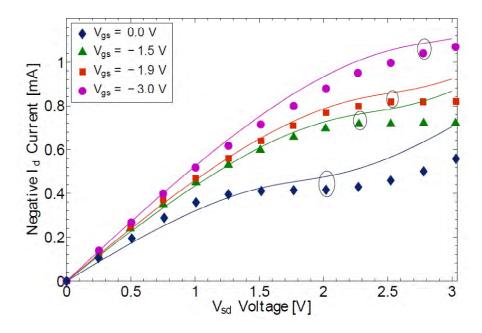

| 3.8  | $I_{ m d}\left(V_{ m sd} ight)$ of FET2                       | 51 |

|      |                                                               |    |

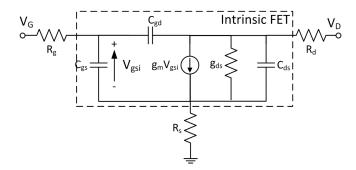

| 4.1  | Small signal circuit of a FET                                 |    |

| 4.2  | EC of the FET and its parasitics                              |    |

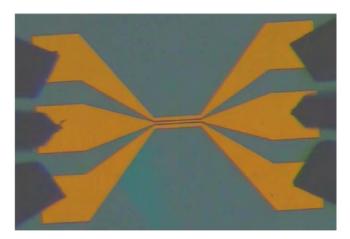

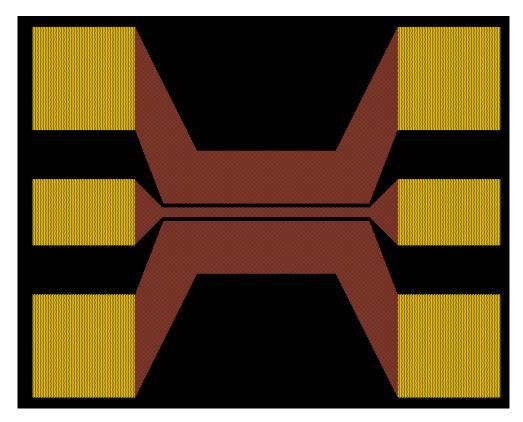

| 4.3  | Microphotograph of the CPW                                    |    |

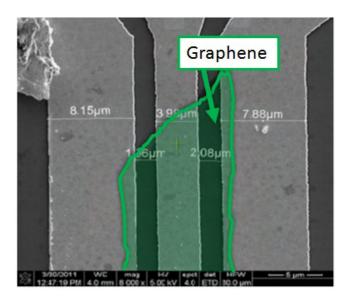

| 4.4  | SEM of the CPW                                                | 60 |

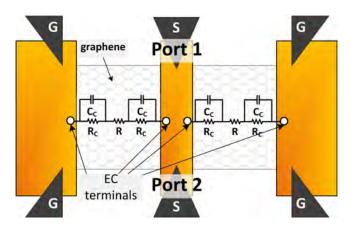

| 4.5  | CPW test bed                                                  | 62 |

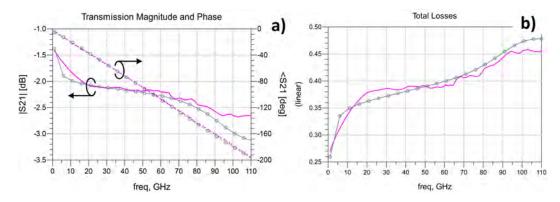

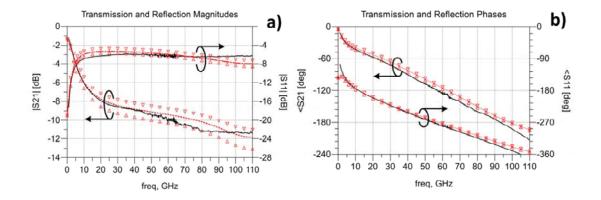

| 4.6  | Reference structure S-parameters                              | 63 |

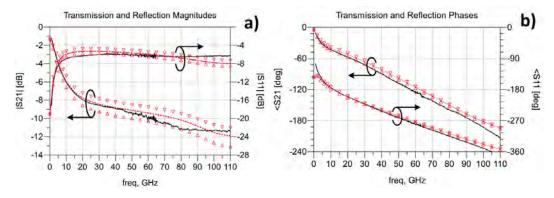

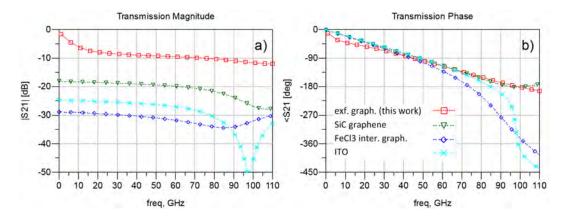

| 4.7  | Graphene-loaded structure S-parameters                        | 63 |

| 4.8  | S-parameters, prospective simulation                          | 65 |

|      |                                                               |    |

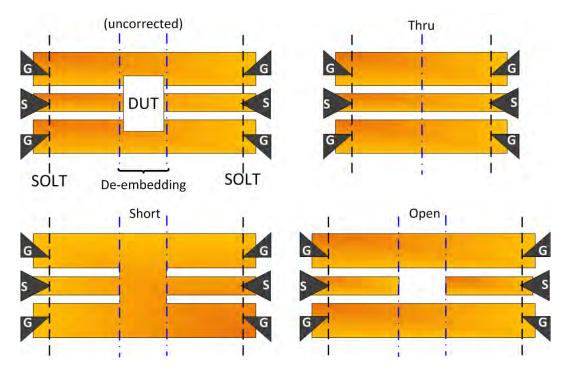

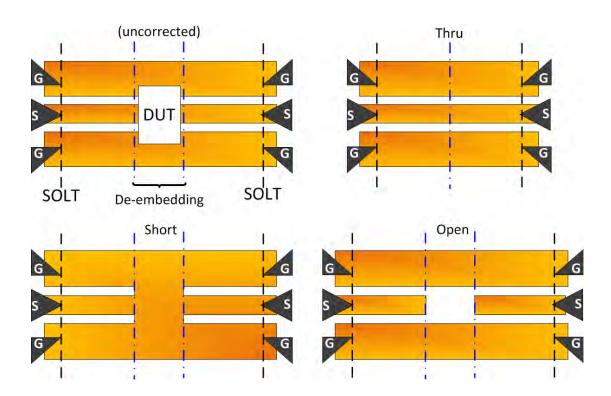

| 5.1  | De-embedding standards                                        |    |

| 5.2  | HRS MoM layout                                                |    |

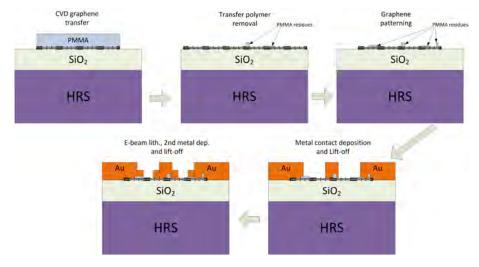

| 5.3  | Graphene on HRS, process steps                                |    |

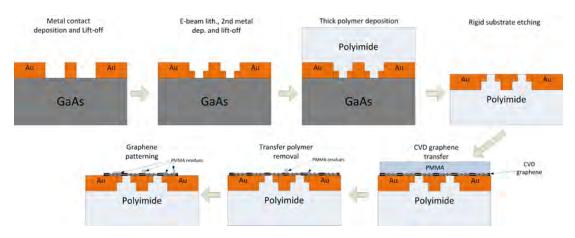

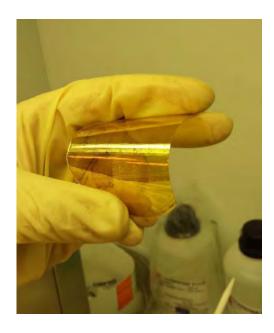

| 5.4  | Graphene on Polyimide, process steps                          |    |

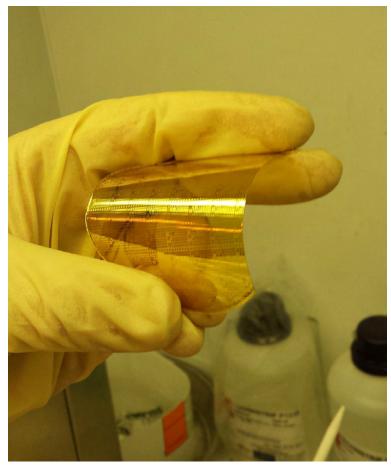

| 5.5  | Photograph of PI sample                                       |    |

| 5.6  | Layout of the full period                                     | 77 |

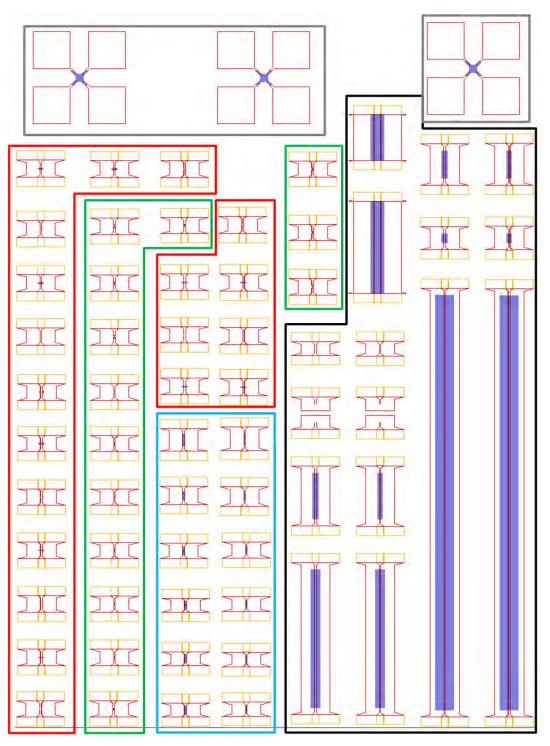

| 5.7  | Final layout                                                  | 79 |

| 5.8  | BCB MoM simulations                                           | 80 |

| 5.9  | Open-Short $ S_{21} $ difference, MoM simulations             | 81 |

| 5.10 | SU8 sample electrode separation in SEM                        | 82 |

|      |                                                               | 83 |

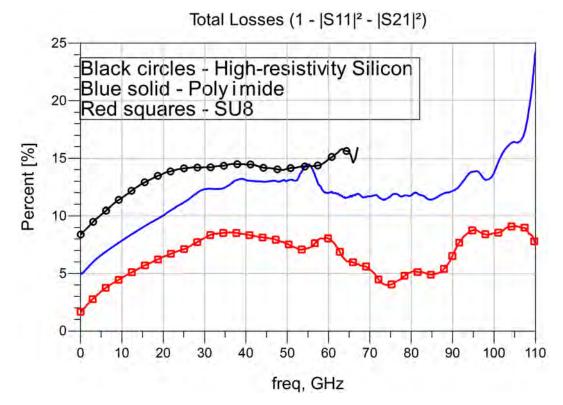

|      | Total losses for HRS, SU8 and PI compared                     | 84 |

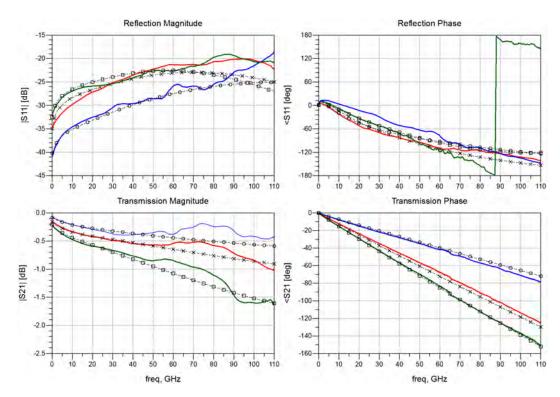

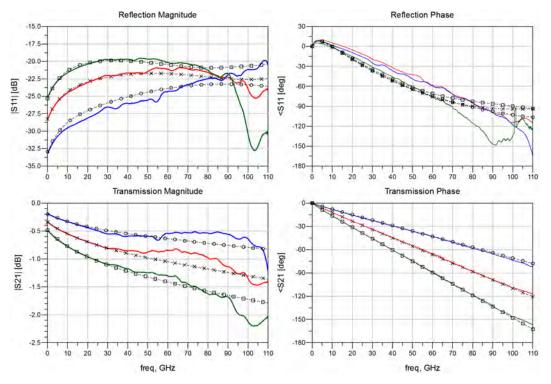

| 5.13 | SU8 sample, meas. and MoM sim. compared                       | 85 |

|      | PI sample meas and MoM sim compared                           | 85 |

### vi LIST OF FIGURES

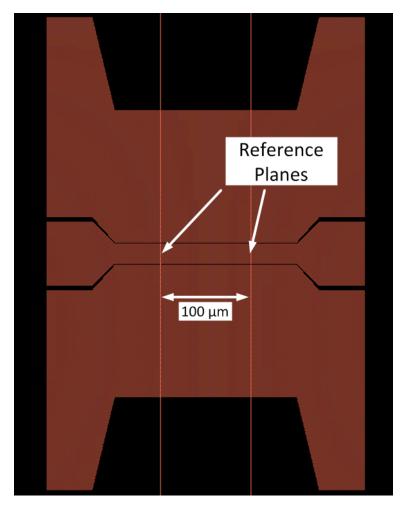

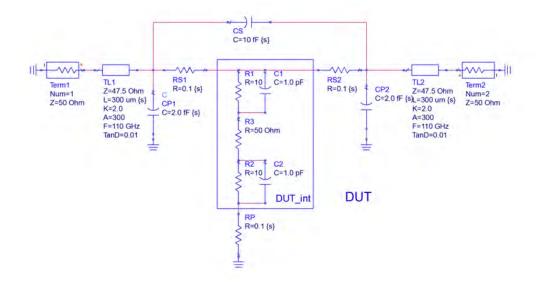

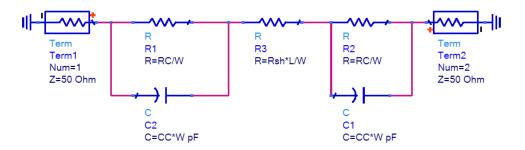

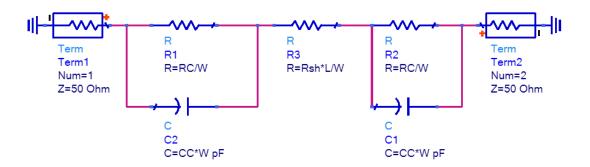

| 5.15 | Test DUT circuit                              | . 86 |

|------|-----------------------------------------------|------|

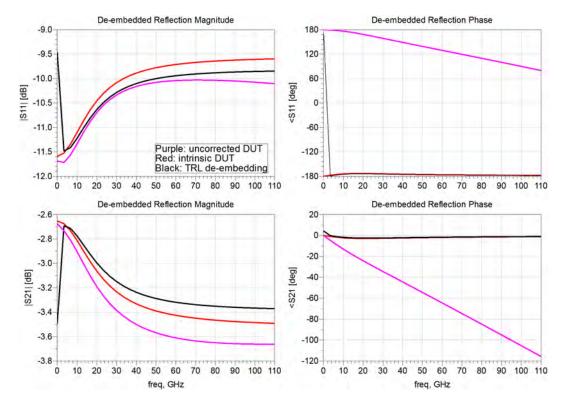

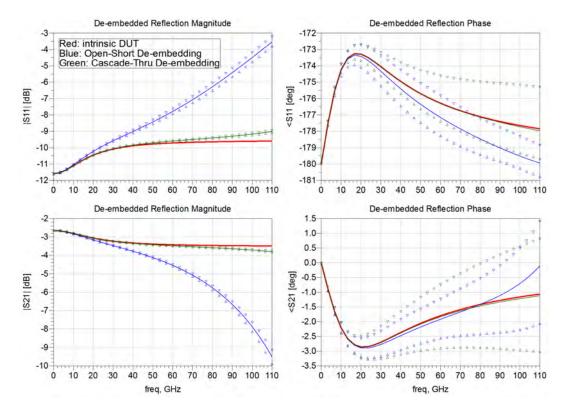

| 5.16 | TRL de-embedding                              | . 87 |

| 5.17 | Open-Short and Cascade-Thru compared          | . 89 |

| 5.18 | Equivalent circuit                            | . 91 |

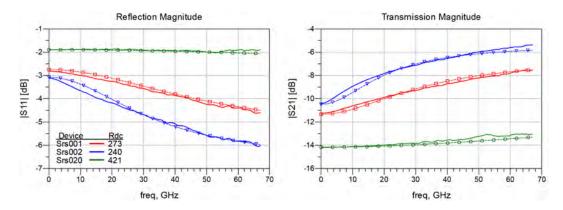

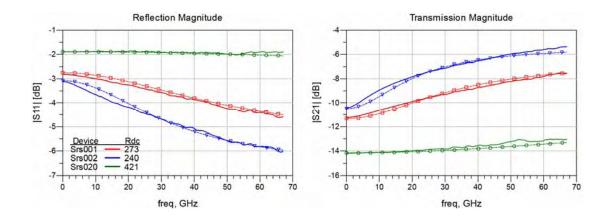

| 5.19 | Graphene devices measurements and simulations | . 91 |

# List of Tables

| 2.1 | Contact Resistance at Room Temperature                      | 16 |

|-----|-------------------------------------------------------------|----|

| 2.2 | Contact Resistance at Low Temperature                       | 16 |

| 3.1 | Structure dimensions                                        | 49 |

| 3.2 | Simulated $g_{\rm m}$ for FET1                              | 50 |

| 3.3 | Peak transconductance $g_{\rm m}$ for FET2                  | 52 |

| 3.4 | Fit parameters for FET1 and FET2                            | 52 |

| 3.5 | Model Comparison                                            | 53 |

| 4.1 | MoM simulation materials                                    | 62 |

| 4.2 | Comparison of contact resistances                           | 64 |

| 4.3 | Simulated performance comparison with alternative solutions | 65 |

| 5.1 | TRL Line standards                                          | 76 |

| 5.2 | Materials param for $Z_0$                                   | 78 |

| 5.3 | CPW line parameters                                         | 78 |

| 5.4 | Errors of de-embedding techniques                           | 89 |

| 5.5 | Open-Short and Cascade-Thru de-embedding errors compared    | 89 |

| 5.6 | Measured DC resistance values                               | 90 |

| 5.7 | Extracted contact and sheet resistances                     | 90 |

### Chapter 1

### Introduction

Graphene, in its simplest definition, is a single atomic sheet isolated out of the graphitic stack. In each one of these sheets, carbon atoms occupy the vertices of hexagons in what is sometimes called the honeycomb lattice. They form a very strong  $\sigma$  bond with the three adjacent atoms through  $sp^2$  hybridization. The remaining 2p orbital is then available to form a  $\pi$  bond with adjacent atoms. The so formed extended  $\pi$ -electron system allows for the electronic conduction in graphene and determines its electrical and optical properties [1]. Graphene is one of the many allotropes in which molecular carbon can be found and some of them are related to its very structure. Fullerenes and Carbon Nanotubes (CNT) are hollow structures where the graphene sheet is rolled on itself or around an axis (the tube axis, orthogonal to the chiral vector), while graphite is the result of stacking graphene planes in the hexagonal (AB) or rhombohedral (ABC) order. The characteristics of those allotropes thus derive directly from graphene. The strength of its  $sp^2$  bonds and its consequent chemical stability are the ground for its excellent mechanical properties: a Young's modulus of 1 TPa [2], which is more than the double of silicon carbide [3], and a breaking strength virtually 100 times larger than a steel film of the same thickness.

Electrical properties of graphene are just as good as, or even more exciting than, mechanical ones: electron mobilities beyond  $2.5 \times 10^5 \text{ cm}^{-2}\text{V}^{-1}\text{s}^{-1}$  have been found at room T, four times than state of art III-V semiconductors [4] and 200 times that of Si, thanks to the reduced electron-phonon interaction [5] when the substrate is carefully chosen [6] or eliminated by suspension technology [7]. These high values are associated with long distances between scattering events for traveling electrons: mean free paths larger than  $1 \mu m$  have been reported [6], allowing the exploration of room-temperature ballistic transport electronics with existing technological capabilities. Higher values of mobilities were obtained for graphene suspended devices at liquid helium temperatures

(more than  $1.0 \times 10^6$  cm<sup>-2</sup>V<sup>-1</sup>s<sup>-1</sup>, [8]), but not yet as good as compound semiconductors  $(35 \times 10^6$  cm<sup>-2</sup>V<sup>-1</sup>s<sup>-1</sup> has been achieved, [9]), supporting and limiting the interest in room temperature operation.

Graphene's performance in electron and thermal conduction are full of records: electron saturation velocities demonstrated experimentally and theoretically up to  $7 \times 10^7 \, cm/s$  [10],[11], much higher than both peak and high-field saturation velocities for Si and III-V semiconductors; current density as large as  $10^8 \, \text{A/cm}^2$  [12], five orders of magnitude higher than copper interconnects; in-plane thermal conductivity higher than 3,000 Wm<sup>-1</sup>K<sup>-1</sup> [13], larger than single-crystal diamond and ten times larger than copper.

Finally, optical properties of graphene are very peculiar too: an optical opacity of 2.3% over a very broad spectrum, practically wavelength-independent in the range between far-infrared and blue light [14]. Moreover, compared with other semiconductors used as saturable absorbers, graphene absorbs more photons per unit surface and unit thickness, meaning greater efficiency per volume and greater chances to saturate with high-intensity light pulses.

However, graphene's properties are such for the isolated single layer, and stacking more layers on top of each other gives mere graphite as a result, a quite different material from graphene. This means that the great majority of physical properties that depend also on the thickness of the material, such as the sheet resistance, the maximum current density, and the optical absorptivity per surface, show values that, even when comparable with established technologies, are not excellent.

Graphene has been shown to really be a unique material, with many excellent properties that cannot be found altogether in one material alone. However, the unsatisfying values of other essential properties hinder its application as a replacement for every electronic technology developed up to date: In high frequency electronics, graphene will not likely replace Si or III-V semiconductors in the short term. The domain of flexible and transparent electronics instead is quickly gaining momentum, since today's most used material, Indium-Tin Oxide, is increasingly expensive and difficult to find. Graphene, with its superior mechanical and optical properties has already attracted the attention of consumer electronics giants like Samsung and Sony [15]. Both high frequency and flexible electronics domains need an accurate study of graphene's contact parasitics. Finally, there's an entirely new domain that can be explored and that can pave the way for millimeter waves and THz electronics, and that is room-temperature ballistic electronics [16]. This thesis will scrutinize the effects of ballistic transport and the contact parasitics, respectively on field effect transistors and interconnects.

### 1.1 Thesis structure

Chapter 2 will introduce a collection of fundamental concepts about the physics of graphene. This will be used to review and understand the state of the art on graphene modeling. Two main subjects will be discussed: in the first part a survey of the modeling of graphene field effect transistors in DC will be done; in the second part, the modeling of graphene passive structures will be reviewed. The metal contact and the electronic propagation in graphene are considered as two deeply connected aspects of the same subject, and their analysis will be developed in both DC and RF.

In Chapter 3 the DC model of a graphene nanoribbon FET will be presented, along with the modifications needed to extend it to large-area graphene devices.

In Chapter 4 an RF structure, a CPW line, loaded with graphene, will be analyzed by means of an equivalent circuit for graphene and electromagnetic modeling of the line. This will allow for the extraction of the metal/graphene contact impedance.

In Chapter 5 the design of an improved RF structure with a set of deembedding standards will be shown, along with measurements, analysis of the EM data and retro-simulations results. This will provide a low-loss access fixture for the RF characterization of graphene and deembedding of data. The graphene sheet and contact impedance will be measured and analyzed in both low and high frequency.

In the Conclusions chapter the innovations to the state of art contained in this manuscript will be resumed, and possible new directions of work will be outlined.

### References

- P. Wallace, "The Band Theory of Graphite", *Physical Review*, vol. 71, no. 9, pp. 622–634,

May 1947. DOI: 10.1103/PhysRev.71.622.

- [2] C. Lee, X. Wei, J. W. Kysar, and J. Hone, "Measurement of the elastic properties and intrinsic strength of monolayer graphene.", *Science (New York, N.Y.)*, vol. 321, no. 5887, pp. 385–8, Jul. 2008. DOI: 10.1126/science.1157996.

- [3] L. Tong, M. Mehregany, and L. G. Matus, "Mechanical properties of 3C silicon carbide", Applied Physics Letters, vol. 60, no. 24, p. 2992, 1992. DOI: 10.1063/1.106786.

- [4] K. Nakayama, K. Nakatani, S. Khamseh, M. Mori, and K. Maezawa, "Step Hall Measurement of InSb Films Grown on Si(111) Substrate Using InSb Bilayer", *Japanese Journal of Applied Physics*, vol. 50, 01BF01, Jan. 2011. DOI: 10.1143/JJAP.50.01BF01.

- [5] S. Morozov, K. Novoselov, M. Katsnelson, F. Schedin, D. Elias, J. Jaszczak, and A. Geim, "Giant Intrinsic Carrier Mobilities in Graphene and Its Bilayer", *Physical Review Letters*, vol. 100, no. 1, pp. 11–14, Jan. 2008. DOI: 10.1103/PhysRevLett.100.016602.

- [6] A. S. Mayorov, R. V. Gorbachev, S. V. Morozov, L. Britnell, R. Jalil, L. a. Ponomarenko, P. Blake, K. S. Novoselov, K. Watanabe, T. Taniguchi, and a. K. Geim, "Micrometer-scale ballistic transport in encapsulated graphene at room temperature.", *Nano letters*, vol. 11, no. 6, pp. 2396–9, Jun. 2011. DOI: 10.1021/nl200758b.

- [7] K. Bolotin, K. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P. Kim, and H. Stormer, "Ultrahigh electron mobility in suspended graphene", *Solid State Communications*, vol. 146, no. 9-10, pp. 351–355, 2008.

- [8] E. V. Castro, H. Ochoa, M. I. Katsnelson, R. V. Gorbachev, D. C. Elias, K. S. Novoselov, a. K. Geim, and F. Guinea, "Limits on Charge Carrier Mobility in Suspended Graphene due to Flexural Phonons", *Physical Review Letters*, vol. 105, no. 26, p. 266 601, Dec. 2010. DOI: 10.1103/PhysRevLett.105.266601.

- [9] V. Umansky, M. Heiblum, Y. Levinson, J. Smet, J. Nübler, and M. Dolev, "MBE growth of ultra-low disorder 2DEG with mobility exceeding 35x106cm2/Vs", *Journal of Crystal Growth*, vol. 311, no. 7, pp. 1658–1661, Mar. 2009. DOI: 10.1016/j.jcrysgro.2008.09. 151.

- [10] I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. L. Shepard, "Graphene field-effect transistors based on boron nitride gate dielectrics", in 2010 International Electron Devices Meeting, IEEE, Dec. 2010, pp. 23.2.1–23.2.4. DOI: 10.1109/IEDM.2010.5703419.

- [11] D. K. Ferry, "Transport in graphene on BN and SiC", in 2012 12th IEEE International Conference on Nanotechnology (IEEE-NANO), IEEE, Aug. 2012, pp. 1–5. DOI: 10.1109/ NANO.2012.6322126.

- [12] J. Moser, A. Barreiro, and A. Bachtold, "Current-induced cleaning of graphene", Applied Physics Letters, vol. 91, no. 16, p. 163513, 2007. DOI: 10.1063/1.2789673. arXiv: 0709.0607v1.

- [13] A. a. Balandin, "Thermal properties of graphene and nanostructured carbon materials.", Nature materials, vol. 10, no. 8, pp. 569–81, Aug. 2011. DOI: 10.1038/nmat3064.

- [14] R. R. Nair, P. Blake, a. N. Grigorenko, K. S. Novoselov, T. J. Booth, T. Stauber, N. M. R. Peres, and a. K. Geim, "Fine structure constant defines visual transparency of graphene.", Science (New York, N.Y.), vol. 320, no. 5881, p. 1308, Jun. 2008. DOI: 10.1126/science. 1156965.

- [15] T. Kobayashi, M. Bando, N. Kimura, K. Shimizu, K. Kadono, N. Umezu, K. Miyahara, S. Hayazaki, S. Nagai, Y. Mizuguchi, Y. Murakami, and D. Hobara, "Production of a 100-m-long high-quality graphene transparent conductive film by roll-to-roll chemical vapor deposition and transfer process", Applied Physics Letters, vol. 102, no. 2, p. 023112, 2013. DOI: 10.1063/1.4776707.

- [16] G. Moddel, Z. Zhu, S. Grover, and S. Joshi, "Ultrahigh speed graphene diode with reversible polarity", *Solid State Communications*, vol. 152, no. 19, pp. 1842–1845, Oct. 2012. DOI: 10.1016/j.ssc.2012.06.013.

### Chapter 2

### Literature Review

In this chapter some fundamentals on graphene technology and physics will be presented. The current state of the art in graphene DC and RF modeling will be reviewed, as well as some recent studies on the graphene/metal contact. Those subjects will be elemental parts of a larger concept: a graphene universal model, from DC to RF that includes metal contact parasitics.

### 2.1 Graphene Technology

Graphene can be obtained from various sources achieving different levels of quantity and quality. Moreover, each source allows for different processes, devices and finally applications that can be targeted.

#### 2.1.1 Graphene Isolation and synthesis

The first report on the isolation of graphene was published in 2004 in a seminal paper from K. Novoselov and A. Geim [1]. Their simple but very effective method of the scotch-tape, associated with the optical identification on 285 nm SiO<sub>2</sub> substrates, gave virtually anybody access to a breakthrough research subject as graphene, without the need of important resources to acquire and process the material. Although the circumstances are now changed, for the first few years the mechanical exfoliation of graphene was the preferred method to get sparse, small but high-quality graphene flakes. The graphite source can be natural or artificial (HOPG or Kish). The flake size achievable would rarely be larger than 100  $\mu m$ , with the exception of those sold by commercial firms like Graphene Industries that can reach one millimeter in length. This is anyway a very small value compared to artificially grown graphenes, making its price very high.

Moreover, these flakes are sparsely distributed over the wafer and it's a very human-intensive operation to look for them. This prevents the fabrication of a batch of devices on the same wafer, limiting strongly the number of devices that can be fabricated within reasonable time and resources. The flake is a continuous region of one or few layers of graphene. The relatively low density of defects within the crystallites and their large size in exfoliated graphene compared to other graphene forms, like CVD graphene, are the origin of its high quality in terms of electron mobility, with mobility values typically around  $2 \times 10^4 \, cm^2 V^{-1} s^{-1}$  on SiO<sub>2</sub> substrates, while values of  $2.5 \times 10^5 \, cm^2 V^{-1} s^{-1}$  have been reached at room temperature on hexagonal-BN (h-BN) substrates [2]. Similar values have been obtained for suspended exfoliated graphene [3], eliminating all substrate interaction, but the high complexity of such a technology hinders any realistic application. Easy access and high quality made this graphene source the most preferred for lab research and small-number prototype fabrication.

Graphene from SiC decomposition is a high-quality graphene source discovered from the group of W. de Heer [4]. It is based on the thermal decomposition of SiC by Si sublimation and the segregation of C atoms on graphitic layers; in early reports is also called epitaxially grown graphene. The C segregation can happen on both the faces of the wafer: the (0001) and the  $(000\overline{1})$  one, respectively the Si-face and the C-face. Typical temperatures and pressures are 1600° and 100 mbar for Si-face and 1450° and  $1e^{-4}$  mbar for C-face, both in argon atmosphere [5]. This thermal process results in the formation of few-layer graphene on the Si-face and of a thicker graphene stack on the C-face, although in some cases high-quality graphene monolayer have been obtained on the C-face too [6]. Because of the Si desorption the surface of SiC forms narrow terraces of graphene a few micrometers wide, connected by steps with higher electrical resistance. This type of graphene allows for both batch processing and high quality samples, but has the inconvenient of the very high cost of the pristine SiC wafers and their small size compared to those normally used in electronic industry. Moreover, SiC is a very hard and difficult to process material. A bandgap around 260 meV is associated with few-layer graphene on SiC; this value appear to depend inversely on the sample thickness and should reach zero for four layers [7], suggesting some interaction from the underlying substrate. Other reports correlate the bandgap to the strain induced by the substrate [8]. Anyhow, its value is too small to allow for the complete switch-off of the transistor [9]. The electron mobility reaches  $3.0 \times 10^4 \, cm^2 V^{-1} s^{-1}$  [10], although it depends on the alignment of the direction of transport with substrate terraces [11]. SiC graphene is then a high-cost, high-performance material for batch fabrication of devices, though only for niche applications like high-frequency electronics.

Chemical Vapor Deposition (CVD) of polycrystalline graphene is based on the decomposition at 1000° of a carbon precursor (methane or ethanol) and segregation of carbon

atoms on a foil of catalyst, a transition metal with low solubility for carbon (in most cases Cu) with a very smooth surface [12]. In order to be used, graphene must be separated by the catalyst: a transfer polymer (typically PMMA) is spun on graphene to provide an alternative substrate, the catalyst is etched away and graphene can then be placed on any substrate desired; in some reports graphene is simply peeled off the metal with a PDMS polymer allowing for the reuse of the catalyst [13], but the mechanical stress of the peeling can break the graphene, especially in manual operation. Roll-toroll production has been demonstrated by Samsung in 2010 with the fabrication of a 30-inch graphene foil [14], and recently industrial-grade continuous production has been performed by Sony, yielding a 100 m long monolayer graphene foil [15], revealing evident interest from both industrial groups in developing transparent and flexible electronics. Large continuous areas of graphene can be synthesized, but unfortunately the crystallite size is rather small and the quality depends strongly on the roughness of the catalyst metal. Mobility values of 0.5 and 2  $m^2V^{-1}s^{-1}$  can be obtained respectively on SiO<sub>2</sub> and h-BN substrates. Finally, the transfer step exposing graphene to PMMA or other polymers pollutes its surface with polymer residues, affecting its electron mobility and surface charge [16]. To date this technique, although cheaper than SiC decomposition, still bares high costs because of energy consumption and the production of a smooth Cu foil to be etched off. The optimization of the process can offer a cheap way to large-scale production of graphene for photonics and displays applications.

Liquid-phase suspensions of graphene can be obtained through the exfoliation of graphite in non-aqueous solvents [17] or water-based surfactants [18]. The surface tension of these solvents favors an increase in the total area of the graphite material, making it to split in thinner platelets. Particle size is typically below 1  $\mu m$ . Another way to obtain a liquid-phase graphitic material is to oxidize graphite to obtain graphene oxide, which is easily soluble in water. It can be deposited as an ink and ultrasound sonication allows its thinning down to monolayer. However, it must be reduced by thermal treatment to obtain graphene, although a complete reduction of all oxide is hardly achievable [19]. Laser scribing allows selective reduction of graphene oxide and allows the interesting possibility to pattern Reduced Graphene Oxide (RGO) without the use of lithography [20]. Graphene and RGO solutions provide low-quality but very low cost techniques. This makes them attractive for applications like printed and flexible electronics, electromagnetic shielding and supercapacitors.

In Fig. 2.1 a comparison between cost and quality of the type of graphene is shown. In conclusion, depending on the application targeted it's possible to select the most appropriate type of graphene, choosing upon the desired cost, performance and adaptability.

FIGURE 2.1: Quality vs. Cost for graphene production. Adapted from [21].

### 2.2 Graphene Physics

The theoretical investigations on the band structure of graphene started in 1947 with the work of Wallace [22]. At the time perfectly 2D crystals were considered unstable at any physical temperature [23], and graphene was just considered as a building block for graphite. The interest on the detailed physical properties came indeed from this latter material, as it was used a few years earlier by Enrico Fermi as a neutron moderator in the first nuclear pile. A quantum model of the electronic properties of monolayer graphene was then necessary, and was later enriched by the Slonczewski-Weiss-McClure (SWM) band structure of graphite [24],[25], derived within the tight-binding description up to the second-nearest neighbor hopping term. A more detailed and updated formulation can be found in [26]. Semi-classical physics have been used as the bare minimum to understand the origin of graphene's physical properties. A full-quantum description of graphene, including Dirac fermions, spinors and Pauli matrices, although fascinating is unfortunately out of scope for this manuscript, as well as the treatment of the effects of magnetic fields. A more detailed explanation can be found in [27].

#### 2.2.1 Electronic Bandstructure

The six atoms in the hexagonal honeycomb structure can be thought as a triangular lattice with a basis of two atoms per unit cell, residing respectively in the two equivalent lattice sites A and B. The two lattice vectors are  $\mathbf{A_0} = (a/2)(3, sqrt3)$  and  $\mathbf{B_0} = (a/2)(3, -sqrt3)$ , where  $a \approx 0.142$  nm is the carbon-carbon distance. In

momentum space the first Brillouin zone is delimited by the two inequivalent points  $K = (2\pi/3a, 2\pi/(3sqrt3a))$  and  $K' = (2\pi/3a, -2\pi/(3sqrt3a))$ . These corners are called Dirac points and the physics of electron and hole carriers in the close vicinity of those points is of particular importance. The electronic band dispersion obtained for the conduction  $(\pi^*)$  and the valence  $(\pi)$  bands, a low-energy approximation zeroing the second-nearest neighbor hopping term, is usually written as follows:

$$E_{\pm}(q) = \pm \hbar v_F q + \mathcal{O}(q/k)^2, \qquad (2.1)$$

where q is the translation of the momentum vector k at one Dirac point and its modulus is small  $(q = |q| \ll 2\pi/a)$ . This bandstructure has two remarkable properties: first, at the Dirac points (q = 0) the conduction and valence band touch each other and intersect, leaving no energy gap. This qualifies graphene as a zero band-gap semiconductor or, as it is also called, a semi-metal. Second, the energy dispersion is linear with momentum, resulting in a carrier group velocity constant over energy  $(v_g \simeq v_F)$ , where  $v_F \approx 1e^8 \,\mathrm{ms}^{-1}$  is the Fermi velocity); moreover, the effective mass is directly proportional to momentum and zeroes at zero energy [28]. This is a very different behavior than common semiconductors, whose dispersion has a parabolic shape and carrier velocity is function of the second derivative of the dispersion.

The density of states (DOS) is linear too; its value is zero at thermal equilibrium (E = 0) and 0 K. Each point  $\mathbf{q}$  is twofold spin degenerate (indicated with  $g_s = 2$ ) and, because of the two inequivalent Dirac points  $\mathbf{K}$  and  $\mathbf{K}'$ , also called valleys, is also twofold valley degenerate ( $g_v = 2$ ). The DOS then reads as follows [29]:

$$\rho_{gr}(E) = \frac{g_s g_v}{2\pi (\hbar v_F)^2} |E|. \tag{2.2}$$

At non-zero temperature, the energy integral of the DOS times the Fermi-Dirac distribution results always in a non negligible electron sheet density. Moreover, graphene is not perfectly planar and presents some corrugation on its surface (ripples), that however are the reason for which it can exist at non-zero temperatures without crumbling or decomposing [30]. This should induce charge inhomogeneities in neutral graphene, i.e. electron and hole puddles that increase the graphene conductivity at zero energy.

### 2.2.2 Consequences of the absence of bandgap

The most striking consequence of the lack of a bandgap is that a device made of graphene cannot stop the current flow. One of the most important achievements of Si CMOS technology, along with the ideal signal reconstruction, is the possibility to completely switch off the logic element to reduce the power consumption of the IC. A bandgap at

10

least comprised between 400 and 500 meV should be necessary for digital logic operation [9], [31]. Recently, the importance of a transport gap has also been stated for RF transistors [32], where devices don't switch off completely but a high output resistance  $r_0$ , i.e. saturation behavior, is necessary to obtain a high intrinsic gain  $G_{int} = g_m r_0$ [9]. Graphene FETs provide very high transconductance, but the lack of a well-defined saturation region reduces heavily the advantage of a graphene power amplifier.

A few methods exist to open a gap in the bandstructure of graphene, while some device concepts other than the conventional FET allowed for a remarkable  $I_{ON}/I_{OFF}$  ratio. The first, perhaps most obvious, way to create a bandgap is to localize the electronic wavefunction by reducing the lateral size of the Graphene Nanoribbon (GNR), down to a few nanometers or tens of nanometers, obtaining a quasi-1D structure. The small DOS and the reduced dimensions of the GNR nanotransistor enhanced ballistic quantum transport, making graphene competitive with carbon nanotubes and III-V HEMTs. GNRs are very similar to carbon nanotubes, with the difference that a CNT has periodic boundary conditions. The confinement gap typically scales as the reciprocal of the width (1/W), depending on the crystallographic direction, i.e. the edge [33]: conversely to CNTs, zigzag GNRs are always metallic while armchair GNRs result in three families, two of which semiconducting and one metallic, depending on the width. The inverse proportionality of the bandgap with the width has been validated experimentally with values reaching 300 meV for ribbons smaller than 30 nm, but without any decisive evidence of a dependence on crystallographic direction [34]. Moreover, defective edges and charge puddles alter the transport properties of the nanoribbon, eventually fragmenting it in a collection of quantum dots, making the transport gap to include conductance peaks instead of a homogeneous switch-off behavior [35]-[37]. Edge disorder also perturbs heavily the mobility, which is the main advantage of graphene over Si [38]. However, the need for a saturating behavior has pushed researchers to pattern graphene in reduced-width strips in high-frequency mixers [39] and amplifiers [40]. Ribbons of 100 nm in the first case and 50 nm in the second one allowed to increase the  $I_{ON}/I_{OFF}$ ratio and to improve RF Figures of Merit (FOM) as  $f_{max}$ .

A particular kind of bilayer graphene (BLG), the Bernal stacked one, has the interesting property of creating a small gap between the parabolic conduction and valence bands (sometimes referred to as a "Mexican hat") when a vertical electric field is applied. In Bernal stacked graphene, half of the carbon atoms are placed above the center of the underlying hexagon, and half above the corners, i.e. above C atoms. Unfortunately Bernal BLG is mostly obtained by mechanical exfoliation, which is a costly and humanintensive task. The number of studies available in literature of direct growth of Bernal BLG is also very limited [41], [42]. In addition, the working principle is more complicated and to create a vertical electric field two gate electrodes are necessary. Achievable bandgaps are quite limited, with experimental values of 130 meV and  $I_{ON}/I_{OFF}$  ratios of 100 at RT [43].

An alternative, more exotic, configuration is the Vertical Graphene Transistor based on the tunnel current through a thin dielectric between a graphene layer and another electrode. A device with a graphene layer as second electrode has been presented in 2012, where in addition to the tunnel stack a third isolated gate is present (a doped Si wafer and its surface oxide) which allowed for the triode modulation of the tunnel current [44]. An  $I_{ON}/I_{OFF}$  ratio of 50 has been achieved. No RF operation has been demonstrated yet.

A variant of this configuration is the graphene hot-electron transistor, which is actually a graphene implementation of the hot-electron metal-insulator-metal-insulator-metal (M-I-M-I-M) transistor, a concept close to the BJT. Graphene is used as a low resistivity and extremely thin base electrode of a device composed by an emitter-base tunnel junction and a base-collector filtering dielectric (a relatively thick Alumina layer). This operation principle has been explored independently by two labs, and interesting  $I_{ON}/I_{OFF}$  ratios of  $10^5$  have been achieved [45], [46]. Unfortunately, present-day literature has not yet recognized the main problem involved by such devices, which is the same that plagued in the first place the concept of a M-I-M-I-M tunnel transistor: an extremely low current gain, which resulted in collector currents 10 orders of magnitude smaller than those simulated with NEGF models [47].

### 2.3 Graphene FET models

As stated in § 2.2, full-quantum models like Tight-Binding (TB) [26] and Density-Functional Theory (DFT) [48] calculations were the first to be developed for graphene. When graphene was experimentally discovered in 2004, they were the first tool used for the investigation of its properties. However, their computational cost depends on the number of atoms of the material piece to be modeled, thus its use is limited to extremely small surfaces (or volumes). This fact influenced the kind of devices which theoretical researchers were first interested to. GNRs are structures of very limited surface and considerable bandgap. They were the motivation for the highly envisaged "graphenium-inside" computer processor [49], in the sense that it was a research subject that offered exciting performances derived directly from a quantum effect like ballistic transport [50]–[53]. In addition, semiclassical ballistic models were applied to GNR-FET [54]–[57]. However, the validation of GNR models versus device measurement is more complicated due to the technological difficulties in realizing defect-free ribbon edges, so

it was mainly done against TB models. The development of an empirical model of the GNR-FET has been largely inhibited for the same reason.

On the other hand, empirical characterization of graphene was done on micrometer-sized devices, therefore transistors based on large-area graphene (GFET). For that range of dimensions, the main electronic transport mechanism is drift-diffusion and, due to its larger dimensions compared to GNR-FET, the simulation of its behavior was hardly achievable with full-quantum models. Semiclassical modeling was instead a more appropriate tool for the analysis of its characteristics, and existing physical and semi-empirical models [58], [59] for semiconductors were adapted to graphene [60], [61]. The comparison of those models to device measurement is easily achievable and strengthens the reliability and the accuracy of those approaches. In this work, large-area graphene transistors will be simply referred as GFET. Moreover, the aim of this work is to model single-layer graphene devices, whereas few-layer devices will be considered as out of scope.

### 2.3.1 Physical models

Quantum models are numerical tools in which the set of quantum mechanics equations are discretized and evaluated for each atom of the entire device. Those models allow for the computation of the drain current in the ballistic limit through Tight Binding (TB) theory for all drain and gate biases. The TB problem is solved using Non-Equilibrium Greens Functions (NEGF) formalism [52], [62], [63] or the scattering matrix approach [64], [65].

The TB simulation of the device is done in a number of steps, here briefly reviewed: the Dirac Hamiltonian is discretized using the Finite Difference (FD) method; the  $N \times N$  FD matrix, where N is the number of atoms in the channel, is constructed using the values of the overlap integrals computed through finer models as DFT; the solution for the eigenvalues of the matrix gives the bandstructure of the channel, from which the number of transmitting modes is extracted for the specified gate and drain bias; finally the Landauer equation is applied to each mode, yielding the net current of the device. The overall computational cost of TB methods, already elevated, scales as  $N^2$  and is not suitable for compact modeling in circuit simulators. The band structure produced by those models is generally compared for validation with DFT simulations. Large-area short-channel graphene has also been simulated, although in the ballistic transport limit [63].

Semiclassical ballistic models for GNR-FET simulation are simplified approaches that avoid the Hamiltonian discretization step typical of TB models; they instead derive the bandstructure using either analytical equations or off-line TB-computed values. They

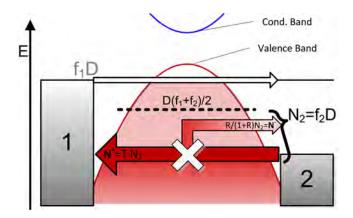

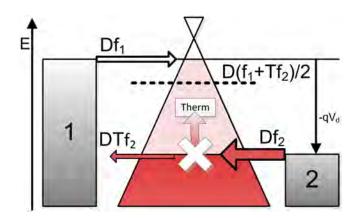

include a number of approaches, both semi-analytical and analytical ones. A type of semiclassical semi-analytical nanotransistor model can be found in [54], [66]; it is the adaptation to GNR of the MOS nanotransistor Top-of-the-barrier model [67]. In this theoretical framework the conduction relies on transmission modes, each allowing a quantized amount of current through the Landauer equation [68] for ballistic transport. The net number of transmitting modes is the result of the balance of two injected electron fluxes, one from source and one from drain [69]. The channel potential determines which modes are able to transmit by changing the alignment of the energy state distribution to the Fermi energy. The electrostatic problem for the channel is simplified into the solution of a single non-linear system of equations, which is solved iteratively by successive approximations. Finally the current is evaluated for transmitting modes through the Landauer equation for ballistic transport. The model operation will be discussed in greater detail in 3. Analytical implementations of this type of model, which employ only closed-form equations for the computation of the channel potential, has also been presented [70], [71]. In conclusion, Top-of-the-barrier models allow for the simulation of the ballistic conduction phenomenon, which is a quantum effect and is significant for GNR-FET, without the use of extensively numerical tools and taking into account a simplified picture for device electrostatics. The drift-diffusion conduction mechanism is not considered here, neither is any scattering mechanism. Being ideal ballistic conduction the theoretical limit to which nanoscaled devices tend, there doesn't exist yet any measurable device that can be fabricated to validate those models.

A more complicate semiclassical analytical model for single layer and BLG nanoribbon transistor simulation is shown in [57], with the implementation of a scattering mechanism in [72]. It is based on the Boltzmann Transport Equation for the electron transport and represents the channel potential in the weak nonlocality approximation formalism; this allows expressing the channel potential in an analytical form. The model is then evaluated to various limiting cases corresponding to the amount of charge induced in the channel by the top-gate electrode. This model allows relating analytically the current and the transconductance with geometrical dimensions of the device. However, the validation is an issue even for this work, which does not present any comparison to finer models or measurements.

Semiclassical approaches have been applied also to large-area graphene FET devices. Although they are all based upon the drift-diffusion transport equations, they can be categorized from semi-analytical to purely analytical approaches. The existence of a large number of GFET device measurements in literature enables the validation of these models.

A type of semiclassical semi-analytical for GFET is shown in refs. [60], [73], [74]. In those works a numerical approach for the computation of the channel electrostatics is employed: the channel length dimension is discretized in a vector of points; the selfpotential of channel carriers and the quantum capacitance effects are then iteratively evaluated for each point. The resulting potential profile is used to find the longitudinal electric field and the current using the drift-diffusion transport equation. Another semianalytical approach derives a closed-form expression to account for quantum capacitance [75]; on the other hand, it uses an iterative method to solve for the internal bias of the intrinsic transistor. Finally, purely analytical models don't use iterative methods at all [76], [77], but it's not clear whether they take into account the contribution of external drain and source resistance as [75] does. Those models are well suited for the simulation of long-channel GFET devices, and include short-channel effects through the empirical account for saturation velocity. In this way they can take into account a limited amount of ballistic transport in a more general drift-diffusion picture. However, the case of the nanotransistor where nearly the entirety of transport is sustained by quantum effects cannot be correctly taken into account. The validation of those models is generally done versus measurements, except for the work presented in [76], [77]. Their accuracy together with the small computational load makes those models suitable for compact modeling in circuit simulators. An example of such a possibility is given by the implementation in VHDL-AMS and SPICE language of a semi-analytical drift-diffusion model as shown in [78], [79].

### 2.3.2 Empirical models

Empirical models are less devoted to the understanding of the physics involved in the device operation, while they are more suitable for the reproduction of the measurements of a small class of devices, typically brought together for similar geometrical dimensions and materials used. Those models generally contain a greater number of parameters that don't have any physical meaning. Moreover, they typically use a smaller amount of iterative loops in favor of closed form expressions.

An empirical physics-based compact model is presented in [61]. It extends the virtual-source model originally developed for short-channel Si CMOS [59] to the GFET case. It is similar to the Top-of-the barrier model, with the use of the drift-diffusion theory in the place of the ballistic transport. In this model the operation of the device is divided in three regions, depending on the type of carriers present in the channel: only electrons, only holes or both of them. The charge density is computed empirically, while the current in the intrinsic transistor is computed with the drift-diffusion equation for each region. As in [75], the computation of the current is part of an iterative loop

that ensures its self-consistence with both internal and external (applied) bias. This step is also commonly done by SPICE-like tools as in [80], but in this particular one it must be done inside the model itself to determine the correct operating region. Finally empirical smoothing functions are employed to ensure the continuity of the current up to the first derivative between two regions. The simulated current is then validated versus measurements. This model provides a numerically efficient and accurate compact model of the GFET operation that can be readily implemented in circuit simulators. However, the use of different set of equations for different regions may introduce artifacts in the shape of the transconductance  $g_m$ . Moreover, while its continuity is ensured by the smoothing functions, the continuity of its derivative is not taken into account and can represent an issue of this approach (see section 1.3 in [81]).

In conclusion, it has been shown that the simulation of graphene devices can be approached with different levels of physical detail, starting from full-quantum modeling of graphene nanotransistors to the empirical modeling of large-area graphene transistors. Greater detail is associated to a geometrically smaller domain that can be simulated and in which the assumptions introduced maintain their validity. A model with validity extending from the GNR nanotransistor to the long-channel GFET is not known to date. Moreover, the validation versus measurements should be gauge of quality, that for GFET are available while for nanotransistors are not.

### 2.4 Graphene/metal contact and propagation models

In mono-layer graphene the conduction takes place onto the surface of the material, in the system of  $\pi^*$  electrons and  $\pi$  holes that are located out of the plane. The surface also is in direct contact with metals; thus the electronic conduction properties are deeply influenced by the type and strength of the interaction between metal and graphene. It is then reasonable to say that the contacted graphene behaves as a different material compared to freestanding graphene. The graphene under the metal together with the layers of the metal with which it interacts is called a graphene-metal complex. The modeling of its specific physical and electrical properties is addressed by means of physical-chemical modeling and empirical modeling.

The most relevant electrical parameter is the contact resistance  $R_C$ . The regions that are adjacent to the contact are also chemically and electrically affected by the metal. Those regions contribute as well to the overall resistance of the device because of altered amount and type of carriers they contain. In this work the access resistance in a typical graphene device will be referred as the total resistance between the bulk of the metal and the contact-independent graphene. In the specific case of a FET, this latter region

| Ref. | Metal stack                           | $R_C \left[\Omega \cdot \mu \mathrm{m}\right]$ |

|------|---------------------------------------|------------------------------------------------|

| [85] | Pd/Au                                 | $230 \div 900$                                 |

| [85] | Ti/Au                                 | $430 \div 900$                                 |

| [86] | thin Cr/Pd                            | $350 \div 750$                                 |

| [87] | Ni                                    | > 500                                          |

| [88] | $\mathrm{Ti}/\mathrm{Pd}/\mathrm{Au}$ | 525  (top)                                     |

| [89] | Clean Au                              | $95 \div 128$                                  |

| [90] | Ti                                    | $20 \div 80$                                   |

Table 2.1: Contact Resistance at Room Temperature.

Table 2.2: Contact Resistance at Low Temperature.

| Ref. | Metal stack               | $R_C \left[\Omega \cdot \mu \mathrm{m}\right]$ | $\overline{\mathrm{T}}$ |

|------|---------------------------|------------------------------------------------|-------------------------|

| [85] | Pd/Au                     | 110÷470                                        | 6 K                     |

| [91] | $\mathrm{Ti}/\mathrm{Au}$ | > 800                                          | $0.25~\mathrm{K}$       |

| [92] | Cu                        | 135                                            | 4 K                     |

will be the one controlled by the gate electrode alone. The contact resistance will be defined instead as the resistance between metal and graphene directly underneath. The case of a device too short to show a contact-independent region will not be considered.

The contact resistance is a parasitic that inhibits the performance of a device, in particular the transconductance [82]. The extrinsic transconductance is obtained by the derivative  $\delta I_D/\delta V_G$  measured on the external device terminals; it is related to the intrinsic one as follows:

$$g_{m,x} = \frac{g_m}{1 + R_S g_m} \tag{2.3}$$

where  $R_S$  is the source access resistance (which contains the contact resistance term). The International Technology Roadmap for Semiconductors has selected the contact resistance as one of the target parameters to be minimized for graphene to be employed in semiconductor industry. A target value of  $1e-8\,\Omega\cdot\mathrm{cm}^{-2}$  has been proposed [83]. For MOSFET technology instead it is  $80\,\Omega\cdot\mu m$  per contact, which is about the 10% of the transistor's on-resistance  $V_{DD}/I_{ON}$  [84]. In Tables 2.1 and 2.2 a summary of values of  $R_C$  from recent studies is collected.

### 2.4.1 Physical and Chemical models of the contact

Metal-graphene contact is a very active subject of current study, and the physical mechanisms behind it are not completely understood. Advances in the modeling of the contact were motivated by new phenomena, introduced by new experiments and that it was necessary to account for.

In the first graphene transistors an asymmetry in the electron and hole branches of the V-shaped  $I_D(V_G)$  was shown. It was first noticed by [93] and was later explained experimentally by the presence of doping: along with the shift of the minimum conductivity point (i.e. Dirac point) in the  $V_G$  axis, the slope of the left branch increased for p-type doping, and conversely on the right branch for n-type doping [94]. A photocurrent study confirmed the presence of p-n junctions in the region adjacent the metal contacts, suggesting the possibility that doping was induced by the metals that contacted graphene [95]. P-n junctions within the channel are expected to increase the access resistance of a FET device [96], i.e. the resistance between the metal contact and gate-controlled region of the FET channel. The presence of a metal-doped region was explained by chemical models for complexes made of graphene and various metals within the density functional theory (DFT) [97], [98]. This is a quantitative technique of computational chemistry to obtain ground-state electronic properties of many-body systems, in particular atoms and molecules; more details are contained in [99].

DFT was used to study the band-structure of graphene-metal complexes, along with their work function and bonding energy for various metals. Those studies allowed distinguishing two categories of complexes upon the strength of the metal-graphene binding: physisorbed graphene, where graphene's band-structure is mostly preserved; and chemisorbed graphene, where the contact is more intimate and the band-structure of the complex is something different from both metal and graphene. Chemisorbed metals can provide better mechanical stability and electrical connection than physisorbed ones [97]. However, for the purpose of an equivalent circuit of contacted graphene, in this manuscript there will be no distinction between chemisorbed and physisorbed metals.

The formation of the graphene-metal complex is conceptually divided in four steps in Fig.2.2. In (a) the clean metal and intrinsic graphene are separated. The different magnitude of their work functions induces doping in graphene when the vacuum potential of the materials gets aligned (b). The common Fermi level is pinned to the metal's one and graphene's band structure is shifted (towards higher energies in this case), creating a doping potential  $\Delta E_F$ ".

However, a strong Pauli-exclusion interaction occurs between the metals' inner orbitals (s-electrons) and graphene  $\pi$ -electrons. It repels electrons from the metal-graphene interface and significantly shifts down graphene's energy levels, leaving unaltered the metal's ones because of the large difference in amount of states between the two materials [100]. The depletion in electrons at the interface leads to the formation of an electric dipole, influencing the magnitude and eventually the sign of the doping. The potential generated by the dipole, marked in [98] as a quantity  $\Delta_c$ , adds up with the previous potential difference value and gives  $\Delta E_F \prime = \Delta E_F \prime \prime - \Delta_c$ , as seen in Fig.2.2(c). In [98] is

FIGURE 2.2: The Work functions of metal and Graphene, in successive steps: non in contact (a); alignment of vacuum potentials and initial graphene doping (b); the formation of the Pauli repulsion potential  $\Delta_c$  (c); the charge transfer and further reduction of the potential, up to its zeroing at a distance from the metal when pristine graphene is encountered (d).

proposed that the potential added by this Pauli-interaction dipole should have a value nearly independent from the metal or the systems, so that the doping type and value can be predicted within some limits for metals with known working functions. However, in [100] is stated that this potential value is indeed very sensitive to the filling of the outermost s-orbital of the metal, thus to the metal itself. As a consequence of the doping induction, a charge transfer process happens which mitigates the doping itself.

As matter of fact, not all of the attracted charges can be sustained by graphene for a certain amount of doping. Each elemental charge generates a self-potential, marked in Fig.2.2(d) as  $\Delta_{tr}$ , which acts on the graphene itself and, because of the limited amount of states in graphene, shifts back significantly the Fermi level to values closer to neutrality. It is useful to stress the point that transferred charge, which is generated by the reequilibration of Gauss law, is substantially different from the charge dipole generated from the Pauli-exclusion interaction. How this latter charge behaves in presence of electric fields is still a matter of study. Transferred charge shifts graphene's energy levels up (n-doped graphene) or down (p-doped graphene), compensating the overall potential of graphene under the metal, then the doping itself. The final value of the doping is  $\Delta E_F$ . In (d) is also shown the region of graphene far from the contact which regains its intrinsic state. The region comprised between those two points is called *charge transfer region* [95].

So, with DFT studies it is possible to identify the origin of doping from adsorbed metals in graphene and predict their value. Based upon DFT calculations, an empirical model of graphene doping from metals has been presented [98]. The results proposed by DFT calculations include a detailed description of many useful physical and electrical parameters. However, those results must be taken carefully because small variations in the structural parameters of the metal's atomic lattice [101] or in the computational method used [102] can yield a difference in graphene doping of several hundreds of meV, and even a change of doping type.

Photocurrent studies have confirmed that the metal-induced doping extends spatially towards uncontacted graphene forming the charge transfer region, creating then a junction with gate-controlled graphene [95]. In Fig.2.3(a) a back-gate FET is shown that, depending on the gate potential, modulates the doping of its charge transfer regions (shaded in green for the case  $V_G = 0$  in (b)), and therefore its access resistance  $R_{S,D}$ .

The first work that focused on the extension of this region was a DFT study of metal-contacted graphene nanoribbons (GNR) [104], whereby the potential of metal-induced doping potential was suppressed after few nanometers from the edge of the contact. Moreover, this study shows that the potential of contacted graphene start a smooth transition towards uncontacted graphene before crossing the metal edge. This is a result

FIGURE 2.3: Potential and resistivity along the channel of a graphene FET. (a) structure of the back-gated FET; (b) Electrostatic potential represented as the trace of the Dirac point of graphene for  $V_G>0\,V$  (blue dash-dotted line),  $V_G=0\,V$  (black dotted line) and  $V_G<0\,V$  (red dash-double-dotted line); (c) Resistivity along the channel for various gate voltages. In yellow the area of the access resistances  $R_S$  and  $R_D$ .  $\rho_{DP}$  is the resistivity at the Dirac point in graphene. Adapted from [103].

that can be found in more recent models (notably [85]) and that will be discussed in greater depth in the last part of this section. However, the fact that the charge-transfer process is neglected and the use of ill-defined boundary conditions, as pointed out by [105], tend to lower the importance of this study.

An analytical model of the charge transfer region and its spatial extension has been proposed in [105]. This model uses the Thomas-Fermi approach to study the band bending caused by metal contacts on undoped, chemically doped and electrically doped (i.e. with a gate electrode) graphene. The extension of the charge transfer region depends on the decay of the electrostatic potential by the charge screening, which strength depends on the doping and on the presence of electrical gating. This screening is generally weak, and makes the potential to decay with the distance from the metal contact as  $x^{-1/2}$  and  $x^{-1}$  for undoped and doped graphene [105]. The predicted charge transfer region is therefore of considerable size. The position of the junction as well as its type (p-n, p'-p, etc.)

FIGURE 2.4: Access resistance of a double-gate graphene FET. (a) the structure; (b) The Fermi level  $E_F$  (solid black) and the trace of the Dirac point (blue dash-dotted) along the channel; (c) the equivalent circuit of the extrinsic transistor.

depends on the metal-induced doping and gate voltage. This model thus allows for the prediction of the dimension and type of the metal-induced junction, which is responsible for the increase of the access resistance and of the asymmetry of the  $I_D(V_G)$  transfer characteristic in graphene FETs. However its complexity and the lack of a comparison with access resistance measurements make its use difficult. On the other hand, another analytical model [106] proposes to use linear-graded charge transfer regions instead.

In Fig.2.4 a double-gated graphene FET is shown along with its equivalent circuit in (c).  $R_S$  and  $R_D$  are the access resistances; each of them is the series of the contact resistance  $R_C$ , the charge transfer junction resistance  $R_{junc}$  and of the resistance  $R_{ch}$  that comes from the section of the channel not controlled by the top-gate. Self-aligned contacts in top-gated GFETs allow for the minimization of access resistance and for a better electrostatic control of the channel [6], which results in graphene completely covered either by the gate electrode stack or by the contact electrodes. The extension of the charge transfer region should be also minimized. A comparison between a transistor with a partially gated channel and one with self-aligned contacts has been performed in [107]. A better control of the channel through the top gate was found, together with a modulation effect by the back-gate potential on the electron-hole asymmetry in the  $I_D - V_{G,top}$  characteristic. Being the term  $R_{ch}$  minimized by contact auto-alignment, it cannot contribute to the asymmetry modulation; instead, this effect is ascribed to contacted graphene. This means that a modulation of the doping profiles in the graphene

regions underneath the source/drain contacts by the back-gate voltage should be possible. Authors of [107] then claim that the back-gate impacts the alignment of the Fermi level relative to the graphene cone dispersion relation. An electrostatic control of the Fermi level of contacted graphene through the back-gate should be possible, contradicting the thesis that the Fermi level of the graphene-metal complex is firmly pinned to the metal's one. However, it's not clear what would be the effect of the back-gate on the term  $R_{junc}$ , which is neither under the contact nor totally controlled by the top-gate.

An explanation to the back-gate control of the doping of contacted graphene, along with its effect on  $R_{junc}$ , is presented in [108]. In case of weak electronic interaction between metal and graphene (physisorption), graphene's pristine electronic band structure is preserved, and the metal/graphene interfacial layer demonstrates a dielectric-like behavior. The modulation effect is then modeled through an effective thin metal-graphene interfacial dielectric layer, whose capacitance concurs with the much weaker back-gate capacitance to the electrostatic control of the Fermi-level in contacted graphene. The dielectric layer should be thin enough to sustain a tunneling current through it, defining a tunneling contact resistivity across the interface. However, an overall equivalent circuit with both the capacitive and resistive terms of the contact has not been presented by the authors. On the other hand, the transport across the junction is considered ballistic and it is modeled through the Landauer equation of transport in the NEGF formalism. The two terms of the resistance are thought independent and separated, thus the overall access resistance can be calculated as the series of all terms. This approach then allows for the computation of the electron-hole asymmetry effect through the modeling of the impact of back-gate voltage on the doping of the contact. However, it must be noted that this approach does not include any interaction between metal and graphene apart from the electrostatic one, and does not consider any Fermi level pinning; in short, the metal-graphene contact is not considered as a chemical complex. Moreover, the model by construction is not able to extract both the interface capacitance and the metal-induced doping at the same time, therefore it leaves the doping as a free parameter, which could be an issue in this approach.

The effect of the gate on the electronic properties of the contact has been studied in more depth in [100]. Within the frame of DFT simulations used to compute the band structure of physisorbed and chemisorbed graphene, the effect of an externally applied electric field to the complex has been analyzed. DFT simulations have shown that an external electric field can shift graphene's energy-levels up and down relative to the Fermi level, which is pinned by the metal substrate; this allows for the back-gate modulation of graphene's work function and doping [100]. Anyway, it's not clear whether the electric field affects only the alignment of the energy levels or affects also the Pauli-exclusion interaction dipole, i.e. the equilibrium distance between metal and carbon atoms.

A model that combines most of the results from DFT simulations with the geometry of the contact is presented in [85]. Here the transport along the graphene surface underneath the metal is also considered, proposing the concept of a distributed transmission of carriers from graphene to metal. In this model the contact is no more considered as only dependent on the width of the contact; instead, a transport mechanism would be present in contacted graphene also beyond the contact edge, and a contact length dimension would be involved. The transport from free-standing graphene, crossing the p-n junction towards beyond-the-edge contacted graphene is thought as ballistic; in addition to this, another mechanism would be the tunneling transport across the graphene/metal interface. The electric contact is considered to be the result of the concurrency of those two transport mechanisms: the only scattering process suffered by the graphenegraphene transport is the graphene/metal tunneling, and the overall transmittance is treated as the coherent cascade of the two transmittances [108]. The model includes the results of DFT simulations through the empirical model introduced by [98] for the modeling of the doping; this latter is further affected by the back-gate through electrostatic doping. The conductivity of contacted graphene depends on the doping, and so does the transmittance of the graphene-graphene transport. The unit-length contact conductance is finally evaluated using a modified Landauer formula, combining the two transmittances. Anyway, because of its complexity, this model contains a number of free physical parameters that makes its use for real measurement datasets very difficult.

At first a dependence of the contact resistance on length has been argued by [87], supporting only a width dependence of  $R_C$ ; however, those experiments were prone to the minimum feature length of around 1  $\mu$ m by the technology adopted by the authors. In [85] the residual potential difference between metal and graphene is shown to decrease with distance from the edge, in a similar way as proposed by [104], and should reach zero in few hundreds of nanometers, that is well below the experimental limits of [87]. Finally it has been shown experimentally in [109] that reducing the contact length below 200 nm would make the resistance to increase inversely linearly with contact length, thus contradicting the results of [87]. The model proposed in [85] allows relating the metal-induced doping, the electrostatic doping and the geometry of the contact to its resistance. The trend of the dependence of  $R_C$  on length has been therefore confirmed. However more accurate measurements would allow extracting a precise law for this dependence, if any; such kind of law has been extracted for semiconductors already in the '70s, and will be presented in the next section.

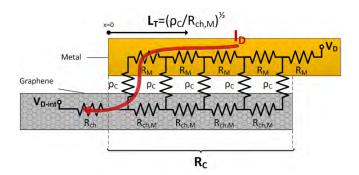

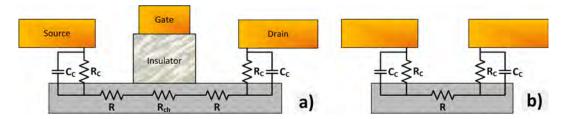

FIGURE 2.5: The Transmission Line Model (TLM) circuit for contact resistance. The current  $I_D$  crowds in a transfer length  $L_T$  neighborhood from the edge of the metal, following the least resistance path.

### 2.4.2 DC models and measurements

When a metal is in contact with another material with a lower conductivity, either a semiconductor or a semimetal, the current naturally flows through the least resistance path and enters the semiconductor only near the edge of the metal. This effect is called *contact current crowding* and it's thoroughly described in the Transmission Line Method (TLM) for planar devices by [110]. Its equivalent circuit is shown in Fig.2.5 for the case of a metal-graphene contact. The units of the quantities in the image are the following: contact resistance  $R_C$  [ $\Omega$ ·mm], specific interface resistance  $\rho_C$  [ $\Omega$ mm<sup>2</sup>], metal sheet resistance  $R_M$  and graphene-under-metal sheet resistance  $R_{ch,M}$  [ $\Omega/\square$ ], transfer length  $L_T$  [nm].

In this model the semiconductor sheet thickness is zero, which is a perfectly adequate assumption for graphene, less for traditional semiconductors (see § 3.4 of [111]). So, the current flow is distributed on one-dimension. In horizontal direction there are the sheet resistivities,  $R_M$  for metal and  $R_{ch,M}$  for contacted graphene, and on vertical sections the interface resistivity  $\rho_C$ . For semiconductors the resistivity of the free-standing material is the same of the contacted one. The analytical solution of the model gives an hyperbolic cotangent dependence of  $R_C$  on contact length:

$$R_C(L) = \frac{\rho_C}{L_T} \coth(L/L_T). \tag{2.4}$$

This equation was also confirmed for CNT by measurements of a device in which the contact length was increasingly reduced by FIB and laser ablation [112], [113].In [87] the sheet resistances of contact and uncontacted graphene are assumed equal in value  $(R_{ch} = R_{ch,M})$ , but with the result that  $R_C$  is almost independent on length; this brought the authors to deduce that the most of the current crowds at the edge of the contact, mostly because of the great difference in value between  $R_{ch,M}$  and  $R_M$ .

The large difference in resistivity should be further enhanced by the higher scattering that electrons in contacted graphene should suffer, larger than in free-standing graphene; this assumption is supported by an increased signature in the defect-related D band in Raman spectroscopy of graphene through a thin metal film [103]. However, no increased signature of the D band is reported in [114]. Anyway, the TLM picture does not include the resistor  $R_{junc}$  (see Fig.2.3), so it's not clear which role should play the junction in the overall access resistances  $R_S$  and  $R_D$ .

The most used procedure to measure  $R_C$  is the Transfer Length Method (again, abbreviated as TLM) which was originally proposed by Shockley [115]. It has been later refined as the measurement of the resistance of a pairs of devices with unequal contact separation; the contact resistance  $R_C$  is extrapolated by the y-intercept of the R vs. L plot, while the resistivity of the semiconductor is given by the slope of the R-length plot. For short length contact, of the order or less than  $L_T$ , it can yield  $\rho_C$  too. This method is however prone to at least two sources of error: one that comes from the geometry, in which strip width and contact separation variation can induce significant error on the final  $R_C$  [116]. This can be minimized by the excact geometrical characterization of the measured devices, as done in [90]. Moreover, non-uniformities of the electrical parameters can lead to errors in the extracted contact parameters even if there is no error in the measured electrical and geometrical parameters [117]. Finally, metal overlays with high sheet resistances can also alter effective  $R_C$  value [118].