2 mint

# SPACE SHUTTLE Main Engine Controller Assembly Phase C-D

QUARTERLY PROGRESS REPORT 27 May 1973 - 9 September 1973

Submitted to: Rocketdyne Division Rockwell International Corporation

Per: Rocketdyne Contract No. R20SPA550031 Data Procurement Document No. 900001 Data Requirement Document No. 55-M-004

2770- 3024

HONEYWELL Government and Aeronautical Products Division

Printed in U.S.A.

W2101-QPR-3-73

21 September 1973

CONTRACTOR OF STREET

#### FOREWORD

This is the sixth quarterly progress report submitted in response to Data Requirement 55-M-006 of Contract R20SPA550031. It is a progress status report of work performed by Honeywell as a subcontractor to Rocketdyne Division of Rockwell International Corporation. Honeywell is responsible for the Phase C-D design and development of the Space Shuttle Main Engine (SSME) Controller Assembly. This report covers the period 27 May through 9 September 1973.

- ii -

# - iii -

## CONTENTS

•

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SECTION I   | SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                                    |

| SECTION II  | ANALYSIS AND DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7                                                                                                                    |

|             | Schedule<br>Technical Problems<br>Thermal Design<br>System Power<br>Printed Wiring Board Screening Tests<br>Weight<br>System Design<br>Current Controller Configuration<br>System Design Studies                                                                                                                                                                                                                                                                                                                                                                                      | 7<br>8<br>9<br>12<br>13<br>13<br>14<br>14                                                                            |

|             | System Specifications<br>Control System Analysis and Simulation<br>Design Verification Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16<br>58                                                                                                             |

|             | Hardware Design<br>Computer Interface Electronics (CIE)<br>Input Electronics<br>Output Electronics<br>Power Supply Electronics<br>Engineering Model (EM)<br>Simulation Interface Adapter (SIA)<br>Controller Mechanical Design<br>Digital Computer Unit<br>GSE/FTE Design<br>Command and Data Simulator (C&DS)<br>Controller Memory Programmer<br>Controller Checkout Console (CCC)<br>Factory Test Equipment (FTE)<br>Software Design<br>Memory Size and Process Time<br>Operational Program Requirements<br>Operational Program Design<br>Controller Acceptance Test (CATP) Program | 61<br>61<br>62<br>64<br>65<br>68<br>70<br>72<br>77<br>79<br>79<br>79<br>79<br>80<br>80<br>81<br>81<br>82<br>82<br>85 |

|             | Requirements<br>Controller Acceptance Test Program Design<br>Computer Acceptance Test Program (CMTP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85<br>85                                                                                                             |

| SECTION III | MANUFACTURING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87                                                                                                                   |

|             | Controller<br>Activation Schedule<br>Production Control/Flow Charts<br>Milestone Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87<br>87<br>87<br>90                                                                                                 |

•

.

|             | Digital Computer Unit<br>Activation Schedule<br>Production<br>GSE, FTE                                                                                                                          | 90<br>90<br>91<br>92                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| SECTION IV  | QUALITY ASSURANCE<br>Controller<br>Accomplishments<br>Significant Problems<br>Hardware, Process, and Procurement Plans<br>Digital Computer Unit                                                 | 97<br>97<br>97<br>98<br>98<br>98                     |

| SECTION V   | RELIABILITY<br>Controller<br>Test Monitoring<br>Design Reviews<br>FMECA<br>Nonconformance Reporting<br>Parts Management<br>Schedule<br>Digital Computer Unit                                    | 101<br>101<br>101<br>102<br>103<br>103<br>104<br>104 |

| SECTION VI  | MAINTAINABILITY<br>Maintainability Analysis and Prediction<br>Maintainability Verification<br>Support Hardware Recommendations                                                                  | 107<br>107<br>107<br>107                             |

| SECTION VII | SYSTEM SAFETY<br>General Status<br>Quantity of Catastrophic or Critical<br>Hazardous Conditions                                                                                                 | 109<br>109<br>109                                    |

|             | Hazardous Conditions<br>Hazardous Condition Summary<br>Accident/Incident Review<br>System Safety Hazards Analyses<br>System Safety Plan<br>Design Reviews<br>Changes with Safety-Related Impact | 109<br>109<br>110<br>110<br>110<br>110               |

- iv -

·

#### - v -

## ILLUSTRATIONS

| Figure |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

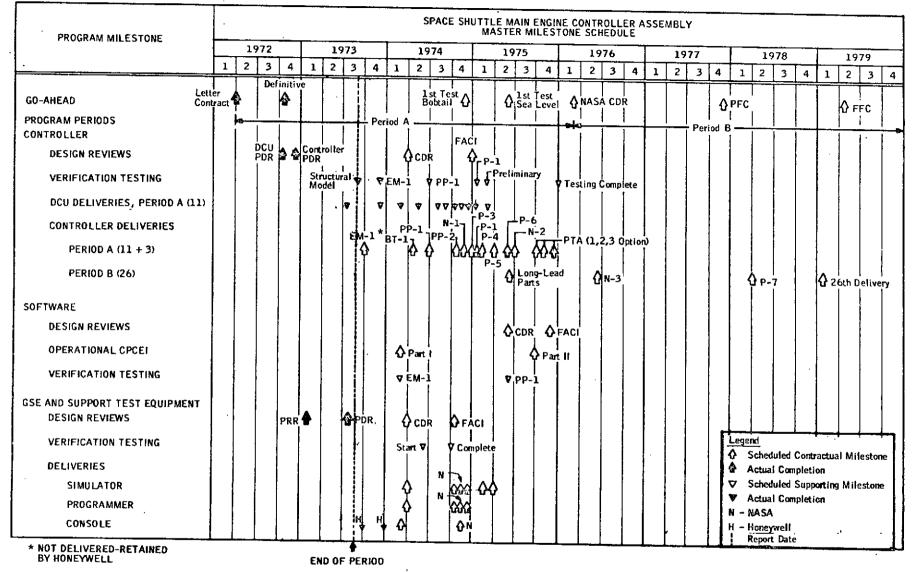

| 1      | SSME Controller Assembly Master Milestone Schedule                    | 2    |

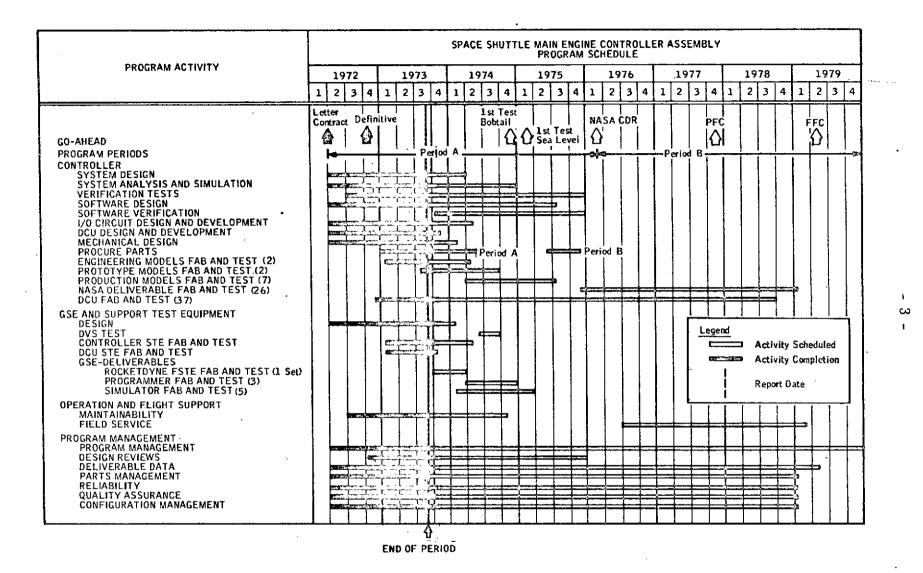

| 2      | SSME Controller Assembly Program Schedule                             | 3    |

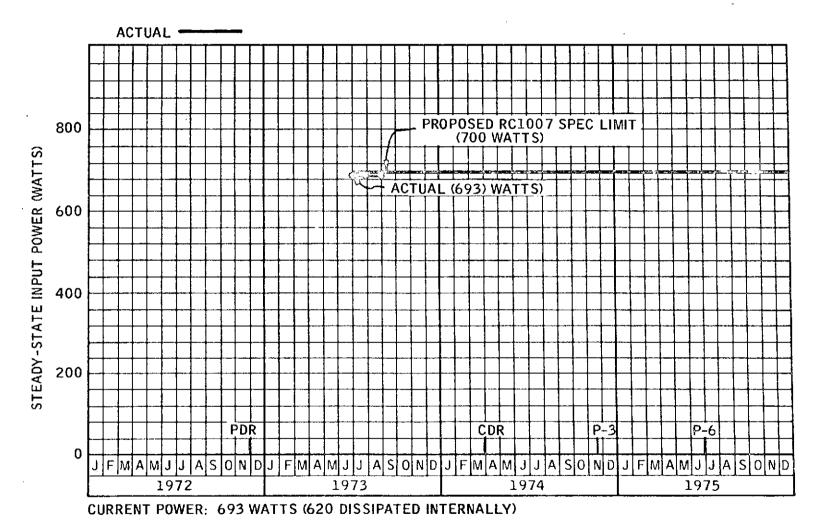

| 3      | Input Power Requirements - Steady-State (Start<br>Preparation)        | 10   |

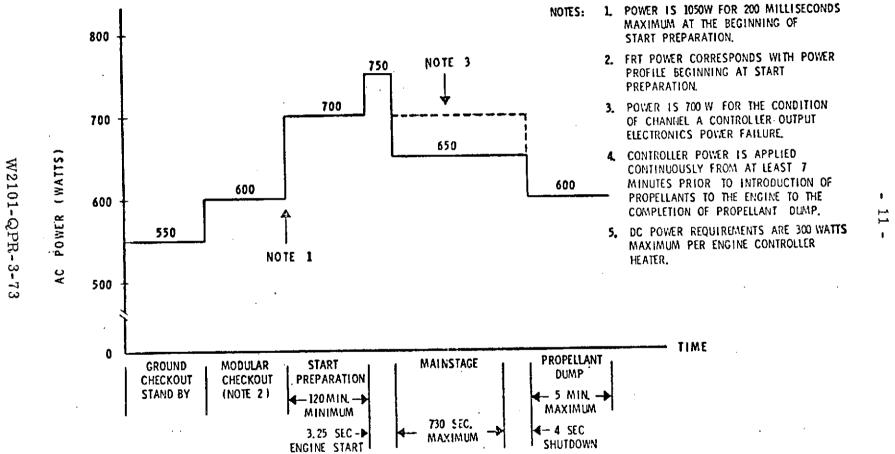

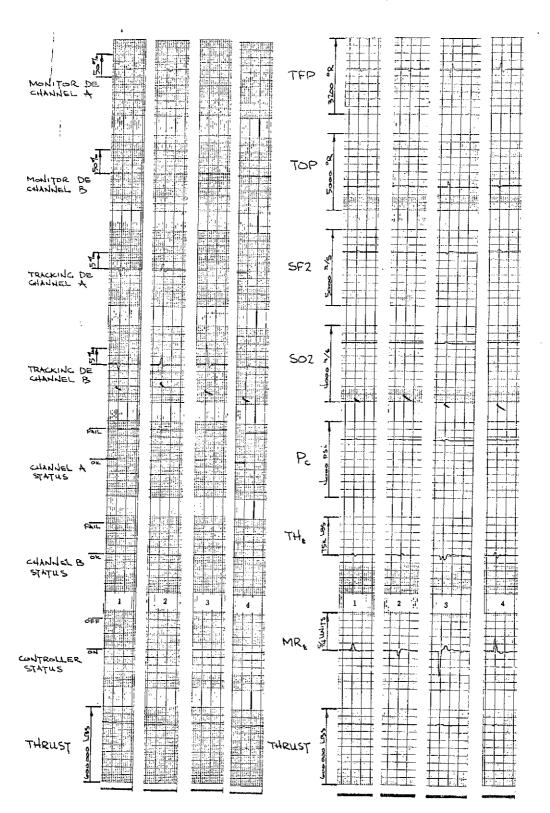

| 4      | Engine Electrical Power Profile                                       | 11   |

| 5      | OPV Servoactuator Failures at NPL                                     | 22   |

| 6      | OPV Servoactuator Failures at MPL                                     | 23   |

| 7      | FPV Servoactuator Failures at NPL                                     | 24   |

| 8      | FPV Servoactuator Failures at MPL                                     | 25   |

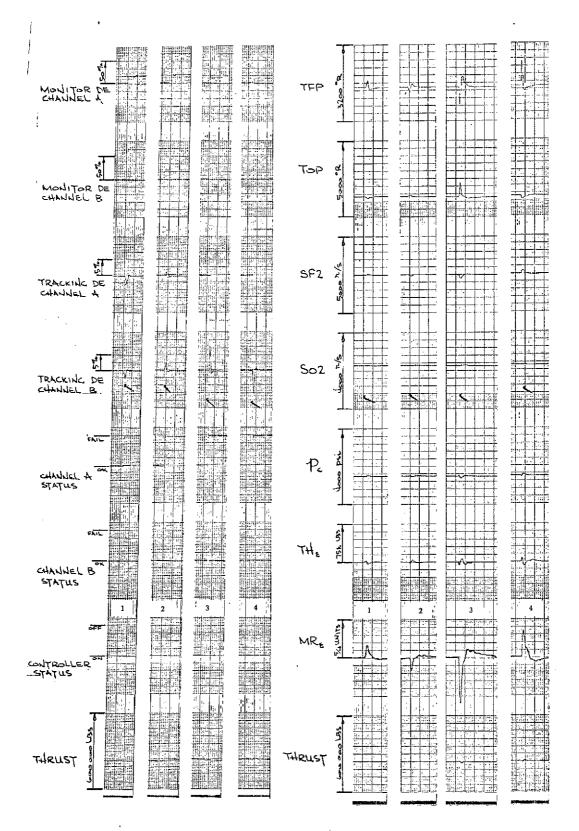

| 9      | MOV Servoactuator Failures at MPL                                     | 26   |

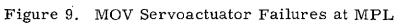

| 10     | Servoactuator Block Diagram                                           | 31   |

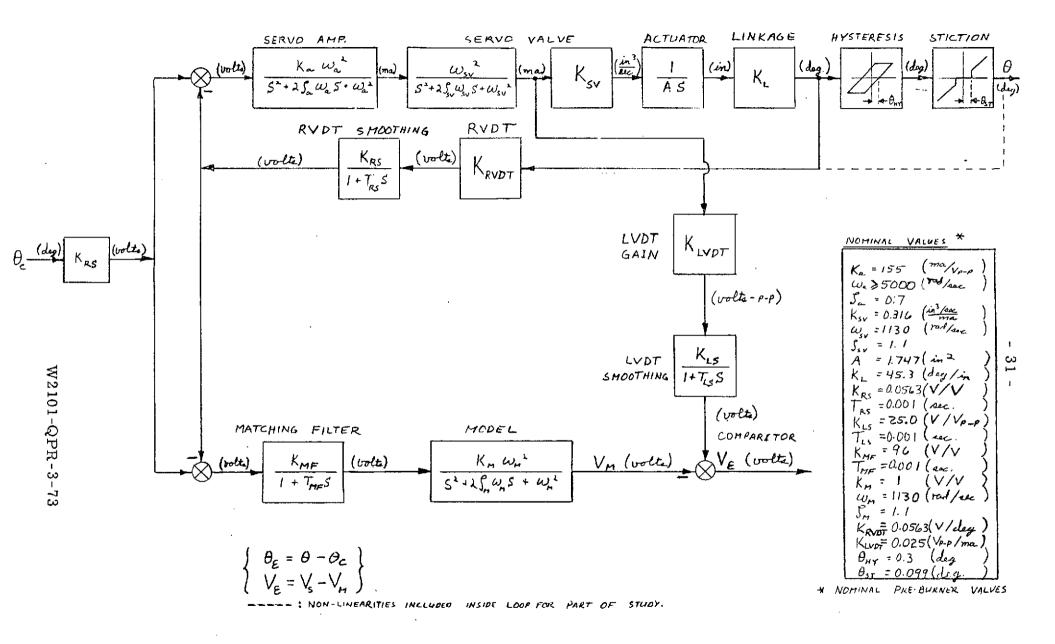

| 11     | Step Commands (+5 degrees)                                            | 32   |

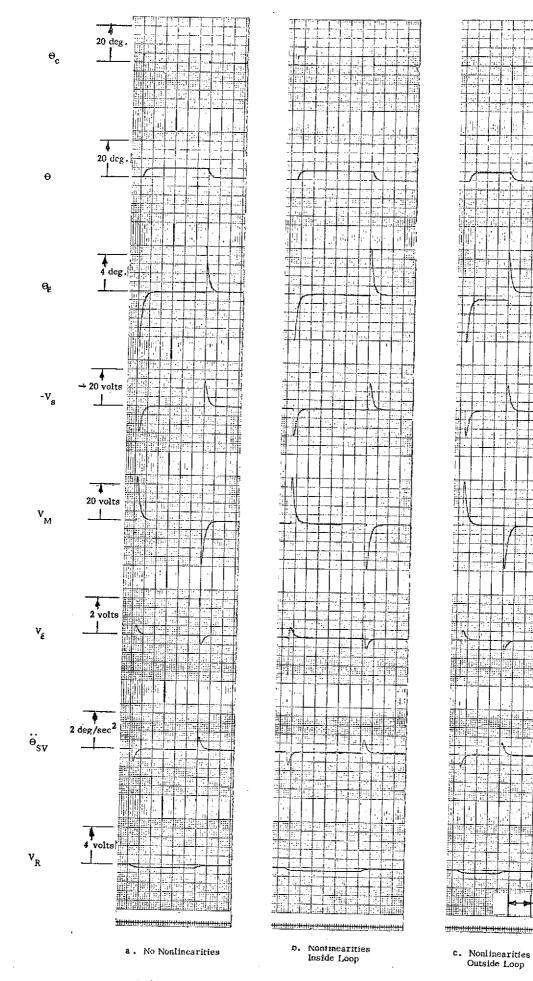

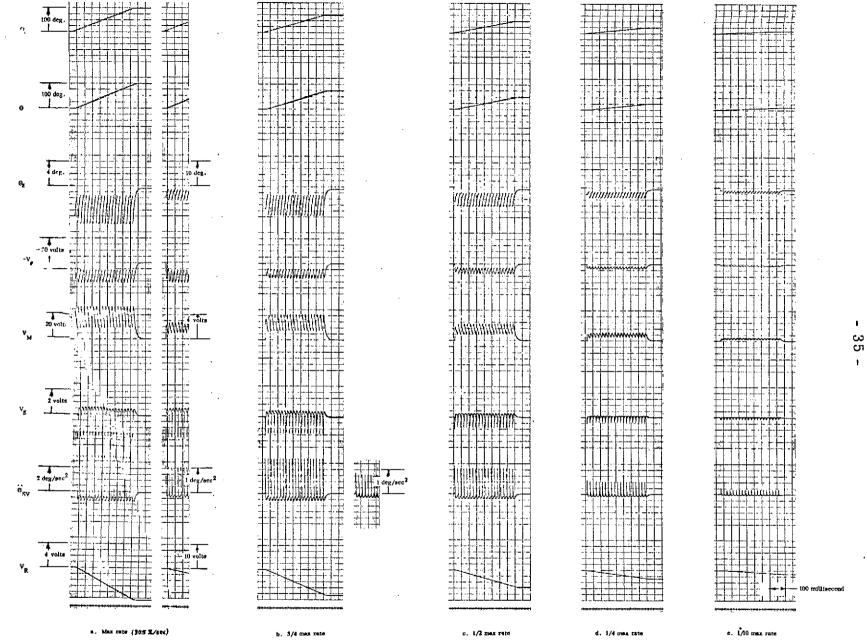

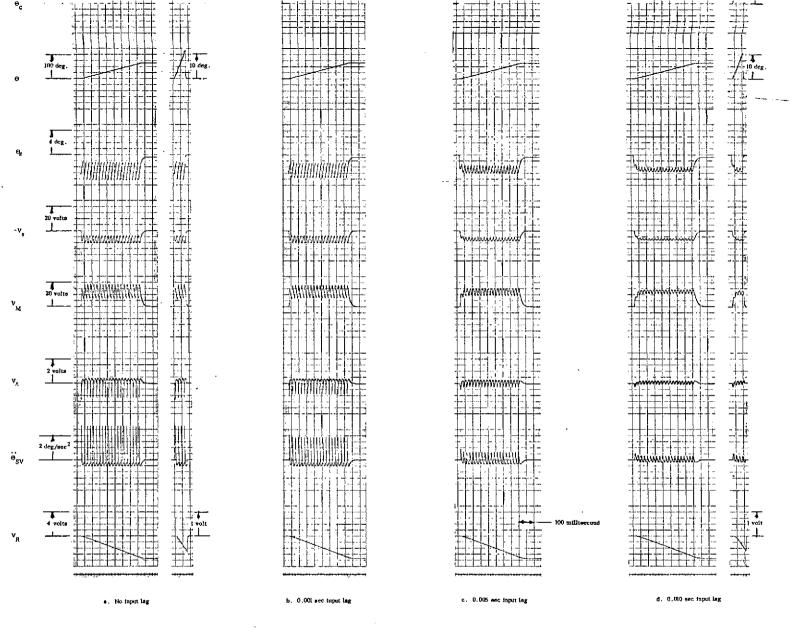

| 12     | Smooth and Staircase Ramp Commands (200%/sec)                         | 33   |

| 13     | Staircase Ramp Commands - Effects of Different<br>Ramp Rates          | 35   |

| 14     | Staircase Ramp Commands (200%/sec) Effects of<br>Input Lag Filter     | 36   |

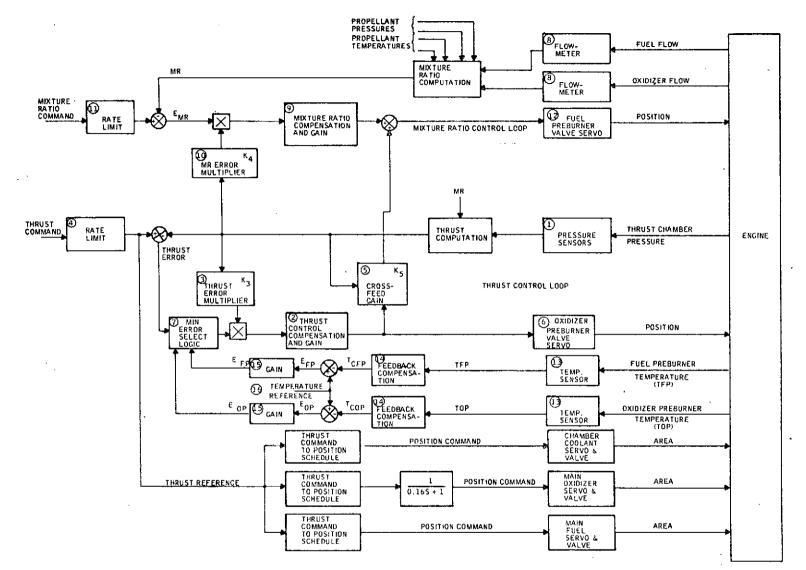

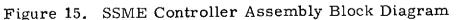

| 15     | SSME Controller Assembly Block Diagram                                | 39   |

| 16     | OPV Servoactuator Failures at MPL (Engine Sensitivity)                | 43   |

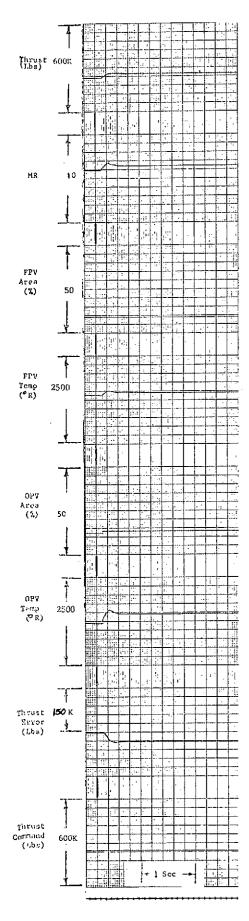

| 17     | Open-Loop OPOV Steps at MPL (Engine Sensitivity)                      | 44   |

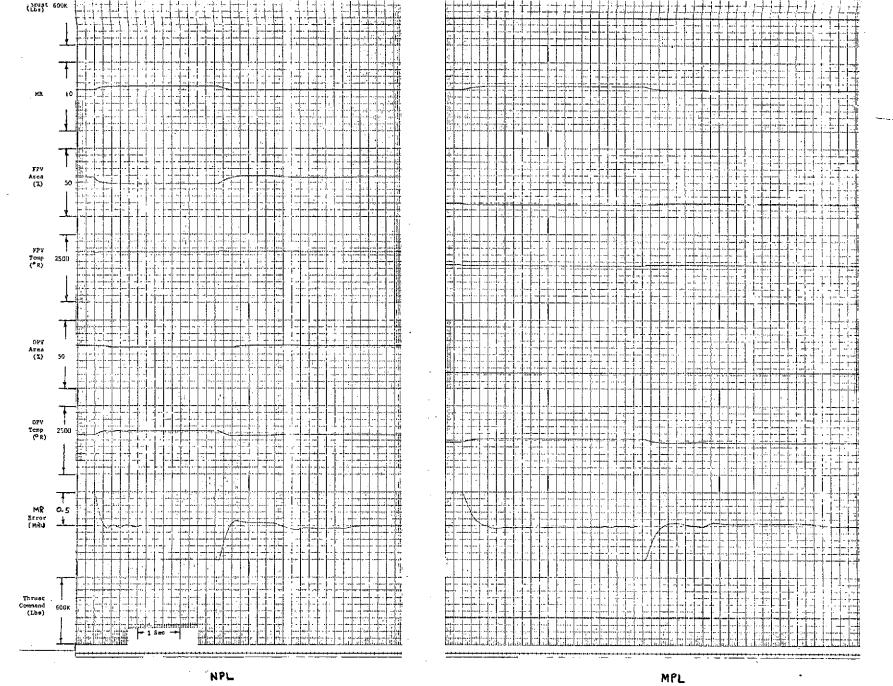

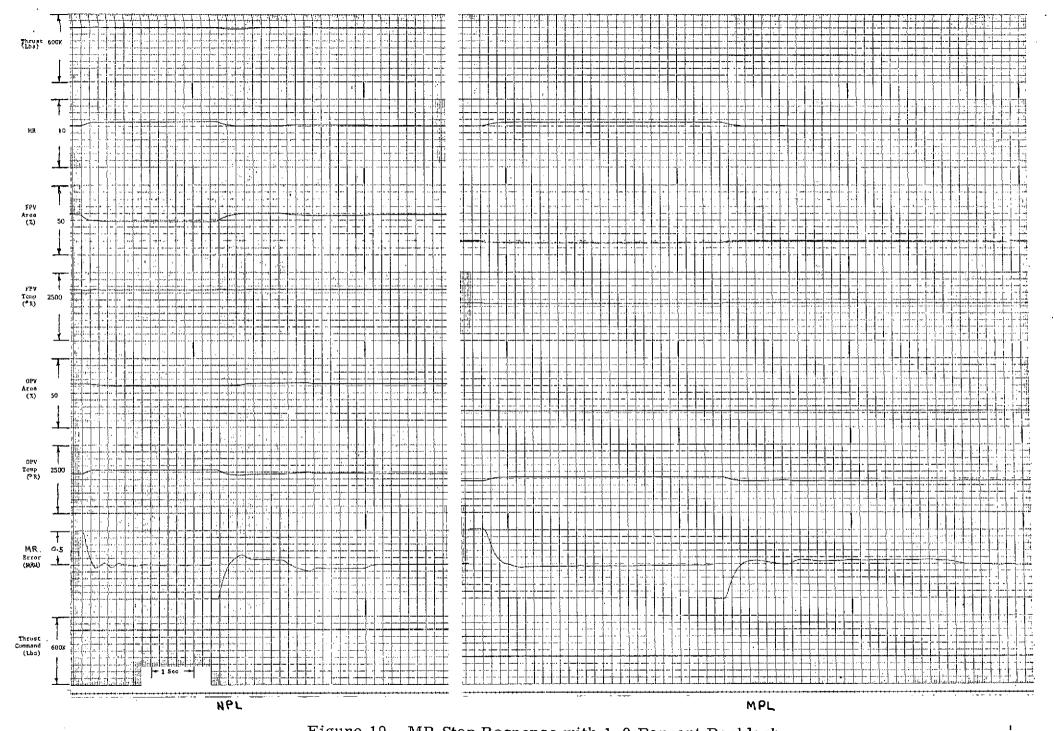

| 18     | MR Step Response with 0.5 Percent Backlash                            | 50   |

| 19     | MR Step Response with 1.0 Percent Backlash                            | 51   |

| 20     | MR Step Response with 1.0 Percent Backlash Valves<br>1/5 Nominal Gain | 52   |

.

.

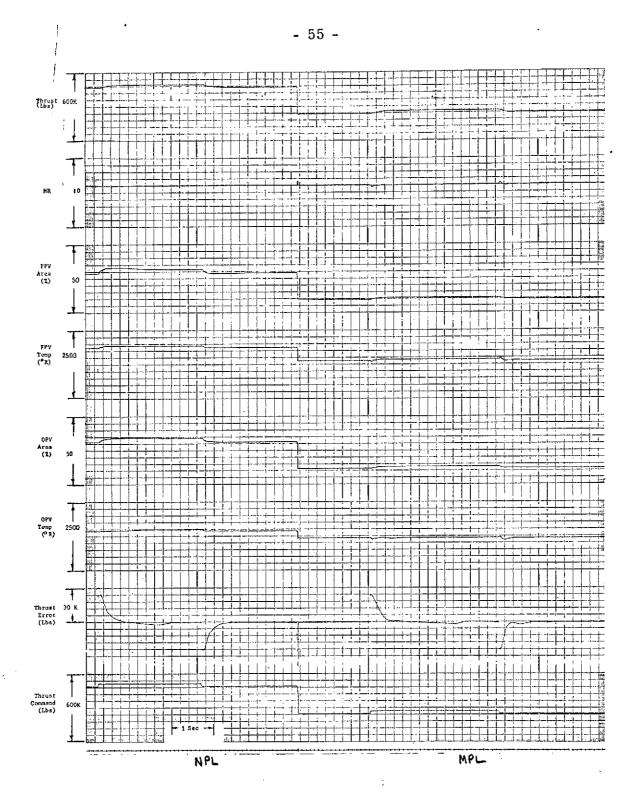

| 21 | Thrust Step Response with 1.0 Percent Backlash                                 | 54         |

|----|--------------------------------------------------------------------------------|------------|

| 22 | Thrust Step Response with 1.0 Percent Backlash<br>Valves 1/5 Nominal Gain      | 55         |

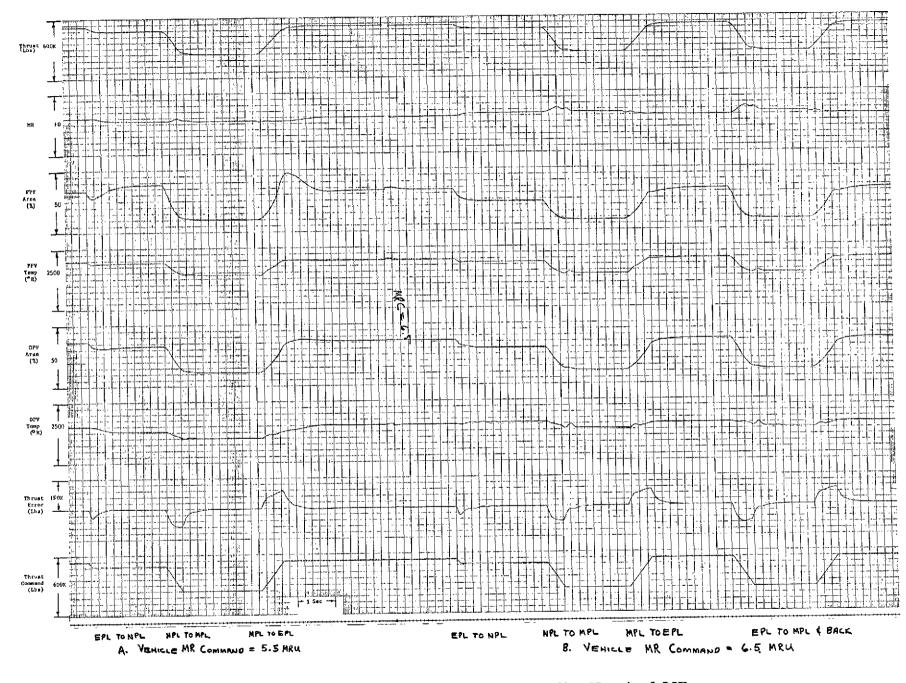

| 23 | Thrust Range Response at Off-Nominal MR Command<br>Levels                      | 57         |

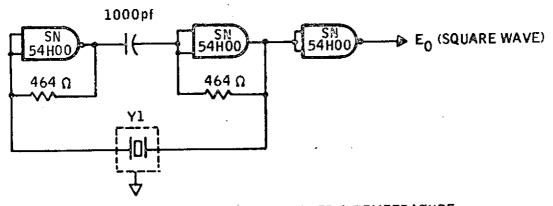

| 24 | Preferred Crystal Oscillator Circuit                                           | 64         |

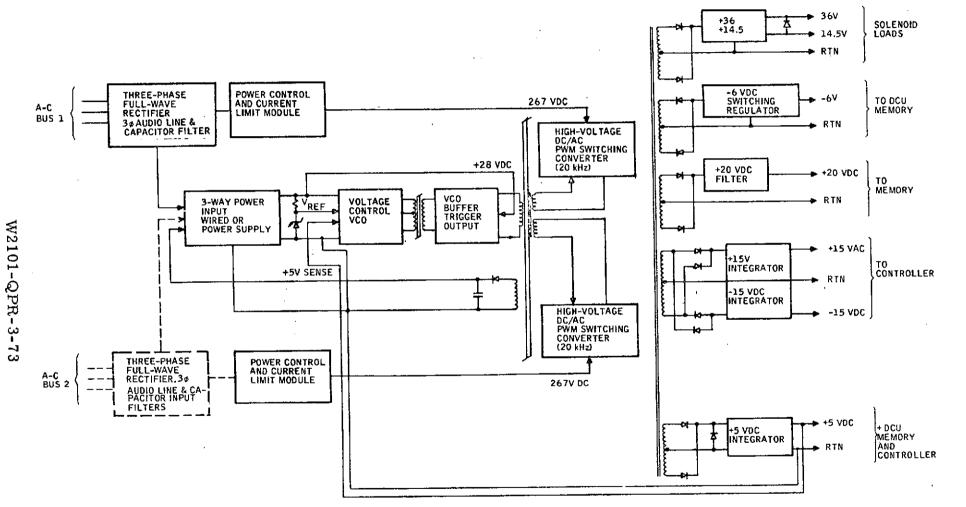

| 25 | Partial Block Diagram of Power Supply Circuitry                                | 67         |

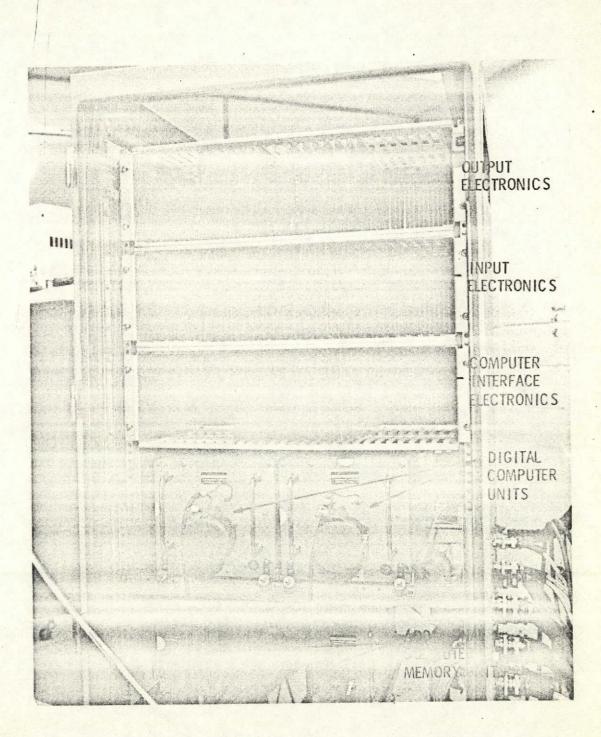

| 26 | Engineering Model Controller                                                   | <b>6</b> 9 |

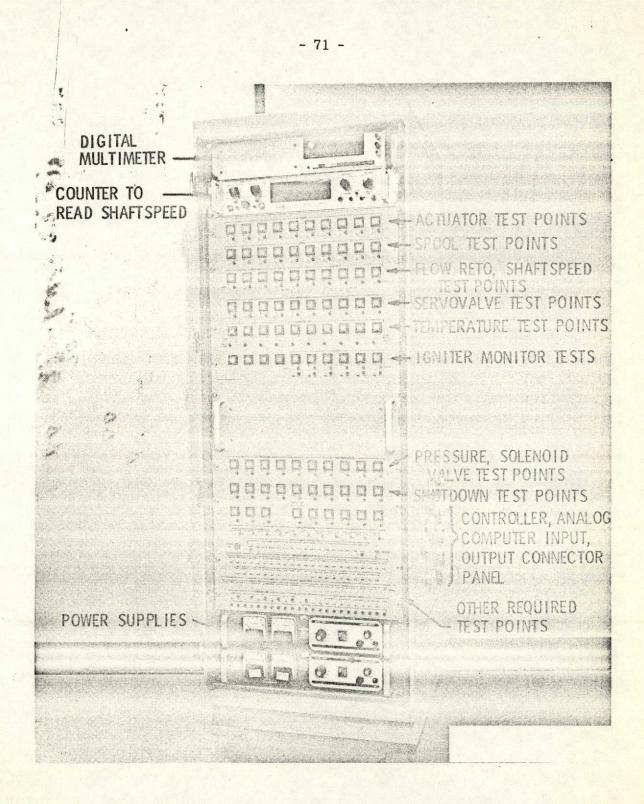

| 27 | Simulation Interface Adapter                                                   | 71         |

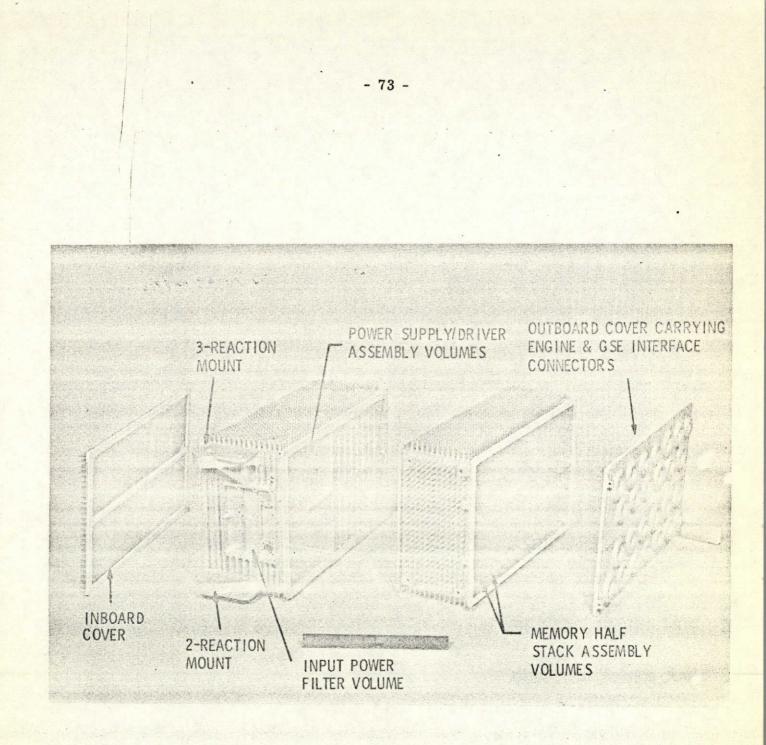

| 28 | Controller Case Inboard, Outboard and Cover<br>Assemblies                      | 73         |

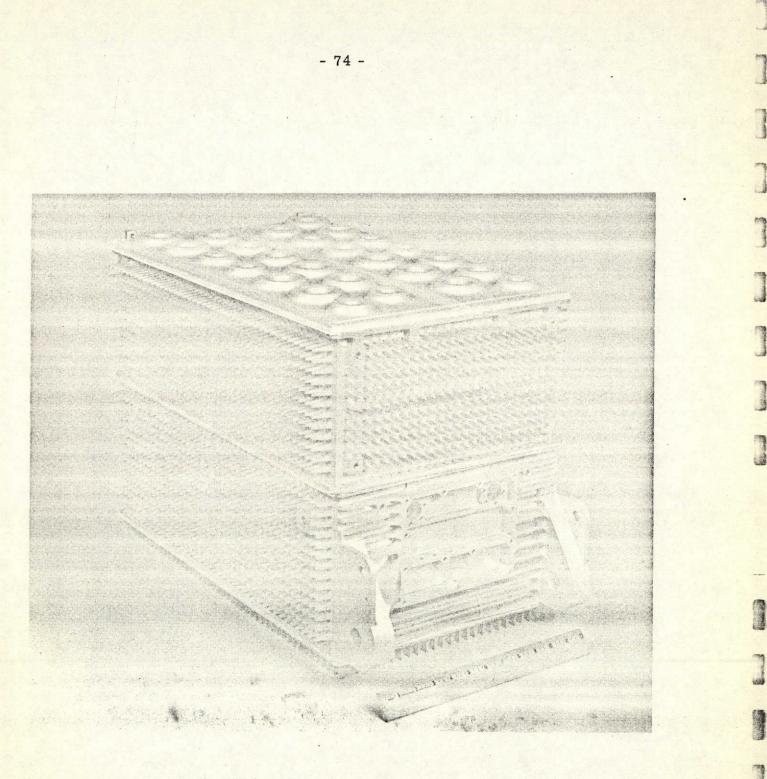

| 29 | Controller Case                                                                | 74         |

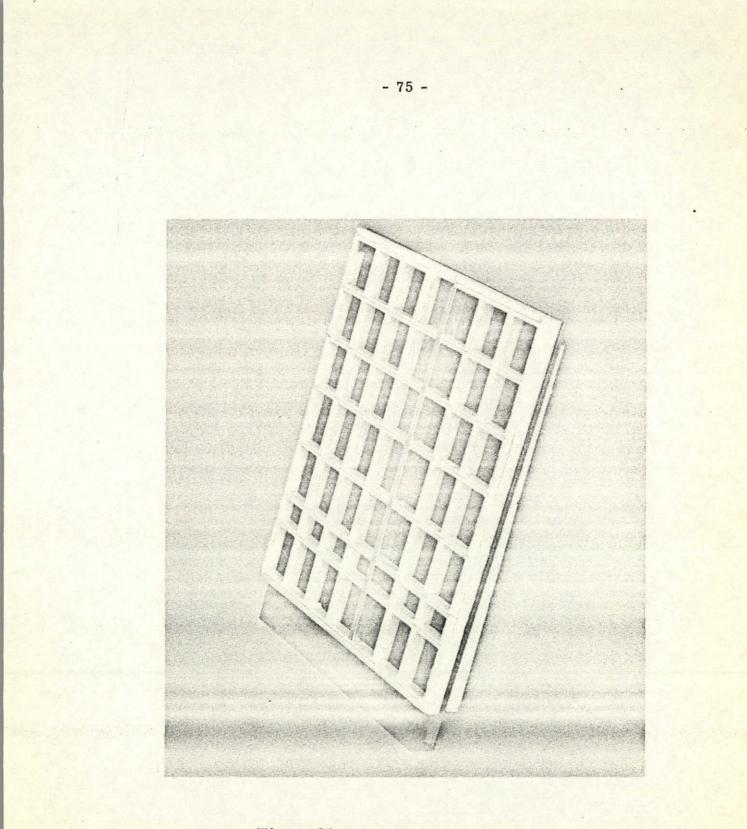

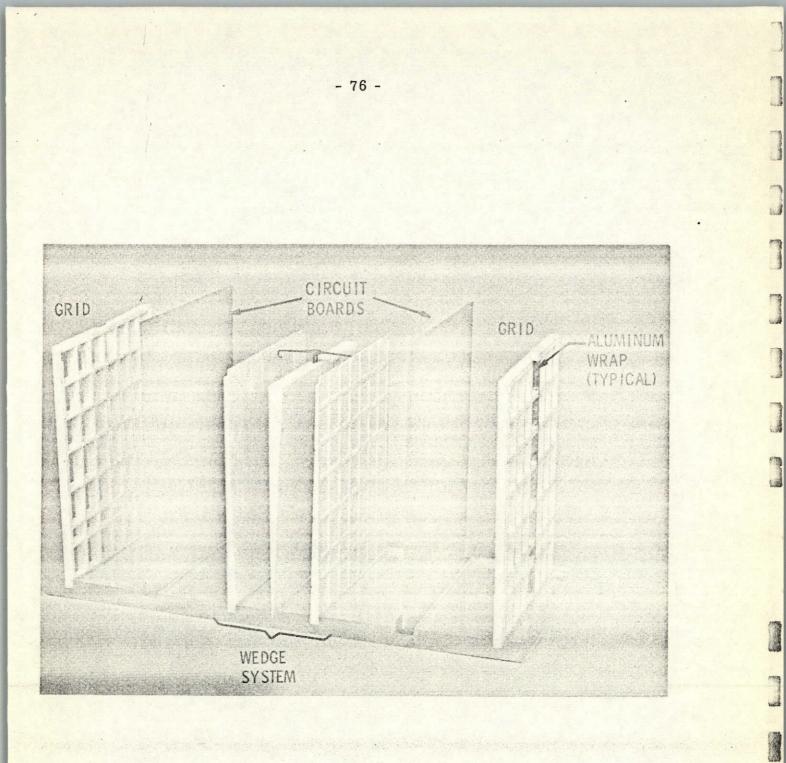

| 30 | Circuit Board and Grids                                                        | 75         |

| 31 | Circuit Boards and Foam Pack Parts for Structural<br>Model DVS Tests           | 76         |

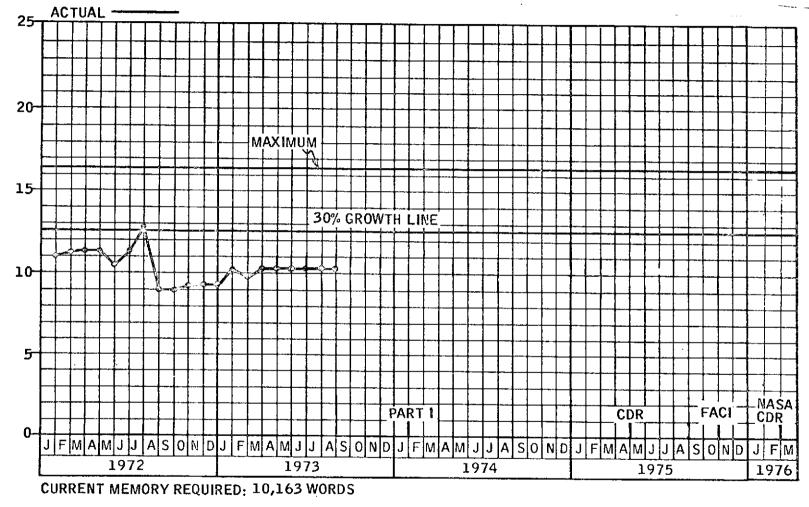

| 32 | Operational Program Memory Size Requirements                                   | 83         |

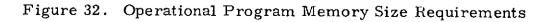

| 33 | Operational Program Process Time Requirements                                  | 84         |

| 34 | Combined Milestone Chart for Activation Schedule<br>for Delivery of PP-1 Model | 88         |

| 35 | Line-of-Balance Chart for Fabrication of PP-1 Model                            | 89         |

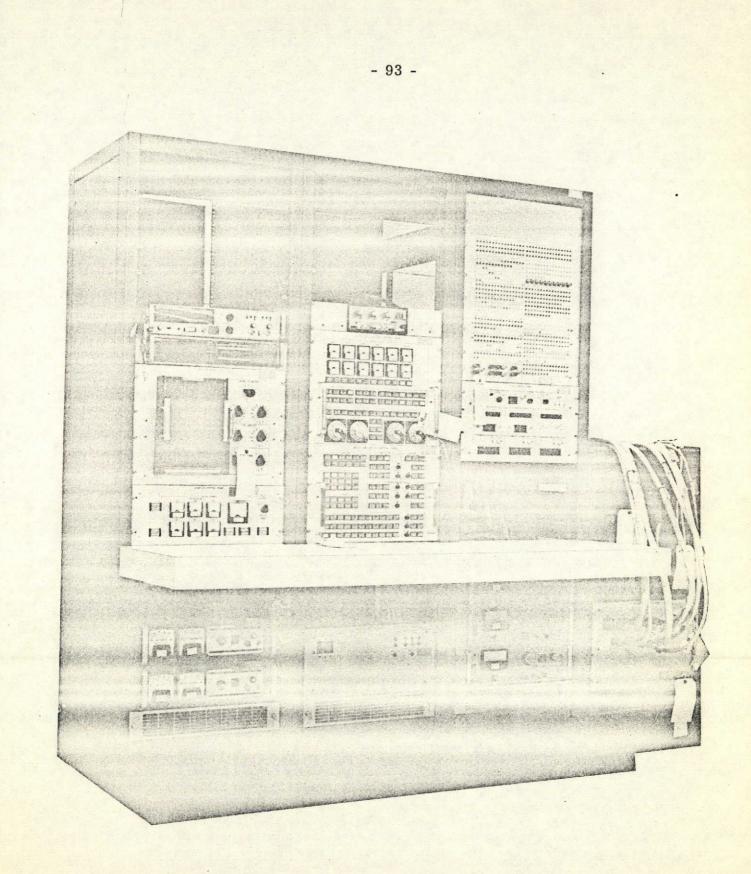

| 36 | Controller Checkout Console                                                    | 93         |

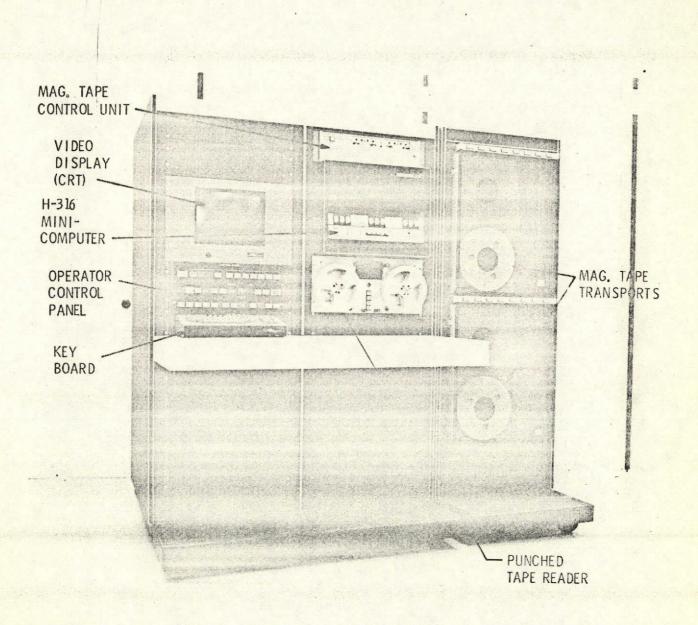

| 37 | Command and Data Simulator System                                              | 95         |

|    |                                                                                |            |

.

- vi -

,

2. 1

## SECTION I SUMMARY

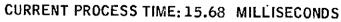

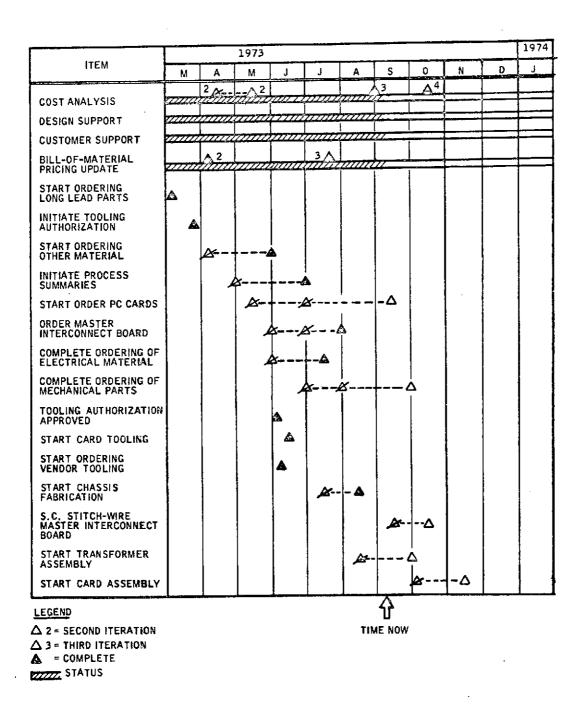

The program schedule status has improved in some areas, worsened in others, and continues to receive full attention. The program baseline is shown in Figure 1 and a summary of the actual status is shown in Figure 2. More comprehensive schedule information is given in the Logic Networks and Key Milestone Charts submitted under Rocketdyne Data Requirements 55-M-007.

System design and system analysis and simulation continue slightly behind schedule, while design verification testing has improved. Input/output circuit design has improved, but digital computer unit (DCU) and mechanical design continue to lag. Part procurement has been impacted by delays in printed-circuit board assembly drawing releases. These are the result of problems in generating suitable printed-circuit artwork for the very complex and high-density multilayer boards.

Previously reported schedule recovery efforts have proved effective and functional and integration testing of engineering model EM-1 is projected for completion by the 1 October 1973 target date. The schedule position of BT-1 has also improved, but projected late DCU deliveries present a potential problem. The schedule position of PP-1 is jeopardized by this and by the late design releases, and a vigorous schedule recovery effort is being applied here also.

The ability of the controller to operate continuously in the most severe operating modes was demonstrated by simulation runs on a thermal math model of the complete assembly. The model is being updated and new runs will be performed to predict the improvements derived from new power profiles.

Figure 1. SSME Controller Assembly Master Milestone Schedule

12

Figure 2. SSME Controller Assembly Program Schedule

Detailed models of selected subassemblies are also being prepared to determine component temperatures.

Thermal screening tests were completed on multilayer printed-wiring boards. Small cracks detected in the solder joints for transistor leads indicated the need for improvements in parts mounting, process, and workmanship techniques. A plan of action has been established to effect the required changes prior to formal Design Verification Specification (DVS) testing.

All hardware and elements of engineering model EM-1 with the exception of power supplies have been integrated and functional testing is in process. On 1 October 1973, integration with the real-time simulation will begin.

Nineteen Design Verification Test Procedures were submitted, and work was completed on 14 out of 19 design verification tests in process during the period. Twelve test reports were completed and submitted.

Design documentation for EM-1 was completed and release of PP-1 documentation was begun. The printed-wiring board component density and the number of board layers are greater than anticipated. The resulting problems in programming and mechanizing these more complex subassemblies in the automated graphics systems has resulted in delays in board documentation, and schedule recovery action is being implemented. Printed-wiring board vendors have been extending delivery promises and procurement action is being taken to improve delivery.

Parts for the structural thermal model (STM) have been fabricated and assembly has started.

Memory plated-wire equipment was certified to produce wire that meets the temperature operating range of Shuttle environments. Memory planes were produced and keeper plating accomplished with excellent yield results on the

initial lot. Six out of six planes were accepted through plating as contrasted to less than 50 percent yield of planes through keeper plating on past programs.

The GSE Preliminary Design Review (PDR) was completed.

Build of the in-house command and data simulator (C&DS) was completed and checkout and debug is being performed on the hardware and the executive software.

The first computer checkout console (CCC) was completed and is being used to support EM-1. Unit 2 to be used and shipped for BT-1 is in checkout, and unit 3 is in build.

## PRECEDING PAGE BLANK NOT FILMED

- 7 -

## SECTION II ANALYSIS AND DESIGN

#### SCHEDULE

The schedule position of the Analysis and Design activities ranges from onschedule to 8 weeks behind. The most critical items are production prototypeprinted wiring board drawing releases with a negative slack of 7 weeks for the Input/Output Assembly boards and 6 weeks for the DCU. The delays are primarily a result of problems in initial programming and mechanization of the automated graphics systems needed to produce the high-density multilayer space shuttle boards. An intensive effort is under way to accelerate releases and to recover some of the negative slack.

The power supply design is also 8 weeks behind schedule due to modifications being performed to improve the efficiency and voltage regulation. Nominally this represents an 8-week impact on Engineering Model EM-1, but this has been circumvented through the use of substitute commercial power supplies until the Space Shuttle design is available.

#### TECHNICAL PROBLEMS

#### Thermal Design

Simulation runs were performed on an updated thermal math model as noted in the prior quarterly report and were published in Thermal Study Report W2101-TSR, dated 18 June 1973. The updated model reflected revised and less severe environmental temperature conditions and improvements in the controller thermal design.

Three runs were made at different power dissipation conditions within the controller. The runs predicted that the controller may be operated continuously in either the ground checkout standby mode or the modular checkout mode, provided compartment air and well temperatures do not exceed 95°F and the engine temperatures do not exceed 100°F. The predicted internal temperature rise on circuit cards was reduced by the increased card-to-partition conductance achieved through foil-wrapped foam grids in the foam pack assemblies. The runs also predicted up to 7°F over temperature at the power supply rectifier-filter diode junctions during the propellant drop and chilldown portion of the start-preparation operating mode. The power supply design will be directed toward correcting this condition.

Subsequent to issuance of the Thermal Study Report, the controller power dissipation and power dissipation time lines were updated to reflect new data provided by Rocketdyne in SPSCN-20 to RC1007, Rev. D.

The math model was again updated to reflect the new data and simulation runs will be performed to determine the impact of these parameter changes on the controller temperatures. The runs will cover the following conditions:

• Steady-state standby mode @ 95°F ambient and 100°F engine

- Start preparation, sequences 1 through 4

- Steady-state flight-readiness test in sequence 4 mode @ 95°F ambient and 100°F engine

Significant reductions in controller internal temperatures are anticipated.

Detailed math models are also being created for the power supply/driver assembly and selected circuit boards. Simulation runs will be performed in September to investigate component temperatures.

#### System Power

The power-reporting basis was changed during the reporting period to more closely relate to the critical power dissipation conditions in the thermal analysis. This new basis includes allowances for leak detector circuits, spare on/off solenoid valves, and component variations. The basis also reflects the condition of maximum controller assembly internal power dissipation which, except for a few seconds during engine start, occurs in the start preparation phase. The start preparation phase is most critical to controller operation because it may continue for an indefinite period.

In Figure 3, the predicted input power of 693 watts is compared with the 700watt limit proposed in Rocketdyne letter ROM-CA3-305. The predicted controller internal power dissipation is also given. The proposed engine electrical power profile is shown in Figure 4.

Figure 3. Input Power Requirements - Steady-State (Start Preparation)

10 Т.

1

#### Printed Wiring Board Screening Tests

Multilayer Printed Wiring Board (PWB) thermal screening tests were completed by the Aerospace Division. These tests were performed to evaluate PWB Board integrity, solder joints on typical components, and memory plane integrity, and were conducted on typical Aero and G&APD populated boards. Test report DVSTR No. 002 dated 30 August 1973 was transmitted by Aero to G&APD. An addendum dated 31 August 1973 was prepared by G&APD and the complete test report package was presented to NASA/Rocketdyne at Florida on 5 September 1973.

The test results revealed heat cracks on some of the solder points where the transistor leads entered the joint. Based upon an analysis of the solder joints and component mountings, and upon a critique by the NASA soldering committee, a plan of action was established to prove the design and to test alternative solutions. The plan includes test boards as similar as possible to the final design, built and inspected to defined documentation. The plan also encompasses improved stress relief in component leads, workmanship standards, operator training, wave soldering techniques, parts mounting and handling techniques, and thermal overlay effects. A total of eight board assemblies representing four different configurations will be tested, with a goal of completing the tests by the start of PP-1 build.

#### Weight

Weight reporting on the controller has been changed to a monthly basis via Customer Engineering Letter (CEL 3-SSEC-236). The current weight has increased to 197.2 pounds as a result of structural and thermal improvement and power supply design maturity.

#### SYSTEM DESIGN

Significant milestones reached during this period were the initiation and completion of a significant portion of the system functional and integration testing on EM-1. Testing has progressed according to plan, and the 1 October 1973 completion date for functional testing should be met in spite of a late start.

Initial system testing on EM-1 was started 9 August 1973 using a simple functional channel of electronics consisting of the following:

- A single DCU and associated computer interface electronics

- A single channel of output electronics

- Three channels of input electronics

As of 7 September, the redundant channels were all added, so that the EM-1 unit is complete with the exception of power supplies. Laboratory power supplies are being used in the interim until the EM-1 supply is available.

Testing to date has included a satisfactory functional check of all controller hardware, with the exception of the channel B output electronics. That test will be completed by 12 September. The hardware functional testing has been done with simple program elements to facilitate testing. As hardware testing is completed on 12 September, the initial version of the Controller Acceptance Test Program will be loaded and software testing initiated.

## Current Controller Configuration

The system mechanization is basically unchanged from that previously reported. A revision of the input electronics write control logic was made, however, to remove a potential single point failure source.

#### System Design Studies

Considerable attention was given during this period to studies of failure simulations and to means of alleviating concerns resulting from these studies. Failure simulation studies regarding the actuation system determined that allowable response times to detection and correction of failures are marginal and that actuator position monitoring requirements are very stringent. Methods of achieving a satisfactory failure response time were devised for all propellant control values except the OPV. Because of an unsuitably high engine sensitivity to actuator position, it appears that the response time of the fail operate torque motor valves alone exceeds that necessary to adequately respond to OPV failures. Any solution devised by Rocketdyne for the high engine sensitivity should help this condition, however. Honeywell plans to propose changes to the RC1010 requirements in the near future to effect the failsafe performance improvements mentioned above. These proposed changes will also cover software revisions which will remove a potential single point failure resulting from a failed failsafe valve having shorted turns.

A review of the self-test mechanization was made to determine if areas exist where the software timing requirements might be eased. Two improvements were devised which save a total of about 0.3 to 0.4 millesecond. This includes deletion of power supply monitoring inflight (it is retained for ground checkout) and a revision of the power-off timer test routine. Details of these changes were provided to Rocketdyne via CEL.

#### System Specifications

A number of additional SPSCNs were received from Rocketdyne during this period. Current controller requirements are defined in the following specifications and SPSCN's:

- RC1007 Rev D plus SPSCNs 013,015,003,006,010,004,008,011,

016,017,019,023,009R,032,033,002,012

- RC1009 Rev. E plus SPSCNs 001,002,003,005,006

- RC1010 Rev D plus SPSCNs 002,010,011,001,005

- RC00001 Rev E plus Amendment 3

Honeywell system requirements specifications presently in effect are:

- HRS 24402-01 Rev. B

- HRS 24403-01 Rev. C

- DS 24405-01 Rev. F

÷

Control System Analysis and Simulation

Servoactuator Failure Mode Study --

<u>Summary</u> -- The effects of servoactuator failures at their valves and positional pick-offs were observed using the 231R/Sigma-5 engine/controller simulation. Study results allowed two generalized conclusions to be made:

- 16 -

- The analog monitor, which is concerned with failures at the servoamplifiers, servovalves, servovalve models, LVDTs, etc., adequately detects and corrects for failures in its domain under most conditions.

- 2) The actuator tracking technique of RC1010, which is concerned with failures at the servoactuators, RVDTs with their associated electronics, etc., is unsatisfactory for detecting and correcting failures at the servoactuator outputs.

<u>Conclusions and Recommendations</u> -- These conclusions and recommendations for improvement will require both hardware and software changes:

Failures in the servoactuator system which positions the OPV are critical and can be remedied only by Engine System Changes. Failures to servoactuator systems that position the other four propellant valves (FPV, MFV, MOV, CCV) can be handled adequately if the recommended changes given here are adopted.

- 2) A reduction in the error action level (EAL) of the analog monitor, currently set at 50 percent of servovalve spool displacement, is desirable if design is not compromised, but is not necessary. However, a reduction is recommended if the actuator tracking EAL is reduced to less than 5 percent. The importance of these two EALs whose ratio must not exceed 10, is that it assures that failures associated with the servovalve will be detected and corrected by the analog monitor rather than the actuator tracking software downstream, a potentially serious situation.

- 3) Rewrite Paragraph 3.2.1.1.7.1 of RC1010 so that each indicated servoactuator position error is treated and acted upon individually. If an active channel failure is confirmed, command switchover to the standby channel. If a standby channel failure is confirmed, update the appropriate flag in the data tables so that a failure in the active channel will command failsafe mode. On switchover from a confirmed active channel failure to the standby channel, delay actuator tracking sampling of it for two nominal computation cycles so that the actuator, having possibly been driven well away from its trim position by the failure, can return and reduce the tracking error to less than the 5 percent EAL, thereby avoiding a single-point failure situation.

- 4) Excessive servoactuator rate capability and high control effectiveness of the preburner propellant valves (OPV and FPV), especially at or near minimum power levels (MPL), contribute to failsafety problems. These are beyond the design responsibility of Honeywell and may well be justified as is. However, either some relief must be obtained here or the problems at MPL must be dismissed as not important based on projected engine duty cycles.

<u>Discussion</u> -- Failures can occur in two general areas of the servoactuator loops: those associated with the servovalves and their electronics, and those at the servoactuator outputs. Failure monitoring is two-stage: an analog monitor concerned with failures near the servovalves, and actuator tracking using software methods.

While there is no requirement that each monitoring stage detect and correct for failures within its immediate domain, such a requirement appears desirable from failsafety considerations. Further discussion of this point is made later in this section.

Five specific failure types were used in the study. At the servovalves, step valve displacement hangups both less and greater than the EAL of 50-percent spool displacement were used. These were applied in both directions so that positioning of the servoactuator tended to open and close the propellant valves. At the actuator outputs, RVDTs and their associated electronics were failed in three ways: minimum, maximum, and 50-percent outputs.

If item 3 of the Conclusions and Recommendations section is adopted, failures in the servoactuator loops for the FPV, MFV, MOV and CCV propellant valves can be safely handled. It will take something like the modification in Item 4 to safely handle failures in the OPV actuator loop.

OPV actuator loop failures cause two kinds of problems. A failure which tends to close the OPV at MPL depresses the main chamber pressure to seriously low levels. Nominally at 50 percent this critical engine parameter can trigger engine shutdown if it reaches 40 percent. Similarly, at EPL where the main chamber pressure is nominally 109 percent, a failure tending to open the OPV can drive this pressure up to 114 percent and cause shutdown. Perhaps these failures can be tolerated if the shutdown limits are expanded. But a more

serious problem occurs when a failure tends to open the OPV while at MPL. Oxidizer propellant is ported into the preburner chamber where a fuel-rich mixture exists. Before the failure is detected, verified, and switched out, the preburner temperature is beyond its limit. One of two things can happen: either a shutdown occurs (the temperature is a critical engine-limit parameter), or temperature override is selected (under conditions not intended for it) in the controller and both preburner valves are closed, the temperature error closing the OPV and the crossfeed term closing the FPV. Of course, until the faulty channel is removed, neither of these can occur. In the meantime the computer continues to compute engine thrust and mixture ratio but the validity of these calculations is questionable. The best that can happen here is a shutdown, since the possibility of a flight hazard exists.

A satisfactory solution to handling OPV actuator loop failures may cause other problems. Lowering the actuator tracking EAL looks promising until the matter of an increased ratio of EALs is examined closely. Suppose the actuator tracking EAL is lowered to 2.5 percent, raising the ratio to 20, twice the recommended value. If a failure at the servovalve now occurs, of a kind that is not immediately detected by the analog monitor, the actuator tracking software will have to respond. But the failure will cause both RVDTs to display identical values. When the computed actuator position is compared with these, both look like failures and a single-point failure situation is apparent.

The objective here is to reduce the amount of time it takes for a failed channel to be detected, verified, and switched out. This can be demonstrated by removing all solenoid and sampling delays. Of course, this is no solution, but it appears that an attempt to minimize the time to get rid of a failed channel is not going to solve the problem. An alternative suggests itself here. As long as there is little that can be done to speed up switching out a failed channel, try instead to minimize the disturbance the failure causes. This can be done by reducing the rate capability of the servoactuators.

Table 1 contains the maximum servoactuator rates required to handle legitimate controller commands. But the major propellant value actuators (MFV and MOV) are specified at maximum rates of 370 percent per second and the minor propellant value actuators (FPV, OPV, CCV) and 305 percent per second (see Table 1, RC1008).

| Actuator | Peak Actuator Rates Commanded |                      |  |  |

|----------|-------------------------------|----------------------|--|--|

| netutor  | Mainstage                     | Startup and Shutdown |  |  |

| FPV      | 40                            | 150                  |  |  |

| OPV      | 40                            | 150                  |  |  |

| CCV      | 100                           | 100                  |  |  |

| MFV      | 60                            | 150                  |  |  |

| MOV      | 55                            | 100                  |  |  |

## Table 1. Maximum Controller-Commanded Actuator Rates

This excessive rate capability adds to the severity of the engine disturbance during failures, and reduced rate capability for at least the preburner valve actuators should be recommended. There may be good reasons for not reducing rates via mechanical or hydraulic changes to the servoactuators, but the job could be done electronically by limiting the servoamplifier outputs so that any command, legitimate or illegitimate (failures), could not command rates exceeding 150 percent per second. Such limiting yould restrict the violence of all RVDT failures plus those failures near the servovalves except mechanical failures to the servovalves themselves. This last unchecked

failure is undesirable but nothing short of reduced OPV effectiveness will eliminate it.

The fact that the most severe failure problems occur at low engine thrust levels hints at a way to rationalize them away. Engine duty cycles for typical missions would probably show the engine at low thrust levels for a low percentage of the time. MPL then becomes a very brief transitory condition on the way to either startup or shutdown.

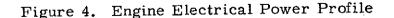

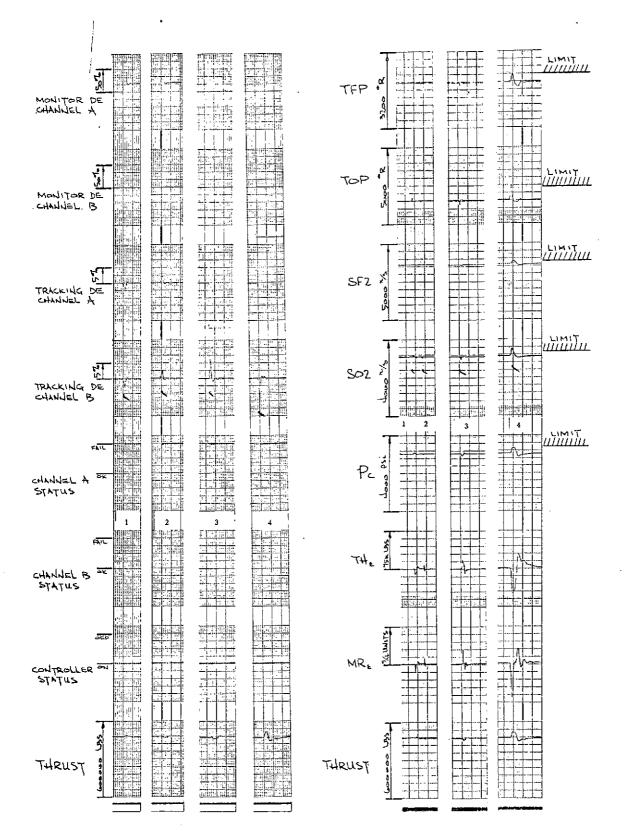

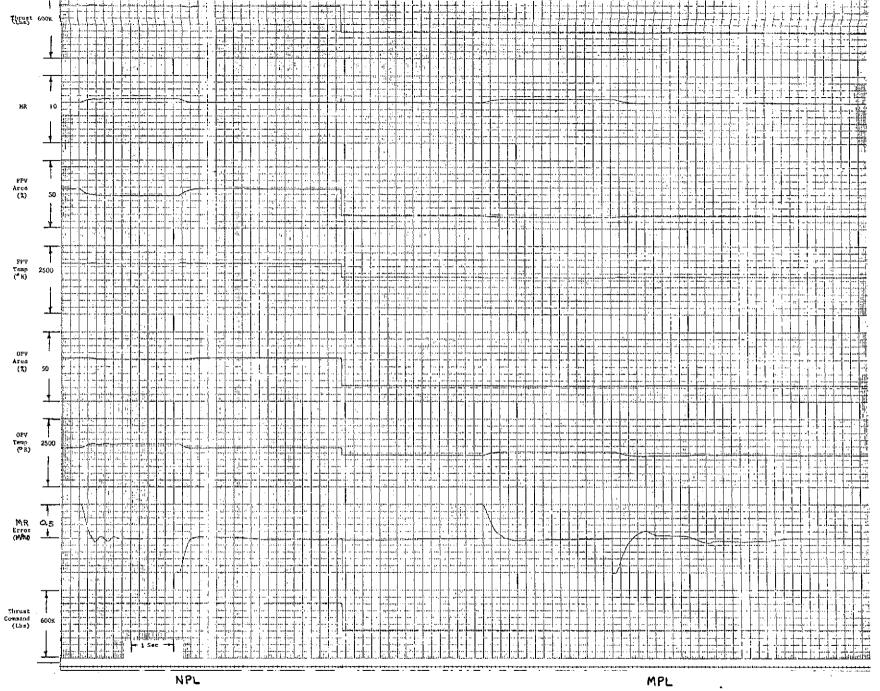

<u>Results</u> -- The time histories contained in Figures 5 through 9 are separated into two sets. Each strip in a set has a number which identifies the particular failure type. These failure types are:

- Servovalve step hangup, less than the EAL of the analog monitor, positions actuator so that propellant valve tends to open

- 2) Same as 1 except that propellant valve tends to close

- 3) RVDT output goes to maximum value

- 4) RVDT output goes to minimum value

The eight parameters in the set at the left, starting at the top of the Figures are:

1 and 2 - The differential errors (DE) the analog monitor sees in Channels A and B. This is the differential sum of the servovalve and its model. When the sum equals or exceeds the monitor EAL, currently set at 50 percent of spool travel,

Figure 5. OPV Servoactuator Failures at NPL

| Kenditor DE                   |  | TF        |  |

|-------------------------------|--|-----------|--|

| HONITOR DE<br>CHANNEL B.      |  | το        |  |

| Tercking de<br>Channel 4      |  | SF2       |  |

| TRACKING DE<br>CHANNEL B      |  | S S       |  |

| FAIL<br>CULANDUEL A<br>STATUS |  | P.        |  |

| caluduleL B                   |  | τι,       |  |

| CONTROLLER<br>STATUS          |  | MR.       |  |

| THRUST                        |  | 1 4 4 1 1 |  |

Figure 6. OPV Servoactuator Failures at MPL

- 23 -

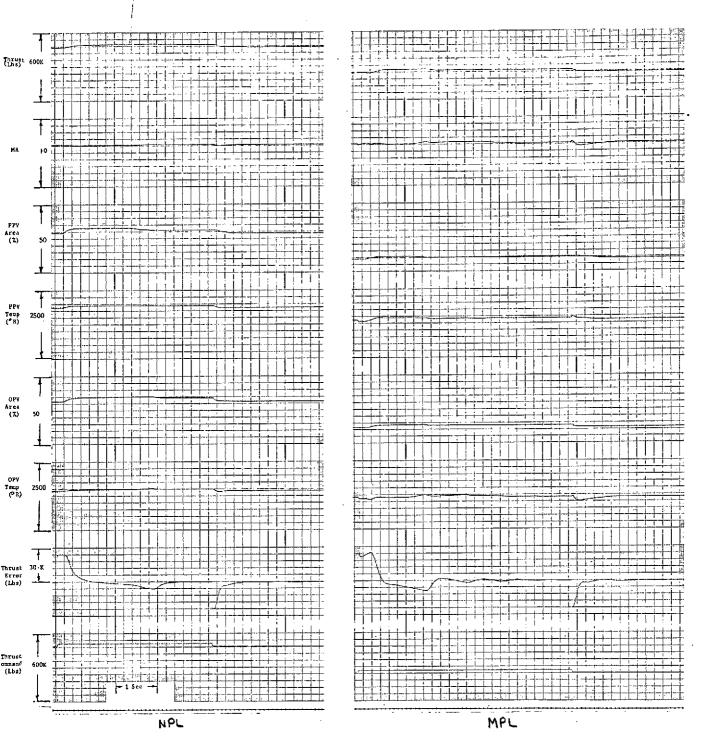

Figure 7. FPV Servoactuator Failures at NPL

2

Figure 8. FPV Servoactuator Failures at MPL

| MONITOR DE<br>CHAUJEL 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TFP    | 3306 °   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|--|

| Moditor DE .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Тар    |          |  |

| TRACKING DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SF2    | 2000 M/S |  |

| TRACKING DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 502    |          |  |

| CALANINEL A<br>STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P.     |          |  |

| THE CHANNEL B. CHANNEL | THE    |          |  |

| CONTROLLER<br>STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MR     |          |  |

| CONTROLLER<br>STATUS<br>THRUST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | THRUST |          |  |

,

W2101-QPR-3-73

- 26 -

for at least two milliseconds, the analog monitor sends an interrupt to the computer.

3 and 4 - The differential errors the computer generates by comparing the computed actuator position with each RVDT displayed position. When either of these equals or exceeds the tracking EAL, currently set 5 percent equivalent actuator displacement, the computer enters 200-Hz cycling to test the indicated failure.

- 5 and 6 Discretes that indicate completion of switchout of faulty A channel, or recognizing (or switchout of) faulty B channel.

- A discrete that indicates the completion of switchout of a second failure and putting engine into pneumatic shutdown.

8 - Engine thrust.

The parameters in the set at the right, starting at the top of the Figures, are:

- 1) Preburner temperature, "fuel-side" of engine

- 2) Preburner temperature, "oxidizer-side" of engine

- 3) Shaft speed, high-pressure fuel turbopump

- 4) Shaft speed, high-pressure oxidizer turbopump

- 5) Main combustion chamber pressure

- 6) System thrust error

- 7) System mixture ration error

8) Engine thrust

0

The first five items in the second set are engine-limit-control shutdown parameters. It is not known what limit level these parameters will be compared with (see Table VI, RC1007 for range of values), but servoactuator failures cause transient disturbances to these parameters. Whatever the limit settings, failsafety mode operation must be quick enough to avoid excessive transients in them.

- 28 -

The timer for the time histories is at the lower edge of the strips. Each tick is 20 milliseconds.

The selection of propellant valve axes and engine power levels for the servoactuator failures given in Figures 5 through 9 was dictated by two considerations. These were, first, to choose conditions where failures are most likely to cause problems and, second, to illustrate graphically how the servoactuator failsafety system operates. Using the first of these eliminated the main fuel (MFV) and coolant control (CCV) propellant valves at all engine thrust levels and the main oxidizer valve (MOV) at high engine thrust. The failsafety system operated well in removing failures in these circumstances while keeping engine transients to minor or insignificant levels.

A review of Figures 5 through 9 demonstrates that while engine transients are significant, failures in the FPV and MOV axes are corrected satisfactorily. It is in Figures 5 and 6, which deal with failures in the OPV axis, that fail-safety problems persist. Figure 5, with the engine at 100 percent of thrust, seems to indicate that failures are adequately handled, but this is a bit deceptive. Failures numbered 5 and 8, which tend to open the OPV, generate transients which put some of the critical engine shutdown parameters close to triggering levels. With the engine at EPL (109 percent, not included in the Figures), a shutdown is even more likely. In a similar way, failures 2 and 4, which tend to close the OPV, reduce main chamber pressure ( $P_c$ ) close to shutdown level (see Figure 6). It is not known at what levels the engine-limit shutdown parameters will be set, but Table IV, RC1007, contains a range

of values for each. The limit levels shown on the extreme right borders of Figures 5 and 6 are as follows: TFP is  $2250^{\circ}$ R, TOP is  $2400^{\circ}$ R, SF2 is 4000 rpm, SO2 is 35000 rpm, and P<sub>c</sub> is 40 percent and 112 percent.

A more difficult problem of handling a failure is illustrated in Figure 6. At low engine thrust levels, failures that then open the OPV (1 and 4) cannot be switched out quickly enough to avoid a shutdown, either through an apparent single-point failure or triggering an engine-limit parameter. The response labeled 1A demonstrates what quickness can do. It is the repeat of the response labeled 1, except that the 12-millisecond solenoid switching time was removed. This small saving of time, (which, of course, is no solution to the problem), is sufficient to permit both switchout of the failed channel and control recovery from the disturbance.

The RVDT failure labeled 4 (see Figure 6) does not generate differential errors in the analog monitor so the actuator tracking software will respond. The accumulated delays here are much more severe, i.e., no priority interrupt, failure verification is required, and the solenoid switchout time. This particular failure is so rapid and disruptive that a basic change in the sensitivity of the OPV must be considered. Such a change is beyond Honeywell design responsibility.

The importance of the ratio of EALs has been emphasized previously. Failures labeled 1 and 2 in all the Figures can be used to make this point. For example, in Figure 5 it is clear that the analog monitor is responsible for the detection and switchout of the failure. (Note that the monitor DE reaches its EAL of 50 percent spool travel before either of the tracking DEs reach their EAL of 5 percent actuator displacement.) But this type of failure affects the actuator output also, and both A and B actuator tracking differential errors reach approximately 2.5 percent, or half, of their EAL. Suppose that it is possible to lower the tracking EAL to 2.5 percent, a beneficial change. If this is done, then failure types like 1 and 2 could slip by the analog monitor (that is, the

tracking EAL will be reached before the analog monitor EAL) and be interpreted by the system as a single-point failure. To avoid this, any reduction in the actuator tracking EAL must be accomplished by a reduction in the analog monitor EAL. (The converse of this is not true.) The conclusion to be drawn here is that the ratio of EALs must be maintained at a value not to exceed the current value of 10.

### Servo Actuator Analog Study --

<u>Summary</u> -- A brief analog study was performed on the servo actuators used to position the SSME propellant valves. The purpose of the study was to examine the effects of various inputs (step and ramp commands) on the servo valve monitor and nonlinearities such as stiction and backlash.

The servo actuator performed well with no nuisance tripping of the servo valve monitor. The effects of the system on the complete engine and controller system is beyond the scope of the study.

<u>Background</u> -- Figure 10 represents the block diagram used to simulate the servo actuator system on a PACE 231R analog computer (No. C13). The broken line shows the modification necessary to obtain computer runs with the nonlinearities (stiction and backlash) inside the servo/actuator loop. It is currently believed that the nonlinearities lie outside the loop. Comparisons of the two nonlinearity configurations, along with runs with no nonlinearities, can be seen in both Figures 11 and 12.

Only the fuel preburner oxidizer valve was investigated in this study which, from previous analysis, appears to be the most sensitive servo actuator as far as tripping the servovalve monitor is concerned.

<u>Results</u> -- Figure 11 shows results of  $\pm 5$ -degree step commands ( $\pm 6.25\%$ ). This input is unrealistically large because even at maximum commands

Figure 10. Servoactuator Block Diagram

Figure 11. Step Commands (+5 degrees)

W2101-QPR-3-73

100 millisecond

- 32 ·

|                 | a . No Nonlinearities  | b. Nonlineartices<br>Inside Loop<br>SMDOTH RAMP COMMANDS | c, Nonhnearnies<br>Curside Loup | d. No Nonlinearities | c. Noulincaritics<br>Inside Loop<br>STAIRCASE RAMP COMMANDS | I. Nonlinearities<br>Outside Loop | и                |

|-----------------|------------------------|----------------------------------------------------------|---------------------------------|----------------------|-------------------------------------------------------------|-----------------------------------|------------------|

| γ <sub>R</sub>  |                        |                                                          |                                 |                      |                                                             |                                   | 100 millisecond  |

| e<br>esv        | 2 deg/sec <sup>2</sup> |                                                          |                                 |                      |                                                             |                                   |                  |

| v <sub>e</sub>  |                        |                                                          |                                 |                      |                                                             |                                   |                  |

| У.<br>М.        |                        |                                                          |                                 |                      |                                                             |                                   | ו<br>ט<br>ט<br>ט |

| -v <sub>e</sub> | -20 volts +            |                                                          |                                 |                      |                                                             |                                   |                  |

| ę               |                        |                                                          |                                 |                      |                                                             |                                   |                  |

| 0               | 100 deg.               |                                                          |                                 |                      |                                                             |                                   |                  |

| e<br>c          | 100 deg.               |                                                          |                                 |                      |                                                             |                                   |                  |

Figure 12. Smooth and Staircase Ramp Commands (200%/sec)

W2101-QPR-3-73

- 33 -

(305%/sec) the digital ramp, or "staircase", command will be comprised of steps no larger than 4.88 deg. Maximum input rates of 200%/sec is more realistic. The only significant effect of the nonlinearities is the hangoff in Output position error  $\theta_{\epsilon}$  (due to the linkage hysteresis) amounting to 0.3 to 0.4 degrees. This hangoff is not seen by the servovalve monitor, but could adversely affect the system performance. The peak voltage error at the comparator  $V_{\epsilon}$  is only 2 volts and 6.25 volts are required to trip the monitor (for 2 ms).

Figure 12 shows more comparisons of runs with no nonlinearities, inside and outside the servo loop. The same conclusions can be made as in Figure 11 concerning hangoff position error ( $\theta_{\epsilon}$ ) and the servovalve comparator voltage error ( $V_{\epsilon}$ ). Also compared in the figure is the staircase input (expected from the digital computer) against the nonrealistic smooth ramp input. Although the staircase commands do not present any problems in the servovalve monitor, they may cause problems in total system performance.

Figure 13 shows the effects of various ramp rates for the staircase commands on the servo/actuator and monitor. As expected, the smaller the ramp rate, the smaller the measured effects.

Figure 14 shows what happens when the input command is lagged. This tends to smooth out the steps of the staircase input but at the expense of slowing down the system if and when quick response is required.

This study did not consider engine performance since the engine and controller are not included in the simulation.

# Engine/Controller Frequency Response per RL00001 Revision E --

<u>Summary</u> -- Stability margins for the RL00001 Revision E engine/ controller were determined at selected points in the operational envelope,

W2101-QPR-3-73

Figure 13. Staircase Ramp Commands - Effects of Different Ramp Rates

1

1

Figure 14. Staircase Ramp Commands (200%/sec) Effects of Input Lag Filter i

36 -

using the digital KNOVOL program. Minimum gain margins thus obtained are 10db for the thrust loop and 18db for the MR loop. Phase margins exceed 60 deg for both loops. These values are well within the design goals of 8db gain margin and 45 deg phase margin. The gain and phase margins obtained from this study are summarized in Table 2.

| Control<br>Loop | Power<br>Setting | Nominal<br>MR | Forcing Function                                 | Gain<br>Margin<br>(db) | Phase<br>Margin<br>(deg) |

|-----------------|------------------|---------------|--------------------------------------------------|------------------------|--------------------------|

| Thrust          | NPL              | 6,0           | 2%(A/A)OPV Decrease                              | 14                     | 90                       |

| Thrust          | NPL              | 6.0           | 2%(A/A)OPV Increase                              | 12                     | 84                       |

| Thrust          | MPL              | 6.0           | 2%(A/A)OPV Decrease                              | 19                     | 90                       |

| Thrust          | MPL              | 6.0           | $2\%(A/\overline{A})_{OPV}$ Increase             | 11                     | 82                       |

| MR              | NPL              | 6.0           | $2\%(A/\overline{A})_{FPV}$ Decrease             | 21                     | 90                       |

| MR              | NPL              | 6.0           | 2%(A/A) <sub>FPV</sub> increase                  | 23                     | 85                       |

| MR              | MPL              | 6,0           | 2%(A/A) <sub>FPV</sub> Decrease                  | 25                     | 60                       |

| MR              | MPL              | 6.0           | 2%(A/A)FPV Increase                              | 28                     | 80                       |

| Thrust          | MPL              | 6.5           | 0.5% $(X/\overline{X})_{OPV}$ Increase           | 12                     | 60                       |

| MR              | MPL              | 6,5           | 1%(X/ <del>X</del> ) <sub>FPV</sub> Increase     | 21                     | 85                       |

| Thrust          | NPL              | 6,5           | 1%(X/X)OPV Decrease                              | 10                     | 60                       |

| MR              | NPL              | 6.5           | $1\%(X/\overline{X})_{FPV}$ Decrease             | 18                     | 90                       |

| Thrust          | MPL              | 5, 5          | 0.5%(X/ $\overline{X}$ ) <sub>OPV</sub> Increase | 15                     | 65                       |

| MR              | MPL              | 5.5           | 1%(X/ <del>x</del> ) <sub>FPV</sub> Decrease     | 28                     | 90                       |

| Thrust          | NPL              | 5.5           | $1\%(X/\overline{X})_{OPV}$ Decrease             | 13                     | 85                       |

| MR              | NPL              | 5, 5          | $2\%(X/\overline{X})_{FPV}$ Decrease             | 25                     | 90                       |

Table 2. Gain and Phase Margins

<u>Discussion</u> -- Two simulations were used in obtaining the above information. The data at MR = 6.0 was obtained from the PACE 231R/Sigma 5 simulation prior to switchover to the verification simulation on the PACE 700/Sigma 5 equipment. Data at MRs of 5.5 and 6.5 was then obtained from the latter equipment.

It should be noted that the two sets of data were obtained from the simulations using different forcing functions. The 231R (MR = 6) data has value area steps as the input function while the 700 (MR = 5.5, 6.5) data has value position steps as the input function. The above difference results in the open-loop gain of the two sets of data being different by the displacement to area gain of the propellant values.

The controller configuration used in these studies is shown in Figure 15 and Table 3.

<u>Frequency Responses for MR = 6.0 (231R Data</u>) -- An oxidizer preburner valve area step was used to force the thrust loop, and the fuel preburner valve area step forced the MR loop. The loop not being forced was closed so that the responses were of the augmented engine. Gain and phase margins are obtained by adding the appropriate controller and engine response plots and observing the phase angle at the point of unit (0db) loop gain, for the phase margin, and noting the loop gain at the point where the total phase angle is 180 deg.

<u>Frequency Responses at MR = 6.5 and 5.5 (PACE 700 Data)</u> -- This data was obtained in a similar manner to the 231R data except displacement rather than area steps were used. It should be noted that the phase angle on these responses is in error by 180 deg due to a programming discrepancy.

W2101-QPR-3-73

• 39

0

# Table 3. Key to Figure 15, SSME Controller Assembly Block Diagram

| Control Loop                                                                                                | Thrust Control                                                                                                                                                                                                                    | Mixture Ratio<br>Control                                                                                                | Temperature Limit<br>Control                                                                            |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Sensor:<br>Type<br>Response<br>Feedback Compensation                                                        | 1<br>Pressure<br>> 600 rad/sec<br>None                                                                                                                                                                                            | 8<br>Turbine flowmeters<br>> 200 rad/sec first order<br>None                                                            | $(13)$ Temperature resistance bulb $0, 5 \text{ sec first order}$ $(14)  \frac{(S/1.66+1)}{(S/12.5+1)}$ |

| Forward Loop Compensation<br>and NPL Gain<br>Sample Rate<br>Output Range                                    | 2 0.45 x 10 <sup>-3</sup> (S/15 + 1) ≸ Stroke<br>50 samples/sec                                                                                                                                                                   | 9 -30 (S/33.3 + 1) \$ stroke<br>MR unit-sec<br>50 samples/sec                                                           | Product of boxes 2 and 15:<br>$E'/E = 105(1 + ABS(E/100)) lb/^{\circ}R$<br>50 samples/sec               |

| Gain Coefficient<br>At NPL and Above<br>At MPL and Below<br>Linear with Thrust Level<br>Between MPL and NPL | (3) К <sub>3</sub><br>1,0<br>0.6                                                                                                                                                                                                  | 10 K <sub>4</sub><br>1.0<br>0.25                                                                                        | None                                                                                                    |

| Control Limits<br>Range<br>Rate                                                                             | 480 lb/msec maximum                                                                                                                                                                                                               | (1)<br>6.0 at EPL<br>5.5 - 6.5 NPL to MPL<br>1 MRU/sec maximum                                                          | 16 Nominal reference temperatures:<br>1895°R - FPV<br>2040°R - OPV                                      |

| Crossfeed Gain<br>At NPL and Above<br>At MPL and Below<br>Linear with Thrust Level<br>Between MPL and NPL   | 5         K5           1.1         \$ Stroke FPV           1.32         \$ Stroke OPV                                                                                                                                             | None                                                                                                                    | None                                                                                                    |

| Valve Position Control<br>Response                                                                          | $ \begin{array}{c} 6 \\ \hline 0 \\ \text{Xidizer preburner} \\ \text{Oxidizer valve} \\ \hline \\ \hline \frac{75^2}{\text{S}^2 + 75\text{S} + 75^2} & \underbrace{\$ \text{Stroke}} \\ \hline \$ \text{Stroke} \\ \end{array} $ | 12 Fuel preburner oxidizer<br>valve<br>$\frac{75^2}{S^2 + 75S + 75^2} \xrightarrow{\text{\# Stroke}}{\text{\# Stroke}}$ | None                                                                                                    |

| Error Select Logic ·                                                                                        | 7<br>Logic selects and transmits most<br>negative error signals received                                                                                                                                                          | None                                                                                                                    | See thrust error select logic                                                                           |

- 40 -

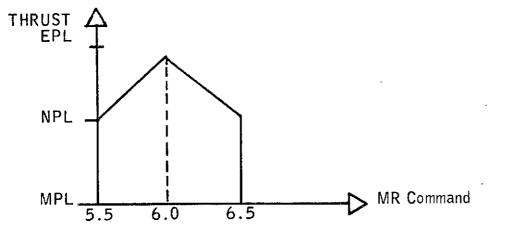

Engine Sensitivity to Preburner Propellant Valve Motion -- Current studies at Honeywell indicate that the preburner propellant valves have an excessively high engine control sensitivity at minimum power level (MPL). This high . sensitivity results in problems with possible premature engine failure due to the oxygen preburner valve (OPV) and potentially poor mixture ratio control definition due to the fuel preburner valve (FPV).

#### Oxygen Preburner Valve Failures --

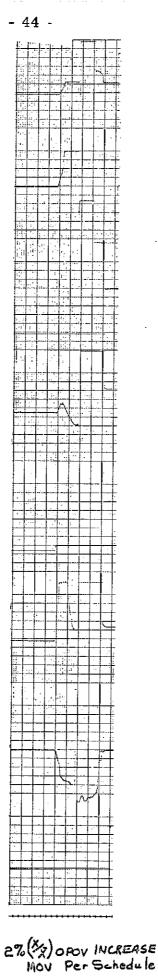

<u>Summary</u> -- The studies at Honeywell on the engine system simulations indicate that the current engine definition has a high risk of premature failure during servoactuator malfunction. Specifically failures of the oxygen preburner propellant valve (OPV) servoactuator which cause slewing in the opening direction, at minimum power level, cause the oxygen preburner temperature to exceed 5000 degrees Rankine. In Figure 16, traces 1 and 4 demonstrate the reaction of the engine to the above mentioned type of failure. The open-loop test runs of Figure 17 point out two significant aspects of the engine operation at minimum power level. The first is that it takes less than 2 percent step in the OPV valve to cause the oxygen preburner to go above 5000°R temperature. The second is that the deep throttling schedule requirements of the main oxidizer valve, at low power levels, is a major contributor to the problem.

Modifications to the engine system definition in the following areas will contribute to alleviating the problem:

- Decrease the main oxidizer valve (MOV) valve schedule; i.e., do not throttle the valve area to a low value during MPL operation.