NASA SP-6507

# PARTS, MATERIALS, AND PROCESSES EXPERIENCE SUMMARY

Volume II

# PARTS, MATERIALS, AND PROCESSES EXPERIENCE SUMMARY

Volume II

Prepared under contract for NASA by Lockheed Missiles & Space Company

# **FOREWORD**

Scientific and engineering organizations within the National Aeronautics and Space Administration, the Department of Defense, and throughout the aerospace industry are greatly concerned about the impact of system failures related to parts, materials, and processes. Establishment of the NASA ALERT reporting program in 1964, expanded in 1968 to include participants of the Government-Industry Data Exchange Program (GIDEP), provided the means for sharing and benefiting from each other's experience with these types of failures. Extensive data accumulated from ALERT reports have proved a valuable method of communicating problems and providing assistance in avoiding or minimizing recurrences.

In order that this accumulated experience be made readily available, this publication, *Parts, Materials, and Processes Experience Summary*, condenses and catalogs ALERT and other information on basic design, reliability, quality and application problems. Designers, engineers, failure analysts and other reliability and quality personnel will find the answers to many application and problem-avoidance questions.

This publication was developed under contract NAS2-6060 by the Lockheed Missiles & Space Company, Inc., Sunnyvale, Calif., under the leadership of W.L. Finch, W. Geller, and S. Ognibene. The contract was administered under the technical direction of NASA's Ames Research Center, Moffett Field, Calif., with G.E. DeYoung as technical monitor. This effort and the significant assistance provided by the members of the NASA Parts Steering Committee are gratefully acknowledged.

This issue of the Summary is a revision of CR-114391, Feb. 24, 1972. It includes, new, expanded, and revised material reflecting additional NASA experience and responses to the questionnaire sent to Government and industry personnel.

It is expected that this summary will be revised periodically to disseminate new and expanded information on existing topics and possibly new topics. Any suggestions or recommendations that will enhance its usefulness will be most welcome and should be referred to the Office of Safety and Reliability and Quality Assurance, NASA Headquarters, Washington, D.C. 20546.

GEORGE C. WHITE Director, Safety and Reliability and Quality Assurance

# INTRODUCTION

# **OBJECTIVE**

The objective of this Parts, Materials, and Processes Experience Summary is to provide the general engineering community with the accumulated experience from ALERT reports issued by NASA and the Government-Industry Data Exchange Program (GIDEP), and related experience gained by Government and industry. It provides expanded information on selected topics by relating the problem area (failure) to the cause, the investigation and findings, the suggestions for avoidance (inspections, screening tests, proper part applications, requirements for manufacturer's plant facilities, etc.), and failure analysis procedures.

# **ALERT PROGRAM**

The ALERT program is a system for communicating common problems with parts, materials, and processes. The ALERT program has as its basic objective the avoidance, or at least the minimization, of the recurrence of parts, materials, and processes problems, thus improving the reliability of equipment produced for and used by the Government. An ALERT report is prepared when an item is believed to be in common usage and the problem may affect other users; copies are distributed to all participants in the ALERT program.

Information on the ALERT program may be obtained from the Office of Safety and Reliability and Quality Assurance, NASA Headquarters, Washington, D.C. 20546 (phone 202-755-2284); or from the GIDEP Administration Office, Fleet Missile Systems Analysis and Evaluation Annex, Code 862, Naval Weapons Station, Seal Beach, Corona, Calif. 91720 (phone 714-736-4677; Autovon: 933-4677).

# ORGANIZATION OF SUMMARY

This two-volume publication is divided into 18 sections, one of which is a miscellaneous category. The other sections represent 17 major topics derived from the GIDEP major classification code. The GIDEP code number is shown on each section divider to assist in obtaining related data from test and qualification reports on parts and materials, scientific reports, technical information, manufacturing techniques, and specifications contained in the GIDEP file. Each section presents fundamental concepts followed by problems that have been experienced and suggestions for their avoidance; guidelines for producing good parts and materials; and procedures for determining why a failure occurred. Introductory remarks and a table of contents precede each section.

The 17 major topics (attaching methods, capacitors, transistors, etc.) were selected because they represent 82 percent of the ALERT reports issued by NASA and GIDEP through Aug. 31, 1972. The remaining reports are included through the medium of ALERT summaries in the miscellaneous section of Volume I.

# ALERT ITEM NO.

Where appropriate within a section, each ALERT report has been assigned an "ALERT ITEM NO." in order to provide a cross reference between an ALERT referenced in the Problem/Screening Summary subsection and the same ALERT shown in the ALERT Summaries subsection.

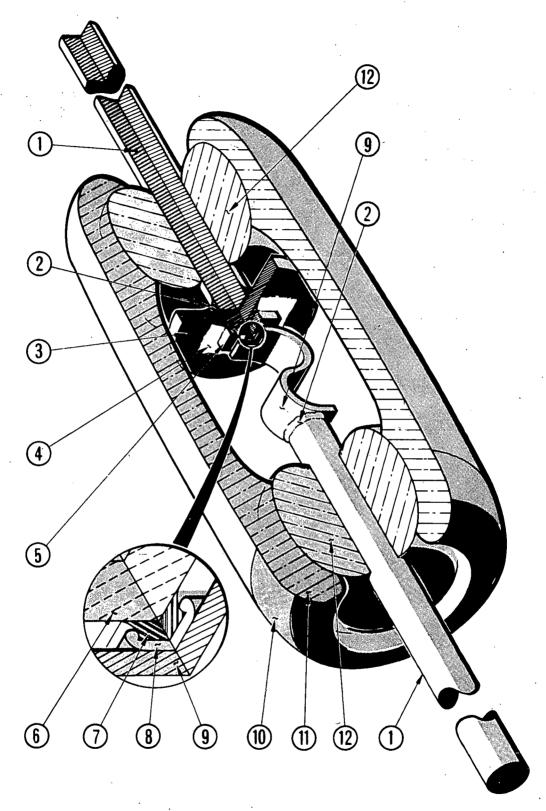

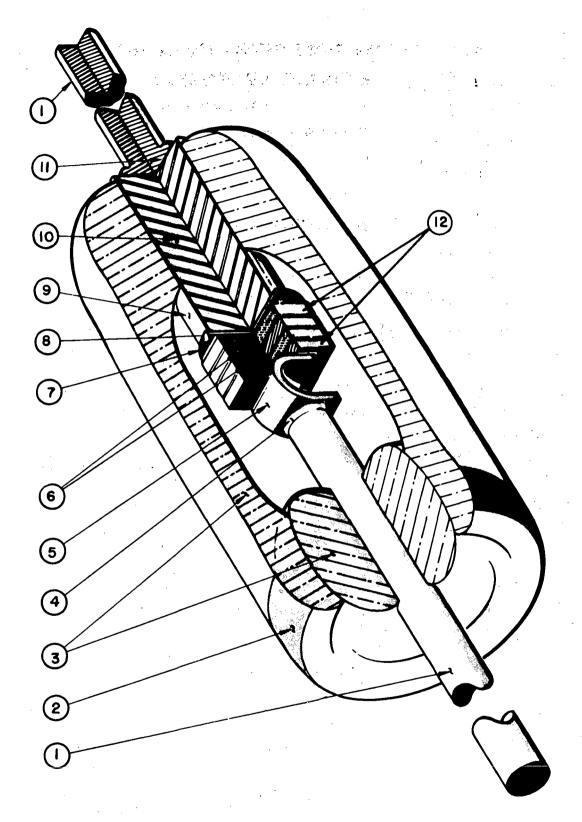

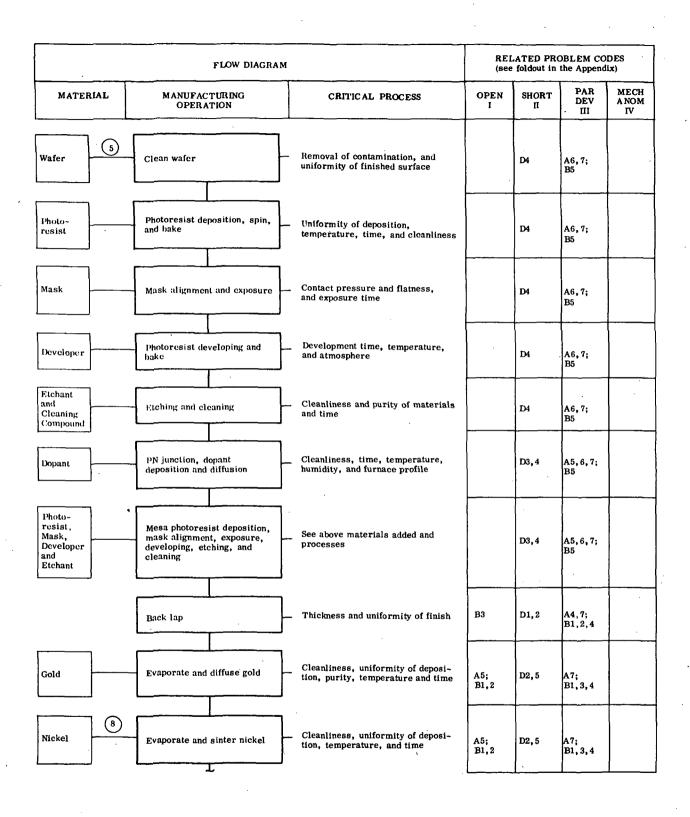

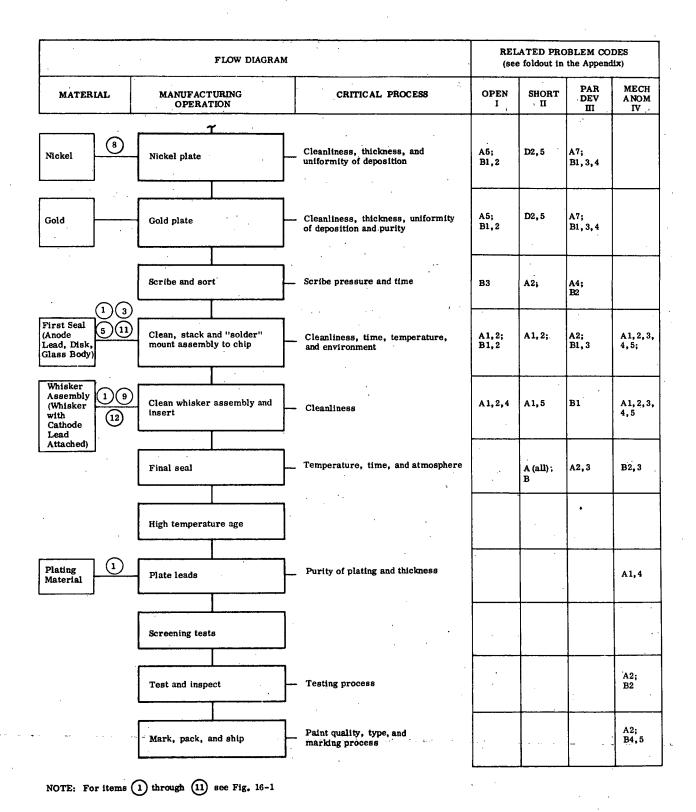

# **CODE FOR PROBLEM AREAS AND CAUSES**

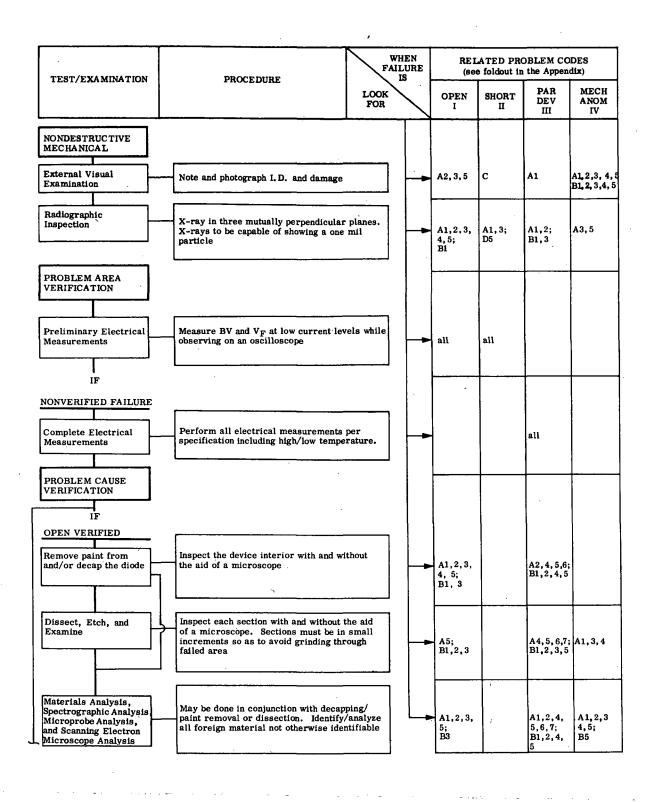

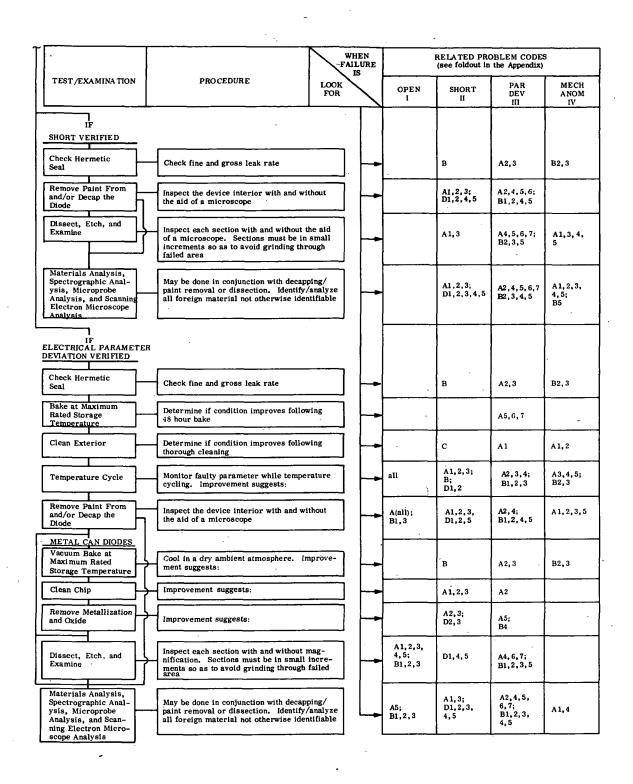

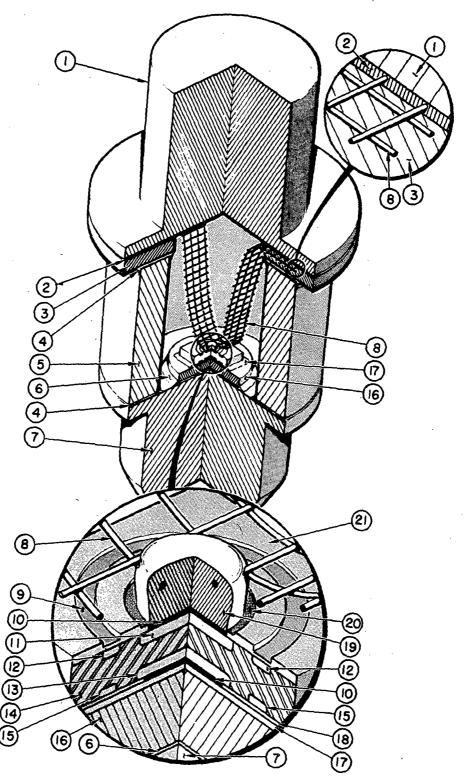

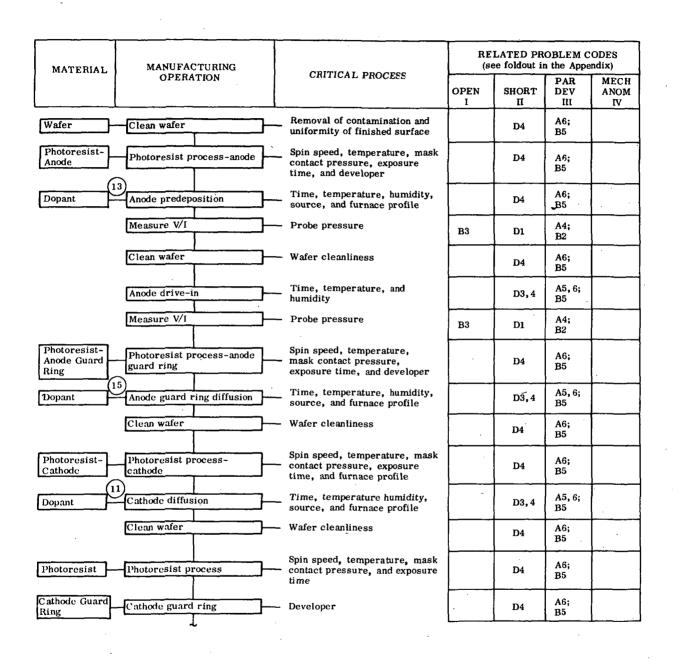

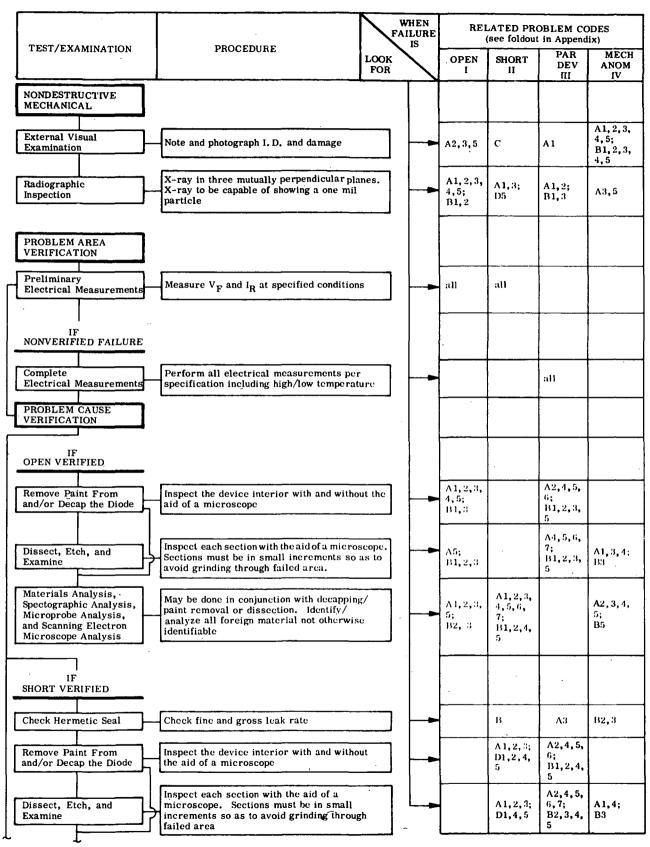

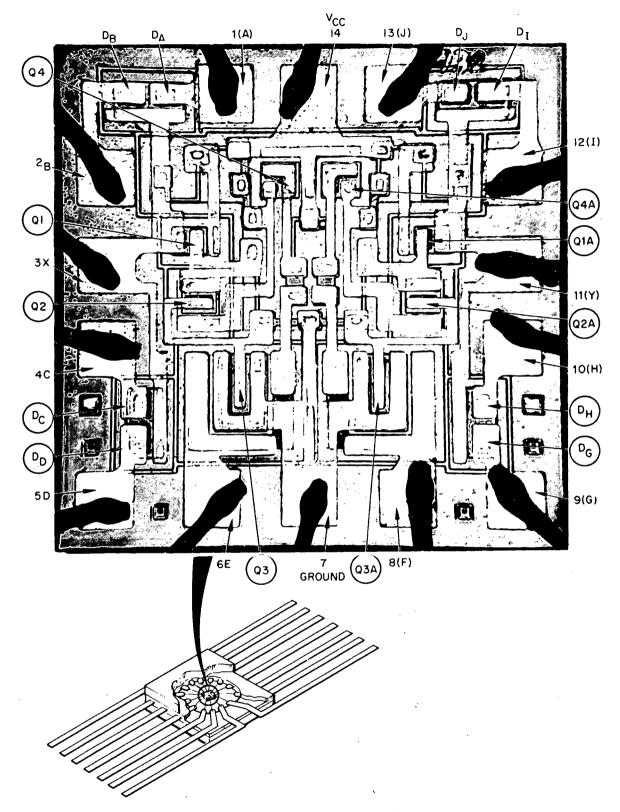

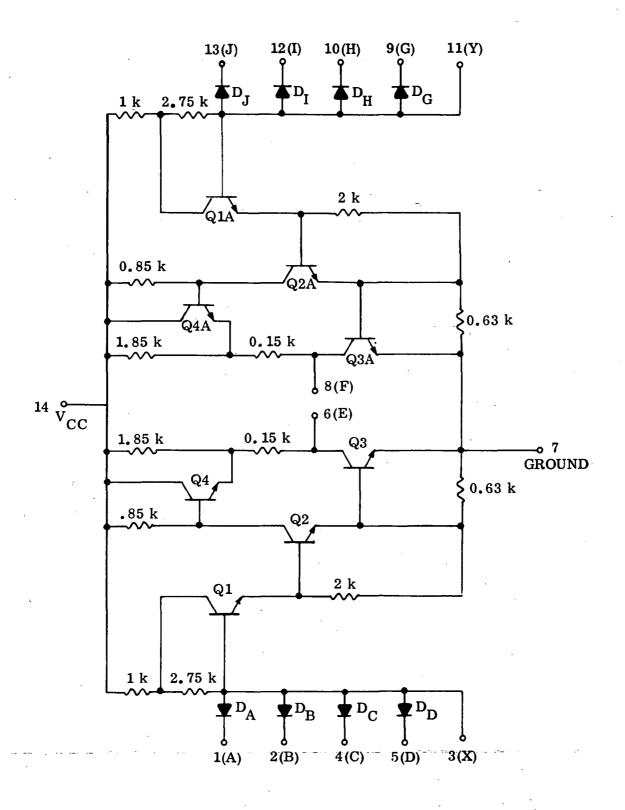

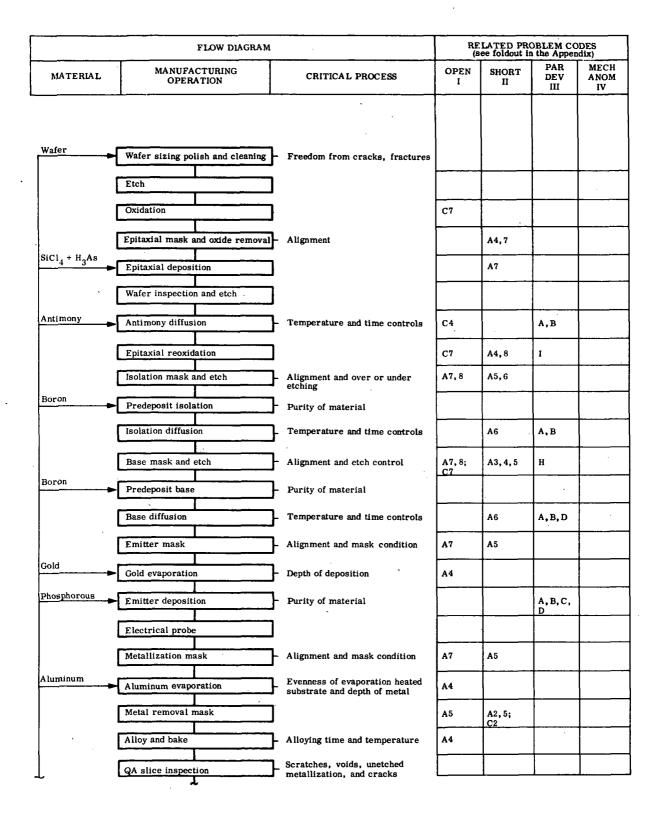

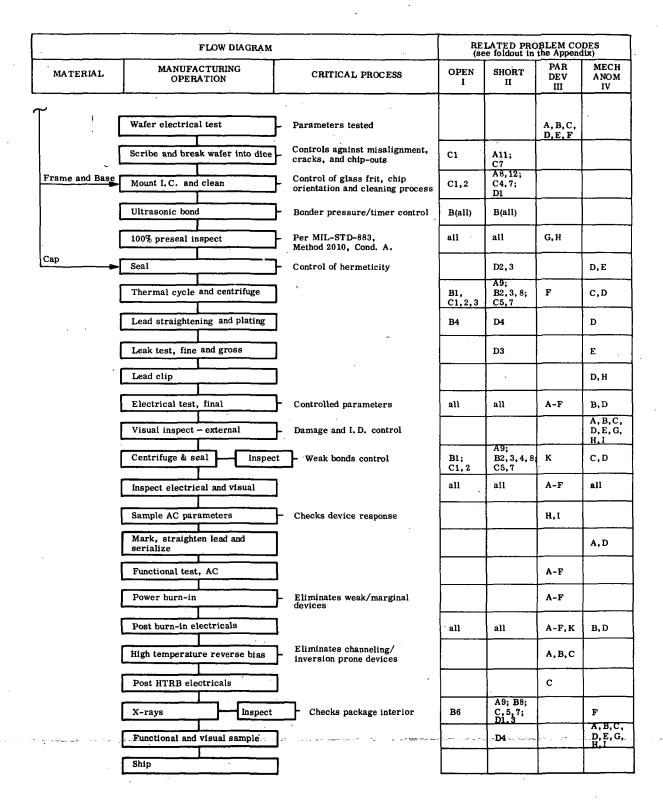

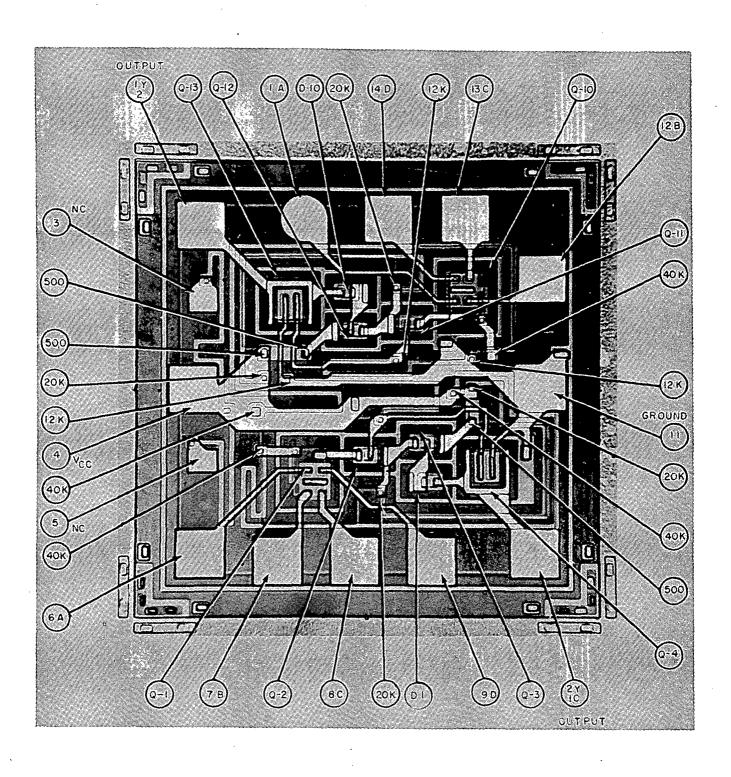

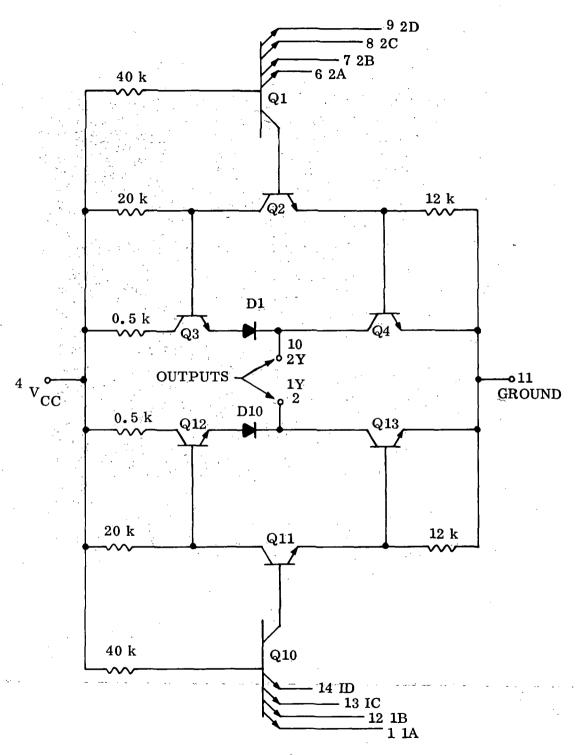

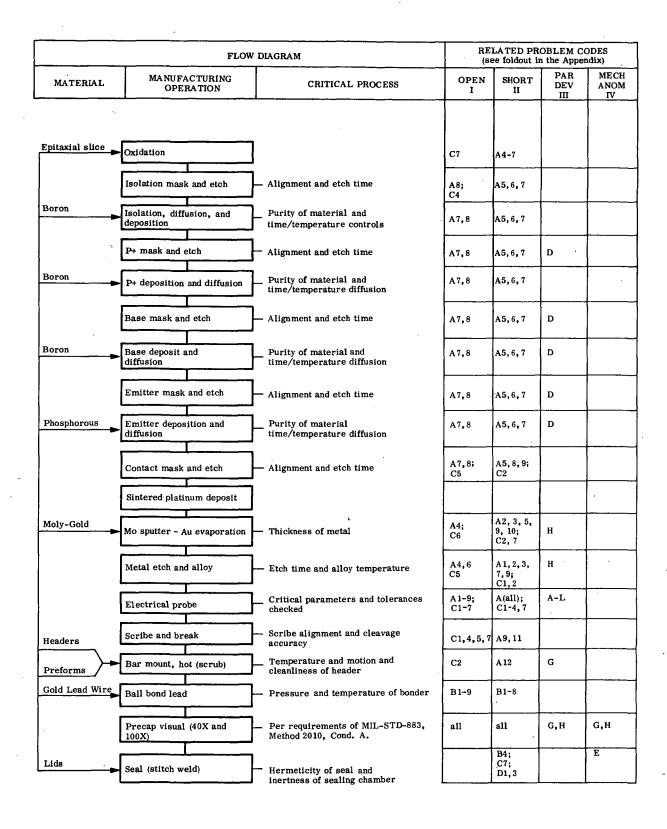

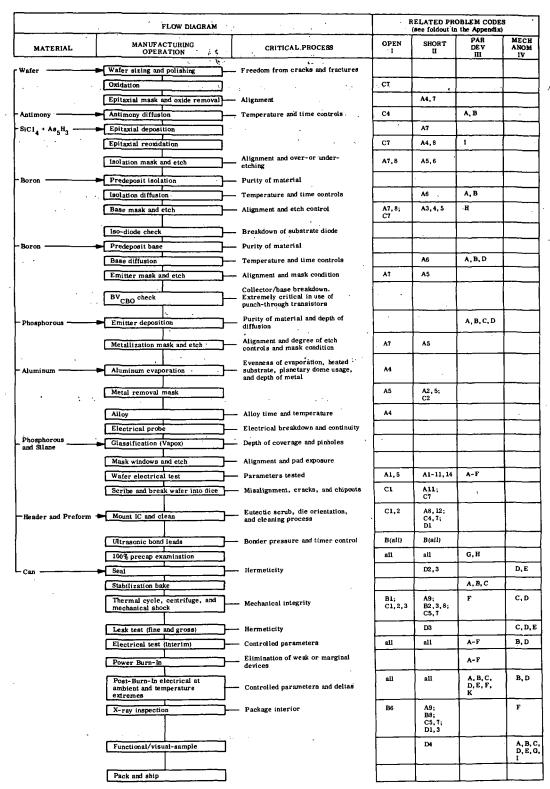

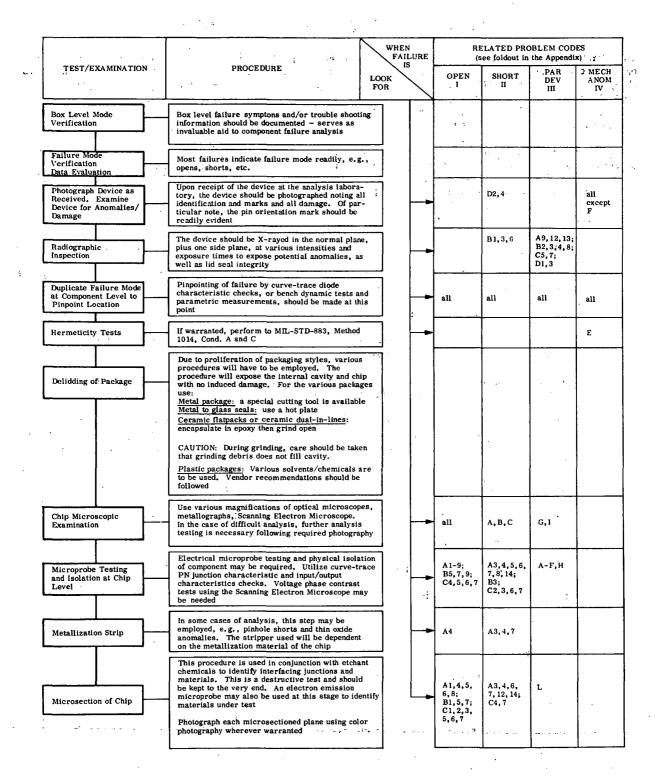

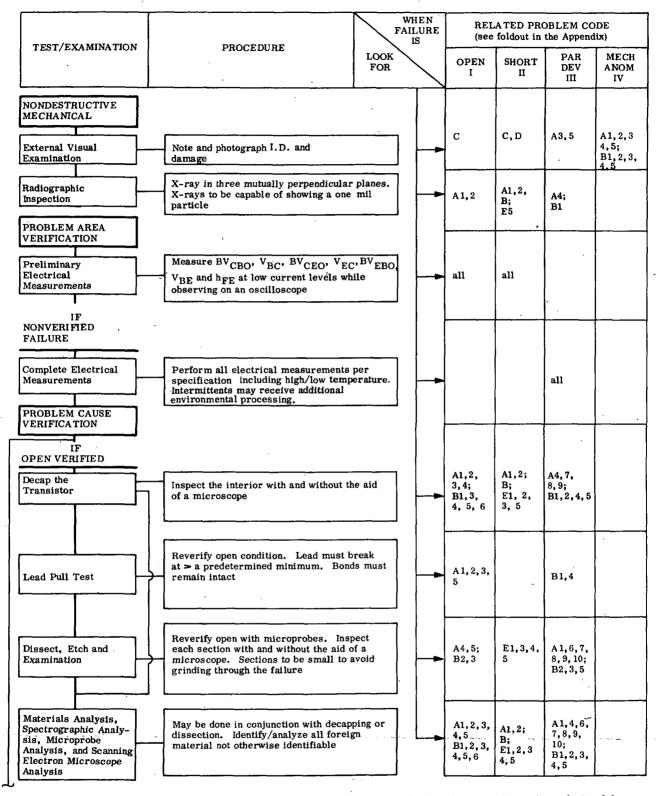

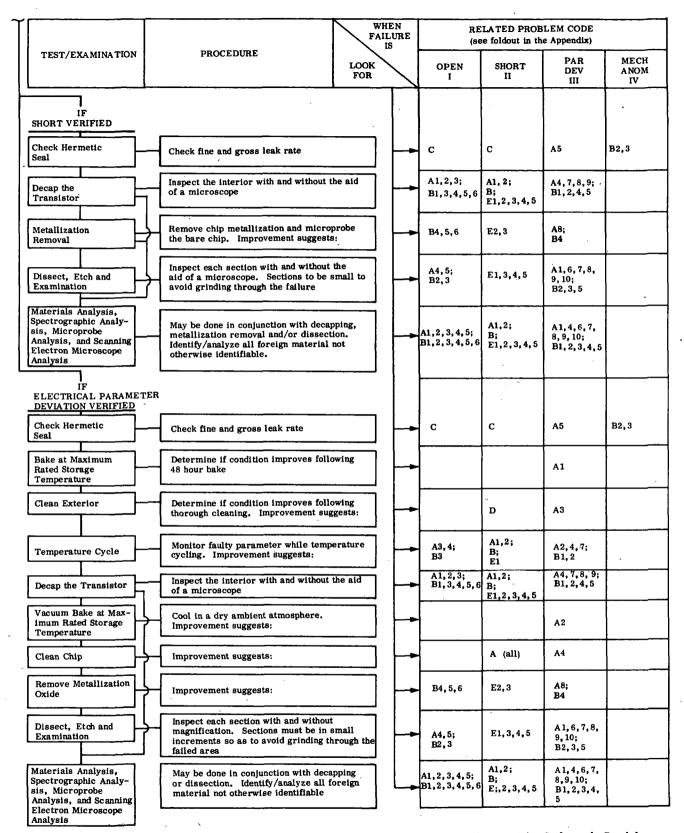

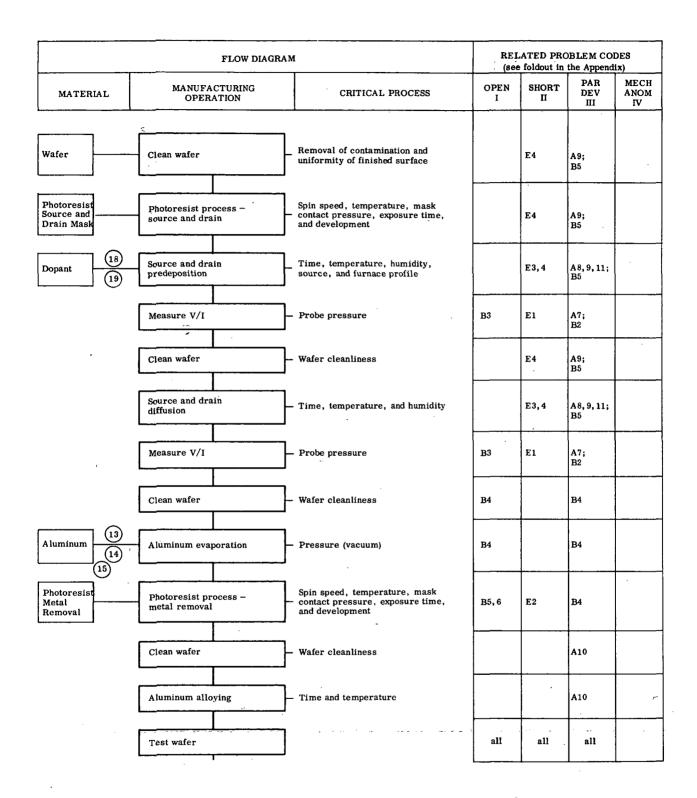

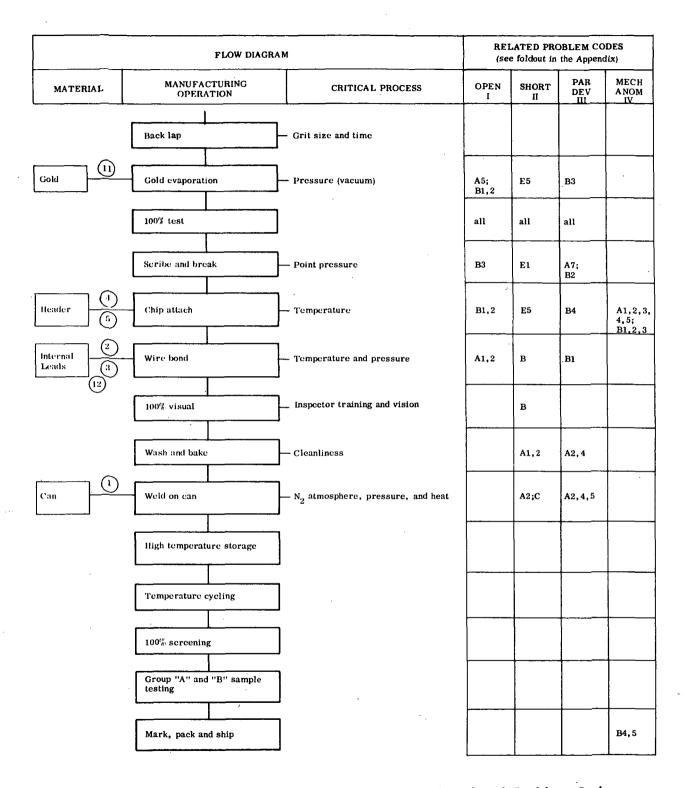

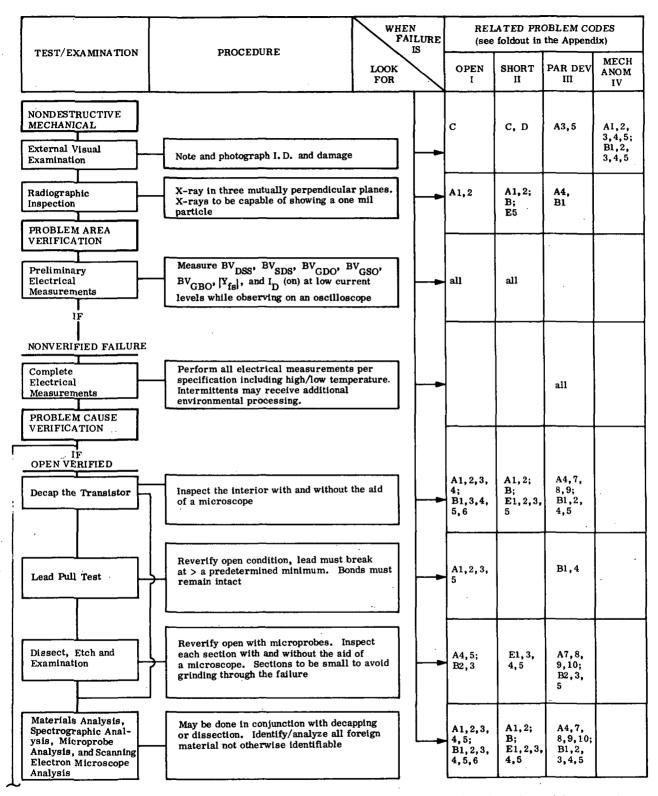

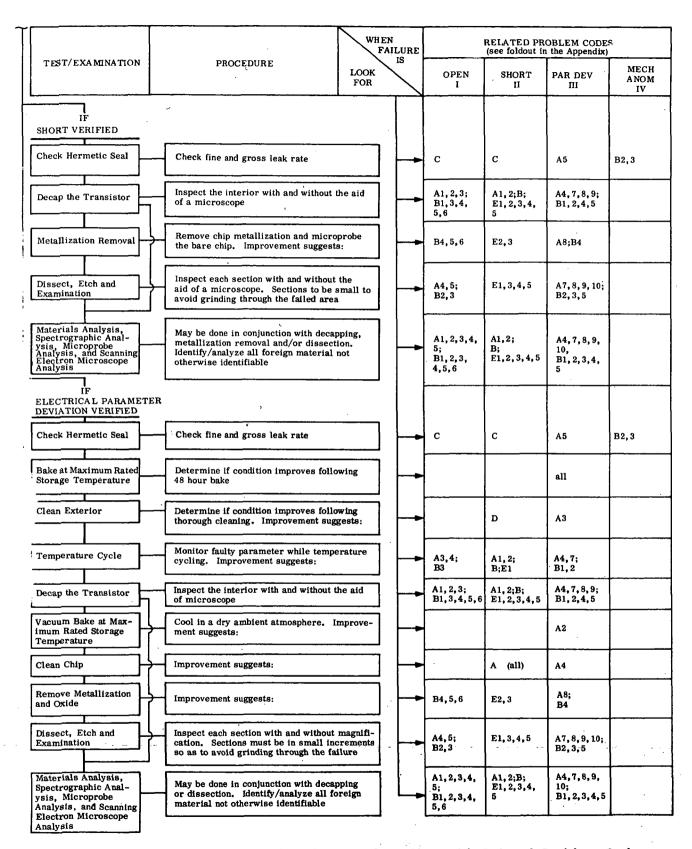

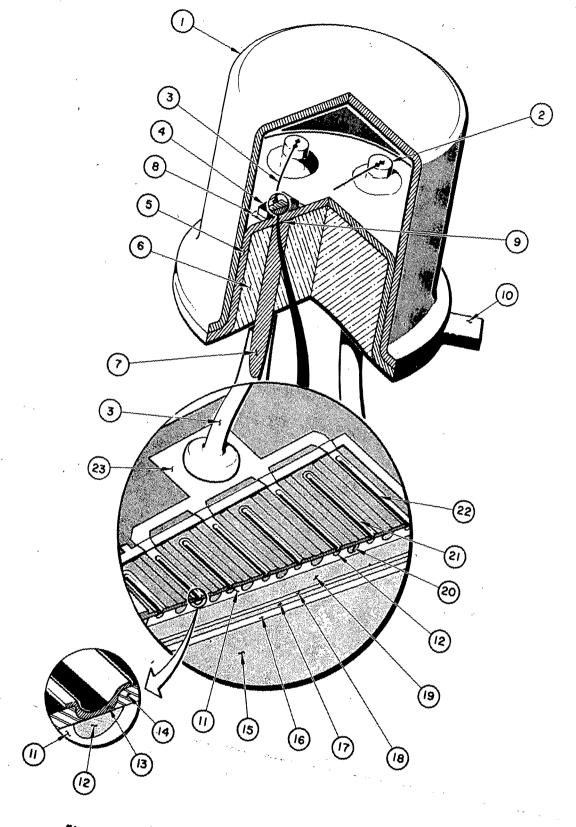

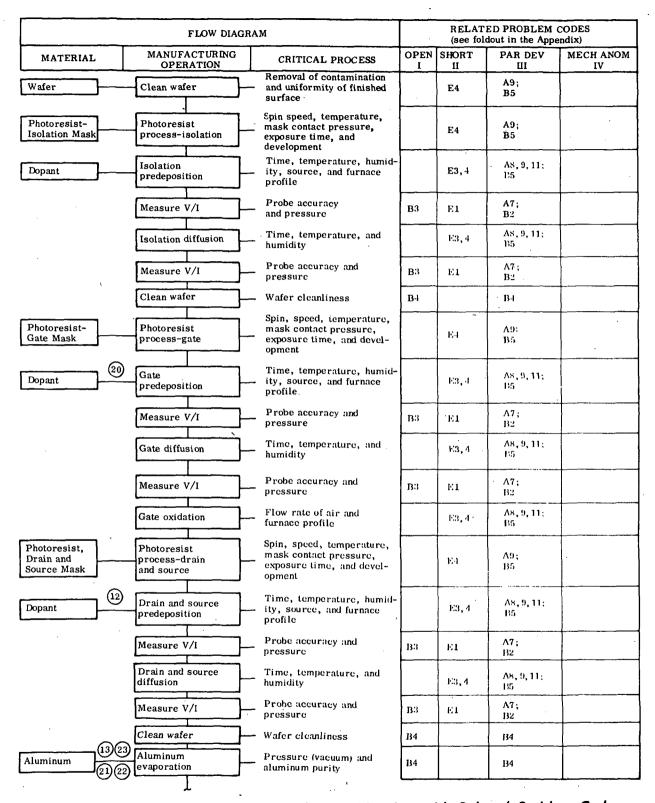

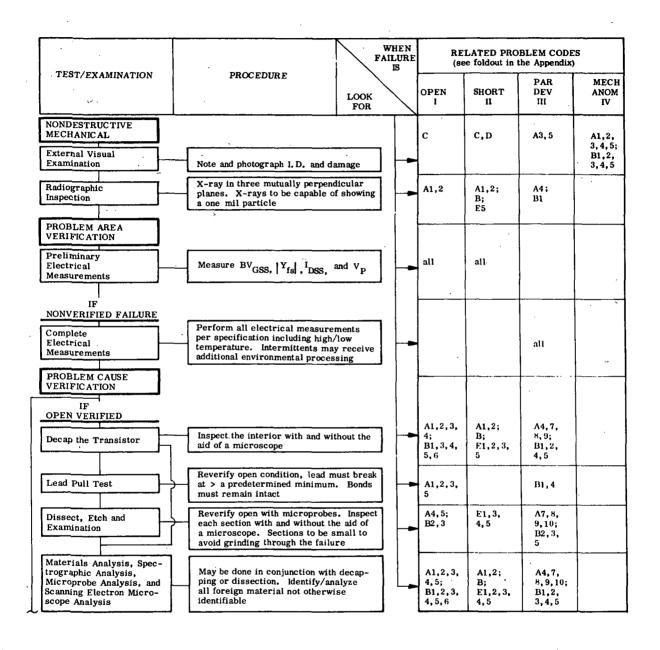

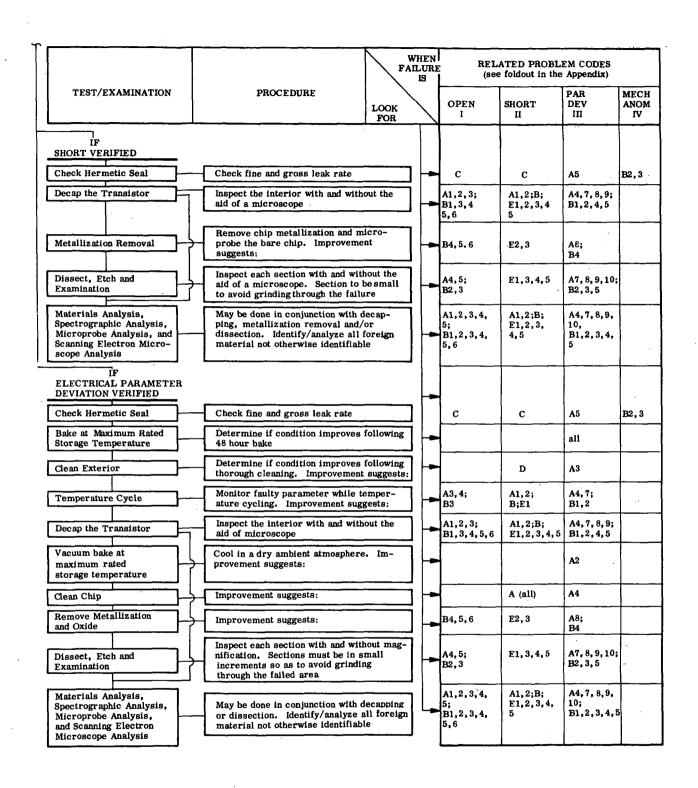

Some sections employ a coding system to identify the major problem areas and their causes. The code is entered in the Problem/Screening Summary subsections, on the assembly flow diagrams, and on the failure analysis flow diagrams. A separate foldout (Problem Codes and Definitions) defines the code used in a particular section of the publication. All foldouts are located in the appendix. The coding system ties together the problem area/cause, the preventive action, the critical process during assembly, and the failure analysis step. For instance within Section 3 (Capacitors), ALERT Item No. 7 in the Problem/Screening Summary subsection indicates a "Short" as the problem area, with the cause being "Breakdown of dielectric." Also shown are the suggested screens that should detect the problem area/cause. The foldout for Section 3 (Capacitors) establishes the problem code of the area/cause as "IID." This code in the Ceramic Capacitor-Typical Assembly Flow with Related Problem Codes diagram (fig. 3-2) indicates that "thin spots and contamination" during the "slip cast dry and roll green stock" operation can eventually cause a short because of dielectric breakdown. In a similar manner, the Ceramic Capacitor-Failure Analysis Flow with Related Problem Codes diagram (fig. 3-3) shows that the problem area/cause can be detected at the "radiographic inspection," or at the "depotting and examination" or the "dissection and examination" stages of the failure analysis procedure. The two diagrams can also be used in other ways. Possible problem areas/causes are depicted for any stage in the assembly operation, thus facilitating the creation of a process control check-off list. If the problem area is known, possible causes are shown for any stage in the failure analysis procedure.

# REFERENCES

The title and responsible agency for a military standard or specification, or for a NASA special publication or handbook, are given in the list of references located at the back of the publication.

# **KEYWORD INDEX**

Keyword indexing is provided in order to facilitate easy search and reference; e.g., an ALERT report for a particular relay may contain the words: "relay," "contamination," and "solder." Looking up those words in the index will lead to that particular relay problem; the words "contamination" or "solder" will also lead to other ALERT reports on other types of parts.

# Volume I

| hara i.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | and the state of t |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Section,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page        |

| Something                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FOREWORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | iii         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 ATTACHING METHODS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ٧           |

| - 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-1         |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 BATTERIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 CAPACITORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-1         |

| September                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 FASTENERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .5-1        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6 FUSES/CIRCUIT PROTECTIVE DEVICES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7 GASKETS/SEALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 7-1       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-1         |

| a de la companya de l | 9 ORDNANCE/PROPULSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-1         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 RELAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10-1        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 RESISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-1        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 SWITCHES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12-1        |