N74-17909

SUBJECT TO CHANGE

DESIGN OF A FAULT TOLERANT AIRBORNE DIGITAL COMPUTER, VOLUME I -ARCHITECTURE

J. H. Wensley, et al

194 pr 313

Stanford Research Institute Menlo Park, California

October 1973

ITEM \$ 7.00

17 APR 1975 MCDONNELL DOUGLAS RESEARCH & ENGINEERING LIBRARY ST. LOUIS

**DISTRIBUTED BY:**

National Technical Information Service U. S. DEPARTMENT OF COMMERCE 5285 Port Royal Road, Springfield Va. 22151

M75-12723

Final Report

# DESIGN OF A FAULT TOLERANT AIRBORNE DIGITAL COMPUTER

Volume I – Architecture

By: J. H. WENSLEY, K. N. LEVITT, M. W. GREEN, J. GOLDBERG, and P. G. NEUMANN

Prepared for:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION LANGLEY RESEARCH CENTER HAMPTON, VIRGINIA 23365

NICHOLAS MURRAY - CONTRACT MONITOR

CONTRACT NAS1-10920

PRICES SUBJECT TO CHANGE

(NASA-CR-132252)DESIGN OF A FAULTN74-17909TOLERANT AIRECRNE DIGITAL COMPUTER.VOLUME 1:ARCHITECTURE Final ReportVOLUME 1:ARCHITECTURE Final ReportUnclas(Stanford Research Inst.)Unclas

CSCL 09B G3/08 16207

STANFORD RESEARCH INSTITUTE

Menlo Park, California 94025 · U.S.A.

Reproduced by NATIONAL TECHNICAL INFORMATION SERVICE US Department of Commerce Springfield, VA. 22151

STANFORD RESEARCH INSTITUTE MENLO PARK, CALIFORNIA 94025 (415) 326-6200

ERRATA

December 10, 1973

To: Distribution

Reference:

Final Report

"Design of A Fault Tolerant Airborne Digital Computer Volume I Architecture"

"Design of a Fault Tolerant Airborne Digital Computer Volume II Computational Requirements and Technology"

SRI Project Number 1406

National Aeronautics and Space Administration Prepared for: Langley Research Center Hampton, Virginia 23365

Eclosed is errata labal to add to your cover of volumes one and two of Final Report.

10

Volume I: 132252 Volume II: 132253 ak vou. The

Sr. Clerical Assistant

eec Encls. 1406

Final Report

October 1973

# DESIGN OF A FAULT TOLERANT AIRBORNE DIGITAL COMPUTER

Volume I – Architecture

By: J. H. WENSLEY, K. N. LEVITT, M. W. GREEN, J. GOLDBERG, and P. G. NEUMANN

ib

## Prepared for:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION LANGLEY RESEARCH CENTER HAMPTON, VIRGINIA 23365

NICHOLAS MURRAY - CONTRACT MONITOR

CONTRACT NAS1-10920

SRI Project 1406

Approved by:

D. R. BROWN, Director Information Science Laboratory

BONNAR COX, Executive Director Information Science and Engineering Division

Volume I of this report is concerned with the architecture of a fault tolerant digital computer for an advanced commercial aircraft. All of the computations of the aircraft, including those presently carried out by analogue techniques, are to be carried out in this digital computer. Among the important qualities of the computer are the following: (1) the capacity is to be matched to the aircraft environment, (2) the reliability is to be selectively matched to the criticality and deadline requirements of each of the computations, (3) the system is to be readily expandable and contractible and (4) the design is to appropriate to post 1975 technology. Three candidate architectures are discussed and assessed in terms of the above qualities. Of the three candidates, a newly conceived architecture, Software Implemented Fault Tolerance (SIFT), provides the best match to the above qualities. In addition SIFT is particularly simple and believable. The other candidates, Bus Checker System (BUCS), also newly conceived in this project, and the Hopkins multiprocessor are potentially more efficient than SIFT in the use of redundancy, but otherwise are not as attractive. Volume II of the report is concerned with a detailed description and categorization of the computations and with a discussion of the technology available for realizing the computer system.

# PRECEDING PAGE BLANK NOT FILMED

## TABLE OF CONTENTS

| ABSTI | ACT                                                                           | . <b>i</b>           |

|-------|-------------------------------------------------------------------------------|----------------------|

| LIST  | OF ILLUSTRATIONS                                                              | x                    |

|       |                                                                               | ci                   |

|       | CE                                                                            | i                    |

| I     | INTRODUCTION                                                                  | 1                    |

|       | A. Purpose of the Study                                                       | 1                    |

|       | B. Organization of the Report                                                 | 2                    |

| II    | REVIEW OF RELIABILITY TECHNIQUES                                              |                      |

|       | A. Introduction                                                               | 7                    |

|       | B. Coding Techniques                                                          | 10                   |

|       | C. The Trivial Duplication and Triplication Codes                             | 11                   |

|       | D. Use of Less Trivial Codes for Enhancing<br>Processor Reliability           | 13                   |

| •     | _,,g                                                                          | 14<br>21             |

| •     | E. Use of Codes for Memory                                                    | 24                   |

|       | 2. Bounds on Code Redundancy2.3. Specific Codes for Correcting Framed Burst3. | 24<br>26<br>30<br>31 |

|       | F. Summary of System Aspects of Redundancy                                    | 10                   |

|       | REFERENCES - CHAPTER II                                                       | 43                   |

| III   | MPLICATIONS OF COMPUTATIONAL REQUIREMENTS                                     | 45                   |

| IV    | MPLICATIONS OF TECHNOLOGY                                                     | 51                   |

PRECEDING PAGE BLANK NOT FILMED

v

| v   | A C       | HECKLIST AND A SURVEY OF FAULT TOLERANT ARCHITECTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55       |

|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | Α.        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55       |

|     | в.        | Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56       |

|     | c.        | STAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63       |

|     | D.        | ЕХАМ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66       |

|     | Е.        | Hopkins Scheme (HS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70       |

|     | F.        | ARMMŜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72       |

| •   | G.        | AADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75       |

|     | н.        | MARCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76       |

|     | REF       | ERENCES - CHAPTER V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79       |

| VI  | SOF       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81       |

|     | Α.        | Grand and Deck of the second | 81       |

|     | в.        | Major Characteristics of SIFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 87       |

| · . | c.        | Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88       |

|     | D.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89       |

|     | Ė.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92       |

|     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95       |

| ·.  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97       |

|     | F.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01<br>03 |

|     | G.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|     | <b>u.</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 03       |

|     | H.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 09<br>15 |

|     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15       |

|     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16<br>19 |

|     | Ι.        | Alternative Design Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20       |

|     | J.        | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23       |

vi

| VII        | BUS  | CHECKER SYSTEM                                                                                                      | 5               |

|------------|------|---------------------------------------------------------------------------------------------------------------------|-----------------|

|            | Α.   | Introduction                                                                                                        | ;               |

| ·<br>· .   | В.   | High-Level Description of Architecture                                                                              | \$ <sup>°</sup> |

|            |      | 1.Hardware Components1282.Global Description of System Operation130                                                 | -               |

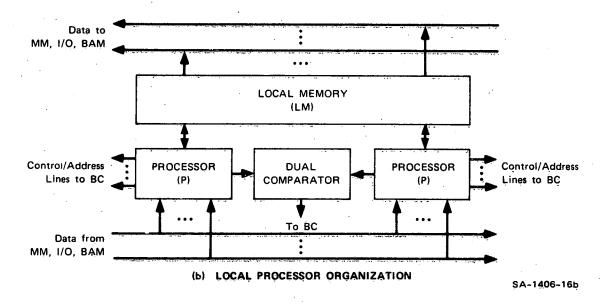

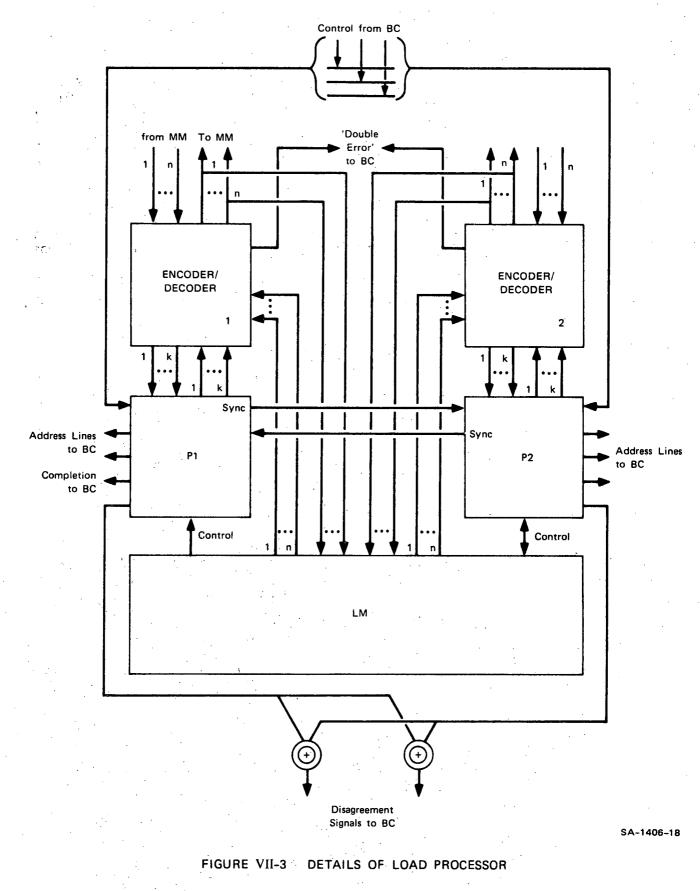

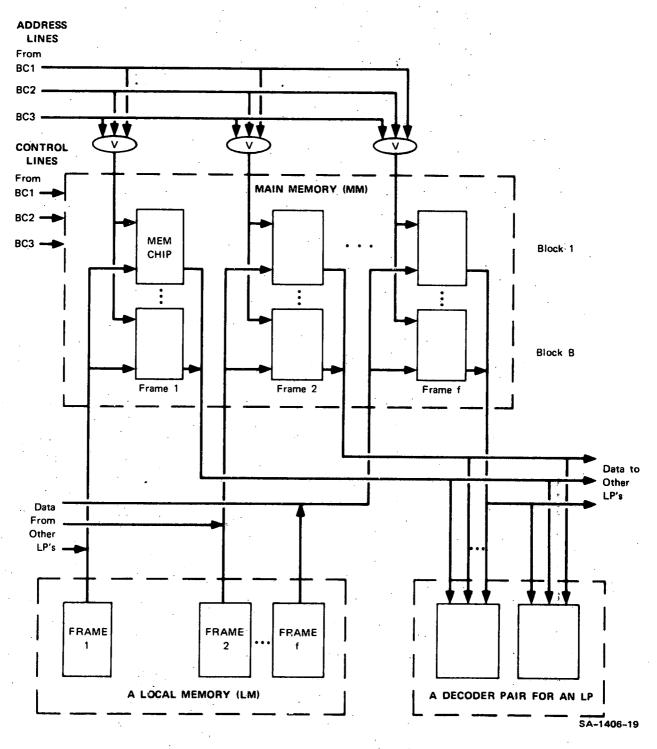

|            | c.   | Description of Major Blocks                                                                                         | 3               |

|            |      | 1.Local Processor1332.Main Memory Organization1353.Bus Checker Organization138                                      | 5               |

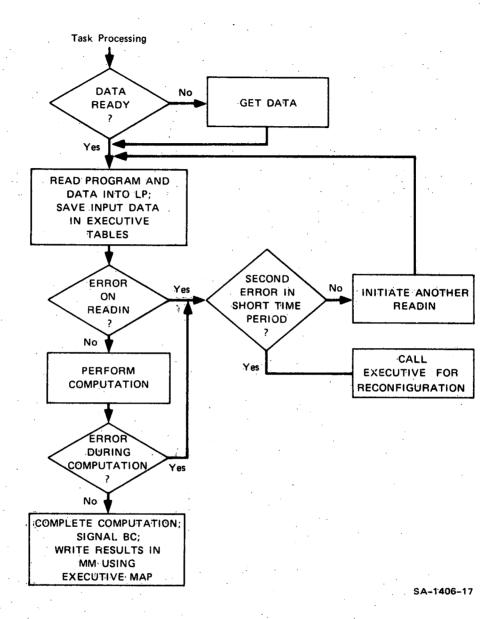

|            | D.   | Executive Operation                                                                                                 | 2               |

|            |      | 1.Application Task Scheduling1422.Background Executive Processing1433.Single Error Processing1444.Executive Load145 | -<br>3<br>1     |

|            | Ε.   | Reliability and Performance                                                                                         | 5               |

|            | F.   | Embellishments and Discussions                                                                                      | )               |

| VIII       | SUM  | MARY AND CONCLUSIONS                                                                                                | 3               |

|            | Α.   | Summary                                                                                                             | 3               |

|            | В.   | Conclusions                                                                                                         | 7               |

| APPEN      | DICE | S                                                                                                                   |                 |

|            | Α.   | ALLOCATION AND SCHEDULING SYSTEM ROUTINE                                                                            | 1               |

| . <b>.</b> | В.   | COMPARISON OF THE SIFT SYSTEM AND A MULTI-CHANNEL SYSTEM B-                                                         | 1               |

vii

## LIST OF ILLUSTRATIONS

| Figure | II-1   | A Nonredundant Circuit                                                                                           |

|--------|--------|------------------------------------------------------------------------------------------------------------------|

| Figure | 11-2   | Coded Version of Circuit Using Winograd-Cowan Concept 16                                                         |

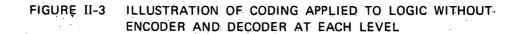

| Figure | 11-3   | Illustration of Coding Applied to Logic Without<br>Encoder and Decoder at Each Level                             |

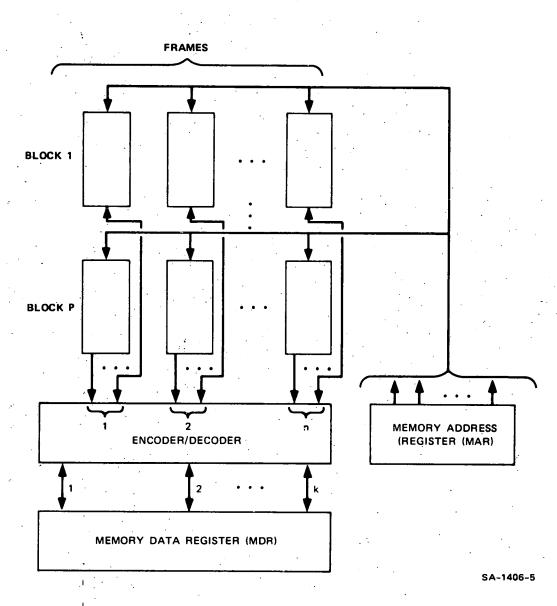

| Figure | II-4   | Coding Scheme for Memory                                                                                         |

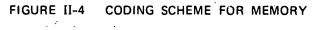

| Figure | II-5   | Frames of a Block-Code Word                                                                                      |

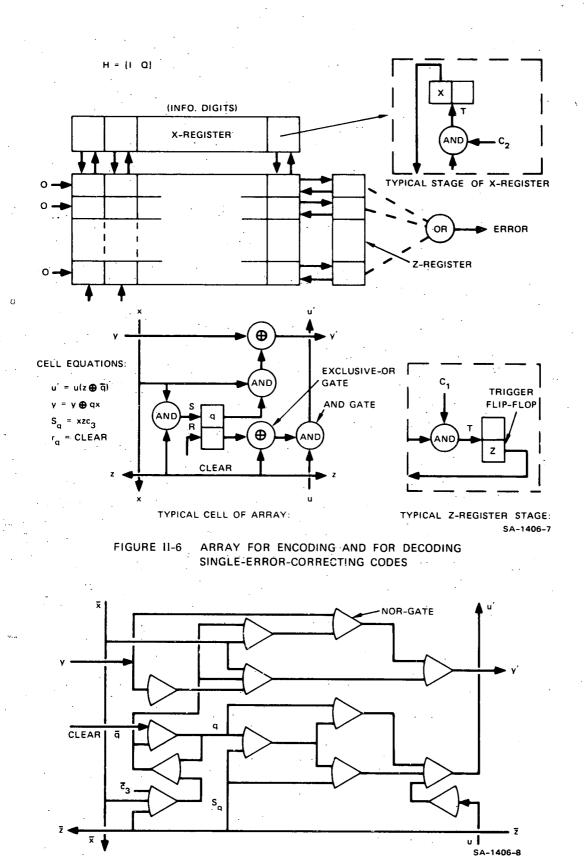

| Figure | II-6   | Array for Encoding and for Decoding Single-Error-<br>Correcting Codes                                            |

| Figure | II-7   | NOR-Gate Realization of Main-Array Cell                                                                          |

| Figure | VI-1   | SIFT System Configuration                                                                                        |

| Figure | VI-2 . | An Example of Task/Processor Allocation                                                                          |

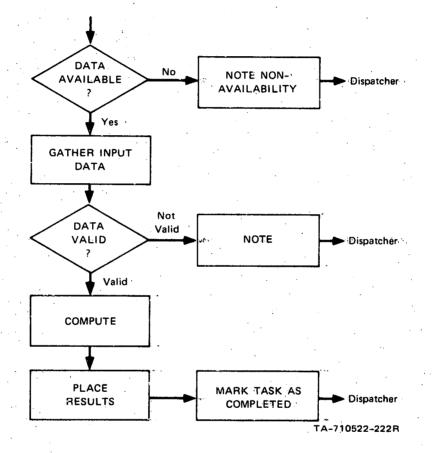

| Figure | VI-3   | Typical Task Flow                                                                                                |

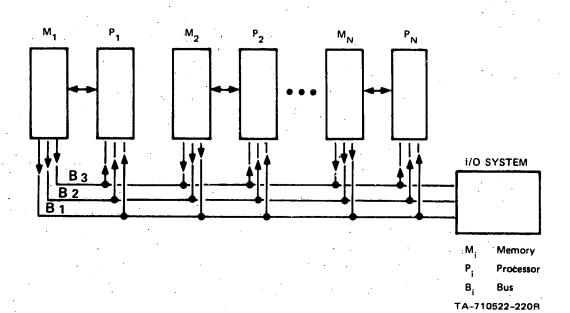

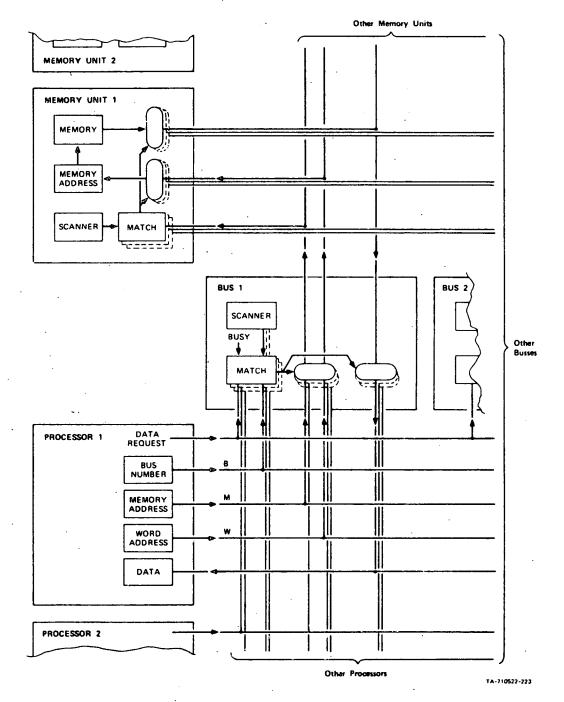

| Figure | VI-4   | Processor/Bus/Memory Connection                                                                                  |

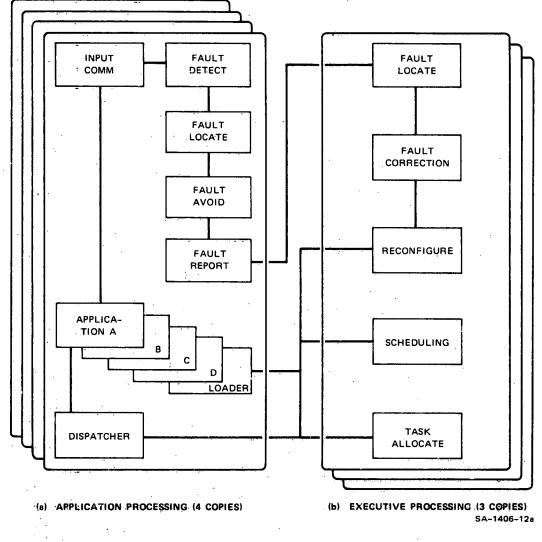

| Figure | VI-5a  | Application and Executive Structure                                                                              |

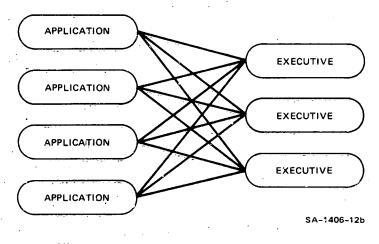

| Figure | VI-5b  | Application and Executive Connectivity                                                                           |

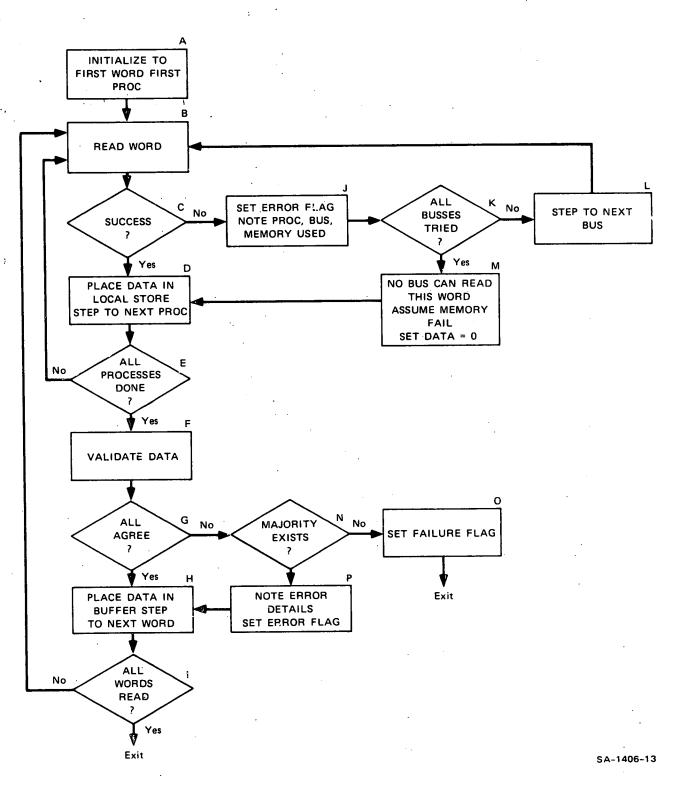

| Figure | VI-6   | The Getdata Subroutine                                                                                           |

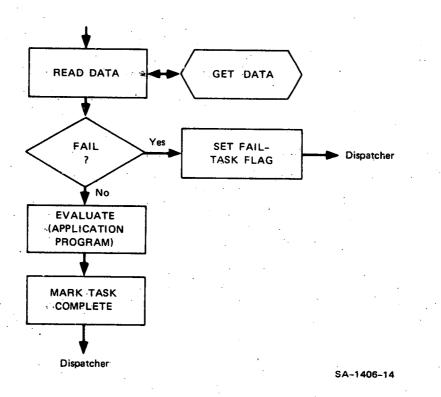

| Figure | VI-7   | Typical Application Task                                                                                         |

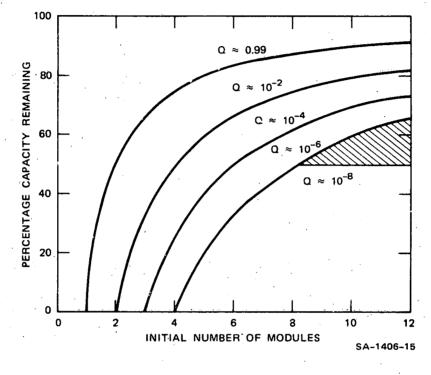

| Figure | VI-8   | Probability (Q) of Differing Percentage Capacity<br>Remaining, as a Function of the Initial Number<br>of Modules |

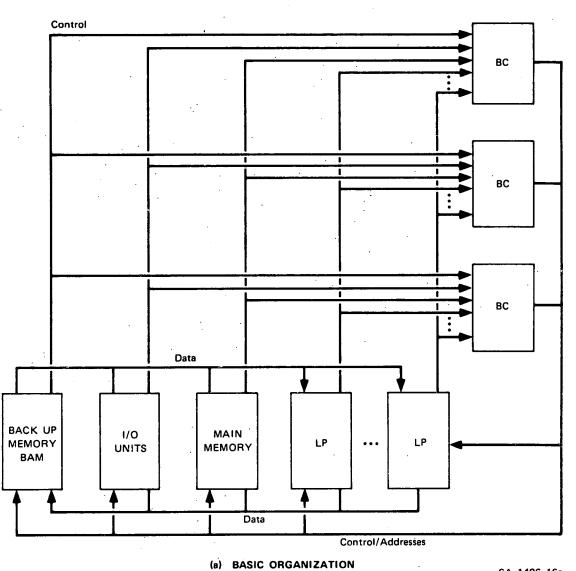

| Figure | VII-1  | High Level View of BUCS                                                                                          |

| Figure |        | High Level View of BUCS Operation                                                                                |

| Figure | VII-3  | Details of Local Processor                                                                                       |

| Figure | VII-4  | Main Memory Organization                                                                                         |

| Figure | VII-5  | Bus Checker Organization                                                                                         |

| Figure | A-1    | Allocation and Scheduling Data Structures                                                                        |

| Figure | A-2    | Allocation Algorithm 1                                                                                           |

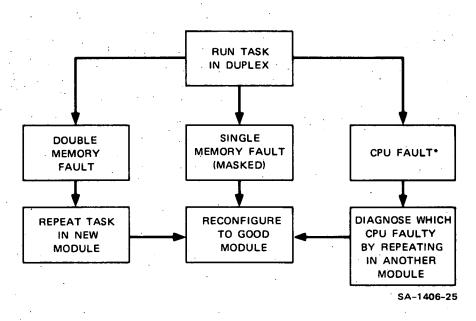

| Figure | B-1    | SIFT with Coding, Reconfiguration Strategy<br>for Most Critical Tasks                                            |

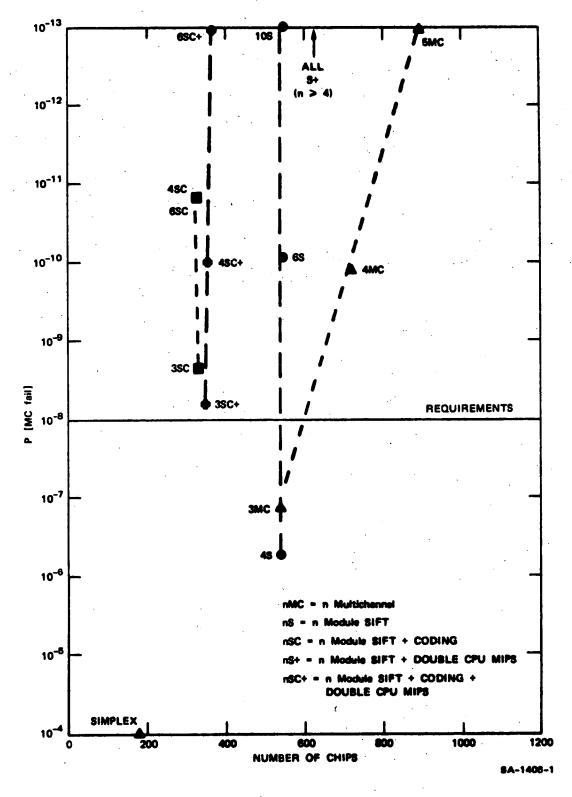

| Figure | B-2    | Summary Comparison of SIFT and Multi-Channel                                                                     |

PRECEDING PAGE BLANE NOT FILMED

ix

## LIST OF TABLES

| • •           |        |                                                                             |      |

|---------------|--------|-----------------------------------------------------------------------------|------|

| Table         | II-1   | H-Matrices for (7, 4; 2) and (6, 3; 2) Codes                                | 18   |

| Table         | II-2   | Redundancy for Correcting Cyclic and Framed Bursts                          | 30   |

| Table         | 11-3   | H-Matrix for (15, 12; 4) Code                                               | 32   |

| Table         | II-4   | Matrix for (16, 12; 4) Code                                                 | 32   |

| Table         | II-5   | Redundancy for Best Known Codes for Single-Frame<br>Correction, $b = g = 4$ | 33   |

| Table         | II-6   | Summary of Decoder Complexities for Hamming Codes                           | 39   |

| Table         |        | Computing Requirements, Applications                                        | 46   |

| Table         |        | Computing Requirements, Applications                                        | 40   |

| Table         | _      |                                                                             |      |

| Table         |        | Computing Requirements, SIFT Executive                                      | 105  |

| Table         |        | Probability of Non-Tolerated Double Fault                                   | 112  |

| Table         | VI-3   | Probability of Failure of Different Number<br>of Modules                    | 112  |

| Table         | VI-4   | Probability of Losing N Modules                                             | 113  |

| Table         | VI-5   | Stack Organized Computer Organization                                       | 118  |

| Table         | VIII-1 | Comparison of Fault-Tolerant Procedures                                     | 155  |

| Table         | VIII-2 | Candidate Comparisons by Checklist Categories                               | 156  |

| Table         | VIII-3 | Performance Comparison of Candidates                                        | 156  |

| Table         | A-1    | Example Data for Allocation Function                                        | A-7  |

| Table         | A-2    | Application of Algorithm 1 for Data in<br>Table 1 and P = 6                 | A-8  |

| Table         | _ B-1  | Computation and Memory Requirements                                         | B-1  |

| Tab <b>le</b> | B-2    | Reliability Estimates for Multi-Channel System                              | B-3  |

| Table         | B-3    | SIFT Processor and Memory Requirements                                      | B-4  |

| Table         | B-4    | Reliability Estimates for a 4-Module SIFT                                   | B-4  |

| Tab <b>le</b> | B-5    | Reliability Estimates for a 6-Module SIFT                                   | B-5  |

| Table         | B-6    | Reliability Estimates for a 10-Module SIFT                                  | B-6  |

| Table         | B-7    | Reliability Estimates for a 3-Module SIFT with Coding in Memory             | B-7  |

| Table         | B-8    | Reliability Estimates for 4- and 6-Module SIFT with Coding in Memory        | B-8  |

| Table         | в-9    | Summary of Size and Reliability of Alternative<br>Architectures             | B-10 |

|               |        |                                                                             |      |

PRECEDING PACE BLANK NOT FILMED

хi

#### PREFACE

This report, issued in two volumes, summarizes the work of Stanford Research Institute on Contract NAS1-10920. The goal of the contract was to specify the design of a computer, destined for use as the central computer in an advanced, high-performance commerical aircraft. Because of the critical nature of many of the computations, fault tolerance was the primary design goal of the computer. Other important design goals of the computer relate to

- The matching of the architecture to the aircraft computations

- The capability for expansion or contraction to meet the requirements of various missions

- The suitability to post 1975 technology.

Volume I is concerned with the architecture of fault tolerant computers, that are matched to the aircraft environment. We selected and studied three candidate architectures as part of Task I of the contract. Two of these architectures, Software Implemented Fault Tolerance (SIFT) and Bus Checker System (BUCS) are new and as such are described in detail. The third candidate architecture is a multiprocessor concept that is due to Al Hopkins of MIT-Draper Laboratories. We are aware of the extensive work that has been devoted to fault tolerant techniques and architectures over the past decade. However, a survey of this work has pointed out significant deficiencies in each architecture, for our particular constraints. For the most well-known of these previously studied architectures we document the deficiencies.

Volume II of the report is organized as two parts. Part 1 is concerned with the computational requirements of an aircraft, wherein it is assumed that all of the computations scattered among special purpose analogue and mechanical computers would be carried out by a centralized digital computer. In addition to the usual computations associated with a commercial aircraft, e.g. navigation, stability augmentation, decrab, we also assume advanced cockpit displays and fly-by-wire. These various computations are categorized according to criticality, and for each computation we derive such parameters

xiii

PERCEDING PAGE BLANK NOT FUMED

as memory requirements, processor requirements, iteration rates, the tolerable down time and the amount of data that must be saved in the event of failure. These results are concisely tabulated.

Part 2 of Volume II is concerned with the technology for realizing the central computer. It is assumed that production would commence in the late 1970's. The two aspects of the realization that we consider are concerned with logic and memory and with module interconnections. With regard to logic and memory we assess the various technologies, MOS, CMOS, BIPOIAR, etc., as a function of requirements of speed, reliability, cost, number of units. In addition we discuss such realizations as customized large scale integrated (LSI), medium scale integrated (MSI), programmable logic in the light of the above requirements. With regard to interconnection technology the primary goal is to prevent the propagation of faults beyond some predetermined module boundaries. Various approaches toward achieving this fault confinement are assessed in terms of speed, cost, reliability.

We would like to acknowledge the support of Nick Murray and his colleagues at NASA-Langley--Sal Bavuso, Larry Spencer, Bill Dove, and Brian Lupton. They interacted with us on all phases of the project and provided valuable guidance. On the computation aspects many aircraft and avionic specialists provided us with detailed descriptions of algorithms as well as experience on the conversion of analogue algorithms to a digital representation. With regard to architecture, we have had stimulating discussions with Al Hopkins, Al Avizienis, Bill Carter, Bill Martin, Barry Borgerson and Jim Miller. Many of their ideas are reflected in our candidate architectures.

xiv

#### I INTRODUCTION

#### A. Purpose of the Study

The purpose of this study is to aid NASA in specifying the design of a computer, destined for use as the central computer in an advanced, highperformance commercial aircraft. This computer, or more realistically, computer complex, is to

- be responsible for all of the aircraft computations currently being carried out by analogue, mechanical or dedicated, special purpose digital computers,

- (2) be capable of carrying out computations associated with an advanced aircraft of the type similar to the proposed Advanced Technology Transport (ATT),

- (3) exhibit sufficiently high reliability such that the probability of a computer failure adversely effecting the flight is negligible as compared with other system failures. In particular, the design goal is  $10^{-8}$  failures/hour for the flight critical function. For computations that are not flight critical higher failure rates can be tolerated.

- (4) be readily expandable and contractible so as to meet the needs of various missions,

(5) be matched to the post 1975 component technology. The present study is composed of three tasks, as follows:

<u>Computational Requirements</u>: The purpose of this task is to survey all of the computations being carried out in contemporary commercial aircraft (e.g. navigation, autopilot, autoland, control of cabin pressure) and in the projected ATT (e.g. advanced stability augmentation, collision avoidance). The survey is to reveal aspects of these computations that influence the architecture of the computer including, word size, memory requirements, reliability, recovery time from a failure. Volume II of this report describes, in detail, the algorithms for each computation and extracts from these

algorithms some of the crucial parameters for the individual. computations. Chapter III of this volume summarizes the information and presents a global view of the implications of the computations on the computer aircraft.

<u>Technology</u>: The purpose of this task is to survey the technology associated with the various system blocks of the computer. If this computer is to be produced in large quantities, production will commence in the late 1970's. Volume II of this report discusses in detail the prognoses for the following technologies: logic, main read-write memory, read-only memory, buffer-type memory, back-up memory, and interconnections. For each of these technologies the report discusses speed, reliability and cost.

<u>Architecture</u>: The purpose of this task is to specify the architecture of three candidate computers, each of which can match the computational and reliability requirements, and the technology constraints revealed in the other two tasks. The hardware and software systems of the candidates are to be specified to a level such that the overall reliability can be assessed. In essence then, each candidate is to be specified in terms of a concept, wherein detailed design and analysis is to be avoided unless required for the reliability assessment. For example, a detailed description is needed of the process of recovering from a suspected transient fault, but a detailed description of the arithmetic unit is not needed unless it embodies some particular fault tolerance scheme. This volume summarizes our work on the architecture task.

## B. Organization of the Report

Chapter II briefly reviews the reliability enhancement techniques that have been proposed and analyzed during the past 15 years. Our review is purposely terse since most of these techniques are, by now, well-known. The intent is to delineate a set of concepts that are used in the three architectures.

$\mathbf{2}$

Chapter III is concerned with the implications of the computational requirements task. Here we summarize the results of the computation survey and convert the results into computer parameters: e.g., word size, I/O bandwidth, fault recovery time, multiprogramming characteristics.

Chapter IV discusses constraints on the architecture as revealed by the technology task. For example, we discuss the impact of LSI technology on approaches toward applying redundancy and on the desirability of using slow memories to aid in system recovery. A primary feature of the technology task is a review of interconnection technology, at all system levels (chip-chip, card-card, subsystem-subsystem), and the impact of various approaches to interconnection on the problem of fault isolation.

Chapter V is a "checklist" for the design of a fault-tolerant computer, for the particular aircraft environment that we are confronted with. We summarize here, for example, the fault types that must be accounted for, the various alternative approaches to system design, the components of the reliability analysis, and in general the details to look for in the design and analysis of the computer.

Perhaps the simplest architectural concept that can meet the reliability requirements involves the use of three or more complete computers operating in a locked-step manner. We call such an approach the <u>multi-</u> <u>channel concept</u> (MCC). The basic reliability technique is trivial here-a simple voting or adaptive voting suffices. However, there are still important design decisions required for the multi-channel concept, in particular relating to the operating system procedures for transient fault recovery, and to communication among the computer units. However, we decided not to pursue this concept, for the following reasons

- NASA Langley is in the process of establishing a detailed design and implementation effort based on the MCC.

- Comparable reliability performance can be achieved with a system that consumes less hardware redundancy. Such a cheaper system takes advantage of the possibilities for allocating sub-tasks to independent processor units, and the possibilities for using less costly coding techniques in memory.

• All of the interesting software problems attendant to the MCC are confronted in practically all types of fault tolerant architectures.

In the second half of Chapter V we survey existing architectures that have been suggested for various fault tolerant applications. It is clear that NASA-Langley should pursue an existing concept provided it is matched to the aircraft requirements. The systems that we surveyed are the following:

- Self-Testing and Repairing Computer (STAR) of JPL.

- All Application Digital Computer (AADC) of the Naval Air, Systems Command.

• Experimental Aerospace Multiprocessor (EXAM) of NASA-Electronics Research Center.

- Automatically Reconfigurable Modular Multiprocessor System (ARMMS) of NASA-Marshall Space Flight Center and of Hughes.

- Modular Architecture for Reliable Computer Systems (MARCS) of IBM-Yorktown.

- A Fault-Tolerant Information Processing System for Advanced Control Guidance and Navigation (Hopkins' Multiprocessor) of MIT Draper Laboratory.

This chapter will present detailed information on each of these systems, but for purposes of summary we feel that only the Hopkins' Multiprocessor should be considered as a candidate architecture, although extensive design and analysis must be carried out to ensure that the concept is suitable to our environment. To be fair to the architects of some of the other systems we should state that their concepts have not yet confronted all of the reliability questions. Hence most of the concepts can be adapted to achieve fault tolerance although this design process would probably entail as much work as de reloping a new system from start, and may not produce a better machine than one designed explicitly for the environment we have in mind. Chapter VI presents a discussion of the Software Implemented Fault Tolerance Concept (SIFT), one of two candidate architectures that we designed anew. We recommend that SIFT be selected for pursual in further design phases since it meets all of our reliability, computational, and cost objectives, and, moreover, it is likely to be the least costly in the construction of a prototype. This attractiveness in cost is due to the following factors:

- The fault detection and recovery processes are carried out by software (although firmware or special hardware would also suffice).

- (2) All units could be simple "off-the-shelf" computers, or be realized from existing designs.

- (3) Very little ancillary hardware, (the only exception being a bus structure) is required to implement the concept.

- (4) The architecture is well-suited to varying reliability requirements among the computations.

Hence, the SIFT concept could be experimentally evaluated by programming special executive routines on 3 or 4 minicomputers.

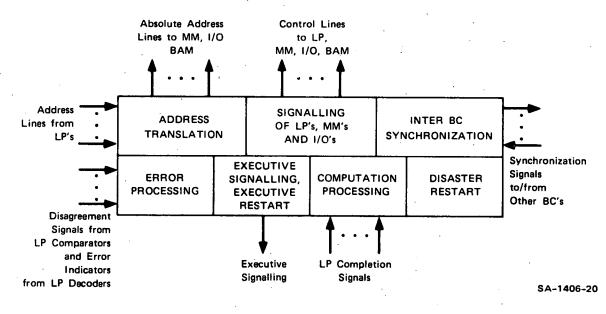

Chapter VII presents a discussion of another, newly conceived candidate architecture, denoted as the Bus Checker System (BUCS). BUCS was inspired by the architectures covered in our survey.

As in SIFT, processing units that are nearly conventional suffice as the primary computing elements. However, the memories utilize coding techniques to enhance reliability at a relatively low cost, and a "smart" bus acts in concert with a software executive to detect faults and reconfigure the system.

Chapter VIII summarizes the characteristics of the three candidate architectures and presents our conclusions and recommendations.

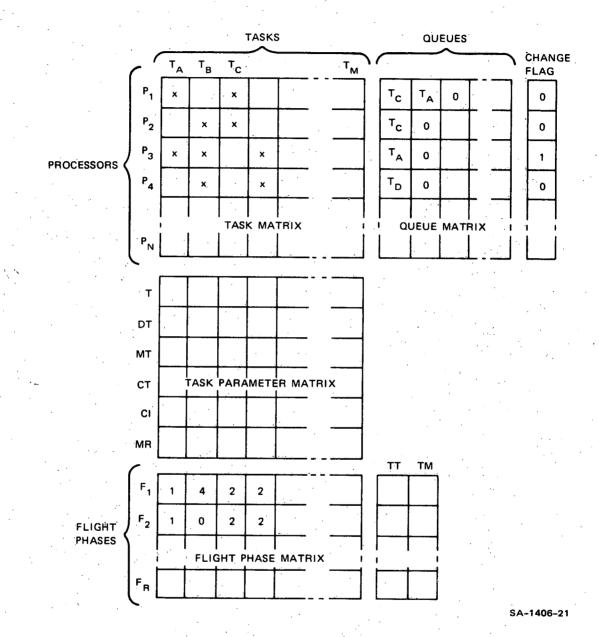

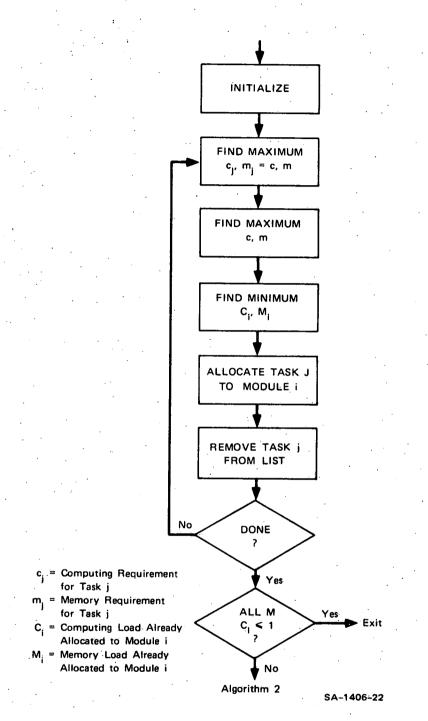

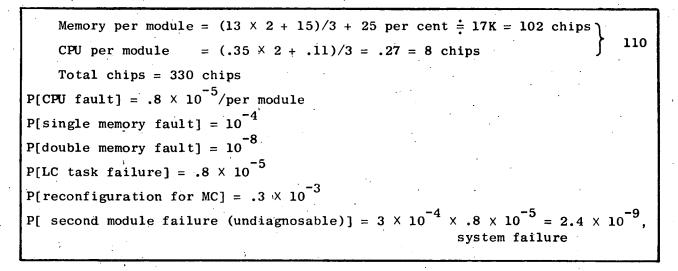

Appendix A describes the detailed design of an algorithm for SIFT that allocates computational tasks to processors. Appendix B presents a detailed comparison of the SIFT architecture with the multi-channel concept, in terms of reliability and redundancy.

### A. Introduction

In this chapter we review the various redundancy techniques for improving digital system reliability that have been proposed during the past 15 years. Our review is intentionally brief since

- (1) There have been no fundamental breakthroughs since our last survey 1 of the field six years ago.

- (2) Most of the redundancy techniques that are theoretically interesting are only applicable at the component level. The constraints imposed by the emerging LSI technology (see Chapter IV) are such that redundancy should be applied over chips, not within the components of chips. Hence relatively few redundancy techniques remain relevant, and moreover system architecture considerations are now of primary interest.

- (3) The underlying concepts are relatively simple.

We have concluded that architectural considerations are of primary importance in the design of a reliable digital computer, as compared with so-called low-level redundancy techniques. For example, workable strategies for recovering from transient faults, or the protection of programs and data in the event of a fault are less understood than abstract redundancy techniques. However, some of these redundancy techniques, originally intended for low-level application, form the basis for enhancing system reliability even when applied at a high level.

The attainment of high reliability in a system requires that

- (1) Faults be detected subsequent to their occurrence.

- (2) Errors produced by these faults be masked or the faulty unit should be disconnected and be replaced by an operational one.

The following terminology has become more or less standard in the reliability field. A <u>fault</u> is the actual malfunctioning of an element. An <u>error</u> is the appearance of incorrect data, on some data line, as a result of a fault. FILMED FRUCT BLANK NOT FILMED 7 Two techniques have been seriously proposed to accomplish fault detection, namely:

- (1) The data lines of the system are encoded so that under fault-free conditions the signals on the data lines form a code word in an error detecting/correcting code. The occurrence of any fault, within a detectable class, is to introduce an error such that a non-code word appears on the data lines. (Duplication is an instance of a trivial error-detecting code.)

- (2) All system blocks are subject to periodic diagnosis in order to determine if a fault has occurred since the last attempt at diagnosis. There are important system questions concerned with such high-level diagnosis, in particular how to account for faulty diagnosing units.<sup>2,3</sup>

A third possible technique involves the use of a checking program that can carry out consistency checks on another program. This technique is not studied here because it is clearly dependent on the particular application programs.

For our application the use of periodic diagnosis is not recommended as the primary fault detection process since

- (a) transient faults are not detected nor prevented from causing data loss by periodic diagnosis,

- (b) the effectiveness of diagnostic routines remains suspect, given the present state of the art,

- (c) the real-time nature of most of the computations precludes the possibility of buffering computed results pending the results of a diagnostic test,

- (d) diagnostic test schedules derived by contemporary systematic approaches usually guarantee detection of only single or double gate type failures. However, in LSI chips more complicated fault behavior seems to be possible including multiple gate faults, and shorts in interconnections.

The diagnostic approach to fault detection does have a role in certain system functions. As we demonstrate later a memory system can be effectively diagnosed provided other auxiliary error-detection techniques are used. Moreover a form of diagnosis is essential in initializing the computer system, and in effecting a recovery from a "massive transient" fault.

One notes that technique (1) incorporates only spatial redundancy while technique (2) incorporates primarily temporal redundancy. That is in the diagnosis approach certain time periods that otherwise would be devoted to useful computation are set aside for purposes of detecting faults. It might be fruitful to explore approaches that combine the attractive features of the spatial and temporal approaches.

Once a fault has been detected, and pinpointed, it remains to apply some form of corrective action. When error correcting codes are used, the decoder can produce at its output the intended code word, thus correcting the effects of the fault. Another approach is to utilize the error detecting possibilities of the code to point to a faulty unit, in which case the faulty unit is replaced by an operational unit. For the diagnosis approach the implication is that the corrective action is unit replacement. One recognizes that there are important questions concerned with unit replacement, e.g., data recovery, and establishing the proper state in the newly connected unit. The solution of these problems is a dominant theme of the later sections of this report. In this chapter we concentrate on fault detection and fault correction using coding approaches.

In Section B below we outline the aspects of coding theory pertinent to this discussion. Section C briefly discusses the use of the trivial duplication and triplication codes in fault detection and masking. Section D discusses the disadvantage (apparent) of utilizing more complicated codes in the processor portion of the computer. Section E demonstrates the use of coding techniques in the memory sections, in particular involving techniques wherein a symbol in a higher order alphabet (greater than two) is associated with an LSI memory chip. Section F presents some comparisons among the techniques for memory systems, and summarizes our views on redundancy techniques for this application.

#### B. Coding Techniques

The following is a very brief background of the pertinent aspects of coding theory. An (n, k;q) code contains  $q^k$  code words of length n, wherein each of the symbols is taken from the field GF(q). The number of redundant digits is r = n - k. The Hamming <u>distance</u> of the code, d, is the number of places in which a pair of code words contain differing symbols, minimized over all pairs of code words. For a code of distance d, any combination of t or fewer errors can be corrected, t < d/2, and any combination of  $\delta$  or fewer errors beyond t can be detected when  $\delta = d - (2t-1)$ . In a linear code the  $q^k$  code words form a linear subspace.

For a systematic code, the encoding processes may be thought of as being applied to an n-digit codeword (X, Y) that consists of a k-digit information portion X and an r-digit check portion Y. The task of the encoder is, of course, the calculation of the Y vector from the X vector, assumed given. For an  $r \times n$  parity check matrix H in echelon canonical form, namely

$$H = [Q_{r \times k} : I_{r \times r}],$$

the computation of Y may be expressed as Y = QX.

The decoding process, when error correction is desired, involves converting a "received" vector  $(X^*, Y^*)$ , which may differ from the "transmitted" vector because of errors, into the code word which is closest in Hamming distance to the received word. The decoding process might only involve <u>error</u> <u>detection</u> in which case the decoding process merely indicates that a received word is not equal to a code word. The decoding process might involve a combination of error correction and detection, in which case, for example, if the received word is within distance two of a code word that code word emerges from the decoder, otherwise an error indication emerges.

The distance properties of the code bear a simple relationship to the columns of the H-matrix. The code has distance d iff (if and only if) all combinations of d - 1 or fewer columns of the H-matrix are linearly independent, and there exists a set of d columns that are linearly dependent. For low distance codes, say d < 4, the decoding process is easily carried

out by reference to the H-matrix. The product  $QX^{*}$  is formed from  $X^{*}$ , and then the reference to the H-matrix. The product  $QX^{*}$  is formed from  $X^{*}$ , and then the received digits are added to form the error syndrome

$$Z = QX^* - Y^*,$$

where it is understood that all of the operations are carried out according to the rules of the field GF(q). An error has occurred if and only if Z is non-zero. For single-error correction, the digit position in error is identified by the corresponding column in H being a nonzero multiple (in GF(q)) of Z. For double error correction the correspondence is between a linear combination of a pair of columns in H and Z.

### C. The Trivial Duplication and Triplication Codes

Perhaps the simplest error detection scheme that can be visualized is to use two independent systems, each computing ostensibly the same result and to compare the results for disagreement. If each system has a single binary output line then the code being utilized is a (2, 1; 2) code, with H-matrix H = [1 1]. If the systems contain more than one output line then the entire system is duplicated, and the corresponding lines in each replicate form the positions of distinct duplication codes. The underlying assumption is that a single fault only introduces an error **on** an output line(s) in one system. Hence, with knowledge of the probability of a fault the effectiveness of the duplication approach can be assessed when incorporated in a system configuration. There are several possible system configurations that use duplication as the basic error detection mechanism. These include

(1) an ensemble of processor pairs wherein one pair is active in computation at a given instant. The detection of an error in this active pair, by virtue of a disagreement, precipitates the replacement of this pair by another pair. It is possible that no effort is expended to diagnose the faulty pair to pinpoint the possible single faulty system--a concept proposed in the Hopkins candidate architecture discussed in Chapter V.

(2) The same concept as above except that a diagnosis is carried out to pinpoint the possibly fault-free unit in a failed pair, and return it to service.

Section F discusses the reliability performance of a coded memory system.

The simplest error correction scheme involving coding is to use three independent systems to carry out a calculation, and to take a majority vote of the results. As in the duplication case above, if each system contains more than one output line, the vote is taken independently for each output line trio. The code being utilized is a (3, 1;2) code with H-matrix

$H = \left[ \begin{array}{c} 1 & 1 & 0 \\ 1 & 0 & 1 \end{array} \right]$

There are several extensions and system implications of this simple triplication code as follows.

- (1) An (n, 1;2) code can be utilized wherein any combination of  $\lfloor (n-1)/2 \rfloor$  or fewer<sup>\*</sup> failures are masked and one extra failure is detected if n is even. The decoder is a threshold network with n inputs and a threshold of  $\lceil n/2 \rceil$ .

- (2) A (3, 1; 2) code is utilized to both correct a single error and to distinguish the system block in error. Thus upon the occurrence of an error some control external to the blocks in question switches out the dissenting block, if it is other than a combinational network, the inserted block must be initialized to the state of the other blocks. Note that in the candidate architectures to be described the switchover is accomplished by an executive operating in part with software and in part with hardware.

The notation  $\lfloor x \rfloor$  and  $\lceil x \rceil$  signifies the largest integer less than or equal to x, and the largest integer greater than or equal to x, respectively.

An (n, 1; 2) code is utilized wherein n is varied as faults (3) occur and are corrected. This adaptive scheme, proposed by Pierce.<sup>4</sup> Goldberg.<sup>5</sup> and undoubtedly others, operates as follows. As in technique (1) above the decoder is initially set at a threshold of  $\lceil n/2 \rceil$ , and thus the system can correct any combination of  $\lfloor (n-1)/2 \rfloor$  or fewer faults (permanent or transient). When the first failure occurs, the malfunctioning block is logically disconnected, whence the code is transferred to a (n', 1; 2) code, where n' = n - 1. The next failure results in an additional decrementing to n'' = n' - 1, and so on until the code length is reduced to three or possibly two. Obviously, this approach (3) exhibits more fault tolerance than technique (1), and is comparable in fault tolerance to technique (2) is generally to be preferred because it is compatible with graceful degradation. Technique (3) is to be preferred only for those applications that cannot endure the switchover time associated with (2), or for those applications that cannot attain multiple transient fault tolerance with technique (2).

## D. Use of less Trivial Codes for Enhancing Processor Reliability

Ever since the coding theorists have demonstrated the effectiveness of error correcting codes in increasing the reliability of information transmission, a search has been underway to uncover a similar concept for computation. There have been numerous noble attempts, but, in our opinion there seems to be no coding technique for the processor portion of the computer that is more effective than the trivial techniques of the previous section. This is especially the case for the processors that are suitable for our environment since they are relatively small, being only about 2,000 gates or several LSI chips.

We divide this discussion into sections concerned with arbitrary logic and arithmetic.

## 1. Arbitrary Logic

By arbitrary logic we refer to the irregularly structured combinational and sequential circuits in a processor responsible for timing, control, condition sensing, register transferring, logic operations, etc. For such circuits no preferred or canonical methods of realization have emerged, and hence in attempting to apply redundancy techniques to such circuits it must be assumed that arbitrary logic is utilized in the realization.\*

The goal of using coding techniques in association with arbitrary logic is to detect the occurrence of failures in a replaceable module, without incurring the excessive redundancy attendant to the use of replication codes. In communication systems, wherein the main design consideration is transmission rate, the redundancy associated with the use of coding is simply r/n, the ratio of redundant bits to code length. The situation is significantly more insidious in the case of coding techniques as applied to arbitrary logic.

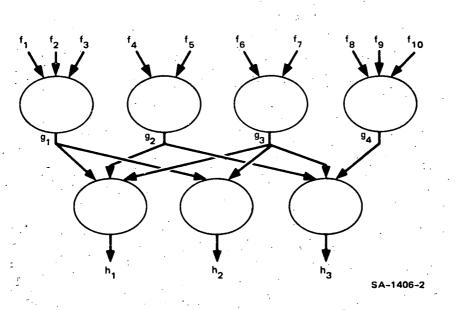

To illustrate this point consider the circuit depicted in Figure II-1, where it is assumed that  $g_1$  is an arbitrary function of  $f_1$ ,  $f_2$ ,  $f_3$ , and is generated in an indivisible module. A similar assumption applies to  $g_2$ ,  $g_3$ ,  $g_4$ ,  $h_1$ ,  $h_2$ ,  $h_3$ . The indivisibility property of the various modules means that a module failure will cause an error in the output. Winograd and Cowan<sup>6</sup> (WC) have suggested a coding scheme to provide fault tolerance in a circuit of the type depicted in Figure II-1. The WC method for this circuit is depicted in Figure II-2. The intention here is to provide a mechanism so that an error due to failure at any level is corrected before it propagates to the next level. To achieve this three extra

Microprogramming techniques for the realization of control functions can eliminate much of the arbitrary logic associated with conventional combinational and sequential realizations. Moreover, the microprogram memory can be made fault tolerant by the relatively inexpensive coding techniques described in Section E below. For the aircraft environment we have in mind the processor(s) constitute a relatively small proportion of the total system and hence, unless a significantly larger computation load is envisaged, the trivial replication coding techniques will suffice.

FIGURE II-1 A NONREDUNDANT CIRCUIT

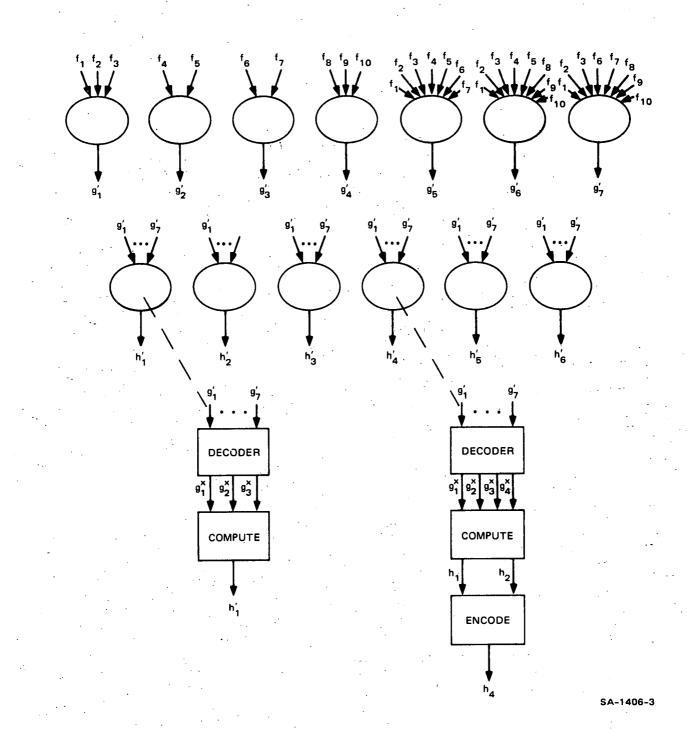

FIGURE II-2 CODED VERSION OF CIRCUIT USING WINOGRAD-COWAN CONCEPT

g-modules are included such that in the absence of failures the signals on the lines  $g_1, \ldots, g_7$  correspond to a Hamming single error-correcting (7, 4;2) code. (The number of information lines at a level, in this case k = 4, is determined by the number of modules in the nonredundant circuit at that level.) At the next level, namely the h-level, the modules produce signals corresponding to a single error-correcting (6, 3; 2) code. (The H-matrices for these two codes are depicted in Table II-1.) The particular way in which this is to be carried out is to provide a set of modules each of which exhibits three roles: (1) decodes the signals appearing on the previous level to produce estimated error-free versions of the signals needed by the corresponding irredundant modules, (2) computes the irredundant signal, (3) encodes the signal so as to produce the corresponding signal in the code at the next level.

This three stage process is illustrated in Figure II-2 for the computation of signals  $h'_1$  and  $h''_4$ . With regard to  $h_1$  the signals  $g'_1, g'_2, \ldots, g'_7$ , are passed through a decoder to generate estimates,  $g'_1, g'_2, g'_3$  of the signals  $g_1, g_2, g_3$ . (If no failures or only a single failure occurred in the ensemble of g modules, then the estimates are indeed the desired signals.) The signals  $g_1, g_2, g_3$  are then combined to form the signal  $h'_1$ . The encoding process for  $h'_1$  is simply the identity operation since  $h_1$  corresponds to an information digit. On the other hand  $h'_4$  corresponds to a check digit, which by reference to Table II-1 is specified by  $h'_4 = h'_1 + h'_2$ . This exclusive OR operation is carried out in the encode portion of the  $h_4$  module.

As we previously mentioned, the coded version, as shown, implementing single error-correcting codes, can mask failures, provided no more than one module in a given level is afflicted. If one measures the redundancy as the number of modules in the coded version, then the cost seems quite favorable as compared with the use of the trivial replication codes. In the case illustrated single fault masking is achieved with less than twice the number of modules. However, one immediately notes that the modules utilized are significantly more complex than those appearing in the original version. This added complexity is both in the number of inputs to the modules and in the functions realized in the modules.

|   | g <sub>1</sub> | <sup>g</sup> 2 | g <sub>3</sub> | g <sub>4</sub> | g <sub>5</sub> | <sup>g</sup> 6 | g <sub>7</sub> |  |

|---|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| 1 | 1              | 1              | 1              | 0              | 1              | 0.             | 07             |  |

|   | 1              | 1              | 0              | 1              | 0              | 1              | 0              |  |

|   | 1<br>1<br>1    | 0              | 1              | 1              | 0              | 0              | 1              |  |

|   |                |                |                | .`             |                |                |                |  |

|   |                |                | •              |                |                |                |                |  |

(7, 4; 2)

$\begin{bmatrix} h_1 & h_2 & h_3 & h_4 & h_5 & h_6 \\ 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 0 & 1 \end{bmatrix}$  (6,3;2)

# Table II-1

H-Matrices for (7, 4; 2) and (6, 3; 2) Codes

In general it is not easy to measure the complexity of the redundant, as compared with the nonredundant case but a few general observations can be made.

- (1) Typically, the realization of modules as LSI chips results in a pin limited design, rather than one which is logic complexity limited. Hence the WC cost measure that relates to the number of modules is not tenable.

- (2) In view of (1) the increase in complexity due to the use of close packed codes, e.g., Hamming codes, is greater than the threefold increase in complexity due to the use of the trivial (3, 1; 2) code.

- (3) The use of low-density codes<sup>7</sup> is likely to decrease the module complexity, but at the cost of more modules. Briefly, low density codes are codes wherein the H matrix has a small proportion of 1's relative to 0's and hence the decoder portion of the module is likely to require fewer inputs.

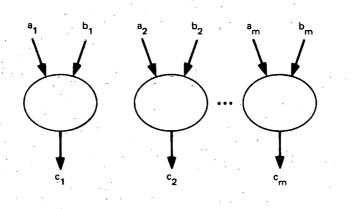

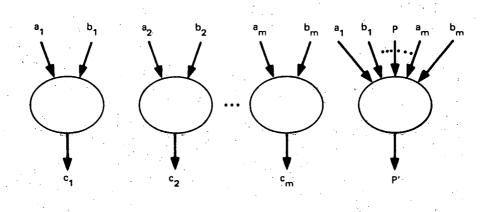

Several modifications of the WC approach are possible to reduce the complexity, and possibly lead to more attractive coding implementations. Instead of supplying an encoder and decoder at each level in a multi-level circuit, it is possible to achieve fault tolerance with a single encoder at the overall circuit input and a decoder at the output. In this case the errors are clearly not corrected at each level in the circuit, but at each level sufficient redundant modules are provided to preserve the code. As an example consider the situation depicted in Figure II-3 wherein, in the nonredundant case, Figure II-3(a), the circuit is a row of AND gates. The code in question is the (n, n-1; 2) code that corresponds to a single parity check. As illustrated in Figure II-3 the input lines to the circuit level include the single parity check P. The parity check P' at the output is to be such that if parity is not satisfied at the input, due to a failure at some previous level, then parity is to be satisfied at the P' levels. Also if a failure occurs in the set  $C_1$ , and  $C_n$ , the parity is also set to be

(a) NONREDUNDANT CASE

(b) CODED CASE

SA+1406-4

satisfied at P'. Thus the equation for P' becomes

$P' = \underline{if} a_1 + b_1 + a_2 + b_2 + \dots + a_n + b_n + P = 1 \underline{then}$  $c_1 + c_2 + 1 \underline{else} c_1 + c_2 .$

It takes little observation of this function to realize that the module computing P' is at least as complicated as the initial row of AND gates. Hence we conclude that, for this type of coding scheme simple duplication is no less attractive for single error detection than more complex coding schemes. A similar conclusion has been reached by Pierce.<sup>8</sup>

For the processors we have in mind it appears that for the detection and correction of errors the simple duplication and triplication codes are the most attractive. We stress that this conclusion is based upon the present art of processor design and of applying codes to arbitrary logic. As we show later, coding techniques as applied to memory are quite attractive and feasible. It is also possible that codes will be useful for portions of the bus systems. Since the application of codes to the system is dependent on the particular architecture, we defer discussion of this question to those sections concerned with architecture.

## 2. Arithmetic