https://ntrs.nasa.gov/search.jsp?R=19740019605 2020-03-23T07:12:01+00:00Z

NASA CONTRACT NO. NAS 9-12990 NASA DRD NO. SE-266TA

CR-128804

# REQ Z H MA 28 UNIVERSAL COMPUTER TEST STAND 80 NDED Genera VINU (RECOMMENDED CQMPUTER TEST C C E E REQUIREMENTS, REPORT) ERSAL POTES Tectric COMPUTER n S Co.) CSCL **JANUARY 19, 1973** TEST 14B G3/11 Unclas 42270 N74-27718

CONTRACT No. NAS9-12990

DRD No. SE-266TA

# UNIVERSAL COMPUTER TEST STAND

(Recommended Computer Test Requirements)

January 19, 1973

Engineer Shay, Project Harris

Program W. Nawor Manager

O'Gara, Manager Β. Subcontracts

## ABSTRACT

#### RECOMMENDED COMPUTER TEST REQUIREMENTS

The objective of this report is to investigate techniques which would be used to characterize aerospace computers with the Space Shuttle application as end usage.

The first section surveys the system level digital problems which have been encountered and documented in several Aerospace Companies. Tests were then devised by these companies to discover the system problems prior to vehicle installation.

From the large cross-section of tests, an optimum set is recommended. The report demonstrates that this set has a high probability of discovering documented system level digital problems within laboratory environments.

The second section defines a baseline hardware, software system which is required as a laboratory tool to test aerospace computers.

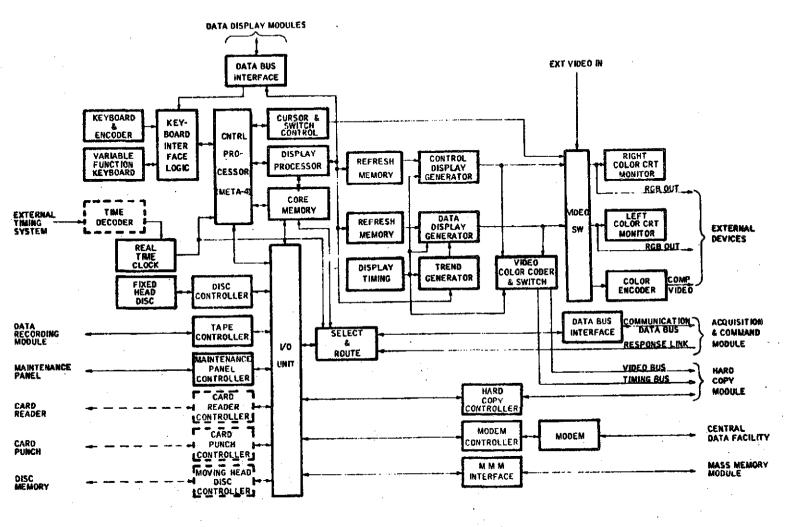

The third section surveys the GSE equipment candidates and recommends the Unified Test Equipment (UTE) as the laboratory system to be considered for the computer test set.

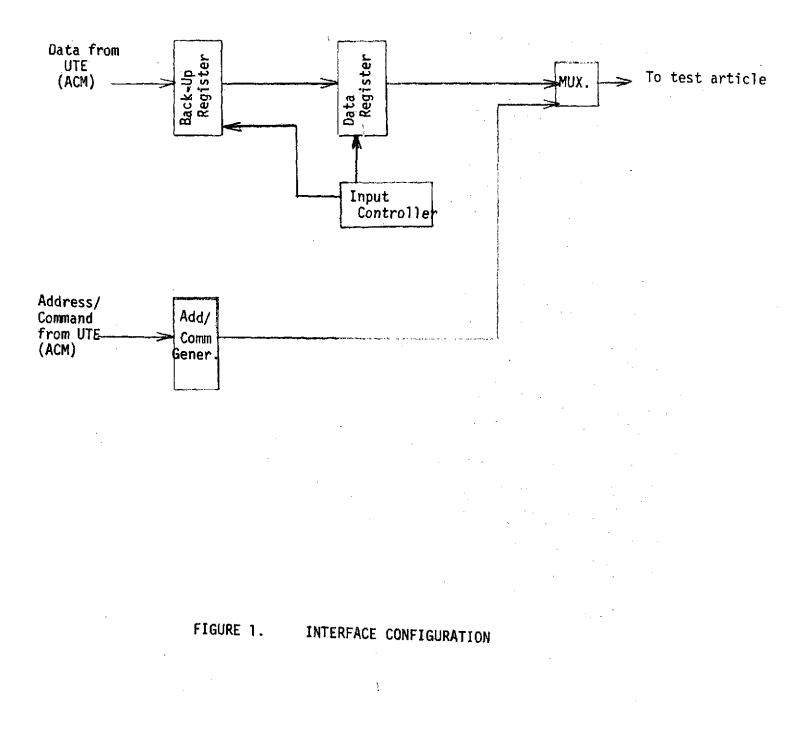

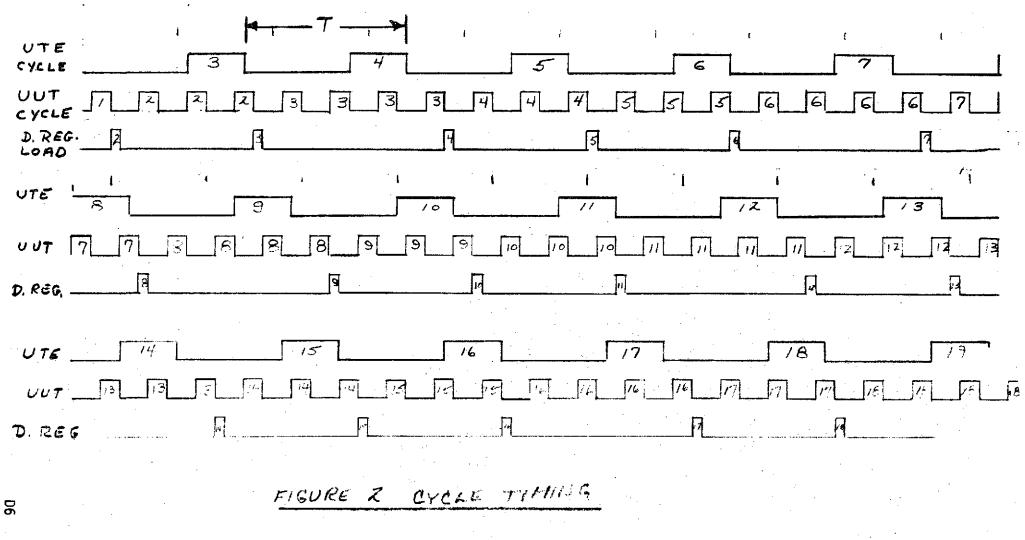

The fourth section of the report contains hardware and software baselines and additions necessary to interface the UTE to aerospace computers for test purposes.

| Ι.   | SYSTEM PROBLEM AND TEST METHOD SURVEY                                                                                                                                                                 | -J                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|      | A. INTRODUCTION<br>B. STUDY IMPLEMENTATION<br>C. GENERAL<br>D. PROBLEM SURVEY AND ANALYSIS<br>E. COMPILATION OF SYSTEM TEST AND ANALYSIS<br>F. BASELINE TESTS<br>G. CONCLUSIONS<br>H. RECOMMENDATIONS | 1<br>2<br>3<br>5<br>10<br>17<br>24<br>25 |

| II.  | UCTS BASELINE SYSTEM DEFINITION                                                                                                                                                                       | 36                                       |

|      | A. INTRODUCTION<br>B. SYSTEM FLEXIBILITY<br>C. EASE OF OPERATION<br>D. GSE MINIMUM REQUIREMENTS                                                                                                       | 36<br>36<br>39<br>41                     |

| III. | SYSTEM TRADEOFF                                                                                                                                                                                       | 44                                       |

|      | A. NOVA 1200<br>B. DDP-516<br>C. PDP-11<br>D. 4PI-EP<br>E. UTE                                                                                                                                        | 44<br>45<br>45<br>46<br>47               |

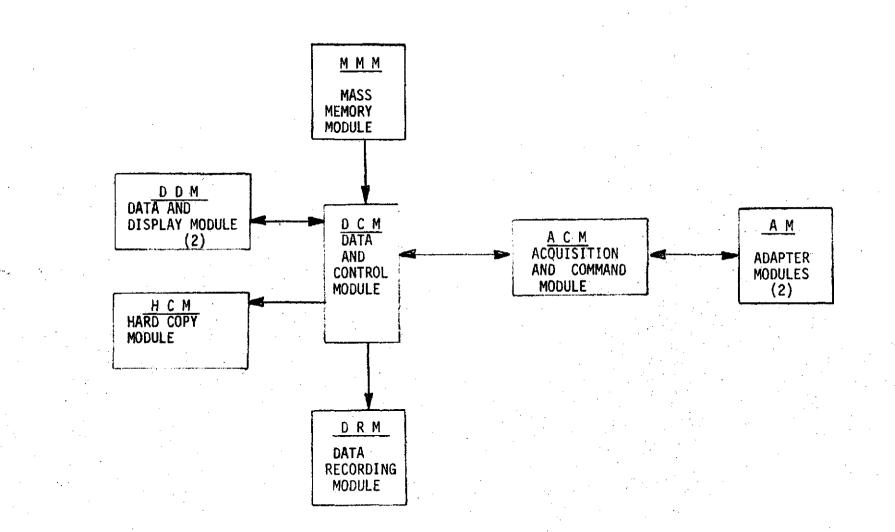

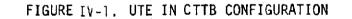

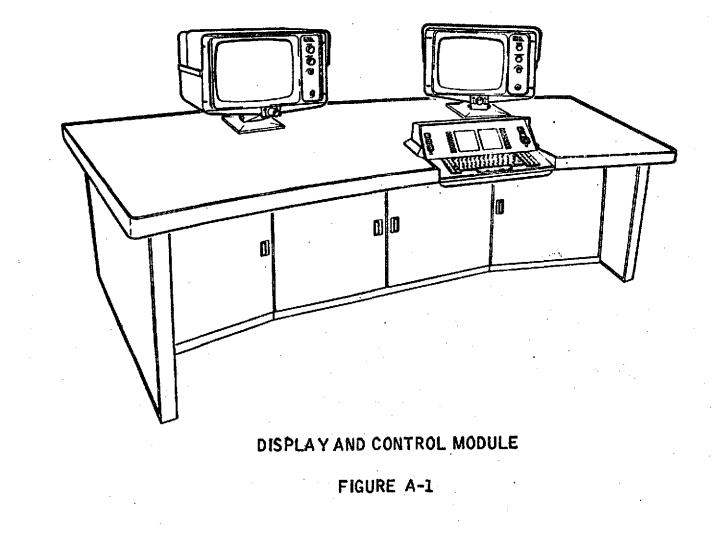

| IV.  | SYSTEM DESCRIPTION                                                                                                                                                                                    | 51                                       |

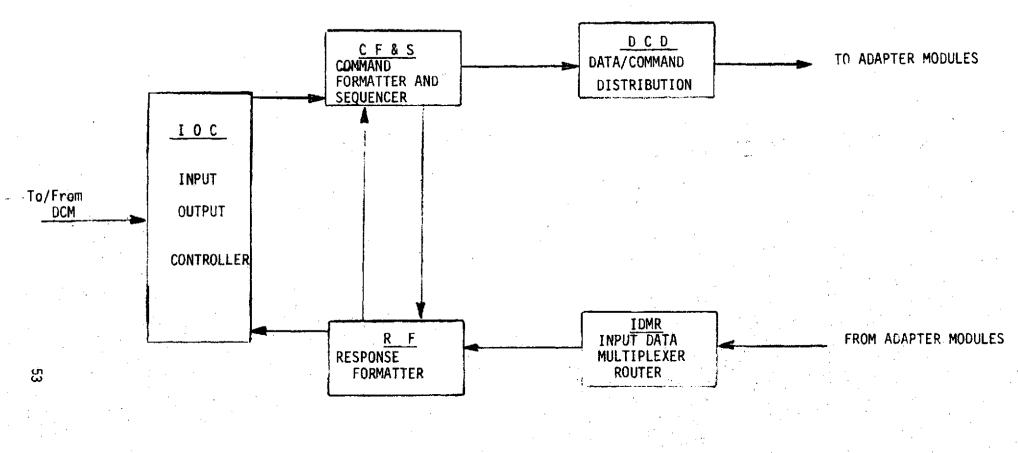

|      | A. INTRODUCTION<br>B. HARDWARE DESCRIPTION<br>C. SOFTWARE DESCRIPTION                                                                                                                                 | 51<br>56<br>71                           |

# PAGE

# APPENDICES

|    |                                                             | PAGE |

|----|-------------------------------------------------------------|------|

| Α. | PROBLEM REPORTS                                             | Â    |

| Β. | TEST METHOD SURVEY                                          | B1   |

| С. | CANDIDATE COMPUTER SUBROUTINE<br>REQUIREMENTS SPECIFICATION | C1   |

| D. | CYCLE RATIO TEST METHOD                                     | 01   |

| Ε. | UTE HARDWARE DESCRIPTION                                    | El   |

| F. | UTE SOFTWARE DESCRIPTION                                    | Fl   |

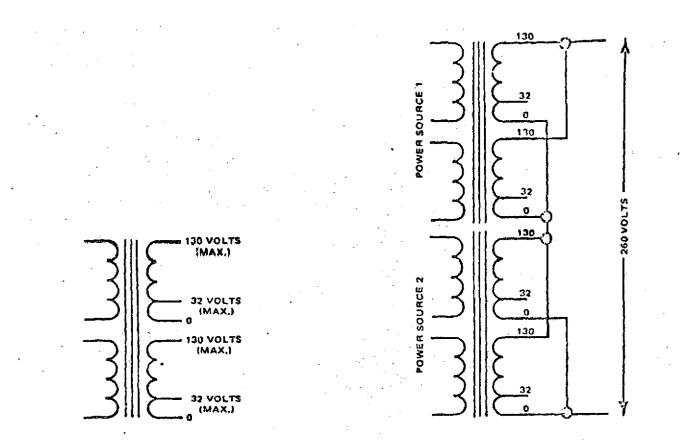

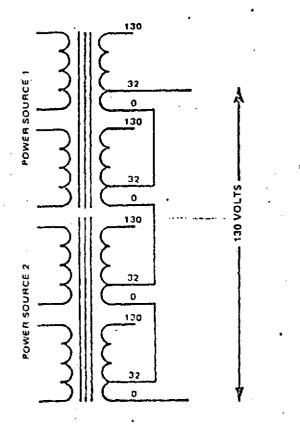

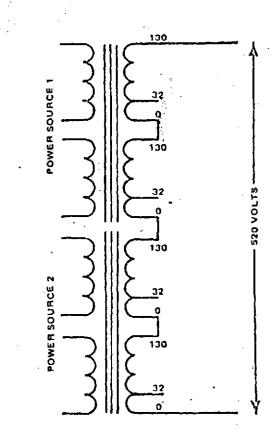

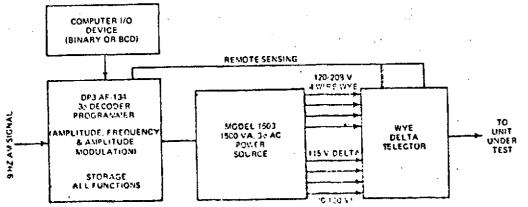

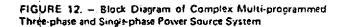

| G. | POWER TESTS                                                 | G1   |

| Н. | THERMO TEST SYSTEM                                          | หา   |

# FIGURES

-

|             |                                 | PAGE |

|-------------|---------------------------------|------|

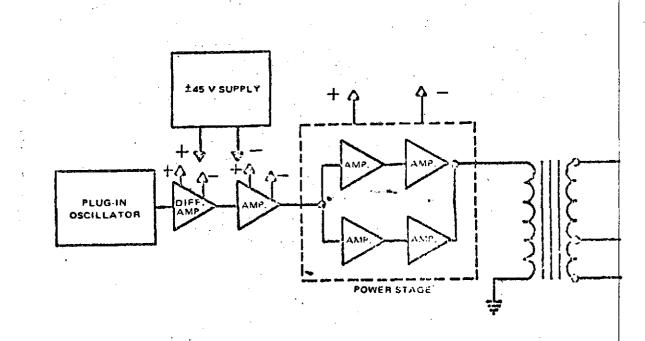

| FIGURE II-1 | UCTS SYSTEM BLOCK DIAGRAM       | 42   |

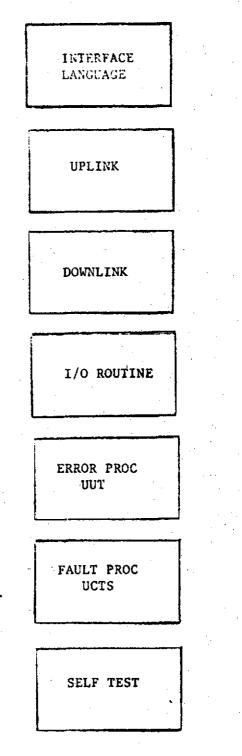

| FIGURE I1-2 | MODULAR SOFTWARE                | 43   |

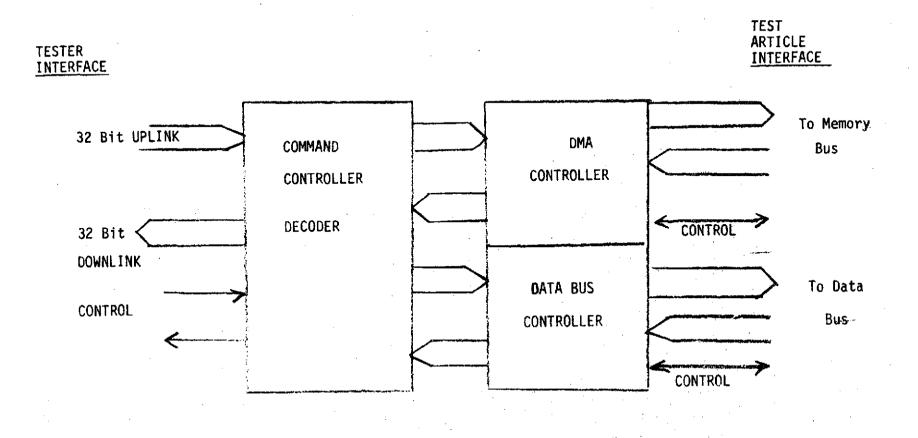

| FIGURE IV-1 | UTE IN CTTB CONFIGURATION       | 52   |

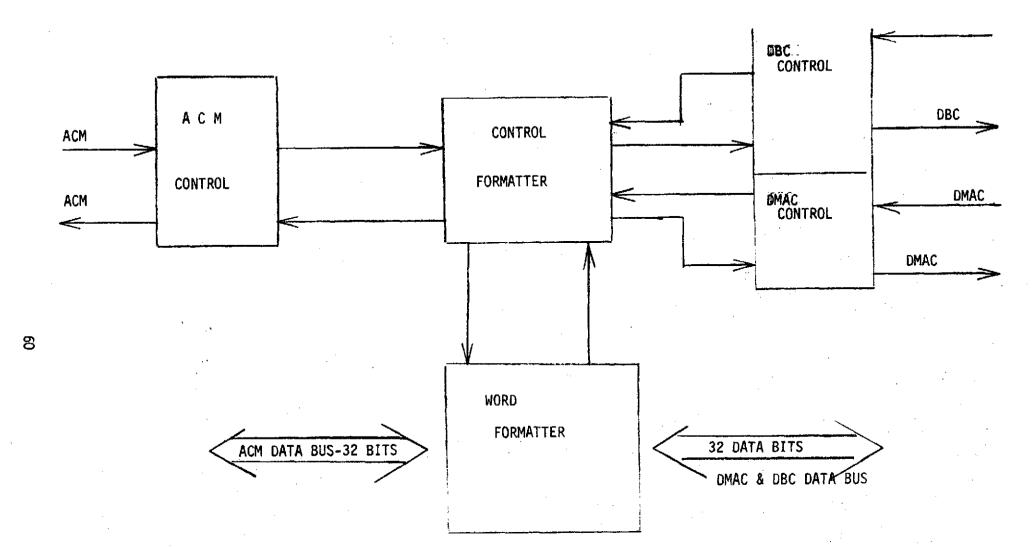

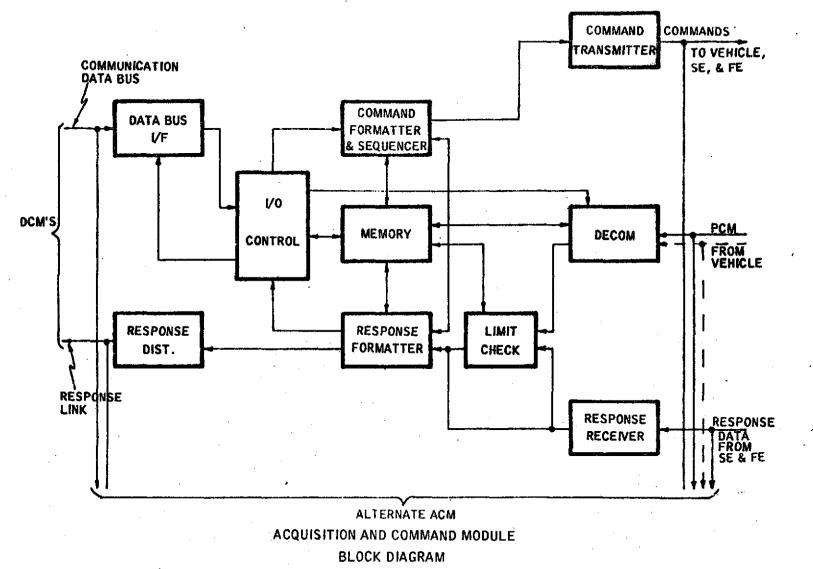

| FIGURE IV-2 | ACM BLOCK DIAGRAM               | 53   |

| FIGURE IV-3 | UTE SOFTWARE MODULES            | 54   |

| FIGURE IV-4 | COMPUTER ADAPTER MODULE         | 55   |

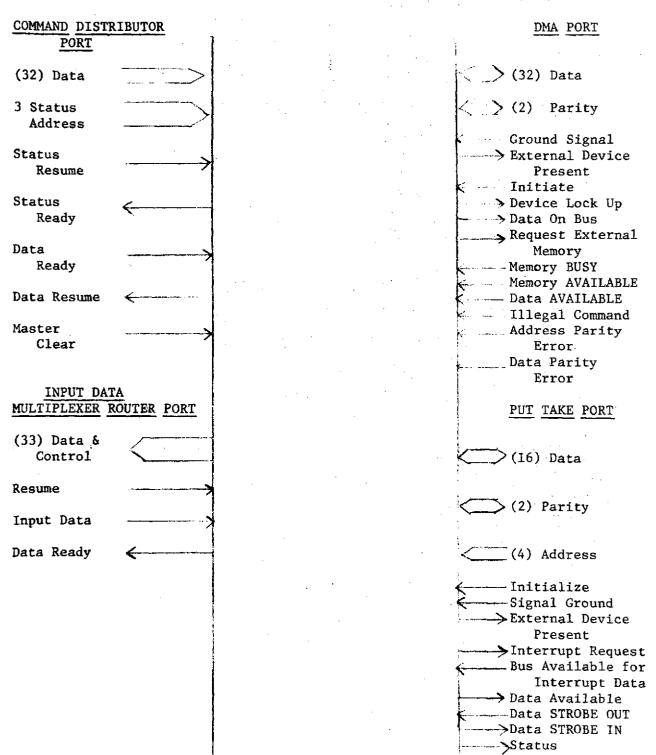

| FIGURE IV-5 | CAM INTERFACE SIGNALS           | 57   |

| FIGURE IV-6 | CCD BLOCK DIAGRAM               | 60   |

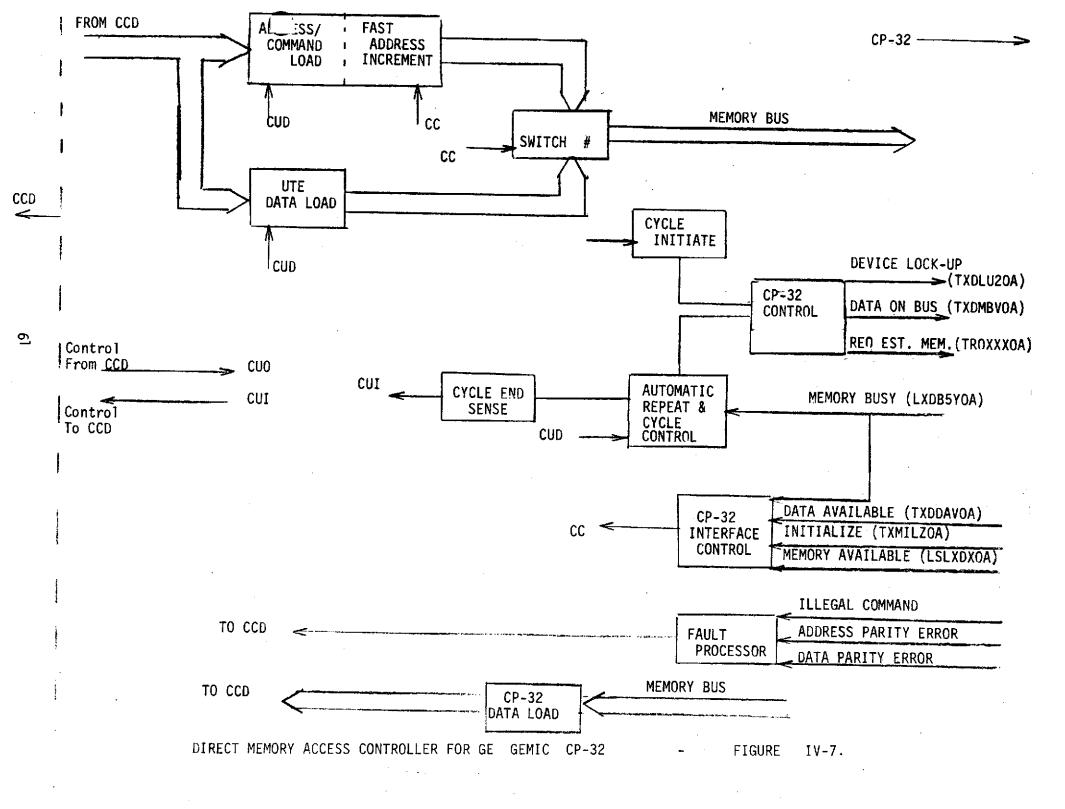

| FIGURE IV-7 | DIRECT MEMORY ACCESS CONTROLLER | 61   |

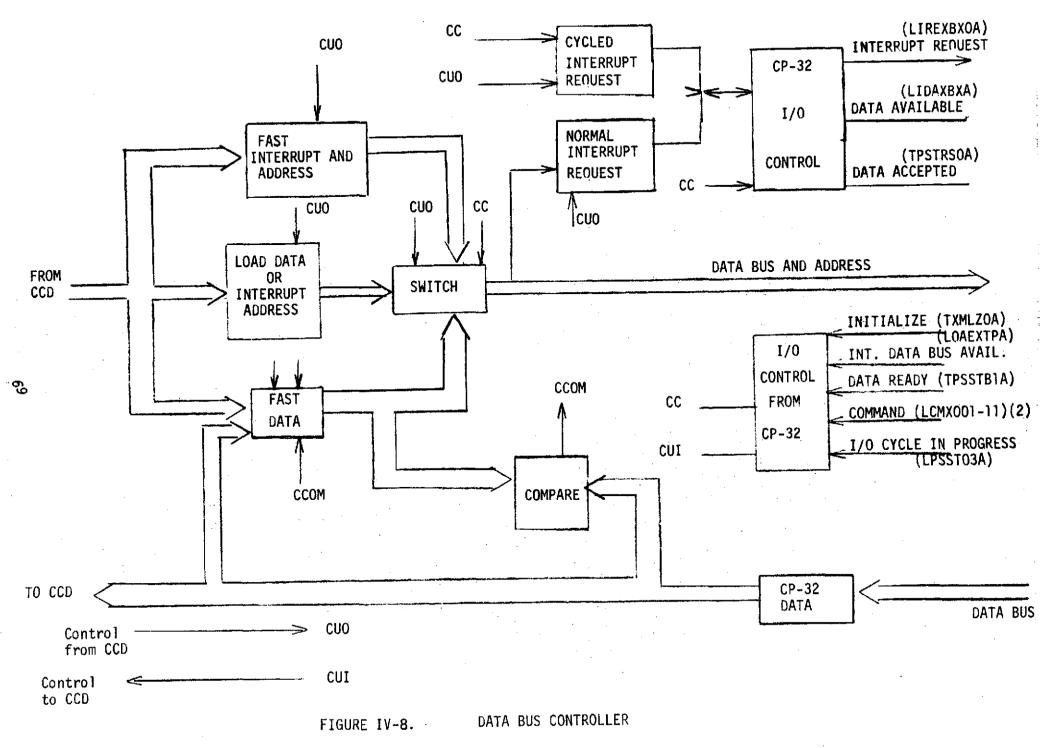

| FIGURE IV-8 | DATA BUS CONTROLLER             | 69   |

# TABLES

|           |                                                                   | PAGE |

|-----------|-------------------------------------------------------------------|------|

| TABLE I   | SURVEY OF SYSTEM DIFFICULTIES<br>DETECTED AFTER NORMAL ACCEPTANCE | 26   |

| TABLE II  | PROBLEM CATEGORY WEIGHTING                                        | 29   |

| TABLE III | ROUND 1 - TEST PREFERABILITY                                      | 30   |

| TABLE IV  | ROUND 2 - TEST PREFERABILITY                                      | 32   |

| TABLE V   | TEST PREFERABILITY RESULTS AFTER<br>6 ROUNDS                      | 34   |

| TABLE VI  | EFFICIENCY RATING ACCUMULATION                                    | 35   |

•

#### I. SYSTEM PROBLEM AND TEST METHOD SURVEY

#### A. INTRODUCTION

The purpose of this study is to arrive at an optimal set of tests to be specified for the Universal Computer Test Stand (UCTS). The tests are to be optimized from a standpoint of test effectiveness, cost and efficiency to uncover digital system problems not normally found in subsystem quality testing.

To achieve this objective, the following guidelines were used:

. Discover and document actual digital system problems

- . Compile a list of tests to uncover those documented problems

- . Optimize and coorelate test and problem data

<u>Digital Problem Survey</u>. This survey was implemented to learn what types of system problems were found throughout the aerospace industry. This gave the survey team an opportunity to document the problems and to have a documented baseline from which to choose system tests. <u>Test Compilation</u>. The tests to detect the problems surveyed were also documented during the "Problem Survey". A large list (37 individual tests) was generated which, if all were implemented on any tester, would require a large amount of time and money.

Optimization and Data Correlation. To reduce the test and problem data to a usable economical form, an optimization technique was used. The Optimization technique which was used was implemented with various weighted criteria and analyzed with a test criterion function equation.\*

\*Woodson, T.T. Introduction to Engineering Design, pp 202-235; 1966; McGraw Hill Inc.

# B. STUDY IMPLEMENTATION

To achieve the study objective it first became necessary to find and document those problems encountered in computer installations. With this completed, it was possible to generate a test list from the survey comprised of various tests designed to uncover the documented problems. It is impractical to design a test for each problem individually. However, by grouping problems of similar nature (i.e. EMI, grounding), tests can be developed to cover a problem category. Thus, there was a need to group problems into categories. At this point the list of problems was divided into categories. The problem categories were compared to the test groups to find an optimal set of tests. A test weighting criteria was established to eliminate the least effective tests. Considerations for the test weighting criteria includes the following:

> - Cost - Test Effectiveness - Problem Severity

<u>Cost</u> - Cost is considered because it will have a direct impact on UCTS hardware cost and test time. Tests which require hours of test time or large quantities of hardware should have low priority considerations.

<u>Test Effectiveness</u> - This criteria is rated against each of the nine problem categories to determine how well the test uncovers the particular problem category. For instance, a test which is only meant for EMI will not be effective against a hardware type problem such as a broken connector pin.

<u>Problem Severity</u> - This criteria considers the severity of the problem in terms of four problem weighting criteria: difficulty of isolation, frequency of occurrence, mission criticality, and safety criticality.

The following example shows the reasoning that made it necessary to consider problem severity. If, for example, Test 1 covers only problem Category A and Test 2 (same cost as 1) covers only problem Category B and each test covers their problem category equally well, which test is better? If problems in Category A are more critical (severe) then Test 1 should be rated higher.

With these three criteria selected, a method was derived to incorporate them into a meaningful test rating figure for each test. These rating figures will then permit the selection of an optimal set of tests.

C. GENERAL

The following summary will detail the implementation of the test study. The summary is divided into five major sections.

- (1) System Problem Survey and Analysis

- (2) Compilation of System Test and Analysis

- (3) Baseline Tests

- (4) Conclusions

- (5) Recommendations

# 1) System Problem Survey and Analysis

This section includes system problems not normally found during Acceptance Tests, but found during system integration. The problems were categorized into nine (9) groups. The groups were then analyzed and weighted against each other to determine the degree of severity for each group. The degree of severity is on a scale of 0 to 24 where 24 indicates a most severe problem and 0 would be the least severe.

The severity of problem group was used as an input to determine the optimal group of tests.

#### (2) Compilation of System Test and Analysis

This section consists of a test list and the analysis of that list. Each test was given an efficiency rating from 0 to 1 for each problem category. A test that was judged to be very effective in uncovering a type of problem was given a high efficiency rating (near 1) for that problem category.

Considering the efficiency rating, problem severity, and cost, a list of highly efficient tests are recommended for the purposes of evaluating Space Shuttle candidate computers.

#### (3) <u>Baseline Tests</u>

This section contains a list of functional tests which were deemed a minimum requirement to gain insight into the performance of each candidate computer.

#### (4) Conclusions

The results of the problem and test survey are presented including the recommended optimum test list and the minimum baseline tests to be performed.

# (5) <u>Recommendations</u>

A recommended list of tests and procedures are presented in this section.

# D. PROBLEM SURVEY AND ANALYSIS

#### 1. Introduction

This section includes the list of System integration problems which were compiled from several sources categorized and weighted as to severity.

#### 2. Background

The main purpose of the UCTS is to detect problems generally not found until the computer is installed and operational. It is therefore felt that the purpose of the UCTS is to find those problems that have previously gone undetected through qualification tests, but were then found during system integration testing. This background led to the different weighting factors which were assigned to the problem analysis criteria.

## 3. Object

The object of this survey is to obtain from several sources, information which pertains to system problems not normally detected during final factory Acceptance Testing. Data was obtained from several sources within the General Electric Company, from Grumman Aerospace Corporation and from Apollo History documents. Listed below are the various sources from which digital system problem data was obtained:

a. General Electric, Aerospace Electronics Systems Dept., Utica, NY

b. General Electric, Ordnance Systems Division, Pittsfield, Mass.

c. General Electric, Space Systems Operation, Valley Forge, Penna.

d. General Electric, Apollo Ground Support Dept., Houston, Texas

e. Grumman Aerospace Corporation, Bethpage, Long Island, N.Y.

f. Apollo Problem History Report, compiled by Draper Laboratories at Massachusetts Institute of Technology.

Due to the nature of the information gathered from the above sources, the specific programs cannot be revealed. Appendix A contains a complete list of the problems surveyed.

4. Results of Survey

Table 1 shows the results of the problem survey. It is shown that the various problems fit into categories with four (4) to eight (8) individual different problems in each category. These categories are listed below:

| Design<br>EMI | Memory<br>Noise | Hardware |

|---------------|-----------------|----------|

| Grounding     | Power           |          |

| I/0           | Software        |          |

Within each category there are two subcategories which describe the problem symptom and the eventual cause of the problem. These two categories were used to analyze the problem severity and will be discussed below. It was found that after obtaining data from more than two of the above sources, the problems started to repeat. For instance, the problem symptom of "computational errors" under the category of NOISE was documented twice by the survey team as shown in Table 1 by the two in parenthesis (2).

Once a large percentage of individual problems exhibited similar characteristics, it became meaningless to continue the survey.

5. Analysis of Data

5.1 Introduction

The data as previously noted was divided into nine categories. An individual problem, however, because of its complex nature might appear in more than one category. An example of this is the "computer stoppage" symptom which appears in the Design, EMI, Noise Power, software and hardware.

Several problems were classed in more than one category. An example of this is the case ground to signal ground isolation problem. This was categorized both in EMI and Grounding. As a result, a circled number appears next to this problem. A circled number next to a problem indicates that this problem is categorized elsewhere in Table 1.

Once the entries were categorized, it was necessary to determine which category of problems was more severe than others so that these values could also be used for test organization. In order to determine this, a problem severity concept was adopted using the following criteria:

- Difficulty of Isolation

- Frequency of Occurrence

- Mission Critical

- Safety Critical

Weights were assigned to each of the above criteria based on the importance of each with respect to the objective of the study. The study objective as pointed out above is to find the optimal test which will be the most cost effective to test the most severe problems.

#### 5.2 Weighting Philosophy

Those problems that are most difficult ( and therefore expensive ) to find are the problems that will obtain the most attention by the UCTS. For this reason, the first (of a final four) problem weighting criterion was developed. This criterion, termed Difficulty of Isolation (DI) was given a maximum rating of 10. If a problem was hard to isolate, it would receive a DI of 10, if not so difficult, such as a broken wire, the DI might be 2.

It was felt that emphasis should be given to problems that occurred often within any one category. This frequency of occurrence concept should be closely tied to difficulty to isolation as it is only those problems that are difficult to isolate that are going to be well documented and, as a result, covered in the problem survey. The Frequency of Occurrence (FO) criterion was developed to handle this concept and was assigned a lesser maximum value of 8. (Not quite as important a criterion as DI but still an important factor in the determination of relative problem category "importance").

What if two problem categories are rated equal after DI and FO determinations? There were two criteria that were developed to be deciding factors in such close cases. If a problem is determined to be safety critical or critical to mission completion, it should contribute to the severity of the problem.

In the case of the UCTS, safety criticality or mission criticality of problems should not be a major consideration in problem severity because it is assumed that those problems which the UCTS is responsible for finding are problems that would have been eventually found (after computer installation but before the actual mission).

For all these problems that would have been found before the actual mission, the question of safety and mission becomes academic, for those problems are assumed to be solved before the mission and then do not exist during the mission.

For this reason, these two criteria were rated low (not severe) compared to DI and FO. Safety criticality (SC) was assigned a

maximum of 4 and mission criticality assigned a maximum of 2; safety being of greater importance than mission, assuming manned flights.

#### 5.3 Problem Weighting

All individual problems within each category were then assigned a value for DI (from 0 to 10), SC (from 0 to 4) and MC (from 0 to 2). From these values an average DI, SC and MC was derived for each problem category.

The problem category weight then became the sum of the category's average DI, average SC, average MC and FO. Where the category FO was the ratio of the number of problems in the category to the maximum number of problems in any category, multiplied by the maximum number of problems in any category, multiplied by the maximum scale rating for FO (8).

The equation used to determine average DI, average SC, average MC and FO are as follows:

F0<sub>j</sub> =

Difficulty of Isolation

$DI_{j} = \sum_{i=1}^{N_{j}} \frac{DI_{ij}}{N_{j}}$ (1)

N<sub>j</sub>

$\frac{1}{N_{j}} \cdot \sum_{\substack{j \\ \substack{k \\ j}}}^{N_{j}} \left\{ SC_{ij} \left\{ (0-4)^{k} \right\} \right\}$ (3)

(2)

Frequency of Occurrence

Safety Critical

Mission Critical MC =  $\frac{1}{N_j}$ ,  $\frac{N_j}{N_j}$  (0-2) (4)

Where the subscript j indicates the jth category (i.e. EMI), Nj indicates the number of problems in the jth category and  $N_{max}$ is the maximum number of problems in a single category. DI<sub>j</sub>, FO<sub>j</sub>, SC<sub>j</sub> and MC<sub>j</sub> are the difficulty of isolation, frequency of occurrence safety criticality and mission criticaltiy, respectively of the problem category and DI<sub>ij</sub>, FO<sub>ij</sub>, SC<sub>ij</sub> and MC<sub>ij</sub> are the ith problem in the jth category for each parameter. The expression

(a-b) represents the phrase " on a scale of a to b." The results of weighting and summing are shown in Table II. The weighting was a committee effort of hardware digital engineers and the results shown represent a consensus of opinion of those engineering.

#### 5.4 Results of Weighting

Table II indicates that several categories contain critical problem areas (EMI, Power and noise). The total severity of weighting for these three categories ranges from 16.7 to 17.7.

The next most severe problem categories are shown to be design, grounding, memory and software with a range of 13.7 to 14.9.

The least severe problem categories are the I/O, and hardware with weighting of 11.4 and 7 respectively. The results of the problem category weighting have no real meaning until it is used in the test effectiveness analysis.

#### E. COMPILATION OF SYSTEM TEST AND ANALYSIS

#### 1. Introduction

This section contains system tests used by manufacturers which were surveyed in Section D-3 of this study to uncover system integration problems found after in-plant subsystem acceptance tests had been completed. Also contained herein are various tests which are used to assure that the digital equipment meets design specifications.

#### 2. Background

As pointed out previously, this study concerns itself with test practices of digital equipment manufacturers. Since the Military Standards are well documented, this section of the study concentrates on tests which the surveyed manufacturers have imposed upon themselves which are in addition to or parallel with

those documented in the Military Standards. These tests were necessary to uncover those documented problems and to test specifications unique to each manufacturers digital equipment.

3. Object

The object of this study is to compile a list of system tests and analyze those tests. An optimum set of efficient tests will be generated as a minimum set of tests to be used by the UCTS.

#### 4. Results of Survey

The survey resulted in a comprehensive list of tests which were used by different manufacturers to uncover the documented problems listed in Table I of this report. These tests are listed in Appendix B of this report.

#### 5. Analysis of Data

#### 5.1 Introduction

The first step in the test analysis was to judge the effectiveness of each test in uncovering problems in each problem category. Evaluations were also made in regard to relative test expense. Overall test effectiveness was then evaluated on the basis of test efficiency, problem category weighting, and test cost considerations. An optimized list of tests was then compiled by combining overall test effectiveness with a mathematical technioue designed to compensate for overlapping test coverage (redundancy considerations).

#### 5.2 Weighting Philosophy

As previously stated, the objective is to optimize the test list for UCTS operation. In order to do this, an analysis of test quality was made. It is important that the judgment be made on the lowest feasible level in order to make the judgment as objective as possible.

#### 5.2 Test Weighting

All tests were judged on the same criterion. Each test was assigned an efficincy rating (E) for each of the nine problem categories based on a scale from 0 to 1. A test would be analyzed in each problem area by making judgment as to how well that test could bring about the discovery of computer problems in that category. The more "efficient" (capable) a test was in detecting problems in a particular problem category, the higher (closer to 1) its efficiency rating (E) would be for that category. For example, a test designed specifically for power problem detection would have a high E for the power category but probably would have a low E for the memory category because of its inability to detect a memory failure of the computer.

After assigning an efficiency rating to each test for every problem category (nine ratings per test), each test was given a cost factor (I) based on 0 to 1. A test deemed relatively expensive would have a high I (near 1) while an inexpensive test would have a low I.

#### 5.4 Overall Test Effectiveness

A basis was formulated from which overall test effectiveness could be made. Effectivness variables included, problem weights, cost factors and efficiency ratings of each test for every problem category.

A criterion function was developed to handle these test parameters in a meaningful way.

The criterion function (CF) developed was:

$$CF_{i} = \underbrace{j = 1}^{9} \quad \overset{W_{j}E_{ij}}{1 + I_{i}}$$

(5)

Where CF<sub>i</sub> = Criterion function of Test #i

I; = Cost factor of Test #1

W<sub>i</sub> = Problem weight of problem category #j

$E_{ij}$  = efficiency rating for test #i on problem category #j This function favorably ranks inexpensive tests which efficiently detect a broad range of problem categories. When tests become more expensive, or less effective in detection of problems, or less effective in their detection of a wide variety of problems; their criterion function (overall test effectiveness) drops accordingly. This particular CF gave appropriate significance of each test parameter to the total evaluation of the test in question.

Cost factors, efficiency ratings, and CF's are tabulated in matrix form for each test (Table III). This matrix also includes the partial products  $W_j E_{ij}$  for each test in each problem category.

5.5 Redundancy Considerations

5.5.1 Purpose

?

Results of Table III indicate that Test #1 (Transient Radiation) is the best overall test that was analyzed. Test #2 has the second largest CF but this should not necessarily mean that Test #2 is the second best overall test.

There were many of the proposed tests which would uncover the same type of problems. Therefore, these tests would overlap their problem solving abilities. To avoid recommending different tests that have redundant problem solving abilities, a technique was developed to decrease intra-test redundancy.

As an exaggerated example, assume that the first test selected (highest CF) detected all noise and power problems ( $E_{power} = E_{noise} = 1.00$ ) but not other type ( all other E's = 0). Also assume that the test with the second largest CF and  $E_{power} = E_{noise} = 1.00$  with all other E's = 0. It is obvious that with the best test implemented, the test with the second highest CF adds nothing to the problem detection ability of the first test. It is necessary for optimization to consider and remove the redundancy between tests already selected and tests still being analyzed.

#### 5.5.2 Redundancy Technique

After the first matrix was completed (Table III) which contains weights for overall test effectivness for each test, Test #I was selected as the best test. The efficiency ratings of Test #1 were then used as a percentage of problem coverage for each respective problem category.

The efficiency ratings of all remaining tests were then retabulated (to the nearest hundreth) taking problem coverage by previously selected tests into account. New ratings become:

$E_{ij} = E_{ij} (1 - E_{j \text{ Total}})$ where  $E_{ij} = \text{new adjusted efficiency rating for Test #i}$ on problem category #j

E<sub>ij</sub> = original efficiency rating (from first matrix)

E<sub>iTotal</sub> = total problem coverage.

This is the sum of the test efficiency ratings of all previously selected tests for problem category j. The test efficiency ratings used are the ones tabulated for the test at the time it was selected.

#### 5.6 Finalized Analysis Procedure

The first matrix was established as previously indicated (see Table III). Test #1 had the highest CF. The efficiency ratings of this test then became the total problem coverage  $(E_{jTotal})$ . New efficiency ratings were then used (as in first matrix) to form a second matrix to select the second best test. See Table IV for second matrix.

The highest CF on this matrix was Test #3. The efficiency ratings of Test #3 used in this second matrix (Round #2) were then added to the total problem coverage to form the new total problem coverage to be used in Matrix #3 (Round #3). This was continued until all problem categories had a high rate of being detected.

#### 5.7 Analysis of Results

Table V is a table of results derived from the matrix analysis. Each test number appears with its rank after each round of matrices. The tests were ranked after each matrix (round) completion

(6)

according to their CF's. Ranks went from 0 to 36 with 0 rank given to the highest CF (Test #1). After a test was selected, its rank was frozen in subsequent rounds. This enables quick examinations to be made from one round to another to detect test rank shifts due to redundancy compensations.

Notice that between Rounds 1 and 2 there is considerable shifts in rank, especially in the tests with low rank numbers. For example, Test number 8 was ranked 3 after the first round, but dropped to a rank of 6 after the second round.

Generally, in the first few rounds, numberous rank changes took place. This was due to the fact that the first few tests selected caused significant changes in new problem coverage percentage for the succeeding matrix. Table VI shows the problem coverage percentages in each problem area after each round was completed. Notice how drastically these percentages change over the first few rounds while by the 5th or 6th rounds, percentage changes were comparatively minor.

This trend explains why rank changes from the 5th to the 6th rounds were minor; and as a result of these facts, we propose to let the ranks of the 6th round stand as a test order criterion for the tests suggested in this report. This list provides a basis on which an optimum test set can be proposed.

5.8 Results of Redundancy Considerations

After six "rounds" of redundancy matrix manipulation, six tests were selected as the best overall tests to detect the documented problems. The following shows the accumulated test effectiveness

for the problem categories: Design (58%); EMI (91%); Grounding (60%); I/O (66%); Memory (81%): Noise (88%); Power (77%); Software (28%); and Hardware (81%). These test effectiveness ratings express an anticipated percentage of problem discovery in the various problem areas. Thus, after the selection of the best six tests, the problem area of software is still relatively neglected. In order to add significant coverage to this problem area, Test #2 (ranked eighth) must be included. This will increase software coverage about 50%.

This indicates that an optimum set of tests include the tests ranked one to eight. These eight tests provide a maximum (approximately 73% coverage) problem coverage for such a limited number of tests.

#### F. BASELINE TESTS

#### 1. General

The following set of tests are recommended as a minimum to evaluate the performance of a candidate computer. It is suggested that the following tests be performed to obtain computer performance baseline.

The tests are divided into three sub-classes, each designed to test a particular test article function.

The sub-classes are:

Primitive Diagnostic Tests Computer Functional Tests Simulated Space Shuttle Environment Tests  Primitive Diagnostic Tests consist of six tests designed to discover that part of the computer hardware which may have failed during evaluation testing:

The Primitive Tests include:

Memory Test I/O Test Arithmetic Test External Interrupt Test Address Modification Test Complex Instruction Test

a. Memory Test

The memory test will consist of writing into and reading from memory through the Direct Memory Access (DMA) port. The test will include putting through simple data words at a reasonably slow rate. If the read data differs from the written data, it can be assumed that the memory is not functioning properly.

b. <u>I/O Test</u>

This test involves an I/O transaction through the program controlled input-output port with memory interaction optional. This test is designed to ascertain health of the logic and software involved in I/O transactions.

c. Arithemtic Test

This test will ascertain the health of the arithmetic unit by requiring execution of some elementary arithmetic functions such as add or subtract.

d. External Interrupt Test

This test will ascertain the health of the interrupt logic and software and will be accomplished by sending external interrupts from the UCTS to the Test article.

#### e. Address Modification

This tests the ability of the software and hardware to modify addresses as specified by the manufacturers literature. This test involves all the hardware previously mentioned plus additional registers and control logic for working storage and control respectively. This will also help ascertain the effectivity of the illegal modification traps.

#### f. Complex Instructions

Once it has been established from the above tests that the computer can execute individual simple instructions and can modify addresses, then the health of the remainder of the machine can be diagnosed by requiring it to do complex instructions (i.e., floating point divide, etc).

3. Computer functional tests are designed to ascertain the performance of the candidate computer in comparison to the manufacturer's specifications. These tests measure accuracy and execution time of certain tasks listed below:

> Computational Ability Time Class of Instructions Matrix Manipulation Logical Ability I/O Efficiency I/O - DMA Efficiency Memory Exerciser Code Conversion Math Routines

#### a. <u>Computational Ability</u>

This test involves high Central Processor Unit (CPU) usage over a relatively long time span (minutes). This test is designed to test the computational ability of the machine and catch any timing problems that tend to build-up after several minutes of operation.

b. Time Class of Instruction

In order for the computer user to get a working feeling for the speed of his machine, some elementary timing measurements must be taken. The goal of this test is to time a class of instructions such a general register, transfer and bit manipulation. The machine would repeat that instruction several times. Measurements of speed of each instruction would be accomplished by taking the total time for repeated instruction execution and dividing that time by the number of instruction executions. This test should be done with several individual instruction classes.

#### c. Matrix Manipulation

An evaluation technique which requires high computational ability and many other features such as shift and bit manipulation is contained in a matrix manipulation program. This test will time the matrix program process and measure its accuracy.

d. Logical Ability

This test is designed to ascertain the ability of candidate computer to perform shifting tasks, incrementing, list manipulation and general overhead functions. Time and accuracy of this program execution will be the measurement criteria.

#### e. I/O Efficiency

A critical parameter from subsystem integration point of view is the through-put of the machine at the program controlled I/O port. This test is designed to evaluate that parameter by presenting information at the I/O port. the data will be presented at a constant frequency and the test article will be programmed to run at maximum I/O frequency. By monitoring the data accepted by the test article, the true maximum I/O rates can be ascertained. Appendix D contains an explanation of this method along with reasons for its use.

#### f. DMA Efficiency

This test is performed in the same manner as in 3(e) except the computer port now being exercised is the DMA.

#### g. I/O-DMA Efficiency

This test involves exercising both I/O and DMA ports simultaneously at a changed frequency to ascertain the ability of the computer to handle heavy throu put loads on both ports.

#### h. Memory Exerciser

This test is designed to detect memory problems such as "bit creep" and memory noise in the mainframe memory whether core or plated wire. The memory is exercised at a high rate with a worse case "noise" pattern for the purposes of uncovering missing or changing bit problems which may occur under worse case noise conditions.

#### i. Code Convert

NASA expressed a need for conversion of fixed to floating point and back to fixed as part of the Space Shuttle Requirement. This test is designed to measure the performance of each individual computer to perform the conversion task. The test is designed to measure the accuracy and time involved to accomplish the conversion.

#### j. Math Routines

For computers such as guidance and navigation computers, certain mathematical subroutines must be executed. These include but are not limited to sine, cosine, arctan and square root. This test will require the execution of these functions with speed and accuracy as measurement criterion.

#### 4. Simulated Space Shuttle Environment Tests

This series of tests will be used to ascertain the effectiveness of the candidate machine to handle space shuttle type programs.

These tests are listed below:

Round Robin Evaluation Concurrent Jobs

#### a. Round Robin

The round robin in the space shuttle vehicle takes advantage of at least two pieces of hardware, the computer and an external data acquisition unit. The data acquisition unit is continually polling all subsystem sensors. When changes larger than a programmed delta occur in the sensor status, the result is stored in a change stack. The change stack contains both the sensor address and change data.

The computer software system takes advantage of the rotating "change" stack with a software pointer, pointing to the location of the hardware pointer. The contents of the hardware pointer specifies the address of the last variable to be written in the stack. This data contained in the stack is then transferred into main memory and properly acted upon.

In simulation, the UCTS computer inputs data into the change stack through the DMA port. The frequency at which the list is updated is increased at controlled increments. The number of words which are fed to the change list are counted by a hardware counter.

The test computer then reads a hardware counter and the data between the location of the hardware pointer through the last address to be written in.

Data is checked, sent back to the candidate computer at a higher rate, being counted by a hardware counter until overload occurs.

If the hardware counter indicates more word transfers than the stack is capable of handling, an overload condition results. This point is then recorded as the saturation point of the round robin program.

This test measures the ability of the candidate computer to handle high data rate changes under simulated space shuttle conditions.

# b. Concurrent Jobs

This test involves the round robin evaluation coupled with simultaneous mathematical routine execution, code conversions and I/O, DMA transactions. Data for computer evaluation includes time and accuracy of intermediate results as well as final results.

## G. CONCLUSIONS

#### 1. Introduction

The results of the study showed that a set of optimum tests were generated to effectively detect those document system type problems.

In addition, a baseline set of tests are recommended as a minimum to assure functional candidate computer capabilities.

2. Base Line Tests

The following lists the base line tests:

#### Primitive Diagnostic Tests

Memory I/O Test Arithmetic External Interrupt Address Modification Complex Instruction

## Computer Functional Tests

Computational Ability Time Class of Instructions Matrix Manipulation Logical Ability I/O Efficiency I/O - DMA Efficiency Memory Exerciser Code Conversion Math Routines

#### Simulated Space Shuttle Tests

#### Round Robin Concurrent Jobs

3. Recommended Test Set to Detect documented System Problems:

| <u>Test</u>                   | <u>Test</u> # |

|-------------------------------|---------------|

| Transient Radiation           | 1             |

| Inadvertant Power Transient   | 3             |

| Line Impulses                 | 2             |

| Random Interrupt              | 9             |

| Voltage and Ground Wire Check | 6             |

| Electrostatic Discharge Test  | 8             |

| Power Line Pulses             | 4             |

| Maximum Interrupt Speed       | 26            |

Descriptions of these tests are included in the Test Methods Survey (Appendix B).

4. Survey Method Effectiveness

The survey should not be considered a final word in testing, but should be used as a base for test development.

#### H. RECOMMENDATIONS

It is recommended that in order to completely test a candidate computer for space shuttle applications, the following procedure be adopted in order to compile sufficient, meaningful data.

1. Recommended Test Procedure.

- a. Implement all tests explained in G-2 of this report. Do these tests in a quiet (noiseless) room temperature atmosphere to obtain computer baseline data.

- b. Repeat 4.1.1 under each of the conditions specified in G-3 of this report. This will give the computer user a complete set of data from which space shuttle operation can be predicted. This will also give the user a detailed analysis of which environmental condition causes difficulty with the computer operation.

# TABLE 1

|    |                                              |                                                                                  |              |                                              |                                 |          |                                   | · · ·                                     |

|----|----------------------------------------------|----------------------------------------------------------------------------------|--------------|----------------------------------------------|---------------------------------|----------|-----------------------------------|-------------------------------------------|

|    | DESIG                                        | <u>N</u>                                                                         |              | EMI                                          |                                 |          | GROUNDING                         | <u>i</u>                                  |

|    | CAUSE                                        | SYMPTOM                                                                          | <del> </del> | CAUSE                                        | <u>SYMPTOM</u>                  | <u>-</u> | CAUSE                             | <u>SYMPTOM</u>                            |

| ۱. | Out of spec<br>pulse                         | System failure                                                                   | 1.           | Unknown<br>Case gnd                          | System lock-up<br>Computational | ļ.       | ground isolation (8               | Computational errors<br>during RF testing |

| 2. | Marginal .<br>components                     | Computer<br>stoppage                                                             | •            | signal gnd<br>isolation ®                    | errors during<br>RF testing     | 2.       | Multipoint ground<br>system       | Computational errors                      |

| 3. | Tiring<br>problem                            | Computer<br>stoppage                                                             | з.           | Bad memory<br>bits caused                    | Various system<br>failures      | 3.       | Removing ground connector induced | Bad memory and register data              |

| 4  | Peripheral on/uft caused                     | Erroneous<br>initial data                                                        | <b>.</b> .   | by transfects                                |                                 | •        | signal transients<br>③ (2)        |                                           |

| 26 | extraceous<br>pulses stored<br>.in buffer. 1 |                                                                                  | 4.           | Transients due<br>to connector<br>separation | Bad memory and register data    |          |                                   |                                           |

| Ĵ. | Multiple I/O<br>processing<br>deficiency     | dump 1/0<br>channel<br>doesn't<br>always execute                                 | 6.           |                                              | 3<br>Bad computer bits          |          |                                   |                                           |

| 5. | Priority<br>interrupt<br>lock-up             | Highest priority<br>interrupt hogs<br>computer if no<br>"1" level is<br>achieved |              | supply                                       |                                 |          |                                   |                                           |

| 7. | Priority<br>interrupt<br>lock-up 10          | Inadequate<br>burst I/O<br>capability                                            |              |                                              |                                 |          |                                   |                                           |

|    | •                                            |                                                                                  | •            |                                              |                                 |          | ал.<br>С                          |                                           |

## SURVEY OF SYSTEM DIFFICULTIES DETECTED AFTER NORMAL ACCEPTANCE

TABLE I (continued)

|   |     | <u> </u>                                                                |                            |     | MEMORY                       |                                   |      | NOISE                                                   |                      |

|---|-----|-------------------------------------------------------------------------|----------------------------|-----|------------------------------|-----------------------------------|------|---------------------------------------------------------|----------------------|

|   |     | CAUSE                                                                   | SYMPTOM                    |     | CAUSE                        | SYMPTOM                           |      | CAUSE                                                   | SYMPTOM              |

|   | ۱.  | Rapic I/O Trans-<br>actions                                             | Reduced processor<br>speed | 1.  | Bad bits ②                   | Various s <i>item</i><br>failures | 1.   | unterminated signal connector pins (2)                  | Computational errors |

|   | 2.  | Rapid interrupt<br>Sequence                                             | Reduced processor<br>speed | 2.  | Low temperature<br>bit creep | Bad memory<br>data                | . 3. | Adjacent signal<br>crosstalk                            | split pulses         |

| 2 | 3.  | Peripheral on/off<br>caused extraneous<br>pulses stored in<br>buffers 1 | Erroneous initial<br>data  | 3.  | Ambient temp.<br>bit creep   | Bad memory<br>data                | 4    | Adjacent signal<br>crosstalk                            | bad data             |

| 7 | 4   | Gesign failure 🛈                                                        | Inadequate burst           | 4.  | Adjacent word<br>disturbance | Bad memory<br>data                | 5.   | Excessive Cable<br>length                               | Bad transmitted data |

|   | · · | design faiture (10)                                                     | I/O capability             |     |                              | · ·                               | 6.   | Signal Transients<br>induced by cable<br>separation (2) | Bad data             |

|   |     |                                                                         |                            | · . |                              |                                   | 8.   | Relay Noise                                             | Computer Stoppage    |

|   |     |                                                                         | •                          | -   |                              | · .                               |      | •                                                       |                      |

.

# Table 1 (continued)

| POWER             |                                                                    |                            |                   | SOFTWARE                                               |                                                                   |                                         | HARUWARE                                      |                                                         |          |  |  |  |  |             |

|-------------------|--------------------------------------------------------------------|----------------------------|-------------------|--------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|---------------------------------------------------------|----------|--|--|--|--|-------------|

| CAUSE             |                                                                    | SYMPTOM                    |                   | CAUSE                                                  | SYMPTOM                                                           | CAU                                     | SE                                            | SYMPTOM<br>Various System Failures<br>Computer stoppage |          |  |  |  |  |             |

| . Power transient |                                                                    | Clock sync 1<br>modulation |                   | modulation<br>mary Various system 3<br>lue to failures |                                                                   | Improper<br>Instruction<br>Sequence (2) | Computer stoppage                             |                                                         |          |  |  |  |  | d connector |

| •                 | bits due to power up and down                                      | Programming<br>errors      | Computer Stoppage |                                                        |                                                                   | 2. Ba<br>Note:                          | d cables<br>Failure to<br>test immediately    |                                                         |          |  |  |  |  |             |

|                   | (3)<br>Low prime power                                             | Computer<br>Stoppage       | 4.<br>5.          | Language<br>selection<br>Software error                | Reduced processing<br>speed<br>Computer acts on<br>non-legal code | ·                                       | after power-on<br>ignores numerous<br>faults. |                                                         | ti s     |  |  |  |  |             |

|                   | Low prime power                                                    | Intermittent<br>failures   | . •               |                                                        |                                                                   | •                                       | • • •                                         |                                                         | •<br>• • |  |  |  |  |             |

|                   | EMI in power<br>supply                                             | Bad computer<br>bits       |                   |                                                        |                                                                   |                                         | •                                             | · · · ·                                                 | •        |  |  |  |  |             |

|                   | Power interrupt<br>recycle different<br>for different<br>equipment | Bad computer<br>bits       |                   | an a               |                                                                   |                                         |                                               |                                                         |          |  |  |  |  |             |

| P8 #   | DESIGN |      |       | 1        | EMI   |     |          | GROUNDING |    | 1/0 |     | 1/0 |          | MEMORY |     | NOISE |      |     | POWER |      |     | SOFTWARE |      |    | HARDWARE |    |    |

|--------|--------|------|-------|----------|-------|-----|----------|-----------|----|-----|-----|-----|----------|--------|-----|-------|------|-----|-------|------|-----|----------|------|----|----------|----|----|

|        | DI     | SC   | MC    | 10       | SC    | MC  | IO       | SC        | MC | DI  | SC  | MC  | 01       | SC     | MC  | UI    | SC   | MC  | DI    | SC   | MC  | 01       | SC   | MC | DI       | SC | MC |

| 1      | 6      | 2    | 0     | 10       | 2     | 0   | 5        | 2         | }  | 5   | 2   | 1   | 7        | 4      | 2   | 6     | 2    | 1   | 4     | 1    | ۱., | 8        | 2    | 0  | 3        | 2  | ٥  |

| 2      | 9      | 3    | 1     | 8        | 2     | 1   | 6        | 3         | 1  | 5   | 2   | ۱   | 6        | 3      | 1   | 6     | 2    | 1   | 6     | 3    | 1   | 8        | 2    | 1  | 3        | 2  | 0  |

| 3      | 7      | 3    | 1     | 6        | 3     | . 1 | 7        | 3         | 1  | 6   | 2   | .5  | 6        | 3      | ۱   | 8     | 4    | 2   | 6     | - 3  | 1   | - 4      | 2    | 1  |          |    |    |

| 4      | 6      | 2    | Ō     | 7        | 2     | 2   | 7        | 3         | 1  | 3   | 2   | 0   | 6        | 3      | 1   | - 8   | 3    | 1   | 6     | 3    | 1   | 5        | 1    | D  | . ,      |    |    |

| 5      | 3      | 2    | 1     | 7        | 2     | 2   |          |           |    | Į   |     |     |          |        |     | 3     | 2    | 1   | 3     | 2    | 1   | 7        | 1.5  | 0  |          |    |    |

| . 6    | 3      | 2    | 1     | 7        | 2     | 0   |          |           |    | [.  |     |     |          |        |     | 5     | 3    | 1   | 3     | 2    | 1   |          |      |    |          |    |    |

| 7      | 2.5    | 1    | 0     |          |       |     |          |           |    |     |     |     |          |        |     | 5     | 3    | 1   | 7     | 3    | 1   |          |      |    |          |    |    |

| 8      |        |      |       | <u> </u> |       |     | <u> </u> |           |    | ļ   |     |     | <u> </u> |        |     | 5     | 3    | 1   |       | 2    | ]   |          |      |    |          |    |    |

| AVE .  | 5.2    | 2.1  | .6    | 7.       | 5 2.2 | 1   | 6.25     | 2.75      | 1  | 4.8 | 2   | .6  | 6.3      | 3.3    | 1.3 | 5,8   | 2.8  | 1.1 | 5.3   | 2.4  | 1   | 6.4      | 1.7  | .4 | 3        | 2  | 0  |

| FO     |        | 7    | ····· | 1        | 6     |     | 1        | 4         |    |     | 4   |     |          | 4      |     |       | 8    |     | -     | 8    |     | -        | 5    |    |          | 2  |    |

| WEIGHT |        | 14.9 |       | 1.       | 16.7  |     | 1        | 14        |    | 1   | 11. | 4   |          | 14.9   | )   |       | 17.7 | 7   |       | 16.7 |     | 1        | 13.5 |    | •        | 7  |    |

TABLE II - PROBLEM CATEGORY WEIGHTING (based on Difficulty of Isolation, Safety Criticality, Mission Criticality and Frequency of Occurrence)

#### TABLE III - ROUND 1 - TEST PREFERABILITY

|                                                                                                                                                                                                                                       |                                  | PROBLEM  <br>WEIGHT(W)                 | DESIGN EMI G<br>14.9 16.7                                         |                                                        | GROUNDING                                       | 1/0                                                            | MEMORY<br>14.9                                                 | NOISE<br>17.7                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|

| SIME                                                                                                                                                                                                                                  | TEST #                           | ICOST FACTOR                           | E WE                                                              | E WE                                                   | E WE                                            | E WE                                                           | E WE                                                           | E WE                                                   |

| Fransient Radiation<br>MI-Electrical Field Susceptibility<br>Mg. Field Radiated Susceptibility<br>MI Mag. Field Susceptibility<br>EMI Audio & RF Susceptibility                                                                       | 1<br>35<br>38<br>34<br>37        | 1.1<br>1.3<br>1.3<br>1.2<br>1.2        | .1 1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49    | .7 11.69<br>.2 3.34<br>.2 3.34<br>.1 1.67<br>.2 3.34   | .2 2.80<br>.2 2.80<br>.1 1.40<br>.1 1.40<br>0 0 | .0 .0<br>.2 2.28<br>.1 1.14<br>.1 1.14<br>.1 1.14              | .3 4.47<br>.2 2.98<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49 | .6 10.62<br>.2 3.54<br>.1 1.77<br>.1 1.77<br>.2 3.54   |

| Line Impulses<br>EMI Transient (spike) on power lines<br>Inadvertant Power Transient<br>Power Line Pulses<br>Cable Bundle                                                                                                             | 2<br>36<br>3<br>4<br>5           | 1.2<br>1.4<br>1.6<br>1.6<br>1.4        | .1 1.49<br>.1 1.49<br>.2 2.98<br>.1 1.49<br>0 0                   | .4 6.68<br>.1 1.67<br>.1 1.67<br>.2 3.34<br>.3 5.01    | .1 1.40<br>0 0<br>.1 1.40<br>.1 1.40<br>.1 1.40 | .2 2.28<br>.1 1.14<br>.2 2.28<br>.1 1.14<br>.1 1.14<br>.1 1.14 | .3 4.47<br>.1 1.49<br>.2 2.98<br>.2 2.98<br>.2 2.98<br>.2 2.98 | .4 7.08<br>.1 1.77<br>.1 1.77<br>.2 3.54<br>.3 5.31    |

| V. Itage & Ground Wire Check<br>Oscillator Check<br>Electrostatic Discharge<br>Syike on Ground<br>Random Interrupt<br>Tesp. variation vs Moisture .                                                                                   | 6<br>7<br>8<br>14<br>9           | 1.1<br>1.5<br>1.2<br>1.2<br>1.3<br>3.0 | .1 1.49<br>.2 2.98<br>.1 1.49<br>.2 2.98<br>.2 2.98<br>.2 2.98    | .1 1.67<br>0 0<br>.3 5:01<br>.2 3.34<br>0 0<br>0 0     | 0 0 .1 1.40                                     | 0 0<br>.1 1.14<br>.1 1.14<br>.1 1.14<br>.4 4.56<br>0 0         | .1 1.49<br>0 0<br>.2 2.93<br>.1 1.49<br>.3 4.47<br>0 0         | 1 1.77<br>0 0<br>.3 5.31<br>.1 1.77<br>0 0<br>0 0      |

| Overtepperature Response<br>Three Phase Unbalance<br>Power Transients & Switch Toggles<br>Wix. Interrupt Speed<br>EMI-Input/Output Threshold<br>EMI-Emissions from Computer (time)                                                    | 11<br>12<br>13<br>26<br>28<br>29 | 1.2<br>1.5<br>1.2<br>1.5<br>1.7<br>1.3 | .1 1.49<br>.1 1.49<br>.1 1.49<br>.2 2.98<br>.1 1.49<br>.1 1.49    | 0 0<br>0 0<br>.1 1.6<br>0 0<br>.3 5.0<br>.2 3.3        | 0 0 .2 2.80                                     | .3 3.42                                                        | .1 _1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>0 0<br>0 0        | 0 0<br>0 0<br>1 1.77<br>0 0<br>.3 5.31<br>0 0          |

| EMI-Emissions from Computer (Freq.)<br>EMI - Static Residual,Resultant Field<br>EMI - Static Residual,Resultant Field<br>EMI-E field from Computer<br>Mag. Field Radiated Emissions<br>AF Susceptibility on Power Lines<br>Echo Check | 30<br>31<br>33<br>39<br>40<br>42 | 1.7<br>1.2<br>1.5<br>1.3<br>1.2<br>1.2 | .1 1.49<br>0 0<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>.1 1.49<br>0 0 | .2 3.3<br>.2 3.3<br>.2 3.3<br>.1 1.6<br>.1 1.6<br>.0 0 | 4 .1 1.40<br>4 .1 1.40<br>7 0 0<br>7 0 0        | 0 0<br>0 0<br>0 0                                              | 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>.6 8.94                     | 0 0<br>.1 1.77<br>.2 3.54<br>.1 1.77<br>.1 1.77<br>0 0 |

| Power Interrupt<br>Gircuit Frotect on Test Connectors<br>Memory Sum Check<br>Memory Protect Verification<br>I/O Speed & Buffering<br>Random Bit word generator                                                                        | 43<br>44<br>45<br>46<br>47<br>48 | 1.8<br>1.1<br>1.6<br>1.2<br>1.2<br>1.2 | 0 0<br>.1 1.49<br>0 0<br>0 0<br>.1 1.49<br>.1 1.49                |                                                        | .1 1.40<br>0 0<br>0 0                           | 0 0<br>0 0<br>.2 2.28<br>.1 1.14<br>.3 3.42<br>0 0             | 0 0                                                            | 0.0                                                    |

#### TABLE [1] - ROUND 1 (continued)

.

|                                                                                                                                                                                                                                                                                                 |                                                     | POWER<br>16.7                                                                            | SOFTWARE<br>13.5                                                   | HARDWARE<br>7                                                       |                                                                                       |                                                                                               |                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------|

| ·····                                                                                                                                                                                                                                                                                           | TEST #                                              | E WE                                                                                     | E WE                                                               | E WE                                                                | WE                                                                                    | CF                                                                                            | RANK                                               |

| Transient Radiation<br>EMI-Electrical Field Susceptibility<br>May, Field Radiated Susceptibility<br>EMI May, Field Susceptibility<br>EMI Audio & RF Susceptibility<br>Line Engulses<br>EMI Transient (spike) on power lines<br>Fridventant Power Transient<br>Power Line Pulses<br>Cable Bundle | 1<br>35<br>38<br>34<br>37<br>2<br>36<br>3<br>4<br>5 | .2 3.34<br>0 0<br>0 0<br>.2 3.34<br>.1 1.67<br>.2 3.34<br>.6 10.02<br>.5 8.35<br>.1 1.67 | 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0 |                                                                     | 34.41<br>17.13<br>10.63<br>9.66<br>14.34<br>25.07<br>11.60<br>25.15<br>24.29<br>18.21 | 31.282<br>13.176<br>8.176<br>8.050<br>11.950<br>20.892<br>8.286<br>15.719<br>15.182<br>13.007 | 1<br>6<br>17<br>18<br>11<br>2<br>16<br>4<br>5<br>8 |

| Valtage & Ground Wire Check<br>-scillator Check<br>Electrostatic Discharge<br>Spike on Ground<br>Pandom Interrupt<br>Teup, variation vs. Moisture                                                                                                                                               | 6<br>7<br>8<br>14<br>9<br>10                        | .1 1.67<br>0 0<br>.1 1.67<br>.1 1.67<br>- 0 0<br>.1 1.67                                 | 0 0<br>0 0<br>0 0<br>0 0<br>.2 2.70<br>0 0                         | .3 2.10<br>.1 .70<br>.1 .70<br>.1 .70<br>.2 1.40<br>.2 1.40         | 14.39<br>4.82<br>19.70<br>14.40<br>16.11<br>6.05                                      | 13.082<br>3.213<br>16.416<br>12.000<br>12.392<br>6.05                                         | 7<br>34<br>3<br>10<br>9<br>24                      |

| Overtemperature Response<br>Toree Phase Unbalance<br>Fower Transients & Switch Toggles<br>Mix. Interrupt Speed<br>EMI Input/Output Threshold<br>EMI-Emissions from Computer (time)                                                                                                              | 11<br>12<br>13<br>26<br>28<br>29                    | .1 1.67<br>.1 1.67<br>.2 3.34<br>0 0<br>0 0<br>.1 .167                                   | .1 1.35<br>0 0<br>0 0<br>.3 4.05<br>0 0<br>0 0                     | .1 .70<br>.1 .70<br>.1 .70<br>.2 1.40<br>.1 .70<br>.1 .70<br>.1 .70 | 7.84<br>6.49<br>13.00<br>13.34<br>17.59<br>8.60                                       | 6.533<br>4.327<br>10.833<br>8.293<br>10.347<br>6.615                                          | 23<br>28<br>-12<br>15<br>13<br>22                  |

| EMI-Emissions from Computer (Freq.)<br>EMI - Static Residual, Resultant Fields<br>EMI-E field from computer<br>Mag. Field Radiated Emissions<br>and Susceptibility on Power lines<br>Echo Cneck                                                                                                 | 30<br>31<br>33<br>39<br>40<br>42                    | .1 1.67<br>.1 1.67<br>0 0<br>0 0<br>.2 3.34<br>0 0                                       | 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0                             | .1 .70<br>0 0<br>.1 .70<br>0 0<br>0 0<br>0 0                        | 8.60<br>8.18<br>10.47<br>4.93<br>8.27<br>11.22                                        | 5,508<br>6,816<br>6,980<br>3,792<br>6,891<br>9,350                                            | 26<br>21<br>19<br>33<br>20<br>14                   |

| Power Interrupt<br>Dirouit Protoct on Test Connectors<br>Mimory Sum Check<br>Minory Protect Verification<br>1.0 Speed & Buffering<br>Fundom bit word generator                                                                                                                                  | 43<br>44<br>45<br>46<br>47<br>48                    | .3 5.01<br>0 0<br>0 0<br>1 1.67<br>0 0<br>0 0                                            | .1 1.35<br>0 0<br>0 0<br>0 0<br>0 0<br>.1 1.35                     | .2 1.40<br>0 0<br>.1 .70<br>0 0                                     | 7.85<br>4.29<br>8.24<br>5.00<br>4.91<br>5.03                                          | 4.361<br>3.900<br>5.150<br>4.167<br>4.092<br>4.192                                            | 27<br>32<br>25<br>30<br>31<br>29                   |

#### CALLE IN - ROUND 2 - TEST PREFERABILITY

|                                                                                                                                                                                               |                                  | PROBLEM<br>WEIGHT(W)                          | DESIGN<br>14.9                                                         | EMI<br>16.7                                                   | GROUNDING                                                         | 1/0<br>11.4                                                | MEMORY<br>14.9                                                         | NOISE<br>17.7                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------|--|

| NAME                                                                                                                                                                                          | TEST #                           | I COST FACTOR                                 | E NE                                                                   | E WE                                                          | E WE                                                              | E WE                                                       | E WE                                                                   | E wE                                                    |  |

| Transient Radiation<br>EMI-Electrical Susceptibility<br>Mag. Field Radiated Susceptibility<br>EMI Mag. Field Susceptibility<br>EMI Audio & RF Susceptibility                                  | 35<br>38<br>34<br>37             | 1.3<br>1.3<br>1.2<br>1.2                      | .1<br>.09 1.34<br>.09 1.34<br>.09 1.34<br>.09 1.34                     | .7<br>.06 1.00<br>.63 1.00<br>.63 .50<br>.06 1.0              | .2<br>.16 2.24<br>.08 1.12<br>.08 1.12<br>0 0                     | 0<br>.2 2.28<br>.1 1.14<br>.1 1.14<br>.1 1.14              | .3<br>.14 2.08<br>.07 1.04<br>.07 1.04<br>.07 1.04                     | .6<br>.08 1.42<br>.04 .71<br>.04 .71<br>.08 1.42        |  |

| Line Impulses<br>ENI Transient (spike) on power lines<br>Inadvertant Power Transient<br>Power Line Pulses<br>Cable Eundle                                                                     | 2<br>36<br>3<br>4<br>5           | 1.2<br>1.4<br>1.6<br>1.6<br>1.4               | .09 1.34<br>.09 1.34<br>.18 2.68<br>.09 1.34<br>0 0                    | .12 2.0<br>.03 .50<br>.03 .50<br>.06 1.00<br>.09 1.50         | .08 1.12<br>C 0<br>.03 1.12<br>.08 1.12<br>.08 1.12               | .2 2.28<br>.1 1.14<br>.2 2.28<br>.1 1.14<br>.1 1.14        | .21 3.12<br>.07 1.04<br>.14 2.08<br>.14 2.08<br>.14 2.08               | .16 2.85<br>.04 .7!<br>.04 .7!<br>.08 1.42<br>.12 2.14  |  |

| Voltage & Ground Wire Check<br>Oscillator Theck<br>Electrostatic Discharge<br>Spike on Ground<br>Random Interrupt<br>Temp. variation vs Moisture                                              | 6<br>7<br>8<br>14<br>9<br>10     | 1.1<br>1.5<br>1.2<br>1.2<br>1.3<br>1.0        | .09 1.34<br>.12 2.68<br>.09 1.34<br>.09 1.34<br>.18 2.68<br>.18 2.68   | .03 .50<br>0 0<br>.09 1.50<br>.06 1.00<br>0 0                 | 24 3.36<br>0 0<br>.08 1.12<br>.16 2.24<br>0 0<br>0 0              | .1 1.14                                                    | .07. 1.04<br>0 0<br>.14 2.08<br>.07 1.04<br>.21 3.12<br>0 0            | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$   |  |

| Overtemperature Response<br>Three Prase Unbalance<br>Power Transients & Switch Toggles<br>Max. Interrupt Speed<br>EMI-Input/Output Threshold<br>EMI-Emissions from Computer (time)            | 11<br>12<br>13<br>26<br>28<br>29 | 1.2<br>1.5<br>1.5<br>1.5<br>1.7<br>1.3        | .18 2.68<br>.09 1.34<br>.09 1.34<br>.18 2.68<br>.09 1.34<br>.09 1.34   | 0 0<br>0 0<br>.03 .50<br>0 0<br>.09 1.50<br>.06 1.00          | 0 0<br>0 0<br>.08 1.12<br>0 0<br>.16 2.24<br>.03 1.12             | .1 1.14<br>.1 1.14<br>.1 1.14<br>.3 3.42<br>.2 2.28<br>0 0 | .07 1.04<br>.07 1.04<br>.07 1.04<br>.07 1.04<br>.07 1.04<br>0 0<br>0 0 | 0 0<br>0 0<br>104 .71<br>0 0<br>.12 2.14<br>0 0         |  |

| EMI- Emissions from Computer (Freq)<br>EMI- Static Residual, Resultant Fields<br>EMI-E Field from Computer<br>Mag. Field Radiated Emissions<br>RF Susceptibility on Power Lines<br>Echo Check | 30<br>31<br>33<br>39<br>40<br>42 | 1.7<br>1.2<br>1.5<br>1.3<br>1.2<br>1.2        | .09 1.34<br>0 0<br>.09 1.34<br>.09 1.34<br>.09 1.34<br>.09 1.34<br>0 0 | .06 ).00<br>.06 1.00<br>.06 1.00<br>.03 .50<br>.03 .50<br>0 0 | .08 1.12<br>.08 1.12<br>.08 1.12<br>.08 1.12<br>0 0<br>0 0<br>0 0 | 0 0                                                        | 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>.42 6.25                     | 0 0<br>.04 .71<br>.08 1.42<br>.04 .71<br>.04 .71<br>0 0 |  |

| Power Interrupt<br>Circuit Protect on Test Connectors<br>Memory Sum Check<br>Memory Protect Verification<br>I/O Speed & Buffering<br>Random Bit Word Generator                                | 43<br>44<br>45<br>46<br>47<br>48 | 1.8<br>1.1<br>1.6<br>1.2<br>1.2<br>1.2<br>1.2 | 0 0<br>.09 1.34<br>0 0<br>0 0<br>.09 1.34<br>.09 1.34                  | 0 0<br>0 0<br>0 0<br>0 0<br>0 0                               | 0 0<br>.08 1.12<br>0 0<br>0 0<br>0 0<br>0 0                       | 0 0<br>0 0<br>.2 2.28<br>.1 1.14<br>.3 3.42<br>0 0         | .07 1.04<br>0 0<br>.28 4.17<br>.07 1.04<br>0 0<br>.07 1.04             | 0 0<br>0 C<br>0 0<br>0 0<br>0 0<br>0 0                  |  |

# TABLE IV - ROUND 2 (continued)

|                                                                                                                                                                                                                                                                                                 | ſ                                                   | POWE<br>16.7                                           |                                                        |                                        | TWARE                            | HA                         | RDWARE<br>7                                                |                                                                           |                                                                                  |                                                     |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------------|----------------------------------|----------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------|-----|

| NAME                                                                                                                                                                                                                                                                                            | TEST #                                              | E                                                      | WE                                                     | E                                      | WE                               | E                          | WE                                                         | WE                                                                        | CF                                                                               | RANK                                                |     |

| Fransient Radiation<br>EMI-Electrical Field Susceptibility<br>Mag. Field Radiated Susceptibility<br>EMI Mag. Field Susceptibility<br>EMI Audio & RF Susceptibility<br>Line Impulses<br>EMI Transient (spike) on power lines<br>Inadvertant Power Transient<br>Power Line Pulses<br>Cable Bundle | 1<br>35<br>38<br>34<br>37<br>2<br>36<br>3<br>4<br>5 | .2<br>0<br>0<br>.16<br>.08<br>.16<br>.48<br>.40<br>.08 | 0<br>0<br>2.68<br>1.34<br>2.68<br>8.07<br>6.73<br>1.34 | 0<br>0<br>0<br>0<br>0<br>0<br>.1<br>.1 | 0<br>0<br>0<br>1.35<br>1.35<br>0 | 0.10500.1.1.1.1.1.1        | ETotal<br>.7<br>0<br>.7<br>0<br>.7<br>.7<br>.7<br>.7<br>.7 | 11.06<br>6.35<br>6.55<br>8.62<br>14.05<br>8.11<br>19.49<br>16.88<br>10.02 | 8.502<br>4.885<br>5.458<br>7.183<br>11.708<br>5.793<br>12.181<br>10.550<br>7.157 | 1<br>8<br>20<br>18<br>12<br>3<br>17<br>2<br>5<br>13 |     |