https://ntrs.nasa.gov/search.jsp?R=19740021457 2020-03-23T06:12:48+00:00Z Jill with 29570 N74-29570 NASA CR120905 DESUGN, DEVELOPMENT, AND FABRICATION OF A MICROMINIATURIZED ELECTRONIC ANALOG SIGNAL TO DISCRETE TIME INTERVAL CONVERTER by A. D. Schoenfeld and K. K. Schuegraf a202122 SYSTEMS GROUP TRW SEP KEC STAD NASA STIFACI Wear J. Weard Prepared for AERONAUTICS AND SPACE ADMINISTRATION VATIONA NASA Lewis Research Center ور کر ا Contract NASL2

|                                                                                                                                                                                                                                                             | 2. Government Accession No.                                                                                                                                                                                                                                                                             | 3. Recipient's Catalog No.                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Report No.<br>CR-120905                                                                                                                                                                                                                                  | 2. Government Accession No.                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                |

| 4. Title and Subtitle<br>Design, Development and Fabrica                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                         | 5. Report Date<br>August 1973                                                                                                                                                                                                  |

| Electronic Analog Signal to Dis                                                                                                                                                                                                                             | screte Time Interval Converter.                                                                                                                                                                                                                                                                         | 6. Performing Organization Code                                                                                                                                                                                                |

| 7. Author(s)                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                         | 8. Performing Organization Report No.                                                                                                                                                                                          |

| A. D. Schoenfeld and K. K. Schu                                                                                                                                                                                                                             | Jegraf                                                                                                                                                                                                                                                                                                  | 10. Work Unit No.                                                                                                                                                                                                              |

| 9. Performing Organization Name and Address                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                |

| TRW Systems Group<br>One Space Park                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                         | 11. Contract or Grant No.                                                                                                                                                                                                      |

| Redondo Beach, Calif. 90278                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                         | NAS12-2017                                                                                                                                                                                                                     |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                         | 13. Type of Report and Period Covered                                                                                                                                                                                          |

| 2. Sponsoring Agency Name and Address                                                                                                                                                                                                                       | <b></b>                                                                                                                                                                                                                                                                                                 | Contractor Report                                                                                                                                                                                                              |

| National Aeronautics and Space<br>Lewis Research Center<br>Cleveland, Ohio 44135                                                                                                                                                                            | Administration                                                                                                                                                                                                                                                                                          | 14. Sponsoring Agency Code                                                                                                                                                                                                     |

| 5. Supplementary Notes<br>Assistance of Technical Editing<br>Vincent R. Lalli<br>Lewis Research Center                                                                                                                                                      | g Provided by                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                |

| Cleveland, Ohio 44135<br>6. Abstract                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                |

| was completed. Discrete compon<br>on a thin-film ceramic substrat                                                                                                                                                                                           | te containing nichrome resistors wi                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                |

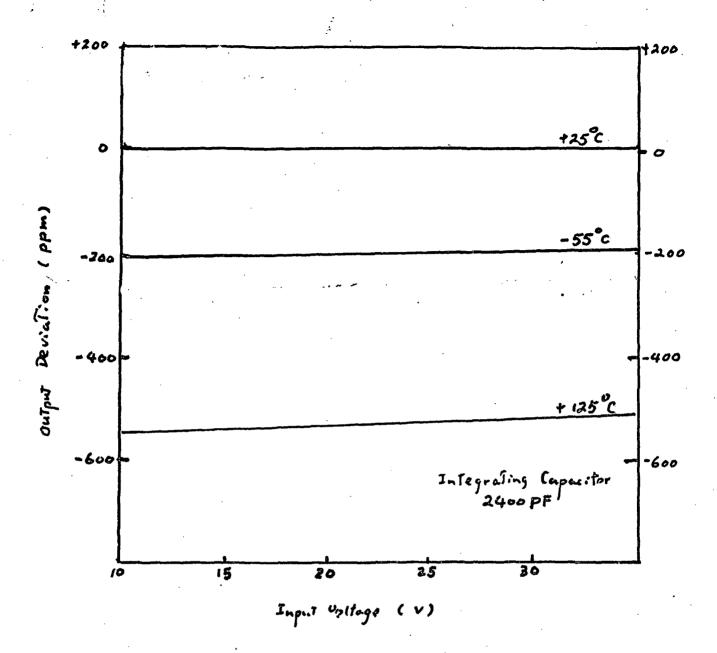

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation b<br>tage reference, the module was<br>temperature range of -55°C to +                                               | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s                                                                                                                                                                                       | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range                                                                         | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of $-55^{\circ}$ C to +<br>variation was less than +300 pa | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than +300 pa           | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than +300 pa           | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta                           |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than <u>+</u> 300 pa   | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u>                           | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta<br>±3mV for a 10V output. |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation b<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than <u>+</u> 300 pa    | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u><br>18. Distribution State | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta<br>±3mV for a 10V output. |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than +300 pa<br>       | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u><br>18. Distribution State | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta<br>±3mV for a 10V output. |

| on a thin-film ceramic substrat<br>The finished assembly is enclos<br>The module can be used whenever<br>for the purpose of regulation be<br>tage reference, the module was<br>temperature range of -55°C to +<br>variation was less than +300 pa<br>       | te containing nichrome resistors wi<br>sed in a flat package measuring 3.3<br>r conversion of analog to digital s<br>by means of pulse modulation. In<br>applied to control the duty cycle<br>125°C, and an input voltage range<br>arts per million, i.e., less than <u>+</u><br>18. Distribution State | ith gold interconnections.<br>30 by 4.57 centimeters.<br>signals is required, in particula<br>conjunction with a precision vol<br>of a switching regulator within<br>of 10V to 35V. The output-volta<br>±3mV for a 10V output. |

ľ

à

**ii** //

# FOREWORD

The authors wish to express grateful acknowledgment of major contributions to this program by Dr. F. C. Schwarz and Mr. R. Cocosa of NASA/ERC, and by Mr. J. J. Biess and Mr. W. T. Ruhl of TRW Systems. Dr. Schwarz originated the conceptual design of the Analog Signal to Discrete Time Interval Converter system, and has provided technical direction throughout the program effort. Mr. Cocosa conducted exploratory system development at NASA/ERC. Mr. Biess performed a significant portion of the work on the system design and development at TRW. Mr. Ruhl was responsible for a considerable part of the microelectronic network development, fabrication, and tests.

iii

# TABLE OF CONTENTS

|     |    |              |                                                                                              | Page |

|-----|----|--------------|----------------------------------------------------------------------------------------------|------|

|     | ۱. | INTR         | ODUCTION                                                                                     | 1    |

|     | 2. | DESC         | RIPTION OF ASDTIC CONTROL CONCEPT                                                            | 4    |

|     | 3. | ASDT         | IC MODULE DESIGN AND DEVELOPMENT                                                             | · 9  |

|     |    | 3.1          | Control Parameter Requirements, Selection<br>& Testing                                       | 9    |

|     |    | 3.2          | ASDTIC Module Current Demand                                                                 | 16   |

| ••. | 4. | ASDT         | IC MODULE FABRICATION AND TEST                                                               | 17   |

|     |    | 4.1          | Component Testing                                                                            | . 17 |

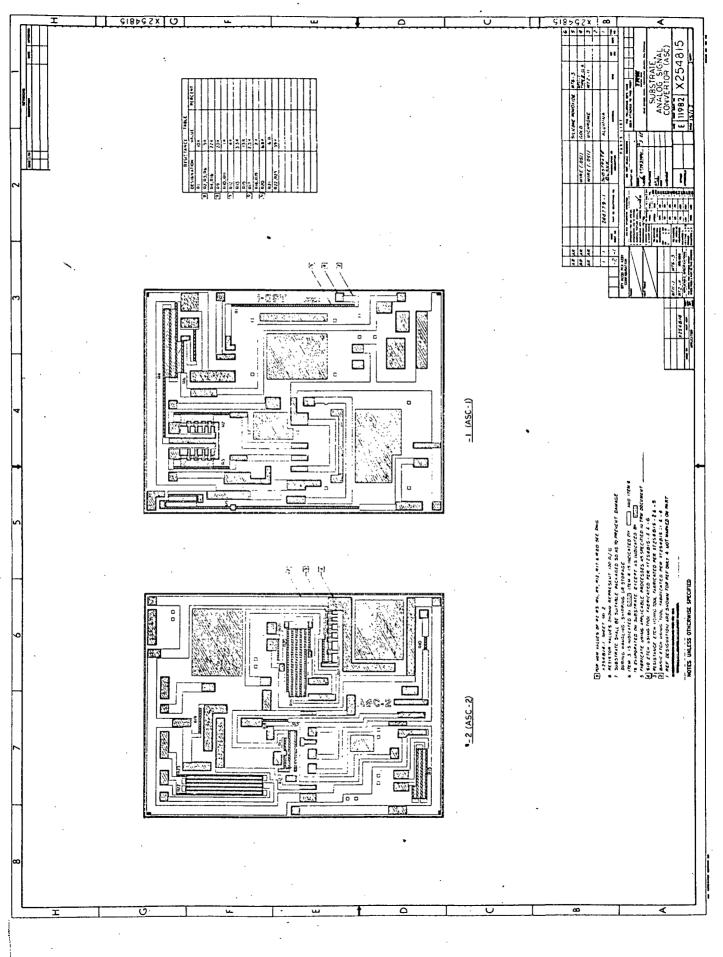

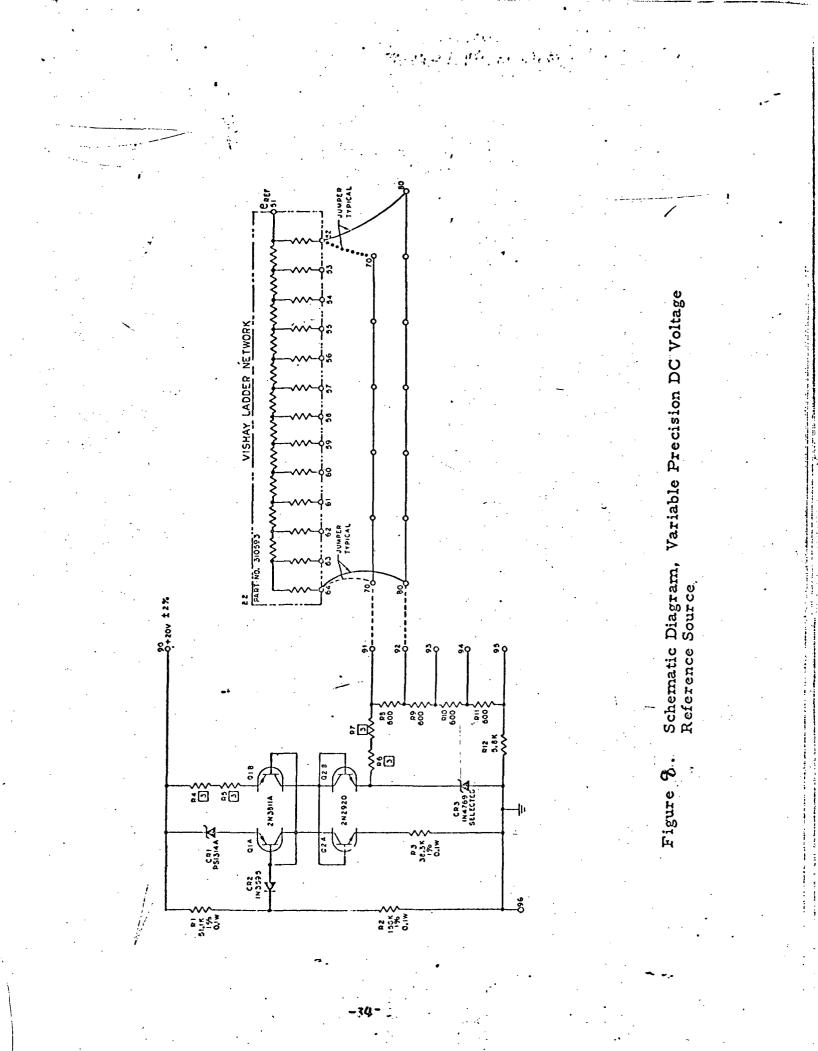

|     |    | 4.2          | Layout and Packaging                                                                         | 19   |

|     |    | 4.3          | Substrate Fabrication                                                                        | 23   |

|     |    | 4.4          | Assembly                                                                                     | 27   |

|     |    | 4.5          | Adjustment and Test                                                                          | 27   |

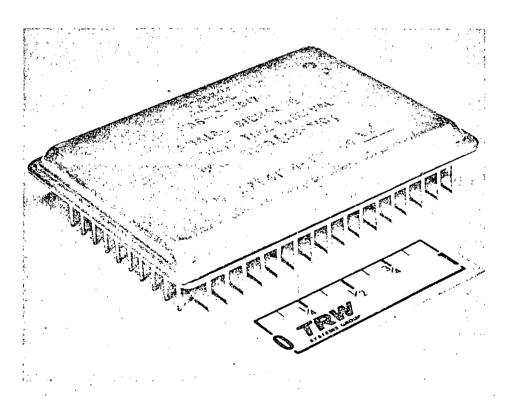

|     | 5. | FABR<br>SOUR | ICATION OF PRECISION DC VOLTAGE REFERENCE<br>CE                                              | 33   |

|     | 6. |              | OCIRCUIT ASDTIC MODULE APPLIED TO CONTROL<br>ST CIRCUIT SWITCHING CONVERTER                  | 38   |

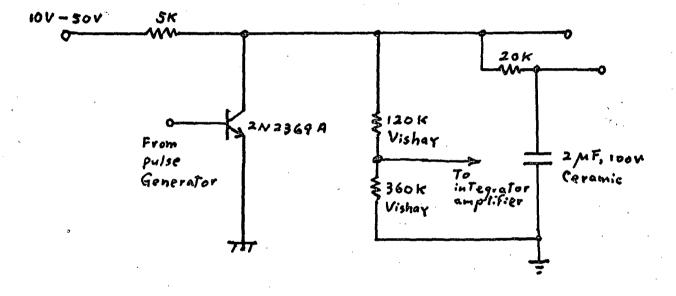

|     |    | 6.1          | Converter Test Circuit Block Diagram                                                         | 38   |

|     |    | 6.2          | Converter System Requirements                                                                | 41   |

|     |    | 6.3          | Converter System Error Analysis                                                              | 42   |

|     |    | 6.4          | Peripheral Circuit Schematics & Description                                                  | 45   |

|     |    | 6.5          | Switching Regulator Test Circuit Performance                                                 | e 50 |

|     | 7. | CONC         | LUSIONS                                                                                      | 52   |

| •   | 8. | REFE         | RENCES                                                                                       | 53   |

|     | 9. | APPEI        | NDICES                                                                                       | 54   |

|     |    | 9.1          | Test Fixtures, Procedures, and Results for<br>IC Components Used in the ASDTIC Module        | 54   |

|     | ·  | 9.2          | Worst-Case Variation of Precision Reference<br>Voltage Source                                | 62   |

|     |    | 9.3          | Series Switching Regulator Instability Relat<br>to Constant-Frequency ASDTIC Duty-Cycle Cont |      |

#### SUMMARY

The objective of this effort was to devise an electronic control system in microcircuit form which can be used to effect pulse-modulation control for a variety of power switching regulators.

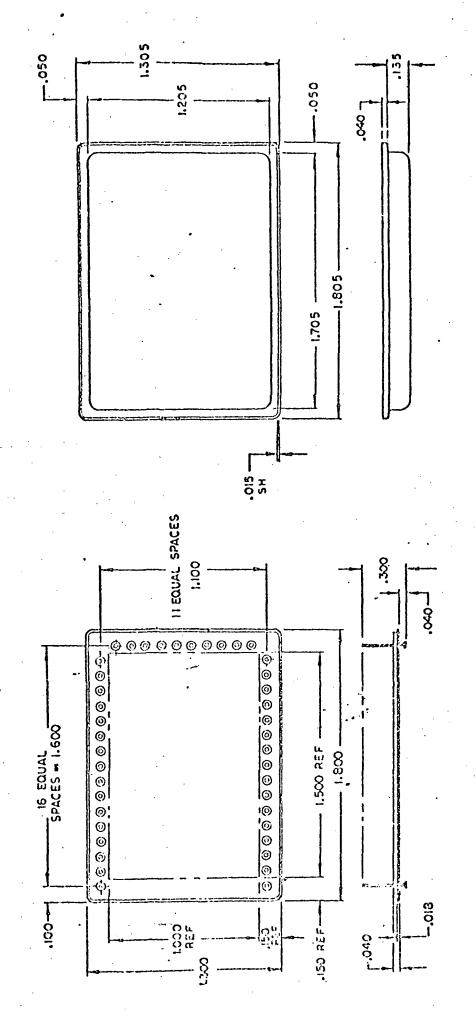

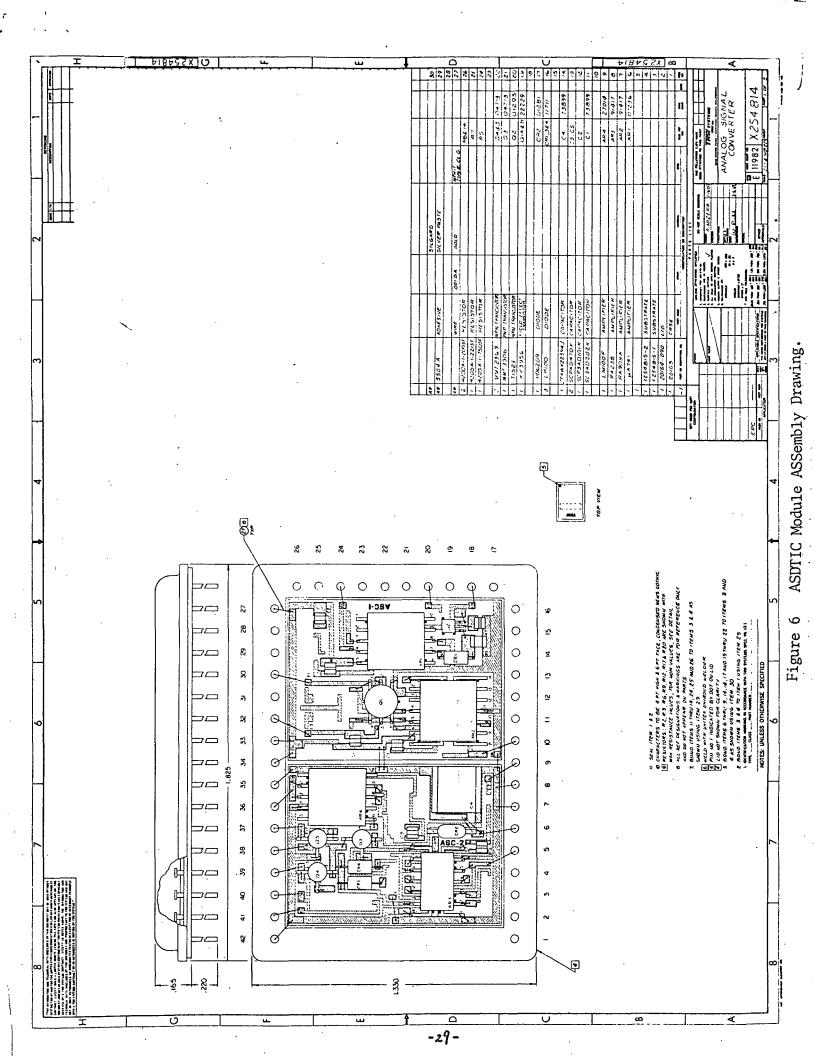

The electronic network consists of four major functional blocks: the series regulator, the dc amplifier, the integrator amplifier, and the threshold detector. Fabrication of these functional blocks was accomplished by use of state-of-the-art hybrid-circuit techniques. The finished microcircuit assembly is enclosed in a flat package measuring 3.30 by 4.57 centimeters.

All circuits designed, developed, assembled, and tested as a result of this program effort fully met the specified goals for voltage gain, frequency response, stability, temperature drift, and other performance requirements.

The application of the microminiaturized ASDTIC module to a test converter circuit shows that the 0.1 percent regulation requirement over an input-voltage range of 10 to 35V and a temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C can be readily met. Typically, the voltage regulation at room temperature is  $\pm 30$  parts per million. The temperature drift, attributable to the microelectronic module over the specified temperature range, is  $\pm 150$  parts per million.

#### 1. INTRODUCTION

X

The Analog Signal to Discrete Time Interval Converter Program (ASDTIC) was initiated at NASA/ERC in 1966. Its objective was to devise an electronic circuit to be used wherever conversion of analog to digital signals is required, in particular, for the purpose of transmission of an analog signal through the technique of pulse modulation. By virtue of this basic function, the network is directly applicable for controlling the duty cycle of the switching type dc to dc converter regulators. The control system, as developed, collects information from the power system in the form of significant analog signals and produces a sequence of control signals at discrete time intervals. The control signals cause rectangular voltage pulses to be generated in the power network for voltage transformation and regulation.

The ASDTIC concept initiated at NASA/ERC was envisioned to offer the following inherent merits: (1) the control system performance is immune to component parameter changes with the regulator, and (2) the control system is capable of achieving simultaneously regulator stability, static performance, and dynamic response. Based on the ASDTIC control concept, preliminary circuits were breadboarded and tested at NASA/ERC to substantiate the high performance envisioned. Subsequently, the control circuit was further developed and refined at TRW to improve the power drain, the current limiting, the flexibility, and other control-circuit performances.

The component parts of this electronic control circuit consist of various IC's, which lent themselves readily to circuit microminiaturization. The micro-circuit development was performed at TRW Systems under contract NAS12-2017. Through this effort, discrete components and IC's comprising the circuit were assembled on a thin-film ceramic substrate containing thin-film nichrome resistors with gold interconnections. **[3]**

-/-

This report covers work accomplished on Design, Development, and Fabrication of a Microminiaturized Electronic Analog Signal to Discrete Time Interval Converter. Contract work during the period 1 July 1968 to 15 October 1969, was performed through the following tasks:

ASDTIC Module Electrical Design and Development

Tasks of this phase include the following:

- Define detail control-parameter requirements for the ASDTIC module.

- o ASDTIC Module Circuit Design.

- ASDTIC Module Component Testing, Evaluation and Selection.

- o ASDTIC Module Breadboard and Test.

- 2. ASDTIC Module Fabrication and Test

The tasks include:

1.

- Microelectronic network ASDTIC module component testing and package design.

- Layout and photomask fabrication for the thinfilm resistor and interconnect assembly.

- Fabrication and assembly of the microelectronic

ASDTIC module.

- o Testing of the ASDTIC module.

- 3. Precision DC Voltage Reference Fabrication

The tasks include the circuit development, the worstcase analysis, and the fabrication of a precision voltage reference.

-2-

# Test Circuit Switching Regulator Utilizing the ASDTIC Module and the Precision Reference

The tasks include the development of a test circuit switching regulator and the analysis of control system errors.

The effort of the first two tasks led to the assembly of the microminiaturized ASDTIC module, which is enclosed in a flat package measuring 3.30 by 4.57 centimeters. In conjunction with Task 3, a single-sided PC board measuring 8.2 by 14.6 centimeters was fabricated, which contains both the ASDTIC module and the precision dc voltage reference.

All circuits designed, developed, assembled, and tested as a result of this work fully met contract specifications for voltage gain, frequency response, linearity, tracking, stability, temperature drift, input and output impedances, and system performance.

The program thus successfully demonstrated the feasibility of microminiaturizing the Analog Signal to Discrete Time Interval Converter and the precision reference, which paved the way for future converter control-circuit standardization.

-3-

#### 2. DESCRIPTION OF ASDTIC CONTROL CONCEPT

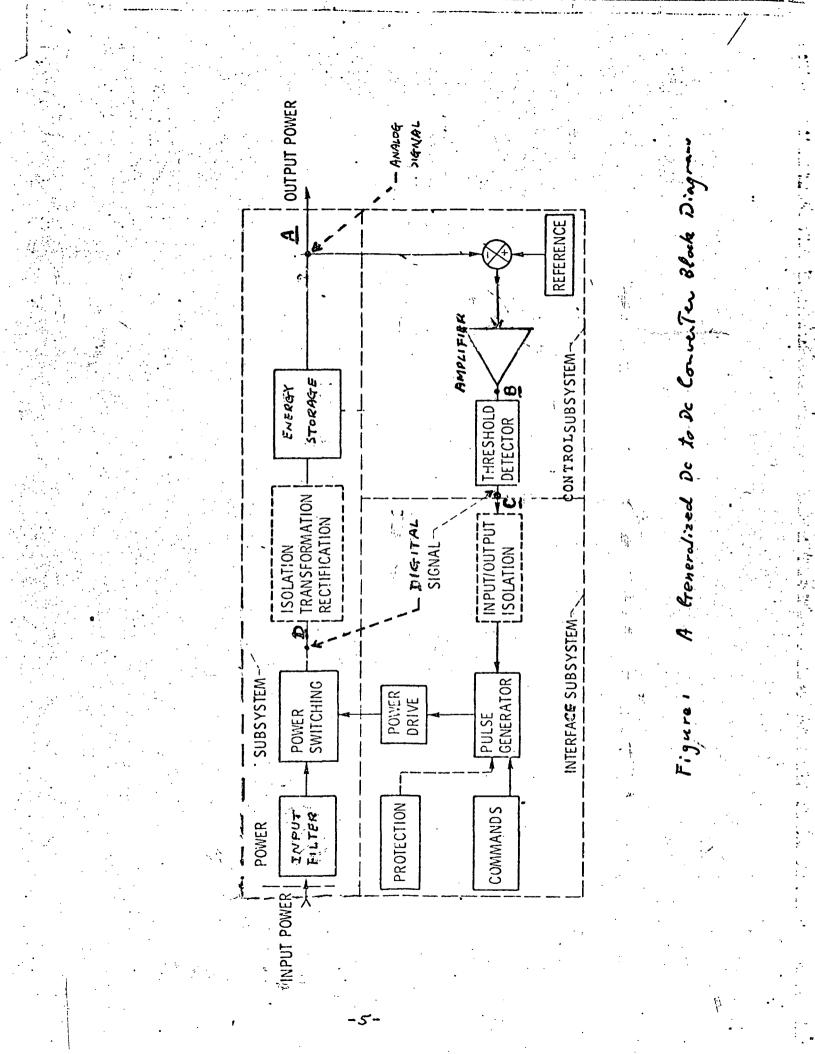

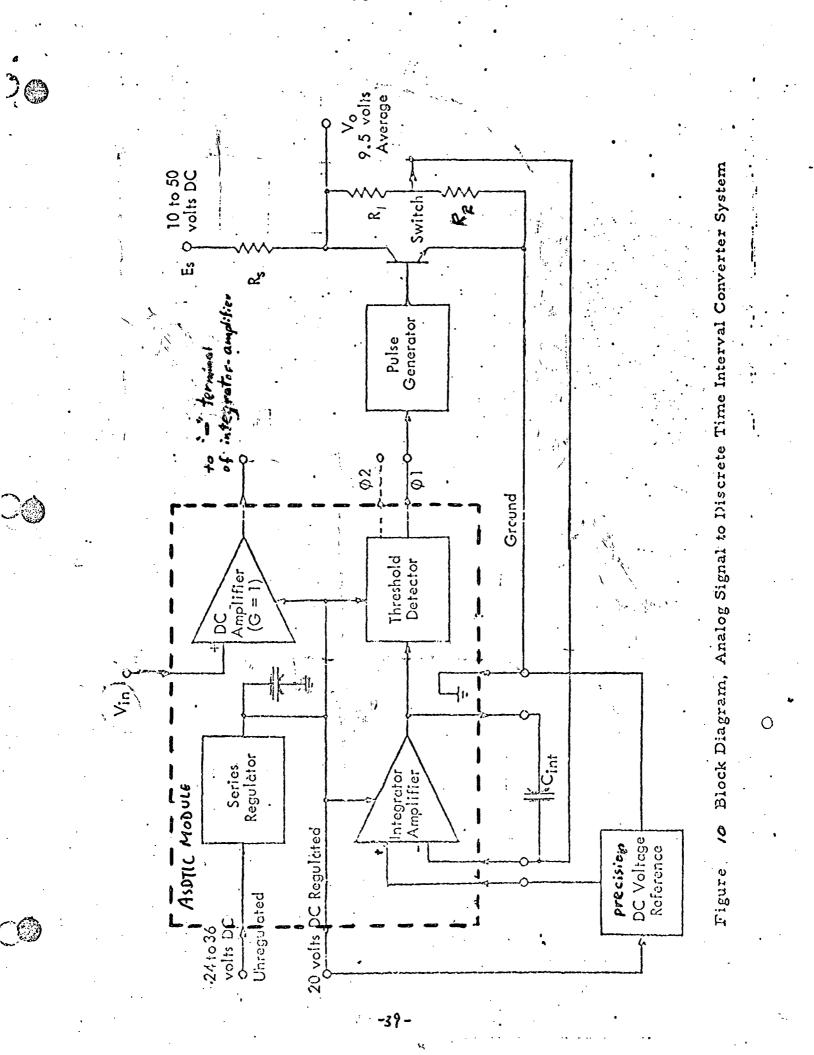

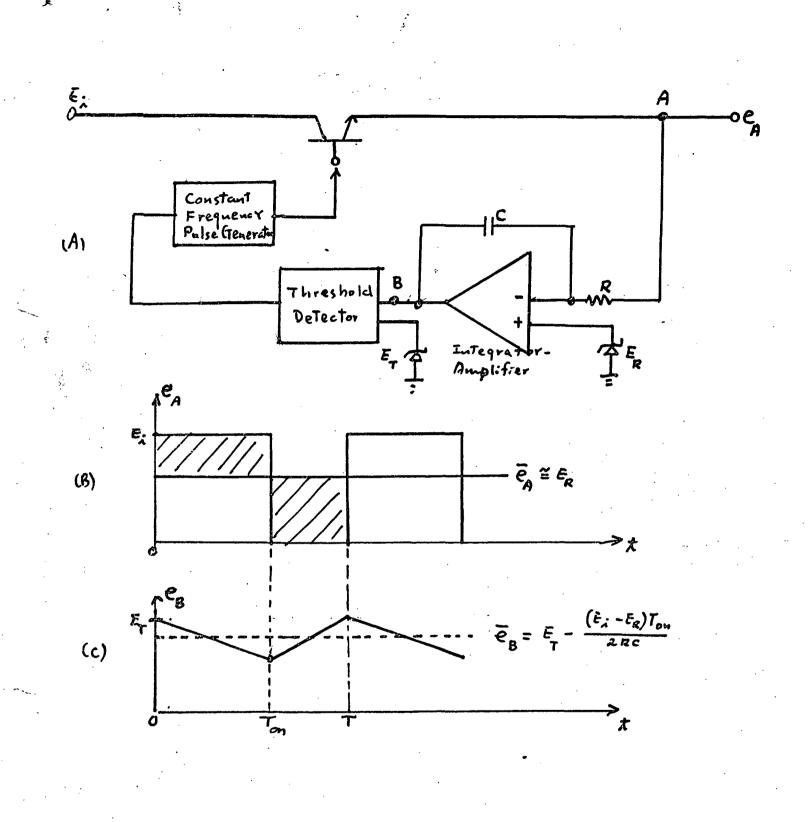

A dc to dc converter shown in Figure 1 consists of three subsystems; the control subsystem, the interface subsystem, and the power subsystem. Starting with the converter output at point <u>A</u> and tracing clockwise, the analog signal at <u>A</u> is processed by the control subsystem, and is transformed into a digital output signal at point <u>C</u>. This digital signal, along with other protection and command signals, is being processed by the interface subsystem to provide the proper on/off control of the power switch. The output of the power switch at point <u>D</u> of Figure 1 forms a voltage pulse train. The digital pulses are converted back to an analog signal by the energy-storage block, thus returning the signal to point A.

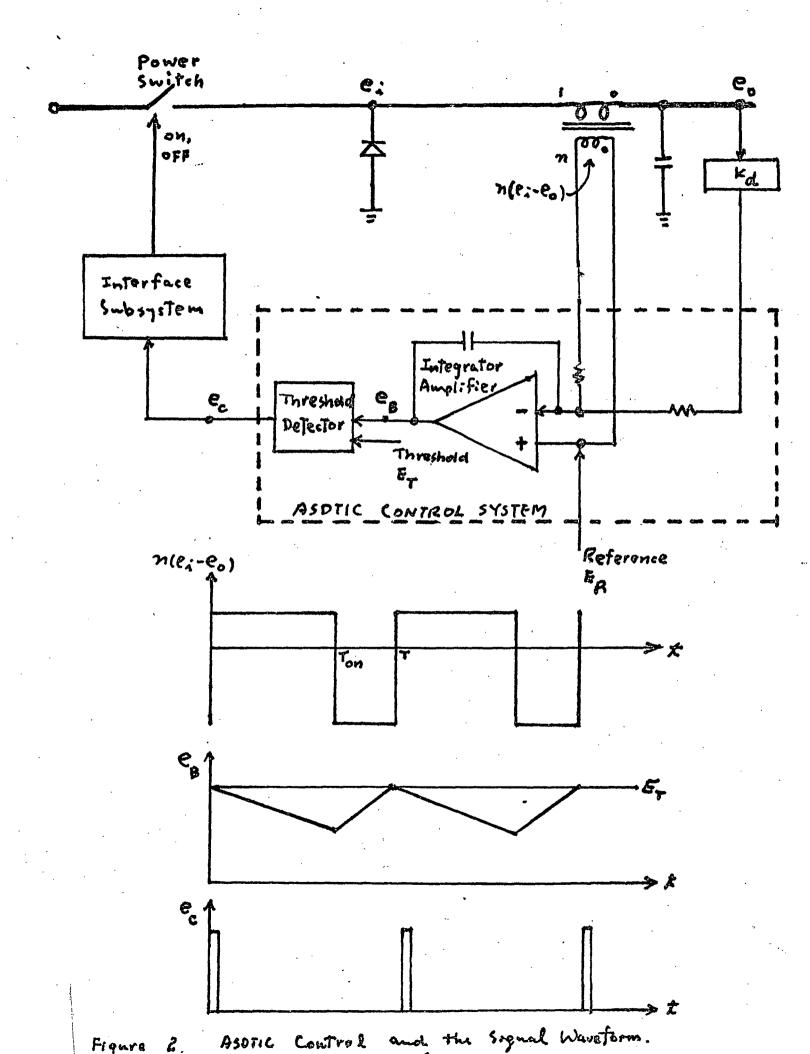

The microelectronic network package and the precision reference were developed in this program to serve as the control subsystem for all types of dc to dc converters. Its unique feature is the capability of processing two feedback control signals, rather than processing a single feedback control signal sensing exclusively the specific converter quantity to be regulated. Using a switching series regulator as an example, the essential network elements comprising this two-loop ASDTIC control subsystem is illustrated in Figure 2.

The error-processing component of the ASDTIC concept is a highgain error amplifier with a capacitor feedback, i.e., an integrator. Two input signals are applied to the integrator-amplifier through two feedback control loops. The first loop senses the dc output voltage  $e_o$ of the converter, divides it by a factor  $K_d \stackrel{\leq}{=} 1$ , and compares  $K_d e_o$  to the amplifier reference  $E_R$ . The difference  $e_{dc} = K_d e_o - E_R$  becomes the dc error input. In conjunction with a threshold-detector level  $E_T$ , the dc output level of the integrator-amplifier is determined by  $e_{dc}$ . The second loop senses the ac component of  $(e_i - e_o)$  across the filter inductor, transforms it by a factor  $n \stackrel{\geq}{=} 1$ , and feeds  $e_{ac} = n (e_i - e_o)$  differentially to the integrator-amplifier. The rectangular ac voltage  $e_{ac}$ , along with the much smaller dc error  $e_{dc}$ , are integrated. The

-4-

integrator triangular output, severing as the ramp function, is superimposed on the amplified dc error to intersect the thresholdlevel  $E_T$ . The threshold detector output  $e_c$  actuates the interface subsystem to control the duty cycle of the power switch.

The ASDTIC control thus includes, basically, the dc- and ac- loop sensing, the integrator-amplifier for error processing and ramp generation, and the threshold detector. Its adaptability to all switching regulators is apparent. For as long as there exists within the regulator an inherent ac waveform suitable for ramp-function generation, the ASDTIC control can be conveniently applied.

As stated previously in Section 1, the two-loop control concept was breadboarded preliminarily and tested. In relation to a conventional single-loop control, the performance improvement as a result of using this control concept was experimentally substantiated. This performance advantage, in conjunction with its universal appeal for controlling all types of switching regulators, prompted the decision to reduce this control concept into a microelectronic network package. The package, along with the precision voltage reference, fulfills a standardized control system, shown in Figure 1.

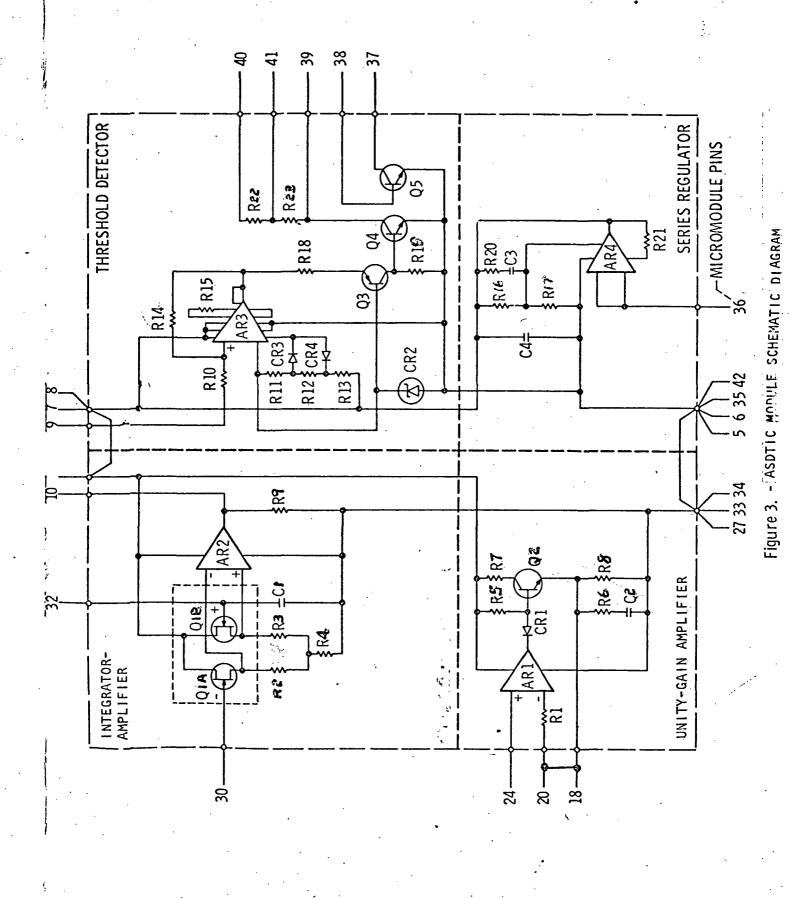

The microelectronic package contains four major network elements:

- o Integrator Amplifier

- o Threshold Detector

- o Unity-Gain Amplifier

- o Series Regulator

The electrical functions served by the integrator amplifier and the threshold detector have been previously described.

The unity-gain amplifier is used between the integrator amplifier and the sensed converter output (usually the output voltage). Its function is to eliminate the loading effect of the integrator amplifier to the resistive voltage divider sensing the regulated output. This function can be optional when dealing with a low-voltage output where the divider resistances are low and the integrator loading effect is negligible. However, it is indispensible when the regulated output

-7-

voltage is high (e.g., <sup>10</sup>KV for high power TWT) where the divider resistance is in the order of hundreds of megohms.

The series regulator is needed to provide a regulated bias voltage for all aforementioned operational amplifiers.

Having identified these major network elements, the design, development, fabrication, and test of the ASDTIC module containing these elements, are presented in the subsequent sections. The presentation, supplemented by that of a precision dc voltage reference, completely describe a microminiaturized control subsystem applicable to all types of switching regulators.

# 3. ASDTIC MODULE DESIGN AND DEVELOPMENT

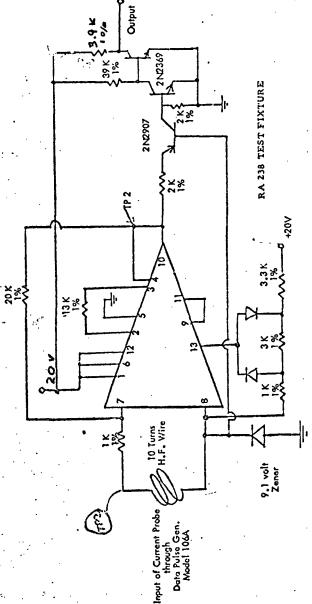

The schematic diagram of the microelectronic ASDTIC module, consisting of the integrator-amplifier, threshold detector, series regulator, and the unity-gain amplifier, is shown in Figure 3. The schematic also shows the relevant pin assignment of the module. The parts list for components shown in Figure 3 is given in Table I.

## 3.1 Control Parameter Requirements, Selection and Testing.

The control parameter requirements, the network component selection, and the breadboard testing for each of the four major networks are summarized in Table II.

-10+

.

- 740

# TABLE I. PARTS LIST, MICROMINIA URIZED ASDTIC MODULE

| Circuit Description | Part Type           | Vendor                  |

|---------------------|---------------------|-------------------------|

| ARI                 | RM4101-Q            | Raytheon                |

| AR2                 | RA909A              | Radiation, Inc.         |

| AR3                 | RA238               | Radiation, Inc.         |

| AR4                 | LMIOOF              | National Semiconductors |

| Q1                  | KY3956              | Union Carbide           |

| Q2                  | TIS23               | Texas Instruments       |

| 03                  | MMT 3906            | Motorola                |

| QJ<br>Q4, Q5        | MMT2369             | Motorola                |

| CR1, CR3, CR4       | • LP100             | General Instrument      |

| CR2                 | PD6209              | TRW                     |

|                     | 1BX050S222J, 2200pf | Varadýne                |

| C1<br>C2            | 1BN050S101J, 100pf  | Varadyne                |

| C2<br>C3            | 1BN050S470J, 47pf   | Varadyne                |

| C4                  | WX22394J, 0.39uf    | JFD Electronics         |

| RI                  | 10K                 | *                       |

| R2                  | 4.5K                | *                       |

| R3                  | 4.5K                | *                       |

| ∧⊃<br>R4            | 22K                 | *                       |

| R5                  | 2C754F, 750K        | Varadyne                |

| R6                  | _ 5K                | varadyne<br>*           |

| R7                  | 1C224F, 220K        | Varadyne                |

| R8, R14             | 2C204F, 220K        | Varadyne                |

|                     | 20K                 | *                       |

| R9<br>R10           | 20K<br>1K           | *                       |

| RII                 | IK<br>IK            | *                       |

| R12                 | 4K                  | *                       |

|                     | 3.3K                | *                       |

| R13                 | 13K                 | *                       |

| R15<br>R16          | 22K                 | *                       |

|                     | 1.8K                | *                       |

| RI7                 | 2K                  | *                       |

| R18                 | 2K<br>2K            | *                       |

| R19                 | 6.8K                | *                       |

| R20                 | 6 ohms              | *                       |

| R21                 |                     | *                       |

| R22                 | 39K                 | *                       |

| R23                 | 39К                 | <b>^</b>                |

| •                   |                     |                         |

# \*Thin-Film Nichrome Resistors

.

-11-

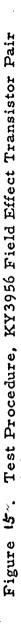

| 10-to-1 inhalance allowable for transistor       0. The circuit configuration control impedance to two states for imput impedance to two states intributed and the form (XY356) manufactured integrator transistor perate for total input current and perate the imput current and addiation. Inc.       0. A matched N-channel junction integrator analizatured integrator transistor work follows         0. The integrator formulation.       0. The driver stage is required to perate both current and perate the imput current and maintain to olimitate the imput current and editation. Inc.       0. The driver stage is required to perate perate perate perate perate the imput current and perate the imput current and editation. Inc.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage is required to be driver stage.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage stage is acquired to be driver stage.         20db gain at 100Kir with slew       0. Minimization of the imput current and editation. Inc.       0. The driver stage.         20db gai |                                                              | CIRCUIT IMPLEM<br>BOARD TESTING.<br>CONTROL PARAMETER<br>REQUIREMENTS                                                                                                   | CIRCUIT IMPLEMENTATION, COMPONENT SELECTION, AND BREAD-<br>BOARD TESTING.<br>CIRCUIT IMPLEMENTATION | COMPONENT SELECTION<br>BREADBOARD TESTING                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

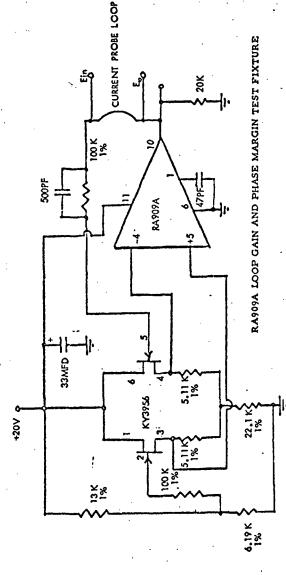

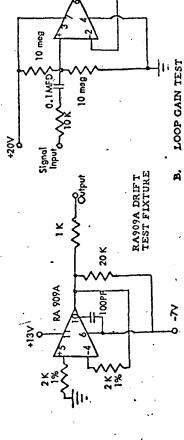

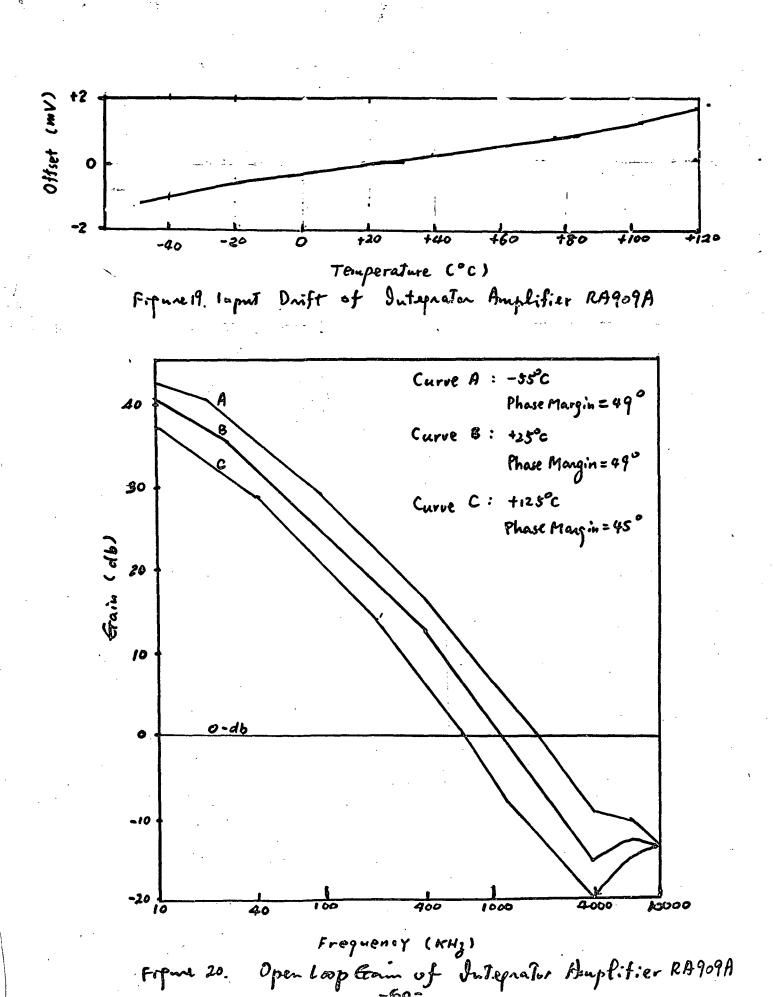

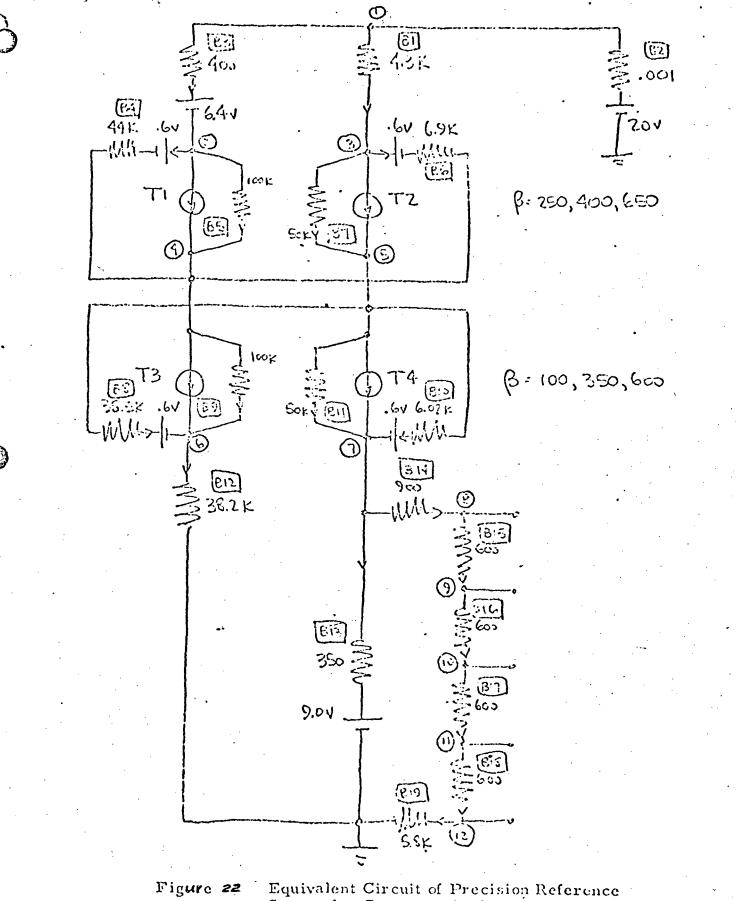

| ent.<br>in at 100KHz with slew offset temperature coefficient. The drift characterist<br>V/us: offset temperature coefficient. The drift characterist<br>is greater than 100db, is accomplished by trimming re-<br>margin greater than 45<br>over the temperature<br>over the temperature<br>and minimum peak-to-<br>megrator output voltage<br>and 200mV.<br>requirements must be met<br>incuit with only modest<br>demands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-t<br>for<br>inte<br>drif<br>volt                          | balance allow<br>impedance to<br>terminals.<br>imum for tota<br>to both curre<br>fset temperat                                                                          |                                                                                                     | A matched N-channe<br>FET pair (KY3956)<br>by Union Carbide<br>as the driver stag<br>The integrator-am<br>lected was the RAG                                                                                              |

| m and minimum peak-to-<br>megrator output voltage<br>and 200mV.<br>requirements must be met<br>ircuit with only modest<br>demands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20db ga<br>rate 1V<br>dc gair<br>phase m<br>degree<br>range. | gain at 100KHz with<br>1V/us.<br>in greater than 100c<br>margin greater thar<br>e over the temperatu                                                                    |                                                                                                     | <ul> <li>real action, inc.</li> <li>The drift characteristic tested over the temperateristic range, and was found to within the requirement.</li> <li>Testing of open-loop fic cy response of the completered.</li> </ul> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Maximu<br>peak i<br>of 8V<br>These<br>by a c<br>power        | Maximum and minimum peak-to-<br>peak integrator output voltage<br>of 8V and 200mV.<br>These requirements must be met<br>by a circuit with only modest<br>power demands. |                                                                                                     | ature range gives a minimum<br>phase margin of 45 degrees at<br>125°C.                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              | •                                                                                                                                                                       |                                                                                                     | · · ·                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |                                                                                                                                                                         |                                                                                                     |                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                              |                                                                                                                                                                         |                                                                                                     |                                                                                                                                                                                                                           |

•.

| ,                     |   |     | •                                                                                                                                                            | Table | II. (Cont'd)                                                                                                                                                              |                     |

|-----------------------|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                       |   |     | CONTROL PARAMETER<br>REQUIREMENTS                                                                                                                            |       | CIRCUIT IMPLEMENTATION                                                                                                                                                    | COMPONENT SELECTION |

|                       | - |     |                                                                                                                                                              |       |                                                                                                                                                                           | BKEAUBUAKU IESI ING |

| Threshold<br>Detector |   | 0 0 | +4uA maximum input current.<br>Power to its output circuitry<br>can be provided by an external<br>source voltage ranging from 5V<br>to 32V.                  | 0     | It consists of a dc amplifier o<br>AR3, a reference diode CR2, and<br>a three-transistor level-shift<br>driver Q3, Q4, and Q5.                                            |                     |

| •                     |   | 0 0 | Negative-going output pulse falls<br>within 0.lus. Positive-going<br>pulse rises within 0.3us.<br>The delay of the threshold detec-<br>tor is less than lus. | 0     | To prevent the amplifier from<br>saturating and exhibiting long<br>storage time, the output swing<br>of the threshold-dector ampli-<br>fier is limited by diode clamping. | ·IIOTAdims          |

|                       |   | 0   | ble of s<br>0.5V.                                                                                                                                            | 0     | A small amount of hysteresis is<br>controlled by R14 and R18 to<br>approximately 25mV.                                                                                    | · ·                 |

| -13-                  |   |     | • • • • • • • • • • • • • • • • • • •                                                                                                                        | 0     | Transistors Q4 and Q5 provide<br>the flexibility of having either<br>a logical-0 or a logical-1 signal<br>at the threshold-dector output.                                 | •.                  |

|                       |   | •   |                                                                                                                                                              |       |                                                                                                                                                                           |                     |

|                       |   |     |                                                                                                                                                              |       |                                                                                                                                                                           |                     |

|                       |   |     |                                                                                                                                                              |       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                     |                     |

|                       | • |     |                                                                                                                                                              |       |                                                                                                                                                                           |                     |

|                       |   |     |                                                                                                                                                              |       |                                                                                                                                                                           |                     |

|                       |   |     |                                                                                                                                                              |       |                                                                                                                                                                           |                     |

|                       |   |     |                                                                                                                                                              |       | · · · · ·                                                                                                                                                                 |                     |

| •                |                                                                                                                                                                                           | Table II. (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | CONTROL PARAMETER<br>REQUIREMENTS                                                                                                                                                         | CIRCUIT IMPLEMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                           | COMPONENT SELECTION<br><sup>6</sup><br>BREADBOARD TESTING                                                                                                                                                                                                                                                                                                                                                                                                                          |

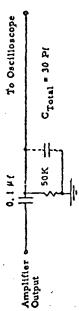

| ulator<br>o<br>o | Input voltage 24V to 32V, output<br>voltage at 20V ±2%.<br>Output Current 12mA.<br>Output impedance less than 2 ohms<br>from dc to 100KHz.<br>Stable under all operating condi-<br>tions. | <ul> <li>It consists of a dc amplifier<br/>AR4, sensor resistors R16 and<br/>R17, compensating network C3,<br/>C4, and R20, and current-limi-<br/>ting resistor R21.</li> <li>The combination of C3, C4, and<br/>R20 provides the low output<br/>impedance and regulator stabil-<br/>ity.</li> <li>This configuration differs<br/>from that recommended by the<br/>manufacturer, which resulted<br/>in high output impedance at<br/>high frequencies.</li> </ul> | <ul> <li>o The LM100 voltage regulator was selected as the best flat pack in production at the time.</li> <li>o A worst-case output-voltage regulation of +1.5% was measured at +125°C at high line and heavy load.</li> <li>o In testing the open-loop frequency response, a minimum phase margin of 45 degrees was obtained at +125°C.</li> <li>o Worst-case output impedance occurs at -55°C, and stays very much constant from 10KHz up to 100KHz at about 1.70hms.</li> </ul> |

|                  |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Serie Regul

14-

|                         |            | CONTROL PARAMETER<br>REQUIREMENT                                                                                                                       | CIRCUIT IMPLEMENTATION                                                                           | COMPONENT SELECTION<br>§<br>BREADBOARD TESTING                                                                                |

|-------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Unity-Gain<br>Amplifier |            | The driving source resistance<br>less than 10,000 ohms.                                                                                                | o The unity-gain amplifier con-<br>sists of amplifier AR1, a diode-                              | o Raytheon's RM4101-2 was used as ARL.                                                                                        |

|                         | <b>O</b> . | Input voltage for normal opera-<br>tion was 6V to 8V. During tran-<br>sient, the voltage it can take<br>is between 0 and 10.5V.                        | o The emitter tollower output                                                                    | al ac gain<br>lowed the lc<br>to be much<br>than the                                                                          |

|                         | 0          | The voltage gain is $1 \pm 0.01$ from dc to 10KHz.                                                                                                     | stage Q2 provides low output<br>impedance when operated in its<br>linear range. It also provides | analysis would indicate. The<br>difference is resolved by<br>considering the common-mode                                      |

|                         | 0          | 5 megohms input impedance or greater.                                                                                                                  | current limiting by saturating<br>or cutting off when its output-                                | rejection ratio.<br>• For 6V <v, <sv,="" devia-<="" td="" the=""></v,>                                                        |

| - 15                    | 0          | Less than an output impedance<br>of 25 ohms from dc to 10KHz<br>when output is not current-<br>limiter.                                                | current that is exceeded.                                                                        | tion in V <sub>out</sub> from linearity<br>is about 15µV for the worst-<br>unit tested.                                       |

| • -                     | <b>O</b> . | Greater than 45-degree phase<br>margin over the temperature<br>range.                                                                                  | · · ·                                                                                            | <pre>o The input impedance is in the<br/>order of 50 megolms. The out<br/>put impedance is about 7.5<br/>ohms at 10KHz.</pre> |

| •.<br>• •               | <b>`O</b>  | (V <sub>out</sub> - V <sub>in</sub> ) is less than 5mV at 25°C. The temperature tracking over -55°C to +125°C and 6V to 8V of input voltage is +0.5mV. |                                                                                                  | o the leakage curre<br>CRl at 125°C, the<br>urrent of transisto<br>re than 50µA (about                                        |

|                         | о<br>,     | Drift at constant temperature<br>is less than 10µV/Hour and 50µV/<br>day.                                                                              | ·<br>·<br>·                                                                                      | at an output voltage of 6V.<br>• A phase margin of 43 degrees<br>was measured for resistive                                   |

|                         |            | •<br>•<br>•                                                                                                                                            |                                                                                                  | perature range.                                                                                                               |

|                         |            |                                                                                                                                                        | •                                                                                                |                                                                                                                               |

|                         | "          | · · ·                                                                                                                                                  |                                                                                                  |                                                                                                                               |

Table II. (Cont'd)

-

## 3.2 ASDTIC Module Current Demand

The current demand from the various microelectronic circuits is listed in Table III. At high duty cycle of 0.9 to 0.95, the pwoer demand increased slightly because the threshold detector remains in on-state a large percentage of the time. The maximum total current through the series regulator is 13 milliamps. In conjunction with a series regulator output voltage of 20V, the maximum total power drain is 260 milliwatts.

# TABLE 111

| ,                                 |                                             | ,                                    |

|-----------------------------------|---------------------------------------------|--------------------------------------|

| ltem                              | Current<br>0.3 to 0.9<br>Duty Cycl <b>e</b> | Current<br>0.9 to 0.95<br>Duty Cycle |

| Series Regulator                  | 200mA                                       | 2.0mA                                |

| Reference and<br>Divider          | 1.5mA                                       | 1.5mA                                |

| DC Amplifier                      | 1.3mA                                       | 1.3mA                                |

| Integrator                        | 2.5mA                                       | 2.5mA                                |

| Threshold Detector<br>(Low Level) | 4.2mA                                       | 5.7mA                                |

| Total through Series<br>Regulator | 11.5mA                                      | 13.OmA                               |

# ASDTIC MODULE CURRENT DRAIN

-16-

# 4. ASDTIC MODULE FABRICATION AND TEST

Subsequent to the cricuit design and breadboard testing to verify preliminarily all electrical characteristics, the program proceeded toward the manufacturing of the microminiaturized ASDTIC module. Specifically, the program effort can be described in the following tasks: (1) Component testing, (2) Layout and Packaging, (3) Subsrate fabrication, (4) Assembly, and (5) Testing.

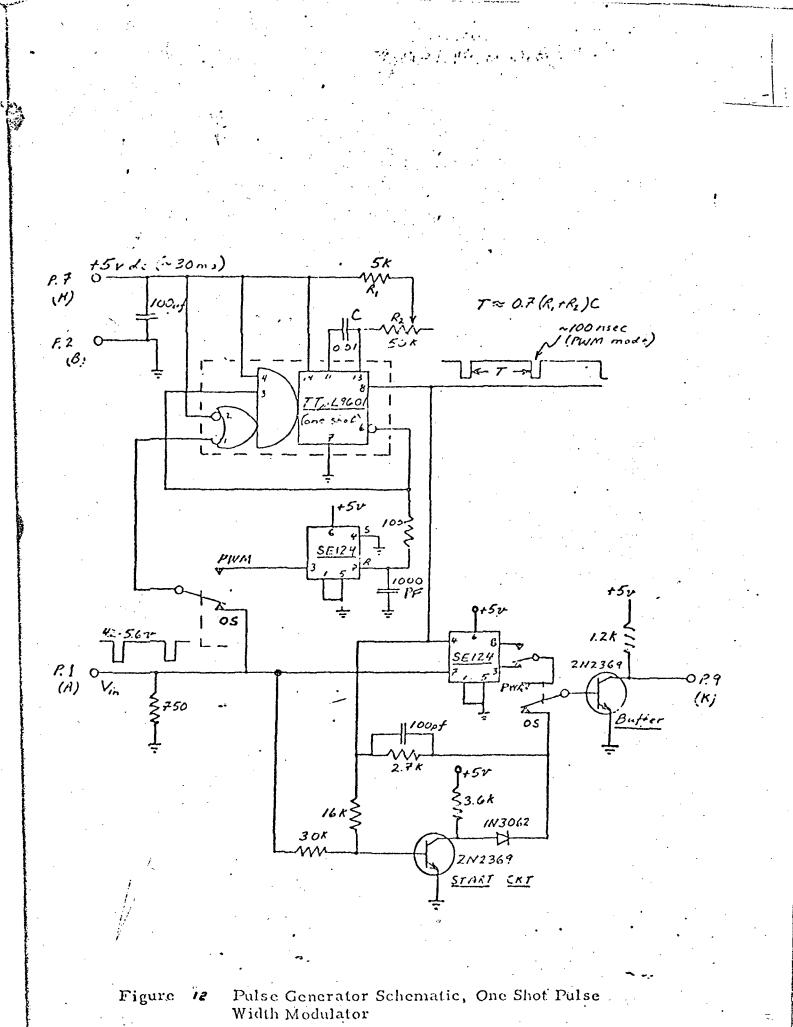

4.1 COMPONENT TESTING