# Final Report DEVELOPMENT OF AN IMAGE CONVERTER OF RADICAL DESIGN

July 1972

Prepared for

MARSHALL SPACE FLIGHT CENTER

Huntsville, Alabama

Under

NASA 8-5112

$\mathbf{B}\mathbf{y}$

WESTINGHOUSE ELECTRIC CORPORATION

Baltimore, Maryland

Reproduced by

NATIONAL TECHNICAL

INFORMATION SERVICE

US Department of Commerce

Springfield, VA. 22151

PRICES SUBJECT TO CHANGE

(NASA-CR-120350) DEVELOPMENT OF AN IMAGE CONVERTER OF RADICAL DESIGN Final Report (Westinghouse Electric Corp.)

N74-31666

CSCL 09E

Unclas '09 17019

G3/09

# Final Report DEVELOPMENT OF AN IMAGE CONVERTER OF RADICAL DESIGN

July 1972

Prepared for

MARSHALL SPACE FLIGHT CENTER

Huntsville, Alabama

Under

NASA 8-5112

Ву

WESTINGHOUSE ELECTRIC CORPORATION

Baltimore, Maryland

#### FOREWORD

This final report was prepared by E.L. Irwin and D.L. Farnsworth of the Westinghouse Electric Corporation, Systems Development Division, Baltimore, Maryland. The reporting period covered is from July 1962 to July 1972. This effort was covered by contract NAS 8-5112. The NASA MSFC Program Monitor was C.T. Huggins.

Preceding page blank

## TABLE OF CONTENTS

|                                   |      | Page         |

|-----------------------------------|------|--------------|

| 1. INTRODUCTION                   |      | 1-1          |

| 2. SENSOR MONOLITHS               | 9 J. | 2-1          |

| 2.1 Device Design                 |      | 2-1          |

| 2.2 Bipolar Structure             | ·,   | 2-5          |

| 2.3 Mosaic Design                 | e e  | 2-7          |

| 3. FABRICATION TECHNOLOGY         |      | 3 <b>- 1</b> |

| 3.1 Material Preparation          |      | 3-1          |

| 3.2 Epilaxial Growth              | y v  | 3-3          |

| 3.3 Oxidation                     |      | 3-5          |

| 3. 4 Diffusion                    | •    | 3~8          |

| 3.5 Photoengraving                |      | 3 <b>-</b> 9 |

| 3.6 Mosaic Processing             |      | 3-13         |

| 4. FUNCTIONAL THEORY              |      | 4-1          |

| 4. l Integration Mode Operation   |      | 4-2          |

| 4.1.1 Single Phototransistors     |      | 4-2          |

| 4.1.2 Junction Capacitance Ratios |      | 4-13         |

| 4.1.3 Array Phototransistors      |      | 4-14         |

| 4.1.4 Switching Considerations    |      | 4-26         |

| 4.2 Performance Characteristics   |      | 4-28         |

| 5. SYSTEM METHODOLOGY             |      | 5-1          |

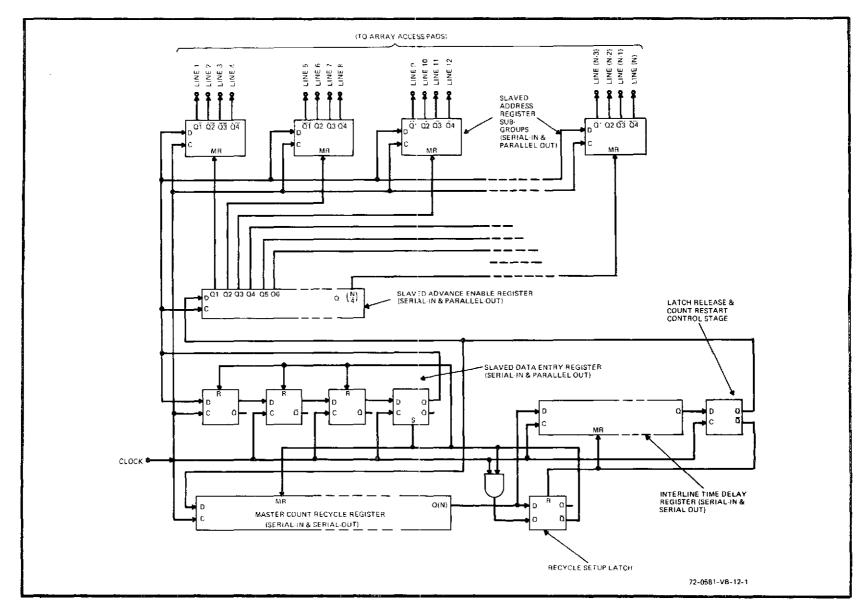

| 5.1 Array Scanning                |      | 5 - 2        |

| 5. 2 Signal Acquisition           |      | 5-34         |

| 5.3 Signal Processing             |      | E .44        |

|                                                  | Page          |

|--------------------------------------------------|---------------|

| 5.4 Information Display                          | 5 <b>-6</b> 1 |

| 5.5 Signal Conditioning                          | 5-66          |

| 6. DEPLOYMENT PROFILE                            | 6 - 1         |

| 6. l Line-Array Systems                          | 6-1           |

| 6.2 Matrix Array Systems                         | 6-6           |

| 7. 400-BY-500 CAMERA                             | 7 – 1         |

| 7.1 Mechanical Layout                            | 7-3           |

| 7.2 Electrical Specifications                    | 7-14          |

| 7.3 System Operation                             | 7-23          |

| 7.3.1 General Operating Instructions             | 7-23          |

| 7.3.2 Removal and/or Change of Cover Plate       | 7-24          |

| 8. SUMMARY AND CONCLUSIONS                       | 8-1           |

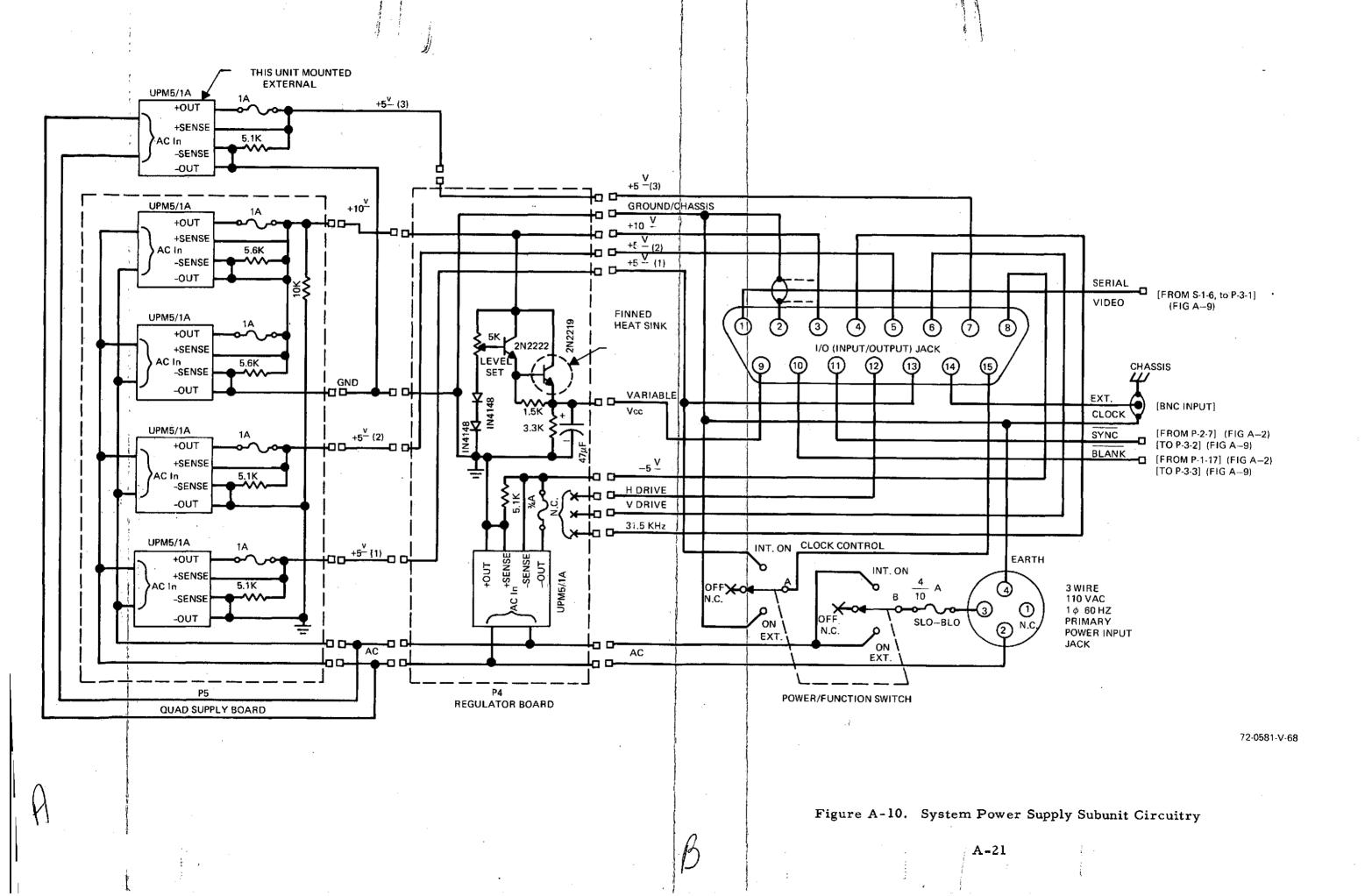

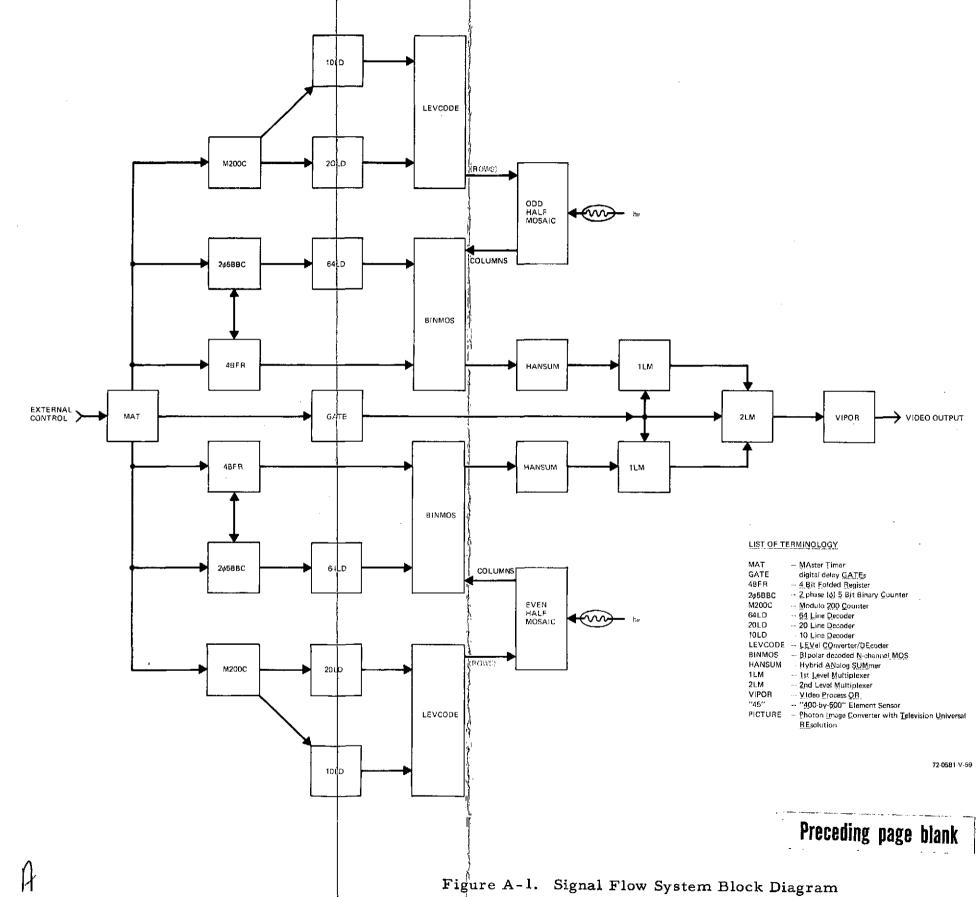

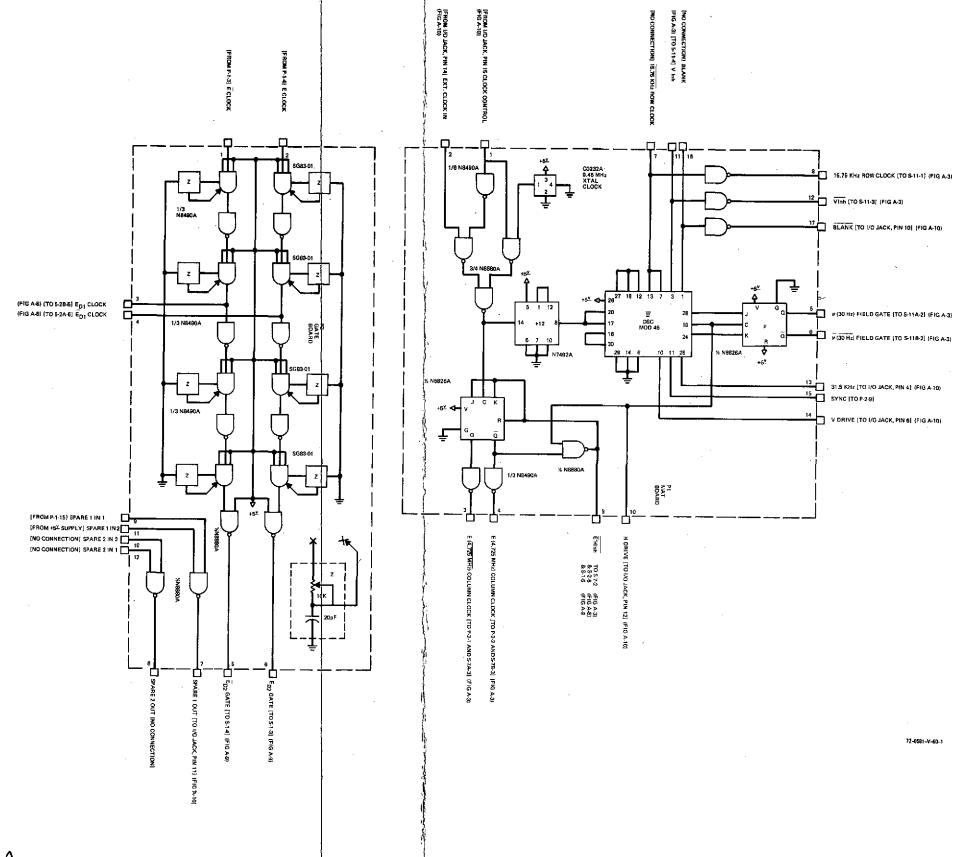

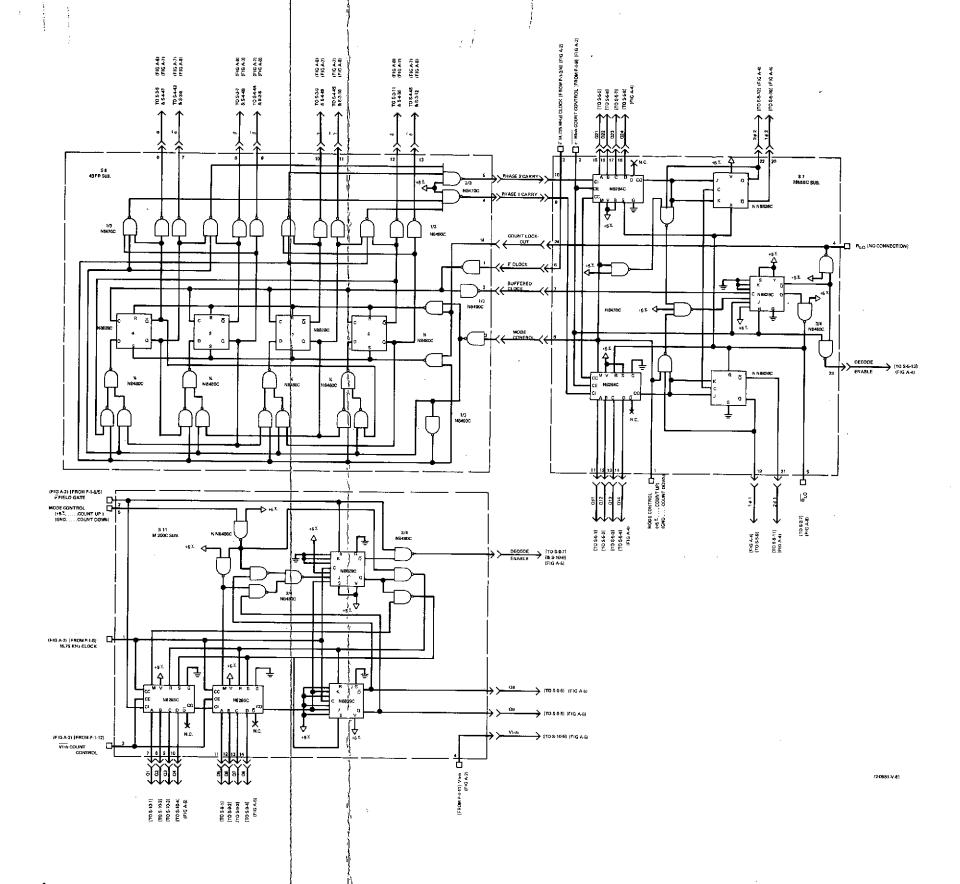

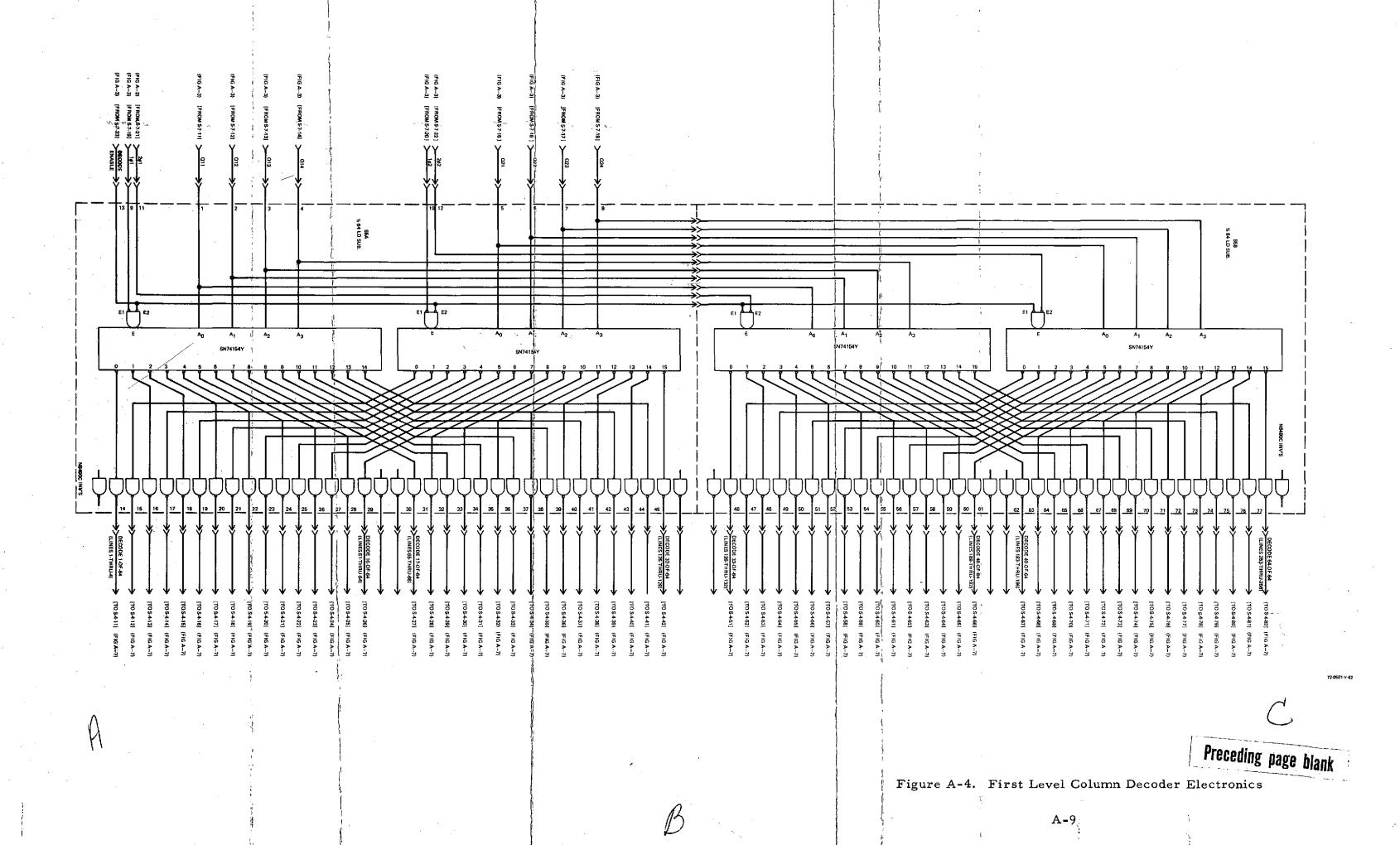

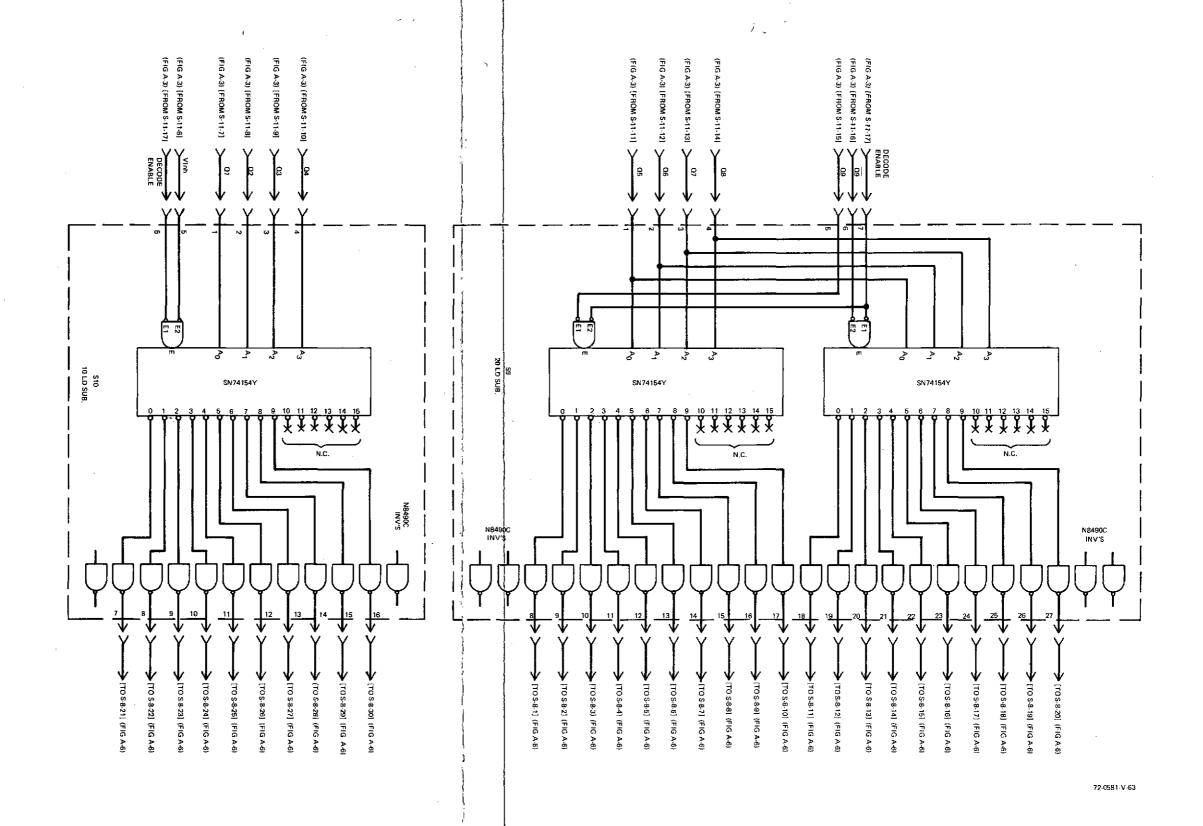

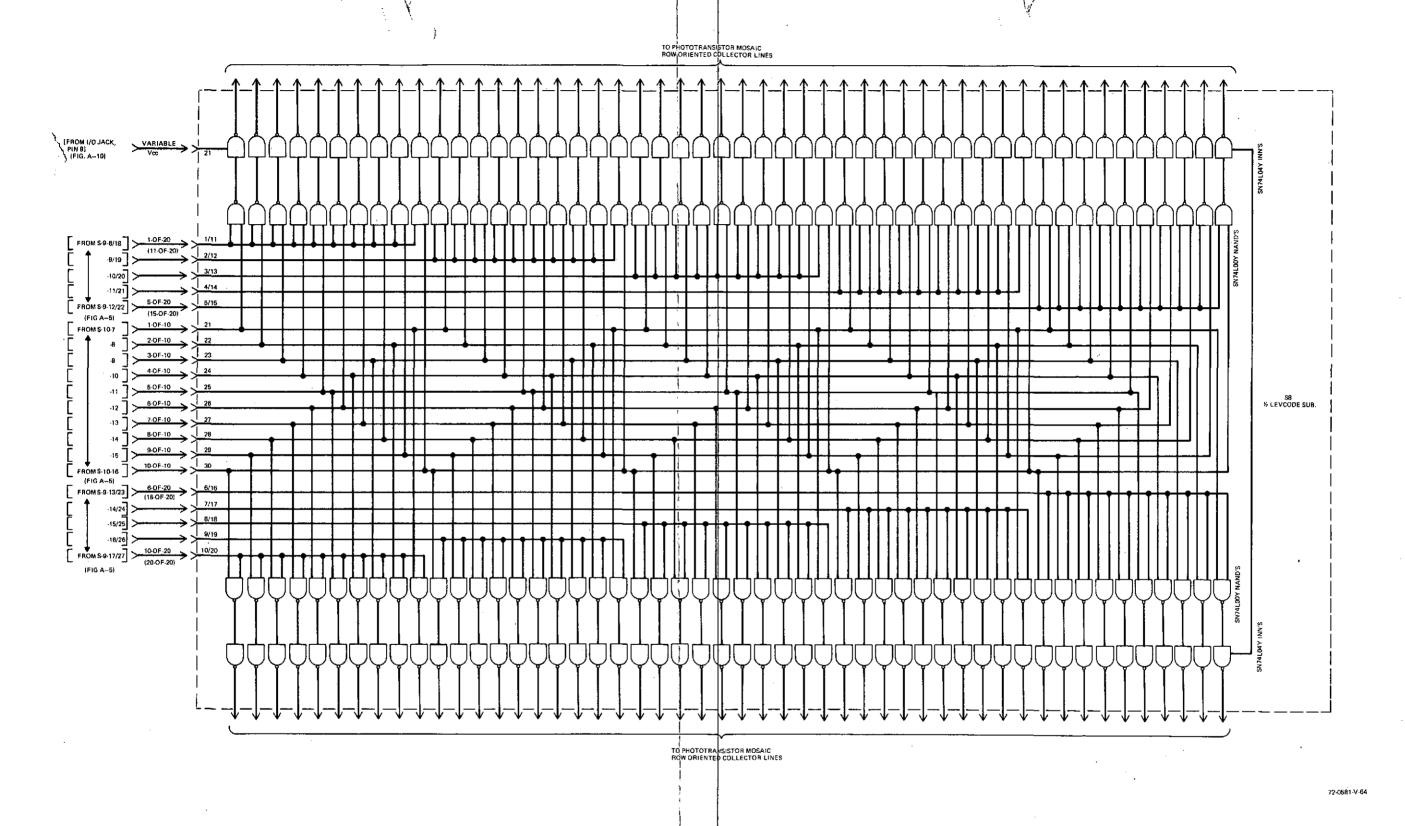

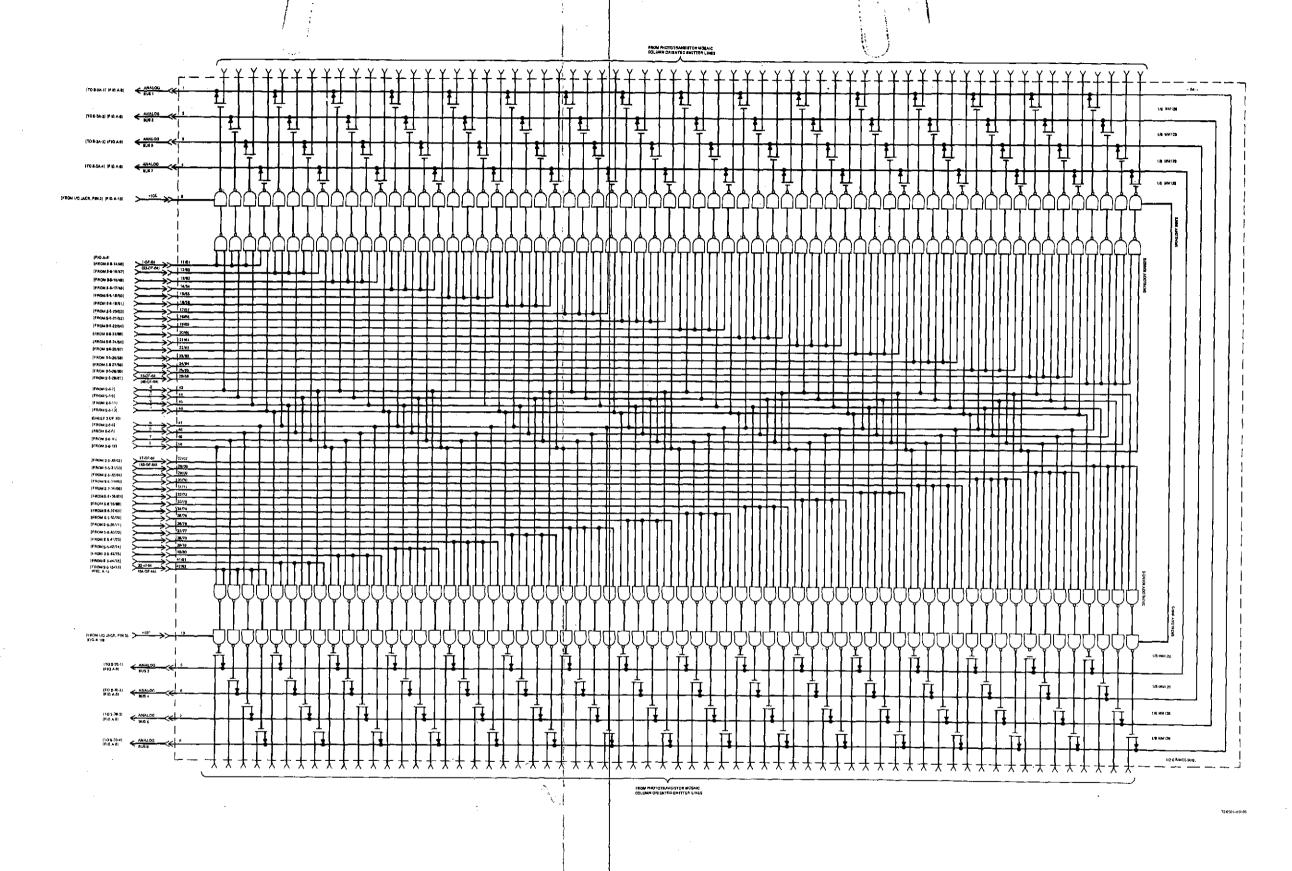

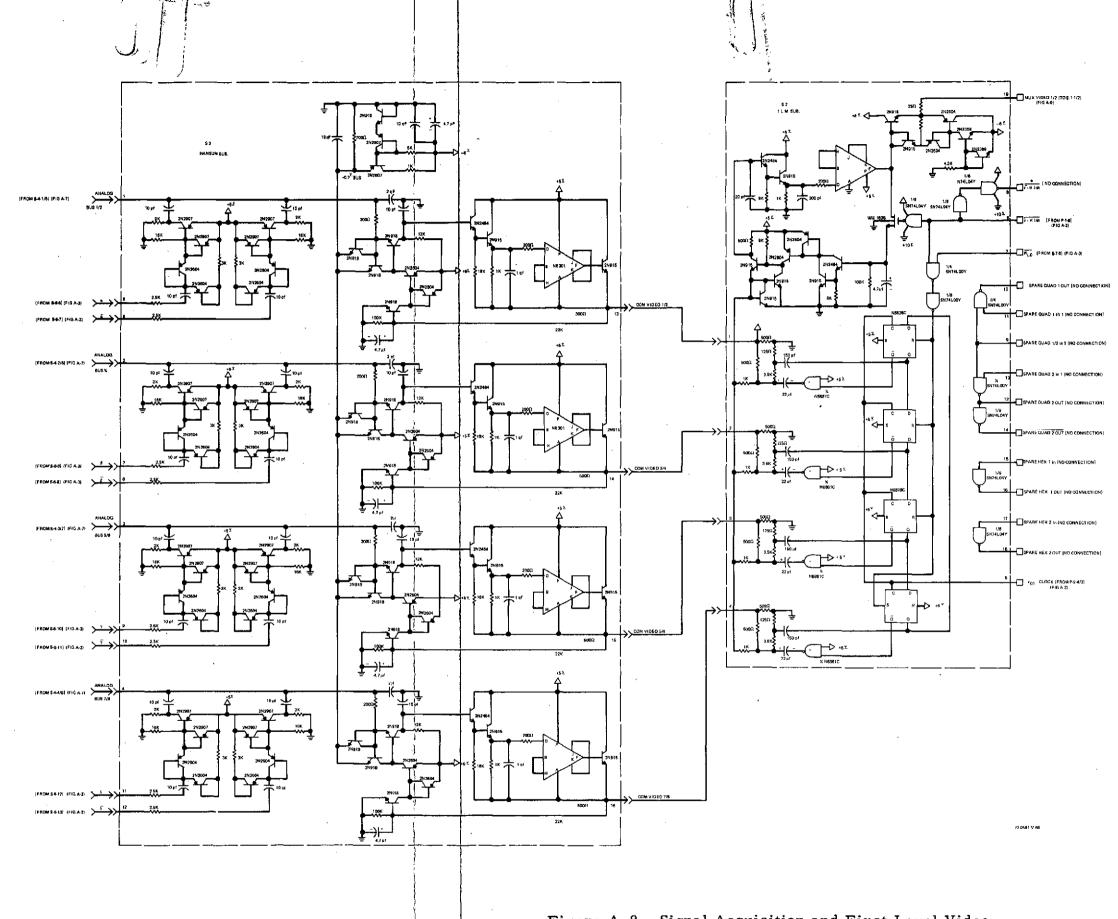

| Appendix A. Picture 45 Camera Schematic Diagrams | A-1           |

## LIST OF ILLUSTRATIONS

| Figure |                                                                                    | Page |

|--------|------------------------------------------------------------------------------------|------|

| 1-1    | Delivered System Time-Progress Chart for NAS 8-5112-<br>Program                    | 1-2  |

| 2-1    | Structure of the Phototransistor Mosaic Selected                                   | 2-4  |

| 2-2    | Transistor Structure                                                               | 2-6  |

| 2-3    | Impurity Profile                                                                   | 2-6  |

| 2-4    | 400-x-500 Element Mosaic Dimensions                                                | 2-9  |

| 2-5    | Photomicrographs of a Corner of Each of the Photomask                              | 2-11 |

| 3-1    | Open Tube Thermal Oxidation Apparatus                                              | 3-6  |

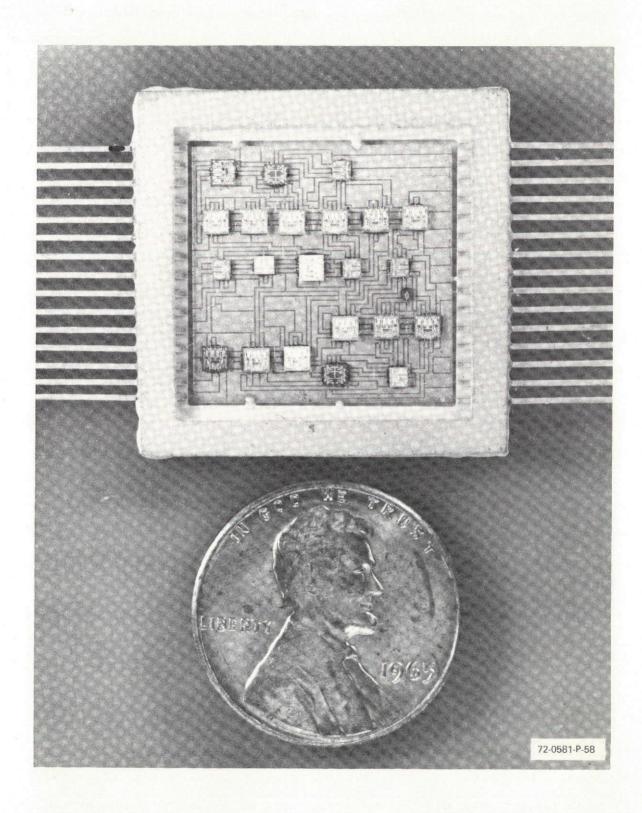

| 3-2    | 400-x-500 Element Silicone Phototransistor Matrix Array                            | 3-16 |

| 4-1    | Phototransistor Integration Mode of Operation                                      | 4-3  |

| 4-2    | Output Waveform - Phototransistor Integration Mode                                 | 4-8  |

| 4-3    | Section of Collector Strip - Mosaic Configuration                                  | 4-15 |

| 4-4    | Equivalent Circuit of Mosaic-Strip Collector Configuration                         | 4-16 |

| 4-5    | Common Emitter Line Capacitance                                                    | 4-17 |

| 4-6    | Operation of Phototransistor in Mosaic                                             | 4-20 |

| 4-7    | Equivalent Circuits of Phototransistor Tmn                                         | 4-24 |

| 4-8    | Emitter Line Switch Capacitance                                                    | 4-27 |

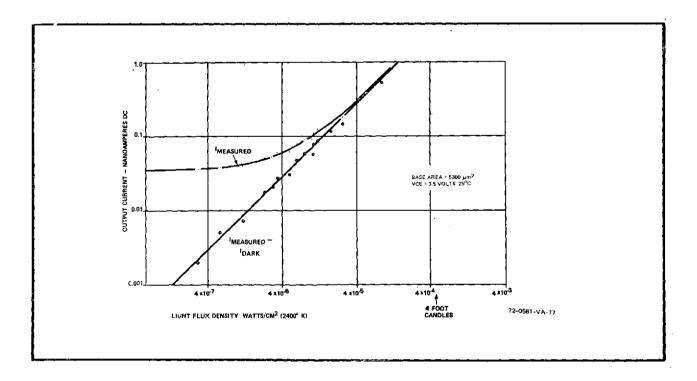

| 4-9    | Steady State Phototransistor Response                                              | 4-28 |

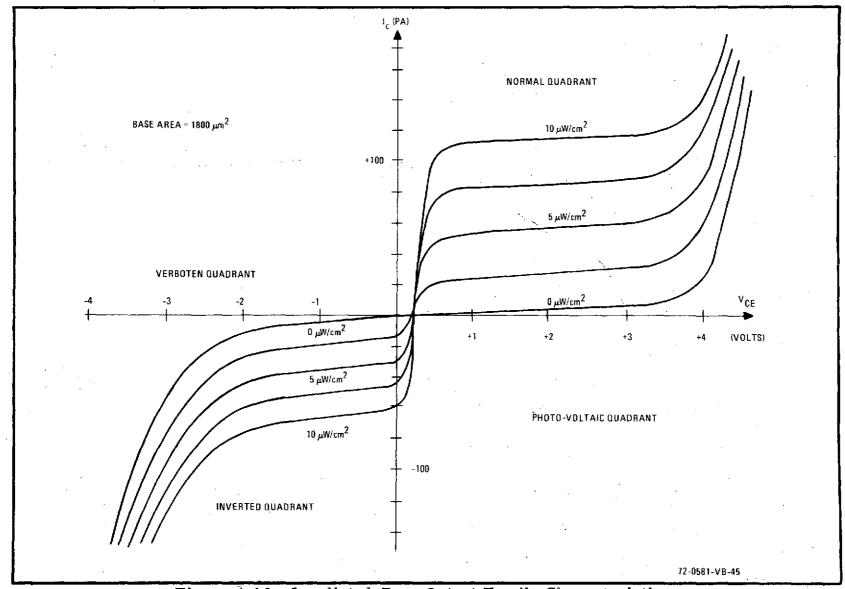

| 4-10   | Irradiated-Based Output Family Characteristics of Phototransistor                  | 4-31 |

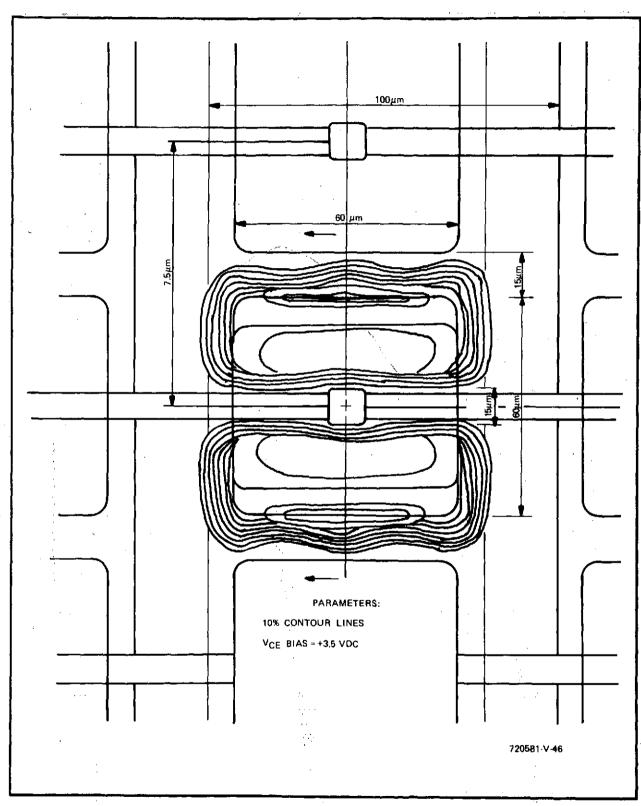

| 4-11   | Sensitivity Contour Map for Small Geometry Sensor Mosaic                           | 4-33 |

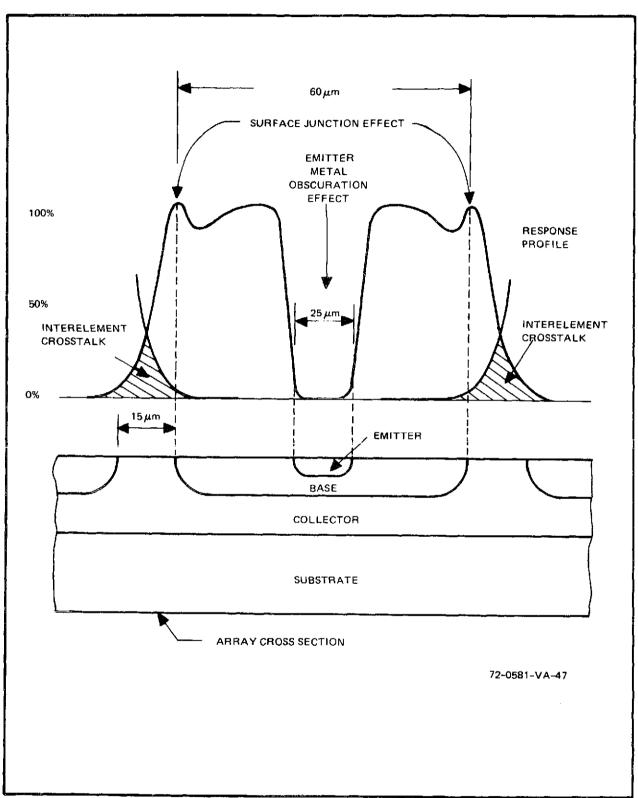

| 4-12   | Sensitivity Profile Map for Small Geometry Sensor Mosaic                           | 4-34 |

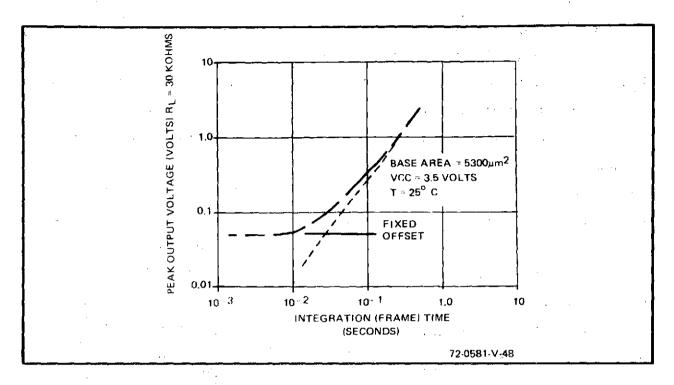

| 4-13   | Pulsed Mode Phototransistor Dark Response                                          | 4-35 |

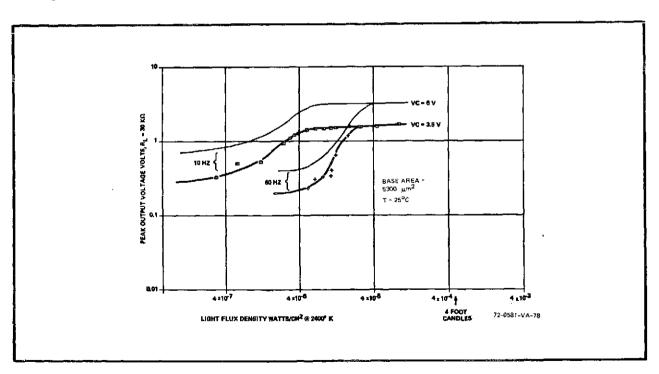

| 4-14   | Pulsed Mode Transfer Characteristics at Two Frame Rates for Two Collector Voltages | 4-36 |

| Figure |                                                                                                                            | Page          |

|--------|----------------------------------------------------------------------------------------------------------------------------|---------------|

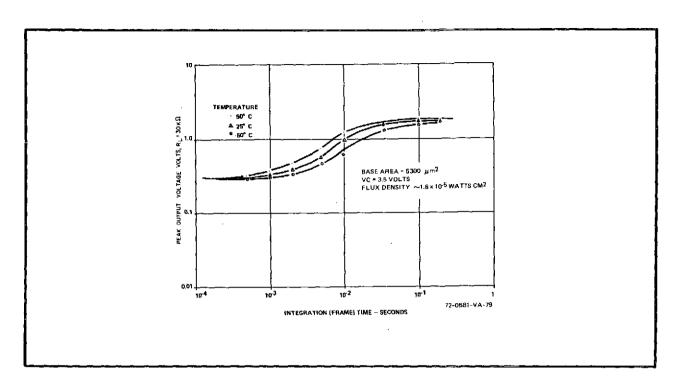

| 4-15   | Temperature Dependence of Pulsed Integration                                                                               | 4-38          |

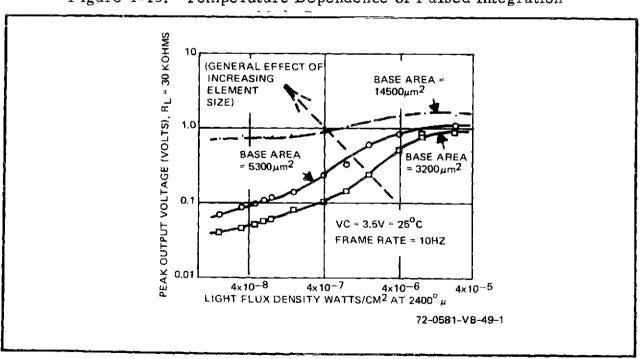

| 4-16   | Pulsed Mode Transfer Characteristics for Different<br>Element Designs                                                      | 4-38          |

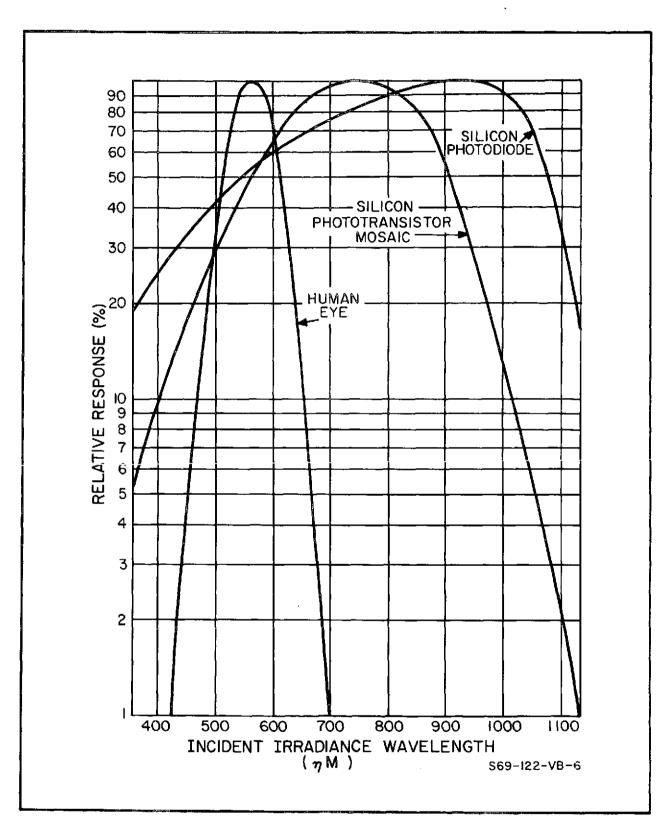

| 4-17   | Spectral Response Comparison                                                                                               | 4-40          |

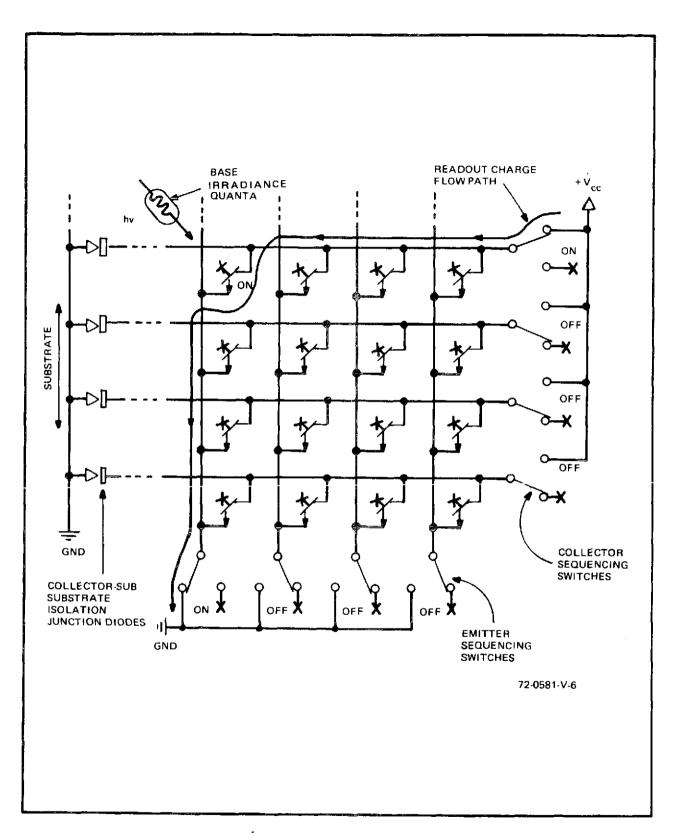

| 5-1    | Schematic for 4-x-4 Element Section of a Phototransistor<br>Matrix                                                         | 5-4           |

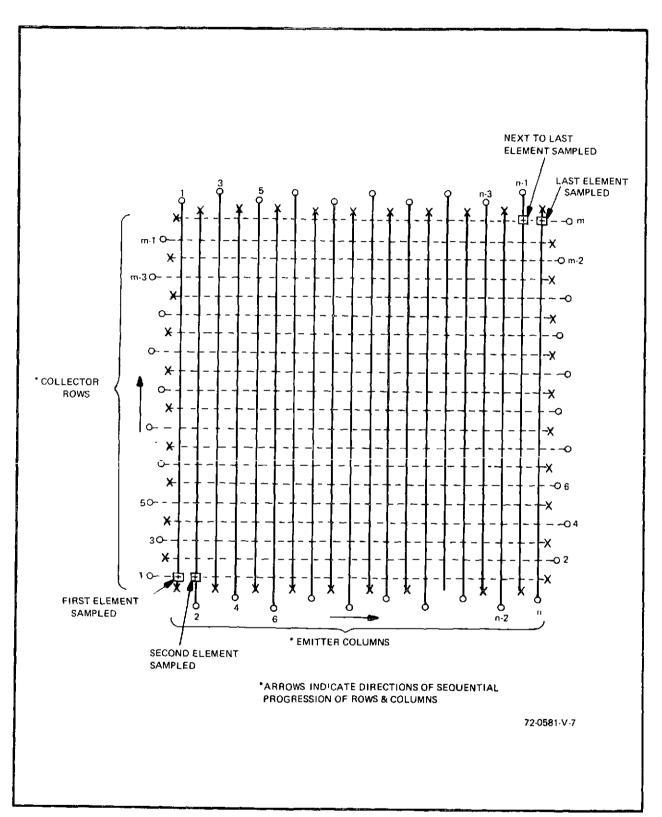

| 5-2    | Basic Elemental Interrogation Format for X-Y Accessed Sensor Mosaics                                                       | 5-6           |

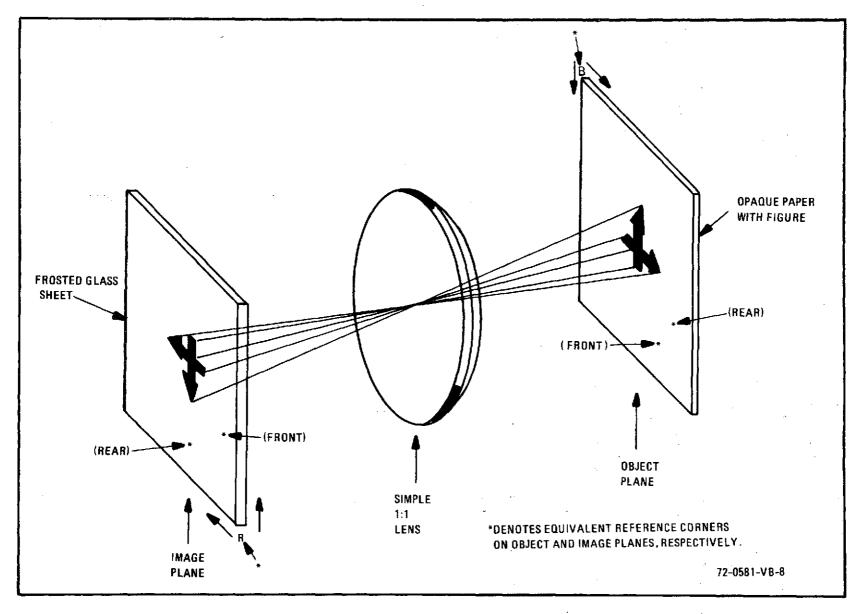

| 5-3    | Optical Interface Image Inversion Through Simple Lens                                                                      | 5-7           |

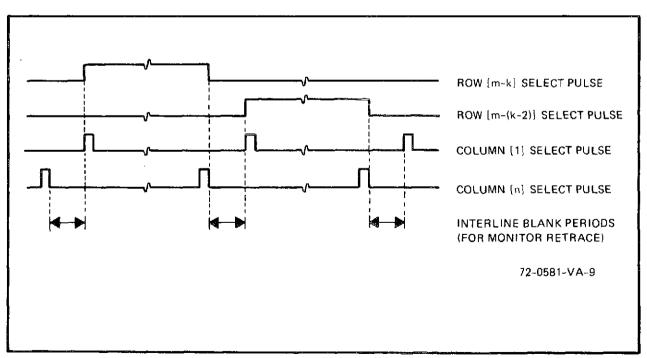

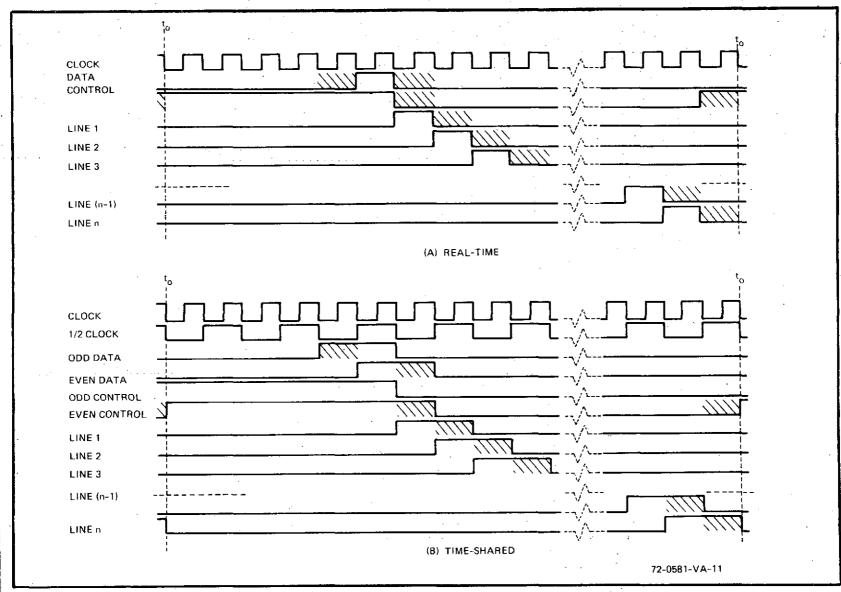

| 5-4    | Basic Electronic Scanning Digital Timing Relationships for an M-by-N Element Array with Row Interlacing                    | 5 <b>-</b> 8  |

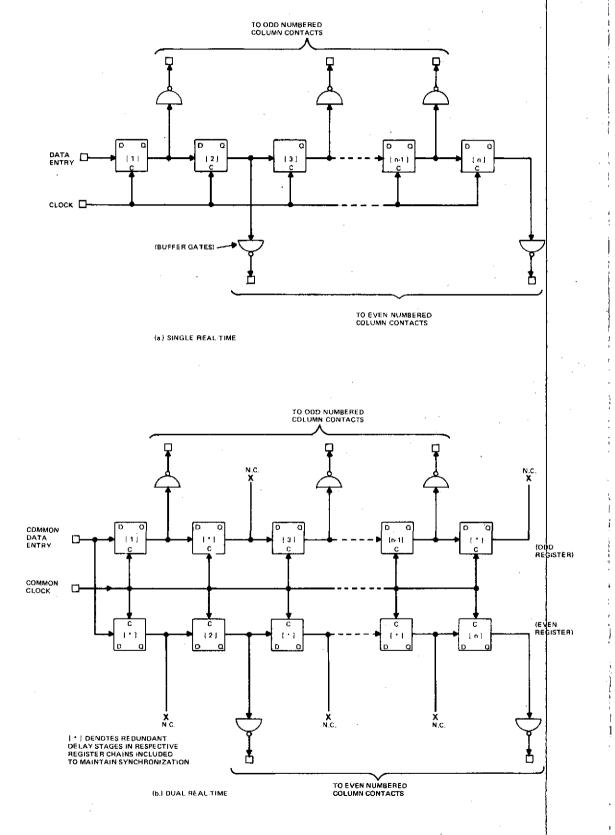

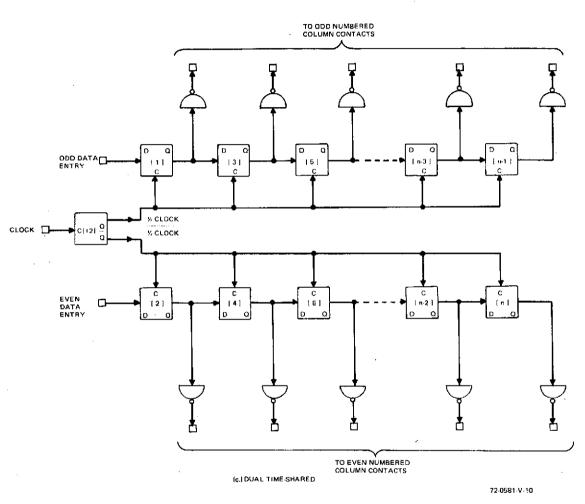

| 5-5    | Shift Register Column Sequencer Chains                                                                                     | 5-11          |

| 5-6    | Column Sequencer Timing Diagram                                                                                            | 5-13          |

| 5-7    | Serial Shift Register Sequencer with Built-in Control Redundancy                                                           | 5-14          |

| 5-8    | Shift Register Scanned 50-x-50 Element MIC System Design with Control Redundancy                                           | 5-16          |

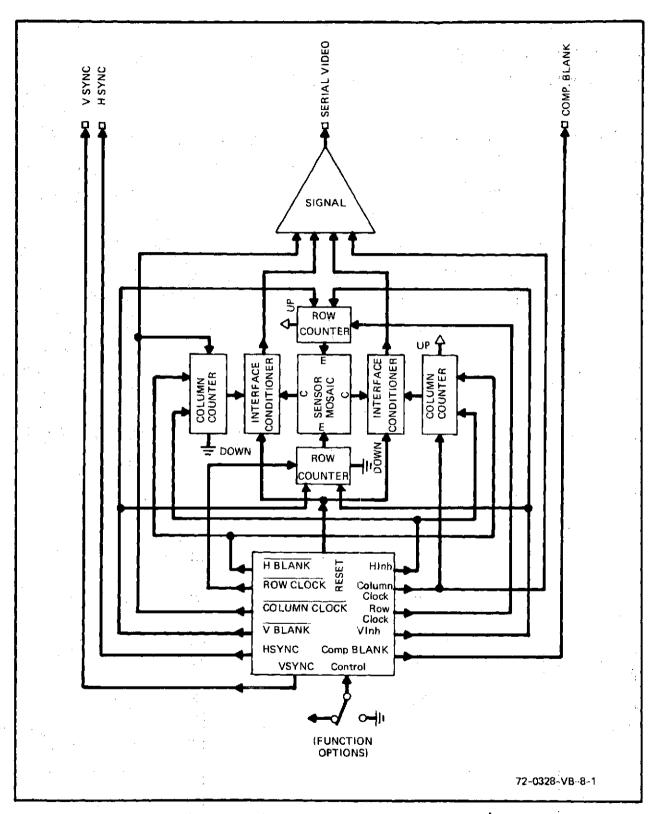

| 5-9    | Generalized Split-Function Counter/Decoder Timed MIC System Design                                                         | 5-17          |

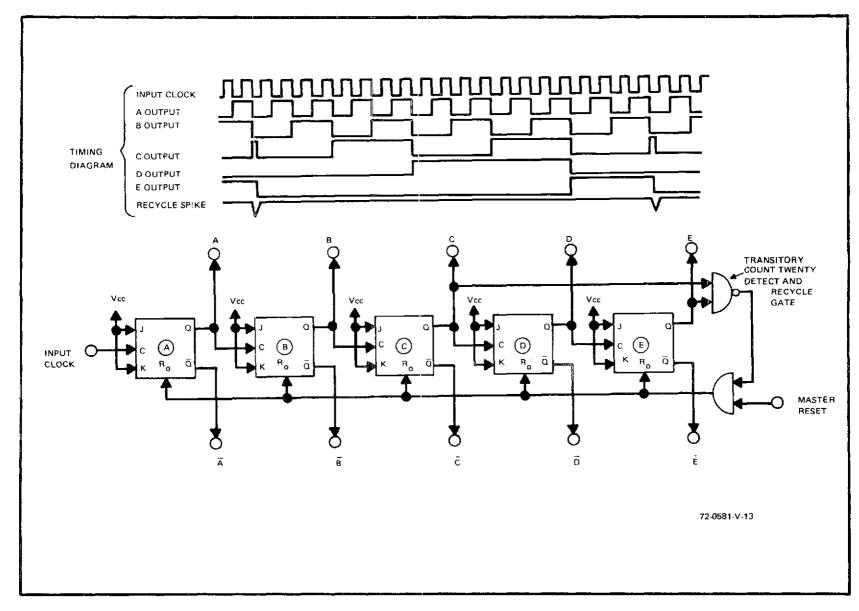

| 5-10   | Asynchronous Modulo 20 Ripple Counter Design                                                                               | 5-20          |

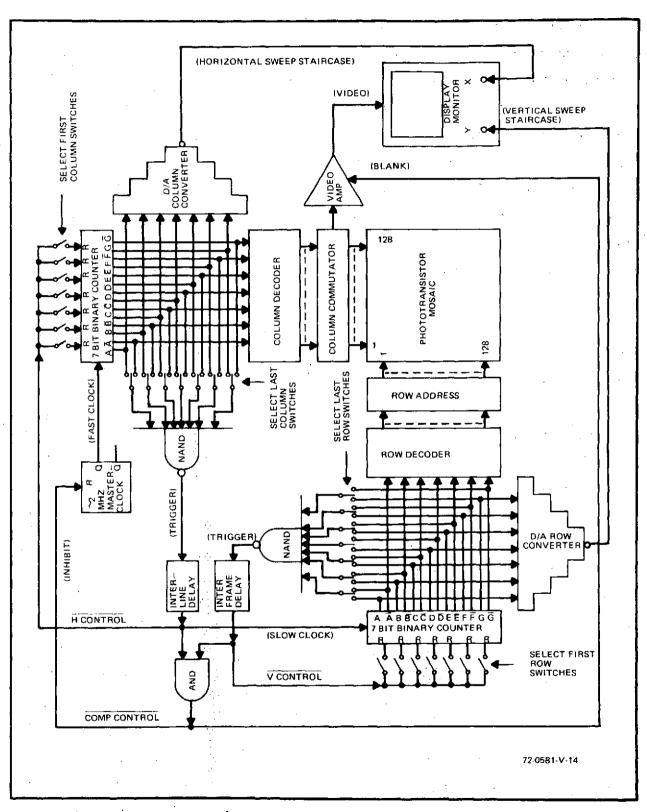

| 5-11   | Counter/Decoder Timed 128-x-128 Element MIC System Design Featuring Sector Scan Selection                                  | 5-21          |

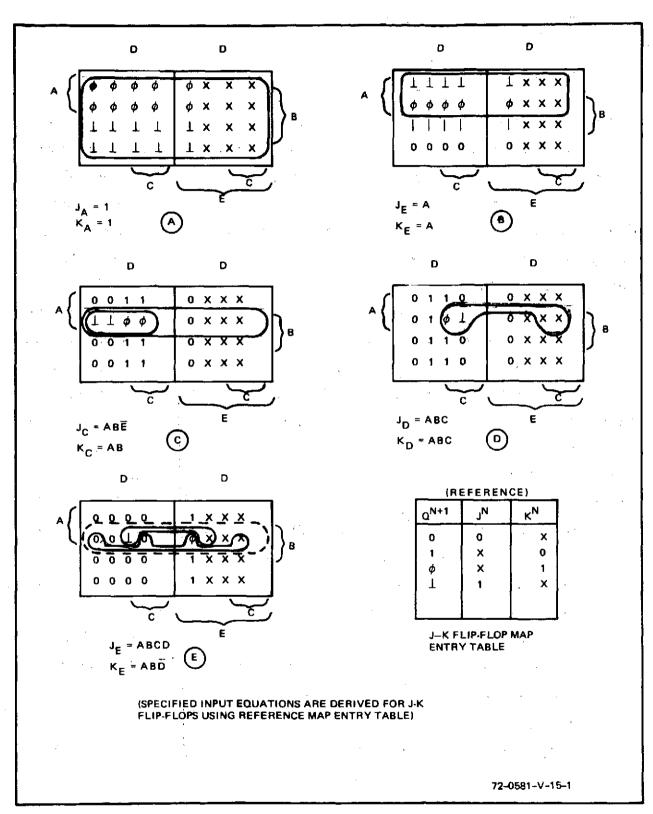

| 5-12   | Karnaugh Mappings of Flip-Flop Input Conditions for Sample Design Modulo 20 Counter                                        | 5-25          |

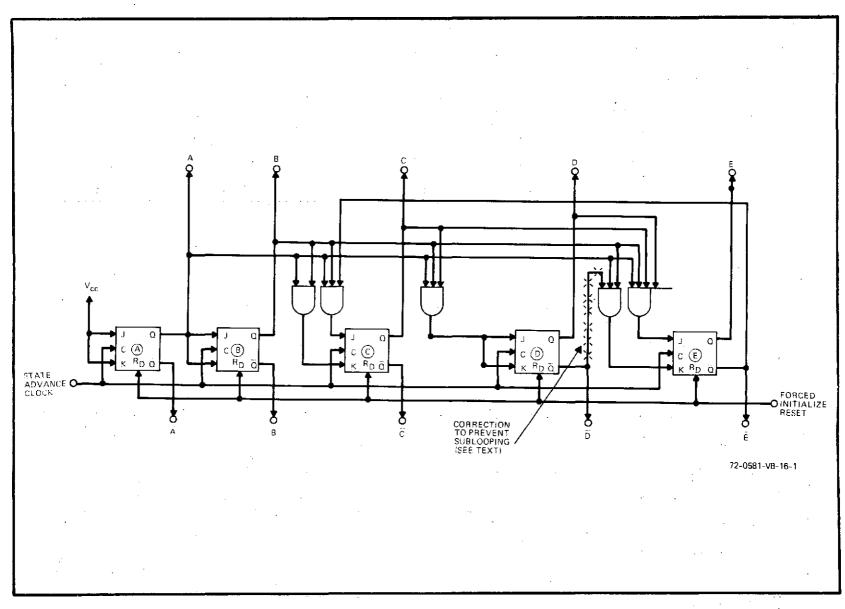

| 5-13   | Circuit Diagram Implementation of Modulo 20 Counter<br>Flip-Flop Input Equations Derived from Karnaugh Maps                | 5-27          |

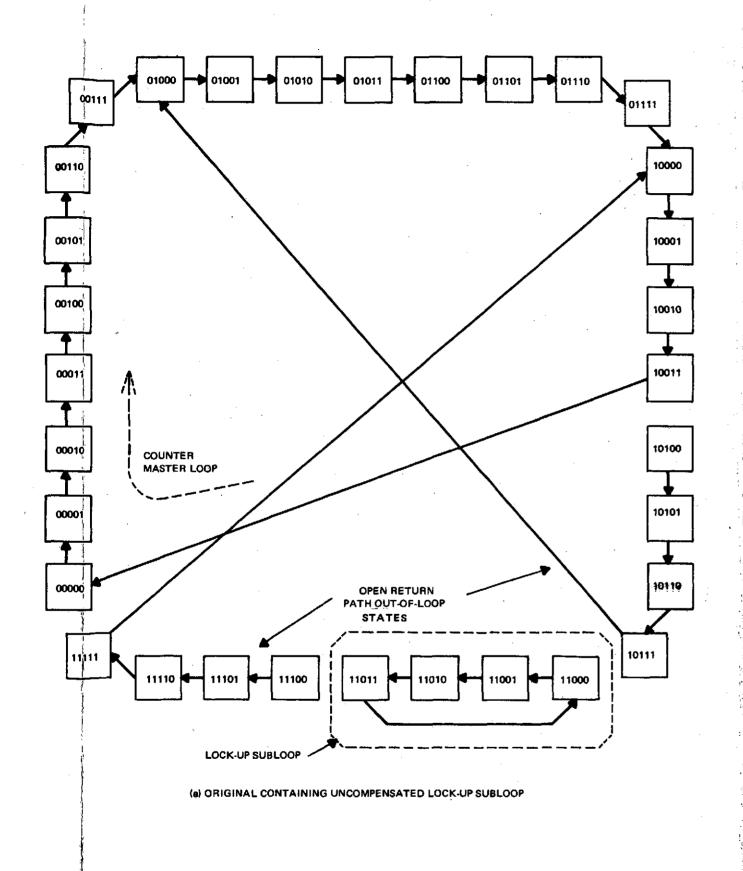

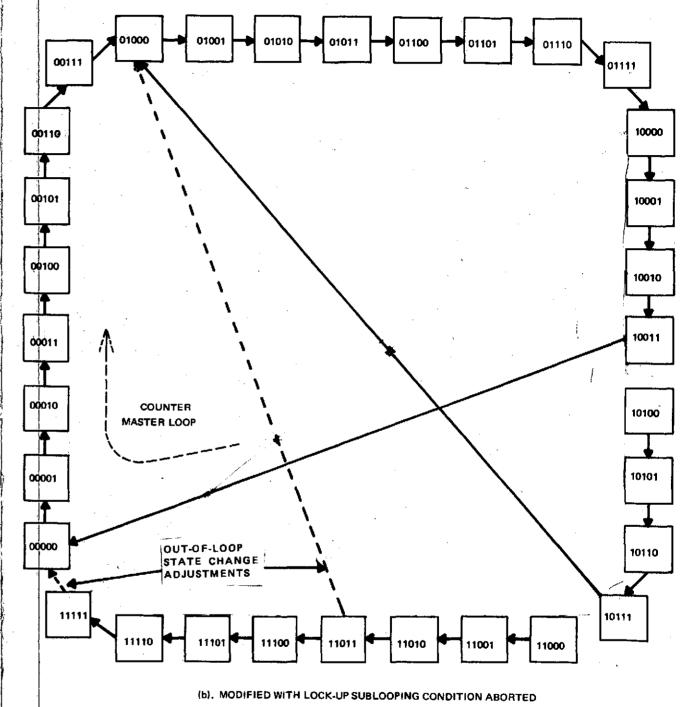

| 5-14   | State Diagrams for Modulo 20 Counter Design                                                                                | 5-29          |

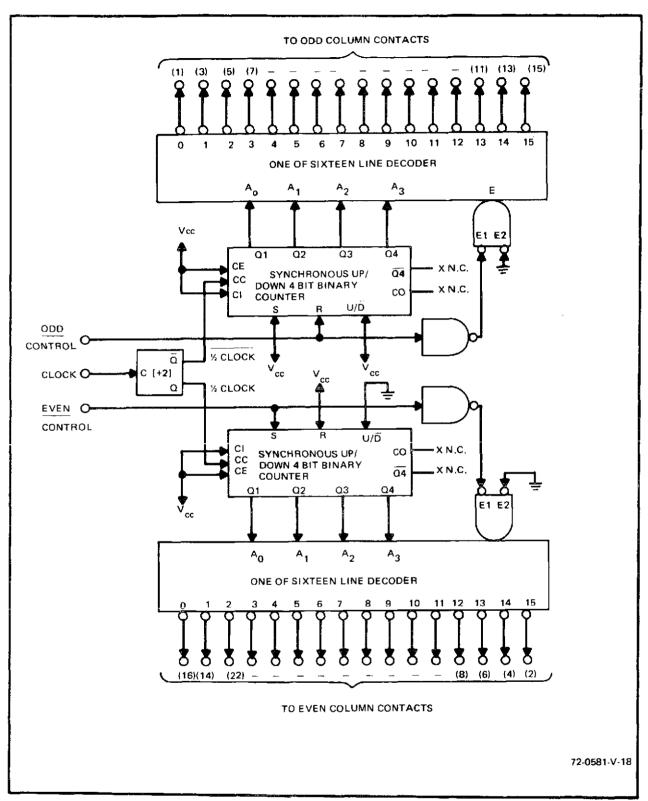

| 5-15   | Time-Shared Synchronous Counter/Decoder Column<br>Sequencer Design Using Commercial Logic Blocks                           | 5-32          |

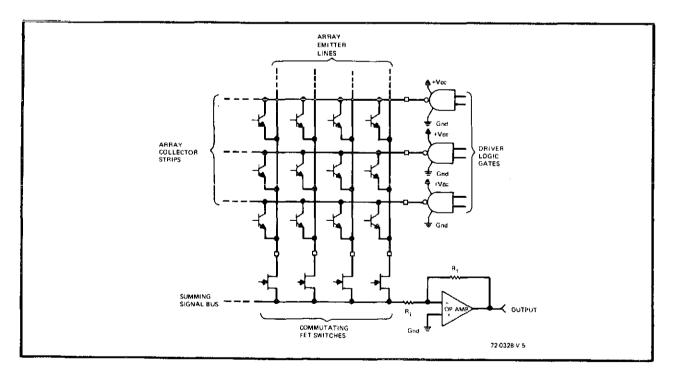

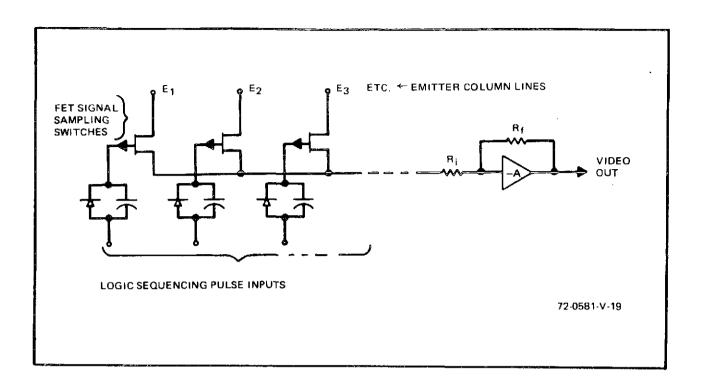

| 5-16   | Standard Emitter Readout for Phototransistor Arrays Using J-FET Line Commutation and Operational Amplifier Signal Scanning | 5 <b>-</b> 34 |

| Figure |                                                                                                                                                      | Page          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

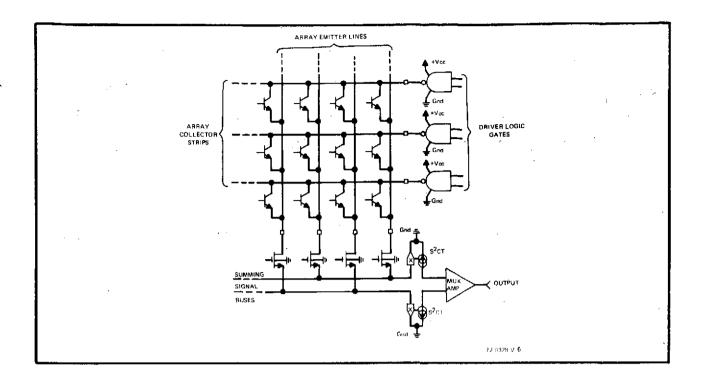

| 5-17   | Time-Shared Emitter Readout for Phototransistor Arrays Using Multiplexed MOS-FET Line Commutation and Solid-State Current Transformer Signal Summing | 5-37          |

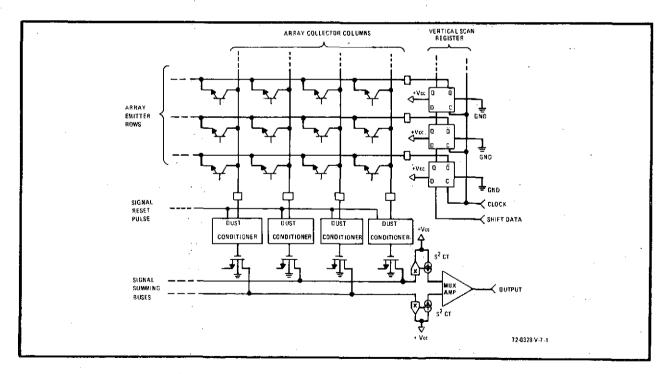

| 5-18   | Time-Shared DUST Interface for Phototransistor Arrays Using Multiplex MOS-FET Column Commutation and Solid-State Current Transformer Signal Summing  | 5-39          |

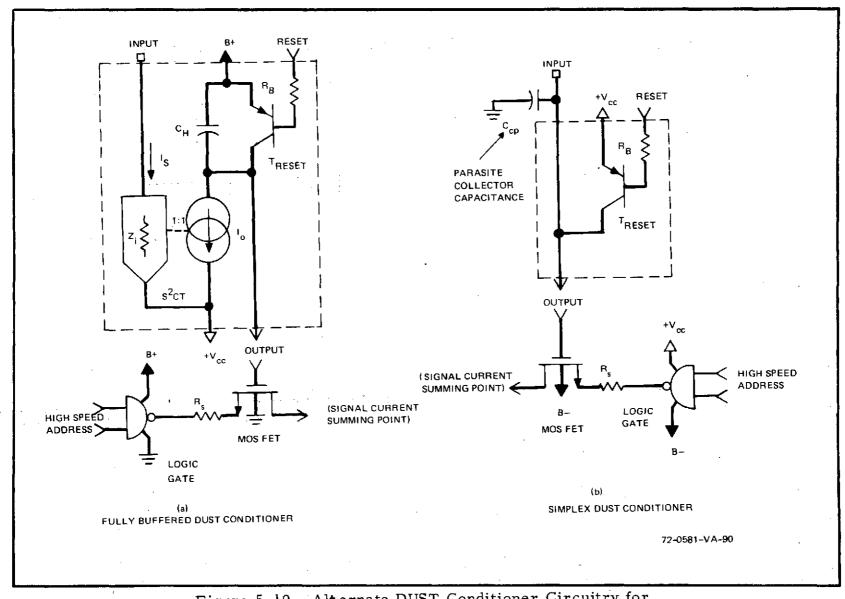

| 5-19   | Alternate DUST Conditioner Circuitry for Integrated Array Imagers                                                                                    | 5-41          |

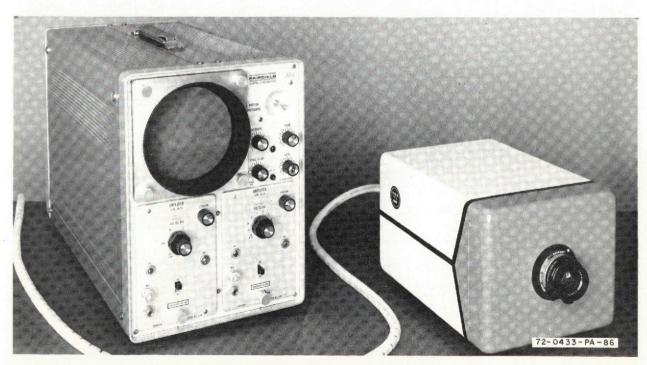

| 5-20   | 100-x-128 Element Integrated Array Camera and Monitor                                                                                                | 5-45          |

| 5-21   | Op Amp Commutation Summing                                                                                                                           | 5-46          |

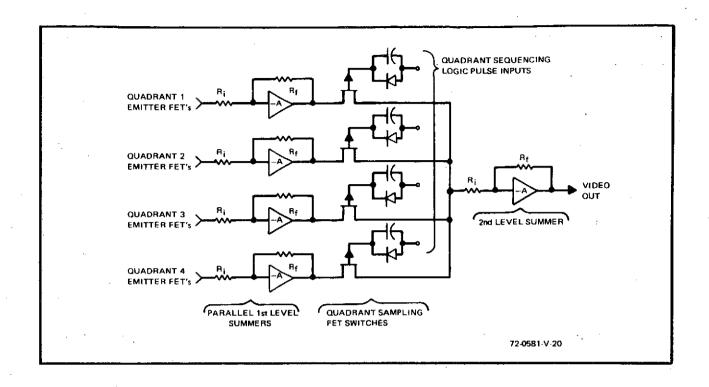

| 5-22   | Dual Level Op Amp Commutation Summing                                                                                                                | 5-47          |

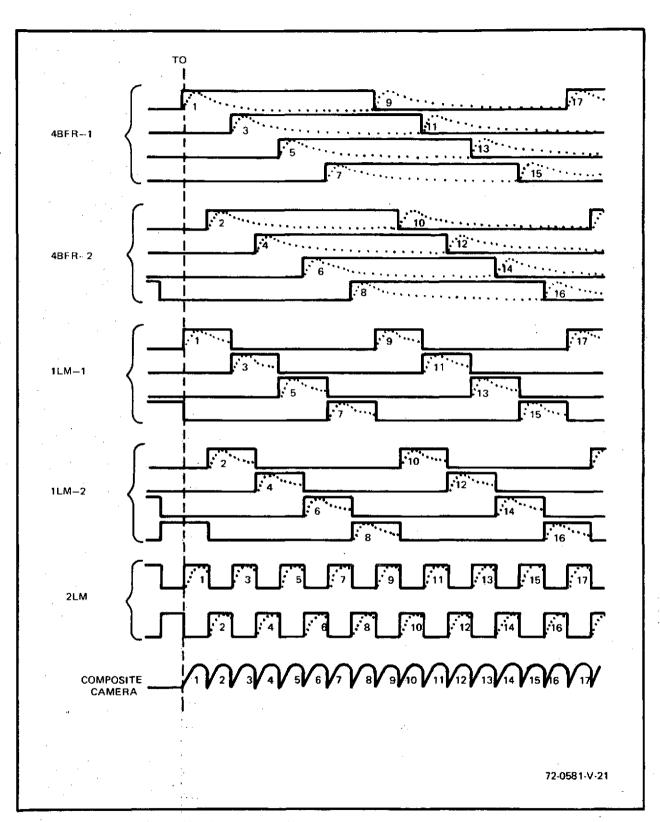

| 5-23   | Idealized Timing Interrelationships for Video Signals Processed Through "45" PICTURE System Electronics                                              | 5-49          |

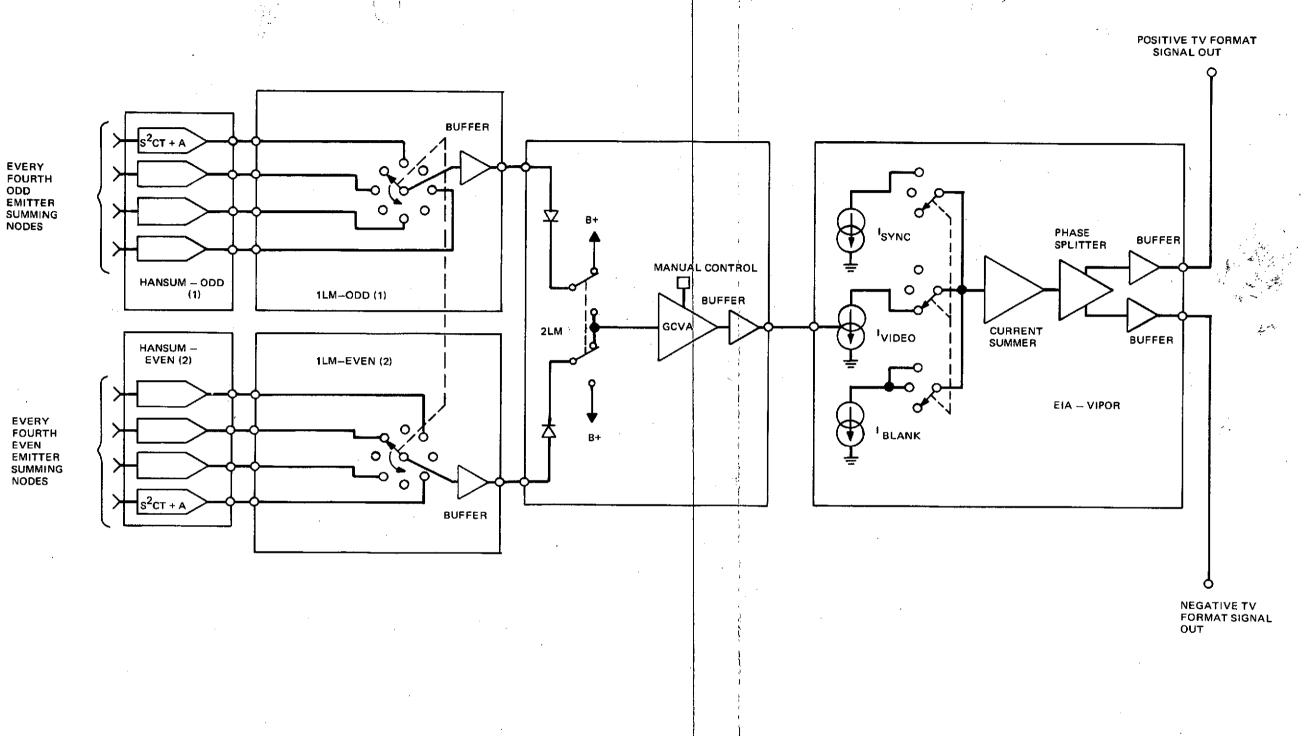

| 5-24   | Basic Function Diagram of Analog Signal Chain in 400-x-500 Element Integrated Array Camera                                                           | 5-50          |

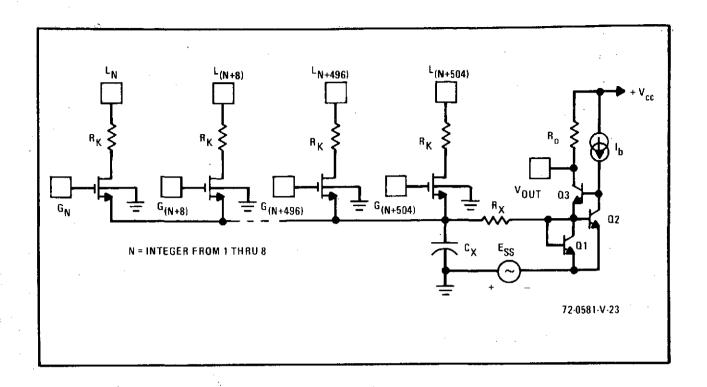

| 5-25   | One-of-Eight Solid-State Current Transformer Summed Signal Commutation Channels in PICTURE ''45" Camera                                              | 5-51          |

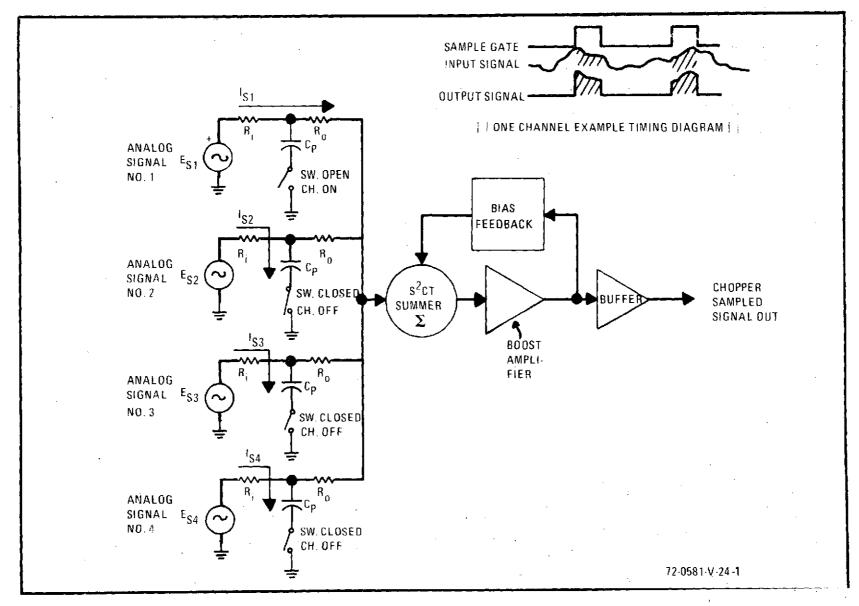

| 5-26   | Four-Channel Analog Sampling Processor Using Parallel Capacitively Clamped Chopping                                                                  | 5-53          |

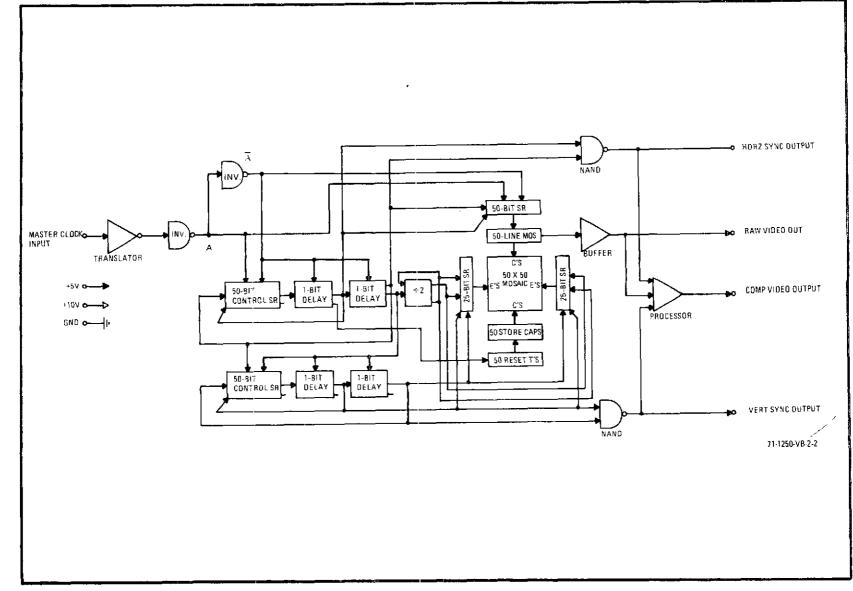

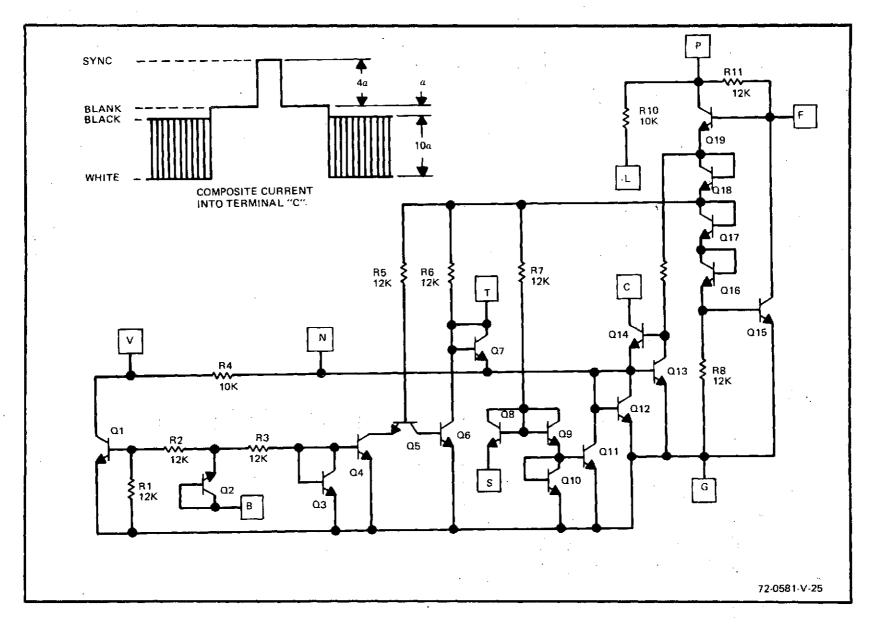

| 5-27   | Low Power LSI Configured EIA TV Format Video Generator                                                                                               | 5 <b>-</b> 55 |

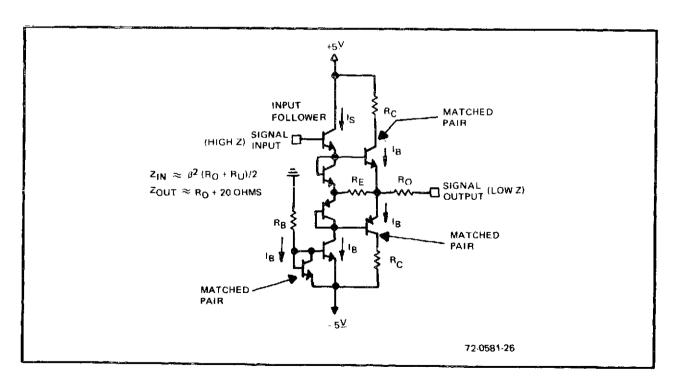

| 5-28   | High Performance Complementary Push-Pull Power Line Driver                                                                                           | 5-56          |

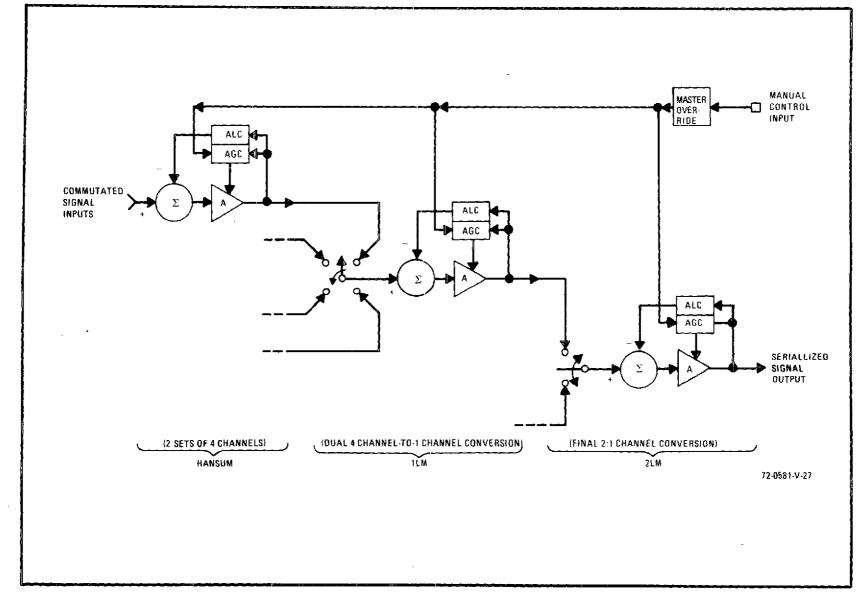

| 5-29   | Time-Shared Analog Signal Processor Chain with Self-Looping Per-Stage Automatic Gain Control                                                         | 5 <b>-</b> 58 |

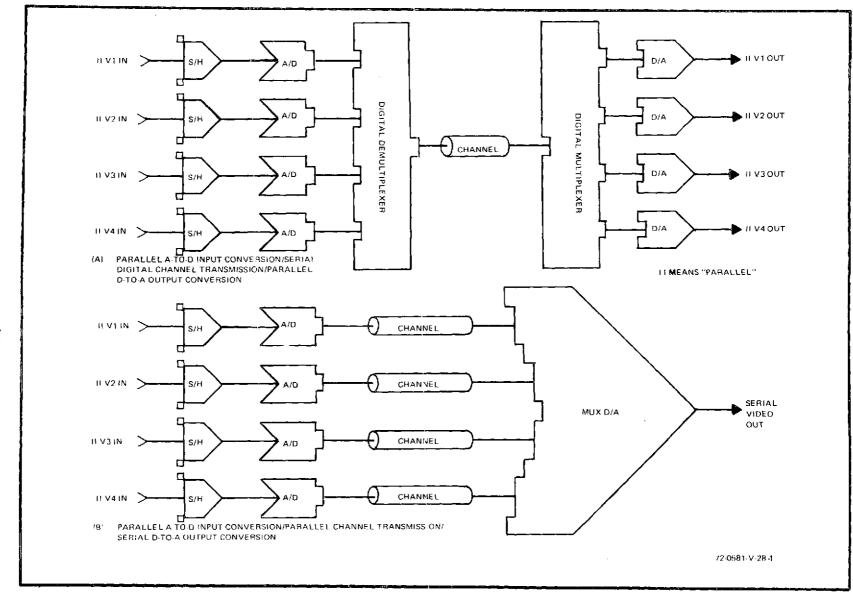

| 5-30   | Block Diagram Examples of Digital Conversion of Analog<br>Data                                                                                       | 5-60          |

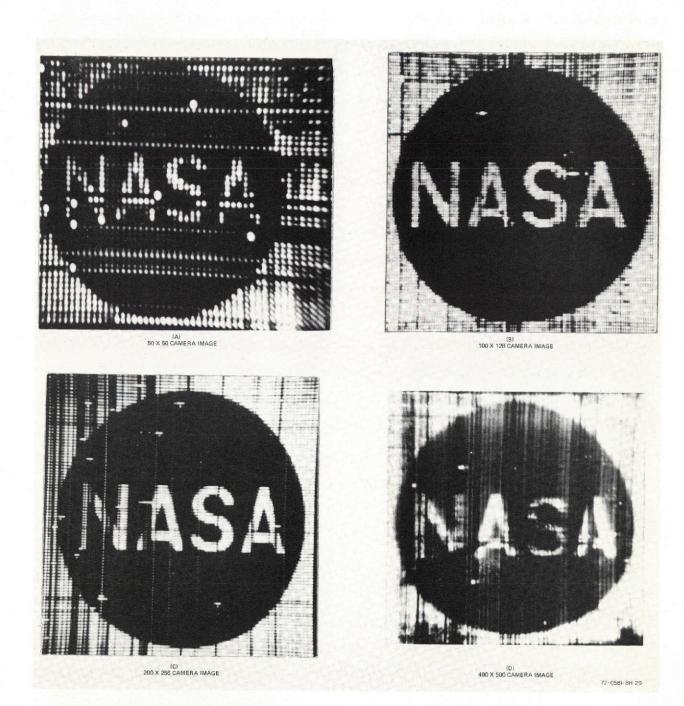

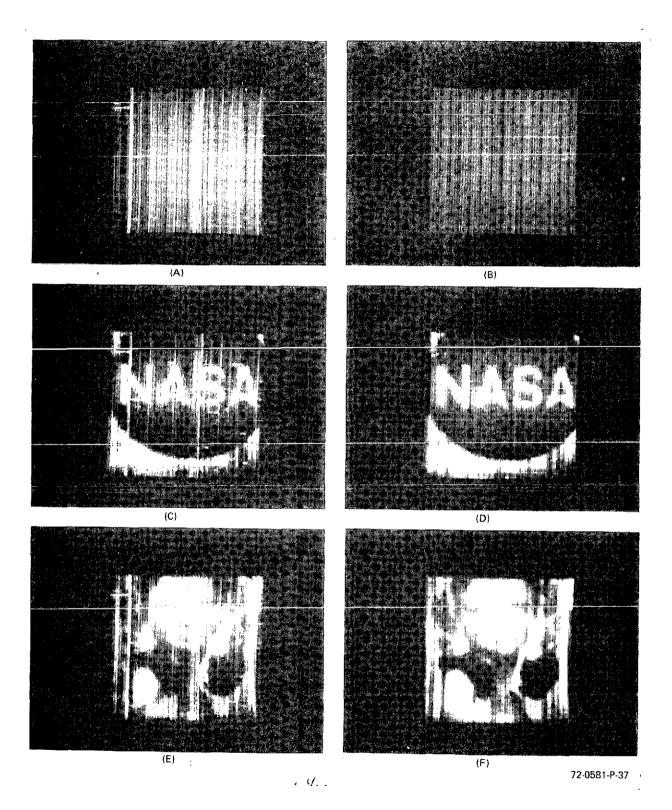

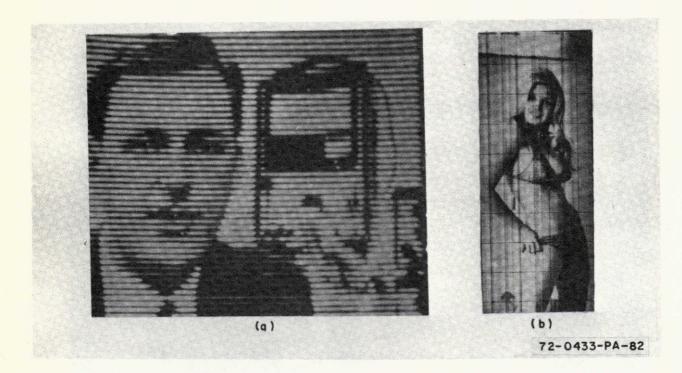

| 5-31   | Representative Display Monitor Photos of Output Images<br>from Successive Generations of the Image Converter of<br>Radical Design                    | 5-63          |

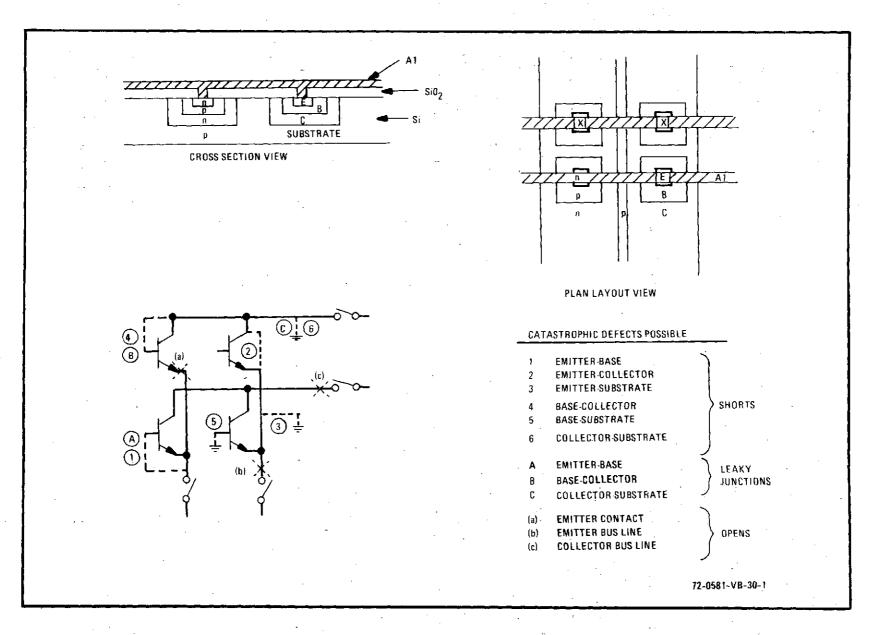

| 5-32   | Possible Failures in Phototransistor Monoliths                                                                                                       | 5-65          |

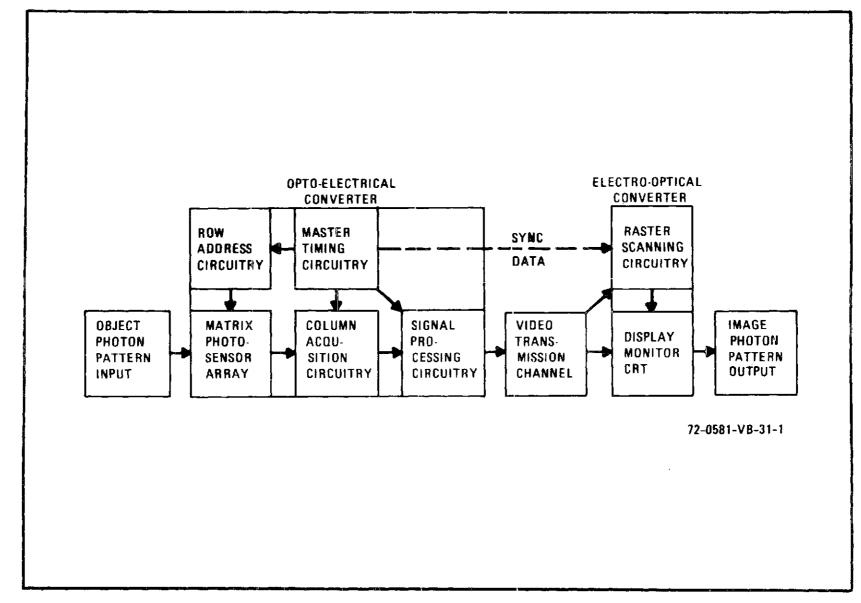

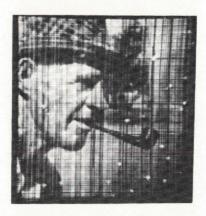

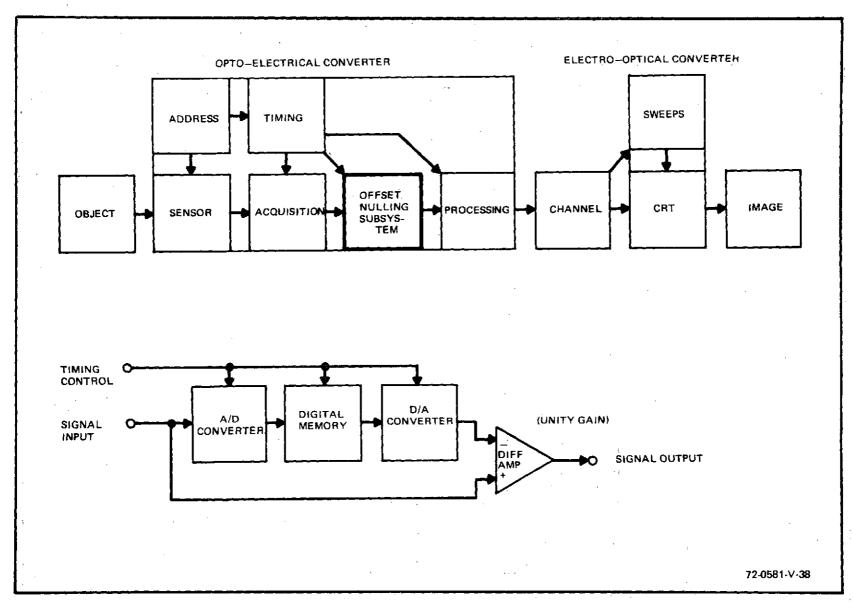

| 5-33   | General Block Diagram of Imaging System                                                                                                              | 5-68          |

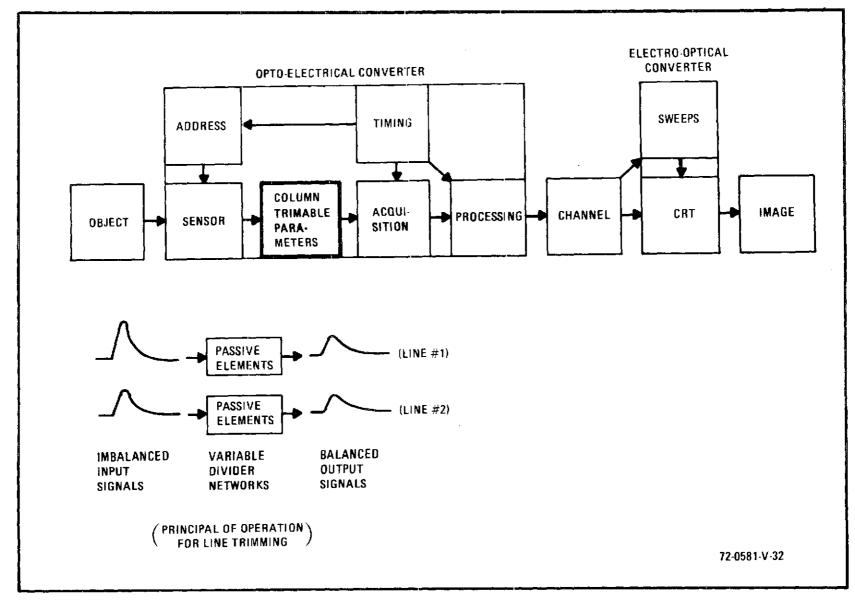

| 5-34   | Imager Block Diagram with Column Trimmable Parameters Inserted                                                                                       | 5-70          |

| Figure       |                                                                                      | Page          |

|--------------|--------------------------------------------------------------------------------------|---------------|

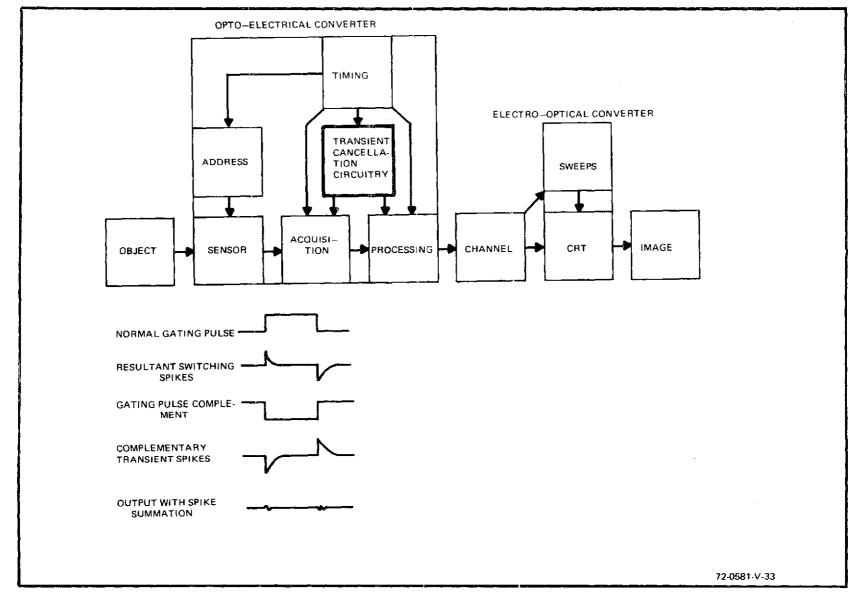

| 5-35         | Imager Block Diagram with Transient Cancellation<br>Circuitry Added                  | 5-72          |

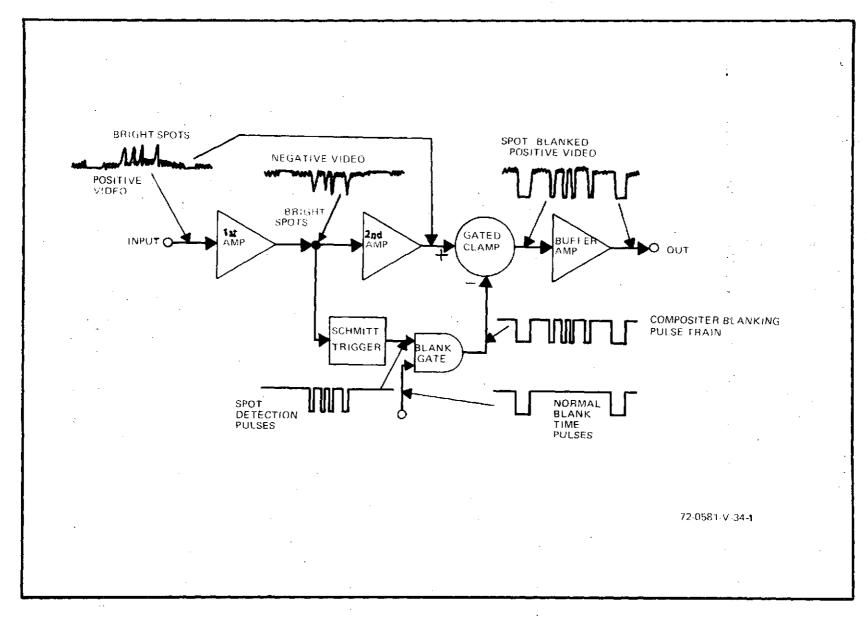

| 5-36         | Block Diagram of Overamplitude Bright Spot Blanker                                   | 5-73          |

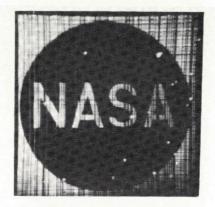

| 5-37         | Effect of Bright Spot Blanking on Image Appearance                                   | 5 <b>-</b> 75 |

| 5-38         | Imager Block Diagram with Postconverter Processing Supplied                          | 5-76          |

| 5-39         | Effect of Postconverter Processing on Image Appearance                               | 5-78          |

| 5-40         | Imager Block Diagram with Commutation Offset Nulling<br>Subsystem Installed          | 5-79          |

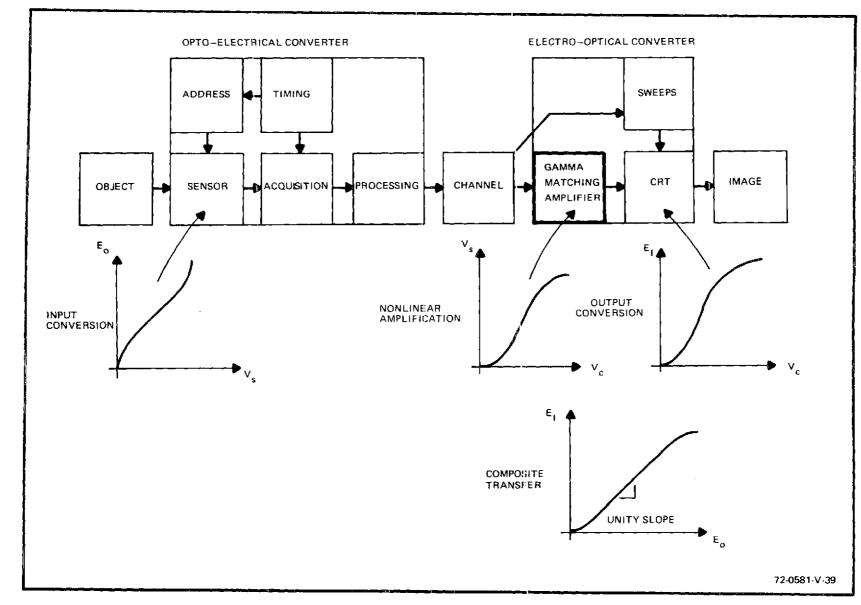

| 5 <b>-41</b> | Imager Block Diagram with Input/Output Gamma Matching Provided                       | 5+80          |

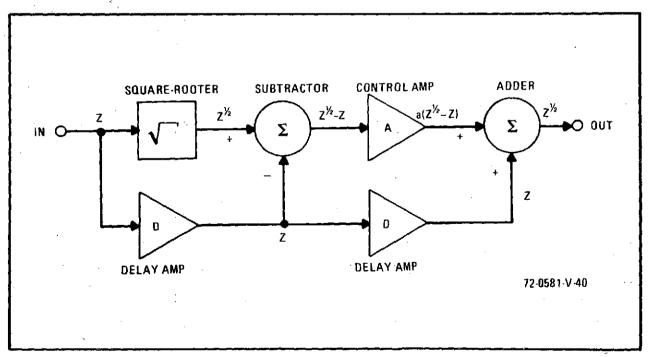

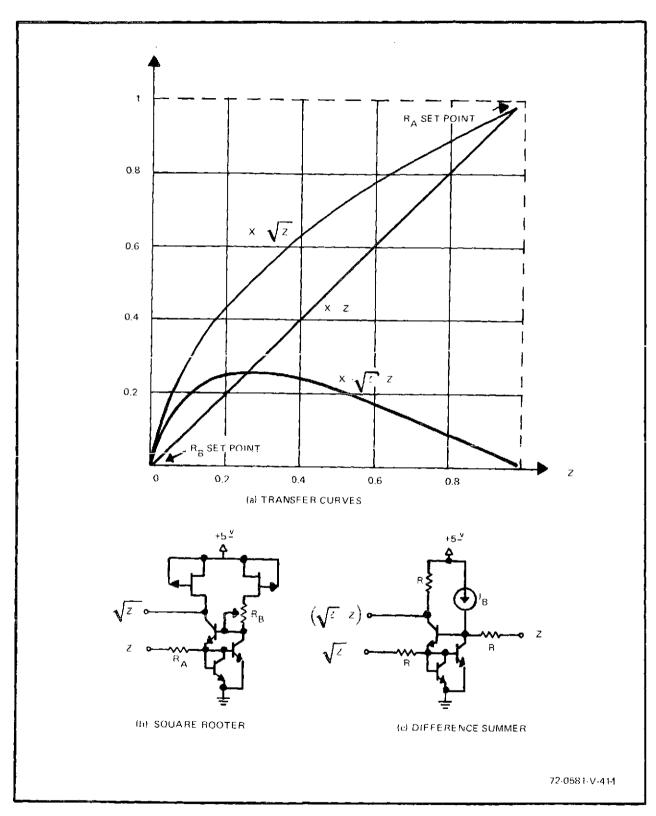

| 5-42         | Functional Block Diagram of Reciprocal Gamma Synthesizer                             | 5-81          |

| 5-43         | Reciprocal Gamma Synthesizer Primary Function Specifications                         | 5-82          |

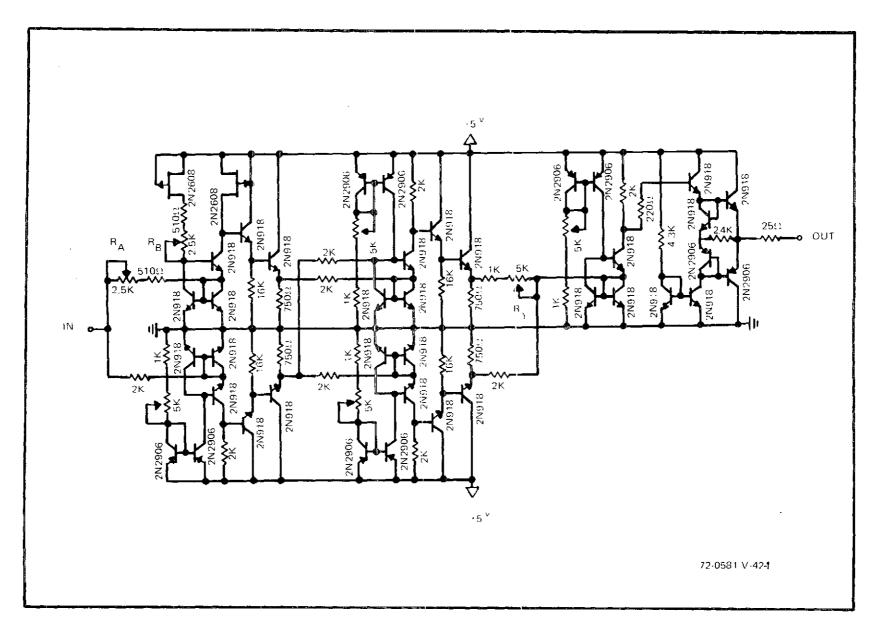

| 5-44         | Composite Reciprocal Gamma Synthesizer Circuit                                       | 5-84          |

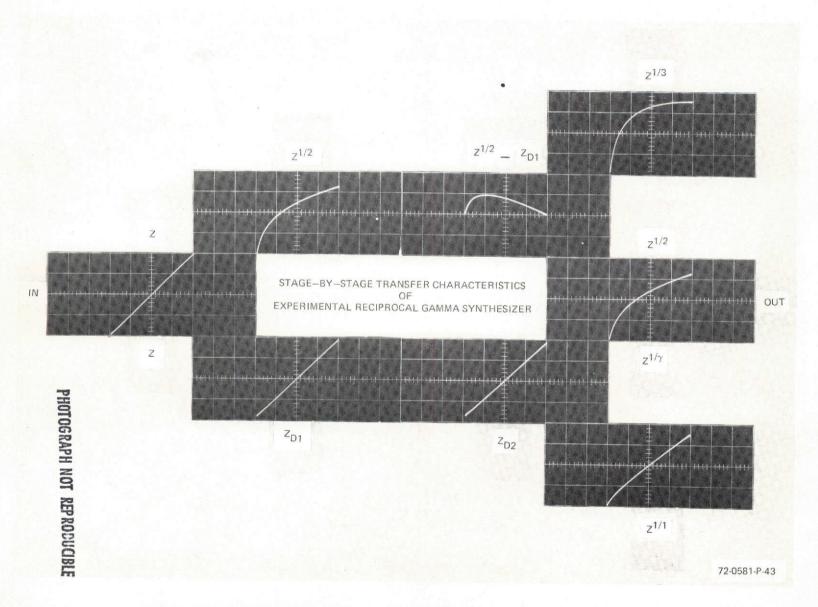

| 5-45         | Stage-by-Stage Transfer Characteristics of Experimental Reciprocal Gamma Synthesizer | 5-85          |

| 6-1          | Montage of Phototransistor Line Arrays                                               | 6-2           |

| 6-2          | Early Model of Linear 80 Element Phototransistor Array with Hybrid Bare Chip Logic   | 6-3           |

| 6-3          | 400 Element Line Array Fabricated in 50 Element Sections                             | 6-5           |

| 6-4          | Hybrid Scanned Imaging                                                               | 6-6           |

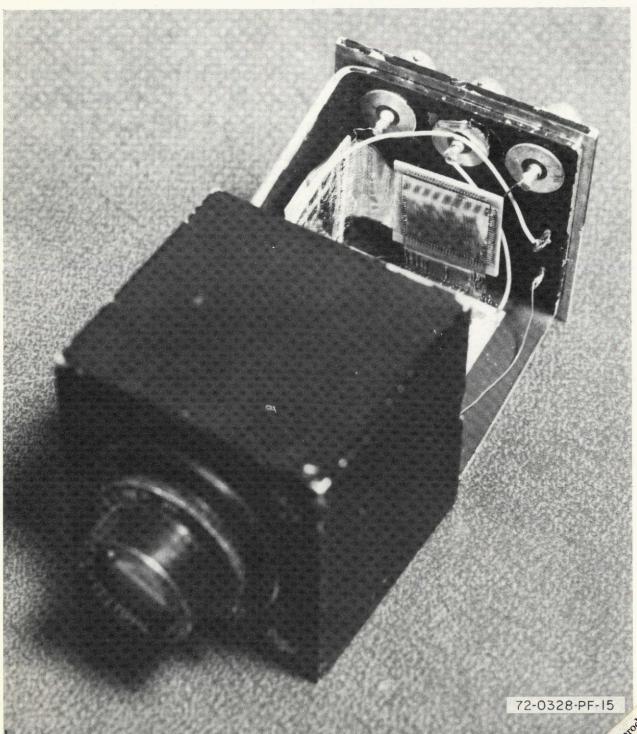

| 6-5          | "Cubic Inch" 50-x-50 Element Camera                                                  | 6-8           |

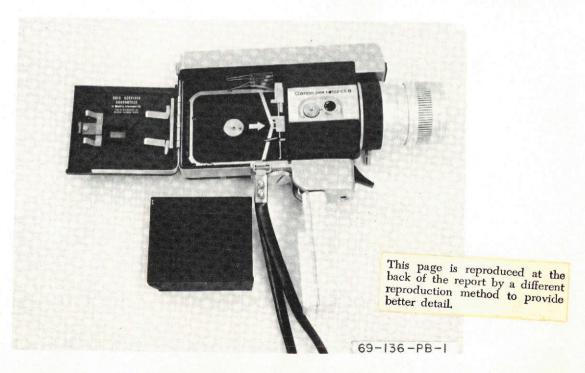

| 6-6          | Super 8 Movie Camera Packaged Integrated Image Converter                             | 6-9           |

| 6-7          | 2.6-by-3 Inch Electronics Substrate in Super 8 Image Converter                       | 6-11          |

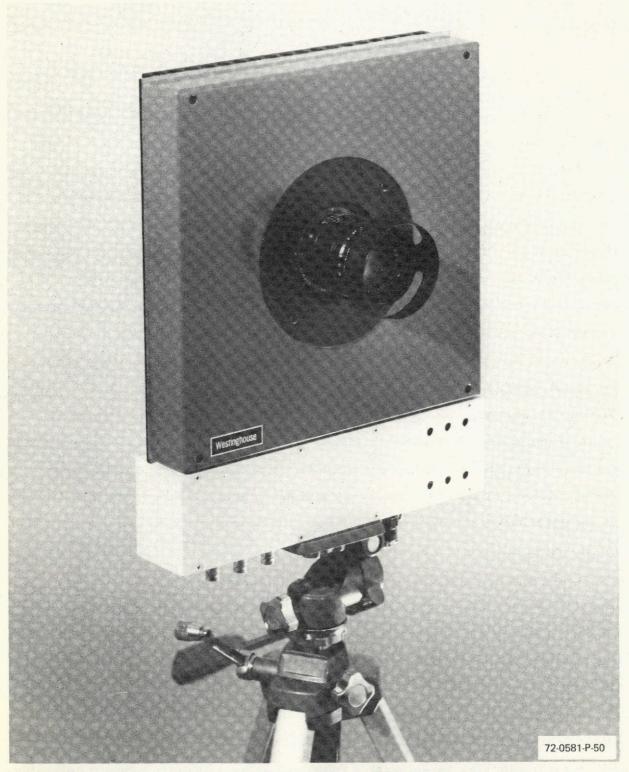

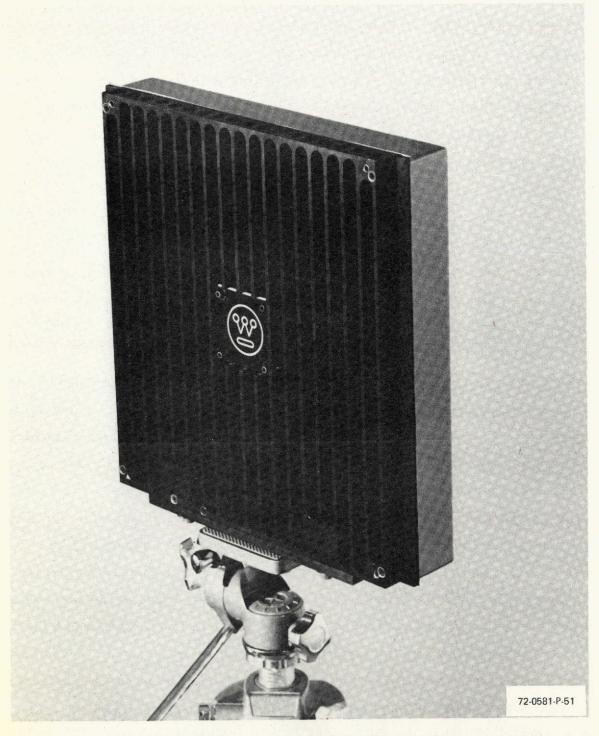

| 7-1          | Engineering Model 400-x-500 Element Integrated Array Camera                          | 7-2           |

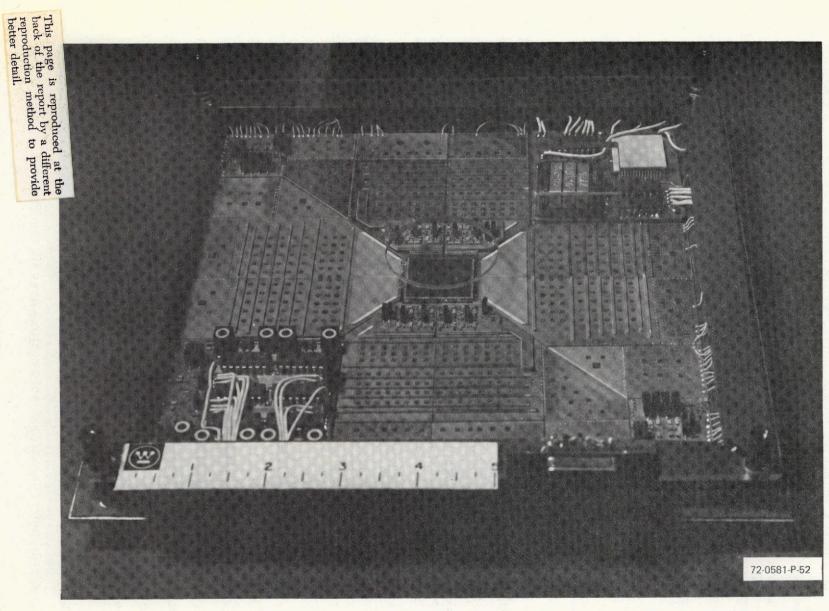

| 7-2          | Backplane View of 400-x-500 Element Camera Mainframe                                 | 7 - 4         |

| 7-3          | Internal View of 400-x-500 Camera Mainframe Showing LSHI Packaging Layout            | 7-6           |

| Figure |                                                                   | Page |

|--------|-------------------------------------------------------------------|------|

| 7-4    | Master Control Electronics PC Board in 400-x-500 Camera           | 7-8  |

| 7-5    | Unique Trapezoidal Shape Substrate Used in 400-x-500<br>Camera    | 7-10 |

| 7-6    | Wiring Channel Interfaced First Level Multiplier (1LM) Substrate  | 7-11 |

| 7-7    | Compound Level Column Interrogation Substrate in 400-x-500 Camera | 7-12 |

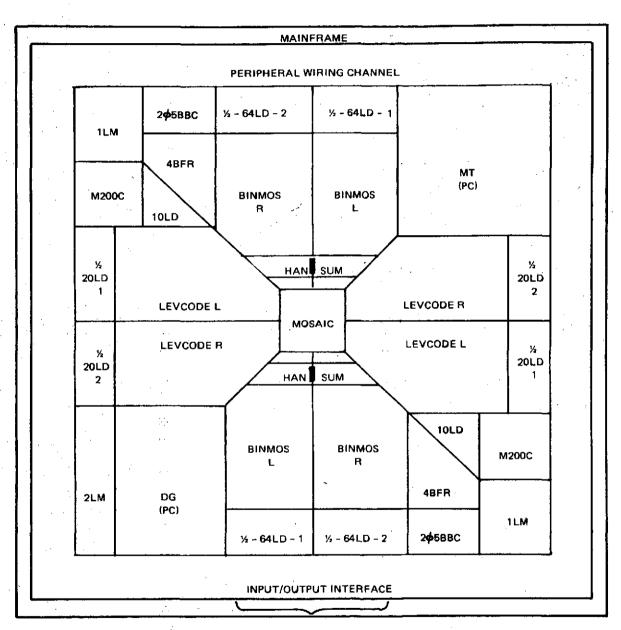

| 7-8    | "45" PICTURE Camera Mainframe Substrate Layout                    | 7-15 |

| 7-9    | Westinghouse EIA TV Format Digital Sync Generator                 | 7-17 |

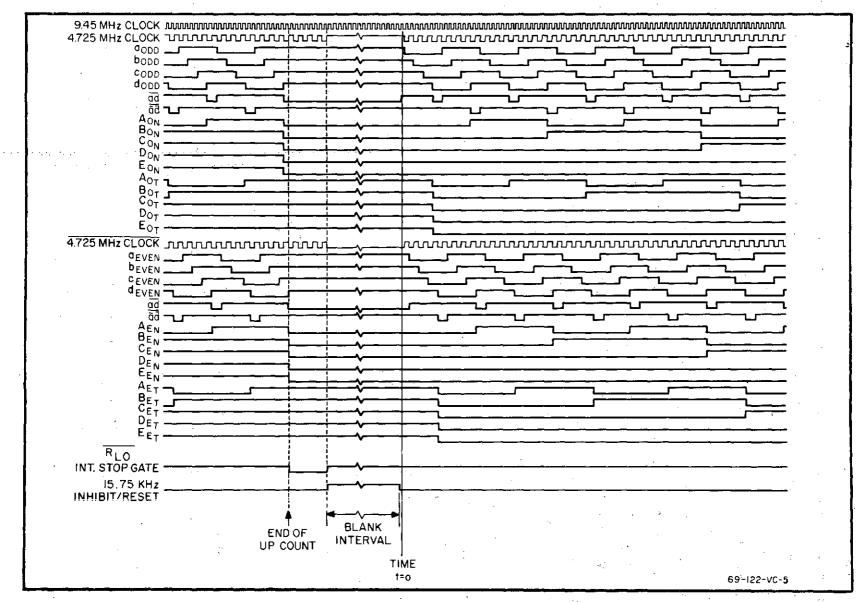

| 7-10   | Column Counter Timing Diagram                                     | 7-21 |

$\sigma_{ij} = \sigma_{ij} = \sigma_{ij} = \sigma_{ij}$

#### 1. INTRODUCTION

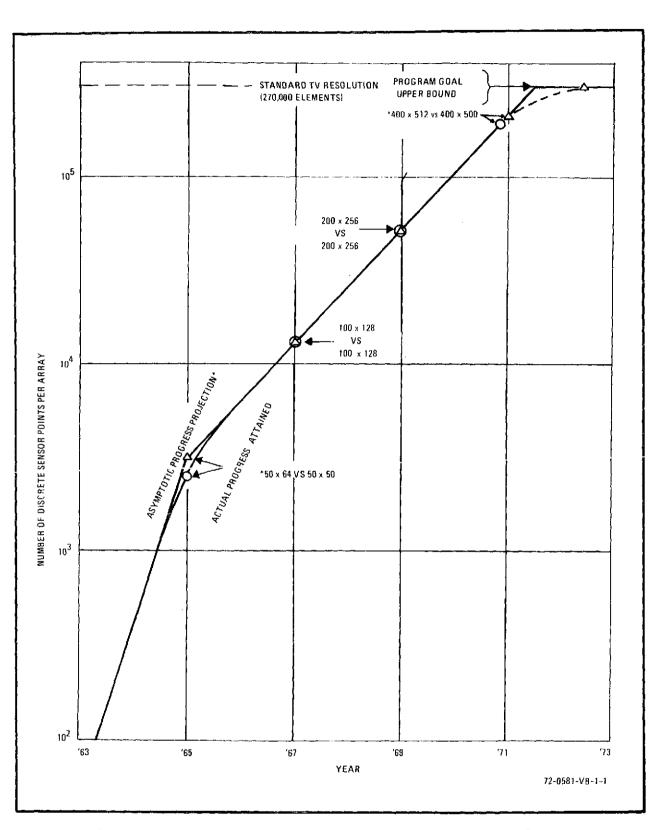

Westinghouse, working under a variety of development programs, has been actively engaged in the field of photon response phenomena since the early 1960's. Through these efforts a number of fully implemented totally solid-state image converter systems have been assembled and the feasibility of a multiplicity of others has been demonstrated. Figure 1-1 presents a time-wise description of the progress made on solid-state array cameras between 1962 and the present under the current contract NAS 8-5112 to NASA's G. C. Marshall Space Flight Center; an effort which has capitalized on and closely paralleled advances in state-of-the-art semiconductor technology and has, as a result, contributed significantly to improvements in the field of solid-state imaging.

While the photosensitive nature of semiconductor materials was long recognized and even discussed in elementary physics courses, the full potential of the phenomenon remained in the hinterland until the advent of the aerospace age. Interest in this area, which has grown rapidly over the last decade, received its initial impetus from the stringent weight, power, and reliability requirements imposed on the special purpose sensors used in spacecraft, satellites, and interplanetary probes. To meet these requirements and produce acceptable all solid-state, electronically scanned (as opposed to electron-beam scanned) imaging systems, investigators have employed a wide variety of approaches to the fabrication of photo-responsive devices. Among the most promising of these have been thin-film sensors, monolithic photo-FET's, and epitaxially diffused phototransistors and photodiodes. The present program has led most recently to production of an advanced engineering model camera which employs a 200,000 element

ì

Figure 1-1. Delivered System Time-Progress Chart for NAS 8-5112 Program

phototransistor array (organized in a matrix of 400 rows-by-500 columns) to secure resolution comparable to commercial television.

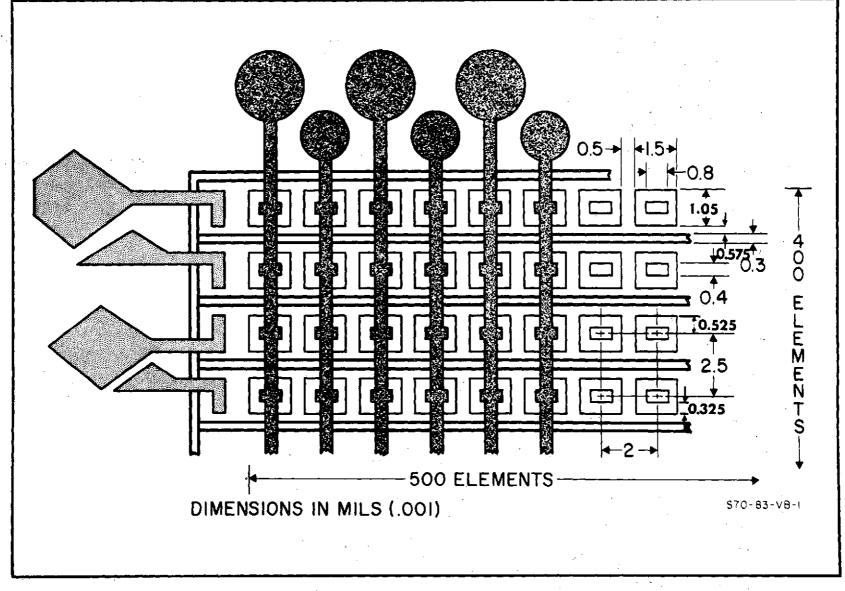

As with former generations of lower density phototransistor matrices, these 400-x-500 element mosaics have a well established X-Y physical architecture. Collector rows are initially formed by an isolation diffusion process such that each collector is separated from all other collectors by back-to-back pn junctions. Into each collector region bases and emitters are then diffused at selected intervals. Electrical connections are affected at the ends of each collector row while successive emitter columns are interconnected by aluminum conductors terminated in bonding pads. The surface dimensions of a high density "45" array consist of 0,002-by-0,0025 inch center-to-center spacings of emitters and collectors, respectively, for a total active detector area of 1 square inch. The 0.0025-inch center-to-center collector row spacing includes the width required for the isolation diffusion used to separate collector strips.

Response of solid-state photosensors to varying wavelengths of radiation is fundamentally a function of the materials used in their construction.

While detectors fabricated from a wide variety of materials are under active investigation, the greatest degree of success thus far has been achieved with silicon devices due to the well established technologies involved. The spectral response of these mosaics is essentially that of intrinsic silicon. Some shift in peak response occurs as a result of the thicker overlaying oxide layers and shallow diffusions that exist with integrated sensor arrays. These factors, particularly the oxide thickness, can be controlled to a limited degree if it is desired to shift the mosaic response.

In addition to the high resolution camera which makes use of a 400-x-500 element phototransistor mosaic, a number of lower resolution solid-state array cameras have also been developed during the course of this program. The first fully electronically scanned image converter system known, for instance, was built in 1965. This camera incorporated a 50X-by-50Y photo-

transistor array and was initially designed to have its sensor elements operate in what is known as the static or dc mode—the only mode recognized up to that time.

Peculiarities noted in the system's scanned video soon led, however, to specification of the dynamic charge-storage or integration mode of operation for pn junction photodetectors. Detailed analyses revealed that the new operating mode constituted a major improvement in readout philosophy, so the 50-x-50 camera electronics was modified to capitalize on this advanced technique.

A portable demonstration camera was next delivered to NASA in 1967. This system has been shown and reported on extensively. It employs a phototransistor mosaic having 100Y-by-128X lines, and which therefore contains more than quadruple the number of individual sensor points that were available in 50-x-50 mosaics.

Improvements in the related technology of photolithography permitted a second quadrupling of the number of distinct photosensitive points per array in the third generation of matrices developed in 1968. These arrays were fabricated with 200 rows and 256 columns of sensor elements and have proven to have quite good performance when placed in a laboratory test vehicle readout system. One of the major provisions made in this particular adaptive electronics setup was the ability to preselect any given region or any single element out of any array under test for more detailed study. Comprehensive investigations carried out with the system subsequently facilitated specification of the systemological refinements that were necessary for successful acquisition and processing of the image video from succeeding generations of higher resolution phototransistor monoliths.

Confirmation of the techniques evolved through these studies was first realized in 1971 with a direct probing wafer evaluation test stand. This unit was designed specifically to pretest 400-x-500 element arrays while they were still in their original postprocessing, unscribed wafer form. Through

this expendiency their respective functional capabilities could be determined and compared without the necessity of completely bonding up each individual mosaic as it is fabricated. The electronics employed in this prober system is identical to that deployed in the fully implemented high resolution camera, except that the latter makes more extensive use of hybrid bare chip packaging.

## 2. SENSOR MONOLITHS

#### 2. 1 DEVICE DESIGN

In general, all current approaches to solid-state imaging utilize arrays of diodes, diode-diodes, diode-transistors, transistors, or hybrid thin film photoconductor-diode or transistor structures.

The advantages of the diode approach lie primarily in the ease of fabrication of diode arrays, the achievable packaging densities, and the relatively good uniformity achievable between elements. Line arrays of over 400 elements have been fabricated in silicon. Since only a single diffusion is necessary to achieve isolation in a line array, there is less processing damage involved with these structures and therefore better performance. Extension of diode sensing arrays to two dimensions requires additional processing to achieve isolation unless a separate lead is attached to each diode for read out, an approach which is impracticle for large size arrays. Provision for isolation reduces the achievable packaging density, introduces a cross talk and parasitic sensor element to the structure, and complicates the processing at the expense of minority carries life time.

If the overall array consists of adjacent line arrays utilizing XY interconnection techniques, two problems arise. First, unless all unaddressed

rows and columns terminate in zero impedance, there are multiple photoconductive cross-talk paths through the various rows and columns which

preclude use of the mosaic for any but single spot imaging applications. With

zero impedance terminations, however, photovoltaic cross-talk problems

arise.

The second disadvantage of a sequentially read diode mosaic, however, is the inability to operate such an array in a light integration mode. As a result, the output signal level is strictly a function of the light incident on the element during the readout time, with a resultant loss of overall light collection efficiency. For a mosaic as small as 100 x 100 elements, only 0.01 percent of the incident photons would contribute to the readout signal. As a result, simple diode arrays were not considered to be candidates for extensive imaging systems, such as those envisioned at the onset of this effort.

The next simplest structure is the diode-diode structure, which provides several advantages over the simple diode array. By way of explanation, this structure consists of one diode array which provides a commutating function and a second array matched on a one-to-one basis which provides the sensing function. Since each light sensor is isolated from the interconnection bus by a back biased diode except during its read period, cross talk is significantly reduced.

In the case in which a back-biased photodiode is used as the light sensor, charge storage light integration can be employed. The phenomenon described in detail elsewhere depends upon the charging of the light sensing diode to approximately the pulsing voltage level during each read cycle. This charge decays between read pulses as a function of the photon induced hole-electron pairs and junction leakage, and the output signal is obtained by monitoring the amount of charge replaced during each read pulse. While the diode-diode structure possesses the light integration phenomenon, the output signal available from the small diodes needed for large-order mosaics is such that direct readout of such a device is difficult. With XY interconnections, a voltage source is applied to the selected column in the other axis, and the charge transfer is monitored. Since all elements are interconnected, the pulse applied to the row is coupled to all of the elements along the row through the parasitic capacitances associated with the overall structure, as well as

through the leakage paths from the various unselected columns to ground. If the parasitic capacitances are large compared to the sensing diode capacitance, application of a readout pulse results in almost completely recharging the sensing element due to the current flow into the parasitic capacitance, effectively reading them out. For large-scale small total area mosaics, typical diode capacitances are on the order of a few picofarads, while the parasitic capacitances are generally orders of magnitude larger.

Conceptually, the diode-diode structure offers another advantage: the commutating diodes can be made using one technology (generally silicon because of the high quality junctions which can be achieved in this material) and the sensing diodes with a material whose characteristics match the particular spectral response desired.

In addition to the internal parasitic discharge problem, an external problem exists with the selection switches used to address the readout point. In most cases, the turn-on transient for the sampling switch will swamp the readout signal. If FET or MOS switches are used, this transient can act either to add charge to the readout bus or to remove charge from the bus, depending upon the polarity of the switching pulse applied to the gate. This problem is not unique to the diode-diode structure, although it is generally more severe with small quantities of charge available in such a mosaic.

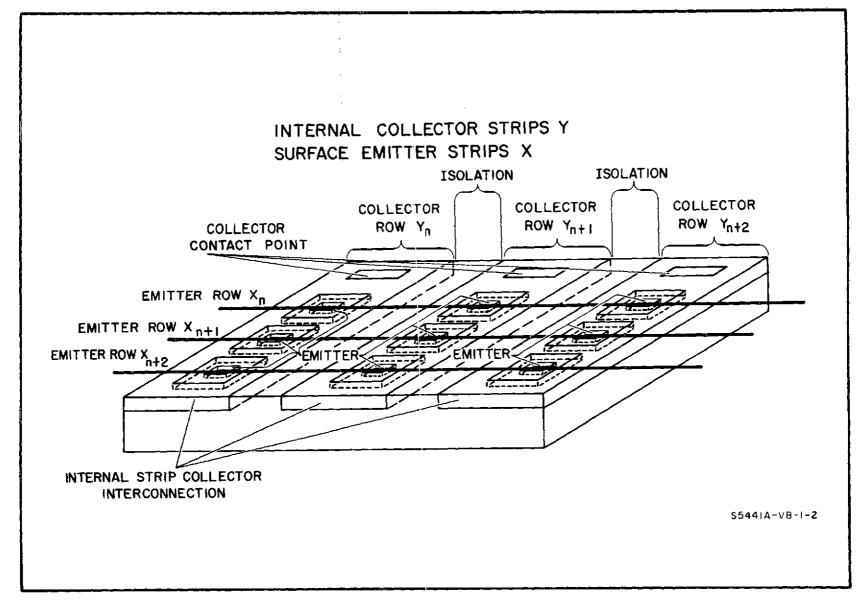

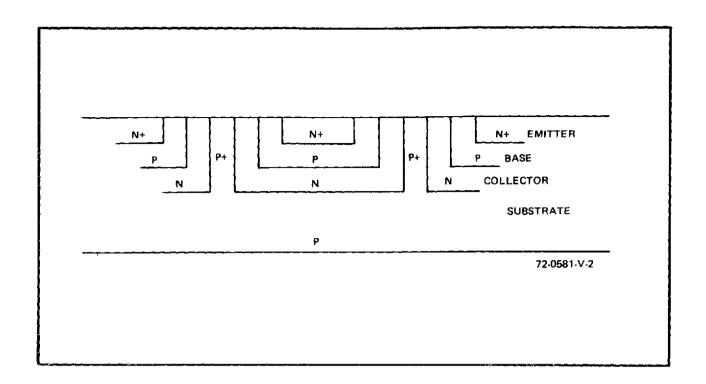

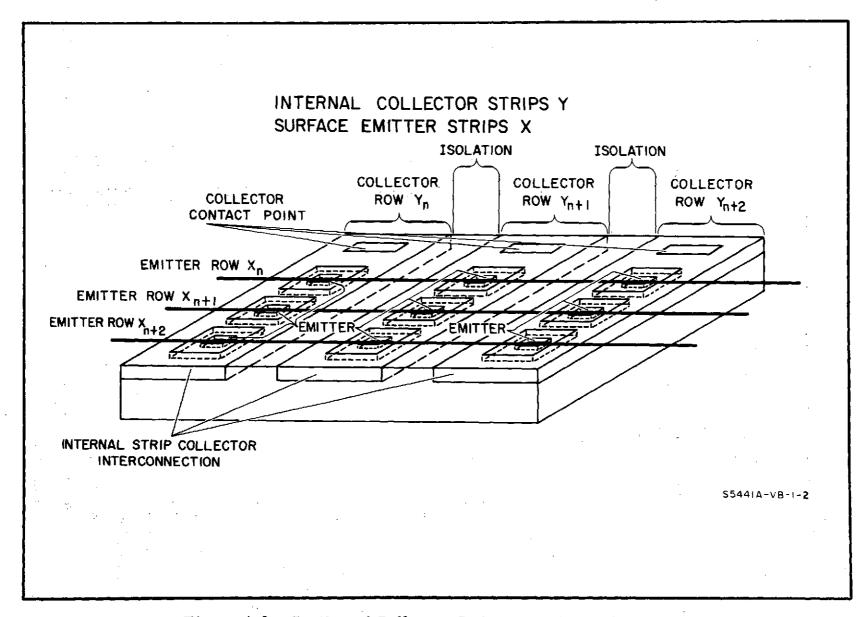

The phototransistor mosaic is a form of diode-diode structure in which the structure is fabricated so as to have transistor action through the junctions. The structure would look essentially identical to a diode-diode structure, and the readout approach is generally similar. The strip collector mosaic is a specific configuration where the rows of transistor elements have a common, low impedance collector strip and the emitters of transistors in a column are connected by a metallized strip. As described, the phototransistor mosaic consists of an array of phototransistors with emitters and collectors, respectively, interconnected in row and column fashion. Figure 2-1 best illustrates the structure of the phototransistor mosaics selected.

Figure 2-1. Structure of the Phototransistor Mosaic Selected

#### 2. 2 BIPOLAR STRUCTURE

The bipolar transistor structure is one of the best examples of the control and use of the pn junction which is produced by oxide-masked diffusion. The transistor structure to be described is illustrated in figure 2-2.

This is a double-diffused epitaxial transistor in the mosaic configuration. The diffused-epitaxial construction results in a four-layer npnp structure. A p+ isolation diffusion results in n type tubs or regions that are electrically separated by the back-to-back pn-junction diodes likewise formed during this diffusion step.

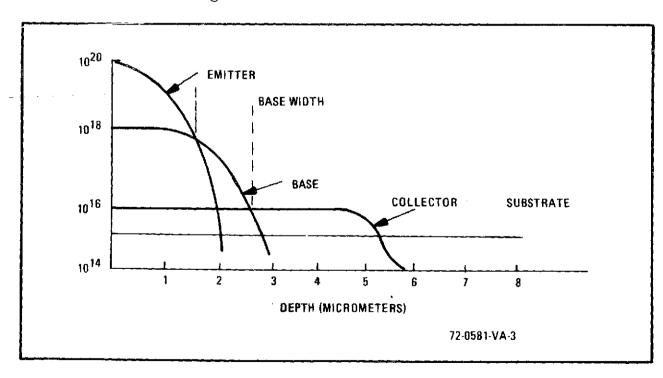

Current-voltage characteristics, gain, capacitance, etc, all depend upon the impurity profiles present in the four layer structure. Essentially, the impurity profile is described by the cross-sectional profile of the active device region. The typical starting substrate material is p-type silicon of about 10-ohm-cm resistivity. This corresponds to an acceptor impurity density of about 10<sup>15</sup> atoms/cm<sup>3</sup>. By a process of epitaxial deposition a layer of n type silicon is grown on the p type substrate to a thickness of 5 micrometers. When suitably isolated by a p+-type diffusion this layer becomes a series of long tubs electrically isolated from each other by back-to-back pn junction diodes. The isolation diffusion is accomplished by the planar process and is of sufficient depth to completely penetrate the n-type layer. Two additional planar diffusion steps are used to complete the npnp structure illustrated. A typical diffused impurity profile is illustrated in figure 2-3 where the impurity atom concentration is shown on a log scale as a function of linear penetration into the semiconductor surface. The epitaxial substrate junction is almost abrupt except for some concentration grading due to diffusion effects. This junction provides parasitic, voltage-dependent capacative coupling to the substrate which varies approximately as  $V^{-1/2}$ . The capacitive contribution due to sidewall regions formed by the isolation diffusion varies more nearly as  $V^{-1/3}$  and is in parallel with the coupling capacitance. Typically the sidewall capacitance is about 0.1 pF/mil<sup>2</sup> for the abrupt junction component and 0.2 pF/mil<sup>2</sup> for the graded sidewall junction component. 2-5

Figure 2-2. Transistor Structure

Figure 2-3. Impurity Profile

The isolated epitaxial n-region forms the collector regions of the mosaic. This region has uniform impurity doping, as shown in figure 2-3 with a typical donor concentration of  $10^{16}$  atoms/cm<sup>3</sup>. A p-type region is diffused into this n-type region to form the base of the transistors; the boundary between the p- and n-type regions is the collector junction. Since this is now a graded junction, the associated transistion capacity varies as  $V^{-1/3}$  and is strongly dependent on the impurity concentration of the n-type region; a higher impurity concentration results in a lower capacity per unit area.

In designing the collector region the resistivity and thickness values that will eliminate collector current saturation must be selected. A particularly effective technique is to introduce a buried layer. This is a layer of high conductivity n-type silicon which is selectively placed between the n-collector and p-substrate. This buried layer functions as a shunting path for the collector current and lowers collector series resistance.

The resistivity and thickness of the collector region also determines collector breakdown. From a knowledge of the breakdown field in silicon and from depletion layer thickness calculations, a choice of resistivity and thickness may be made. The n-type emitter diffusion determines the base width value. The emitter is a high-conductivity n+ layer. Emitter injection efficiency depends strongly on the concentration ratio of impurity atoms in the emitter to impurity atoms in the base. In addition, for the diffused emitter the concentration gradient near the emitter junction has an important effect on injection efficiency, so that the emitter junction depth should be considered, particularly for operation at low levels.

#### 2. 3 MOSAIC DESIGN

The selection of a phototransistor mosaic as the sensor for the solid-state camera required that a technique be devised whereby the concept could be utilized. The concept and the technique devised is illustrated in figure 2-1. Each of the internal strip collectors is isolated from its neighbor by the junction formed between them. The collectors are n-type and the substrate

p-type. Individual bases are selectively diffused into these collector tubs and emitters in turn diffused into the bases. The emitters are then interconnected into separate rows by means of a surface aluminum strip.

Connection to the collectors is made at the collector ends as shown. Not shown in this illustration is the low resistance n-type region provided as a subdiffusion beneath each collector row.

The isolation width to a great extent controls the size of the mosaic. That is, it functions to limit packing density. To provide the isolation, boron is diffused through an oxide window completely through the epitaxial layer. The minimum window opening is a compromise function between optical resolution available over an inch line and yield. A broken isolation line, broken because of a photographic plate fault, dirt particle, mask pin hole, etc, will result in paralleling two collectors, effectively doubling the apparent capacity of those elements and in general degrade the response of two rows. A widening of the isolation line, caused by many of the above sited defects, can cause a base to substrate short or a bad element.

The usable line width has decrease by almost an order of magnitude during the course of this endeavor, from a usable width of 0.003 inch to 0.003 inch wide as used in the 400-x500 element design.

Other factors associated with the isolation diffusion limit mosaic size. This boron diffusion must penetrate the epitaxial layer completely; however, for each unit downward the diffusion also spreads laterally nearly two units (one on each side of center). Thus, if the epitaxial layer is 15 micrometers deep, then through a 75 micrometer window the diffusion width would be about 100 micrometers or greater than 0.004 inch wide. Early epitaxial layers had to be about this thick to provide good surfaces and uniformity. At present it is possible to grow epitaxial layers of 5 micrometers thickness of good uniformity of both thickness and resistivity. Thus the progress made in optical resolution has been augmented by epitaxial control and quality to lower the isolation space requirements to those shown in figure 2-4.

Figure 2-4. 400-x-500 Element Mosaic Dimensions

The photosensitive junction of principal interest in the phototransistor element is the base collector junction, both its periphery and bottom. Due to the thin diffusion utilized it is possible for this buried segment to absorb effectively the shorter wavelength photons. Under these conditions it is essential that the base be made as large as possible while the emitter is made as small as possible. The width of the base is restricted by the following: (1) the side wall of the isolation diffusion, (2) the extent of the depletion region, and (3) misalignment tolerances. As outlined above the base must not be allowed to short, either directly or via a depletion layer or channel, to the isolation diffusion. Furthermore, it is impossible to expect that the base window mask willbe aligned perfectly to the isolation pattern. Present state of the art allows a plus or minus 0.0001 inch maximum misalignment which may arise from physical misplacement of the mask to slight size descrepancies in the masks themselves. The dimensions selected and shown in figure 2-4 reflect these considerations and are compromises between absolute tolerances and yield and performance.

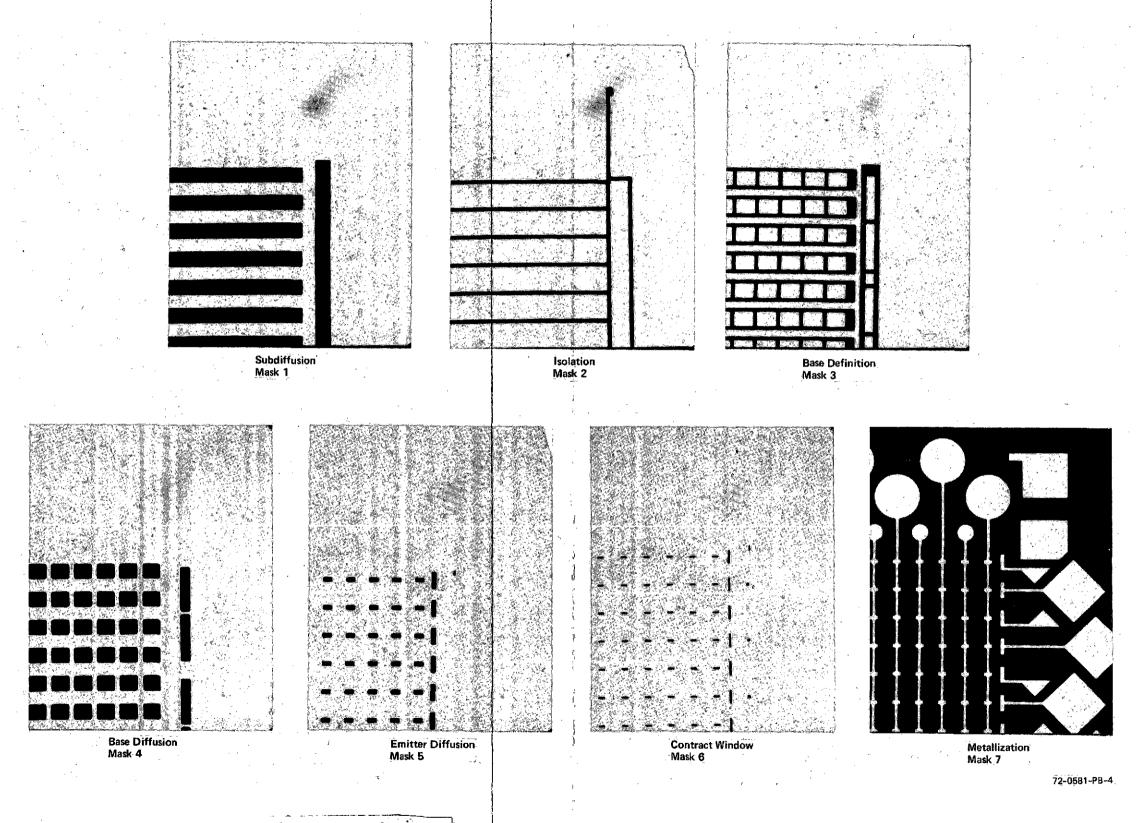

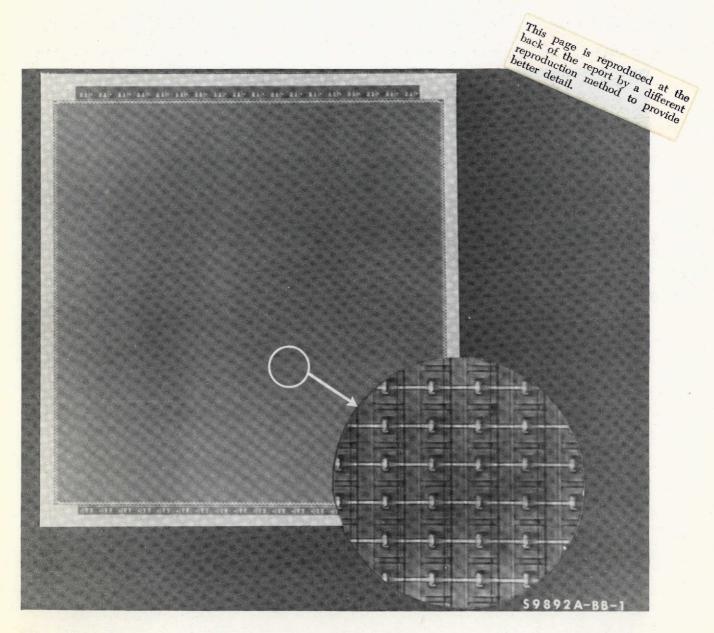

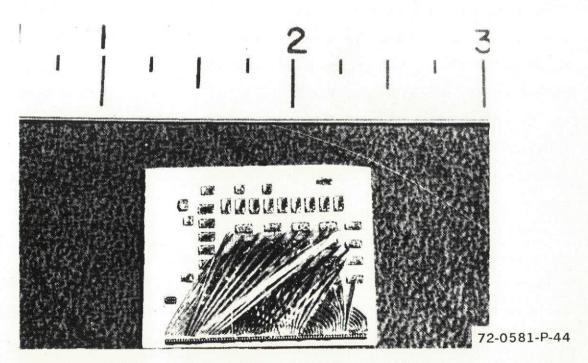

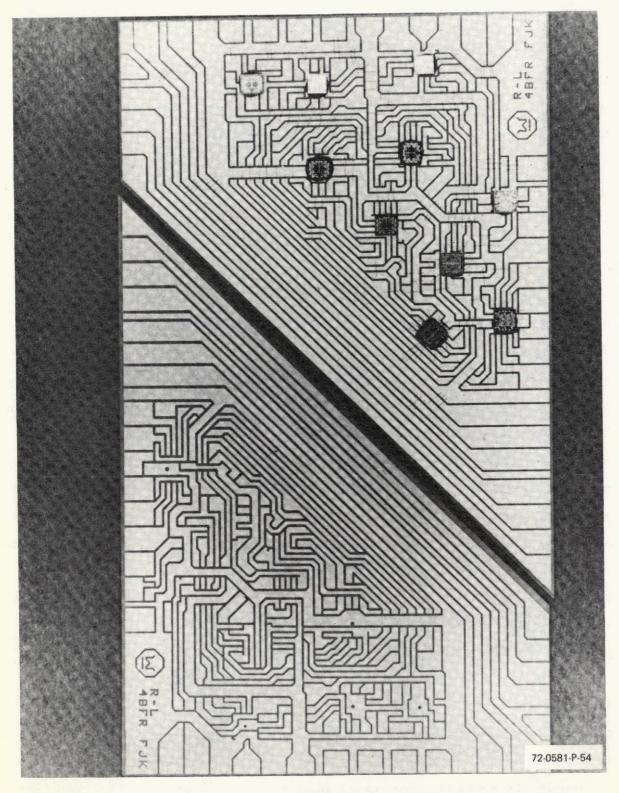

Figure 2-5 shows photomicrographs of a corner of each of the photomasks used to delineate the requisite areas of the mosaic. The following section will describe the processes and the specific application to the  $400 \times 500$  element array.

This page is reproduced at the back of the report by a different reproduction method to provide better detail.

Figure 2-5. Photomicrographs of Corner of Each Photomask

B

2-11,

## 3. FABRICATION TECHNOLOGY

#### 3.1 MATERIAL PREPARATION

The objective of material preparation is to produce a suitable surface on the silicon wafer for mosaic fabrication. The ideal surface for planar device fabrication generally is one that is flat, defect free, and uniform. These physical characteristics as well as the electrical parameters of the material must be compatible with all subsequent processing steps.

The physical specifications imposed by epitaxial growth require that the wafer surface be essentially free of defects and work damage. The surface is first prepared by mechanical lapping and polishing. Then the residual work damage is removed by chemical polishing and a short vapor etch (high temperature HCl etch).

The planar device fabrication process demands that the surface topology be flat so that junction depths move uniformly and predictably into the crystaline structure. To achieve proper electrical characteristics, an undisturbed crystal structure is necessary; therefore, such surface defects as scratches, microcracks, or insufficient removal of lapping damage must be prevented.

Defects such as pits, spikes or orange peel which often appear after subsequent processing, may have their cause or origin established during the material preparation steps. Therefore, great care must be taken to avoid contamination of the silicon, the equipment, or the materials used in the wafer preparation process.

Various methods have been used to provide damage free silicon wafers for mosaic fabrication. Among these are chemical polishing, mechanical-chemical polishing, and electro-chemical polishing. The chemical approach offers the greatest ease in obtaining defect free, uncontaminated wafers.

However, it is necessary to have a good mechanically polished surface to obtain a flat surface free of orange peal defects. Mechanical-chemical polishing provides a wafer that is usually sufficiently prepared for epitaxial growth. Electrochemical polishing combines an electrical potential, an etchant, and light to produce very useful surfaces; however, the cost is comparatively high.

The crystals used for mosaic processing are grown by the Czachralski method. These ingots, of suitable diameter, are sliced into wafer form utilizing diamond impregnated saws. The surface of the wafer at this point has considerable damage in the form of furrows and microcracks which extend some distance into the material. This damage is removed by planatary lapping, a process which also planarizes the major surfaces and reduces the wafer to a predetermined thickness. While the lapping removes the gross saw damage it in turn introduces damage due to the abrasive grit action to a depth of about 15 micrometers. After a very thorough cleaning to remove all traces of abrasive the finished wafers are given an optical polish. During this operation the 15 micrometer damage is removed but the 1 micrometer abrasive introduces its damage. The depth of penetration though is only a few micrometers. This damage is in turn removed by a slow chemical polish carried out in a rotary etcher. This etching introduces no further damage and does remove that introduced during the polishing operation.

The wafers must be inspected for surface flaws. Acceptable wafers have a specular surface which cannot be seen by direct microscopic examination. Dark-field illumination must be used to detect the minute long, thin scratches which may result from contaminated abrasive. The wafers, after inspection, are cleaned by vapour degreasing in trichlorethylene, boiling sulfuric acid, and deionized water. The dried wafers are then ready for further processing.

#### 3.2 EPILAXIAL GROWTH

There are a number of conditions that should be satisfied for the successful growth of thin expitaxial films on a substrate. These are:

- a. The deposited molecules must have a controlled degree of mobility on the substrate surface.

- b. Isotropic forces must be present at the surface to promote a specific layer orientation.

- c. The interface between substrate and film must not become delocalized by chemical reactions, alloying, impurity deposition, or impurity diffusion from the substrate.

- d. The layer must wet the substrate surface.

- e. The substrate must be free of mechanical defects which may serve as nucleation sites for a different crystal order then that obtained by the chemically active sites on the substrate surface.

For the condensation of a nonatomic gas, surface mobility can be controlled by the thermal energy of the substrate. Surface temperature fluctuations may promote surface reactions or even chemical reactions that can destroy the layer structure. These effects can be minimized by lower substrate temperatures, but a decrease in temperature requires a slower deposition rate to obtain a good epitaxial orientation. The lower temperature also enhances the spurious nucliation of diatomic or polymeric forms, either of which may tend to reduce or inhibit surface mobility. This leads to a nonoriented dispersion of growths on the substrate.

To obtain quality simiconductor epitaxial layers, silicon epitaxial systems must be controlled to close tolerances for certain parameters. A suitable silicon compound is introduced into a reaction chamber where the proper temperature, thermal gradient, carrier gas and impurity gas flows, and concentrations are capable of being closely controlled. With the proper control of these parameters, there is a thermal descomposition of the silicon bearing compound at the surface of the heated substrate which results in a

single crystaline form of epitaxial layer silicon being deposited on the heated substrate. By simultaneously controlling the type and concentration of impurities introduced in the gas train during the deposition, both the doping level and the conductivity type of the deposited layer may be closely regulated. The doping level of epitaxial layers grown in this manner is generally homogeneous, unlike the impurity concentration profile resulting from the diffusion process.

Epitaxial growth for some of the more common silicon bearing compounds occurs according to the following overall reaction:

$$SiH_4 + H_2 \rightarrow Si + 3H_2$$

For reasons of apparatus and control simplicity gaseous impurities such as phosphine, arsine, and diborane are used. A typical silicon epitaxial run proceeds as follows:

#### Step

- 1. Wafer cleaning by organic solvent, hot acid, and hot water.

- 2. Introduce wafers and carrier into reactor.

- 3. Purge with N2

- 4. Purge with H2

- 5. Heat up and soak.

- 6. High temperature HCl etch.

- 7. High temperature purge

- Actual disposition compound flow through reactor.

#### Reason

To remove residual polishing contamination and heavy metals.

To remove all oxygen from the reactor.

To replace all N<sub>2</sub> with H<sub>2</sub> and ready the system for high temperature operation.

To allow system to approach thermal equalibrium.

To produce a completely clean defect free surface.

To clear spent reagents from reactor.

To deposit layer thickness with proper levels type of dopant.

8a. Introduction of controlled dopant flow.

9. High temperature purge

To clear spent reagents from reactor tube.

10. Cool in H2

11. Purge H<sub>2</sub> with N<sub>2</sub>

To remove H<sub>2</sub> before spinning as a safety precaution.

After inspection which consists of surface examination and test to determine layer thickness, type, and conductivity, the wafers are then sent to the next operation, oxidation.

#### 3.3 OXIDATION

The term "thermal oxides" refers to those oxides formed from a thermally activated reaction of silicon with oxygen, water, or other oxygen bearing species. The techniques currently in use involve reactions with oxygen and steam.

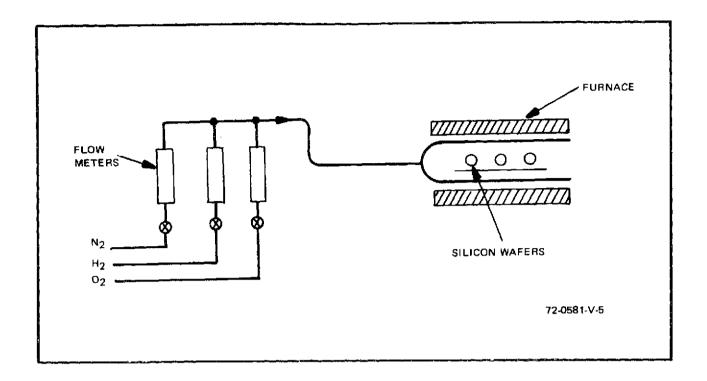

Thermal oxidation involves the heating of silicon substrates to temperatures in excess of 900°C in atmospheres of dry oxygen or steam. This is accomplished in an open tube at atmospheric pressure as illustrated in figure 3-1.

The oxidation of silicon by dry oxygen, steam, or combinations of these is themodynamically possible at room temperature; however, the reaction rate is so slow that it makes this method impractical. For temperatures less than 900°C at atmospheric pressure, the reaction rate is still quite slow. Practical thermal oxidation techniques therefore use higher temperatures, typically in the range of from 1000 to 1200°C, so that the time required to achieve oxide thicknesses suitable for masking purposes is on the order of 20 to 90 minutes. These processes are primarily controlled by the exposure of oxygen or water molcules to the silicon-oxide interface. The reaction rate is described by the parabolic law

$$x^2 = kt$$

Figure 3-1. Open Tube Thermal Oxidation Apparatus where x is the oxide weight or thickness, t is the time, and k is the rate constant. The rate constant varies as a function of the material resistivity or impurity doping and also as a function of crystal orientation.

The parabolic law holds true for temperatures above 1100°C. Below 1100°C the relationship between x and t is found by experiment to depart from the above relationship and become more linear. Specifically, for temperatures below 1000°C an expression of the type

$$x^2 + k_1 x = k_2 t$$

concurs more closely with observations. The lower the temperature, the more linear the relationship becomes, which indicates that  $k_1$  and  $k_2$  are temperature dependant.

There are many methods that can be used to determine the thickness of oxide films. Optical interference techniques are the most commonly used and the most accurate. However, some optical methods are destructive to

an extent. Techniques developed by Tolansky for measuring Fizeau fringes have been used to measure the thickness of oxide film on silicon. In general, the oxide thickness can be determined by the color appearance of the wafer when viewed under controlled conditions. These colors are shown in table 3-1.

TABLE 3-1

SILICON OXIDE THICKNESS AND INTERFERENCE

COLOR RELATIONSHIPS

| Thisknoon | (Micrometers) |

|-----------|---------------|

| Inickness | (Micrometers) |

| Color  | 1     | 22   | 3    | 4    |

|--------|-------|------|------|------|

| Grey   | 0.01  |      |      |      |

| Tan    | 0.03  |      |      |      |

| Brown  | 0. 05 |      |      |      |

| Blue   | 0.08  |      |      | •    |

| Violet | 0.10  | 0.28 | 0.46 | 0.65 |

| Blue   | 0.15  | 0.30 | 0.49 | 0.68 |

| Green  | 0.18  | 0,33 | 0.52 | 0.72 |

| Yellow | 0.21  | 0.37 | 0.56 | 0.75 |

| Orange | 0.22  | 0,40 | 0.60 |      |

| Red    | 0.25  | 0.44 | 0.62 |      |

These relationships are such that the color serves adequately for an inprocess oxide thickness test.

The impurity masking ability of an oxide is dependent upon a number of factors. The most important factor is the value of the diffusion coefficient of the diffusing impurity in silicon. Two other factors are the type of oxide used for masking and the particular method of diffusion. All of the common donor impurities have small diffusion coefficients; hence they may be readily used; however, of the common p-type diffusants, only boron has the requisite low value. The minimum oxide thickness necessary to completely mask the diffusion of an impurity using this process has been determined experiment-

ally and found to be about 7000°A, a thickness readily obtained in a reasonable amount of time and at a reasonable temperature.

## 3.4 DIFFUSION

The diffusion process consists of two phases: (1) a deposition, and (2) a drive-in phase. During the deposition phase, the impurity is deposited upon the surface of the silicon wafer; a short diffusion into the surface takes place. The deposition resistivity or impurity atom concentration is generally controlled by holding the temperature constant and varying the time of deposition.

Following the inital deposition phase, the wafers are removed from the deposition furnance and placed in a drive-in furnance. The redistribution of impurities takes place in the drive-in furnance, resulting in changes in the sheet resistivity, impurity gradient, and junction depth. The heating of the wafer is performed in an impurity free atmosphere so that the only diffusion occurring is a redistribution of those impurities originally introduced during the deposition phase. The impurity redistribution may be modified by introducing controlled amounts of oxygen into the drive-in furnance, thus modifying the sheet resistivity. Also, during this drive-in procedure, the oxide required to protect the junction is grown.

The two-step process of diffusion, though more complex then a single, is preferred because:

- a. Improved control and reproducibility of the diffusion is achieved. By separating the process into two steps the diffusion can be monitored more closely, and compensations can be made in the second step for errors in the first.

- b. The oxides used for masking are more effective. Usually, the initial deposition step is done at a lower temperature than the redistribution step. The impurity doped glasses formed over the entire SiO<sub>2</sub> masked silicon are then removed by an HF etch, having only doped areas at those places in the silicon where diffusion is required. The lower temperature deposition

step therefore makes oxide masks more effective against the diffusion of impurities since oxide masks that would fail in a single step diffusion are satisfactory in a two-step process.

- c. The use of a two-step process results in a Gaussian distribution of the diffusing impurity. For some applications, the Gaussian distribution is more desirable than the complimentary error function distribution that results from a one-step process.

- d. A two-step diffusion process is more flexible and makes more effective use of the diffusion facilities available.

#### 3.5 PHOTOENGRAVING

An oxide growth on a silicon wafer serves as an effective mask to prevent the diffusion of impurities. This mask material is grown uniformly on the wafer and thus does not afford a method of selectively diffusing an impurity into the silicon to form the various elements of the phototransistor matrix. Therefore, a photomask must be generated and the oxide selectively removed.

The photographic pattern is initiated with an engineering sketch drawn at about a 500 X scale. Each rectangular shape is reduced to its x and y origin and its  $\Delta x$  and  $\Delta y$  components. This format is required by the computer aided design system currently in use. These data cards along with instructions for matrixing the mosaic pattern are, with the appropriate program cards, introduced into the computer. The output is in the form of a line drawing of each level plus a composite of all levels.

If detailed examination of these plots reveals no errors, a magnetic tape is prepared by converting the data cards previously used to data points required for the pattern generator. This machine produces master reticles of the component parts of the mosaic at a scale of 10:1. These reticles are then composed in a step and repeat camera into the final photomask master plates. Submasters and working plates are made from these.

The high resolution obtained in exposing the plate can be lost if the developing procedure is improper. After exposure the plate is placed in reagent of methyl alcohol for 30 to 45 seconds. This treatment not only preconditions the emulsion surface for the developers, but it also helps remove the pink stain (sensitizer stain) sometimes seen in the developed plate. The antihalation backing is also removed by this treatment. Eastman Kodak D-8 is used full strength at 65°C. This alteration is the usual developing technique used to provide a denser image than can otherwise be obtained. The emulsion takes 2 minutes to properly develop, and continued agitation of all baths gives the best results. The developed plate is then placed in a 4 percent acetic acid solution for 15 seconds to neutralize the developer. Afterwards the plate is fixed and hardened in the conventional manner.

A modified form of Kodak Metal Etch Resist has been found to be the most suitable resist for this use. The resist is mixed, one part KMER to one part KMER thinner, and placed in capped tubes for centrifuging at 2000 g's for 16 hours. To increase the viscosity of the resist, the caps are removed and centrifugation is continued for 4 hours. The cleaned resist is then separated from the sludge by decanting, and the visocity adjusted.

The resist is now ready to be used in the photoengraving process. Ten cubic centimeter syringes make satisfactory dispensing units. A filtering unit containing a 0.8-micrometer filter is attached to the end of the syringe and a no. 17 hypodermic needle is attached to that.

When an oxidized silicon wafer is taken from the oxidation or diffusion furnances, it is inspected for defects. The wafer is then sprayed with trichloroethylene to remove any dirt or dust that may have settled on the wafer. It is important that no mechanical contact be made with the oxide surface since this could cause severe undercuting when the wafer is etched. The wafer is then stored in a clean furnace at 200°C for a minimum of 30 minutes. Storage of up to 2 days does not affect the wafer, but prolonged storage sometimes causes a change in etch factor.

The resist is dispensed from the hypodermic syringe through the filter and onto the wafer which has been placed on a spinner. The wafer is spun at 6000 rpm for 20 seconds. A slight downdraft of air around the spinner head will remove any strings of resist that form while the resist is being spun from the wafer.

Several factors affect the resist thickness: spin speed; the acceleration of the spinner head to full speed; resist viscosity; and, to a lesser extent, humidity. These parameters must be taken into account or increased resist thickness will result causing either poor resolution or an excessive number of pinholes.

The wafer is placed on a cold Teflon boat and put into an oven at 110 to 120 °C for 12 minutes. A teflon boat is preferred to prevent the wafer from sticking to the boat if the resist flows to the underside of the wafer. If a Teflon boat is not used, the oven temperature must be lowered to about 95 °C to adjust for the heat sink properties of the Teflon. After bakeout, the wafers should be stored in a clean area to prevent dust from settling which later could cause pinholes in the resist by blocking exposure light. To minimize undercutting the wafers should be processed through developing the same day they are coated.

The wafer is placed on a mechanism that alignes it with the photographic mask. Light fringes must be seen at two points or good mechanical contact is not made and poor resolution results. Before the resist is applied, the wafer flatness must be within 20 light fringes, as measured with an optical flat, or resolution will not be uniform across the wafer. It is necessary that a radium of 0.005 inch be present at the edge of the wafer since a buildup of resist at the periphery of the wafer would prevent intimate contact. To assure intimate contact a light mechanical pressure is applied to the wafer.

A Sun Gun is placed 1 foot from the wafer and turned on for 30 seconds to expose the resist. The pattern is developed by placing the wafer on a vacuum chuck in the vertical plane and spraying it with KMER developer for

30 seconds. Immediately after developing, the wafer is spray rinsed in a solution of 80 percent isopropyl alcohol and 20 percent KMER thinner for 15 seconds and blown dry. A stronger developing system will give sharper, cleaner lines; but some care must be exercised to keep from blowing narrow lines in the pattern from the wafer.

The image may now be inspected since the developing solvents have disolved the unexposed resist leaving the exposed resist pattern on the wafer. The inspection should include a check for proper alignment, cleanliness of the smallest openings, and completeness of the resist pattern.

The wafers are placed on a 1/2 inch thick Teflon block and placed in a postbake oven at 180°C for 20 minutes to drive off the developing solvents. Extended bakeout causes the resist to flow and close very narrow openings. A shorter bakeout may degrade adhesion.

The etching solution for oxide etching is:

Ten parts of solution A are added to one part of solution B. The etch rate of this solution is 750 Å per minute for a neutral thermal oxide. Of course, this etch rate is related to temperature. Measurements for a cooled etchant show that there is no improvement in the etch factor over that found for it at room temperature.

The time required to completely remove the oxide from the open areas on the wafer is obtained by dividing the oxide thickness by the etch rate. One minute is added to the calculated value to allow for possible variations in the oxide thickness. If the wafer is removed from the etchant before the oxide has been completely removed, some difficulty in etching and undercutting will result. This is apparently caused by leaching action of the resist.

A suitable etchant for aluminum is:

phosphoric acid 25 parts

nitric acid 1 part

acetic acid 5 parts

The bath is heated to 75-80°C. The wafer is supported and lowered into the bath. Etching is very rapid and the wafer must be withdrawn as soon as the aluminum disappears from the etched areas. The etch rate is about 15,000 Å per minute.

The removal of the resist from oxide coated wafers is accomplished by immsing the wafers in hot (150°C) sulfuric acid for 5 minutes and then rinsing in deionized water. This method is used for complete removal of resist between diffusions. However, in the case of aluminum coated wafers the acid would also remove the aluminum; therefore, a commercial resist stripper such as J-100 is used. This is heated to 85 to 90°C and the wafers immersed for 5 minutes. The wafer is then spray rinsed to remove the stripper and any residual resist.

#### 3.6 MOSAIC PROCESSING

The conversion of these processing techniques to an operational mosaic is carried out by submitting wafers to a step-by-step process. Each group of wafers carries written instructions as to how each step is to be accomplished. Mechanical-chemically polished wafers are prepared in bulk and stored until needed. After assembling the required number of wafers, the processing proceeds as follows:

| Step               | Purpose                                                  |

|--------------------|----------------------------------------------------------|

| 1. Chemical Polish | To removed the last traces of surface damage and clean.  |

| 2. Oxidation       | Grow thermal oxide 5000A deep.                           |

| 3. Photoengraving  | Open windows through which the subdiffusion can be made. |

|     | Step                 | Purpose                                                                                                                  |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------|

| 4.  | Arsenic Diffusion    | Diffuse arsenic 20-30 fringes deep 80-100 ohms/sq. to reduce collector strip resistance and prevent collector pinch off. |

| 5.  | Epitaxy              | Grow a 5 micrometer 0.5 ohm-<br>cm arsenic doped layer (all<br>oxide remove prior to epi growth)                         |

| 6.  | Oxidation            | Grow a thermal oxide 7000A deep.                                                                                         |

| 7.  | Photoengraving       | Open windows for the isolation diffusion.                                                                                |

| 8.  | Boron diffusion      | Diffuse boron to a depth of 19-20 fringes 5 to 10 ohms/sq to isolate each collector row.                                 |

| 9.  | Photoeng raving      | Open windows for the base di-<br>ffusion.                                                                                |

| 10. | Boron diffusion      | Diffuse boron to depth of 8 fringes 300 ohm/sq to form the base regions.                                                 |

| 11. | Photoengraving       | Open windows for the emitter diffusion.                                                                                  |

| 12. | Phosphorus Diffusion | Diffuse phosphorus 6 fringes deep 5 to 10 ohms/sq to form the emitter.                                                   |

| 13. | Silox Passivation    | Provide phophorus doped oxide as a passivation glass over the mosaic.                                                    |

| 14. | Photoengraving       | Open windows where contact will be made to the silicon.                                                                  |

| 15. | Phosphorus Diffusion | Diffuse phophorus very shallowly 5 to 11 ohm/sq to reduce contact resistance.                                            |

| 16. | Silox Passivation    | Provide phosphorus doped oxide as a passivation glass.                                                                   |

| 17. | Photoengraving       | Open windows where metal must contact the mosaic.                                                                        |

|     | Step                 | Purpose                                                             |

|-----|----------------------|---------------------------------------------------------------------|

| 18. | Aluminum Evaporation | Provide a 10,000Å film of aluminum over the mosaic.                 |

| 19. | Photoengraving       | Etch the aluminum into the required pattern.                        |

| 20. | Sinter               | Heat treat the aluminum-silicon interface to provide ohmic contact. |

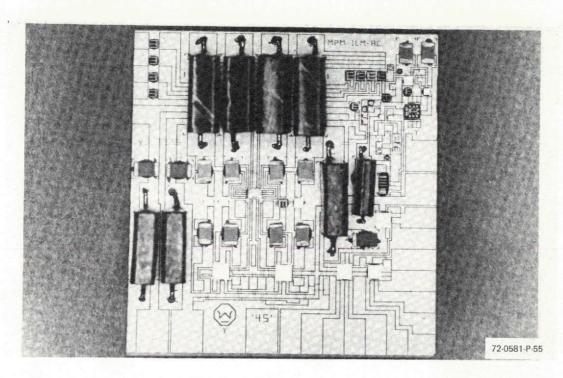

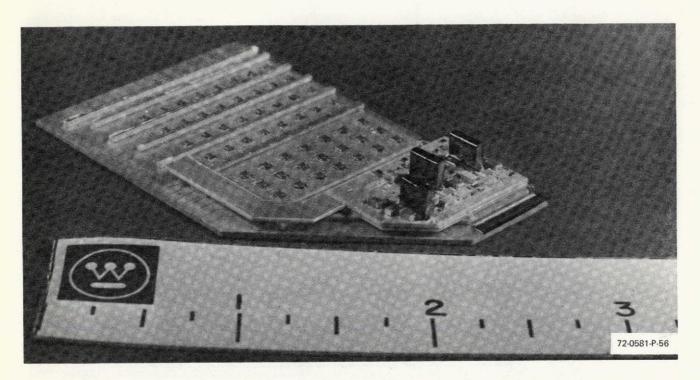

After successfully completing each of these steps, the wafer is then ready for testing. Of course, in-process test are conducted at each step and those wafers failing are rejected. However, those wafers passing these static do tests may fail due to defects that cannot be screened this way. The problem is that no contact can be made to the base regions of the mosaics in process, nor can extensive probe measurements be carried out. The physical size of the particular regions as well as the possibility of mosaic damage or contamination rule out these possibilities. Tests sites are provided at the mosaic periphy and these provide in-process test data. While not conclusive, this data does provide the only in-process electrical checks available. Figure 3-2 is a picture of a completed mosaic.

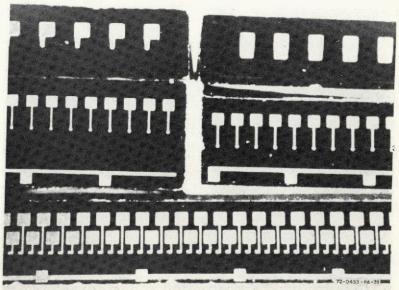

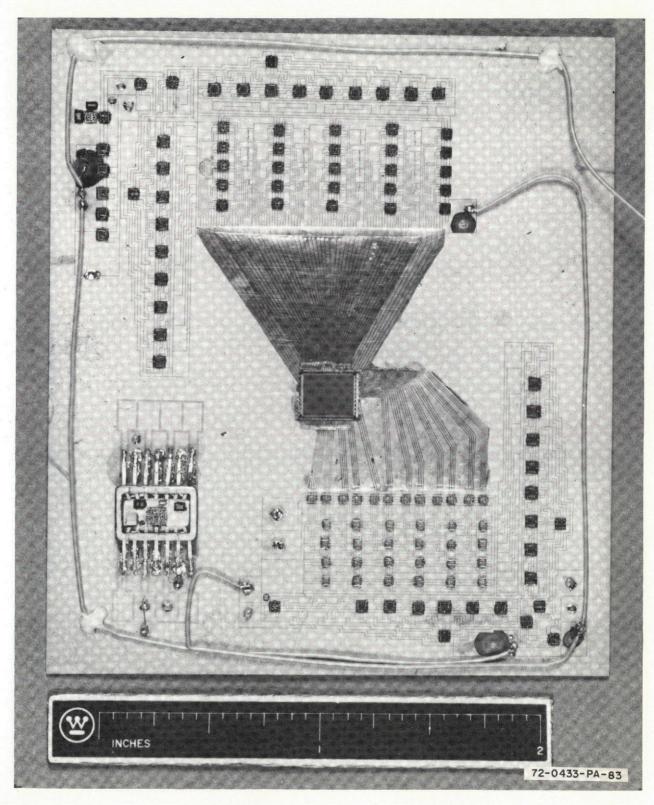

Figure 3-2. 400-x-500 Element Silicon Phototransistor Matrix Array

#### 4. FUNCTIONAL THEORY

Two alternate readout modes of operation are obtainable with phototransistor sensors: the dc or continuous mode and the integration (charge storage) mode. The dc mode of operation is the basic mode for continuous operation of the phototransistor, whereby photon generated carriers in or near the base region are beta multiplied, resulting in an output current proportional to the instantaneous photon flux on the sensor. When employed in large scale arrays, this mode of operation offers several drawbacks. First, output current is highly dependent on the beta of the phototransistor which, in a large array, might vary significantly from sensor to sensor, resulting in nonuniformity or loss of dynamic range. In addition, output signal level for normally encountered light levels is in the microvolt range for reasonably low values of load resistors. This low output level, coupled with an inherently high output impedance, normally requires that some amplification prior to commutation be provided.

The phototransistor integration mode, discovered in the course of development of the 50-x-50 element solid-state image converter for this program, is a dynamic mode of operation in which a transient output pulse is observed. This pulse is a measure of the total number of photons incident upon the light sensitive regions during the time between element samples.

Incident light continuously generates carriers which are stored on the junction capacitances of the phototransistor. Sampling consists of monitoring the discharge of the collector-base junction capacitance through a load resistance. The magnitude of the output transient depends on the total amount of light generated charge which was stored since the previous sampling.

The output obtained in this manner greatly exceeds that which would be obtained by reading out the static, light-generated photocurrent, which is a function of the light flux on the element only during the sample time.

# 4.1 INTEGRATION MODE OPERATION

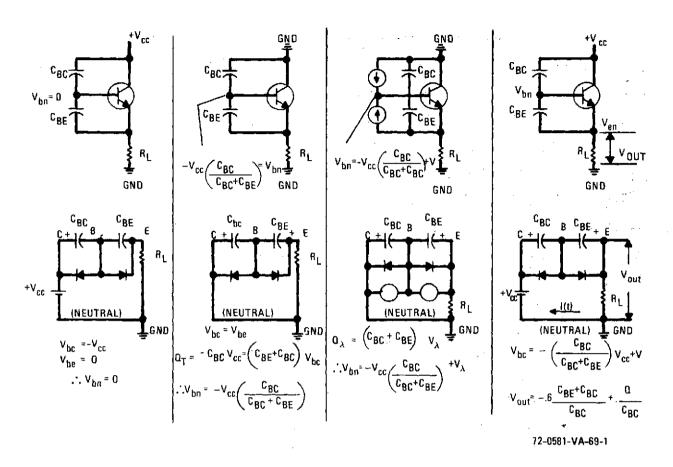

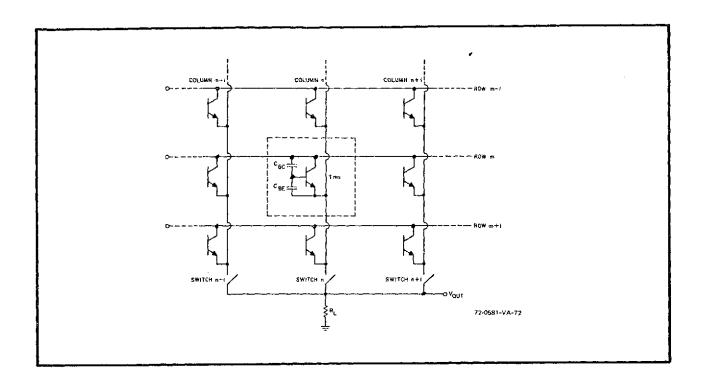

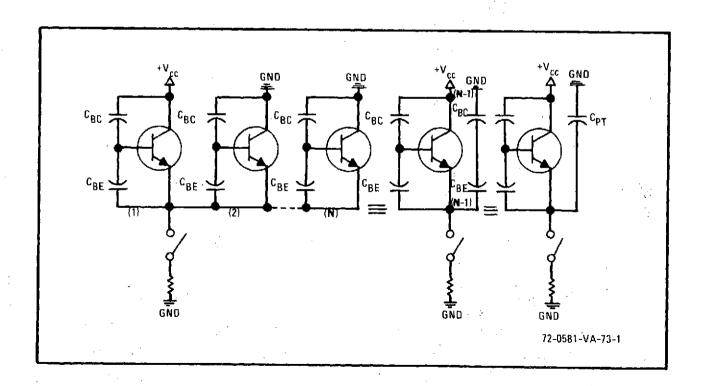

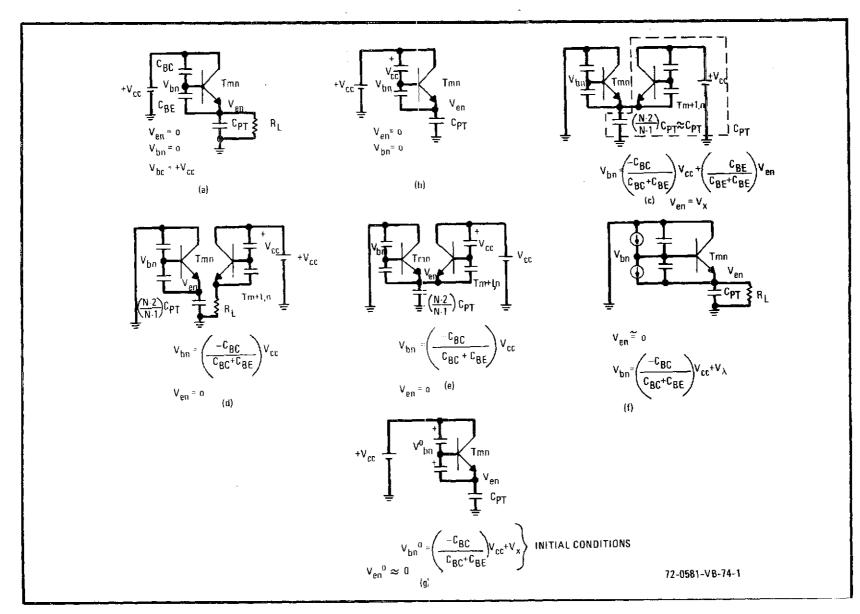

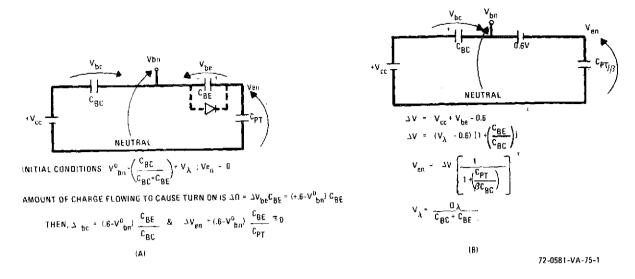

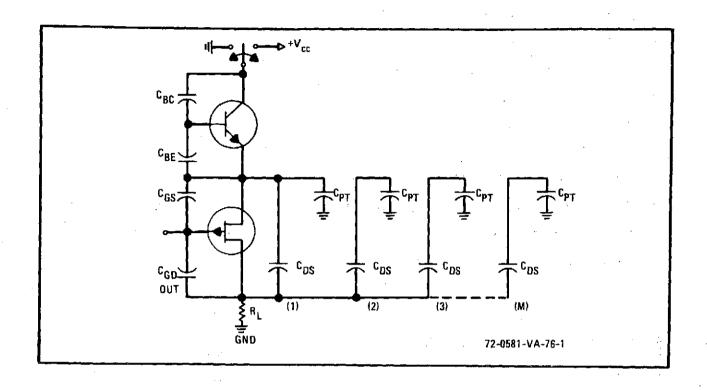

In the analyses that follow, the effect of varying the readout/sampling period will be studied for a single discrete or noninteractive line array of phototransistor elements. The results will subsequently be extrapolated to arrays of phototransistors by adding in the extra parasitic elements that come into play with large mosaics and act to load their operation. Figure: 4-1 shows the circuit configurations and the equivalent circuit diagrams that are used to describe respective portions of the total operating cycle of a phototransistor. The two capacitors shown as  $C_{BC}$  and  $C_{BE}$  are the base-collector and base-emitter junction depletion layer capacitances. The voltages specified pertain only to the case in which the readout period is long compared to any of the circuit time constants (Case II). Corresponding expressions for a very short (Case III) and an intermediate length (Case III) period are developed later in the text.

# 4.1.1 Single Phototransistors

Under the given stipulation that the readout period is very long, figure 4-1(a) shows the conditions that prevail at the end of this sampling interval. With the readout bias still applied at this point, it is assumed that sufficient time has expired to allow the collector-base capacitance (C<sub>BC</sub>) to completely charge up to the V<sub>cc</sub> supply voltage (Case I). At the beginning of this readout condition, the voltage across this capacitance had been reduced to a value lower than V<sub>cc</sub> due to the charge generated by both light and leakage during the integration period.

<sup>\*</sup> The charge generated consists of electron-hole pairs produced in both the p and n material at the collector-base and base-emitter junctions. These carriers tend to neutralize the charge at the junction and thereby reduce the voltage across the junction.

Figure 4-1. Phototransistor Integration Mode of Operation (a) Readout; (b) Reverse Bias; (c) Integration; (d) Instantaneous Readout

Since the voltage across  $C_{BC}$  is lower than  $+V_{CC}$  at the beginning of readout, current starts flowing from the supply through  $C_{BC}$  and into the base of the transistor. Therefore, the base-emitter diode becomes forward biased as transistor action begins. For silicon, about +0.6 volt is dropped across this forward biased junction. As  $C_{BC}$  becomes charged to  $+V_{CC}$ , the current flowing into the base decreases, thereby decreasing the voltage drop across the base-emitter junction (this can be visualized by considering the current-voltage characteristic of the forward-biased base-emitter diode). Therefore, the assumption of a long read period (Case I) implies: (1) complete charging of  $C_{BC}$  to  $+V_{CC}$ ; (2) no current flowing into the base junction; and (3) the voltage drop across the base-emitter diode to be zero. (Later in the

analysis it will be seen that this assumption leads to the presence of an extra term in the output expression which subtracts from the output of the device.) Therefore, the base-emitter capacitance is assumed completely discharged (it is assumed that no significant dc light generated current is flowing).

At the conclusion of this readout period, the device is reverse-biased (figure 4-1(b)) by returning the collector to ground. (We will consider the effects of emitter sampling switches later.) This voltage change charges the combination of  $C_{BC}$  and  $C_{BE}$  so as to back-bias both junctions. The charging of  $C_{BC}$  and  $C_{BE}$  in series through  $R_{L}$  causes a negative spike at  $R_{L}$ , but this spike has little energy. Its amplitude is normally limited by the rise time of the collector bias, since the exponent

$$R_{L} \left( \frac{C_{BE} \quad C_{BC}}{C_{BE} + C_{BC}} \right)$$

is normally very short. When this charging has taken place  $V_{\rm bc} = V_{\rm bc}$ . Since the emitter and collector are both at ground, by charge conservation

$$Q_{t} = -C_{BC} V_{cc} = (C_{BE} + C_{BC}) V_{bc}$$

(1)

where  $\mathbf{Q}_{t}$  is the total charge stored on the base node during the readout period.

At the beginning of reverse-biasing when the collector is returned to ground, one notices that  $C_{BE}$  and  $C_{BC}$  are effectively put in parallel when looking from the base to ground. This means that any charge generated in the base will neutralize charge  $Q_t$  which is shared on  $C_{BC}$  and  $C_{BE}$ . Then the maximum charge which can be generated  $(Q_{\lambda max})$  and still be theoretically read out is  $-Q_t$  (i.e., the voltage change due to photon generated charge is in opposition to supply voltage). From (1) it follows that

$$v_{bc} = \left(\frac{-C_{BC}}{C_{BE} + C_{BC}}\right) v_{cc}$$

and, since  $V_{bn} = V_{bc}$ , this leads to

$$V_{bn} = \left(\frac{-C_{BC}}{C_{BE} + C_{BC}}\right) V_{cc}.$$

(2)

The reversed-biased condition described directly above initiates the integration period (figure 4-1(c)).

The current generators shown represent the photon and leakage current generation in both junctions. It is noted that the quasi-static equilibrium condition requires that  $V_{bc} = V_{be}$  at each instant throughout integration. Therefore, if we assume a total light/leakage generated charge =  $Q_{\lambda}$ , then  $Q_{\lambda} = (C_{BC} + C_{BE}) V_{\lambda}$ , where  $V_{\lambda}$  is the voltage decrease (in magnitude) on each junction due to charge generation.  $Q_{\lambda}$  cannot exceed  $Q_{t}$ ; so  $Q_{t}$  is a measure of device dynamic range. In addition,  $Q_{\lambda}$  is dependent on the light sensitivity of the device and the time allowed for the integration period.

$$V_{bn} = \left(\frac{-C_{BC}}{C_{BE} + C_{BC}}\right) \quad V_{cc} + V_{\lambda}. \tag{3}$$

The readout cycle begins by returning the collector to  $+V_{cc}$  (figure 4-1(d)). Assuming this voltage rise occurs instantaneously, both the base node-to-neutral return voltage  $(V_{bn})$  and the emitter to neutral voltage  $(V_{en})$  will instantaneously rise  $V_{cc}$  volts, so that

$$v_{bn} = v_{cc} - v_{cc} \left( \frac{c_{BC}}{c_{BC} + c_{BE}} \right) + v_{\lambda} = v_{cc} \left( \frac{c_{BE}}{c_{BC} + c_{BE}} \right) + v_{\lambda}$$

(4)

and  $V_{en} = V_{cc}$ .

A transient current will begin flowing immediately, and the emitter voltage V will tend toward ground. The time constant  $(\tau)$  for the transient current is equal to

$$\tau = R_{L} \left( \frac{C_{BC}C_{BE}}{C_{BC} + C_{BE}} \right)$$

(5)

Transistor action is not present at this point because the base-emitter junction capacitance is charged such that the junction is reversed-biased.

Transient current flow with this time constant will continue until the voltage across the base-emitter junction is sufficient to forward-bias the base-emitter diode (nominally at +0.6 volt), thus turning on the transistor. This turn-on point is derived as follows (V is defined as the voltage at the emitter when the phototransistor turns on). As V falls to V on, V bn will fall from the level of (4) by an amount equal to

$$(V_{cc} - V_{on}) \left( \frac{C_{BE}}{C_{BE} + C_{BC}} \right)$$

.

Thus, at the point of turn-on,  $V_{en} = V_{on}$  and

$$v_{bn} = v_{cc} \left( \frac{c_{BE}}{c_{BC} + c_{BE}} \right) + v_{\lambda} - (v_{cc} - v_{on}) \left( \frac{c_{BE}}{c_{BE} + c_{BC}} \right); (6)$$

which, upon combining teams, simplifies to

$$V_{bn} = V_{\lambda} + V_{on} \left( \frac{C_{BE}}{C_{BE} + C_{BC}} \right).$$

(7)

By noting that  $V_{en} = V_{on}$  and assuming  $V_{bn} - V_{en} = V_{be} = +0.6$  volt at turn on, it is then found that

$$0.6 = V_{\lambda} + V_{on} \left( \frac{C_{BE}}{C_{BE} + C_{BC}} \right) - V_{on} = V_{\lambda} - V_{on} \left( \frac{C_{BC}}{C_{BC} + C_{BE}} \right)$$

or, solving in terms of V, that

$$v_{on} = (v_{\lambda} - 0.6) \left[ 1 + \left( \frac{C_{BE}}{C_{BC}} \right) \right]$$

(8)

But, since

$$v_{\lambda} = \frac{Q_{\lambda}}{C_{BE} + C_{BC}}$$

this in turn converts to

$$v_{on} = \left(\frac{Q_{\lambda}}{C_{BC}}\right) - 0.6 \left[1 + \left(\frac{C_{BE}}{C_{BC}}\right)\right]$$

(9)

It can be seen that the voltage termed  $V_{on}$  is directly proportional to the integrated charge. This is the output voltage  $(V_{out})$  read in the integration mode (i.e.,  $V_{on} \equiv V_{out}$ ). The last term in this equation is the term referred to at the beginning of the analysis and appears because of the long readout period (figure 4-1(a) and accompanying discussion). This term represents the voltage lost in turning on the base-emitter diode and subtracts from the lower end of the dynamic range, as can be seen when we consider that  $V_{out}$  cannot fall below zero volts. The light generated charge needed to bring  $V_{on}$  just to zero volts is, from (9),

$$\left(\frac{Q_{\lambda}}{C_{BC}}\right) = 0.6 \left[1 + \left(\frac{C_{BE}}{C_{BC}}\right)\right].$$

Thus, at least this much light generated charge is lost in turning on the transistor.

Realizing this, (9) must be modified when expressed in terms of V out to read (for Case I, where a long readout time is assumed such that no voltage appears across the base-emitter diode at the end of readout)

$$\begin{aligned} \mathbf{v}_{\mathrm{out}} &= \left(\frac{\mathbf{Q}_{\lambda}}{\mathbf{C}_{\mathrm{BC}}}\right) &-0.6 \quad \left[1 + \left(\frac{\mathbf{C}_{\mathrm{BE}}}{\mathbf{C}_{\mathrm{BC}}}\right)\right]; \ \mathrm{for}\left(\frac{\mathbf{Q}_{\lambda}}{\mathbf{C}_{\mathrm{BC}}}\right) > \ 0.6 \left[1 + \left(\frac{\mathbf{C}_{\mathrm{BE}}}{\mathbf{C}_{\mathrm{BC}}}\right)\right] \\ \mathbf{v}_{\mathrm{out}} &= 0; & \mathrm{for}\left(\frac{\mathbf{Q}_{\lambda}}{\mathbf{C}_{\mathrm{BC}}}\right) \leq \ 0.6 \left[1 + \left(\frac{\mathbf{C}_{\mathrm{BE}}}{\mathbf{C}_{\mathrm{BC}}}\right)\right] \end{aligned} \tag{10}$$

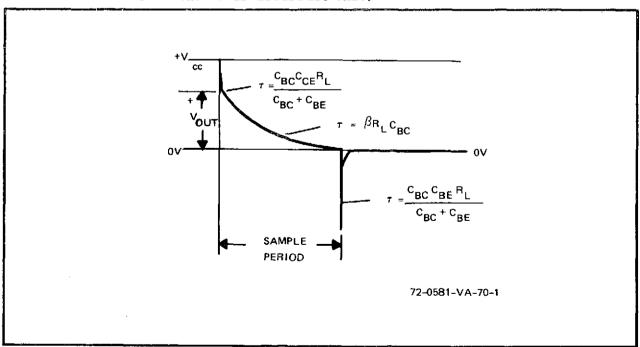

At this point, assuming the first condition in (10), the time constant increases to  $\beta R_L C_{BC}$ , since the transistor is on and  $C_{BE}$  is fully charged to 0.6 volt. The output waveform will look as shown in figure 4-2. The point of turn on  $(V_{out})$  is the desired output, since it is proportional to  $Q_{\lambda}$  and is independent of  $\beta$ . The transient spike in figure 4-2 prior to  $V_{out}$  represents a noise voltage in the output. There are several ways of minimizing this spike, however. First of all, in sensor arrays there will normally be a device turning off for each device turning on, and the two noise spikes thus created are similar in amplitude and opposite in polarity so that they should cancel to some extent in the common output load resistor. Secondly, the rise time of the sampling pulse  $\tau_{\rm g}$  will normally be longer than the time constant ( $\tau$ ) of the noise transient (see equation (5)), since the values of  $C_{\overline{BE}}$ and C are quite small. For instance, in a representative silicon n-p-n mosaic, typical values are R  $_{L}$  = 2K and C  $_{BC}$  = C  $_{BE}$  = 0.2 pF so that  $\tau = 0.2$  ns. The  $\tau_s$  factor should be small compared to  $\beta R_L C_{RC}$ , however, so that no active discharge begins prior to the application of full bias to the This means that it is desirable that:

Figure 4-2. Output Waveform - Phototransistor Integration Mode

$$R_{L} \left( \frac{C_{BE} C_{BC}}{C_{BE} + C_{BC}} \right) < r_{s} < R_{L} C_{BC}$$

which can be achieved by minimizing C<sub>BE</sub> with respect to C<sub>BC</sub>.

Recalling again that  $Q_{\lambda}$  cannot exceed  $Q_{t}$ , it is found, upon plugging the expression (1) for  $Q_{\lambda} = -Q_{t} = C_{BC}^{V}$  into (10), that

$$v_{\text{out}_{\text{max}}} = v_{\text{cc}} - 0.6 \left[ 1 + \left( \frac{c_{\text{BE}}}{c_{\text{BC}}} \right) \right]. \tag{11}$$