NASA CR-132486

## A FOLLOW-ON STUDY FOR

#### MINIATURE SOLID-STATE PRESSURE TRANSDUCER

Distribution of this report is provided in the interest of information exchange. Responsibility for its contents resides in the author or organization that prepared it.

Prepared for

National Aeronautics and Space Administration Langley Research Center Langley Station Hampton, Virginia

Final Report

August 1974

(Prepared under Contract NASI-9005 by the Engineering and Environmental Sciences Division of the Research Triangle Institute, Research Triangle Park, North Carolina.)

#### FOREWORD

This report was prepared by the Research Triangle Institute, Research Triangle Park, North Carolina on NASA Contract NAS1-9005, "A Follow On Study for Miniature Solid State Pressure Transducers." This investigation was performed by members of the Envrionmental and Engineering Programs Group of the Research Triangle Institute. Staff members contributing significantly to this investigation include Dr. Robert M. Burger, Dr. J. J. Wortman, C. D. Parker, R. P. Donovan, A. D. Brooks, H. L. Honbarrier and R. T. Pickett. This work was administered under the direction of the Flight Instrument Division, Langley Research Center, by Mr. Charles A. Hardesty.

The work was carried out in two parts chronologically. Part A describes the first investigation, a totally Research Triangle Institute in-house effort. The time period for this work was March 1969 to August 1970. The activities described in Part B include the liberal use of outside vendors to supply various parts and services in the manufacture of prototype test units. The period of performance for this portion of the contract was December 1970 to June 1974. The RTI Project Leader for Part A of this effort was C. D. Parker and for Part B was R. P. Donovan.

#### ABSTRACT

This two part final report summarizes the activities of a developmental program to design, fabricate and test an absolute pressure transducer based upon the piezojunction properties of silicon. The prime problem addressed here is the development of a housing capable of applying the high stress levels needed for sensitive piezojunction operation but at the same time, free from the creep effects and the fragility that limit the usefulness of previous designs.

The first part of the report describes the initial fabrication and tests and reviews the theory of sensor performance. The second part incorporates two recommendations of the first part (the use of commercially manufactured silicon planar mesa diodes and the adoption of an all-silicon structure for loading) and presents some preliminary test data on the transducers thus fabricated. These initial measurements show much improved performance over any previously fabricated piezojunction transducers but testing is incomplete and several problems in manufacturing technology remain.

# CONTENTS

# PART A: March 1969 - August 1970

| Section |                                                  | Page |

|---------|--------------------------------------------------|------|

| I       | INTRODUCTION                                     | 1    |

| II      | THEORETICAL CONSIDERATIONS - A SUMMARY           | 3    |

|         | Energy Band Considerations                       | 3    |

|         | Deformation Potential Coefficients               | 7    |

|         | Calculated Values of $\gamma_{\nu}(e)$           | 7    |

|         | Effect of Stress on p-n Junction Characteristics | 11   |

|         | Calculations of Sensitivity for Mesa Devices     | 13   |

| III     | TRANSDUCER DESIGN CONSIDERATIONS                 | 19   |

|         | Junction Element                                 | 19   |

|         | Capsule Design                                   | 19   |

|         | Performance Limits                               | 26   |

| IV      | SEMICONDUCTOR PROCESSING                         | . 27 |

|         | Planar Mesa Technology                           | 27   |

|         | Fabrication Critique                             | 29   |

|         | Summary                                          | 33   |

| v       | TRANSDUCER FABRICATION                           | 37   |

|         | The Capsule Diode                                | 37   |

|         | Transducer Housing                               | 42   |

|         |                                                  | , ·  |

| VI      | EXPERIMENTAL RESULTS                             | 45   |

|         | Introduction                                     | 45   |

|         | Discussion                                       | 45   |

|         | Transducer No. 1                                 | 50   |

|         | Transducer No. 2                                 | 56   |

|         | Transducer No. 3                                 | 56   |

|         | Transducer No. 4                                 | ,65  |

|         | Planar-Mesa Diodes                               | 65   |

|         | Instrumentation                                  | 68   |

| VII     | CONCLUSIONS AND RECOMMENDATIONS                  | 71   |

# CONTENTS PART B: December 1970 - June 1974

| Section  |     |                                                                                                                   | Page                             |

|----------|-----|-------------------------------------------------------------------------------------------------------------------|----------------------------------|

| I        | INT | RODUCTION                                                                                                         | 73                               |

| II       | NEW | TECHNOLOGY                                                                                                        | 75                               |

|          |     | Silicon-to-Silicon Seals Using Sputtered<br>Borosilicate Glass<br>Housing Considerations                          | 76<br>77                         |

| III      | DES | IGN                                                                                                               | 81                               |

| IV       | FAB | RICATION                                                                                                          | 83                               |

|          |     | Cavity and Mesa Etching Coating Dicing and Glass Etching First Electrostatic Seal Second Electrostatic Seal Tests | 83<br>85<br>87<br>88<br>89<br>90 |

| V        | RES | ULTS                                                                                                              | 93                               |

| VI       | CON | CLUSIONS AND RECOMMENDATIONS                                                                                      | 105                              |

|          |     |                                                                                                                   |                                  |

| APPENDIX | X A | CAPSULE DIODE MASK-SET                                                                                            | 107                              |

| APPENDIX | КВ  | SEMICONDUCTOR PROCESSING PROCEDURES                                                                               | 117                              |

| APPENDIX | K C | THE RELATIONSHIP OF STRESS TO STRAIN                                                                              | 121                              |

| APPENDIX | K D | LOW TEMPERATURE ELECTROSTATIC SILICON-TO-SILICON SEALS USING SPUTTERED BOROSILICATE GLASS                         | 125                              |

| APPENDIX | ΚE  | SOLICITATION MAILED TO POTENTIAL SUPPLIERS FOR THE FABRICATION OF PRESSURE TRANSDUCER PARTS                       | 127                              |

| REFERENC | CES |                                                                                                                   | 143                              |

# LIST OF ILLUSTRATIONS

| <u>Figure</u> |                                                                                                                                   | Page |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| 1             | The Valence Bands of Silicon Near $\overline{k} = 0$                                                                              | 4    |

| 2             | The Split Valence Bands of Silicon for a Compressional Stress                                                                     | 4    |

| 3             | Ratio of Stressed to Unstressed Minority Carrier Density for a Hydrostatic, [100], [011] and [111] Uniaxial, Compressional Stress | 9    |

| 4             | Ratio of Stressed to Unstressed Minority Carrier Density for a [100], [011] and [111] Uniaxial, Tensional Stress                  | 10   |

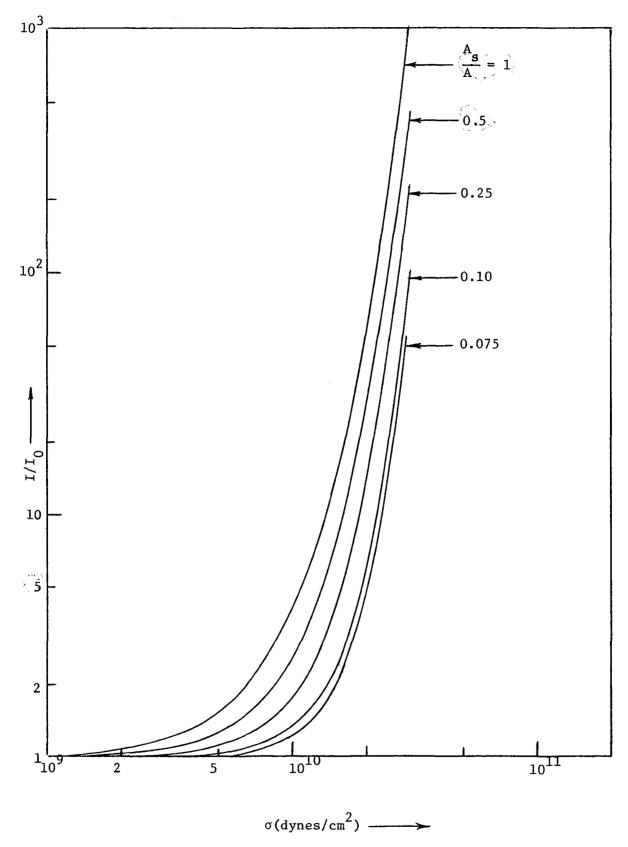

| 5             | I/I $_0$ Versus Stress ( $\sigma$ ) for Various Ratios of Stress Area To Total Area ( $A_s$ /A)                                   | 14   |

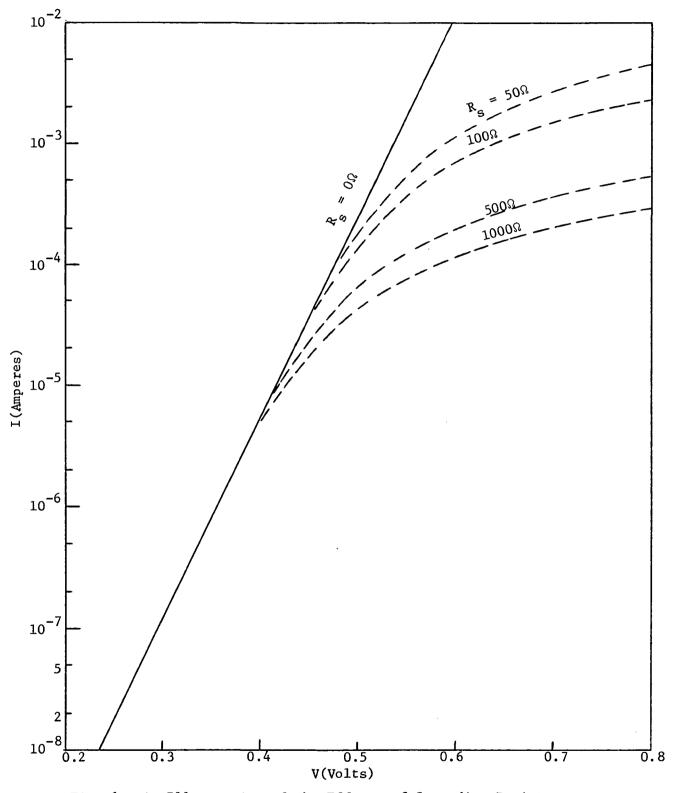

| 6             | An Illustration of the Effects of Spreading Resistance                                                                            | 17   |

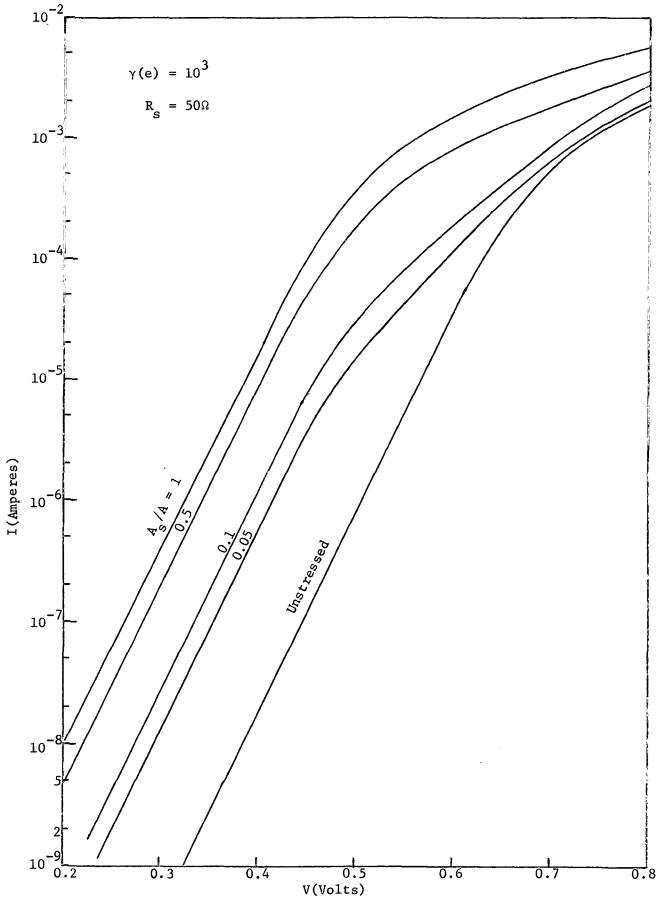

| 7             | The Combined Effects of Spreading Resistance and<br>Stressed Area to Total Area Ratios                                            | 18   |

| 8             | An Illustration of the Capsule Diode                                                                                              | 20   |

| 9             | I/I <sub>0</sub> Versus Stress for an A <sub>s</sub> /A Ratio of 0.175                                                            | 21   |

| 10            | A Fixed Diaphragm, Uniformly Loaded                                                                                               | 22   |

| 11            | Relative Change in Current Per Unit Pressure                                                                                      | 25   |

| 12            | Final Capsule Diode Design                                                                                                        | 28   |

| 13            | Initial Capsule Design                                                                                                            | 30   |

| 14            | Uneven Etch of Junction Area Close to Top of Mesa                                                                                 | 34   |

| 15            | An Illustration of the Glass Wafer Fabrication Technique                                                                          | 38   |

| 16            | An Illustration of the Completed Port-Side and Vacuum-Side Glass Wafer                                                            | 39   |

| 17            | An Illustration of the Anodic Bonding Procedure                                                                                   | 40   |

| 18            | Anodic Bonding Apparatus for the Port-Side Cover                                                                                  | 41   |

# LIST OF ILLUSTRATIONS (continued)

| Figure |                                                                        | Page |

|--------|------------------------------------------------------------------------|------|

| 19     | Photograph of a Completed Capsule Diode                                | 42   |

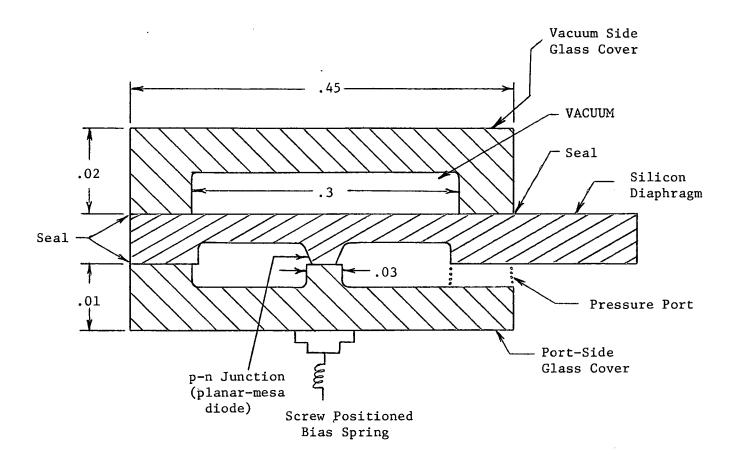

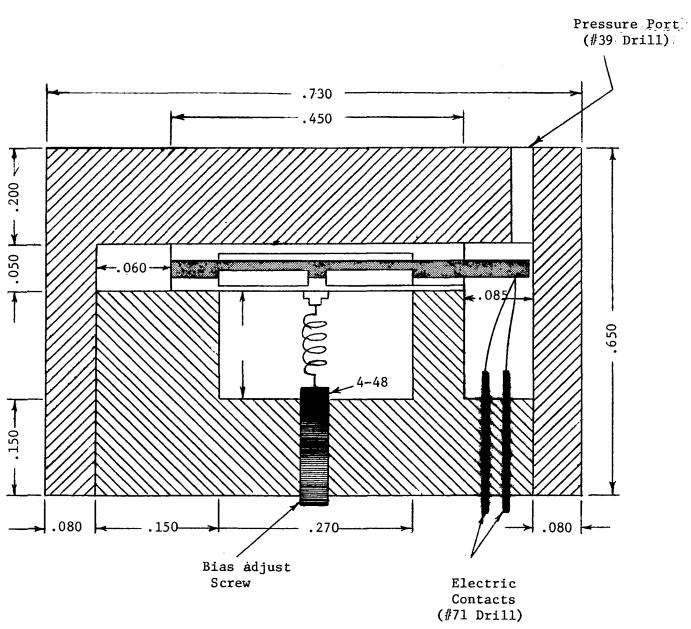

| 20     | An Illustration of the Complete Transducer                             | 43   |

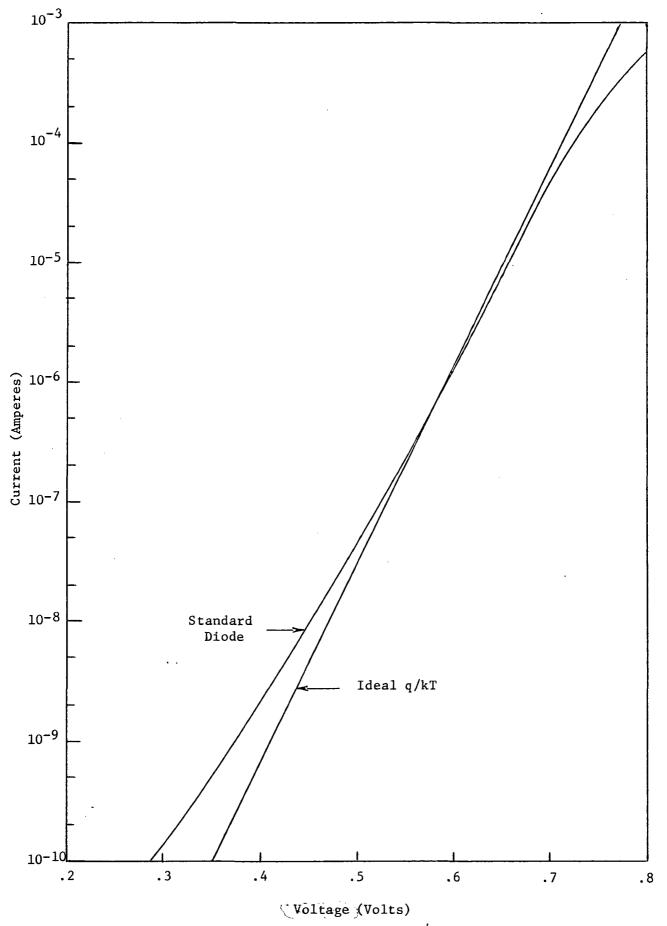

| 21     | Log I-V Characteristics of the Standard Diode and the Ideal q/kT Slope | 46   |

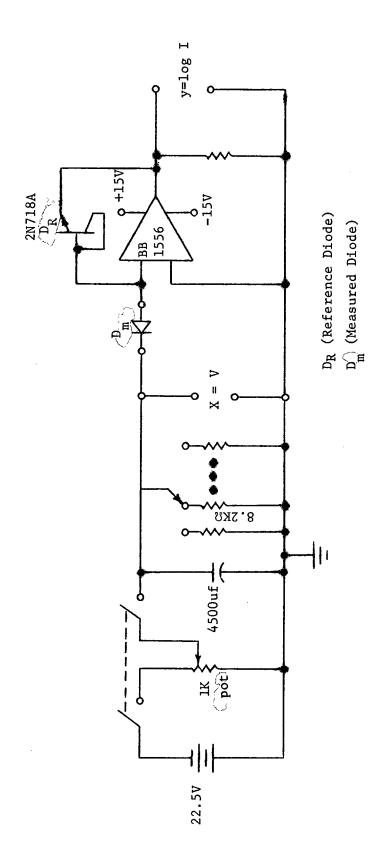

| 22     | Log Current Versus Voltage Plotter Circuit                             | 47   |

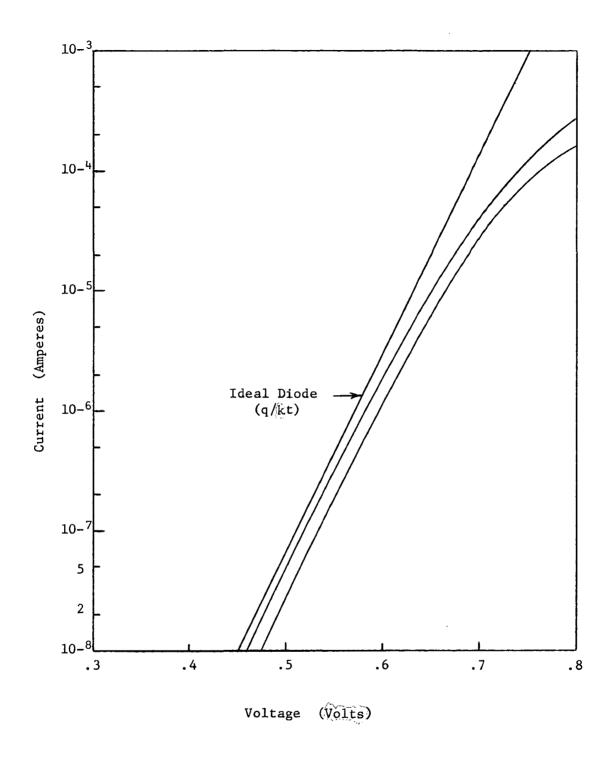

| 23     | Log I-V Characteristics of Large Area, Planar<br>Mesa Diodes           | 49   |

| 24     | Log I-V Characteristics of Transducer No. 1 Diode at Various Stages    | 51   |

| 25     | Characteristics of Transducer No. 1; Bias Condition11                  | 52   |

| 26     | Log I-V Characteristics of Transducer No. 1; Bias Condition 2          | 53   |

| 27     | Log I-V Characteristics of Transducer No. 1; Bias Condition 3          | 54   |

| 28     | Log I-V Characteristics of Transducer No. 1; Bias Condition 4          | 55   |

| 29     | Characteristics of the Planar-Mesa DiodedUsed in Transducer No. 2      | 57   |

| 30     | Log I-V Characteristics of Transducer No. 2, Bias Condition 1          | 58   |

| 31     | Log I-V Characteristics of Transducer No. 2, Bias Condition 2          | 59   |

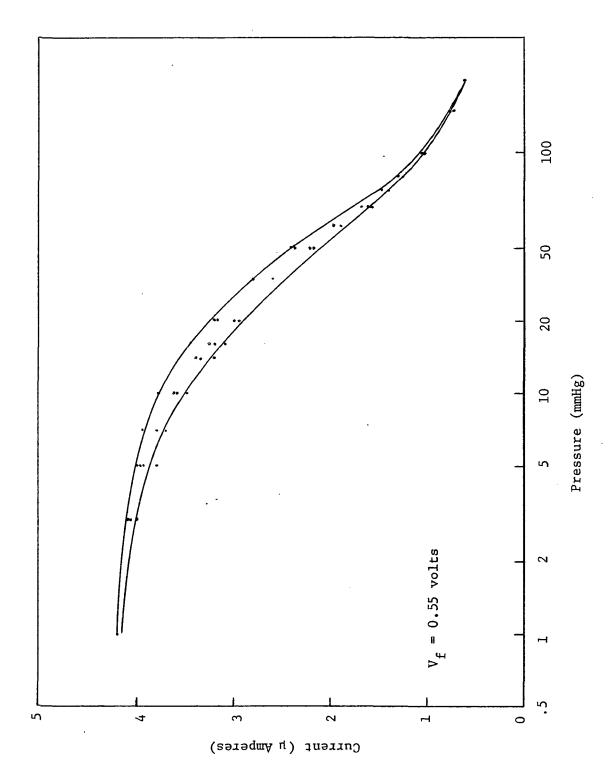

| 32     | PressureCurrent Characteristics of Transducer No. 2                    | 60   |

| 33     | Log I-V Characteristics of Transducer No. 3 Diode at Various Stages    | 61   |

| 34     | Log I-V ${\it Characteristics}$ of Transducer No. 3, Bias Condition 1  | 62   |

| 35     | Log I-V Characteristics of Transducer No. 3, Bias Condition 2          | 63   |

# LIST OF ILLUSTRATIONS (continued)

| Figure      |                                                                                               | Page |

|-------------|-----------------------------------------------------------------------------------------------|------|

| <b>36</b> 6 | Log I-V Characteristics of Transducer No. 3, Bias Condition 3                                 | 64   |

| 37          | Log I-V Characteristics of Pressure Transducer No. 44                                         | 66   |

| 38          | Test Apparatus for Planer-Mesa Diodes                                                         | 67   |

| 39          | Bridge Readout Circuit for Pressure Transducer                                                | 69   |

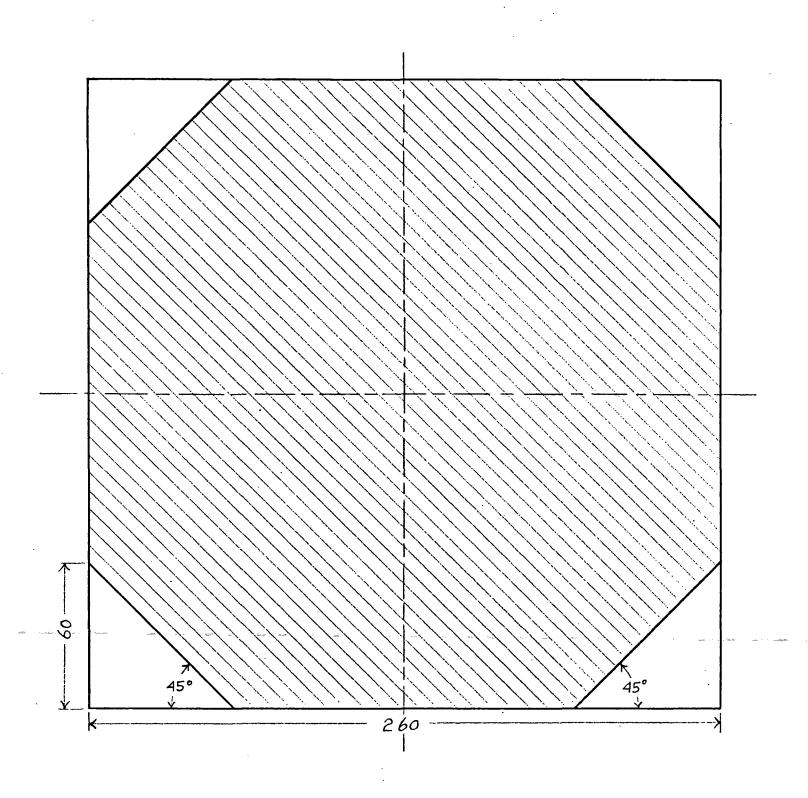

| 40          | Illustration of the Housing Configuration                                                     | 78   |

| 41          | Piezojunction Transducer                                                                      | 91   |

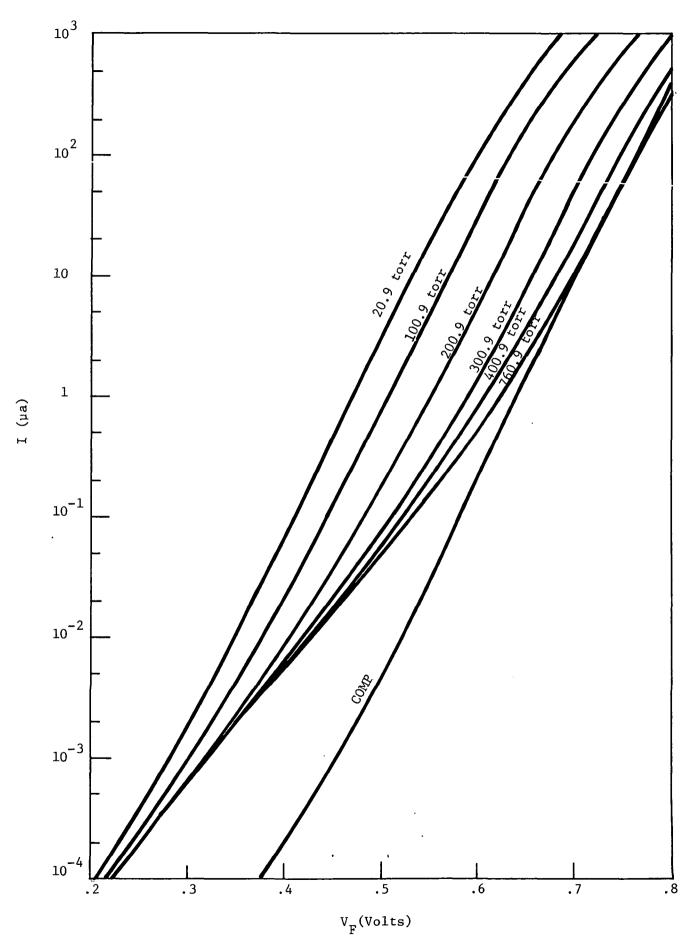

| 42          | Log Current-Voltage Characteristics of Transducer 29-1                                        | 95   |

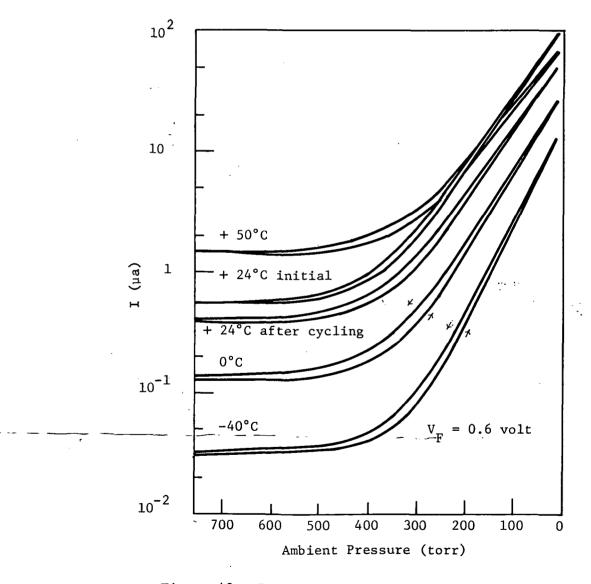

| 43          | Pressure Sensitivity of Transducer 29-1                                                       | 96   |

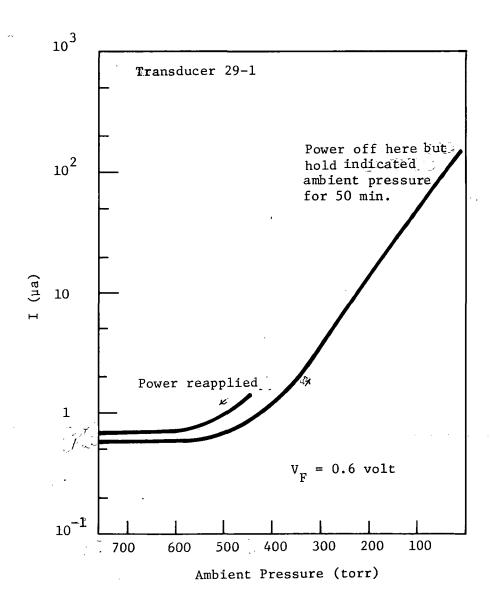

| 44          | Evidence for Hysteresis in the Absence of Temperature<br>Effects because of Power Dissipation | 99   |

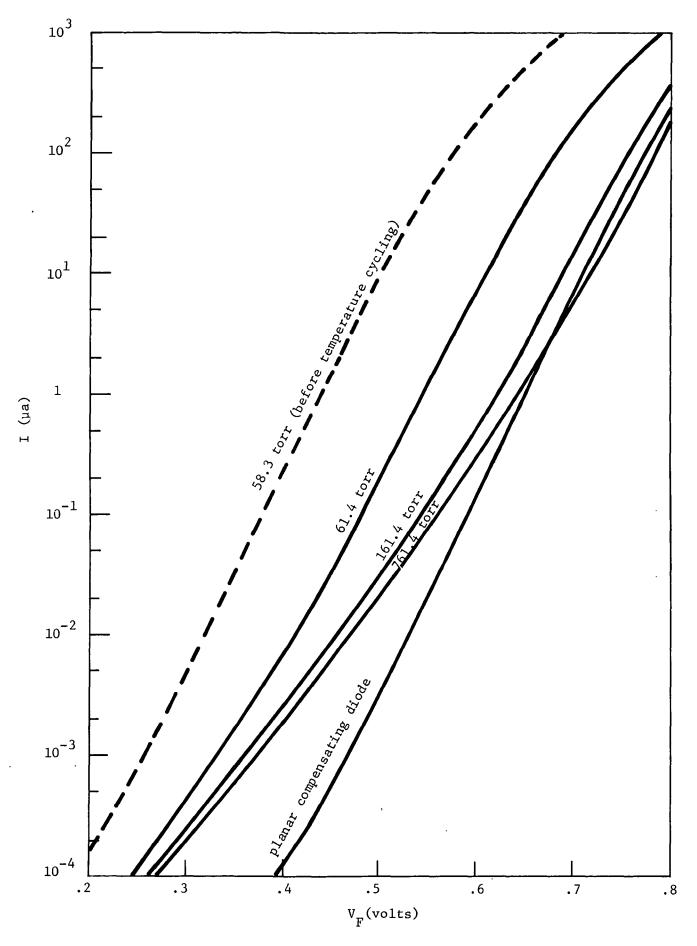

| 45          | Log Current-Voltage Characteristics of Transducer 8-7                                         | 101  |

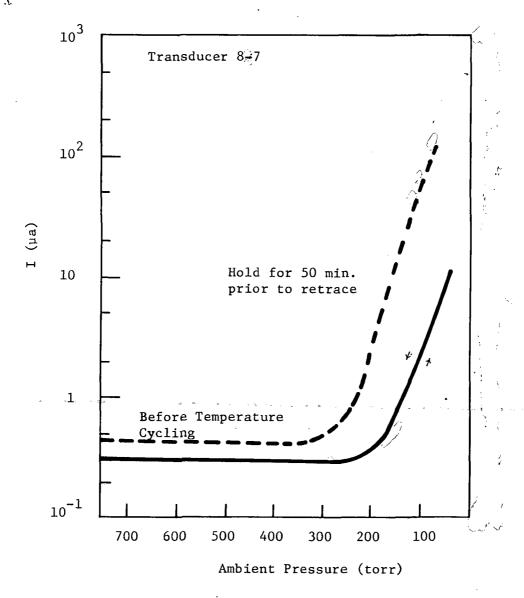

| 46          | Pressure Sensitivity of Transducer 8-7                                                        | 102  |

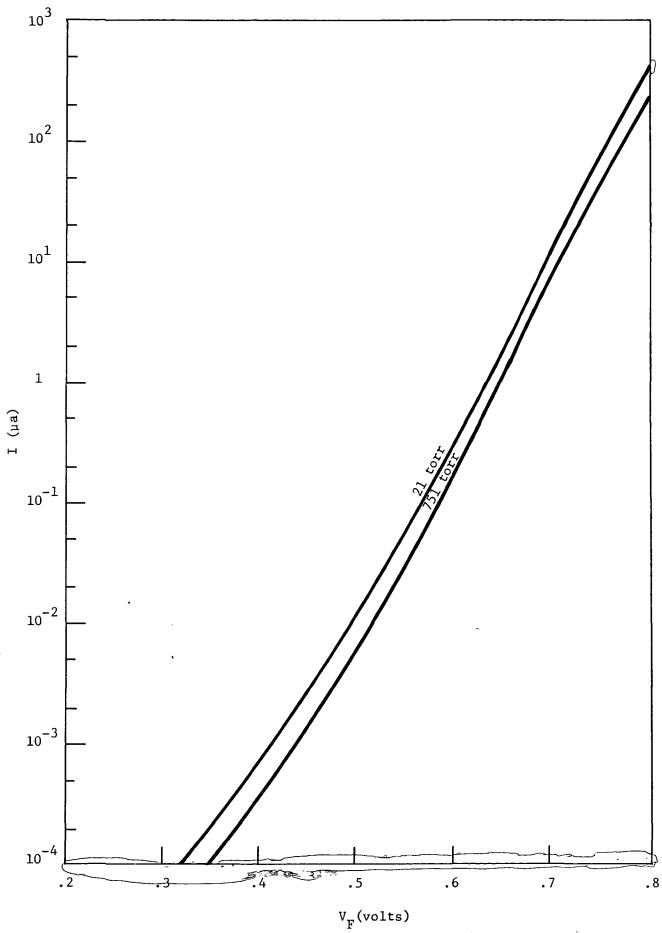

| 47          | Log Current-Voltage Characteristics of Transducer 10-15                                       | 103  |

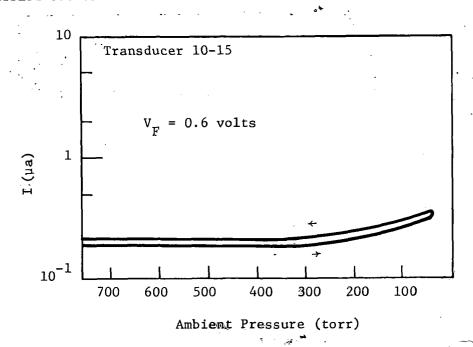

| 48          | Pressure Sensitivity of Transducer 10-15                                                      | 104  |

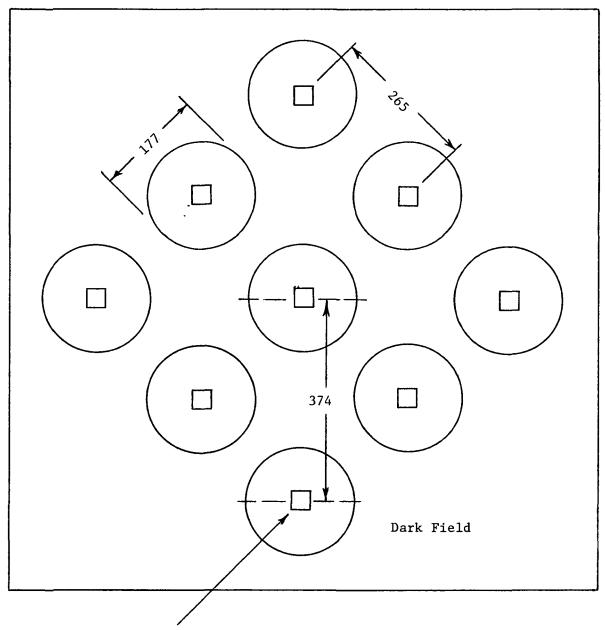

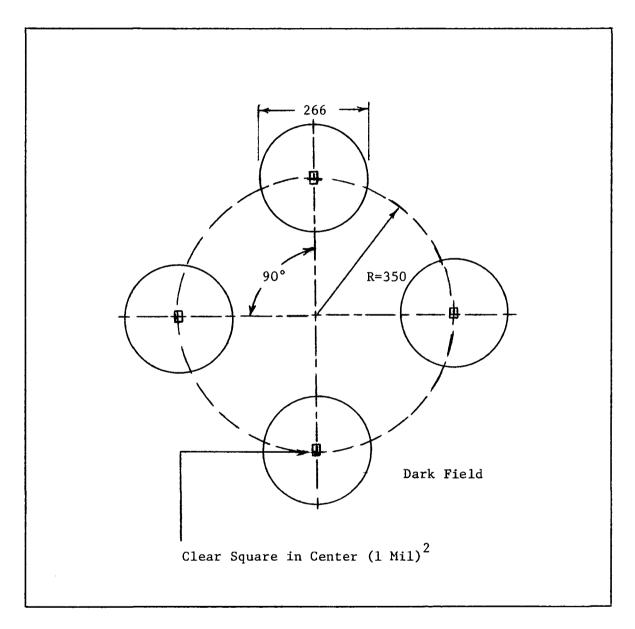

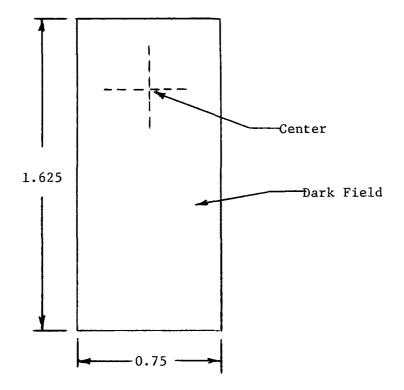

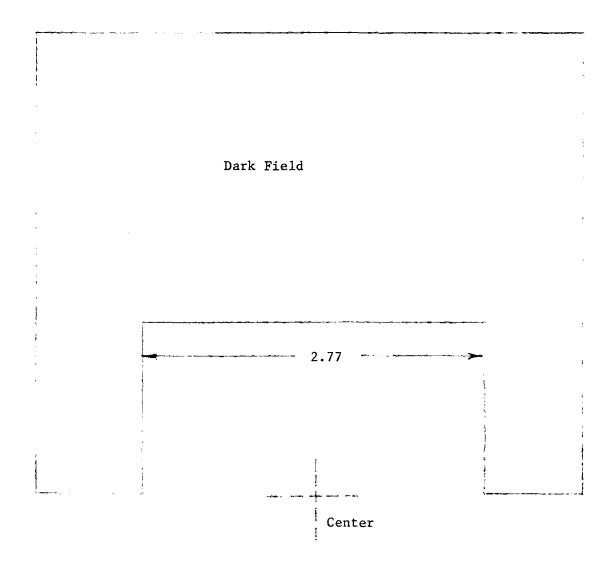

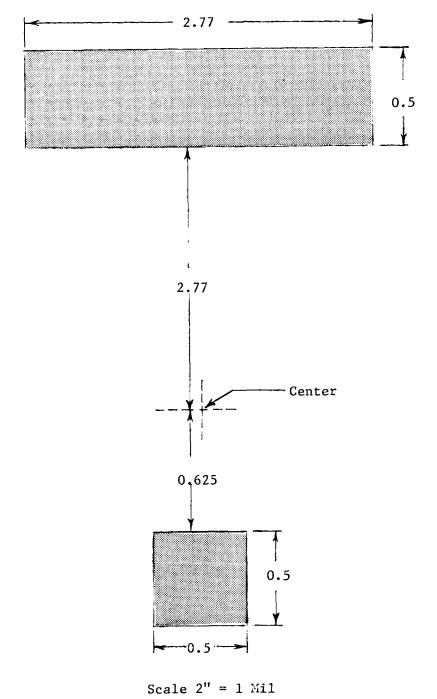

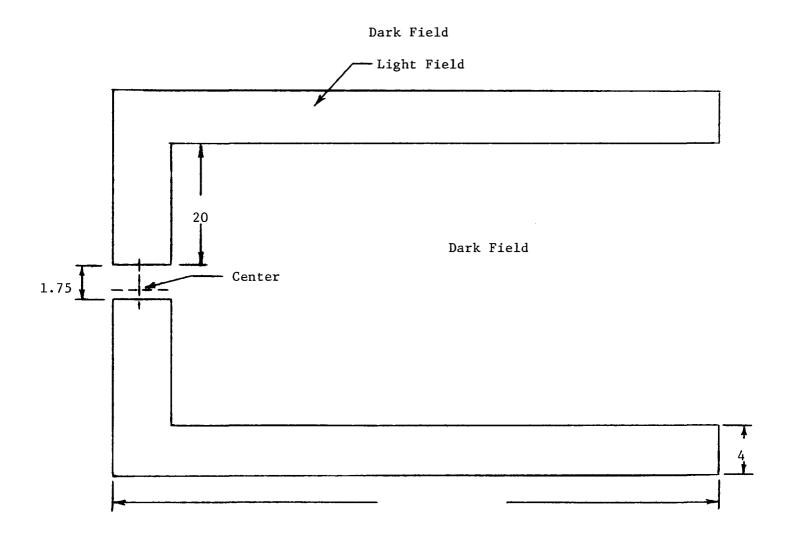

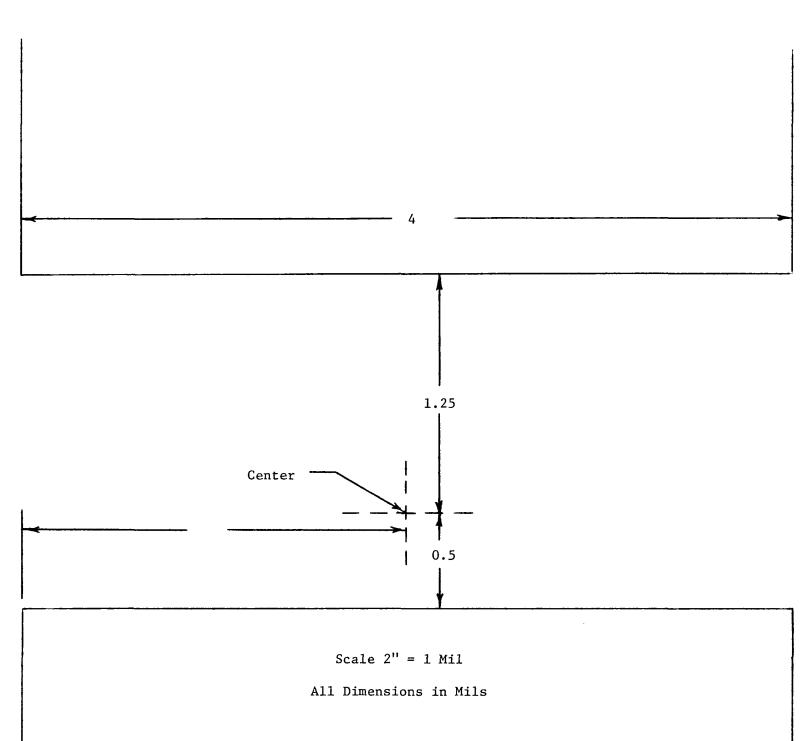

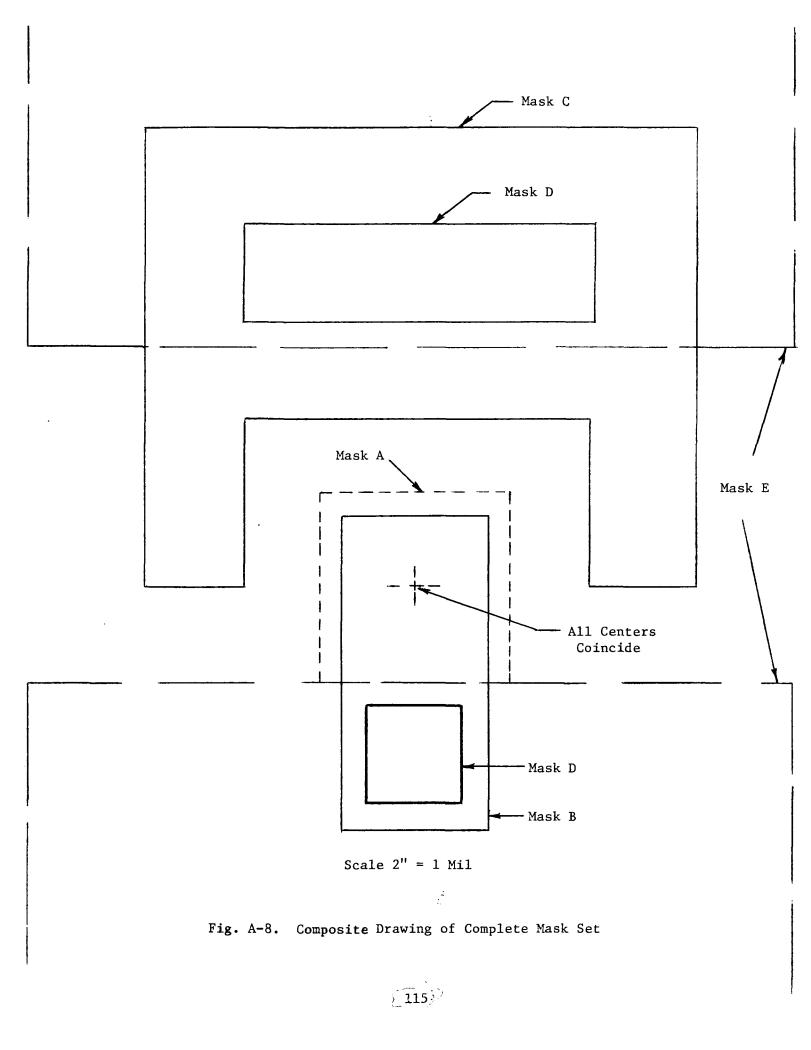

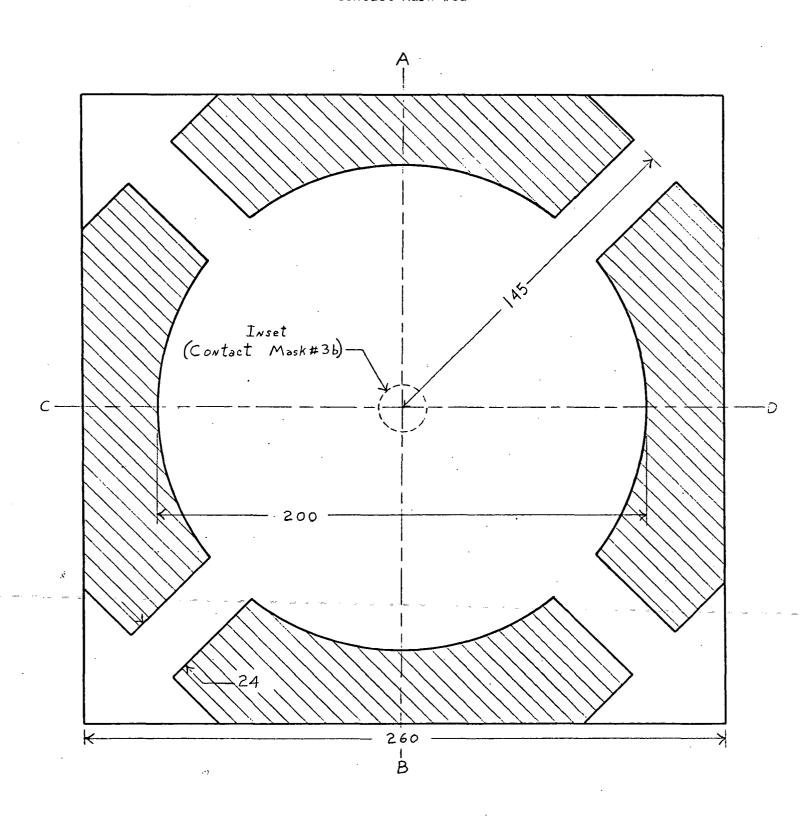

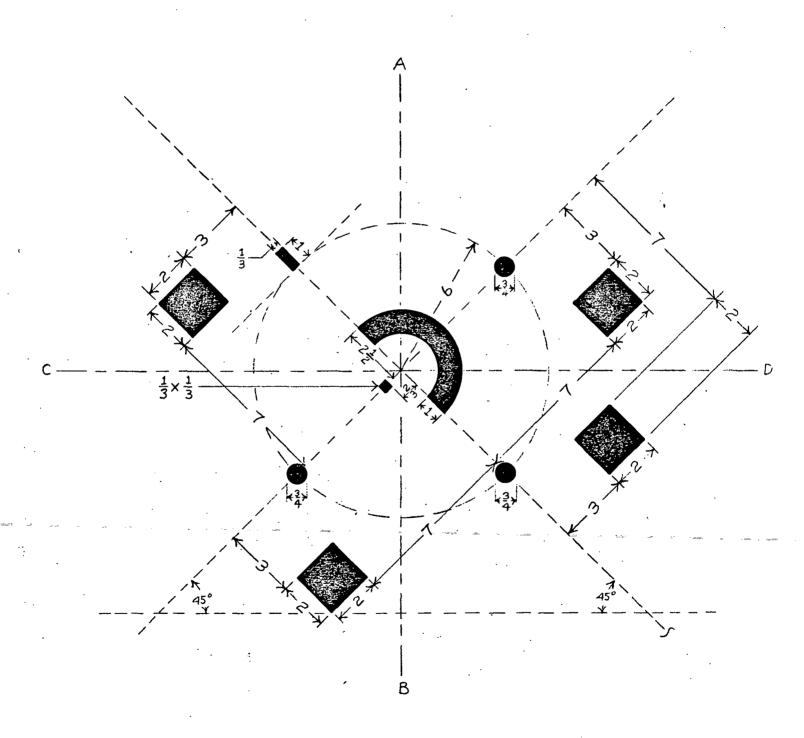

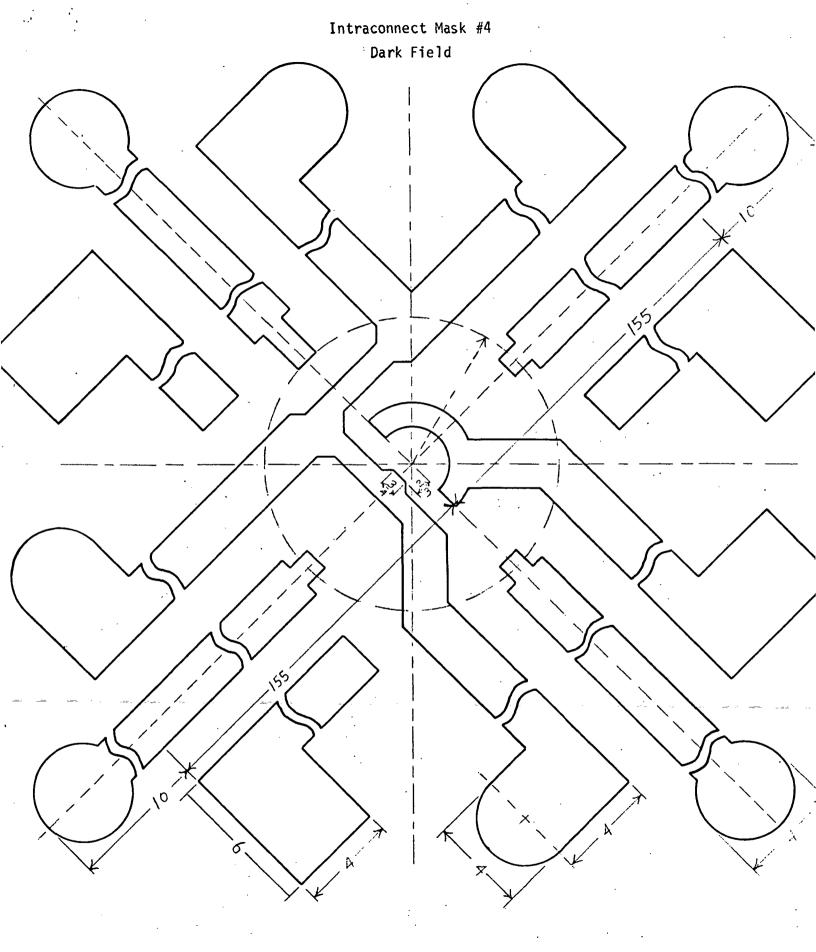

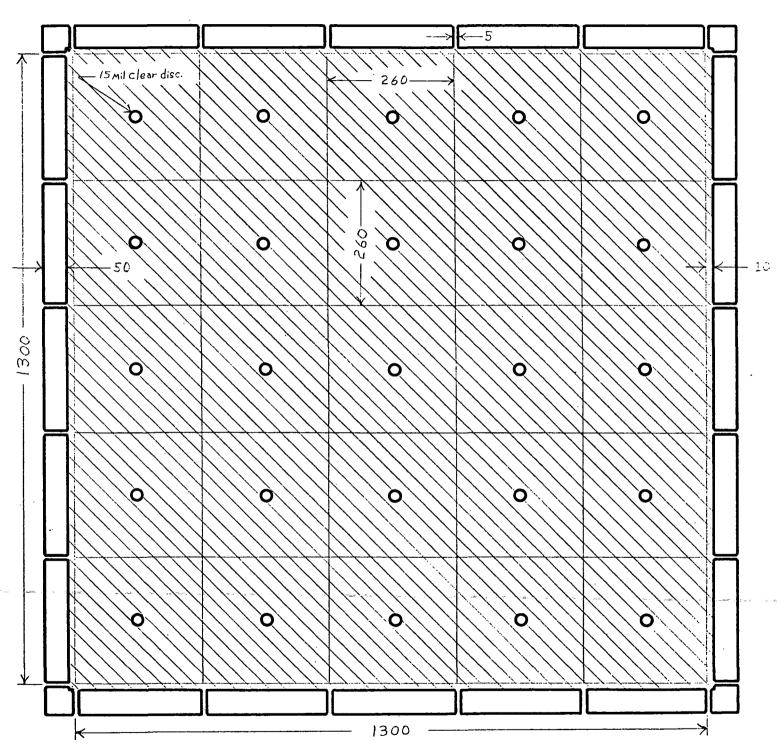

| A-1         | Mask 1-A                                                                                      | 108  |

| A-2         | MaskaA                                                                                        | 109  |

| A-3         | Mask B                                                                                        | 110  |

| A-4         | Mask C                                                                                        | 111  |

| A-5         | Mask D                                                                                        | 112  |

| А-б         | Mask E                                                                                        | 113  |

| A-7         | Center Detail of Mask E                                                                       | 114  |

| A-8         | Composite Drawing of Complete Mask Set                                                        | 115  |

### LIST OF SYMBOLS

```

a, b, c

constants

deformation potential coefficient (eV)

D

deformation potential coefficient (eV)

D_1

deformation potential coefficient (eV)

E

energy corresponding to zero strain (eV)

energy of the Fermi level (eV)

E

energy of the j = 3/2, "heavy" hole band (eV)

E_{v1}

energy of the j = 3/2, "light" hole band (eV)

E_{V2}

energy of the j = 1/2 split-off hole band (eV)

E<sub>V3</sub>

energy of the conduction band minima (eV)

E_{C_{\mathbf{i}}}

hydrostatic strain

e

strain components referred to crystal axes

e,

\Gamma_{25}

valence band edge point

γ<sub>.,</sub>(e)

ratio of minority carrier density with strain to that without strain

Planck's constant (6.624/25 \times 10^{-27} \text{ erg's})

ħ

total p-n junction current (A)

IT

I

ideal p-n junction current (A)

generation-recombination junction current (A)

IR

angular momentum quantum number

j

Boltzmann's constant (8.62 \times 10^{-5} \text{ eV/}^{\circ}\text{K})

k

wave vector (cm<sup>21</sup>)

ī

m

Ci

effective electron masses associated with the conducting band

energy minima (g)

{\rm ^{\it m}_{\it Vi}}

effective hole masses associated with the valence band energy

maxima (g)

```

## LIST OF SYMBOLS (continued)

```

electron density (cm^{-3})

n

electron density-corresponding to zero stress (cm^{-3}).

hole density (cm^{-3})

p

hole density corresponding to zero stress (cm^{-3})

electronic charge (1.602 \times 10<sup>-19</sup> C)

q

stress level (dynes/cm<sup>2</sup>)

base-region stress (dynes/cm<sup>2</sup>)

\sigma_{\mathbf{h}}

emitter-region stress (dynes/cm<sup>2</sup>)

Т

absolute temperature (°K)

V

p-n junction voltage (V)

v_{\rm B}

unstressed breakdown voltage of a p-n junction (V)

deformation potential coefficients

\Xi_{\mathbf{u}}

deformation potential coefficients

```

#### A FOLLOW-ON STUDY FOR MINIATURE SOLID-STATE

#### PRESSURE TRANSDUCERS

PART-A: March 1969 - August 1970

#### SECTION I

#### INTRODUCTION

The work discussed in this report was a continued effort to exploit the stress-sensitive piezojunction effect in fabricating a solid-state pressure transducer. The piezojunction effect refers to the sensitivity of the electrical properties of a p-n junction to mechanical stress (or strain) in the vicinity of the junction. It occurs at high stress levels; e.g., beginning at  $10^9$  dynes/cm $^2$  in silicon, and is characterized by an exponential increase in minority carrier density as stress is increased above the threshold level. Consequently, the presence of such a stress is readily apparent in the V-I characteristics of a p-n junction.

This work was preceded by two years of effort; i.e., Contract Nos. NAS1-6249 and NAS1-7489, to demonstrate the feasibility of using the piezojunction effect as the sensory phenomenon in a pressure transducer. Several pressure transducers were fabricated, and these have been described (Refs. 1, 2). By way of review, the most successful transducers were fabricated using a silicon needle sensor in which the p-n junction was fabricated in the tip of a silicon needle. This unique configuration had several advantages including the elimination of alignment-related problems that are inherent in the indenter point configuration, the problem of coupling stress to such a minute region of a much larger silicon plane, and a stressed area to total junction area ratio approaching unity. The silicon needle sensor also has a serious handicap. Fabricating the needle sensor is extremely difficult. Numerous individual hand operations and operator judgment decisions are required and, consequently, laboratory yields were low. Although a technology evolved at RTI for fabricating the needle sensor, it was difficult to reproduce in the laboratory and was never tried on a production line basis. More recently, only configurations which are compatible with standard semiconductor processing practices and adaptable to a production line technique were considered. A second disadvantage of the needle sensor is fragility. The units fabricated into sensitive pressure transducers were frequently damaged by slight overpressures.

Pressure transducers fabricated more recently; i.e., during the current effort, are a significant improvement over earlier transducers. The sensitive element is a capsule diode; i.e., a planar-mesa diode structure sealed between two glass diaphragms. Although considerable

difficulty was encountered in the fabrication of the diode structure in our limited laboratory, the entire process requires only standard state-of-the-art processes and should present no significant problems to a production line facility. Additionally, the capsule diode structure is an absolute pressure gauge with a built-in vacuum reference and cannot be damaged by oven pressure. Unlike preceding configurations, the capsule diode is designed to see a minimum stress during storage conditions; i.e., one atmosphere pressure.

Capsule diode pressure transducers have been fabricated. These have been disappointing in terms of demonstrated sensitivity. Several factors have limited the achievement of the sensitivity potential of the piezojunction phenomenon. First, junction yields were very low and many of the transducers fabricated began with less than ideal junction sensors. Secondly, the semiconductor processing facility in use was not state-of-the-art and the ideal junction geometry could not be achieved. Finally, other parts; e.g., the glass wafers, were not standard items and were hand-fabricated in a facility not adapted for working with glass. However, transducers were fabricated that detected absolute pressure changes of approximately one mm Hg and these had a built-in vacuum reference and a dynamic range of one atmosphere. There is little doubt that a state-of-the-art semiconductor processing facility with a glass-oriented technology can fabricate a similar transducer that realizes the promised sensitivity.

#### SECTION II

#### THEORETICAL CONSIDERATIONS - A SUMMARY

A complete theoretical discussion of the piezojunction phenomenon has been published by Wortman, et al., (Refs. 3-5). It has been summarized in reports on previous feasibility studies, and an extended summary is included in this section in the interest of completeness.

#### Energy Band Considerations

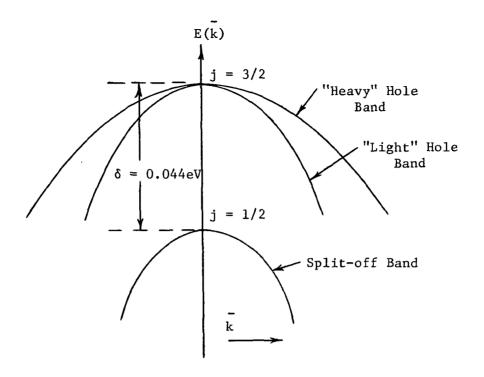

The electrical characteristics of semiconductors and the piezojunction phenomenon are conveniently described in terms of the energy band structure. Silicon, as is the case for all semiconductors, has a forbidden energy region (energy gap) separating the valence energy levels (valence band) and the conduction energy levels (conduction band). In momentum space (k-space), the maximum valence levels in silicon occur at k = (000) and the minimum conduction levels occur in the <100> directions. The maximum valence levels,  $\Gamma_{25}^{1}$ , are degenerate in energy with a separation resulting from the two angular momentum quantum numbers, j = 3/2 and j = 1/2. The j = 1/2 level is approximately 0.04 eV below the j = 3/2 and is neglected in the computations that follow in this section. The  $\Gamma_{25}^{\prime}$  level is also degenerate at k = (000) and is slightly split for  $k \neq (000)$  due to spin orbit coupling. The  $\Gamma_{25}^{\dagger}$  valence levels of silicon near k = (000) are illustrated for silicon in Fig. 1. The splitting of the  $\Gamma_{25}^{\prime}$  (j = 3/2) level for  $k \neq$  (000) causes the effective masses for the two levels to be different, and the upper and lower levels are frequently referred to as "heavy" holes and "light" holes, respectively.

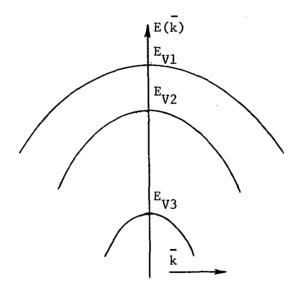

When stress is applied to the silicon crystal, the  $\Gamma'_{25}$  (j = 3/2) energy levels become non-degenerate as illustrated in Fig. 2.  $E_{V1}$  and  $E_{V2}$  are the  $\Gamma'_{25}$  (j = 3/2) "heavy" and "light" hole energy levels, and  $E_{V3}$  is the  $\Gamma'_{25}$  (j = 1/2) energy level. Since it is the width of the forbidden energy gap that is of interest, it is convenient to consider the change in the  $\Gamma'_{25}$  (j = 3/2) energy levels with strain. These are given by

$$\Delta E_{V1} = E_{V1} - E_{o} = D_{d}e + \{(\frac{2}{3}D_{u})^{2}(e_{1}^{2} + e_{2}^{2} + e_{3}^{2} - e_{1}e_{2} - e_{1}e_{3} - e_{2}e_{3}) + \frac{1}{3}(D_{u}^{\prime})^{2}(e_{4}^{2} + e_{5}^{2} + e_{6}^{2})\}^{1/2},$$

(1)

Figure 1. The Valence Bands of Silicon Near k = 0 (Ref. 5)

Figure 2. The Split Valence Bands of Silicon for a Compressional Stress (Ref. 5)

and

$$\Delta E_{V2} = E_{V2} - E_{o} = D_{d}e - \{(\frac{2}{3}D_{u})^{2}(e_{1}^{2} + e_{2}^{2} + e_{3}^{2} - e_{1}e_{2} - e_{1}e_{3} - e_{2}e_{3}) + \frac{1}{3}(D_{u}^{\dagger})^{2}(e_{4}^{2} + e_{5}^{2} + e_{6}^{2})\}^{1/2},$$

(2)

where the D's are the deformation potential coefficients, and the  $e_i$ 's are the components of strain (see Appendix C). More specifically,  $D_d$  is the energy level shift per unit dilation of the  $\Gamma'_{25}$  (j = 3/2) band edge,  $D_u$  is proportional to the splitting of the band edge induced by uniaxial shear strain along the [100] axis, and  $D_u$  is proportional to the band edge splitting induced by uniaxial shear strain along the [111] axis.  $E_0$  is the unstrained  $\Gamma'_{25}$  (j = 3/2) energy level (Ref. 3).

Strain also induces changes in the conduction bands, and changes in the conduction band minima are of equal importance with changes in the valence band maximum. Silicon has six conduction band minima located along the principal crystal axes. Since these minima change in pairs; i.e., since one cannot distinguish between the conduction band minima located along the [100] and  $[\bar{1}00]$  axes, only three conduction band minima need be considered,  $E_{C1}$ ,  $E_{C2}$  and  $E_{C3}$ . Changes in these conduction band minima in the stress region of interest are given by (Ref. 3)

$$\Delta E_{C1} = E_{d} e + E_{u} e_{1},$$

$$\Delta E_{C2} = E_{d} e + E_{u} e_{2},$$

$$\Delta E_{C3} = E_{d} e + E_{u} e_{3},$$

(3)

where the  $\Xi$ 's are the deformation potential coefficients, and the  $e_i$ 's are the engineering strain components along the crystal axes, (see Appendix C) and

$$e = e_1 + e_2 + e_3$$

(4)

Changes in the valence band and conduction band maxima and minima energy levels gives rise to a change in the carrier concentrations in the conduction band. In silicon, for example, the density of electrons associated with the six conduction band minima is given by

$$n = 2\left(\frac{2\pi kT}{h^2}\right)^{3/2} \left\{ m_{C1}^{3/2} \exp\left[-\left(\frac{E_{C1} - E_{F}}{kT}\right)\right] + m_{C2}^{3/2} \exp\left[-\left(\frac{E_{C2} - E_{F}}{kT}\right)\right] + m_{C3}^{3/2} \exp\left[-\left(\frac{E_{C3} - E_{F}}{kT}\right)\right] \right\},$$

(5)

where  $E_F$  = the Fermi energy level, and  $m_{Ci}$  = the effective electron masses associated with the energy minima. Equation (5) can be rewritten as

$$n = \frac{n}{3} \exp(\frac{\Delta E}{kT}) \left[ \exp(-\frac{\Delta E}{kT}) + \exp(-\frac{\Delta E}{kT}) + \exp(-\frac{\Delta E}{kT}) \right], \quad (6)$$

where n  $_{_{O}}$  = unstressed electron density, and  $\Delta E_{_{\rm F}}$  = change in the Fermi level. Similarly, the carrier concentration associated with the valence band maxima is given by

$$p = 2\left(\frac{2\pi kT}{h^2}\right)^{3/2} \left\{ m_{V1}^{3/2} \exp\left[-\left(\frac{E_F - E_{V1}}{kT}\right)\right] + m_{V2}^{3/2} \exp\left[-\left(\frac{E_F - E_{V2}}{kT}\right)\right] \right\}$$

(7)

where  $m_{Vi}$  = effective masses associated with the valence band maxima,  $E_{Vi}$ . In Eq. (7), the  $\Gamma_{25}'$  (j = 1/2) energy level has been neglected. If the small difference between  $m_{V1}$  and  $m_{V2}$  is also neglected, a good approximation for silicon, Eq. (7) can be written as

$$p = \frac{P_o}{2} \exp(-\frac{\Delta E_F}{kT}) \left[\exp(\frac{\Delta E_{V1}}{kT}) + \exp(\frac{\Delta E_{V2}}{kT})\right], \qquad (8)$$

where  $p_0$  = the hole concentration with no stress.

The  $\exp(-\frac{\Delta E}{kT})$  terms in Eqs. (6) and (8) can be evaluated by setting the majority carrier density equal to the impurity density and assuming the ionization energy to be independent of stress. Consequently, the hole density remains constant in p-type material, for example, and

$$\exp\left(\frac{\Delta E}{kT}\right) = \frac{1}{2} \left[ \exp\left(\frac{\Delta E}{kT}\right) + \exp\left(\frac{\Delta E}{kT}\right) \right] . \tag{9}$$

Substituting Eq. (9) into (6) yields the ratio of stressed to unstressed minority carrier density,  $\gamma_{ij}(e)$ , in the p-type material as (Ref. 3)

$$\gamma_{v}(e) = \frac{n}{n_{po}} = \frac{1}{6} \left[ \exp(\frac{\Delta E_{v1}}{kT}) + \exp(\frac{\Delta E_{v2}}{kT}) \right] \left[ \exp(-\frac{\Delta E_{c1}}{kT}) + \exp(-\frac{\Delta E_{c2}}{kT}) + \exp(-\frac{\Delta E_{c2}}{kT}) \right]$$

$$+ \exp(-\frac{\Delta E_{c3}}{kT}) \right] .$$

(10)

Following a similar procedure for n-type material, it can be shown that (Ref. 3)

$$\frac{p_n}{p_{no}} = \frac{n}{p_{po}} = \gamma_{v}(e) . \qquad (11)$$

#### Deformation Potential Coefficients

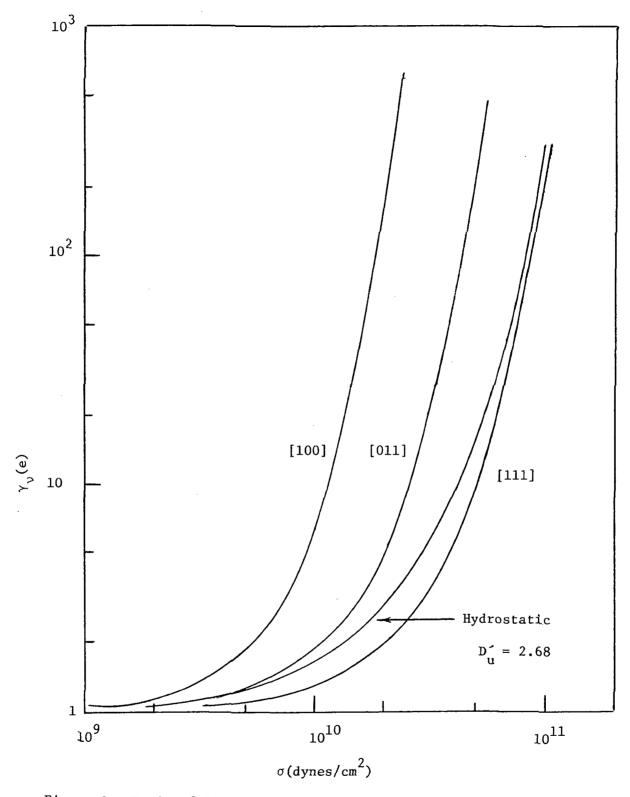

The deformation potential coefficients have been evaluated both theoretically and experimentally, and the values used herein are underlined in Table I. It is possible that the deformation potential coefficients change with doping. In particular, the value  $D_u^{\dagger}$  is uncertain, however, the value of 2.68 eV/unit dilation appears to be the better value from experimental observations. The function  $\gamma_{\nu}(e)$  has been calculated using the above value of  $D_u^{\dagger}$ .

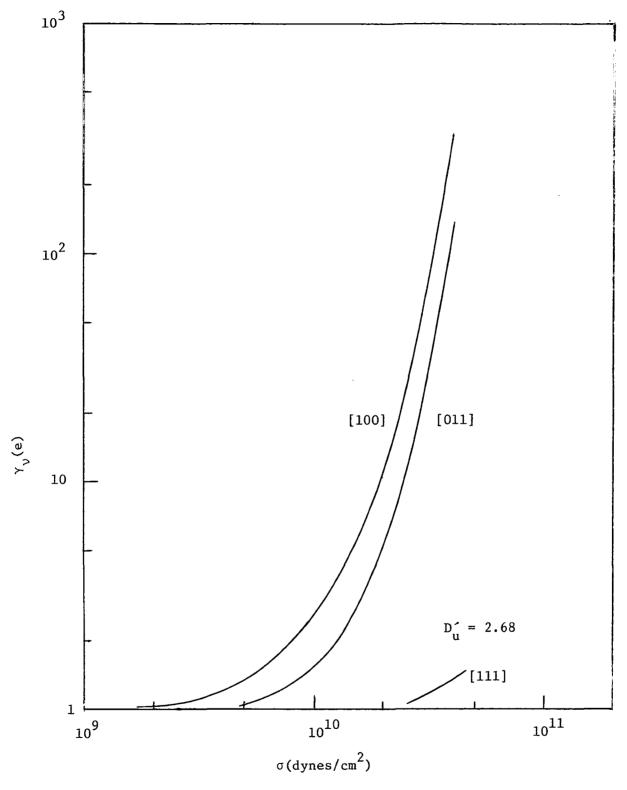

# Calculated Values of $\gamma_{\nu}(e)$

The ratio of stressed to unstressed minority carrier density,  $\gamma_{\nu}(e)$ , has been calculated for hydrostatic and uniaxial [100], [011] and [111] tensional and compressional stresses. Figures 3 and 4 are plots of  $\gamma_{\nu}(e)$  as a function of compressional and tensional stresses, respectively, for  $D'_{\nu}=2.68$ . For a hydrostatic and uniaxial [100] stress,  $\gamma_{\nu}(e)$  is independent of  $D'_{\nu}$ . The exponential increase in  $\gamma_{\nu}(e)$  with stress in a basic characteristic of the piezojunction phenomenon. It is evident from Fig. 3  $\gamma_{\nu}(e)$  is most sensitive to a [100] compressional stress, and least sensitive to a [111] tensional stress. It is also evident that the piezojunction effect is significant at stress levels greater than  $10^9$  dynes/cm²; i.e., order-of-magnitude changes occur in  $\gamma_{\nu}(e)$  with changes in stress. The mechanical strength of silicon limits the stress that can be applied to a p-n junction in silicon and is the basic limination to changes that can be achieved in  $\gamma_{\nu}(e)$ . The fracture strength

Table I. (Ref. 5)

Deformation Potential Coefficients (eV/unit dilation) for Si. (Kleinman's theoretical values are shown in brackets. Values used in this investigation are underlined.)

| Coefficient                           | Si                                         |

|---------------------------------------|--------------------------------------------|

| $^{ m D}{ m d}$                       | [- <u>2.09</u> ]                           |

| $^{\mathrm{D}}\mathrm{u}$             | 2.04, a [3.74]                             |

| D't                                   | 2.68, a 10, e [4.23]                       |

| <sup>E</sup> d .                      | [- 4.99]                                   |

| $\Xi_{\mathbf{u}}$                    | 11, <sup>b</sup> 8.3, <sup>c</sup> [+ 9.6] |

| $D_{d} - (E_{d} + \frac{1}{3} E_{u})$ | - <u>1.44</u> , <sup>d</sup> [- 0.30]      |

a J. C. Hensel and G. Feher, Phys. Rev. <u>129</u>, 1041 (1963).

b D. K. Wilson and G. Feher, Phys. Rev. <u>124</u>, 1968 (1961).

c J. E. Aubrey, W. Gubler, T. Henningsen, and S. H. Keonig, Phys. Rev. <u>130</u>, 1667 (1963).

d W. Paul, J. Phys. Chem. Solids 8, 196 (1959).

e J. J. Wortman, Private Communication.

Figure 3. Ratio of Stressed to Unstressed Minority Carrier Density for a Hydrostatic, [100], [011] and [111] Uniaxial, Compressional Stress

Figure 4. Ratio of Stressed to Unstressed Minority Carrier Density for a [100], [011] and [111] Uniaxial, Tensional Stress

of silicon varies from sample to sample and depends to a large extent on the surface conditions (Ref. 7). However, order of magnitude changes have been experimentally observed in  $\gamma_{ij}(e)$ .

Effect of Stress on p-n Junction Characteristics

The effect of stress on p-n junction characteristics has been described by Wortman, et al., in terms of  $\gamma_{\nu}(e)$ . Changes in other parameters are assumed to be negligible as compared with the exponential change of  $\gamma_{\nu}(e)$  with stress above  $10^9$  dynes/cm<sup>2</sup>. This model also neglects the contribution of surface generation-recombination currents.

The total current (I) in p-n junctions is the sum of the ideal current ( $I_I$ ) and the generation-recombination currents ( $I_R$ ).

$$I = I_{T} + I_{R} . \tag{12}$$

For forward biased conditions, the bulk generation-recombination current is given approximately by

$$I_{R} = \frac{a \gamma_{V}(e) [\exp(qV/kT) - 1]}{1 + b \sqrt{\gamma_{V}}(e) \exp(qV/kT)},$$

(13)

where a and b are device constants. The ideal current is given by

$$I_{T} \approx c \gamma_{V}(e) \left[ \exp(qV/kT) - 1 \right], \qquad (14)$$

where c is a device constant. Equation (12) becomes (Ref. 4)

$$I = \frac{a \gamma_{v}(e) [\exp(qV/kT) - 1]}{1 + b\sqrt{\gamma_{v}}(e) \exp(qV/2kT)} + c \gamma_{v}(e) [\exp(qV/kT) - 1] . (15)$$

It is of interest here to consider the p-n junction current under different bias conditions. For large forward biases, Eq. (15) is approximately

$$I \simeq \frac{a}{b} \left( \gamma_{\nu}(e) \right)^{1/2} \exp(qV/2kT) + c \gamma_{\nu}(e) \exp(qV/kT) . \tag{16}$$

It is significant that for large forward biases; i.e., V > 0.3 volts, p-n junction current will have a larger dependence on the ideal component of current than the generation-recombination component. For reverse-bias conditions the ideal current is much less than the generation-recombination current. The effects of stress on the generation-recombination current in the reverse-biased mode is not easily described. Experimentally, reverse-biased p-n junctions have been observed to be very sensitive to stress and relatively independent of voltage for voltages less than the breakdown voltage. The forward-biased characteristics, as shown in Eq. (16) are dependent upon  $\gamma_{_{\rm N}}(e)$  and the applied voltage.

Hauser and Wortman (Ref. 5) have also investigated the effect of mechanical stress on the breakdown voltage of p-n junctions and, in the case of silicon, found the change in breakdown voltage to be

$$\frac{\Delta V}{V_B} \approx - (10^{-12} \text{ cm}^2/\text{dyne}) \sigma \tag{17}$$

where  $\sigma$  is the applied stress,  $\Delta V$  is the change in breakdown voltage and  $V_B$  is the unstressed breakdown voltage. The change in breakdown voltage is also independent of orientation. Since the breakdown voltage is a linear function of stress whereas the junction current at a voltage less than breakdown voltage is an exponential function of stress, the latter mode of operation is potentially a more sensitive transducing mechanism. However, if voltage is held constant across the device in the breakdown region, current can change greatly with small voltage changes. Breakdown voltage is also less sensitive to temperature changes than junction currents, and this mode of operation may have advantages in some applications.

The effects of stress on more complex silicon p-n junction structures is also of interest. Wortman, et al., has investigated the effects of stress upon transistor characteristics and p-n-p-n switches (Ref. 3). If both sides of the emitter-base junction of a transistor are stressed, the base and collector currents are changed several orders of magnitude for small changes in stress above  $10^{10}$  dynes/cm<sup>2</sup>. The current gain will not be affected if both junctions are similarly stressed. If only the emitter side of the junction is stressed (e<sub>e</sub> >> e<sub>b</sub>) the base current increases orders of magnitude with stress while the collector current remains unchanged. Consequently, gain is reduced by stressing the emitter side of the base-emitter junction. If only the base side of the junction is stressed (e<sub>e</sub> << e<sub>b</sub>), the base and collector currents remain approximately the same.

## Calculations of Sensitivity for Mesa Devices

It will be assumed that only forward-biased diodes will be used. This assumption eliminates considerations of the unknown behavior of reverse-biased p-n junctions. From a fabrication point of view it is very difficult to construct devices for sensor applications in a predict able and consistent manner whose reverse I-V characteristics are reproducible. This is a direct result of a dominating generationrecombination current in the reverse-biased mode for silicon devices. For discussion purposes, a second assumption will also be made which is only diodes whose forward-biased I-V characteristics are of the "ideal" or Shockley type will be considered; i.e., no generation-recombination current components ( $I_R \ll I_T$ ). In practice this will require forwardbiased voltages on the order of 0.3 volts or greater. Imposing this requirement will insure that only devices with known and well-understood characteristics are used. It automatically will eliminate hysteresis effects which could result from trapping effects and hence influence the piezojunction effects. That is, the characteristics will not be a function of generation-recombination centers in the material which could be influenced by stress.

Using the above assumptions, the simple piezojunction theory based on deformation potential theory is applicable. For the simple geometry in which the total stressed area is the total junction area, A, and large forward bias, the current-voltage characteristics are related to stress through  $\hat{\gamma}$ ,

$$I = I_o \gamma(\sigma) e^{qV/kT} , \qquad (18)$$

where the assumption has been made that  $e^{qV/kT} >> 1$ .

In the case where only a part of the junction is stressed, A<sub>s</sub>, the current can be accounted for by considering two parallel components

$$I = I_0 \left( \frac{A_s}{A} \gamma(\sigma) + \frac{A - A_s}{A} \right) e^{qV/kT}$$

Equation (19) assumes that both the stressed and unstressed portions of the junction have equal voltages applied. A second assumption which is implied in Eq. (19) is that the stressed area is independent of the applied stress; i.e.,  $A_g \neq f(\sigma)$ .

For the case of a flat top mesa, Eq. (19) will hold. Figure 5 shows plots of  $\Delta I/I$  as a function of stress for a [100] oriented sample with various  $A_{\rm g}/A$  ratios.

Fig. 5. /1/10 Versus Stress ( $\sigma$ ) for Various Ratios of Stress Area To Total Area ( $A_s/A$ ).

Spreading resistance problem. - The effects of spreading resistance, R, in p-n junctions can be accounted for by considering the resistance to be in series with the diode. This assumption allows the linear summation of the voltages; i.e.,

$$v_a = v + v_R , \qquad (20)$$

where V is the diode voltage,  $V_R$  is the voltage dropped in the diode other than that across the junction, and  $V_a$  is the applied voltage. The current equation for the diode is, therefore, modified as follows

$$q(V_a - IR)/kT$$

$I = I_0 (e^{a} - 1)$ , (21)

where  $V_R = IR$ .

As shown by Eq. (21), the spreading resistance is important when IR is comparable to the applied voltage. If the junction is operated at a current level such that the spreading resistance is important it will reduce the stress sensitivity of a junction if the junction is operated with a fixed forward voltage. The spreading resistance of a junction can be calculated using the resistivity expression R =  $\rho \ell/A$ , where  $\ell$  and A are effective values. The current through the unstressed part of the junction,  $I_{II}$ , is

$$I_{U} = I_{O} \left( \frac{A - A_{S}}{A} \right) \exp q(V_{a} - I_{U} \rho \ell / [A - A_{S}]) / kT$$

(22)

and that through the stressed part,  $I_s$ , is

$$I_{s} = I_{o} \frac{A_{s}}{A} \gamma(e) \exp q(V_{a} - I_{s} \rho \ell/A_{s}) kT . \qquad (23)$$

The total current is

$$I = I_{S} + I_{U} . (24)$$

As is easily seen by combining Eqs. (22) - (24), the current-voltage characteristics are very complex functions of stress. The problem is not as impossible to handle as it may at first appear. For example,  $I_{\overline{U}}$  is unaffected by stress and it can be easily estimated in a practical case by measuring  $I_{\overline{U}}$  and taking the ratio of  $A_{\overline{S}}/A$  at a bias level such that the spreading resistance is not important.

The spreading resistance in the unstressed case, R  $_{\rm o}$ , can be determined from an I-V plot. Once it is obtained one can estimate R  $_{\rm U}$  and R  $_{\rm S}$  by the following equations

$$R_{o} = \frac{\rho \ell}{A}$$

(25)

$$R_{U} = \frac{R_{o} A}{A - A_{s}}$$

(26)

$$R_{s} = \frac{R_{o} A}{A_{s}}$$

(27)

Figure 6 shows the effect of spreading resistance on the V-I characteristics of a typical laboratory junction with various values of spreading resistance. As shown in Fig. 6, one would be limited to current magnitudes less than  $10^{-5}$  amperes if the spreading resistance is unavoidable. The effect of a 50 ohm spreading resistance in the unstressed case is shown in Fig. 7 for a  $\gamma(e)$  of  $10^3$ . Note the various area effects. For the A<sub>S</sub>/A ratio of 0.1 a practical current limit of  $10^{-5}$  would be the upper value for a sensor current if spreading resistance effects were to be avoided.

Fig. 6. An Illustration of the Effects of Spreading Resistance.

Fig. 7. The Combined Effects of Spreading Resistance and Stressed Area to Total Area Ratios.

#### SECTION III

#### TRANSDUCER DESIGN CONSIDERATIONS

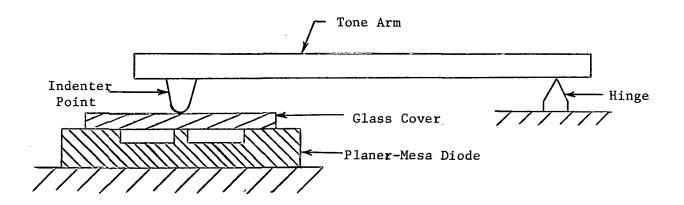

#### Junction Element

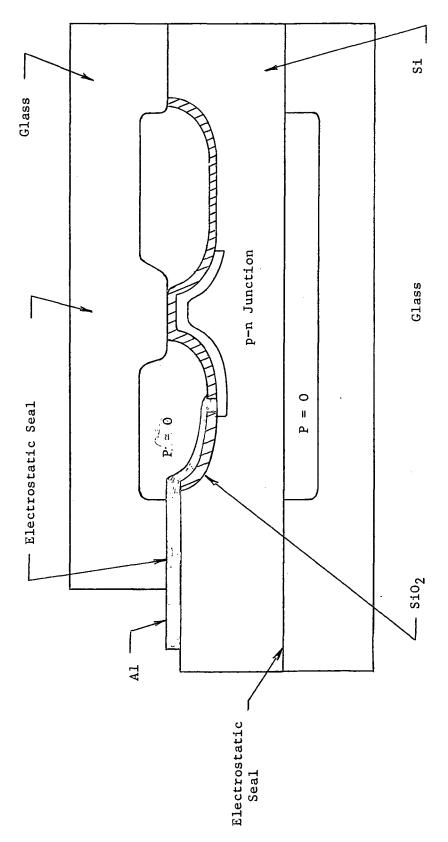

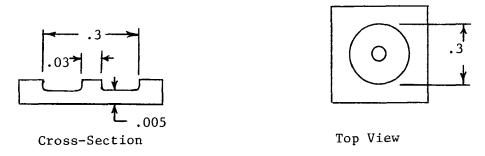

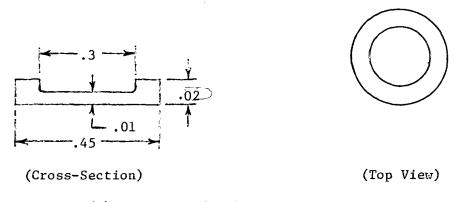

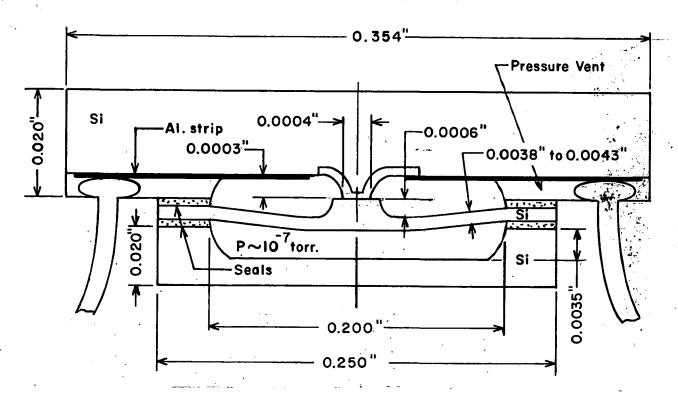

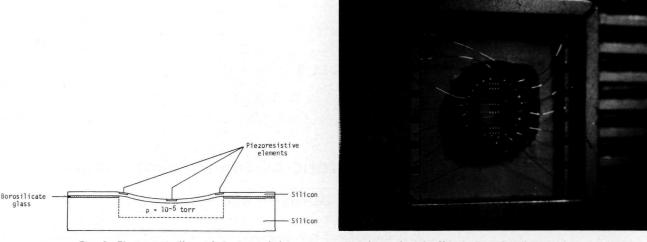

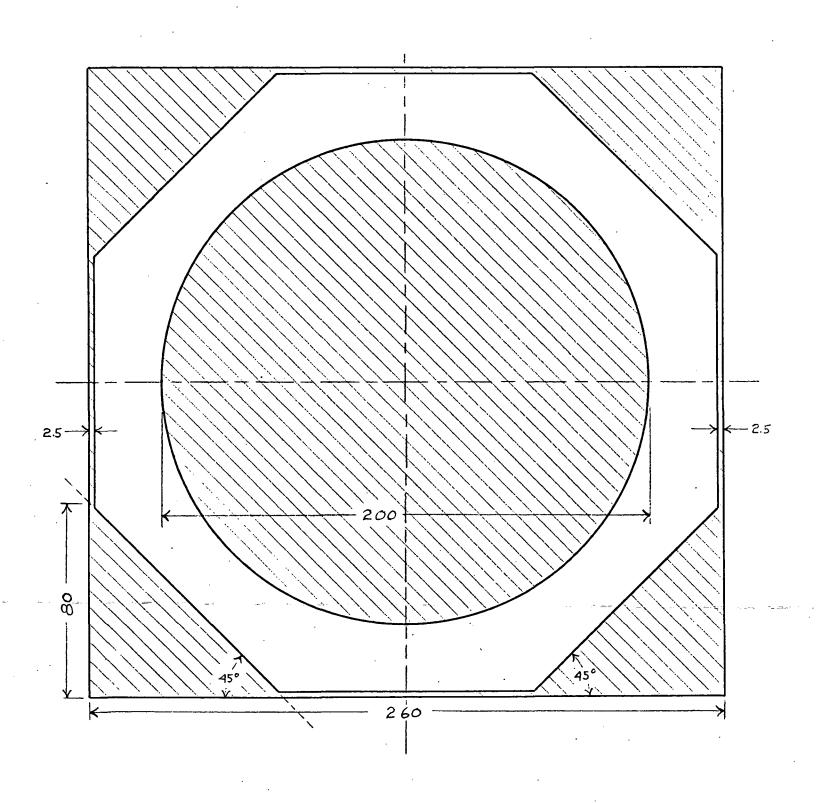

A practical pressure transducer based on the piezojunction effect will be heavily dependent on the solid-state semiconductor technology. The sensing junction configuration, geometry, dimensions and electrical properties are all limited to the state-of-the-art semiconductor processes. Within this technology and a knowledge of the theory and experimental data on the piezojunction effect, a mechanical system must be devised to utilize the effect in a practical manner. An evolutionary process has lead to a mechanical configuration which utilizes a planar-mesa diode fabricated on a silicon diaphragm as the sensor element. A glass wafer containing a cavity for a vacuum reference has evolved as the pressure element on one side of the silicon diaphragm, and a glass pressure plate is used on the opposite of the vacuum to apply stress to the sensing junction. Figure 8 is a sketch of this basic system.

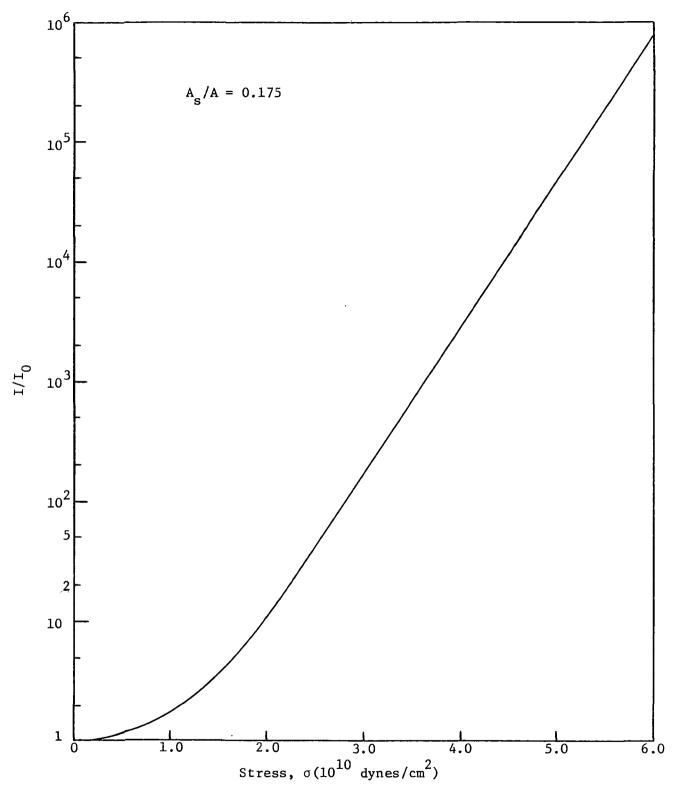

Based on the semiconductor technology, which is discussed in Sect. IV of this report, it was estimated that the smallest mesa area which could be reproducibly fabricated in the RTI laboratory was on the order of 1/4 square mils. The smallest total diode area which would not cause the junction to fall on the side of the mesa and would allow for contacts to the junction was on the order of 1.25 square mils. Based on these numbers, a stressed to unstressed area ratio of 0.175 was selected as a practical limit. It is, of course, very desirable to increase this ratio as much as possible for reasons discussed in Sect. II. Using the above ratio value, a stress magnitude is required which will change the current through the stressed area by a factor of approximately ten before any significant change is observed in the total junction current. Figure 9 is a theoretical sketch of I/I<sub>O</sub> as

as a function of stress for the stressed area to total area ratio  $(\frac{s}{A})$  of 0.175. Note the straight line in Fig. 9 above 2 × 10 dynes/cm<sup>2</sup>. The task is to design a transducer which utilizes this sensitivity in a practical configuration to measure the desired pressure.

## Capsule Design

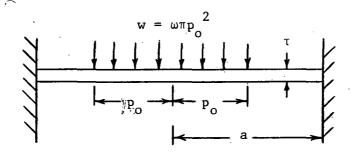

Analysis of the Design. - The following is a discussion of the design of the capsule diode illustrated in Fig. 8. To begin, consider a silicon diaphragm with fixed edges and with a uniform load applied as shown in Fig. 10. The deflection y, of the center of the diaphragm is given by

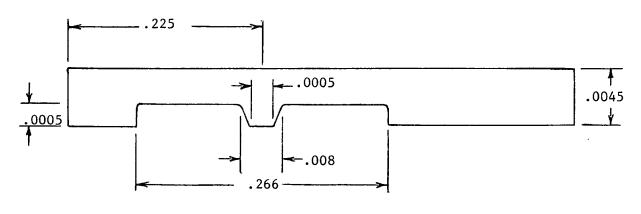

Silicon Diaphram Dimensions (all dimensions in inches)

Figure 8. An Illustration of the Capsule Diode

Fig. 9. I/I $_0$  Versus Stress for an  $\rm A_s/A$  Ratio of 0.175.

$$y = \frac{-3W(m^2 - 1)}{16\pi E^2 m^2 t^3} \left[ 4a^2 - 4r_0^2 \log \frac{a}{r_0} - 3r_0^2 \right]$$

(28)

where m is the reciprocal of Poisson's ratio and E is Young's modulus (Ref 8). For small values of  $r_{\rm o}$  such that the load is a concentrated load, the deflection is

$$y = \frac{-3W(m^2 - 1)a^2}{4\pi E m^2 t^3} . (29)$$

These equations are good only for small deflections; i.e., no ballooning. Using Eq. (28) and Eq. (29) and the principle of superposition, it can be shown that if the center of the diaphragm is held fixed by a support on one side and a uniform load on the other side, the center support will carry 1/5 of the total load. The remaining 4/5 of the uniform load will be carried by the fixed edges of the diaphragm.

$\omega = uniform load (force/area)$

Fig. 10. A Fixed Diaphragm, Uniformly Loaded.

Assume the silicon diaphragm of Fig. 10 to have the dimensions of the diaphragm in Fig. 8, i.e., a thickness (t) of 5 mils and a diameter of 270 mils. An atmosphere of pressure would cause a deflection of 13 mils. (This value was calculated using a value of 2.17  $\times$  10  $^{10}$  1b/in for Young's modulus and 0.25 for Poisson's ratio.) If the silicon diaphragm has a mesa supported by a fixed post such as the port-side glass wafer of Fig. 8, the silicon mesa would experience a force of 0.21 1b or 9.3  $\times$  10 dynes with one atmosphere of pressure applied. If the silicon mesa has an area of 1/4 square mil, a force of 9.3  $\times$  10 dynes will yield a stress of 5.8  $\times$  10 dynes/cm².

Consider next the complete capsule diode of Fig. 8. If the glass post is caused to contact the silicon mesa when the pressure is one atmosphere, the mesa would be stressed to  $5.8\times10^{10}~\rm dynes/cm^2$  when the pressure was zero. At some pressure between an atmosphere and zero, the diode would be stressed at  $2 \times 10^{10}$  dynes/cm<sup>2</sup>, for example. (This value was selected from the linear portion of Fig. 9.) The lower the pressure at which this value of stress occurs, the greater will be the sensitivity of the capsule diode at low pressures. A worst-case condition could be for a stress of  $2 \times 10^{10}$  dynes/cm<sup>2</sup> to correspond to an atmosphere of pressure.

Referring again to the capsule diode structure of Fig. 8, the stress applied to the diode can be expressed as

$$\sigma = C_1 - C_2 P \tag{30}$$

where  $C_1$  and  $C_2$  are constants and P is the applied pressure. Assuming the worst-case conditions of the preceeding paragraphs; when  $\mbox{\ensuremath{P}}$  is zero,  $\sigma$  is 5.8  $\times$   $10^{10}$  dynes/cm², and when P is 760 mm Hg,  $\sigma$  is  $2 \times 10^{10}$  dynes/cm<sup>2</sup>. It follows that  $C_1$  is  $5.8 \times 10^{10}$  dynes/cm<sup>2</sup> and  $C_2$  is 5 × 10<sup>7</sup> dynes/cm<sup>2</sup>/mm Hg. Equation (30) becomes

$$\sigma = 5.8 \times 10^{10} \text{ dynes/cm}^2 - 5 \times 10^7 \text{ dynes/cm}^2/\text{mm Hg}$$

(31)

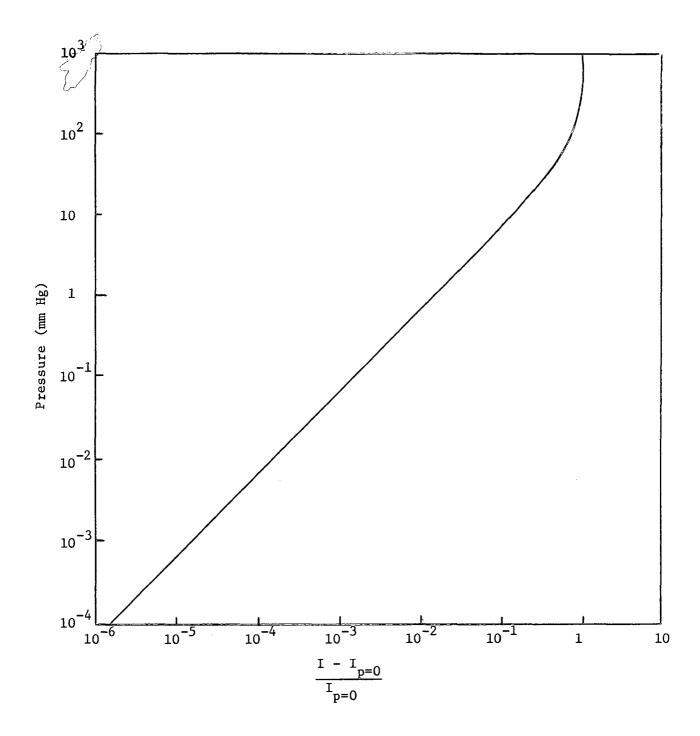

Combining Eq. (31) with the curve in Fig. 9 (or with Eq. (19)), the following expression is obtained for the current as a function of pressure

$$I/I_0 \approx 8.8 \times 10^5 \text{ exp } (-1.5 \times 10^{-2} \text{ P/Torr})$$

(32)

Figure 11 is a plot of Eq. (32) in which  $I/I_0$  at P=0 has been chosen as the normalizing factor. Note that the relative change in current per unit pressure is

$$\frac{\Delta I}{I} / \Delta P \simeq 1.5 \times 10^{-2} / \text{Torr} . \tag{33}$$

A change in pressure of  $10^{-2}$  Torr would result in a relative current change of 1.5  $\times$  10<sup>-4</sup>. This small change would be difficult to detect.

If no mechanical bias were applied to the junction such that the stress was zero at 760 Torr, then

$$\frac{\Delta I}{I} / \Delta P \approx 2.2 \times 10^{-2} / \text{Torr} . \tag{34}$$

Fig. 11. Relative Change in Current Per Unit Pressure.

Another possibility is to fix the diaphragm system such that no pressure is applied to the junction until some reduced pressure level is reached such as 100 Torr. For this case

$$\sigma = 0$$

; P > 100 Torr

$\sigma = (6 \times 10^{10} - 6 \times 10^8 \text{ P/Torr}) \text{ d/cm}^2$ ; P < 100 Torr. (35)

This yields a significantly improved sensitivity as shown in Eq. (36).

$$\frac{\Delta I}{I} \simeq 1.7 \times 10^{-1}/Torr. \tag{36}$$

#### Performance Limits

The transducers fabricated during this program were disappointing in that sensitivity goals were not achieved and, of more significance, the transducers were not repeatable (See Sect. VI). A basic limit to performance was the poor quality of the planar-mesa diodes fabricated. Surface and/or generation-recombination currents were characteristic of most of the diodes, and excessive spreading resistance limited the diodes to undesirably low voltage biases. These limiting factors have been discussed previously. Others are discussed in the following paragraph.

Moving Diaphragm Problem. - The capsule diode configuration of Fig. 8 is theoretically stable with a unique value of force (stress) applied to the diode for a given pressure and initial bias value. It is a complex mechanical system, however, that apparently fails to provide adequate stability. It is difficult, for example, to obtain a smooth control of the initial stress with the screw adjustment, and simply touching the bias screw has a noticeable effect on the diode characteristics.

The complexity of the system is apparent if the various diaphragms are represented as springs. The resulting system consists of three seried springs, one end fixed (hopefully) by the position of the bias adjust screw and the other acted upon by a force proportional to pressure. It is suggested that subsequent designs eliminate some of this complexity. If the port-side glass cover could be clamped in a fixed position relative to the vacuum-side cover, for example, the system would be considerably less complex consisting of a single spring (diaphragm) and a force proportional to pressure. Since the initial stress-bias is not critical, one method would be to fix the position of the port-side glass with epoxy after the bias is set. A second method would contact a larger area of the port-side cover directly with the bias adjust screw. If the screw were fabricated from the ceramic material used to fabricate this housing, additional temperature stability would be gained (See Sect. V). After stressbiasing, the position of the screw could be fixed with epoxy.

#### SECTION IV

#### SEMICONDUCTOR PROCESSING

The processing philosophy followed during this investigation differs in detail from that of the predecessor contract, NAS1-7489, in that the silicon shape chosen for fabrication is more compatible with the standard processing methods of the highly developed planar silicon technology. Under the preceding program, the silicon was shaped into a needle-like rod and the p-n junction was fabricated on the tip of this needle. The chief problems of this approach were the difficulty in defining the region of the p-n junction on the tip of the needle and, once having defined the junction area, making contact to both sides of the junction. The present design configuration—the planar—mesa approach—is an attempt to retain the sensitivity of the needle configuration and, at the same time, simplify the fabrication over that required for the needle approach.

## Planar Mesa Technology

A brief history and background of the planar-mesa technology as well as an outline of its essential features are given in Ref. 9. The description given in Ref. 9 serves as a starting point for the development carried out under the present contract.

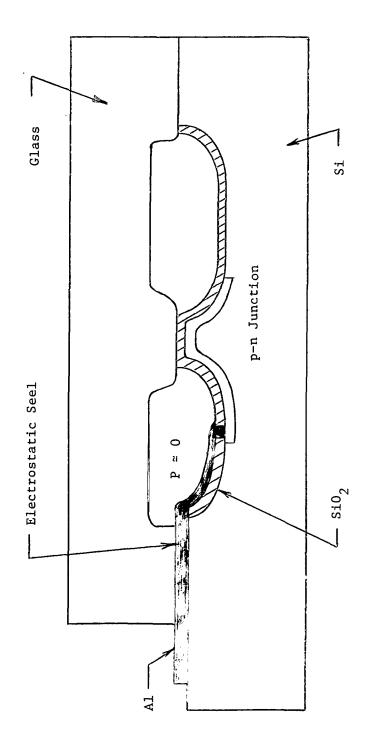

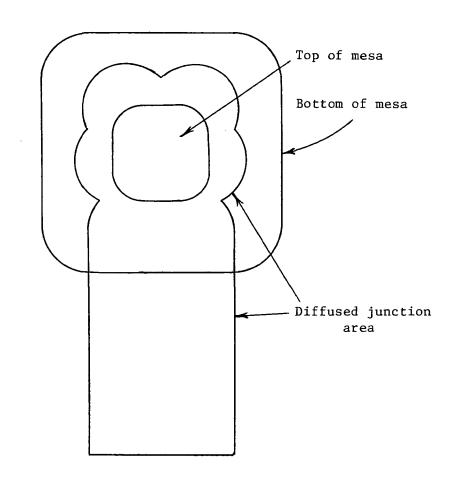

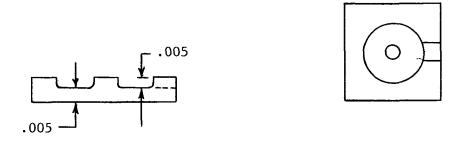

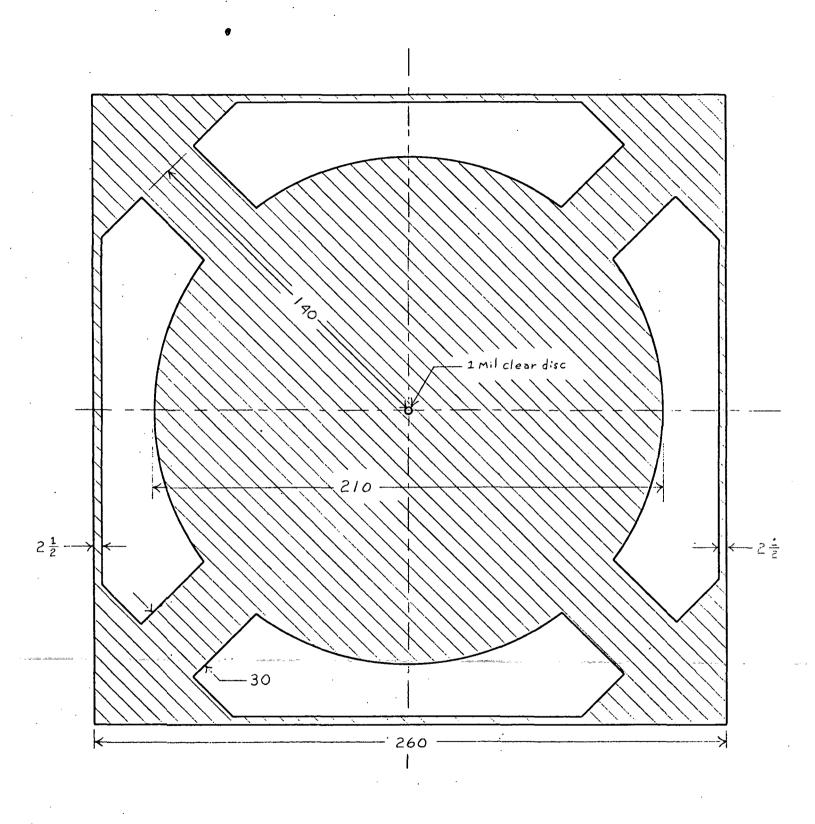

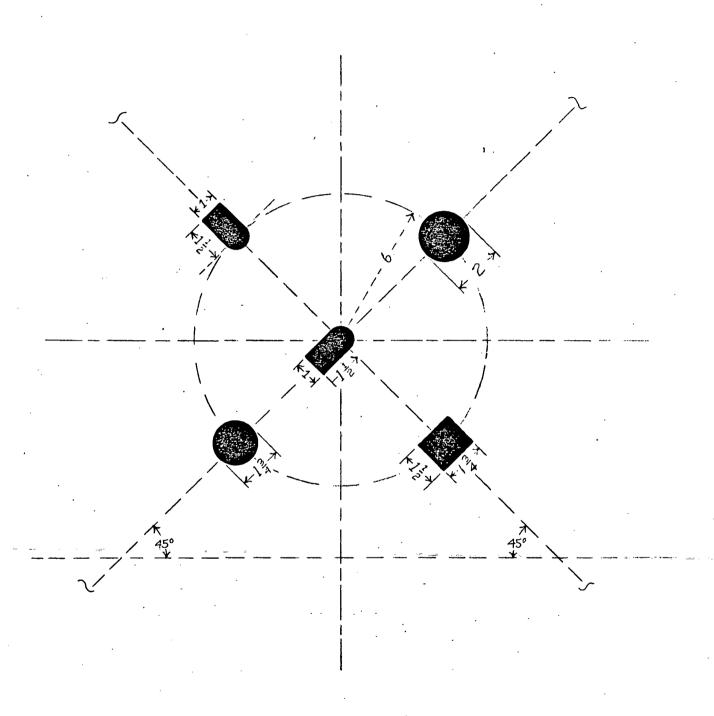

A cross section of the planar mesa in the capsule diode configuration is sketched in Fig. 12. This structure employs the planarmesa as the stress sensitive element and incoporates several other noteworthy features as well: 1) the use of the Mallory Electrostatic Sealing Process to effect a hermetic seal around the periphery of the silicon diaphragm. If the sealing operation is carried out in a vacuum, the cavity between the glass lid and the silicon chip containing the pressure sensitive mesa is effectively a zero reference of pressure.

2) the use of a single planar-mesa (as opposed to a previously employed tri-mesa configuration) which is loaded by a self-aligned mesa in the opposing glass lid. The matching edges of the silicon chip and the glass lid serve to align the glass mesa with the silicon mesa in a parallel, mechanically stable position.

The assembly of this structure is summarized as follows:

- 1) The planar-mesa diode is diffused and etched as described in Section  $V_{\star}$

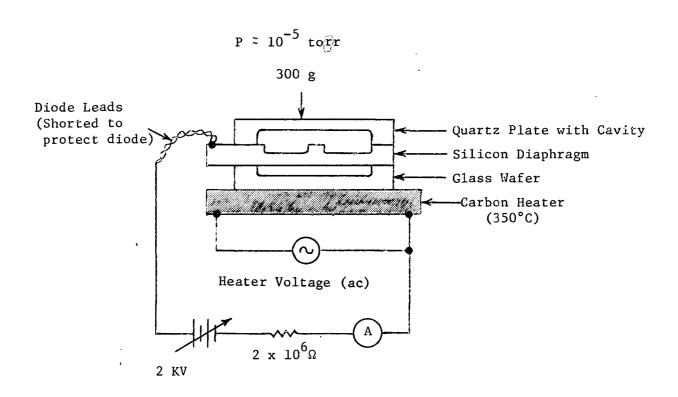

- 2) A vacuum-side glass wafer, etched to the general configuration illustrated in Fig. 12, is anodically sealed to the silicon diaphragm by the electrostatic sealing process described by Pomerantz and others at Mallory (Ref. 10). This sealing process is carried out inside a vacuum chamber at a pressure of approximately  $10^{-5}$  torr.

Figure 12. Final Capsule Diode Design

3) Finally, the port-side glass wafer is sealed to the diode-side of the silicon diaphragm. This seal is carried-out in an atmosphere of pressure and features a pressure-port into the cavity. In this design, the vacuum reference deflects the silicon diaphragm away from the glass mesa that serves as a stress-plate for the planar-mesa diode. At an atmosphere, for example, the diode may not be stressed or may not even contact the port-side wafer. As pressure decreases, the force on the diode increases.

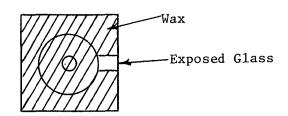

An earlier design is illustrated in Fig. 13. This design used a single glass wafer, required a single seal, and the diode was located in the vacuum reference cavity. This design required an anodic seal over a surface supporting the metallization stripes, and this was frequently troublesome. A more significant difficulty was that the diode was at maximum stress at ground level or one atmosphere of pressure.

# Fabrication Critique

While the schemes outlined above for fabricating and housing piezo-junction diodes are quite compatible with standard planar processing, various problems did arise during fabrication. These problems are discussed briefly in the following paragraphs.

Pinholes in the oxide. - The first major problem in fabrication arose when making a planar-mesa diode structure in which the dimensions were adjusted so that a single diode in the center of a 1-1/4 inch wafer constituted the silicon diaphragm. This large area silicon cavity permitted a large magnification of pressure differential, and hence, resulted in a more sensitive structure. However, this structure required contacts to the diode that extended from the center of the wafer to the periphery in order that gold wires could be bonded outside the sealed cavity. Using the standard photo-resist process resulted in an unacceptably high incidence of shorts between the expanded aluminum contact on top of the oxide and the underlying silicon.

The origin of these pinholes was in the photoresistive film itself. When etching the diffused region on the ohmic contact windows, contact holes in the photoresist film permitted the oxide to be etched away from other regions as well. When an oxide hole was formed in the oxide beneath the evaporated aluminum contact path, a weak spot or a low resistance path was introduced into the structure.

Various remedies were investigated to minimize these pinholes, such as the use of resists other than the standard KPR used initially. The most common resist used in the industry at present is Kodak Metal Etch Resist (KMER). However, resolution using this relatively thick resist is sometimes marginal for the dimensions involved in the structure discussed herein. This is particularly true when defining contact holes through the existing oxide in order to establish ohmic contact to the

Figure 13. Initial Capsule Design

various regions of silicon. After some trial and error experimentation, the resist chosen for this project fabrication was KPR-2. This is a relatively new resist only recently developed by Kodak. It is a compromise between the highest resolution and the best etch resistance and freedom from pinholes. The resist film itself is not as thick as KMER, but it is generally thicker than the KPR utilized initially.

While the KPR-2 approach did reduce the incidence of pinholes, it did not solve the problem in a practical sense. Many devices still failed because of shorts between the connecting aluminum leads and the substrate. The practice adapted then was to employ the photoresist to define the diode regions in the center of the wafer, and to coat the bulk of the remaining wafer with black wax prior to etching. Black wax is a commercial wax dissolved in toulene or trichlorethylene and painted on the surface with a brush or other applicator. Toward the end of the fabrication program, photoresist itself was utilized in the same manner; that is, after contact printing the desired region, a thick paint-on photoresist layer was applied over the bulk of the oxide to be masked during the etch. This technique essentially solved the pinhole problem although the complete elimination of this failure mode was not achieved. process, however, is highly unsatisfactory for a production line process and improvement is mandatory before serious manufacturing begins.

Aluminum opens at the silicon step. - A second problem that arose in fabrication was cracks in the aluminum intraconnecting contact path as it crossed over the etched diaphragm cavity boundary. This open appeared as a small, sharp crack in the aluminum film generally located at the top of the step. Two actions were taken to reduce this failure mode:

- 1) After standard mesa etching, the silicon wafer was given a short post etch with no mask in place in order to further round any corners existing as a result of the silicon etch. If the total etching time to form the desired mesa height was 60 seconds with the oxide mask in place, for example, the oxide was removed and the silicon wafer reimmersed in the silicon etch with no mask at all for another 8 seconds. During this post-etch, the sharp corners existing at the cavity edge were attacked more rapidly and hence tended to be rounded and present a less abrupt change in topography for supporting the aluminum film.

- 2) In the vicinity of the boundary between the etched cavity and the outer ledge, the aluminum stripe was covered with additional etch masking material after photoengraving but prior to etching. This additional masking was on the aluminum stripes only. Because of the step in the surface the thickness of the spun-on photoresist is less uniform and generally results in a thinner than normal coating at the

top of the step--the location at which cracks in the aluminum were observed to appear. The additional masking material prevented aluminum removal at the step during etching. These two actions significantly reduced aluminum strip failures.

Large surface components in the diode current-voltage characteristics. The most serious shortcoming in the diodes fabricated was large surface components of current in the current-voltage characteristic of the diodes. The source of these large surface components was never fully traced, but is presumed to be primarily a reflection of contamination during various processing steps, although the mask design probably contributed to the problem. Surface current components manifest themselves as nonideal currents, particularly at low values of forward bias. They are readily recognizable on plots of log-current versus voltage (log I-V) as departures from the ideal  $\frac{q}{kT}$  slope. Bulk generation-recombination components also contribute to departures from ideal behavior, but these components exhibit  $\frac{q}{2kT}$  characteristics. Surface components, particularly channels, are characterized by a log current dependence of  $\frac{q}{nkT}$  where n is greater than 2. The diodes fabricated exhibited both dependences and while the existence of a value of n> virtually guarantees that the diodes is dominated by its surface properties, the converse is not true. Low bias behavior of  $\frac{q}{2kT}$  does not guarantee that the source of the non-ideal current is bulk regeneration-recombination. Surface current components can also exhibit this voltage dependence.

Other evidence suggesting that the surface was dominating the electrical characteristics of the diodes fabricated was their susceptibility to relatively mild heat cycles in various ambients (such as that associated with the electrostatic sealing process, or with the sintering operation used to reduce the series resistance of ohmic contacts). These relatively low temperature processes modified the properties of the junction dramatically, strongly suggesting that the modifications seen are those due to surface components.

To eliminate surface components requires clean processing conditions. Contamination can be introduced from mishandling prior to receiving wafers, during any of the processing steps such as oxidation, diffusion and metallization or from handling during testing. One of the most successful methods for evaluating the cleanliness of a process is to grow an oxide in a given furnace and then subject MOS capacitors fabricated from the oxide to various bias-temperature stresses. A state-of-the-art, clean oxide can withstand 300°C under a field of 5 x  $10^5$  V/cm to  $10^6$  V/cm without exhibiting any noticeable change in its capacitance-voltage characteristic. Such tests carried out in the RTI laboratory have consistently revealed oxides inferior to the state-of-the-art.

A second cause of extraordinarily large surface components arises in the design of the capsule diode. In this design, the diffused area is narrower than the oxide mask used to etch the mesa. This disparity in relative sizes means that the junction intersects the surface of the silicon partway up the mesa side. This circumstance itself is not obviously objectionable, except that experience in printing the various photomasks using planar-mesa substrates shows that light reflection from the mesa walls during exposure causes non-uniformities in the regions printed. Consequently, the periphery of the diffused region is not the rectangular region designed into the masks, but a distorted cloverleaf geometry of extra long periphery such as illustrated in Fig. 14. This type of pattern greatly increases the surface component of current because of the increased periphery of the junction. In addition, the fact that the junction occurs well up the side of the mesa means that some of the stress loading the mesa also appears in this region. Consequently, any stress sensitivity of the surface component is reflected in the diode stress sensitivity characteristic. Surface components are notoriously uncontrollable and, in general, units exhibiting a large component of surface current were not processed further so that little stress testing of these surface components was carried out.

Correction of these two deficiencies—the one in processing cleanliness and contamination control; the other in mask design—are two recommended steps for improving the diode characteristics. Neither of these steps were taken during this program. In any continuing activity, modifications in procedures to eliminate both sources of surface currents should be a first order of priority.

Both p-on-n and n-on-p structures were investigated throughout the course of the program in an effort to improve the quality of the resulting diodes. Results were comparable with the two processes with the exception that yields were higher on using a p-type substrate with an n-diffusion. Additionally, this configuration, in principle, can be a one-diffusion process since the aluminum used to establish ohmic contact to the diffused region can also be used to establish ohmic contact to the substrate. When using the reverse configuration, an additional n+ diffusion must be carried out in order to create a region of n-type impurity sufficiently heavily doped so as to avoid forming a p-n junction when the aluminum is alloyed into the silicon.

The final procedures utilized in fabricating the diodes are described in Appendix B, and a detailed description of the mask-set is included in Appendix A.

# Summary

The major fabrication problem was an inability to eliminate surface components from the diode I-V characteristics. State-of-the-art fabrication

Figure 14. Uneven Etch of Junction Area Close to Top of Mesa.

can reasonably expect a two order-of-magnitude improvement over what was routinely observed at RTI. Other diode design features seemed adequate.

The present diode design is not necessarily optimum, but short-comings in design are overshadowed by fabrication problems at present.

## SECTION V

#### TRANSDUCER FABRICATION

# The Capsule Diode

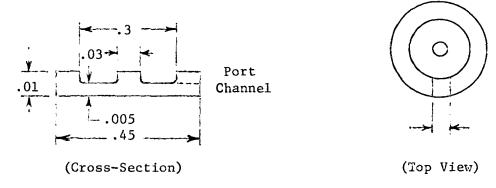

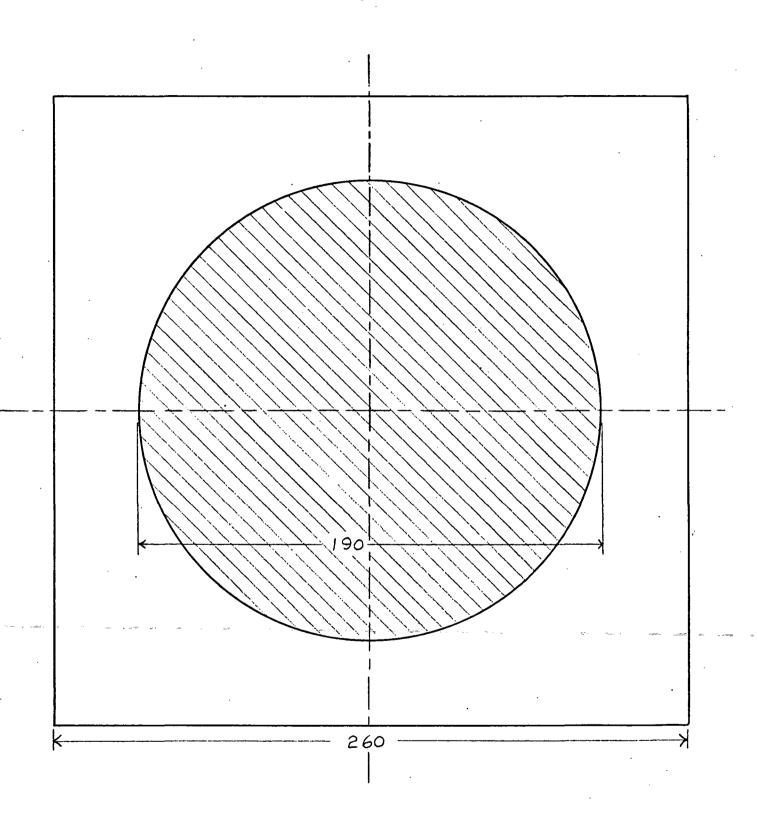

Component Fabrication. - A sketch of the capsule diode is shown in Fig. 8. The dimensions included correspond to a 2  $\times$  2 array of diodes on a single wafer. The diameter of the cavity etched in the silicon is 266 mils, and the cavity depth is approximately 3 mils. The processing steps for fabricating the planar-mesa diodes are described in Appendix B. Appendix A includes additional detail with a description of mask sets for both 2  $\times$  2 and 3  $\times$  3 diode arrays on a single water.

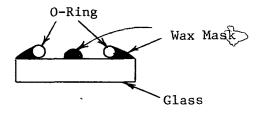

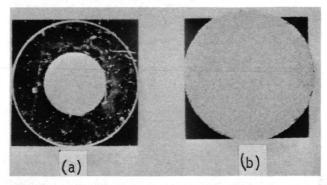

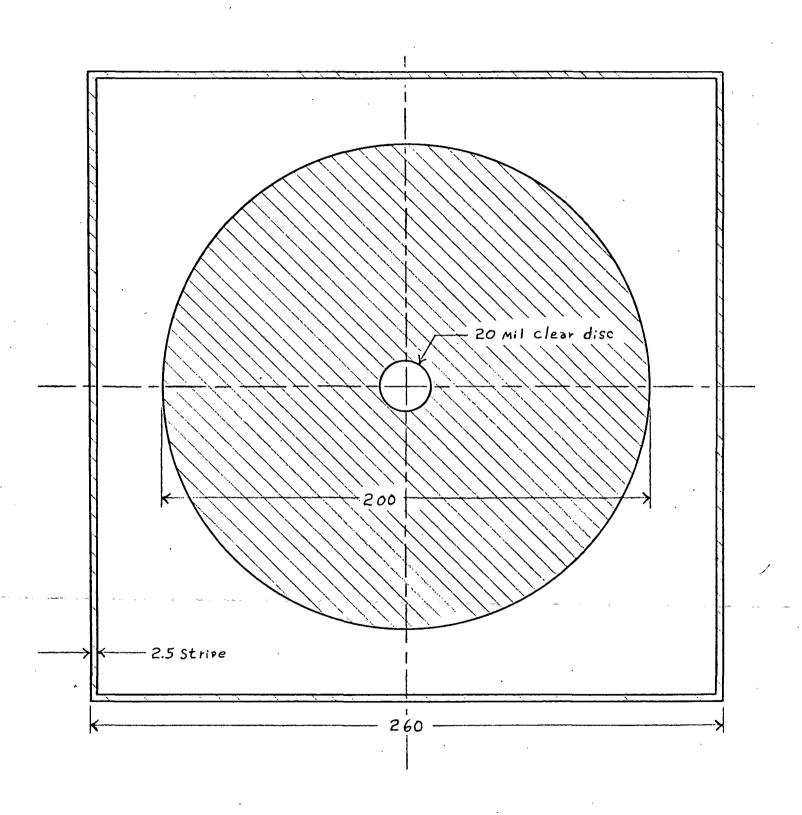

The port-side and vacuum-side glass wafers in Fig. 8 are a heat resistant, drawn glass. Cavities are formed in the glass wafers by etching in an agitated 50% HF solution. This process is illustrated in Fig. 15, The wafer thickness is fixed by mechanically lapping the backside and the corners are removed by grinding against a siliconcarbide surface. Finally, the center post is lapped with a 3' alumina compound as a precaution against sealing between the planar-mesa diode and opposing glass pressure-post during the anodic bonding procedure. The vacuum-side glass wafer is formed in a similar fashion; however, only a single etch-step is required for this less-complex structure. An illustration of the completed port-side and vacuum-side glass wafers is shown in Fig. 16.

The final component of the capsule diode is the silicon diaphragm containing an array of planar-mesa diodes. Semiconductor processing procedures for fabricating these diodes are described in Appendix B. Additional steps are as follows: (1) the 0.008" wafer is lapped, etched and mechanically polished on the back surface to yield a 0.004" diaphragm with a polished surface suitable for anodic bonding, (2) the wafer is scribed to separate the various diodes, and (3) masked with black wax and etched to yield the desired shape. One mil (.001") gold leads are T.C. bonded to complete the structure.

Component Assembly. The assembly of the glass wafers and planarmesa diodes into capsule diodes utilizes the anodic bonding procedure described by Pomerantz and others at Mallary (ref. 10). The initial step is to bond the vacuum-side wafer to the back of the silicon diaphragm in a vacuum so as to form a vacuum-reference cavity. Figure 17 illustrates this procedure. The quartz plate provides a means of applying the 300 g force at the silicon-glass interface, but does not take part in the bonding procedure. The anodic bonding occurs only between the silicon diaphragm and glass wafer. The dc current is initially constant at approximately 200 $\mu$ A until bonding occurs. After the bond forms, current decreases significantly. The heater circuit and dc circuit are then opened and the assembly allowed to return to room temperature.

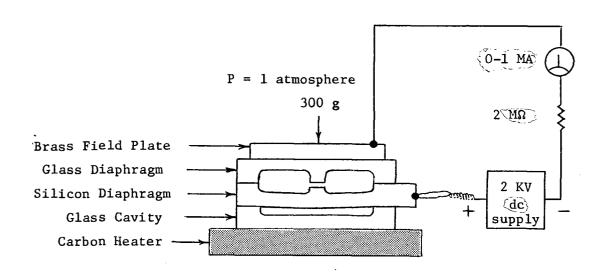

The port-side wafer is sealed to the silicon diaphragm in a similar process, but at an atmosphere of pressure. This apparatus is illustrated in Fig. 18. This seal completes the capsule diode structure illustrated in Fig. 8.

(a) Masking Technique for 1st Etch

(b) Port-side Glass Wafer after 1st Etch

(c) Masking for 2nd Etch (Pressure Port)

(d) Port-side Glass Wafer after 2nd Etch

Figure 15. An Illustration of the Glass Wafer Fabrication Technique (all dimensions in inches)

(a) Port-side Glass Wafer

(b) Vacuum-side Glass Wafer

Figure 16. An Illustration of the Completed Port-side and Vacuum-side Glass Wafer

(all dimensions in inches)

Figure 17. An Illustration of the Anodic Bonding Procedure.

Figure 18. Anodic Bonding Apparatus for the Port-Side Cover.

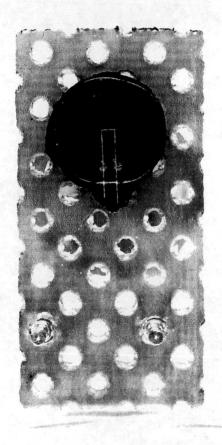

A photograph of the completed capsule diode is included in Fig. 19.

# Transducer Housing

In Fig. 20, the capsule diode is shown mounted in a housing that completes the transducer. The two piece, ceramic housing is bonded together with epoxy to securely hold the capsule diode around its perimeter as illustrated. It provides complete protection for the capsule diode, and contains a bias spring and bias adjust screw for setting an initial stress-bias on the transducer. The housing material is a commercially available ceramic that can be conventionally machined into precision parts. After machining, the ceramic material is hardened by firing in an oven.

Figure 19. Photograph of a Completed Capsule Diode

(all dimensions in inches)

Figure 20. An Illustration of the Complete Transducer.

# Page Intentionally Left Blank

#### SECTION VI

### EXPERIMENTAL RESULTS

#### Introduction

Diodes suitable for use as a piezojunction sensor have been discussed previously in this report. Some diode characteristics e.g., junction depths and surface carrier concentrations, are measured destructively for a given set of diffusion parameters and remain relatively unchanged. Physical geometries are fixed by the mask-set and, in the case of the planar mesa diode, the etching parameters. Other controlling parameters are the resistivity and orientation of the starting silicon. Every effort was made to optimize these various parameters. After the diodes were processed, their quality was judged on the basis of their easily observed I-V characteristics.

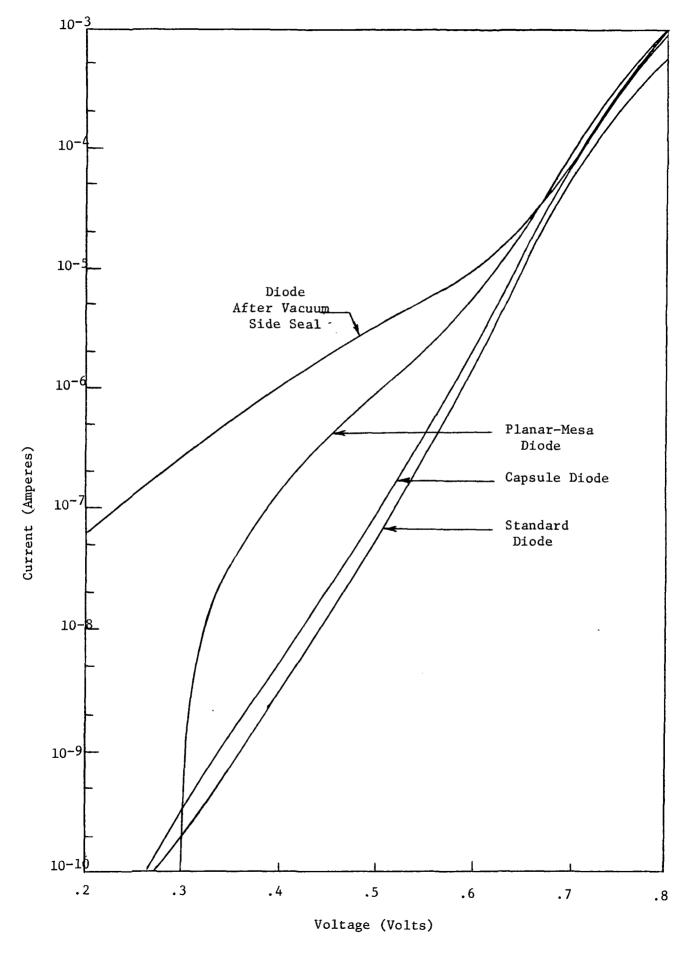

The ideal diode has been previously described. In summary, it is a diode whose log current versus voltage (log I-V) plot has a constant slope of q/kT extending over several orders-of-magnitude change in current (I). This ideal curve is included in Fig. 21 along with the curve of a good quality diode used as a standard during later stages of this investigation. The standard curve in Fig. 21 was frequently used for comparison purposes and is found on many of the diode and transducer curves included in this report.

The standard diode in Fig. 21 illustrates some of the limitations that are encountered in practical diodes. Its slope, while significantly better than the q/2kT indicative of generation-recombination currents, is clearly not the ideal q/kT. The slope decreases in the vicinity of 0.3 V as predicted by the diode equation. At higher current levels, e.g., current levels corresponding to greater than 0.7 V bias, the slope again decreases due to the presence of spreading (series) resistance in the silicon.

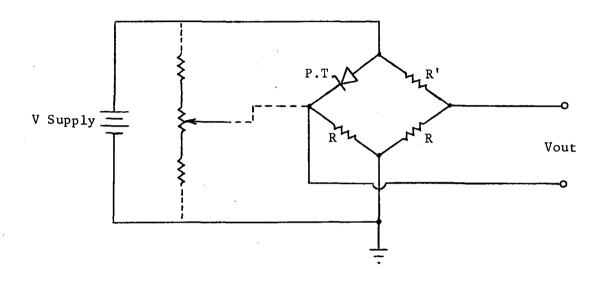

The standard diode, log I-V plot shown in Fig. 21 was generated in a log current plotter circuit. This plotter was used to generate most of the log I-V plots in this report. Its validity was established by comparing the standard diode curve with a point by point plot, and checked frequently by comparing the standard with this original data. The circuitry for this plotter is shown in Fig. 22 where the D is the diode to be measured.

# Discussion

Numerous silicon wafers were started through processing to become planar mesa diodes, capsule diodes, and finally pressure transducers. The yield of transducers was low. Most of the starting

Figure 21. Log I-V Characteristics of the Standard Diode and the Ideal q/kT Slope.

Figure 22. Log Current Versus Voltage Plotter Circuit

wafers were dropped after semiconductor processing, and others were lost during sealing operations. This section discusses the characteristics of some of the units that eventually yielded transducers.

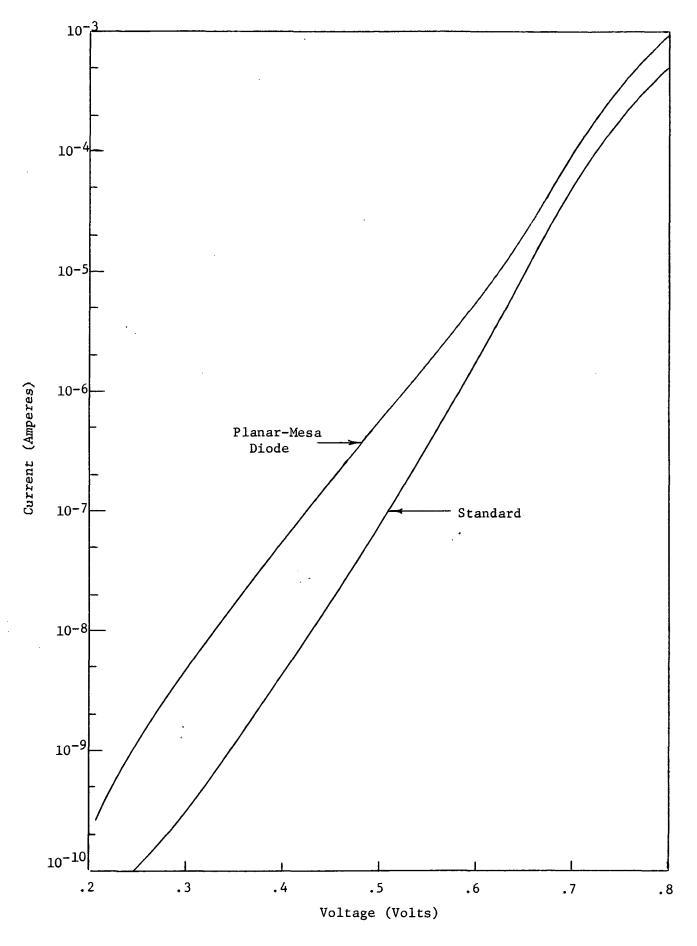

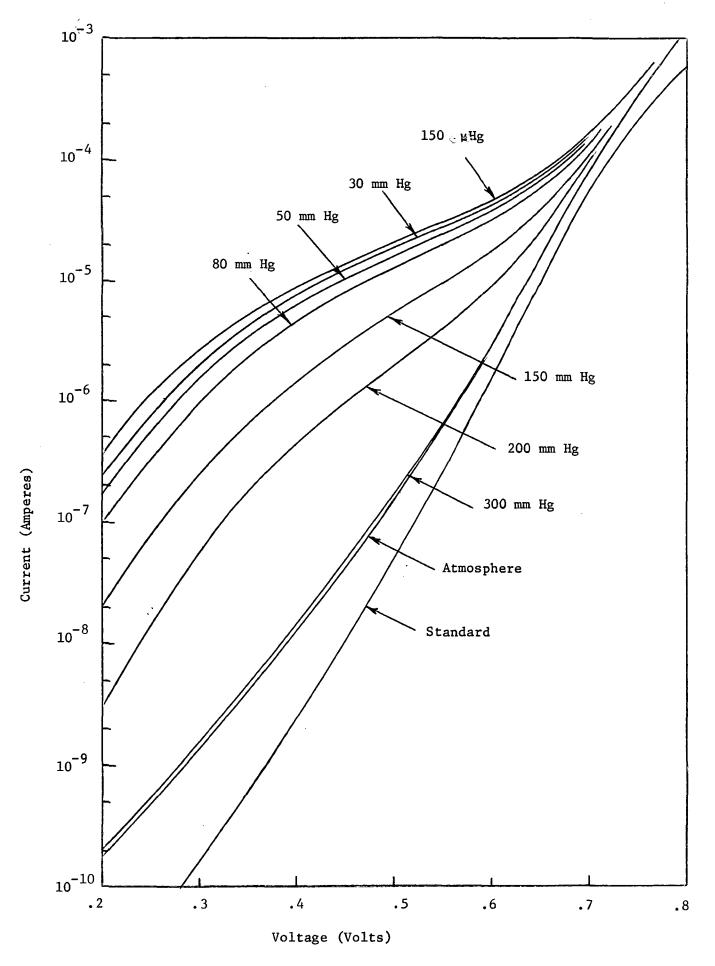

Some earlier planar-mesa diodes. - Some of the best slopes, i.e., approximately q/kT, were achieved early in the program as illustrated in Fig. 23. In Fig. 23, the log I-V characteristics of two planar-mesa diodes are compared with an ideal q/kT slope. At current levels below 10  $\mu$ A, these diodes were nearly ideal, but the series resistance effect is apparent above that current level. (Data points were not taken below  $10^{-8}$  A.) These earlier diodes were not compatible with the capsule diode design. The mask-set provided for one diode per wafer, and the etched diaphragm area was too large for the capsule concept.

The curves of Fig. 23 were generated from point by point data, but they are presented on the standard scale used throughout this report to enhance comparisons.

Figure 23. Log I-V Characteristics of Large Area, Planar-Mesa Diodes

#### Transducer No. 1

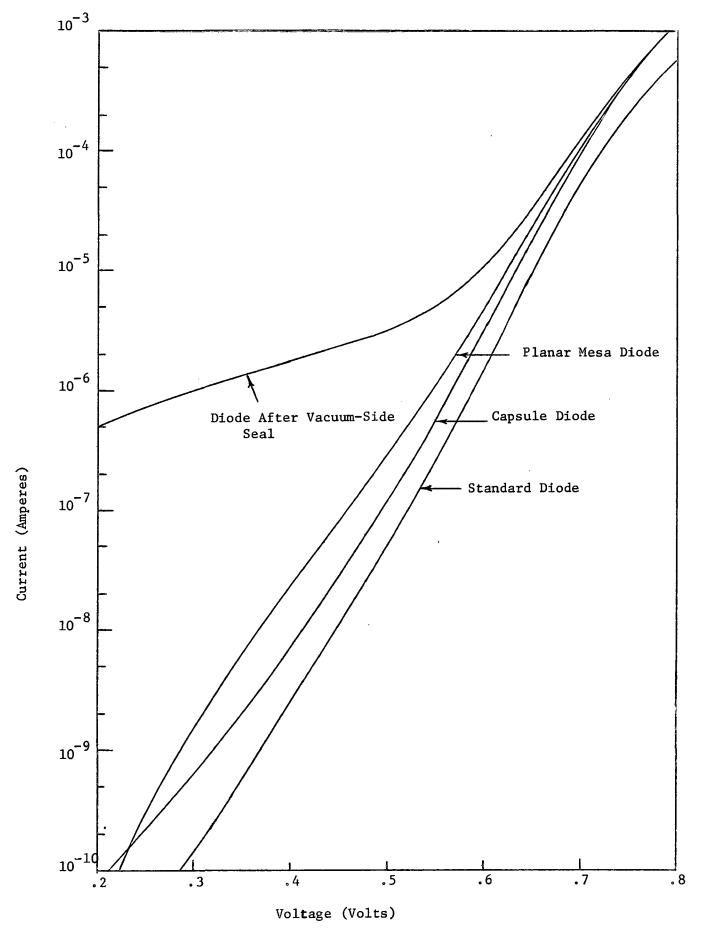

The log I-V characteristics of the diode used in Transducer No. 1 are illustrated in Fig. 24. These curves suggest that the diode had surface leakage problems that were influenced by moderate heat during additional processing. Although the final curve, i.e., the capsule diode curve, compares closely with the standard diode, the initially poor characteristics caused concern over the long-term stability of the diode.

The planar-mesa diode curve in Fig. 24 suggests the diode is unusable. It is a poor diode with only a narrow region of acceptable slope. Series resistance is apparent above 0.7 V, and surface leakage is in evidence below that value. The steep slope at very low voltage biases is unexplained. After the vacuum-side seal was completed, the diode was even more dominated by surface problems. When completed as a capsule diode, the characteristics are greatly improved. Apparently, the heat applied during the sealing operation has altered the surface properties.

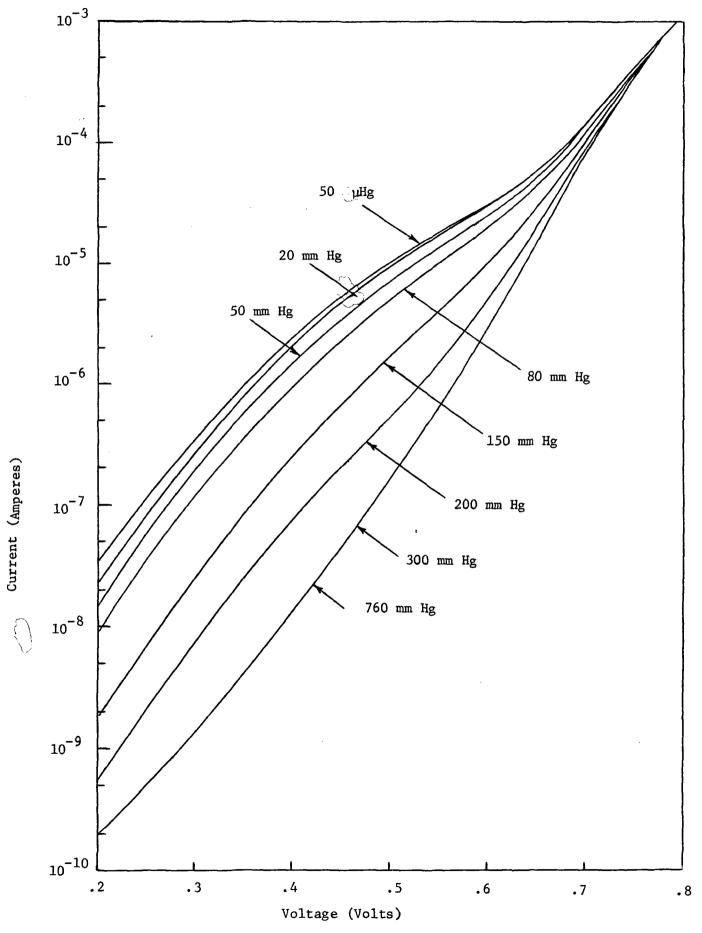

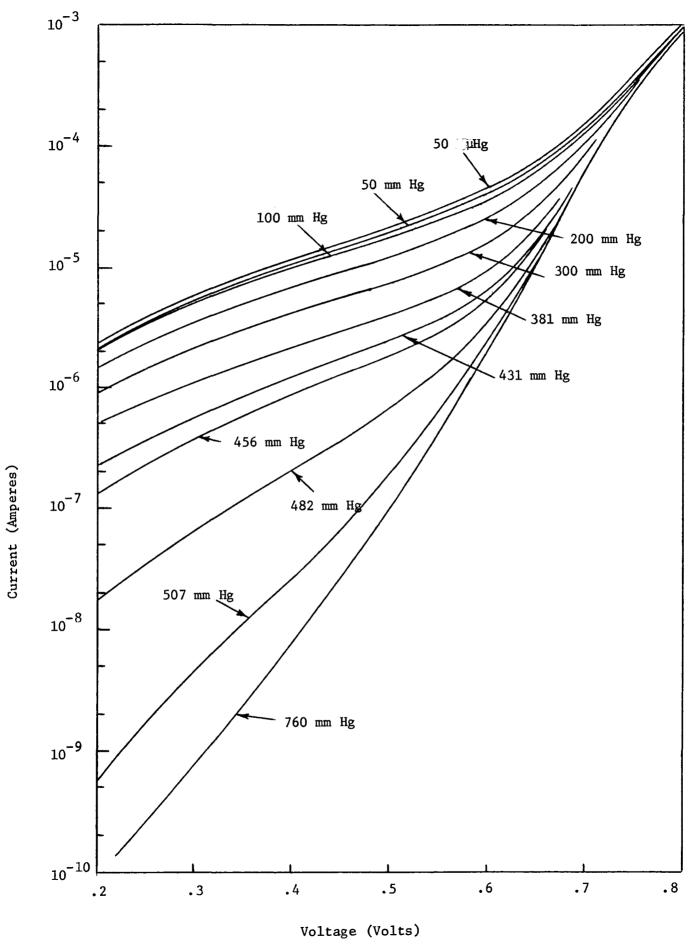

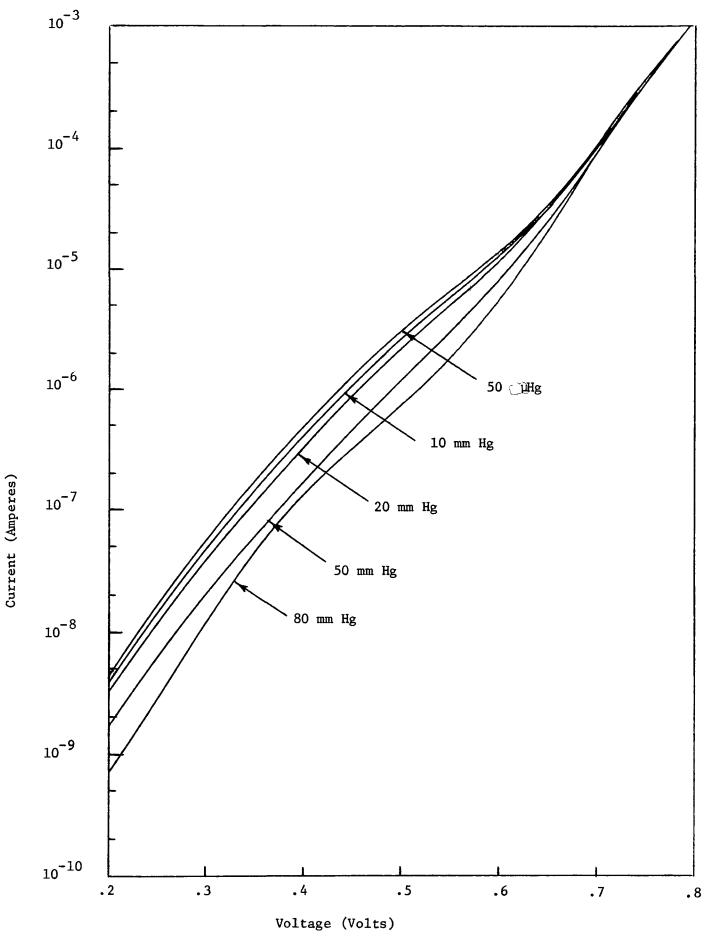

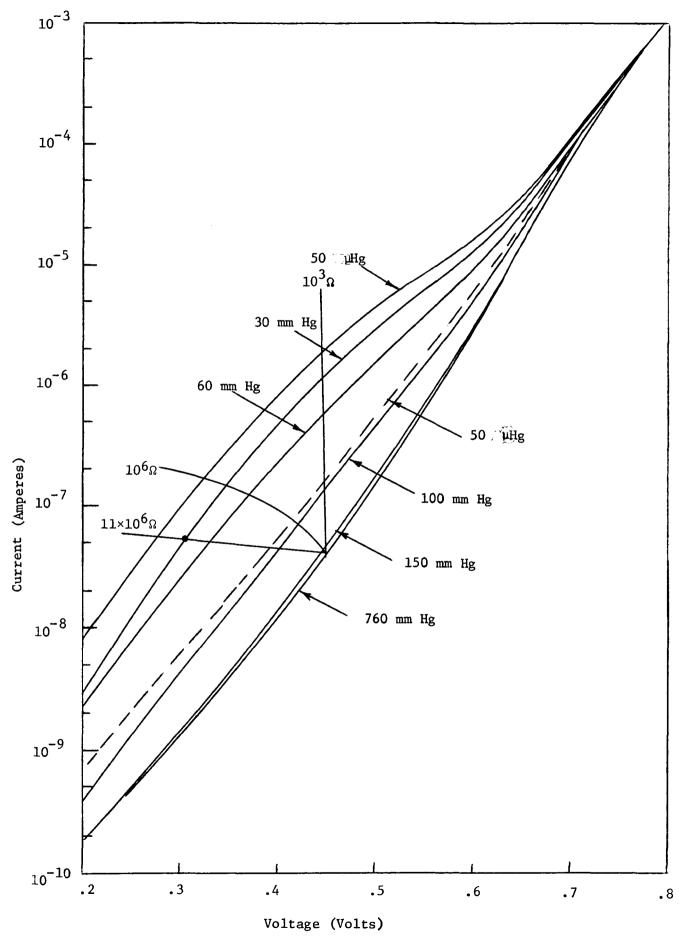

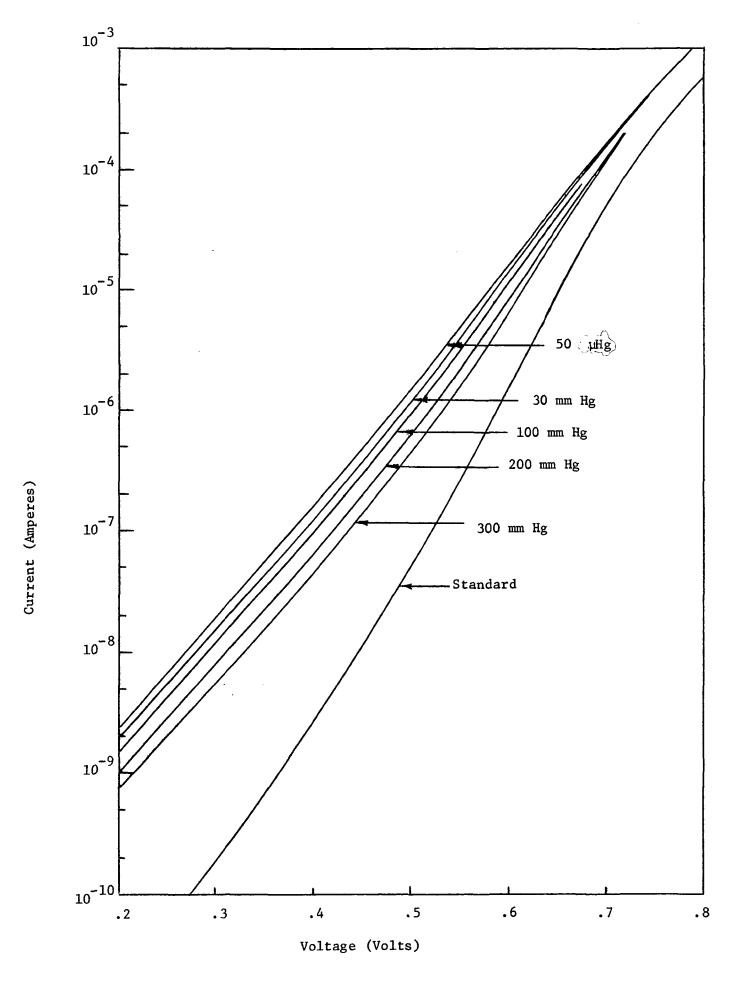

As a completed, housed transducer, the characteristics of a unit are partially determined by the stress bias, i.e., the force applied by the bias spring of Fig. 20. The log I-V characteristics of Transducer No. 1 are illustrated in Figs. 25 through 28 for various bias conditions. The bias was set in each case with the transducer in a vacuum since this also set the maximum stress the capsule diode would experience (increasing the pressure reduced the applied stress.) The 50  $\mu\text{mHg}$  curve in each figure corresponds to the initial bias. The limiting effect of the series resistance is readily apparent in each figure. In Fig. 25, for example, the series resistance limits the usefulness of the transducer to a voltage bias below 0.6 V. Generally it is advantageous to operate at a high voltage bias.

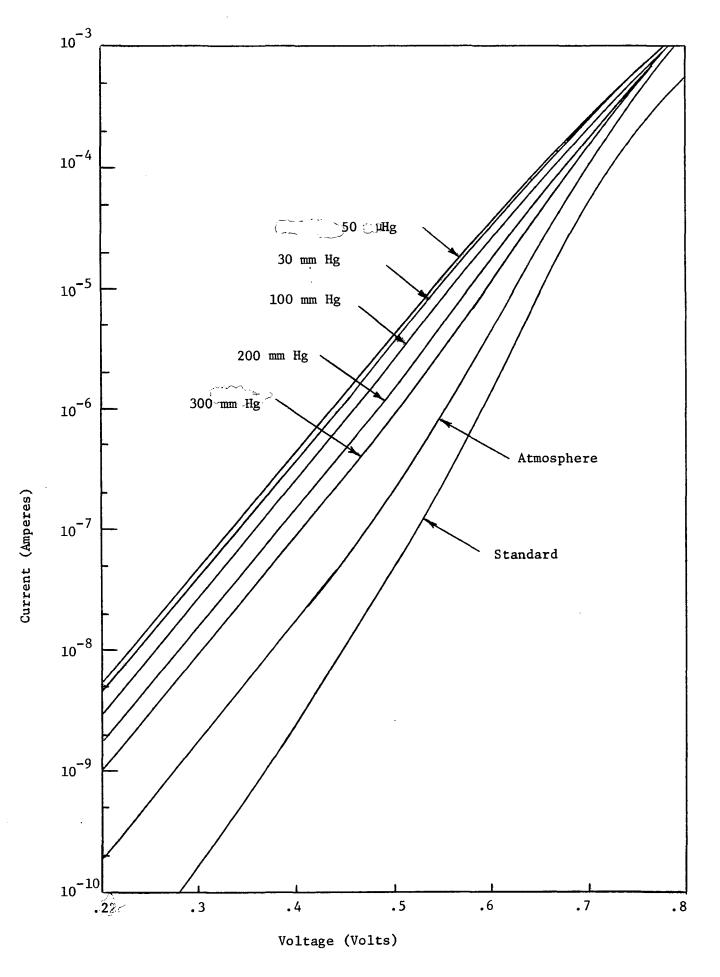

By altering the initial stress bias, the region of sensitivity for the transducer can be changed. In Fig. 25, for example, the initial stress bias was such that at 300 mm Hg, the stress was removed and the transducer was insensitive to further pressure increases. In Fig. 26, the initial stress bias was significantly higher and relatively large changes occurred between 300 mm Hg and in 700 mm Hg.

None of the transducers described in this report were significantly stress-biased with the biasing spring. So few were completed that it was decided not to risk damaging them by applying a higher stress. In each case, significant increases in sensitivity could have been gained with increased stress.

Fig. 27 illustrates a third initial stress-bias condition, and Fig. 28 a fourth. Additionally Fig. 28 illustrates the lack of repeatability achieved in this transducer. (The three lines labeled with resistance values in Fig. 28 are discussed in a subsequent section on instrumentation). The initial bias was set at a pressure of 50 µHg and several curves plotted

Figure 24. Log I-V Characteristics of Transducer No. 1 Diode at Various Stages

Figure 25. Characteristics of Transducer No. 1; Bias Condition 1.

Figure 26. Log I-V Characteristics of Transducer No. 1; Bias Condition 2.

Figure 27. Log I-V Characteristics of Transducer No. 1; Bias Condition 3.

Figure 28. Log I-V Characteristics of Transducer No. 1; Bias Condition 4

corresponding to pressure increases to 760 mm Hg. The pressure was decreased again to 50  $\,\mu{\rm Hg}$  and the plotter circuit operated. The results are shown as a broken curve in Figure 28. This lack of repeatability is traceable to the housing. When unhoused diodes were subjected to ON-OFF stress conditions, the results were repeatable.

## Transducer No. 2

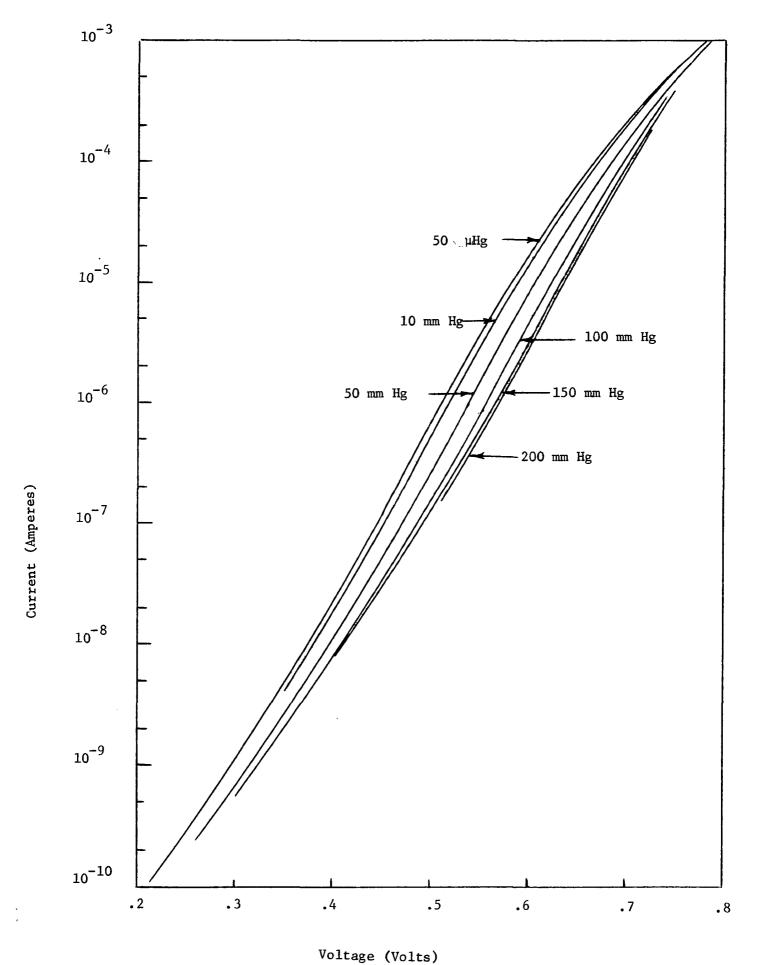

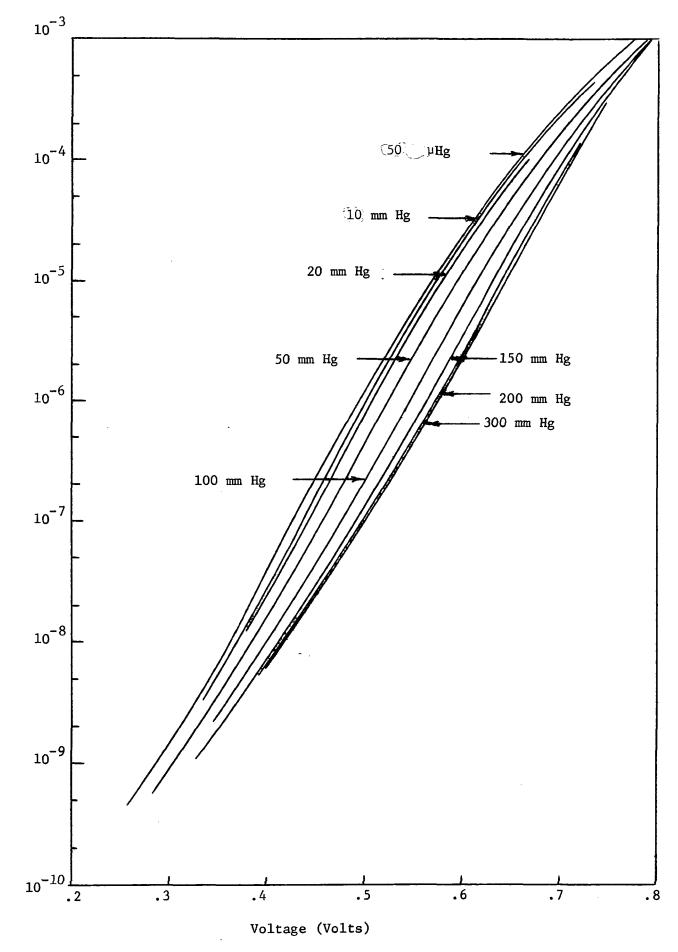

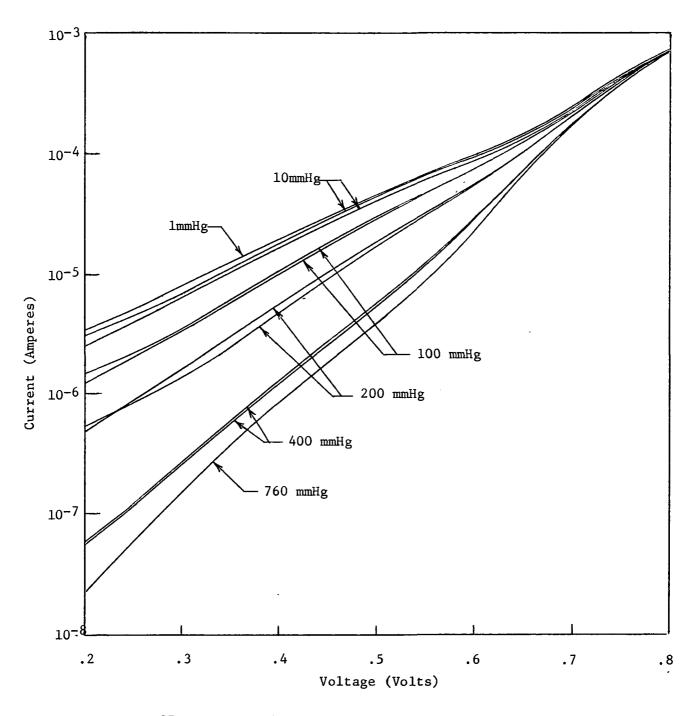

The log I-V characteristics of the diode used in fabricating Transducer No. 2 are shown in Fig. 29. This diode shows the characteristic resistance effect above 0.7 V, and some surface leakage. It is reasonably a good diode, however. The minimum slope is significantly greater than the q/2kT characteristic of generation-recombination current. During the sealing process, this diode was also improved to have the characteristics shown in Fig. 30. The 200 mm Hg curve in Fig. 30 corresponds to the capsule diode without any stressbias. This transducer was stressed-bias in a vacuum (50 mHg curve) and the curves of Fig. 30 generated. All of these curves compare favorably with the q/kT slope, and the transducer appeared very stable. When the pressure was returned to 50 mHg, the original curve was retraced.