# DESIGN, PROCESSING, AND TESTING OF LSI ARRAYS FOR SPACE STATION

RY

W. C. SCHNEIDER

# **QUARTERLY TECHNICAL REPORT NO. 14**

#### **AUGUST 1974**

|   | ACCUMANTAL PROGRAMMA AND                  | 274 22424   |

|---|-------------------------------------------|-------------|

| ı | (NASA-CR-120444) DESIGN PROCESSING AND    | ห74-33180 \ |

|   | TESTING OF LSI ARRAYS FOR SPACE STATION   |             |

|   | Quarterly Technical Report, 1 Apr 30      | ,           |

|   | Jun. 1974 (Radio Corp. of America) : 16 p | Unclas      |

|   | HC \$4.00 CSCL 20L                        | G3/26 48813 |

Distribution of this report is provided in the interest of information exchange and should not be construed as endorsement by NASA of the material presented. Responsibility for the contents resides with the organization that prepared it.

PREPARED UNDER CONTRACT NO. NAS12-2207 BY RCA LABORATORIES

PRINCETON, NEW JERSEY 08540

GEORGE C. MARSHALL SPACE FLIGHT CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

HUNTSVILLE, ALABAMA 35812

Mr. John Gould

Technical Monitor

S&E-ASTR-RM

NAS12-2207

George C. Marshall Space Flight Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

Huntsville, Alabama 35812

Requests for copies of this report should be referred to:

NASA Scientific and Technical Information Facility P. O. Box 33, College Park, Maryland 20740

| 1. Report No.                                                                                                                                                  | 2. Government Accession                                                                                                                                                                                                                            | No.                                                                         | 3. Recipient's Cate                                                                     | alog No.                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| 4. Title and Subtitle                                                                                                                                          |                                                                                                                                                                                                                                                    |                                                                             | 5. Report Date                                                                          | <u></u>                                                                             |  |

| DESTEN PROCESS                                                                                                                                                 | IC AND DECEMBED OF                                                                                                                                                                                                                                 | J                                                                           | July 1974                                                                               |                                                                                     |  |

| LSI ARRAYS FOR S                                                                                                                                               | NG, AND TESTING OF PACE STATION                                                                                                                                                                                                                    |                                                                             | 6. Performing Orga                                                                      | nization Code                                                                       |  |

| 7. Author(s) W. C. Schneider                                                                                                                                   |                                                                                                                                                                                                                                                    |                                                                             | 8. Performing Organization Report No PRRL-74-CR-53                                      |                                                                                     |  |

| 9. Performing Organization Nam                                                                                                                                 | e and Address                                                                                                                                                                                                                                      | 1                                                                           | O. Work Unit No.                                                                        |                                                                                     |  |

| RCA Laboratories<br>Princeton, NJ 08                                                                                                                           | 540                                                                                                                                                                                                                                                | ī                                                                           | 11. Contract or Gran                                                                    | it No.                                                                              |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                                    | [i                                                                          | 3. Type of Report                                                                       | and Period Covered                                                                  |  |

| 2. Sponsoring Agency Name and                                                                                                                                  | Address                                                                                                                                                                                                                                            |                                                                             | Qtly. Techn                                                                             | ical Report                                                                         |  |

| George C. Marsha                                                                                                                                               | ll Space Flight Cent                                                                                                                                                                                                                               | L.                                                                          | No. 14(4/1/                                                                             | •                                                                                   |  |

| National Aeronau<br>Huntsville, Alaba                                                                                                                          | tics & Space Adminis<br>ama 35812                                                                                                                                                                                                                  | tration                                                                     | 4. Sponsoring Ager                                                                      | icy Code                                                                            |  |

| 5. Supplementary Notes                                                                                                                                         | :                                                                                                                                                                                                                                                  |                                                                             |                                                                                         |                                                                                     |  |

| leaded low-power 256-bit random as aluminum-gate cur sense version les silicon-gate RAM sapphire beam-les SOS TA5388 device have good electribeam-leaded 256-b | research program is high-performance mecess memory (RAM). Trent-sense version to the present eff. Some problems united process developments using a Si <sub>3</sub> N <sub>4</sub> pastical parameters. Testit RAM (TA6567) bord NASA, Huntsville, | Previous and a sile fort to make to the entere pressivation and a ded on ce | e-semiconductoricon-gate volume a beam-loe silicon-oresented. Be layer were cal samples | ctor (MOS),<br>th the<br>oltage-<br>eaded<br>n-<br>eam-leaded<br>shown to<br>of the |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                                    |                                                                             |                                                                                         | ,                                                                                   |  |

| 7. Key Words (Selected by Auth                                                                                                                                 | or(s)) 18. I                                                                                                                                                                                                                                       | Distribution Stat                                                           | tement                                                                                  |                                                                                     |  |

| Random access men<br>Beam-lead process                                                                                                                         | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                            |                                                                             |                                                                                         |                                                                                     |  |

|                                                                                                                                                                |                                                                                                                                                                                                                                                    |                                                                             | *                                                                                       |                                                                                     |  |

| 9. Security Classif. (of this rep                                                                                                                              | ort) 20. Security Classif. (of t                                                                                                                                                                                                                   | his page)                                                                   | 21. No. of Pages                                                                        | 22. Price                                                                           |  |

| Unalessified                                                                                                                                                   | Unclassifia                                                                                                                                                                                                                                        |                                                                             | 16                                                                                      |                                                                                     |  |

<sup>\*</sup>For sale by National Technical Information Service, Springfield, Virginia 22151.

# TABLE OF CONTENTS

| Sectio | n                                 | Page |

|--------|-----------------------------------|------|

| SUMMAR | Y                                 | . 1  |

| I.     | INTRODUCTION                      | . 2  |

| II.    | BEAM-LEAD SOS PROCESS DEVELOPMENT | . 3  |

|        | A. SigN4 Passivation Layer        | , 3  |

| III.   | BEAM-LEADED 256-BIT RAM TA6567    | . 9  |

| IV.    | PERSONNEL AND EXPENDITURES        | . 10 |

| ٧.     | NEW TECHNOLOGY APPENDIX           | . 11 |

|        | REFERENCES                        | . 12 |

# LIST OF ILLUSTRATIONS

| Figur | e                                                                                   | P | age |

|-------|-------------------------------------------------------------------------------------|---|-----|

| 1.    | SEM of gold beams and base metal on corner of BL/SOS chip                           |   | 4   |

| 2.    | SEM profile of gold beam on BL/SOS chip                                             | • | 5   |

| 3.    | SEM via opening in photoresist after etching the copper and plating the gold pillar | • | 5   |

| 4.    | SEM of same area as in Fig. 3 with photoresist removed                              | • | 6   |

| 5.    | SEM of same area as in Fig. 3 with completed gold beam lead                         | • | 6   |

| 6.    | Photomicrograph of BL/SOS TA5388 circuit on the wafer before scribing               |   | 7   |

| 7.    | Photomicrograph of BL/SOS TA5388 circuit after scribing, breaking, and expanding    |   | 8   |

| 8.    | Photomicrograph of BL/SOS TA6567 256-bit RAM chip bonded onto a ceramic substrate   |   | 9   |

# DESIGN, PROCESSING AND TESTING OF LSI ARRAYS FOR SPACE STATION

bу

W. C. Schneider

RCA Laboratories

Princeton, New Jersey 08540

#### SUMMARY

The goal of this research program is the development of a beam-leaded low-power, high-performance metal-oxide-semiconductor (MOS), 256-bit random access memory (RAM). Previous success with the aluminum-gate current-sense version and a silicon-gate voltage sense version led to the present effort to make a beam-leaded silicon-gate RAM. Some problems unique to the silicon-on-sapphire beam-lead process development are presented. Beam-leaded SOS TA5388 devices using a Si3N4 passivation layer were shown to have good electrical parameters. Ten mechanical samples of the beam-leaded 256-bit RAM (TA6567) bonded on ceramic substrates were delivered to NASA, Huntsville, Alabama.

#### I. INTRODUCTION

RCA has been a pioneer in the research and development of siliconon-sapphire (SOS) technology. The many facets of this program include materials and basic device research, computer-aided circuit design, mask-making techniques, and advanced CMOS array design using largescale integration (LSI).

Support has previously been made available to develop an aluminumgate current-sense version and a silicon-gate voltage-sense version of the low-power, high-performance CMOS/SOS 256-bit random access memory (RAM). Success with both types of the RAM resulted in the present phase of this project to develop a low-power, high-performance metaloxide-semiconductor (MOS), 256-bit RAM with beam leads. The development of the beam-leaded SOS technology has combined the standard SOS process with a modified microbridge beam-lead process. The mechanical feasibility of this technology has been demonstrated using as the test vehicle a dual complementary pair plus inverter (TA5388). circuit was fabricated on SOS and metallized using the beam-lead base metal and gold beam technology; it was then laser-scribed, separated, and bonded to a standard 14-lead ceramic DIP. Stable TA5388 devices have been made using a SiaNA passivation layer. Subsequent efforts have been to improve the beam-lead processing and to establish the electrical base line data for the beam-lead CMOS/SOS devices using the TA5388 circuit.

The 256-bit beam-leaded RAM circuit (TA6567) was processed, and ten mechanical samples assembled on ceramic substrates were delivered to NASA, Huntsville, Alabama.

#### II. BEAM-LEAD SOS PROCESS DEVELOPMENT

The beam-lead SOS process development is mainly concentrated on the Si<sub>3</sub>N<sub>4</sub> passivation layer, gold pillar and beam formation, and subsequent chip separation and bonding to a ceramic substrate. The Ti/Pd/Au base metal process is satisfactory from both an electrical viewpoint and a mechanical viewpoint.\* The development areas are discussed below.

# A. Si<sub>3</sub>N<sub>4</sub> Passivation Layer

The present procedure requires the  $\mathrm{Si}_3\mathrm{N}_4$  layer to be deposited by CVD in the AMT800 reactor just prior to the opening of contacts and the base metal step. The contacts are first opened in the  $\mathrm{Si}_3\mathrm{N}_4$  layer and then through the  $\mathrm{Si}_2$  layer by chemical etching. The first goal is to determine the optimum thickness for electrical passivation that is consistent with the standard processing techniques.

An experiment on BL/SOS\*\* TA5388 circuits with three different Si<sub>3</sub>N<sub>4</sub> passivation layer thicknesses (500 Å, 1200 Å, and 2000 Å) was completed; mechanically good beams were obtained. The initial hand-probed electrical test data indicate good passivation for all thicknesses of Si<sub>3</sub>N<sub>4</sub>. No threshold voltage shift was observed after gold beam formation, as was previously reported (ref. 1). Additional evaluation and electrical testing are being done on the wafers.

#### B. Gold Pillar and Beam Formation

One of the more critical parts of the BL/SOS process is the formation of the second level of gold metallization, i.e., the pillar and beam formation. The processing sequence was described in detail in Quarterly Technical Report No. 12 (ref. 2).

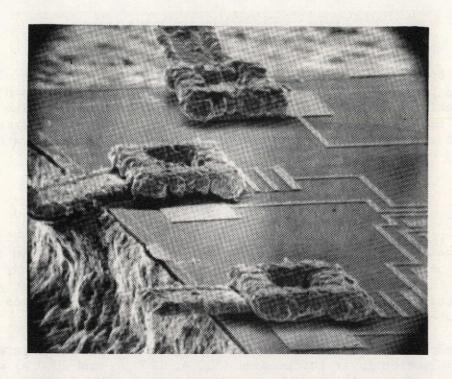

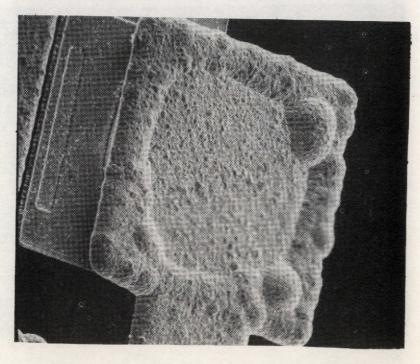

Figure 1 is a scanning electron micrograph (SEM) photograph of three beams and the base metal on the corner of a BL/SOS chip. The

<sup>\*</sup>The base metal process gives good ohmic contacts between the silicon and the base metal. Also, it passes the "scotch tape" adhesion test; i.e., scotch tape is smoothed out over the base metal on a wafer and then pulled off rapidly without removing the base metal. This qualitative test is an indicator of good base-metal-to-substrate adhesion. \*\*BL/SOS - beam-lead silicon on sapphire.

Figure 1. SEM of gold beams and base metal on corner of BL/SOS chip.

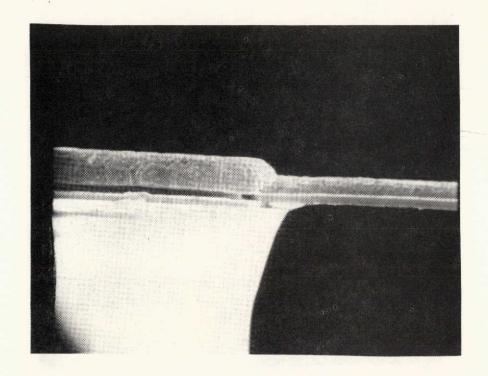

SOS wafer was laser-scribed and broken by mechanical roller breaking. The photomicrograph is shown for orientation purposes in this discussion. Notice the large grain size of the electroplated gold, especially around the pillar or anchor pad. This condition can be minimized by controlling the PH and the percentage of gold in the electroplating bath. Figure 2 shows a scanning electron microscope (SEM) photograph of a beam and pillar formed in a well-controlled gold-plating bath. Here the grain size of the gold at the top of the beam is smaller than that of the beams in the previous case. In both cases, the gold at the bottom of the beam was well defined by the photoresist and then rounded off as the beam thickness approached and then exceeded the thickness of the photoresist. This variation in beam cross section has not presented any problem in subsequent processing.

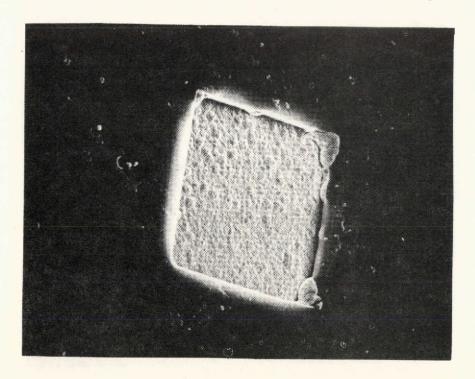

The subsequent series of SEM photographs (Figs. 3 through 5) show the build-up of the gold pillar and beam. Figure 3 shows the via opening defined in the photoresist after etching the copper to expose the base metal and after plating the gold pillar. Figure 4 is the same

Figure 2. SEM profile of gold beam on BL/SOS chip.

Figure 3. SEM via opening in photoresist after etching the copper and plating the gold pillar.

Figure 4. SEM of same area as in Fig. 3 with photoresist removed.

Figure 5. SEM of same area as in Fig. 3 with completed gold beam lead.

area with the photoresist removed to expose the copper layer that replicates the area surrounding the via. The contact pad and base metal, and a rectangular contact opening to the protective diode array are clearly outlined. Note the nonuniform plating of gold around the edge of the via opening that causes the beam gold to plate thicker around the edge of the pillar opening. This effect is observed on most of the beam leads made by this process on SOS and does not cause a problem in subsequent processing.

## C. Chip Separation and Bonding

The laser scribing and breaking of beam-leaded SOS wafers as described in a previous report (ref. 3) is a fairly standard technique. Additional improvements will be to increase the throughput and the scribing alignment accuracy.

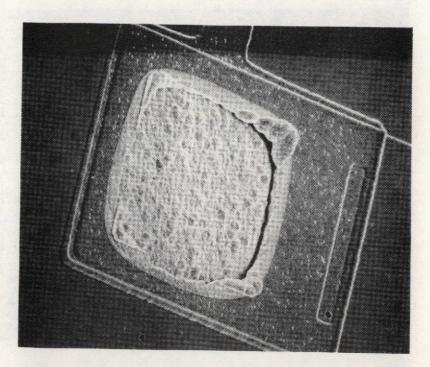

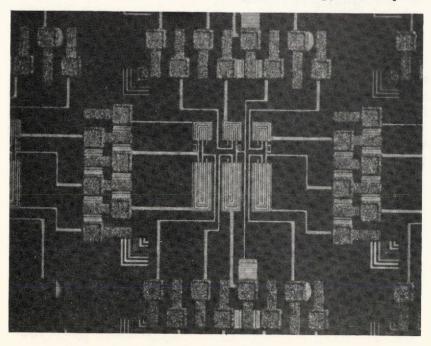

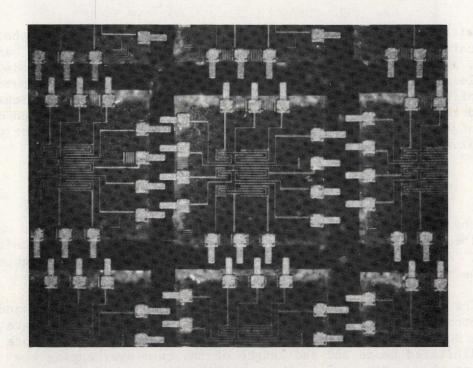

The feasibility of separating the chips using a wafer expander was demonstrated but not optimized. Figure 6 is a photomicrograph of the BL/SOS TA5388 circuit on the wafer before scribing. Note the interdigitated beams and the length of the beam overhanging the adjacent chip. Figure 7 is the same circuit (the magnification differs from that in Fig. 6 but only the relative spacing is important for this discussion) after scribing, breaking, and expanding.

Figure 6. Photomicrograph of BL/SOS TA5388 circuit on the wafer before scribing.

Figure 7. Photomicrograph of BL/SOS TA5388 circuit after scribing, breaking, and expanding.

With the proper expansion, the beams are no longer interdigitated and a chip can be easily removed without bending the beams.

The assembly of beam-leaded SOS chips on the ceramic substrate is done by "wobble-bonding." Both the BL/SOS TA5388 dual complementary pair plus inverter circuit (53 mils x 53 mils, 14 beams) and the BL/SOS TA6567 256-bit RAM circuit (135 mils x 145 mils, 28 beams) have been wobble-bonded on ceramic substrates. Further discussion of the TA6567 is given in Section III.

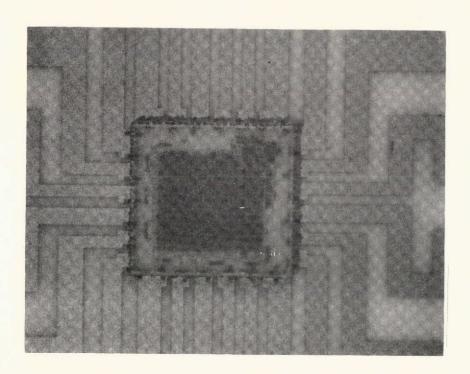

#### III. BEAM-LEADED 256-BIT RAM TA6567

The description of the beam-leaded silicon-gate 256-word by 1-bit static SOS CMOS RAM designated as TA6567 was given in previous quarterly reports (refs. 1 and 2). In this quarter, the TA6567 beam-leaded chip has been successfully fabricated and assembled as a mechanical sample on a ceramic substrate. Figure 8 is a photomicrograph of the TA6567 chip beam-leaded to a 24-pin DIP ceramic substrate. The actual circuit outline is visible through the transparent sapphire substrate. Ten mechanical samples of this type were delivered to the Contract Monitor this quarter to satisfy one part of the deliverable items listed under Contract No. NAS12-2207.

Figure 8. Photomicrograph of BL/SOS TA6567 256-bit RAM chip bonded onto a ceramic substrate.

REPRODUCIBILITY OF THE ORIGINAL PAGE IS POOR

### IV. PERSONNEL AND EXPENDITURES

During the quarter reported herein the following personnel contributed to the contract:

W. C. Schneider

Project Scientist

R. J. Hollingsworth

Total expenditures through June 30, 1974 have been \$202,280 including profit. Problem areas that may create an overrun: none at this time.

# V. NEW TECHNOLOGY APPENDIX

It was concluded from the review of the work that there were no reportable items of New Technology under the contract during the period covered by this report.

#### REFERENCES

- 1. W. C. Schneider and R. J. Hollingsworth, Design, Processing, and Testing of LSI Arrays for Space Station, Quarterly Technical Report No. 13, Contract NAS12-2207, May 1974.

- W. R. Lile and R. J. Hollingsworth, <u>Design</u>, <u>Processing</u>, and <u>Testing</u> of <u>LSI Arrays for Space Station</u>, <u>Quarterly Technical Report</u> No. 12, Contract NAS12-2207, February 1974.

- 3. W. R. Lile and W. J. Greig, <u>Design</u>, <u>Processing</u>, and <u>Testing of LSI Arrays for Space Station</u>, Quarterly Technical Report No. 11, Contract NAS12-2207, October 1973.