# MAN-COMPUTER INTERACTIVE DATA ACCESS SYSTEM (McIDAS)

Continued development of McIDAS and operation in the GARP Atlantic Tropical Experiment

> Verner E. Suomi Space Science and Engineering Center University of Wisconsin-Madison 1225 West Dayton Street Madison, Wisconsin 53706

# March 1975 Final Report Contract NAS5-23296 For Period August 1973 to December 1974

## Prepared for

GODDARD SPACE FLIGHT CENTER Greenbelt, Maryland 20771

TECHNICAL REPORT STANDARD TITLE PAGE

| 1. Report No.                                                                       | 2. Government Accession No.                    | 3. Recipient's Catalog No.              |

|-------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|

| 4. Title and Substitle MAN-COMPUTER INTERACTIVE<br>DATA ACCESS SYSTEM (MCIDAS)      |                                                | 5. Report Date<br>March 1975            |

| Continued Development<br>in the GARP Atlantic                                       | of McIDAS and Operation<br>Tropical Experiment | 6. Performing Organization Code         |

| 7. Author(s)<br>Verner E. Suomi                                                     |                                                | 8. Performing Organization Report No.   |

| 9. Performing Organization Name and Address<br>Space Science and Engineering Center |                                                | 10. Work Unit No.                       |

| University of Wiscons<br>1225 West Dayton Stre                                      |                                                | 11. Contract or Grant No.<br>NAS5–23296 |

| Madison, Wisconsin                                                                  | 53515                                          | 13. Type of Report and Period Covered   |

| 12. Sponsoring Agency Name and Addre<br>Goddard Space Flight<br>Greenbelt, Maryland | Center                                         | Final<br>Aug 73 - Dec 74                |

| orcembert, narytanu                                                                 | 20771                                          | 14. Sponsoring Agency Code<br>901       |

15. Supplementary Notes

#### 16. Abstract

Using McIDAS, the complete output of the Synchronous Meteorological Satellite (SMS-A) was recorded on one inch magnetic tape during the GATE period. 4337 images were recorded, 97.75% of all data transmitted.

The McIDAS quality control subsystem tests cloud track vectors against four sets of criteria; (1) rejection if best match occurs on correlation boundry, (2) rejection if major correlation peak is not distinct and significantly greater than secondary peak, (3) rejection if correlation is not persistent, and (4) rejection if acceleration is too great.

The cloud height program determines cloud optical thickness from visible data and computer IR emissivity. From IR data and temperature profile cloud height is determined.

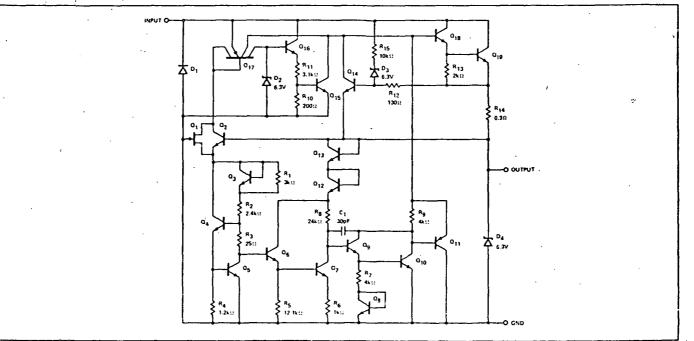

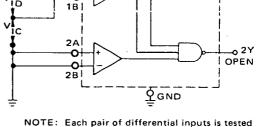

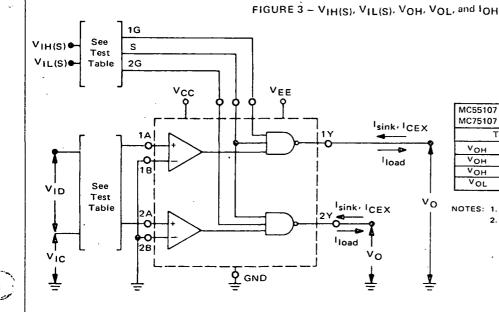

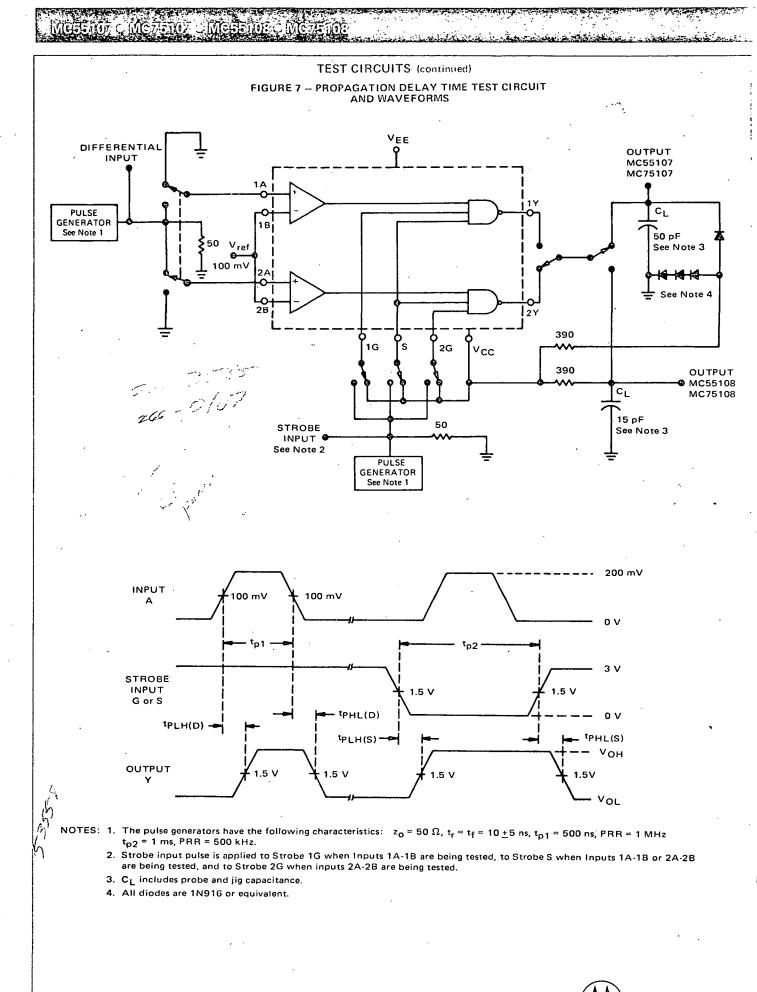

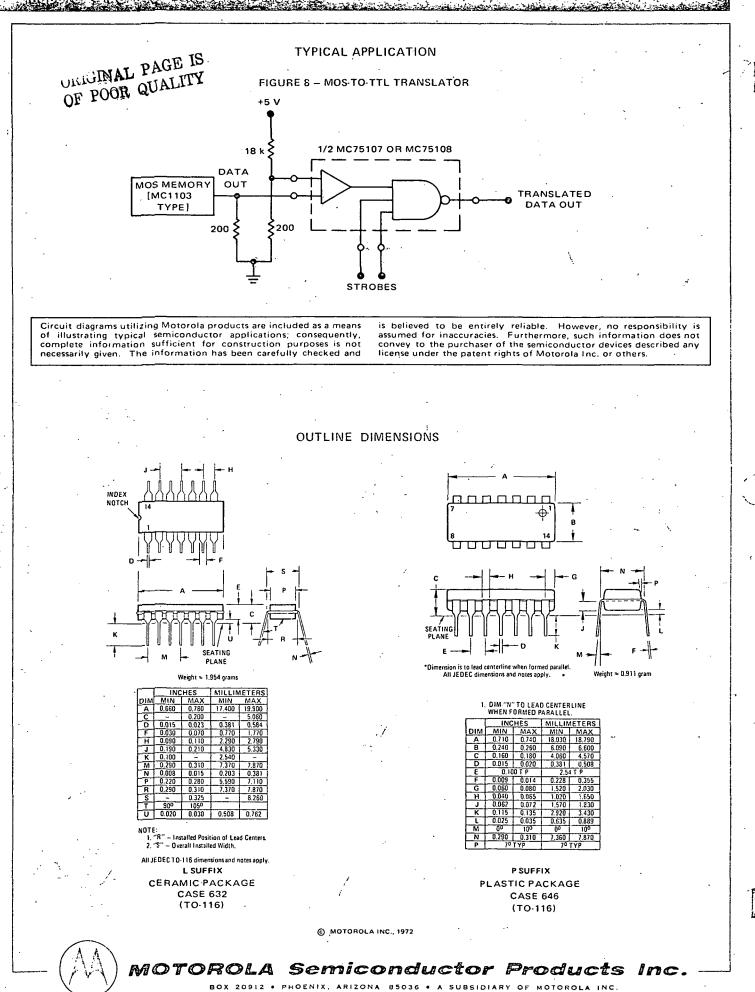

The report also includes complete McIDAS functional description and electronic schematics.

| 17. Key Kords (S. lected by Author(s))                                        |                          | 18. Distribution Statement |                  |            |

|-------------------------------------------------------------------------------|--------------------------|----------------------------|------------------|------------|

| Data Processing<br>Video display<br>Satellite Meteorology<br>Wind Measurement | <b>y</b>                 | • •                        |                  | •<br>•     |

| 19. Security Classif. (of this report)                                        | 20. Security Classif. (c | of this page)              | 21. No. of Pages | 22. Price* |

| None                                                                          | None                     |                            |                  |            |

\*For sale by the Clearinghouse for Federal Scientific and Technical Information, Springfield, Virginia 22151.

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                               |               | 1. |   | PAGE                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arch | niving SMS Data During Gate                                                                                                                                                                                                                                                                                                                                                                                                                   | •             |    |   | 1-1                                                                                                                                                                                     |

| Clou | d-Track Quality Control                                                                                                                                                                                                                                                                                                                                                                                                                       |               | ·  | • | 2-1                                                                                                                                                                                     |

|      | Introduction<br>Technique 1<br>Technique 2<br>Technique 3<br>Technique 4<br>Future Developments<br>Summary                                                                                                                                                                                                                                                                                                                                    | 2             |    |   | 2-1<br>2-2<br>2-2<br>2-5<br>2-6<br>2-8<br>2-8                                                                                                                                           |

| SMS  | Cloud Heights                                                                                                                                                                                                                                                                                                                                                                                                                                 | :             |    |   | 3-1                                                                                                                                                                                     |

| į    | Introduction<br>Determination of Emissivity<br>Cloud Height Program<br>Operation and Assessment of Cloud<br>Summary<br>Recommendations for Improvements                                                                                                                                                                                                                                                                                       | Height System |    |   | 3-1<br>3-2<br>3-17<br>3-27<br>3-29<br>3-29                                                                                                                                              |

| McII | AS Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                     |               |    |   |                                                                                                                                                                                         |

| •    | McIDAS Archive System<br>General Theory of Operation<br>Detailed Theory of Operation<br>DUS Antenna Subsystem<br>Archive Subsystem<br>Bit Syncs<br>DUS/Archive Interface<br>Archive Control<br>Data Buffers<br>Documentation Generator<br>Modulator<br>Recording Subsystem<br>Slant Track Video Recorder<br>Slant Track Video Recorder<br>Slant Track Control Board<br>MSU Subsystem<br>Demodulator<br>MSU Control<br>Real Time SMS Interface | · · ·         |    |   | $\begin{array}{c} 4-1 \\ 4-3 \\ 4-4 \\ 4-5 \\ 4-6 \\ 4-8 \\ 4-9 \\ 4-16 \\ 4-23 \\ 4-26 \\ 4-27 \\ 4-28 \\ 4-30 \\ 4-32 \\ 4-30 \\ 4-32 \\ 4-33 \\ 4-35 \\ 4-39 \\ 4-40 \\ \end{array}$ |

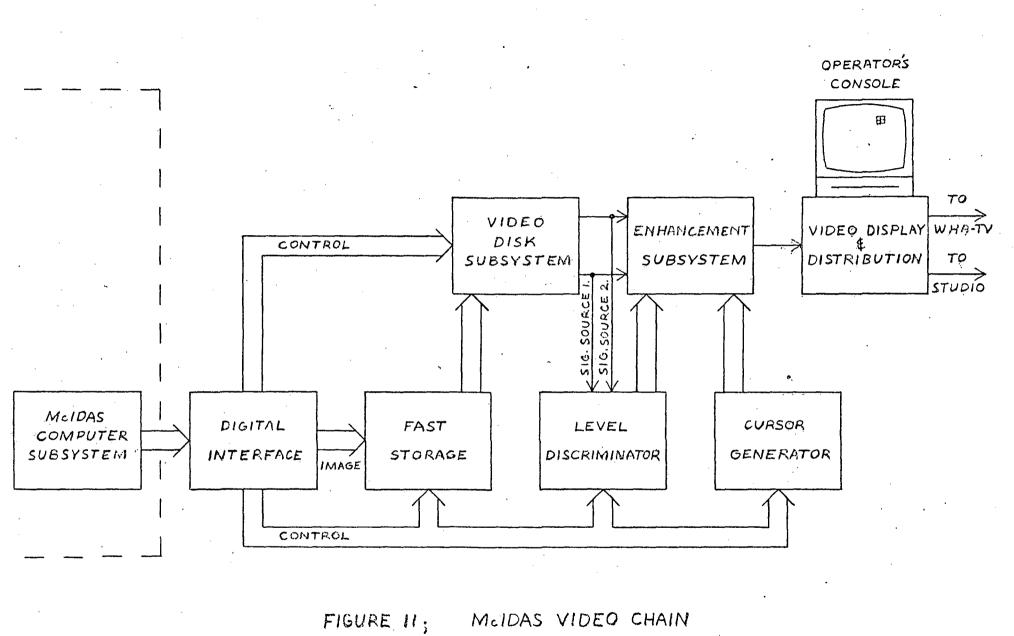

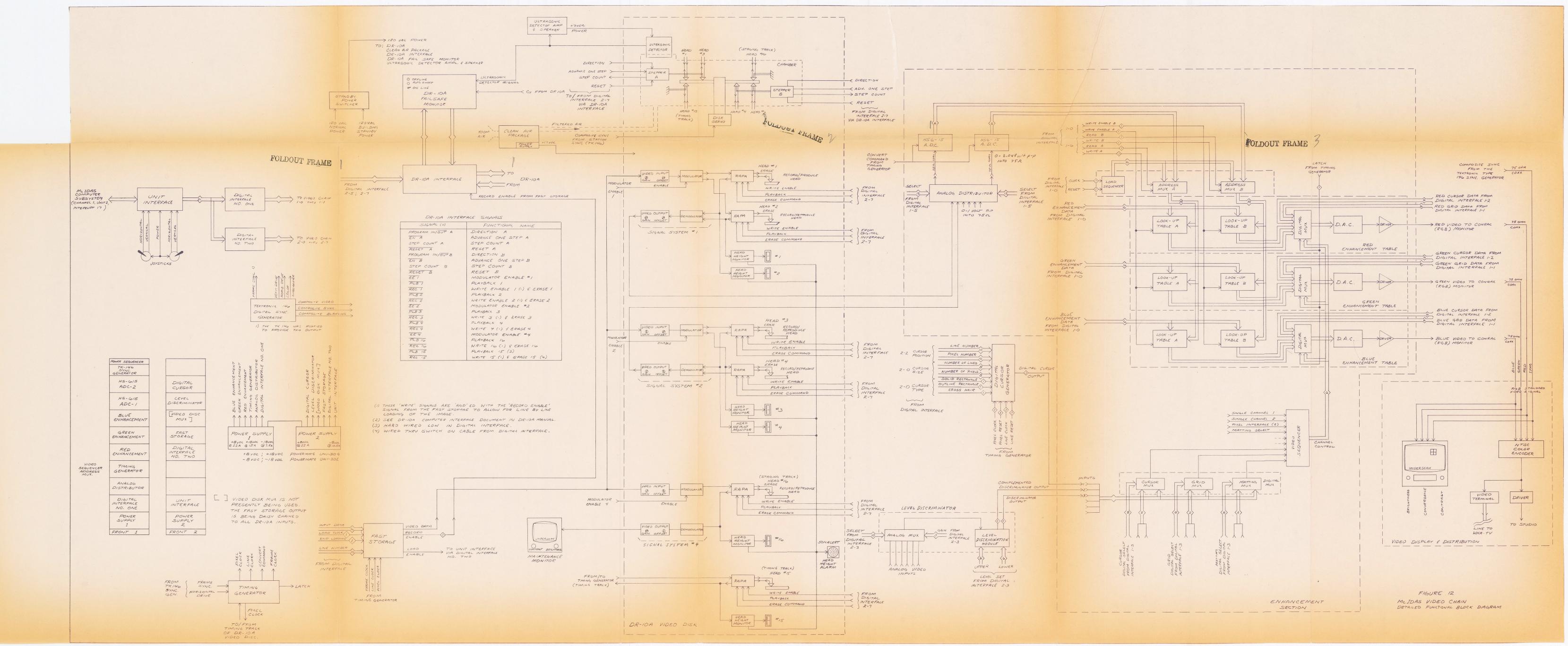

|      | <u>McIDAS Video Chain</u><br>General Theory of Operation<br>Detailed Theory of Operation<br>Unit Interface<br>Digital Interfaces<br>Timing Generator<br>Video Disk Subsystem                                                                                                                                                                                                                                                                  | •             |    |   | 4-40<br>4-42<br>4-43<br>4-46<br>4-50<br>4-54                                                                                                                                            |

# TABLE OF CONTENTS

# McIDAS Video Chain (cont.)

| Enhancement Subsystem          | 4-55 |

|--------------------------------|------|

| General                        | 4-55 |

| Analog Distributor             | 4-58 |

| Analog to Digital Converter    | 4-60 |

| Address Mux                    | 4-61 |

| Enhancement Tables             | 4-63 |

| Video Sequencer                | 4-66 |

| Digital Multiplexer            | 4-68 |

| Fast Storage                   | 4-69 |

| Digital Cursor Generator       | 4-75 |

| Level Discriminator            | 4-80 |

| Video Display and Distribution | 4-82 |

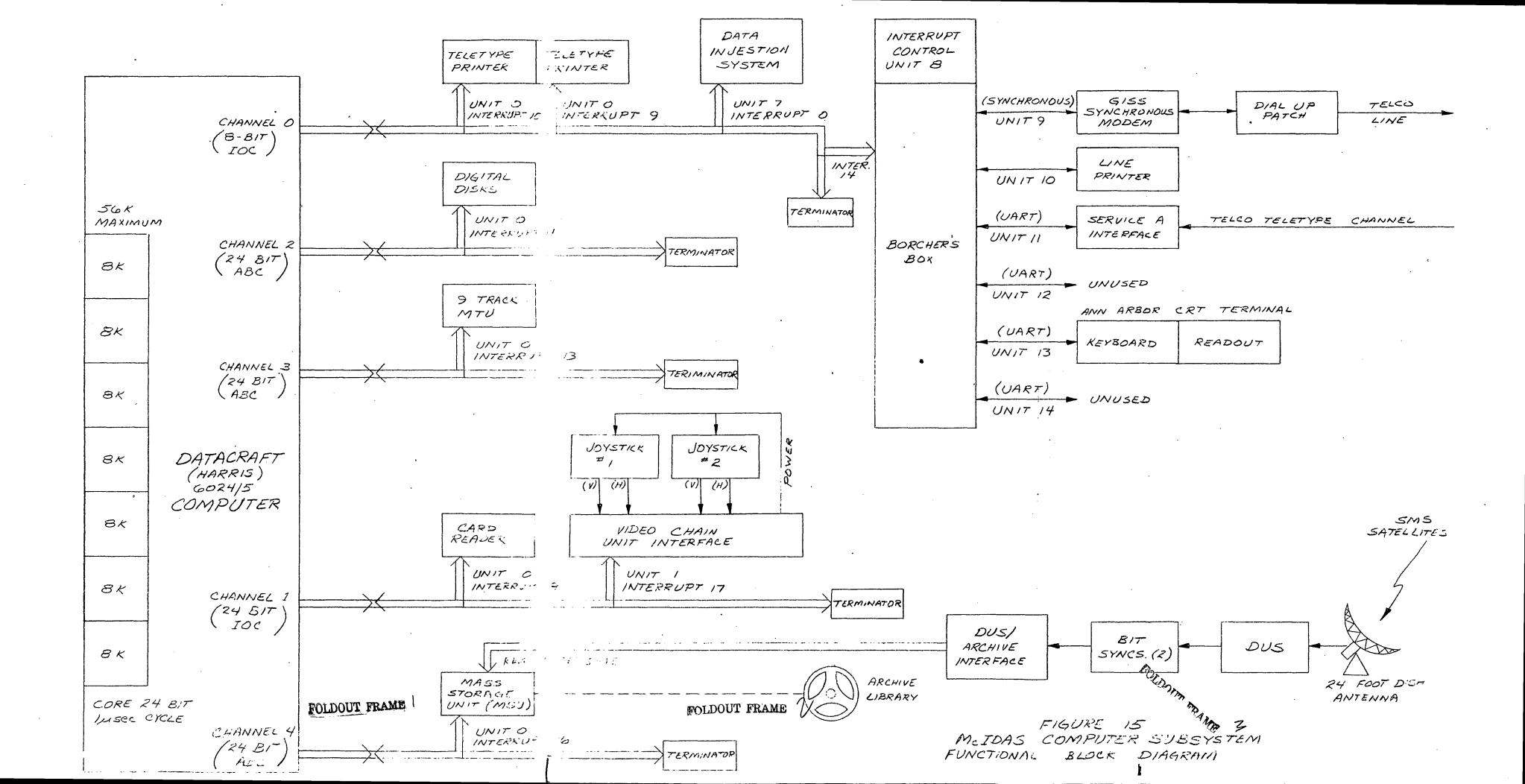

| McIDAS Computer Subsystem      | 4-84 |

| General Theory of Operation    | 4-84 |

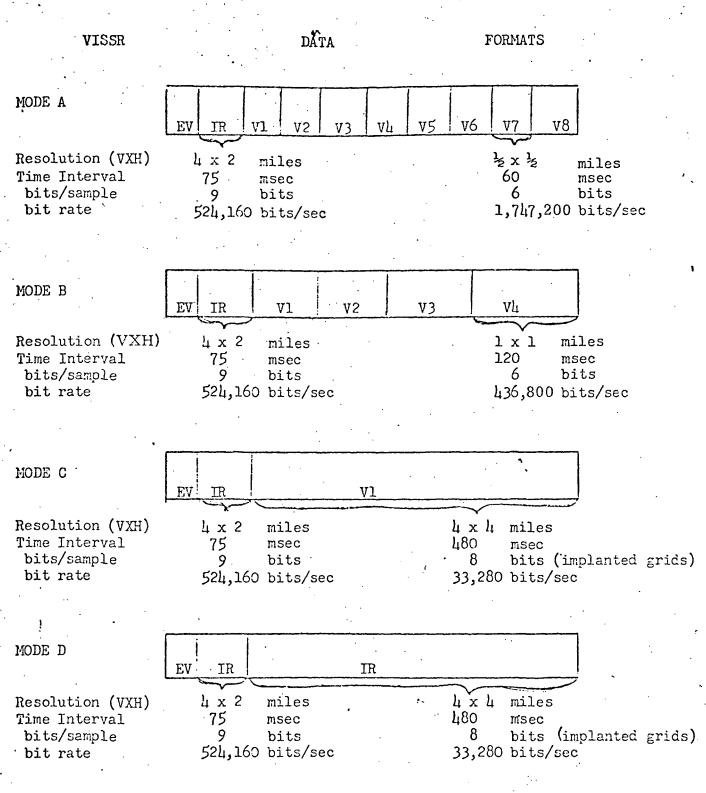

APPENDIX A - SMS VISSR Data Formats

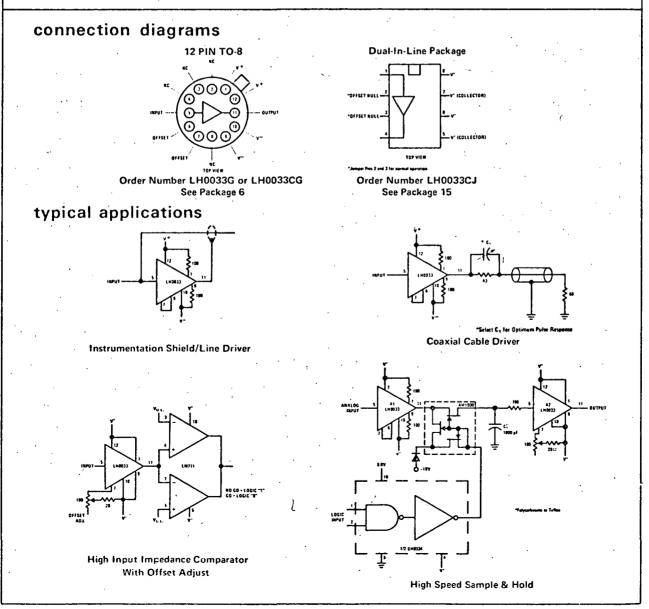

APPENDIX B - Miscellaneous Data Sheets

APPENDIX C - Digital Interface Bit Assignments

## Schematics

#### LIST OF FIGURES

#### CLOUD-TRACK QUALITY CONTROL

- FIGURE 1 Occurrence of Best Match Coefficient on Boundary

- FIGURE 2 Image Match Surface Parameterizing Comparison of Multiple Peaks

- FIGURE 3 Match Surface Arrays of Same Cloud Target over Two Different Time Intervals

- FIGURE 4 Alignment of Two Match Surfaces at Coincidence of Best Match Coefficients

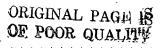

- FIGURE 5 U and V Velocity Residuals of Wind Sets Measured over Two Independent Time Intervals

#### SMS CLOUD HEIGHTS

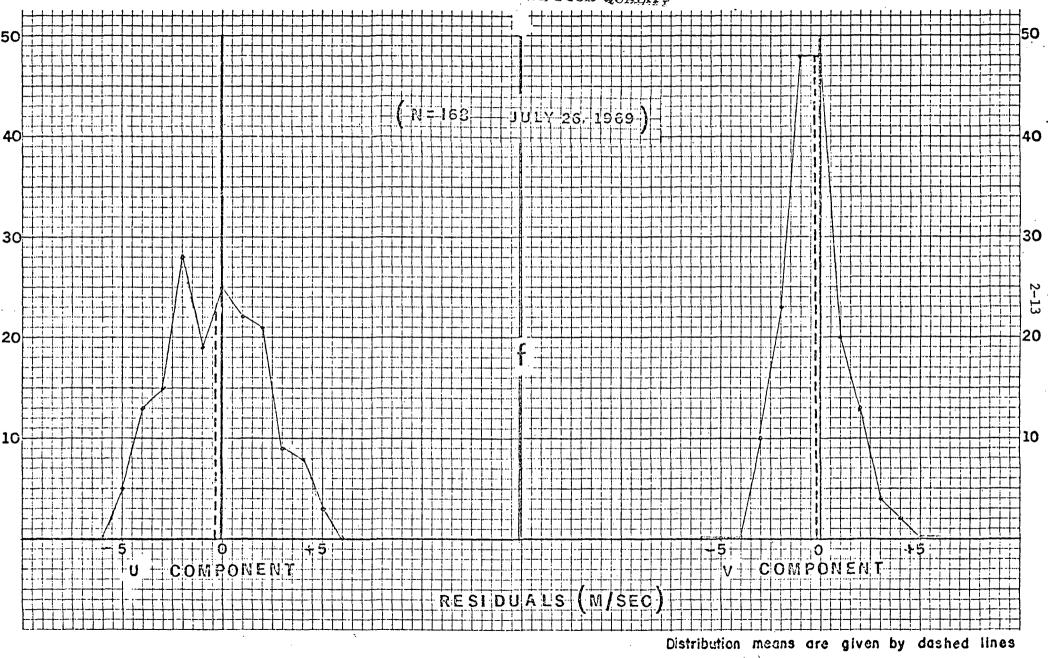

- FIGURE 1 Variation of the Brightness of a Cloud With and Without Sea Surface Albedo Correction

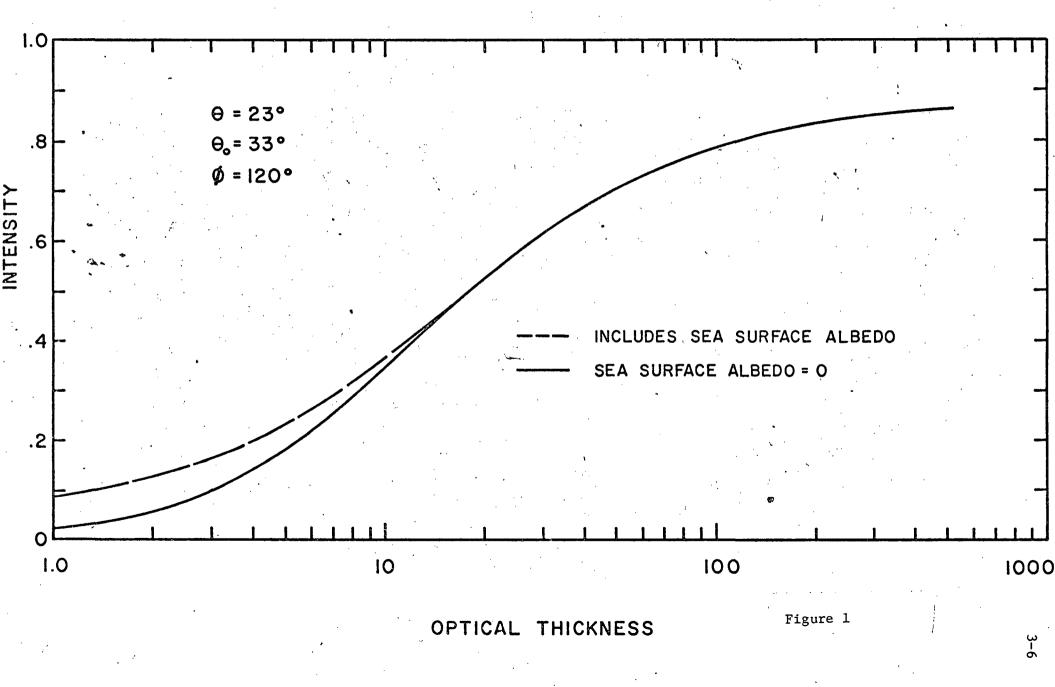

- FIGURE 2 Variation at the Brightness of a Cloud with Changes in the Particle Size Distribution

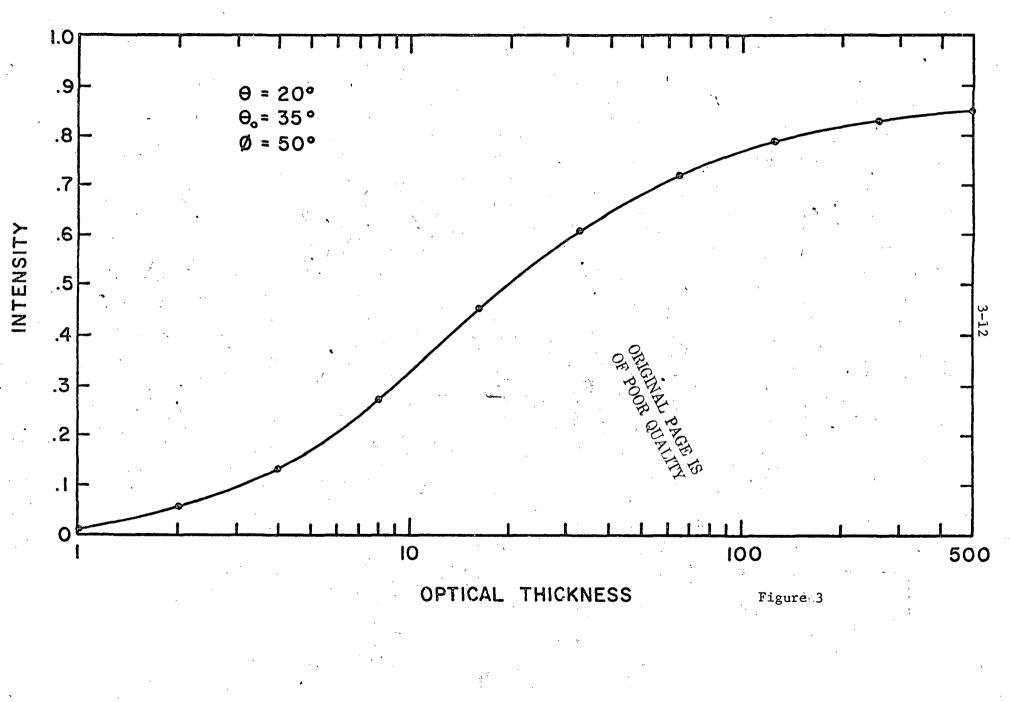

- FIGURE 3 Variation of the Brightness of a Plane Parallel Cloud with Changes in the Optical Thickness of the Cloud

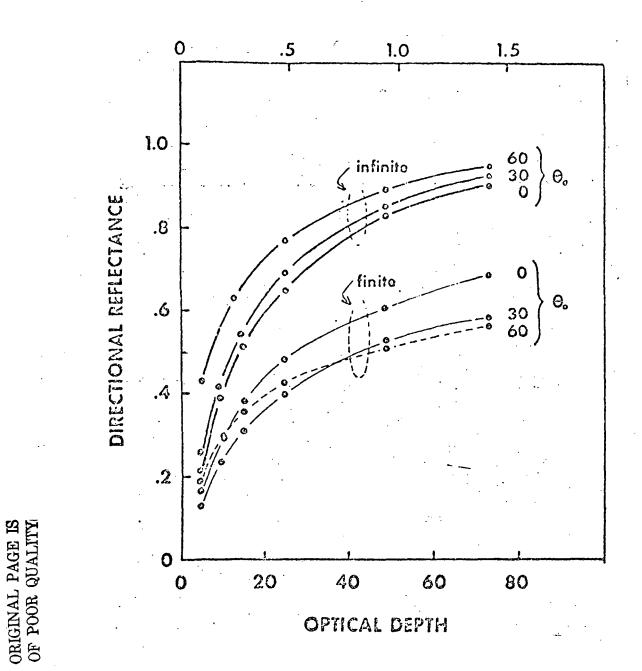

- FIGURE 4 Directional Reflectance of Infinite Clouds and Finite Cubic Clouds (from McKee and Cox, 74)

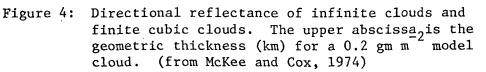

- FIGURE 5 Variation of the Emissivity of a Water Cloud for Different Optical Thicknesses

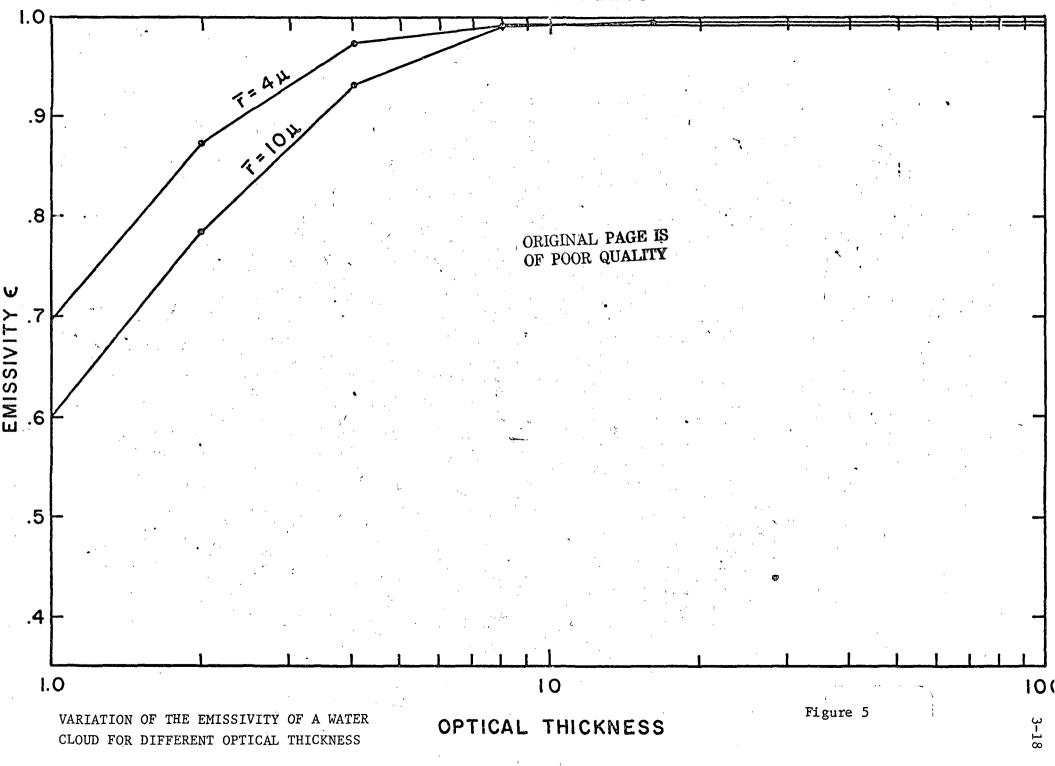

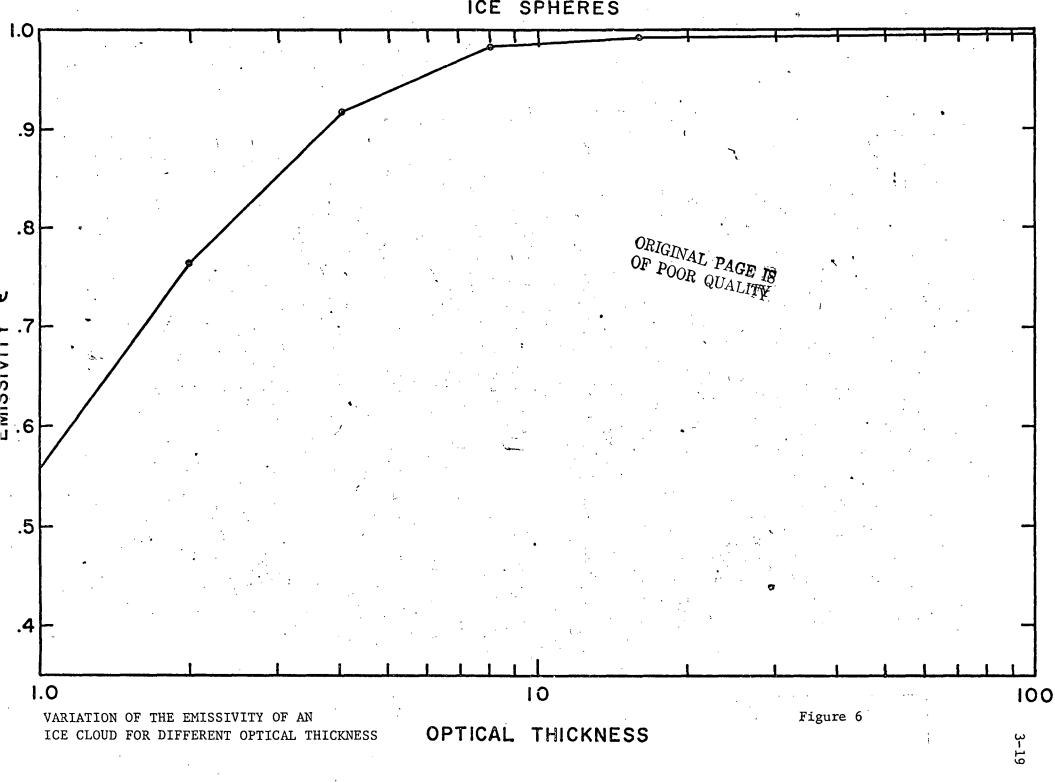

- FIGURE 6 Variation of the Emissivity of an Ice Cloud for Different Optical Thicknesses

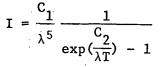

- FIGURE 7 Apparent Blackbody Temperature of Clouds for Different Optical Thicknesses

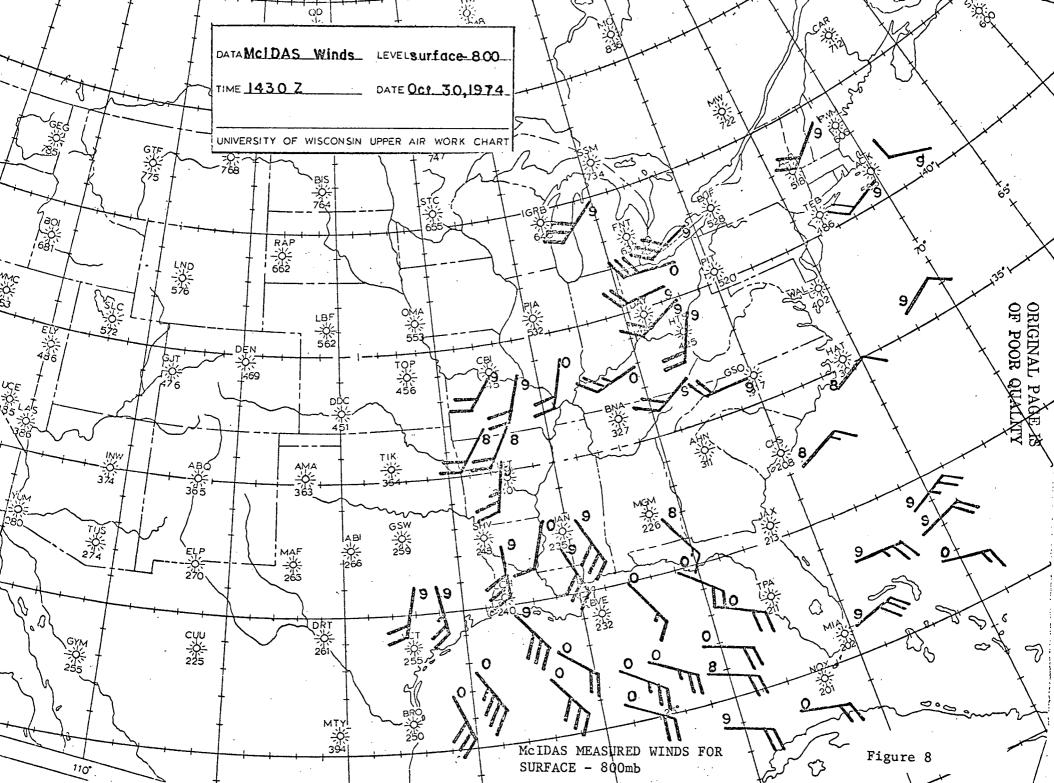

- FIGURE 8 McIDAS Measured Winds for Surface 800mb

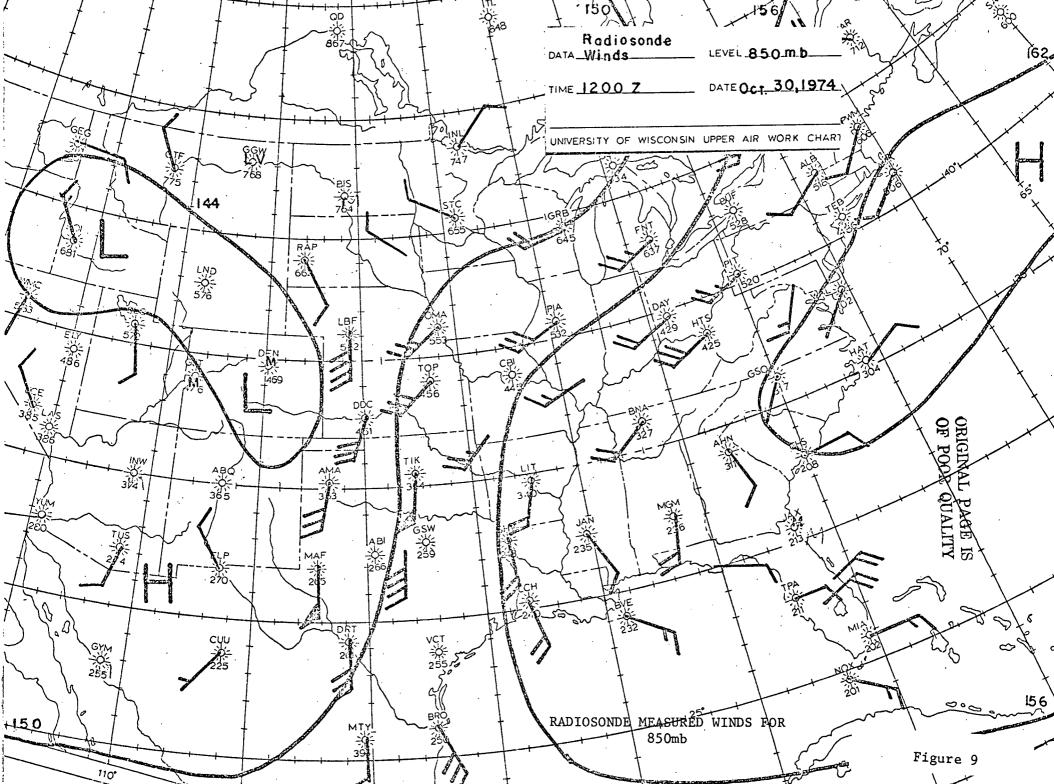

- FIGURE 9 Radiosonde Measured Winds for 850mb

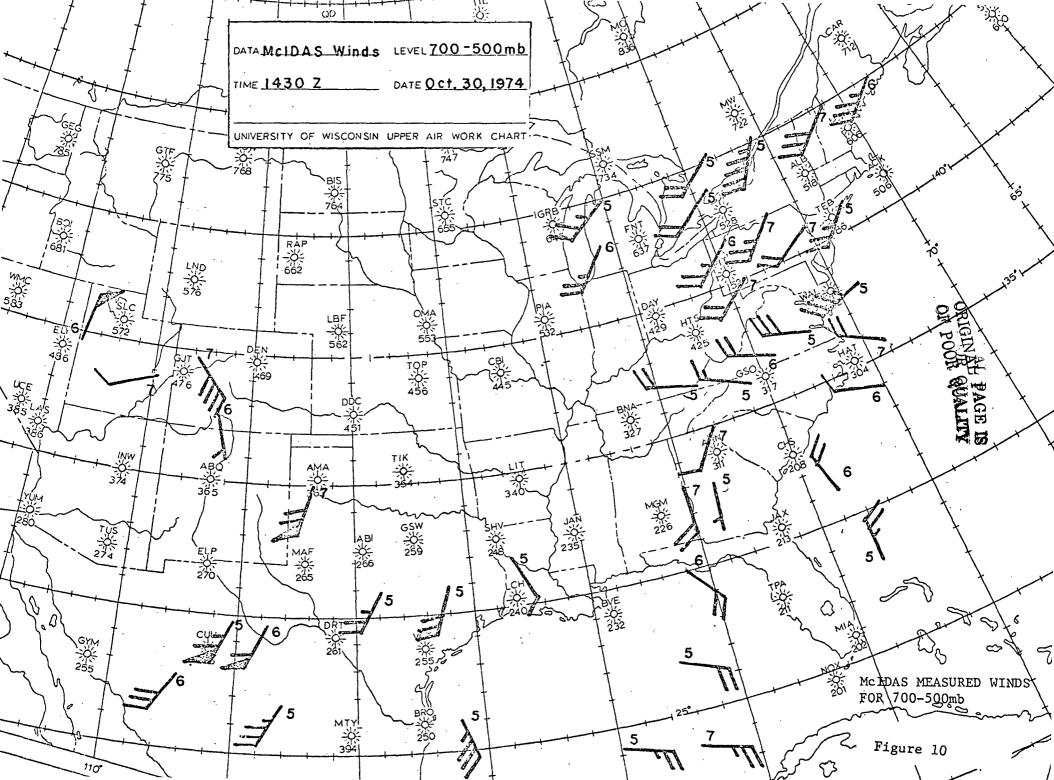

- FIGURE 10- McIDAS Measured Winds for 700-500mb

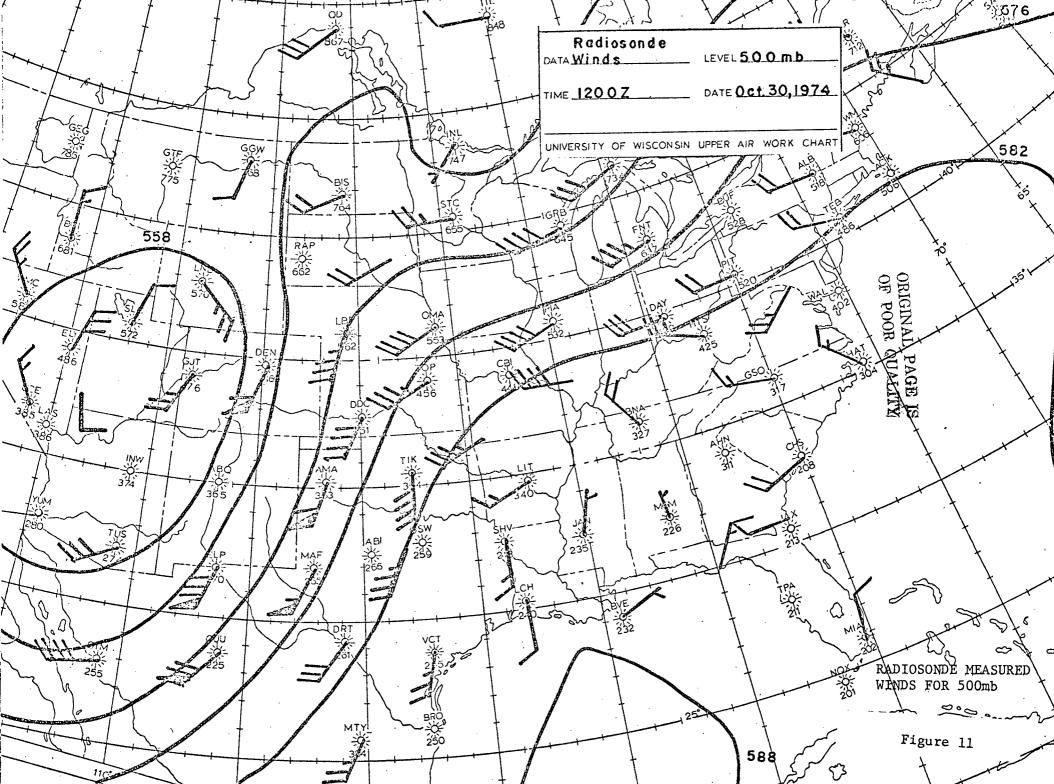

- FIGURE 11- Radiosonde Measured Winds for 500mb

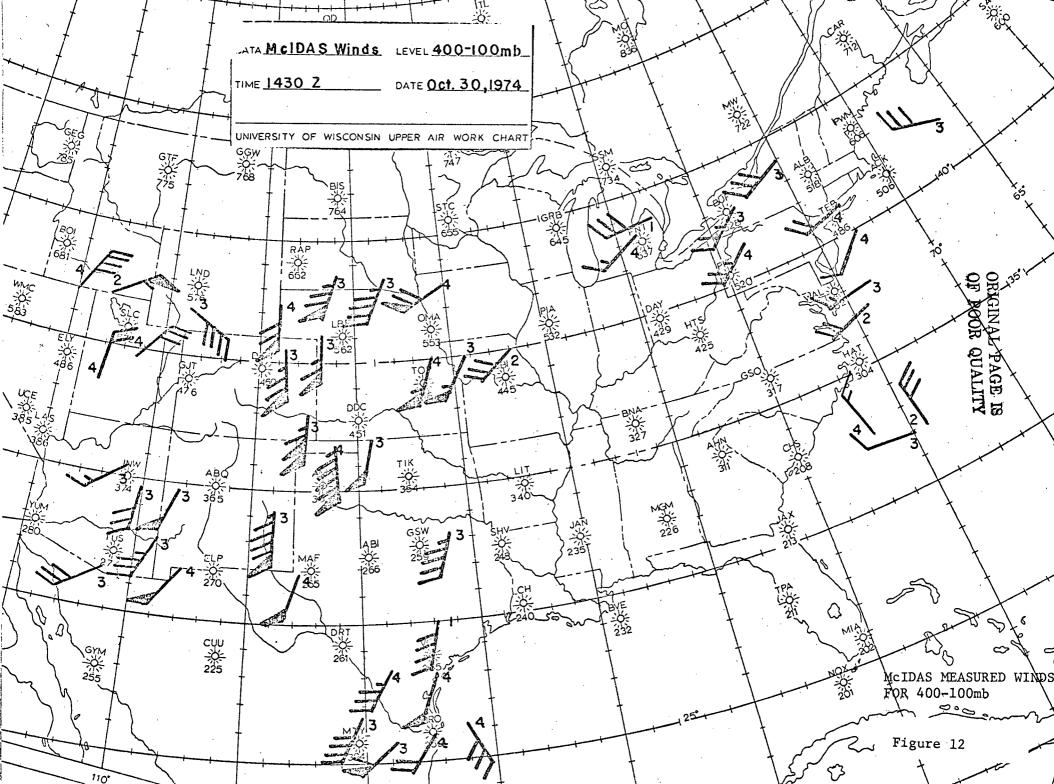

- FIGURE 12- McIDAS Measured Winds for 400-100mb

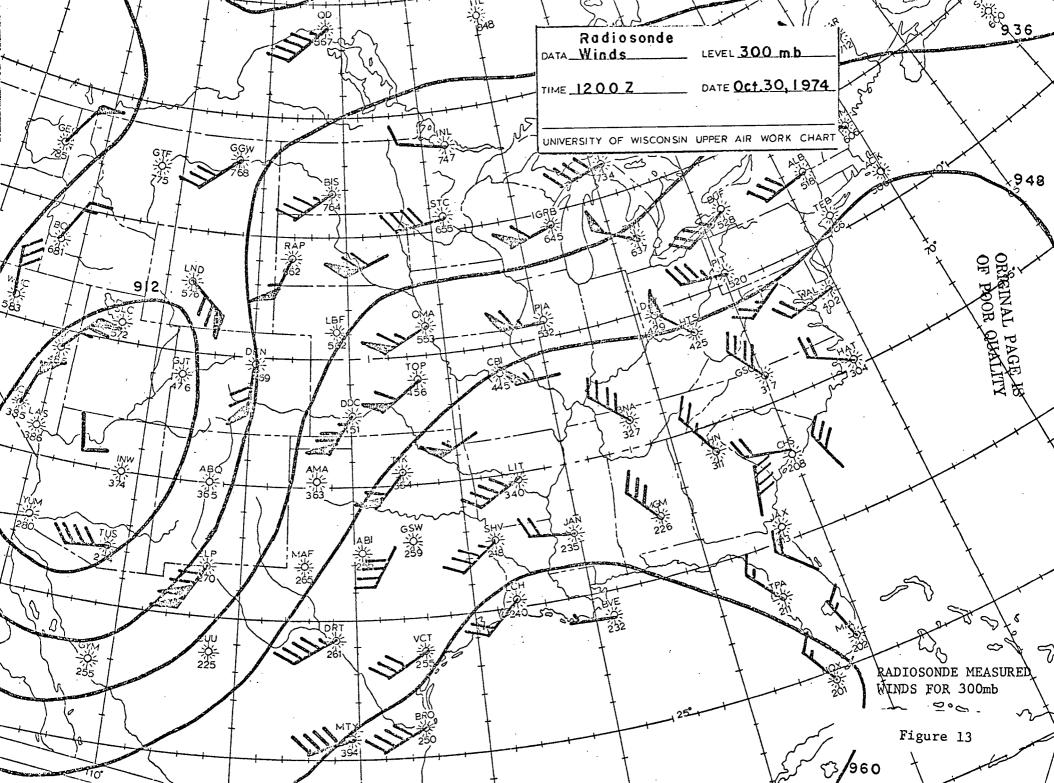

- FIGURE 13- Radiosonde Measured Winds for 300mb

## McIDAS FUNCTIONAL DESCRIPTION

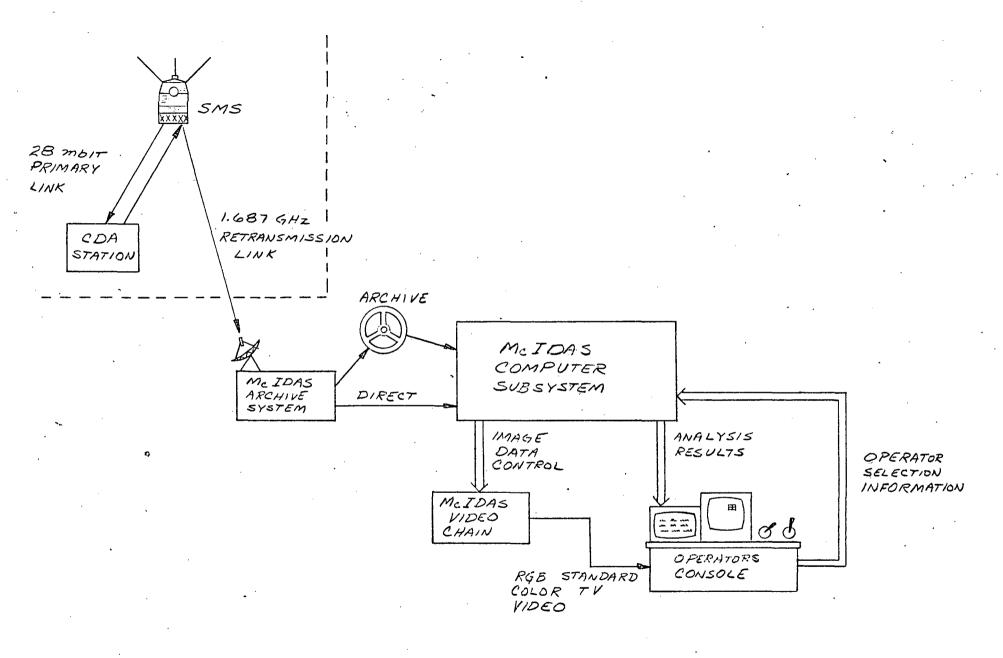

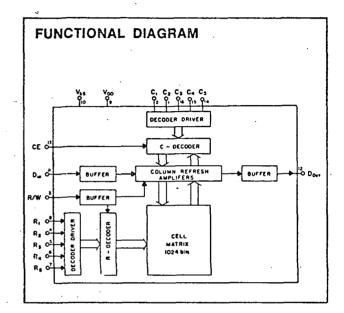

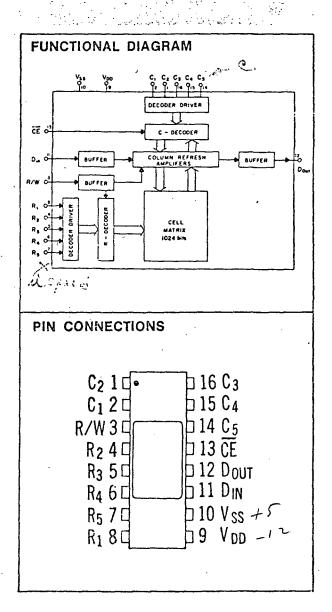

- FIGURE 1 McIDAS System Functional Block Diagram

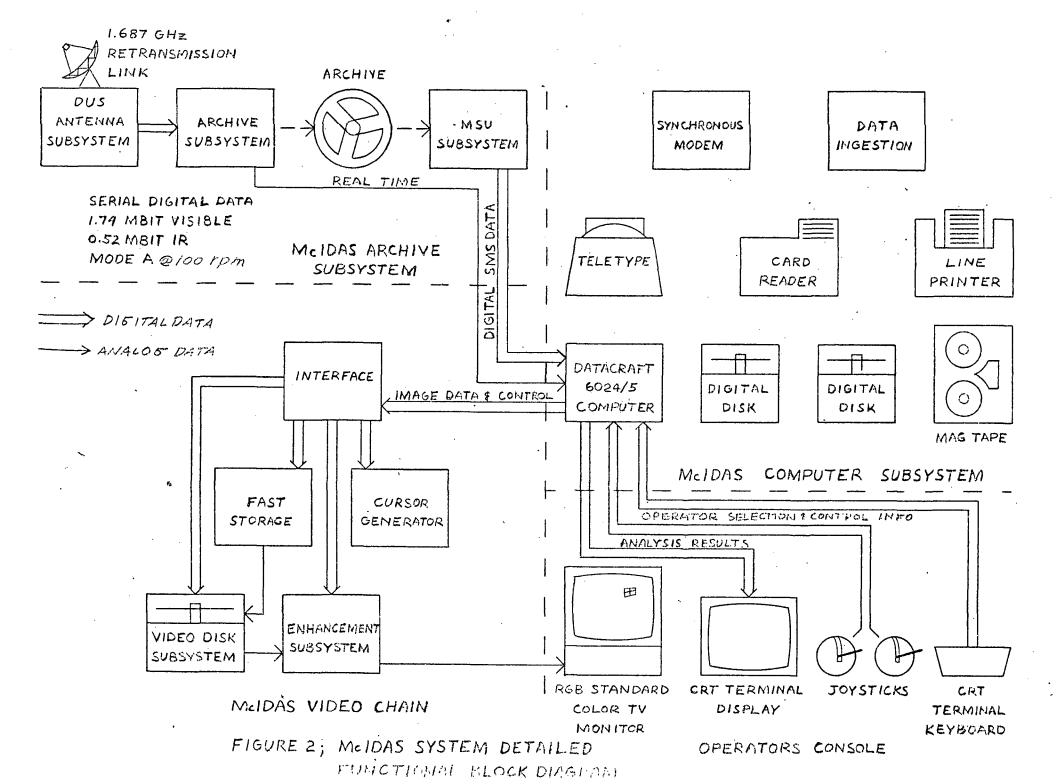

- FIGURE 2 McIDAS System Detailed Functional Block Diagram

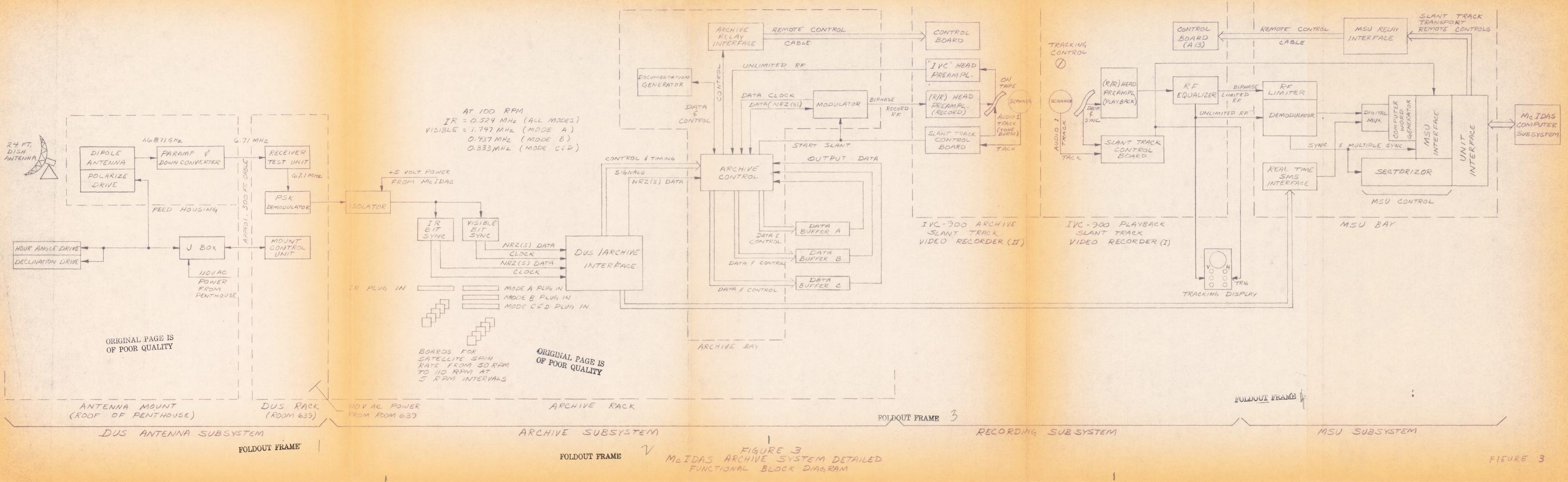

- FIGURE 3 McIDAS Archive System Functional Block Diagram

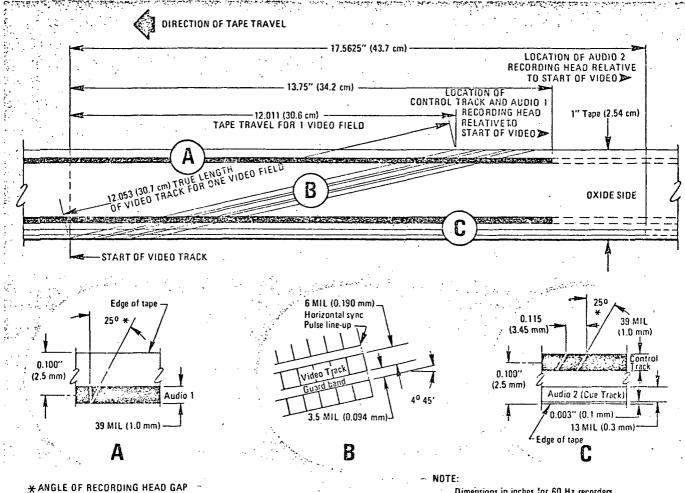

- FIGURE 4 Slant Track Video Recorder Tape Format

- FIGURE 5 Documentation Data Format

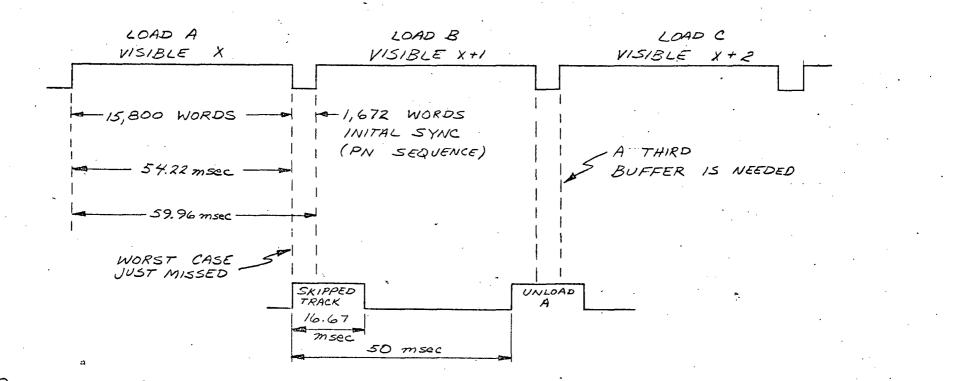

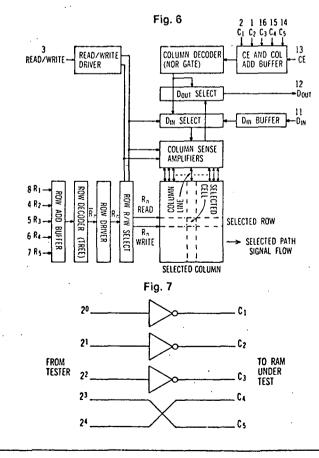

- FIGURE 6 Data Buffer Load/Unload Sequence

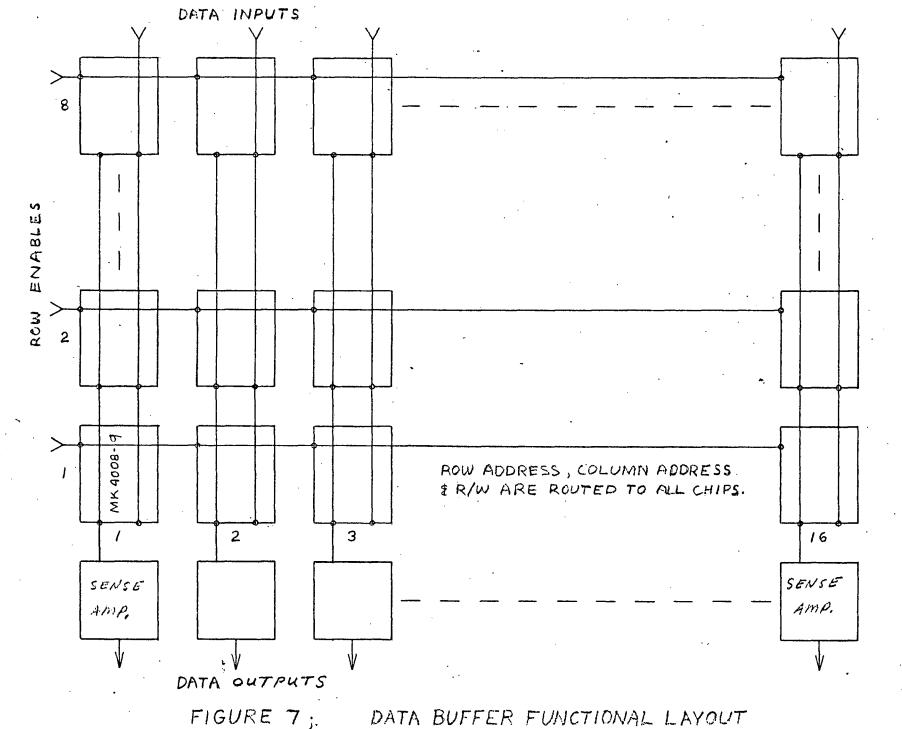

- FIGURE 7 Data Buffer Functional Layout

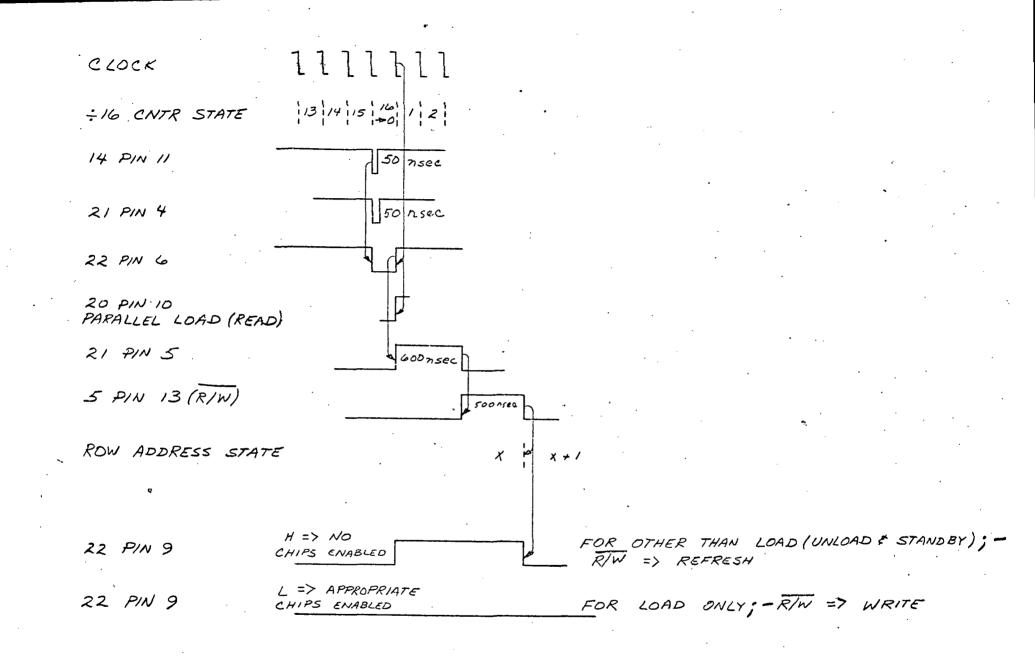

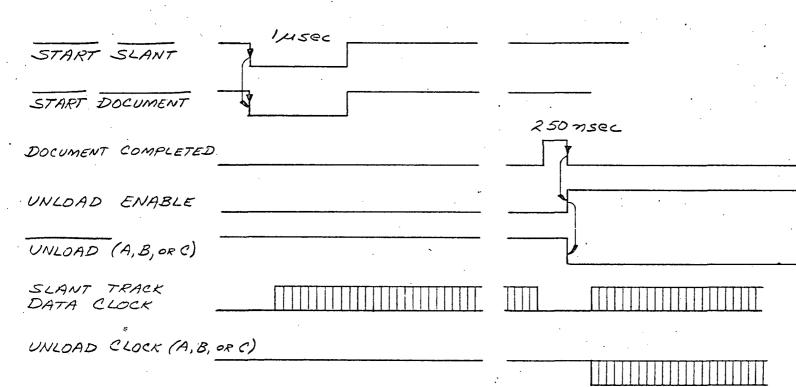

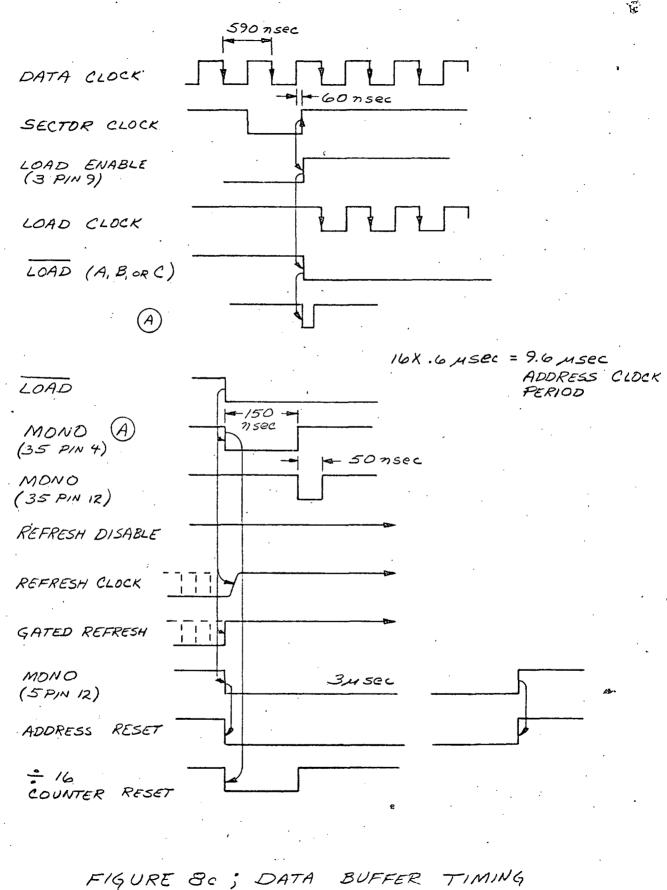

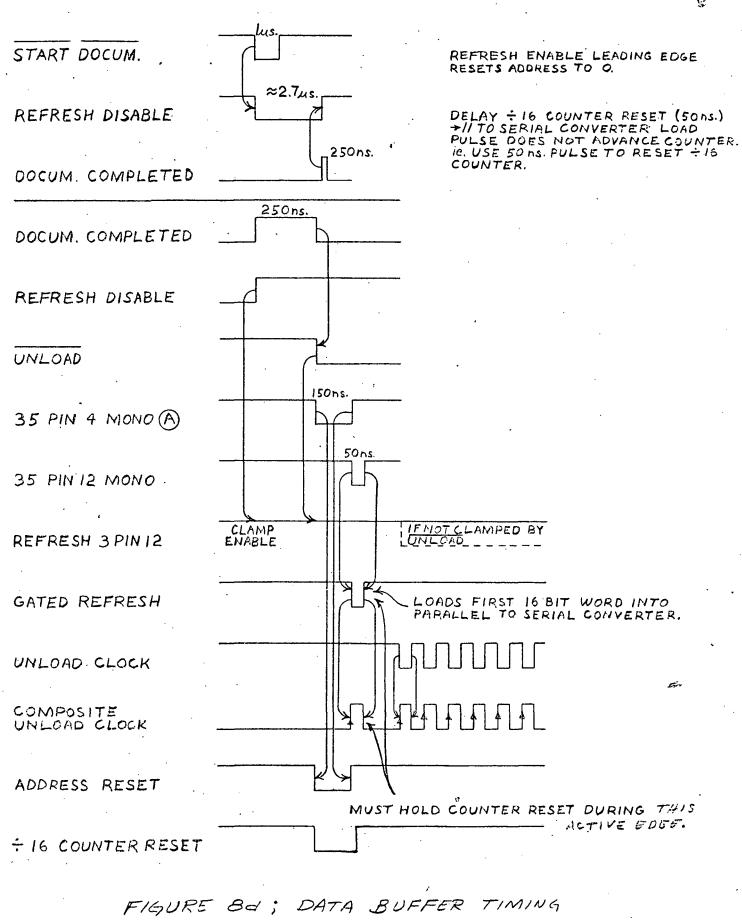

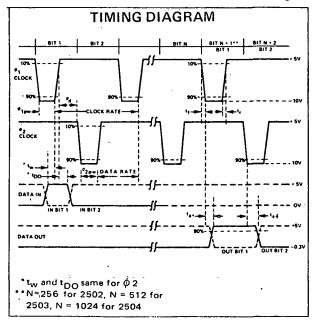

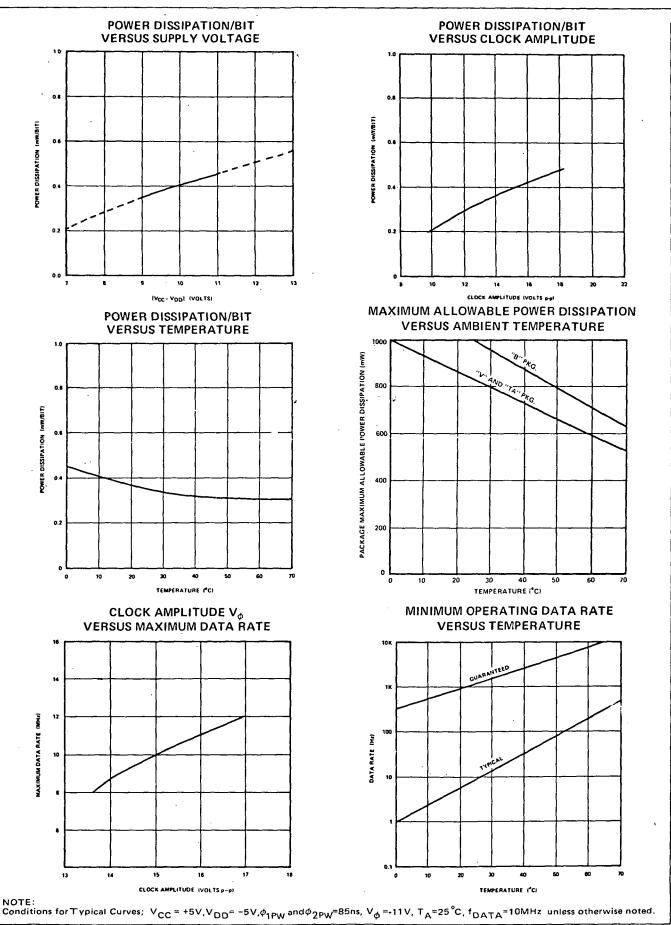

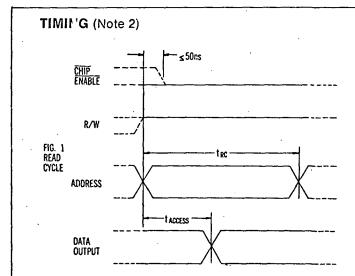

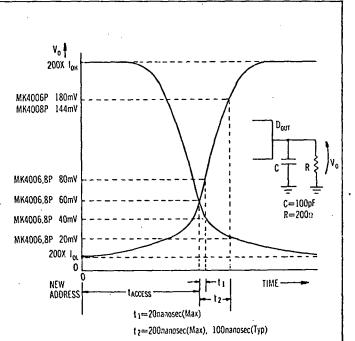

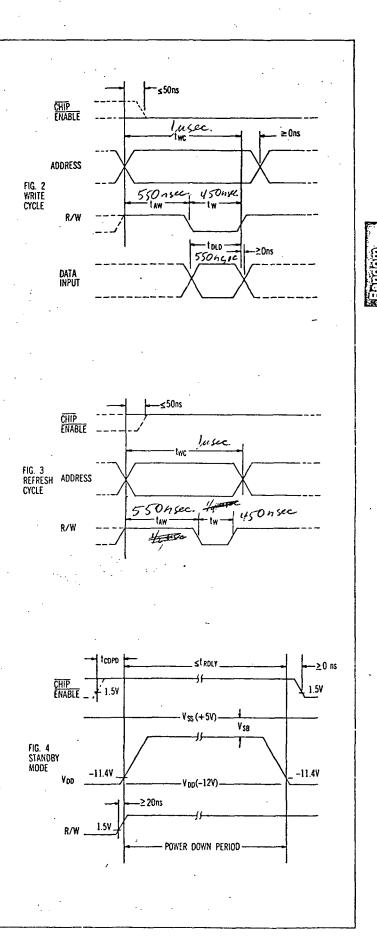

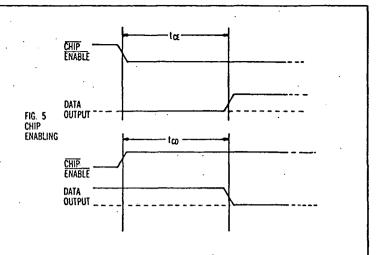

- FIGURE 8 Data Buffer Timing

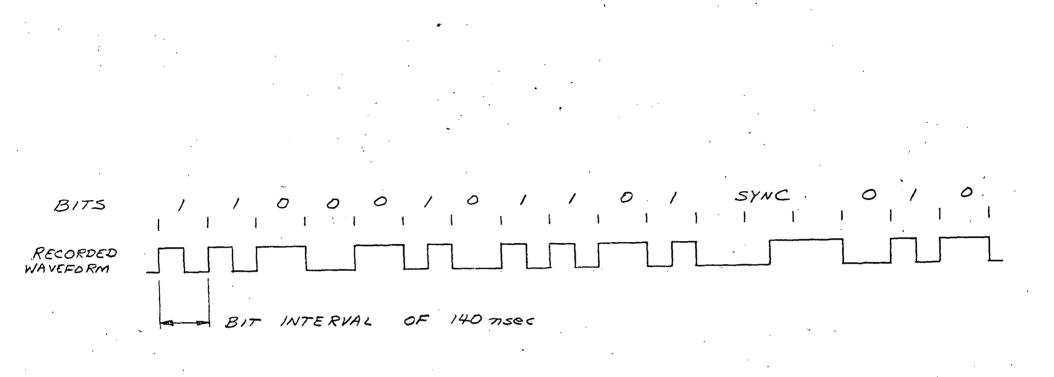

- FIGURE 9 Biphase Encoding Format

- FIGURE 10 Archive Track Format

- FIGURE 11 McIDAS Video Chain Functional Block Diagram

- FIGURE 12 McIDAS Video Chain Detailed Functional Block Diagram

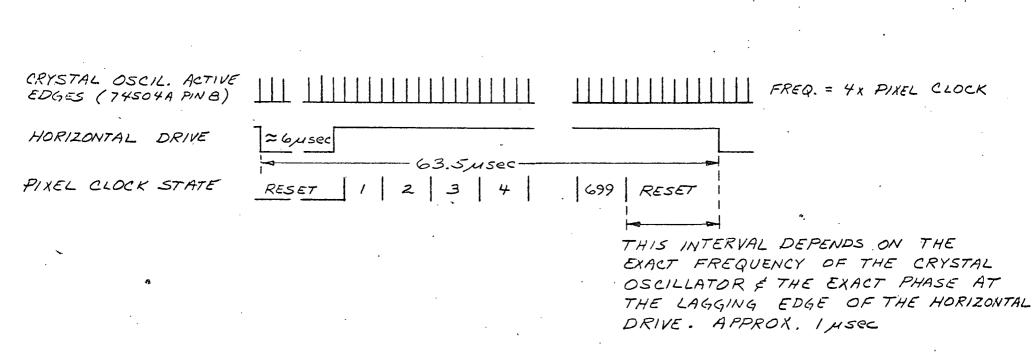

- FIGURE 13 McIDAS Video Chain Timing Format

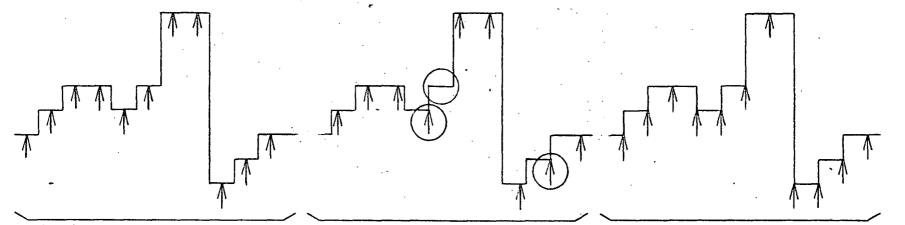

- FIGURE 14 Resampling Comparisons

- FIGURE 15 McIDAS Computer Subsystem Functional Block Diagram

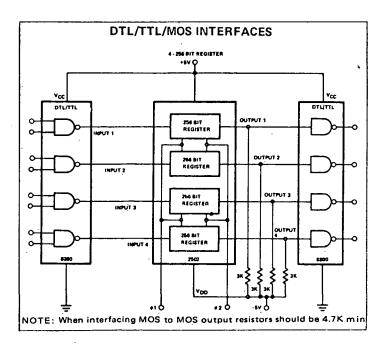

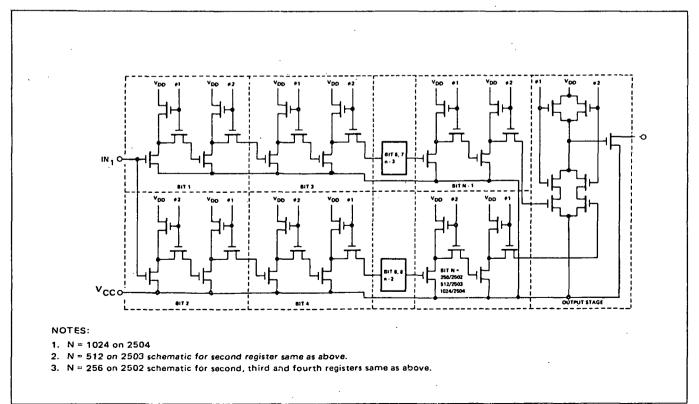

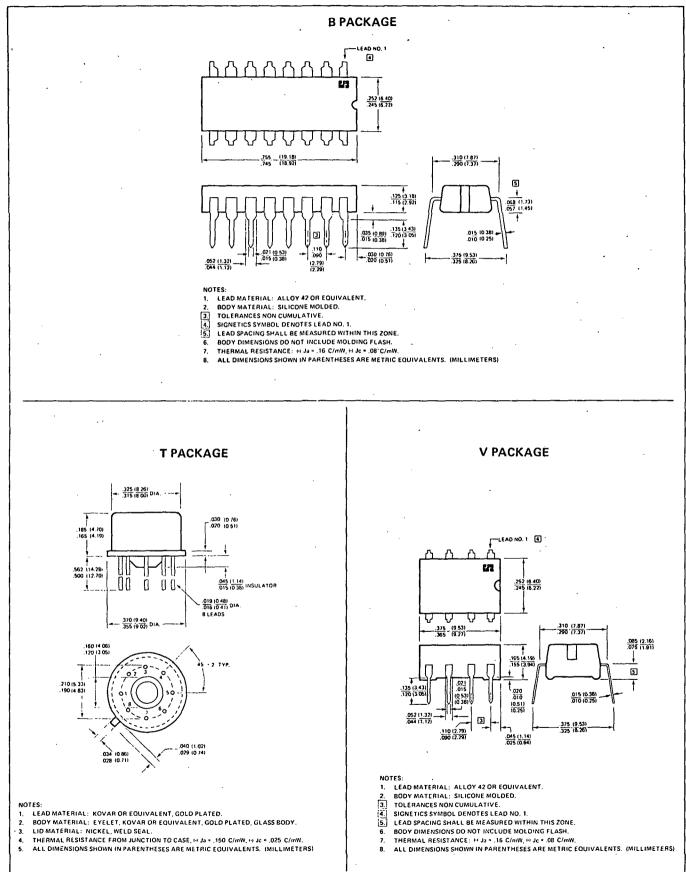

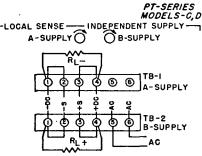

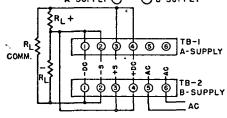

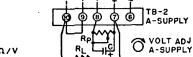

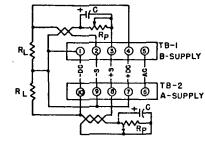

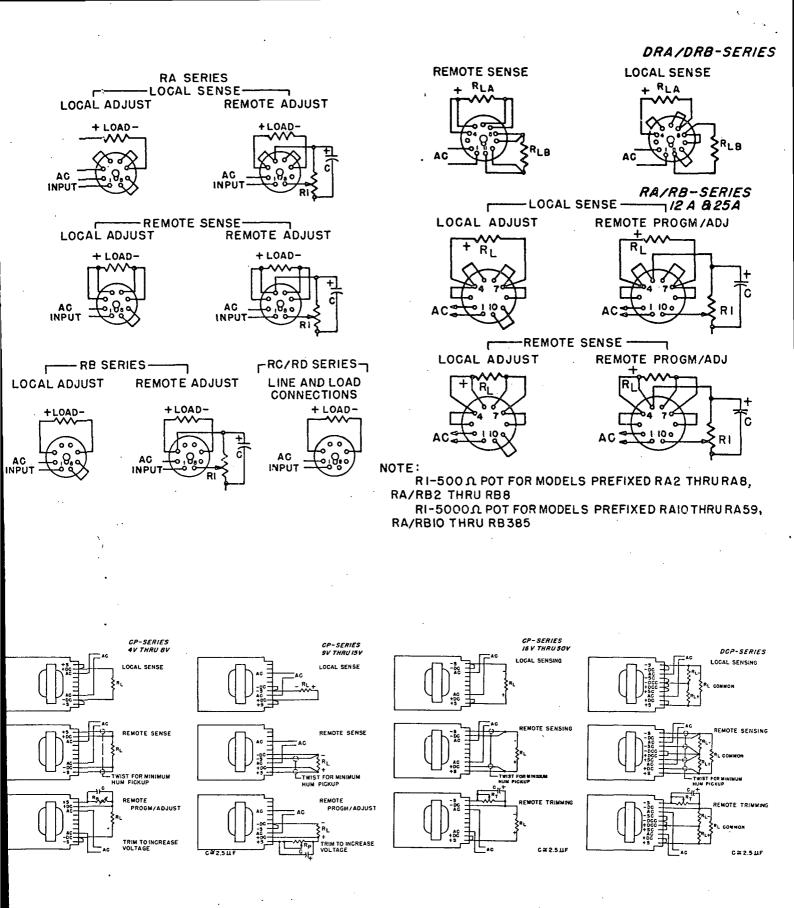

ARCHIVE SYSTEM

SMS Isolator

DUS/Archive Interface (Not available at this time)

DUS/Archive Interface Data Stripper and Display

Archive Control

Archive Control Layout

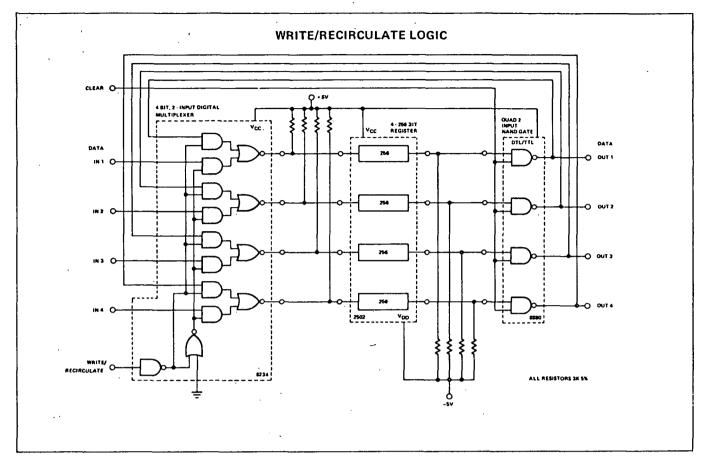

Data Buffer

Data Buffer Layout

Data Buffer Memory Board Layout

Documentation Generator

Modulator

Head Clog Monitor

Archive Relay Interface

Slant Track Control Board

RF Limiter

Demodulator

MSU Control

MSU Relay Interface

Universal 24-bit Unit Interface (Set of 5)

Archive Power Box

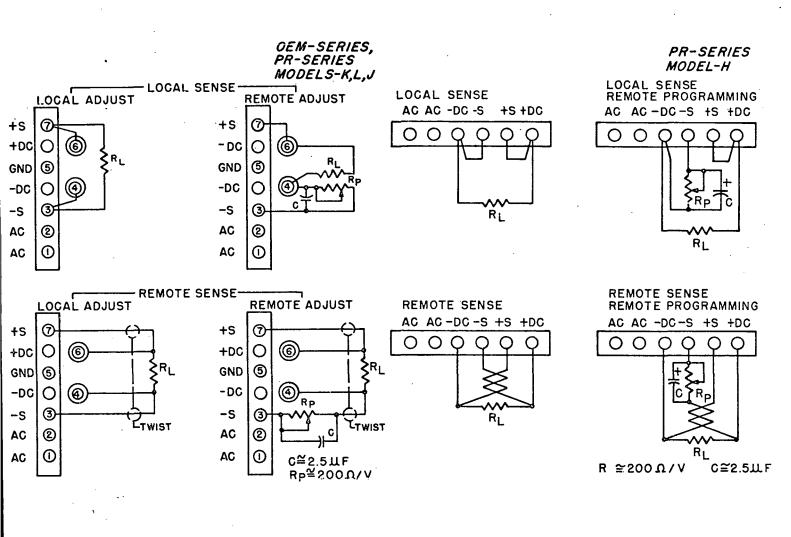

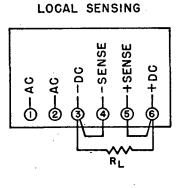

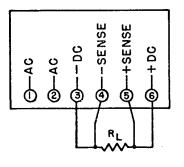

VIDEO CHAIN

McIDAS Unit Interface

Digital Interface No. One or Two (Set of 2)

Fast Storage

DR-10A Stepper Interface

DR-10A Record Interface

DR-10A Disc Monitor

DR-10A Playback Interface

Enhancement Table (Set of 2)

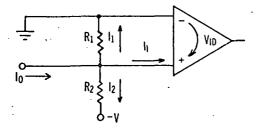

Analog Distributor

Address Multiplexer

Digital Multiplexer

Video Sequencer

Timing Generator

Digital Cursor

Level Discriminator

Subsystem Interconnection Diagram Cabinet #1 Subsystem Interconnection Diagram Cabinet #2 Data Ingestion System (Set of 2) ز يوتو

### PREFACE

This is the final report of work performed under NASA Contract NAS5-23296 during the period from 13 August 1973 to 11 December 1974. The report includes the complete functional descriptions and schematics for all of the subsystems of the Man-computer Interactive Data Access System (McIDAS). This documentation of McIDAS is the deferred portion of the final report on Contract NAS5-21794 also. The many minor changes in the McIDAS hardware which have been made during the past 18 months are incorporated in the schematics; therefore the documentation set represents the full shaken-down version.

The sections on Cloud-Track Quality Control and SMS Cloud Heights describe major portions of the cloud-track wind measurement technique developed at SSEC. Other major segments such as Navigation and WINDCO have been described earlier. It should be noted that development and refinement of all portions of the cloud-track wind measurement system are continuing. Therefore, one may expect that details of the system descriptions contained in this report will differ increasingly from current practice as time goes on.

I would like to thank the authors of several sections of this report for their excellent work. We all recognize that the number of people who have contributed to our successes in the McIDAS effort has been large and I view their work with grateful admiration. Not the least of those who have helped us has been Mr. Jim Greaves, GSFC Technical Monitor of McIDAS work. Jim has combined patience with insistence, understanding with firm direction, flexibility with highest integrity to establish a most effective and enjoyable relationship between ourselves and the National Aeronautics and Space Administration.

Verner E. Suomi Principal Investigator

#### ARCHIVING SMS DATA DURING GATE

GARP Data Systems Tests and the GATE program have requirements for rather sophisticated SMS image processing for the extraction of meteorological information. The McIDAS incorporates many of the needed extraction techniques provided it has a high quality readily accessible data base. The archive system developed under this contract provides that base.

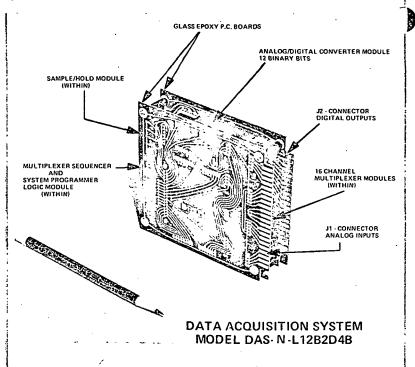

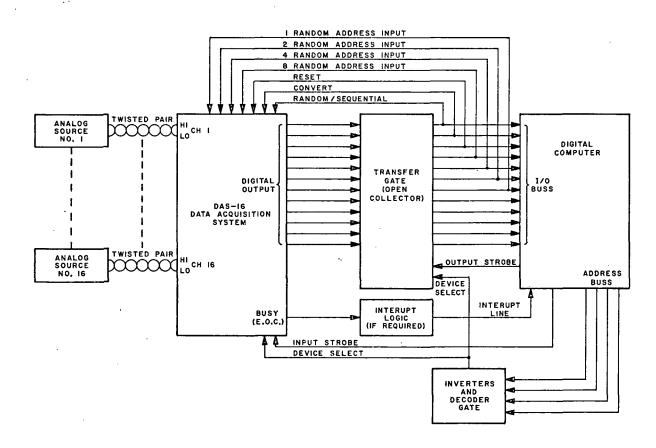

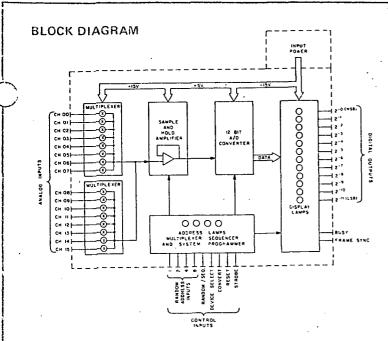

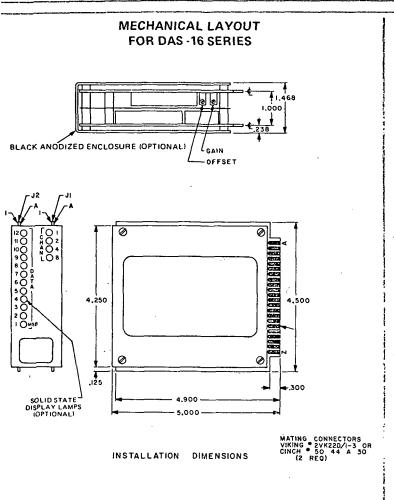

The archive system consists of a 24 foot parabolic antenna, the receiver and controller, interface electronics, data buffers and an IVC video slant track recorder. The storage capability is approximately 32 full resolution SMS images per reel of tape. This represents about 5 x  $10^{10}$  bits per reel.

Beginning in May 1974 plans were laid for the manning and training of personnel for the 24 hour archiving effort during GATE. Manuals, logging forms, etc. were prepared and students hired in anticipation of a 15 June starting date. However, due to NASA-NOAA system testing, archiving was not started until 27 June 0830 GMT. The training of the archive personnel (students) was accomplished by previously checked out staff members during the first two weeks of archiving. Archive quality checking was done on a nearly daily basis by displaying 12 samples of data from each data tape on the McIDAS system. Visual inspection was the only evaluation technique used. Only two minor problems were observed in the data until 8 August. One problem was bad chips in the data buffers which resulted in loss of approximately 1% of the data in each image. This was a continuing problem throughout the entire archive period as replacement of bad chips frequently caused others to fail. The other problem was the occasional (.2% per image) scrabbling of a line of data due to a dropped data bit. This problem was

eliminated in the first week of archiving. In total, equipment failures caused the loss of 96 images. One-third of each of 45 additional images were also lost due to an incomplete fix of one of the equipment problems. The period of this data loss was 1630 GMT, 6 August to 1800 GMT, 9 August. A second data recording problem effected data (184 images) between 1030 GMT, 12 September and 0400 GMT, 16 September. The problem was a drift in the alignment of record slant track recorder. The data quality is very high, but playback requires continuous manual adjustment of the playback recorder alignment. Archiving was completed as of 2350 GMT, 28 September 1974 at the end of GATE.

The statistics for the archive are as follows:

| 4437 | Images transmitted                                       |

|------|----------------------------------------------------------|

| 4    | Images missed by operator errors                         |

| 96   | Images unusable due to equipment failure                 |

| 4337 | Usable images recorded (97.75%)                          |

| 45   | Degraded (noisy third line)                              |

| 4292 | High quality images recorded (96.75%)                    |

| 184  | Difficult to read                                        |

| 4108 | Operational usable high quality images recorded (92.59%) |

## CLOUD-TRACK QUALITY CONTROL

#### INTRODUCTION

Any set technique for tracking cloud motions has inherent limitations on the accuracy of its results. If such tracking errors can be reduced by discarding apparently bad measurements, the value of the remaining wind vectors increases due to their increased reliability. However, bad measurements cannot be discarded without losing some accompanying good measurements. Quality measurements, compensation for missing data, and smoothing techniques can provide vector sets which will produce a better estimate of the wind field than will a data set containing spurious anomalies that distort the true circulation. This philosophy has guided the selection of a number of wind quality control criteria which discard measurements with a high probability of being in error while maintaining the through-put of the McIDAS.

How can such criteria be set? The image match procedures on the McIDAS determines a cloud's displacement based on the similarity of cloud features from two different satellite images taken over the same area at two different times. If this similarity satisfies a 'best fit' criterion in comparison to all other lag positions under consideration, that displacement is assigned to the cloud's motion. If the image match procedure is determined to have failed or to be below acceptable quality based on further criteria, that measurement will be discarded.

Four such criteria are discussed in this report. In the SSEC McIDAS these quality control criteria are combined with an operator's careful judgement to minimize the possibility of a bad measurement being accepted by the system.

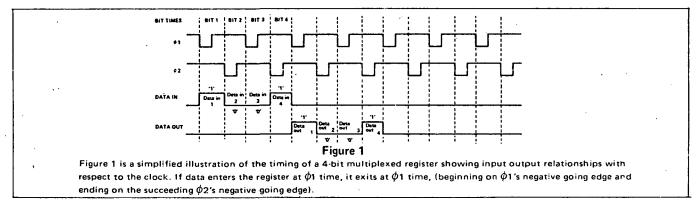

Three techniques are applied during the image matching process; the last technique is not utilized until after wind vectors have been generated. Two methods require wind vector pairs separated by a time interval of 30-60 minutes. McIDAS wind computation is a cloud tracking process, which accumulates cloud motion measurements by tracking individual cloud targets in three (or more) successive image frames. This process provides at least two successive independent wind estimates which can be compared. The SSEC image matching techniques use a cloud target grid at time t, along with a larger data match grid at time t, containing the cloud target. An image matching grid is generated by the application of one of several metrics. The image match grid is composed of lag coefficients for each lag position the small target grid  $(t_1)$  can take with respect to the larger data match grid  $(t_2)$ . These lag coefficients are scanned for the best match coefficient. The position of the best match coefficient is generally defined as the occurrence of the greatest relative maximum on the image match surface.

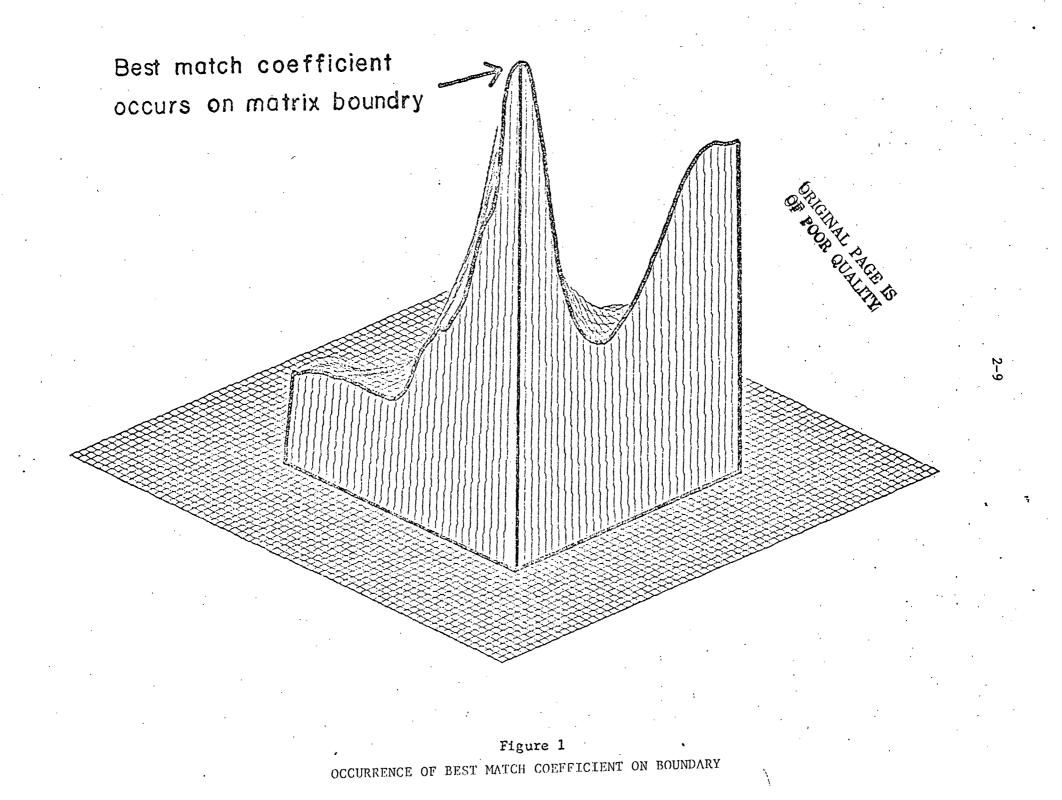

## TECHNIQUE 1: Best Match Occurrence on Matrix Boundary

Since the image match procedure is dependent on finding a relative maximum on the match coefficient surface, the occurrence of a maximum on the boundary of the match coefficient array prevents the confirmation of a local maximum. A match coefficient which occurs on the boundary of an image match coefficient matrix is illustrated in FIGURE 1. These cases are marked with a type 1 error code and can be discarded by the system. TECHNIQUE 2: Secondary Peak Comparison

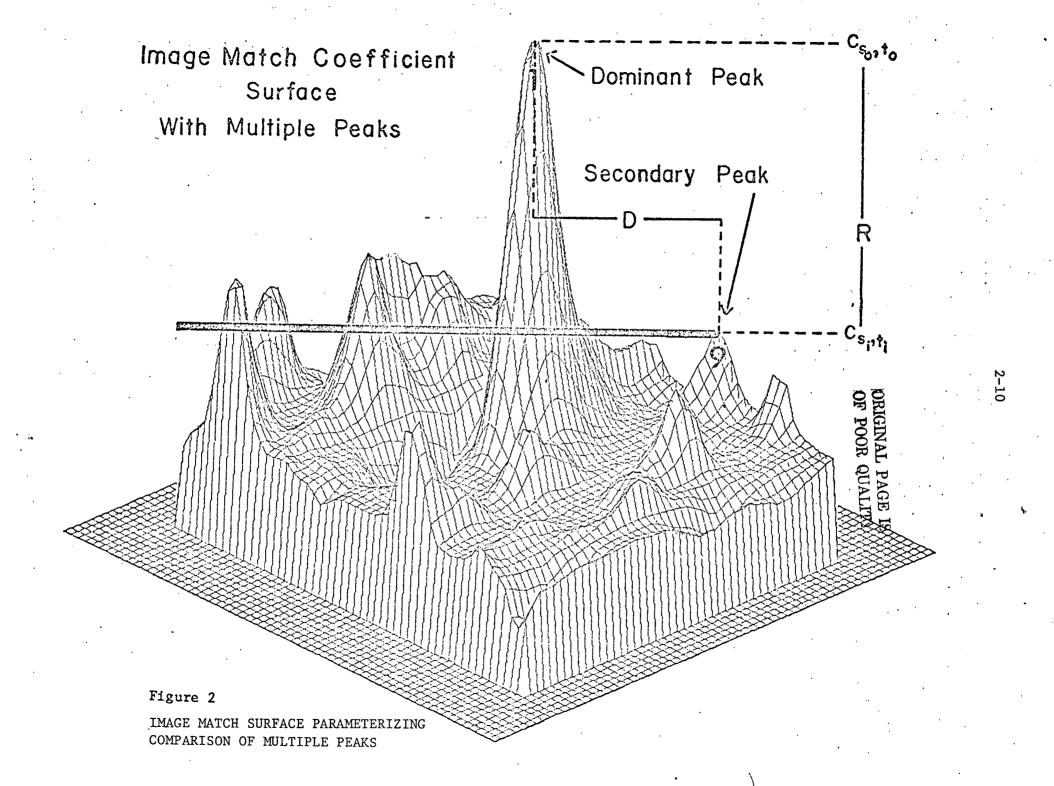

Generally, an image match surface has more than one relative maximum. We distinguish the greatest relative maximum as the best match coefficient.

Other relative maxima are referred to as secondary peaks of the image match coefficient surface. It is natural to compare secondary peaks to the best match coefficient. These peaks may represent a number of possibilities. Leese has suggested that, in certain cases, they represent cloud displacements of the non-predominant cloud layers contained in the target grids. Our investigations have shown that, generally, these peaks represent spurious target matches, noise spikes and echo peaks in the image match surface. FIGURE 2 illustrates an image match coefficient surface containing multiple peaks.

We have tried to develop a basis for deciding which relative maximum indicates the true cloud displacement. Our analysis of image match surfaces has revealed that secondary peaks are basically spurious alignments unless they occur close to the absolute maximum or compete in size comparison. Our criterion for a good measurement is a well defined dominant peak, as indicated in FIGURE 2. Quality control can be applied whenever the surface analysis indicates an ambiguous case.

The surface analysis technique determines three characteristics of secondary peaks with respect to the dominant peak. FIGURE 2 illustrates these characteristics with respect to peaks 1 (dominant peak) and 9 (secondary).

- a. Difference between secondary peak and dominant peak coefficients (R)

- b. Distance between secondary peak and dominant peak positions (D)

- c. Area dominated by stronger peaks with respect to secondary

peak (surface area above thick horizontal line) These characteristics are determined as follows:

Consider a  $t_1$  target grid of size k lines by  ${\tt l}$  elements and a larger

$t_2$  match grid of size m lines by n elements. These grids will generate a (m-k+l) by (n-l+l) image match coefficient grid C. Let p be the number of line lags of C such that,

$$\mathbf{p} = \mathbf{m} - \mathbf{k} + \mathbf{1}$$

and q be the number of element lags where

$$q = n - \ell + 1.$$

Let  $c_{(s,t)}$  be the image match coefficient of matrix C at lag position (s,t) where s=1, p, t=1, q. Let Y be the set of image match coefficients of C greater than or equal to c (s,t). Then, c (s,t) is a secondary peak if and only if no entry of Y is a neighboring point to c (s,t). A neighboring point is defined as a point adjacent to the  $c_{(s,t)}$  in question. Note that the dominant peak is also considered a secondary peak in this context. An algorithm which systematically finds necessary peaks in decreasing order of their magnitude is as follows. Let the indices (s,t) of C be ordered in an array D such that  $i \leq j$  implies that  $c_{(s,t)_i} \leq c_{(s,t)_i}$ . This is done efficiently with an oscillating tree sort. Then c(s,t), is necessarily the coefficient of the dominant peak and (s,t), is its lag position. Let N be the number of secondary peaks in C. A secondary peak position function  $f(j) = (s,t)_{i(j)}$  is defined for j=1, N. Let f(1) be the lag position of the dominant peak. The second value of f is found by testing the ordered lag positions in D following f(1) for the first one not adjacent to a prior position. This gives f(2) which is defined as  $(s,t)_{i(2)}$  where  $i_{(2)}$  is the index of the entry in the ordered lag index array D. Further secondary peaks are found in the same manner until the array D is exhausted.

The difference R, between the secondary peak coefficient  $c_{(s,t)}_{i(j)}$  and the dominant peak coefficient  $c_{(s,t)}$ , is tested against a constraint parameter. When one applies the Euclidean Norm, each match coefficient measures the square of the rms difference at that alignment position. There are three types of noise preventing zero rms difference at the correct alignment position; sampling noise, feature evolution noise, and random noise. The random noise is small since the comparison of cloud features is averaged over reasonably large areas. The sampling noise and the feature evolution noise are basically inseparable. However, if one has the additional information that large smooth features are under consideration, sampling noise will be smaller. One can estimate the total effect of the sampling noise and the feature evolution noise from the size of the minimum Euclidean Norm coefficient. The difference between the maximum coefficient and the next largest relative maximum coefficient should exceed this minimum Euclidean Norm coefficient for one to have confidence in the displacement measurement.

The distance D, between the secondary peak position  $(s,t)_{i(j)}$  and the dominant peak position  $(s,t)_1$ , is tested against a second constraint parameter. The index i(j), of the ordered lag position array D, corresponding to the total surface area dominating the secondary peak j, is tested against a third constraint parameter. If any of these tests fail, the cloud target is marked with a type 2 error code and can be discarded. TECHNIQUE 3: Image Match Surfaces Comparison

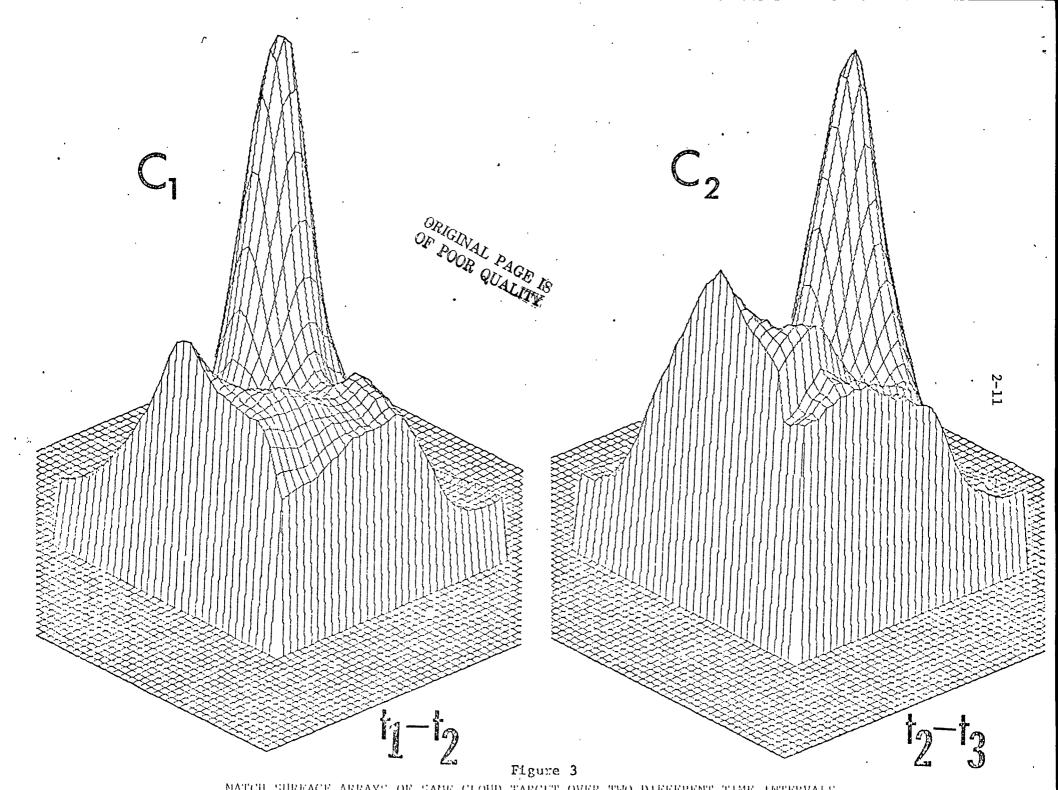

A relatively stable cloud target can be tracked over more than one time interval. A quality control technique can then be applied by comparing the respective image match coefficient surfaces from successive intervals. This comparison produces a cross correlation coefficient and measures both cloud target evolution and differential motion across the cloud field. FIGURE 3 shows two image match surfaces  $C_1$  and  $C_2$ , resulting from tracking

a cloud target over two adjacent thirteen minute time intervals. The similarity between the surfaces indicates that the cloud target was stable and that it was moving with its neighboring clouds.

For comparison, the matching surfaces are aligned so that the best matching coefficients from each matrix coincide. The resultant intersection contains two sub-surfaces which can be compared or correlated. FIGURE 4 portrays this alignment between two image match matrices. The cross correlation coefficient between the two sub-surfaces is an estimate of congruency which can be tested against a congruency threshold parameter. If the coefficient is below the criterion, the cloud target is marked with a Type 3 error code and can be discarded.

## TECHNIQUE 4: Acceleration Criteria

Wind measurements that are made removed from severe weather activity are expected to be smooth with respect to time. Hence, acceleration terms across a period of one hour are expected to be small. The McIDAS system enables an operator to select the same cloud target for displacement measurement over two or more successive time intervals. The software provides for the computation of acceleration terms (\*u and v component residuals) and further allows the discarding of wind measurements if the accelerations exceed set criteria.

Two acceleration terms are generated. The north-south components (v components) of two successive measurements are subtracted and tabulated into a table of intervals, yielding a v residual frequency distribution. The east-west components (u components) of the wind are treated identically. Plotting an acceleration frequency distribution yields two results. First, the spread of the distribution estimates the variance of the image matching technique's ability to resolve cloud displacements. Second, the shift of

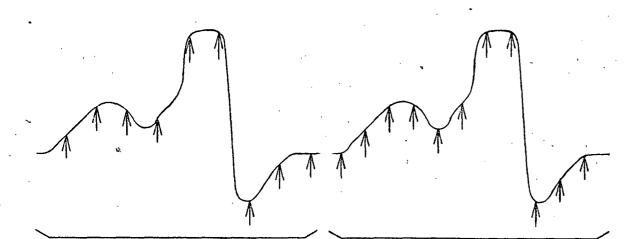

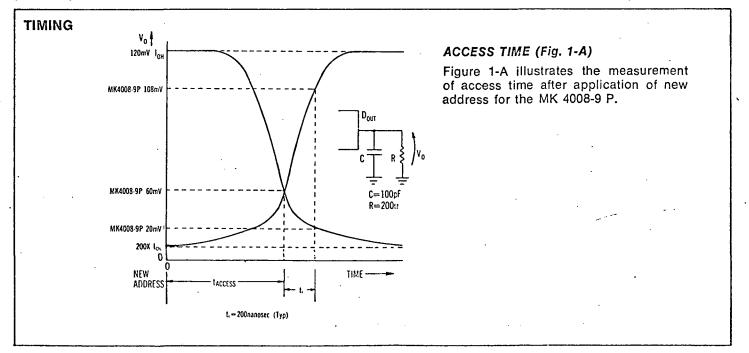

the mean value of the dispersion from the origin of zero acceleration estimates the acceleration bias induced in the wind measurements by the navigational scheme. FIGURE 5 illustrates such a table. Both u and v residual distributions are shown representing 168 vector pairs from July 26, 1969 ATS-III data.

Note that the mean value of each distribution is within 1 meter per second of zero acceleration. These differences provide a best estimate of navigational alignment accuracy. The spread of each distribution estimates the magnitude of random error in the measurments. Comparison of the distributions shows that the u component spread is greater than the v component spread. The larger variance is due to line jitter inherent in the ATS data, supporting the argument that the line step system is more stable than the line sweep system. Thus, the random error of the measurements can be constrained by discarding cases which exceed selected acceleration criteria. Cloud targets which do not meet consistency parameters are marked with a Type 4 error code.

There are meteorological situations with strong acceleration forces such as cyclonic or anti-cyclonic circulation, jet streams and frontal zones. Checks for u and v consistency (low acceleration restrictions) will discard valid measurements. Quality control in these instances requires either relaxing the u and v consistency constraints or checking other parameters. Two alternative consistency checks can be applied with the McIDAS software; these are a wind direction and absolute velocity check.

Clouc tracking is done in a lagrangian coordinate system. Since cloud displacements are associated with the dynamic flow, cloud target paths of known characteristics can be checked for verification. For example, if

winds associated with a jet stream are decelerating but not turning, a force on a cloud target is perpendicular to the direction of its motion, such as a cloud moving along the spiral of a vortex, the kinetic energy of the cloud mass ( $\frac{1}{2}mV^2$ ) is conserved. Hence the absolute velocity  $V = u^2 + v^2$  can be checked for consistency.

#### FUTURE DEVELOPMENTS

Future software will provide the system operator with more information on wind field quality. 'Time, height and spatial smoothing techniques (symmetric and asymmetric) will be available to merge vector clusters to a single best wind estimate. At the same time, conventional data will be made available for comparison. Analysis procedures will then be used to judge, on a weighted scale, the validity of wind estimates.

#### SUMMARY

McIDAS is an interactive system under control of the judgement of its operator. Automated quality control techniques serve only as an information source on the quality of cloud displacement measurements and do not automatically discard wind estimates. The system was designed to operate in this manner to minimize software validity check mis-evaluations. The operator uses the ability to synthesize a field of wind measurements displayed with their corresponding imagery, in a dynamically consisten situation, to finalize judgement on weach wind vector. This is the final step of the McIDAS quality control process.

MATCH SURFACE ARRAYS OF SAME CLOUD TARGET OVER TIME INTERVALS TWO FFERENT - D I

Cí

•

•

Alignment at Best Match Coefficients

Shaded area represents intersection containing sub-surfaces which can be tested for congruency

Figure 4 ALIGNMENT OF TWO MATCH SURFACES AT COINCIDENCE OF BEST MATCH COEFFICIENTS

Figure 5

U AND V VELOCITY RESIDUALS OF WIND SETS MEASURED OVER TWO INDEPENDENT TIME INTERVALS

#### · SMS CLOUD HEIGHTS

## I. INTRODUCTION

The determination of cloud height is important for many meteorological studies using satellite data. In the estimation of winds from cloud tracers, the height of the cloud tracer is of fundamental importance. One method of determining cloud height has been to obtain the temperature of the cloud using an infrared radiometer on a spacecraft operating in a "window" region of the infrared spectrum. Knowing the temperature of the cloud, one can obtain the height of the cloud from a vertical temperature profile of the area of interest. Fritz and Winston (1962), Rao and Winston (1963), and Kuffler, DeCotiis, and Rao (1973) have developed procedures for estimating cloud height from satellite infrared radiation data. A basic assumption used in these procedures was that the clouds were opaque, and hence, had emissivities equal to 1.

This method of determining heights has been reasonably successful for a coarse height resolution, except for cirrus type clouds. Cirrus clouds present the problem that their emissivity is not unity. Experimental studies such as Kuhn (1963), Kuhn and Weickmann (1969), and theoretical studies such as Jacobowits (1970), and Liou (1974) have shown that the emissivity of cirrus clouds is substantially less than unity and varies with cloud thickness.

To improve the infrared estimate of a cloud top height, the emissivity of the cloud needs to be obtained from some independent source. Using the fact that both the visible reflectance and the infrared emissivity are dependent upon the total number of cloud particles in a vertical column through the cloud, Shenk and Curran (1973) have shown that cirrus cloud heights can be determined to within  $\pm$  50 mb. The determination of optical thickness enables

one to determine the emissivity of the cloud. Knowing the emissivity of the cloud, the true temperature of the cloud top can be determined from the 10-12 micron infrared radiation. The height then follows from the temperature and a known vertical temperature profile.

#### **II** DETERMINATION OF EMISSIVITY

The main difficulty in obtaining the emissivity of a cloud is the determination of the cloud thickness. This could be done by using a normalized reflectance which corrects for the effects of viewing and solar zenith angles. The thickness of the cloud can then be inferred from the brightness of the cloud.

The normalization of the light reflected from clouds is not a trivial matter. The reflected light from clouds depends upon several variables:

a. The droplet size distribution and shape of the cloud particles.

b. The number density of scattering particles in the cloud.

c. The cloud thickness.

d. The angular conditions of the measurement system (the zenith angles of the sun and the sensor and their relative azimuth angle).

e. The shape of the cloud.

Since information on all the variables is not available to the satellite sensor, some of the effects must be parameterized in any normalization technique.

A. Brightness Normalization

There have been several approaches to normalization. The simplest has been to neglect all of the variables and assume the clouds are perfect isotropic reflectors and obey Lambert's law. The intensity of the reflected light will vary as the cosine of the solar zenith angle for an unchanging cloud. Martin and Soumi (1972) have shown that the tops of cumulonimbus clouds display a Lambertian behavior, and a cosine correction can be used to normalize the

brightness of thick cumulonimbus clouds.

There is, however, considerable evidence in the literature that neglecting all the variables and assuming isotropic reflectance can lead to erroneous results. Bartman (1967), Ruff et al. (1968), and Brennan and Bandeen (1970) have experimentally measured the scattering from clouds. They found clouds generally show an anisotropic reflectance pattern which varies with solar zenith angle. Normalization procedures based on this empirical data base have been developed by Sikula and Vonder Haar (1972). The main problem with this type of normalization has been the limited amount of empirical data available. Since empirical data on the variation of the reflectance pattern which is caused by variations in cloud thickness is generally not available, the normalization procedures based on empirical data generally have neglected the effects of cloud thickness.

To overcome the limitations of a restrictive data base, the normalization procedure which has been developed at the Space Science and Engineering Center, University of Wisconsin for the SMS/GOES data makes use of a theoretical multiple scattering model to generate a large data base for a large number of possible sun and observation angles. Data was generated for 16 different thicknesses of clouds.

B. Multiple Scattering Model

The multiple scattering program which was used to generate the data base of cloud reflectance patterns was a doubling method model developed by James Hansen of NASA's Goddard Institute for Space Studies. The details of the model are published in the January 1971 issue of the Journal of Atmospheric Sciences. Results from the model are published in the November 1971 issue of JAS (Hansen, 1971, a,b).

The doubling method works for a plane-parallel homogeneous cloud. Numer-

ical computations begin with a layer of such small optical thickness that scattering and transmission can be described by single scattering theory. The cloud thickness is built up by putting two layers together and computing the interactions that take place. The process of taking two layers, computing the transmission, reflection and interaction, combining the two into a single layer and then repeating the process for the new layer is the "doubling" procedure. By doubling, the thickness of the cloud increases by a factor of two after each computation, so very thick clouds can be generated quickly on the computer.

The single scattering phase function used as input to the multiple scattering doubling program was Deirmendjian's C-1 cloud model phase function. The forward scattering peak of the phase function was truncated and spread by the multiple scattering model (Hansen-Pollack, 1970). In the doubling model, 5 terms in the Fourier expansion were used, 3 terms in the sum over internal reflections between layers, 15 zenith angles were used for the Gauss quadrature integrations, and 37 azimuth angles were used. Conservative scattering was used with the local single scatter albedo set to unity.

The model as originally configured had the surface under the cloud as a perfectly absorbing black surface not accepting any other lower surface. While land and sea surfaces are dark compared to cloud, they are not entirely negligible, particularly for thin clouds. To include the sea surface brightness, the assumption was made that the light reflected from the sea was small compared to the light reflected from the thicker clouds, so that the energy which was lost by the light coming from the sea through the cloud toward the satellite did not interact with the light scattered originally in the cloud. The cloud scattering and the sea surface reflectance were computed separately and the results added.

The sea surface brightness was computed using sea surface albedo values

from Payne (1972). Payne performed an extensive experimental study of the albedo of the sea surface from a fixed platform and published tables of sea surface albedo as a function of the sun's altitude and atmospheric transmittance. To use these tables, the downward flux through the clouds and the atmospheric transmittance were computed. The flux impinging on the sea surface was then multiplied by the approximate albedo value to give a value for the flux propagating upwards from the sea surface. This upward flux was used as a new source of radiation and the directional transmittance to the satellite was computed using the multiple scattering program. The intensity of the sea surface was then added to the intensity of the cloud. Figure 1 shows the graph of intensity versus optical thickness with and without the sea surface brightness. As can be seen from the graph, the effect is significant for thin clouds.

The Rayleigh scattering of the atmosphere has been neglected in these calculations because its effect is smaller than the other effects. The sea surface brightness, as seen in Figure 1, is approximately .08. The brightness due to Rayleigh scattering for this geometry will be .018, a factor of four less.

At present the cloud height program only has a brightness data base of scattering from clouds with the sea surface beneath. This data base is presently used over land surfaces also. A similar data base for land areas could be added to the system in the future.

## C. Parameterization of Variables

The amount of light scattered from real clouds depends upon the droplet size distribution of the cloud, the number density of scatters, the cloud thickness, the angular geometry of the sun and sensor, and the finite shape of the cloud. Some of these variables can be measured and used in the

VARIATION OF INTENSITY WITH AND

WITHOUT SEA SURFACE ALBEDO

normalization, but others must be parameterized.

The physical thickness and the number density of the droplets can be combined into the single variable of optical thickness:

$\tau = KZ; K = \sigma \rho$

$\tau$  = optical thickness

Z = physical thickness

K = extinction coefficient

$\sigma$  = scattering cross section

$\rho$  = number density of scatters

The optical thickness  $\tau$  of a layer is such that unit radiation normally incident upon the layer is reduced by single scattering in passing through to  $e^{-\tau}$ . The optical thickness, rather than the physical thickness, has been used in all the multiple scattering calculations since it combines the effects of the variables of number density and scattering cross sectional area.

The effect of variations in the particle size distribution on the intensity of light reflected from clouds is minor. The wavelength of the light is on the order of .5 microns. The particle size distribution of clouds have radii on the order of 5 to 10 microns (Diem, 1948). The droplets are very large compared to the wavelength of the light being scattered. The single scatter phase function has a very large forward scatter peak. Hansen (1971b) has shown in the near infrared that variations in the size of the particles do not greatly influence the multiple scattering intensities when the particles are large compared to the wavelength of the light. Figure 2 shows the variations in reflected intensity for visible light caused by differences in the particle size distribution for 4, 7, and 10 micron average radius particles. The phase functions for these particle distributions were generated by a Mie scattering program developed by James Hansen, NASA/GISS. The particle size

VARIATION OF INTENSITY

WITH PARTICLE SIZE

distributions of each had a variance of .111. The particle size distribution used was a variation of the gamma distribution (Hansen, 1973b). The vertical axis in Figure 2 is intensity in theoretical units for an input flux of  $\pi$ , while the horizontal axis is optical thickness. The sun and the sensor both had a zenith angle of 0°. A 12 micron average radius particle size distribution was also computed, but its curve for Figure 2 was indistinguishable from the 10 micron curve. Consequently, for this study the variation of intensities of scattered light caused by variations in the particle size distribution has been neglected. The 4 micron average radius distribution of Diermendjian was chosen to represent all clouds including cirrus.

The effects of the shape of the clouds is largely unknown. The plane-parallel cloud which was used in the theoretical multiple-scattering doubling program had no horizontal limits. Experimental measurements of scattering from clouds such as Bartman (1967) and Brennan and Bandeen (1970) generally use stratus type clouds which also have no horizontal limits. For clouds with vertical extent approximately equal to their horizontal extent, such as cumulus clouds, some light energy should be lost or gained through the sides in addition to what comes through the top and bottoms. McKee and Cox (1974) have performed a study on the effects of the finite shaped clouds by using a Monte Carlo multiple scattering program on a cube. The angular resolution of their study was limited to light leaving the top, side, and bottom of the cube. Their results show that the upward reflected light from the cube is about 25% less than for the semi-infinite cloud. However, their angular resolution was not sufficient to distinguish between the intensity of light coming from the top center and the intensity coming from the top edges. One would expect more light to escape from the edges than from the middle and a gradient of

brightness should be established due to the light escaping out the sides. Unfortunately, there is presently no data available on this problem. Consequently, for this study, the intensities from the doubling program, which uses a semi-infinite horizontal extent cloud, will be used. Although there will be some errors at the edges of the clouds, the errors at the centers of the clouds should be small.

The parameters related to the angles of the sun and the sensor can easily be calculated with the knowledge of the position of the cloud, position of the satellite, and the position of the sun. Since a wind measurement using cloud tracers already requires an accurate navigation of the satellite, the information required to calculate the angle of the measurement is readily at hand.

In determining the scattered intensity of the cloud, the variables have been reduced to optical thickness and angles. The effect of particle size distribution is small and the effect of finite size of clouds has been neglected. The determination of cloud thickness, and the implied normalization which takes place, can be performed by taking the intensity measurement from a calibrated satellite and converting it to optical thickness through use of the tables of intensity versus optical thickness generated by the multiple scattering program. This optical thickness can therefore be used in the determination of the emissivity of the cloud.

D. Calibration of the Satellite Sensor

Unfortunately, like the Applications Technology Satellites (ATS) the SMS/GOES satellite lacks an on board calibration for the visible sensors. To perform quantitative radiance calculations, such as determination of cloud thickness, the satellite must be calibrated. To calibrate a satellite in orbit, a landmark of known brightness must be found. Previous

attempts at calibration include using the moon (Hansen, 1968), White Sands, New Mexico and the South American salt flat Solar de Uyuni (Griffith and Woodley, 1973). Calibrations using these landmarks have been hampered by the lack of detailed knowledge of the bi-directional reflectivity characteristics of these landmarks.

This study has taken a different approach at calibration of satellite images. Figure 3 shows an example of intensity versus optical thickness for the case of a solar zenith angle of 35°, satellite zenith angle of 20°, and relative azimuth angle of 50°. As can be seen from the figure, as the cloud becomes very thick, the intensity approaches a limiting value. The fact that clouds become intensity saturated and reach a limiting value has been the basis for a satellite calibration technique. Using the multiple scattering program, it was determined that the optical thickness 512 has a brightness which is within 3% of the ultimate limiting brightness. A cloud with optical thickness 512, droplets of 10 micron diameter, and droplet density of 250 droplets/cm<sup>3</sup> (as is representative of a large convective cloud) would have a physical thickness on the order of 14 km or 40,000 feet. Consequently, if edge effects can be neglected, any well-developed thunderstorm or tropical cloud cluster should have an intensity within 3% of the brightness of an infinitely thick cloud observed under the same sun and satellite angles. Small variations in the physical thickness should not make much difference in the brightness of these very thick clouds.

The calibration procedure used in this study involved selecting a very bright thick cloud and assigning it an optical thickness of 512. The ratio of the theoretical intensity of a cloud of optical thickness 512 to the measured intensity of the very thick cloud was designated the calibration factor alpha ( $\alpha$ ). With this calibration factor, any measured intensity can be converted into theoretical units by multiplying it by alpha.

VARIATION OF THE BRIGHTNESS OF A PLANE PARALLEL CLOUD WITH CHANGES IN THE OPTICAL THICKNESS OF THE CLOUD

A check on the assumption that variations in cloud thickness has little effect on the intensity of these thick calibration clouds was made by using clouds with known heights from radar as calibration clouds for ATS III data. A preliminary calibration check involved thunderstorms in the Miami area with tops ranging from 44,000 feet to 51,000 feet. The standard deviation of the calibration factors for these clouds was within 2% of the mean calibration factor. Selection of calibration clouds from different parts of the earth so that the local time, satellite, and sun angles would vary did not appreciably affect the consistent determination of alpha.

When the calibration factor  $\alpha$  determined from deep convective clouds was used in the determination of the emissivity of clouds as is described later in this report, the calculations gave an emissivity of cirrus clouds equal to unity. The clouds, therefore, were too thick. If, however, the calibration factor  $\alpha$  was reduced from the measured .8 to .45, the emissivity calculations showed reasonable results. The reduction in the calibration factor would be necessary if the deep convective clouds used for calibration were losing light from their sides. The study by McKee-Cox (1974) showed that light does leak out the sides of finite cubic clouds. Figure 4 reproduces a graph from their report showing the comparison of the infinite horizontal extent cloud and the finite cubic cloud using a Monte Carlo . multiple scattering technique. When the doubling method multiple scattering intensities used in this study are converted into the directional reflectance to conform to the convention of McKee and Cox, the doubling results agree closely with the infinite case of the Monte Carlo results. The reduction of the calibration factor therefore is consistent with the results of McKee and Cox.

E. Infrared Emissivity of Water and Ice Clouds

The infrared emissivity of clouds has been calculated using Kirchhoff's

law, equating the emissivity to the absorptivity. The absorptivity of the cloud was calculated from the radiative transfer through the cloud by the multiple scattering program configured to compute fluxes.

The infrared radiative transfer through a cloud is influenced by the size and shapes of the scattering particles, and the real and imaginary parts of the refractive index. The real part of the index of refraction is the parameter usually called the index of refraction in optics. The imaginary part of the index of refraction is related to the absorption of light by the scattering particles. Using Mie scattering theory the three fundamental optical parameters (the phase function, the single scatter albedo and the extinction cross section) can be computed from the particle size distribution and the index of refraction. While Liou (1973) has computed Mie theory parameters for ice cylinders, most studies, including this one, have used spheres in the Mie theory calculations. The Mie theory calculations in this report were made using the Mie scattering program developed by James Hansen of NASA/ GISS. The single scatter albedo calculated from Mie theory is the fraction of the energy incident on a single particle which is scattered. In the visible regions of the spectrum, the single scatter albedo is unity with no absorption. In the infrared regions, the single scatter is less than one, so absorption occurs during scattering events. Table 1 shows the dependence of the single scatter albedo on the particle size distribution for spheres of ice and water with light of wavelength 11.5u incident on them, The indices of refraction were taken from Irvine and Pollack (1968). The imaginery part of the index of refraction for ice in the portion of the tables for  $10\mu$ -12 $\mu$ of Irvine and Pollack appears to contain an error. The data should be a factor of 10 larger. The initial calculations of this study used the value of the imaginary part which was listed in the original paper, but all the calculations using the ice calculations have been re-done using

| Ta | Ь1 | P | 1 |

|----|----|---|---|

| та | L  |   | - |

## Ice Spheres

| Average Radius | Single Scatter Albedo |  |

|----------------|-----------------------|--|

| 30µ            | .497                  |  |

| 50µ            | .510                  |  |

| 80µ)           | . 520                 |  |

| <b>12</b> 0µ   | . 526                 |  |

# Water Droplets

| .240 |

|------|

| .409 |

| .484 |

| .492 |

|      |

the correct value.

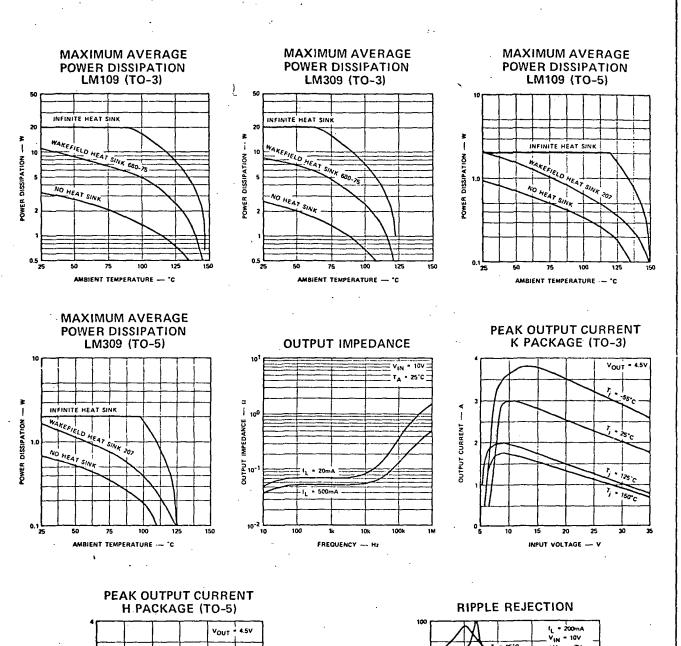

The emissivity of the clouds was calculated using the multiple scattering program configured to compute fluxes. The transmitted downward flux was computed at the bottom of the cloud and the reflected upward flux at the top of the cloud was computed for normally incident unit flux. The absorption was obtained from the difference between the incident flux and transmitted and reflected fluxes. The emissivity was set equal to the absorption. Figure 5 shows the variation of emissivity versus optical thickness for droplets of 4 to  $10\mu$  radius for  $11.5\mu$  radiation. Figure 6 shows the same for ice spheres. Since the single scatter albedo does not vary appreciably for variations in the sizes of ice spheres, the curve shown in Figure 6 is valid for all sizes of ice particles.

#### III. CLOUD HEIGHT PROGRAM

A. Methods of Height Computation for Different Types of Clouds

The cloud height program developed from the information of the preceding sections was written as a subroutine of the WINDCO cloud tracking program of the Space Science and Engineering Center. The cloud height program was designed so that the height of each tracer cloud would be determined automatically during the processing of the cloud tracking. The subroutine determines the height of wind tracer clouds by using the visible brightness to determine the thickness of the cloud. From the cloud thickness, the emissivity of the cloud is determined. Knowing the emissivity, the true temperature of the cloud top can then be determined. The height is gotten from a standard atmosphere of temperature vs. height, corrected for latitude and date. The height computation for each cloud adds about 1 second of processing time to the wind computation.

The cloud height program is configured to perform three passes at the cloud tracer. The first pass determines whether the center of the cloud can be considered blackbody. The optical thickness of the center pixel is computed, and the emissivity is computed from the optical thickness. If the emissivity is greater than .94 the cloud is considered to be blackbody and the blackbody temperature of the center pixel is used directly to compute the height of the tracer cloud.

If the first pass fails because of non-unity emissivity of the center pixel, a second pass at the data is performed. This second pass inquires if the cursor was not centered on the cloud, and a cloud with unity emissivity lies within the target grid of the cursor. A histogram of the brightness values of the target grid is computed, and the brightness cutoff for the brightest 20% of the population is determined. The entire data array is searched, and for each pixel brighter than the cutoff intensity, its emissivity is computed. For the subset of the 20% of the array's pixels, the average intensity and average emissivity is computed. If the average emissivity is greater than .94, the cloud is considered blackbody and the average radiative temperature of this 20% sample is used to obtain the height of the cloud.

If the first two passes at the data fail, the cloud is too thin to be considered a blackbody, and it is necessary to solve for the radiation coming from the cloud. Two areas in the target grid are needed to do this. The assumption is made that the ground in both areas has the same temperature, and the cloud cover for both areas is at the same height. The radiation reaching the infrared sensor for area 1 and 2 is

$$I_{1} = I_{g}(1-N_{1}) + \varepsilon_{1}N_{1}I_{c} + (1-\varepsilon_{1})N_{1}I_{g}$$

(1)

$$I_{2} = I_{g}(1-N_{2}) + \varepsilon_{2}N_{2}I_{c} + (1-\varepsilon_{2})N_{2}I_{g}$$

(2)

with

$I_{\sigma}$  = radiation coming from the ground

$I_c = radiation$  coming from the cloud cover

N = fractional cloud cover

$\varepsilon$  = emissivity

Subscripts 1 and 2 refer to areas 1 and 2.

Assuming that the fractional cloud cover and the emissivities can be measured, there are two equations with two unknowns,  $I_g$  and  $I_c$ . Solving for the radiation coming from the cloud yields:

$$I_{c} = \frac{I_{1}(1-N_{2}\varepsilon_{2}) - I_{2}(1-N_{1}\varepsilon_{1})}{\varepsilon_{1}N_{1} - \varepsilon_{2}N_{2}}$$

(3)

The two areas in the target grid are selected by finding the visible brightest and dimmest areas of the target grid. The brightest area (1) will have radiation mainly from the cloud while the dimmest area (2) will have radiation mainly from the ground. Equation 3 can be solved with a minimum of error this way.

The fractional cloud cover is determined from the visible. The two areas each cover 32 visible pixels. The spatial resolution of the visible sensor has a strong effect on the estimates of the percentage of cloud cover. A study by Shenk and Salomonson (1971) showed that if a cloud/no cloud threshold technique is used to determine percentage cloud cover, the cloud must be 100 times larger than the spatial resolution for the calculated percentage to be within 10% of the true percentage. This study also showed if a two threshold approach (all cloud/50% cloud/no cloud) is taken, the cloud must only be 10 times larger than the resolution of the camera.

The fractional cloud cover routine used in the cloud height program is a modification of the two threshold approach. The fractional cloud cover is calculated for each pixel and a running sum kept. To obtain the fractional cloud cover of a single visible pixel an arbitrary threshold of optical thickness 1 was established. Cloud pixels whose measured brightness corresponded to an optical thickness greater than 1 were considered completely covered with clouds. Pixels with the brightness of the sea surface were considered to have no cloud cover. For pixels whose brightness was between these two thresholds, the fractional cloud cover was considered to be proportional to the optical thickness. The infrared radiances and emissivities used in equation (3) are averages from each of the two areas.

B. Method of computing optical thickness

The optical thickness of a cloud is determined from the brightness of the cloud. A multiple scattering program using the doubling method developed by James Hansen of NASA/GISS was used as the source of data for the conversion between brightness and optical thickness. Since the McIDAS Datacraft computer is too small to run the multiple scattering program, a large table of 77,824 intensities was generated on the University of Wisconsin's UNIVAC 1110 and stored on the McIDAS digital disk. This represents all possible combinations of 16 solar zenith angles, 16 satellite zenith angles, 19 relative azimuth angles, and 16 optical thicknesses. The received SMS visible data has a six bit word with a square root digitization. To deal with a linear brightness scale, the SMS data is squared, giving a 12 bit word. The table of intensities has been multiplied by a scaling factor of 3166.9 prior to storage so that a 12 bit integer word which matches the SMS intensity resolution can be achieved. The height program first determines the solar zenith angle, satellite zenith angle, and the relative azimuth angle for the center of the cloud being tracked. The conversion of any visible pixel in that cloud from brightness to optical thickness is done by using the large table

of intensities. Since the table only holds data at finite angles, an interpolation must be performed to obtain the optical thickness for a unique set of input angles. The program first generates a table of 16 intensities for 16 standard optical thicknesses by doing a linear interpolation from data on the digital disc. The intensity I, which is a function of sun angle  $\theta_{o}$ , satellite angle  $\theta$ , azimuth angle  $\phi$ , and optical thickness  $\tau$ , can

be determined by

$$\mathbf{I}_{(\theta, \theta_{o}, \phi, \tau)} = \left(\frac{\partial \mathbf{I}}{\partial \theta}\right)_{\theta_{o}, \phi, \tau}^{d\theta} + \left(\frac{\partial \mathbf{I}}{\partial \theta_{o}}\right)_{\theta, \phi, \tau}^{d\theta} + \left(\frac{\partial \mathbf{I}}{\partial \phi}\right)_{\theta, \phi, \tau}^{d\phi} + \left(\frac{\partial \mathbf{I}}{\partial \tau}\right)_{\theta, \theta_{o}, \phi}^{d\tau} + \left(\frac{\partial \mathbf{I}}{\partial \tau}\right)_{\theta, \theta_{o}, \phi}^{d\tau} + \mathbf{I}_{(\theta_{1}, \theta_{o}, \phi_{1}, \tau_{1})}^{d\theta}$$

0

with  $I_{(\theta_1, \theta_1, \phi_1, \tau_1)}$  being known.

For a constant optical thickness the intensity I can be obtained by finite differences as

$$\mathbf{I}_{(\theta,\theta_{0},\phi)} = \frac{\Delta \mathbf{I}}{\Delta \theta} \Big|_{\substack{\theta_{0},\phi}}^{(\theta-\theta_{1})} + \frac{\Delta \mathbf{I}}{\Delta \theta_{0}} \Big|_{\substack{\theta_{0},\phi}}^{(\theta-\theta_{0},\phi)} + \frac{\Delta \mathbf{I}}{\Delta \theta_{0}} \Big|_{\substack{\theta_{0},\phi}}^{(\phi-\phi_{1})} + \mathbf{I}_{(\theta_{1},\theta_{0},\phi_{1},\phi_{1})}^{(\theta-\theta_{1},\phi_{1},\phi_{1},\phi_{1})} \Big|_{\substack{\theta_{0},\phi}}^{(\theta-\theta_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi_{1},\phi$$

In the partial derivatives, i.e.,  $\frac{\Delta I}{\Delta \theta} \Big|_{\substack{\theta_{0}, \phi}}$ , the quantities  $\theta_{0}$  and  $\phi$  are held

constant. Since there are only values of I at finite values of  $\theta_{01}$  and  $\theta_{02}$ ,  $\phi$ , and  $\phi_{2}$  available on either side of  $\theta_{0}$  and  $\phi$ , the finite values closest to  $\theta$  and  $\phi$  were chosen for the derivatives. The calibration factor of the visible sensor is then used to convert the observed brightness into the same units as the intensities on the digital disk. Then a linear interpolation is performed on the table of 16 intensities for 16 standard optical thicknesses to convert the observed brightness into optical thickness.

C. Method of Computing Cloud Emissivity

Once the optical thickness of a tracer cloud pixel has been determined, the emissivity at 11.5µ for that optical thickness is computed. The program uses a table of emissivity vs. optical thickness for a water droplet particle size distribution with average radius of 4 microns, and an ice sphere particle size distribution. Figures 5 and 6 of this report show these curves. Since these curves differ slightly, a method of distinguishing between ice and water clouds is necessary.

The cloud type identification routine used in this program makes the assumption that any cloud with a true temperature higher than 250°K is a water cloud, and any cloud with temperature lower is an ice cloud. Using an assumed surface temperature of 295°K and homogeneous clouds, curves of the apparent blackbody temperature of these cloud were generated using:

$I_{\text{received}} = \varepsilon I_{\text{cloud}} + (1-\varepsilon) I_{\text{ground}}$

and Plank's law

Figure 7 shows the curves for ice and water clouds. As can be seen from the curves, they do not agree and there is an area of ambiguity between the two curves for small optical thicknesses. The apparent blackbody temperature for ice clouds can be warmer than for water clouds. The operator supplied flag of the height guess is used to help resolve this ambiguity.

The program uses linear interpolation to generate the point on the curves which correspond to the input optical thickness. If the input measured blackbody radiative temperature is colder than the water curve, the cloud is definitely an ice cloud. If the input temperature is warmer than the ice curve, it is a water cloud. If the input temperature lies between the two curves where the ambiguity occurs, the operator's height guess is checked. If the height guess is less than 500 mb, the cloud is assigned an ice type. Otherwise, it is assigned a water type.

APPARENT BLACKBODY TEMPERATURE OF CLOUDS FOR DIFFERENT OPTICAL THICKNESSES

Once the type of cloud has been established, the emissivity of the cloud is calculated by linear interpolation of the emissivity tables.

D. Method of Converting Between Temperature and Height

The height program computes the true temperature of the cloud top. То convert from temperature to height, a sounding of temperature vs. height is necessary. Ideally, current synoptic soundings should be used for this task, but unfortunately, the Space Science and Engineering Center does not presently have access to world wide synoptic soundings. The cloud height program uses standard atmospheres corrected for latitude and the time of year. Standard atmospheres for latitudes 15°, 30°, 45°, 60°, and 75° for January and July are used. The standard atmospheres extend up to the tropopause, but inversions have been made almost isothermal so as to produce a function of temperature which is single valued with height. A linear interpolation of soundings is made between latitudes for the two times of the year, January and July. Then an interpolation using a cosine function is performed to correct the standard atmosphere soundings to the current data of the cloud tracer.

If current synoptic soundings were made available, the cloud program could easily use them. The program was constructed using a modular design. The conversion from temperature to height is a separate subroutine which could easily be replaced with one which uses current soundings instead of standard atmospheres.

E. Nighttime Heights

During nighttime cloud tracking operations, only the infrared channel is available. Hence there is no information available from the visible channel for the determination of cloud thickness and cloud emissivity. Preliminary analysis of the SMS infrared images coupled with the visible images show that there are no immediately obvious clues (such as area,

texture, etc.) which exist in the infrared image which could be used to determine the emissivity of the cloud in an automatic height determination system. Consequently the preliminary nighttime heights algorithm has been kept simple and uses the blackbody assumption. The center pixel of the cloud is used to determine the height. This algorithm will be used until the statistical error analysis algorithms have been completed and studies can be done on nighttime algorithm improvements such as searching for the coldest area of the cloud, averaging techniques, and manual guessing of the emissivity.

#### IV. OPERATION AND ASSESSMENT OF CLOUD HEIGHT SYSTEM

The cloud height system was installed on the McIDAS system in August 1974, and received its first major use during the Data System Test of October 28-November 1, 1974. The cloud height system is configured so that the heights of the tracer clouds are computed automatically as the operator selects the candidate cloud tracers. No additional effort is required of the operator beyond setting up the initial conditions of the processing and the selection of the cloud tracers. The cloud height system can also be used separately from the cloud tracking system. The operator can put the cursor over the cloud of interest, press H on the keyboard, and the cloud height in kilometers and millibars plus some diagnostics will be displayed. Other diagnostic commands are also available.

The cloud height program uses some simplifications and parameterizations of the clouds whose heights are being measured (such as parameterization of particle size distributions of clouds, horizontal homogeneous assumption, etc.) which result in an accuracy of the cloud height system of no better than +50 mb. Preliminary analysis of the consistency of the height

computation over two consecutive picture pairs shows this error expectation to be reasonable for the lower clouds, but the upper level clouds might have relative errors as large as  $\pm 100$  mb for the present configuration of the cloud height system.

The absolute accuracy of the cloud height system is at present unknown. Requests have been made for aircraft observations of cloud top height, cloud base height, and the temperature of the cloud, but we have not yet received any of these reports. The winds produced during the Data System Test of October 28-November 1 were transmitted to the National Meteorological Center (NMC) by way of NASA's Goddard Institute of Space Studies. The validation analysis of these wind sets by NMC has not been made available yet.

The absolute accuracy of any height determination depends upon the absolute accuracy of the VISSR thermal channel calibration on the SMS/GOES satellite. While the system has an onboard calibration system, problems such as unexpected thermal gradients continue to limit absolute accuracy of the system. During the times of eclipse in the fall and spring, diurnal variations in the sensitivity of the instrument can cause diurnal errors of 3.5°K for warm sea surface measurements. A long term drift of sensitivity of the instrument has caused errors as large as 5°K in sea surface measurements. Cloud temperature errors were somewhat less than this. A new thermal channel calibration was applied to the satellite on October 31, 1974.

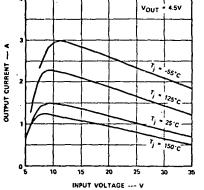

To obtain a preliminary idea on the performance of the cloud height accuracy, plots of the wind fields generated from cloud motions were compared against plots of wind fields measured by radiosondes over the United States. These plots are shown in Figures 8-13. The winds generated by the cloud motions have been divided into three groups, (surface-800 mb, 700-500 mb, and 400-100 mb). The heights assigned to the individual vectors

are plotted next to the vectors. The heights are in hundreds of millibars so O=near surface, 9=900 mb, etc. The radiosonde winds are for 1200Z of October 30, 1974. The cloud winds are for 1400-1500Z. The sunrise line is just to the west of the wind measurements on the surface-800 mb plot of cloud winds. Measurements of upper level winds west of this line were made using only the IR channel. As can be seen by the visual comparison of the McIDAS cloud winds and the radiosonde winds, there appears to be good agreement between the two types of measurements.

Work has started on a verification against radiosondes and an error analysis system for height and wind determinations. When this system has been completed, a much better assessment of the accuracy of the cloud heights will be available.

#### V. SUMMARY

A cloud height determination system has been developed which takes into account the variable emissivity properties of clouds. The visible brightness of the cloud is used to calculate the optical thickness. The optical thickness is used to compute the infrared emissivity of the cloud. The true temperature of the cloud can be calculated using the emissivity. From the temperature of the cloud and a sounding, the height can be determined. The cloud height system is operational and is coupled to the WINDCO cloud tracking system so that the heights of tracer clouds are computed automatically along with the wind computation. The height computation adds approximately 1 second to each wind calculation time.

#### VI. RECOMMENDATIONS FOR IMPROVEMENTS

The cloud height system at present is usable and appears to give good results. However, there are several areas which could use some more work for

improving the system.

A. Verification and Error Analysis

The cloud height and wind determination systems need scientific verification. Verification is not a trivial problem and deserves a serious effort. Verification needs to be made against "primary" standards such as independent aircraft measurements of cloud height and motions. Verification also needs to be made against "secondary" standards such as radiosonde wind fields. Also, since the winds generated by cloud motions are primarily intended for numerical models, the numerical models should be used in the verification to see how these cloud winds improve the forecasts. Before improvements can be added to the height and wind systems, a good verification system is needed to judge the value of the improvements.

#### B. Infrared Calibration

Since the absolute accuracy of the cloud height system depends on the accurate calibration of the infrared sensors, and since there are errors in the present calibration, further work is required on IR calibration.

C. Visible Calibration