OCTOBER 1975

CR-137758 CONTRACT NAS 2-8327

# SATELLITE ON-BOARD PROCESSING FOR EARTH RESOURCES DATA

FINAL REPORT

N76-16592

(NASA-CR-137758) - SATILLITE ON-BOARD PROCESSING FOR EARTH RESOURCES DATA Final Report (Wintek Corp., Lafayette, Ind.) Unclas Unclas G3/43 09579 G3/43 09579

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

AMES RESEARCH CENTER

MOFFETT FIELD, CALIFORNIA

PRICES SUBJECT TO CHANGE

NATIONAL TECHNICAL INFORMATION SERVICE U.S. DEPARTMENT OF COMMERCE SPRINGFIELD, VA. 22161

4

PREPARED BY

902 NORTH NINTH STREET LAFAYETTE, INDIANA 47904

# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM THE BEST COPY FURNISHED US BY THE SPONSORING AGENCY. ALTHOUGH IT IS RECOGNIZED THAT CER-TAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RE-LEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE.

CR 137758 CONTRACT NAS 2-8327

Contributors:

R. E. Bodenheimer

- R. C. Gonzalez

- J. N. Gupta

- K. Hwang

- R. W. Rochelle

- J. B. Wilson

- P. A. Wintz

#### SATELLITE ON-BOARD PROCESSING

FOR EARTH RESOURCES DATA

ż

#### FINAL REPORT

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

AMES RESEARCH CENTER

MOFFETT FIELD, CALIFORNIA

PREPARED BY

902 North Ninth Street Lafayette, Indiana 47904

-

.

Project Director:

P. A. Wintz WINTEK CÓRPORATION

Technical Monitor:

Edgar Van Vleck NASA/ARC

# TABLE OF CONTENTS

|   |                                                               | Page     |

|---|---------------------------------------------------------------|----------|

| Ò | INTRODUCTION                                                  | - 9      |

| ł | EARTH RESOURCES ALGORITHMS AND DATA SETS                      | 13.      |

| - | 1.1 USER REQUIREMENTS                                         | 13       |

|   | 1.1.1 Applications Survey                                     | 13       |

|   | 1.1.1.1 Agriculture (A)                                       | 14       |

|   | 1.1.1.2 Coastal-Zone Studies (C)                              | 14       |

|   | 1.1.1.3 Forestry (F)                                          | 15       |

|   | 1.1.1.4 Geography (G)                                         | 15       |

|   | 1.1.1.5 Geology (L)                                           | 16       |

|   | 1.1.1.6 Hydrology (H)                                         | 16       |

|   | 1.1.1.7 Meteorology (M)                                       | 18       |

|   | 1.1.1.8 Global Oceanography (0)                               | 19       |

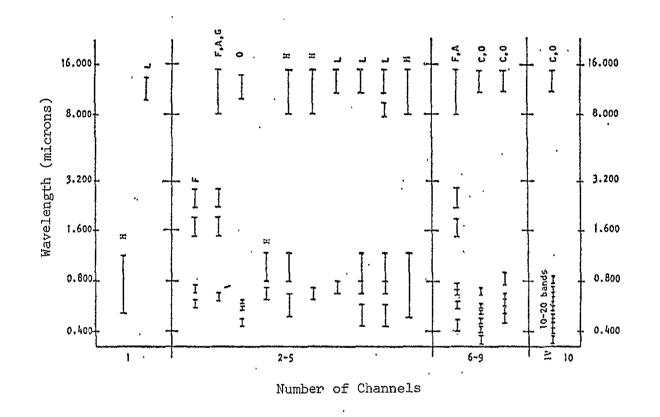

|   | 1.1.2 Data Requirements Survey                                | 20       |

|   | 1.1.2.1 Number of Spectral Bands                              | 21       |

|   | 1.1.2.2 Repeat Coverage                                       | 21       |

|   | 1.1.2.3 Spatial Resolution and Field of Coverage              | 21       |

|   | 1.1.2.4 Data Rates                                            | · 21     |

|   | 1.1.3 Algorithms Survey                                       | 26       |

|   | 1.1.3.1 Maximum-Likelihood Algorithm                          | 27       |

|   | 1.1.3.2 Perceptron Algorithm                                  | 27       |

|   | 1.1.3.3 Table Look-Up Algorithm                               | 29       |

|   | Two Dimensional Case                                          | 29       |

|   | Four-Dimensional Case                                         | 32       |

|   | 1.1.3.4 Clustering Algorithm                                  | 33       |

|   | 1.2 MSS SENSOR TECHNOLOGY                                     | 38       |

|   | 1.2.1 Electromechanical Scanners                              | 38       |

|   | 1.2.1.1 Detector Cooling Systems                              | 39       |

|   | 1.2.1.2 Optical Systems                                       | 41       |

|   | 1.2.1.3 Hadamard System                                       | 41       |

|   | 1.2.2 Solid-State Scanners                                    | 42       |

|   | 1.3 PREPROCESSING ALGORITHMS                                  | 47       |

|   | 1.3.1 Sensor Corrections                                      | 47       |

|   | 1.3.1.1 Radiometric Response                                  | 48       |

|   | 1.3.1.2 Determination of Gain and Offset                      | 48       |

|   | 1.3.2 Data Bulk Reduction                                     | 49       |

|   | 1.3.2.1 Coding                                                | 50<br>50 |

|   | 1.3.2.1.1 Transform Coding                                    | 50<br>52 |

|   | 1.3.2.1.2 Coding by BLOB                                      |          |

|   | 1.3.2.2 Feature Selection<br>1.4 CANDIDATE FOR DETAILED STUDY | 52<br>54 |

|   | 1.4.1 Baseline Data Format                                    | 54<br>55 |

|   |                                                               | 55<br>55 |

|   | 1.4.2 Preprocessing Algorithms                                |          |

|   | 1.4.2.1 Coding<br>1.4.2.2 Feature Selection                   | 55<br>57 |

|   | 1.4.2.3 Conclusion                                            | 57<br>58 |

|   | 1.4.3 Analysis Algorithms                                     | 58<br>59 |

|   |                                                               | 55       |

| 2 | ON-BOARD PROCESSOR REQUIREMENTS                               | 61       |

|   | 2.1 ALGORITHM COMPUTATIONAL REQUIREMENTS                      | .61      |

.

.

C

TABLE OF CONTENTS (Continued)

~

|                                                                                    | Page        |

|------------------------------------------------------------------------------------|-------------|

| 2.1.1 Preprocessing Algorithms                                                     | 62          |

| 2.1.2 Basic Computational Requirements                                             | 62          |

| 2.1.3 Storage Considerations                                                       | 63          |

| 2.1.4 Analysis Algorithms                                                          | 63          |

| 2.1.4.1 Basic Computational Requirements                                           | 63          |

| 2.1.4.2 A Numerical Comparison                                                     | 67          |

| 2.1.4.3 Storage Considerations                                                     | 69          |

| 2.1.4.4 Determination of the Algorithm Constants                                   | 69          |

| 2.2 COMPUTER ARCHITECTURE AND ORGANIZATION                                         | 71          |

| 2.2.1 Historical Data                                                              | 71          |

| 2.2.2 Parallel Processor                                                           | 72          |

| 2.2.3 Pipeline Processor                                                           | 73          |

| 2.2.4 Array Processor                                                              | 73          |

| 2.2.5 Multiprocessor                                                               | 73          |

| 2.2.6 Memory                                                                       | 73          |

| 2.2.6.1 Program Memory<br>2.2.6.2 Working Memory                                   | 74          |

| 2.2.6.3 Bulk Memory                                                                | 74          |

| 2.2.6.4 New Memory Technologies                                                    | 75<br>75    |

| 2.2.7 Software                                                                     | 75<br>76    |

| 2.2.8 Computer Architecture Examples                                               | 70          |

| 2.2.8.1 Microprocessor Organization for the Maximum-                               | ,,          |

| Likelihood Algorithm                                                               | 78          |

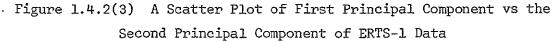

| Processing Element PE1                                                             | 79          |

| Processing Element PE2                                                             | 79 .        |

| Processing Element PE3                                                             | 81          |

| Processing Element PE4                                                             | 81          |

| 2.2.8.2 Microprocessor Organization Using Table Look-<br>(TLU)                     | Up 85.      |

| 2.2.8.2.1 On-Board Computer Organization for                                       |             |

| Table Look-Up Pattern Classification                                               | n 86        |

| 2.2.8.2.2 Multi-Microprocessor Computer System                                     | m for       |

| On-Board Table Look-Up Pattern Class                                               | sifi- ·     |

| cation                                                                             | 90          |

| 2.2.8.3 Microprocessor Organization for the Expanded I<br>mum Likelihood Algorithm | Maxi-<br>92 |

| 2.2.8.4 Hardware Organization for the Expanded Maximur                             |             |

| Likelihood Algorithm                                                               |             |

| 2.2.8.4.1 Serial Organization                                                      | 99          |

| 2.2.8.4.2 Parallel Organization                                                    | 101         |

| 2.2.8.4.3 The Optimal Organization                                                 | 102         |

| 2.2.8.4.4 Comparison of the Three Computer                                         |             |

| Organizations                                                                      | 105         |

| 2.2.8.5 A Hardware Table Look-Up Processor                                         | 105         |

| 2.3 ON-BOARD PROCESSOR ENVIRONMENTAL EFFECTS                                       | . 109       |

| 2.3.1 Orbit                                                                        | 110         |

| 2.3.1.1 Earth-Synchronous Orbit                                                    | 110         |

| 2.3.1.2 Sun-Synchronous Orbit                                                      | 111         |

| 2.3.2 Spacecraft Environment                                                       | 111         |

|                                                                                    |             |

| TABLE OF CONTENTS (Continued)                       | ,           |

|-----------------------------------------------------|-------------|

|                                                     | Page        |

| 3 TECHNOLOGY FORECAST AND ASSESSMENT                | 113         |

| 3.1 PERFORMANCE MEASUREMENT CRITERIA                | 113         |

| 3.2 COMPONENT TECHNOLOGY                            | 115         |

| 3.2.1 1975 Component Technology                     | 115         |

| 3.2.2 1975-1985 Component Technology                | 11 <b>7</b> |

| 3.3 SYSTEM TECHNOLOGY                               | 119         |

| 3.3.1 Technology Forecasting Model                  | 120         |

| 3.4 ON-BOARD PROCESSOR TECHNOLOGY                   | 121         |

| 3.5 FORECAST FEEDBACK SYSTEM                        | 124         |

| 3.5.1 Input Data                                    | 125         |

| 3.5.2 Output Data                                   | 125         |

| 3.5.3 Feedback Loop                                 | 125         |

| 3.6 OTHER TECHNOLOGIES                              | 126         |

| 3.6.1 The tse Computer                              | 126         |

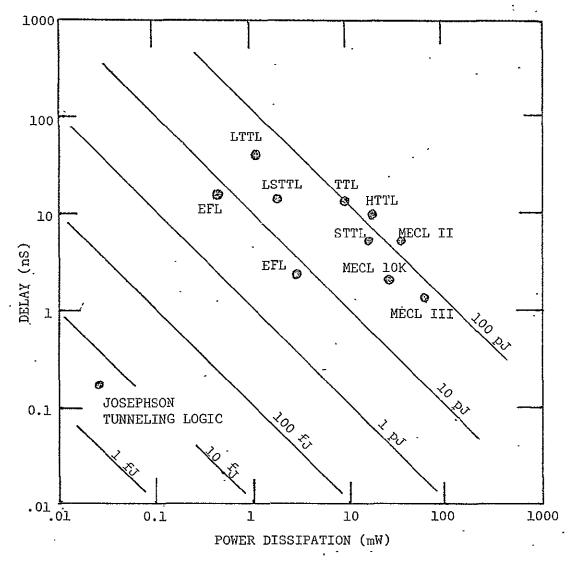

| 3.6.2 Josephson Tunneling Devices                   | 130         |

| 4 FEASIBILITY, TRADE-OFF, AND SENSITIVITY ANALYSIS  | 137         |

| 4.1 COMPLEXITY FUNCTION DEPENDENCE ON M, n, r, b, a | nd R 138    |

| 4.1.1 The Microprocessor Maximum Likelihood Met     |             |

| 4.1.2 Hardware Maximum Likelihood Method (HML)      | 139         |

| 4.1.3 Microprocessor Table Look-Up (µPTLU)          | 140         |

| 4.1.4 Hardware Table Look-Up (HTLU)                 | 141         |

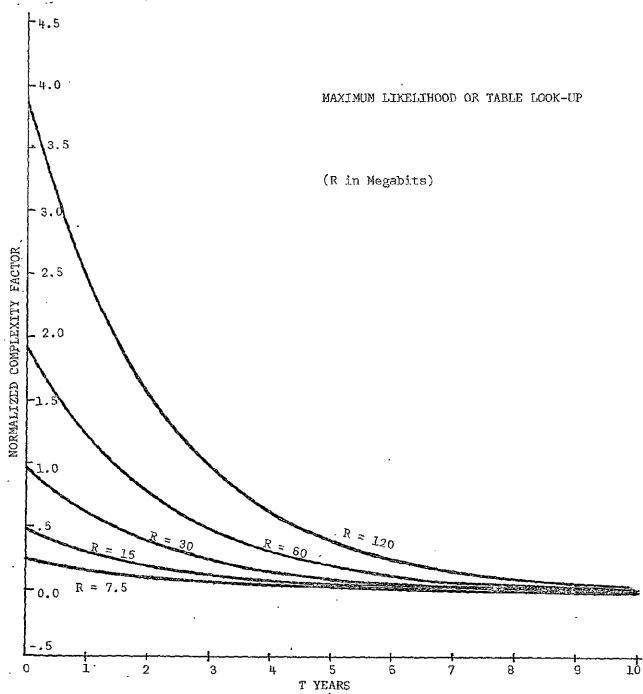

| 4.2 COMPLEXITY FUNCTION DEPENDENCE ON TIME          | 141         |

| 4.3 EVALUATION OF SYSTEM CONSTANTS                  | 142         |

| 4.3.1 Evaluation of $\lambda_0$                     | 143         |

| 4.3.2 Evaluation of $\lambda_1$                     | 143         |

| 4.3.3 Evaluation of $k_1$ , $k_2$ , $k_3$ , $k_4$   | 144         |

| 4.4 SENSITIVITY ANALYSIS                            | 145         |

| FEASIBILITY ANALYSIS                                | 147         |

| 4.4.1 What is Feasible                              | 148         |

| 4.4.2 Feasibility Curves                            | 149         |

| 4.5 POSSIBLE EFFECTS OF NASA STIMULUS TO INDUSTRY   | 181         |

| 5 SUMMARY, CONCLUSIONS AND RECOMMENDATIONS          | 182         |

| 5.1 SUMMARY                                         | 182         |

| 5.1.1 Study Objective                               | 182         |

| 5.1.2 User Applications Survey                      | 183         |

| 5.1.3 Data Analysis Algorithm Survey                | 184         |

| 5.1.4 Preprocessing Algorithms                      | 185         |

| 5.1.5 Algorithm Computational Requirements          | 186         |

| 5.1.6 Technology Forecast and Assessment            | 186         |

| 5.1.7 On-Board Processor Designs                    | 187         |

| 5.1.8 Feasibility Trade-Off and Sensitivity Ana     |             |

| 5.2 CONCLUSIONS                                     | 193         |

| 5.3 RECOMMENDATIONS                                 | 193         |

| 5.3.1 Handling the On-Board Processor Output Da     |             |

| 5.3.2 Dates for Cost-Effective Launches             | 194 '       |

| 5.3.3 Stimulation of Industry                       | 194         |

|                      | LIST OF TABLES                                                                                            |            |

|----------------------|-----------------------------------------------------------------------------------------------------------|------------|

| Table                |                                                                                                           |            |

| Number               | Title                                                                                                     | 'Page'     |

|                      |                                                                                                           |            |

|                      |                                                                                                           |            |

| 0.8(I)               | List of Symbols                                                                                           | 12         |

| 1.1.2(I)             | Typical Data Rate Ranges                                                                                  | 24         |

| 1.1.2(II)            | List of Applications                                                                                      | 25         |

| 1.3.1(I)             | Radiance Necessary to Produce Full Scale at the                                                           |            |

| • •                  | Multiplexer Output (mw/cm <sup>2</sup> · ster)                                                            | 48         |

| 1.4.2(I)             | Variance Eigenvalues and Eigenvectors of ERTS-1 Data                                                      | 58         |

| 2.1.1(I)             | A Comparison of Analysis Algorithms for One Data Frame                                                    | 68         |

| 2.2.8(I)             | Program for Generating x-m in PF1                                                                         | <b>7</b> 9 |

| 2.2.8(II)            | Program for Generating $x-m$ in PEL<br>Program for Generating $\overline{A_{-1}}^{k}$ in PE2 <sub>1</sub> | 80         |

| 2.2.8(III)           | Program for Generating $\overline{d_1}(x)$ in PE3                                                         | 81         |

| 2.2.8(IV)            |                                                                                                           |            |

|                      | Program for Determining Classification k in PE4                                                           | 82         |

| 2.2.8(V)             | Comparison of Current and Projected Program Execution                                                     |            |

| a = a (u - 1)        | Times for the Processing System of Figure 2.2.8(1)                                                        | 32         |

| 2.2.8(VI)            | Comparison of Current and Projected Program Execution                                                     |            |

|                      | Times for the Processing System of Figure 2.2.8(3)                                                        | 83         |

| 2.2.8(VII)           | Comparison of Current and Projected Program Execution                                                     |            |

|                      | Times for the Processing System of Figure 2.2.8(4)                                                        | 84         |

| 2.2.8(VIII)          | Computed Upper-Limit Estimates for Main Storage and                                                       |            |

|                      | Table-Making Calculations for the Case Q=12                                                               | 89         |

| 2.2.8(IX)            | Actual Requirements for Main Storage and Table-Making                                                     |            |

|                      | Calculations for the Case Q=12                                                                            | 90         |

| 2.2.8(X)             | Major System Characteristics of the Multiprocessor                                                        |            |

|                      | System for 4-Channel Table Look-Up                                                                        | 91         |

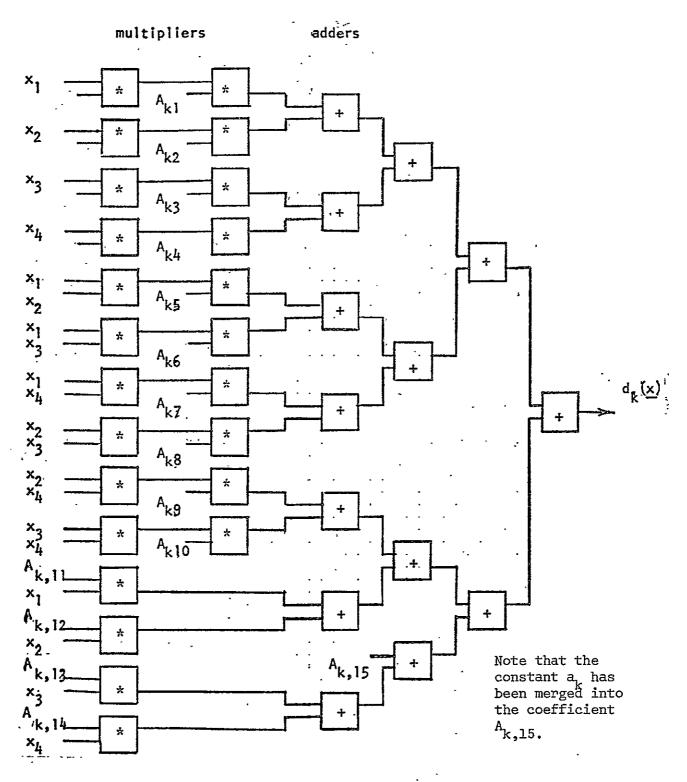

| 2.2.8(XI)            | Program for Generating $d_k(x)$ in PE2                                                                    | 93         |

| 2.2.8(XII)           | Comparison of Current and Projected Execution Times                                                       | 50         |

| 20200(1122)          | for the Processing System of Figure 2.2.8(8)                                                              | 93         |

| 2.2.8(XIII)          | Comparison of the Number of Microprocessors Required for                                                  |            |

| 2.2.0(111)           |                                                                                                           |            |

| 2.2.8(XIV)           | the Processing System of Figure 2.2.8(8)                                                                  | 94         |

| 2.2.8(X1V)           | Comparison of Current and Projected Execution Times for                                                   |            |

|                      | the Processing System of Figure 2.2.8(9)                                                                  | 95         |

| 2.2.8(XV)            | Comparison of the Number of Microprocessors Required                                                      |            |

| ()                   | for the Processing System of Figure 2.2.8(9)                                                              | 95         |

| 2.2.8(XVI)           | Comparison of Number of Microprocessors for Different                                                     |            |

|                      | Function and Multiplication Implementations                                                               | 96         |

| 2.2.8(XVII)          | System Hardware Requirements for the Microprocessor                                                       |            |

|                      | Processing System Using ROM Multipliers                                                                   | 97         |

| 2.2.8(XVIII)         | Same as Table 2.2.8(XVII) Except the ROM Multipliers                                                      |            |

|                      | Are Replaced by PLA Multipliers                                                                           | 97         |

| 2.2.8(XIX) :         | System Hardware Requirements for the Microprocessor                                                       |            |

|                      | Processing System Using Hardware Multipliers                                                              | 98         |

| 2.2.8(XX)            | System Hardware Requirements for the Microprocessor                                                       |            |

|                      | Processing System of Figure 2.2.8(8) Using Hardware                                                       |            |

|                      | Multipliers and Eq. (2.2.8-8) Implementation                                                              | 98         |

| 2.2.8(XXI)           | System Hardware Requirements for the Microprocessor                                                       | 50         |

|                      |                                                                                                           |            |

|                      | Processing System of Figure 2.2.8(9) Using Hardware                                                       | 00         |

| ·<br>• • • • • • • • | Multipliers and Eq. (2.2.8-8) Implementation                                                              | 98         |

| 2.2.8(XXII)          | Time and Hardware Requirements for the Serial Computer                                                    |            |

|                      | Organization ·                                                                                            | 100        |

|                      |                                                                                                           |            |

LIST OF TABLES (Continued)

| Number       | Title                                                     | Pa  |

|--------------|-----------------------------------------------------------|-----|

| 2.2.8(XXIII) | Time and Hardware Requirements for the Parallel           |     |

|              | Computer Organization                                     | 1   |

| 2.2.8(XXIV)  | Time and Hardware Requirements for the Optimal Computer   |     |

|              | Organization                                              | 1   |

| 2.2.8(XXV)   | Comparison of the Three Computer Organizations            | 1   |

| 3.2.1(I)     | Some 1975 Component Technologies                          | 1   |

| 3.2.1(II)    | Qualitative Comparison of MOS Circuit Techniques          | 1   |

| 3.2.1(III)   | 1975 Component Reliability                                | 1   |

| 3.2.1(IV)    | Comparison of RAM and CCD for Bulk Storage                | 1   |

| 3.2.2(I)     | Possible Trends in Dynamic MOS RAM ∿ 500 ns Cycle Time    | 1   |

| 3.2.2(II)    | Projected 1980 LSI Component Prices                       | ]   |

| 3.3.(I)      | Comparison of Minicomputer/Microcomputer Characteristics  | 1   |

| 4(I)         | On-Board Processor Performance Parameters                 | ]   |

| 4.1.1(I)     | Table Look-Up Memory Requirements                         | ]   |

| 4.1.3(I)     | Mathematical Operations for Classification                | J   |

| 4.2(I)       | On-Board Processor Complexity Functions                   | ]   |

| 4.3.3(I)     | Complexity Functions for the Baseline System Described    |     |

|              | in Section 1.4; i.e., n=4 Spectral Bands M=12 Classes     |     |

|              | b=6 Bits, R=31.2M Bits/Sec and T=0 (1975 Technology)      | 3   |

| 4.3.3(II)    | Scale Factors for the Complexity Functions of Table       |     |

|              | 4.3.2(I) for Each Performance Measure.                    | 2   |

| 4.4.2(I)     | For Each Application Listed in the First Column, the Suc- | . • |

|              | * ceeding Columns List the Year that the Processor        |     |

|              | Becomes Feasible (1000 IC's for the Maximum Require-      |     |

|              | ments Listed in Table 1.1.2(I): N Means Not Feasible      |     |

|              | by 1990.                                                  | 1   |

| 4.4.2(II)    | For Each Application Listed in the First Column, the Suc- |     |

|              | ceeding Columns List the Year that the Processor          |     |

|              | Becomes Feasible (1000 IC's) for the Minimum Require-     |     |

|              | ments Listed in Table 1.1.2(I): N Means Not Feasible      |     |

|              | by 1990                                                   |     |

| 4.4.2(III)   | For Each Application Listed in the First Column, the      |     |

|              | Succeeding Columns List the Year that the Processor       |     |

|              | Becomes Feasible (500 IC's) for the Maximum Requiremen    | t   |

|              | Listed in Table 1.1.2(I): N Means Not Feasible by         |     |

|              | 1990.                                                     |     |

| 4.4.2(IV)    | For Each Application Listed in the First Column, the      |     |

|              | Succeeding Columns List the Year that the Processor       |     |

|              | Becomes Feasible (500 IC's) for the Minimum Require-      |     |

|              | ments Listed in Table 1.1.2(I): N Means Not Feasible      |     |

|              | by 1990.                                                  |     |

| 4.4.2(V)     | For Each Application Listed in the First Column, the      |     |

| •            | Succeeding Columns List the Year that the Processor       |     |

|              | Becomes Feasible (2000 IC's) for the Maximum Require-     |     |

|              |                                                           |     |

|              | ments Listed in Table 1.1.2(I): N means Not Feasible      |     |

# LIST OF TABLES (Continued)

| Table <sup>.</sup><br>Number | Title                                                                                                                                                                                                                      | Page |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2                            |                                                                                                                                                                                                                            |      |

| 4.4.2(VI)                    | For Each Application Listed in the First Column, the<br>Succeeding Columns List the Year that the Processor<br>Becomes Feasible (2000 IC's) for the Minimum Requireme<br>Listed in Table 1.1.2(I): N Means Not Feasible by | ents |

|                              | 1990.                                                                                                                                                                                                                      | 180  |

| 5.1.8(I)                     | Processor Complexity Functions                                                                                                                                                                                             | 188  |

LIST OF FIGURES

| Figure     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Number .   | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

| •          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12   |

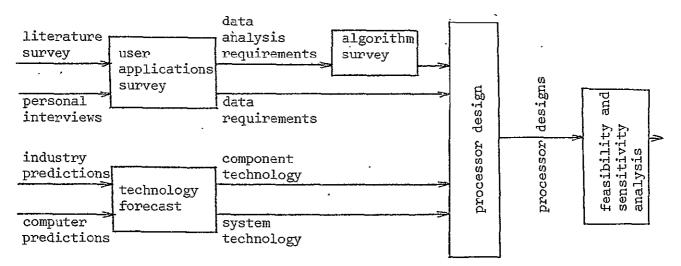

| 0(1)       | Study Plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10   |

| 1.1.2(1)   | Spectral Requirements Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22   |

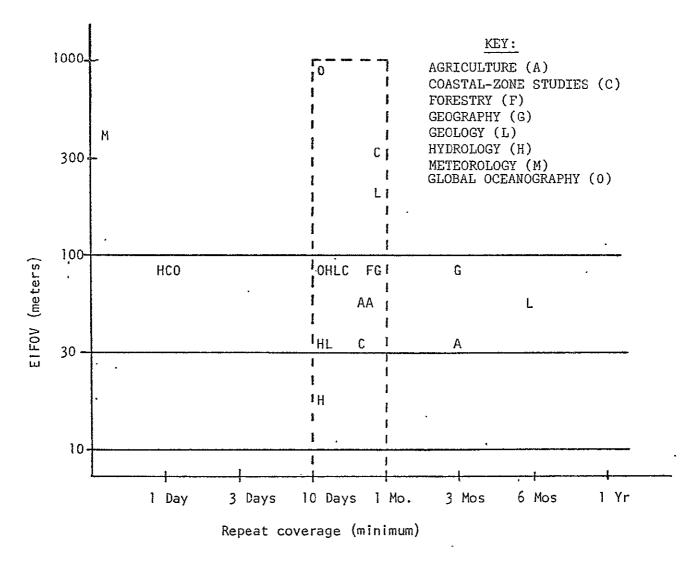

| 1.1.2(2)   | Typical Rates of Coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23   |

| 1.1.3(1)   | Explanation of Classification Algorithm for Two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

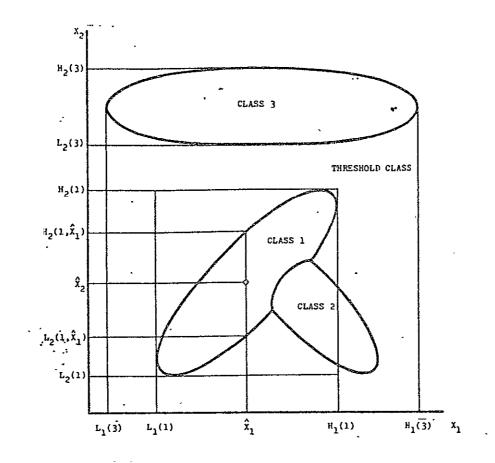

| _          | Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30   |

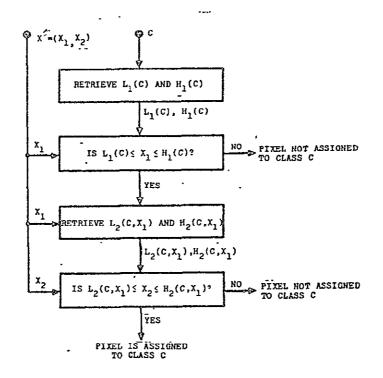

| 1.1.3(2)   | Method for Determining Whether Pixel is from Class C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31   |

| 1.1.3(3)   | Organization of the Prestored Tables of Boundary Infor-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|            | mation for the Case Shown in Figure 1.1.3(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32   |

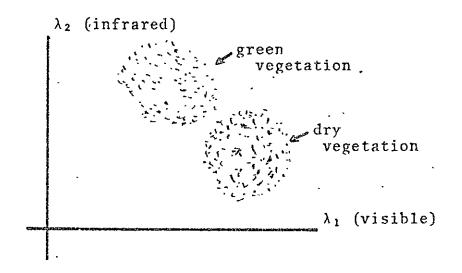

| 1.1.3(4)   | Example of Data Clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35   |

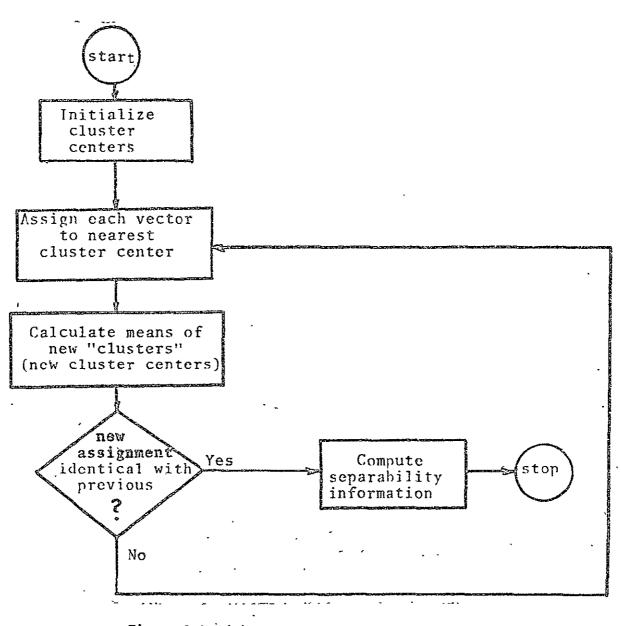

| 1.1.3(5)   | Clustering Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36   |

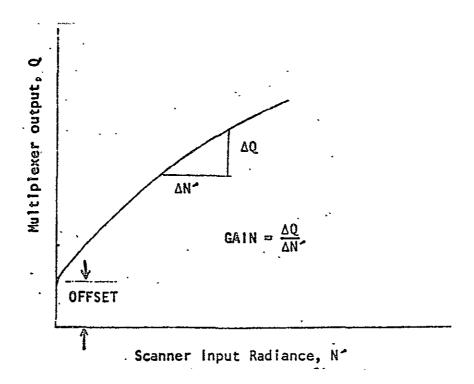

| 1.3.1(1)   | Determination of Gain and Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49   |

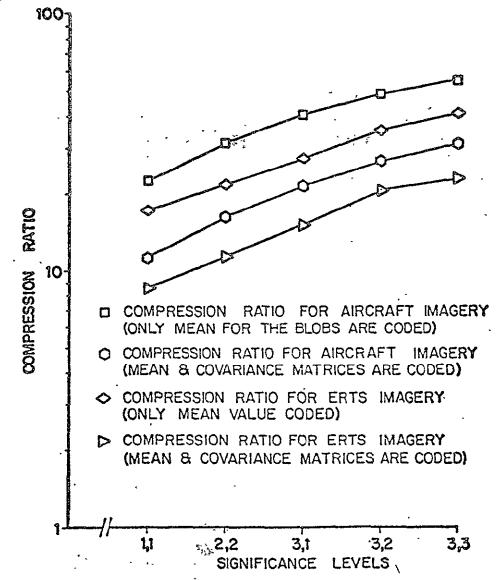

| 1.4.2(1)   | Data Compression Ratio for BLOB-Contour Encoding Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56   |

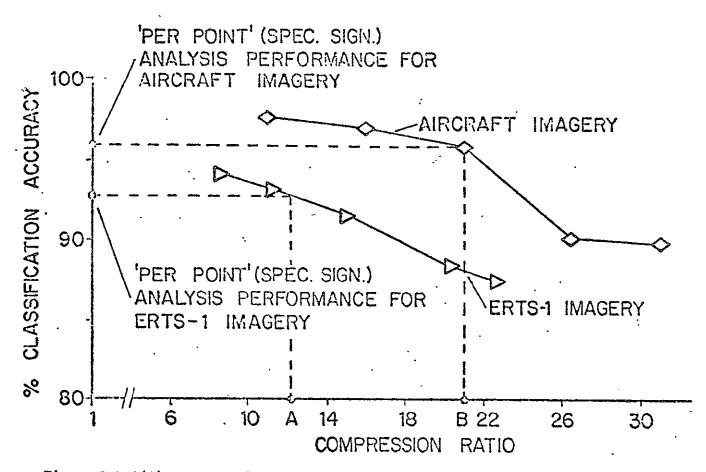

| 1.4.2(2)   | Compression Ratio vs Percent Classification Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57   |

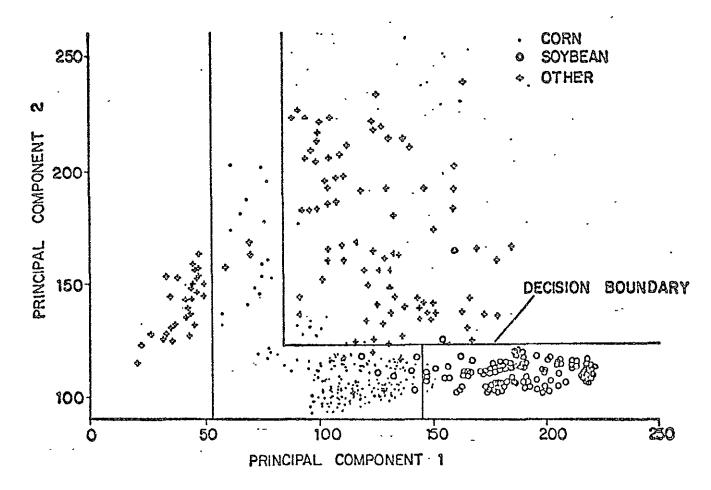

| 1.4.2(3)   | A Scatter Plot of First Principal Component vs the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|            | Second Principal Component of ERTS-1 Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59   |

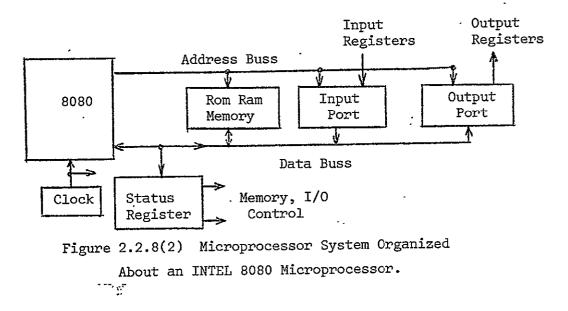

| 2.2.8(2)   | Microprocessor System Organized About an INTEL 8080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|            | Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78   |

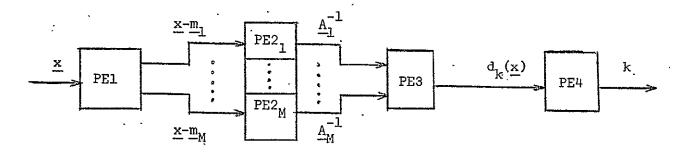

| 2.2.8(3)   | Organization of a Processing System for Executing the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|            | Maximum Likelihood Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83   |

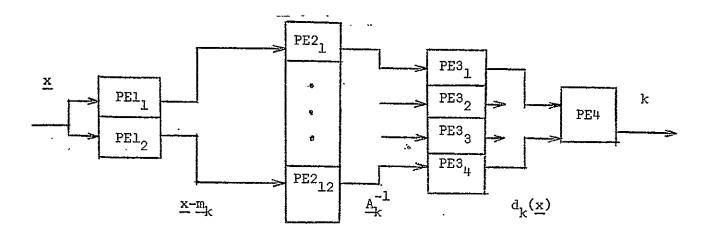

| 2.2.8(4)   | A More Efficient Organization for Executing the Maximum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 2.2.8(5)   | Likelihood Algorithm<br>Microprocessor System Organized About an INTEL 8080                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | · 84 |

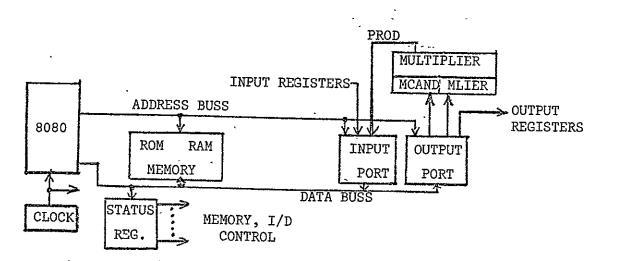

| 2.2.8(5)   | men of the second state of the second s | 01   |

| 2.2.8(7)   | Microprocessor and a Hardware Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 84   |

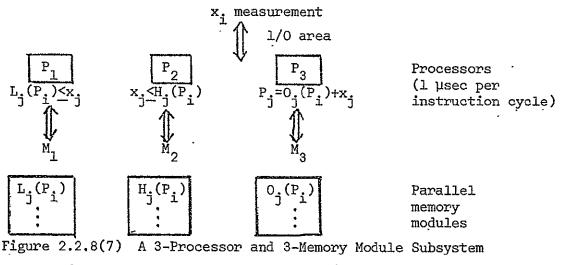

| 2.2.0(7)   | A 3-Processor and 3-Memory Module Subsystem for Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91   |

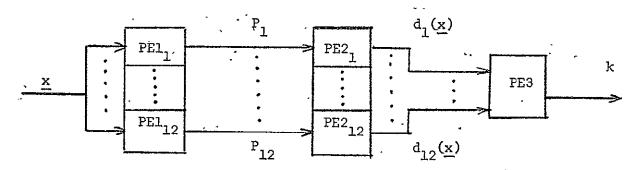

| 2.2.8(8)   | Look-Up Classification (Per Class)<br>A Microprocessor System Organized Similarly to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 91   |

| 2.2.0(0)   | Optimal Pipelined Arithmetic Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92   |

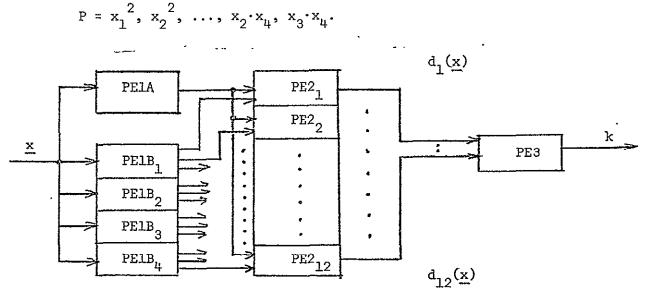

| 2.2.8(9)   | A More Efficient Microprocessor Organization for Imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32   |

| 2.2.0(0)   | • menting Eq. (2.2.8-8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94   |

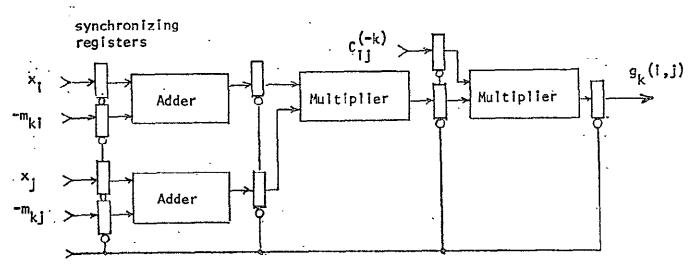

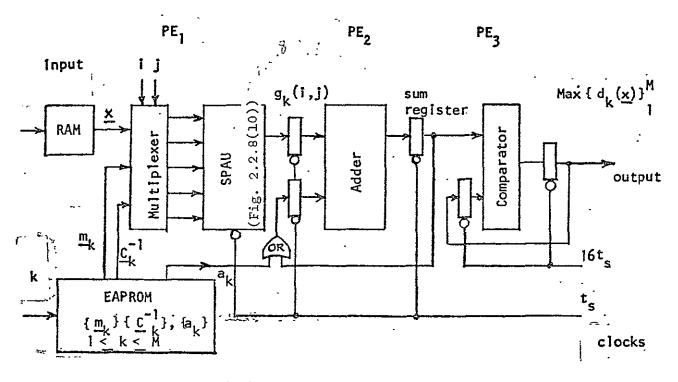

| 2.2.8(10)  | The Serial Pipelined Arithmetic Unit (SPAU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99   |

| 2.2.8(11)  | The Serial Computer Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100  |

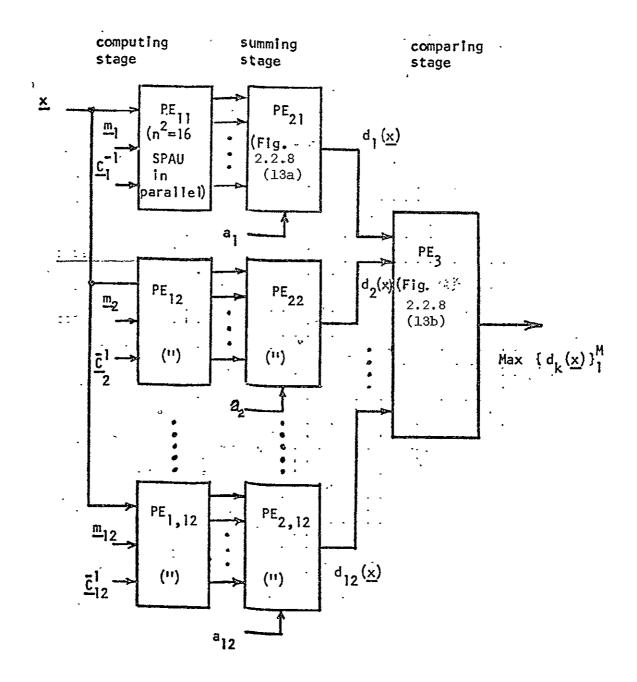

| 2.2.8(12)  | The Parallel Computer Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102  |

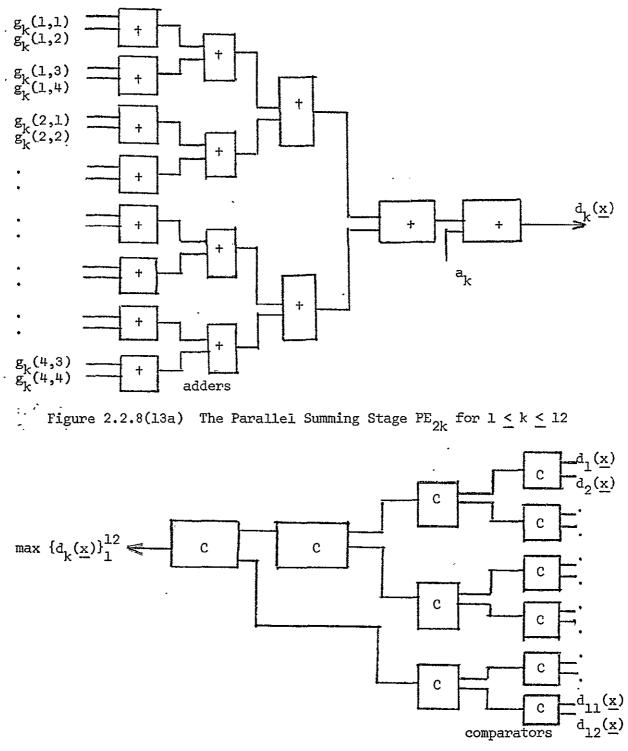

| 2.2.8(13a) | The Parallel Summing Stage $PE_{2k}$ for $1 \le k \le 12$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 103  |

| 2.2.8(135) | The Parallel Comparing Stage PE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 103  |

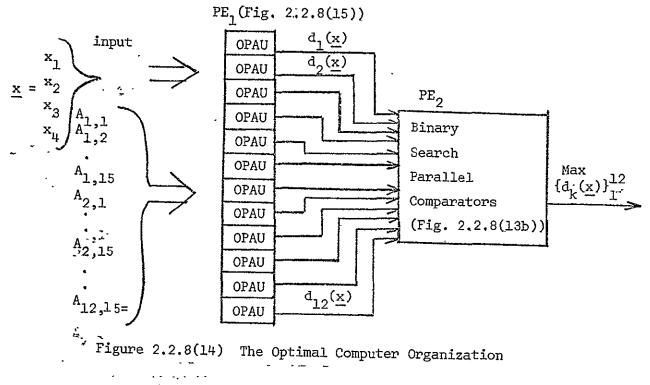

| 2.2.8(14)  | The Optimal Computer Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105  |

| 2.2.8(15)  | The Optimal Pipelined Arithmetic Unit (OPAU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106  |

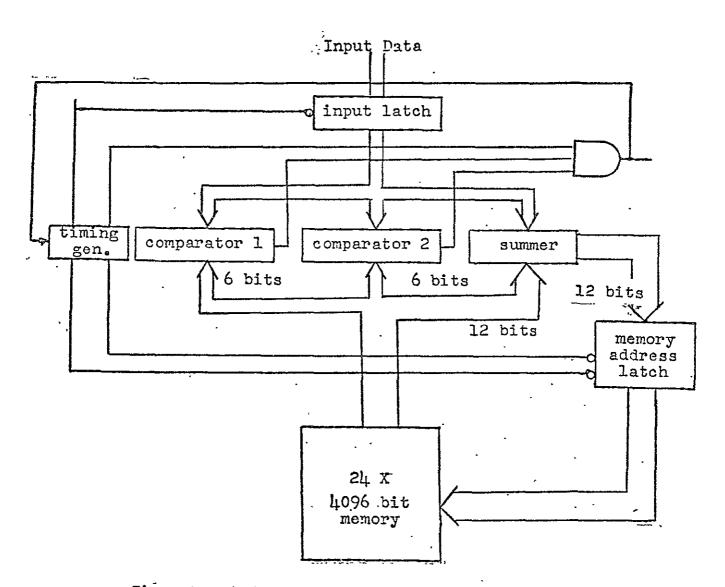

| 2.2.8(16)  | A Hardware Table Look-Up Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107  |

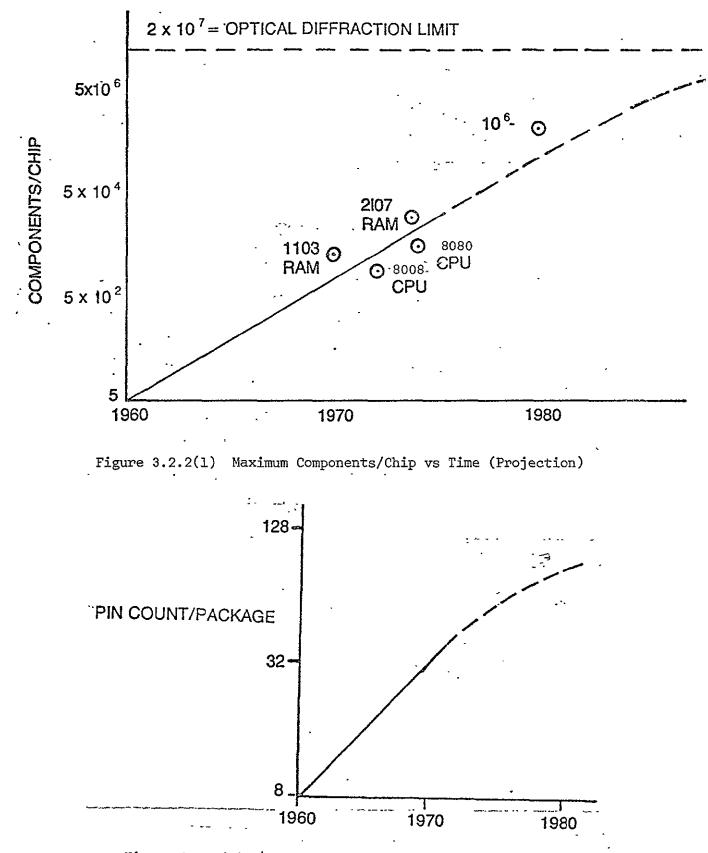

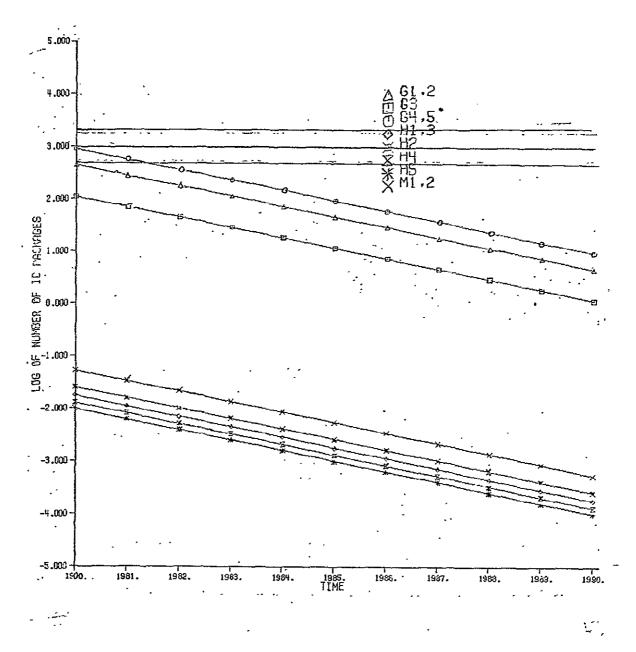

| 3,2.2(1)   | Maximum Components/Chip vs Time (Projection)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 118  |

| 3.2.2(2)   | LSI Package Pin Count Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 118  |

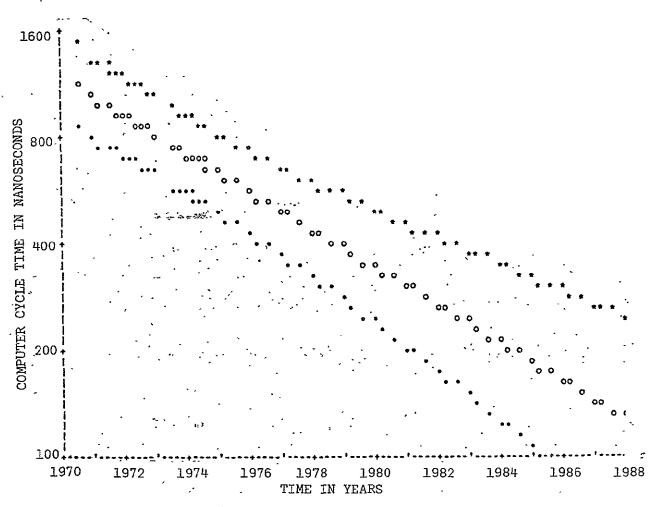

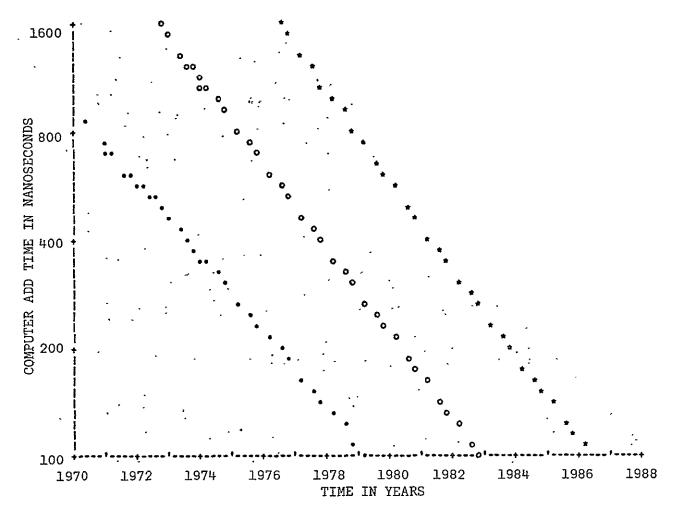

| 3.3.1(1)   | Computer Cycle Time Forecast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121  |

| 3.3.1(2)   | Computer Add Time Forecast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 122  |

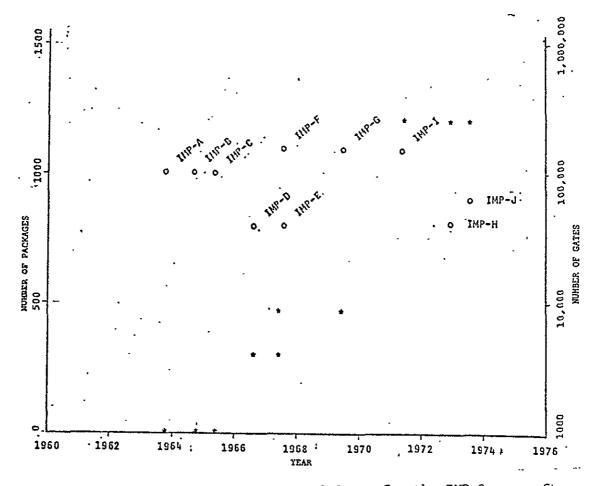

| 3.4(1)     | Numbers of IC Packages and Gates for the IMP Spacecraft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 123  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

LIST OF FIGURES (Continued)

| Figure     |                                                                                                                                                                                                                                                                         |      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Number.    | Title                                                                                                                                                                                                                                                                   | Page |

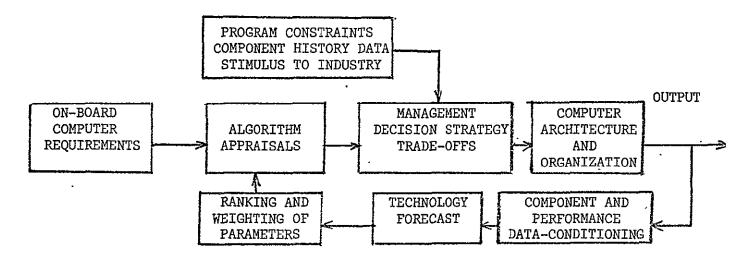

| 3.5(1) -   | Forecast Feedback System Model                                                                                                                                                                                                                                          | 124  |

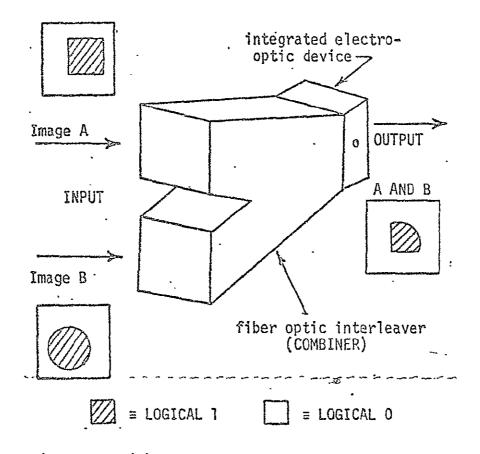

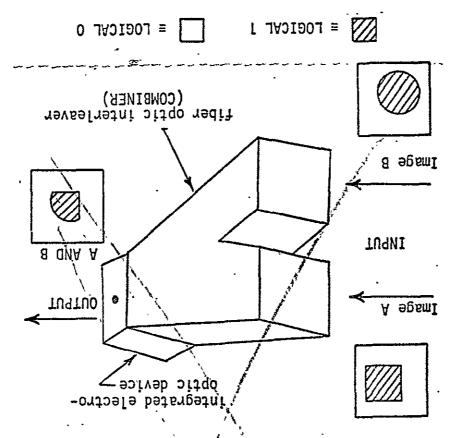

| 3.6.1(1)   | A Two tse Input, Digital AND Gate                                                                                                                                                                                                                                       | 127  |

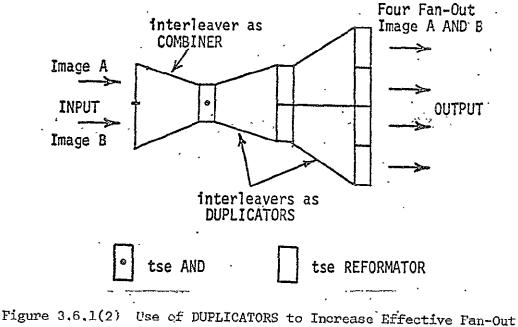

| 3.6.1(2)   | Use of DUPLICATORS to Increase Effective Fan-Out of a                                                                                                                                                                                                                   |      |

| •          | - tse Device to Four                                                                                                                                                                                                                                                    | 128  |

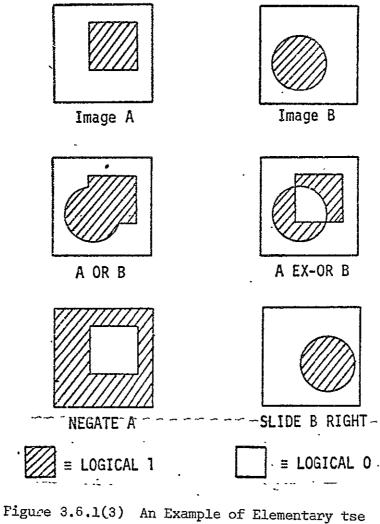

| 3.6.1(3)   | An Example of Elementary tse Operations on Typical<br>Images                                                                                                                                                                                                            | 129  |

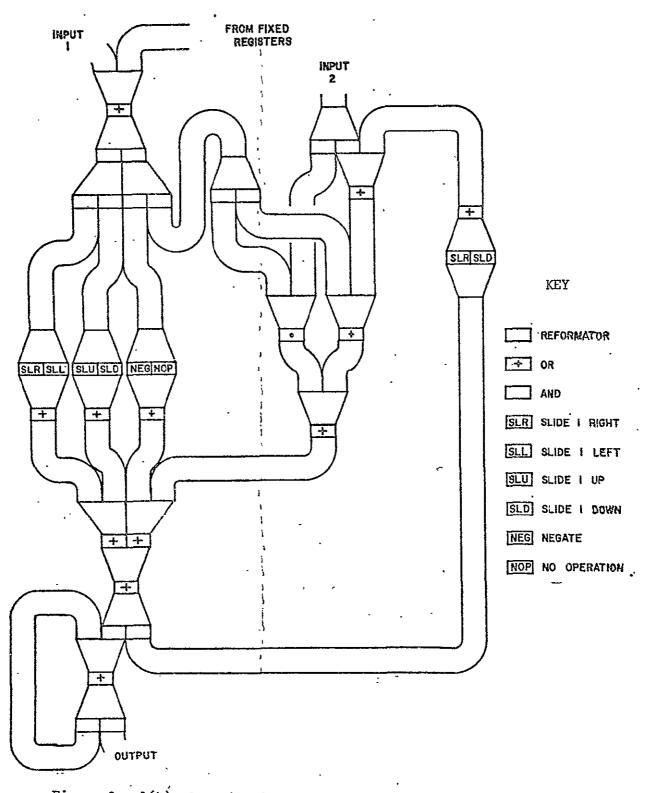

| 3.6.1(4)   | Organization of the tse Logical Operations Unit                                                                                                                                                                                                                         | 131  |

| 3.6.2(1)   | Basic Josephson Tunneling Gate                                                                                                                                                                                                                                          | 132  |

| 3.6.2(2)   | Performance Comparison for Logic Gates [33]                                                                                                                                                                                                                             | 133  |

| 4.4(1)     | Complexity Function Sensitivity to R and T (all Pro-                                                                                                                                                                                                                    |      |

|            | cessors)                                                                                                                                                                                                                                                                | 146  |

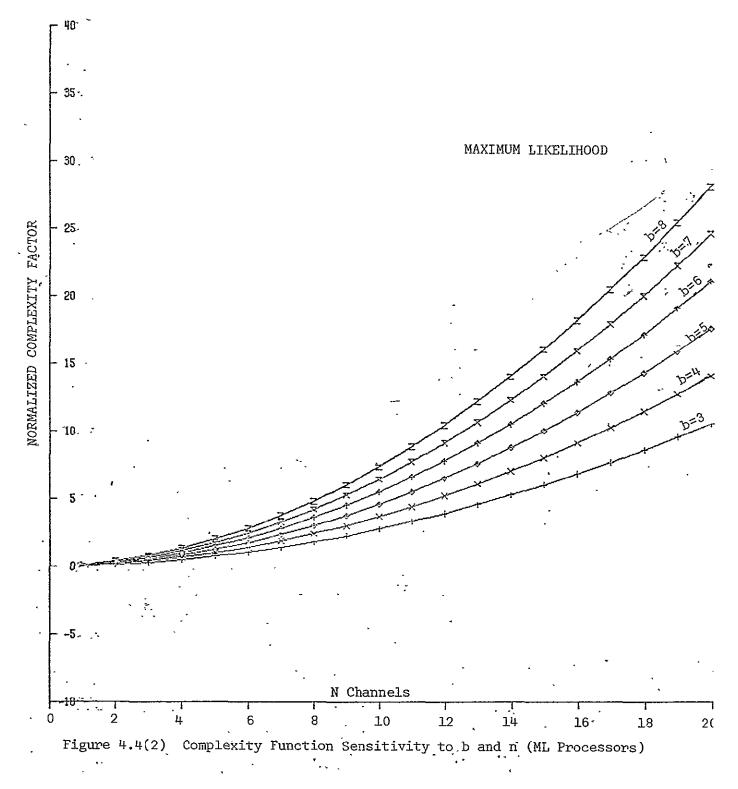

| 4.4(2)     | Complexity Function Sensitivity to b and n (ML Pro-<br>cessors)                                                                                                                                                                                                         | 147  |

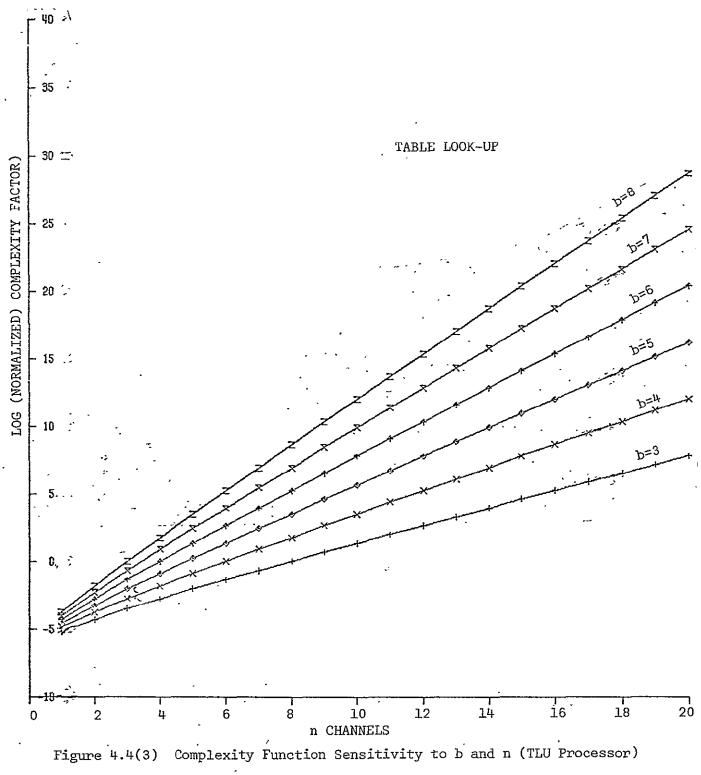

| 4.4(3)     | Complexity Function Sensitivity to b and n (TLU Pro-                                                                                                                                                                                                                    |      |

|            | cessor)                                                                                                                                                                                                                                                                 | 148  |

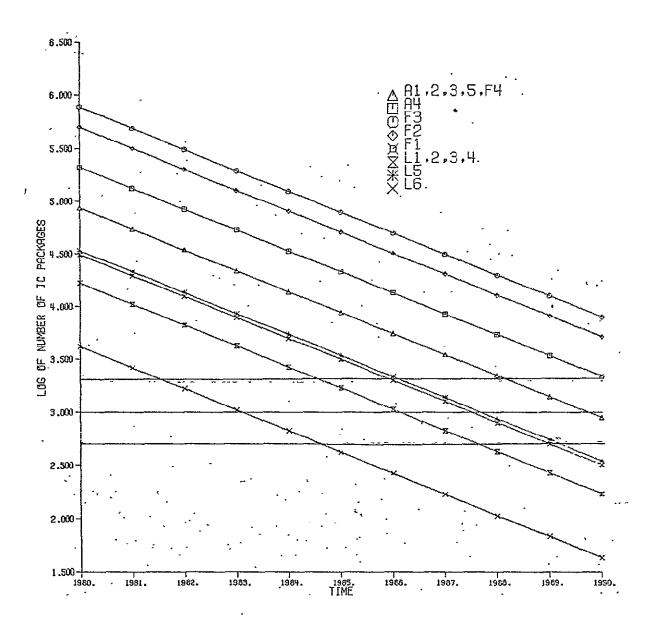

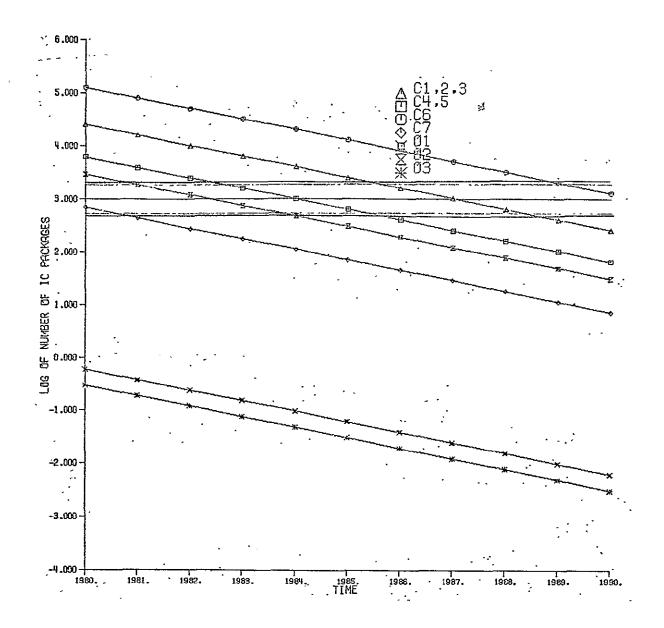

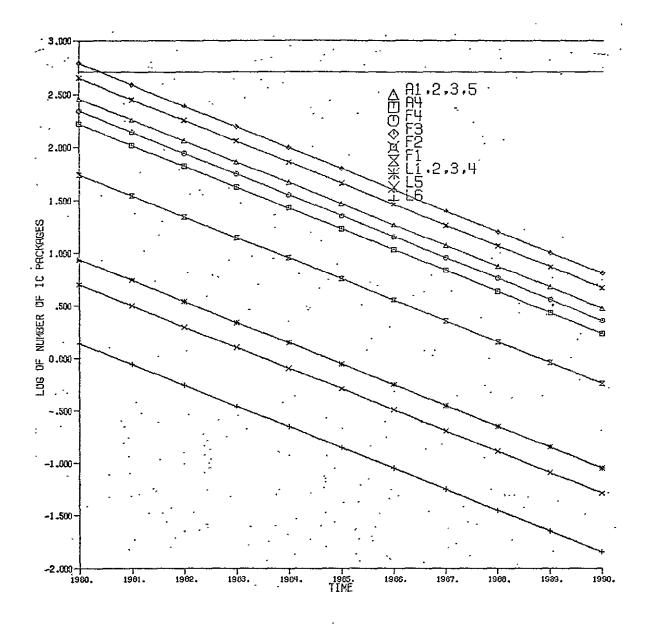

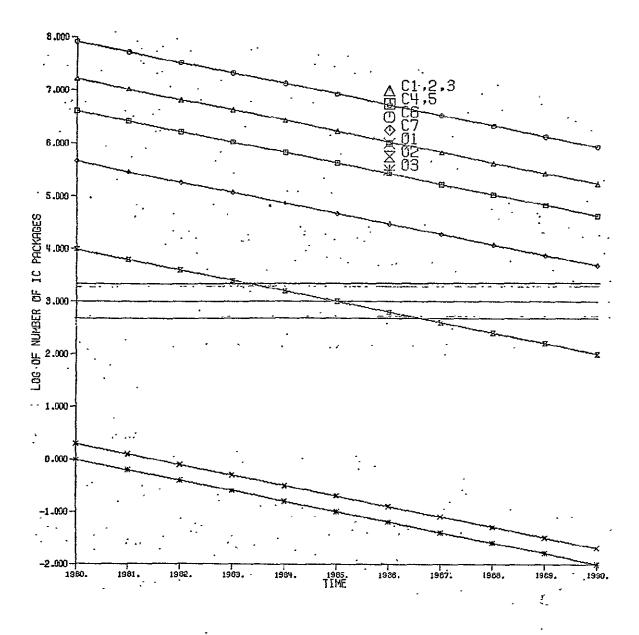

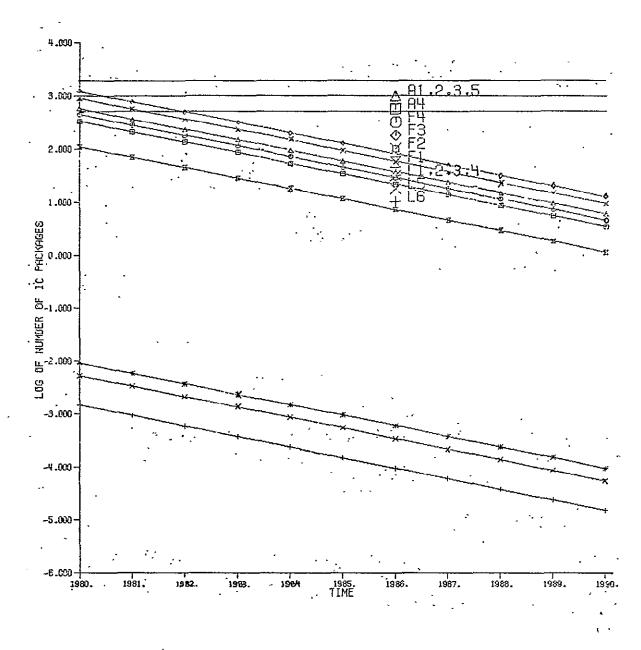

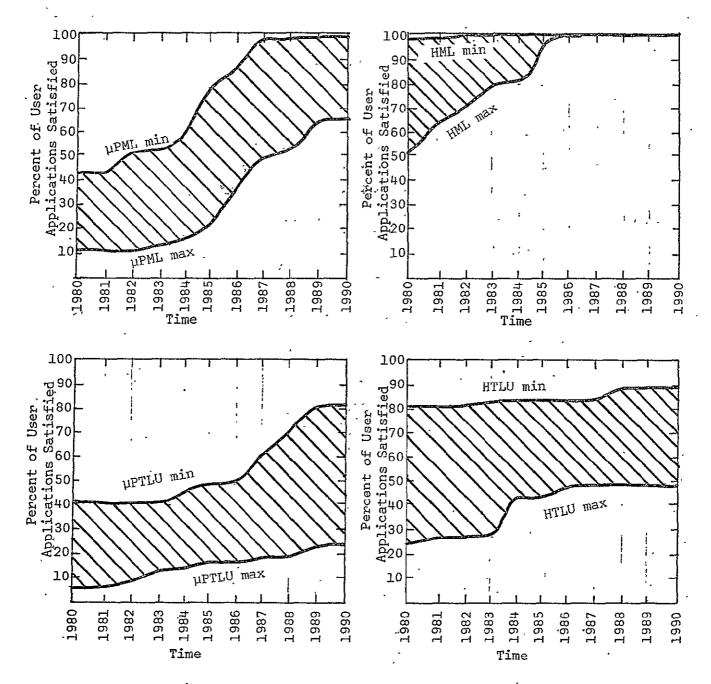

| 4.4.2(1)A  | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Maximum Likelihood (µPML) Processor for the<br>Maximum Data Rate Requirement in Table 1.1.2(I).                                                                                                     |      |

| 4.4.2(I)B  | Applications: Agriculture, Forestry and Geology<br>Number of IC's vs. Launch Date to Implement the Micro-<br>processor Maximum Likelihood (µPML) Processor for the<br>Minimum Data Rate Requirement in Table 1.1.2(1).                                                  | 151  |

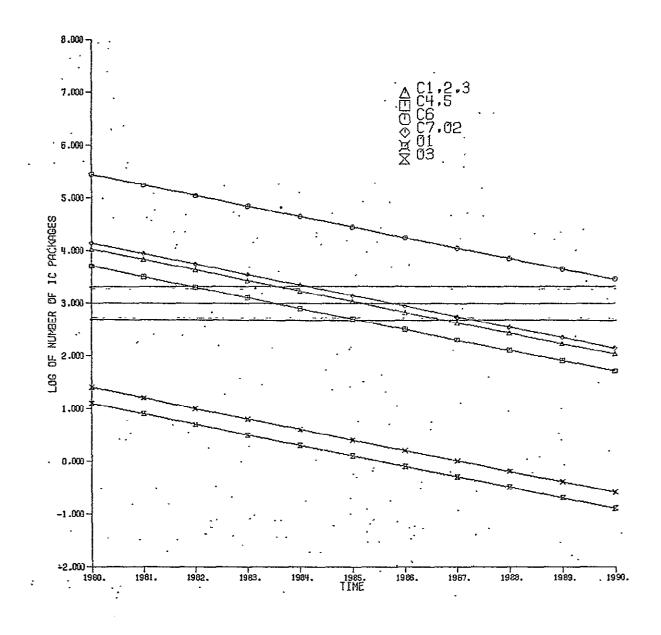

| 4.4.2(2)A  | Applications: Agriculture, Forestry and Geology<br>Number of IC's vs. Launch Date to Implement the Micro-<br>processor Maximum Likelihood (µPML) Processor for the<br>Maximum Data Rate Requirement in Table 1.1.2(I).<br>Applications: Coastal-Zone Studies and Global | 152  |

| 4.4.2(2)B  | Oceanography<br>Number of IC's vs. Launch Date to Implement the Micro-<br>Processor Maximum Likelihood (µPML) Processor for the<br>Minimum Data Rate Requirement in Table 1.1.2(I).<br>Applications: Coastal-Zone Studies and Global<br>Oceanography                    | 154  |

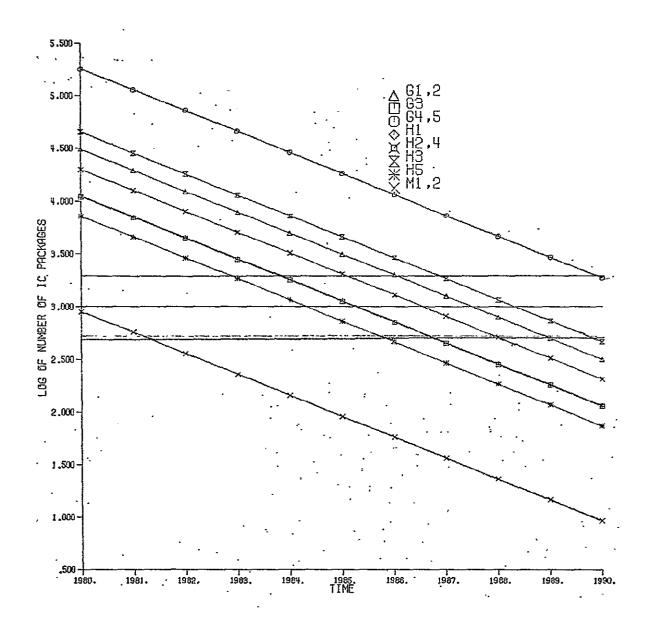

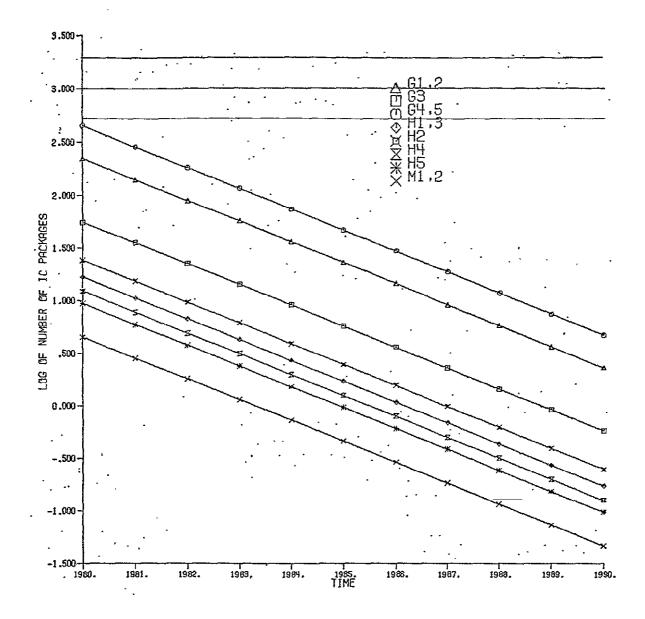

| 4.4.2(3)A  | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Maximum Likelihood (µPML) Processor for the<br>Maximum Data Rate Requirement in Table 1.1.2(I).<br>Applications: Geography, Hydrology and Meteorology                                               | 155  |

| 4.4.2(3)B  | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Maximum Likelihood (µPML) Processor for the<br>Minimum Data Rate Requirement in Table 1.1.2(I).<br>Applications: Geography, Hydrology and Meteorology                                               | 156  |

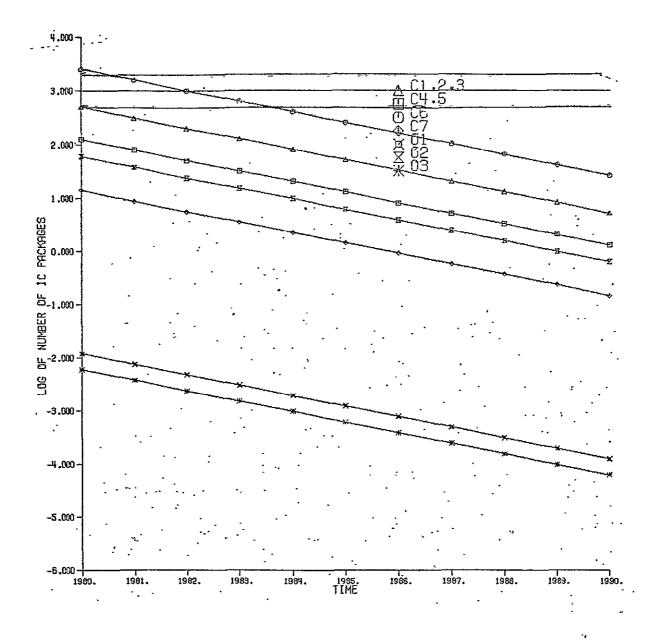

| 4.4.2(4)A  | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processor for the Maximum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Agriculture, Forestry and Geology                                                            |      |

| .4.4.2(4)B | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processor for the Minimum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Agriculture, Forestry and Geology                                                            |      |

|            |                                                                                                                                                                                                                                                                         |      |

LIST OF FIGURES (Continued)

•

| Figure<br>Number | Title                                                                                                                                                                                                                            | Page     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

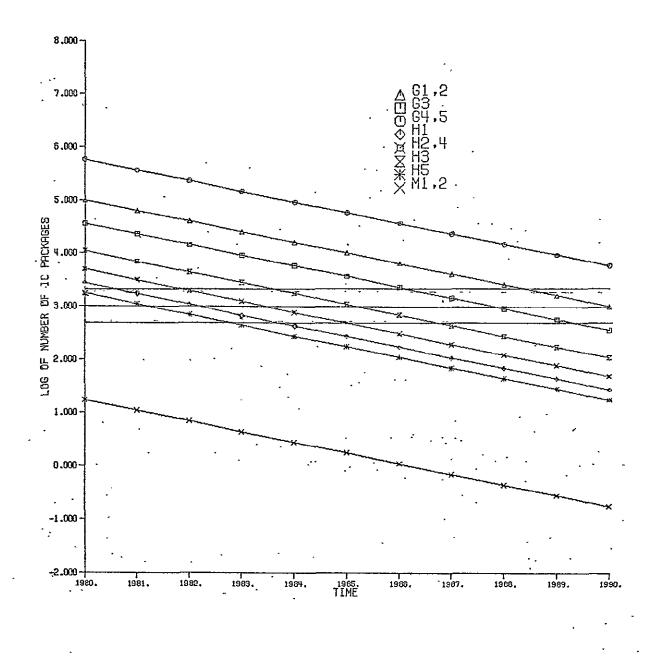

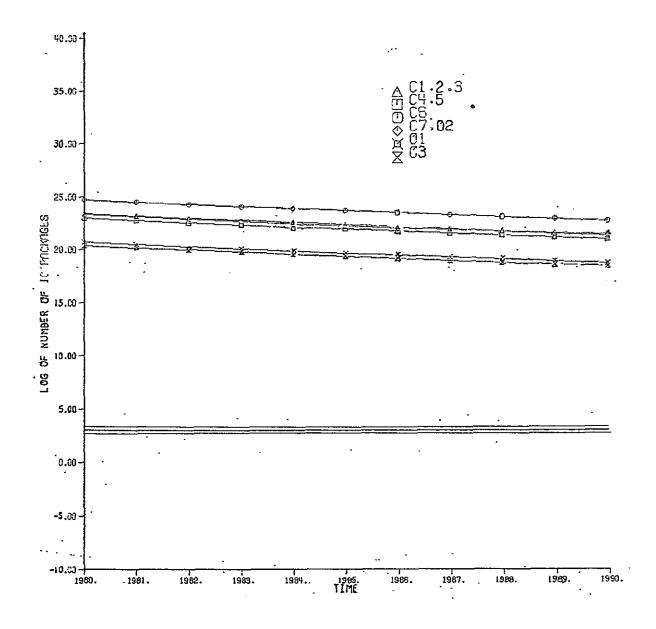

| 4.4.2(5)A        | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processor for the Maximum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Coastal-Zone Studies and Global Oceanography          | :<br>159 |

| 4.4.2(5)B        | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processor for the Minimum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Coastal-Zone Studies and Global Oceanography          | :<br>160 |

| 4.4.2(6)A        | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processdor for the Maximum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Geography, Hydrology and Meteorology                 | :<br>161 |

| 4.4.2(6)B        | Number of IC's vs. Launch Date to Implement the Hardware<br>Maximum Likelihood (HML) Processor for the Minimum<br>Data Rate Requirement in Table 1.1.2(I). Applications<br>Geography, Hydrology and Meteorology                  | : 162    |

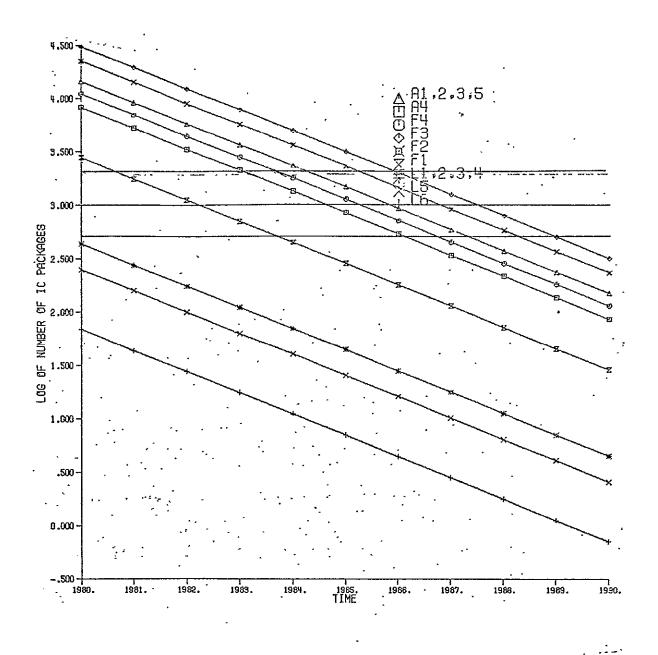

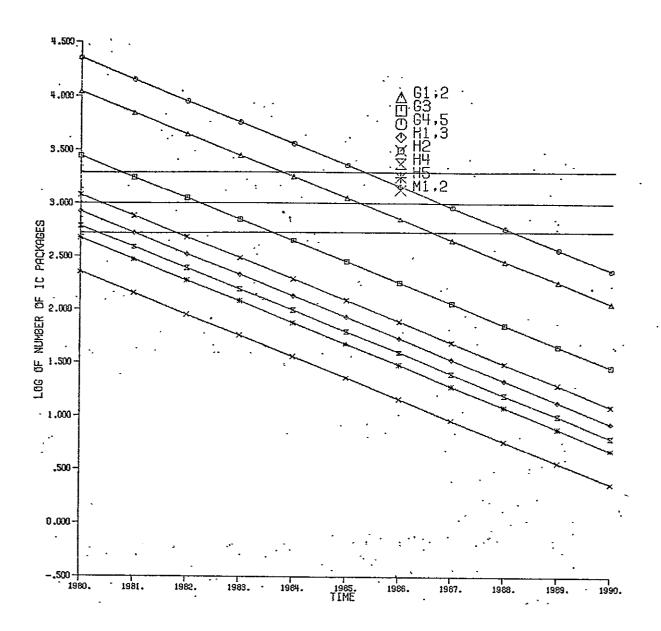

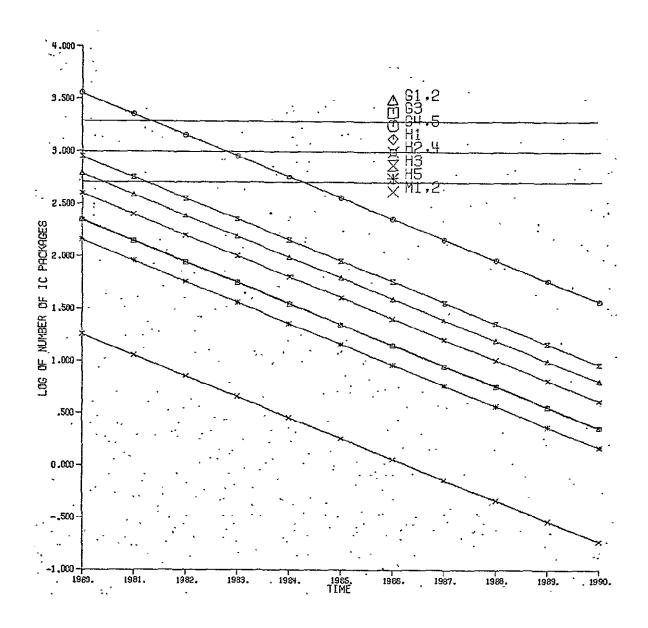

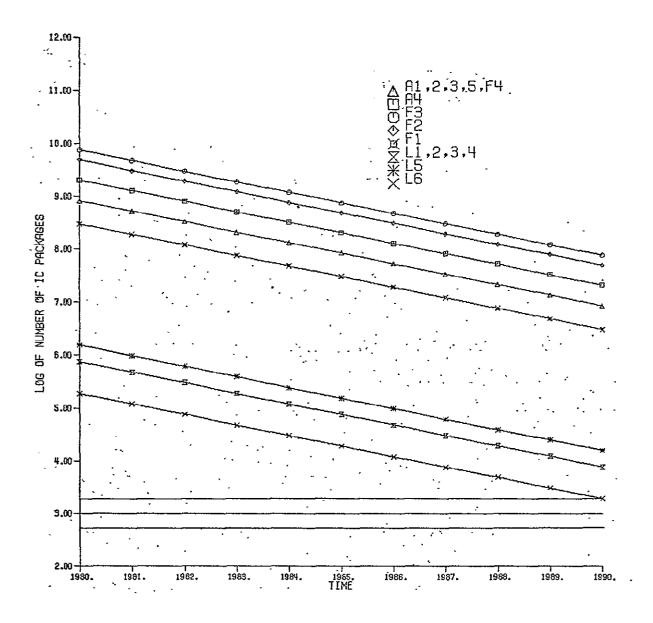

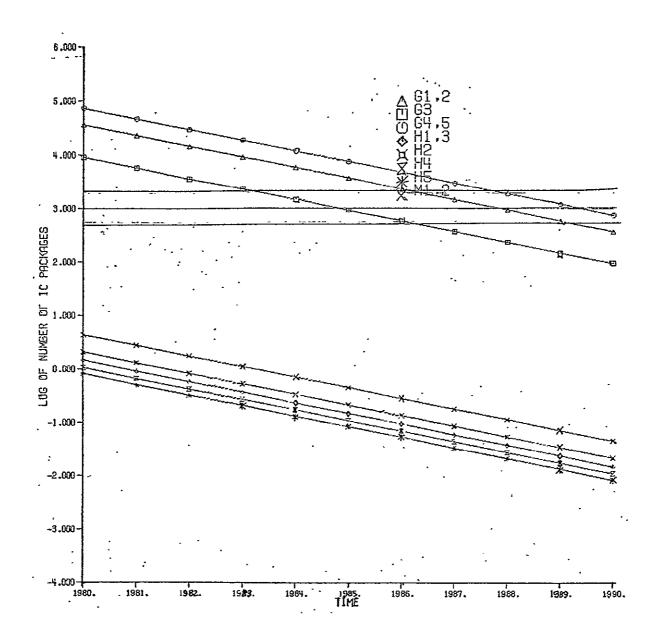

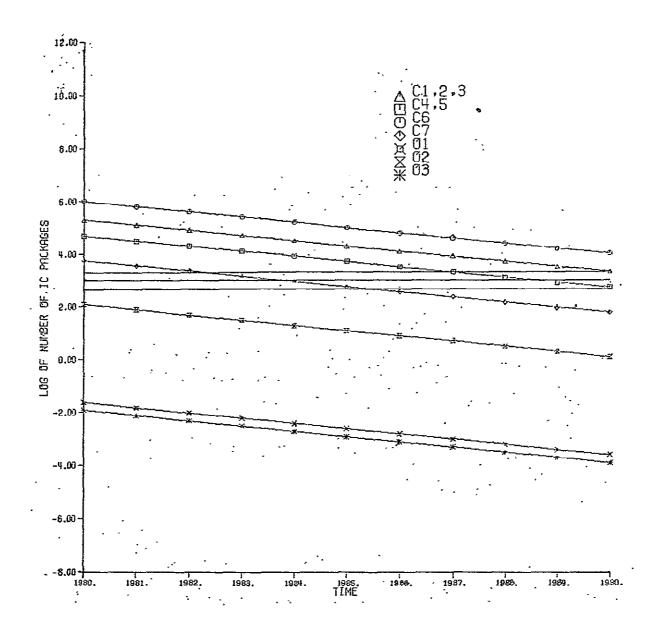

| 4.4.2(7)A        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the Maxi<br>mum Data Rate Requirement in Table 1.1.2(I). Applica-<br>tions: Agriculture, Forestry and Geology            | -        |

| 4.4.2(7)B        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the Mini<br>mum Data Rate Requirement in Table 1.1.2(I). Appli-<br>cations: Agriculture, Forestry and Geology            |          |

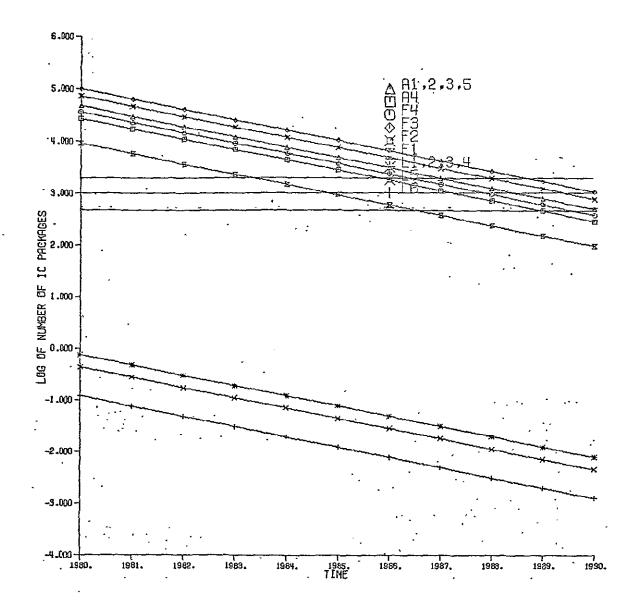

| 4.4.2(8)A        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the Maxi<br>mum Data Rate Requirement in Table 1.1.2(I). Applica-<br>tions: Coastal-Zone Studies and Global Oceanography | .—       |

| 4.4.2(8)B        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the Mini<br>mum Data Rate Requirement in Table 1.1.2(I). Appli-<br>cations: Coastal-Zone Studies and Global Oceanography |          |

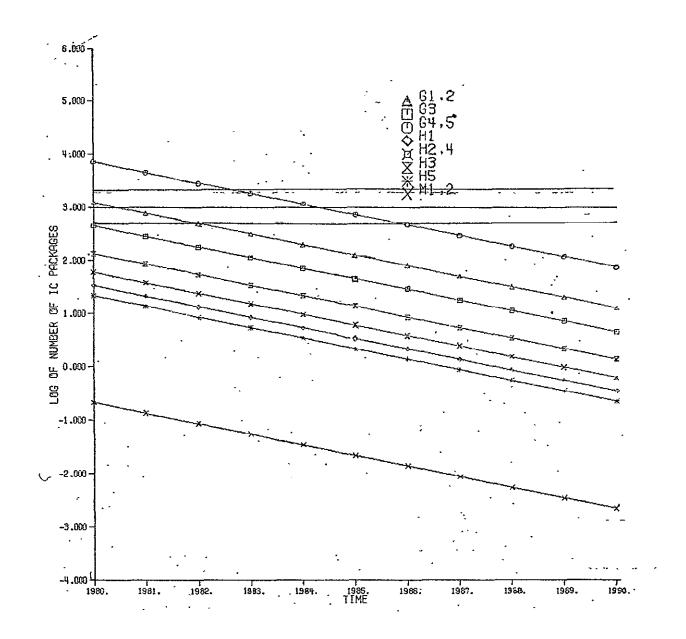

| 4.4.2(9)A        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the Maxi<br>mum Data Rate Requirement in Table 1.1.2(I). Appli-<br>cations: Geography, Hydrology and Meteorology         |          |

| 4.4.2(9)B        | Number of IC's vs. Launch Date to Implement the Micro-<br>processor Table Look-Up (µPTLU) Processor for the<br>Minimum Data Rate Requirement in Table 1.1.2(I).<br>Applications: Geography, Hydrology and Meteorology            | 168      |

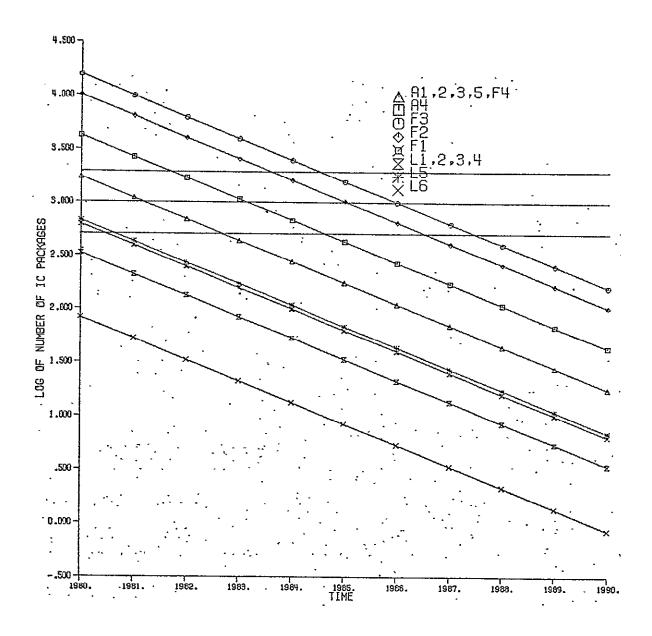

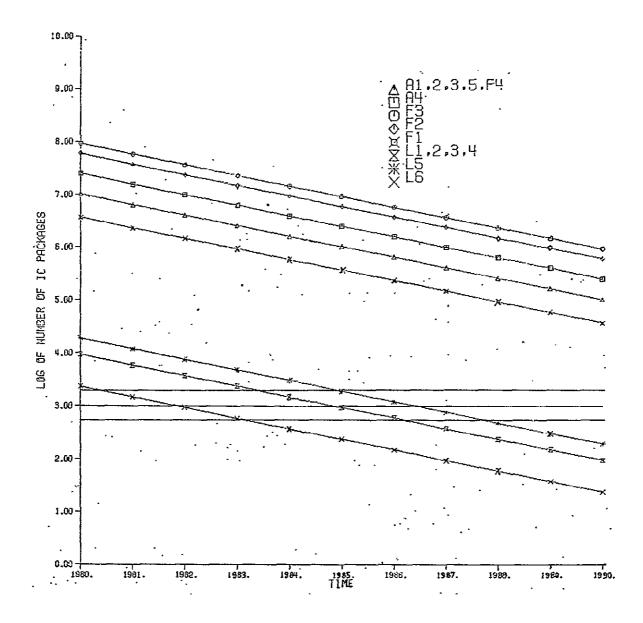

| 4.4.2(10)A       | Number of IC's vs. Launch Date to Implement the Hardware<br>Table Look-Up (HTLU) Processor for the Maximum Data<br>Rate Requirement in Table 1.1.2(I). Applications:<br>Agriculture, Forestry and Geology                        | 169      |

| 4.4.2(10)B       | Number of IC's vs. Launch Date to Implement the Hardware<br>Table Look-Up (HTLU) Processor for the Minimum Data<br>Rate Requirement in Table 1.1.2(I). Applications:                                                             |          |

|                  | Agriculture, Forestry and Geology                                                                                                                                                                                                | 170      |

# LIST OF FIGURES (Continued)

•

.

| Figure<br>Number | Title                                                                                                                                                                                                                | Page     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

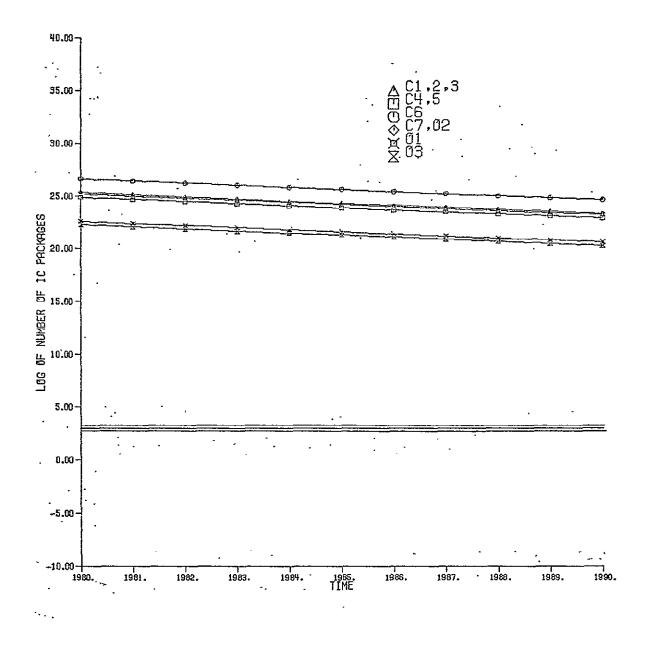

| 4.4.2(11)A       | Number of IC's vs. Launch Date to Implement the Hardware<br>Table Löok-Up (HTLU) Processor for the Maximum Data<br>Rate Requirement in Table 1.1.2(I). Applications:                                                 |          |

| 4.4.2(11)B       | Coastal-Zone Studies and Global Oceanography<br>Number of IC's vs. Launch Date to Implement the Hardware<br>Table Look-Up (HTLU) Processor for the Minimum Data<br>Rate Requirement in Table 1.1.2(I). Applications: | 171      |

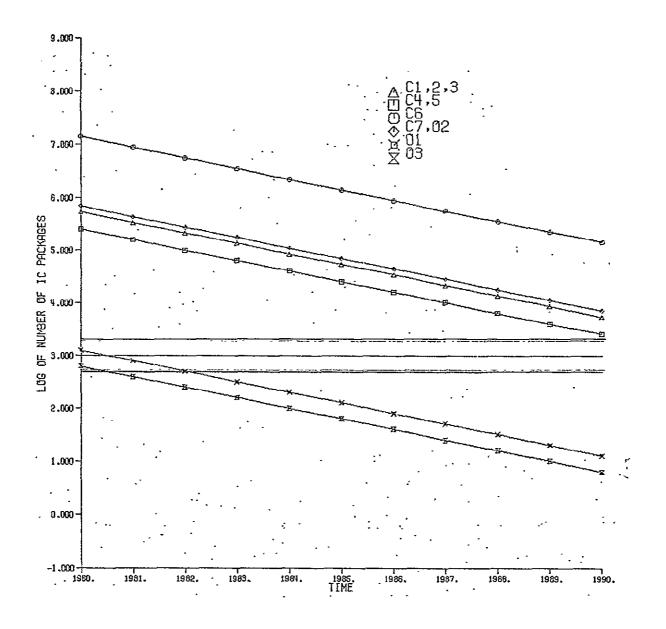

| 4.4.2(12)A       | Coastal-Zone Studies and Global Oceanography<br>Number of IC's vs. Launch Date to Implement the Hardware<br>Table Look-Up (HTLU) Processor for the Maximum Data<br>Rate Requirement in Table 1.1.2(I). Applications: | 172<br>- |

|                  | Geography, Hydrology and Meteorology                                                                                                                                                                                 | 173      |

| 4.4.2(12)B       | Number of IC's vs. Launch Date to Implement the Hardware<br>Table Look-Up (HTLU) Processor for the Minimum Data<br>Rate Requirement in Table 1.1.2(I). Applications:                                                 |          |

|                  | Geography, Hydrology and Meteorology                                                                                                                                                                                 | 174      |

| 5.1.1(1)         | Study Plan                                                                                                                                                                                                           | 183      |

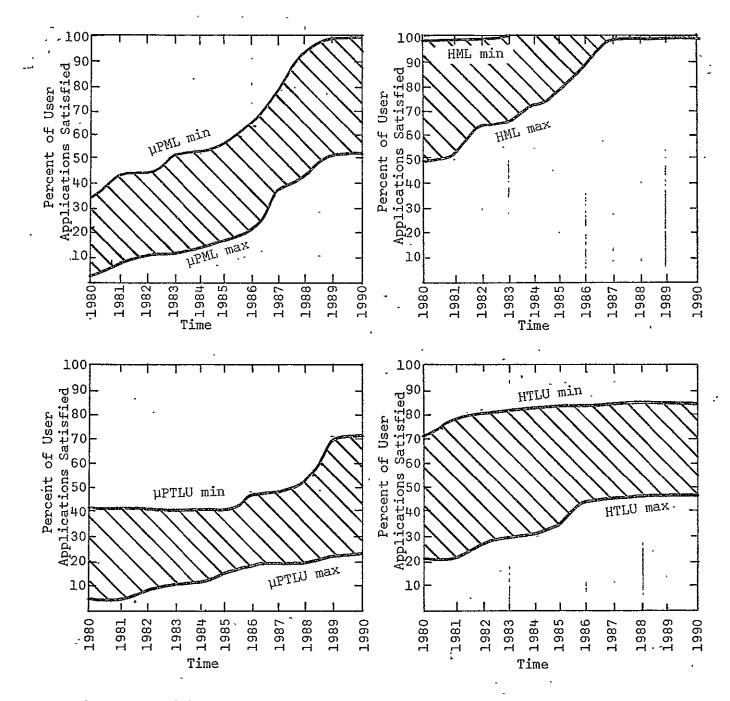

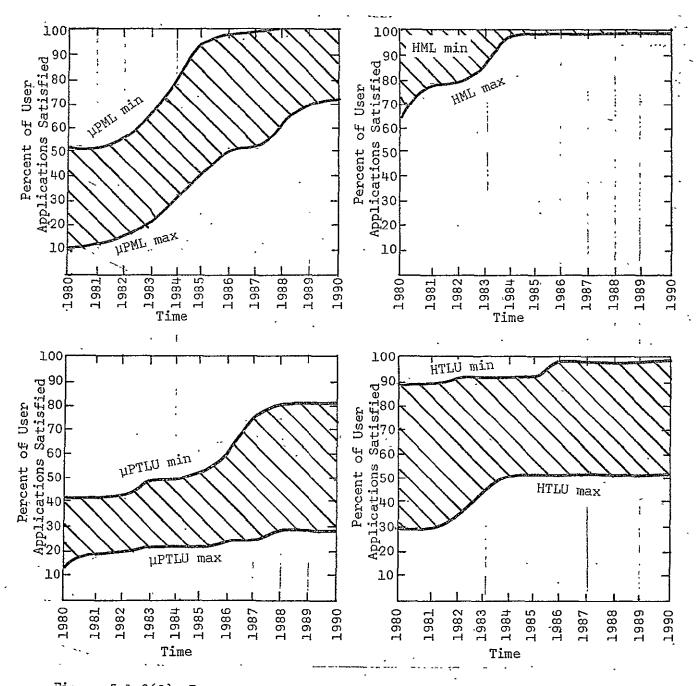

| 5.1.8(1)         | Percent of User Applications Satisfied as a Function of<br>Time (1,000 IC's)                                                                                                                                         | 190      |

| 5.1.8(2)         | Percent of User Applications Satisfied as a Function of<br>Time (500 IC's)                                                                                                                                           | 191      |

| 5.1.8(3)         | Percent of User Applications Satisfied as a Function of<br>Time (2,000 IC's)                                                                                                                                         | 192      |

.

NOTE:

A 28-page summary report is also available as:

Satellite On-Board Processing for Earth Resources Data--Summary Report, CR 137757, NASA/ARC, Moffett Field, California, 94035.

#### 0 INTRODUCTION

Most of the past effort in the field of earth resources data processing has been research oriented. Earth resources imagery has been provided by NASA to a number of researchers who have processed the data in various ways in order to determine what, if any, useful information could be extracted from the given images. These experiments have demonstrated that useful information can indeed be extracted from aircraft and satellite multispectral scanner imagery of the earth's surface. Economic studies have indicated potential cost effective systems based on these techniques. Consequently, it is anticipated that during the 1980-1990 decade earth resources satellites will be designed and flown for specific purposes, i.e., to monitor severe weather systems, to monitor water pollution, to survey and monitor world food production, etc. In. these applications it may be more cost effective to process the data on-board the satellite and transmit the data products directly to the users rather than transmit the raw data to a ground processing station for generating the data products and then distributing the data products to the users via another satellite system.

The purpose of this study was to investigate the feasibility of an onboard earth resources data processor launched during the 1980-1990 time frame. Since about five years are required to design, build, check out, and launch such a system, a 1980 system would be based on 1975 technology, and a 1990 system would be based on 1985 technology.

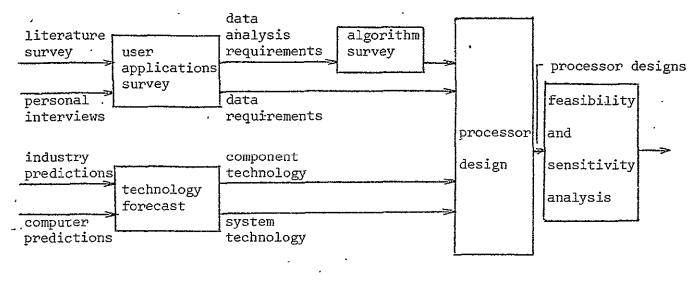

In order to determine the feasibility of on-board processing we must first define the on-board processor. This requires that we define both the technology available for use in the design and the computational requirements required of the processor. The computational requirements depend on the algorithms that the processor must implement which in turn, depend on the data products that must be extracted from the data to satisfy the users. Consequently, in order to determine the feasibility of on-board data processors we must start with a study of projected user applications to define the data format (data throughput rate, number of spectral bands, etc.) and the information extraction algorithms the processor must implement. Based on these constraints and the constraints imposed by the available technology we can design some on-board processors and evaluate their feasibility. The study plan is summarized in Figure 0(1).

Figure 0(1) Study Plan

A brief description of the content of each of the succeeding sections of this report follows.

Section 1. In this section we present the results of a survey of earth resources user applications and their data requirements, earth resources multispectral scanner sensor technology, preprocessing algorithms for correcting the sensor outputs and for data bulk reduction, and a candidate data format to be used in subsequent sections.

Section 2. This section contains the computational requirements required to implement the data analysis algorithms, a review of some computer architectures and organizations, a design of some computer architectures capable of handling the algorithm computational requirements, and a discussion of the on-board processor environmental effects.