# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

# NASA CONTRACTOR REPORT

NASA CR-124210

3

4

1

÷

| (NASA-CR-124210) | LCGSIM USER'S MAN | UAL (MES | N76-22942 |

|------------------|-------------------|----------|-----------|

| Computing, Inc.) |                   | CSCL 09B |           |

Unclas G3/61 25278

ì

2

# LOGSIM USER'S MANUAL

By C. L. Mitchell and J. F. Taylor

M&S Computing, Inc. Huntsville, Alabama 35805

January 13, 1972

Prepared for

NASA - GEORGE C. MARSHALL SPACE FLIGHT CENTER Marshall Space Flight Center, Alabama 35812

| CR-124210                                                                                                                                                                                       |                                                                                                |                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|                                                                                                                                                                                                 | 2. GOVERNMENT ACCESSION NO.                                                                    | 3. RECIPIENT'S CATALOG NO.                                     |

| 4 TITLE AND SUBTITLE                                                                                                                                                                            | <del></del>                                                                                    | 5. REPORT DATE                                                 |

|                                                                                                                                                                                                 |                                                                                                | January 13, 1972                                               |

| LOGSIM USER'S MANUAL                                                                                                                                                                            |                                                                                                | 5. PERFORMING ORGANIZATION CODE                                |

| 7. AUTHOR(S)                                                                                                                                                                                    |                                                                                                | 8. PERFORMING ORGANIZATION REPORT                              |

| C. L. Mitchell and J. F. Tay                                                                                                                                                                    |                                                                                                | 72-0001                                                        |

| 9. PERFORMING ORGANIZATION NAME AND                                                                                                                                                             | ADDRESS                                                                                        | 10. WORK UNIT NO.                                              |

| M&S Computing, Inc.                                                                                                                                                                             |                                                                                                | 11. CONTRACT OR GRANT NO.                                      |

| P. O. Box 5183                                                                                                                                                                                  |                                                                                                | NAS8-25621                                                     |

| Huntsville, Alabama 35805                                                                                                                                                                       |                                                                                                | 13. TYPE OF REPORT & PERIOD COVERE                             |

| 2 SPONSORING AGENCY NAME AND ADDRE                                                                                                                                                              | iss                                                                                            |                                                                |

|                                                                                                                                                                                                 |                                                                                                | Contractor Report                                              |

| National Aeronautics and Space                                                                                                                                                                  | ce Administration                                                                              |                                                                |

| Washington, D. C. 20546                                                                                                                                                                         |                                                                                                | 14. SPONSORING AGENCY CODE                                     |

| SUPPLEMENTARY NOTES                                                                                                                                                                             |                                                                                                | <u> </u>                                                       |

| All program options are expla<br>is given. The detail descripti<br>not included in this report, bu<br>"Programmer's Manual for Lo<br>Programmer's Manual in order<br>LOGSIM Program; however, i | ined and a detailed definition of the internal logic and flo<br>t has been incorporated into a |                                                                |

| familiar with the internal open<br>capabilities inherent within the                                                                                                                             | it will not be necessary for the<br>ration of the LOGSIM Program                               | hat every user review the<br>of the functions performed by the |

| 19. SECURITY CLASSIF, (of this report) | 20. SECURITY GLASSIE, (of this page) | 21. NO. OF PAGES | 22. PRICE |

|----------------------------------------|--------------------------------------|------------------|-----------|

| Unclassified                           | Unclassified                         | 84               | NTIS      |

MSFC - Form 3292 (Rev December 1972)

.

For side by National Technical Information Service, Springfield, Vironna 22(15).

.

4

.

•

| Secti | ion       |                   |                                             | Page |

|-------|-----------|-------------------|---------------------------------------------|------|

| List  | of Figure | 9                 |                                             | v    |

| List  | of Tables |                   |                                             | vii  |

| 1.    | INTRO     | DUCTION           |                                             | I    |

| Ζ.    | LOGSI     | M PROGRA          | AM OPERATIONS                               | 2    |

|       | 2.1       | LOGSIM<br>Decay I | l Representation of Logic Delay and<br>imes | 2    |

|       | 2.2       | Sequenc           | e of LOGSIM Operations                      | 5    |

|       |           | 2.2.1             | Preprocessing                               | 5    |

|       |           | 2.2.2             | Simulation                                  | 7    |

|       |           | 2.2.3             | Postprocessing                              | 7    |

| 3.    | PREPA     | RATION            | OF LOGSIM INPUT DATA                        | 10   |

|       | 3.1       | Program           | n Capabilities and Limitations              | 10   |

|       | 3.2       | Compon            | ent Type Definitions                        | 11   |

|       | 3.3       | Time Sp           | ecifications                                | 19   |

|       | 3.4       | Prepara           | tion of the Logic Network Descriptions      | 19   |

| 4.    | DATA      | CARD FOI          | RMATS                                       | 28   |

|       | 4.1       | Preproc           | essor Data Cards                            | 28   |

|       |           | 4.1.1             | Title (NAME) Card - Optional                | 28   |

|       |           | 4.1.2             | Control (CONT) Card - Optional              | 28   |

|       |           | 4.1.3             | Specifications (SPEC Card - Required)       | 33   |

# TABLE OF ©ONTENTS (continued)

ð

•

| Section |          |                                                                             | Page |

|---------|----------|-----------------------------------------------------------------------------|------|

|         | 4.1.4    | Time (DTMR, DTMF, DTCM) Cards<br>Required                                   | 34   |

|         | 4,1.5    | New Gate Specification (NEWGATE)<br>Cards - Optional                        | 35   |

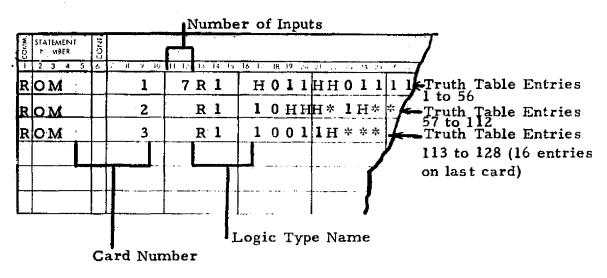

|         | 4.1.6    | Read-Only-Memory Specification<br>(ROM) Cards - Optional                    | 40   |

|         | 4.1.7    | Logic Gate Description (NET) Cards -<br>Required                            | 43   |

|         | 4, 1, 8  | Generator Description (GEN) Cards -<br>(one GEN or GENF required)           | 48   |

|         | 4.1.9    | Generator Function Description (GENF)<br>Cards - (one GEN or GENF required) | 49   |

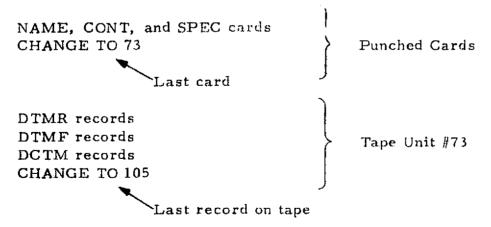

|         | 4.1.10   | Logical Unit Change (CHANGE TO) Cards                                       | 52   |

| 4.2     | Postproe | cessor Data Cards                                                           | 53   |

|         | 4.2.1    | Control (CONT) Card - Optional                                              | 53   |

|         | 4.2.2    | Character (CRCT) Card - Optional                                            | 54   |

|         | 4.2.3    | Character Shift (SHFT) Card -<br>Optional                                   | 56   |

|         | 4.2.4    | Level Comparison (CMP) Cards -<br>Optional                                  | 57   |

|         | 4.2.5    | Compare Function (CMPF) Cards -<br>Optional                                 | 58   |

|         | 4.2.6    | Output Print List (PNT) Cards -<br>Required                                 | 59   |

|         | 4.2.7    | Output Time Slot (SLOT) Cards -<br>Required                                 | 60   |

# TABLE OF CONTENTS (continued)

| Section |        |                       | Page |

|---------|--------|-----------------------|------|

| 5.      | LOGSIM | OUTPUT INTERPRETATION | 62   |

|         | 5.1    | Preprocessor Output   | 62   |

|         | 5.2    | Postprocessor Output  | 69   |

Contraction of the second

and the second second

# LIST OF FIGURES

d

| No.        | Title                                                                                                                 | Page   |

|------------|-----------------------------------------------------------------------------------------------------------------------|--------|

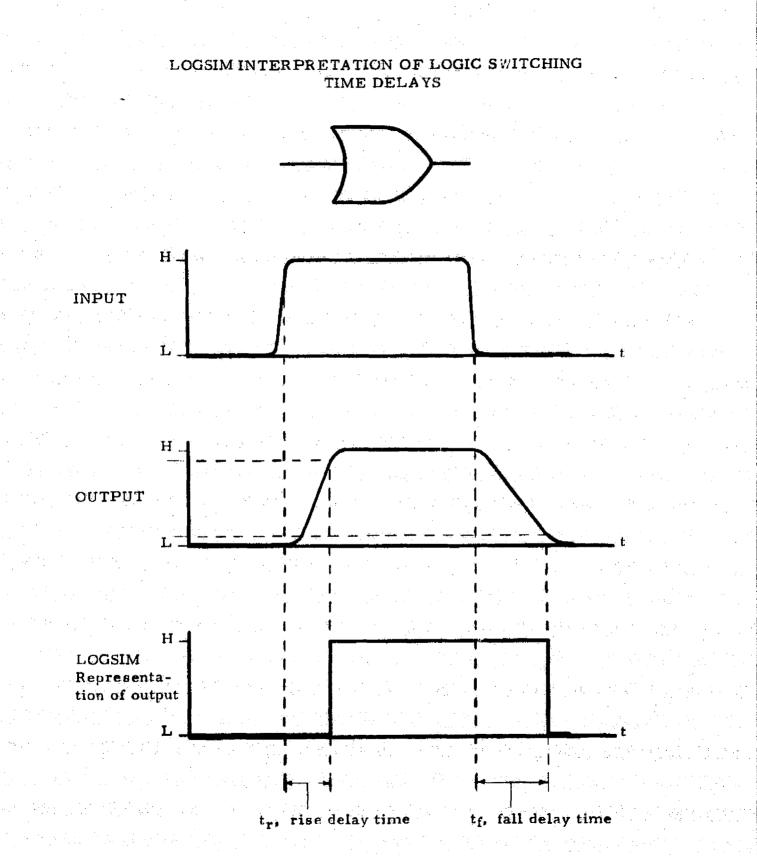

| 2-1        | LOGSIM Interpretation of Logic Switching Time<br>Delays                                                               | 3      |

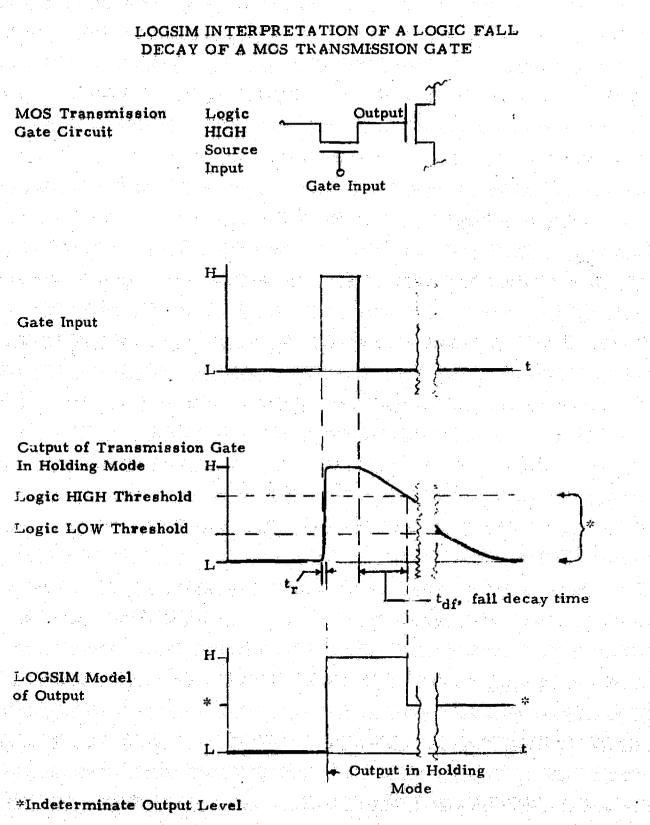

| 2-2        | LOGSIM Interpretation of a Logic Fall Decay of a<br>MOS Transmission Gate                                             | 4      |

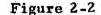

| 2-3        | LOGSIM Flow of Execution                                                                                              | 6      |

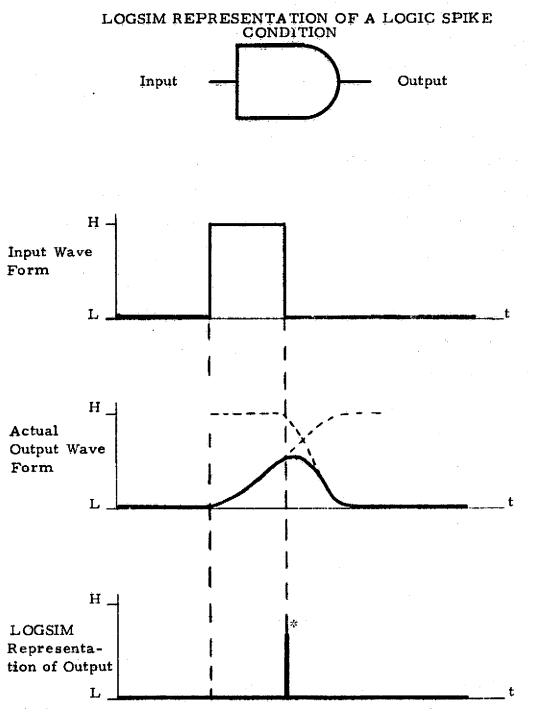

| 2-4        | LOGSIM Representation of a Logic Spike Condition                                                                      | 8      |

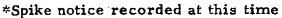

| 3-1        | Sample MOS Logic Network                                                                                              | 22     |

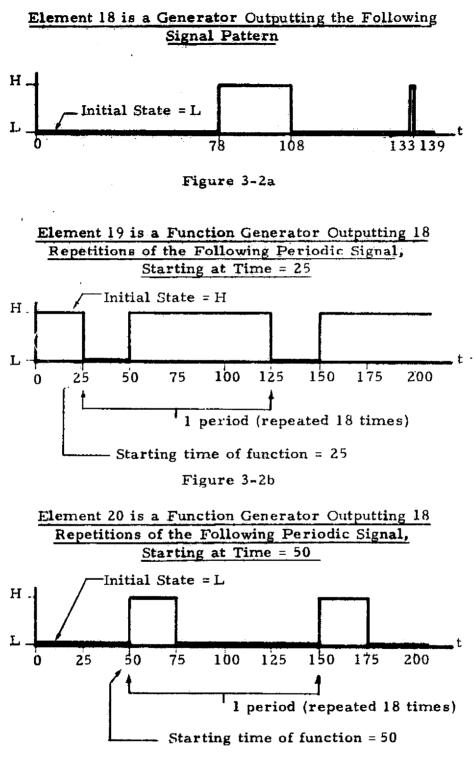

| 3-2        | Input Signals for the Sample MOS Logic Circuit                                                                        | 24     |

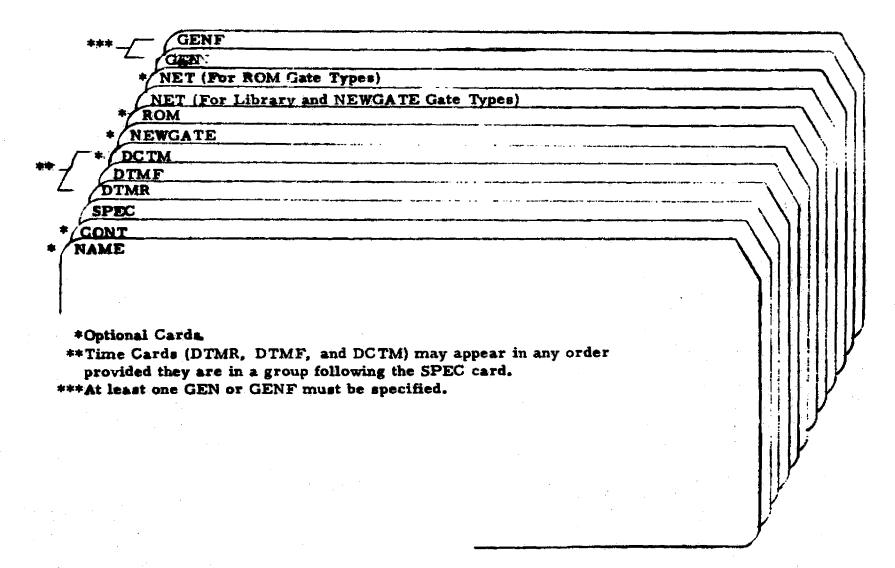

| <b>4-1</b> | LOGSIM Preprocessor Data Card Arrangement                                                                             | 29:    |

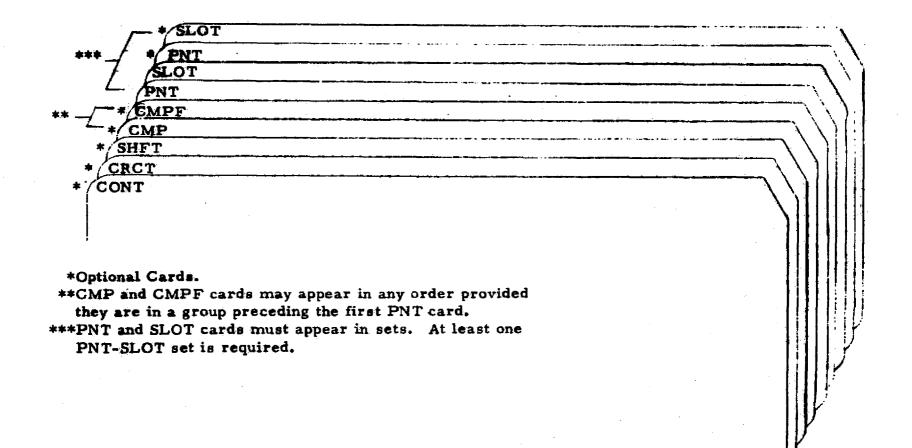

| 4-2        | LOGSIM Postprocessor Data Card Arrangement                                                                            | 30     |

| 4-3        | <b>Data Cards for Preprocessing of the Sample MOS</b><br>Logic Network                                                | 31     |

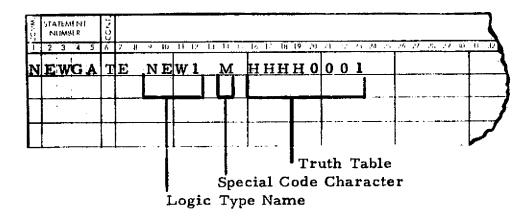

| 4-4        | <b>Examples</b> of NEWGATE and MULTICARD ROM<br>Specifications                                                        | 39, 44 |

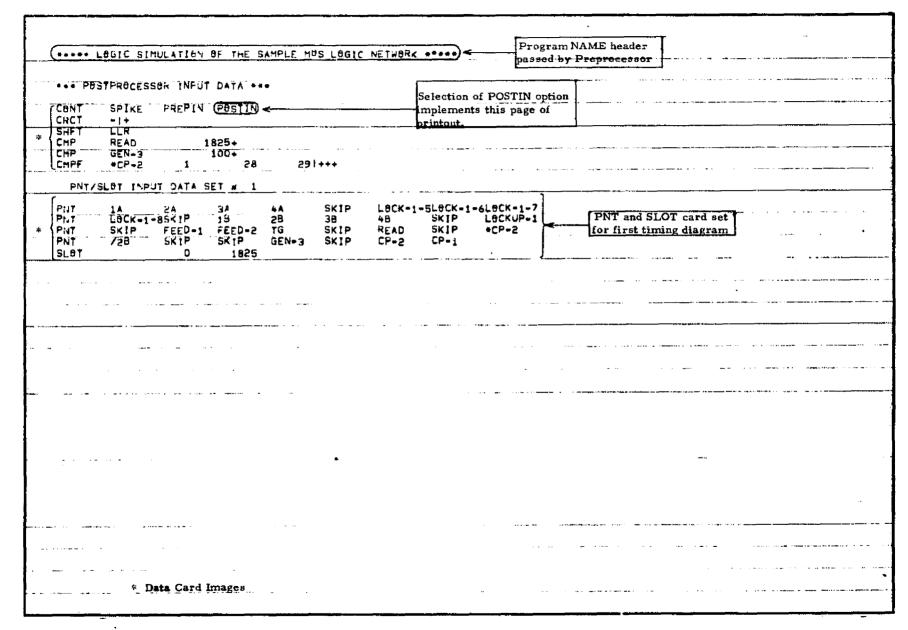

| 4-5        | Data Cards for Postprocessing of the Sample MOS<br>Logic Circuit                                                      | 55     |

| 5-1        | Preprocessor Printout: Input Data (Sample MOS<br>Logic Network)                                                       | 63     |

| 5-2        | Preprocessor Printout: NET Input Data (Sample<br>MOS Logic Network)                                                   | 64     |

| 5-3        | <b>Preprocessor Printout:</b> GEN and GENF Input Data (Sample MOS Logic Network)                                      | 65     |

| 5-4        | <b>Preprocessor Printout:</b> Input Data Diagnostics Page & Specifications List (Sample MOS Logic Network)            | 66     |

| 5-5        | Preprocessor Printout: Lists of Delay Gates &<br>Inverters Automatically Constructed (Sample of<br>MOS Logic Network) | 67     |

### LIST OF FIGURES (continued)

| No.  | Title                                                                                             | Page |

|------|---------------------------------------------------------------------------------------------------|------|

| 5-6  | Preprocessor Printout: Connectivity List (Sample<br>MOS Logic Network)                            | 68   |

| 5+7  | Postprocessor Printout: Input Data (Sample MOS<br>Logic Network)                                  | 70   |

| 5-8  | Postprocessor Printout: Preprocessing Input Data<br>(Sample MOS Logic Network)                    | 71   |

| 5-9  | Postprocessing Printout: Options List (Sample MOS<br>Logic Network)                               | 72   |

| 5-10 | Postprocessor Printout: Level Comparison & Com-<br>pare Functions List (Sample MOS Logic Network) | 73   |

| 5-11 | Postprocessor Printout: Print Matrix For First<br>Timing Diagram (Sample MOS Logic Network)       | 74   |

| 5-12 | Postprocessing Printout: First Page of First Timing<br>Diagram (Sample MOS Logic Network)         | 76   |

# LIST OF TABLES

| <u>No.</u> | <u>Title</u>                                                                                             | Page       |

|------------|----------------------------------------------------------------------------------------------------------|------------|

| 3-1        | Summary of Program Options                                                                               | 12,13      |

| 3-2        | LOGSIM Logic Element Type Library                                                                        | 14,15      |

| 3-3        | LOGSIM Library Logic Truth Tables                                                                        | 16,17      |

| 3-4        | NEWGATE Truth Table Output Definition                                                                    | 18         |

| 3-5        | Read-Only-Memory Cutput State Definitions                                                                | 20         |

| 3-6        | Truth Table for the Read-Only-Memory in the Sample MOS Logic Network                                     | 23         |

| 3-7        | Element Description List for the Sample MOS<br>Logic Network                                             | 25         |

| 3-8        | Delay and Decay Time Sets for the Sample MOS<br>Logic Network                                            | 27         |

| 4-1        | NEWGATE Special Code Character Interpretations                                                           | 36         |

| 4-2        | Majority Logic Interpretation                                                                            | 36         |

| 4-3        | "Any Low Sets" Interpretation                                                                            | 37         |

| 4-4        | "Any High Sets" Interpretation                                                                           | 37         |

| 4-5        | NEWGATE Truth Table Characters                                                                           | 38         |

| 4-6        | ROM Truth Table Characters                                                                               | 41         |

| 4-7        | Number of ROM Cards and Truth Table Entries<br>Required to Specify a Read-Only-Memory with "n"<br>Inputs | 42         |

| 4-8        | Characters Required for Level Specification on NET,<br>GEN, and GENF Cards                               | 47         |

|            |                                                                                                          | aget de la |

. . .

#### INTRODUCTION

The Logic Simulation Program (LOGSIM) was designed to serve an important role in computer aided design of electronic circuits, that is, to provide the designer with a means by which to verify the intended logic of a design prior to implementation of the circuit hardware.

A description of the logic network and its input signals is provided by the user as input data. LOGSIM verifies all input data and identifies any errors with diagnostic messages before proceeding with simulation. Simulation consists of switching the output levels of network elements in response to input level changes and recording all such events on magnetic tape. This tape is then processed according to user specifications to produce logic timing diagrams of any or all element outputs.

LOGSIM is capable of simulating very large logic networks within a modest amount of computer core memory. Although it has been written in Fortran IV to minimize machine dependency, its array dimensions are effectively adjusted during run-time to allow each simulation to make optimum use of the available memory. The program has an internal logic library of 15 logic element types to which the user may add new element types by simply defining their operation. In addition, the user may define complex logic functions as read-onlymemories (ROMs) with up to 15 inputs each.

LOGSIM is a three-valued logic simulator, in that the unknown (indeterminate) state can be represented and propagated as well as logic HIGH and logic LOW. This feature eliminates the necessity for network initialization and, in conjunction with other special provisions discussed in Section 2, permits simple and complete logic modeling of metal-oxide-semiconductor (MOS) circuitry.

- 1 -

1

### 2. LOGSIM PROGRAM OPERATIONS

# 2.1 LOGSIM Representation of Logic Delay and Decay Times

In order for logic circuitry to be simulated on an ideal binaryvalued basis, some relationship must be established between the ideal LOW and HIGH levels and the delayed level transition which occurs in reality. Due to physical constraints of a device, its levels cannot change instantaneously. Figure 2-1 illustrates the delays in switching from LOW to HIGH and HIGH to LOW. The LOGSIM approach is to establish the switching time as the time when the gate in reality has switched 90% of the change between levels. Hence, a gate is considered switched from LOW to HIGH after a rise delay time,  $t_r$ , which is the actual time necessary to switch 90% of the way from LOW to HIGH. The same applies for HIGH to LOW switching with a fall time delay,  $t_r$ .

The rise and fall delay times are supplied by the user for each circuit element. The user may specify up to 255 different rise delay times and up to 255 different fall delay times for one simulation. These times should be based on the characteristics of the devices which implement the logic. Varying the delay times for different simulations of a logic network will show the user the changes in the logical operation due to delay time variations.

In addition to its capabilities for modeling normal propagation delays, LOGSIM has special provisions for modeling the decay of stored charge on MOS logic circuits. Figure 2-2 illustrates a MOS transmission gate circuit for which such a model is very useful. The output node of the transmission gate is charged by the source when the gate input goes HIGH. This node is expected to hold the charge after the gate input returns to logic LOW. Since leakage resistance will slowly drain the charge, there is some fall decay time,  $t_{df}$ , after which the voltage at the output node will have fallen below the logic HIGH threshold level. The output must be considered indeterminate after this decay time has elapsed. The charge decay begins when the transmission gate is turned off by its gate input and the output switches into a charge holding mode.

Section 3.2 describes how the user may define the holding mode as one of the possible output states of MOS logic elements. Either a rise decay time or a fall decay time may be specified for any logic element having a holding mode (both may, in fact, be specified but such a model may not be meaningful).

-Ź.

REPRODUCIBILITY OF THE ORIGINAL PAGE IS PROFE

-3-

Figure 2-2 illustrates the LOGSIM interpretation of a fall decay time. The output responds to a LOW to HIGH input transition by switching from LOW to HIGH in some rise delay time  $t_r$ . However, when the input returns to LOW and the gate's output node is in a holding mode, the output voltage actually drifts slowly toward a LOW state. If a user specifies a fall decay time, the program will interpret it as being the time,  $t_{df}$ , in which the output drifts from the HIGH level to the logic HIGH threshold level. After that time LOGSIM assigns the output level an indeterminate state, and it remains at that state until another input pulse causes the output to change to a specific state. The user may choose to ignore the decay of the output, and may omit the decay time specification. The program then interprets the decay time as infinite and the output will hold its previous state indefinitely.

#### 2.2 Sequence of LOGSIM Operations

LOGSIM was designed in the form of three main programs. The three programs may be run together at one time, or may be run at different times, as long as the data to be transferred between programs is preserved. Figure 2-3 illustrates the general flow of execution of the three programs: the Preprocessor, the Simulator, and the Postprocessor.

#### 2.2.1 Preprocessing

During preprocessing the input data is read in the form of 72 column card images, where the first four characters of each record identify the record type. The input device may be changed at any point during the input of data. The Preprocessor Program validates the data and provides diagnostic messages whenever necessary. All of the data will be read and interpreted, regardless of errors, eliminating the need for repetitive runs to locate coding errors. The Preprocessor outputs the image of the data records under appropriate headers enabling the user to quickly determine how the data has been interpreted and if the logic has been specified correctly. As a user's option, the Preprocessor will also generate a connectivity list showing each gate and its loads.

After the data is read and validated, the Preprocessor outputs a parameter record, images of all of the input data records, and a list of all of the logic element names to a data tape to be used later by the Postprocessor. The Preprocessor then packs and converts the circuit data into a form compatible with the Simulator Program's input format. This data is saved on a binary disk file awaiting simulation.

REPRESENTATION OF THE ORIGINAL PAGE IS POOR

#### 2.2.2 Simulation

The Simulator accesses only the disk file created by the Preprocessor for its input data. The first record of this file specifies the desired simulation options and the organization of the data arrays describing the logic network. After these arrays have been stored in memory, the program proceeds by initializing logic element outputs. Initial levels of the input signal generators have been specified by the user along with any other element output levels which are known. The program first assigns initial output levels to the logic elements based on the initial generator levels. If some initial levels cannot be determined, program options determine whether simulation is to halt, or to proceed with some elements initially indeterminate. The initial levels which the user has specified are now compared with the level assignments established by the program. Another program option specifies whether inconsistent levels cause simulation to halt, or to continue using the user's initial levels. Upon completion of initialization of the outputs, the program writes the initial level of all logic elements to the data tape being generated for the Postprocessor.

The actual simulation begins by finding the first generator level changes and entering these new levels into an element status table. Each element loading one of the changed signals is then examined to determine if its output is affected. Appropriate delay times are added to the current time to find the times at which the future events are to be scheduled. When all loads have been examined, the current time is advanced to that of the next scheduled events, and the process repeats itself. As the new level of each scheduled event is entered in the element status table, it is also recorded on the events tape for the Postprocessor. Simulation continues until the current time has been advanced beyond the time limit set by the user.

In addition to recording logic events, the simulator detects possible spike conditions which may cause faulty logic operation. Figure 2-4 illustrates how this condition arises when the input of a logic element changes too rapidly for the output to follow. The simulator will always record a notice of the spike condition and maintain the element's output at its original level. The user may choose, at postprocessing, to have these notices printed with the timing diagram output.

#### 2.2.3 Postprocessing

The user specifies the format of the printed output with a small

-8-

URANAL A STUTION THE

set of data cards. Since the Postprocessor is completely independent of the preceding program segments, it may be run more than once to reprocess the events tape of a given simulation. Thus, the Preprocessor and Simulator need not be rerun to produce timing diagrams in a new format or of different logic elements.

Among the items specified by the Postprocess data cards, are the characters which the user prefers to have printed indicating HIGH, LOW, and indeterminate levels, and how each is to be shifted on the timing diagram. The user also chooses which element outputs are to be printed, in what order, with what spacing, and over what simulation time intervals.

The levels of any of the circuit elements can be compared to specified reference levels at any time. When the levels do not compare a message is printed, and the output continues unless the user has specified that it be terminated on a mismatch.

The Postprocessor reads the list of circuit element names and their initial conditions from the data tape, and prints a list of the signals to be output before starting a timing diagram. The timing diagram begins with the initial conditions of each element on the timing diagram or optionally a list of all initial conditions. Logic events are read from the data tape and the status of the selected elements is printed for each time within the specified time interval at which an event occurs. The timing diagram is thus compressed in that there is no printout for times at which logic is not changing states (except for the start and end times of each time slot, at which the status is always printed). After each timing diagram is complete, the program determines if another timing diagram is to be printed for another set of element outputs and time slots. If so, the data tape is rewound and the program generates another timing diagram according to the user's specifications. In this manner an unlimited number of timing diagrams can be printed by a single Postprocessor run.

-9-

3.

#### PREPARATION OF LOGSIM INPUT DATA

The LOGSIM program has been designed to minimize the user effort required for logic simulation, while retaining flexibility in handling new types of logic components. To minimize transcription errors and simplify interpretation of program inputs and outputs, each element of the user's logic network is identified by a unique alphanumeric name. This name also represents the primary output signal of that gate. The logic network is defined to the program by providing the following data for each component:

o component name

o component parameter specifications

o input signal names

The LOGSIM Preprocessor analyzes this data to identify errors such as duplicated or misspelled element names, missing input data, and inconsistent parameter specifications.

#### 3.1 Program Capabilities and Limitations

The user should be aware of several program limitations while constructing logic networks for simulation. Program capacity is limited by the amount of dimensioned memory, the exact number of elements simulated during one run being a function of the complexity of interconnections, the number of input signal specifications, and size of ROM truth tables. A capacity of 3000 to 5000 elements can normally be expected with the program's current dimensions. Larger networks must be divided into two or more sections for separate simulation. The only other inherent limitation restricts to 255, the number of rise time values, fall time values, rise decay time values, and fall decay time values.

The user should configure his logic so that all functions are performed by components which are either elements of the program's internal library or are specially defined as new gate types or ROMs. It should be noted that all LOGSIM components have a single output. The complement of this output, however, may be specified as an input to other elements by preceding the signal's name with a slash (/). LOGSIM will automatically generate this complement signal and distribute it where required, effectively providing the user with two

outputs from the component. Any other forms of multiple output components must be broken up before being defined to the program.

As indicated in Section 2, LOGSIM provides the user with a variety of program options. Table 3-1 provides a summary of these options.

#### 3.2 Component Type Definitions

The standard LOGSIM component library of 15 logic element types spans both bipolar and MOS technologies. These element types are completely described in Tables 3-2 and 3-3. All logic elements used in a simulation run must conform to one of the library types or to a type which is specially defined. Thus some logic functions may have to be synthesized by using logic types available in the LOGSIM library to provide an equivalent logic function. Any number of inputs may be specified for those logic types in Table 3-2 that do not require a fixed number of inputs. All inputs must be specified for logic types with a fixed number of inputs.

New gate (NEWGATE) types may be defined for a particular simulation run by the eight-character sequence,  $Q_1$  to  $Q_8$ , described in Table 3-4, where each Q may represent any of the output states defined. Only the states  $Q_1$  through  $Q_4$  are used to specify an unclocked element. States  $Q_1$  through  $Q_8$  define a clocked element, where  $Q_1$  through  $Q_4$  define the possible outputs when the clock is at a LOW state, and  $Q_5$  through  $Q_8$  define the outputs for a HIGH clock state. Specific logic types which may be defined are:

o Majority logic

o "Any LOW sets" logic

o "Any HIGH sets" logic

o Three input flip-flops

Five input flip-flops

0

These are defined in detail in Section 4.1.5. There is no limit to the number of inputs that a new gate type element may have, however, if it has been defined as clocked ( $Q_1$  through  $Q_8$  defined), the last input will be considered the clock.

# SUMMARY OF PROGRAM OPTIONS

# Options Available at Preprocessing

| OPTION | ON/OFF | RESULT                                                                                                  |

|--------|--------|---------------------------------------------------------------------------------------------------------|

| FROMTO | On     | A connectivity list is printed during pre-<br>processing.                                               |

|        | Off    | Connectivity list is not printed.                                                                       |

| IGNORE | On     | Simulation continues despite indeter-<br>minate initial levels.                                         |

|        | Off    | Simulation terminates if all initial levels cannot be established.                                      |

| NONCON | On     | Simulation accepts user specified initial levels if inconsistent with those established by the program. |

|        | Off    | Simulation terminates if there are any conflicting initial states                                       |

| FOLLOW | On     | Simulator tries to establish ROM output for any indeterminate inputs.                                   |

| 10110  | Off    | Simulator assigns ROM output level in-<br>determinate for any indeterminate inputs.                     |

| DEBUG  | On     | Debug data is printed during simulation.                                                                |

|        | Off    | No simulator debug data is printed.                                                                     |

Table 3-la

-12-

# SUMMARY OF PROGRAM OPTIONS (Continued)

# Options Available at Postprocessing

| OPTION  | ON/OFF | RESUL T                                                                  |

|---------|--------|--------------------------------------------------------------------------|

| PREPIN  | On     | Preprocessor input data is printed during postprocessing.                |

|         | Off    | Preprocessor input data is not printed during postprocessing.            |

| POSTIN  | On     | Postprocessor input data is printed.                                     |

|         | Off    | Postprocessor input data is not printed.                                 |

| SPIKE   | On     | Spike notices are printed.                                               |

|         | Off    | Spike notices are not printed.                                           |

| INITIAL | On     | All initial element levels are printed before first timing diagram.      |

|         | Off    | Timing diagram element initial levels are printed in each timing diagram |

| COMSTOP | On     | Output ceases and message is printed on first level comparison mismatch. |

|         | Off    | A message is printed for each level com-<br>parison mismatch.            |

Table 3-1b

-13-

# LOGSIM LOGIC ELEMENT TYPE LIBRARY

| LOGSIM<br>NAME | LOGIC TYPE                              | LOGIC DESCRIPTION                                                                                                                                                                                                                                                                                   |

|----------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OR             | OR                                      | Any input HIGH will yield a HIGH out-<br>put and all inputs LOW will yield a LOW<br>output.                                                                                                                                                                                                         |

| NOR            | NOR                                     | Any input HIGH will yield a LOW out-<br>put and all inputs LOW will yield a<br>HIGH output.                                                                                                                                                                                                         |

| AND            | AND                                     | Any input LOW will yield a LOW out-<br>put and all inputs HIGH will yield a<br>HIGH output.                                                                                                                                                                                                         |

| NAND           | NAND                                    | Any input LOW will yield a HIGI (out-<br>put and all inputs HIGH will yield a<br>LOW output.                                                                                                                                                                                                        |

| MOR            | MOS NOR                                 | Gate with a clocked load device. The last input listed is treated as the clock.                                                                                                                                                                                                                     |

| MORT           | MOS NOR<br>with trans-<br>mission gate  | Gate with a clocked load device and<br>clocked internal transmission gate.<br>The last input listed is treated as the<br>clock.                                                                                                                                                                     |

| MAND           | MOS NAND                                | Gate with a clocked load device. The<br>last input listed is treated as the clock.                                                                                                                                                                                                                  |

| MANT           | MOS NAND<br>with trans-<br>mission gate | Gate with a clocked load device and<br>clocked internal transmission gate. The<br>last input listed is treated as the clock.                                                                                                                                                                        |

| CFF            | Clocked flip-<br>flop                   | Clocked, three-input, set-reset flip-flop<br>The third input is treated as the clock,<br>and the flip-flop is enabled during a neg-<br>ative clock. The first input is assumed<br>to be the set input with the second input<br>assumed to be the reset line. All three<br>inputs must be specified. |

### Table 3-2

-14

REPRODUCIBILITY OF THE ORIGINAL PAGE IS POOR

# LOGSIM LOGIC ELEMENT TYPE LIBRARY (continued)

| LOGSIM<br>NAMELOGIC TYPELOGIC DESCRIPTIONEXOREXCLUSIVE<br>ORTwo-input gate in which either input<br>HIGH will yield a HIGH output. Both<br>inputs LOW or HIGH will yield a LOW<br>output.SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these<br>lines take effect in zero time. |                                                                                                                |              |                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------|

| ORHIGH will yield a HIGH output. Both<br>inputs LOW or HIGH will yield a LOW<br>output.SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input friggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the flifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                 | 11 A.                                                                      | LOGIC TYPE   | LOGIC DESCRIPTION                           |

| SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | EXOR                                                                                                           | EXCLUSIVE    | Two-input gate in which either input        |

| SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                           |                                                                                                                | OR           |                                             |

| SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |              |                                             |

| SRFFSet-reset<br>flip-flopTwo-input flip-flop. The first input<br>is assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                |              |                                             |

| flip-flopis assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |              |                                             |

| flip-flopis assumed to be the set input and the<br>second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SRFF                                                                                                           | Set-reset    | Two-input flip-flop. The first input        |

| Second input is assumed to be the<br>reset input. When both inputs are<br>HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                           | · · · · ·                                                                                                      | flip-flop    |                                             |

| JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |              |                                             |

| HIGH, the output is undefined.JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                              |              | -                                           |

| JKFFJ-K flip-<br>flopTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |              |                                             |

| flopbut when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |              | intering the output is inactined.           |

| flopbut when both inputs are HIGH, the<br>output changes state. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JKFF                                                                                                           | J-K flip-    | Two-input flip-flop similar to SRFF.        |

| MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                |              |                                             |

| MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SR FF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\sigma_{\rm eff} = 10^{11} {\rm eff} + 10^{11} {\rm eff}$                                                     |              |                                             |

| MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock.CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |              |                                             |

| MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |              |                                             |

| MCLKMOS trans-<br>mission gateTwo-input flip-flop similar to SRFF,<br>but when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |              |                                             |

| mission gatebut when both inputs are HIGH, the<br>output changes stage. The first input<br>is assumed to be the J input and the<br>second input is assumed to be the K<br>input.TJKFTriggerable<br>J-K flip-flopThree-input triggerable J-K flip-flop<br>similar to CFF. The third input is<br>assumed to be the clock input, and<br>the flip-flop is enabled on a positive-<br>to-negative transition of the clock,CJKFClocked J-K<br>flip-flopFive input J-K flip-flop similar to<br>TJKF with direct set and reset lines.<br>The third input is assumed to be the<br>set, the fourth, the reset; and the fifth,<br>the clock. Enabling signals on these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |              | nibar.                                      |