|                                                     |                                                                   | CR-151984       |

|-----------------------------------------------------|-------------------------------------------------------------------|-----------------|

| (NASA-CR-151984)<br>Defense and Space<br>A07/MF A01 | HYBRID RECEIVER STUDY (TRW<br>Systems Group) 130 p HC<br>CSCL 17B | N77-24342       |

|                                                     | G3/32                                                             | Unclas<br>34169 |

## HYBRID RECEIVER STUDY

By

Marvin S. Stone Peter L. McAdam Oliver W. Saunders

April 1977

Distribution of this report is provided in the interests of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

Prepared under Contract No. NAS2-9367 by

TRW DEFENSE AND SPACE SYSTEMS Redondo Beach, California

for

AMES RESEARCH CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# **HYBRID RECEIVER STUDY**

By

Marvin S. Stone Peter L. McAdam Oliver W. Saunders

April 1977

Distribution of this report is provided in the interests of information exchange. Responsibility for the contents resides in the author or organization that prepared it.

Prepared under Contract No. NAS2-9367 by

TRW DEFENSE AND SPACE SYSTEMS Redondo Beach, California

for

AMES RESEARCH CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

#### ABSTRACT

This final report presents the results of a 4 month study to design a hybrid analog/digital receiver for outer planet mission probe communication links. The scope of this study includes functional design of the receiver; comparisons between analog and digital processing; hardware tradeoffs for key components including frequency generators, A/D converters, and digital processors; development and simulation of the processing algorithms for acquisition, tracking, and demodulation; and detailed design of the receiver in order to determine its size, weight, power, reliability, and radiation hardness. In addition, an evaluation was made of the receiver's capabilities to perform accurate measurement of signal strength and frequency for radio science missions. CONTENTS

|    |      |                                                           | Page   |

|----|------|-----------------------------------------------------------|--------|

| 1. | INTR | RODUCTION                                                 | 1-1    |

|    | 1.1  | Receiver Performance                                      | 1-1    |

|    | 1.2  | Receiver Characteristics                                  | 1-4    |

|    | 1.3  | Receiver Description                                      | 1-6    |

|    | 1.4  | Receiver Operation                                        | 1-12   |

| 2. | RECE | IVER DESCRIPTION                                          | 2-1    |

|    | 2.1  | Analog Processor                                          | 2-1    |

|    |      | 2.1.1 RF/IF Subsystem                                     | 2-1    |

|    |      | 2.1.2 Numerically Controlled Oscillator                   | 2-4    |

|    | 2.2  | A/D and Sample and Hold                                   | 2-8    |

|    |      | 2.2.1 I/Q Downconversion by IF Sampling                   | 2-10   |

|    |      | 2.2.2 A/D Loading and Dynamic Range                       | 2-13   |

|    |      | 2.2.3 Sample and Hold Circuit                             | 2-17   |

|    | 2.3  | Digital Processor Description                             | 2-18   |

|    |      | 2.3.1 Digital Signal Processor Characteristics            | 2-18   |

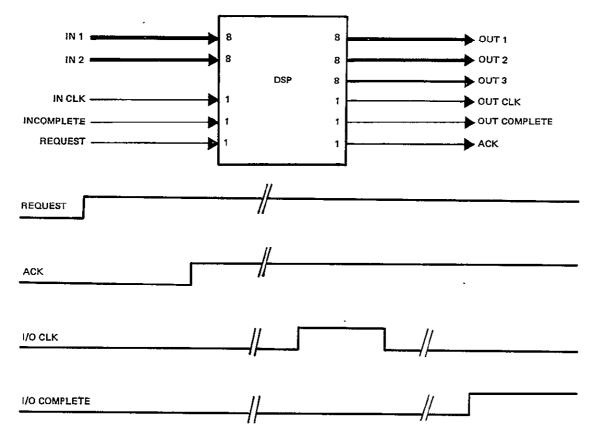

|    |      | 2.3.2 I/O Interfaces                                      | 2-25   |

|    |      | 2.3.3 Processing Capabilities                             | 2-27   |

|    |      | 2.3.4 Algorithm Development Procedure                     | 2-36   |

| 3. | SYST | EM ANALYSIS AND ALGORITHM DESIGN                          | 3-1    |

|    | 3.1  | Coarse Frequency Acquisition                              | 3-1    |

|    |      | 3.1.1 Acquisition Performance Objectives                  | 3-1    |

|    |      | 3.1.2 Sequential Detection Algorithm Description          | 3-2    |

|    |      | 3.1.3 Sequential Detection Algorithm Performance Analysis | 3-5    |

|    | 3.2  | Tracking Algorithms for DPSK and FSK                      | 3-20   |

|    |      | 3.2.1 Coarse Frequency Tracking Algorithms                | 3-20   |

|    |      | 3.2.2 Coarse Bit Timing Algorithms                        | 3-26   |

|    | 3.3  | Demodulation Algorithms                                   | 3-31   |

|    |      | 3.3.1 DPSK Demodulation and Decision Directed Tracking    | · 3-31 |

|    |      | 3.3.2 FSK Demodulation and Decision Directed Tracking     | 3-35   |

|    | 3.4  | Simulation Results for DPSK and FSK Demodulation          | 3-38   |

| 4. | RECE | IVER CHARACTERISTICS                                      | 4-1    |

|    | 4.1  | Mechanical Layout                                         | 4-1    |

|    | 4.2  | Reliability                                               | 4-1    |

|    | 4.3  | Interfaces                                                | 4-8    |

|    | 4.4  | Component Selection                                       | 4-10   |

|    |      | 4.4.1 Digital LSI/MSI                                     | 4-10   |

۷

## CONTENTS (Continued)

|      |        |         |                                            | Page | š |

|------|--------|---------|--------------------------------------------|------|---|

|      |        | 4.4.2   | A/D and D/A Converters                     | 4-13 | 3 |

|      |        | 4.4.3   | Active RF Components                       | 4-14 | ł |

|      |        | 4.4.4   | Operational Amplifiers and Analog Switches | 4-14 | ł |

| 5.   | RADIO  | SCIENCE | MISSION                                    | 5-1  |   |

|      | 5.1    | Signal  | Power Measurement                          | 5-1  |   |

|      | 5.2    | Frequen | cy Measurement                             | 5-5  |   |

| APPE | NDIX A | . COMP  | ONENTS SURVEY                              | A-1  | • |

### ILLUSTRATIONS

| re_                                                                       | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

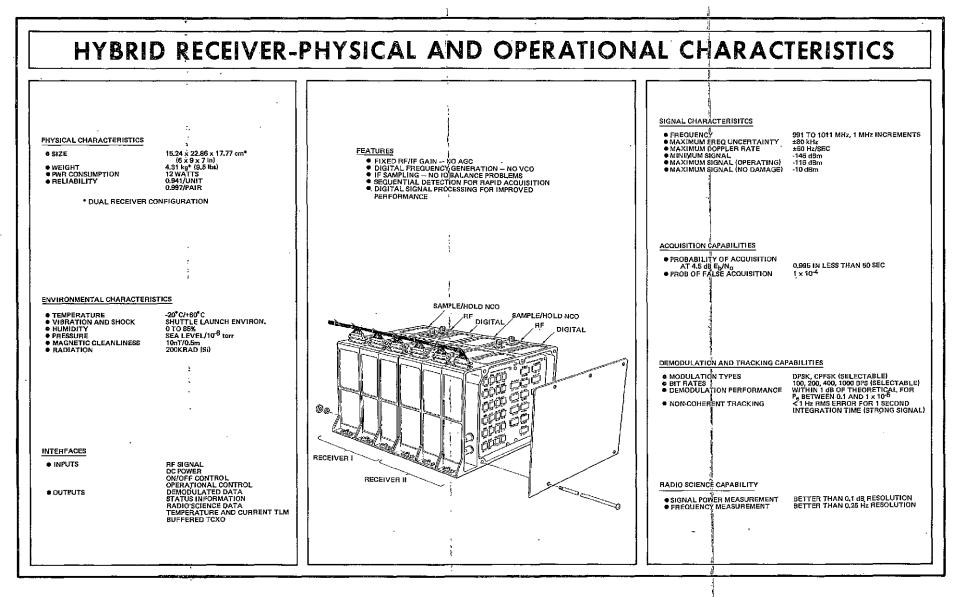

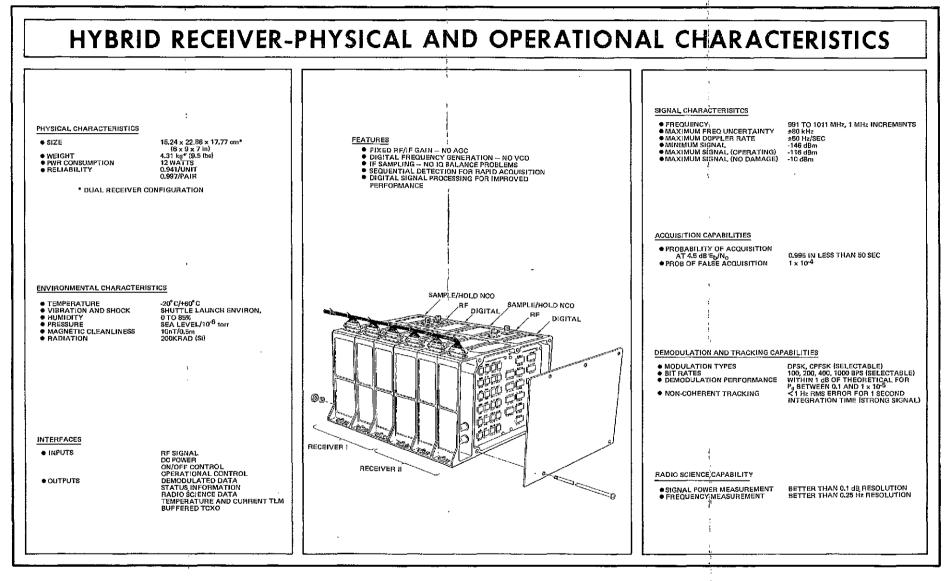

| Hybrid Receiver Physical and Operational Characteristics                  | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hybrid Receiver Functional Diagram                                        | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Digital Signal Processor Functional Diagram                               | 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Coarse Frequency Acquisition                                              | 1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Coarse Frequency Tracking and Coarse Bit Timing                           | 1-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

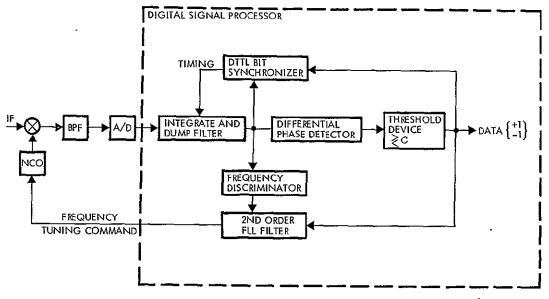

| Demodulation of DPSK Data                                                 | 1-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

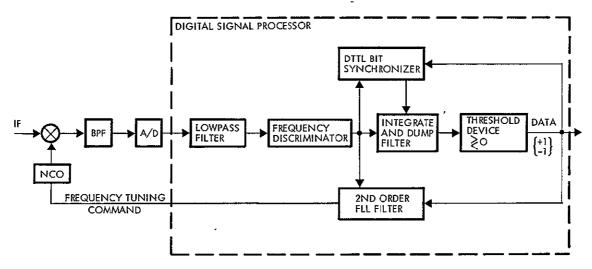

| Demodulation of CPFSK Data                                                | 1-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Hybrid Receiver Simplified Block Diagram                                  | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

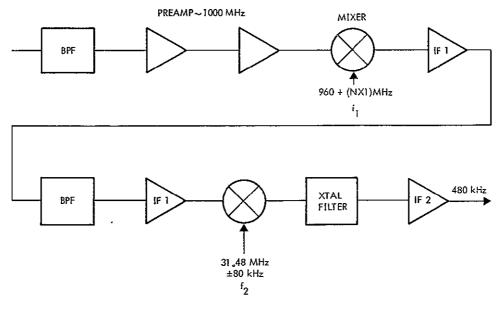

| Hybrid Receiver Front End                                                 | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Noise Figure Calculation                                                  | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

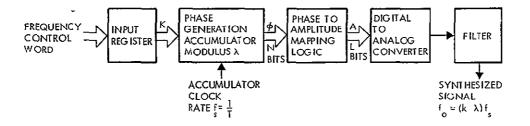

| Digital Phase Accumulation                                                | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NCO Design                                                                | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NCO Waveforms                                                             | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

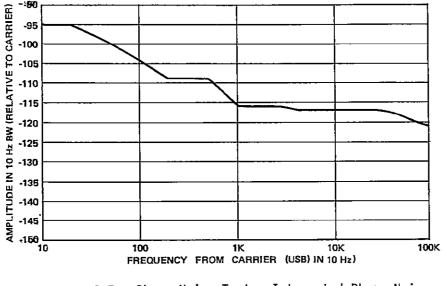

| Phase Noise Test. Integrated Phase Noise: -67 dB (0.03° RMS Phase Jitter) | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RF/A-to-D Interface                                                       | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

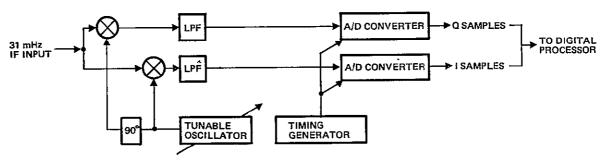

| RF/A-to-D Interface Functional Equivalent                                 | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

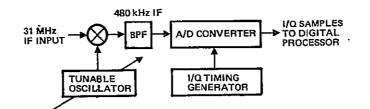

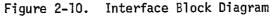

| ) Interface Block Diagram                                                 | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

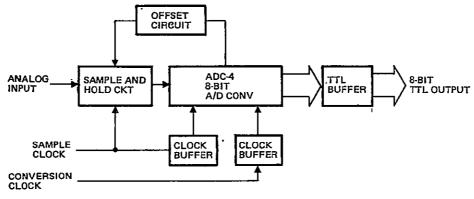

| A/D and Support Circuitry                                                 | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

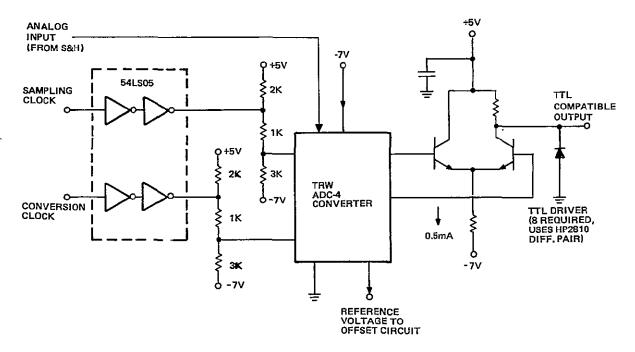

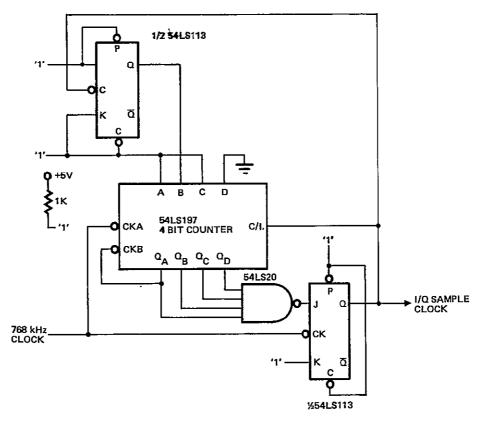

| I/Q Sampling Generation                                                   | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

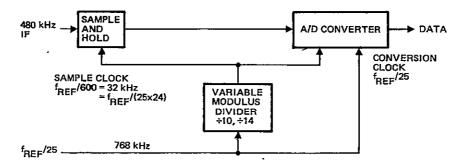

| B Hybrid Receiver I/Q Sampling Scheme                                     | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Variable Modulus Divider                                                  | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

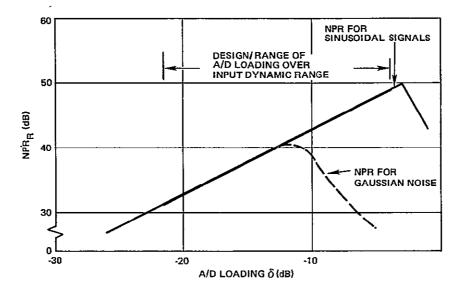

| A/D Loading and NPR Performance                                           | 2-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

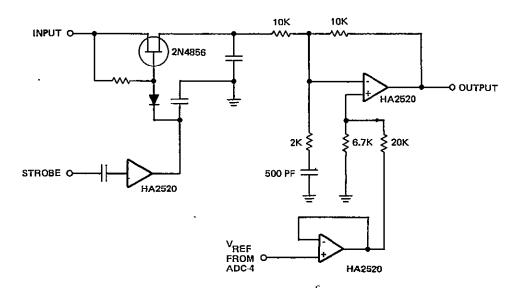

| Sample and Hold Circuit                                                   | 2-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

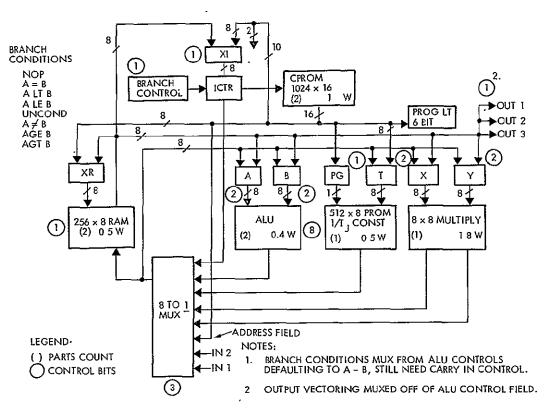

| ' Digital Signal Processor (DSP) Block Diagram                            | 2 <b>-</b> 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

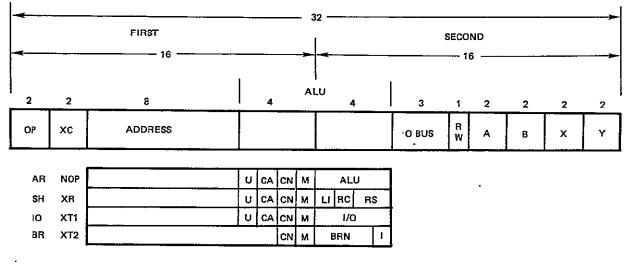

| 3 Control ROM Format                                                      | 2-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

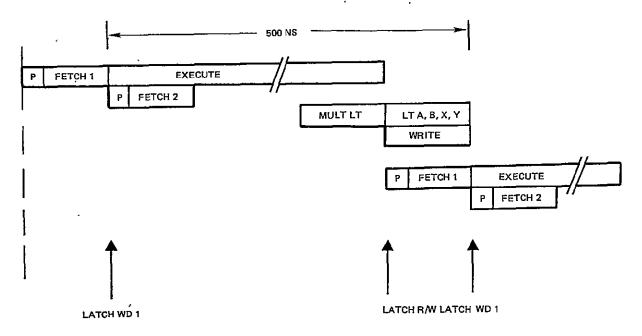

| DSP Fetch Sequence                                                        | 2-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ) Hybrid Receiver Interface                                               | 2-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

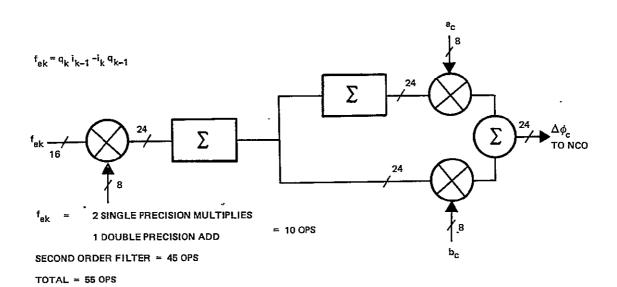

| Basic Second Order Filter                                                 | 2-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

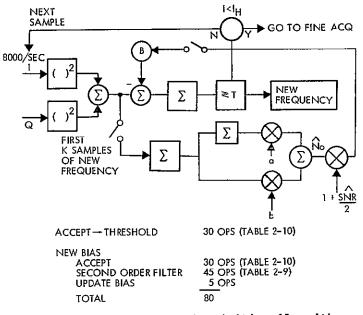

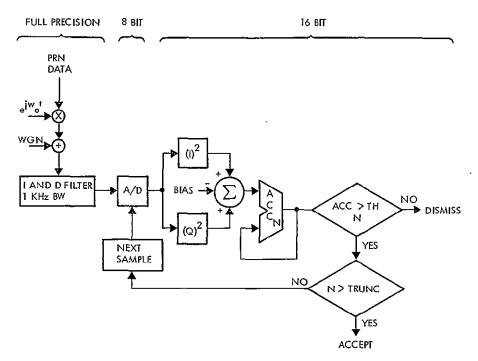

| Coarse Acquisition Algorithm                                              | 2-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Frequency Lock Loop Filter                                                | 2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

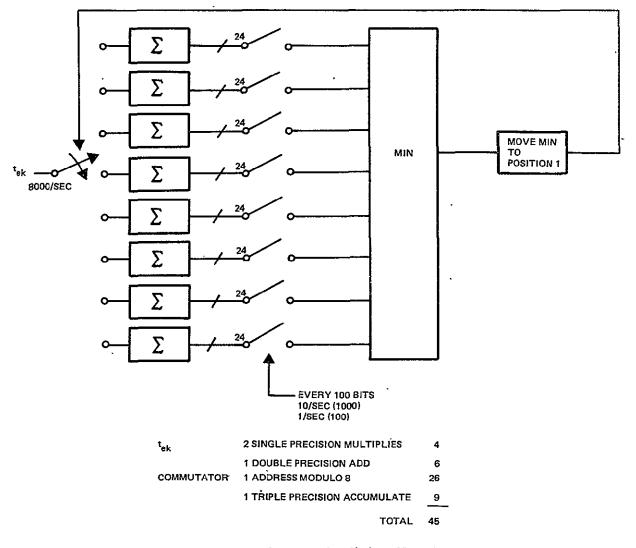

| Coarse Bit Timing Algorithm                                               | 2-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

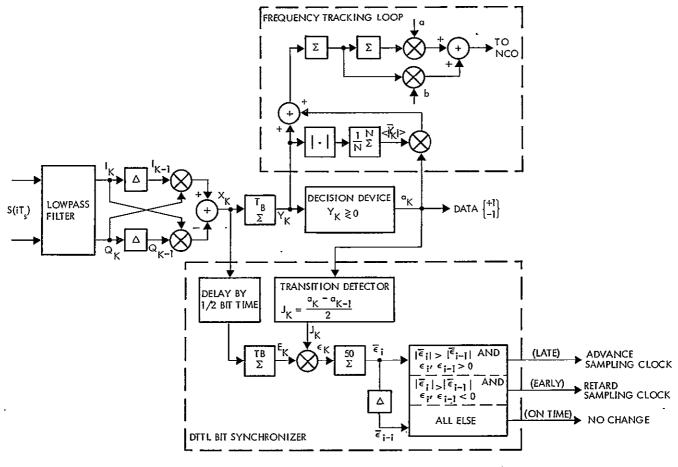

| 5 Frequency Tracking Loop                                                 | 2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5 Fine Bit Timing                                                         | 2-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

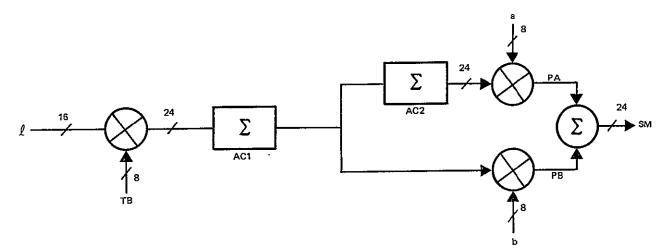

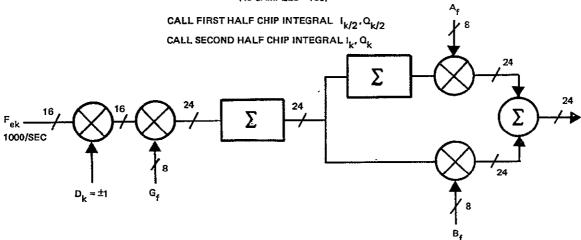

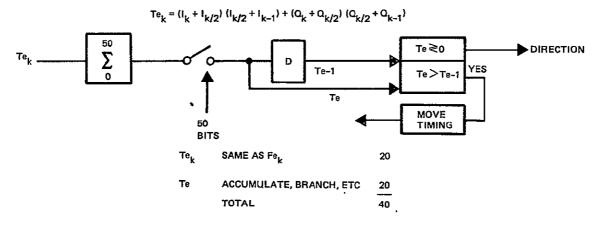

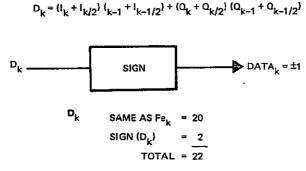

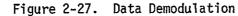

| Data Demodulation                                                         | 2-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

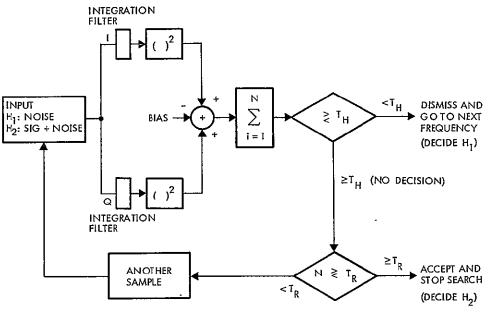

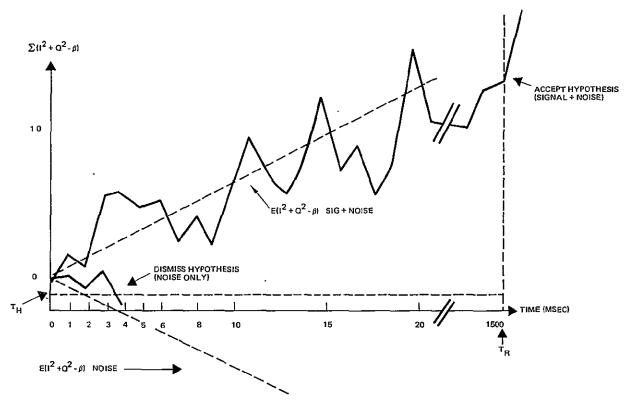

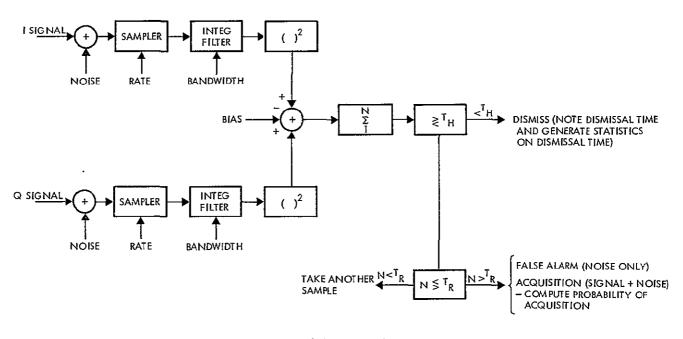

| Sequential Detection Algorithms                                           | 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Sequential Detection Example                                              | 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

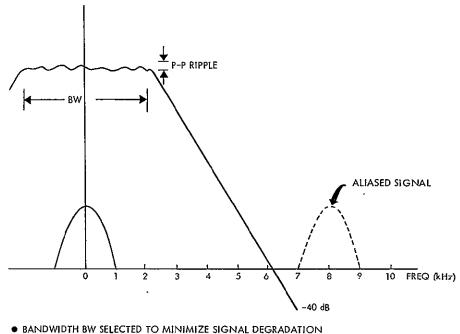

| IF Filtering Considerations                                               | 3-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                           | Hybrid Receiver Physical and Operational CharacteristicsHybrid Receiver Functional DiagramDigital Signal Processor Functional DiagramCoarse Frequency AcquisitionCoarse Frequency Tracking and Coarse Bit TimingDemodulation of DPSK DataDemodulation of CPFSK DataHybrid Receiver Simplified Block DiagramHybrid Receiver Front EndNotse Figure CalculationDigital Phase AccumulationNCO DesignNCO WaveformsPhase Noise Test. Integrated Phase Noise: -67 dB (0.03° RMSPhase Jitter)RF/A-to-D InterfaceRF/A-to-D Interface Functional EquivalentInterface Block DiagramA/D and Support CircuitryI/Q Sampling GenerationHybrid Receiver I/Q Sampling SchemeVariable Modulus DividerA/D Loading and NPR PerformanceSample and Hold CircuitDSP Fetch SequenceHybrid Receiver InterfaceBasic Second Order FilterCoarse Acquisition AlgorithmFrequency Lock Loop FilterCoarse Bit TimingData DemodulationSequential Detection AlgorithmsSequential Detection Algorithms |

## ILLUSTRATIONS (Continued)

| Figure |                                                                                            | Page   |

|--------|--------------------------------------------------------------------------------------------|--------|

| 3-4    | Finite Word Size Simulation                                                                | 3-8    |

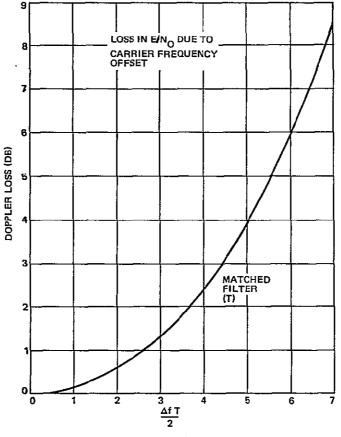

| 3-5    | Loss in E/N' Due to Carrier Frequency Offset                                               | 3-9    |

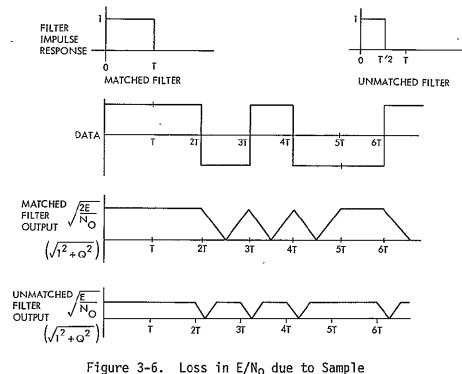

| 3-6    | Loss in E/N Due to Sample Time Offset                                                      | 3-10   |

| 3-7    | Sequential Detection Algorithm Simulation Block Diagram                                    | 3-11   |

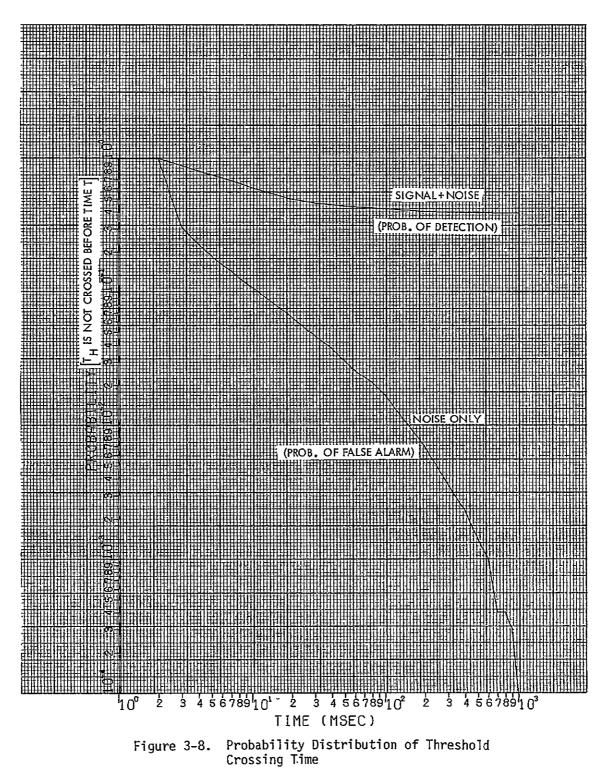

| 3-8    | Probability Distribution of Threshold Crossing Time                                        | 3-13   |

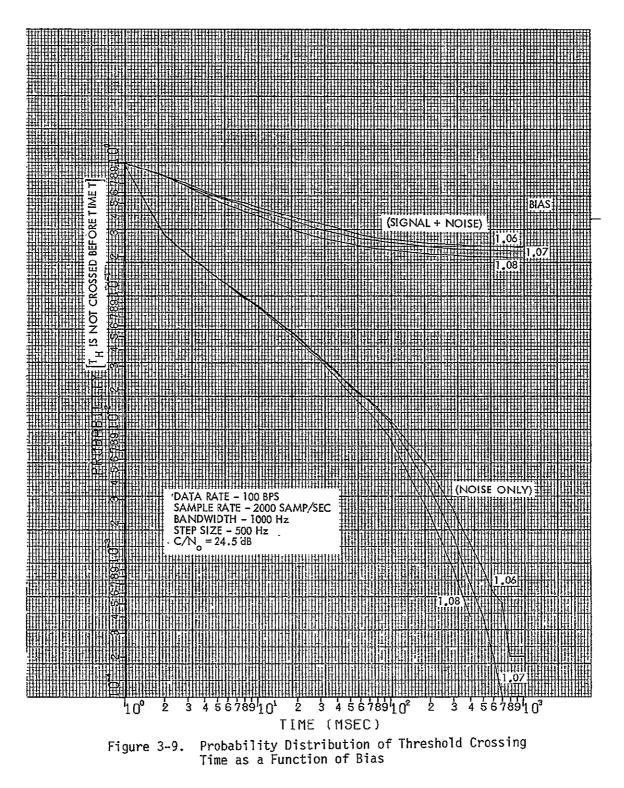

| 3-9    | Probability Distribution of Threshold Crossing Time as a Function of Bias                  | 3-16   |

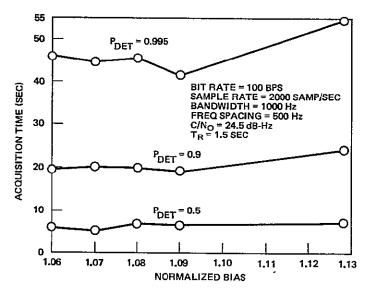

| 3-10   | Acquisition Time vs Bias                                                                   | 3-17   |

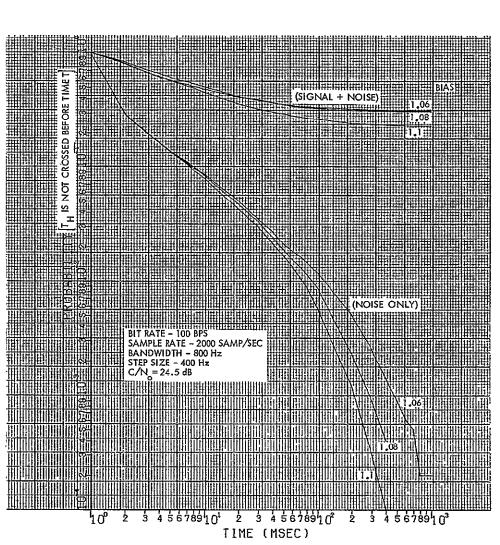

| 3-11   | Probability Distribution of Threshold Crossing Time for Integration<br>Bandwidth of 800 Hz | 3-18   |

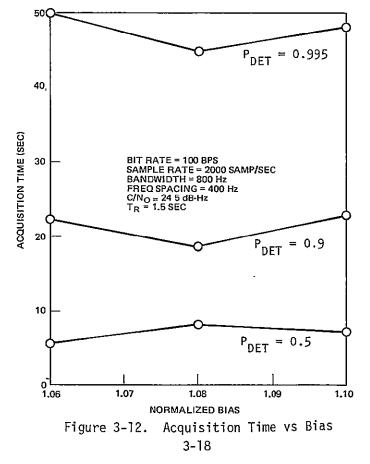

| 3-12   | Acquisition Time vs Bias                                                                   | 3-18   |

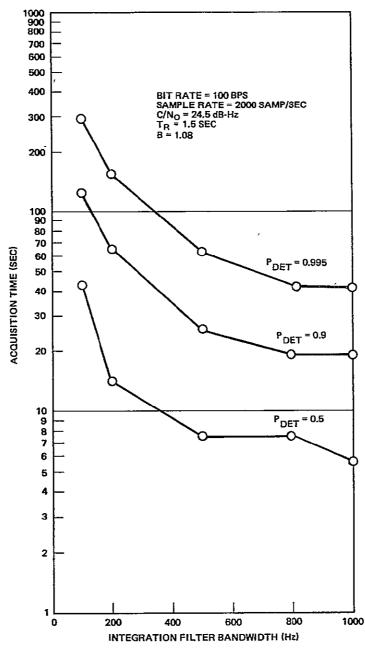

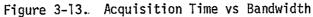

| 3-13   | Acquisition Time vs Bandwidth                                                              | 3-19   |

| 3-14   | Probability of Detection vs Time                                                           | 3-21   |

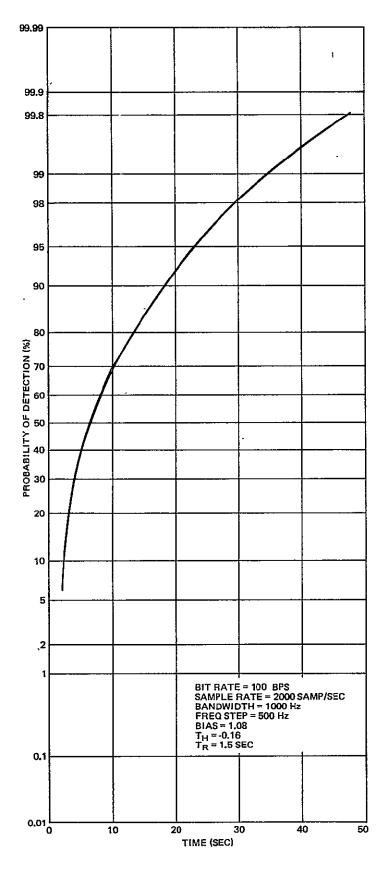

| 3-15   | Sin(X) and Tan <sup><math>-1</math></sup> Discriminator Characteristics with Data Wipeoff  | 3-22   |

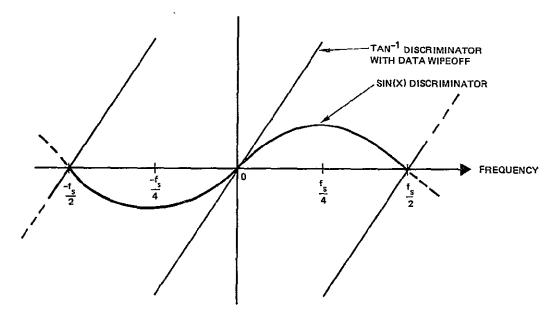

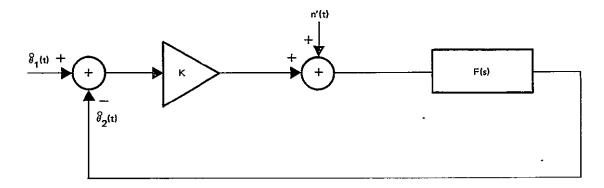

| 3-16   | Frequency Tracking Loop Analytical Model                                                   | 3-24   |

| 3-17   | Frequency Tracking Equivalent Loop Model                                                   | 3-25   |

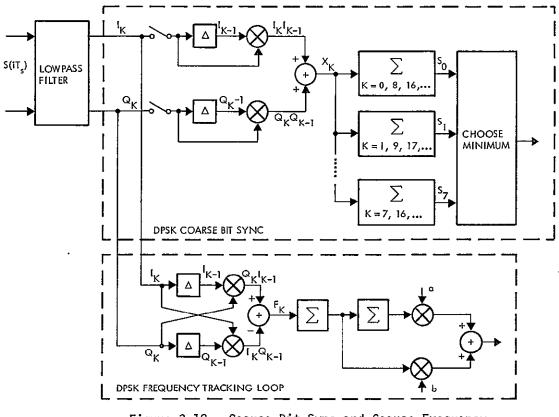

| 3-18   | Coarse Bit Sync and Coarse Frequency Tracking for DPSK Data                                | 3-25   |

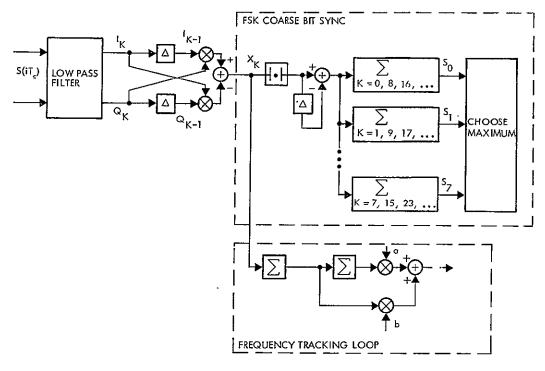

| 3-19   | Coarse Bit Sync and Coarse Fréquency Tracking for FSK Data                                 | 3-27   |

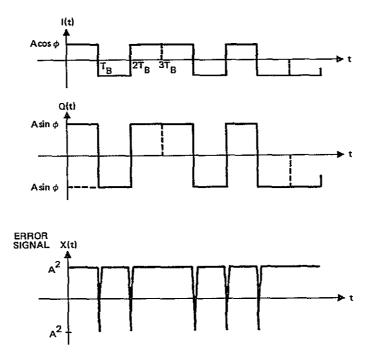

| 3-20   | Coarse Bit Timing Example for DPSK Data                                                    | 3-28   |

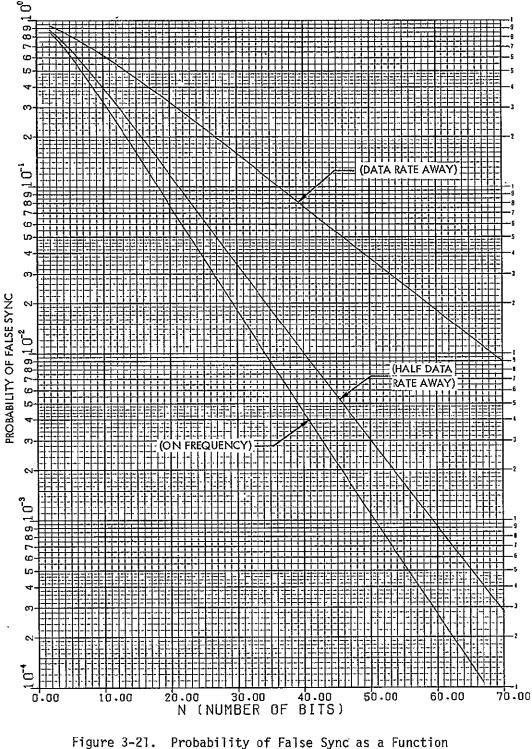

| 3-21   | Probability of False Sync as a Function of Carrier Frequency Offset                        | 3-30   |

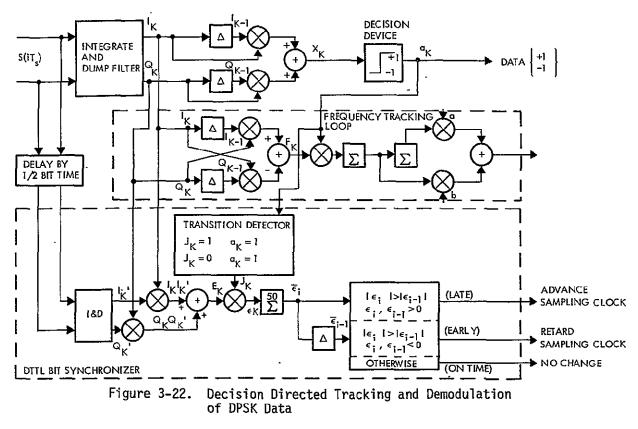

| 3-22   | Decision Directed Tracking and Demodulation of DPSK Data                                   | 3-32   |

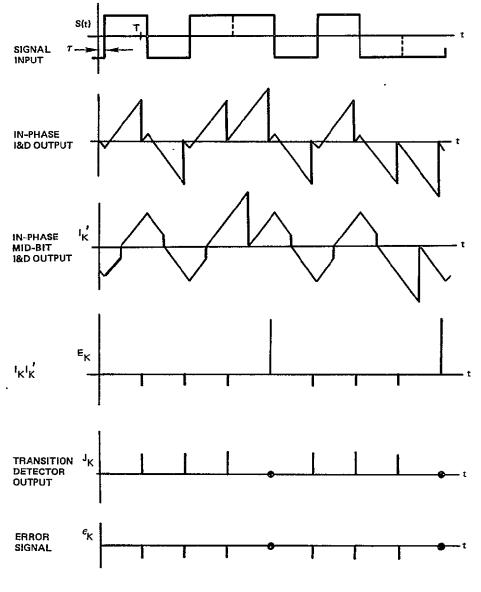

| 3-23   | DTTL Bit Synchronization for DPSK Data. Early by $	au$ Seconds — Data in I-Channel         | 3-34   |

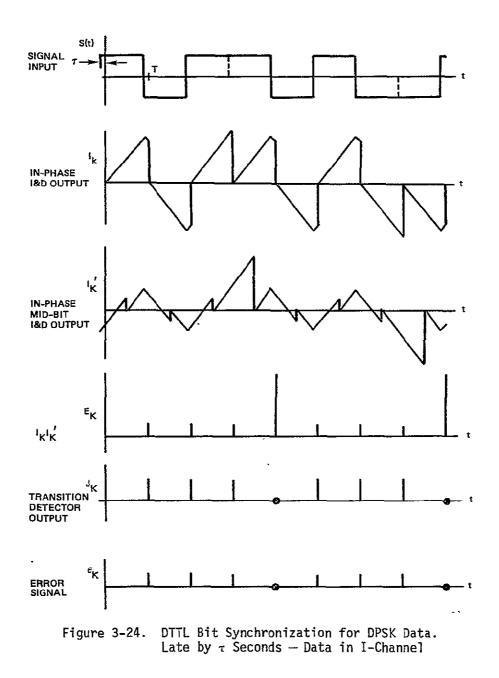

| 3-24   | DTTL Bit Synchronization for DPSK Data. Late by $	au$ Seconds — Data in I-Channel          | 3-35   |

| 3-25   | Decision Directed Tracking and Demodulation of FSK Data                                    | 3-36   |

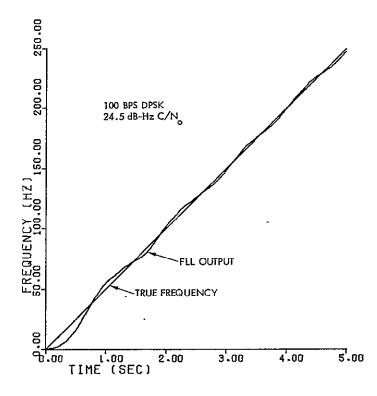

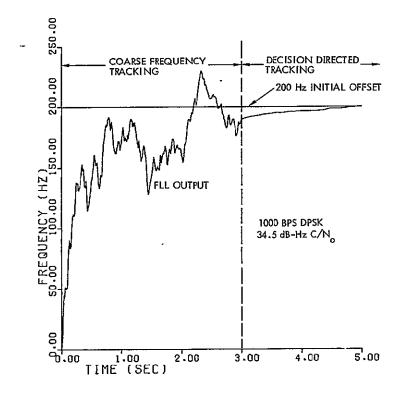

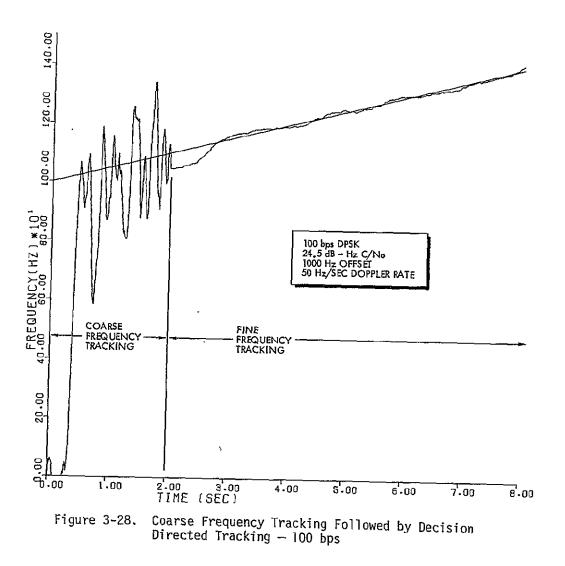

| 3-26   | Decision Directed Frequency Tracking                                                       | 3-39   |

| 3-27   | Coarse Frequency Tracking Followed by Decision Directed Tracking — 1000 bps                | 3-39   |

| 3-28   | Coarse Frequency Tracking Followed by Decision Directed Tracking —.<br>100 bps             | · 3-40 |

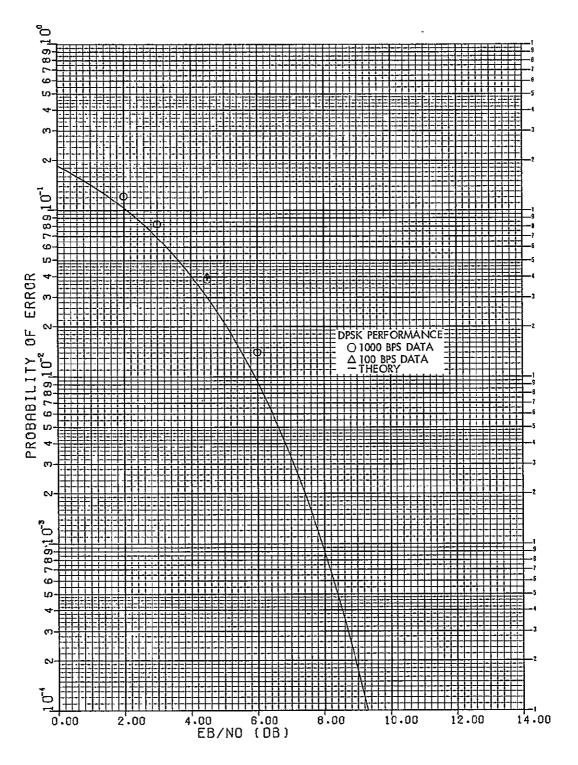

| 3-29   | DPSK Bit Error Probability Performance                                                     | 3-41   |

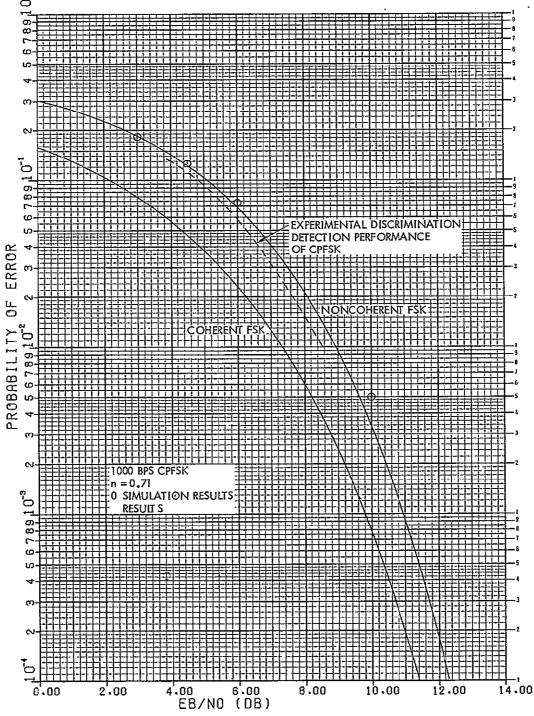

| 3-30   | Performance of Discriminator Detection of CPFSK                                            | 3-43   |

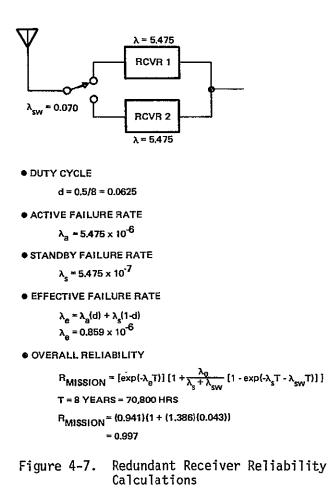

| 4-1    | Hybrid Receiver Physical and Operational Characteristics                                   | 4-2    |

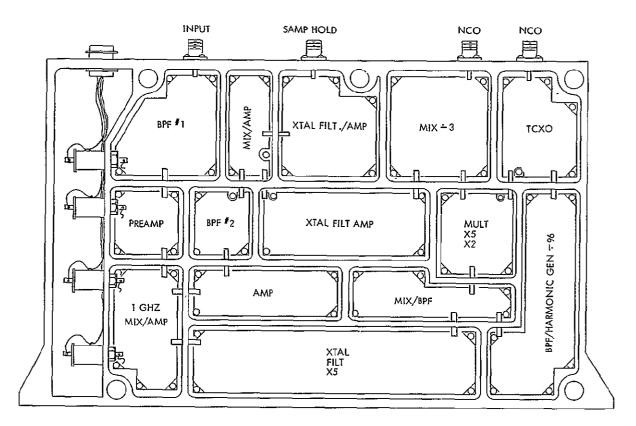

| 4-2    | RF/IF Slice                                                                                | 4-3    |

| 4-3    | RF Section                                                                                 | 4-4    |

| 4-4    | Frequency Generator                                                                        | 4-4    |

| 4-5    | Digital System                                                                             | 4-5    |

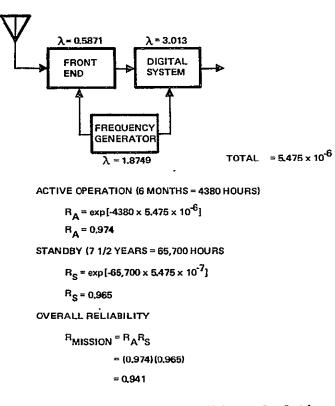

| 4-6    | Receiver Reliability Calculations                                                          | 4-7    |

| 4-7    | Redundant Receiver Reliability Calculations                                                | 4-7    |

-

TABLES

| Table            |                                                                                  | <u>Page</u> |

|------------------|----------------------------------------------------------------------------------|-------------|

| 1-1              | Hybrid Receiver Performance                                                      | 1-2         |

| 1-2              | Radio Science Performance                                                        | 1-3         |

| 1-3              | Processor Utilization                                                            | 1-11        |

| 1-4              | Hybrid Receiver Component Derivation                                             | 1-11        |

| 1-5              | Acquisition and Tracking Performance                                             | 1-15        |

| 2-1              | RF/IF Subsystem Features                                                         | 2-1         |

| 2-2              | Receiver RF Component Derivation                                                 | 2-5         |

| 2-3              | Bias Current Estimation                                                          | 2-6         |

| <b>2-4</b>       | Dynamic Range Calculations                                                       | 2-16        |

| 2-5              | DSP Microprocessor Summary                                                       | 2-20        |

| 2-6              | Storage Element Mnemonics                                                        | 2-23        |

| 2-7              | Basic Instruction Set                                                            | 2-23        |

| 2-8              | Input/Output Ports                                                               | 2-25        |

| 2-9              | Second Order Filter Program                                                      | 2-29        |

| 2-10             | Coarse Acquisition Program                                                       | 2-31        |

| 2-11             | Summary of Processor Speed Loading                                               | 2-33        |

| 2-12             | Program Memory Usage Estimate                                                    | 2-35        |

| 3-1              | Frequency Acquisition Performance Parameters                                     | 3-2         |

| 3-2              | Frequency Acquisition Loss Budget                                                | 3-6         |

| 3-3              | IF Filtering Losses                                                              | 3-8         |

| 3-4              | Summary of Frequency Tracking Simulation                                         | 3-40        |

| 3-5              | 1000 bps DPSK 50 Hz/sec Doppler                                                  | 3-42        |

| 3-6              | 100 bps DPSK 50 Hz/sec Doppler                                                   | 3-42        |

| 3-7              | 1000 bps FSK 50 Hz/sec Doppler                                                   | 3-43        |

| 4-1              | A RF Section Failure Rate Summary                                                | 4-5         |

| 4-2              | Frequency Generator Failure Rate Summary                                         | 4-5         |

| 4-3              | Digital System Failure Rate Summary                                              | 4-6         |

| 4-4              | Hybrid Receiver Interfaces                                                       | 4-8         |

| 4-5              | Operational Control Commands                                                     | 4-9         |

| 4-6              | Active Parts List                                                                | 4-11        |

| 5-1              | Radio Science Performance                                                        | 5-2         |

| 5-2              | Gain Errors                                                                      | 5-3         |

| 5-3              | Signal Power Measurement Error                                                   | 5-4         |

| 5-4              | Frequency Measurement Error Sources                                              | 5-6         |

| <sup>`</sup> 5≁5 | Frequency Measurement Error                                                      | 5-8         |

| 5-6              | Frequency Measurement Error                                                      | 5-10        |

| 5-7              | Effects of Ultra Stable Oscillator Frequency on Internal<br>Receiver Frequencies | 5-11        |

×

#### 1. INTRODUCTION AND SUMMARY

This final report describes the work performed on NASA/Ames Contract No. NAS2-9367, Hybrid Receiver Study. The period of performance was 1 November 1976 to 1 March 1977. The contract monitor was Mr. Terry Grant of NASA/Ames.

The results of feasibility studies of missions to Jupiter, Saturn, and Uranus indicate the desirability of operating a flyby or orbiting spacecraft bus as a relay for the data acquired by the atmospheric probes. A hybrid receiver has been proposed as the vehicle for closing the probe-to-bus communication link in a way which allows maximum flexibility to mission planners, while minimizing development costs by using the same flight hardware for a variety of modulation types and data rates. A receiver which meets these requirements was analyzed and designed during the course of this study.

#### 1.1 RECEIVER PERFORMANCE

The hybrid receiver has been designed to operate over a 20 MHz band centered about 1 GHz, with 20 channels spaced at 1 MHz intervals. A predominant characteristic of the probe communication link at this frequency is the magnitude of the doppler uncertainty over which the system must operate. The receiver has been designed to acquire, track, and demodulate over a total frequency uncertainty of  $\pm 80$  kHz (due to doppler spread and oscillator drift) and to track a doppler rate of  $\pm 50$  Hz/sec. The information bandwidth of the received signal ranges from 100 to 1000 Hz using either differential phase shift keyed (DPSK) or a continuous phase frequency shift keyed (CPFSK) modulation. The signal-to-noise ratios, defined in terms of the ratio of carrier power C to noise spectral density N<sub>0</sub>, may be as low as 24.5 dB-Hz for 1000 Hz. These power levels correspond to an  $E_b/N_0$  of 4.5 dB at both the 100 and 1000 Hz information bandwidths.

The most important consideration in specifying the performance of the hybrid receiver is acquisition time. The active life of the nonrecoverable entry probe for Jupiter atmospheric tests has been estimated at 30 minutes. Of this time, 50 seconds has been allocated for receiver acquisition (minimum  $C/N_0$ , probability of acquisition greater than 0.995, and probability of false acquisition below  $10^{-4}$ ). One fundamental result of the tradeoff study was the determination that a conventional phase-locked receiver is unable to meet this acquisition time requirement by a wide margin. For this reason, a sequential acquisition procedure has been developed which not only achieves the required performance, but also avoids the complexity of performing parallel searches in frequency by means of multiple channels or FFT filtering.

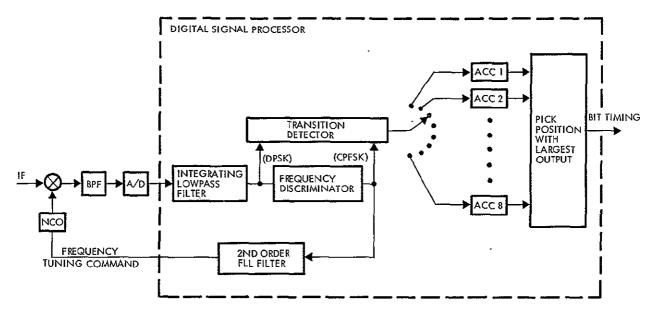

When coarse frequency acquisition has occurred, the receiver is required to lock up and track a 50 Hz doppler rate with less than 1 Hz rms frequency error (1 second

1-1

average and strong  $C/N_0$ ). In order to accomplish this, a second order frequency-lock loop algorithm is incorporated. The receiver also performs bit synchronization with a transition tracking loop, and data demodulation for DPSK and CPFSK signals. Both the frequency and time tracking loops are optimum loops in the sense that the predetection signal-to-noise ratio is maximized by filtering to the data bandwidth, and the demodulation decisions are fed back to the tracking loops (data directed).

The results of extensive analysis and simulation of the hybrid receiver algorithms indicate that all performance specifications are met with margin. For initial acquisition, the probability of acquiring exceeds 0.995 at 45 seconds, while the false alarm rate is below  $10^{-6}$ . The frequency and time tracking loops are able to acquire and track at 24.5 dB C/N<sub>o</sub> not only for 100 Hz of data but also at 1000 Hz. These tracking loops yield a frequency variance of 3 Hz and time jitter of less than 1% at minimum C/N<sub>o</sub>. Simulation of the entire receiver demodulation sequence shows a performance which is within 0.5 dB of the theoretical performance of DPSK and CPFSK signaling. Table 1-1 lists the key performance specifications and capabilities for the hybrid receiver.

| Performance Parameter              | Specification    | Capability          |

|------------------------------------|------------------|---------------------|

| Frequency (selectable)             | 1000 ±10 MHz     | 991, 992,, 1011 MHz |

| Doppler uncertainty                | ±80 kHz          | ±80 kHz             |

| Maximum doppler rate               | ±50 Hz/sec       | ±50 Hz/sec          |

| Minimum signal                     | -146 dBm         | -146 dBm            |

| Maximum signal                     | -116 dBm/Hz      | -116 dBm            |

| Maximum noise (N <sub>o</sub> )    | -166 dBm/Hz      | -166 dBm/Hz         |

| Minimum noise (N <sub>o</sub> )    | -170 dBm/Hz      | -170.5 dBm/Hz       |

| Minimum operating C/N <sub>o</sub> | 24 dB-Hz         | 24.5 dB-Hz          |

| Minimum signal BW                  | 100 Hz           | 100 Hz              |

| Maximum signal BW                  | 1000 Hz          | 1000 Hz             |

| Acquisition time (24.5 dB-Hz)      | 50 sec           | 45 sec              |

| Probability of acquisition         | 0,995            | 0.995               |

| Probability of false acquisition   | 10 <sup>-4</sup> | <10 <sup>-4</sup>   |

| Frequency track error*             | 1 Hz             | 0.2 Hz              |

| Table | 1-1  | Hybrid | Receiver | Performance |

|-------|------|--------|----------|-------------|

| lanic | T_T. |        | VECEIVEL | rentormance |

$^{*}C/N_{O}$  = minimum plus 20 dB, maximum doppler rate

In addition to the demodulation functions, the hybrid receiver design lends itself to extremely accurate measurements of frequency and signal strength. Table 1-2 lists the capabilities of the hybrid receiver in estimating these parameters for the purposes of radio science missions. Because the entire receiver is coherently tied to a single frequency reference and all frequency tuning is done digitally (without voltage controlled oscillators), frequency resolution to 0.14 Hz

| Performance Parameter                                                                                                                          | Statement<br>of Work<br>Specification | Receiver Capability                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------|

| Signal Power Measurement                                                                                                                       |                                       | Receiver oupubling                                                                          |

| Accuracy                                                                                                                                       | ±1 dB                                 | ±0,7 dB                                                                                     |

| Gain stability                                                                                                                                 | ±0,1 dB                               | ±0.1 dB*                                                                                    |

| Averaging times                                                                                                                                | 1 to 60 sec                           | 1,2,4,8,16,32,64 sec                                                                        |

| Estimate uncertainty (3ơ)                                                                                                                      |                                       |                                                                                             |

| 1 kbps, C = $-116$ dBm (high SNR)                                                                                                              |                                       |                                                                                             |

| Single sample<br>0.1 sec (100 samples)<br>10 sec (1000 samples)                                                                                |                                       | $^{\pm 0.04}_{\pm 4.3}$ dB $^{-3}_{\pm 4.3}$ dB $^{\pm 4.3}_{\pm 4.3}$ x 10 $^{-4}_{-4}$ dB |

| 100 bps, C = -146 dBm (low SNR)                                                                                                                |                                       |                                                                                             |

| Single sample<br>1 sec (100 samples)<br>60 sec (6000 samples)                                                                                  |                                       | ±3 dB<br>±0.41 dB<br>±0.056 dB                                                              |

| Frequency Measurement                                                                                                                          |                                       |                                                                                             |

| Frequency Resolution                                                                                                                           | TBD                                   | ±0.114 Hz (24-bit command)                                                                  |

| Averaging times                                                                                                                                | 1 to 60 sec                           | 1,2,4,8,16 sec                                                                              |

| Frequency uncertainty (3ơ)                                                                                                                     |                                       |                                                                                             |

| <pre>100 bps, D = 50 Hz/sec, C = -126 dBm Single sample 1 sec (100 samples) 5 sec (500 samples) 10 sec (1000 samples)</pre>                    | -                                     | ±3.78 Hz<br>±0.378 Hz<br>±0.169 Hz<br>±0.119 Hz                                             |

| <pre>1 kbps, D = 50 Hz/sec, C = -136 dBm<br/>Single sample<br/>1 sec (1000 samples)<br/>5 sec (5000 samples)<br/>10 sec (10,000 samples)</pre> | <br><br>                              | ±7.53 Hz<br>±0.24 Hz<br>±0.11 Hz<br>±0.076 Hz                                               |

| Table | 1-2. | Radio | Science | Performance |

|-------|------|-------|---------|-------------|

\*Assumes regulated power to front end

is possible and filtered doppler estimates can be made with uncertainties below 0.25 Hz. For measuring incoming signal strength, assuming accurate power regulation is provided for the front end RF/IF circuitry, the fixed gain front end (no AGC amplification) allows extremely accurate relative gain measurements. By averaging for periods up to 60 seconds, the estimates of signal strength can be made with relative uncertainties below 0.1 dB.

The accuracies of both the frequency and time estimates are felt to be difficult or impossible to achieve using conventional analog receiver techniques.

#### **1.2 RECEIVER CHARACTERISTICS**

The hybrid receiver has been designed to meet severe environmental and physical requirements. The tightest environmental restrictions placed on the system are in the areas of power dissipation, reliability, and radiation hardness. The hybrid receiver consumes a total of 12 watts of regulated power for a single unit, including all the RF-IF equipment, the A/D conversion, frequency generation, and digital signal processing. This unit is estimated to have a reliability over the 8 year lifetime of the mission of 0.941. Since the specification requires reliability greater than 0.98, two units are called for, one in a stand-by powered down mode. In this configuration, a 0.997 reliability is achieved and no single point failure exists.

The outer planet mission profiles indicate a probable radiation dose of up to 200K rad(Si). At these levels, severe performance degradations can occur in both digital and analog circuits. For this reason, the hybrid receiver was designed using only parts which are inherently radiation resistant, thereby eliminating the need for radiation shielding. The amplifier chain in the analog portions of the radio is constructed using parts which have been previously used on radiation resistant military spacecraft programs or have been radiation tested. In addition, only fixed gain amplifiers have been chosen, thereby eliminating any AGC circuits as sources of degradations. The sample and hold circuits are designed using J-FET's and radiation-hard operational amplifiers. The analog-to-digital converter is a monolithic device developed for the Air Force for radiation hardened applications. Frequency generation for receiver tuning is done in the digital domain, thereby eliminating any VCO problems. The entire digital processor is designed using only bipolar technology. Tradeoff studies dictated the use of bipolar instead of the slightly lower powered C-MOS family because the performance of C-MOS has been shown to degrade in a high radiation environment and C-MOS cannot meet the processing speed requirements.

Figure 1-1 illustrates the environmental and physical characteristics of the hybrid receiver, the packaging concept for the flight hardware, and the fundamental performance capabilities of the design.

7-4

#### **1.3 RECEIVER DESCRIPTION**

The hybrid receiver combines the positive attributes of analog and digital signal processing to achieve a design with maximum flexibility and minimum complexity. The design is based to a large extent on existing analog and digital subassemblies and circuits in order to minimize development cost and risk. The receiver incorporates several unique features which result in significant simplification and/or performance advantages relative to conventional analog receiver design. These features are:

- Fixed RF/IF gain No AGC

- Digital frequency generation No VCO ...

- IF sampling No I-Q balance problems

- Sequential detection for rapid acquisition

- Digital signal processing for improved performance and flexibility.

These features are based on proven design principles and make maximum use of previously developed hardware to minimize development cost and risk. In arriving at the final design of hybrid receiver, the criteria used for making design selections were:

- Satisfying the stated performance specifications

- Minimizing the design complexity to reduce size, weight, and power, and to increase reliability.

- Maximize the flexibility of the design to accommodate varying mission requirements

- Utilize existing designs where feasible.

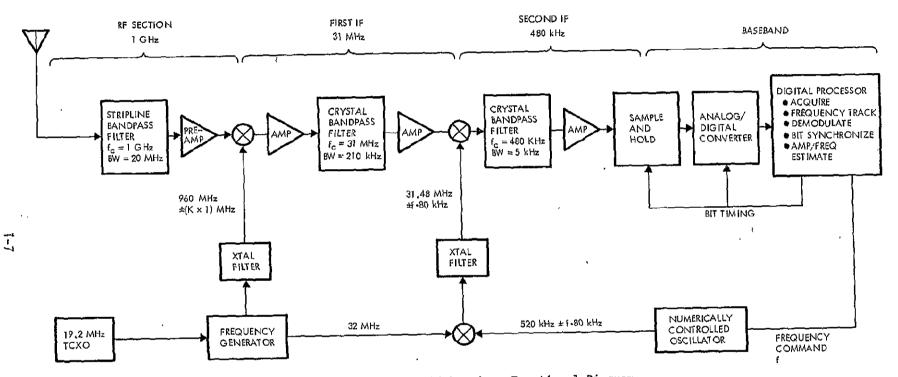

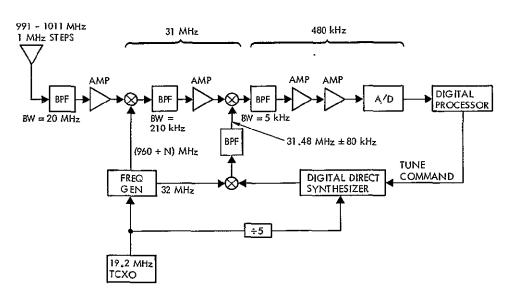

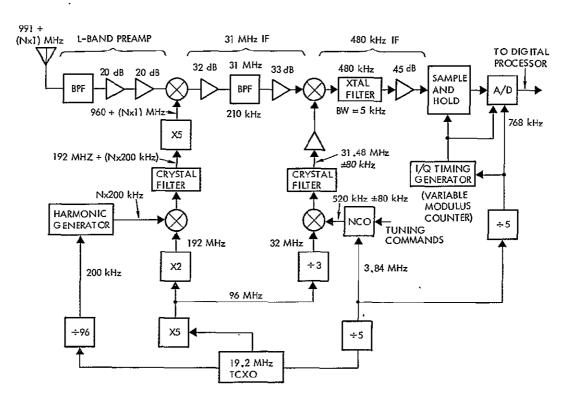

A functional diagram of the hybrid receiver is shown in Figure 1-2.

The design utilizes a triple conversion front end, the third step being an I-Q digital downconversion within the sample-and-hold and A/D converter. The received 1 GHz signal is first bandpass filtered to a 20 MHz bandwidth in a stripline filter, amplified in a two-stage preamplifier module, and amplified again in another two-stage amplifier. The filter bandwidth accommodates any input frequency in the 1000  $\pm 10$  MHz range without redesign, as required. The noise figure for this front end is 3.2 dB and the amplifiers provide a self-limiting feature to protect against large input signals (up to -10 dBm). The design is an adaptation of a TRW L-band receiver used on a military satellite program.

The L-band signal is downconverted to a first IF of 31 MHz, where the signal is amplified again and bandpass filtered. The crystal filter at 31 MHz is a 4-pole amplitude equalized filter having a 3 dB bandwidth of 210 kHz, which accommodates the maximum frequency uncertainty of  $\pm 75$  kHz due to doppler and any offsets due to oscillator drift. The design of this IF strip is taken directly from the TRW work for the

Figure 1-2. Hybrid Receiver Functional Diagram

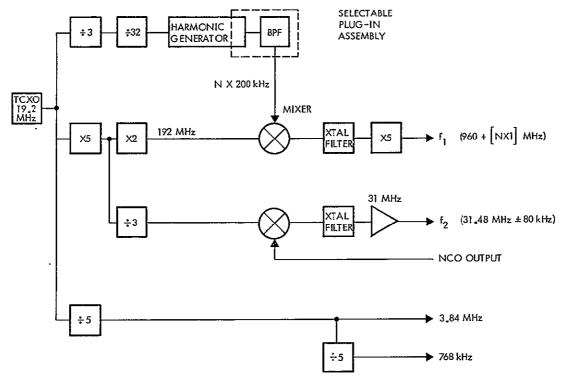

Space Shuttle S-band communications program. The LO source for the 1st downconversion is obtained by selecting (via crystal filter) the desired mixing signal from a comb of frequencies spaced at 1 MHz intervals, thereby providing 20 separate channels in the interval from 991 to 1011 MHz. The comb of frequencies is generated by multiplying the 19.2 MHz reference to 192 MHz, and mixing with a comb of frequencies spaced at 200 kHz which in turn are also generated from the 19.2 MHz source. The resulting 192 MHz comb is filtered to acquire the desired spectral line, and multiplied times 5 to get to 960 MHz. Since all mixing operations are coherent with the 19.2 MHz reference. Assuming a space qualified TCX0, the stability of this LO is  $5 \times 10^{-7}$  per year (long term) and  $1 \times 10^{-9}$  per second (short term). The short term variance at 1 GHz is 1 Hz/sec rms, which is sufficient to allow radio science frequency estimation for averaging times between 1 and 60 seconds.

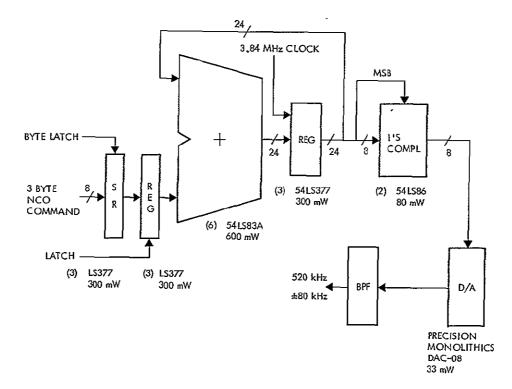

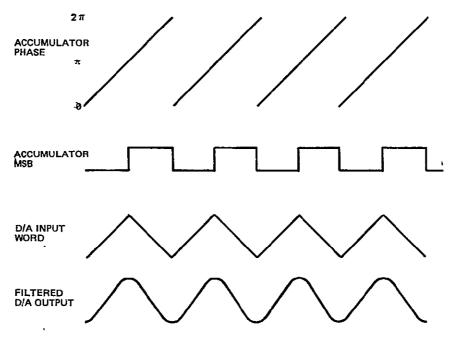

A second downconversion accomplishes the tuning of the receiver across the 160 kHz doppler range, and yields a second IF signal at 480 kHz. This signal is filtered to a bandwidth of 5 kHz, amplified, and applied to the sample and hold circuit for digitizing. The frequency source for the second downconversion results from mixing a 32 MHz reference (19.2 MHz x  $5 \div 3$ ) with a tuning signal which is generated digitally in a numerically controlled oscillator (NCO). The NCO operates by incrementing a phase accumulator  $3.84 \times 10^6$  times per second with an incremental phase generated by the digital processor. This incremental phase is a 24-bit binary word which constitutes the frequency tune command, and has a resolution of 1/4 Hz across the range from 440 to 600 kHz. The resulting phase ramp is mapped to an amplitude, converted to an analog voltage, and filtered to produce the offset tuning source.

The advantage of using a digital NCO for tuning lies in its inherent stability and simplicity. A conventional tunable VCO with a digital-to-analog interface to convert frequency commands to control voltages is replaced by a simple synthesizer with a direct digital interface to the processor. The result is a clean high reliability digital-to-frequency interface design which eliminates the necessity for the high resolution (19 bits for 0.25 Hz resolution) D/A converter needed to attain the specified tuning accuracy with a VCO. A D/A converter is used in the synthesizer, but it requires only 8 bits of resolution. In addition, the long term frequency accuracy reflects that of the 3.84 MHz clock. Since both the 32 MHz reference and the 3.84 MHz clock are derived from the 19.2 MHz oscillator, the overall receiver stability is locked to the precision reference.

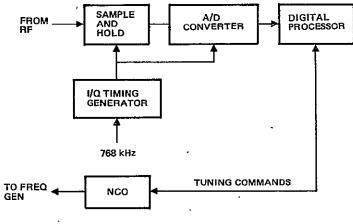

The 480 kHz signal is sampled directly at the second IF by a sample and hold circuit and the samples are quantized to 8 bits in the A/D converter. The sample and hold has an aperture time of 100 psec, which introduces negligible degradation to the sampling process due to sampling time jitter. The 8-bit A/D converter is a monolithic chip of the successive approximation type which is radiation hardened and

1-8

designed for a maximum clock rate of 13 MHz. The A/D converter is a lower power version of a design developed for the Air Force Avionics Laboratory (AFAL).

The input signal to the sample and hold circuit is 5 kHz wide. Calculations show that in this bandwidth the total signal plus noise power varies 17.8 dB as the signal goes from -146 to -116 dBm. By selecting the nominal loading point of the A/D converter to be -4 dB (ratio of rms signal power to A/D input clipping level), the digitizing process introduces quantization noise which is at least 20 dB below the thermal noise over the entire 30 dB variation in signal power. In addition, with signal absent the noise alone loads the A/D to level 8 which allows sufficient quantization to accurately perform the coarse acquisition sequential detection algorithm. Thus the entire receiver front end can be operated with fixed gain, eliminating the need for AGC.

In addition to digitizing the signal, the sampling process accomplishes the final downconversion to baseband, and separates the signal into inphase and quadrature channels. This is accomplished by taking successive pairs of samples spaced by an odd number of quarter cycles at the frequency being converted to baseband. For truly narrowband signals of bandwidth less than the sampling rate, this process yeilds alternating inphase and quadrature samples from the A/D converter. The advantage of this approach lies in its simplicity. The complex and costly quadrature hybrids, mixers, amplifiers, filters, and redundant A/D converters classically used in an analog implementation of the interface with the digital processor are all replaced by a simple direct digital interface. The result is a simple, high reliability analog/digital interface design which eliminates the alignment and balancing procedures normally associated with analog I/Q circuitry.

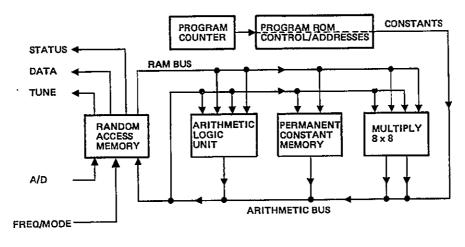

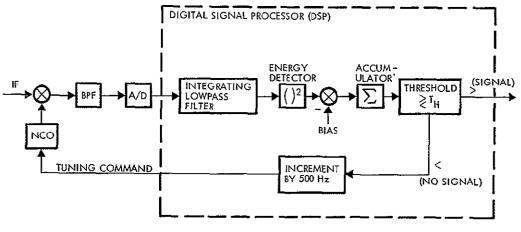

The quantized baseband I-Q samples are transferred to a high speed digital signal processor (DSP) for acquisition and tracking as well as demodulation and symbol synchronization. It was determined that the coarse frequency acquisition requirement was the determining factor in the design of the DSP. A modified sequential detection algorithm was selected for the hybrid receiver because it does not require parallel operations on multiple frequencies, and therefore eliminates the need for high speed (and high power) FFT processing. This algorithm processes a single frequency hypothesis at a time, sweeping across the region of uncertainty in search of the additional energy represented by the signal over the thermal noise.