# CLOCKING AND SYNCHRONIZATION WITHIN A FAULT-TOLERANT MULTIPROCESSOR

by

Howard R. Krauss

B.E. The Cooper Union (1971)

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1972

roun Signature of Author Department of Aeronautics and Astronautics

May 1972

Certified by Thesis Supervisor

Accepted by

Chairman, Departmental Committee on Graduate Students

### CLOCKING AND SYNCHRONIZATION WITHIN

A FAULT-TOLERANT MULTIPROCESSOR

by

### Howard R. Krauss

Submitted to the Department of Aeronautics and Astronautics, May, 1972, in partial fulfillment of the requirements for the Degree of Master of Science.

### ABSTRACT

In this thesis the synchronization requirements of a fault-tolerant multiprocessor are defined and methods of maintenance of synchronism are developed. It is demonstrated that a synchronous fault-tolerant multiprocessor driven by a faulttolerant clock is more efficient and more easily implemented than is an asynchronous fault-tolerant multiprocessor.

Fault-tolerant clocking has been examined intensively here. From fault-tolerance requirements and the established multiprocessor synchronization requirements, general specifications are developed for a fault-tolerant clock. Two general methods of design have been explored, and it has been concluded that if the clock is to be distributed to many modules, faulttolerant clocking through the concepts advanced by William Daly and John McKenna of the C.S. Draper Laboratory, is more practical to implement than is fault-tolerant clocking through failuredetection and subsequent clock substitution. Clocks developed by Daly and McKenna have been examined, refined, and revised. It is demonstrated that it is desirable to have available a fault-tolerant clock which runs at 20 MHz. but that such a frequency is not achieveable by a McKenna-type clock (with use of current technology). A method of achieving the use of a relatively slow McKenna-type clock in conjunction with a frequency multiplier is developed. Also, analog phase-locking techniques are shown to be unsuitable for the design of a faulttolerant clock.

Thesis Supervisor: Albert L. Hopkins, Jr. Title: Associate Professor of Aeronautics and Astronautics

#### ACKNOWLEDGEMENTS

The author wishes to express his gratitude, first and foremost, to Dr. Albert L. Hopkins for the guidance and motivation he provided throughout the production of this thesis. Second he is grateful to John McKenna for having reviewed the work on the McKenna Clock and for the suggestions he made. Also, he is indebted to Mary Shamlian for her aid in typing the text of this thesis.

Finally, the author wishes to offer his thanks to Eileen Hack as well as the many other friends and acquaintances for their parts in filling his life.

This report was prepared under DSR Project 55-23890, sponsored by the Manned Spacecraft Center of the National Aeronautics and Space Administration through Contract NAS 9-4065.

The publication of this report does not constitute approval by the Charles Stark Draper Laboratory or the National Aeronautics and Space Administration of the findings or the conclusions contained herein. It is published only for the exchange and stimulation of ideas.

# TABLE OF CONTENTS

|         |       |                                | Page |

|---------|-------|--------------------------------|------|

| CHAPTER | l     | FAULT-TOLERANT MULTIPROCESSING | 6    |

|         | 1.1   | Introduction                   | 6    |

|         | 1.2   | General Characteristics        | 6    |

|         | 1.2.1 | Fault-Tolerance                | 8    |

|         | 1.3   | Particular Configuration       | 8    |

|         | 1.3.1 | Achievement of Fault-Tolerance |      |

|         |       | Within the Regional Computer   | 10   |

|         | 1.3.2 | Achievement of Fault-Tolerance |      |

|         |       | Within the Local Processor     | 12   |

|         |       |                                |      |

| CHAPTER | 2     | SYNCHRONIZATION                | 13   |

|         | 2.1   | Definitions and Requirements   | 13   |

|         | 2.2   | Loss of Synchronization        | 13   |

|         | 2.3   | A Synchronized System With     |      |

|         |       | Unsynchronized Elements        | 20   |

|         | 2.4   | System Synchronization Through |      |

|         |       | Use of a Common Clock          | 28   |

|         | 2.5   | Conclusions                    | 29   |

# Page

| CHAPTER        | 3     | CLOCKING                           | 31. |

|----------------|-------|------------------------------------|-----|

|                | 3.1   | Specifications of a Fault-Tolerant |     |

|                |       | Clock                              | 31  |

|                | 3.2   | General Methods of Design          | 32  |

|                | 3.3   | Fault-Tolerant Clocking Through    |     |

|                |       | Failure-Detection and Subsequent   |     |

|                |       | Clock Substitution                 | 32  |

|                | 3.4   | The McKenna Clock                  | 42  |

|                | 3.4.1 | First Concept                      | 42  |

|                | 3.4.2 | Current Concept                    | 70  |

|                | 3.5   | Speeding Up the McKenna Clock      | 80  |

|                | 3.5.1 | Advantages of Greater Speed        | 80  |

|                | 3.5.2 | Application of Advanced Device     |     |

|                |       | Technology                         | 80  |

|                | 3.5.3 | Revised Circuit                    | 81  |

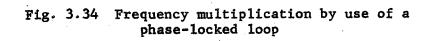

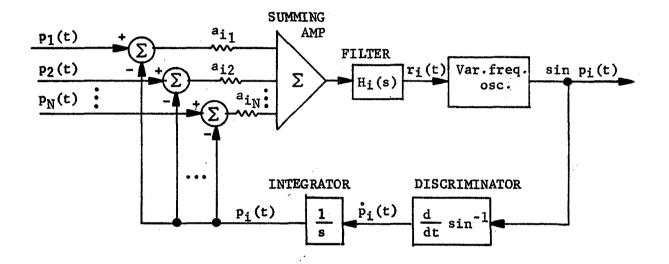

|                | 3.5.4 | Increased Speed by Frequency       |     |

|                |       | Multiplication                     | 84  |

|                | 3.6   | Methods of Synchronization Used    |     |

|                |       | In Pulse-Code Modulation           | 89  |

| CHAPTER        | 4     | CONCLUSIONS                        | 94  |

| -1111<br>-1111 |       |                                    | . – |

| REFEREN        | CES . |                                    | 96  |

•

### CHAPTER 1

#### FAULT-TOLERANT MULTIPROCESSING

## 1.1 Introduction

The concept of a fault-tolerant multiprocessor was developed and explored at the C.S. Draper Laboratory as a method of satisfying future spacecraft guidance requirements. Future space vehicles will require the handling of additional control loops, and as missions become more complex and/or lengthier greater reliability is required. In a proposal to NASA particular emphasis was placed on the application of a fault-tolerant multiprocessor as a space shuttle guidance computer.

# 1.2 General Characteristics

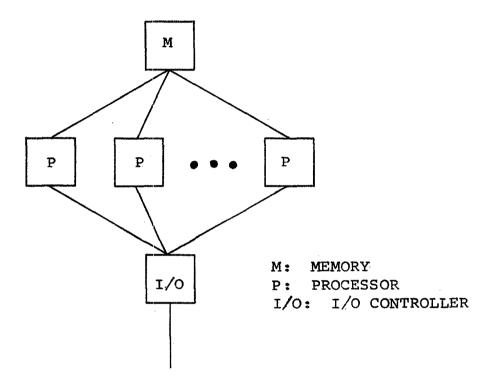

The essential elements of a multiprocessor are two or more processors capable of simultaneously executing different programs (or the same programs) and a common memory accessible by all processors. This collection of units has a single path for input-output communication. A conceptual diagram is shown in Fig. 1.1.

Because of the parallel operation of the individual processors there is a significant increase in computational capability. This parallelism lends itself very well to the requirement of simultaneous control of many loops. The germ

Fig. 1.1 Generalized Multiprocessor

of increased reliability is also inherent within the multiprocessing concept: processors are alike and hence any processor is capable of performing within any control loop at a given time; it is this modularity which is the fundamental idea behind fault-tolerant multiprocessing.

### 1.2.1 Fault-Tolerance

In general, fault-tolerance is achieved through coded redundancy, replicated redundancy, or a combination of the two. Except in special instances, redundancy by replication is more reliable and more simply implemented (Ref. 1). Within the multiprocessor under study, fault-tolerance is achieved through comparison and/or voting amongst replicated units. Some basic assumptions in the design of this system are: (1) failures are independent of one another; (2) the same error will not be made at the same time by two elements which are in a comparison or voting scheme; and (3) multiple errors will not occur so as to outwit the fault-tolerant scheme (roughly equivalent to saying that errors will be separated by some minimum time). In a system which operates such that failures are independent of one another, the probability of assumptions nos. 2 and 3 being violated is extremely small.

### 1.3 Particular Configuration

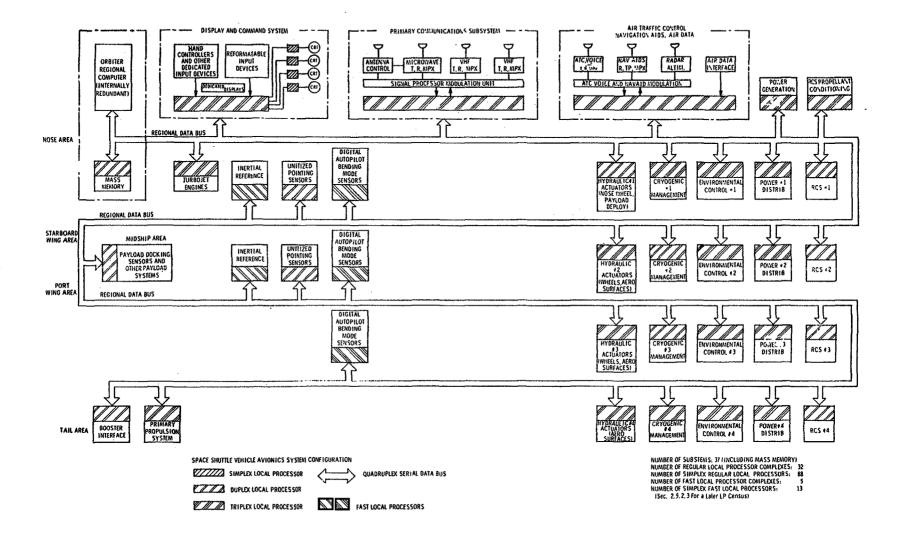

Figure 1.2 is a representation of the data management system recommended for the Space Shuttle. The system is designed to meet a fail operational, fail operational, fail safe (FOFOFS) specification; by this specification it is meant that the system will maintain its performance capabilities after the occurrence of any two failures and, as a result

Fig. 1.2 Assumed System Configuration

of a third failure, in the worst case, suffer a graceful degradation to a configuration which can still assure safe control of the vehicle. The system is hierarchical. The many sensors and effectors compose the lowest level. Next up in the hierarchy, the local processors transform between the serial-multiplex format of the data bus and the sensor-effector formats; also they are charged with the function of assuming those burdens which would unnecessarily overload the top level of the system. At the top, the regional computer provides data processing services to the entire system and manages interactions between subsystems.

The use of multiprocessing techniques in the regional computer (RC) serves both to achieve fault-tolerance and to yield a larger throughput than would be possible with a simplex machine. Within the local processor (LP) duplication of processors is used solely as a tool for the achievement of fault-tolerance.

# 1.3.1 <u>Achievement of Fault-Tolerance Within</u> The Regional Computer

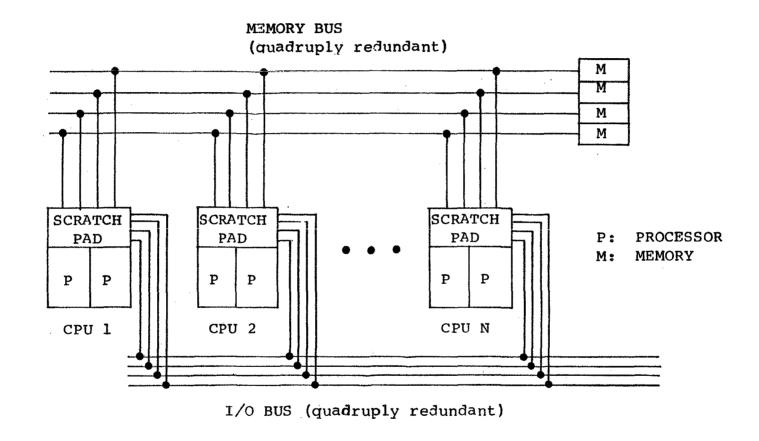

The regional computer multiprocessor configuration recommended by the Draper Lab is shown in Fig. 1.3. Each Central Processing Unit (CPU) consists of two processors and a triplicated scratchpad memory which stores local temporary data and performs input/output (I/O) buffering. The memory, memory bus, and data bus are each redundant. The memory may be accessed by only one CPU at a time, and only one CPU (or LP) may be transmitting on the data bus at any time.

Fig. 1.3 Regional Computer Multiprocessor

.

CPU error detection is achieved by comparing the outputs of the two processors, which run identical programs. The detection of a CPU error triggers Single Instruction Restart (SIR), which consists of the moving of the scratchpad contents of the "failed" unit into memory and the subsequent loading of this information into the next available "healthy" CPU, whereupon the failed job is resumed. The recovery is transparent to the software.

Fault-tolerance requirements are met by providing sufficient CPUs such that after an established number have failed the remainder can provide the necessary response speed and throughput to meet the system requirements. Thus, there is the advantage of extra processing capability before any CPU fails.

# 1.3.2 Achievement of Fault-Tolerance Within The Local Processor

Depending upon system requirements a local processor may be simplex, duplex, or triplex. In any case error detection is achieved as in a CPU: each LP unit contains two processors which perform identical operations and compare outputs. Faulttolerance is not through a restart mechanism, however. In the case of a duplex or triplex LP, local fault-tolerance is achieved by keeping two LP units in synchronism. One feeds the data bus and the other has its output blocked; in the event of a failure of an LP unit, its output is blocked and the other's is enabled. It is because of the differences amongst local processors serving different sensor-effector systems as well as a desire to limit data bus use that this mechanism for achieving fault-tolerance is used rather than an SIR.

#### CHAPTER 2

### SYNCHRONIZATION

### 2.1 Definitions and Requirements

If fault-tolerance is to be achieved through comparison and/or voting amongst replicated units then there are two requirements of operation which establish a need for synchronization. Obviously in order for the comparison to be effective, corresponding output information from each unit must be compared. Second, in order to assure equality of internal operations, accessed input information must be equal at corresponding program points. It should be noted that although synchronization is required, simultaneous production of corresponding information or simultaneous performance of corresponding internal operations are not required. It is best to discard the notion that two events can be made to occur at the same time; in a real system there must always be finite tolerances in the "simultaneous" initiation of events. It is fortunate that the synchronization requirements do not call for simultaneity, but, as shall be seen in Section 2.2, the impossibility of assuring simultaneity gives rise to difficulties in assuring synchronization.

# 2.2 Loss of Synchronization

Assuming that several modules have been synchronized, loss of synchronization may be caused by a slivering of pulses.

A sliver can occur when two independent observers strobe a common signal while it is undergoing a transition. Because of gate thresholds and propagation delays, the observers may see different values of the signal. Slivering can cause differences in the sequences of internal operations (leading to uncorrelated outputs) or in the outputs of replicated comparators.

If the input or the event being strobed is phase-locked (i.e., dependent on the same clock) with the strobe, then slivering may be avoided (barring the event of a failure) through good design techniques. If, however, the observed signal is produced asynchronously, or more generally, if the production of the observed signal is uncorrelated with the strobe or the call for data, then anti-sliver circuits must be utilized as necessary.

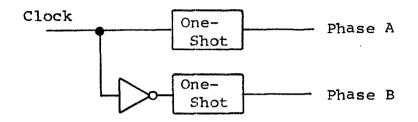

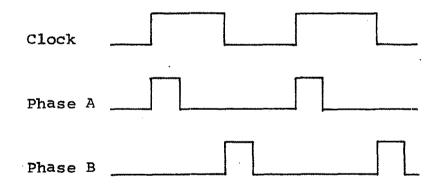

Current designs for anti-sliver circuits require the presence of a two-phase clock. A two-phase clock may be simply produced as illustrated in Fig. 2.1. The pulses of the two phases are mutually exclusive. The application of this clock to an anti-sliver circuit is illustrated in Fig. 2.2. The event pulse is stored in the first buffer; as illustrated, either the concurrent (as in Case 1) or the next (as in Case 2) phase A pulse will cause the event to be stored in the second buffer, which is strobed, after settling, by a phase B pulse, thereby feeding a healthy signal to both units.

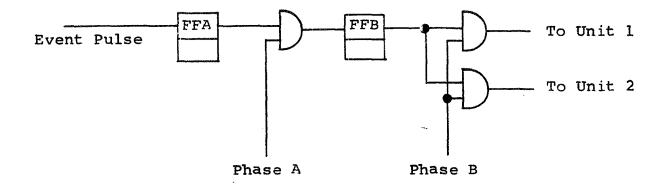

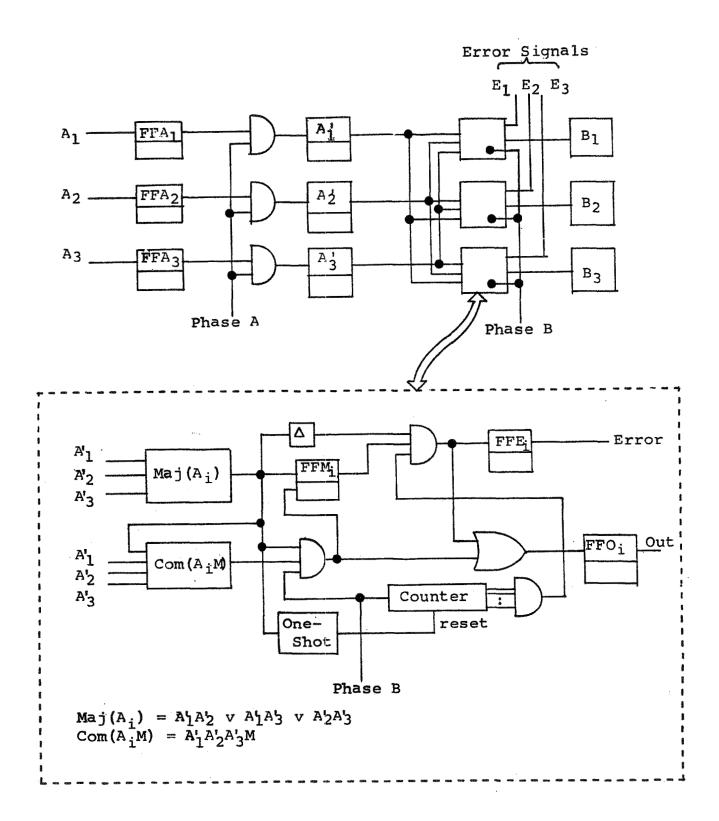

In a fault-tolerant system, when a replicated group of modules is receiving replicated information asynchronously, an anti-sliver unanimity circuit may be used to maintain synchronization. Such a circuit is illustrated in Fig. 2.3. The transmitted information from the A<sub>i</sub>s to the B<sub>i</sub>s is sliver-free

Fig. 2.1 Two-Phase Clock

Fig. 2.2 Anti-Sliver Circuit

•

Fig. 2.3 Anti-Sliver Unanimity Circuit

and all the  $B_i$ s receive synchronized information from all the  $A_i$ s at the same time so that an accurate vote may be taken, and so that the  $B_i$ s remain in synchronism. Each unanimity circuit waits long enough to accumulate all the  $A_i$ s but not so long as to impair operation due to a failure of one of the  $A_i$ s.

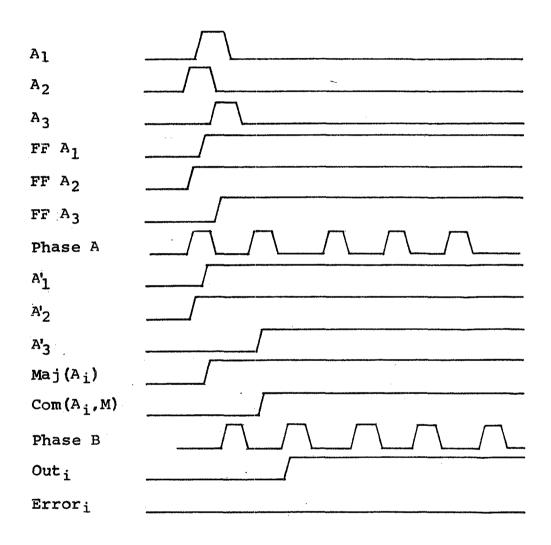

The timing chart in Fig. 2.4 illustrates a possible sequence of events for the case of no failure. The event to be transmitted to the B is A  $\rightarrow$  1. The example shown in Fig. 2.4 indicates that the events,  $A_i \rightarrow 1$ , occurs first in  $A_2$ , second in  $A_1$ , and last in  $A_3$ . Each event,  $A_i \rightarrow 1$ , is held in the corresponding flip-flop, FFA<sub>i</sub>. Concurrent with the first Phase-A pulse shown, only FFA, and FFA, are at logic-level-1; the flip-flops  $A_1^i$  and  $A_2^i$  are set during the first Phase-A pulse. The setting of the flip-flop A' occurs during the second Phase-A pulse. As can be seen in Fig. 2.3, each flipflop  $A_{i}^{\prime}$  is fed to each of the majority and comparator elements; the output of  $Maj(A_i)$  is logic-1 when a majority of the inputs is at logic-1, and the output of Comp(A, M) is logic-1 only when all the inputs are at logic-1. In this example,  $Maj(A_i) \rightarrow 1$ shortly after the first Phase-A pulse, while Comp(A,M) does not go to logic-l until the occurrence of the second Phase-A pulse. The occurrence of Maj( $A_i$ )  $\rightarrow 1$ : causes the counter of Phase-B pulses to be reset to zero, causes the flip-flop FFM; to be set at logic-1, and also feeds the delay element  $\triangle$ . The occurrence of Comp(A<sub>i</sub>M)  $\rightarrow$  1: causes FFM<sub>i</sub> to be reset (here, before the counter reaches an all-1's state, preventing the propagation of an error signal), and causes an output signal to be propagated to all B.s.

Fig. 2.4 Response of an anti-sliver unanimity circuit in the event of no failure

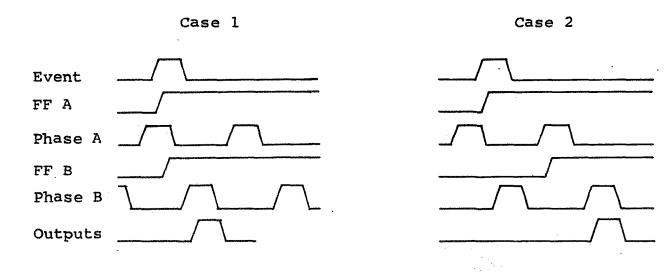

Fig. 2.5 illustrates a possible sequence for the case of a failure of one of the A<sub>i</sub>s. Here A<sub>3</sub> is described as having failed to produce a bit of information (pulse). A1 is shown to precede A2 such that the events are passed on to the majority and comparator elements separated by one Phase-A period. When flip-flop A' goes to logic-1, A' has already been set, and the majority elements go to logic-1, the comparator elements, however, remain at logic-0, as flip-flop A' was not set. Again, as a result of Maj(A,)  $\rightarrow$  1, the counter is reset, FFM, is set, and the delay element is fed. It should be noted that the time-delay element,  $\Delta$ , is used in order to prevent the false indication of an error when an all-1's state is indicated by the counter just prior to reset. The delay time required is dependent on clock frequency and propagation delay between a reset command and a response (assuming the counter was in an all-1's state) at the input of the error-indicating AND gate. In the example shown in Fig. 2.5 it is assumed that a 2-bit counter is used; hence, shortly after the occurrence of the third Phase-B pulse, succeeding the transition  $Maj(A_i) \rightarrow 1$ , each line indicates both an output signal and an error.

# 2.3 <u>A Synchronized System With Unsynchronized</u> <u>Elements</u>

Before considering a multi-layered hierarchial system, it is wise to look at a simple model of this problem. Consider two modules each with one input line and one output line, each receiving and transmitting data serially. At an arbitrary time (t = 0), there is no signal on any line and the internal states of the modules (processors) are equivalent. For all time, t > 0, equivalent input data is received in serial bytes

| <sup>A</sup> 1                      |   |

|-------------------------------------|---|

| <sup>A</sup> 2                      |   |

| A <sub>3</sub>                      |   |

| FF A <sub>1</sub>                   |   |

| FF A <sub>2</sub>                   |   |

| FF A <sub>3</sub>                   |   |

| Phase A                             |   |

| A'1                                 |   |

| A <sup>i</sup> 2                    |   |

| A'3                                 |   |

| Maj(A <sub>i</sub> ) <sub>i</sub>   |   |

| Com(A <sub>i</sub> ,M) <sub>i</sub> | • |

| Phase B                             |   |

| Outi                                |   |

| Errori                              |   |

Fig. 2.5 Response of an anti-sliver unanimity circuit in the event of a failure of one of the A<sub>i</sub>s

by both modules (not simultaneously); it is desired that the modules perform identical operations with identical internal and input data, and that corresponding bits of outputted data be recognized in order to facilitate comparison. In this analysis it is not necessary to consider whether the processors are clock-driven (synchronous) or asynchronous machines; in either case, corresponding produced data bits are separated in time.

Not only may input data be received at different times by the modules, but more significantly it may be received at different points in the program being run by the two modules. In the worst case such a condition may cause calculations to be made with different numbers, or a branch to occur in one processor but not in the other.

Two theorems, which taken together contend that two independent processors (or, in general, modules) may be synchronized, are stated and proved below.

<u>Theorem 1</u>. Two independent modules can be made to perform identical operations with identical internal and input data.

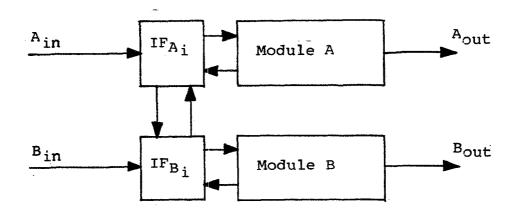

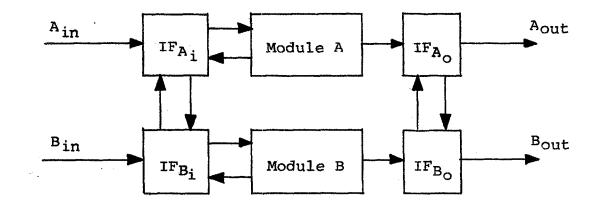

<u>Proof</u>. Assume there is an interfacing unit associated with each module's input. The interfacing units may communicate with each other as well as with their associated modules see Fig. 2.6. As in the case of the modules, the structure and operation of the interfaces are identical with each other. Assume that incoming bytes of information are buffered in corresponding registers within each interface. Let each register have two extra bits (n extra bits - in the case of n parallel modules) above the number used to store input data;

Fig. 2.6 Synchronization of Input Information

these bits are used as check bits: a 1 in, say, the left bit will be taken to mean that the input byte to "me" has been stored in this register, and a 1 in the other bit will mean that the corresponding input byte to the other module has been stored in the corresponding register. Hence each module may be aware if corresponding information is available to both. The precise nature of the structure, possible microprogram, or requirements for fault-tolerance, of the interface units need not be considered presently. Rather the purpose of this discussion is to determine, first, if a system meeting the requirements (stated earlier in this section) is possible. Through use of these check bits by the program the modules may be kept in synchronization. Note that it is important that updating of memory associated with a module by input data be controlled by the program so as to assure equality of available information at corresponding program points. Anti-slivering circuits will not be needed between interface and module as the structure of the programming will exclude slivering difficulties.

<u>Theorem 2</u>. Corresponding bits of output data produced by two independent modules can be recognized.

<u>Proof.</u> For purposes of buffering of information and comparison allow an interface unit to be associated with each module's output. To allow comparison these interfaces have communication with each other. See Fig. 2.7. At an arbitrary t = 0, the registers of the output buffers are clear and no output bytes of information are stored in the registers of the interface. When corresponding registers have been written into, the contents are compared by comparators within both

Fig. 2.7 Synchronization of Asynchronous Modules

interface units. If there is no error the data is released to output and the registers read are cleared.

In order to determine how much buffering space is required consideration must be given to such things as: peak rate of output production, maximum time separation in production of corresponding information; and rate of comparison and clearing of registers within the interface units. If we define the following quantities:

p: peak rate of production (in bits/sec),

n: length of one register (in bits),

- t : time required for comparison and subsequent outputting and clearing of register (in sec.),

- t : maximum time separation in production of corresponding bits, and

- x: the number of registers required for one output interfacing buffer,

then if

$$t_c < \frac{n \text{ bits}}{p \text{ bits/sec}}$$

:

$x = \frac{1}{n} (pt_s + 2n)$

If the nature of the processor is such that it produces information in serial bytes, then the peak rate of production of bits, averaged over several bytes, will be less than p. If we define:

```

a: peak time averaged rate of production

(in bits/sec.), and

t_: averaging time,

```

then if

$$\frac{n \text{ bits}}{p \text{ bits/sec}} < t_c < \frac{n \text{ bits}}{a \text{ bits/sec}}$$

:

$$\mathbf{x} = \frac{at}{n} - \frac{1}{t} \left(\frac{at}{p}\right) + \frac{pt}{n} + 2$$

In the worst case  $t_c = \frac{n \text{ bits}}{a \text{ bits/sec.}}$ , then:

$$\mathbf{x} = \frac{\mathbf{at}}{\mathbf{n}} (1 - \frac{\mathbf{a}}{\mathbf{p}}) + \frac{\mathbf{pt}}{\mathbf{n}} + 2$$

A numerical example would be helpful; consider:

$$p = 10^{7} \text{ bits/sec,}$$

$$n = 16 \text{ bits,}$$

$$t_{s} = 10^{-3} \text{ sec,}$$

$$a = 10^{6} \text{ bits/sec,}$$

$$t_{a} = 1 \text{ sec,}$$

then, if  $t_c < \frac{n}{p}$ :

$$x = \frac{pt}{n} + 2 = 627 \text{ registers};$$

but if  $\frac{n}{p} < t_c < \frac{n}{a}$ :

$$x = \frac{at}{n} (1 - \frac{a}{p}) + \frac{pt}{n} + 2 = 56,877.$$

It can be seen that if the time required to ready a full register for the next load,  $t_c$ , is greater than the time it takes the processor to fill a register,  $\frac{n}{p}$ , then the buffering requirements are large. If  $t_c$  is larger than  $\frac{n}{a}$ , then the buffer must have an infinite number of registers in order to assure successful operation of the interfacing system.

The elements of design of this elementary system may be applied to a multi-layered hierarchical system. The primary drawback is in the requirements which must be imposed on the software of each processor in order to maintain synchronism of operations amongst replicated units. Different software "tricks" will be required for different input information usage; any requirement imposed on software for purposes of maintaining synchronism will serve to decrease processor speed and hence overall system speed. It is generally poor design procedure to depend on software improvisation for system operation.

# 2.4 <u>System Synchronization Through Use Of A</u> <u>Common Clock</u>

Consideration is now given to a system in which all units are synchronous machines and one clock is used for the driving of all units. Replicated units which are driven by the same clock may be defined to be in synchronism in the case of units which, for purposes of fault tolerance, run the same program and receive the same data (the input being controlled by the same clock), the initiation of each corresponding microprogram step as well as the receipt of corresponding bits of information occur concurrently (plus or minus some small tolerance); such units are said to be in tight synchronism.

First consider the same elementary problem explored in Section 2.3: the synchronization of two processing units. Even though corresponding input information and corresponding program steps are synchronized by the same clock, slivering

may allow one unit to recognize an input a microstep before the other. However, to maintain tight synchronism anti-sliver circuits are not necessary; two-phase clocking is sufficient to avoid slivering: one phase (A) is used for receiving and transmitting of information and the other phase (B) for driving the processor. Output bits produced by phase A are buffered and then compared and transmitted by phase B.

In a multi-level hierarchical system, such as the C.S. Draper Laboratory Space Shuttle Guidance Computer proposal, this method of synchronization should be adequate for the entire system. However, information transmitted from sensor to local processor is not likely to be synchronized with the system clock; for such an interface anti-sliver circuits (or anti-sliver unanimity circuits where called for by fault tolerance requirements) can provide the necessary synchronization of receipt of information by local processors.

## 2.5 <u>Conclusions</u>

At first glance the system described in Section 2.4 is quite simple and desirable, especially in light of the alternative (Section 2.3). The difficulty in the design of a system synchronized through use of a common clock lies in the design of the clock. Such a clock must meet the fault-tolerant specifications both in its internal structure and in its distribution around the system; this is no easy task. Nevertheless it is felt that it is much more desirable to add to the complexity of hardware design by calling for a fault-tolerant clock than it is to suffer the pains of dependency on software improvisation required in an unsynchronized system. It should also be noted that although a synchronous process is generally slower

than an asynchronous processor, an asynchronous fault-tolerant multiprocessor, due to increased software requirements and necessary stop and wait periods, would probably be slower than a fault-tolerant multiprocessor driven by a fault-tolerant clock.

#### CHAPTER 3

### CLOCKING

### 3.1 Specifications of a Fault-Tolerant Clock

As stated in Section 2.5, if a common clock is to be used to drive the system, it must meet the fault-tolerance specifications of the overall system. Whether the system specification be fail operational or fail safe, the clock specification must be fail operational; the clock is as fundamental to the system as the power supply. In the case of a fault-tolerant clock designed to drive a Space Shuttle guidance computer, the clock would need to be able to perform after the occurrence of any combination of three independent failures.

Of prime importance in the design is that the synchronized state of the system is affected neither by any mode of failure of the clock nor by the method of recovery from the failed state (i.e., the synchronization of the system must be transparent to clock failures).

For purposes of design and discussion, the distribution of the clock to all parts of the system will be considered as a part of the clock design; this seems logical, as different concepts of fault-tolerant clocking may conceivably warrant different methods of distribution. It should be realized, however, that one of the keys to a good design will be minimization of the number of wires required for distribution. In a system such as that required for the Space Shuttle, distances

between modules may be on the order of 100 feet; in such a geographically distributed system wiring may assume a large share of the cost and complexity.

As a fault-tolerant computing system may have on the order of hundreds of modules, it is desired to minimize the logic required within each to convert the distributed clock information into the one train of clock pulses which is used for driving the module. Any failure of this logic will be considered as a failure of the entire module, which will be detected by comparison of outputs amongst replicated units.

### 3.2 General Methods of Design

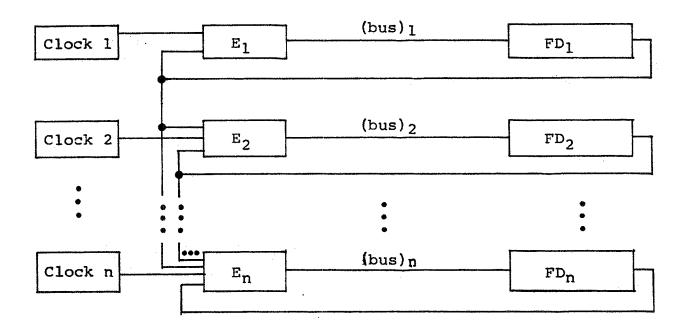

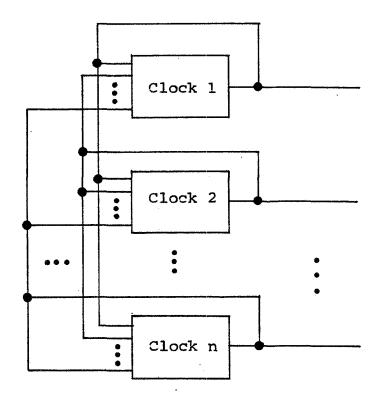

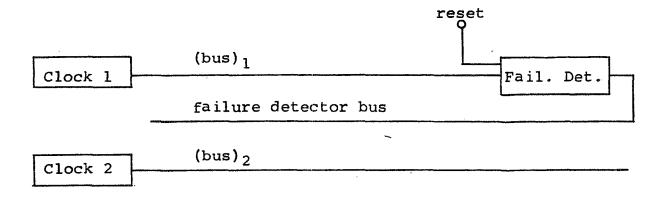

Two general design approaches come to mind: (1) use a single clock in conjunction with a single-wire bus for distribution until the occurrence of a failure in the oscillator or in the distribution, at which time another clock and its associated bus are brought into action; this principle is illustrated in Fig. 3.1; the enable circuits permit only one clock to be distributed at a time; (Enable) passes clock n if and only if failure detectors 1 through n-1 indicate failure (initially clock 1 is distributed); (2) use a group of mutually synchronized oscillators which can tolerate the required number of failures and still have several "good" outputs; see Fig. 3.2.

# 3.3 Fault-Tolerant Clocking Through Failure-Detection and Subsequent Clock Substitution

In this section, through logical development, an exploration is made of the feasibility of a clocking system which achieves fault-tolerance through failure-detection and subsequent

E<sub>i</sub>: (Enable)<sub>i</sub> FD<sub>i</sub>: (Failure Detector)<sub>i</sub>

Fig. 3.1 Fault-Tolerant Clocking through Failure-Detection and Clock Substitution

Fig. 3.2 Fault-Tolerant Clocking through Synchronization of Oscillators

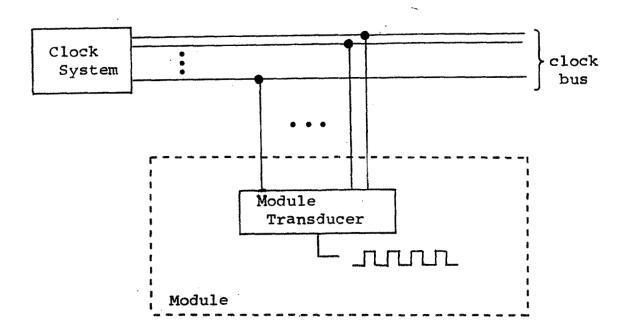

clock substitution. Consider Fig. 3.3; the clock system and the clock bus are to be designed to be fault-tolerant; neither the connection between module and bus, nor the module transducer need be fault-tolerant, as a failure there may be considered to be a failure of the associated module. The design of the module transducer and its connections to the bus, however, is an integral part of the design of the clocking system; the module transducer converts the information on the bus into a single continuous clock waveform and needs to be designed such that the outputs of all module transducers are in synchronism. It will be seen that some elements of the clocking system need to be external to the module, while others need to be associated with the module.

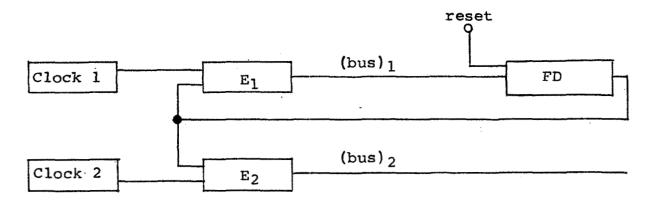

In order to simplify the feasibility study, system design for single-fault-tolerance will be explored first. Figure 3.4 is a general description of a single-fault-tolerant clock. In order to assure that each module utilizes the same clock, failure detection should be external to the module.

The most obvious difficulty in designing the failuredetection and reconfiguration scheme is maintenance of synchronization through the failure and reconfiguration process. In order to prevent the failed clock from feeding the data management system, the clock waveform must be tested for failure before it is used; but in order to detect failures in distribution, the clock waveform must be tested after distribution. it would appear that each module transducer must be designed to "hold" (delay) use of the clock waveform until it is sure that a failure has not occurred. When a failure is detected each transducer holds its output at, say, logic-level-0, until after the clock system has been reconfigured, and a "good" clock

Fig. 3.3 General Fault-Tolerant Clocking Concept

E: Enable FD: Failure Detector

Fig. 3.4 Single-Fault-Tolerant Concept

waveform is available, at which time each transducer passes the good clock waveform. The difficulty now is in assuring that synchronization is maintained through the local transducer process of: output-hold-output.

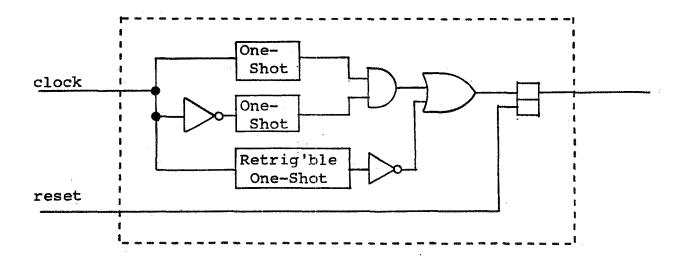

If one of the enable circuits fails such as to produce a random output, the module transducer is required to choose the "good" waveform, if single-fault-tolerance is to exist. The amount of circuitry required for the transducer to choose the "good" waveform can be reduced if the state of the failure detector is made available to the transducers (via a failure detector bus); if this is done, the enable circuits shown in Fig. 3.4 become superfluous. Figure 3.4 may be revised as illustrated in Fig. 3.5. The failure detector may be simply implemented as illustrated in Fig. 3.6. The circuit is designed to allow a tolerance on clock pulse width and separation between pulses; if the tolerance is violated the output of the failure-detector goes to, and is held at, logic-1; the reset capability is provided for initializing the clocking system. The pulse widths of the one-shot outputs determine the tolerance; it is a straightforward procedure to determine the necessary one-shot timing, given: clock frequency, duty-cycle, and allowed variations in both, as well as data concerning tolerances, of the propagation delays and one-shot pulse widths, associated with the failure-detector components. The retriggerable one-shot should have an output pulse width of approximately twice the period of the clock; it assures the detection of a failure to logic-level-0 or logic-level-1.

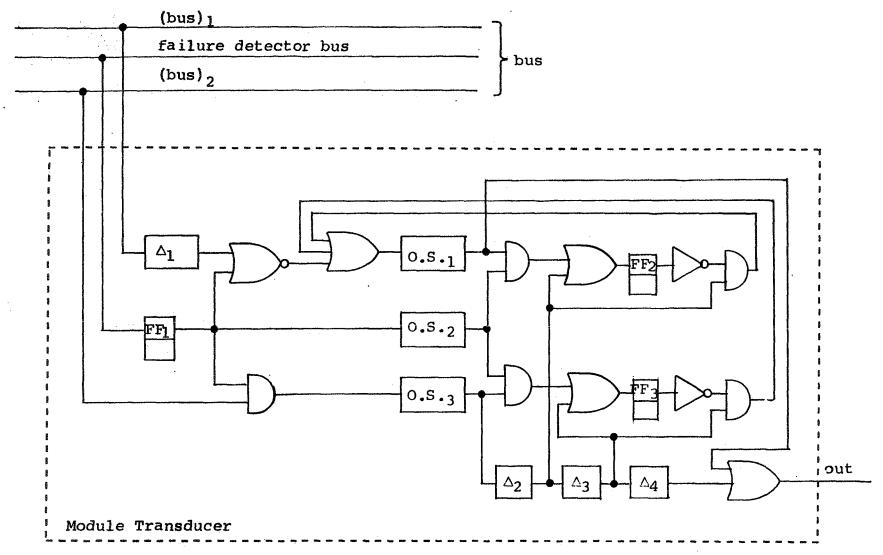

Figure 3.7 is the design of a module transducer which may be used in conjunction with the clock system of Figures 3.5 and 3.6.  $\Delta_1$  is the delay associated with each module transducer;

Fig. 3.5 Revised Single-Fault-Tolerant Concept

Fig. 3.6 Failure Detector

Fig. 3.7 Module Transducer for Single-Fault-Tolerant Clocking through Failure-Detection and Subsequent Clock Substitution

it allows the prevention of the propagation of a failed clock. In a system state prior to clock failure, the waveform of clock 1 is passed through delay,  $\Delta_1$ , and one-shot, o.s., and then to the output. If a failure is indicated,  $FF_1 \rightarrow 1$ , causing the termination of the distribution of clock 1 and the subsequent distribution of clock 2 to each module. Additional circuitry is provided in each transducer for maintenance of synchronization during and after the switching period. Slivering within the transducer in effecting the cut-off of clock 1 and the cut-in of clock 2 may, in some cases, yield an extra pulse associated with clock 1 or an extra pulse associated with clock 2; thus after the switching has taken place the total number of clock pulses supplied to each module may differ by one or two. If an "extra" pulse of clock 1 is propagated, FF<sub>2</sub> is set, and if an "extra" pulse of clock 2 is propagated, FF<sub>3</sub> is set. In those transducers in which FF, or FF, was not set during the switching process, one extra pulse for each unset flip-flop is inserted between the end of the clock 1 waveform and the beginning of the clock 2 waveform, thereby maintaining synchronism. Requirements are established for values of  $\Delta_1$ ,  $\Delta_2$ ,  $\Delta_3$ ,  $\Delta_4$ , and the pulse widths of the one-shots, as well as their tolerances; the requirements are imposed by the system parameters (e.g., clock frequency), as well as by the required method of operation.

It is believed that the module transducer shown in Fig. 3.7 is an example of a minimally complex (or nearly so) transducer required for fault-tolerant clocking through failure detection and subsequent clock substitution. The necessity of requiring such complex operations to be performed on the module level, rather than the external clock system level, has been justified in the development of this section. Because of the

module-level complexity here, it is felt that designs such as described in later sections of this thesis, are much more desirable; hence a detailed analysis of the module transducer illustrated in Fig. 3.7 is not presented.

For n-fault-tolerance, the system becomes more complicated on all levels, and, of course, it is the increased complication on the module level which is particularly undesirable. It is concluded that fault-tolerant clocking through failure detection and subsequent clock substitution is possible, but is extremely costly in hardware implementation.

## 3.4 The McKenna Clock

## 3.4.1 First Concept

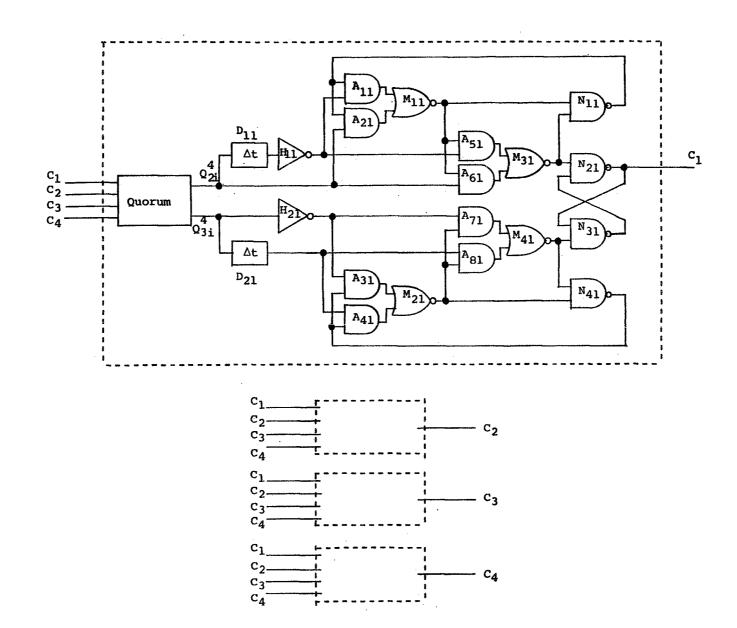

In August, 1971, William Daly and John F. McKenna, in a C.S. Draper Laboratory memo (Ref. 2), described their design of a fault-tolerant clock. Figure 3.8 illustrates the concept proposed for single-fault-tolerance. It is seen that this design conforms to the method of clocking shown in Fig. 3.2 and indeed may be described as a synchronization of oscillators. It should be noted, however, that here a single clock element, apart from the others, is not an oscillator. Rather, as shall be seen in the analysis to follow, each clock element depends on the occurrence of the transition in state of several of the clocks in order to be driven to change its own state.

The quorum function  $Q_a^n$  is defined to be 1 if at least a of the n independent variables  $C_1, C_2, \ldots, C_n$  are 1, and 0 otherwise. For example:

$Q_1^4 = C_1 + C_2 + C_3 + C_4$

Fig. 3.8 Daly-McKenna Clock

$$\begin{aligned}

\varrho_{2}^{4} &= c_{1}c_{2} + c_{1}c_{3} + c_{1}c_{4} + c_{2}c_{3} + c_{2}c_{4} + c_{3}c_{4} \\

\varrho_{3}^{4} &= c_{1}c_{2}c_{3} + c_{1}c_{2}c_{4} + c_{1}c_{3}c_{4} = c_{2}c_{3}c_{4} \\

\varrho_{4}^{4} &= c_{1}c_{2}c_{3}c_{4}

\end{aligned}$$

$Q_2^4$  and  $Q_3^4$  may each be realized through two levels of Boolean gating or through one level of threshold logic. The use of threshold logic, however, offers no advantage unless LSI threshold logic technology is to be used.

All clock lines are distributed to each synchronous module within the system. It will be demonstrated in a later part of this section that majority voting and subsequent filtering within each module is necessary to maintain system synchronization, and an adequate module transducer will be described.

The logic required to induce free-running oscillation after power-on is not shown in Fig. 3.8. For the purposes of this analysis it will be assumed that the clock elements are already oscillating in synchronism at the time of observation. Timing analyses will be made, to demonstrate system performance.

For purposes of analysis the following assumptions are made: each gate has a propagation delay equal to  $\Delta$ ; the propagation delay in forming a quorum function is  $2\Delta$ ;  $\Delta$ t is a pure delay, greater than or equal to  $8\Delta$  (in order to avoid slivering within the clock element which could yield spikes in the output,  $\Delta$ t must be greater than the propagation delay through the series of gates:  $H_{21}$ ,  $A_{31}$ ,  $M_{21}$ ,  $N_{41}$ , which is  $4\Delta$ ; however, since by most manufacturers' specifications propagation delay within a simple Boolean gate may reach to nearly twice the

typical delay time, in the worst case the delay through four gates in series may approach  $8\Delta$ .

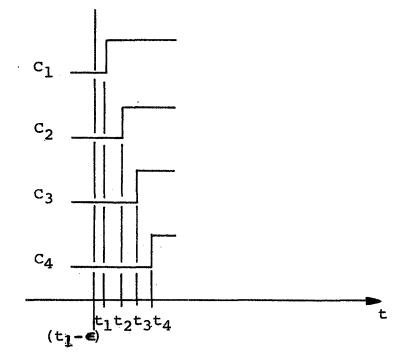

Assume that the clock elements are oscillating in synchronism. Assume that at time:  $t=t_1$ ,  $C_1$  goes to logic -1;  $t=t_2$ ,  $C_2 \rightarrow 1$ ;  $t=t_3$ ,  $C_3 \rightarrow 1$ ; and at  $t=t_4$ ,  $C_4 \rightarrow 1$  (see Fig. 3.9), where  $t_4 > t_3 > t_2 > t_1$ . Assume that at an initial time of observation,  $(t_1 - \epsilon)$ , all propagation, within each clock element, caused by the previous transition,  $C_1 \rightarrow 0$ , has ceased (this will be verified within the analysis to follow); therefore the outputs of the gates (Ref. Fig. 3.8) are as follows:

Initially:

$$C_{i} = 0$$

$Q_{2i}^{4} = 0;$   $Q_{3i}^{4} = 0$

$D_{1i} = 0;$   $D_{2i} = 0$

$H_{1i} = 1;$   $H_{2i} = 1$

$A_{1i} = 1;$   $A_{2i} = 0;$   $M_{1i} = 0$

$A_{3i} = 1;$   $A_{4i} = 0;$   $M_{2i} = 0$

$A_{5i} = 0;$   $A_{6i} = 0;$   $M_{3i} = 1$

$A_{7i} = 0;$   $A_{8i} = 0;$   $M_{4i} = 1$

$N_{1i} = 1;$   $N_{4i} = 1$

$N_{2i} = C_{i} = 0$

$N_{3i} = 1$

Given the initial state and the assumed progression of events, the timing analysis is as follows: for reference purposes all transitions are numbered.

$$C_{1} \rightarrow 1 \text{ at } t_{1} \quad (N_{21} \rightarrow 1) \tag{3.1}$$

Fig. 3.9 Assumed Synchronism

$Q_{2i}^4$  and  $Q_{3i}^4$  remain at 0

... gate  $X_{xi}$ , i = 2,3,4, remain unchanged from the initial state

$N_{31} \rightarrow 0$  at  $t_1 + \Delta$  (the validity of this statement is dependent on the nature of transition (3.1)) (3.2)

$$C_2 \rightarrow 1 \text{ at } t_2 \quad (N_{22} \rightarrow 1)$$

(3.3)

$$Q_{2i}^4 \rightarrow 1 \text{ at } t_2 + 2\Delta$$

(3.4)

$$Q_{3i}^4$$

remains at 0

$N_{32} \rightarrow 0$  at t<sub>2</sub> +  $\Delta$  (as in (3.2)) (3.5)

$$A_{2i} \rightarrow 1 \text{ at } t_2 + 3\Delta \tag{3.6}$$

$$D_{1i} \rightarrow 1 \text{ at } t_2 + 2\Delta + \Delta t$$

(3.7)

$$H_{li} \rightarrow 0 \text{ at } t_2 + 3\Delta + \Delta t \tag{3.8}$$

$$A_{1i} \rightarrow 0 \text{ at } t_2 + 4\Delta + \Delta t \tag{3.9}$$

It has already been assumed that  $\Delta t \ge 8\Delta$ , but it is still interesting to note that for  $\Delta t = 0$ , a short duration pulse might or might not be generated by  $M_{li}$ , yielding possible slivering within the clock's logic and hence unpredictable operation.

$$C_3 \rightarrow 1 \text{ at } t_3 (N_{23} \rightarrow 1)$$

(3.10)

$$N_{33} \rightarrow 0 \text{ at } t_3 + \Delta \text{ (as in (3.2))}$$

(3.11)

$$Q_{2i}^4 \text{ remains at 1}$$

$$D_{1i} \text{ remains at 1}$$

$$Q_{3i}^4 \rightarrow 1 \text{ at } t_3 + 2\Delta \qquad (3.12)$$

$$H_{2i} \rightarrow 0 \text{ at } t_3 + 3\Delta \tag{3.13}$$

$$A_{3i} \rightarrow 0 \text{ at } t_3 + 4\Delta$$

(3.14)

$$M_{2i} \rightarrow 1 \text{ at } t_3 + 5\Delta$$

(3.15)

$N_{4i} \rightarrow 0 \text{ at } t_3 + 6\Delta$  (3.16)

$$D_{2i} \rightarrow 1 \text{ at } t_3 + 2\Delta + \Delta t \tag{3.17}$$

$$A_{8i} \rightarrow 1 \text{ at } t_3 + 3\Delta + \Delta t \tag{3.18}$$

$$M_{4i} \rightarrow 0 \text{ at } t_3 + 4\Delta + \Delta t \tag{3.19}$$

$$N_{3i} \rightarrow 1 \text{ at } t_3 + 5\Delta + \Delta t$$

(3.20)

$$(N_{2i} \equiv C_i) \rightarrow 0 \text{ at } t_3 + 6\Delta + \Delta t$$

(3.21)

$$N_{4i} \rightarrow 1 \text{ at } t_3 + 5\Delta + \Delta t$$

(3.22)

$$A_{4i} \rightarrow 1 \text{ at } t_3 + 6\Delta + \Delta t \qquad (3.23)$$

$$M_{2i} \rightarrow 0 \text{ at } t_3 + 7\Delta + \Delta t$$

(3.24)

$$\mathbf{A}_{8i} \rightarrow 0 \text{ at } \mathbf{t}_{3} + 8\Delta + \Delta \mathbf{t}$$

(3.25)

$$M_{4i} \rightarrow 1 \text{ at } t_3 + 9\Delta + \Delta t$$

(3.26)

## As a result of (3.21):

$$Q_{2i}^{4} \rightarrow 0 \text{ at } t_{3}^{} + 8\Delta + \Delta t \qquad (3.27)$$

$$Q_{3i}^{4} \rightarrow 0 \text{ at } t_{3}^{} + 8\Delta + \Delta t \qquad (3.28)$$

$$A_{2i} \rightarrow 0 \text{ at } t_3 + 9\Delta + \Delta t \qquad (3.29)$$

$$M_{1i} \rightarrow 1 \text{ at } t_3 + 10\Delta + \Delta t \qquad (3.30)$$

$$N \rightarrow 0 \text{ at } t_3 + 11\Delta + \Delta t \qquad (3.31)$$

$$N_{li} \rightarrow 0 \text{ at } t_3 + 11\Delta + \Delta t \tag{3.31}$$

$$D_{1i} \rightarrow 0 \text{ at } t_3 + 8\Delta + 2\Delta t$$

(3.32)

$$H_{1i} \rightarrow 1 \text{ at } t_3 + 9\Delta + 2\Delta t \qquad (3.33)$$

$$\mathbf{A}_{5i} \rightarrow 1 \text{ at } \mathbf{t}_{3} + 10\Delta + 2\Delta \mathbf{t}$$

(3.34)

$$M_{3i} \rightarrow 0 \text{ at } t_{3} + 11\Delta + 2\Delta t \qquad (3.35)$$

$$(N_{2i} = C_{i}) \rightarrow 1 \text{ at } t_{3} + 12\Delta + 2\Delta t \qquad (3.36)$$

$$N_{3i} \rightarrow 0 \text{ at } t_{3} + 13\Delta + 2\Delta t \qquad (3.37)$$

$$N_{1i} \rightarrow 1 \text{ at } t_3 + 12\Delta + 2\Delta t \qquad (3.38)$$

$$A_{1i} \rightarrow 1 \text{ at } t_3 + 13\Delta + 2\Delta t \qquad (3.39)$$

(2 20)

$$M_{1i} \rightarrow 0 \text{ at } t_3 + 14 \triangle + 2 \triangle t$$

(3.40)

$$\mathbf{A}_{5i} \rightarrow 0 \text{ at } \mathbf{t}_{3} + 15\Delta + 2\Delta \mathbf{t}$$

(3.41)

$$\mathbf{M} \rightarrow 1 \text{ at } \mathbf{t}_{3} + 16\Delta + 2\Delta \mathbf{t}$$

(3.42)

$$M_{3i} \rightarrow 1 \text{ at } t_3 + 16\Delta + 2\Delta t \qquad (3.42)$$

$$H_{2i} \rightarrow I \text{ at } t_3 + 9\Delta + \Delta t \tag{3.43}$$

$$\mathbf{A}_{3i} \rightarrow 1 \text{ at } \mathbf{t}_{3} + 10\Delta + \Delta \mathbf{t}$$

(3.44)

$$D_{2i} \rightarrow 0 \text{ at } t_3 + 8 \Delta + 2 \Delta t$$

(3.45)

$$A_{8i} \rightarrow 0 \text{ at } t_3 + 9\Delta + 2\Delta t \tag{3.46}$$

$$A_{4i} \rightarrow 0 \text{ at } t_3 + 9\Delta + 2\Delta t$$

(3.47)

It is seen that the last transition of each gate (up to transition (3.47)) restores the gate to its initial setting. Because of transition (3.36),  $C_{i} \rightarrow 0$  at a time later:  $6\Delta + \Delta t$ ; and because of  $C_i \rightarrow 0$ ,  $C_i \rightarrow 1$  in another increment of time:  $6\Delta + \Delta t$ . The duty-cycle of C<sub>i</sub> is 50%. The period is:

$$T_{ci} = 12\Delta + 2\Delta t$$

Hence the maximum frequency is:

$$f_{max} = \frac{1}{28\Delta}$$

For medium speed TTL,  $\Delta \approx 12$  ns; therefore f  $\approx 3$  MHz.

With use of the above timing analysis, the assertion that

$\Delta t$  must be greater than  $4\Delta$ , for successful operation, may be demonstrated. Assume that  $\Delta < \Delta t < 4\Delta$ ; then transition (3.17) occurs before (3.16) and a possible timing sequence is as follows:

$$D_{2i} \rightarrow 1 \text{ at } t_3 + 2\Delta + \Delta t \qquad (3.48)$$

$$N_{4i} \rightarrow 0 \text{ at } t_3 + 6\Delta$$

(3.49)

$$A_{8i} \rightarrow 1 \text{ at } t_3 + 3\Delta + \Delta t$$

(3.50)

$$A_{4i} \rightarrow 1 \text{ at } t_3 + 3\Delta + \Delta t$$

(3.51)

$$A_{4i} \rightarrow 0 \text{ at } t_3 + 7\Delta$$

(3.52)

$$M_{2i} \rightarrow 0 \text{ at } t_3 + 4\Delta + \Delta t \tag{3.53}$$

$$M_{4i} \rightarrow 0 \text{ at } t_3 + 4\Delta + \Delta t$$

(3.54)

$$M_{2i} \rightarrow 1 \text{ at } t_3 + 8\Delta$$

(3.55)

$$N_{4i} \rightarrow 1 \text{ at } t_3 + 5\Delta + \Delta t$$

(3.56)

$$N_{3i} \rightarrow 1 \text{ at } t_3 + 5\Delta + \Delta t \tag{3.57}$$

$$A_{8i} \rightarrow 0 \text{ at } t_3 + 5\Delta + \Delta t \tag{3.58}$$

$$\mathbf{A}_{\mathbf{8i}} \rightarrow \mathbf{1} \text{ at } \mathbf{t}_{\mathbf{3}} + 9\Delta \tag{3.59}$$

$$\mathbf{A}_{4i} \rightarrow 1 \text{ at } \mathbf{t}_{3} + 6\Delta + \Delta \mathbf{t}$$

(3.60)

$$(\mathbf{N}_{21} \equiv \mathbf{C}_1) \rightarrow 0 \text{ at } \mathbf{t}_3 + 6\Delta + \Delta \mathbf{t}$$

(3.61)

$$M_{4i} \rightarrow 1 \text{ at } t_3 + 6\Delta + \Delta t$$

(3.62)

$$M_{4i} \rightarrow 0 \text{ at } t_3 + 10\Delta \tag{3.63}$$

Transitions (3.61) and (3.62) both occur at  $t_3 + 6\Delta + \Delta t$ , but if (3.62) occurs just before (3.61) the following transition may occur in some clock elements:

$$N_{3i} \rightarrow 0 \text{ at } t_3 + 7\Delta + \Delta t \tag{3.64}$$

$$(N_{2i} \equiv C_i) \rightarrow 1 \text{ at } t_3 = 8\Delta + \Delta t$$

(3.65)

So, it is seen that for  $\Delta < \Delta t < 4\Delta$ , proper operation cannot be assured.

Now assume that  $\Delta t < \Delta$ ; then as a result of transition (3.12):

$$D_{2i} \rightarrow 1 \text{ at } t_3 + 2\Delta + \Delta t$$

(3.66)

$$H_{2i} \rightarrow 0 \text{ at } t_3 + 3\Delta \tag{3.67}$$

$$A_{4i} \rightarrow 1 \text{ at } t_3 + 3\Delta + \Delta t$$

(3.68)

$$\mathbf{A}_{3i} \rightarrow 0 \text{ at } \mathbf{t}_3 + 4\Delta \tag{3.69}$$

Since (3.68) occurs before (3.69),  $M_{2i}$  will not go to 1 and therefore C<sub>i</sub> will not go to 0, yielding a non-oscillatory condition.

It has been shown, in support of the original assertion, that  $\Delta t$  must be greater than  $4\Delta$ . Also, as mentioned, in order to assure operation in the event that gate propagation delays are nearly double nominal value,  $\Delta t$  should be no less than  $8\Delta_{nom}$ .

The principle of operation is seen to be as follows: when  $Q_3^4 \rightarrow 1$ ,  $C_1 \rightarrow 0$   $6\Delta + \Delta t$  later; when  $Q_2^4 \rightarrow 0$ ,  $C_1 \rightarrow 1$   $6\Delta + \Delta t$  later. Differences amongst clock elements in the propagation of the signal triggered by the leading edge of the  $Q_3^4$  pulse or in the propagation of the signal triggered by the trailing edge of the  $Q_2^4$  pulse will cause minor time separations in occurrences of leading and trailing edges amongst clock element 1,  $Q_{21}^4 \rightarrow 1$  before  $H_{11} \rightarrow 1$ , then  $C_1$  is driven to logic-1  $5\Delta$  after  $Q_2^4 \rightarrow 1$ . Similarly, if  $Q_{31}^4 \rightarrow 0$  before  $D_{21} \rightarrow 1$ , then  $C_1$  is driven to logic-0  $6\Delta$  after  $Q_3^4 \rightarrow 0$ .

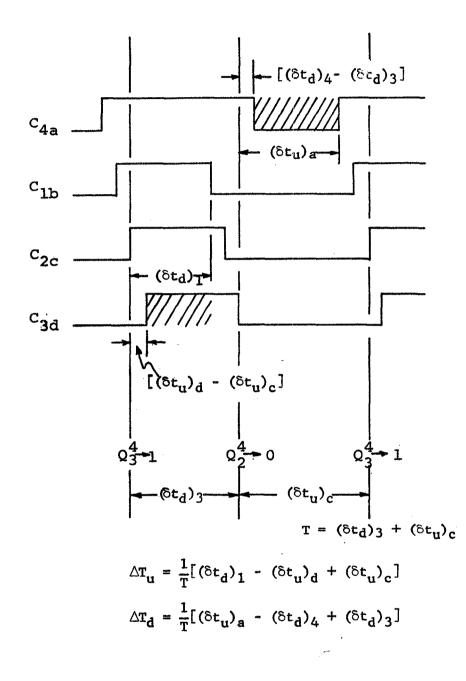

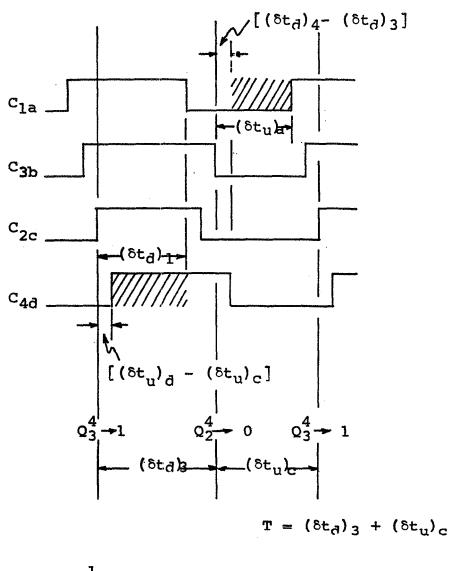

For purposes of determining the effect of differences in propagation delays on clock performance consider the following definitions and analysis: first, assume that the delays of each clock element are within tolerances such that the "set-to-agree"  $(Q_2^4 \rightarrow 1 \text{ drives } C_1 \rightarrow 1 \text{ or } Q_3^4 \rightarrow 0 \text{ drives } C_1 \rightarrow 0)$  function is not utilized in normal operation; now, define the time between the event  $Q_3^4 \rightarrow 1$  (here, Q refers to the conceptual quorum function, not the physical implementation) and the resulting event  $C_1 \rightarrow 0$  as  $(\delta t_d)_i$ ; define the time between the event  $Q_2^4 \rightarrow 0$  and the resulting  $C_1 \rightarrow 1$  as  $(\delta t_u)_i$ . Once the event  $Q_3^4 \rightarrow 1$  has occurred,  $Q_2^4 \rightarrow 0$  will occur  $(\delta t_d)_x$  later, where x is the clock possessing the next to the largest  $(\delta t_d)$ ; after  $Q_2^4 \rightarrow 0$  occurs,  $Q_3^4 \rightarrow 1$  will occur  $(\delta t_u)_y$  later, where y is the clock possessing the next to the largest  $(\delta t_u)$ .

Two specifications which considered together offer a significant measurement of clock performance, may be defined as follows:

$\Delta \mathbf{T}_{\mathbf{u}} \equiv \text{duty-cycle of the function } \mathbf{C}_{1} \quad \mathbf{C}_{2} \quad \mathbf{C}_{3} \quad \mathbf{C}_{4}$  $\Delta \mathbf{T}_{d} \equiv \text{duty-cycle of the function } \mathbf{\overline{C}}_{1} \quad \mathbf{\overline{C}}_{2} \quad \mathbf{\overline{C}}_{3} \quad \mathbf{\overline{C}}_{4}.$

These two specifications indicate, respectively, the size of the overlap region of the clock pulses and the size of the overlap region of the clock 0-states. If there were no differences amongst propagation delays of like elements then  $\Delta T_u$  and  $\Delta T_d$  would both be  $\frac{1}{2}$ . Following is a derivation of the relationships between  $\Delta T_u$ ,  $\Delta T_d$  and the  $(\delta t_u)$ 's,  $(\delta t_d)$ 's:

Assign numbers to the clocks such that:

$$(\delta t_d)_1 < (\delta t_d)_2 < (\delta t_d)_3 < (\delta t_d)_4$$

(3.70)

Assign letters to the clocks such that:

$$(\delta t_u)_a < (\delta t_u)_b < (\delta t_u)_c < (\delta t_u)_d$$

(3.71)

There are 4: distinct sets of the four clock outputs, yet in each case:

the period of the clock is given by:

$$\mathbf{T} = (\delta t_d)_3 + (\delta t_u)_c$$

(3.72)

and

$$\Delta T_{u} = \frac{1}{T} \left[ (\delta t_{d})_{1} - (\delta t_{u})_{d} + (\delta t_{u})_{c} \right] \qquad (3.73)$$

$$\Delta \mathbf{T}_{\mathbf{d}} = \frac{1}{\mathbf{T}} \left[ \left( \delta \mathbf{t}_{\mathbf{u}} \right)_{\mathbf{a}} - \left( \delta \mathbf{t}_{\mathbf{d}} \right)_{\mathbf{4}} + \left( \delta \mathbf{t}_{\mathbf{d}} \right)_{\mathbf{3}} \right] \qquad (3.74)$$

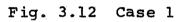

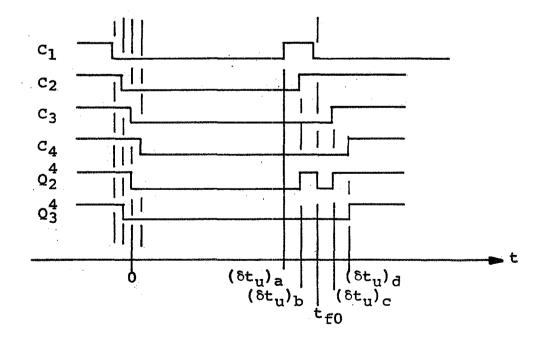

Two cases are illustrated (Figs. 3.10, 3.11) for the purpose of shedding some light on why  $\Delta T_u$  and  $\Delta T_d$  are independent of the manner of the pairings of the  $(\delta t_d)$ 's with the  $(\delta t_u)$ 's in the four clocks.

The percentage variation of the  $(\delta t_d)$ 's and the  $(\delta t_u)$ 's around some nominal value is dependent on both component specifications and component selection; testing and subsequent selection of components will yield a minimum variation. A worstcase analysis will yield a direct correlation between clock performance, as measured by  $\Delta T_u$  and  $\Delta T_d$ , and the tolerances of the  $(\delta t_d)$ 's and  $(\delta t_u)$ 's. If  $(\delta t_u)$  and  $(\delta t_d)$  fall within a range  $\begin{pmatrix} \delta t \\ nom \end{pmatrix}$  (1-x) <  $\delta t$  <  $(\delta t)_{nom}$  (1+x), then from eqns (3.72), (3.73), and (3.74):

$$[\Delta T_{u}]_{\min} = [\Delta T_{d}]_{\min} = \begin{cases} \frac{1-3x}{2}, & x < \frac{1}{3} \\ 0, & x \ge \frac{1}{3} \end{cases}$$

(3.75)

Note that due to the "set-to-agree" function it is unrealistic

Fig. 3.10 Determination of  $\Delta T_u$ and  $\Delta T_d$  - Case 1

$$\Delta T_{u} = \frac{1}{T} [(\delta t_{d})_{1} - (\delta t_{u})_{d} + (\delta t_{u})_{c}]$$

$$\Delta T_{d} = \frac{1}{T} [(\delta t_{u})_{a} - (\delta t_{d})_{4} + (\delta t_{d})_{3}]$$

Fig. 3.11 Determination of

$$\Delta T_u$$

and  $\Delta T_d$  - Case 2

to assume that  $[(\delta t_d)_3 - (\delta t_d)_2]$  or  $[(\delta t_d)_4 - (\delta t_d)_2]$  is larger than  $6\Delta$ , or that  $[(\delta t_u)_c - (\delta t_u)_b]$  or  $[(\delta t_u)_d - (\delta t_u)_b]$  is larger than  $5\Delta$ , but that the above analysis is valid because, in the worst case  $(\delta t_u)_a$  and  $(\delta t_d)_1$  may be equal to  $(\delta t)_{nom}$ . (1-x) and, the other  $(\delta t_d)$ 's and  $(\delta t_u)$ 's equal to  $(\delta t)_{nom}$ . (1+x); in this worst case the set-to-agree function is not utilized.

By nature of the design of the clock, any single failure can <u>directly</u> affect the output of only one clock element. In order to examine the post-failure operation of the circuit it is not necessary to examine the failure-modes of every logic gate; rather it is sufficient to examine the effect on clock operation of one failed clock element. The operation of the clock is examined below for three modes of failure of any one clock element: failed to logic-level-1, failed to logic-level-0, and random oscillation. Flaws in the design of the clock will be exposed, and a revised design will be recommended.

The following definitions will be useful in the analysis:  $Q_n^3 = 1$  if and only if n out of the three "good" clock elements are at logic-level-1.

Using previously defined nomenclature, assign numbers and letters to the three "good" clock elements such that:

$(\delta t_{d})_{1} < (\delta t_{d})_{2} < (\delta t_{d})_{3}$  $(\delta t_{u})_{a} < (\delta t_{u})_{b} < (\delta t_{u})_{c}$

Denote  $(\delta t_d)$  and  $(\delta t_u)$  of the failed clock element, prior to failure, as  $(\delta t_d)_f$  and  $(\delta t_u)_f$ , respectively.

If the failure is to logic-level-l and if the system does

not fail as a result of the occurrence of the failure, then the event  $Q_3^4 \rightarrow 1$  is equivalent to  $Q_2^3 \rightarrow 1$ , the event  $Q_2^4 \rightarrow 0$  is equivalent to  $Q_1^3 \rightarrow 0$ , and the principle of operation of the three good clocks remains the same: once the event  $Q_2^3 \rightarrow 1$ , has occurred,  $Q_1^3 \rightarrow 0$  will occur  $(\delta t_d)_3$  later; as a result of the event  $Q_1^3 \rightarrow 0$ ,  $Q_2^3 \rightarrow 1$  will occur  $(\delta t_u)_b$  later. Therefore the period of oscillation of each good clock is:

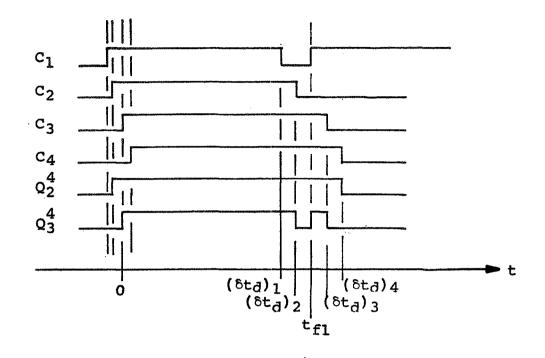

$$\mathbf{T}_{fl} = \frac{1}{(\delta t_d)_3 + (\delta t_u)_b}$$

(3.76)

where the subscript fl denotes failure to logic-level-1. Unless  $(\delta t_d)_f > (\delta t_d)_3$  and  $(\delta t_u)_f < (\delta t_u)_b$ , the period prior to failure differs from  $T_{fl}$ .

If the failure is to logic-level-0 and if the system does not fail as a result of the occurrence of the failure, then the event  $Q_3^4 \rightarrow 1$  is equivalent to  $Q_3^3 \rightarrow 1$ , the event  $Q_2^4 \rightarrow 0$  is equivalent to  $Q_2^3 \rightarrow 0$ , and: once  $Q_3^3 \rightarrow 1$  has occurred,  $Q_2^3 \rightarrow 0$  will occur  $(\delta t_d)_2$ later; as a result of the event  $Q_2^3 \rightarrow 0$ ,  $Q_3^3 \rightarrow 1$  will occur  $(\delta t_u)_c$ later. Therefore the period of oscillation of each good clock is:

$$T_{f0} = \frac{1}{(\delta t_d)_2 + (\delta t_u)_c}$$

(3.77)

where the subscript f0 denotes failure to logic-level-0. Unless  $(\delta t_d)_f < (\delta t_d)_2$  and  $(\delta t_u)_f > (\delta t_u)_c$ , the period prior to failure differs from  $T_{f0}$ .

Prior to failure if  $(\delta t_d)_f > (\delta t_d)_3$  and  $(\delta t_u)_f > (\delta t_u)_c$  then:

$$\mathbf{T} = \frac{1}{(\delta t_d)_3 + (\delta t_u)_c}$$

$$T = \frac{1}{(\delta t_d)_2 + (\delta t_u)_f}$$

$\mathbf{T} = \mathbf{T}_{f0} = \frac{1}{(\delta t_d)_2 + (\delta t_u)_c}$ If  $(\delta t_d)_f < (\delta t_d)_2$  and  $(\delta t_u)_b < (\delta t_u)_f < (\delta t_u)_c'$

If  $(\delta t_d)_f < (\delta t_d)_2$  and  $(\delta t_u)_f > (\delta t_u)_c$ ,

$$T = \frac{1}{(\delta t_d)_f + (\delta t_u)_b}$$

$$(\delta t_d)_f + (\delta t_u)_f$$

If  $(\delta t_d)_2 < (\delta t_d)_f < (\delta t_d)_3$  and  $(\delta t_u)_f < (\delta t_u)_b$

$$\mathbf{T} = \frac{1}{(\delta t_{\star})_{\star} + (\delta t_{\star})}$$

If  $(\delta t_d)_2 < (\delta t_d)_f < (\delta t_d)_3$  and  $(\delta t_u)_b < (\delta t_u)_f < (\delta t_u)_c$ ,

$$T = \frac{1}{(\delta t_d)_f + (\delta t_u)_c}$$

If  $(\delta t_d)_2 < (\delta t_d)_f < (\delta t_d)_3$  and  $(\delta t_u)_f > (\delta t_u)_c$ ,

$$T = T_{f1} = \frac{1}{(\delta t_d)_3 + (\delta t_u)_b}$$

If  $(\delta t_d)_f > (\delta t_d)_3$  and  $(\delta t_u)_f < (\delta t_u)_b$ ,

$$T = \frac{1}{(\delta t_d)_3 + (\delta t_u)_f}$$

If  $(\delta t_d)_f > (\delta t_d)_3$  and  $(\delta t_u)_b < (\delta t_u)_f < (\delta t_u)_c$  then:

If  $(\delta t_d)_f < (\delta t_d)_2$  and  $(\delta t_u)_f < (\delta t_u)_b$

$$\mathbf{T} = \frac{1}{\left(\delta \mathbf{t}_{d}\right)_{2} + \left(\delta \mathbf{t}_{u}\right)_{b}}$$

It has been shown that if the failure is to logic-level-l or logic-level-0, and if the system does not fail as a result of the occurrence of the failure, then the three good clock elements continue operation, but at a frequency determined by the new set of  $(\delta t_d)$ 's and  $(\delta t_u)$ 's of the three operating elements.

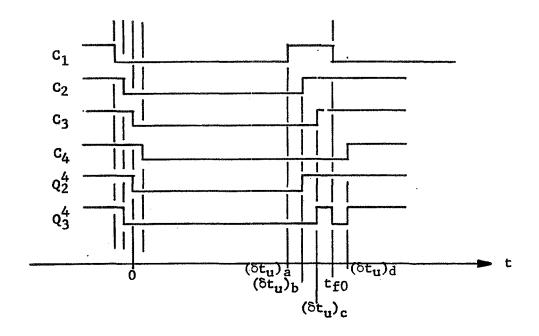

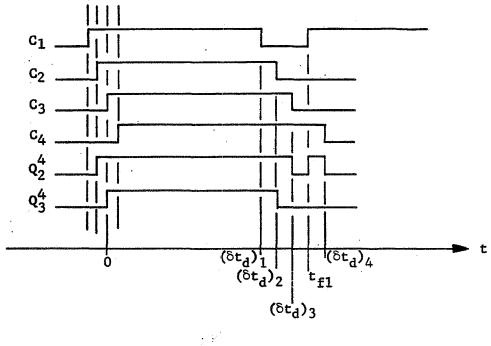

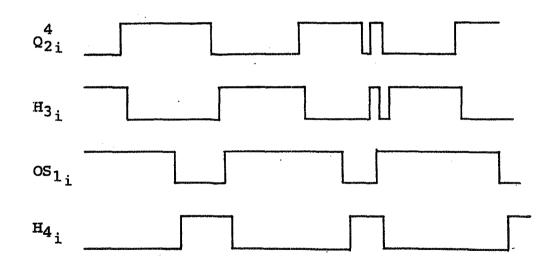

Figures 3.12 through 3.15 show how the occurrence of a failure may induce a spurious short-duration pulse in the waveform of  $Q_2^4$  or  $Q_3^4$ . In the remaining text of the thesis such a short-duration pulse will be referred to as a glitch. It is shown below that the clock will tolerate the failure-modes illustrated in Figs. 3.12 and 3.13, providing that  $(\delta t_d)_i$  and  $(\delta t_u)_i$  are within prescribed tolerances, but that the failure-mode illustrated in Fig. 3.15 may induce a glitch to appear in any clock element output. Because the undesirable transistions which occur in  $Q_2^4$  or  $Q_3^4$  may be extremely rapid, slivering may occur within the clock elements; the study which will be made in each case represents the worst-case analysis.

<u>Case 1.</u> Again, in this case and those following, reference is made to Fig. 3.8. In Fig. 3.12 C<sub>1</sub> fails to logic-1 within the region:  $(\delta t_d)_2 < t_{f1} < (\delta t_d)_3$ ; the analysis of this failuremode follows:

$$Q_{3i}^4 \rightarrow 0 \text{ at } t = (\delta t_d)_2 + 2\Delta \qquad (3.78)$$

$$Q_{3i}^{4} \rightarrow 1 \text{ at } t_{f1} + 2\Delta \qquad (3.79)$$

$$Q_{3i}^4 \to 0 \text{ at } (\delta t_d)_3 + 2\Delta$$

(3.80)

Fig. 3.13 Case 2

Fig. 3.14 Case 3

Fig. 3.15 Case 4

$$H_{2i} \rightarrow l \text{ at } (\delta t_d)_2 + 3\Delta \tag{3.81}$$

$$H_{2i} \rightarrow 0 \text{ at } t_{fl} + 3\Delta$$

(3.82)

$$H_{2i} \rightarrow 1 \text{ at } (\delta t_d)_3 + 3\Delta$$

(3.83)

$$A_{3i} \rightarrow 1 \text{ at } (\delta t_d)_2 + 4\Delta$$

(3.84)

$$A_{3i} \rightarrow 0 \text{ at } t_{fl} + 4\Delta$$

(3.85)

$$A_{3i} \rightarrow 1 \text{ at } (\delta t_d)_3 + 4\Delta$$

(3.86)

$$D_{2i} \rightarrow 0 \text{ at } (\delta t_d)_2 + 2\Delta + \Delta t$$

(3.87)

$$D_{2i} \rightarrow 1 \text{ at } t_{fl} + 2\Delta + \Delta t$$

(3.88)

$$D_{2i} \rightarrow 0 \text{ at } (\delta t_d)_3 + 2\Delta + \Delta t \qquad (3.89)$$

$$A_{4i} \rightarrow 0 \text{ at } (\delta t_d)_2 + 3\Delta + \Delta t \qquad (3.90)$$

$$A_{4i} \rightarrow 1 \text{ at } t_{fl} + 3\Delta + \Delta t \tag{3.91}$$

$$A_{4i} \rightarrow 0 \text{ at } (\delta t_d)_3 + 3\Delta + \Delta t \qquad (3.92)$$

If transition (3.90) occurs while  $A_{3i}$  is at logic-0 (see transitions (3.84) through (3.86)) then  $C_i$  is driven to logic-0 at about the same time that it is being driven to logic-1 by the propagation of the signal:  $Q_2^4 \rightarrow 0$ ; in order to avoid this situation, set:

$$[(\delta t_{d})_{2} + 3\Delta + \Delta t] - [(\delta t_{d})_{3} + 4\Delta] > 0$$

or,

$$(\delta t_d)_3 - (\delta t_d)_2 < \Delta t - \Delta$$

(3.93)

As previously stated, we may define the tolerances of (St) as follows:

$$(\delta t)_{nom.}$$

$(1-x) < (\delta t) < (\delta t)_{nom.}$   $(1+x)$  (3.94)

Combining eqns. (3.93) and (3.94) in a worst-case condition:

$$(\delta t)_{nom}$$

(1+x) -  $(\delta t)_{nom}$  (1-x) <  $\Delta t - \Delta$

or

$$x < \frac{\Delta t - \Delta}{2 \ (\delta t)_{nom}}$$

(3.95)

and since  $(\delta t)_{nom} = 6\Delta + \Delta t$ ,

$$x < \frac{\Delta t - \Delta}{2 \Delta t + 12\Delta}$$

(3.96)

If the system is to be run at maximum frequency,  $\Delta t = 8\Delta$ , and  $x < \frac{1}{4}$ . It is seen that there is a tradeoff between the tolerance of components and the frequency.

<u>Case 2.</u> In Fig. 3.13 C<sub>1</sub> fails to logic-0 within the region:  $(\delta t_u)_b < t_{f0} < (\delta t_u)_c$ ; an analysis similar to that of Case 1 yields:

$$(\delta t_{u})_{c} - (\delta t_{u})_{b} < \Delta t + \Delta$$

(3.97)

Here the requirement on x for successful operation is:

$$x < \frac{\Delta t + \Delta}{2 \Delta t + 12\Delta}$$

(3.98)

This is not as stringent a requirement as Case 1 provides.

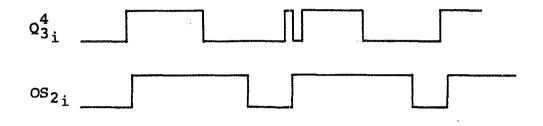

<u>Case 3.</u> In Fig. 3.14  $C_1$  fails to logic-0 within the region:  $(\delta t_u)_c < t_{f0} < (\delta t_u)_d$ . It can be shown (in a manner similar to Case 4) that  $M_{4i}$  may go to logic-0 and back to logic-1, within a time on the order of one propagation delay,  $\Delta$ , this transition occurring shortly before  $C_i$  is driven to logic-0 by the event:  $Q_3^4 \rightarrow 1$  at t=  $(\delta t_u)_d$ ; as a result a glitch may occur

at the output of  $N_{3i}$ , but not within  $C_i$ . In Case 4, however, it is shown that a glitch may occur in  $C_i$ .

<u>Case 4.</u> In Fig. 3.15 C<sub>1</sub> fails to logic-1 within the region:  $(\delta t_d)_3 < t_{f1} < (\delta t_d)_4$ . The analysis of this failure-mode follows:

As a result of  $Q_2^4 \rightarrow 0$  at  $(\delta t_d)_3$ ,  $M_{1i}$  is driven to logic-1. If when  $Q_2^4 \rightarrow 1$  at  $t_{f1}$ ,  $M_{1i}$  is at logic-1,  $A_{6i}$  may go to 1, driving  $M_{3i}$  to logic-0. The length of time that  $M_{3i}$  is at logic-0 is  $\leq (\delta t_d)_4 - t_{f1}$ ; as a result  $C_i$  may go to logic-1 at about  $3\Delta$  after it had gone to logic-0, or a pulse of duration approximately equal to  $\Delta$  may occur in  $C_i$ , or  $C_i$  may be unaffected, yielding a loss of synchronism amongst the clock elements. Also the extra pulse in  $Q_2^4$  may cause a pulse to occur in  $C_i$  just before  $C_i$  is set at logic-1.

Given that  $C_1$  fails to logic-level-1, the probability that system operation is affected as described in Case 4 is the probability the  $t_{f1}$  will occur between  $(\delta t_d)_3$  and  $(\delta t_d)_4$ , or:

$$P_{sf} = \frac{\left(\delta t_{d}\right)_{4} - \left(\delta t_{d}\right)_{3}}{\left(\delta t_{d}\right)_{3} + \left(\delta t_{u}\right)_{c}}$$

(3.99)

where the subscript sf stands for system failure. So the smaller the tolerance on  $(\delta t_d)$ , the smaller is the probability of a system failure being induced by the failure of a clock element to logic-1. It should be noted, however, that if a clock element exhibits a failure-mode of random oscillation, that, over an extended period of operation,  $P_{sf}$  approaches unity. Therefore in order to assure single-fault-tolerance, the circuit of Fig. 3.8 must be modified. Figure 3.16 is the suggested redesign of a clock element. The additional circuitry increases the values

Fig. 3.16 Revised Daly-McKenna Clock

of  $(\delta t_d)_{nom}$  and  $(\delta t_u)_{nom}$ , as follows:

$$(\delta t_u)_{nom} = 9\Delta + \Delta t \qquad (3.100)$$

$$(\delta t_d)_{nom} = 7\Delta + \Delta t$$

(3.101)

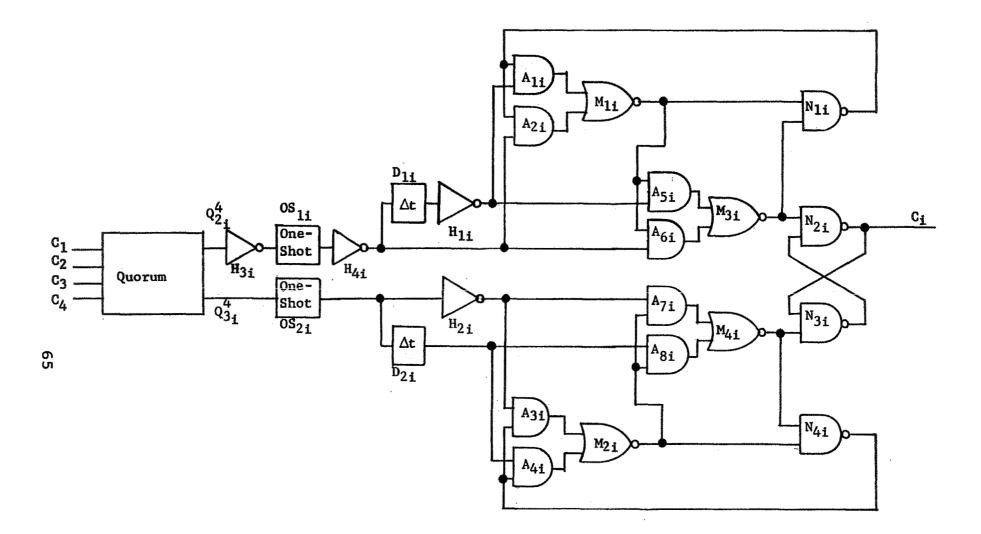

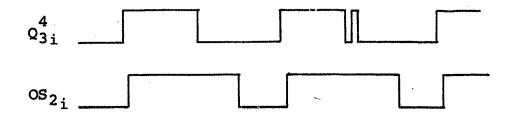

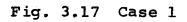

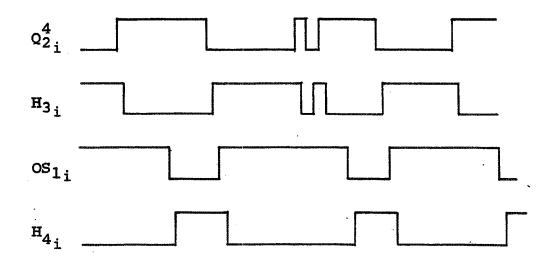

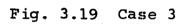

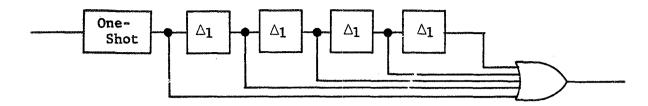

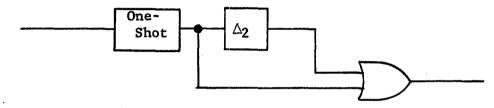

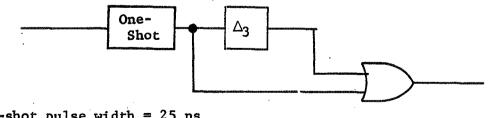

thereby decreasing the duty-cycle slightly. The values of the necessary one-shot pulse widths are dependent on the desired operating frequency of the system (and therefore are dependent on the value of  $\Delta t$ ). Figures 3.17 through 3.20 illustrate how the additional circuitry filters out the extraneous pulses of  $Q_{2i}^4$  or  $Q_{3i}^4$ ; the pulse-width of  $OS_{1i}$  is  $[(\delta t_u)_{nom} + \frac{1}{2}(\delta t_d)_{nom}]$ , and the pulse-width of  $OS_{2i}$  is  $[(\delta t_d)_{nom} + \frac{1}{2}(\delta t_u)_{nom}]$ .

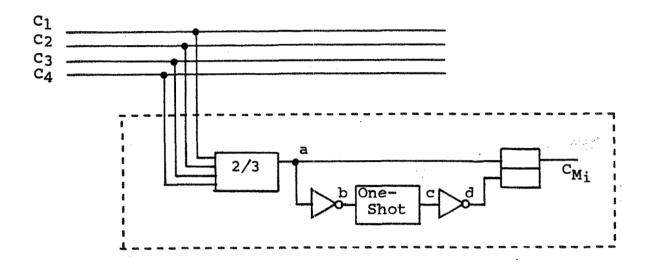

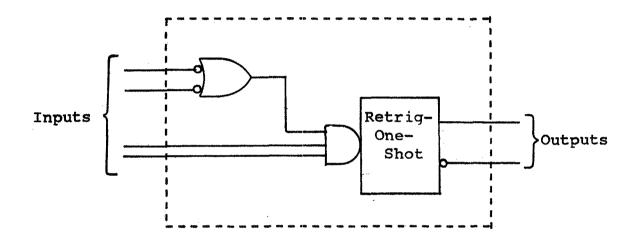

As stated earlier all clock lines are distributed to each synchronous module in the computing system. If the module transducer were simply a two out of three voter, the occurrence of a failure could cause a glitch in the output of the transducer. The subsequent slivering which may occur could destroy the synchronism of the system. Therefore the module transducer must filter out the extraneous pulses. Figure 3.21 is the design of a module transducer which may be used in conjunction with the Revised Daly-McKenna Clock. The pulse width of the one-shot is:  $[(\delta t_u)_{nom} + \frac{1}{2} (\delta t_d)_{nom}]$ . Figure 3.22 illustrates the operation of the module transducer. Note that although the design of the single-fault-tolerant clock requires four clock elements, only three need to be examined to extract a reliable clock. For the sake of uniformity of presentation it has been assumed that all clock lines are distributed. In the event of the development of a reconfigurable voter (2/3 voting with replacement), the implementation of such in place of the simple majority voter in each

Fig. 3.18 Case 2

Fig. 3.20 Case 4

Fig. 3.22 Module Transducer Operation

module transducer could increase the reliability of the clocking system.

For n-fault-tolerance, the number of required clock elements is 3n + 1, as demonstrated by Daly and McKenna. Within the module transducer, the voter increases in complexity but the remainder of the circuitry remains the same. On the clock system level the Daly-McKenna Clock is more costly than the method of clocking examined in Section 3.3, but on the module level it is much less costly.

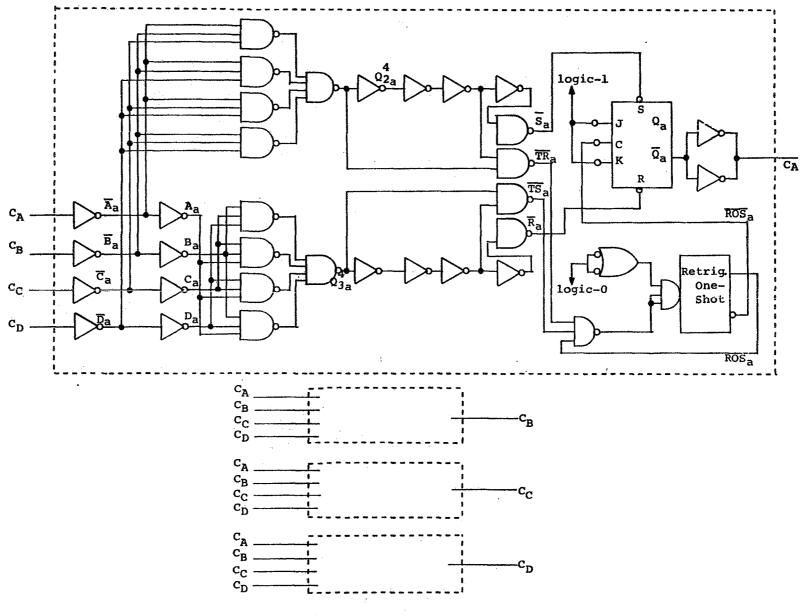

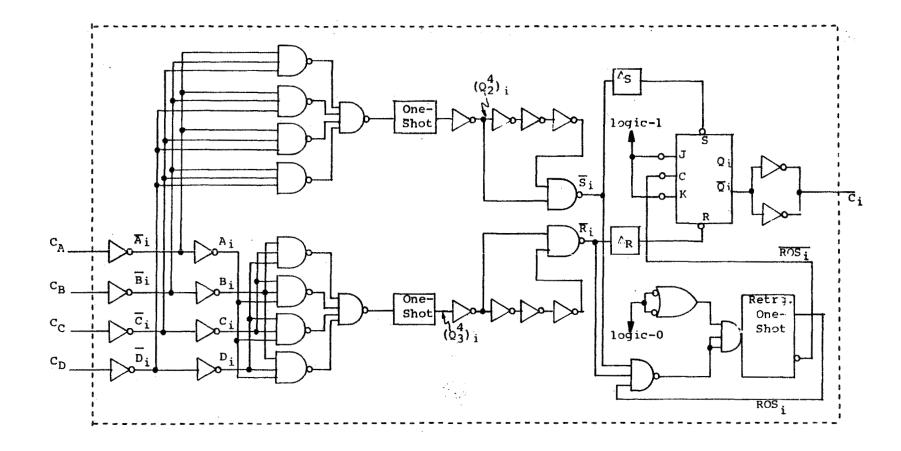

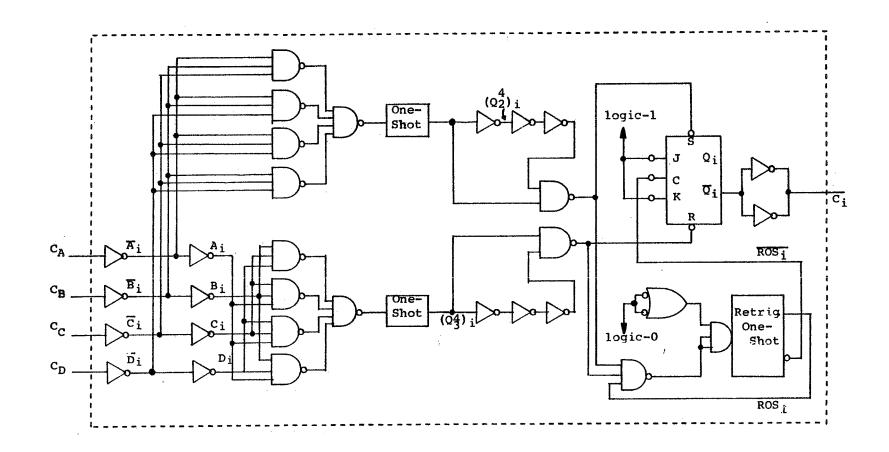

## 3.4.2 Current Concept

In October, 1971, McKenna designed a single-fault-tolerant clock for use in the prototype fault-tolerant multiprocessor (CERBERUS) currently being built at the C.S. Draper Laboratory. The design is shown in Fig. 3.23. The clock has been built, with medium speed TTL technology, and has been demonstrated to survive the imposition of single faults. The frequency of the clock now in existence is about 0.7 MHz.

The operating principles of this clock are similar to those of the first concept. It should be noted that here, each clock element will oscillate at its own chosen frequency if separated from the others. When the system is interconnected, however, each element will conform to one common frequency. As will be demonstrated, the system behaves as follows:  $C_i$ , after a short delay, is set to logic-1 by the occurrence of  $Q_2^4 \rightarrow 1$ , or after a much longer delay, by  $Q_2^4 \rightarrow 0$ ;  $C_i$  is reset to logic-0, after a short delay, by  $Q_3^4 \rightarrow 0$ , or after a much longer delay, by  $Q_3^4 \rightarrow 1$ .

Fig. 3.23 McKenna Clock

The clock is self-starting; remember that the first concept (Fig. 3.8) requires additional logic to induce freerunning oscillation. Some explanation of the clock element structure is called for: the pair of parallel inverters at the  $\overline{Q}$  output of the J-K flip-flop are there to increase the fan-out capability; similarly the eight inverters at the input of each clock element serve to overcome fan-out limitations; as can be seen,  $(Q_2^4)_i$  and  $(Q_3^4)_i$  are each implemented through four levels of gating; the strings of inverters, to which  $(Q_2^4)_i$  and  $(Q_3^4)_i$  are applied, serve to time certain key signals; and the peculiar configuration of the region around the retriggerable-one-shot (see Fig. 3.24) is the internal configuration of the circuit element used.

As in the first concept, all clock lines are distributed to each synchronous module within the system. Simple two-out-of-three majority voting within the module is <u>not</u> sufficient, but, as before, the module transducer illustrated in Fig. 3.21 may be used.

For purposes of analysis of the circuit, the following simplifying assumptions are made:

(1) An element's propagation delay is the same for a

Fig. 3.24 Retriggerable One-Shot used in McKenna Clock

logic-level-l to 0 transition as for a 0-to-l

transition,

- (2) the delay associated with any inverter or NAND gate is equal to  $\Delta$ ,

- (3) the delay associated with a transition caused by clocking the J-K flip-flop is  $2\Delta$ ,

- (4) the delay associated with a transition caused by an applied zero to the SET or RESET input of the J-K flip-flop is  $3\Delta$ ,

- (5) the one-shot triggers when its input AND gate experiences a transition from logic-level-0 to 1; the delay between the input of the AND gate and the output of the one-shot is 2Δ; after the last triggering input to the AND gate, the one-shot will go to logic-level-0 at a time Δt later.

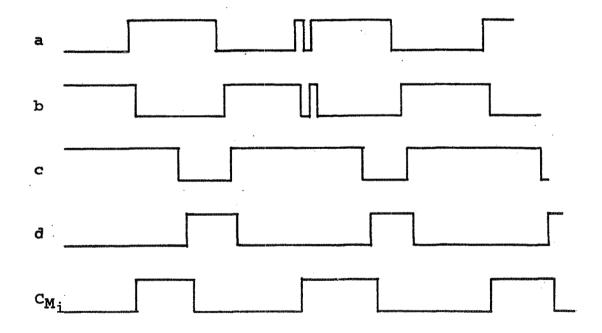

For now, assume that the clock elements are oscillating in synchronism; the clock's self-starting capability may be examined separately. As in the manner of the analysis of the first concept, assume that at time t=t<sub>A</sub>,  $C_A \rightarrow 1$ ; t=t<sub>B</sub>,  $C_B \rightarrow 1$ ; t=t<sub>C</sub>,  $C_C \rightarrow 1$ ; t=t<sub>D</sub>,  $C_D \rightarrow 1$ , where t<sub>D</sub>>t<sub>C</sub>>t<sub>B</sub>>t<sub>A</sub>. Assume that at an initial time of observation,  $(t_A - \epsilon)$ , all propagation, within each clock element, caused by the previous transition,  $C_i \rightarrow 0$ , has ceased; then:

Initially:

$$C_i = 0$$

$(Q_2^4)_i = 0; (Q_3^4)_i = 0$

$\overline{S}_i = 1; \quad \overline{R}_i = 1$

$\overline{TR}_i = 1; \quad \overline{TS}_i = 1$

# ROS, is indeterminable from a static analysis.

Given the initial state and the assumed progression of events, the timing analysis is as follows:

$$C_{A} \rightarrow l at t = t_{A}$$

(3.102)

$$C_B \rightarrow 1 \text{ at } t_B$$

(3.103)

$$(Q_2^4)_i \rightarrow 1 \text{ at } t_B + 4\Delta$$

(3.104)

$$s_i \rightarrow 0 \text{ at } t_B + 5\Delta$$

(3.105)

$$s_i \rightarrow 1 \text{ at } t_B + 8\Delta$$

(3.106)

$$C_{C} \rightarrow 1 \text{ at } t_{C}$$

(3.107)

where,  $t_B < t_C < t_B + 9\Delta$  $C_D \rightarrow 1 \text{ at } t_D$  (3.108)

where,

$$t_{C} < t_{D} < t_{B} + 9\Delta$$

$(Q_{3}^{4})_{i} \rightarrow 1 \text{ at } t_{C} + 4\Delta$  (3.109)

$$TS_i \rightarrow 0 \text{ at } t_C + 5\Delta$$

(3.110)

$$\overline{TS}_{i} \rightarrow 1 \text{ at } t_{C} + 8\Delta$$

(3.111)

$ROS_i$  is triggered either at  $t = t_c + 6\Delta$  or within  $t_c + 3\Delta < t < t_c + 6\Delta$  by its own expiration  $(ROS_i \rightarrow 0)$ ; therefore  $ROS_i$ , i = A,B,C, is triggered at  $t = t_c + 6\Delta$ ;  $ROS_D$  is triggered within  $t_c + 3\Delta < t < t_c + 6\Delta$

$$ROS_{D} \rightarrow 0 \text{ within } t_{C} + 3\Delta + \Delta t < t < t_{C} + 6\Delta + \Delta t \qquad (3.112)$$

$$ROS_{A,B,C} \rightarrow 0 \text{ at } t_{C} + 6\Delta + \Delta t \qquad (3.113)$$

$$C_{D} \rightarrow 0$$

within  $t_{C} + 6\Delta + \Delta t < t < t_{C} + 9\Delta + \Delta t$

(3.114)

$$C_{A,B,C} \rightarrow 0 \text{ at } t_{C} + 9\Delta + \Delta t \qquad (3.115)$$

ROS<sub>D</sub> is triggered within  $t_c + 4\Delta + \Delta t < t < t_c + 7\Delta + \Delta t$ , and ROS<sub>i</sub>, i = A,B,C, is triggered at t =  $t_c + 7\Delta + \Delta t$ .

$$(Q_2^4)_i \rightarrow 0 \text{ at } t_c + 1.3\Delta + \Delta t$$

(3.116)

$$(Q_3^4)_i \rightarrow 0 \text{ at } t_c + 13\Delta + \Delta t$$

(3.117)

$$\overline{\mathrm{TR}}_{i} \rightarrow 0 \text{ at } t_{C} + 13\Delta + \Delta t \qquad (3.118)$$

$$\overline{\mathrm{TR}}_{i} \rightarrow 1 \text{ at } t_{C} + 16\Delta + \Delta t \qquad (3.119)$$

$$\overline{R}_{i} \rightarrow 0 \text{ at } t_{C} + 15\Delta + \Delta t \qquad (3.120)$$

$$\overline{R}_{i} \rightarrow 1 \text{ at } t_{C} + 1.8 \Delta + \Delta t$$

(3.121)

ROS<sub>i</sub> is triggered at  $t_{C} + 14\Delta + \Delta t$ .

.

$$\operatorname{ROS}_{i} \to 0 \text{ at } t_{C} + 14\Delta + 2\Delta t \tag{3.122}$$

$$c_i \rightarrow 1 \text{ at } t_0 \equiv t_C + 17\Delta + 2\Delta t$$

(3.123)

$$(Q_2^4)_i \rightarrow 1 \text{ at } t_0 + 4\Delta \qquad (3.124)$$

$$(Q_3^4)_i \rightarrow 1 \text{ at } t_0 + 4\Delta$$

(3.125)

$$\overline{TS}_{i} \rightarrow 0 \text{ at } t_{0} + 5\Delta \qquad (3.126)$$

$$\overline{TS}_{i} \rightarrow latt_{0} + 8\Delta \qquad (3.127)$$

ROS<sub>i</sub> is triggered at  $t_0 + 6\Delta$ .

$$\operatorname{ROS}_{i} \to 0 \text{ at } t_{0} + 6\Delta + \Delta t \tag{3.128}$$

$$c_{i} \rightarrow 0 \text{ at } t_{0} + 9\Delta + \Delta t$$

(3.129)

$$(Q_{2}^{4})_{i} \rightarrow 0 \text{ at } t_{0} + 13\Delta + \Delta t \qquad (3.130)$$

$$(Q_{2}^{4})_{i} \rightarrow 0 \text{ at } t_{0} + 13\Delta + \Delta t \qquad (3.131)$$

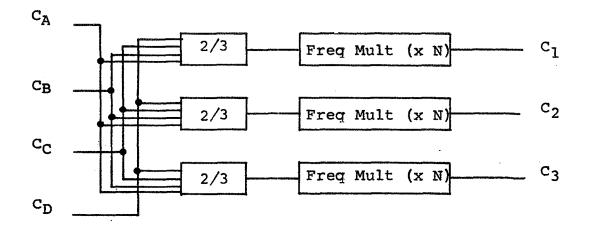

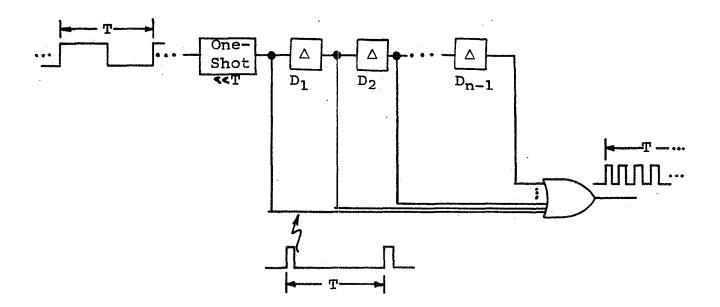

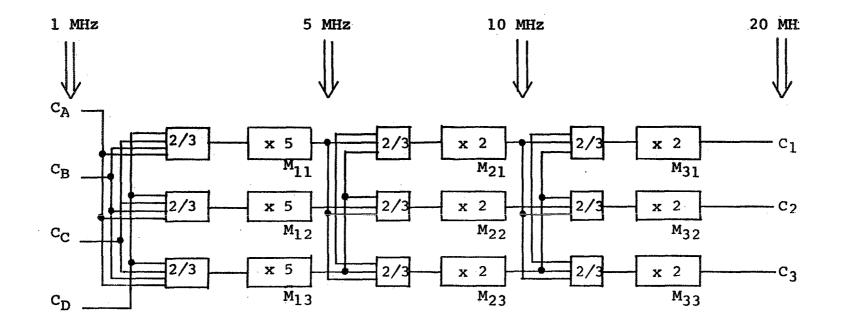

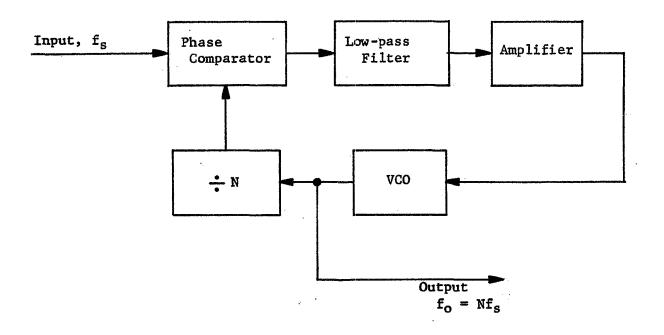

Before proceeding any further with the analysis of the current concept of the McKenna clock, a major fault in the design should be pointed out:  $Q_2^4 \rightarrow 1$  forces  $C_i \rightarrow 1$  (if this transition has not already occurred) at a time  $9\Delta$  later and  $Q_3^4 \rightarrow 0$  forces  $C_i \rightarrow 0$  at a time 10<sup>Δ</sup> later, but in the clock element in which a transition of C  $_i$  occurs as a result of  ${\tt Q}_2^4 {\rightarrow} 1$  or  $Q_3^4 \rightarrow 0$ , the retriggerable one-shot expires, thereby clocking the flip-flop and forcing an unintended change of state; the occurrence of these glitches in two clock outputs could induce a loss of synchronization within the system. A possibility for correcting the design is: remove TR and TS, retrigger the one-shot with  $\overline{S}$  or  $\overline{R}$ , and insert delays between  $\overline{S}$  and the SET input of the flip-flop and between R and the RESET input of the flip-flop, such that the one-shot cannot expire in the half-cycle in which C, has been changed by  $\overline{S}$  or  $\overline{R}$ . To serve such a purpose delay times of  $6\triangle$  are sufficient.