Effect of Interference on Delta Modulator

Encoded Video Signals

Final Report

October 1, 1976 - September 30, 1977

Goddard Space Flight Center

Greenbelt, Maryland

under

NASA GRANT NSG - 5013

Donald L. Schilling

Professor of Electrical Engineering

Principal Investigator

COMMUNICATIONS SYSTEMS LABORATORY

DEPARTMENT OF ELECTRICAL ENGINEERING

(NASA-CR-154523) EFFECT OF INTERFERENCE ON N77-85662

DELTA MODULATOR ENCODED VIDEO SIGNALS Final Report, 1 Oct. 1976 - 30 Sep. 1977 (City Coll. of the City Univ. of New York.) 18 p Unclas 00/32 52962

THE CITY COLLEGE OF THE CITY UNIVERSITY of NEW YORK

REPRODUCED BY

NATIONAL TECHNICAL

INFORMATION SERVICE

US DEPARTMENT OF COMMERCE

SPRINGFIELD, VA 22161

# Effect of Interference on Delta Modulator Encoded Video Signals

Final Report

October 1 1976 - September 30, 1977

Goddard Space Flight Center

Greenbelt, Maryland

under

NASA GRANT NSG - 5013

Donald L Schilling

Professor of Electrical Engineering

Principal Investigator

COMMUNICATIONS SYSTEMS LABORATORY

DE PARTMENT OF ELECTRICAL ENGINEERING

#### Introduction

This final report summarizes several aspects of the research sponsored by the National Aeronautics and Space Administration under NASA Grant NSG - 5013 for the period October 1, 1976 - September 30 1977

During this period of time the effect of interference on delta modulator encoded video signals was studied. This study consists of two facets. The first part concerned with selecting algorithms that could be implemented to operate in real time, the second concerned with comparing the resulting pictures when interference is present.

The first part of the study has now been completed One and two dimensional encoding algorithms have been developed and adaptive deltamodulators constructed A DPCM system has also been designed and built for the purpose of comparison

During the 1977-1978 Grant period we shall be considering the effects of interference on these systems. Following the history of cooperation that has existed between Dr. Schilling and NASA since 1964, the Communications Systems Laboratory has given NASA a video deltamodulation system. NASA will be experimenting with this unit and we are hopeful that these experiments will enhance our knowledge of the effect of real interferers on deltamodulation systems.

# I. An All Digital Adaptive Delta Modulator

#### Introduction

The development of an adaptive delta modulator capable of encoding a television picture has been completed. The delta modulator encoder accepts a 4MHz black and white composite television signal, or NASA's field sequential color television signal, and encodes it into a binary signal at a rate of up to 20 Mb/s. The output bit rate is determined by the user. Useable pictures can be obtained with bit rates between 8 and 20 Mb/s. The higher the rate the better the picture quality.

The digital signal is converted back into analog form by a delta modulator receiver. The receiver requires a bit synchronizer to provide "bit timing" "Word timing" as used in PCM is not necessary with the adaptive delta modulator.

No special circuits are required to provide for horizontal and vertical syncronization of the TV monitor at the receiver. The composite video signal that entered the delta modulator encoder will emerge from the delta modulator receiver with its horizontal and vertical sync pulses intact. Thus the TV monitor will obtain its syncronization from the composite video signal emerging from the delta modulator decoder.

#### Theory of Operation

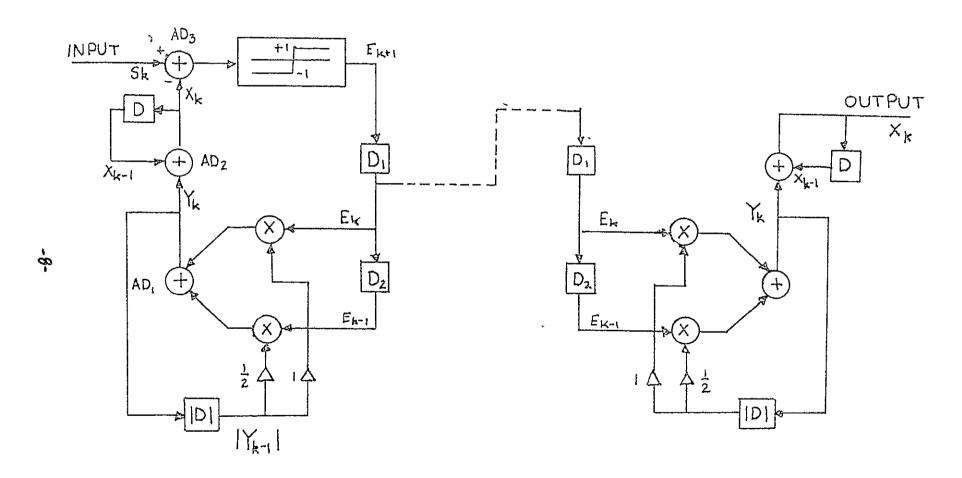

The delta modulator used to digitize the television pictures is shown in block diagram form in Fig. 1. The following is an explanation of the delta modulator algorithm. First, the video signal, S(k), is compared to  $X_k$ . This yields the output of the encoder,  $E_k$ , where

$$E_{k+1} = sgn \left(-S_k - Y_k\right) \tag{1}$$

$X_k$ , is the transmitter estimage, and is obtained using the recursive equation

$$X_{k} = 98 X_{k-1} + Y_{k}$$

(2)

$\boldsymbol{Y}_k$  , is the step size and is generated using the algorithm

$$Y_{k-1} | (E_{k} + 5E_{k-1}); | Y_{k-1} | \ge 2Y_{min}$$

$$Y_{k} = 2Y_{min} E_{k}; | Y_{k-1} | \le 2Y_{min}$$

$$Y_{max}; | Y_{k} | > Y_{max}$$

(3)

where Y is 1/129 of the peak-to-peak video signal and Y is 1/8 of the peak-to-peak video signal.

The delta modulator decoder is just the feedback loop of the encoder. The decoder reconstructs the estimate,  $X_k$ , from the  $E_k$  pulse train and converts  $X_k$  to an analog signal S(t). The quality of the received picture as compared to that of the transmitted picture depends upon how closely S(t) approximates the original signal, S(t)

#### Implementation of the Delta Modulator

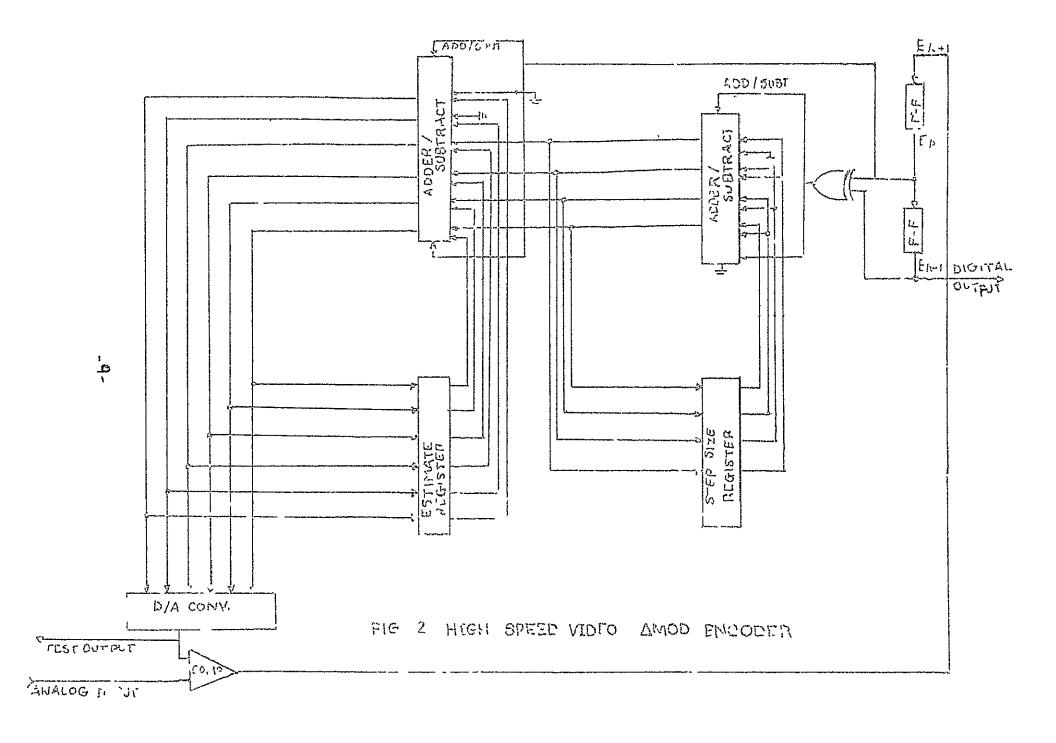

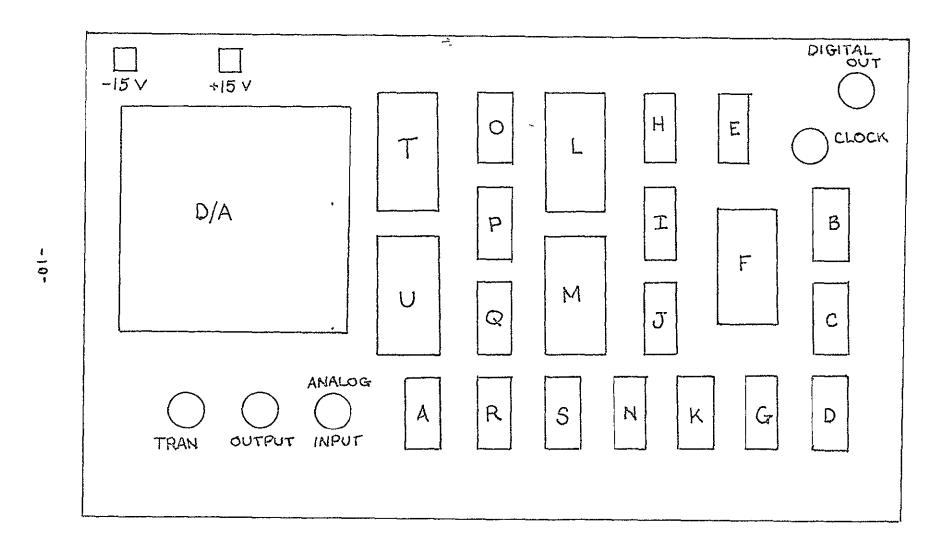

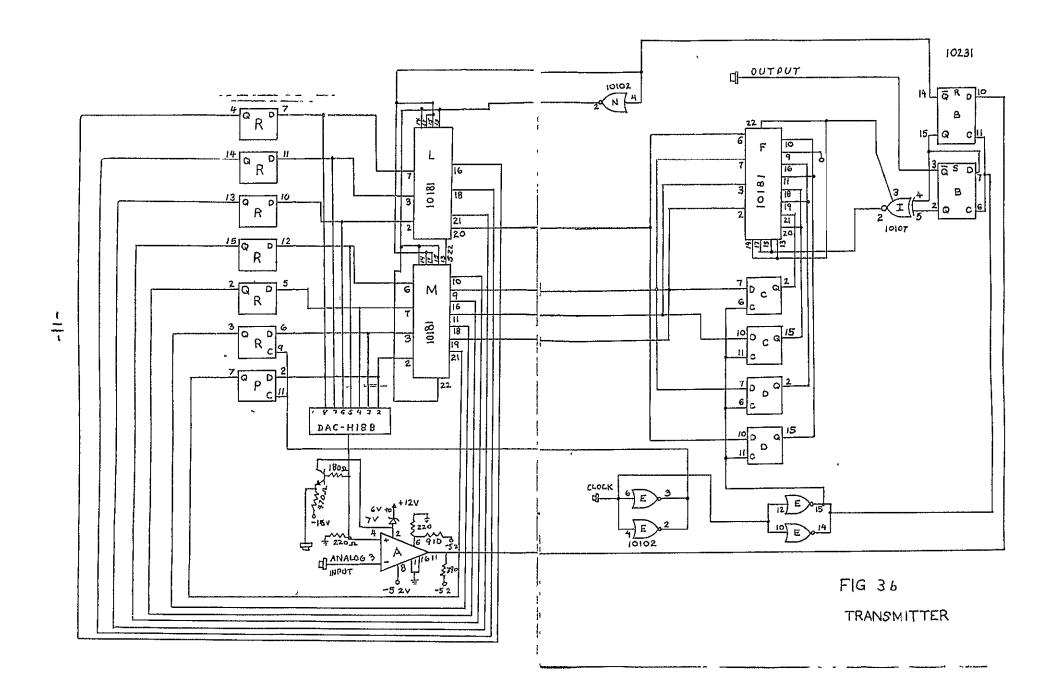

The implementation block diagram is shown in Fig. 2. The two flip-flops on the top of the diagram store  $E_k$  and  $E_{k-1}$ . The upper adder/subracter register, multiplexer and "OR" gates implement Eq. 3, the step size equation. The other adder/subtracters and registers are used to generate Eq. 2, and the D/A converter and comparator implement Eq. 1. The complete circuit schematic for the delta modulator is shown in Fig. 3. It was constructed employing ECL integrated circuits one D/A converter and a high speed comparator. It was built on a single board 8" by 6" and dissipates 7 watts of power.

## Instructions for Using the Delta Modulator

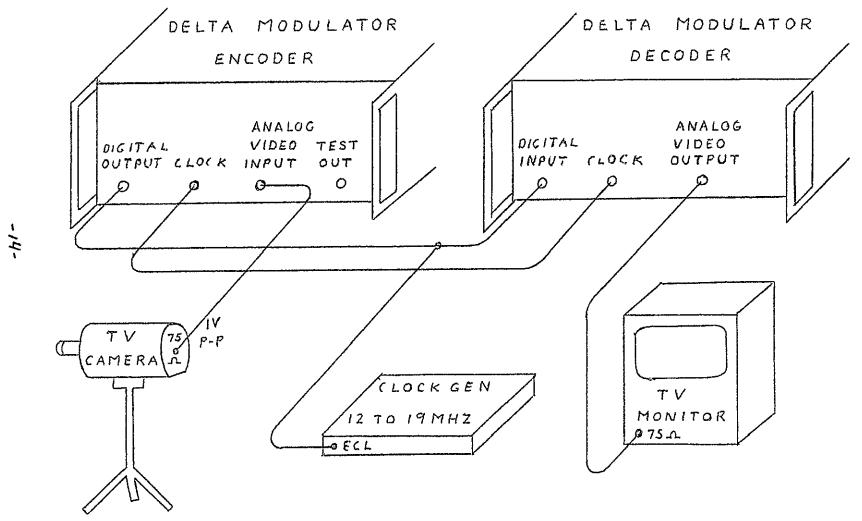

A typical test set-up using the delta modulator encoder and decoder is shown in Fig 5.

The Encoder has four BNC connectors on its front panel The function and electrical characteristics of each connector is listed below:

- (1) Digital Output

- a ECL compatible voltage levels

- b Designed to drive 50 Ω tied to -1 3V

- (2) Clock Input

- a 8 to 19 MHz

- b ECL compatible voltage levels (-0 9V to -1.7V),

- c The input impedance is 50 Ω tied to -1 3V.

- (3) Analog Video Input

- a 1 volt peak-to-peak composite video from TV camera

- b  $75 \Omega$  input impedance tield to ground,

- (4) Analog Video Output

- a 1 volt peak-to-peak composite video from the feedback loop of the encoder. It is used to monitor the operation of the encoder.

The decoder has three BNC connectors on its front panel. The function and electrical characteristics of each connector is listed below-

- (1) Digital Input

- a ECL compatible voltage levels

- b. The input impedance is  $50 \Omega$  tied to -1 3V.

- (2) Clock Input

- a 12 to 20 MHz phase locked to incoming digital data

- b ECL compatible voltage levels (-. 9V to -1 7V)

- c. The input impedance is 50  $\Omega$  tied to -1 3V.

- (3) Analog Video Output

- a. 1 volt peak-to-peak composite video signal

- b Bandlimited to 4MHz by a four pole Butterworth filter

- c. Must be terminated to 75  $\Omega$  to ground.

# II Real Time Two-Dimensional Intraframe Delta Modulator

A two-dimensional intraframe delta modulator which operates in real time has been built. The algorithm is described in great detail in the last semi-annual report and will be appearing in the November issue of the "IEEE Transactions on Communications" in a paper entitled "Adaptive Delta Modulation Systems for Video Encoding"

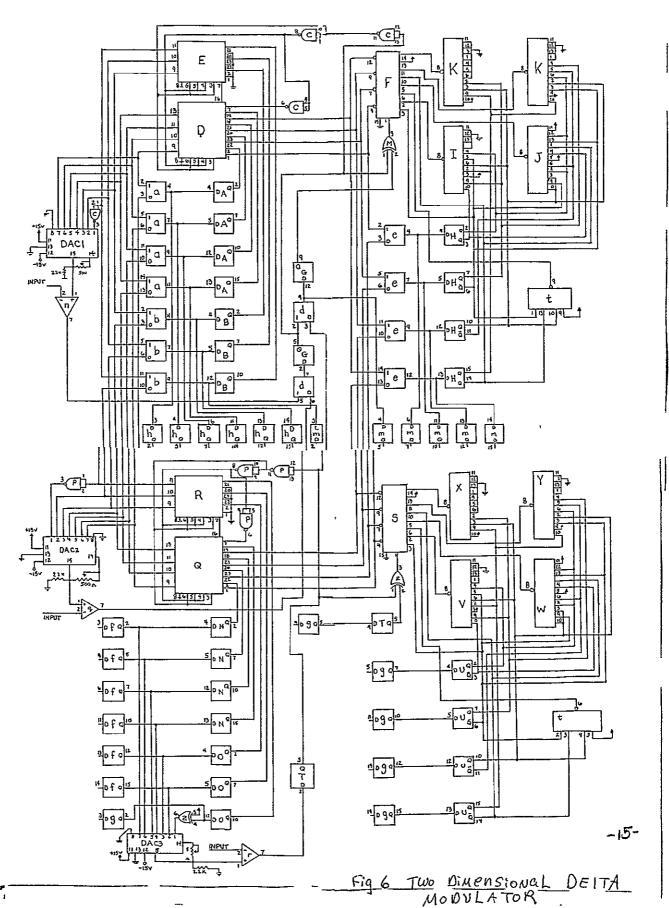

The two-dimensional delta modulator consists of two delta modulators; one that encodes vertically and one that encodes horizontally. At each pixel, decision circuitry compares the estimate from the horizontal and vertical encoders with the value of the pixel to be encoded. The estimate from the horizontal encoder is one pixel to the right of the pixel to be encoded while the vertical estimate is one pixel above the estimate to be encoded. If the vertical estimate is closer in value to the pixel to be encoded, than the horizontal estimate, then the pixel will be encoded from the vertical delta modulator. If the reverse were true then the horizontal delta modulator would be used to encode the pixel,

This encoder requires 2 bits to be transmitted each time the input signal is sampled and therefore operates at the rate of 2 bits/pixel. The second bit is used to signal the receiver as to whether to encode in the horizontal direction or in the vertical direction

The hardware implementation of the delta modulator required about £0 IC's. Twelve of the IC's were required to store a line of video while the rest comprised the horizontal and vertical delta modulators—and the decision circuitry. The circuit schematic, (not including the memory) is shown in Fig. 6. This device is three times as complex as the one dimensional delta modulator.

Even though the two dimensional delta modulator is far more complex than the one dimensional delta modulator we have found both delta modulators to be subjectively equivalent in picture quality at 16 Mb/s. This result contradicts our earlier computer simulations which were presented in the paper "Adaptive Delta Modulation Systems for Video Encoding". The computer simulations suggested that the two dimensional delta modulator would be much better than the one dimensional delta modulator because it lacked edge "bu syness". The two-dimensional delta modulator, however, had edge busyness in the temporal domain A single frame "looked good" but each frame, even from a scene that was not changing, was encoded slightly differently. As each frame was flashed on the screen at a rate of 30 times per second, the differences between frames appeared as edge busyness. The busyness was most pronounced on diagonal lines.

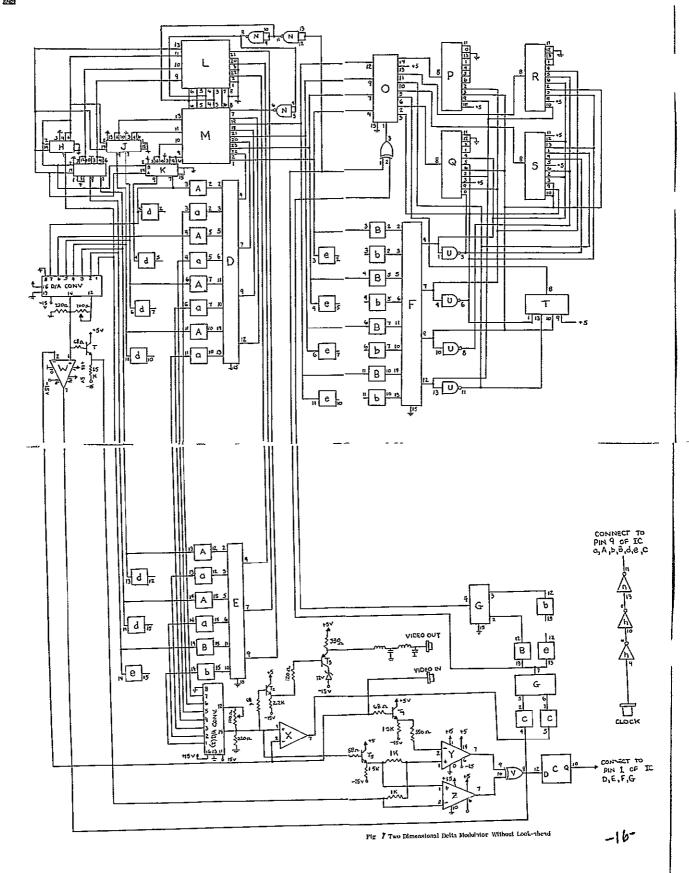

A somewhat simplified implementation of the delta modulator is shown in Fig 7. We think that this delta modulator may find application in slow-scan TV where only a single frame of video is transmitted. Since only one frame is sent the temporal edge busyness will disappear. This delta modulator is currently under construction. Its circuit schematics are shown in Fig. 7.

## III. Papers Published

"Adaptive Delta Modulation Systems for Video Encoding", IEEE Trans. on Comm., November 1977, pp. 1302-1314

"Techniques for Correcting Transmission Errors in Video Adaptive

Delta Modulation Channels, IEEE Trans on Comm, Sept. 1976, pp. 1064-1070

## IV. Papers Presented

"An All Digital Technique for ADM to PCM Conversion" NTC-76

"Two Dimensional Delta Modulator for Picture Encoding" I. S. I. T-76

"SNR Analysis on the SONG ADM for a Sinusoidal Input", I. S. I.  $\tau-76$

### V. Doctoral Student Graduated

Joseph LoCicero, Dissertation: Arithmetic Processing and Digital Conversion of ADM Encoded Signals - 1977

FIG I DIGITAL ADAPTIVE DELTA MODULATOR

1

FIG 30 ONE DIMENSIONAL DELTA MOD TRANSMITTER

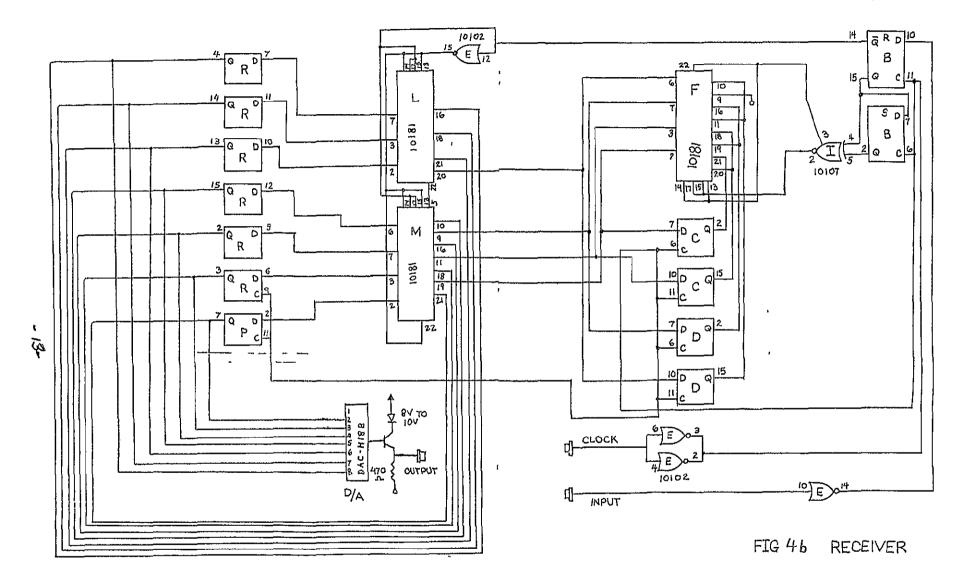

FIG 4a ONE DIMENSIONAL DELTA MOD RECEIVER

FIG. 5 TEST SETUP FOR DELTAMODULATOR

# THE CITY COLLEGE of THE CITY UNIVERSITY of NEW YORK

Convent Avenue at 138th Street, New York, New York 10031

Telephone (212) 281-0470, (212) 368-1444

The City College Research Foundation

The City College Office—Research Foundation of The City University of New York

This report was prepared as an account of Government sponsored work. Neither the United States, nor the Commission, nor any person acting on behalf of the Commission

- A. Makes any warranty or representation, expressed or implied, with respect to the accuracy, completeness, or usefulness of the information contained in this report, or that the use of any information, apparatus, method, or process disclosed in this report may not infringe privately owned rights, or

- B. Assumes any liabilities with respect to the use of, or for damages resulting from the use of any information, apparatus, method, or process disclosed in this report.

As used in the above, "person acting on behalf of the Commission" includes any employee or contractor of the Commission, or employee of such contractor, to the extent that such employee or contractor of the Commission, or employee of such contractor prepares, disseminates, or provides access to, any information pursuant to his employment or contract with the Commission, or his employment with such contractor.

Printed in USA.

Available from the Office of Technical Services

U. S. Department of Commerce

Washington 25, D. C.

Chemistry - Separation Processes for Plutonium and Uranium

AEC Research and Development Report

DECOMPOSITION OF THE TRIBUTYL PHOSPHATE - NITRATE COMPLEXES

bу

G S. Nichols

Separations Engineering Division

November 1960

E. I du Pont de Nemours & Co. Savannah River Laboratory Aiken, South Carolina