(NASA-CR-155613) SILICON ON CERANIC

PROCESS. SILICON SHEET GROWTE DEVELOPMENT

FOR THE LARGE-AREA SILICON SHEET TASK OF THE LACE AND ME AU Unclas

Report, 17 (Honeywell, Inc., Eloomington, G3/44 04173

ERDA/JPL 954356-77/3 Distribution Category UC-63

### SILICON ON CERAMIC PROCESS

Silicon Sheet Growth Development for the Large-Area Silicon Sheet Task of the Low-Cost Silicon Solar Array Project

Annual Report No. 2

by

J. D. Zook, J. D. Heaps

R. B. Maciolek, B. Koepke,

C. D. Butter and S. B. Schuldt

Period Covered: 9/17/76 - 9/19/77

Published Sept. 30, 1977

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, under NASA Contract NAS7-100 for the U.S. Energy Research and Development Administration, Division of Solar Energy.

The JPL Low-Cost Silicon Solar Array Project is funded by ERDA and forms part of the ERDA Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays.

This report contains information prepared by HONEYWELL under JPL subcontract. Its content is not necessarily endorsed by the Jet Propulsion Laboratory, California Institute of Technology, National Aeronautics and Space Administration or the U.S. Energy Research and Development Administration, Division of Solar Energy.

# SILICON ON CERAMIC PROCESS

Silicon Sheet Growth Development for the Large-Area Silicon Sheet Task of the Low-Cost Silicon Solar Array Project

Annual Report No. 2

by

J. D. Zook, J. D. Heaps

R. B. Maciolek, B. Koepke,

C. D. Butter and S. B. Schuldt

Period Covered: 9/17/76 - 9/19/77

Published Sept. 30, 1977

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, under NASA Contract NAS7-100 for the U.S. Energy Research and Development Administration, Division of Solar Energy.

The JPL Low-Cost Silicon Solar Array Project is funded by ERDA and forms part of the ERDA Photovoltaic Conversion Program to initiate a major effort toward the development of low-cost solar arrays.

### TABLE OF CONTENTS

|                                                      | Page |

|------------------------------------------------------|------|

| SUMMARY                                              | 1    |

| INTRODUCTION                                         | 3    |

| TECHNICAL DISCUSSION                                 | 5    |

| Substrate Characterization                           | 5    |

| Introduction                                         | 5    |

| Substrate Compositions                               | 5    |

| Structure and Properties of Ceramic Substrates       | 9    |

| Characterization of Acid-Leached Mullite Refractory  | 11   |

| Residual Stress State in Silicon Layer               | 11   |

| Silicon on Ceramic Coatings                          | 17   |

| Morphology and Microstructure                        | 18   |

| Carbonization                                        | 21   |

| Continuous-Coating Facility                          | 29   |

| Introduction                                         | 29   |

| Description of Continuous-Coating Facility           | 30   |

| Material Evaluation and Solar Cell Fabrication       | 36   |

| Chemical Characterization of SOC                     | 36   |

| Electrical Characterization of SOC                   | 38   |

| Electrical Characterization of Carbon Layers         | 41   |

| Silicon - Carbon Interface                           | 42   |

| Reflectivity Measurements                            | 46   |

| Solar Cell and Photodiode Fabrication                | 47   |

| Characterization of Electrical Contacts              | 51   |

| EBIC Measurements                                    | 53   |

| Scanned Light Beam and Diffusion Length Measurements | 53   |

| Solar Cell and Photodiode Performance                | 59   |

| Parasitic Resistance Analysis                        | 69   |

| Introduction                                         | 69   |

| The Solar Cell Junction Parameters                   | 71   |

| Power Dissipation                                    | 72   |

| Components of Parasitic Resistance                   | 74   |

| Calculation of bwR <sub>P</sub>                      | 77   |

| ORIGINAL PAGE IS OF POOR QUALITY                     |      |

# TABLE OF CONTENTS (CONCLUDED)

| Economic Analysis        |                                | Page<br>78 |

|--------------------------|--------------------------------|------------|

| PROCESSING EFFORTS       |                                | 86         |

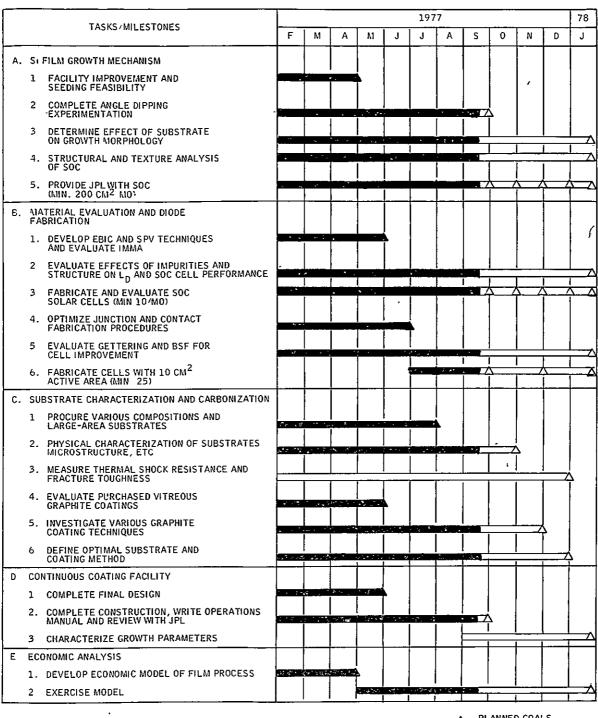

| PROJECTION OF FUTURE ACT | FIVITIES                       | 87         |

| NEW TECHNOLOGY           |                                | 89         |

| SUMMARY OF ANALYSIS AND  | CHARACTERIZATION DATA          | 89         |

| PROGRAM STATUS UPDATE    |                                | 91         |

| REFERENCES               |                                | 95         |

| APPENDICES               |                                |            |

| A HARMONIC ANALYSI       | S OF FRONT STRUCTURE           |            |

| B DISTRIBUTED CELL       | MODEL                          |            |

| C SHEET RESISTANCE       | REDUCTION BY CONTACTING CARBON | FILM       |

| D RESISTANCE OF ELE      | ECTRODE FINS                   |            |

### LIST OF ILLUSTRATIONS

| Figure<br>1 | Alumina-Silicon Phase Diagram                                                                                              | Page<br>8 |

|-------------|----------------------------------------------------------------------------------------------------------------------------|-----------|

| 2           | Thermal Expansion of Mullite Compared to Silicon                                                                           | 9         |

| 3           | Optical Micrographs of McDanel MV20 and Coors S1SI Mullite<br>Refractories (325x)                                          | 12        |

| 4           | Optical Micrograph of Electrically Fused Mullite Substrate (500x)                                                          | 13        |

| 5           | Scanning Electron Micrograph of a Fractured Surface of an MV20 Sample That Had Been Immersed in HF Acid                    | 14        |

| 6           | Thermal Expansion from 25°C to 1000°C of Experimental Substrate Material as a Function of Mullite Content                  | 16        |

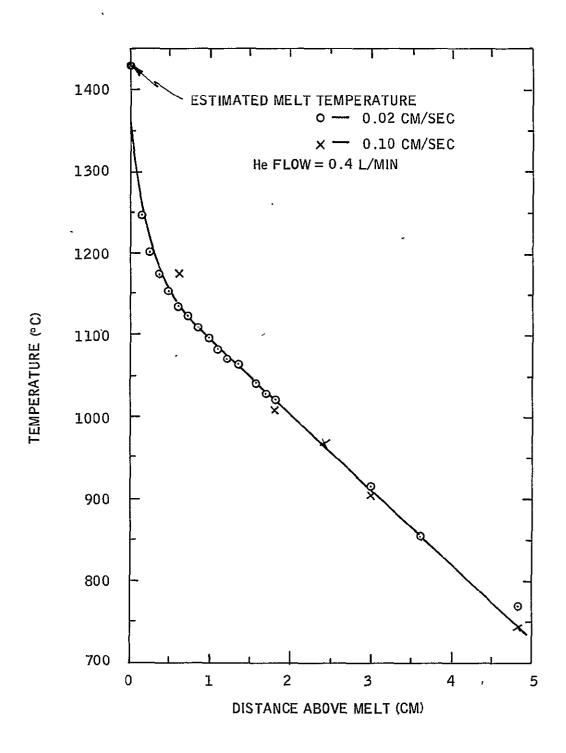

| 7           | Temperature Gradient Above the Melt in Dip-Coating Facility                                                                | 19        |

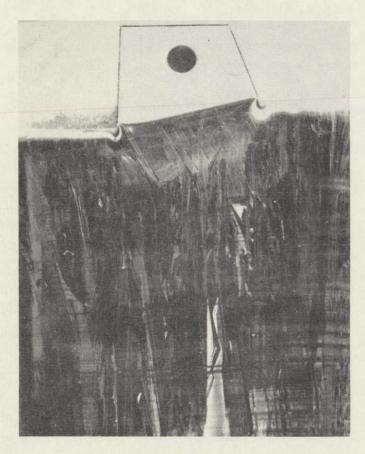

| 8           | Seeded Silicon Sheet Growth                                                                                                | 22        |

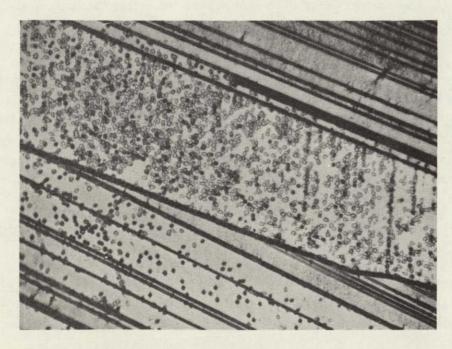

| 9           | Optical Micrograph (500x) of Etched As-Grown Surface Showing Etch Pits                                                     | 22        |

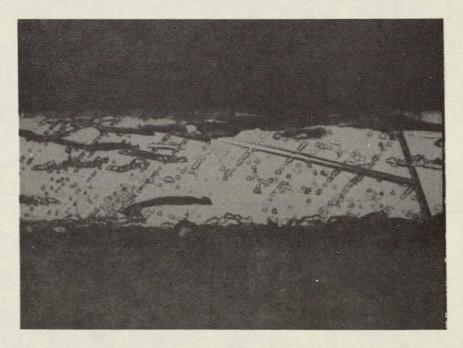

| 10          | Optical Micrograph (500x) of Polished and Eiched Cross Section of Silicon Coating Taken Parallel to Pulling Direction      | 23        |

| 11          | Optical Micrograph (500x) of Polished and Etched Cross Section of Silicon Coating Taken Perpendicular to Pulling Direction | 23        |

| 12          | Optical Micrograph (500x) of Silicon Carbide Layer on Vitre<br>Graf Coated Substrate                                       | 24        |

| 13          | Blistered and Spotty Si Film Formation as a Result of Incomplete Drying of Dylon Carbon Coatings (1.7x)                    | 26        |

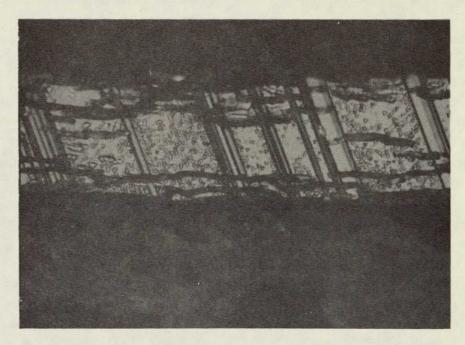

| 14          | Silicon-Ceramic Interface Carbonized with Dag 154 (500x)                                                                   | 28        |

| 15          | Silicon Coating by Inverse Meniscus (SCIM)                                                                                 | 30        |

| 16          | Photograph Showing Early Construction Status of Continuous Coater                                                          | 31        |

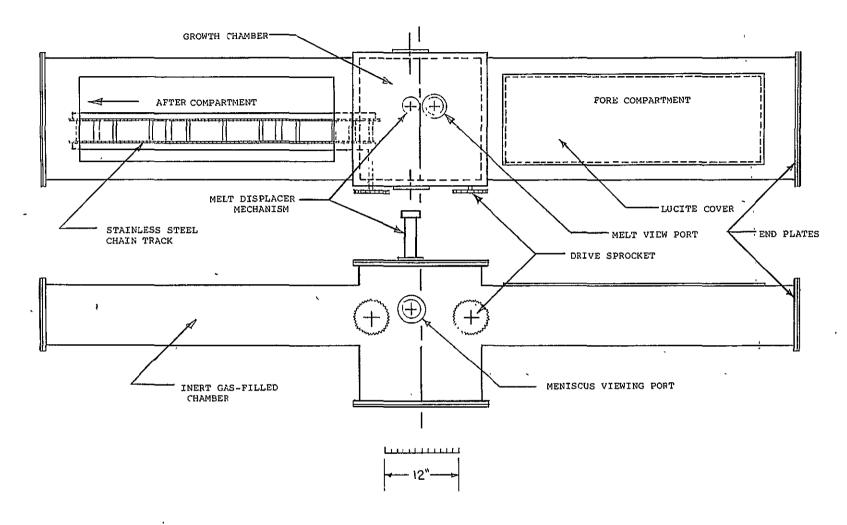

| 17          | Exposed Top View of Continuous-Coating Facility                                                                            | 32        |

| 18          | Cross-Sectional View of Three-Zone Furnace in Growth Chamber                                                               | 33        |

| 19          | Top and Side View of Continuous-Coating Facility                                                                           | 34        |

| 20          | Multi-Element Survey of Melt 27 by Neutron Activation Analysis                                                             | 37        |

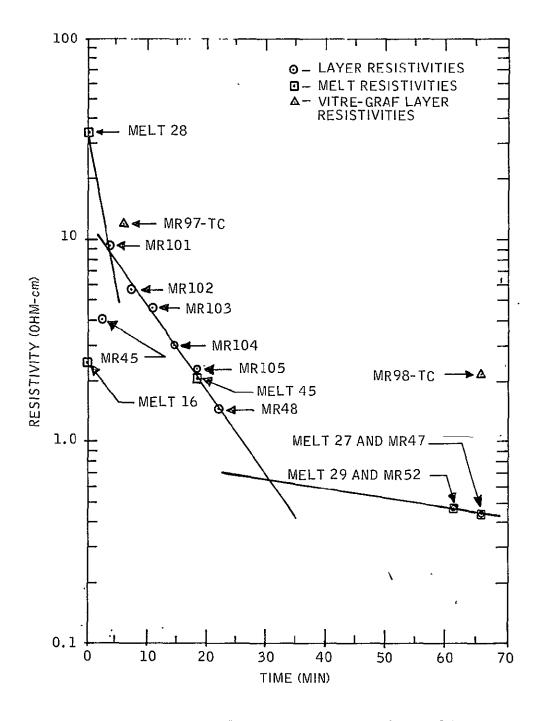

| 21          | Layer and Melt Resistivities Versus Accumulated Time That the Undoped Melts Were Exposed to Mullite                        | 39        |

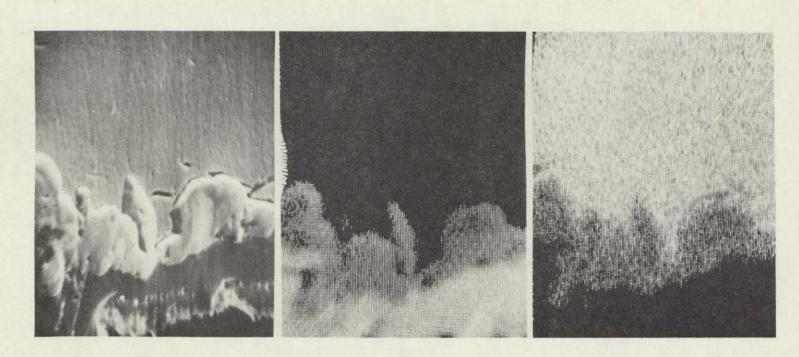

| 22          | Scanning Auger Micrographs of the Silicon-Vitreous Graphite Interface at 2500x                                             | 44        |

## LIST OF ILLUSTRATIONS (CONTINUED)

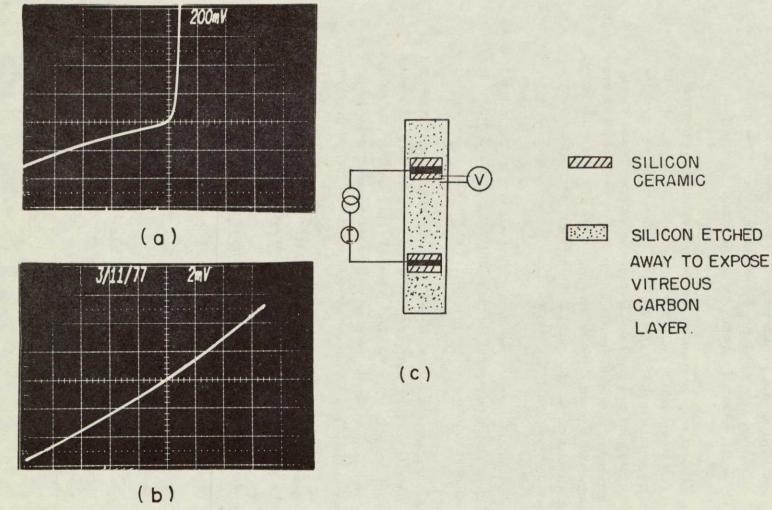

| Figure<br>23 | Silicon-Vitreous Carbon Electrical Contact                                                              | Page<br>45 |

|--------------|---------------------------------------------------------------------------------------------------------|------------|

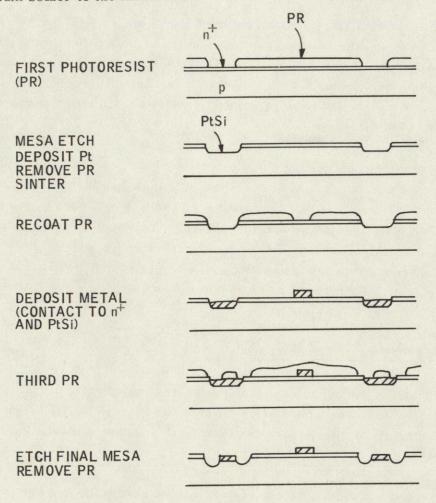

| 24           | Present Fabrication Procedure                                                                           | 48         |

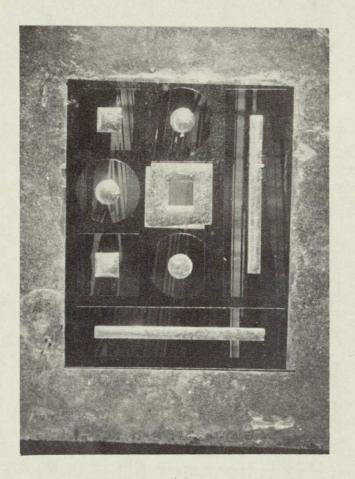

| 25           | SOC Solar Cells (Magnification 6x)                                                                      | 49         |

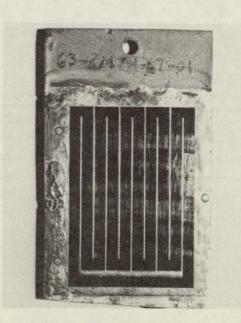

| 26           | Solar Cell with 10 cm <sup>2</sup> Active Area                                                          | 49         |

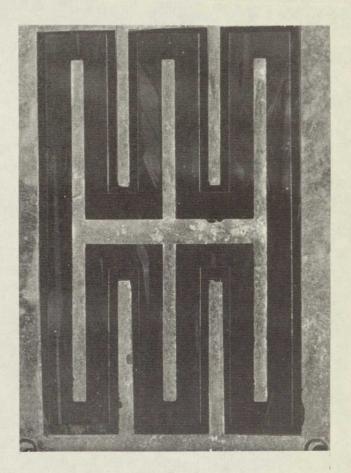

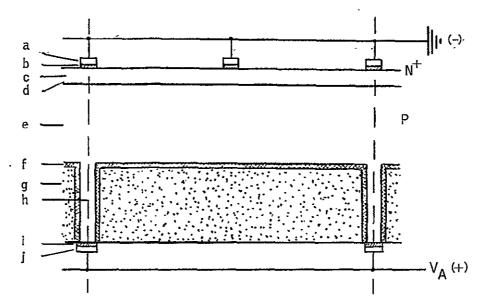

| 27           | Cross-Section of a Portion of a Solar Cell on a Slotted Ceramic Substrate                               | 50         |

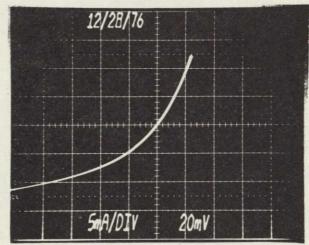

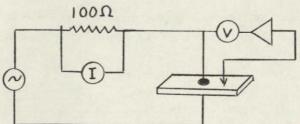

| 28           | Contact Current-Voltage Relationships and Method of Measurement                                         | 52         |

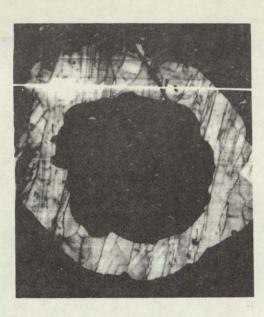

| 29           | EBIC Measurements of Diode Uniformity                                                                   | 54         |

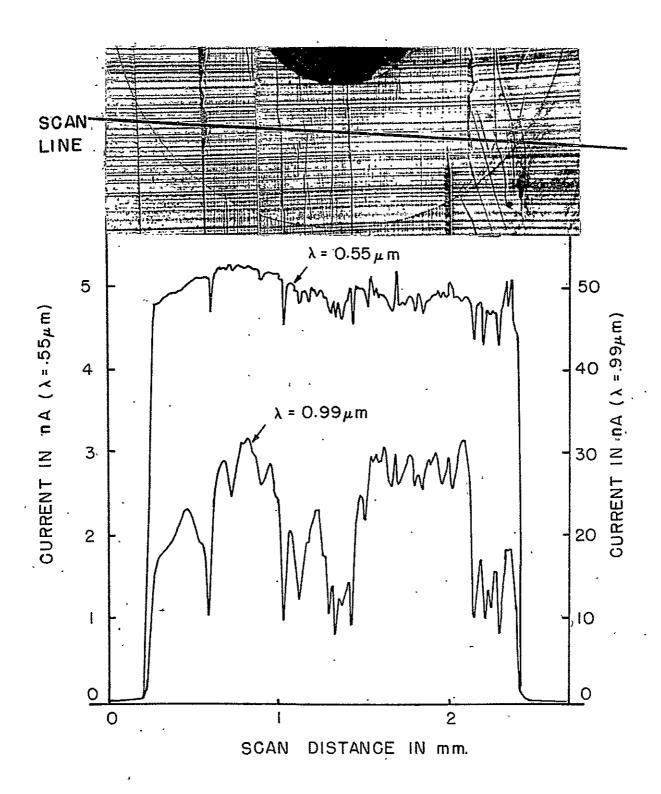

| 30           | Light Beam Scans of Diode R169A-616-1-5                                                                 | 56         |

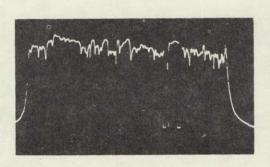

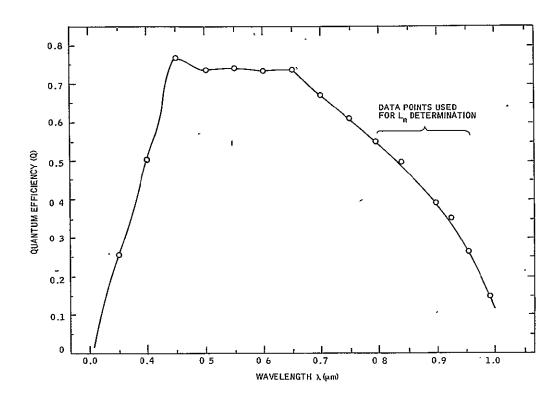

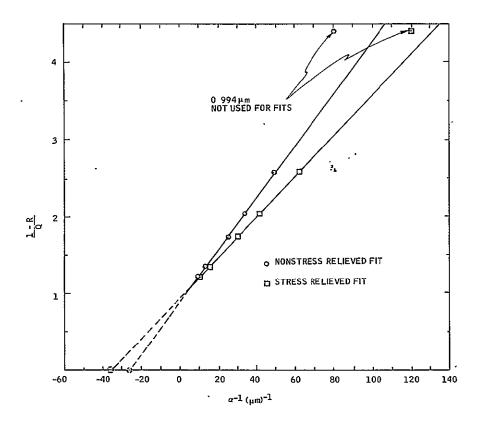

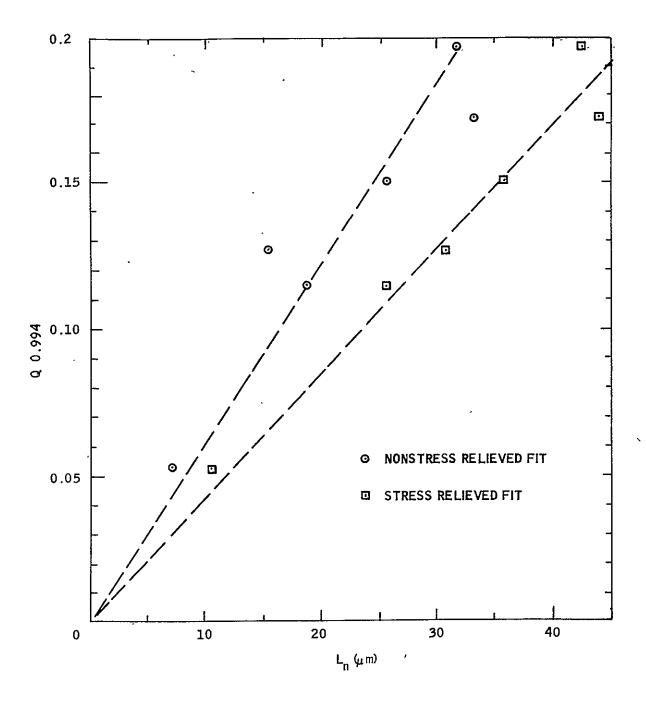

| 31           | External Quantum Efficiency Versus Wavelength                                                           | 57         |

| 32           | Plot of Reciprocal Quantum Efficiency Versus Reciprocal Absorption Coefficient                          | 57         |

| 33           | Plot of Q at 0.994 $\mu$ m Versus L $_{ m n}$ for Various Samples                                       | 58         |

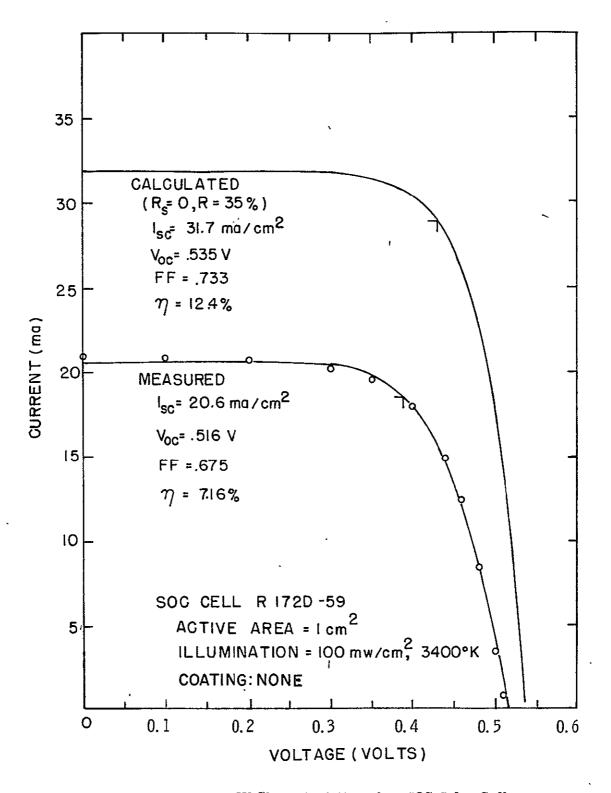

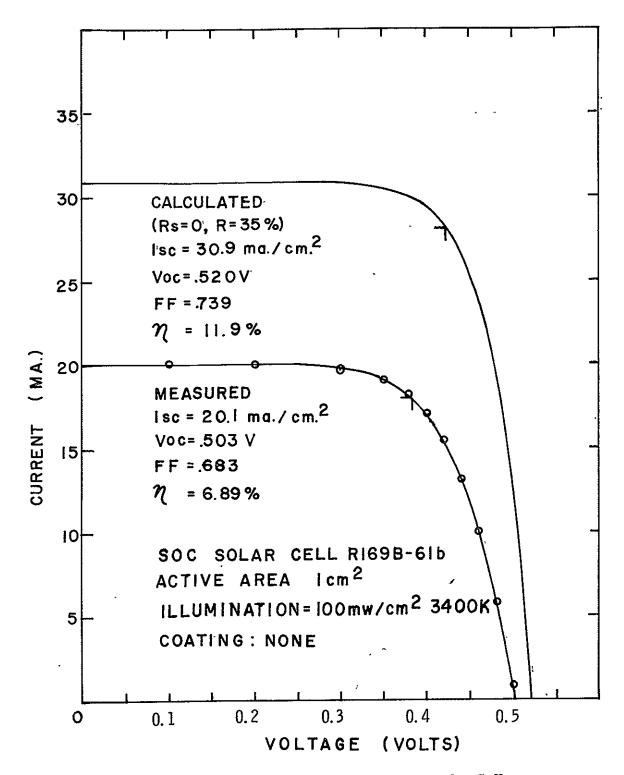

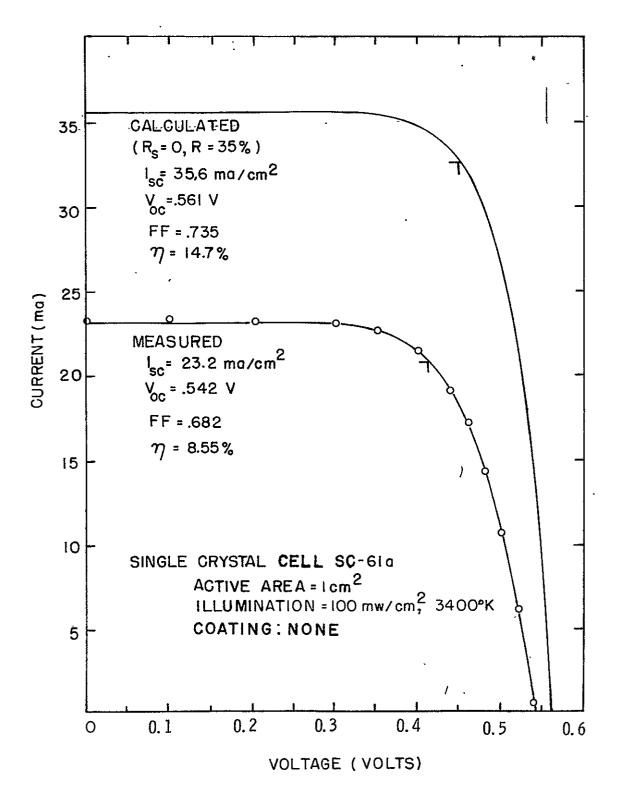

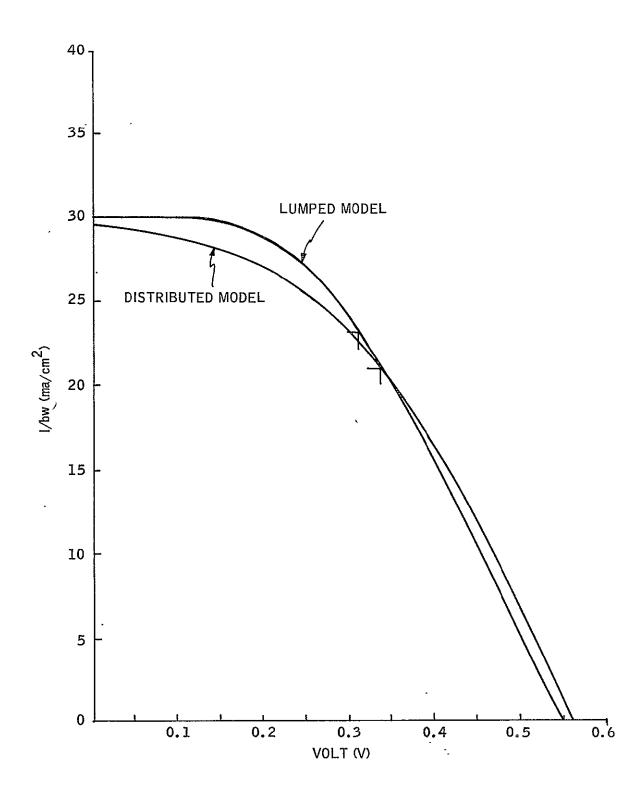

| 34           | I-V Characteristics of an SOC Solar Cell                                                                | 63         |

| 35           | I-V Characteristics of a Single-Crystal Comparison Cell                                                 | 66         |

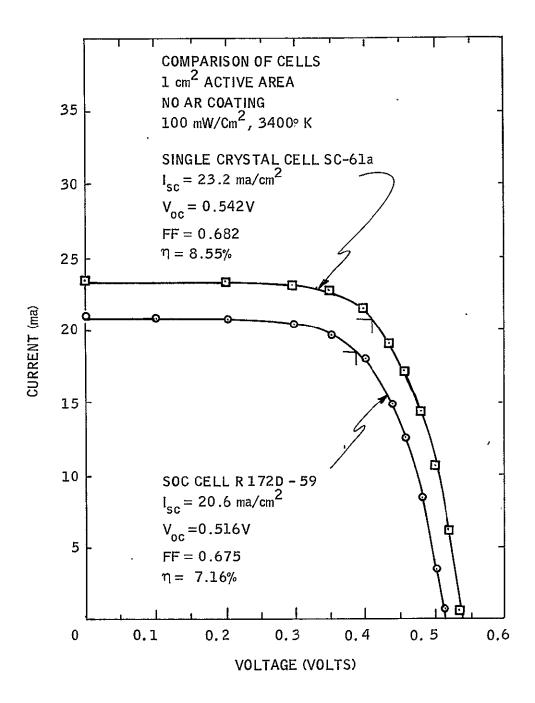

| 36           | I-V Characteristics Comparing an SOC Solar Cell with a Single-Crystal Control Cell                      | 67         |

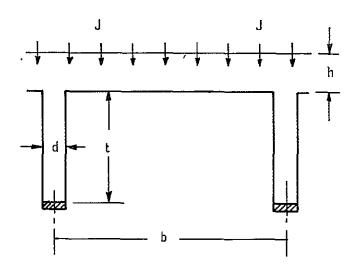

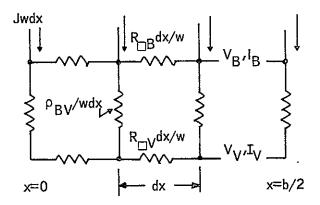

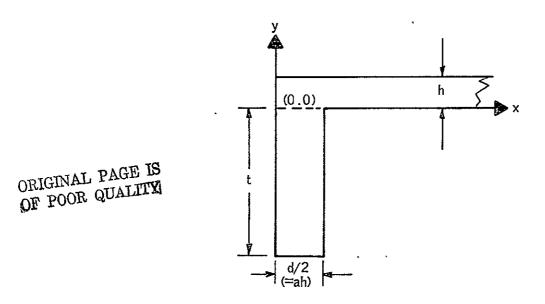

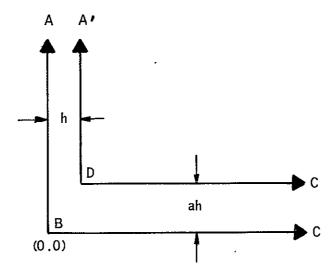

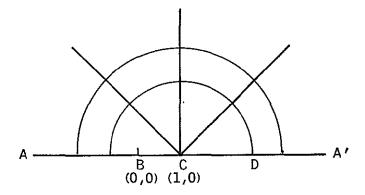

| 37           | One Unit of the Periodic Structure of a SOC Solar Cell                                                  | 70         |

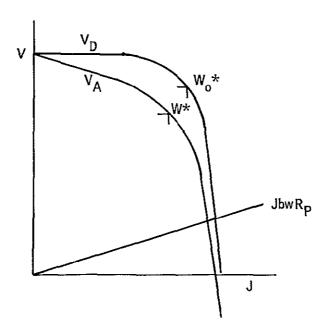

| 38           | Determination of Optimum Solar Cell Operating Point According to Lumped Model for Parasitic Resistances | 70         |

| 39           | Lumped Components of Parasitic Resistance in a Cell Unit                                                | 72         |

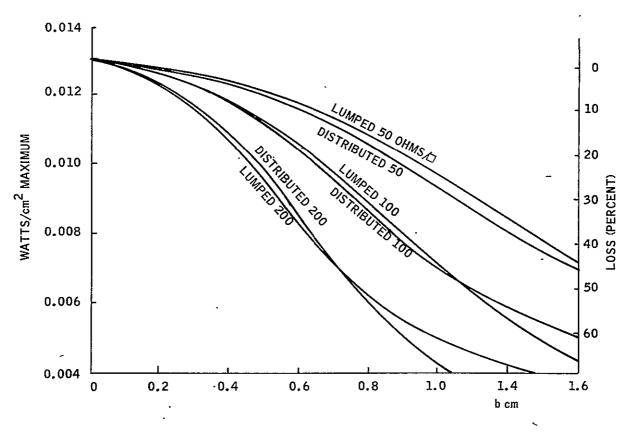

| 40           | Maximum Available Power Density as a Function of Cell Area Times $\mathbf{R}_{\mathbf{P}}$              | 73         |

| 41           | Front Subcell Geometry for the Case b/b' = 2                                                            | 74         |

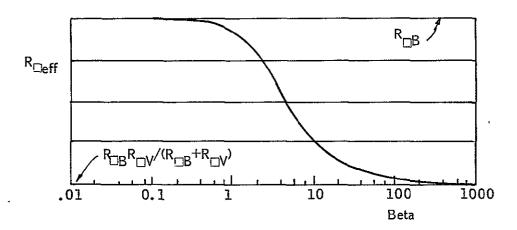

| 42           | Effective Sheet Resistance Versus Beta                                                                  | 76         |

| 43           | Back Cell Geometry                                                                                      | 77         |

| 44           | $bwR_{\mathbf{p}}$ Product as a Function of b for Three Different Base Si Resistivities                 | 79         |

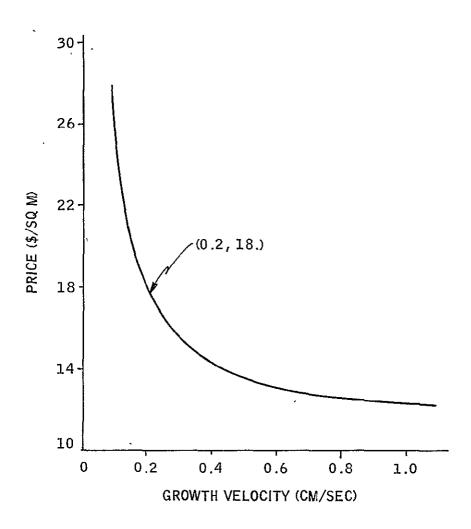

| 45           | Economic Analysis for Growth Rate of 1.0 cm/sec                                                         | 82         |

| 46           | Price Versus Growth Velocity                                                                            | 83         |

### LIST OF ILLUSTRATIONS (CONCLUDED)

| Washington Con Character Date of Co. 1           | Page                                                        |

|--------------------------------------------------|-------------------------------------------------------------|

| Economic Analysis for Growth Rate of U. I cm/sec | 85                                                          |

| Updated Program Plan                             | 92                                                          |

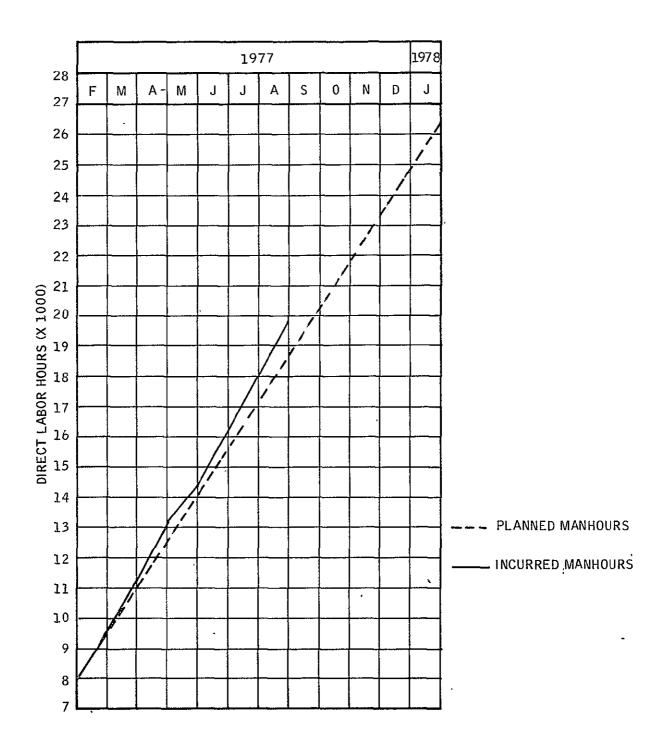

| Updated Program Labor Summary                    | 93                                                          |

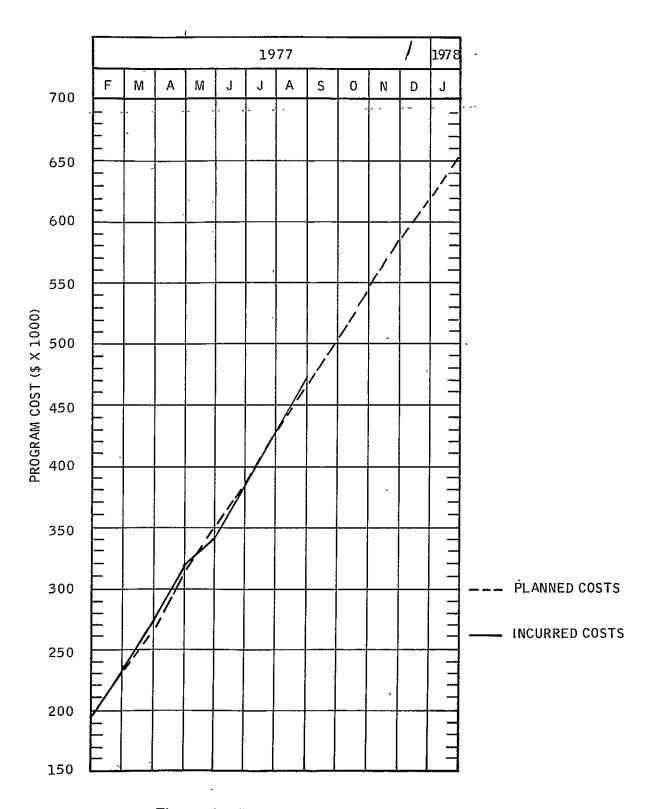

| Updated Program Cost Summary                     | 94                                                          |

|                                                  |                                                             |

|                                                  |                                                             |

|                                                  |                                                             |

|                                                  |                                                             |

| LIST OF TABLES                                   |                                                             |

| Composition of Mulliter Raged Consmis Substrates | Page                                                        |

|                                                  | Updated Program Labor Summary  Updated Program Cost Summary |

Spectrographic Analysis Results of Colloidal Carbon Suspensions

10

27

42

60

62

Properties of Mullite-Based Ceramic Substrates

Performance of Selected Single-Crystal Control Cells

Typical Carbon Sheet Resistivities

Summary of SOC Solar Cell Performance

2

3

4

5

6

#### SUMMARY

The objective of this research program is to investigate the technical and economic feasibility of producing solar-cell-quality sheet silicon by coating one surface of carbonized ceramic substrates with a thin layer of large-grain polycrystalline silicon from the melt. In the past year significant progress was made in all areas of the program.

The physical and chemical properties of the standard mullite refractory used for the majority of the coating runs (McDanel MV20 and Coors S1SI) have been characterized. A number of experimental compositions have been identified and procured from Coors. Characterization of the standard compositions revealed that the thermal expansion of mullite depends on both relative amounts of glass phase and on the impurity level in the glass. Since the thermal expansion in mullite exceeds that of silicon, the silicon coating should be in a state of compression. This was confirmed by x-ray measurements.

After modifying and cleaning the dip-coating facility, silicon on ceramic (SOC) solar cells were fabricated which demonstrate that the SOC process can produce silicon of solar cell quality. SOC cells having 1 cm $^2$  active areas demonstrated measured conversion efficiencies as high as 7 2 percent. Typical open-circuit voltages ( $V_{oc}$ ) and short-circuit current densities ( $J_{sc}$ ) were 0.51 volt and 20 mA/cm $^2$ , respectively. Since the active surface of these solar cells is a highly reflective "as-grown" surface, one can expect improvement in  $J_{sc}$  after an anti-reflection (AR) coating is applied. It is significant that single-crystal comparison cells, also measured without benefit of an AR coating had efficiencies in the 8.5 percent range with typical  $V_{oc}$ 's and  $J_{sc}$ 's of 0.54 volt and 23 mA/cm $^2$ , respectively. Therefore, improvement in cell design and junction diffusion techniques should increase the efficiency of both the SOC and single-crystal cells.

The surfaces of the SOC coatings are predominately {331} with a growth direction of <211>. This texture permits {111} twin planes to occur perpendicular to the substrate and propagate as the grain grows. This texture is similar to that observed in EFG ribbon silicon. Preliminary seeding experiments have been tried and while single-crystal silicon was not forthcoming, results were nonetheless encouraging.

As previously reported, mullite dissolves slightly in molten silicon. It is therefore encouraging to note that even when the melt is given a significant exposure to mullite, SOC solar cells can be made from the resulting silicon with  $V_{\rm oc}$ 's and  $J_{\rm sc}$ 's that are

within 9 percent of those obtained in single-crystal comparison cells. One method for inhibiting this substrate dissolution is to coat the substrate with a vitreous carbon which is impervious to molten silicon. "Vitre-Graf" coatings have demonstrated the feasibility of this concept. Another method is to modify the silicon coating technique in such a way as to reduce the contact area and time the substrate has with the silicon melt. A new continuous-coating facility has been designed and constructed to accomplish this and will soon be in operation. To date, chemical analysis techniques have not revealed any impurity segregation at grain boundaries, either before or after the junction diffusion process.

Electron beam-induced current (EBIC) and light beam-induced current (LBIC) techniques have been used to measure the base region minority carrier diffusion length ( $L_n$ ). Both methods gave similar results but the LBIC method shows that  $L_n$  varies considerably, being relatively constant within a grain, and significantly reduced at grain boundaries.

Since the ceramic is an insulator it is anticipated that electrical contact will be made to the base region of the solar cell via small slots in the substrate. A contact-modeling study reveals that the slotted substrate concept leads to an appreciable series resistance problem unless the slots are made electrically conducting and the base of the silicon has a high conductivity layer at the back. Several carbon coating techniques have been investigated, some of which show promise of providing this needed additional conductivity.

An economic analysis of the SOC process has been completed. The study reveals that in a scaled-up process it is desirable to have silicon coating growth rates greater than 0.2 cm/sec. To date our best solar cells have been made on coatings grown at approximately one-fourth that rate. Emphasis is presently being given to increasing this growth rate without sacrificing the quality of the silicon coating.

#### INTRODUCTION

This research program commenced October 21, 1975. Its purpose is to investigate the technical and economic feasibility of producing solar-cell-quality sheet silicon by coating inexpensive ceramic substrates with a thin layer of polycrystalline silicon. The coating methods to be developed are directed toward a minimum-cost process for producing solar cells with a terrestrial conversion efficiency of 12 percent or greater.

By applying a graphite coating to one face of a ceramic substrate, molten silicon can be caused to wet only that graphite-coated face and produce uniform thin layers of large-grain polycrystalline silicon; thus, only a minimal quantity of silicon is consumed. A dip-coating method for putting silicon on ceramic (SOC) has been shown to produce solar-cell-quality sheet silicon. This method and a continuous coating process also being investigated have excellent scale-up potential which offer an outstanding cost-effective way to manufacture large-area solar cells. The dip coating investigation has shown that, as the substrate is pulled from the molten silicon, crystallization continues to occur from previously grown silicon. Therefore, as the substrate length is increased (as would be the case in a scaled-up process), the expectancy for larger crystallites increases.

A variety of ceramic materials have been dip coated with silicon. The investigation has shown that mullite substrates containing an excess of SiO<sub>2</sub> best match the thermal expansion coefficient of silicon and hence produce the best SOC layers. With such substrates, smooth and uniform silicon layers 25cm<sup>2</sup> in area have been achieved with single-crystal grains as large as 4mm in width and several cm in length. Crystal length is limited by the length of the substrate. The thickness of the coating and the size of the crystalline grains are controlled by the temperature of the melt and rate at which the substrate is withdrawn from the melt.

The solar cell potential of this (SOC) sheet silicon is promising. To date 1 cm<sup>2</sup> solar cells have been fabricated, without the benefit of an antireflection (AR) coating and minimized series resistance, that have conversion efficiencies in the 7 percent region. Such cells typically have open-circuit voltages and short-circuit current densities of 0.51 volt and 20 mA/cm<sup>2</sup>, respectively. Application of an AR coating to these cells . would improve their efficiency in the direction of the program's ultimate 12 percent goal.

ORIGINAL PAGE IS OF POOR QUALITY

Development efforts are continuing in such areas as improvement in growth rate, reduction of progressive melt contamination and optimization of electrical contacts to the base layer of the cell. The investigation has shown that mullite substrates, to a limited extent, dissolve in molten silicon. The aluminum and other impurities of the substrate are believed to adversely affect solar cell conversion efficiency. A special type of graphite coating on the substrate has shown a potential for inhibiting this dissolution of mullite. Should these coatings prove to satisfactorily isolate the substrate from the melt in a cost-effective manner, improved solar cell performance should be forthcoming. An alternate method for reducing substrate dissolution is to reduce the contact area the substrate makes with the silicon melt. Therefore, as previously mentioned, a silicon coating facility has been constructed which is designed to coat large (10 cm x 100 cm) substrates in a continuous manner. It is expected that this new facility will not only improve the growth rate, but also minimize the silicon melt's contact with the substrate. This should reduce the rate at which the melt becomes contaminated. Further, this new facility will permit a study of possible continued grain growth by accommodating the use of longer substrates. It should also reveal problems that are likely to be encountered in a scale-up process.

#### TECHNICAL DISCUSSION

SUBSTRATE CHARACTERIZATION (B. G. Koepke, S. J. Marquardt and M. S. Smeltzly)

### Introduction

The characterization and properties of the ceramic substrates are discussed in this section. To date, the ceramic found to be most suitable for coating with silicon is a refractory clay product (i.e. fireclay in the silica-alumina system containing about 55 wt. %A12O3. The ceramic is a two-phase material containing interlocking crystallites of the mineral mullite (nominal composition 3A12O3·2SiO2) in a continuous glass matrix. The mullite-based refractory can be economically produced by firing naturally occurring clays and other minerals and has good high temperature properties and thermal shock resistance.

Two types of substrates are being produced for this program. Small,  $1 \, 1/2 \times 2 \times 0.100$ inch substrates are used for coating experiments run in the small-dipping facility. Large  $4 \times 40 \times 0.100$ -inch substrates will be used for coating experiments run in the scale-up

continuous coating facility. Substrates are being obtained from two sources, the Honeywell

Ceramics Center and Coors Porcelain Co. The types of substrates produced and the

characterization of these substrates form the bulk of this section.

### Substrate Compositions

Most of the substrates produced for this program have been a commercial fireclay refractory containing alumina and silica in the approximate ratio 55 wt percent/45 wt. %. The substrates of this composition produced at the Honeywell Ceramics Center were manufactured from premixed McDanel MV20 composition by rolling, drying and firing. Substrates of this composition obtained from Coors were designated SISI and were produced by cold pressing and sintering. A number of substrates with experimental compositions based on variations of the MV20 - S1SI "theme" have also been produced and will be described.

Table 1 lists the approximate compositions of the McDanel MV20 and Coors S1Si mullite ceramic substrates. The data for the McDanel ceramic was obtained from a company brochure. The Coors analysis was based on analyses of the starting materials. The only notable difference between the two is the higher Ti in the S1SI.

Table 1. Composition of Mullite-Based Ceramic Substrates (in wt. %)

| <u>Code</u> | Material           | A1203        | SiO <sub>2</sub> | Fe <sub>2</sub> 0 <sub>3</sub> | CaO                 | MgO                  | <u>K2</u> 0 | $\frac{\text{Na}_2^{\text{O}}}{}$ | $\frac{\text{TiO}_2}{}$ | B202 | MnO   | ĊaO  | <u>v205</u> | Comments                                     |

|-------------|--------------------|--------------|------------------|--------------------------------|---------------------|----------------------|-------------|-----------------------------------|-------------------------|------|-------|------|-------------|----------------------------------------------|

| -           |                    |              |                  | Co                             | mmercia             | 1 Compo              | sitions     | ~                                 |                         |      |       |      |             |                                              |

| I           | McDanel MV20       | 55.4<br>52.6 | 42.0<br>43.7     | 0.8<br>0.45<br>1.27            | 0.1<br>0.09<br>0.15 | 0.04<br>0.14<br>0.33 | 0.7<br>0.74 | 0.5<br>0.74<br>0.38               | 0.5<br>0.82<br>1.30     |      | 0.07  | 0.01 | 0.07        | Nom. McDanel<br>Coórs Anal.<br>Emission Spec |

| A           | Coors S1SI         | 57.6         | 38.9             | 0.62                           | 0.13                | 0.25                 | 0.92        | 0.25                              | 1.12                    |      |       |      |             | Coors Anal.                                  |

| II          | McDanel MV30       | 60.0<br>58.3 | 38.0<br>38.9     | 0.5<br>0.82<br>0.79            | 0.1<br>0.19<br>0.04 | 0.2<br>0.19<br>0.33  | 0.5<br>0.48 | 0.08<br>0.10<br>0.13              | 0.5<br>0.83<br>0.90     |      | 0.012 | 0.01 | 0.03        | Nom McDanel<br>Coors Anal.<br>Emission Spec  |

| · ·         |                    | E            | xperime          | ental Co                       | mpositi             | lons fro             | om Coors    | Porcel                            | ain Co.                 |      |       |      |             |                                              |

| В           | High Mullite       | 67.2         | 31.4             | 0.45                           | 0.02                | 0.01                 | 0.16        | 0.18                              | 0.54                    |      |       |      |             | Cooṛ́s Anal                                  |

| С           | High Silica        | 52.2         | 44.7             | 0.56                           | 0.13                | 0.22                 | 0.83        | 0.22                              | 1.01                    |      |       |      |             | Coors Anal                                   |

| D           | Boric Acid         | 56.7         | 38.3             | 0.61                           | 0.13                | 0.24                 | 0.90        | 0.24                              | 1.10                    | 1.50 |       |      |             | Coors Anal                                   |

| E           | Open Porosity      | 57.6         | 38.9             | 0.62                           | 0.13                | 0.25                 | 0.92        | 0.25                              | 1.12                    | •    |       |      |             | Coors Anal                                   |

| F           | High Purity        | 59.5         | 39.1             | 0.44                           | 0.21                | 0.13                 | 0.34        | 0.05                              | 0.30                    |      |       |      |             | Coors Anal                                   |

| G           | Electrically Fused | 77.5         | 21.9             | 0.12                           | 0.00                | 0.00                 | 0.00        | Ó∙35                              | 0.05                    |      |       |      |             | Coors Anal                                   |

| Н           | Reducing Fire      | 57.6         | 38.9             | Ò.62                           | 0.13                | 0.25                 | 0.92        | 0.25                              | 1.12                    |      |       |      |             | Coors Anal                                   |

Early in the program a higher A1<sub>2</sub>O<sub>3</sub> substrate was also obtained from the Honeywell Ceramics Center. The material was produced by slip casting from McDanel MV30 composition mix and contained about 60 wt percent A1<sub>2</sub>O<sub>3</sub>. The nominal chemical analysis of McDanel MV30 mullite is included in Table 1 along with analyses run at Coors. The agreement is reasonable. Semi-quantative chemical analysis using emissions spectroscopy was also performed on samples of MV20 and MV30 at Honeywell to determine the major metallic impurities. These results are also shown in Table 1. The major impurities from the standpoint of the electronic performance of a photovoltaic silicon coating are Ti and Fe.

The success of the coating experiments run with MV20 mullite prompted an effort to see if the properties of the substrate could be optimized by compositional modification. Based on discussions with M. Leipold of J.P.L. and engineers at Coors Porcelain Co. substrates with experimental compositions based on variations of the 55 wt.% A1<sub>2</sub>O<sub>3</sub> composition were identified and have been produced by Coors. The experimental compositions are lised in Table 1 and briefly discussed below.

The high mullite and high silicon modifications were produced to determine whether the mullite or the glass phase dominates the thermal behavior of the substrate during the coating operation.

The boric acid modification is intended to be a body in which the glass phase is doped with B<sub>2</sub>O<sub>3</sub> to produce a low-expansion glass and possibly act as a source of B in the silicon coating. The open porosity modification is a body intentionally produced with higher porosity. The higher porosity will enhance the thermal shock resistance and will allow deeper penetration of the silicon coating into the substrate. The high-purity modification is a body produced from starting materials selected for their low impurity content. As noted in Table 1 the Fe, Na and Ti are noticeably low in this material. The electrically fused mullite is produced from a mixture of electrically fused mullite and silica powders. The impurity levels in this material are understandably low. The reducing fire modification is a standard S1SI mullite body that has been fired in a reducing atmosphere. The intent is to produce a material with high porosity that contains residual carbon in the form of unoxidized binder materials.

Since none of the experimental compositions have been coated with silicon at this time comments pertaining to compositional optimizations of the substrate will have to be referred to future reports.

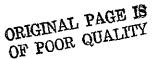

A better idea of the phase relationships existing in fireclay refractories can be obtained from the alumina-silica equilibrium phase diagram of Aksay and Pask shown in Figure 1.

Mullite is a compound that exists over a measurable range of compositions, and, according to Aksay and Pask, melts incongruently. Disagreements on the melting behavior of mullite still exist in the literature. Referring to Figure 1, the equilibrium structure at room temperature of a composition containing about 55 wt. % Al<sub>2</sub>O<sub>3</sub> consists of mullite crystallites in a eutectic matrix consisting of a finely divided mixture of SiO<sub>2</sub> and mullite. In reality, the liquid present at the firing temperature (~1600°C) does not crystallize at the eutectic temperature and instead forms a continuous glass matrix around the mullite crystallites. It should be further mentioned that the clay starting materials do not contain any mullite but decompose during firing into a high-silica liquid into which the mullite crystallizes as firing proceeds.

Figure 1. The Alumina - Silica Phase Diagram According to Askay and Pask. Also shown are the compositions of the various substrate materials currently being examined (the code letters are explained in Table 1).

ORIGINAL PAGE IS OF POOR QUALITY

### Structure and Properties of Ceramic Substrates

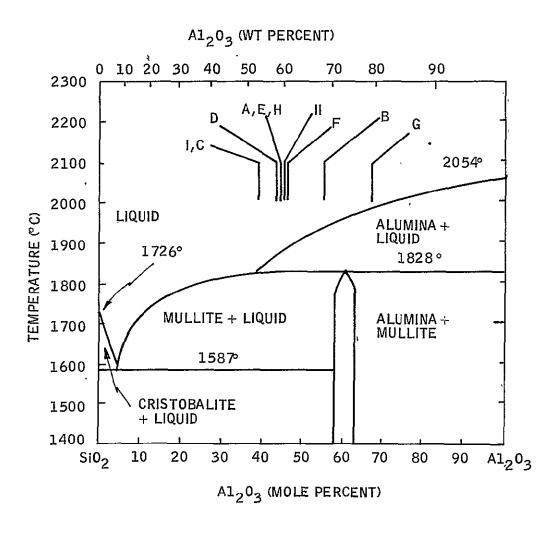

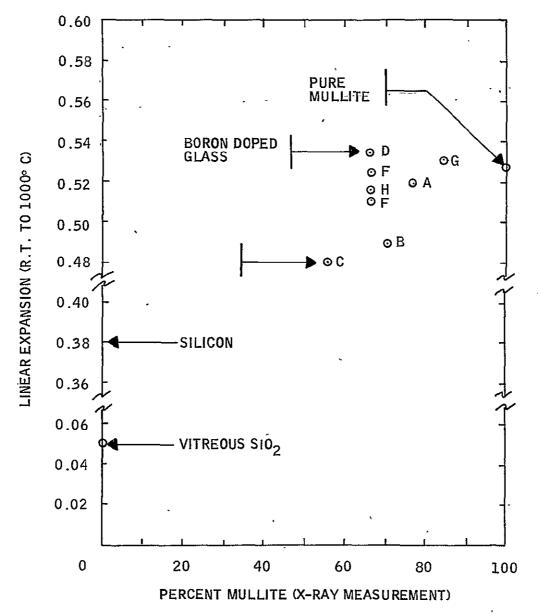

The structures and properties of the substrates were measured at Honeywell and at Coors Porcelain Co. Microstructure, density and modulus of rupture (MOR) determinations were made at Honeywell's Corporate Materials Science Center (CMSC) and density, firing shrinkage, thermal expansion and x-ray percent of mullite were determined at Coors. The Honeywell Ceramics Center provided firing shrinkage data on the MV-20 and MV-30 substrates. A summary of the properties measured to date is given in Table 2. The thermal expansion of these materials is in accordance with the good thermal shock resistance of fireclay refractories. As shown in Figure 2 the thermal expansion of the mullites is slightly greater than silicon. Thus, after cooling to room temperature the silicon coating should be under a compressive stress. Preliminary x-ray measurements (discussed later) of residual stress in the silicon have indicated this to be the case.

Figure 2. Thermal Expansion of Mullite Compared to Silicon

The strengths of the MV20 and boric acid modifications were the lowest of the group. The strongest samples were those containing greater amounts of mullite, i.e. S1SI and the high mullite modification and the material fired in a reducing atmosphere. Both the strength and thermal expansion affect the thermal shock resistance. Materials with low expansion and high strength, such as the high mullite modification, are expected to have good thermal shock resistance.

ORIGINAL PAGE IS OF POOR QUALITY.

10

Table 2. Properties of Mullite-Based Ceramic Substrates

| Code | Material           | Density (gm/cc) | %<br>Porosity | Thickness Shrinkage(%) cial Compos | Length Shrinkage (%) | X-Ray<br>% Mullite | Equil<br>% Mullite | Thermal Expansion R.T1000C (%) | MOR<br>(KPSI)     |

|------|--------------------|-----------------|---------------|------------------------------------|----------------------|--------------------|--------------------|--------------------------------|-------------------|

|      |                    |                 | Commer        | CIAI COmpos                        | TUTORS               |                    |                    |                                |                   |

| I    | McDanel MV20       | 2.50            |               | 14.0                               | 10.2                 |                    | 74                 | 0.495                          | 15.3 <u>+</u> 1.5 |

| A    | Coors S1SI         | 2.70            | 0.32          | 12.1                               | . 16.7               | 76.5               | 81                 | 0.520,                         | 23.7 <u>+1</u> .4 |

| II   | McDanel MV30       |                 |               |                                    |                      | •                  | 82                 | 0.470                          | •                 |

|      | ·                  | Experimenta     | 1 Composi     | tions from                         | Coors Porce          | elain Co.          |                    |                                | •                 |

| В    | High Mullite       | 2.86            | 0.22          | 12.1,                              | 12.7                 | 70.2               | 95                 | 0.485                          | 25.9 <u>+</u> 1.2 |

| С    | High Silica        |                 |               |                                    |                      | 56.1               | 74                 | 0.480                          |                   |

| D    | Boric Acid         | 2.60            | 0.19          | 11.7                               | 13.7                 | 66.8               | 80                 | 0.535                          | 15.6 <u>+</u> .7  |

| E    | Open Porosity      | 2.55            | 7.27          | 11.6                               | 13.8                 | . 66.4             | 81                 | 0.525                          | 18.8 <u>+</u> 1.8 |

| F    | High Purity        | 2.70            | .0.53         | 14.9                               | 19.5                 | 66.8               | 84                 | 0.510                          | 20.1 <u>+</u> 1.0 |

| G    | Electrically Fused | 2.6-2.8         |               | 10.4                               | 11.3                 | 84.2               | 87                 | 0.530                          | 18.6 <u>+</u> 1.4 |

| H    | Reducing Fire      | 2.7-2.9         |               | 12.5                               | 18.1                 | 66.4               | 81                 | 0.515                          | 23.8 <u>+</u> 1.6 |

The average thermal expansion of mullite from R. T. to 1000°C is 0.526 percent<sup>2</sup>. This value is at the upper limit of those listed in Table 2 and, as discussed later, indicates that the thermal properties of the glass phase rather than the mullite are dominating the properties of the substrates.

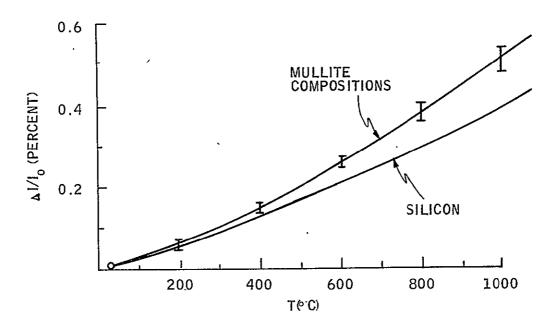

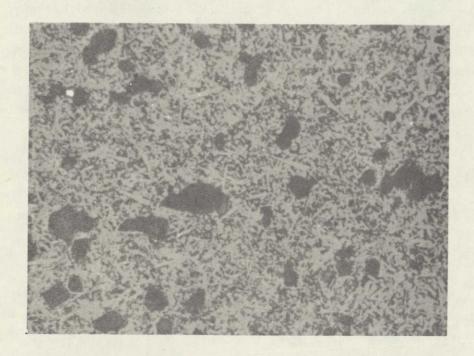

The microstructures of McDanel MV20 and Coors S1SI mullite refractories are shown in Figure 3. The light regions are mullite crystallites and the dark phase is the glass matrix. The S1SI structure has more mullite and less porosity. This is consistent with the data in Table 2; the S1SI has a higher density and contains more A12O3, which corresponds to a higher mullite content. The microstructures of most of the experimental compositions were similar to those shown in Figure 3. The major differences were in the amounts of the phases (i.e. glass, mullite and porosity). The microstructure of the electrically fused mullite body is shown in Figure 4. The light areas are presumably mullite and the dark regions are silica.

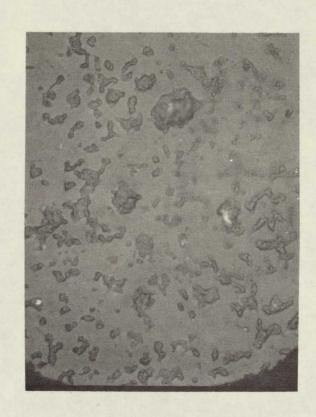

### Characterization of Acid-Leached Mullite Refractory

Most of the impurities in a mullite refractory are in the glass phase. In an effort to eliminate some of the impurities prior to coating, a number of pieces of McDanel MV20 were leached in HF to dissolve the glass phase. A scanning electron micrograph of a fractured cross-section of an MV20 substrate that was immersed in HF until about half the total cross-section had been acid leached is shown in Figure 5a. A higher magnification photo of the interface region at the bottom of the leached layer is shown in Figure 5b while a still higher magnification photo is shown in Figure 5c. The acicular morphology of the mullite crystallites that precipitated during firing is readily apparent. The structure appears to contain only the continuous-glass phase and the mullite needles. The results of EDAX analyses of regions in the center and at the edge of the leached sample showed that, as expected, the A1/Si ratio increased and the K and Ti were lower in the leached region. The Fe content was hardly altered by leaching.

Although the leaching operation lowered the surface impurity content it also weakened the substrate. Leached substrates that were carbon coated and dipped in silicon repeatedly fractured during dipping.

## Residual Stress State in Silicon Layer

The residual stress in the silicon layer can be estimated from an expression used for stresses in glaze coatings applied to ceramics<sup>3</sup>. For a thin-silicon coating on an infinite substrate the stress at temperature, T is

Figure 3(a). Optical Micrograph (325x) of McDanel MV20 Mullite Refractory, Specimen MR114

Figure 3(b). Optical Micrograph (325x) of Coors S1S1 Mullite Refractory, Specimen MC1

Figure 4. Optical Micrograph of Electrically Fused Mullite Substrate (500x)

Figure 5. Scanning Electron Micrographs of a Fractured Surface of an MV20 Sample that had been Immersed in HF to Leach the Glass Phase to a Depth of Approximately One-Third the Specimen Thickness.

Figure 6. Thermal Expansion from 25°C to 1000°C of Experimental Substrate Materials Plotted as a Function of Mullite Content as Measured by X-rays. (The code letters are defined in Table 1)

as determined from Table 1 increases steadily through the series of samples with similar glass contents as follows: B, F, H, E, D.

The boric acid modification material (sample D) has the highest impurity content of all and the largest expansion. Sample A has the same impurity content as samples E and H but contains more mullite. Sample C has a higher impurity content than B but contains more glass. The conclusion here is that the thermal expansion of a mullite-based refractory is determined not only by the relative amounts of glass and mullite in the

ORIGINAL PAGE IS OF POOR QUALITY material but also by the impurity content which primarily resides in the glass and alters its expansion. Impurities such as transition metals may be deleterious to the ultimate performance of the photovoltaic coating. Thus, if substrates were to be designed to be more thermally compatible with silicon, the most likely approach would be by altering the glass content rather than the glass chemistry.

SILICON ON CERAMIC COATINGS (R. B. Maciolek, D. Sauvy, S. Marquardt, and K. Wouri)

During the past year several changes were made in the dip-coating system with the objective of improving precision, reliability, ease of operation and coating quality. A 2 cm-diameter viewing port was installed in the top of the apparatus to make possible the direct observation of the melt and dipping process. Previously the process had been observed using a mirror which suffered from thermal distortion and which, in time, was obscured by vapor deposited material.

An unfortunate accident occurred during the second quarter which contaminated the inside of the melt chamber and prevented any dipping experiments from being conducted during most of the quarter. However, while the apparatus was being disassembled and cleaned the opportunity was taken to revamp the temperature control system and pulling mechanism.

It was decided that a poor impedance match between the Honeywell Dialatrol and the power supply controls was responsible for the unsatisfactory control. That system was discarded in favor of a properly matched one consisting of a Honeywell Deviation Set Point amplifier and a Honeywell Electr-O-Volt controller.

The cable-type dipping mechanism, which did not operate as smoothly as desired, was replaced with a ball screw drive mechanism. Both the temperature control system and the drive mechanism have been satisfactorily used in Czochralski-type crystal growth apparatus used in the Honeywell Research Center for the growth of high-quality optical and electro-optic crystals.

After the apparatus was cleaned and reassembled one of the first runs to be made was a dummy during which the melt was held at a typical growth temperature for six hours, but no substrates were dipped. This was done to check the cleanliness of the apparatus. Resistivity measurements made at the conclusion of the run were high, 100-1,000 ohm cm, n-type, indicating the melt had not been contaminated.

Starting with runs 55 through 77 helium, rather than argon, has been used as the atmosphere in the apparatus. The increased thermal conductivity of He permits higher growth rates and helps to suppress the collection of Si vapor on the viewports and chamber walls.

More recently, a gas mixture of He-10%H<sub>2</sub> has been employed as the atmosphere. The benefits, if any, derived from coating in the presence of hydrogen are currently being assessed.

During the third quarter, two more modifications were made on the apparatus. First, a gas jet was installed inside the growth chamber so that the temperature gradient above the melt can be manipulated. Second, a new pull rod seal was installed and the pull rod itself highly polished to provide smoother mechanical motion upon withdrawal of the samples from the melt. The experiments with the gas jet were only partially successful as the gas flow caused the surface of the melt to solidfy as much as the material on the substrate. Redirection and/or a design of the nozzle should help alleviate this problem.

At the end of run 72 a chromel-alumel thermocouple was inserted into the apparatus in place of the pull rod to measure the temperature gradient above the melt. The result is shown in Figure 7. As expected, the temperature drop immediately above the melt is quite large, >200°C in 0.5 cm. The graph represents average values of continuous scans taken at 0.02 and 0.1 cm/sec. As the distance above the melt increased convection caused temperature fluctuations as large as 100°C.

A new numbering system which has been initiated to identify the samples incorporates certain information about the ceramic substrate and graphite coating. For example, 59-10M6H means the 59th run, 10th substrate dipped in that run; M is for McDanel, 6 is the Ceramic Center's batch identification, and H is for hand-rubbed graphite. The meaning of other letters which may appear is explained in the key at the bottom of the data sheet.

During the past year, 57 runs were made and more than 340 specimens were dipped for an average of six samples per run. The most samples coated in a single run during an eight-hour shift was 26.

## Morphology and Microstructure

During one of the first quarter runs, ten substrates were dipped at an angle of 45 deg to the surface of the melt during insertion and withdrawal from the melt. The objective of this experiment was to see if changing the geometry of the meniscus would influence

Figure 7. Temperature Gradient Above the Melt in Dip-Coating Facility.

the coating rate and/or quality. The principal parameters that were varied were pull rate and the sign of the dip angle (carbon-coated side of the substrate facing up or down). The pull rate was varied from 0.02 to 0.1 cm/sec.

Examination of the silicon coatings showed that angle dipping did not drastically alter the rate or manner in which the coatings solidified. The coatings looked quite comparable to those dipped vertically, with coating thickness decreasing with increasing pull rate. However, it appeared that the coating thickness of the angle-dipped samples was more uniform than those dipped vertically.

It was also interesting to note that those samples dipped with the carbon coating facing up came out of the apparatus with the silicon side clean (no vapor deposited material) and coated completely to the bottom edge, while those dipped with the carbon-coated side down came out with a light vapor-deposited coating and the last ~ 5 mm of substrate virtually bare. The cleanliness of the silicon surface can be explained by self-shielding of the silicon coating from the vapors coming off the melt, by the substrate in one case and direct exposure to them in the other. The lack of coating at the bottom edge of , the samples dipped with the carbon side down is a consequence of the manner in which the liquid "bridge" between the substrate and melt surface is formed and broken at the instant the bottom edge is pulled from the melt.

Four substrates made from segments sliced axially from McDanel's MV-30 slip cast mullite tubing were also dipped. These samples were dipped vertically with the tube axis parallel to the pulling direction. The expected variations in coating thickness were observed as pull rates and temperatures were varied. However, in comparing the nature of the silicon on the convex surfaces to that on the concave surface it appeared that the dendrites formed on the convex surfaces were increasing in width at a somewhat higher rate than that observed on a flat surface. This could be due to either thermal or crystallographic conditions and will be investigated further. These sections of tubing xielded crack-free silicon layers with good adhesion and withstood the thermal shock of being immersed into molten silicon.

In the course of our work during the fourth quarter the effect of substrate width, relative to crucible diameter, on edge nucleation was examined. This was done by dipping substrates of various widths, 37 (standard size), 29, 26, 18 and 12 mm under constant conditions, melt temperature 1440°C and growth rate 0.05 cm/sec, and then examining the nature and extent of the growth at the substrate edge. It appeared that substrate size did not influence edge nucleation and growth. Samples coated under the same conditions showed the same type of edge structure; i.e., on each there was a region 5 mm wide in which the crystals grew in at an angle of 35-45 deg before impinging on the large crystals that were growing down the center portion.

Examination of the coatings grown at different temperatures and rates revealed that the width of the sideways growth region was reduced by the same factors that tend to reduce grain size in general (higher melt temperatures and faster growth rates).

An experiment was also conducted to evaluate the feasibility of coating patterns on the ceramic as defined by the carbon coating. This was done by applying the carbon to the substrate in a series of vertical stripes, 2-7 mm wide with a 2-3 mm spacing. With one run well defined silicon stripes were produced. On a subsequent run the silicon bridged the gaps between the carbon stripes and coated the carbon-free spaces on the substrate. The reason for this cannot be explained at this time but is being investigated.

The crystallographic texture of silicon on ceramic was determined by x-ray diffraction using the Laue method. Laue shots of individual grains were taken on samples MR45 and MR62. The surface of the coating was found to be predominately {331} with a growth direction of <211>. This texture permits a {111} twin plane to occur perpendicular to the substrate and propagate as the grain grows. This texture is similar to that observed in EFG ribbon silicon<sup>5</sup>.

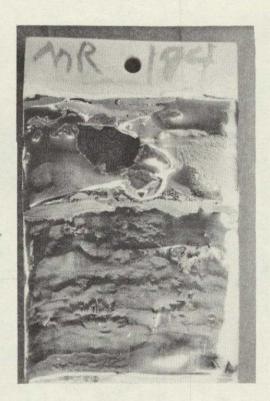

In an effort to promote large grain growth, four substrates were dipped with single-crystal Si seeds attached. Thin wafers of single-crystal Si were simply clamped to the substrate at the top edge of the carbon coating. The results can be seen in Figure 8 which shows the interface between the single-crystal seed and the ensuing silicon film. Although the desired result, single-crystal film growth, did not occur, the procedure shows promise. The seed-film junction is continuous, indicating that with a suitably oriented seed, large grain growth may be induced.

Dislocation density of the silicon coating was investigated using the etch pit technique. Figure 9 is an optical photomicrograph of the etched as-grown surface of sample MR114. Note that certain areas between twin boundaries are dislocation free. The dislocation count obtained from this surface was  $\sim 9 \times 10^6$  cm<sup>-2</sup>. Figures 10 and 11 show optical photomicrographs of polished and etched cross sections of sample MR114 taken parallel and perpendicular to the pulling direction; the dislocation counts from these two surfaces were  $\sim 8 \times 10^6$  and  $\sim 6 \times 10^6$  cm<sup>-2</sup>, respectively.

#### Carbonization

In an effort to identify alternative methods of carbonizing the ceramic, several different techniques were tried during the year. First, four mullite substrates which had a Vitre-Graf graphite coating on all surfaces were dip-coated. The coatings were prepared by

Figure 8. Seeded Si Sheet Growth. The seed in the trapezoidal shape at the top of photo (Wright etch, 2.5x).

Figure 9. Optical Micrograph (500x) of Etched As-Grown Surface (Sample MR114) Showing Dislocation Etch Pits

Figure 10. Optical Micrograph (500x)of Polished and Etched Cross Section of Silicon Coating, Sample MR114, Taken Parallel to Pulling Direction; Etch: Sirtyl; Time: 15 Sec.; Dislocation Count ~8 x 10<sup>6</sup> cm<sup>-2</sup>.

Figure 11. Optical Micrograph (500x) of Polished and Etched Cross Section of Silicon Coating, Sample MR114, Taken Parallel to Perpendicular Direction; Etch: Sirtyl; Time: 15 Sec.; Dislocation Count ~6 x 106cm-2.

Tylan Corporation and are reported to be  $\sim$ 7- $\mu$ m thick. The primary purpose for dip-coating these substrates was to evaluate the passivation capability of these particular graphite coatings in preventing dissolution of the mullite in the silicon melt. Since the resistivity of the silicon layer is a convenient method for obtaining the amount of mullite dissolved, thick (150-400  $\mu$ m) silicon coatings were grown on the substrates to improve the accuracy of the resistivity measurements.

The Vitre-Graf coatings are comparable in wettability to the rubbed-on graphite coatings typically used, but their rate of dissolution in molten silicon is considerably less. Part of the passivation study included soaking a Vitre-Graph coated mullite substrate in molten silicon for a period of one hour. Upon withdrawal of the substrate from the melt after this prolonged soaking, the substrate possessed a smooth, uniform silicon coating, thereby demonstrating the durability of these particular graphite coatings in molten silicon. By comparison, the rubbed-on graphite coatings completely dissolved in molten silicon in less than an hour.

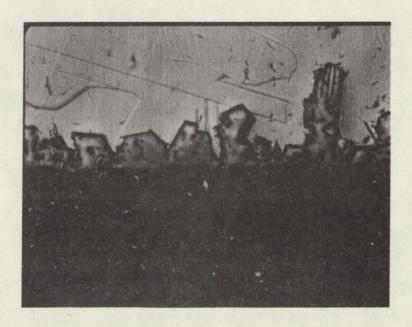

Due to the length of time the substrate was immersed in the molten silicon and the amount of carbon present a silicon carbide layer was formed and is shown in the photomicrograph of Figure 12. Although occasional carbide particles are seen in the silicon layers on hand-rubbed graphite, usually neither the time in the melt nor the amount of carbon present are sufficient to generate an observable layer.

Figure 12. Optical Micrograph (500X) of Silicon Carbide Layer on Vitre-Graf Coated Substrate MR78 that had been Soaked in Melt for 1 Hour.

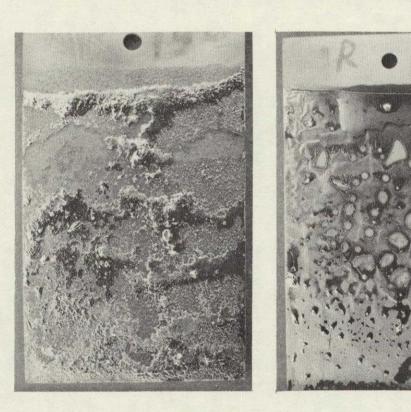

Five different liquid carbon coating compounds were purchased from Dylon Industries. These coatings had the viscosity of latex paint and were water soluble. A total of 22 substrates were dipped that had been coated with the various Dylon compounds. It was found necessary to oven dry these coatings, as residual moisture caused them to blister or "boil" off when dipped in the molten silicon, as shown in Figure 13. It was also noted that the granular nature of most of these coatings promoted nucleation which decreased the grain size, and that carbides formed throughout the Si layer. However, in cases where the granular surface was smoothed by wiping off the excess graphite and the coating was oven dried, the Dylon coatings gave large grain size similar to the hand-rubbed graphite coatings. Unfortunately our chemical analysis of these coatings has revealed that they contain from 1 to 2 percent impurities—a fact the vendor would not reveal—and are probably unsuited for our application.

Another somewhat novel method of carbon coating was also investigated - plasma decomposition of propane gas in an RF sputtering apparatus. The carbon is deposited uniformly and its purity reflects that of the gas. The morphology and grain size of the silicon film formed on such substrates is comparable to those on hand-rubbed graphite coatings.

Several methods of incorporating the carbonization with the ceramic processing were also examined. These were rolling graphite or silicon carbide particles into one surface of the substrate and then firing in an inert atmosphere or just firing the ceramic in an inert atmosphere so that the residue from the organic bonders would form a carbon film. Unfortunately none of these approaches worked with the dipped samples. The plain ceramic fired in an inert atmosphere shattered in the temperature gradient above the melt before it could be dipped. The substrate with silicon carbide developed large blisters and it appeared that the silicon did not wet the surface. The substrate with the graphite particles appeared to have been wet by the silicon, but either there wasn't sufficient carbon or the particles didn't stay embedded to permit the growth of a silicon layer.

Some very promising looking experiments have been conducted using colloidal carbon suspensions obtained from Acheson Colloids Co., Port Huron, Michigan. Four different mixtures are being tested; Dag 154, Electrodag 154, Electrodag 155, and Electrodag 502. The 154 mixtures are graphite in isopropyl alcohol with a dellulosic binder. Electrodag 155 is a mixture of graphite in trichlorethylene with a cellulosic binder. Electrodag 502 is a graphite and carbon black mixture in methyl ethyl ketone (2-butanone) with a fluro elastomer binder. Drying poses no problems and coating thickness is relatively easy to control.

Figure 13. Blistered and Spotty Si Film Formation as the Result of Incomplete Drying of Dylon Carbon Coatings (1.7x)

Spectrographic analysis shows that the dags should be suitable for solar cell application. The results of the analysis are shown in Table 3.

Table 3. Spectrographic Analysis Results of Colloidal Carbon Suspensions from Acheson Colloid Co., Values in ppm.

| Element | Dag 154* | Dag 154  | E'dag 502 | E'dag 154 | E'dag 155 |

|---------|----------|----------|-----------|-----------|-----------|

| AR      | 88       | ND < 10  | 110       | 20        | 33        |

| Мо      | 100      | ND < 33  | 34        | ND < 33   | ND < 33   |

| Sn      | 52       | ND < 10  | ND < 10   | ND < 10   | ND < 10   |

| Ca      | 180      | 43       | 68        | 39        | 56        |

| V       | 33       | ND < 33  | ND < 33   | ND < 33   | ND < 33   |

| Ti      | 24       | 8        | 53        | 7         | 8         |

| Ni      | 15       | 2        | 2         | 2         | 2         |

| Si      | 220      | 35       | 72        | 73        | 51        |

| Pb      | 35       | ND < 33  | ND < 33   | ND < 33   | ND < 33   |

| Mg      | 4        | 2        | 14        | 2         | 3         |

| В       | 3        | ND < 1   | 37        | ND < 1    | 3         |

| Mn      | 4        | 2        | 3         | 2         | 3         |

| Na      | 200      | ND < 100 | 270       | ND < 100  | ND < 100  |

| Fe      | 1500     | 260      | 370       | 285       | 290       |

<sup>\*</sup>Older stock.

The growth morphology of the silicon is not adversely affected by the dags. Metallographic examination of cross sections of silicon-on-ceramic which were carbonized with Dag 154 showed excellent wetting of and bonding to the ceramic surface by the silicon as shown in Figure 14.

Because of the ease of application of the dag mixtures they are now used instead of hand-rubbed graphite to carbonize the ceramic. The dags also lend themselves to conducting carbon doping experiments with the intention being to use the doped carbon layer as a back contact. For this purpose, boron silicate - Dag 154 mixtures were applied to several substrates and dipped. The silicon coatings appeared no different from those on undoped dag and will be fabricated into diodes and cells for further evaluation.

Figure 14. Silicon-Ceramic Interface Carbonized with Dag 154 (500x)

In general, from our experiments, it appears that any means of applying a smooth, uniform, dense coating of carbon of suitable thickness and purity will promote the coating of ceramic with silicon.

ORIGINAL PAGE IS OF POOR QUALITY CONTINUOUS-COATING FACILITY (J. D. Heaps, C. D. Butter, L. D. Nelson and H. A. Wolner)

### Introduction

During this reporting period a continuous-coating facility was designed and at this reporting date its construction is 95 percent completed. It was scheduled to be in operation on 27 September, but due to a scheduling error on the part of the power supply vendor, its operational date has been delayed for two weeks.

This newly constructed facility described below is expected to overcome some of the inherent problems of the dip-coating technique. Its principal advantages are as follows:

- Its coating principle vastly reduces the area of, and the time that the substrate is in contact with the silicon melt. This feature lessens the possibility of the melt being progressively contaminated by the substrate.

- 2.) The new facility permits the use of much larger substrates which should allow the individual crystalline grains to develop larger in size.

- 3.) The scale-up coating through-put of this new technique is potentially superior because it eliminates the dipping and soaking time required with the dip-coating technique.

- 4.) The thermal stability of the solidification zone of the continuous coater should also be superior to the dip-coater since its melt temperature will not be constantly upset by the immersion of unheated substrates.

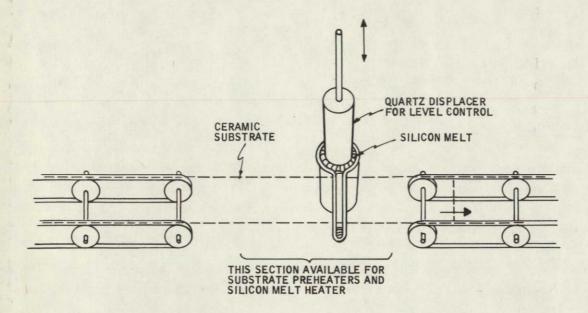

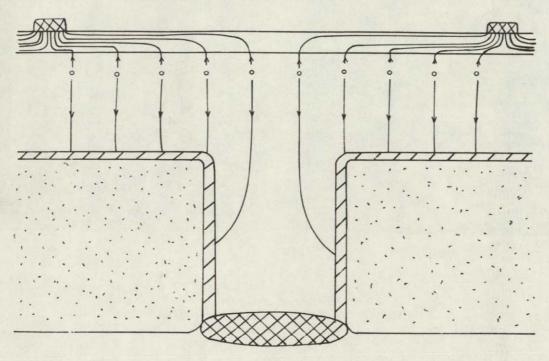

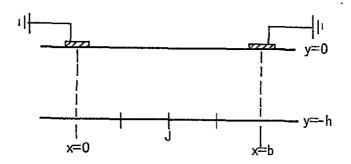

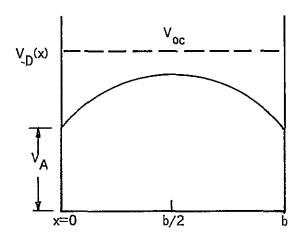

The principle of the continuous coating concept is shown in Figure 15. Graphite-coated ceramic substrates are passed over a silicon-filled side arm of a crucible containing molten silicon. The level of the molten silicon is adjusted so that the surface of the liquid silicon bulges up above the walls of the side arm. The path that the substrate takes over the side arm is such that it comes in contact with the molten silicon but does not touch the walls of the side arm. It is expected that with an appropriate temperature gradient in the solidification zone that the resulting liquid solid interface will be similar to that of the dip coating method and that silicon will continue to nucleate from previously grown silicon.

Figure 15. Silicon Coating by Inverse Meniscus (SCIM)

## Description of Continuous-Coating Facility

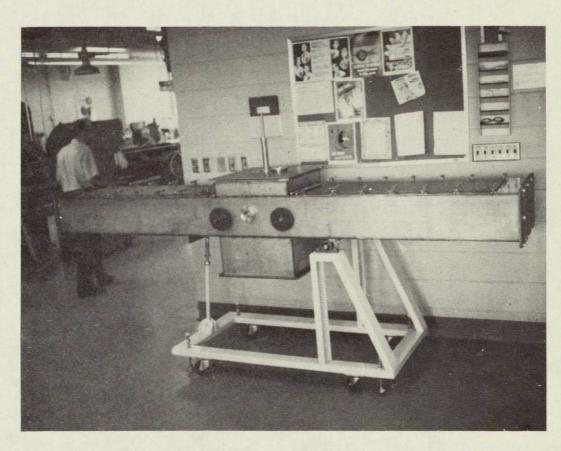

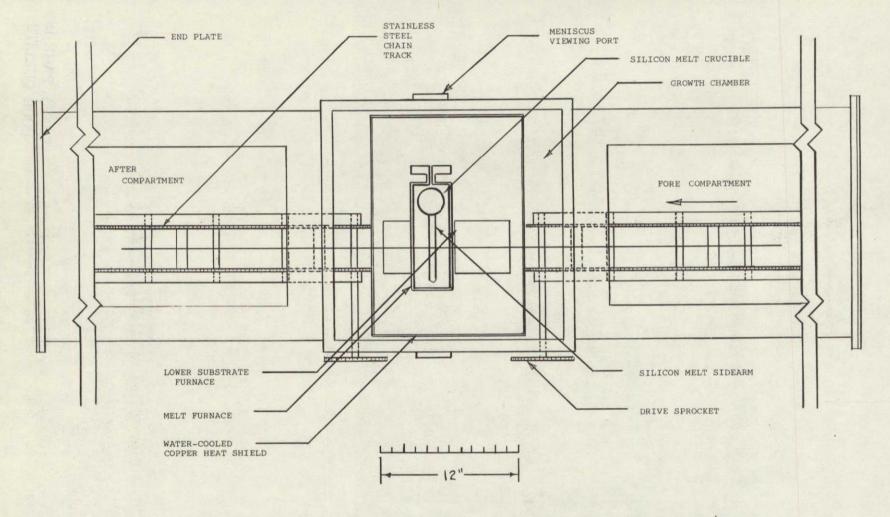

Figure 16 is a photograph of the coater component of the continuous-coating facility. As shown in Figure 17 the coater is divided into three sections: (1) a fore compartment (for substrate loading), (2) a growth chamber (for silicon coating) and (3) an after compartment (for substrate removal). The coater permits 10 cm x 100 cm graphite coated ceramic substrates to pass (coated face down) over a silicon-filled trough-like quartz side arm which is attached to a crucible containing molten silicon (Figure 17). The level of the molten silicon is adjusted so that the surface of the liquid forms a meniscus above the walls of this quartz side arm. As molten silicon in this side arm is used up, it will be automatically replenished by a quartz plunger which displaces the silicon in the main crucible (see Figures 18 and 19). The position of this plunger will be controlled by the use of a laser beam whose path to a light sensor will be interrupted by the silicon meniscus in the side arm when the desired silicon level is achieved.

The growth chamber of the facility is surrounded by a water-cooled copper box (see Figure 17). Three separately controlled graphite furnaces provide temperature zones to perform the following functions:

<sup>\*</sup>Note: This photograph was taken prior to the coater's present state of completion. Reporting time did not permit a current photograph.

Figure 16. Photograph Showing Early Construction Status of Continuous Coater

Figure 17. Exposed top view of continuous coating facility (Top covers are removed and upper substrate furnace and carbon felt insulation are not shown).

Figure 19. Top and side view of continuous coating facility.

- 1. Gradually heat the substrate to the coating temperature.

- 2. Control the temperature of the molten silicon in the main crucible and side arm.

- Provide, as needed, the temperature profile required for desirable crystalline solidification and minimum thermal stress.

The first and second zones are individually powered by SCR-regulated 0-30 Volt. 0-1500 amp, d-c power supplies. Their temperatures are also individually controlled by Honeywell three-mode controllers. The third zone is powered and temperature controlled by a Honeywell Electrodyne-controlled power supply. Each of these furnaces is surrounded by insulating blocks of graphite and carbon felt. Viewing ports are provided for observation of the main crucible during melt-down and for viewing the silicon meniscus in contact with the substrate (see Figure 19).

The inert gas-filled enclosure which houses the growth chamber also includes fore and after compartments for handling uncoated and coated substrates. These compartments contain stainless-steel chain conveyors which carry the substrates to, through, and from the growth chamber. The chain conveyors are driven by a "Digilok" controlled variable-speed drive system which is adjustable for growth velocities of tenths of mm/ sec to many cm/sec. Given an ideally flat substrate, the fore and after chain conveyors are spaced to allow the substrate's center of gravity to carry it from one conveyor to the other. For substrates that are less than flat, rollers assist in positioning the substrate. Until the growth parameter's are established for producing acceptable crystalline silicon coatings, several substrates to be silicon coated will be loaded into the facility's fore compartment (see Figures 17 and 19) via the top opening. They will subsequently be placed on and removed from the chain conveyors using "dry box"-type rubber gloves which are installed in the coater's end plates. Once proper growth parameters have been established, the end plates on the fore and after compartments will be replaced with plates that permit substrates to pass through with a minimum of inert gas leakage.

While the facility was primarily designed to horizontally coat substrates, provision has been made for tilting the entire facility through about  $\pm$  30 degrees. With minor modifications the facility can be adapted to vertically coat substrates. Vertical coating does, however, place a more severe requirement on substrate flatness.

MATERIAL EVALUATION AND SOLAR CELL FABRICATION (J. D. Zook, T. Schuller, R. Hegel, C. Knudson, and A. Peterson)

# Chemical Characterization of SOC

During the first year of the contract it was established by IR spectroscopy at low temperatures that the mullite does contribute aluminum to the melt. Although other techniques for identifying trace impurities have been investigated during the past year, none of these; has been very satisfactory. The studies performed are summarized below.

Neutron activation analysis--Neutron activation analysis was performed by General Activation Analysis, Inc., of San Diego. Samples were prepared from the top edge of the melt (first to solidify) for melts 16, 27 and 28, and a multi-element survey was performed. The result was that no impurities were detected in melts 16 and 28, whereas, in sample 27 Mn, Sm, Na, La, Eu and Br were detected at the ppma level, as shown in Figure 20. This finding makes sense since melt 27 was one in which MV20 mullite had been dipped for over an hour. Melt 16 was boron-doped with no dipping, and melt 28 was a contamination check with no boron doping or dipping. The disappointing aspect of this is that the elements of interest, namely Al, B, P, Fe, Ti and V, cannot be detected in Si at the ppma level by this technique.

Ion Beam Microprobe--Analyses were performed by McCrone Associates of Chicago, Ill. and Applied Research Laboratores (ARL) in Sunland, Ca. The analyses were found to be very sensitive, but were very sensitive to contamination. The impurites B, C, Na, Mg, Al, P, K, Ca, Ti, V, Cr, Fe, Ta, and Pb were found. The quantities of Na, K, and Ta were significantly greater than upper limits found by neutron activation analysis. On the other hand, Fe, Mu, Mg, Ca, Na, Ti and Vare known to be present in the ceramic from emission spectrographic analysis.

Several diode areas were examined in the imaging mode using the IMMA machine at ARL. One region was selected as having a fairly large-angle grain boundary and a region of irregular surface texture, indicating small crystal size. This area was sputtered to a depth such that most of the n<sup>+</sup> phosphorus-diffused layer had been removed. After profiling, the area still showed some mass 27 (Al), 31 (P), 48 (Ti), and 54 (Fe). Images taken with a 10 µm ion beam showed no preferential distribution of any of these impurities.

In general, all of the search for segregation at grain boundaries by this technique gave negative results. The only images which showed nonuniform distribution of impurities were on surfaces that had not been sputtered. Sample MR105 showed clustering of masses 23 (Na), 27 (Al), 48 (Ti), and 54 (Fe7). These did not appear to correlate with structural features.

| OF PO        | ORIGINAL      | SILI          | CON | SAMPI   | _E 27    | FOR J (             | DAVID ZOC         | ) K      | HONEYWELL (           | ) E C           | 197          | 6           |             |

|--------------|---------------|---------------|-----|---------|----------|---------------------|-------------------|----------|-----------------------|-----------------|--------------|-------------|-------------|

| d<br>d       | IGNAL PAGE IS |               | ε   | LEME    | NT<br>(P | CONCENT<br>ARTS PER | RATION<br>MILLION | }        | PRECISION<br>(* OR -) |                 |              |             |             |

| á            | PAGE          |               |     | мΝ      |          | •                   | 092600            |          | .019000               |                 |              |             |             |

|              | A E           |               |     | 54      |          |                     | 060300            |          | .012000               |                 |              |             |             |

|              | 自品            |               |     |         |          |                     |                   |          |                       |                 |              |             |             |

|              | TA ES         |               | NA  |         |          |                     | •685000           |          |                       | <b>.</b> 140000 |              |             |             |

|              |               | •             |     | LA      |          | •                   | 051700            |          | .012000               |                 |              |             |             |

|              |               |               |     | εIJ     |          |                     | 000912            |          | .000340               |                 |              |             |             |

|              |               |               |     | 88      |          |                     | 052400            |          | .013000               |                 |              |             |             |

|              |               |               |     |         |          | •                   |                   |          |                       |                 |              |             |             |

| ELEMENT      | U             | PPER LIMIT    |     | ELEMENT |          |                     | ELEM              | ENT      |                       | EL              | ELEMENT      |             |             |

|              | (PART         | S PER MILLION | }   |         |          |                     | •                 |          |                       |                 |              |             |             |

| ΑG           | ď.            | 3.500000      |     | FE      | <        | 190.0000            | 9N 00             | <        | 1100.00000            | )               | 51           | <+          |             |

| AL           | <•            |               |     | G A     | <        | .10000              | מאַ סכ            | <        | •99000                | 5               | SM           | < e         | ****        |

| AR           | <             | .340000       |     | GD      | <        | 1.10000             | )0 NE             | <        |                       | •               | S N          | <           | 75.000000   |

| AS           | <             | •039000       |     | GΕ      | <        | 12.00000            | 1N 00             | <        | 21 • 000000           | ]               | SR           | <           | 3.400000    |

| ΔU           | <             | .001100       |     | HF      | <        | •14000              |                   | <        |                       | •               | TA           | <           | .047000     |

| B A          | <             | 7.200000      |     | HG      | <        | •0750               |                   | <        | •170000               | )               | T B          | <           | .030000     |

| BR           | <+            |               |     | ΗO      | <        | .0140               | •                 | <        |                       | •               | TE           | <           | 3.400000    |

| CA           | <             | 5500.00000    |     | 1       | <        | 1.40000             |                   | <        | 5900+000000           | 3               | TH           | <           | .180000     |

| CD           | <             | .670000       |     | 1 1/1   | <        | *0041               | ) P P P           | <        | •120000               | 3               | TI           | <+          |             |

| CΕ           | <             | .720000       |     | I R     | <        | •0015(              | )O PR             | <        | •720000               | )               | TL           | <           | 2700,000000 |

| CL           | ٠ <           | 2.300000      | -   | K       | <        | 5.00000             |                   | <        | • 330000              | 3               | ŢΜ           | <           | *100000     |

| C Q          | <             | . 290000      |     | ΚR      | <        | 13.00001            | )O Re             | <        | A • 90000             | )               | U            | <           | .057000     |

| CR           | <             | 1+700000      |     | LA      | <        | 00000000            | P RE              | . <      | •009100               | )               | ٧            | <           | 4700.000000 |

| C S          | <             | .350000       |     | Ľθ      | <        | •01200              | 00 R+             | -        |                       | •               | ₩            | <           | .028000     |

| ςU           | <             | .120000       |     | MG      | < 71     | 000 <b>.000</b>     | DO RU             | <b> </b> | 1.600000              | )               | XΕ           | <           | 2.800000    |

| DY           | <             | .250000       |     | ΜN      | <        | S P 4 O B 4 C B C   | • 5               | <        |                       | •               | Y            | <           | 480.000000  |

| ER           | <             | .380000       |     | M O     | <        | •53000              | )O 58             | <        | •023000               | )               | YB           | <           | .058000     |

| ٤U           | < •           |               |     | N       | <        |                     | 50                | ` <      | •018000               | 3               | ΖN           | <           | 5.100000    |

| F            | <             | 45000.000000  |     | ŊΑ      | <        | Q + + 0 0 0 0 = + 1 | 5 5               |          | •510000               | 2               | ZR           | <           | 37,000000   |

|              | 0 • • • • • · | INDICATES     | THE | UPPI    | ER LI    | MIT COUL            | NOT BE            | CO       | HPUTED                |                 |              |             |             |

| <del>-</del> | ,             | -             | -   |         |          |                     |                   |          | HERAL ACTIVA          | fint            | ı Aı         | AL'         | YSISI INC   |

|              |               |               |     |         |          |                     |                   | υ£       | MERAL MOISE           | ,               |              | , p.        | nan * 214   |

|              |               |               |     |         |          |                     |                   | 1 1      | 575 SGRRENTO          | VAL             |              | , A.        | 92121       |

|              |               |               |     |         |          |                     |                   |          | SAN DIEGO. C          | NL 1            | י טאי<br>סכר | 41 A<br>-6: |             |

|              |               |               |     |         |          |                     |                   |          | PHONE 7               | 14/             | /55          | -51         | ۷,          |

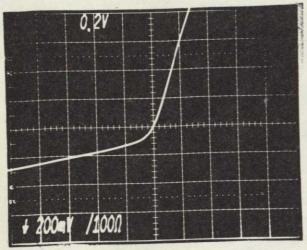

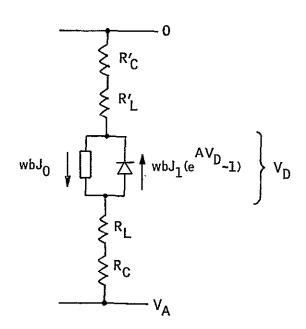

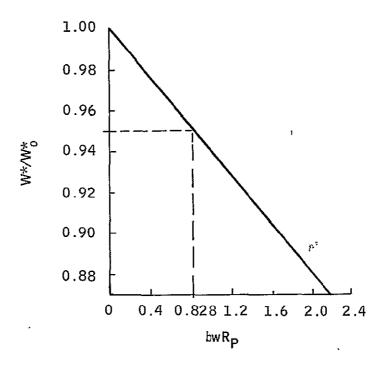

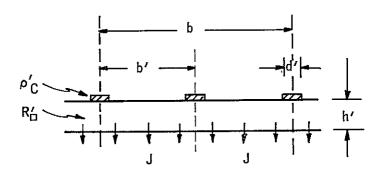

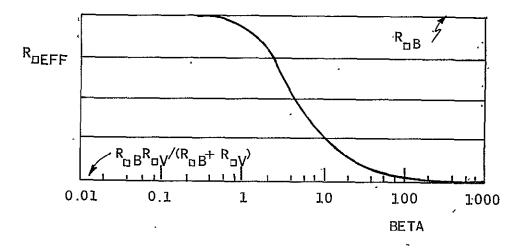

Figure 20. Multi-Element Survey of Melt 27 by Neutron Activation Analysis