CR-135358 TRW 31526, 000

# EXTENDED PERFORMANCE ELECTRIC PROPULSION POWER PROCESSOR DESIGN STUDY

### FINAL REPORT

## **VOLUME II TECHNICAL SUMMARY**

## **NOVEMBER 1977**

by:

## TRW DEFENSE AND SPACE SYSTEMS GROUP POWER CONVERSION ELECTRONICS DEPARTMENT

Prepared For:

# NATIONAL AERONAUTICS AND SPACE ADMINISTRATION NASA LEWIS RESEARCH CENTER

CONTRACT NAS 3-20403

(NASA-CR-135358) EXTENDED PERFORMANCE

ELECTRIC PROPULSION POWER PROCESSOR DESIGN

STUDY. VOLUME 2: TECHNICAL SUMMARY Final

Report, 1 May - 25 Oct. 1977 (TRW Defense

and Space Systems Group) 156 p

Unclas G3/20 25923

# EXTENDED PERFORMANCE ELECTRIC PROPULSION POWER PROCESSOR DESIGN STUDY

FINAL REPORT

VOLUME II TECHNICAL SUMMARY

**NOVEMBER 1977**

by:

TRW DEFENSE AND SPACE SYSTEMS GROUP POWER CONVERSION ELECTRONICS DEPARTMENT

Prepared For:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA LEWIS RESEARCH CENTER

CONTRACT NAS 3-20403

|          |                                                                                                                                                                        |                        |                                                  |                                | ·                |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------|--------------------------------|------------------|--|--|

| 1        | Report No                                                                                                                                                              | 2 Government Access    | ession No 3 Recipient's Catalog No TRW 31526 000 |                                |                  |  |  |

|          | CR-135358                                                                                                                                                              |                        |                                                  |                                |                  |  |  |

| 4        | Title and Subtitle                                                                                                                                                     |                        |                                                  | 5 Report Date<br>November 1977 |                  |  |  |

|          | Extended Performance Electric Pr                                                                                                                                       |                        | rocessor Design                                  | 6 Performing Organiza          |                  |  |  |

|          | Study Volume II Technical Summary                                                                                                                                      |                        |                                                  | o renorming Organiza           | ation code       |  |  |

|          |                                                                                                                                                                        |                        | 0 P-f 0                                          |                                |                  |  |  |

| 7        | Author(s)                                                                                                                                                              | D. Cabaanfald          |                                                  | 8 Performing Organiza          | tion Report No   |  |  |

|          | J J Biess, L Y Inouye, & A D Schoenfeld                                                                                                                                |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        | 1                                                | 10 Work Unit No                |                  |  |  |

| 9        | Performing Organization Name and Address                                                                                                                               | -aun                   |                                                  |                                |                  |  |  |

|          | TRW Defense and Space Systems Group Power Conversion Electronics Department                                                                                            |                        |                                                  | 11 Contract or Grant           | No               |  |  |

|          | Redondo Beach, CA 90278                                                                                                                                                |                        |                                                  | NAS3-20403                     |                  |  |  |

|          |                                                                                                                                                                        |                        | h                                                | 13 Type of Report an           | d Period Covered |  |  |

| 12       | Sponsoring Agency Name and Address                                                                                                                                     | ·                      |                                                  | 1 May 77 - 25                  |                  |  |  |

|          | National Aeronautics and Space A                                                                                                                                       | \dministration         | <u> </u>                                         |                                |                  |  |  |

|          | Lewis Research Center                                                                                                                                                  | Ohao 44325             |                                                  | 14 Sponsoring Agency           | Code             |  |  |

|          | 21000 Brookpark Road, Cleveland,                                                                                                                                       | , 0/110 44135          |                                                  |                                |                  |  |  |

| 15       | Supplementary Notes                                                                                                                                                    |                        |                                                  |                                |                  |  |  |

| l        | project Manager Robert J Frye                                                                                                                                          | e, NASA Lewis Rese     | earch Center, Clevel                             | and, Ohio 44135                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| L.       |                                                                                                                                                                        | <del> </del>           |                                                  |                                |                  |  |  |

| 16       | Abstract                                                                                                                                                               |                        |                                                  |                                |                  |  |  |

| Ì        | Electric Propulsion Power Proces                                                                                                                                       | ssor_Technology_ha     | as processed during                              | the past decade                | to the point     |  |  |

|          | that it is considered ready for concepts were evaluated and comp                                                                                                       | application Dur        | ring this study, sev                             | eral power proce               | ssor design      |  |  |

|          | with a Beam Power Rating Supply                                                                                                                                        | of 2 2KW to 10KW       | for the main propul                              | sion power stage               | Extensions       |  |  |

|          | in power processor performance v                                                                                                                                       | vere defined and w     | were designed in suf                             | ficient detail t               | o determine      |  |  |

|          | efficiency, component weight, part count, reliability and thermal control                                                                                              |                        |                                                  |                                |                  |  |  |

|          | A detail design was performed on a microprocessor as the thyristor power processor controller                                                                          |                        |                                                  |                                |                  |  |  |

| <b>i</b> | A reliability analysis was performed to evaluate the effect of the control electronics redesign                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| ŀ        | A Preliminary electrical design, mechanical design and thermal analysis were performed on a 6KW power transformer for the beam supply                                  |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

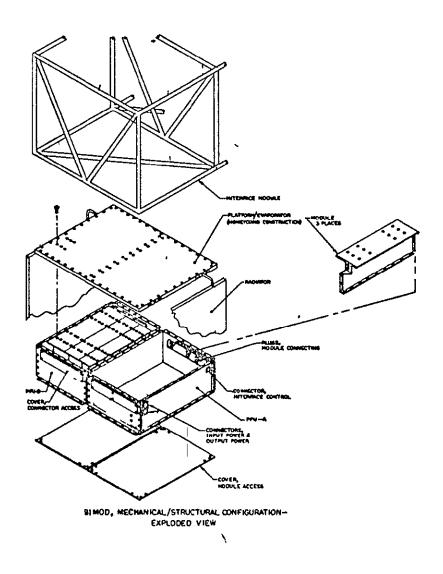

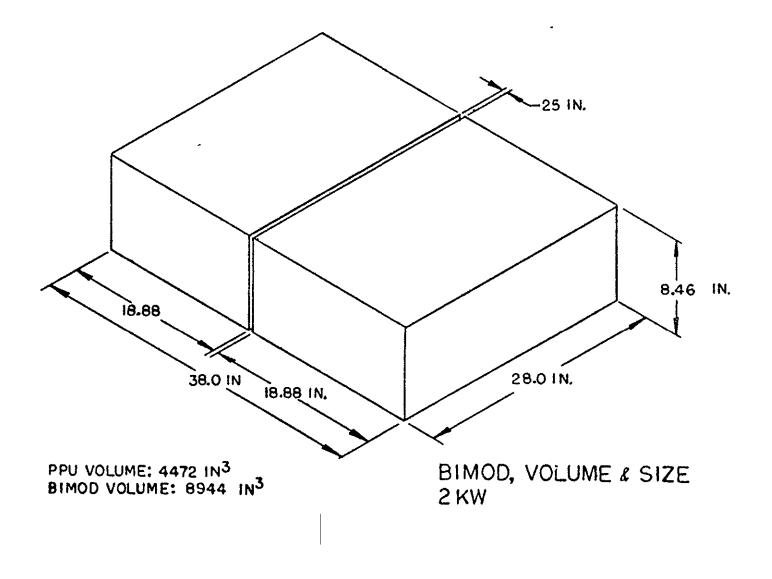

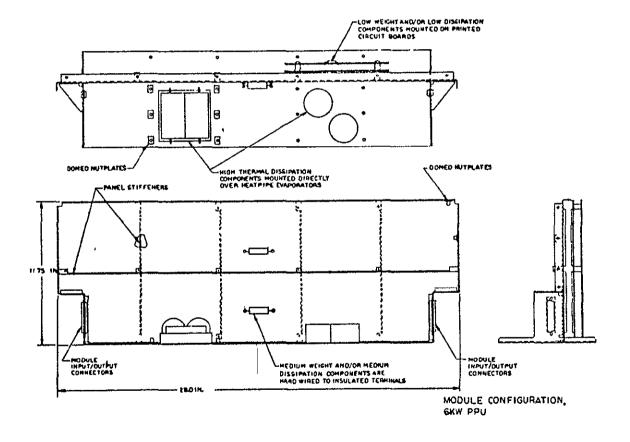

|          | Bi-Mod mechanical, structural and thermal control configurations were evaluated for the power processor and preliminary estimates of mechanical weight were determined |                        |                                                  |                                |                  |  |  |

| 1        | brocessor and bretimmary eseme                                                                                                                                         | ves or meenanied       | . weight were determ                             | meu                            |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                | <b>\</b>         |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| 1        |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| 17       | Key Words (Suggested by Author(s))                                                                                                                                     | <del></del>            | 18 Distribution Statement                        |                                |                  |  |  |

| 1        | Solar Electric Propulsion                                                                                                                                              |                        |                                                  |                                |                  |  |  |

|          | Power Processor                                                                                                                                                        | •                      |                                                  |                                |                  |  |  |

|          | Series Resonant Inverter                                                                                                                                               |                        |                                                  |                                |                  |  |  |

|          |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| L        |                                                                                                                                                                        |                        |                                                  |                                |                  |  |  |

| 19       | Security Classif (of this report)                                                                                                                                      | 20 Security Classif (c | f this page)                                     | 21 No of Pages                 | 22 Price*        |  |  |

|          | Unclassified                                                                                                                                                           | Unclassified           |                                                  |                                |                  |  |  |

|          | Olivianalitied                                                                                                                                                         | 0110103311160          |                                                  |                                | <u></u>          |  |  |

<sup>\*</sup> For sale by the National Technical Information Service, Springfield, Virginia 22151

### FORWARD

The work described herein was performed in the Power Conversion Electronics Department of the Electrical System Laboratory within the Space Systems Division of TRW Defense and Space Systems Group. This department is managed by Mr. Bert J. McComb. The work was funded under contract NAS 3-20403 and monitored by Mr. Robert Frye of the NASA Lewis Research Center. The key technical contributors were:

| J. J. Biess      | Study Manager and Project Systems<br>Engineer                               |

|------------------|-----------------------------------------------------------------------------|

| L. Y. Inouye     | Project Engineer for Power Electronics                                      |

| M. C. Chester    | Project Engineer for Power Magnetics and Power Components                   |

| Efren Mendez     | Project Engineer for Mechanical Design and Power Magnetic Mechanical Design |

| Chuck Louie      | Project Engineer for Digital Interface<br>Unit Microprocessor               |

| Bernîe Shupack   | Project Engineer for Thermal Control of Power Processor and Power Magnetics |

| Bob Heile        | Project Engineer for Reliability                                            |

| A. D. Schoenfeld | Technical and Project Review                                                |

| M. G. Monegan    | Mechanical and Thermal Design Review                                        |

#### SUMMARY

The primary objective of this study was to provide a data base for a program plan for the development of the ion propulsion power processor to support a Halley's Comet Rendezvous Mission. This data base was to include:

- Conceptual design and tradeoffs for an electric propulsion power processor with a power rating up to 10kW beam power.

- Identification of New Technology Requirements and potential savings and risks.

- Selection of a preferred Power Processor Configuration.

- Preliminary Electrical and Mechanical Design of the preferred configuration.

- Program plan for the electric propulsion power processor in support of a Halley Comet Rendezvous Mission.

A preferred configuration for the power processor was selected as a result of detailed analysis of the data base. A complete electrical design was performed for a 6kW and 2.2kW beam supply power processor based on a revised power processor requirement specification and updated electrical design for product improvement in the area of part count reduction, weight reduction and efficiency improvement.

A discussion is presented on the electrical redesign of control electronics and microprocessor for thruster operation. The beam power transformer design is presented with the thermal analysis. A preliminary reliability analysis was performed.

A presentation is made for a method to determine the power processor weight efficiency optimization tradeoff. The accuracy of the optimization is determined by the solar array power vs. weight constant and by the thermal control heat rejection system weight vs. loss constant.

A conceptual mechanical design was performed to identify the electrical, structural and thermal interfaces.

The following is a summary of the 6KW beam power processor design characteristics:

| Electrical | component weight          | 21.3KG |

|------------|---------------------------|--------|

| Electrical | component losses          | 605W   |

| Efficiency | at nominal load           | 91.5%  |

| Part count |                           | 2720   |

| Mechanical | packaging hardware weight | 21.0KG |

|            |                           |        |

Volume . .107 cu meter

The following is a summary of the 2.2KW beam power processor design characteristics:

| Electrical component weight          | 14.4KG |

|--------------------------------------|--------|

| Electrical component loss            | 333W   |

| Efficiency at nominal load           | 89.2%  |

| Part count                           | 2587   |

| Mechanical packaging hardware weight | 14 4KG |

| W-3                                  | 070    |

Volume .073 cu meter

The designs were based on existing component technologies and therefore the technical risks were minimal and would not compromise the overall program schedule.

A detailed program plan schedule and cost estimate in support of the Halley Comet Rendezvous Mission are contained in Volume I, Executive Summary.

## TABLE OF CONTENTS

|      |                                              | Page No. |

|------|----------------------------------------------|----------|

| FORW | ARD .                                        | 1        |

| SUMM | IARY                                         | iı       |

| TABL | E OF CONTENTS                                |          |

| 1.0  | INTRODUCTION                                 | 1        |

| 2.0  | DESIGN TRADEOFF STUDIES                      | 3        |

| 2.1  | Power Distribution System                    | 3        |

| 2.2  | Beam Supply Tradeoff Analysis                | 8        |

| 2.3  | Discharge Supply Tradeoff Analysis           | 12       |

| 2.4  | Low Voltage Supplies Tradeoff Analysis       | 15       |

| 2.5  | Power Processor Configuration Tradeoff       | 20       |

| 2.6  | Power Process Weight-Efficiency Optimization | 26       |

| 3.0  | BASELINE DESIGN                              | 29       |

| 3.1  | Power Distribution System                    | 29       |

| 3.2  | Command System                               | 34       |

| 3.3  | B1-Mod Configuration                         | 36       |

| 3.4  | Power Processor Block Diagram                | 40       |

| 3.5  | Electrical Design                            | 44       |

| 3.6  | Reliability Estimate                         | 93       |

| 3.7  | Beam Power Transformer                       | 108      |

| 3.8  | Beam Power Transformer Thermal Analysis      | 115      |

| 3.9  | Conceptual Mechanical Design                 | 134      |

| 4.0  | RISK ASSESSMENT                              | 143      |

| 4.1  | Critical Technologies                        | 143      |

| 4.2  | Potential Problem Areas                      | 144      |

| 5.0  | CONCLUSIONS                                  | 145      |

|                                                                                                                                                            | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2-1<br>200-400VDC Power Distribution System                                                                                                         | 4    |

| Figure 2-2<br>200-400VDC and 28VDC Power Distribution System                                                                                               | 5    |

| Figure 2-3 Schematic of the Thyristor full Bridge Series Resonant Beam Inverter                                                                            | 9    |

| Figure 2-4 Schematic of the Thyristor half Bridge Series Beam Inverter                                                                                     | 10   |

| Figure 2-5<br>Schematic of Transıstorized Brıdge Series Resonant<br>Dıscharge Inverter                                                                     | 13   |

| Figure 2-6 Schematic for half Bridge 50KHZ Series Resonant Inverter for the Low Voltage Supplies                                                           | 16   |

| Figure 2-7 Schematic of Transistorized 50KHZ Series Resonant Inverter Configuration to supply low voltage outputs for two Thruster in Bi-Mod Configuration | 17   |

| Figure 2-8 Schematic of Buck/Boost DC-DC Converter for typical low voltage supply                                                                          | 18   |

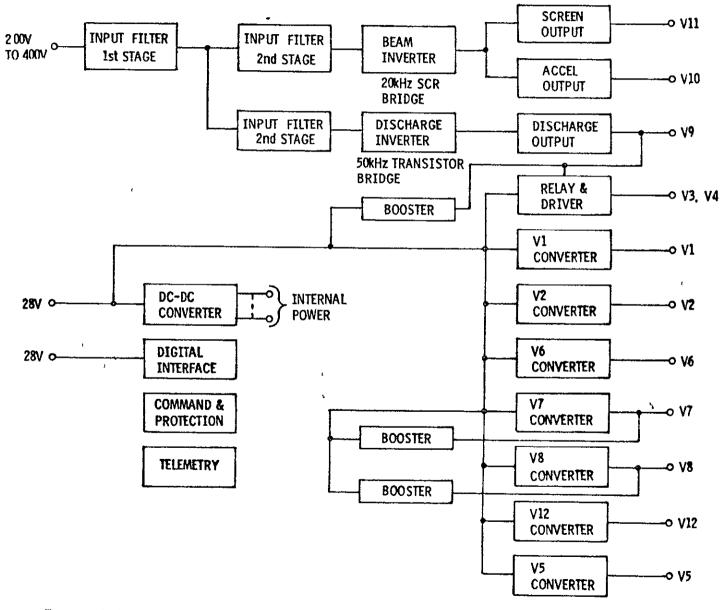

| Figure 2-9 Power Processor Block Diagram (200-400 VDC Input)                                                                                               | 21   |

| Figure 2-10 Power Processor Block Diagram (200-400VDC and 28VDC Input)                                                                                     | 22   |

| Figure 2-11 Power Processor Weight-Efficiency Optimization                                                                                                 | 27   |

| Figure 3-1 Power Distribution System Block Diagram                                                                                                         | 30   |

| Figure 3-2<br>Schematic of DC-DC Converter used to general<br>28VDC Power Bus                                                                              | 31   |

| Figure 3-3 Command System Block Diagram                                                                                                                    | 35   |

|                                                                                     | <u>Page</u> |

|-------------------------------------------------------------------------------------|-------------|

| Figure 3-4 B1-Mod Configuration Block Diagram                                       | 37          |

| Figure 3-5 Bi-Mod Interface Unit Configuration                                      | 38          |

| Figure 3-6 Electric Propulsion Power Processor Block Diagram                        | 41          |

| Figure 3-7<br>Power Processor Grounding System Block<br>Diagram                     | 42          |

| Figure 3-8<br>Input Filter                                                          | 45          |

| Figure 3-9<br>6KW Bridge Series Resonant Invertes                                   | 48          |

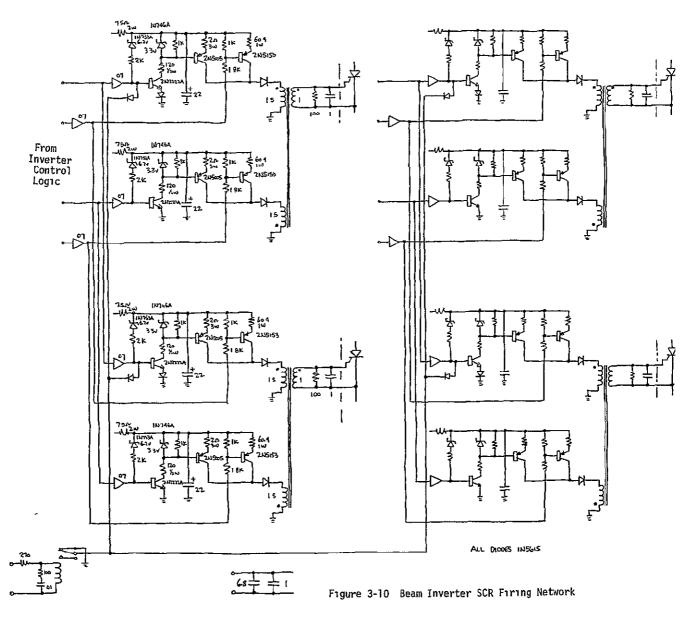

| Figure 3-10<br>Beam Inverter SCR Firing Network                                     | 49          |

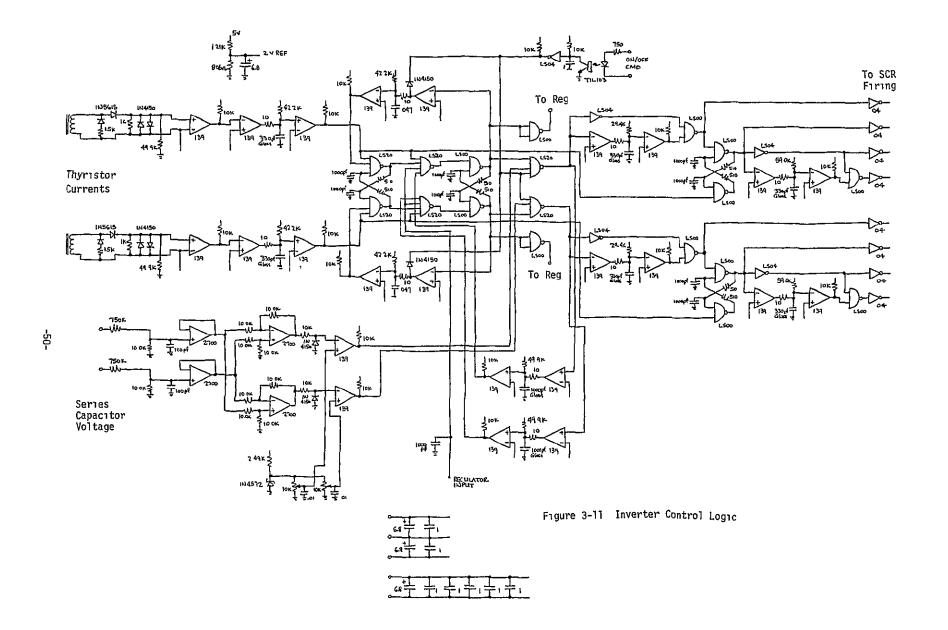

| Figure 3-11<br>Inverter Control Logic                                               | 50          |

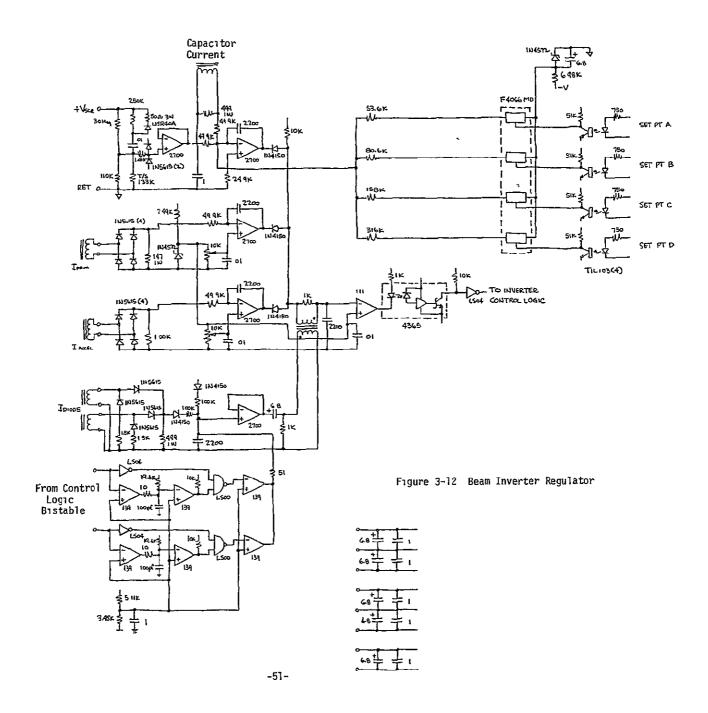

| Figure 3-12<br>Beam Inverter Regulator                                              | 51          |

| Figure 3-13<br>Discharge Inverter Power Stage                                       | 54          |

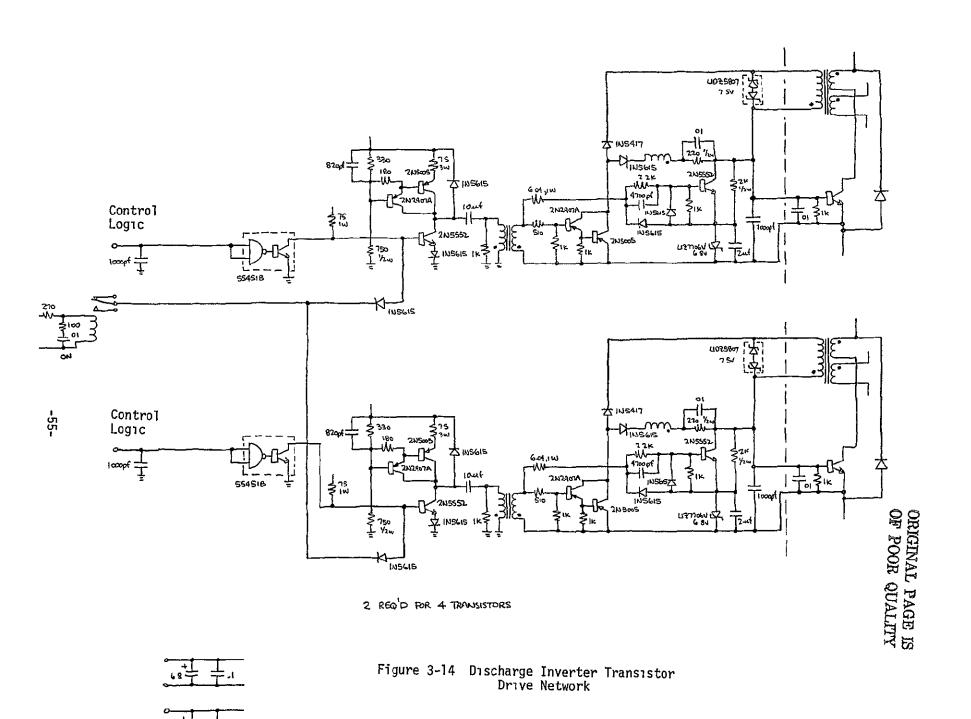

| Figure 3-14<br>Discharge Inverter Transistor<br>Drīve Network                       | 55          |

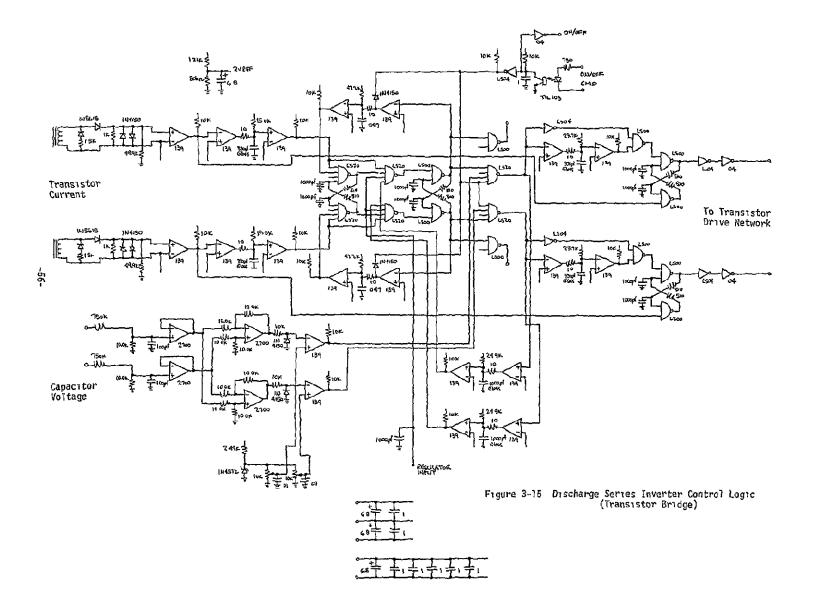

| Figure 3-15<br>Discharge Inverter Control Logic                                     | 56          |

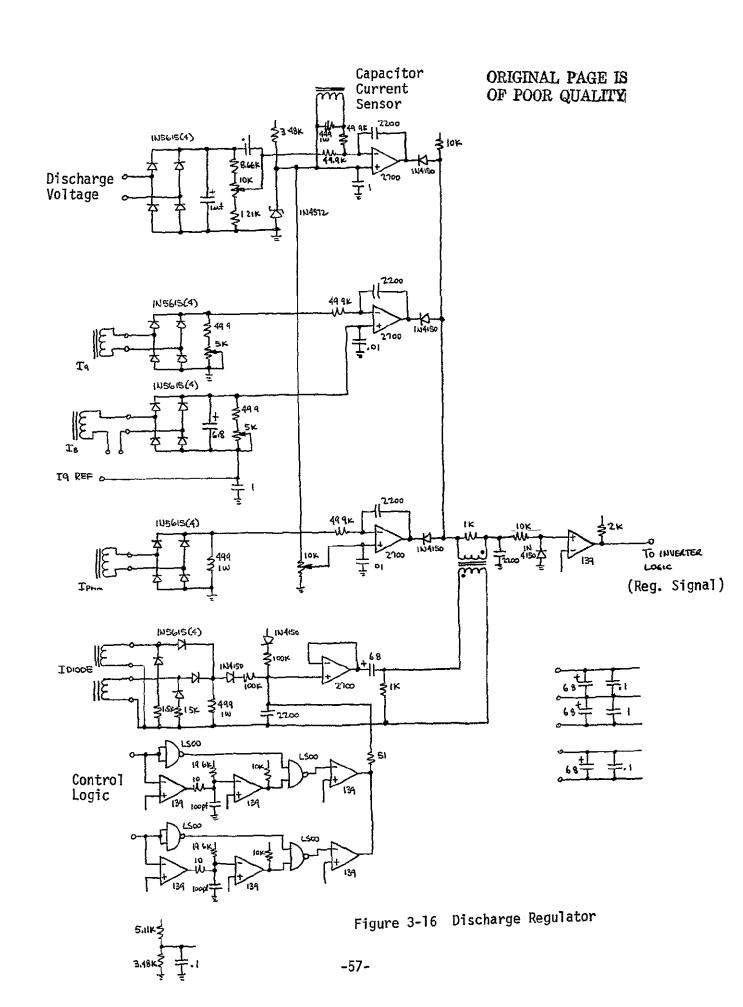

| Figure 3-16<br>Discharge Regulator                                                  | 57          |

| Figure 3-17<br>Dıscharge Booster Converter                                          | 58          |

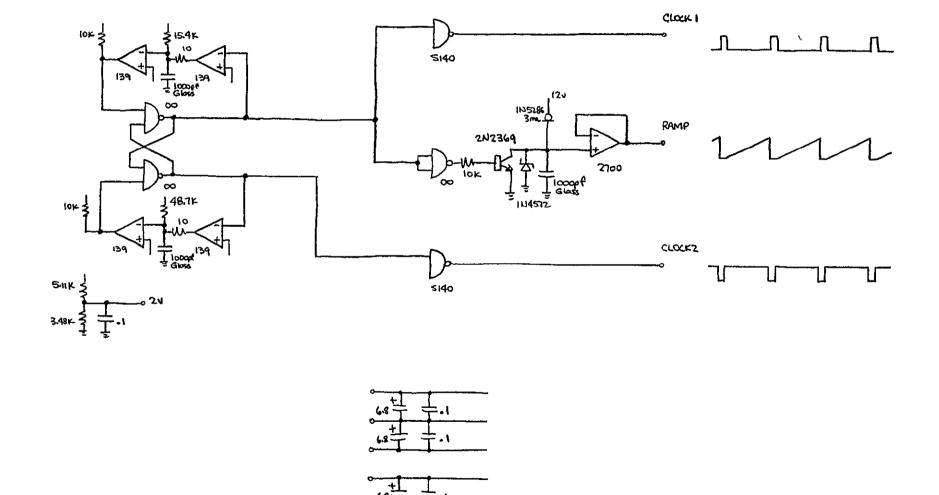

| Figure 3-18<br>Multiple Buck/Boost Converter<br>Master Osillator and Ramp Generator | 61          |

| Figure 3-19<br>Vi Output                                                            | 62          |

| Engues 2, 20                                           | Page |

|--------------------------------------------------------|------|

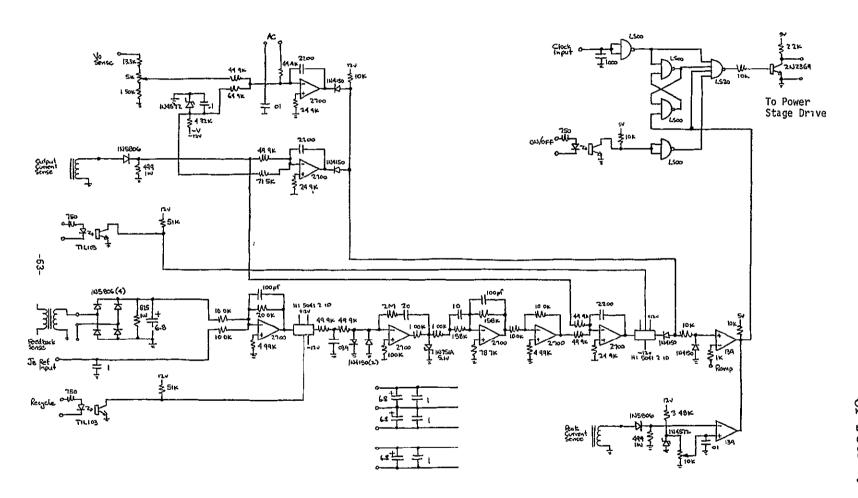

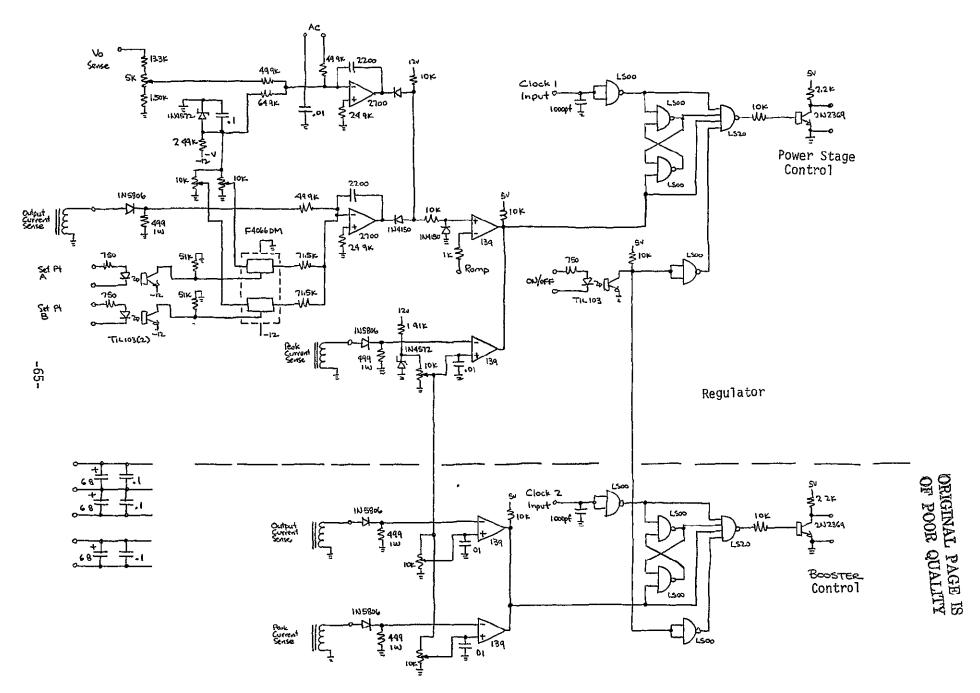

| Figure 3-20<br>Vi Regulator                            | 63   |

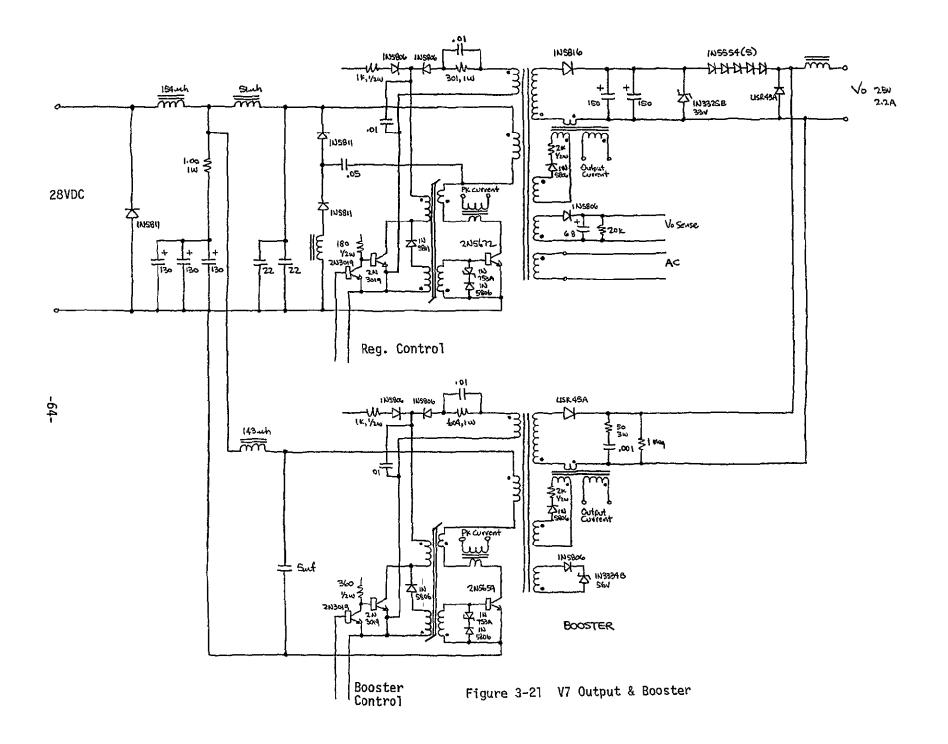

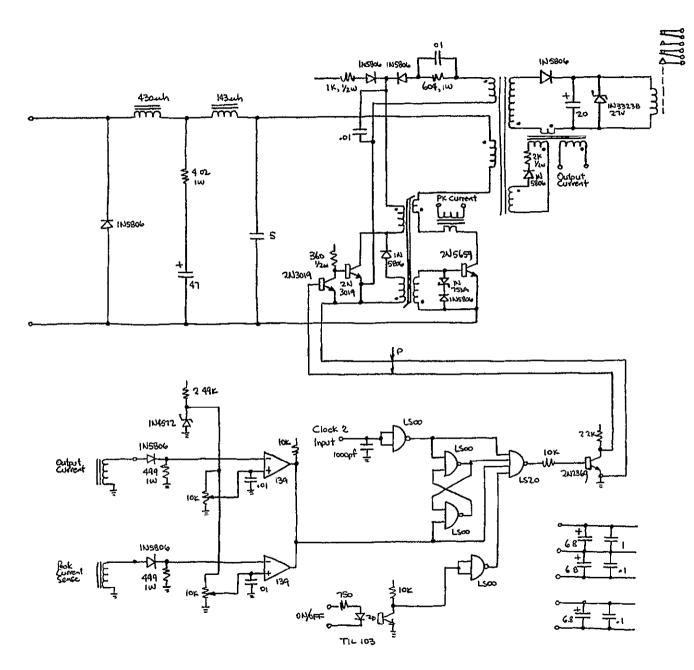

| Figure 3-21<br>V7 Output and Booster                   | 64   |

| Figure 3-22<br>V7 Regulator                            | 65   |

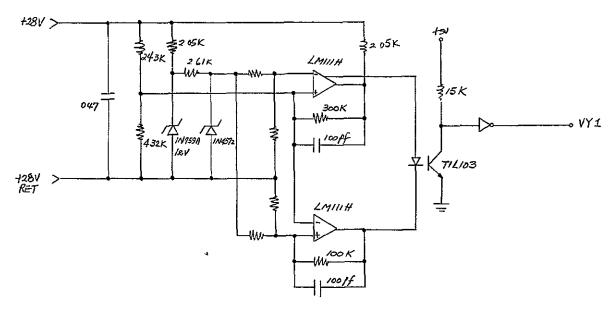

| Figure 3-23<br>Relay Driver                            | 67   |

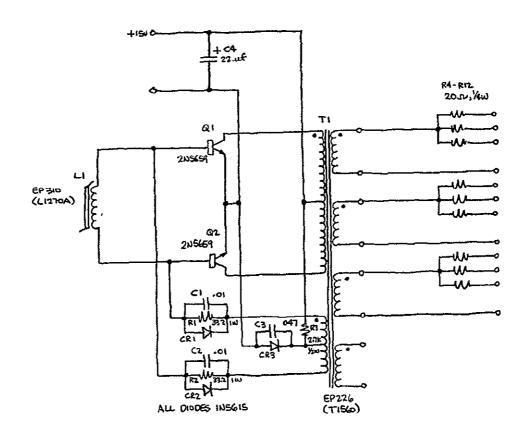

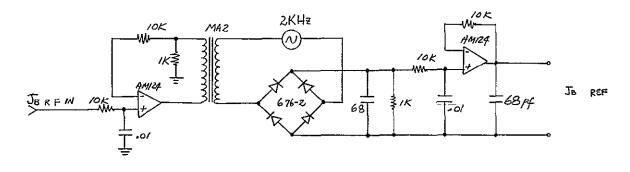

| Figure 3-24<br>TLM Oscillator                          | 70   |

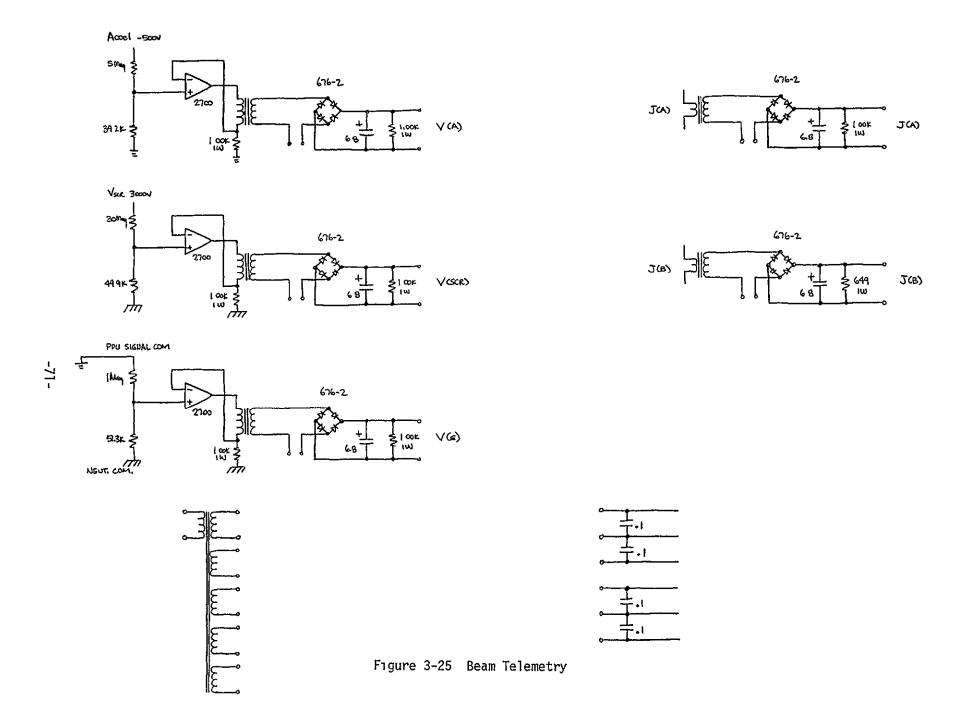

| Figure 3-25 Beam Telemetry                             | 71   |

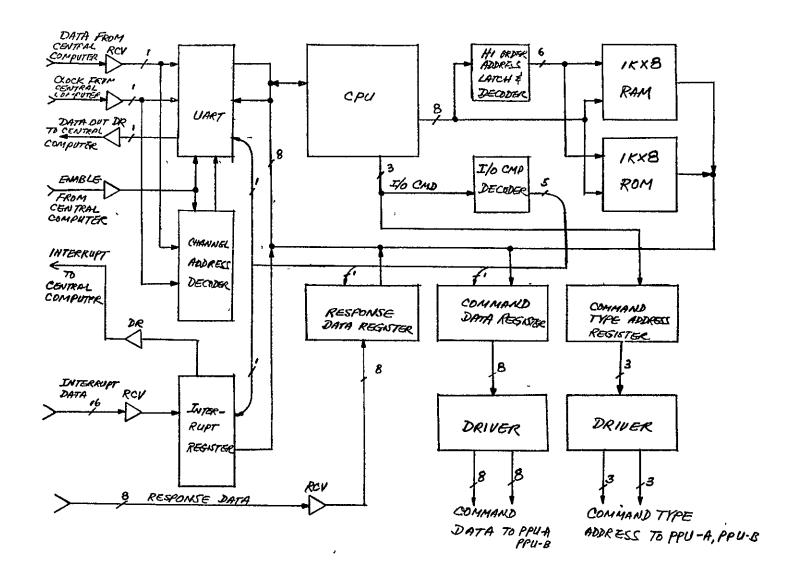

| Figure 3-26<br>Digital Interface Unit<br>Block Diagram | 74   |

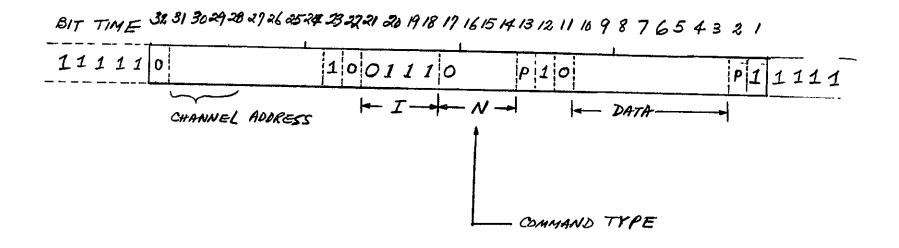

| Figure 3-27 External Command Format                    | 75   |

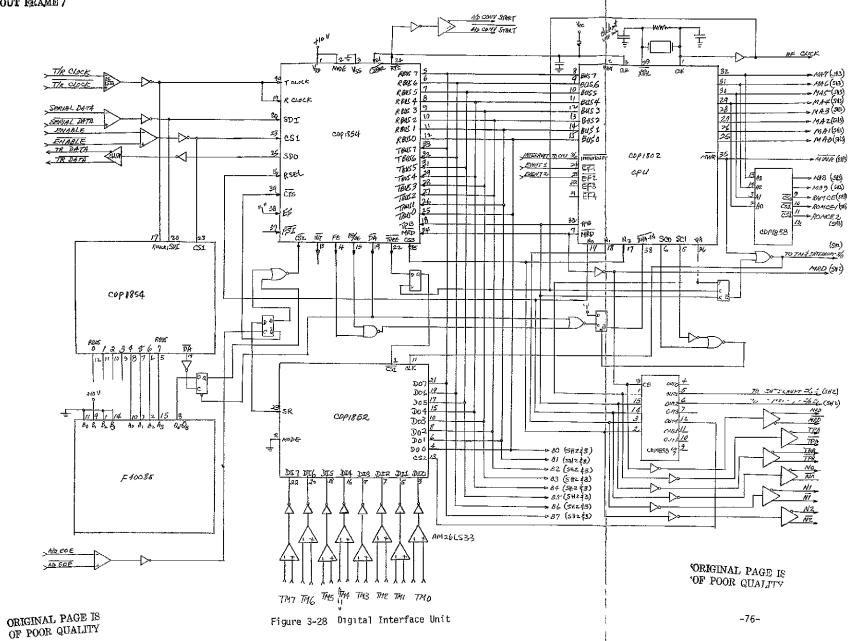

| Figure 3-28<br>Digital Interface Unit                  | 76   |

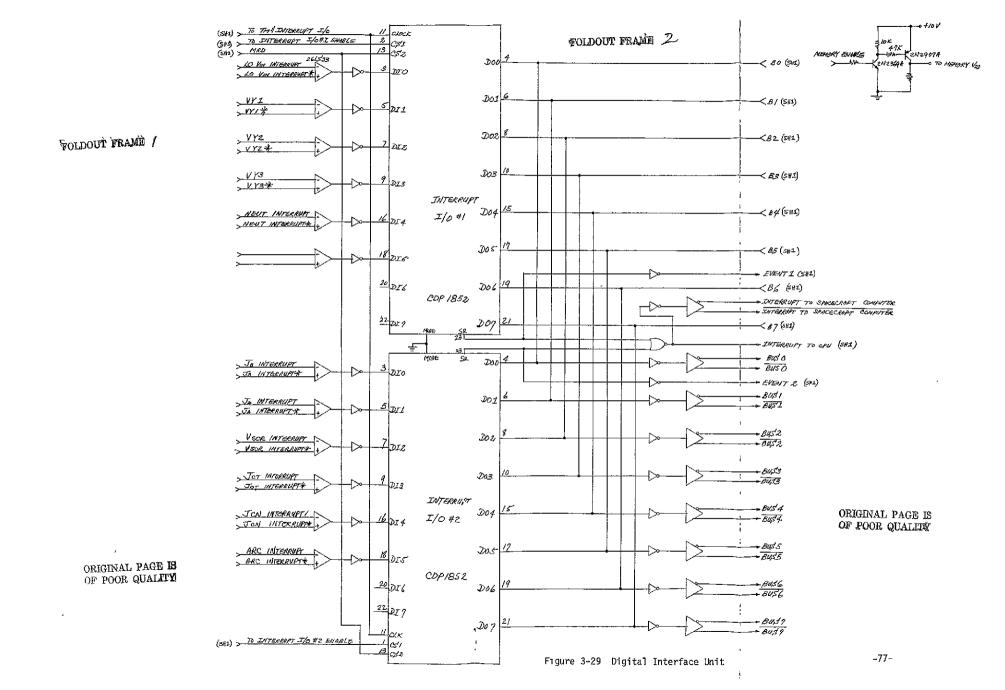

| Figure 3-29 Digital Interface Unit                     | 77   |

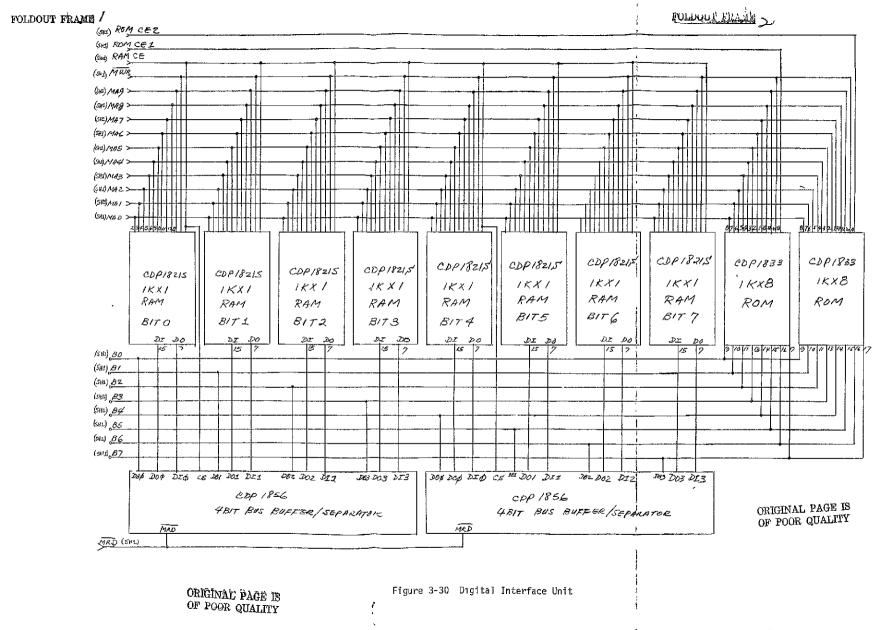

| Figure 3-30<br>Digital Interface Unit                  | 78   |

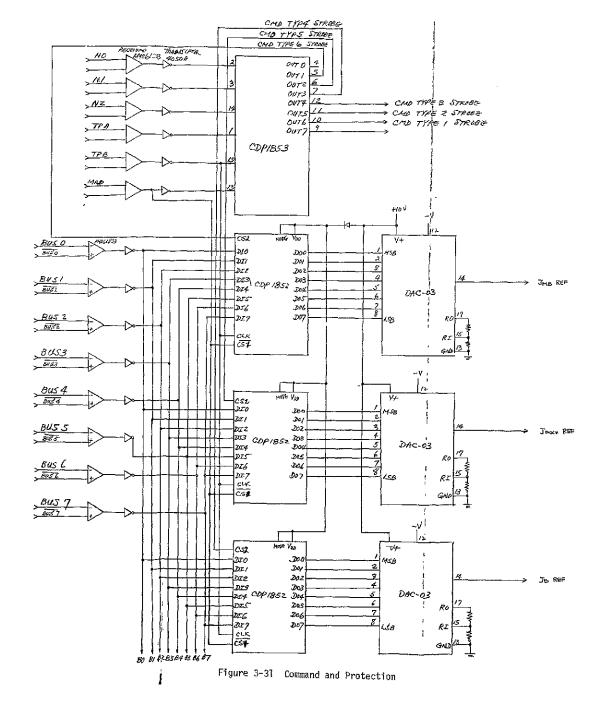

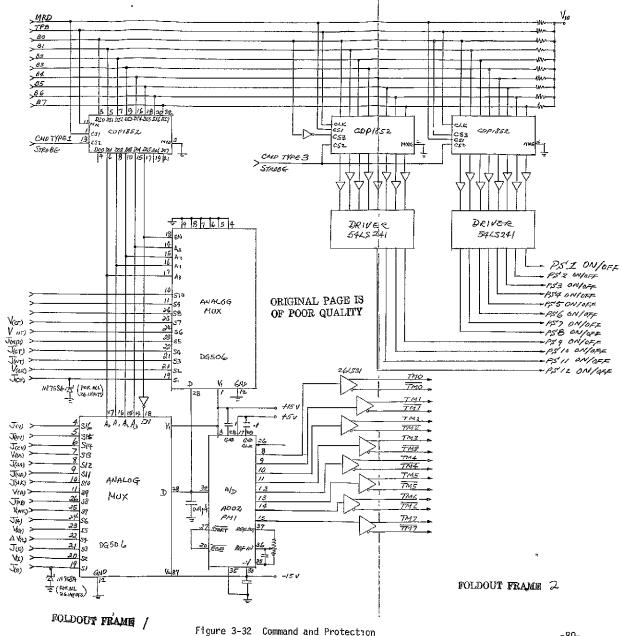

| Figure 3-31 Command and Protection                     | 79   |

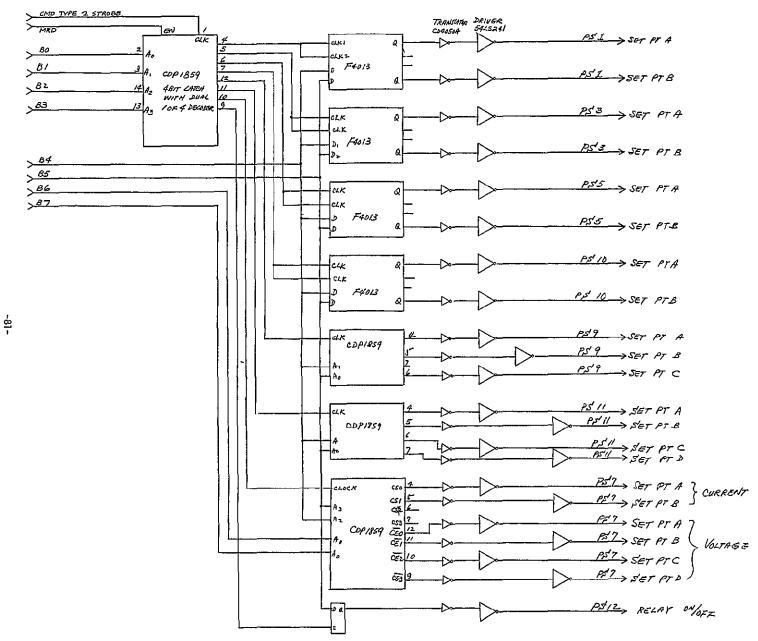

| Figure 3-32<br>Command and Protection                  | 80   |

| Figure 3-33<br>Command and Pretection                  | 81   |

| Figure 3-34<br>Command and Protection                  | 82   |

| Figure 3-35 Command and Protection                     | 83   |

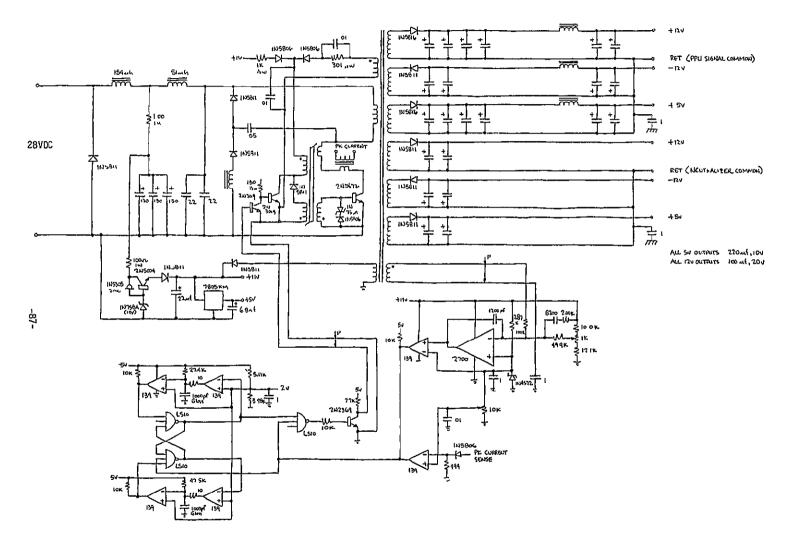

| Figure 3-36 Auxiliary Converter                        | 87   |

| - 0.07                                                          | <u>Page</u> |

|-----------------------------------------------------------------|-------------|

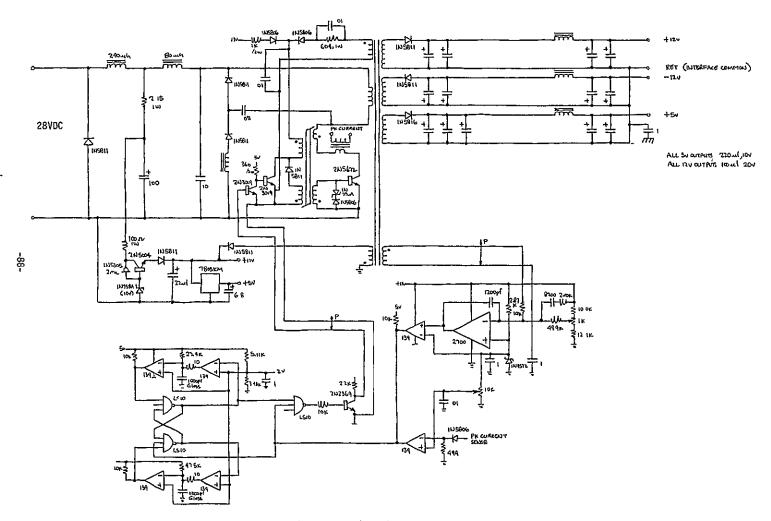

| Figure 3-37 Interface Converter                                 | 88          |

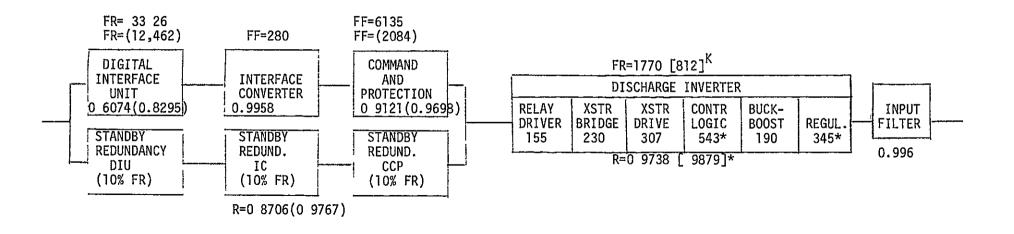

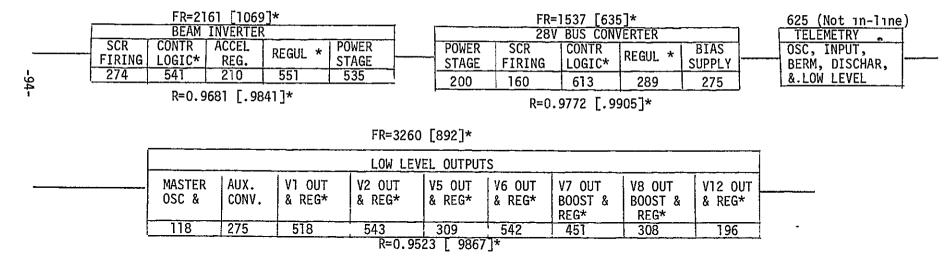

| Figure 3-38<br>PPU Reliability Block<br>Diagram                 | 94          |

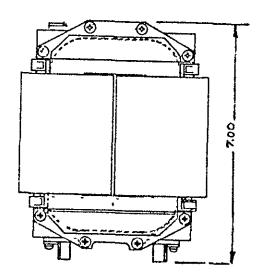

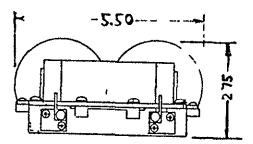

| Figure 3-39<br>Outline Drawing of 6KW<br>Beam Transformer       | 110         |

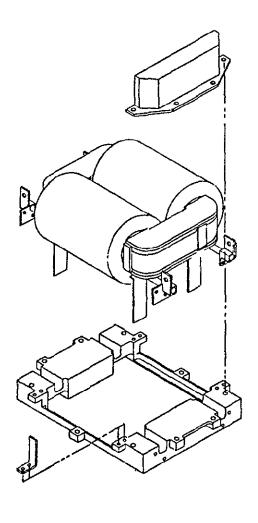

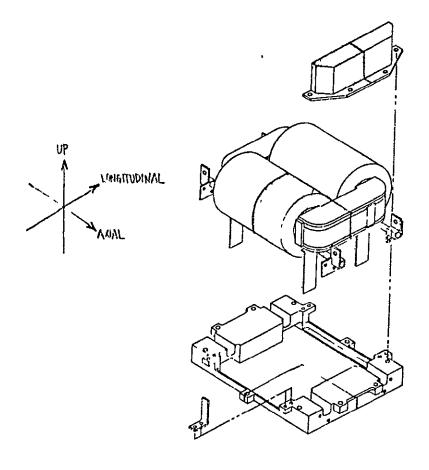

| Figure 3-40<br>6KW Beam Transformer<br>Exploded view            | 112         |

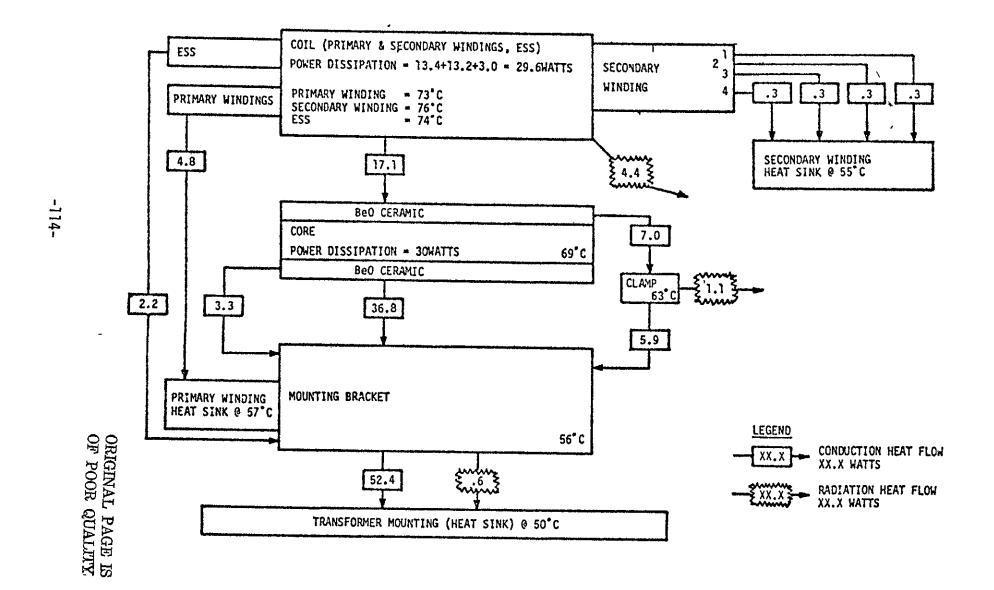

| Figure 3-41<br>6KW Beam Transformer<br>Thermal Analysis Results | 114         |

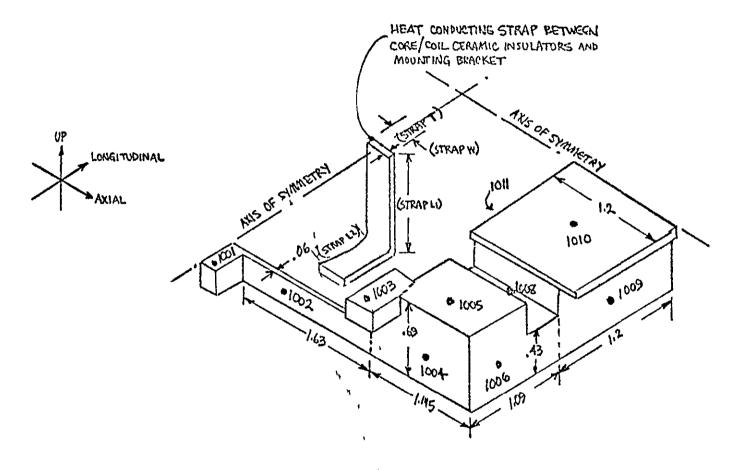

| Figure 3-42<br>Thermal Model -<br>6KW Beam Transformer          | 117         |

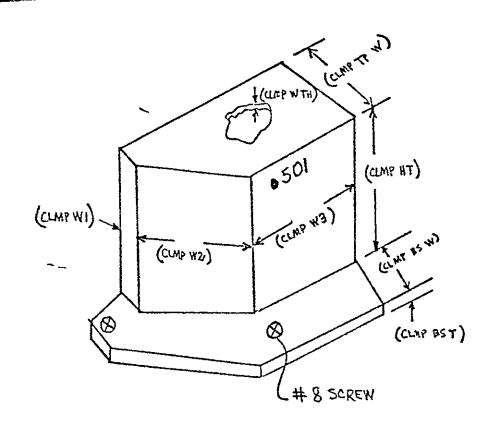

| Figure 3-43<br>Thermal Model -<br>Transformer Mounting Bracket  | 118         |

| Figure 3-44<br>Thermal Model -<br>Transformer Core              | 119         |

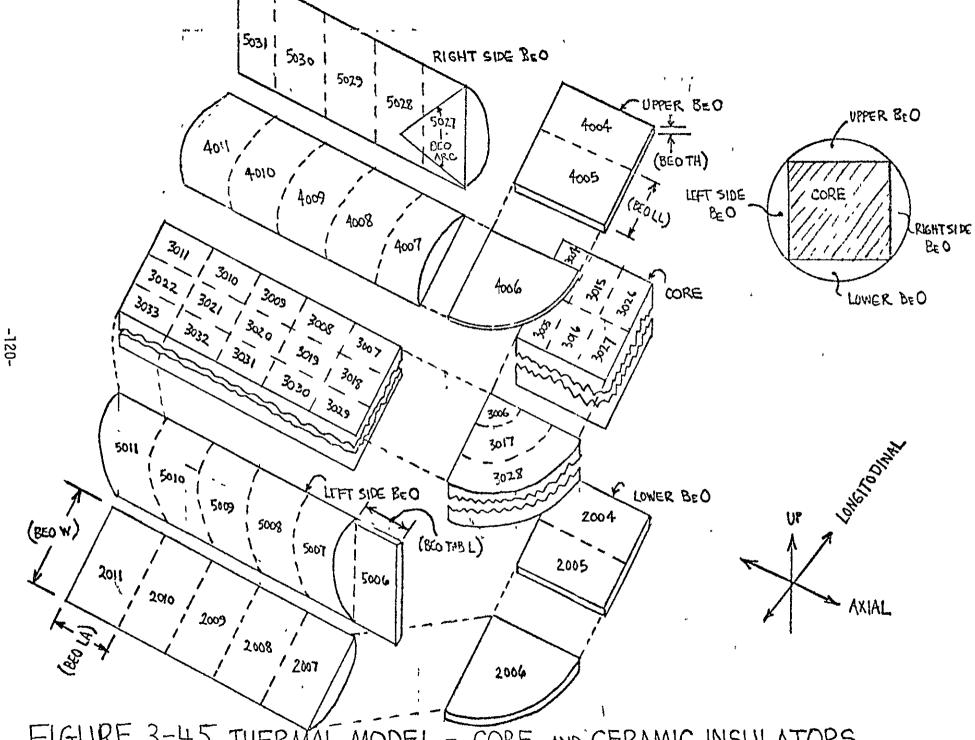

| Figure 3-45<br>Thermal Model-Core and Ceramic<br>Insulator      | 120         |

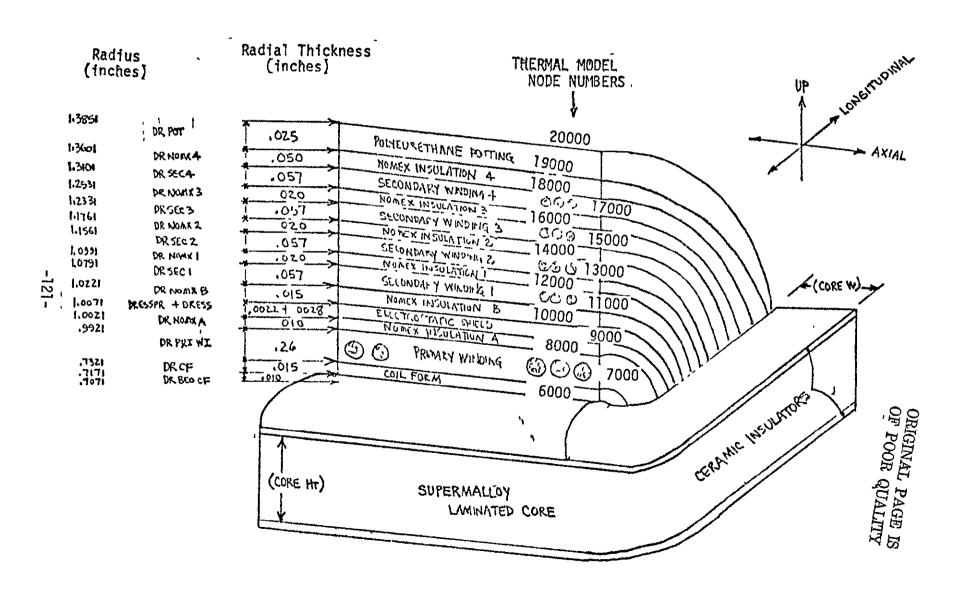

| Figure 3-46<br>Thermal Model - Transformer<br>Coil              | 121         |

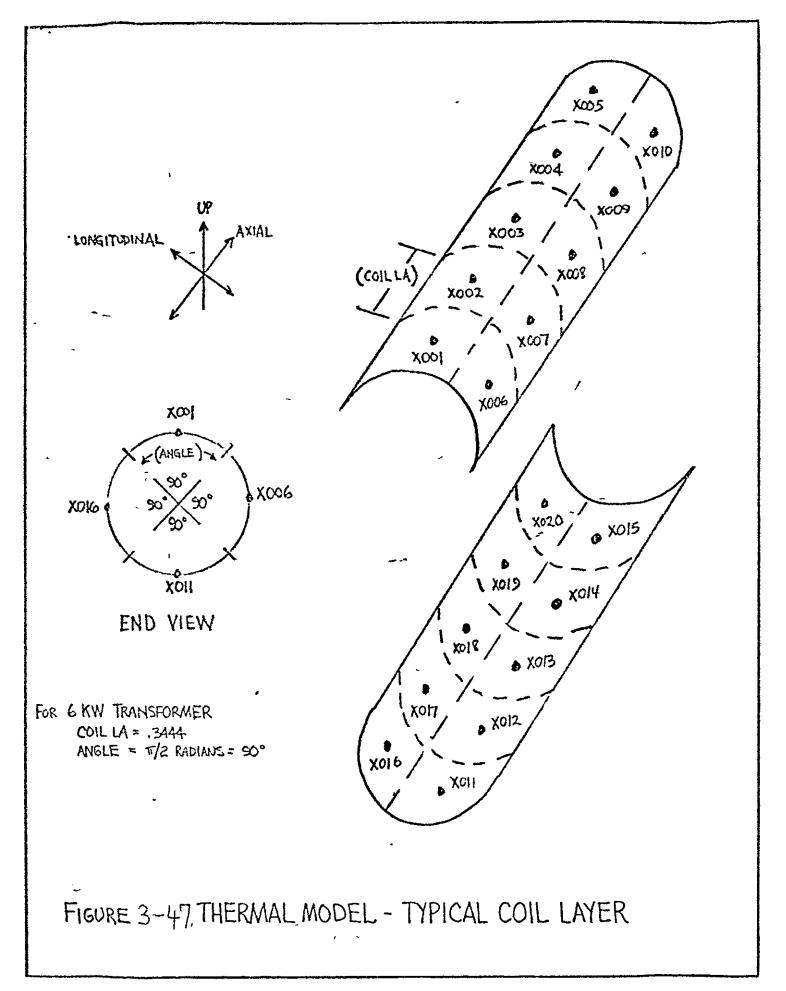

| Figure 3-47<br>Thermal Model -<br>Coil Layer                    | 122         |

| Figure 3-48<br>Thermal Model -<br>Electrostatic Shield          | 123         |

| Figure 3-49 Thermal Model - Clamp to Bracket                    | 124         |

|                                                                                             | Page |

|---------------------------------------------------------------------------------------------|------|

| Figure 3-50 Thermal Model Primary Winding Heat Sink                                         | 125  |

| Figure 3-51<br>6KW Power Transformer (BeO)<br>Heat Flow Diagram                             | 127  |

| Figure 3-52<br>Heat Flow Map -<br>Coil to Ceramic Insulator                                 | 128  |

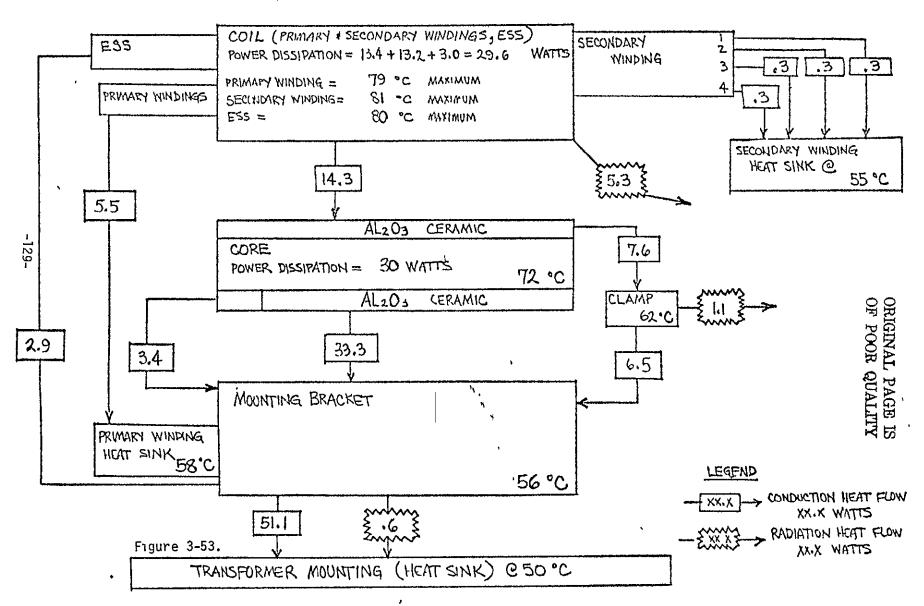

| Figure 3-53<br>6KW Power Transformer (AL <sub>2</sub> O <sub>3</sub> )<br>Heat Flow Diagram | 129  |

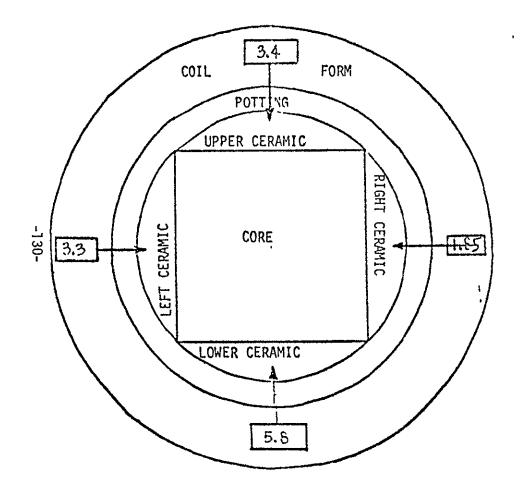

| Figure 3-54 Heat Flow Map - Coil to Ceramic Insulator                                       | 130  |

| Figure 3-55 2KW Power Transformer Heat Flow Diagram                                         | 131  |

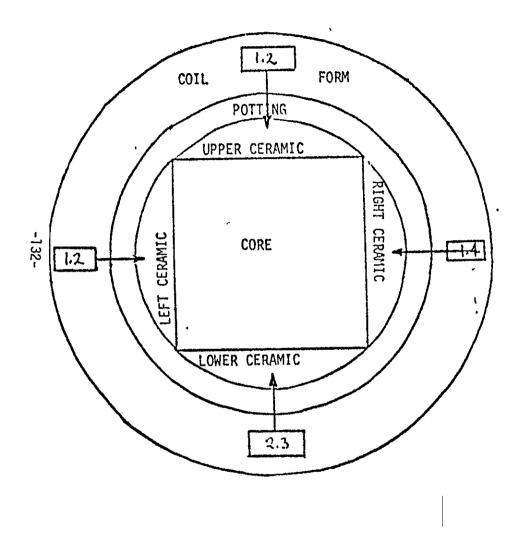

| Figure 3-56<br>Heat Flow Map                                                                | 132  |

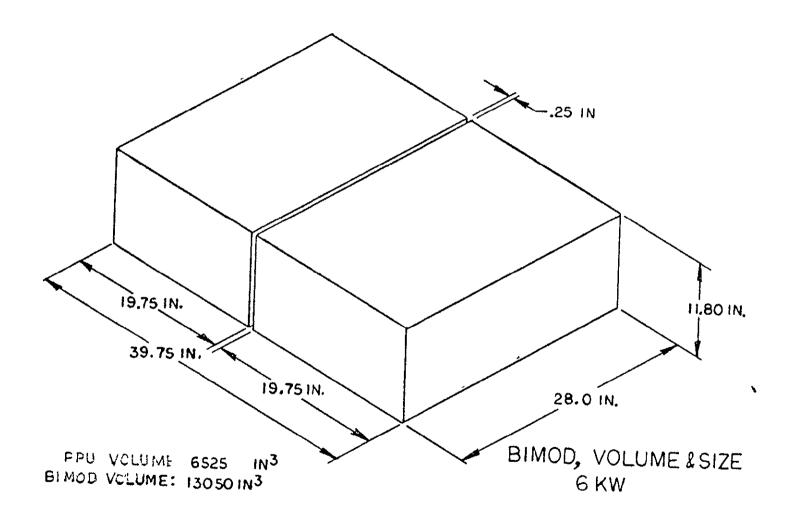

| Figure 3-57 Size and Volume Estimate for 6KW Power Processor                                | 135  |

| Figure 3-58 Bi-Mod Power Processor Conceptual Mechanical Configuration                      | 136  |

| Figure 3-59 Size and Volume Estimate for 202KW Power Processor                              | 138  |

| Figure 3-60 Proposed Module Subassembly                                                     | 139  |

#### 1. INTRODUCTION

Solar electric propulsion is being viewed as matured, developed technology that can be applied to new high energy missions in the 1980 time frame with the Shuttle/IUS as the launch vehicle.

The Halley Comet Rendezvous Mission requires a major decrease in the ion drive systems specific mass currently projected for the 3KW, 30cm ion thruster as approximately 50KG/KW. This requirement necessitates a thrust system design which increases the output power to greater than 6KW.

Because of the increase in output power level, it is necessary to redesign the power processor. Contract NAS3-20403, "Extended Performance Electric Propulsion Power Processor Design Study," performed the necessary conceptual design and tradeoffs to identify the preferred power processor circuit configuration that meet the new requirements while at the same time reducing the specific mass KG/KW and improving the power processor efficiency and reliability.

This study program had three objectives. The first was to evaluate the power processor unit at higher beam supply power levels (from 2.2 to 10KW). The second was to evaluate revised requirements and alternate methods of implementation for the low power supplies of power processing unit; and the third was to develop a power processor plan to support a Hally Comet Rendezvous Mission. The outputs of the first two objectives are system approaches versus weight, efficiency, parts count, reliability, and component technology requirements.

The information obtained from this contracted effort was used in direct support of a Halley Comet Rendezvous Mission study completed in the summer of 1977 and other alternate electric propulsion missions being planned in the 1980 time period.

This report summarizes the results of a six month study to define the design, program plan and cost of the electric propulsion power processor for the Halley's Comet Mission Spacecraft

The following sections summarize the results of the design tradeoff studies. After the selection and approval of the preferred configuration by NASA Lewis, a detailed electrical design, magnetic design and thermal control and conceptual mechanical packaging was performed. An assessment of the technical risks is also presented.

#### 2. DESIGN TRADEOFF STUDIES

The first task of the study program considered a spectrum of alternate power distribution systems, mechanization of the beam supply up to 10KW, mechanization of discharge supply, mechanization of the low voltage supplies and the method of controlling the power processors by means of central computer or localized microprocessor. The following sections present the results of the design tradeoff studies. A method to evaluation of the weight efficiency optimization is presented in Section 2.6. Section 3.0 Baseline Design presents the results of the detail design of the selected power processor configuration.

#### 2.1 Power Distribution System

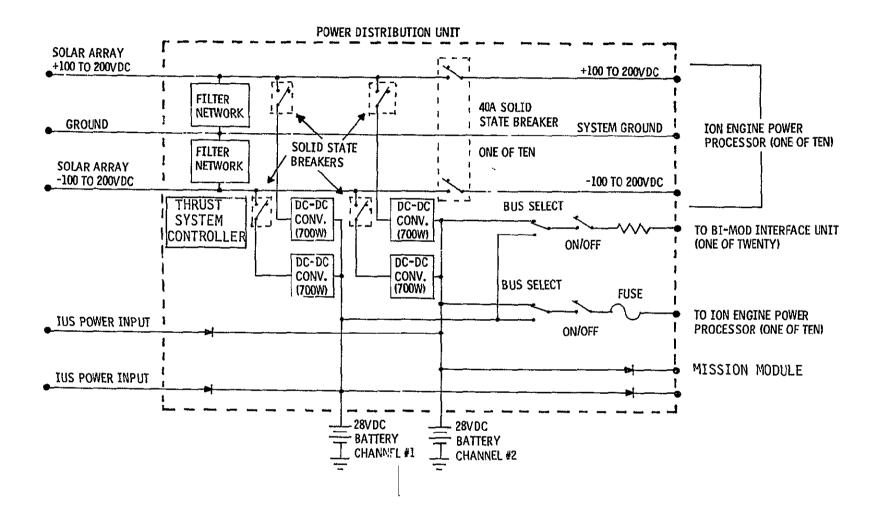

Two separate power distribution systems were studied.

- a) A single 200-400VDC solar array split bus supplies all the power to the thrust subsystem and the mission module.

- b) a 200-400VDC solar array split bus supplies power to beam and discharge supplies for the thrust subsystem and two separate 28VDC solar array buses supply power to the ion thruster low level outputs and the mission module.

The split or center tabled solar array bus reduces the space charge interaction with the solar array and allows the adaption of existing remote power controllers (solid state switchgear) to provide fault isolation in case of power processor failure. These remote power controllers must be used in both the positive and negative power lines and must open at the same time so that they will not be subjected to overvoltage stress.

Figures 2-I and 2-2 present the basic block diagrams for these different power distribution systems. Table 2-I and 2-II summarizes the characteristics of the two different systems.

Figure 2-2 (200-400VDC bus and 28VDC bus) was the selected configuration since it would be more compatible with existing 28VDC hardware developed for other spacecraft programs. The high voltage DC was only used for the high power loads of the ion engine (beam and discharge supplies).

The selected configuration has the maximum reliability with use of solid state breakers to clear failed hardware and redundant 28VDC distribution buses.

Further development is required on the solid state breakers for the ion engine and for the thrust system controller hardware and software.

Figure 2-1. 200-400VDC Power Distribution System

Figure 2-2. 200 to 400VDC and 28VDC Power Distribution System

### Table 2-I. Summary of 200-400VDC Power Distribution System Characteristics

- Plus (+) and Minus (-) Solar Array Voltage Reduces

- a) Component stresses (Solid State Breaker)

- b) Space Charge Interaction

- Filter Network Controls Bus Impedance for EMC

- Thrust System Controller Perform all Power Control & Management (Max Power Tracking, Bi-Mod Control, Failure Analysis, Attitude Control, Thrust & Gimbal Angle).

- Solid State Breaker for Loads on +100 to 200VDC Distribution Bus.

- Low Voltage DC Power Distribution for EMC Control and Ease of Integration of All Low Power Equipment.

- Redundant +28VDC Buses for Low Power Distribution:

- a) Interface with Mission Module

- b) Interface with IUS

- c) Interface with Bi-Mod

- Battery Supplies Transient Loads such as Startup and Fault Clearing.

- Plus (+) and Minus (-) DC-DC Converters Condition Power for 28VDC Bus (700W Rating to Carry Maximum Load if Required for Redundancy).

- On/Off Control, Bus Selection and Fault Clearing for 28VDC Loads.

- Compatible with IUS Power Bus.

## Table 2-II. Summary of 200-400VDC and 28VDC Power Distribution System Characteristics

- Plus (+) and Minus (-) Solar Array Voltage Reduces:

- a) Component Stresses (Solid State Breaker)

- b) Space Charge Interaction

- Filter Network Controls Bus Impedance for EMC.

- Thrust System Controller Performs all Power Control & Management (Max Power Tracking Bi-Mod Control, Failure Analysis, Attitude Control, Thrust & Gimbal Angle).

- Solid State Breaker for Loads on +100 to 200VDC Distribution Bus.

- Low Voltage DC Power Distribution for EMC Control and Ease of Integration of all Low Power Equipment

- Redundant +28VDC Buses for Low Power Distribution.

- a) Interface with Mission Module

- b) Interface with IUS

- c) Interface with Bi-Mod

- Battery Supplies Transient Loads such as Startup and Fault Clearing.

- On/Off Control, Bus Selection and Fault Clearing for 28VDC Loads.

- Compatible with IUS Power Bus.

- Isolated 28VDC Solar Array to Supply Low Level Electronic Loads.

#### 2.2 Beam Supply Tradeoff Analysis

In order to obtain beam power levels up to 10KW with existing high power thyristors, different power stage mechanization and modulization had to be designed and analyzed.

The series resonant inverter power stage configurations selected for review included:

Single full bridge

2 Channel full bridge

2 Channel half bridge

3 Channel half bridge

4 Channel half bridge

4 Channel half bridge

5KW power rating

10KW power rating

10KW power rating

10KW power rating

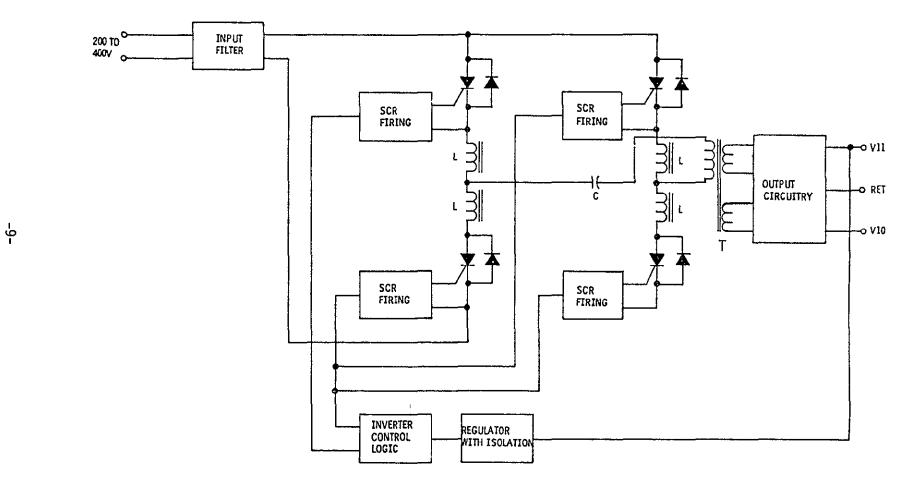

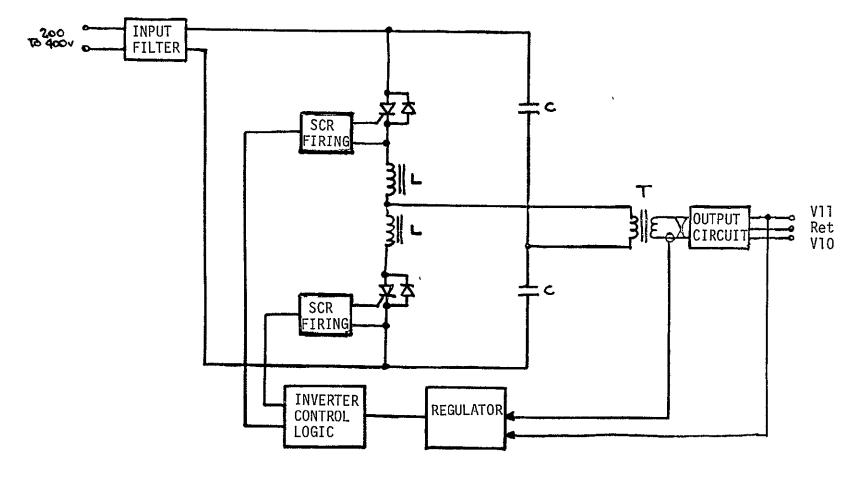

Figure 2-3 presents the schematic of the thyristor full bridge operating at maximum frequency of 20kHz.

Figure 2-4 presents the schematic of the thyristor half bridge operating at maximum frequency of 20kHz.

Table 2-III summarizes the design results of different power and power stage configurations. The single full bridge (6KW rating) was the selected configuration due to its low component weight. The efficiency of all of the beam configurations remained above 93%.

The use of the thyristor series resonant inverter allows power growth with minimal impact on the weight loss and part count. With further development of the power thyristor from the 200A current capability to a 500A rating could easily allow the basic power stage to operate at about 20KW. The basic component limitations at this time is the power thyristor. Additional development of the power transformer may be needed to maintain adequate operating temperatures with the present thermal control techniques.

Figure 2-3. Schematic of the Thyristor Full Bridge Series Resonant Beam Inverter

Figure 2-4. Schematic of the Thyristor Half Bridge Series Resonant Beam Inverter

Table 2-IIİ Summary of Beam Supply Tradeoff Analysis

| CONFIGURATION         | MAXIMUM<br>PWR RATING | COMPONENT<br>WEIGHT (KG) | LOSS<br>(WATTS) * | PART COUNT | POWER STAGE<br>EFFIC. (%) |

|-----------------------|-----------------------|--------------------------|-------------------|------------|---------------------------|

| SINGLE FULL BRIDGE    | 6KW                   | 9. 4                     | 440               | 521        | 93.6                      |

| 2 CHANNEL FULL BRIDGE | 10KW                  | 16.0                     | 743               | 910        | 93 5                      |

| 2 CHANNEL HALF BRIDGE | 6KW                   | 11.4                     | 478               | 740        | 93 1                      |

| 3 CHANNEL HALF BRIDGE | 10KW                  | 18. 1                    | 770               | 1041       | 93 2                      |

| 4 CHANNEL HALF BRIDGE | 10KW                  | 19.1                     | 784               | 1352       | 93 2                      |

|                       |                       |                          |                   |            |                           |

<sup>\*</sup>Losses include power stage and control losses

### 2.3 Discharge Supply Tradeoff Analysis

Due to the relatively lower power rating of the discharge supply (800W), new power conversion technology can be applied. The different configurations analyzed include the following:

- Thyristor 20kHz half bridge series resonant inverter

- Transistor 50kHz full bridge series resonant inverter

The half bridge configuration is similar to that shown in Figure 2-4 and uses the standard power thyristor.

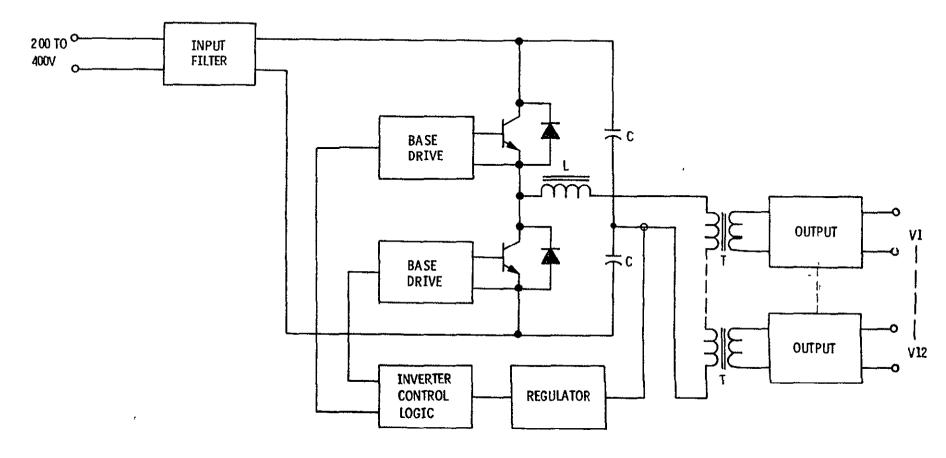

Figure 2-5 presents the schematic of the transistorized 50kHz full bridge series resonant inverter which takes advantage of the faster switching and lower storage times of the power transistors.

Table 2-IV summarizes the design results of the two different configurations.

Due to the electrical component weight saving of about 1.1KG, the 50kHz full bridge transistorized series resonant inverter was selected as the preferred configuration.

There is a penalty in efficiency but when analyzed against the weight efficiency optimization discussed in section 2.6, the overall weight was lower.

Figure 2-5. Schematic of Transistorized Bridge Series Resonant Discharge Inverter

Table 2-IV Summary of Discharge Supply Tradeoff Analysis

| C ONFIGURATION                  | MAXIMUM<br>PWR RATING | COMPONENT<br>WT. (KG) | LOSS AT 415W<br>OUTPUT (W) * | PART<br>COUNT | POWER STAGE<br>EFFIC. (%) |

|---------------------------------|-----------------------|-----------------------|------------------------------|---------------|---------------------------|

| THYRISTOR 20kHz HALF<br>BRIDGE  | 815W                  | 3.3                   | 70.7                         | 331           | 88. 0                     |

| TRANSISTOR 50kHz FULL<br>BRIDGE | 815W                  | 2.2                   | 79. 1                        | 473           | 87 2                      |

<sup>\*</sup>Losses include power stage and control losses

## 2.4 Low Voltage Supplies Tradeoff Analysis

The low voltage supplies greatly affect the total power processor weight, losses and part count. Tradeoffs were performed on new power stage configurations, sharing of power functions between two thrusters in a Bi-Mod configuration and the application of latest integrated circuit technology.

The power electronics mechanization to satisfy the revised power processor requirements include:

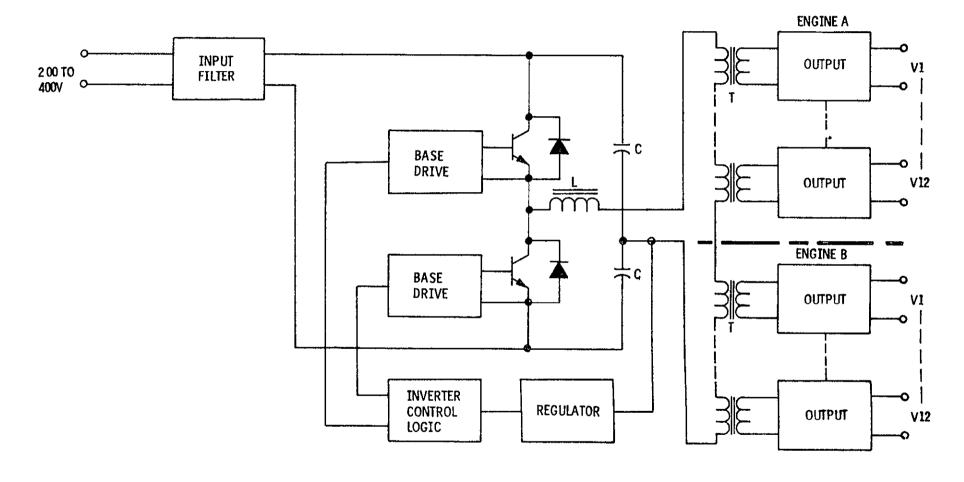

- Transistor Half Bridge 50kHz Series Resonant Inverter (Figure 2-6)

- Transistor Half Bridge 50kHz Series Resonant Inverter to Operate Two Ion Thrusters in a Bi-Mod Configuration (Figure 2-7)

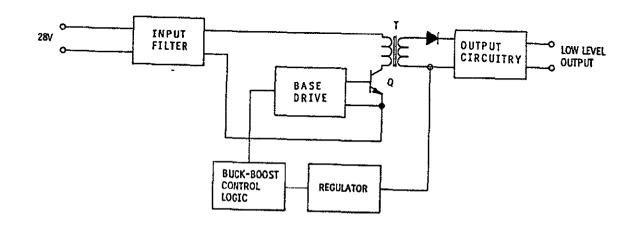

- Buck/Boost DC/DC Converter for Each Separate Output Load (Figure 2-8)

Table 2-V summarizes the characteristics of the low voltage supply configurations.

The dedicated Buck/Boost DC/DC Converter is the preferred configuration mainly since it has the highest overall efficiency in comparison with the other proposed configurations.

It also maintains the high efficiency over wide output power loading which are required when starting up a cold engine and when providing normal steady-state power to operate the ion engine control loops.

No potential advantage were identified in the Bi-Mod Configuration shown in Figure 2-7. It had a potential lower reliability where one series resonant inverter could fail two ion engines.

Figure 2-6. Schematic for Half Bridge 50kHz Series Resonant Inverter for the Low Voltage Supplies

Figure 2-7. Schematic of Transistorized 50kHz Series Resonant Inverter Configurated to Supply Low Voltage Outputs for Two Thrusters in Bi-Mod Configuration

Figure 2-8. Schematic of Buck/Boost DC/DC Converter for Typical Low Voltage Supply

| C ONFIGURATION                                               | MAXIMUM<br>PWR RATING | COMPONENT<br>WT. (KG) | LOSS AT 45W<br>OUTPUT (W) * | PART<br>COUNT                | POWER STAGE<br>EFFIC. (%) |

|--------------------------------------------------------------|-----------------------|-----------------------|-----------------------------|------------------------------|---------------------------|

| Transistor Half Bridge<br>Series Resonant<br>Inverter        | 200W                  | 2.7                   | 65. 8                       | 1001                         | 46.0                      |

| Transistor Half Bridge<br>Series Resonant Inv.<br>for Bi-Mod | 250W                  | 4.8                   | 109. 9(@90W)                | <sup>1673</sup><br>(2 Units) | 48.9                      |

| Dedicated Buck/Boost<br>DC-DC Converter                      | 200W                  | 2.6                   | 25 6                        | 1039                         | 66.5                      |

<sup>\*</sup>Losses include power stage and control losses.

Table 2-V Summary Data for Low Voltage Supply Design Configurations

### 2.5 Power Processor Configuration Tradeoff

Two separate power processor configurations were mechanized to satisfy the requirements of the two power distribution system identified in Section 2.1.

These configurations include:

- a) a single 200-400VDC solar array bus to supply all power (Figure 2-9).

- b) 200-400VDC bus supplies power to high power loads, such as beam and discharge and a 28VDC solar array bus supplies power for the low level supply (Figure 2-10).

In Figure 2-9, three series resonant inverters process all of the 200-400VDC power to the ion engine. 28VDC power is used only for internal power processor control electronics and for microprocessor digital interface units. This configuration is very similar to the (2.7KW) Electrical Prototype Power Processor Unit developed under contract NAS3-19730.

In Figure 2-10, two series resonant inverters process the 200 to 400VDC power to beam and discharge functions of the ion engine. All the remaining low power controller used 28VDC power through dedicated DC-DC Converters.

Table 2-VI and VII summarizes the characteristics for the two power processor block diagrams, respectively.

The major function is listed with its part count, electrical component weight and losses for each major element.

- Beam inverter

- Discharge inverter

- Low voltage supplies

- Input filter

- Low level command, control and telemetry electronics.

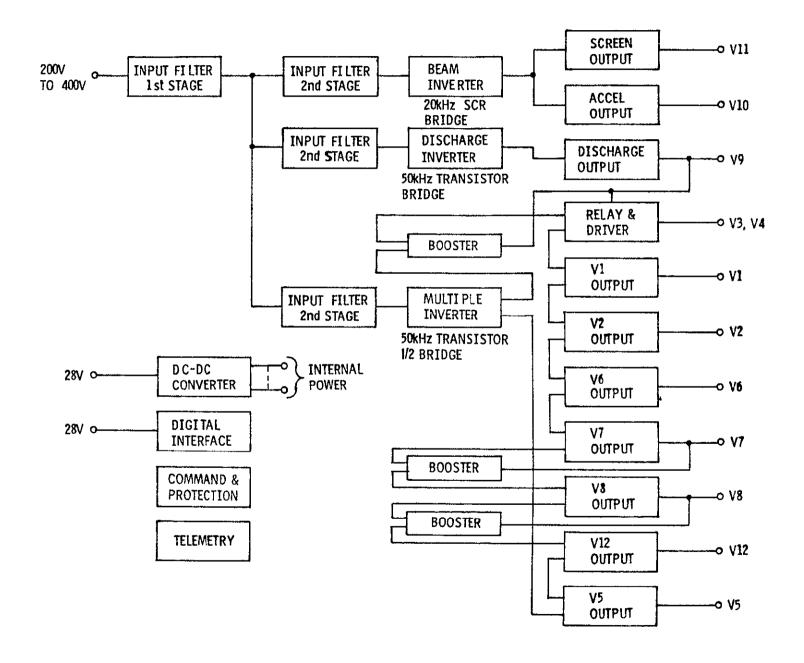

Figure 2-9. Power Processor Block Diagram

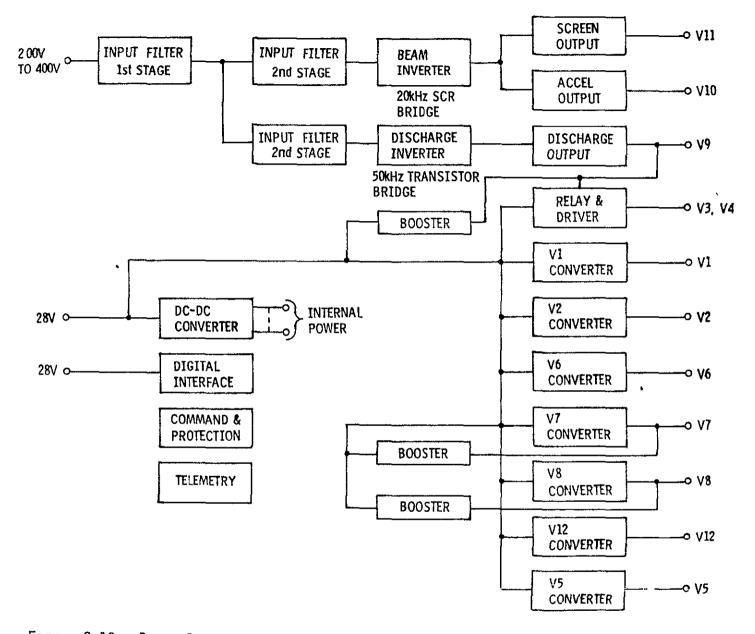

Figure 2-10. Power Processor Block Diagram (200 to 400V and 28V Solar Array Power Distribution)

Table 2-VI Power Processor Estimate - High Voltage System

|                                                                       |                                                                                            | · · · · · · · · · · · · · · · · · · · |                                                |                                                |                  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------|------------------------------------------------|------------------|

|                                                                       |                                                                                            | PART<br>COUNT                         | WEIGHT (gms)                                   | LOSSES<br>(W)(2)                               | EFFIC.           |

| Beam Inverter (6000W)                                                 | Power Stage<br>SCR Firing<br>Series Inverter Control<br>Regulator<br>Accelerator Regulator | 81<br>152<br>125<br>92<br>71          | 8893. 3<br>165<br>116. 45<br>120. 75<br>107. 5 | 408. 42<br>23. 6<br>1. 379<br>2. 121<br>4. 021 | <b>93.6%</b> (1) |

|                                                                       | Beam Total                                                                                 | 521                                   | 9403.0                                         | 439. 541                                       |                  |

| Discharge Inverter (415W)                                             | Power Stage<br>Transistor Drive<br>Series Inverter Control<br>Regulator                    | 33<br>218<br>125<br>97                | 1639 35<br>288. 6<br>116. 45<br>131 8          | 60.64<br>16.0<br>1 379<br>1.082                | 87.3% (1)        |

|                                                                       | Discharge Total                                                                            | 473                                   | 2176. 2                                        | 79. 101                                        |                  |

| Low Voltage Supplies Multiple Inverter (45W) (Series Inverter)        | Power Stage<br>Controls<br>Outputs - Power<br>• Regulators                                 | 10<br>319<br>146<br>526               | 207<br>362, 3<br>1522, 85<br>592 9             | 15.50<br>10 202<br>37.141<br>2 975             | 46% (1)          |

|                                                                       | Multiple Total                                                                             | 1001                                  | <b>2</b> 685 <b>0</b> 5                        | 65 818                                         |                  |

| Input Filter                                                          |                                                                                            | 45                                    | 4410                                           | 20 60                                          |                  |

|                                                                       | Sub Totals                                                                                 | 2040                                  | 18674 25                                       | 605.06                                         | 91. 4%           |

| Felemetry<br>Protection<br>Command<br>Interface Unit<br>28V Converter |                                                                                            | 239<br>235<br>52<br>91<br>122         | 686 35<br>186 3<br>181 6<br>454<br>611 8       | 5 528<br>3 00<br>2 57<br>. 97<br>16 46         |                  |

| Output power = 6460W                                                  | TOTALS                                                                                     | 2779                                  | 20784.3                                        | 633 588                                        | 91 07%           |

|                                                                       |                                                                                            |                                       |                                                |                                                |                  |

Notes (1) (2)

Power stage efficiency only. Losses at two amp beam current

Table 2-VII Power Processor Estimate - High & Low Voltage System

|                                                                       |                                                                                            | PART<br>COUNT                 | WEIGHT<br>(gms)                               | LOSSES<br>(W) (2                          | EFFIC.            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------|-------------------------------------------|-------------------|

| Beam Inverter (6000W)                                                 | Power Stage<br>SCR Firing<br>Series Inverter Control<br>Regulator<br>Accelerator Regulator | 81<br>152<br>125<br>92<br>71  | 8893. 3<br>165<br>116. 45<br>120. 75<br>107 5 | 408 42<br>23 6<br>1.379<br>2.121<br>4 021 | <b>93 6% (</b> 1) |

|                                                                       | Beam Total                                                                                 | 521                           | 9403.0                                        | 439. 541                                  |                   |

| Discharge Inverter (415W)                                             | Power Stage<br>Transistor Drive<br>Series Inverter Control<br>Regulator                    | 33<br>218<br>125<br>97        | 1639 35<br>288.6<br>116 45<br>131 8           | 60.64<br>16.0<br>1.379<br>1.082           | 87.3% (1)         |

|                                                                       | Discharge Total                                                                            | 473                           | 2176.2                                        | 79. 101                                   | •                 |

| Low Voltage Supplies Multiple Outputs (45W) (Buck-Boost)              | Power Stage<br>Controls                                                                    | 336<br>703                    | 1859. 2<br>733 3                              | <b>22.</b> 662 <b>2.</b> 963              | 66 5% (1)<br>-    |

|                                                                       | Multiple Total                                                                             | 1039                          | <b>25</b> 92 5                                | 25.625                                    | <b>.</b>          |

| Input Filter                                                          |                                                                                            | 45                            | 4385                                          | 20.6                                      | _                 |

| ·                                                                     | Sub Totals                                                                                 | 2078                          | 18556.7                                       | 564 867                                   | 919%              |

| Telemetry<br>Protection<br>Command<br>Interface Unit<br>28V Converter |                                                                                            | 239<br>235<br>52<br>91<br>122 | 686 35<br>186 3<br>181 6<br>454<br>611 8      | 5. 528<br>3 00<br>2 57<br>. 97<br>16. 46  | _                 |

| Output Power ≥ 6460W                                                  | TOTALS                                                                                     | 2817                          | 20676 75                                      | 593 395                                   | 91.6%             |

Notes: (1) Power Stage Efficiency Only.

(2) Losses at Two Amp Beam Current.

The Table 2-VII shows that Figure 2-10 has the slightly lower electrical component weight of about 110 grams and a higher efficiency of 0.5%. The real efficiency savings occur when the beam current is varied to 1/4 power level and difference between the low voltage supplies improves the overall efficiency. This will be further discussed in Section 3.5, Electrical Design.

# 2.6 Power Processor Weight-Efficiency Optimization

The optimization of a power processor design is dependent on the design of the spacecraft, basically the solar array and the thermal control system used to reject the heat loss generated by the power processor.

In the solar electric mission, the solar array power capability varies constantly during its mission due to the variation of the distance between the Sun and the spacecraft and makes the optimization more difficult.

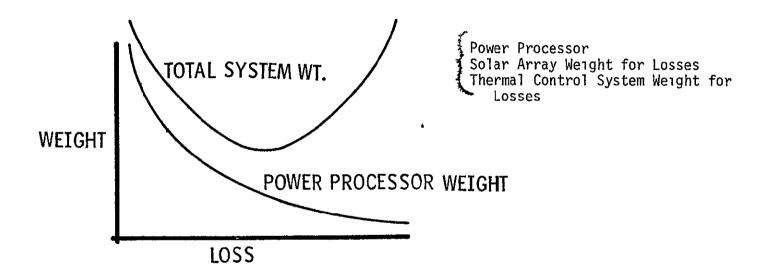

Figure 2-11 shows the characteristic optimization curves where the power processor weight is plotted as a function of its losses. The summation of the weight for the power processor, the weight for the solar array due to losses and the weight of the thermal control system to radiate the internal losses is also plotted as a function of the power processor losses. The optimization point is where the power processor weight is equal to 1/2 of the total weight.

For the Halley's Comet Rendezvous mission, the following spacecraft characteristics were estimated:

| • | Solar Array Density (Averaged overflight profile) | 20KG<br>KW |

|---|---------------------------------------------------|------------|

| • | Thermal Control System Density                    | 28KG<br>KW |

The following is an estimate of the preferred power processor configuration design:

| • | Packaged Weight (2 times component weight)                                               | 40KG      |

|---|------------------------------------------------------------------------------------------|-----------|

|   | Power Processor Losses                                                                   | 593 Watts |

| • | Solar Array Weight for Losses $\frac{20\text{KG}}{\text{KW}} \times .593\text{KW}$ =     | 11.8KG    |

| • | Thermal Control System Weight $\frac{28 \text{KG}}{\text{KW}} \times .593 \text{KW}$ ) = | 16.6KG    |

The total power processor, solar array and thermal control system weight is 68.8KG and the ratio of power processor weight total is .587. This ratio is off the 0.5 point and shows that a different design could reduce the overall weight.

Figure 2-11. Power Processor Weight-Efficiency Optimization

The estimated optimum solution is:

Total weight 65KG

Power processor weight 32.5KG

Power processor losses 677W

Power processor efficiency 90.5%

A redesign of the magnetic components would easily provide these optimum characteristics and provide a thrust system weight savings of 3.8KG per ion thruster.

This example shows the optimization procedure and is dependent on the accuracy of the solar array density and the thermal control system density.

#### 3 0 BASELINE DESIGN

After the review and approval of the preferred configuration by the NASA Project Office on 18 August 1977, a more detailed electrical and mechanical design of the power processor was performed for a beam power rating of 2.2KW and 6KW Both the electrical, mechanical and thermal interfaces were reviewed and incorporated into the preliminary design concept

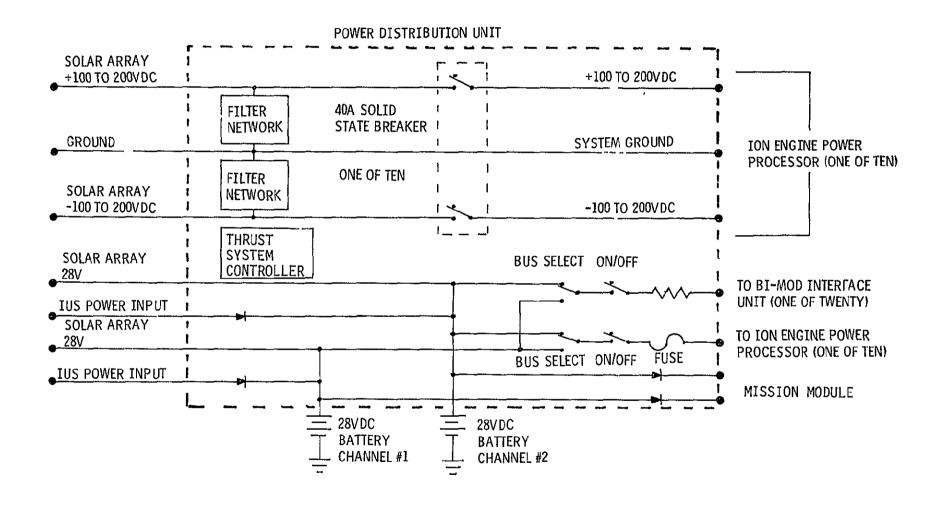

# 3 1 Power Distribution System

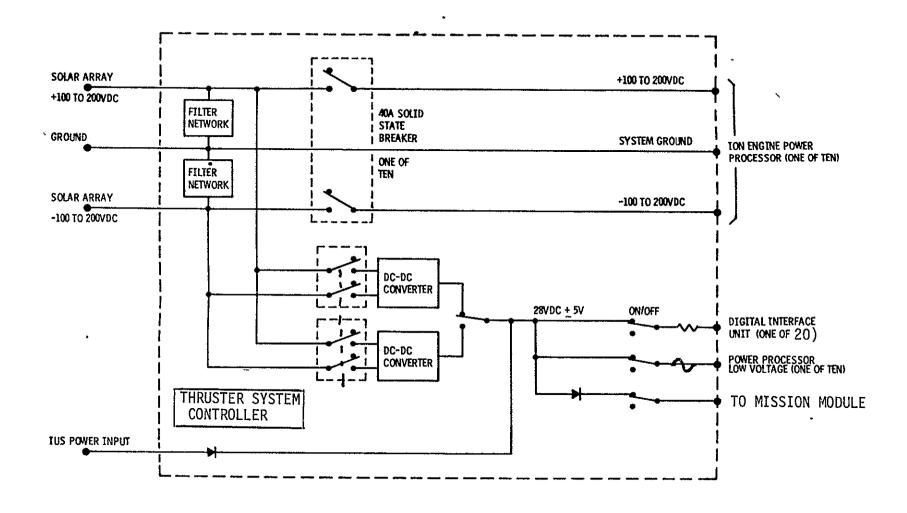

Figure 3-1 illustrates the power distribution system selected by NASA Lewis that was used to establish the necessary electrical interfaces for detailed electrical design of power processor. Power from the high power solar array is supplied to the main power distribution unit at  $\pm 100$  to  $\pm 200 \text{VDC}$  Electromagnetic interference filters control the reflected AC noise that can be returned from the spacecraft load to the large solar array surfaces

Solid state DC breakers are used with each ion engine power processor to protect against any power line failure or failures in the power processor power electronics

The unregulated solar array bus also goes through separate solid state breakers to two redundant DC-DC converters that generate 28VDC @ 1500W output to supply the low voltage electronics of the ion engine power processor and to the spacecraft

By eliminating the DC-DC converter, and using a 28VDC solar array, the power processor design would still be compatible with the new power distribution system

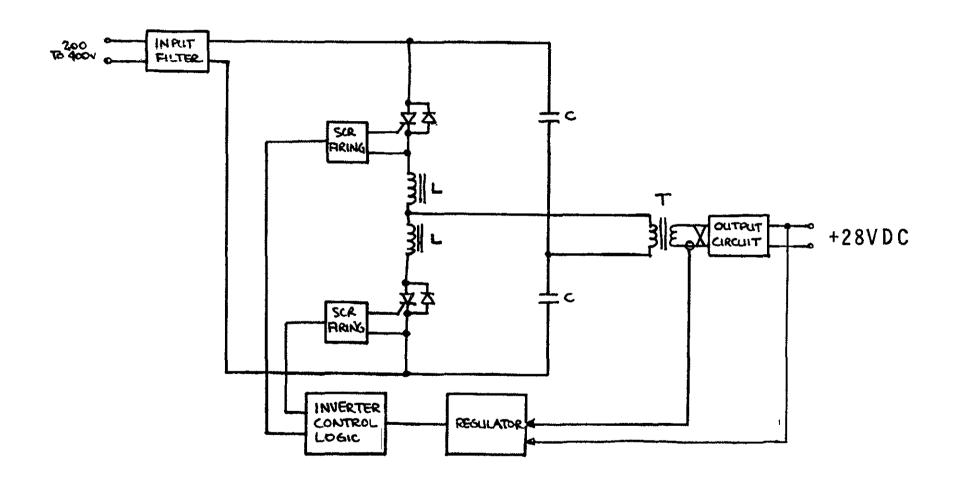

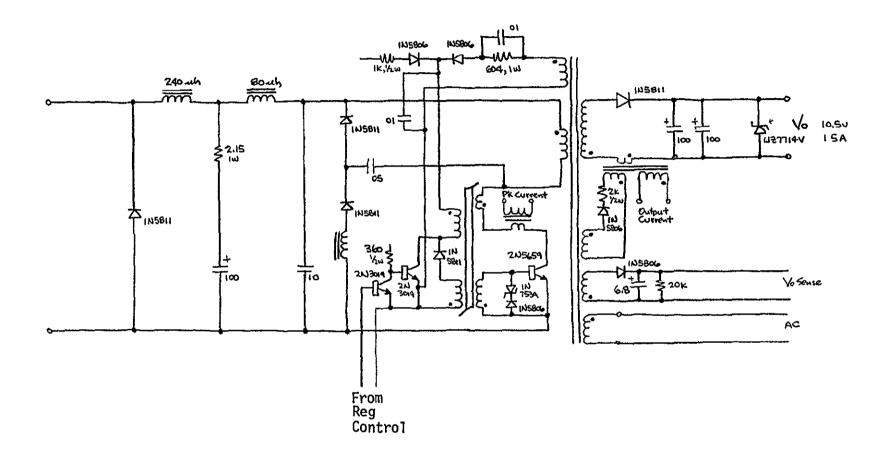

Figure 3-2 illustrates the schematic of the 28V DC-DC converter. It is a half bridge thyristor series resonant inverter operating at 20kHz Table 3-I summarizes the component weight, losses and part count for the electrical design. Preliminary estimate of efficiency is 88% and should be constant for a load range of 25 to 100% during the expected mission flight profile.

During launch, 28VDC power will be supplied directly from the shuttle interim upper stage (IUS) and provides necessary 28VDC power for the ion engine power processors and to the spacecraft.

Figure 3-1. Power Distribution System Block Diagram

Figure 3-2. Schematic of DC-DC Converters Used to Generate 28VDC Power Bus

Table 3-I Summary of 28VDC Bus Converter (1.5KW Output Power Rating)

|                                                               | COMP. WT.          | LOSSES<br>Watts | PART<br>COUNT |

|---------------------------------------------------------------|--------------------|-----------------|---------------|

| Power Stage (Input Filter Series Inverter, Output Transformer | 6677.3             | 186.601         | 55            |

| ectifier and Filter) CCR Firing                               | 90. 83             | 13, 331         | 78            |

| Series Inverter Control                                       | 76. 83             | . 980           | 140           |

| Regulator                                                     | 82.44              | .325            | 72            |

| Bias Supply                                                   | 314. 41            | 2.714           | 91            |

|                                                               | <b>7241. 81</b> gm | 203. 951 W      | 436           |

88% EFFIC

Continued system study is necessary to identify all of the interfaces to ensure a compatible electrical propulsion spacedraft with a Shuttle/IUS Launch Vehicle.

A redundant microprocessor thrust system controller performs all power control and management, Bi-Mod control, thrust control and failure analysis.

The features of this system configuration are:

- +100 to +200VDC supplies the high power loads

- 28VDC power distribution for EMC control and ease of integration of all low power equipment

- Interfaces with Bi-Mod, Mission Module, and IUS

- Filter networks control high power bus impedance for EMC control

- Solid state breakers provide the necessary protection and fault clearing of  $\pm 100$  to  $\pm 200$ VDC for the power system

- Thrust system controls the flow of power and the operation of the ion engines

- On/Off control and fault clearing for 28VDC loads.

Both hardware and software development work are necessary for the power distribution unit in the following areas:

- a) Power Distribution System

- b) Thrust System Controller

- c) Solid State Breakers

- d) DC-DC Converter Line Regulators

### 3.2 Command System

The overall spacecraft command system must include the electric propulsion module and its power processor modules.

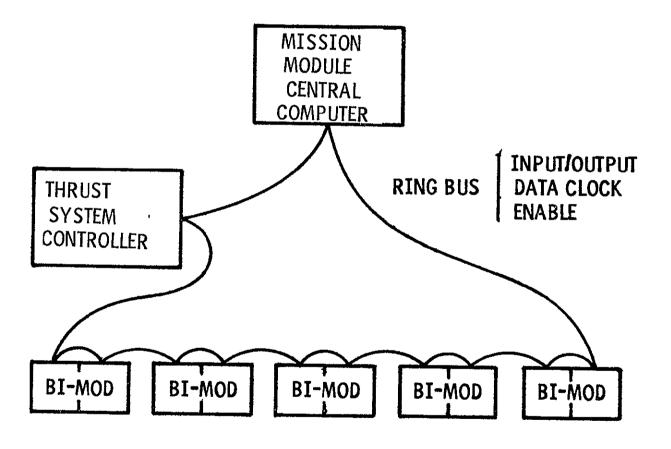

Figure 3-3 shows the basic block diagram for the command system and the inter-relationship of the spacecraft central computer, thrust system controller, located in the power distribution unit and electric propulsion Bi-Mod. The ring bus command line allows for open in the cabling and still allows total system operation.

With the use of microprocessors, most of the operational controls can be located at the Bi-Mod and we can limit the amount of data that must be transferred and processed by the thrust system controller and the spacecraft computer.

A reliability analyses should be performed on the proposed configuration to identify the level of redundancy that should be maintained in the command system.

Figure 3-3. Command System Block Diagram

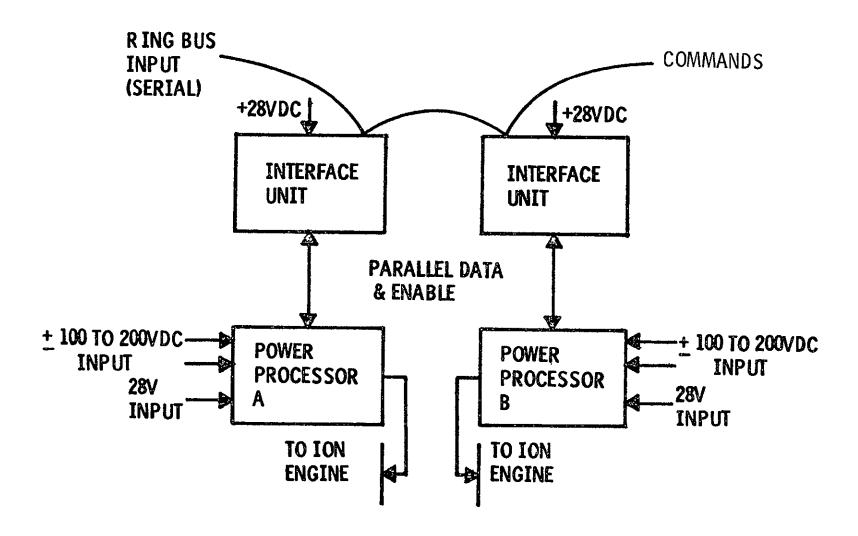

# 3.3 Bi-Mod Configuration

Figure 3-4 shows the block diagram for the electric propulsion Bi-Mod where two ion engines and two power processors form a complete mechanical subassembly. All of the electrical interfaces are illustrated in the diagram:

- Serial command data (high speed)

- 28VDC for microprocessor interface unit

- Low speed parallel command & data between the interface unit and the power processor for high noise immunity

- ±100V to ±200VDC solar array input to each power processor

- 28VDC for the low level power processor electronics

- Power processor output lines to the ion engine gimbals Gimbals controlled by Thrust System Controller.

Each power processor is dedicated to its own ion engine and there is no sharing of electric functions between the power processors.

The ion engines and power processors share only the mechanical structure and heat pipe/radiator assembly to affect a overall system weight saving.

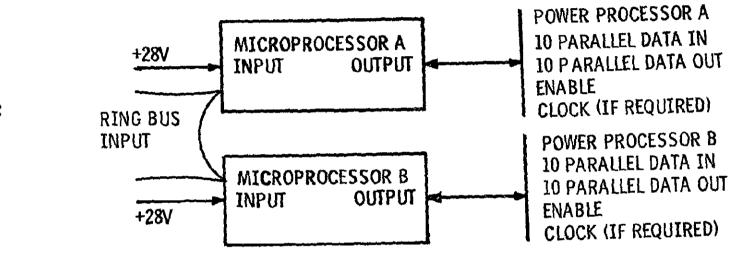

Figure 3-5 shows the interfaces between the microprocessor digital interface unit and the two power processors. The input data to the microprocessor is high speed serial data. The outputs to the power processor are low speed parallel data lines which extra filtering can be added to provide high noise immunity for the power processor control electronics.

Table 3-II summarizes the features of this proposed digital system.

Figure 3-4. Bi-Mod Configuration Block Diagram

Figure 3-5 Bi-Mod Interface Unit Configuration

# Table 3-II Features of Bi-Mod Interface Unit Configuration

- Separate Interface Unit (Microprocessor) for Each Ion Engine

- 28V Power can Turn On/Off Each Interface Unit

- All Output Lines Filtered

- 10 Parallel Outputs (3 for Address & 7 for Data)

- Optical Isolation for Input and Output

- High Speed Input Data/Low Speed Output Data

### 3.4 Power Processor Block Diagram

Figure 3-6 illustrates the basic block diagram for the Extended Performance Power Processor. The 200 to 400VDC bus supplies power through a common first stage input filter and separate 2nd stage input filters to the beam inverter and the discharge inverter, respectively.

28VDC supplies power to the low level outputs each with their own dedicated dc/dc converter that provides the necessary regulation, control and isolation for the different ion engine outputs.

A separated dc/dc converter supplies internal control logic power.

A microprocessor digital interface unit controls the total power processor through the command, protection and telemetry electronics:

- to startup an ion engine

- to throttle the ion engine thrust

- to change power processor set point to be compatible with ion engine thrust

- to recycle the outputs during ion engine arcs or overloads

- to provide an orderly shut-down of the ion engine

The discharge supply V9 is used during startup to supply power to V3 and V4 outputs and reduce the power processor part count.

Separate boosters are used for the V9, V7 and V8 outputs to initiate a discharge in the mercury plasma.

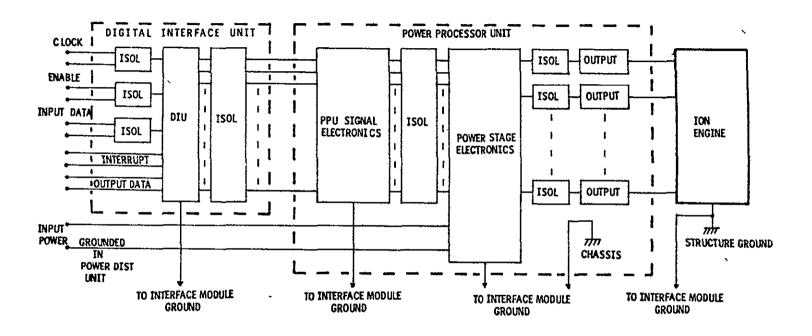

Figure 3-7 presents the grounding system designed into the power processor electronics to eliminate high ground loop currents that could damage the low level control electronics during ion engine overload or shorts.

Both optical coupling and transformer magnetic isolation are used to provide the necessary separation between.

Microprocessor Digital Interface Unit PPU Signal Electronics PPU Power Stage Electronics Ion Engine

A separate ground return wire goes from each area to a single point ground located in the electric propulsion system interface module which connects the solar array and its drive system to the Bi-Mod mechanical assembly.

Figure 3-6. Electric Propulsion Power Processor Block Diagram

Figure 3-7. Power Processor Grounding System Block Diagram

This basic grounding system has been used on three other electric propulsion power processor breadboard designs and the Transmitter Experiment Package without any operational problems. This ground isolation technique does have a slight weight and loss penalty.

#### 3.5 Electrical Design

A detailed electrical design was performed based on the power processor block diagram shown previously in Figure 3-6. Two different designs were performed in support of the following programs:

- Halley Comet Mission Power Processor with a 6KW Beam Supply

- Alternate Electric Propulsion Missions using a Power Processor with the Standard 2.2KW Beam Supply

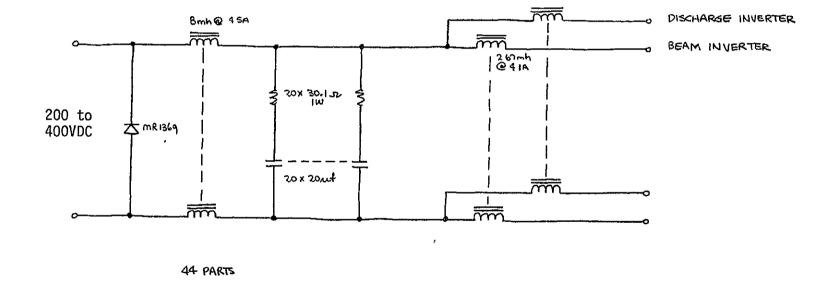

### 3.5.1 Input Filter

Figure 3-8 shows the schematic for the input filter for the Halley Comet Power Processor. It includes a two stage L-C power filter. The first stage capacitor contains series resistance to provide the necessary damping for the high efficiency input filter during input power bus disturbances. Each output load such as the discharge inverter and beam inverter has its own 2nd stage inductor. The second stage capacitors are located near the switching semiconductor located at each inverter. Table 3-III summarizes the input filter design details. This filter design was scaled down for the Alternate Electric Propulsion Missions.

FIGURE 3-8 Input Filter

Table 3-III Design Summary - Input Filter (6KW)

|                                   | WEIGHT    | LOSSES | PART COUNT |  |

|-----------------------------------|-----------|--------|------------|--|

| INDUCTOR - FIRST STAGE            | 1750      | 10.48  | 1          |  |

| CAPACITORS - FIRST STAGE          | 1750      |        | 20         |  |

| INDUCTOR - SECOND STAGE-BEAM      | 750       | 9.67   | 1          |  |

| INDUCTOR - SECOND STAGE-DISCHARGE | 102       | .83    | 1          |  |

| RESISTORS                         | 1         |        | 20         |  |

| DIODE                             | 75.1      |        | ĭ          |  |

|                                   | 4368.I gm | 20.98W | 44         |  |

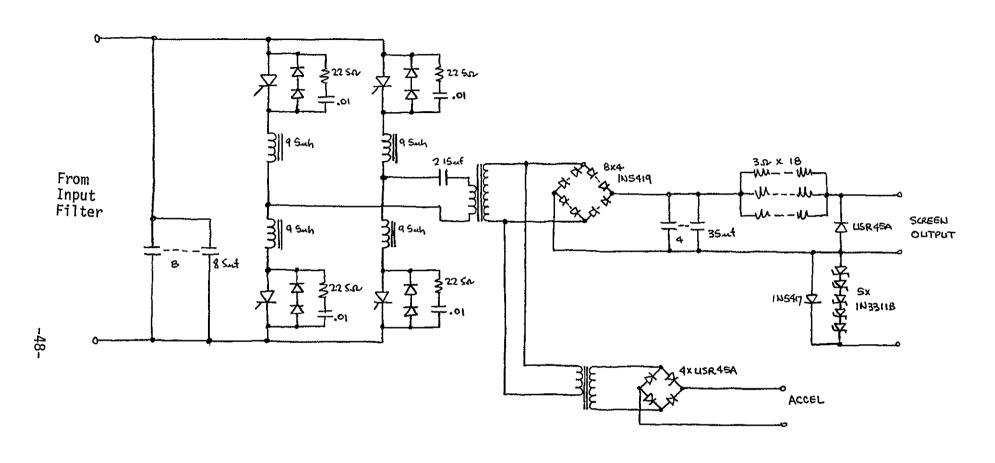

#### 3.5.2 Beam Supply

Figure 3-9 shows the schematic of the thyristor bridge inverter for a 3KV - 2A screen output. It includes four  $9.5\mu h$  series resonant inductors and a single  $2.15\mu F$  series resonant capacitor.

The power transformer feeds the main output power through a diode bridge and output filter capacitor composed of four 0.5 $\mu$ F capacitors. The output resistor network limits the peak surge currents that can flow through the output shorts.

A low power transformer is connected across the main power transformer output winding to develop the negative accelerator potential. The split of transformer reduced the winding and insulation complexity for the main power transformer.

Figure 3-10 is the schematic of thyristor firing network. The firing network provides both turn-on pulse for the thyristor gate-cathode and turn-off pulse to ensure the fast turn-off of the power thyristor.

Figure 3-11 is the redesign of the series resonant inverter control logic using  $T^2L$  digital logic. The basic operation and block diagram of the control logic is presented in NASA CR-134785 Power Processor for a 30 cm Ion Thruster. The thyristor current signal going to zero determines the end of each power half cycle. The series capacitor voltage sensor protects the power stage from excessive capacitor voltage during transient operation

Figure 3-12 is the redesign of regulator control electronics using T<sup>2</sup>L digital logic and low power operational amplifiers. It includes (1) the screen voltage regulator with ASDTIC feedback loop from the output filter capacitors and commands a method to adjust the output voltage level, (2) primary winding current regulator and (3) accelerator output current limit which protects during an output overload.

Table 3-IV presents the design summary for the 6 kW Beam Power Supply.

Figure 3-9 6KW Bridge Series Resonant Beam Inverter

Table 3-IV Design Summary - Beam Inverter SCR Bridge - 6KW

|                         | Component<br>Weight | Losses   | Part Count |

|-------------------------|---------------------|----------|------------|

| POWER STAGE             | 9388.1              | 408.6    | 106        |

| SCR FIRING              | 173.85              | 26.251   | 148        |

| SERIES INVERTER CONTROL | 76.83               | .980     | 140        |

| REGULATOR               | 123.47              | 1.320    | 118        |

| ACCELERATOR REGULATOR   | 89.78               | 2.104    | 50         |

|                         | <del> </del>        |          |            |

|                         | 9852.03 gm          | 439.255W | 562        |

#### 3.5.3 Discharge Supply

Figure 3-13 presents the schematic for the discharge supply. It is a 50kHz transistor full bridge series resonant inverter. The series resonant inductor is  $72\mu h$  and the series resonant capacitor is  $0.14\mu F$ .

Figure 3-14 shows the schematic for the transistor drive network It includes proportional basedrive current and reverse turn-off current.

Figure 3-15 is the control logic for transistorized inverter. It is designed with  $T^2L$  digital logic and is very similar to beam inverter control logic shown in Figure 3-11, except that the interface with transistor drive network is changed.

Figure 3-16 is the discharge output regulation. It includes three regulation signals (1) maximum discharge output voltage (2) discharge current as a function of command reference, and (3) primary current limit for peak output power control.

Figure 3-17 is the schematic of the discharge booster circuit that is used to initiate the mercury arc in the discharge chamber during ion engine startup. The power stage used is a buck/boost converter.

Table 3-V summarizes the discharge supply characteristics.

Figure 3-13 Discharge Inverter Power Stage Transistor Bridge

Table 3-V Design Summary - Discharge Inverter 50kHz Transistor Bridge - 815W Max. (500W Nom)\*

|                         | WEIGHT    | LOSSES * | PART COUNT |

|-------------------------|-----------|----------|------------|

| POWER STAGE             | 1493.6    | 77.54    | 28         |

| TRANSISTOR DRIVE        | 243.17    | 16.990   | 167        |

| SERIES INVERTER CONTROL | 71.03     | .924     | 130        |

| REGULATOR               | 113.87    | .493     | 97         |

| B00STER                 | 134.01    | . 783    | 59         |

| <u></u>                 | 2055.68gm | 96.73W   | 481        |

### 3.5.4 Low Voltage Supplies

The low voltage supplies include the following:

V1 V2 V6 V5 V7 and Booster V8 and Booster V12 Re1ay Driver

Auxiliary electronics necessary for the low voltage supplies include the clock which is a common timing unit for all supplies and ramp which is used for the output regulator stability. All low level control electronics use  $T^2L$  digital electronics and low power operational amplifiers to reduce the overall power drain necessary for the control electronics.

Figure 3-18 is the schematic of the master oscillator with a basic frequency of 25kHz and the ramp generator for output regulator stability.

Only two typical outputs will be presented in the following discussion. All power stages use the buck/boost DC-DC converter. Figure 3-19 is the schematic of the power stage for VI main vaporizer supply. It contains a two stage input filter, energy recovery network to shape the power transistor switching characteristics, proportional basedrive control, peak current sensor and output overcurrent protection.

Figure 3-20 is the schematic of the VI output regulator. It includes (1) maximum output voltage limiter, (2) overcurrent limiter and (3) main ion engine feedback loop that controls the vaporizing power as a function of the ion engine output beam current. The feedback loop includes all the necessary ion engine frequency compensation networks.

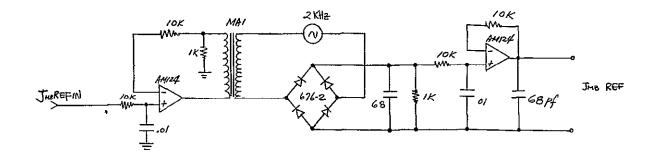

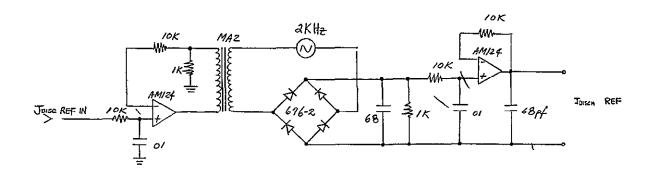

Figure 3-21 is the schematic of the V7 output and its high voltage booster which is used to initiate an arc during an ion engine startup. One buck boost circuit is used as the power stage and a second buck boost circuit is used as the high voltage booster.