https://ntrs.nasa.gov/search.jsp?R=19780024788 2020-03-22T02:08:12+00:00Z

CR-152177

# The ILLIAC IV Memory System: Current Status and Future Possibilities

David Stevenson

May 8, 1978

Revised August 7, 1978

Institute for Advanced Computation NASA-Ames Research Center Moffett Field, California

## CR-152177

# THE ILLIAC IV MEMORY SYSTEM: CURRENT STATUS AND FUTURE POSSIBILITIES

- NAS2-8870 Technology Development Corporation

- NAS2-8728 Lear Siegler Incorporated, Management Services Division

- NAS2-9359 Computer Sciences Corporation

## CONTENTS

|      | Contents                        |                                                    |          |  |  |  |

|------|---------------------------------|----------------------------------------------------|----------|--|--|--|

|      | Tables                          |                                                    |          |  |  |  |

|      | Figures                         |                                                    |          |  |  |  |

|      | Acknowledgements                |                                                    |          |  |  |  |

| I.   | Introduction                    |                                                    |          |  |  |  |

|      | A.                              | Background of the Study                            | 1        |  |  |  |

|      | в.                              | Structure of the Report                            | 2<br>4   |  |  |  |

| II.  | Executive Summary               |                                                    |          |  |  |  |

|      | A.                              | Description of the Current System                  | 4        |  |  |  |

|      |                                 | Alternative Enhancements                           | 6        |  |  |  |

|      |                                 | Relative Merits of the Enhancements                | 8        |  |  |  |

| III. | Cur                             | rent System Status and Use                         | 11       |  |  |  |

|      | A.                              | Present System Configuration                       | 13       |  |  |  |

|      |                                 | 1. System Overview                                 | 13       |  |  |  |

|      |                                 | 2. Illiac Array Memory System                      | 21       |  |  |  |

|      |                                 | 3. Support System                                  | 25       |  |  |  |

|      |                                 | 4. Illiac Speed Enhancements                       | 27<br>33 |  |  |  |

|      | B. Application Program Examples |                                                    |          |  |  |  |

|      |                                 | 1. Twelve Representative Illiac Codes              | 33       |  |  |  |

|      |                                 | 2. Conclusions                                     | 39       |  |  |  |

|      | C.                              | A Memory Model and Its Implications                | 42       |  |  |  |

|      |                                 | 1. Parameters of the Model                         | 42       |  |  |  |

|      |                                 | 2. Memory Size and Data Access Rate                | 46       |  |  |  |

|      |                                 | 3. Bandwidth between Local and Extended Memory     | 48       |  |  |  |

|      |                                 | 4. Extended Memory Size and System Bandwidth       | 50       |  |  |  |

|      |                                 | 5. Summary                                         | 51       |  |  |  |

|      | D.                              | •                                                  | 52       |  |  |  |

|      |                                 | 1. Size of Local and Extended Memory               | 52       |  |  |  |

|      |                                 | 2. Error Correction on Memory                      | 53       |  |  |  |

|      |                                 | 3. Virtual Memory                                  | 54       |  |  |  |

|      |                                 | 4. On-Line File Storage                            | 56       |  |  |  |

|      | Ε.                              | Scope and Characterizations of Future Developments | 59       |  |  |  |

| IV.  | Fut                             | ure Alternatives                                   | 62<br>64 |  |  |  |

|      | A. Technology Survey            |                                                    |          |  |  |  |

|      |                                 | 1. Disk Technology                                 | 65       |  |  |  |

|      |                                 | 2. Solid State Rotating Devices                    | 67       |  |  |  |

|      |                                 | 3. Random Access Memories                          | 69       |  |  |  |

|      |                                 | 4. Concluding Remarks                              | 72       |  |  |  |

, NN

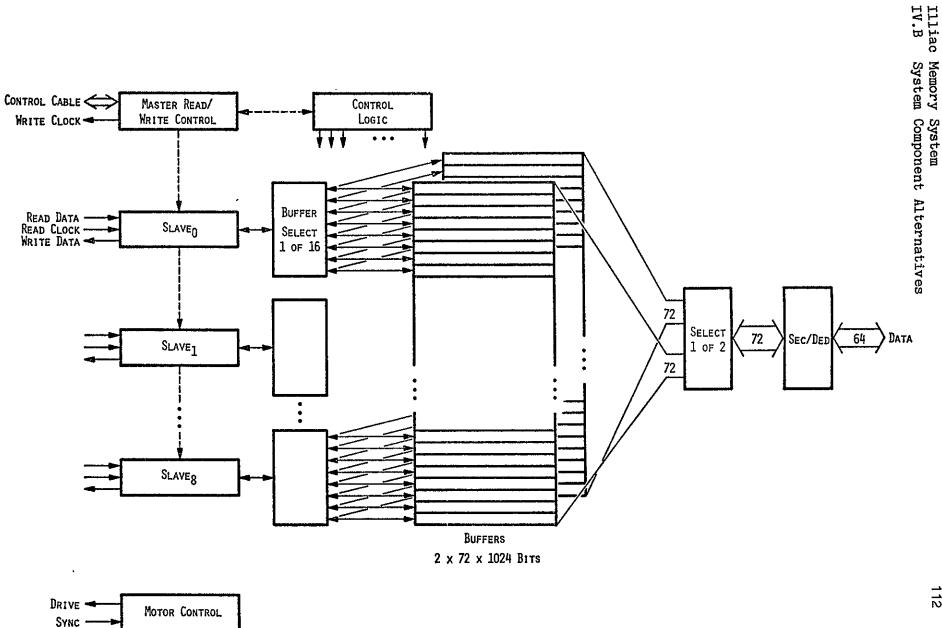

| IV. | в.  | System Component Alternatives                                                               | 73  |

|-----|-----|---------------------------------------------------------------------------------------------|-----|

| _   |     | 1. Local Memory Replacements                                                                | 74  |

|     |     | 2. Extended Memory Replacements                                                             | 79  |

|     |     | a. Charged-Coupled Devices for Extended Memory                                              | 79  |

|     |     | b. RAM Based Extended Memory                                                                | 97  |

|     |     | c. Disk Based Memory System                                                                 | 109 |

|     |     | 3. On-Line File System                                                                      | 113 |

|     | с.  | Alternative Memory Systems and their Evaluation                                             | 120 |

|     | 0.  | 1. Four Million Word Local Memory                                                           | 121 |

|     |     | 2. Sixty-six Million Word CCD Extended Memory                                               | 123 |

|     |     | 3. Sixteen Million Word RAM Extended Memory                                                 | 125 |

|     |     |                                                                                             | 127 |

|     | _   | 4. Relative Merits of the Systems<br>Ability of the Proposed Systems to Meet Future Demands | 130 |

|     | D.  |                                                                                             | 133 |

|     | Glo | ssary of Terms                                                                              |     |

## FIGURES

-

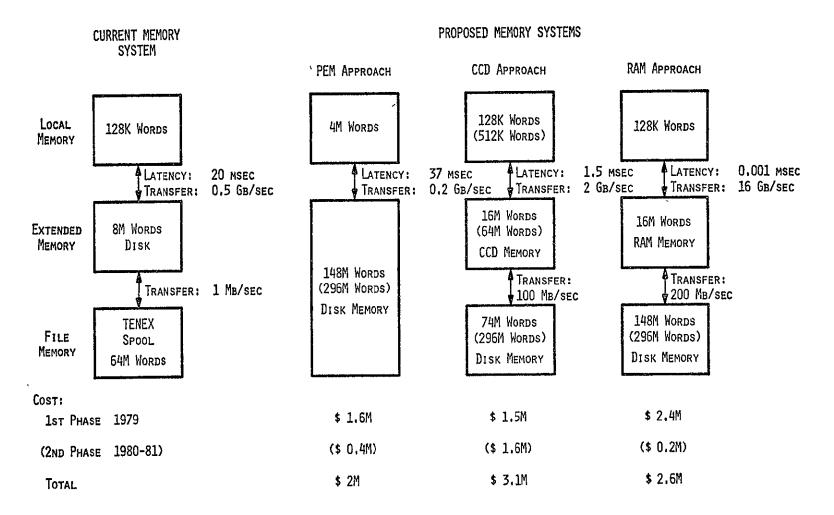

| II.1   | Current and Proposed Memory Systems            | 7   |

|--------|------------------------------------------------|-----|

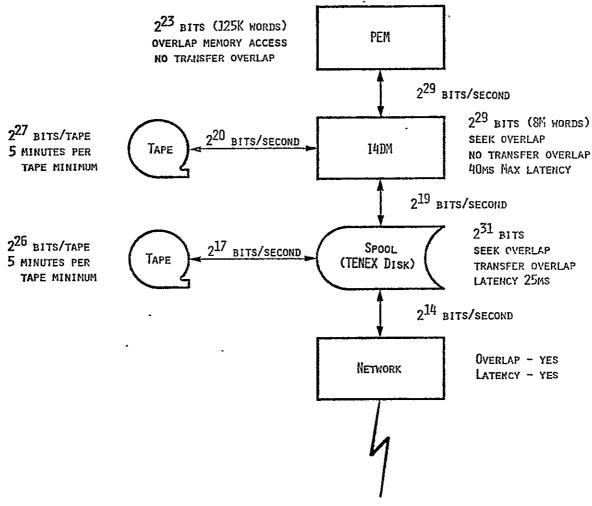

| III.1. | Current Illiac Memory System Characteristics   | 14  |

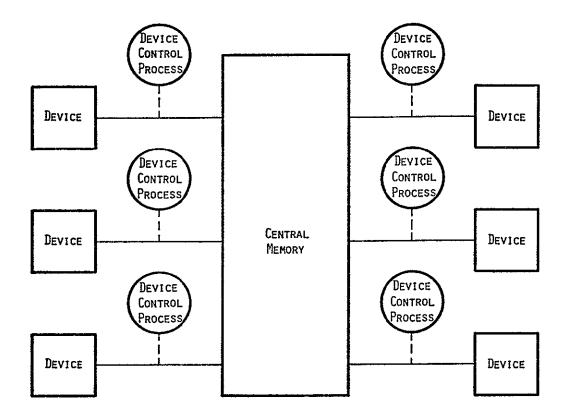

| 111.2. | The Central Memory Concept                     | 16  |

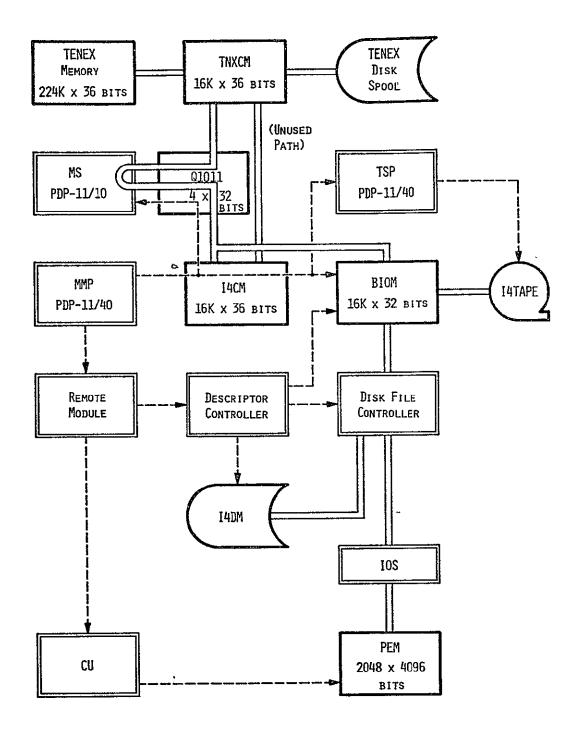

| III.3. | Current System Implementation                  | 17  |

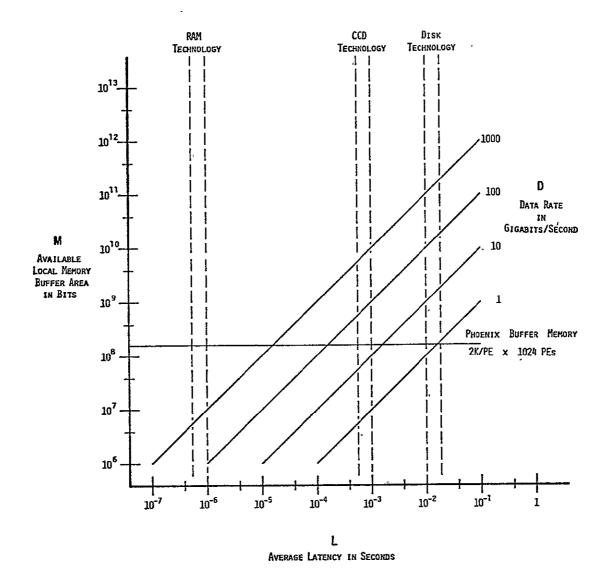

| III.4. | Graphs of $2L = M/DS$                          | 47  |

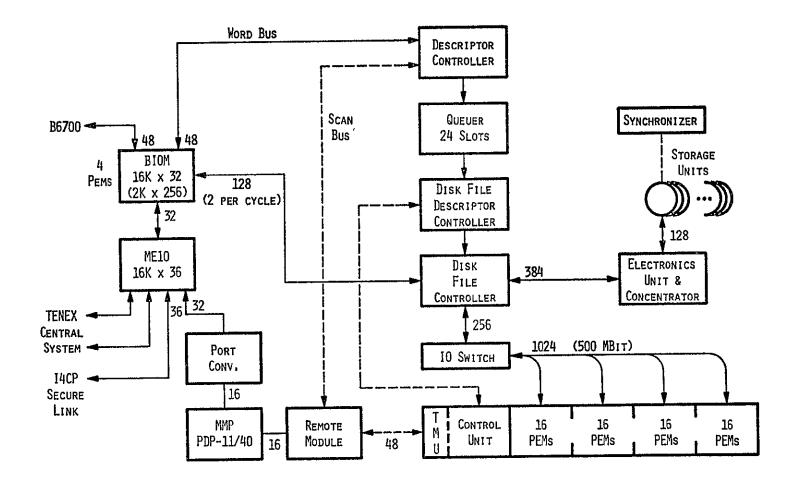

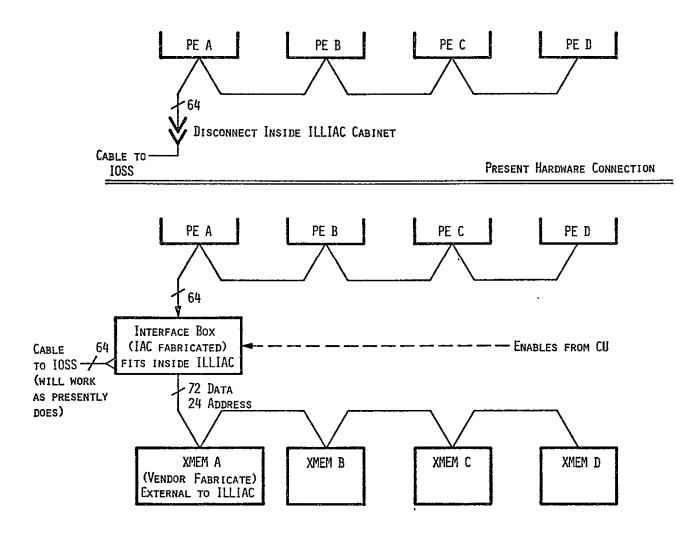

| IV.1.  | Current Illiac IOSS                            | 81  |

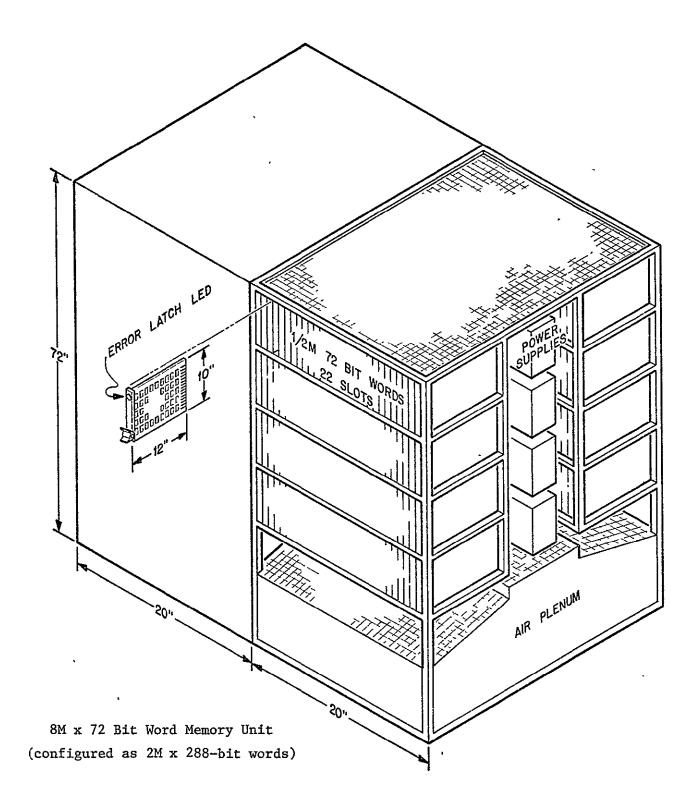

| IV.2.  | 2M Word Memory Unit Physical Layout            | 83  |

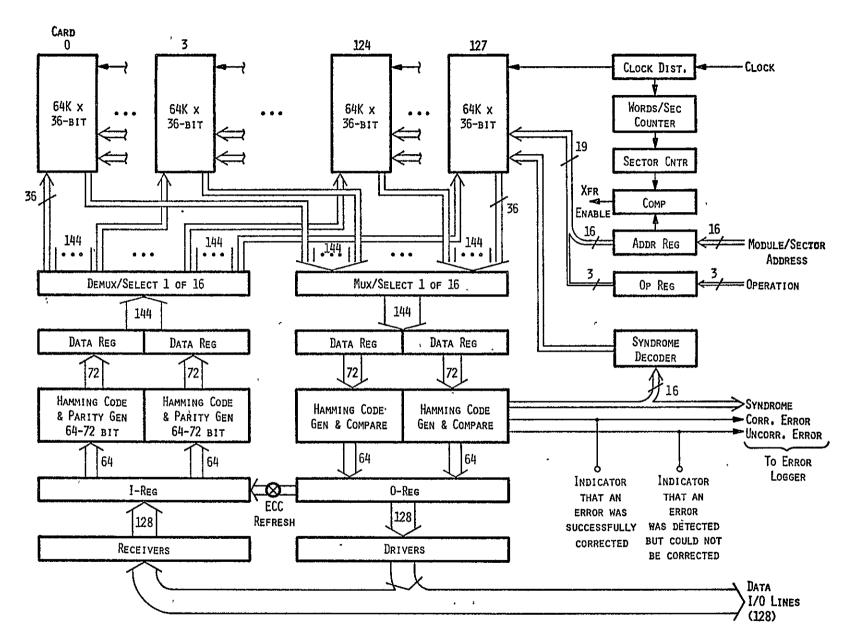

| IV.3.  | 2M 128-bit Word Memory Unit                    | 84  |

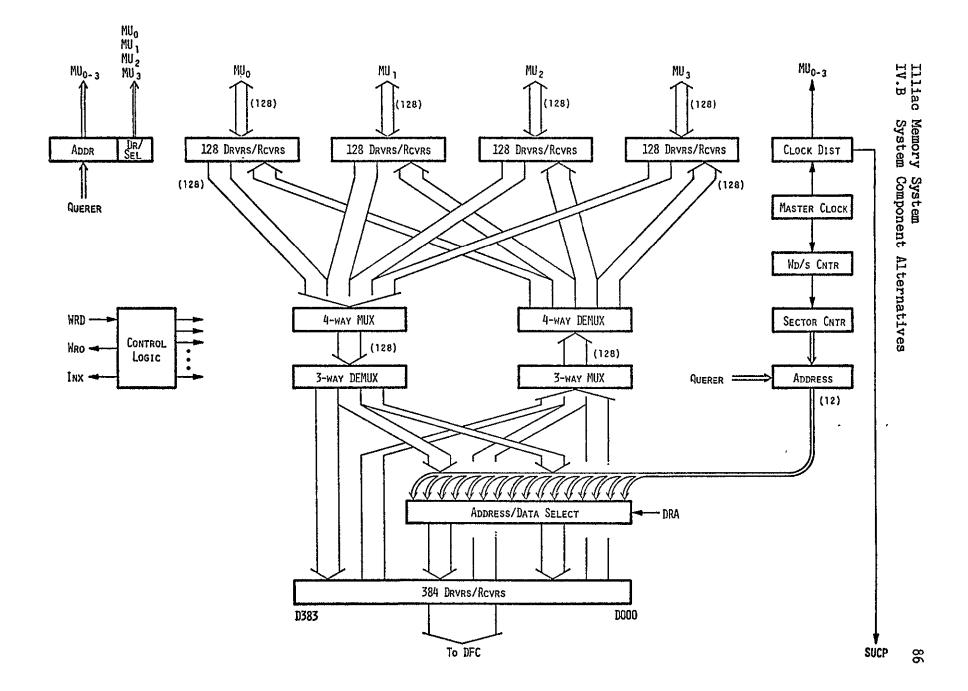

| IV.4.  | EU Replacement Memory Controller               | 86  |

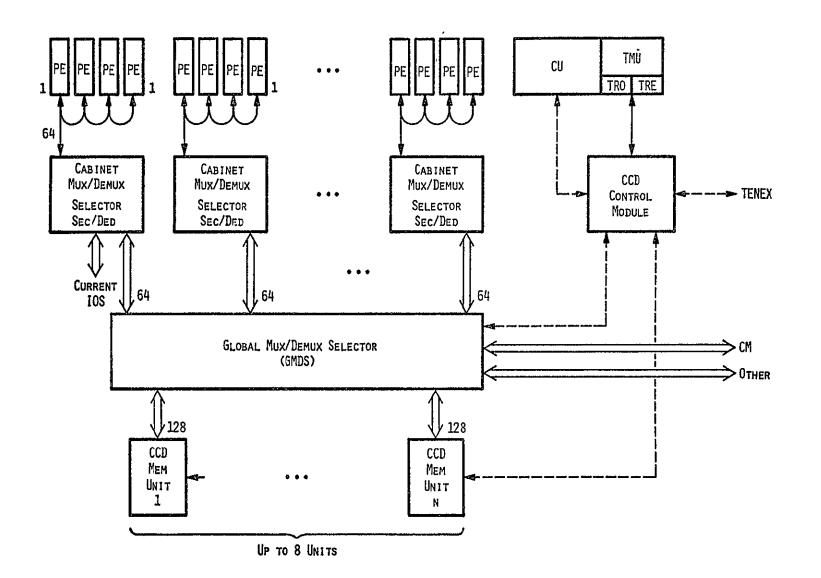

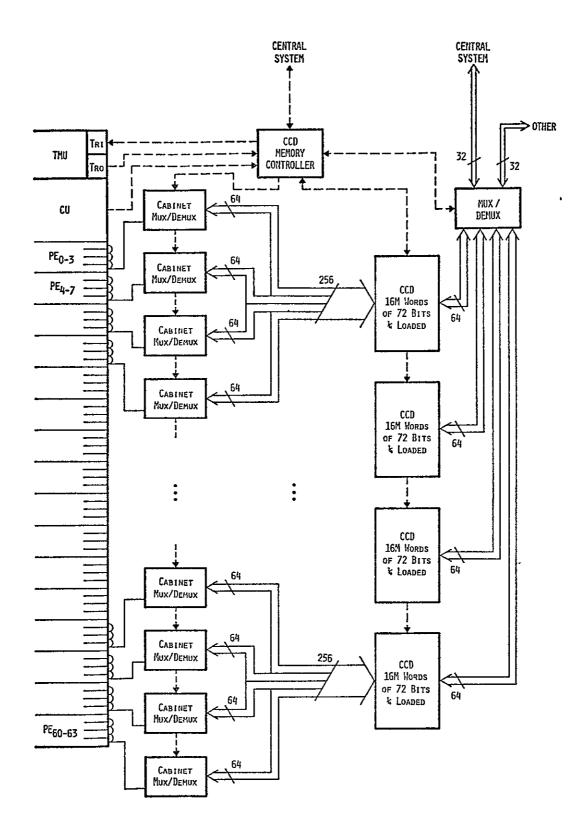

| IV.5.  | CCD Memory System Block Diagram                | 91  |

| IV.6.  | CCD Memory System Using Quarter Loaded Modules | 92  |

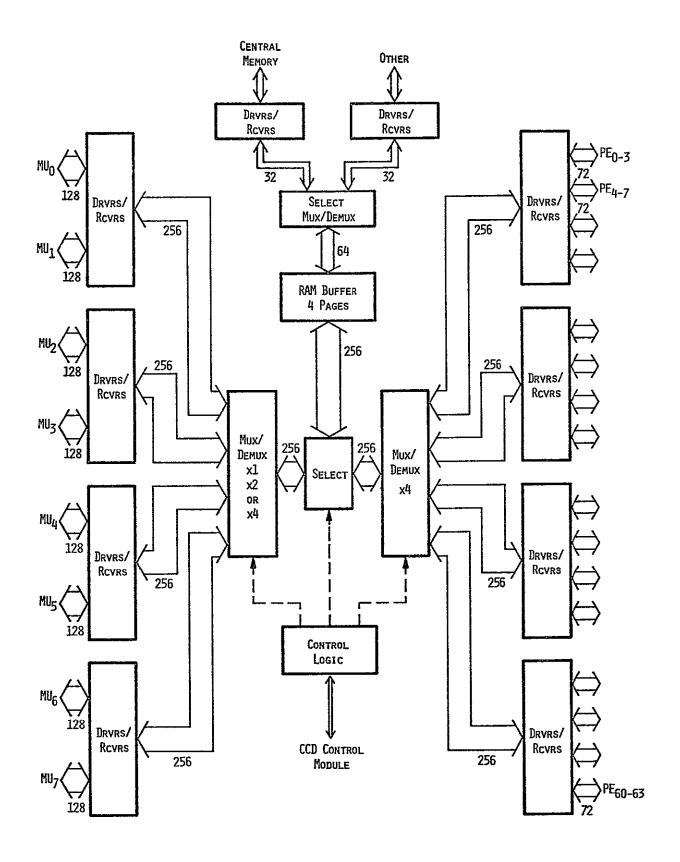

| IV.7.  | Global Mux/Demux Selector                      | 93  |

| IV.8.  | CCD Control Module                             | 95  |

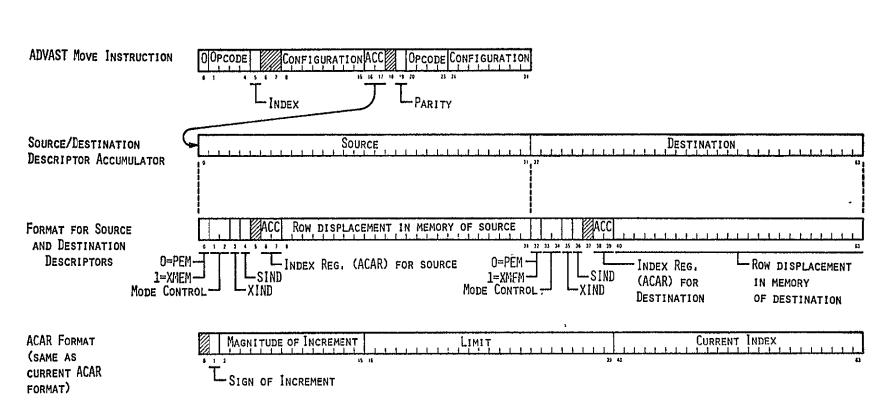

| IV.9.  | Format Specification for Move Instruction      | 99  |

| IV.10. | Move Instruction Timing                        | 100 |

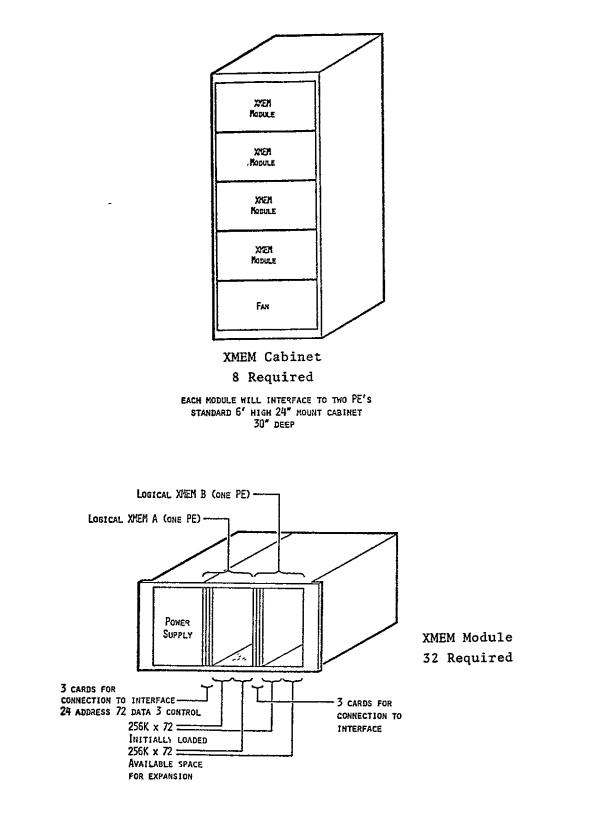

| IV.11. | RAM Memory Unit Physical Layout                | 102 |

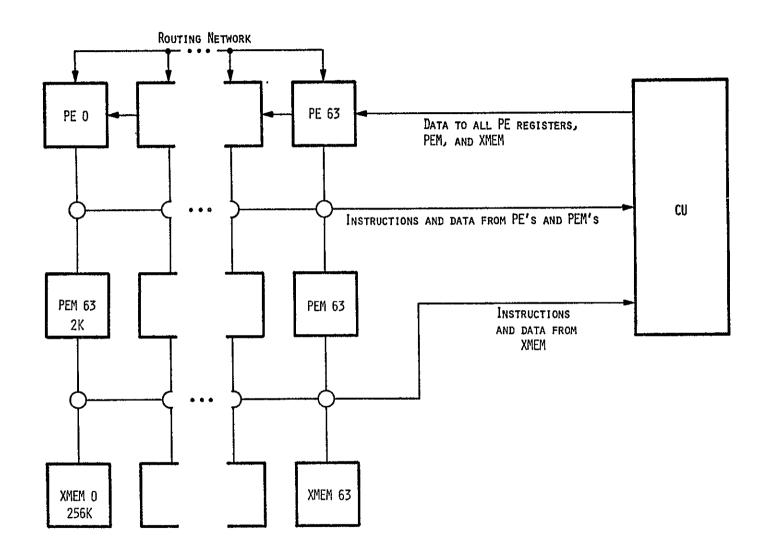

| IV.12. | System Block Diagram for RAM Extended Memory   | 104 |

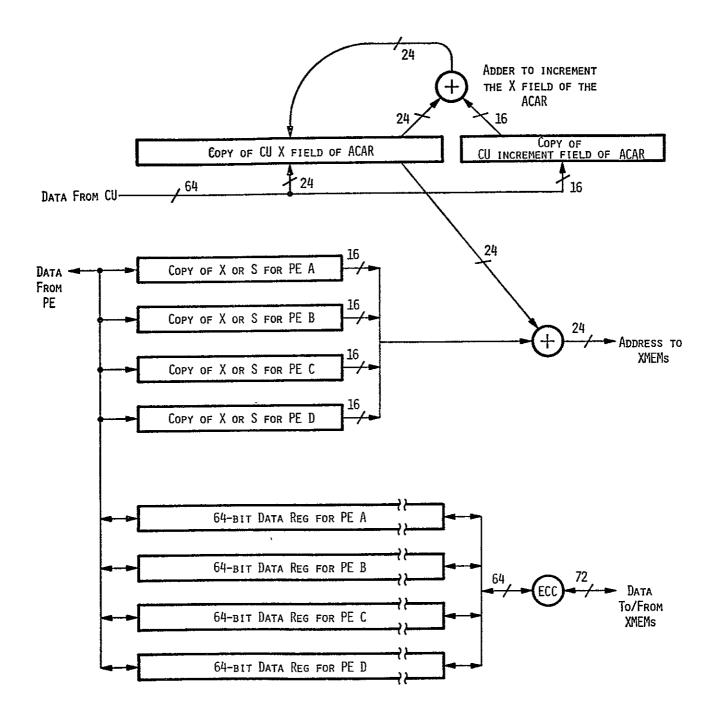

| IV.13. | Connection of RAM Extended Memory to Illiac    | 105 |

| IV.14. | Interface Block Diagram                        | 106 |

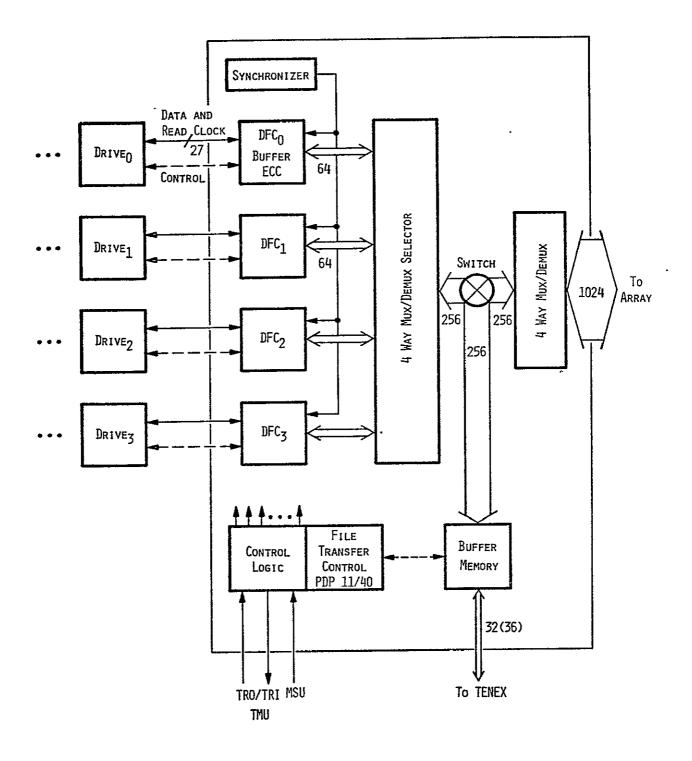

| IV.15. | 14 Extended Memory Using Ampex Disks           | 110 |

| IV.16. | Disk File Controller for Ampex Disk Memory     | 112 |

|        |                                                |     |

## TABLES

### page

| İII.i.   | Characteristics of some Major Illiac Programs           |    |  |  |  |

|----------|---------------------------------------------------------|----|--|--|--|

| III.ii.  | Expected Characteristics of Some Future Illiac Programs | 41 |  |  |  |

| III.ili. | I/O Characteristics of Some Major Illiac Programs       | 44 |  |  |  |

| III.iv.  | Storage Requirements for Illiac Jobs                    | 57 |  |  |  |

| IV.i.    | MTBF Calculations for a 16M Word CCD Memory             | 88 |  |  |  |

#### Acknowledgements

This report represents the work of many members of the Institute. The following individuals gathered information, designed the proposed systems, or otherwise contributed to this report: Jim Bennett, Hal Brown, Hsiau Chang, Gary Feierbach, Al Goodrich, Rich Guyon, Mo Gunn, Stu Hopkins, Chuck Johnson, Glenn Lewis, Ray Lim, Bill Malloy and Steve Tulloh. In addition, the following researchers at NASA-Ames were helpful in supplying information about their Illiac codes and their use of the system: Harry Bailey, Margaret Covert, Harvard Lomax, Walter Reinhardt, Bob Rogallo, Ken Stevens and Alan Wray.

David Stevenson Project Leader

#### I. Introduction

The Illiac IV was conceived in the mid-1960s; design began in 1967 and fabrication two years later. Since that time, memory technology has changed dramatically. For example, the fast local processor memory of the Illiac uses the first commercially available high speed bipolar memory devices (developed especially for the project), each chip having a storage capacity of 256 bits. Today, chips of comparable access speed have up to sixteen times as much storage capacity. A magnetic disk technology was selected for the extended memory of the Illiac. The years since then have seen the introduction of charged-coupled devices and magnetic bubble technology as alternative storage media, and the cost per bit of slow, random access electronic memory devices has decreased to the point that they are economically feasible for billion bit computer memories.

Not only has memory technology progressed, but the requirements being placed on the Illiac have also evolved in the intervening years. Now that considerable experience has been accumulated with two-dimensional models of physical phenomena, scientists in such areas as seismic and aerodynamic research have turned their attention to three-dimensional models, and this change increases memory requirements by at least a factor of ten; also the sheer amount of data being gathered by satellites has significantly increased the volume of data in signal and image processing. Finally, the inevitable deterioration of rotating mechanical devices due to age is beginning to impact the reliability and availability of the current memory system. Fortunately, the advances in memory technology can be brought to bear in relieving the two major pressures on the current memory system: replacements significantly different with respect to size and reliability are now feasible. This report examines several different enhancements.

#### I.A. Background of the Study

This study was charged with examining the future needs of researchers who will use the Illiac and estimating the requirements they will place on the memory system. The staff of the Institute who participated in the study were drawn from a broad base of disciplines: project designers, application programmers, systems specialists, and hardware engineers. Thus the study was capable of investigating all relevant issues concerning the Illiac memory system.

The underlying philosophy of the study was that memory enhancements to the system should be evolutionary rather than revolutionary in nature and that

Illiac Memory System I. Introduction

they should be aimed at meeting the forseeable needs of the Illiac user community during the next five years. The consequences of this philosophy were two-fold. First it was necessary to review the system architecture to determine its inherent limitations and current state. This determined the components which must be replaced and the limitations due to interfacing the replacements with the remaining system. The second consequence was the necessity to review the ways current users manage the system resources in solving their problems. This indicated the characteristics which would be desirable in the replaced components. Determining the characteristics of the current system and its users constituted the first phase of the study.

The second phase of the study considered various alternatives to replacing critical memory components. Three different approaches were explored to the point that their merits and limitations could be reasonably ascertained. The main issues which were considered for each alternative were cost, risk, system impact, software requirements and implementation schedules.

Two major areas concerning the memory system were not included in this study. The first was the user interface: the job control issues of the way users acquire, describe and manipulate the various memory resources in the system. The second area was the performance evaluation of the system: the hardware and software tools used to collect and analyze system performance characteristics for system management and accounting purposes.

#### I.B. Structure of the Report

The next chapter provides an executive survey of the results of this study. The remainder of the report is devoted to a detailed presentation of the material which was gathered during the course of the investigation.

The third chapter presents the findings of the first phase. It begins with a description of the current system, its performance and status, and the limitations it places on possible enhancements. The chapter includes a description of the planned enhancements to the Illiac processor and the probable resulting increase in its speed. There follows a description of representative codes on the Illiac with respect to their memory usage characteristics; these are useful in projecting future computational demands that might be placed on the memory system. A model of the Illiac memory system is developed, and using the characteristics of the example codes, several conclusions about desirable characteristics for the future memory system are drawn. Finally, several less easily quantifiable influences on the memory system are discussed: the relationship between local memory size and the cost of designing user application codes, the need for error correction ability on various memory components, the feasibility of a virtual memory system on the Illiac, and the requirements for an on-line high performance file storage facility.

The final chapter presents the material developed during the second phase of the study. After a brief technology survey, different implementations are presented for each system memory component. Next, three different memory systems are proposed to meet the identified needs of the Illiac user community. These three alternatives differ considerably with respect to storage capacity and accessing capabilities, but they all offer significant improvements over the current system. Each proposed system is analyzed in detail, and their relative merits are discussed. The chapter concludes with a review of the current system weaknesses, and how these weaknesses will be addressed by the proposed memory systems.

#### II. Executive Summary

The memory system of a modern, large scale computer serves three different purposes: from the user's point of view, 1) it holds instructions and data for rapid accessing by the processor, 2) it contains the large data base for the computer to process, and 3) it provides storage for files when they are not being actively processed by the computer. In the Illiac IV computer's memory system, these functions are performed respectively by different memory devices: 1) a fast semiconductor local memory, 2) a large, high performance disk extended memory, and 3) a commercial disk and tape file system. In addition, the memory system has other components for buffering the data transfers between these devices.

The current Illiac memory system has enabled scientists to demonstrate the applicability of parallel processing in such diverse and important areas as computational aerodynamics, climate modelling, satellite image processing and seismic research. These past successes have generated demands for even greater capabilities in the memory system. Unfortunately, the current system, with some components nearing ten years in age, is showing signs of physical deterioration. It is now time to consider replacing some components and adding new facilities in order to insure that the Illiac system will remain responsive to the needs of its research community over the next five years.

#### II.A. Current System Configuration

The IAC computing facility consists of the Illiac IV computer, a Tenex based support system, and various other systems, such as a B6700 computer. The ILLIAC IV is an array processor consisting of sixty-four processing elements under explicit control of a central control unit; the control unit broadcasts instructions for the processing elements to execute. The Illiac processor has two memory components associated with it: a local memory and an extended memory. The file storage memory for the Illiac is currently part of the Tenex file system. Each of these components is generally regarded as inadequate to meet the expected demands on the Illiac during the next five years.

The Illiac has a one million byte (8.4 million bits) fast access local memory called the PEM -- the Processing Element Memory -- which is directly addressable by the processor. Most users have found that this memory is too small for efficient utilization of the machine's computational power (up to 40 million 64-bit floating point operations per second). The major

reason for the inefficiency lies in the fact that the large program data bases reside on the extended memory, with the local memory serving as a buffer area, and the buffer area available in the local memory is usually not large enough to mask all the delay incurred in accessing the extended memory. In addition, there are some programs for which a natural partitioning of the data base (for example a plane of a three-dimensional grid) will not fit in the available storage in local memory, and so an artificial sub-partitioning is employed with the attendant increase in program development time and in program execution time.

The current extended memory of the Illiac is a fixed-head disk which has been specially modified in order to support a transfer rate of 500 million bits per second. The capacity of the disk is around half a billion bits, which for several applications is too small. In addition, the disks themselves are showing signs of increasing deterioration which manifests itself in increasing maintenance costs and decreasing reliability and availability.

Currently, there is no special file system for the Illiac; Illiac files are stored in the Tenex file system in the central support system. This file system has a present capacity of about three billion bits. Since the immense speed of the Illiac makes the processing of very large files feasible, it is estimated that the on-line storage needed to support the Illiac is around eighteen billion bits; thus the storage capacity of the current system is severly limiting. The present system supports a transfer rate from this file system to the Illiac of slightly over one million bits per second. Even with the presently planned enhancement to this file system to increase the transfer rate to five million bits per second, the Tenex file system is clearly inadequate to support the processing of large data sets on the Illiac.

In summary, the Illiac memory system has five areas of weakness: the low bandwidth between the system and the outside world, the lack of adequate file storage space in the system, the inadequate bandwidth between the file system and the array, the transfer characteristics between the extended memory and the local memory (which result in either inefficient use of the development time to reduce this program significant machine or inefficiency), and the declining amount of extended memory available for user programs. For the current users, two of these weaknesses receive most attention: the size of the extended memory and the difficulty in using this memory efficiently. Because of its deteriorating state, the current extended memory will be replaced, and a satisfactory replacement will accentuate the current limitations of the file system.

By examining current codes on the Illiac and considering the planned development of these programs, it is possible to generate guidelines as to necessary or desirable characteristics of future memory systems to support these research projects. Briefly, the major characteristics are size of local and extended memory and the transfer rate between them. A transfer rate of 200 million bits per second is required, with a rate closer to one billion bits per second preferable. The local memory should be large enough to permit adequate buffers to compensate for the latency involved in accessing the extended memory; a ratio of at least 800 thousand bits of local memory for each millisecond of latency of the extended memory is dictated by the Illiac's current application programs. The capacity of the extended memory is governed by the size of the problems to be solved on the Illiac; a minimum size for the extended memory is one billion bits (sixteen million 64-bit words) with four billion bits preferred (sixty-six million words). This study identified three different approaches to memory systems enhancement which would meet these requirements.

## II.B. Alternative Approaches to System Enhancement

A review of the currently available memory technologies indicates that there are three approaches to enhancing the Illiac system which are technologically and economically feasible and still meet the performance characteristics demanded of the Illiac memory system. Basically there are two philosophies to enhancing the Illiac memory: concentrate on the local memory or on the extended memory. Emphasizing the local memory leads to one design; namely, a large local memory and a mundane (by Illiac standards) extended memory. Concentrating on the extended memory instead, two solutions are considered: a memory using charged-coupled devices for a high performance disk-like replacement or a random access memory using high integration semiconductor components. Both of these extended memory replacements also require a staging memory to buffer transfers between the support system and the Illiac, thus an on-line file system dedicated to Illiac files is included in each proposed memory enhancement. In the first approach, the extended memory can also serve these functions. These three approaches and their relative merits will be briefly described; they are summarized in figure II.1.

The first approach consists of a four million word local memory and a disk-based extended memory. The extended memory has an initial capacity of nine billion bits and can be increased in increments of 2.25 billion bits; a second phase calls for doubling the initial capacity. The transfer rate between local and extended memory is a maximum of 350 million bits per second, but the sustained rate would probably be closer to 200 million bits per second. The extended memory would also be used for buffering file transfers from the Illiac system to the external world, and it would also maintain Illiac files on-line for periods of one to two weeks (such as temporary files created for re-start purposes, or between runs in a multiple-run experiment). The cost of the initial configuration is approximately 1.6 million dollars and the second phase is about 200 to 500 thousand dollars, the later estimate depending upon whether error correction is found to be needed in the local memory. One would expect that most of the programs for such a system would restrict their data base so as to reside entirely in the local memory, with the extended memory being used to hold output and re-start data. Only a few programs would be expected to use the extended memory to hold the active data base of a program, and the large local memory insures that there would be adequate

LEGEND: K = 1024, M = MILLION, MSEC: MILLISECOND, WORDS = 64 BITS, MB = MEGABIT = MILLION BIT, GB = GIGABIT = BILLION BIT

Figure II.1.

Illiac Memory II. Executive

System Summary memory available for buffer areas. The transfer rate is less than half the current local to extended memory transfer rate, although this degradation would have a relatively minor effect on the total execution of most current programs. This approach is called the PEM approach since it concentrates on the local memory of the Illiac.

The second approach consists of a sixty-six million word extended memory, a half million word local memory, and a combined buffer memory and file memory. The first phase calls for a sixteen million word extended memory using charged-coupled devices and a five billion bit buffer/file memory The second phase consists of increasing the using disk technology. extended memory to the full sixty-six million word capacity and increasing the buffer/file memory to eighteen billion bits. It also includes enhancing the local memory to half a million words. The performance of the extended memory is such that problems users currently have using the disk-based extended memory will be reduced by an order of magnitude during the first phase and further alleviated during the second. The cost of this approach is approximately one and a half million dollars for the first phase and 1.6 million dollars for the second. This approach is called the CCD approach since this is the memory technology chosen for the extended memory.

The third approach is a sixteen million word extended memory which has the same characteristics as the present local memory. It also has the same buffer/file memory as the PEM approach. This extended memory would be constructed out of high density random access semiconductor memory chips. The second phase of this approach would be limited to increasing the buffer/file memory from nine to eighteen billion bits. By using a random-access extended memory, this approach virtually eliminates user objections to the current extended memory. The cost of this approach is approximately 2.4 million dollars for the first phase and 200 thousand dollars for the second. This approach is called the RAM approach since this is the memory technology chosen for the extended memory.

The schedule for all three approachs are virtually identical; the first phase being completed during 1979, and the second phase proceeding during the 1980-81 time frame.

-

#### II.C Relative Merits of the Enhancements

The three approaches differ primarily with respect to initial cost, final memory , size, system impact, effect on program development, and demand on the Institute's resources for hardware development. The technological risk involved in the three approaches are acceptable: there is essentially no risk involved in the RAM or PEM approaches. The CCD approach has the greatest amount of technological risk associated with it, since the technology chosen for the extended memory has not yet been used in large scale memories. With respect to implementation risk, the RAM approach is significantly greater than the other two since it involves a much more complex coupling with the control unit. The amount of in-house development required for these three approaches All approaches use the same system for the varies considerably. although buffer/file memory, and theinterface, complex. is Ignoring this common task, the CCD approach requires no straight-forward. in-house development aside from specification, the PEM approach requires a modest involvement, and the RAM approach requires a considerable amount of in-house development.

The three approaches have different impacts on the current system software and on user's program development efforts. Again, the impact of the buffer/file memory on the current support system is roughly constant for the three approaches, and will be ignored in this discussion. The PEM approach requires negligible changes to the current system software. For the CCD approach, the rapid response time of the disk replacement will necessitate the current control mechanism being replaced by an I/O executive dedicated exclusively to managing transfers between local and extended memory. This will require the development of the appropriate The RAM approach also requires considerable system system software. software changes, since it involves adding an instruction to the current Illiac repetoire: changes must be made in the assembler and probably in the As far as the impact of these three programming languages as well. approaches on user code development is concerned, the PEM approach will be of most help to users whose problems fit in the four million word memory; for larger problems, about the same level of effort will be required as is now being expended. However, the capability to have much larger buffer areas may mitigate the amount of time which must now be spent during program design in order for a program to be reasonably efficient under the The CCD approach, by significantly improving the current configuration. performance characteristics of the extended memory, will greatly reduce the effort required to use the machine efficiently. The RAM approach should virtually eliminate the problems users experience with the current extended memory, except for those few larger problems which will not fit in the extended memory and must use the buffer/file memory for part of their active data bases.

As a final point of comparison, the relative performances of the three memory systems varies depending upon the size of the active data base being processed. The target Illiac applications for the fully enhanced Illiac system can be grouped into four categories according to the size of their data base: those problems with less than one half million words, those problems with one half to sixteen million words, those problems with sixteen to sixty-six million words and those problems with greater than sixty-six million words. Problems in the first category are best served by either the RAM or CCD approach with a 5 to 50% degradation expected going to the PEM approach. This is due to the fast local memory provided with these two approaches. Since the fast local memory in the CCD approach is one half verses the one eighth million words of the PEM approachs about 10 to 50% better performance would be expected of the CCD approach in this range. Problem data bases in the second category, those in the one half to sixteen million word range, would best be served by a RAM memory system. A 5 to 10% degradation is expected going to CCD since this is the amount of time most programs will lose moving data between the local and extended memories. A degradation of up to 50% should be expected with the PEM approach for problems under four million words; above four million words the degradation would be 100% since part of the data base must then be stored on disk. Problem data bases in the third category, in the sixteen to sixty-six million words range, would perform 100% better with the CCD approach over RAM and PEM since data bases in the latter cases would be stored on disk. For the last category, over sixty-six million words, the picture reverses with both the RAM and PEM approaches performing 25 to 30% better than the CCD approach. This is due to the fact that in the CCD memory system the extended memory has only two high performance disk controllers instead of the four used in both the PEM and RAM approaches.

In summary, all three approaches increase the reliability and availability of the Illiac system while significantly reducing a major cause of the inefficient use of the Illiac and also reducing the high cost of program With respect to cost and technological risk, the three development. approaches are comparable although their differences are perceptible. With respect to the amount of system software changes, the CCD and RAM approaches require significantly more work than the PEM approach. There are four major differences in the three approaches. First, in respect to in-house development and required modifications to the Illiac (and the resultant unavailability of the Illiac), the RAM approach is significantly more demanding on the Institutes resources than the other two. Second, the RAM approach is significantly more expensive for a minimal configuration (the first phase) and the CCD approach considerably more expensive for the Third, with respect to the size of the data base which complete system. can be processed without having to resort to the complexities of using a disk base memory efficiently, the PEM approach is the most restrictive, the RAM next most restrictive, while CCD is least restrictive. Finally, with respect to the complexity of program design, PEM and RAM approaches are roughly comparable, with the CCD approach being significantly greater, and the PEM approach significantly greater still for large programs using its buffer/file memory to hold active data sets. All three approaches are feasible and significantly improve the memory system characteristics; the selection of one approach over the others should depend upon the relative importance of these last four differences.

#### III. Current System Status and Use

This chapter presents the technical background used in evaluating the various memory enhancements to be discussed in the next chapter. It is the product of a multi-disciplinary approach by the Institute to examine the current memory system and the way the memory is currently being used. The critical factors involved in system performance are identified, and an attempt is made to anticipate the potential bottlenecks of future use of the system. The organization of this chapter and the major results are summarized as follows.

The first section gives an overview of the system organization, both the hardware and the software. The current status of the hardware is briefly discussed: the basic reliability of the processor and local memory continues to improve, but incipient failure modes of the local memory indicate that replacement of the printed circuit cards is likely to be required within a few years. The extended memory, being a disk, is showing the inevitable effects of wear on physical devices, and an estimated lifetime of more than two years would be optimistic. The design of the system software for managing data movement in the system is such that alterations to the various physical components of the memory system are expected to have only localized impact on the remainder of the system software. Currently, data movement into the system and within the system is rather limited. Faster input devices are available; however, data movement within the system will probably be a major bottleneck unless steps are taken to replace the hardware and re-organize the components. The section concludes with a discussion of the scheduled enhancements to the Illiac processor to increase its computing power: an increase in processing speed of up to a factor of two is expected during the next year.

The second section surveys some of the major codes which have been developed for the Illiac, plus some possible future developments of these and other codes. From the point of their memory usage characteristics, these codes could process their data-base at rates of 10 to 100 million bits per second, with 60 million bits per second being typical. However, the latency of the disk, and the transfer rate between disk and local memory, cut this rate by a factor of two or more. Data bases for current Illiac problems range from half a million to ten million 64-bit words; this is often due to the size of available memory (for the data base and storage of output data). Removing this limitation would, of course, increase the demands on the file transfer capability of the system.

The third section presents a model of the Illiac memory system. Using this model and the surveyed codes, guidelines can be developed for the characteristics of acceptable memory replacements. The bandwidth between local and extended memory should be at least 200 million bits per second,

and preferably between 600 and 1000 million bits per second. And it should be possible to load the extended memory from the support system at a rate greater than 6 million bits per second; this requirement indicates that a high bandwidth, on-line file storage facility directly connected to the extended memory is desirable.

The fourth section discusses four miscellaneous issues which affect the evaluation of memory system enhancements. The first concerns the sizing of the array memory. The local memory should be large enough to reduce the complexity of user codes (and the attendant high development costs) which results from a local memory too small for the natural formulation of user problems. The best estimate of a lower bound for local memory size is half a million words. The extended memory should have a capacity of at least one billion bits, although applications exist which are well suited to the Illiac architecture except that they require four billion bits of storage for their data bases. Second, semiconductor memories of more than half a million words have been shown by field experience to require the capability of detecting and correcting random errors, and this capability may be needed in an enhanced memory system for the Illiac unless significantly more reliable memory chips are used. Third, the concept of a virtual memory for the Illiac is discussed, together with a possible implementation A virtual memory is the popular and an estimate of its performance. solution to reducing the cost of program development since it relieves much of the burden from the programmer to explicitly move data around in a hierarchic memory system, such as the Illiac's; however, this has usually accompanied by considerable degradation of processor execution been capability. And fourth, in order to alleviate the problems of manual handling of large files in the current system, a reliable, on-line file storage facility is needed. Estimates of the capacity of such a storage facility indicates that at least eighteen billion bits are required.

The last section reviews the major weaknesses of the present system and indicates the various guidelines developed in the preceeding four sections for improving the system performance. This final section, then, presents a summary of the major conclusions of this chapter.

#### III.A. Present System Configuration

The Illiac IV memory system includes all memory in the IAC system used by Illiac jobs. As such, it consists of both the array memory itself and the support system memory. This section presents a description of the hardware and system software involved in the memory system. It begins with an overview of the system and its current status, then proceeds with a more detailed discussion of the array memory and the support system. It concludes with a description of the Illiac processor and the possibilities of increasing its execution speed since a faster processor will place greater demands on the memory system.

#### III.A.1. System Overview

The Illiac memory system can best be understood by consulting Figure III.1. This diagram shows the components used for data storage, and specifically does not show data transfer media. It depicts the Illiac memory system as it appears to the users. The current memory capacities and the maximum data rates which the hardware provides are indicated in the figure; sustained ransfer rates are somewhat less and depend upon system load. For a user, the ultimate consideration is that the Illiac system throughput is currently limited by an input/output rate of about one megabit (million bits) per second if the data go ultimately to tape; for strictly network users the rate is even less. This could be increased to five megabits per second by using higher performance disks and tapes now commercially available. On-line file storage in the IAC system is currently Tenex disks (called SPOOL in the figure); there is no on-line mass storage device in the Illiac memory system. There is some question whether, in the absence of such a device, increases in memory size and processor speed will significantly increase the effectiveness of IAC's support of the research community.

When a data set is to be processed by the Illiac, it is moved onto the Illiac's memory, either from the Tenex disks or directly from tape. Large data sets are placed on the extended memory (Illiac IV Disk Memory -- I4DM); the program and small data sets are placed in the processor's local memory (Processing Element Memory -- PEM). Data on the extended memory must be brought into local memory for processing; this movement is under the explicit control of the executing program. The Illiac is currently operated in a dedicated fashion: the array memory resources (PEM and I4DM) are assigned to one user at a time; there is no multi-programming use of the Illiac.

Note: Transfer Rates Listed are Maximum Rates

Current Illiac Memory System Characteristics

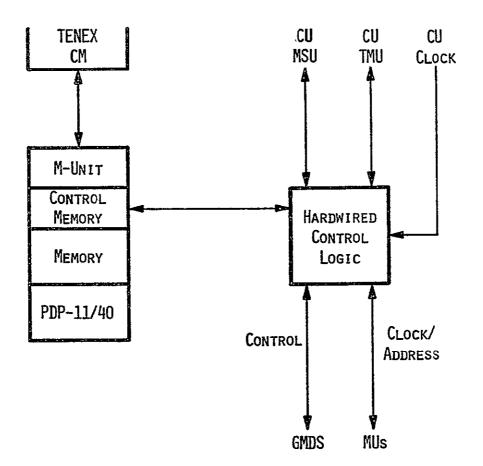

The philosophy behind the implementation of IAC's data movement system is the central memory concept (see Figure III.2). The central memory is used to buffer data between storage devices. Each device has an associated device control process, which can cause the device to perform input or output to or from pages in the central memory. Thus, a device to device transfer is decomposed into two phases: a source device to central memory transfer, followed by a central memory to destination device transfer. In this way, each device control process requires only the ability to manipulate the device and interface to the central memory. This provides a general mechanism for establishing a data transfer path between any two storage devices in the system with a fraction of the complexity required in a conventional architecture. Also, the installation or removal of a device is greatly simplified by the central memory concept.

Transfer of data occurs through buffer pages in the central memory; these pages are shared by the source and destination devices. The source device control process causes the buffers to be filled and then it signals the destination device that the transfer has been completed. When signaled, the destination device control process causes the buffer contents to be emptied into its storage device and it then signals that this phase of the transfer has completed.

The user process which requires data movement must set up the two device control processs before the transfer can begin. This involves sending appropriate device addressing information to each device control process, acquiring buffer pages to be shared by the two devices, and specifying the communication path between the two control processes. After this initialization, the transfer is started for both device control processes and continues until all pages have been transferred.

#### III.A.1.a. Current Configuration

The preceding paragraphs describe the concept underlying the IAC data movement system; however, the actual configuration has not evolved to this idealized state. This is primarily due to the fact that a suitable central memory is not yet operational, and a generalized buffer management system has not been developed.

The current implementation of the central memory (see Figure III.3) consists of a number of smaller memory units. For each memory module, only a subset of the system devices can access it. This means that many transfer paths are not available, and some paths require an intermediate transfer to move data from a buffer in one memory to a buffer in another memory. The device for transforming a processor's logical address in the central memory into a physical location in one of the memory modules is called a Q1011.

\* Current System Implementation

The general method of communication between device control processes discussed above is not implemented in the current system. Most device control processors communicate with only one other device control process, using a specialized communication protocol. The basic techniques are common to all of the methods used for interprocess communication. Because most devices are involved in only one transfer path, the buffer page assignments are fixed instead of dynamically allocated as indicated in the above discussion.

The current central memory interface to the Illiac subsystem consists of three 16K word memory units (where K stands for 1024): the Buffer Input/Output Memory (BIOM), the Tenex Buffer Memory (TNXCM), and the Illiac Central Memory (I4CM). No storage device has a direct access path to all of these memory units. TNXCM contains the Tenex buffers for data passage between the Tenex file system and the Illiac subsystem. The BIOM, considered as part of the Illiac subsystem, contains another set of buffers for data passage between Tenex, the Illiac and the Illiac Tape facility (I4TAPE). Control of these data movement processes is communicated through the I4CM unit. The Tenex system controls data movement between the TNXCM and the Tenex disk; the Memory Server Process (MS) controls transfers between TNXCM and the BIOM. Figure III.3 shows the interconnection of these devices in the current system implementation.

Within the Illiac subsystem, data movement is controlled by the Memory Management Process (MMP). It can exert control over the Illiac Disk File Controller (DFC) via the Remote Module and the Descriptor Controller (DC) in order to transfer data between the Illiac Disk Memory (I4DM) and the Processing Element Memory (PEM). The I4DM-PEM transfer proceeds through the DFC and the Input/Output Switch (IOS). The MMP also has the capability of delegating control to the Tape System Process (TSP) to transfer data between the I4DM and I4TAPE; data in this transfer moves through the DFC and the BIOM. The MMP has the further capability of moving data between either the I4DM or the PEM and the central system by using the BIOM. This is accomplished by passing control to the MS processor to handle the BIOM to Tenex transfers; it retains control over the DFC through the Remote Module and the DC. Note that the DFC, in addition to providing control over the I4DM, acts to establish a data path between any pair of the I4DM, PEM or BIOM units. In particular the I4DM to PEM path provides the very high transfer rate necessary for efficient Illiac utilization.

A transfer between Tenex Disk and either the I4DM or the PEM must be made through the intermediate TNXCM memory because Tenex disk cannot directly access the BIOM. The MS processor is used to bridge this gap in central memory because it can access both TNXCM and the BIOM.

There are three control processes which direct the movement of data within the Illiac System. The Memory Management Process (MMP) controls transfers between the BIOM, PEM and I4DM. The MMP Server process (MS) controls transfers of data between Tenex disk and TNXCM. MS also performs the actual movement of data between TNXCM and the BIOM. The Tape System Process (TSP) controls transfers between the Illiac Tape System (I4TAPE) and the BIOM. Each of the three device control processes, MMP, TSP, and MS, runs in a separate dedicated minicomputer. III.A.1.b. Interprocess Communication

In the general central memory concept, a user process sets up a source control process and a destination control process, and establishes the communication between them. In the current configuration, the communication paths are predefined. The task of initializing the two device control processes is usually handled by one of the control processes. A Tenex user process communicates with the dominant device control process, which in turn initializes itself and the other device control process. In the case of the Illiac system, the MMP is always the dominant device control process.

The basic communication mechanism used in the current configuration is a pair of memory locations called slots. The slots are in the I4CM and each slot provides a full duplex communication path; requests are placed in one of the locations, and results are returned in the other. Slots are used for comunication between Tenex user processes and the MMP, between MMP and MS, and between MMP and TSP. A special slot mechanism for communication between an Illiac process and the MMP is implemented with Illiac hardware registers, rather than central memory locations.

The transfer between I4TAPE and I4DM is initiated by a user process in Tenex. This process communicates the specification to the MMP, which initializes both TSP and itself for a transfer using the BIOM as the central memory buffer.

Data transfer between Tenex Disk and the I4DM is a bit more complicated. The Tenex Disk can transfer data only to TNXCM; an intermediate process, MS, is used to move the data between TNXCM and BIOM. The Tenex user process communicates with the MMP, which initializes the MS process and itself for a transfer using the BIOM as the central memory buffer. A transfer between Tenex Disk and PEM is similar, the only difference being that the MMP directs data to the PEM instead of to the I4DM.

The transfer between PEM and I4DM is initiated by a process running on the Illiac. For efficiency, the transfer is made directly between the devices without using a buffer. The MMP is the device control process for both the PEM and the I4DM; its role in the transfer is mainly to initiate the transfer. After converting the logical area name to a physical location on the I4DM, the MMP constructs a file descriptor for the Descriptor Controller (DC). The DC is the part of the array's I/O Sub-System (IOSS) which actually controls data movement between I4DM, PEM and BIOM.

Except for the PEM-I4DM transfer, all data movement must be initiated by a Tenex process. This implementation maintains Tenex as the central resource allocation facility. To allow an Illiac process to initiate data movement, a companion process to the Illiac (CMOVE) is available during an Illiac run. The Illiac process communicates with CMOVE through a message system managed by the MMP. The CMOVE process uses the data movement control described previously for Tenex initiated transfers.

III.A.1.c. Current Hardware Status

The current state of the hardware components will have an effect on the planing of enhancements. These can be briefly summarized as follows.

Local Memory (PEM)

An increasing number of problems are being isolated to micro-cracks in the printed circuit boards and this may require their replacement en masse at some future date. The chip failures are at a tolerable rate; however, they are no longer manufactured.

Processing Elements (PEs) and the Control Unit (CU)

Although the processing elements are the most failure prone devices, simply because of numbers, their reliability record has been constantly improving. From July 5 to 31, 1977, for example, only 17 of the 214,256 chips in the PEs failed. The chips used in the PEs are no longer manufactured, but in general the spare level is high. It may be necessary to go into prototype chip production for the few chips whose supplies are low. The record of reliability for the Control Unit has also been constantly improving; during the same period in July, for example, only 5 of the 17,136 chips in the CU failed.

Disk Memory (I4DM)

The extended memory of the Illiac is currently implemented using disk technology. It is the least controllable resource in the system. The disks are old but are being refurbished. This component has an estimated remaining life of from two to three years but has the disadvantage that it is not expandable at reasonable cost. It is also probable that as this mechanical system ages, its reliability will decrease and its maintenance costs will increase. The available capacity of the disks has been declining during the recent years. Of the originally implemented 16 million word memory, only 8 million words were ever on-line, and the last year has seen the capacity continue to decline. By the first of this year, the capacity seemed to have stabilized at around 5 million 64-bit words being routinely available, although this is slowly increasing.

About two years ago the disks were synchronized and the electronics were modified and adjusted. Since that time the number of disks available to users increased to a high of seven disks; this process took about a year. In the last year the disks which had accumulated 50 to 60 thousand operational hours began to require bearing replacement. The number of available disks deteriorated to two or three before the required maintenance tools could be designed and fabricated. Two of the four disks currently operational are reconditioned ones. Four more disk units will be re-installed during the first half of 1978.

#### Central System

The PDP-11's that are used for control processors have a very good As the system throughput improves, however, it reliability record. may turn out that their speed must be augmented by special hardware or However, the bulk of the processors will adequately newer devices. perform their functions. The PDP-10 also has a good record. The only As demands on the IAC system consideration for it is throughput. increase, enhancements may be required. The current PDP-10's at IAC are KI models, which are about two and a half times as slow as the fastest PDP-10 (the KL model). But since the IAC system uses a software paging device and relatively slow memories, the difference in available computing power may be closer to a factor of five. Using a faster memory, for example, would increase the available processing power by approximately fifty percent.

The Tenex file storage devices, both tapes and disk, have the worst record of reliability of the central system components, requiring two to four hours a week for preventive maintenance and emergency repair. Overall, their record is good, however. They were adequate for the environment of the Institute a year ago: in-house development and friendly Illiac users. But as the Institute moves toward general availability of Illiac service, an improvement is appropriate, with the present hardware remaining for the in-house development system.

Overall, the hardware in the Illiac system is in fair to good condition. However, the effects of age on the mechanical devices such as disks (especially I4DM) are beginning to impact the availability and usefulness of the system to an appreciable extent. Also, as the speed of the Illiac itself improves, the demands on the system (especially the peak demands associated with moving Illiac data files around: the demands most visible to the user community) will increasingly reveal the already noticeable weaknesses of the system. The remainder of this section will treat the individual components of the memory system in greater detail, discussing the limitations they place on possible enhancements.

#### III.A.2. Illiac Array Memory System

There are three major components to the memory system of the array itself (called the IOSS -- the I/O Sub-System). These are the PE memory (PEM), the extended memory (I4DM), and a buffering memory to the support system

Illiac Memory System III.A. Present System Configuration

(BIOM). Controlling the transfer of data among these memories is the Descriptor Controller (DC) and the Memory Management Processor (MMP). These devices are described in more detail in this section, their performance characteristics are given, and the limitations their current implementations place on future enhancements are indicated.

Data can be transferred between any two of the three memories at a rate of 500 megabits per second. These transfers are initiated by the MMP, a PDP-11 model 40. There are request ports to the MMP for these transfers. Both an Illiac program and processes running on the PDP-10 or other PDP-11s can request these transfers.

Processor Local Memory (PEM)

The Illiac's local memory is 2K rows of 4096 bits. The present cycle time and access time are ten clock cycles; the present clock rate is 12.5 megahertz. It is likely that the cycle time will be reduced to two clocks while the access will be reduced to four clocks. This implies that only operations which can be explicitly overlapped will be able to use the two clock cycle, other operations will be limited by the four clock access. The clock rate will also be increased to 16 megahertz. The PEM proper can be increased in capacity while retaining these enhancements; various possibilities are considered in Chapter IV.

The PEM has a number of requesting ports. A request on any port will use 4096 bits of PEM bandwidth regardless of the number of bits used per reference. For example, the I4DM is specified as being a 500 megabit per second path -- that is, it requests 1024 bits every 2 microseconds. Actually, each 1024 bit reference accesses 4096 bits of PEM. Each requesting port to the PEM is similar, only the bandwidth utilization varies.

The present PEM has 32 thousand chips of 256 bits each. A new PEM design could use up to the same number of chips and still have enough extra room for error correction. Using 32 thousand chips (plus 4 thousand for error correction) the memory could be 4096 bits by up to 32K rows. This is the limit if the current architecture is kept. The Illiac instruction format allows for 16 bits to specify an address with PE local memory, and this places a natural limit on the addressable size of PEM, namely 64K words per PE or four million words for the entire local memory. In addition, the address lines from the PE to its memory are currently 11 bits wide, although provision has been made to accommodate a 16-bit address cable. This means that a local memory larger than the current memory will require additional, although minor, modifications to the hardware. Finally, it should be noted that there is adequate power and cooling capacity to support up to 40 thousand of the memory chips that are now commercially available and meet the speed requirements.

Another PEM limitation is the bus to the I/O sub-system (IOSS) which connects the PEM to the I4DM and BIOM. It is 1024 bits out of a 4096 bit data register. The multiplexing required limits the IOSS bandwidth ultimately to 1024 bits every Illiac clock. The best possible transfer rate is therefore 16 gigabits (billion bits) per second with a 16 megahertz clock. However, this limitation could be circumvented if the bus were jettisoned entirely, for example if each PE had its own slice of extended memory directly associated with it.

#### Extended Memory (I4DM)

By the early part of 1978 there were four disks in operation in the I4DM, for a maximum available memory of five million words. With the refurbishing program under way, this may increase by as much as a factor of two for the remainder of the year.

The disks require 40 milliseconds per revolution, so that on the average 20 milliseconds is required between the time that a random I/O request is made and the requested data is available. This latency factor can be significant in determining the total run time for some user programs; section III.B treats this issue in more detail. In general, disk latency is a major issue for most of the users of the Illiac, and it is often cited as a major hinderance in developing codes for the machine.

The Illiac disk is addressable to a quarter of an Illiac page (a page is 64K bits). Each band of Illiac disk has 300 Illiac pages. It is a limitation of the disk hardware that between any two transfer requests at least 3/4 of an Illiac page must be skipped. However each request may be for a large but contiguous portion of a disk. The current I4DM places no restrictions on a possible replacement, other than that the communication protocol with the DC remain the same. By moving the MMP/DC functions into the CU/extended memory enhancement, even this limitation is removed. This report assumes that there is no significant restriction on replacing I4DM.

#### **BIOM Operation**

The BIOM is a true multiport memory. It has a capacity of eight Illiac pages, or 512K bits. A fast port, capable of the IOSS 500 megabit transfer rate, accesses the memory over a 128-bit path. The other four ports access the memory as 16K words of 32 bits each. An access on these slower ports takes 5 clocks of 200 nanoseconds each. The BIOM has three devices connected on these slow ports: the B6700, the Descriptor Controller (IOSS), and an interface from a PDP-10 Memory (commonly called the ME-10). The connection to the B6700 is used for data transfer between the PDP-10 and the B6700; very soon an alternate path between these two devices will be provided, so the interference this causes to current array performance need not be considered in evaluating enhancements.

The Descriptor Controller, which controls all IOSS data paths, stores its 'result descriptors' in the BIOM via its memory port. The current software permanently allocates one Illiac page of the BIOM for the storage of these descriptors. An additional page is reserved for transfers to the B6700. Therefore only six Illiac pages are available for buffering the transfer of data between I4DM and the central system. The control path of the Descriptor Controller is the only control path which causes enough conflict to merit mentioning in detail in this report. The dedication of one quarter of the BIOM to the descriptors described above is a significant factor in determining the maximum throughput rate through the BIOM and limits the system to 14DM transfer rate to ten megabits per second. The current system has a peak transfer rate of two megabits per second, so the BIOM is quite adequate for the present configuration. However, the BIOM must be replaced for transfer rates over ten megabits per second to be possible.

The ME-10 is a modified PDP-10 memory module which allows standard PDP-10 requesting devices to access the BIOM. The BIOM appears to be the upper 16K words of a 32K word ME-10. The word size of the BIOM is 32-bits rather than the 36-bits of the PDP-10; thus for the BIOM half of the module, only the most significant 32 bits of data respond; the least significant bits must be all zero for parity considerations. The PDP-10 processor, as well as other processors described below, can access the BIOM through this modified ME-10.

#### MMP Operation

The MMP provides the operating system of the Illiac (it replaces the B6700 in the original design of the Illiac IV). As such it does no explicit data transfers. It can request IOSS transfers, access the communications sections of memory, operate the Illiac console, and respond to Illiac interrupts from user code (most often these interrupts are also IOSS transfer requests). The MMP is request driven; in the communication area of memory (I4CM) there is a set of request ports (called slots) with which a Tenex or PDP-11 process can make a request for action by the MMP. These ports have a response portion for the MMP to signal that the request has been completed; these response ports must be accessed by the requestor to determine the state of the operation. The Illiac program can also request MMP operations and obtain results through a separate interface. The performance of these interfaces in the present configuration is not a major bottleneck. Performance measurements of the I4DM-MMP operation indicate that overhead due to the MMP accounts for two to four milliseconds, which is usually only ten to twenty percent of the data movement time.

The major limitation of the MMP is that it is a PDP-11 and can only poll memory and respond to interrupts at minicomputer speeds. Presumably at some point the overhead here may become significant, especially if advances are made in other areas. The alternatives are to put the MMP functions into the Illiac control unit itself, or to use a fast microprocessor.

In order to make the interface between an Illiac program and the I4DM understandable and to increase the availability of the disk, a mechanism was invented to allow the Illiac user to access the Illiac disk using file-like area names. The conversion between these names and the physical disk is made by the MMP based on a file kept current This file is initialized by the ALLOC subsystem, which is on Tenex. The file, in charge of assigning the physical areas on the disk. called the I4D-file, can be larger than can be contained in the local storage of the MMP; this arises when complex maps of the disk are employed. The current MMP memory will hold a description of 13K pages of I4DM, which is about three times the number of I4DM pages currently available. Thus each page can appear in three different logical areas. For a larger disk area, such complex maps will no longer fit within the MMP local memory, and this local memory is almost as large as the PDP-11 can accomodate.

The high bandwidth among the memories in the IOSS is a major feature of the Illiac system: it permits the efficient manipulation of the very large data bases which occur in large scale scientific computing. However, the latency of the I4DM tends to make it difficult for many Illiac programs to realize this efficiency. The path to the outside world, the BIOM, is currently limited less by the size of its buffer memory than by the rate at which the support system can transfer data.

#### III.A.3. Support System

The Illiac support system consists of a PDP-10 processor with a Tenex operating system, together with several PDP-11 satellite processors to handle file transfers. The interface to the ARPA network is the standard IMP and will not be discussed in this report.

#### MS

The MMP Server (MS) is a process which runs on a PDP-11 model 10. It will transfer data between a Tenex System Memory and the BIOM. It manages the buffers in both memories, making disk requests to both responsible processors (PDP-10 and MMP). MS also provides enough added efficiency that the transfer rate between the two disks is now at about one megabit per second, which is an increase of an order of magnitude over the previous implementation in which Tenex controlled the transfer. The key to the improvement is an optimized transfer capability installed at the interrupt level of the PDP-10 disk routine. The details and timing of this interface are still under development, but MS is ultimately limited by its memory copy mechanism. The hardware used to move a block of data from one memory to another was not designed for this purpose originally and for this reason MS has a bandwidth limit of about 1.9 megabits per second.

#### **I4TAPE**

The I4TAPE process is very much like MS; it buffers transfers between the tape units dedicated to the Illiac and the BIOM. However, since there is no contention for the tape units as there is for the Tenex disks in MS, the data rate is limited only by buffering and the synchronization with the Illiac disk rotation. Realistic rates of 1.33 megabits have been achieved. The tape hardware transfers at 1.92 megabits per second, but gaps, start/stops, and disk latency reduce the efficiency. The overhead of the Illiac program making the request has not been measured, but it is estimated at about 10 seconds to The tape service is limited by the initiate the process. implementation that requires a Tenex process to handle each transfer This implementation was chosen so that the interface to the request. Illiac user would be simple and flexible.

#### PDP-10

The Tenex memory system is ultimately limited to 256K words by the addressability of the peripherals. The age of the drum and disk systems are the cause of this limitation; newer devices have a greater addressing range. The Tenex memory was recently increased by more than 100K words from the original 128K words. This more than doubled the amount available for users and decreased the idle time from the 30 to 50% level to the 0 to 5% level (measured during peak times with load averages in excess of 10.0).

There are three sub-systems which run in the Tenex environment and control data movement within the Illiac memory system: MOVE, RUN and ALLOC/DALLOC. MOVE controls data movement between the I4DM and either a Tenex file or I4TAPE. While the data movement is initiated by MOVE, direct control is maintained by the appropriate PDP-11 process: MMP, TSP, or MS. RUN controls the loading of the Illiac. Overall control is maintained by RUN, but direct control of program movement and status communication is maintained by the MMP. In addition, post-run dump is controlled by RUN, as is elapsed execution time monitoring. CMOVE, a sub-process of RUN, is maintained as a communications terminal for an Illiac program to control data movement involving the Tenex system. ALLOC/DALLOC controls the allocation and de-allocation of specific I4DM bands to area designators so that Illiac or Tenex processes can access these areas on a "by name" basis, rather than by physical location. Modifications to the Illiac memory system would directly affect only ALLOC/DALLOC, provided the MMP, TSP, and MS interface protocols remain fixed. The various proposed memory enhancements in this report will have little impact on these Tenex sub-systems, with the possible exceptions of the introduction of an on-line file storage device and a large staging memory adjunct to the extended memory system. Either of these will require additional system control modules. However, the impact of memory enhancements on existing Tenex software is not of significant scale to warrant consideration in evaluating the proposed modifications.

The present disk and tape hardware could be replaced by hardware which has peak data rates of ten megabits per second. Having these devices, would afford the capability of approaching the peak data rates of which the system is capable. Thus it is possible that I/O into the system could improve by almost a factor of ten in a dedicated mode. However, in a shared memory multiprocessing system such as Tenex and the central memory concept, the average data rate will be lower than ten megabits per second, and a system improvement by a factor of about five is anticipated.

#### Summary

The file transfer rate within the support system is currently slightly over one megabit per second, thus movement of large Illiac files takes about one minute per million words (64-bit words), and this is well within a factor of two of the limitations of the current hardware and system design. One megabit per second is also the I/O rate between the support system and the outside world. Faster tape and disk units could improve the peak I/O rate by almost a factor of ten. To increase the transfer rate within the system itself requires faster processors (within the current implementation) or additions of special purpose hardware for the explicit purpose of supporting high block transfer rates for moving very large files.

#### III.A.4. Illiac Speed Enhancements

The processing speed of the Illiac determines the demands that will be placed on the memory system. In considering enhancements to the memory, it is therefore necessary to take into considerations the improvements that may be made in the execution rate of the Illiac. The following discusses the improvements that are being considered; the conclusion is that an increase in the observed speed of the processor could be as much as a factor of two, or better. III.A.4.a. Description

The Illiac processor itself consists of a central Control Unit (CU) which fetches and decodes instructions and generates enable signals to control the execution of sixty-four processing elements (PEs). The CU is divided into two major units: ADVAST (advanced station) and FINST (final station). The role of ADVAST is to process instructions which deal with program control and to prepare instructions to be executed by the PEs. The role of FINST is to take the instructions intended for parallel execution by the array and to convert them into sequences of enable signals which actually control the PEs.

The CU was originaly designed to run at 25 megahertz (40 nanosecond cycle), but early in the design the speed was reduced to 20 megahertz. The PEM was designed to run at a 10 megahertz rate and be pipelined with respect to responding to memory requests. It can probably be run at 8 megahertz now.

The PEM rate is additionally limited by the fact that the operand select gating in the PE is used both for sending the address to the PEM from the PE and for receiving the data from the PEM. This constrains the fetch rate to once per two cycles (which fits well with the megahertz PEM rate). The current PEM access time is about 200 nanoseconds; with the various delays that are added in the PE by sending the address and receiving the data into the same register, the PEM access time is probably limited to four cycles at 16 megahertz.

The floating-point add and multiply instructions seem to be the most frequently occurring PE instructions, and indeed the PEs were designed mainly to be floating point add and multiply functional units. Consequently, PE arithmetic has little potential for increased speed-up. The original design called for a seven cycle add and a nine cycle multiply for 64-bit floating-point arithmetic. At this time the add also takes nine cycles because of some long signal paths in the PE. The two extra cycles were added to allow more time where the long paths are used. There is a possibility that at least one of the cycles in the seven cycle add can be eliminated and this would reduce the number of cycles to six, thus limiting the arithmetic bandwidth for this particular instruction to 170 million floating-point results per second (at 16 megahertz). This is an upper bound since it includes no time for fetching operands and saving results.

III.A.4.b. Speed-up of Simple Loops

It is instructive at this point to consider some simple code examples; these can indicate what processor speed-up is possible. Consider the following loop of code:

Illiac Memory System III.A. Present System Configuration

| LOOP: | LDA X(ACO)     | ; load accumulator from X(indexed by ACO) |

|-------|----------------|-------------------------------------------|

|       |                | ; store accumulator                       |

|       | TXLTM ACO,LOOP | ; increment address pointer and branch    |

The machine currently takes sixteen cycles to execute this loop (per time through the loop) which consists of nine or ten cycles for the load and four or five for the store, with a dead cycle (which is included in all FINST instructions) between each. This amounts to a transfer rate of 4096 bits (one row) per 1.28 microseconds, or 3.2 gigabits per second.

Were the memory fetch to be overlapped in FINST so that a new memory cycle could be prepared before the old one finished, the same loop could take as few as six cycles, which is a speed-up of a factor of 2.5 times. In this case an example of how to take advantage of such overlap of memory requests is as follows:

| LOOP: | LDA   | X(ACO)   |   |      |            |

|-------|-------|----------|---|------|------------|

|       | LDB   | X+1(ACO) | ; | load | B register |

|       | STA   | Y(ACO)   |   |      |            |

|       | STB   | Y+1(ACO) |   |      |            |

|       | TXLTM | ACO,LOOP |   |      |            |

The effective rate is increased because the PE can fetch the next word while the first word is arriving. The new rate is two rows per eight cycles or a speed-up of a factor of four. Such programming currently results in no program speed-up because the data must be in the receiving register before FINST will begin execution of another instruction. The new transfer rate would be (using 16 megahertz clock rate) almost 16.4 gigabits per second or a factor of 5.12 increase. Incidentally, ADVAST now takes 15 cycles in the former loop (2 for each indexed PE instruction and 11 for the TXLTM) and 19 cycles in the second loop, so quite a few enhancements to ADVAST would have to be installed in order for FINST to be used effectively in these cases. For example, a one cycle indexed PE instruction and a four cycle TXLTM would be sufficient. Both of these enhancements are feasible.

Consider another loop:

| STARTUP: | LDS   | W(ACO)   |   | pre-load S register     |

|----------|-------|----------|---|-------------------------|

| LOOP:    | LDA   | S        | ; | load accumulator from S |

|          | ADRN  | X(ACO)   | ; | add X to accumulator    |

|          | ADRN  | Y(ACO)   |   |                         |

|          | LDS   | W+1(ACO) |   |                         |

|          | STA   | Z(ACO)   |   |                         |

|          | TXLTM | ACO,LOOP |   |                         |

This is a rather trivial Z=W+X+Y and contains a pre-fetch of the next W to take advantage of full overlap of memory operations with arithmetic. There are four memory operations (three fetches and a store) which account for most of the 38 clocks that this loop currently takes -- the 18 cycles in the two additions are hidden. At 12.5 megahertz (the current frequency) this amounts to about 42 million floating-point results per second. The best possible performance for this loop is 14 cycles at 16 megahertz, or 146 million floating-point results per second, for a speed-up of a factor of 3.5.

Thus considering just the throughput gains to be made from increasing the memory access rate, and a faster clock rate, it appears that an increase in processing speed of upwards of a factor of two is possible. The rest of this discussion concentrates on enhancements to the processor itself.

#### III.A.4.c. Additional Processor Enhancements