|            | A COMPARISON OF HARDWARE DESCRIPTION LANGUAGES                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Prepared by                                                                                                                                                       |

|            | SAJJAN G. SHIVA                                                                                                                                                   |

|            | Department of Computer and Information Science's                                                                                                                  |

|            | ,<br>Final Technical Report                                                                                                                                       |

|            | October 1978                                                                                                                                                      |

|            |                                                                                                                                                                   |

|            | Grant NSG-8057                                                                                                                                                    |

|            | "Evaluation of Digital System Design Languages"                                                                                                                   |

|            | George C. Marshall Space Flight Center                                                                                                                            |

|            | National Aeronautics and Space Administration                                                                                                                     |

|            | Huntsville, Alabama                                                                                                                                               |

| <br>DESCRI | -CR-157762) A CCMPARISON OF HARDWARE N78-33788<br>IPTION LANGUAGES Final Report (Alabama<br>Univ., Huntsville.) 115 p HC A06/MF<br>CSCL 09B Unclas<br>G3/61 33781 |

|            | REPRODUCED BY<br>NATIONAL TECHNICAL<br>INFORMATION SERVICE<br>U.S DEPARTMENT OF COMMERCE<br>SPRINGFIELD, VA. 22161                                                |

|            | Alabama Agricultural and Mechanical University<br>SCHOOL OF TECHNOLOGY<br>HUNTSVILLE, ALABAMA                                                                     |

|            |                                                                                                                                                                   |

. 9

## A COMPARISON OF HARDWARE DESCRIPTION LANGUAGES

Prepared by SAJJAN G. SHIVA Department of Computer and Information Sciences Alabama A & M University Normal, AL 35762

> Final Technical Report October 1978

## Grant NSG-8057

"Evaluation of Digital System Design Languages" George C. Marshall Space Flight Center National Aeronautical and Space Administration Huntsville, Alabama

Submitted by;

a Shin. ЪМ

Sajjan G. Shiva Principal Investigator

## FOREWORD

+

This is a technical summary of the research work conducted since October 1, 1977 by the Alabama A & M University towards the fulfillment of Grant NSG-8057, from the George C. Marshall Space Flight Center, Huntsville, Alabama. The NASA Technical officer for this grant is Mr. John M. Gould, Electronics and Control Laboratory.

## A COMPARISON OF HARDWARE DESCRIPTION LANGUAGES

Sajjan G. Shiva

## ABSTRACT

Several high level languages have evolved over the past few years to describe and simulate the structure and behavior of digital systems, on digital computers. The characteristics of the four prominent languages (CDL, DDL, AHPL, ISP) are summarized. A criterion for selecting a suitable HDL for use in an automatic Integrated Circuit design environment is provided.

## TABLE OF CONTENTS

| LIST | C OF 1 | /IGURES                           | -VI |

|------|--------|-----------------------------------|-----|

| 1.   | INTRO  | DDUCTION                          | 1   |

| 2.   | COMPT  | JTER DESIGN LANGUAGE              | 5   |

|      | 2.1    | Syntax Rules                      | 6   |

|      | 2.2    | Declaration Statements            | 7   |

|      | 2.3    | Continuations                     | -13 |

|      | 2.4    | Comment Cards                     | -13 |

|      | 2.5    | Operators                         | -14 |

|      | 2.6    | Micro Statements                  | -16 |

|      | 2.7    | Switch Statements                 | -17 |

|      | 2.8    | Labeled Statements                | -17 |

|      | 2.9    | End Statement                     | -18 |

|      | 2.10   | Card Format                       | -18 |

|      | 2.11   | Translator                        | -18 |

|      |        | Simulator                         |     |

|      | 2.13   | Design Examples                   | -24 |

|      | 2.14   | Extensions                        | -37 |

| 3.   | INST   | RUCTION SET PROCESSOR             | -42 |

|      | 3.1    | Syntax Rules                      |     |

|      | 3.2    | Operators                         |     |

|      | 3.3    | Arithmetic Representations        | -44 |

|      | 3.4    | Descriptions                      | -45 |

|      | 3.5    | Behavioral Expressions            | -51 |

|      | 3.6    | Qualifiers                        |     |

|      | 3.7    | ISPS Definitions                  | -60 |

|      | 3.8    | Predeclared Entities              | -61 |

|      | 3.9    | Reserved Keywords and Identifiers | -62 |

|      | 3.10   | The Complete Minicomputer         | -63 |

|      | 3.11   | ISPS Simulator                    | -66 |

٠

,

•

. . .

| 4.  | HARD   | NARE PROGRAMMING LANGUAGE         | 69   |

|-----|--------|-----------------------------------|------|

|     | 4.1    | Syntax Rules                      | 70   |

|     | 4.2    | Declarations                      |      |

|     | 4.3    | Control Sequence                  | 71   |

|     | 4.4    | Combinational Logic Units         | 72   |

|     | 4.5    | Comments                          | 73   |

|     | 4.6    | Simulator                         | 73   |

|     | 4.7    | Design Example                    | 74   |

| 5.  | DIGI   | TAL SYSTEM DESIGN LANGUAGE        | 82   |

|     | 5.1    | Syntax Rules                      | 83   |

|     | 5.2    | Declaration Statements            | 83   |

|     | 5.3    | Operations                        | 85   |

|     | 5.4    | IF-Values Clause                  | 88   |

|     | 5.5    | Identifier                        | 89   |

|     | 5.6    | Operator Declaration              | 90   |

|     | 5.7    | State Declaration                 | 91   |

|     | 5.8    | Automaton and System Declarations | 92   |

|     | 5.9    | Advanced Features                 | 96   |

|     | 5.10   | Translator                        | 96   |

|     | 5.11   | Simulator                         | 96   |

|     | 5.12   | Design Example                    | 98   |

| 6.  | COMP   | ARISON                            | -101 |

| 7.  | CONCI  | LUSIONS                           | -104 |

| REF | ERENCI | 2S                                | -106 |

# LIST OF FIGURES

| 2-1 | Serial Twos Complementer                    | 25 |

|-----|---------------------------------------------|----|

| 2-2 | A Sequential Circuit                        | 30 |

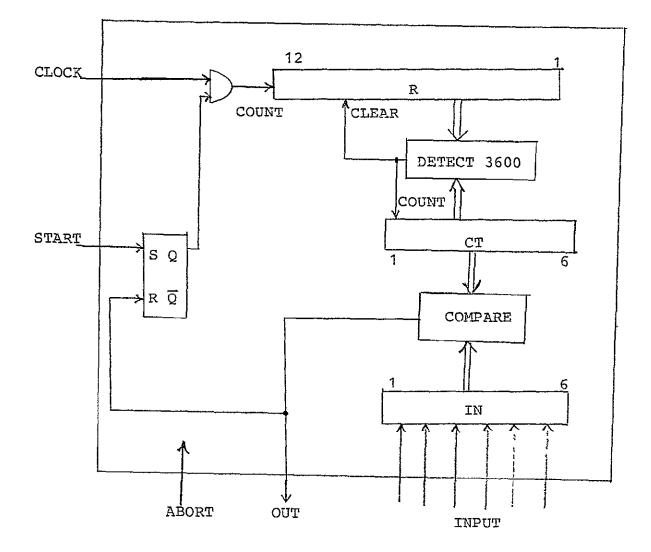

| 2-3 | Variable Timer                              | 35 |

| 2-4 | CDL Description of Variable Timer           | 36 |

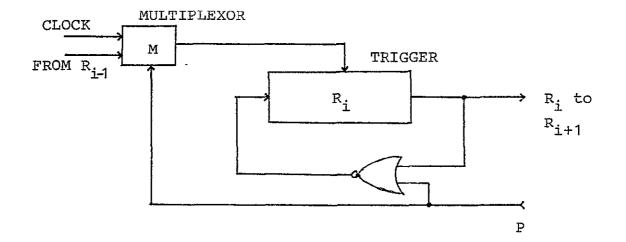

| 2-5 | A Typical Cell of the Ripple Counter        | 38 |

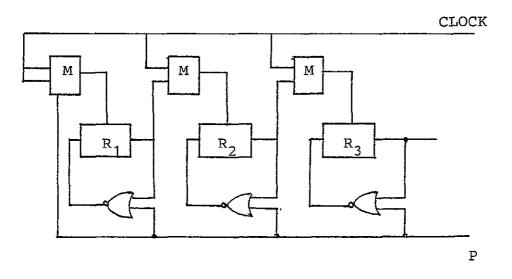

| 2-6 | A 3 Stage Ripple Counter                    | 38 |

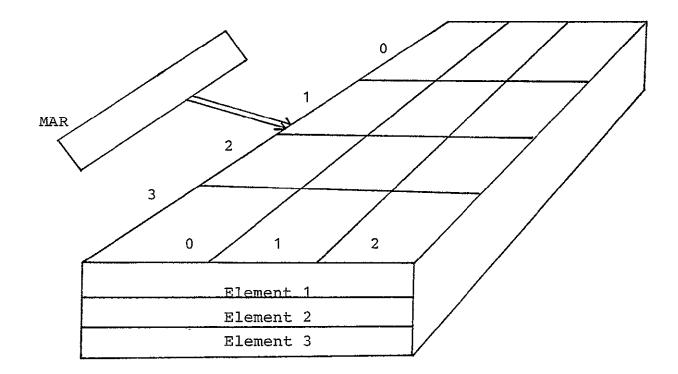

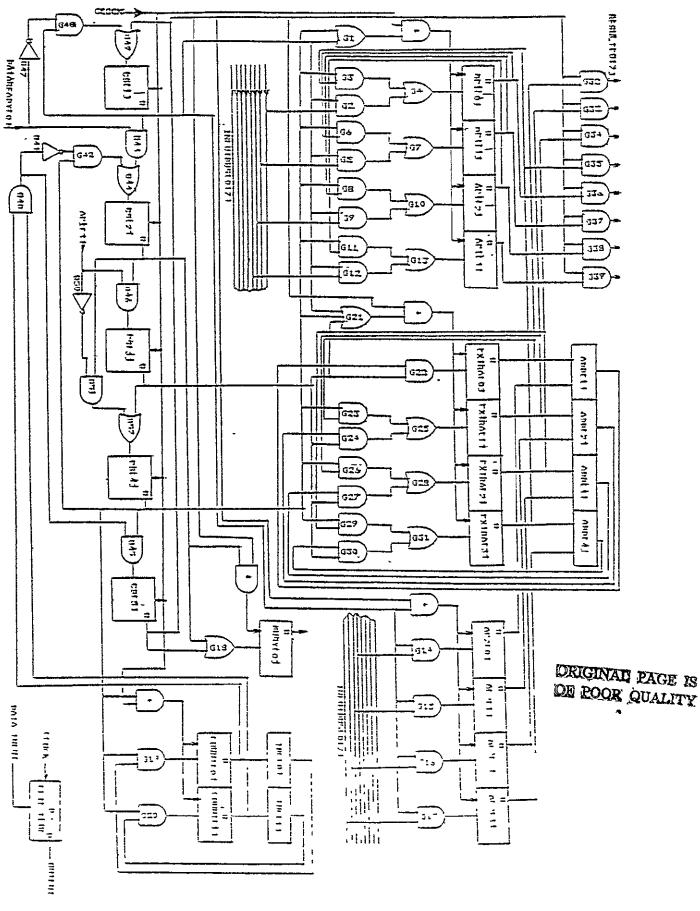

| 4-1 | Multiplier Block Diagram                    | 75 |

| 4-2 | HPSIM Program Input File for the Multiplier | 76 |

| 4-3 | HPSIM Output Listing for the Multiplier     | 76 |

| 4-4 | HPCOM Output                                | 79 |

| 4-5 | HPCOM Output                                | 80 |

| 4-6 | Multiplier                                  | 81 |

| 5-1 | DDL Operators                               | 86 |

#### 1. INTRODUCTION

Any digital system can be described in the following six levels of complexity:

- Algorithmic level which specifies only the algorithm used by the hardware for the problem solution;

- Processor, memory, switch. (PMS) level which describes the system in terms of processing units, memory components, peripherals and switching networks;

- Instructional level (programming level) where the instructions and their interpretation rules are specified;

- Register transfer level where the registers are system elements and the data transfer between these registers are specified according to some rule;

- 5) Switching circuit level where the system structure consists of an interconnection of gates and flip-flops and the behavior is given by a set of Boolean equations; and

- 6) Circuit level where the gates and flip-flops are replaced by the circuit elements such as transistors, diodes, resistors etc.

Logic diagrams, Boolean equations and programming languages have been used as the media of description. The complexity of logic diagrams and Boolean equations increases as the system complexity increases and are not suitable for describing the hardware to a computer in a design automation environment, although the recent advances in computer graphics might make the input of logic diagrams to a computer easier. The common programming languages do not have all the features required to describe the hardware. Hardware description languages (HDL) evolved as a solution. An HDL is similar to any other high level programming language and makes the hardware designer's task easier by providing a means of:

-1-

- 1) Precise yet concise description of the system;

- Convenient documentation to generate users manuals, service manuals, etc;

- Inputting the system description into a computer, for simulation and design verification at various levels of detail;

- Software generation at the preprototype level, thus bridging the hardware/software development time gap;

- Incorporating design changes and corresponding changes in documentation, efficiently;

- Designer/user (teacher/student) communication interface at the desired level of complexity.

Several HDL's have been reported [1-30]. The translators and simulators are also written for some of these HDL's. The tendency has been to invent a new HDL to suit a perticular design automation environment, basically due to the difficulty in transporting the translators and simulators on to the new computing systems and extending these to accomodate the requirements of the new design environment. Attempts to standardize HDL's are underway.

Hardware Description Languages are designed to describe both the structural and behavioral characteristics of a digital system, to a computer. The fundamental properties of hardware systems and the art of hardware design process dictate the essential features of an HDL. For an HDL to be a useful design tool it has to possess the following properties:

- It has to have a natural way of describing the parallelism, nonrecursive nature and timing issues in digital hardware.

- 2) The structure and control parts of the hardware should be easily described and preferably the description of the two parts be separated so that a user interested in the

behavior of the system need not concern himself with the structure of the system. This also provides the flexibility to use hardware, software or firmware for the control part, whichever is economical.

- The language should serve as a medium at all levels of system description.

- 4) The design changes should easily be incorporated into the description and corresponding translation should be done preferably without a complete retranslation. This feature will be useful for an interactive environment.

- 5) The language should be easy to learn and remember, to accommodate the software shy, hardware designer, although the hardware engineer can not neglect the software aspects anymore, due to the impact of microprocessors. The design system should be portable, thus necessitating the the translators and simulators of HDL be written in higher level languages.

- 6) Two approaches to systems design are often proposed: The bottom-up approach where the elementary components are combined to form more complex ones and the top-down approach where the system is decomposed into collection of subsystems until the elementary components are reached. In practice, the designer may choose a combination of the two approaches. The structural detail at any design level varies from designer to designer. The HDL should allow the designer to control the amount of detail during each design phase.

- 7) The description of the LSI and MSI modules as system components should be straight forward, so is the inclusion of newer modules. If the system is partitioned by the designer to accommodate standard modules, this partitioning should be retained by the HDL translators and simulators.

All the above requirements are not met by any one HDL now available. The solution has been to design a new HDL to suit an individual design environment. AHPL, CDL, DDL and ISP have been the most popular languages, partly due to their early introduction as general purposes HDL's. These languages were developed in university environments and are used in teaching digital logic design. New features are being added to these languages to make them more versatile. Well tested translators and simulators are available for these languages. A bibliography of the literature on HDL's is provided in [8].

The characteristics of CDL, ISP, AHPL and DDL are summarized in Chapters 2,3,4 and 5. A comparison of these characteristics to select a language suitable for use in an automatic integrated circuit design environment is provided in Chapter 6.

#### 2. COMPUTER DESIGN LANGUAGE (CDL)

Computer Design Language was proposed originally by Chu [1-3]. A translator and simulator were written for a subset of this language [4]. Several modifications are made to this translator and simulator [5,6]. The present version [7] is implemented on IBM 370/115.

CDL describes the structural and functional parts of a digital system. The structural components like memory, registers, clocks, switches, etc. are declared explicitly at the beginning of the description. The functional behavior of the element are described by the commonly used operators and user defined operators. Valid data paths are declared implicitly whenever there is a data transfer. Both parallel and sequential opeations are allowed. Synchronous operations require a conditional test for an appropriate signal. The language is easy to understand and is highly readable.

All the variables in a CDL description are global. The system description can be only at one level, and there is no subroutine facility in CDL, thus making it unsuitable for describing hardware in a modular fashion. Gate delays and asynchronous operations can not be adequately described. It is not possible to include special hardware components like integrated circuits in a description. However, its simplicity of structure and its portability resulting from the FORTRAN implementation, have made CDL a popular language. The descripton of CDL Syn- tax and Semantics as accepted by the present version of tran- slator and simulator is presented.

-5-

## 2.1 SYNTAX RULES

<u>Variables</u> - variable names may contain 1 - 4 characters, the first of which must be alphabetic. The remaining characters may be alphabetic or numeric. Embedded blanks or special characters other than "+","-",",","\*","/",".","'","\$", and "=" are ignored. Variable names longer than 4 characters may be used and will appear on the listing, however their significance to the Translator is limited to the leftmost 4 characters. Some examples of variable naming follow:

Valid:

| Name    | CDL Name |   |    |       |

|---------|----------|---|----|-------|

| A1BC    | A1BC     |   |    |       |

| ABbCD   | ABCD     | b | is | blank |

| A1#CD   | A1CD     |   |    |       |

| START1  | STAR     |   |    |       |

| START 2 | STAR     |   |    |       |

Invalid:

|       | Reason                      |

|-------|-----------------------------|

| 1B3D  | Nonalphabetic 1st character |

| AB.CD | contains special character  |

Reserved words - The following may not be used as variable names: IF, THEN, ELSE, DO, CALL, RETURN, and END.

<u>Constants</u> - Constants may be entered in three forms subject to the following conditions:

| Form        | <u>Max. Digits</u> |

|-------------|--------------------|

| Binary      | 32                 |

| Hexadecimal | 8                  |

| Decimal     | 9                  |

-6-

Hexadecimal constants are denoted by a colon (:) preceding the significant digits. Binary constants are preceeded by a semicolon (;).

In general, for numeric constants, blanks and special characters other than those listed in the discussion of variable names are ignored. Characters outside the permissible set for the form used are also ignored. Some examples of numeric constants follow:

| Valid   | Value                        |

|---------|------------------------------|

| 1234    | 1234 <sub>10</sub>           |

| :100F   | 100F <sub>16</sub>           |

| ;110011 | 1100112                      |

| ;12b101 | 11012                        |

| Invalid | Reason                       |

| A345    | 1st character not numeric    |

|         | (will be treated as variable |

|         | name)                        |

## 2.2 DECLARATION STATEMENTS

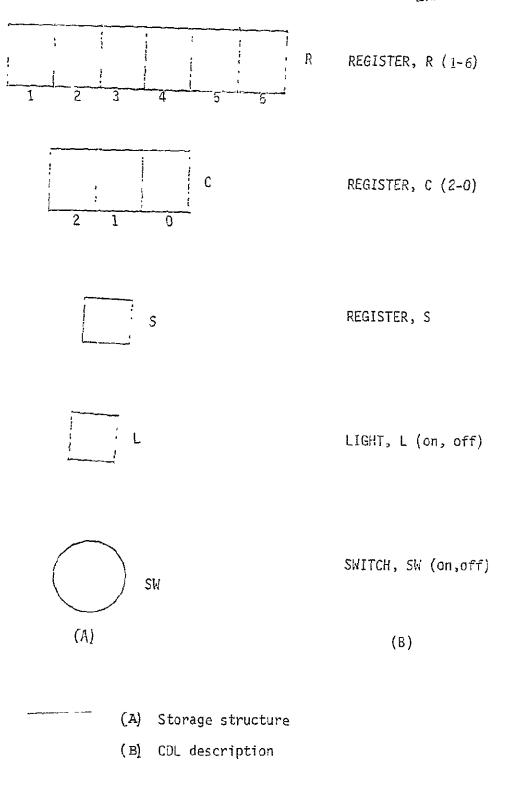

The following devices are permitted in CDL:

| Reg: | isters    | Terminals |

|------|-----------|-----------|

| Sub  | registers | Lights    |

| Memo | ories     | Bus       |

| Deco | oders     | Clocks    |

| Swit | tches     |           |

The syntax for a declaration statement 1s: DEVICE, list where the type of device begins in column two. Mixed notation for devices and other keywords is shown in the following paragraphs. The first four characters are significant and must not contain embedded blanks or special characters. The following table relates keywords and acceptable abbreviations:

| Keyword     | Abbreviation |

|-------------|--------------|

| REGISTER    | REGI         |

| SUBREGISTER | SUBR         |

| MEMORY      | MEMO         |

| DECODER     | DECO         |

| SWITCH      | SWIT         |

| TERMINAL    | TERM         |

| LIGHT       | LIGH         |

| BUS         | BUS          |

| BLOCK       | BLOC         |

| CLOCK       | CLOC         |

Note that the comma trailing the device name is mandatory.

## **REGISTER DECLARATION:**

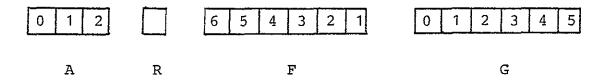

REGI,A(0-2),R,F(6-1),G(0-5) This declares the following:

#### SUBREGISTER DECLARATION:

SUBREGISTER, G(OP) = G(0-2), F(OR) = F(6-4)

The subregister is always used with a register name, and it refers to a part of that register. All referenced registers must have been previously declared. A general tendency is to give two subregisters the same name. e.g. SUBR,R(OP)=R(0-3),A(OP)=A(0-3) This is incorrect!

```

A correct statement of the above would be:

SUB,R(OPR)=R(0-3), A(OP)=A(0-3)

```

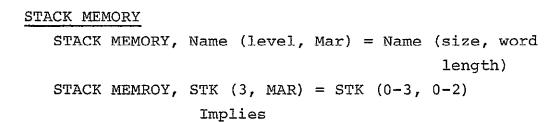

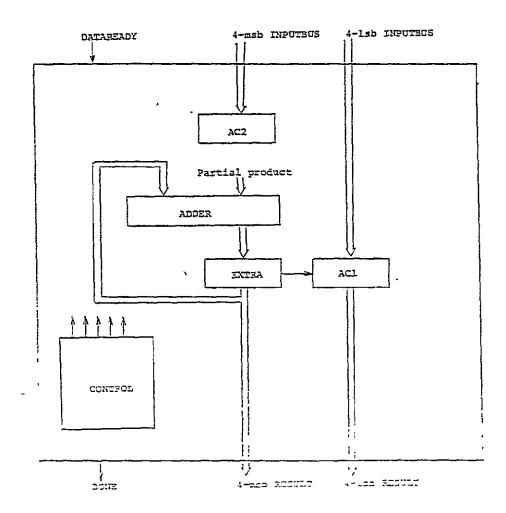

## MEMORY DECLARATION:

MEMO, M(R) = M(0-77, 0-10), N(J) = N(0-6, 3-1)

M and N are the names of the memories; R and J are the corresponding address registers which should have previously been declared; 0-77 and 0-6 represent the limits of the addresses of the words in the memories; 0-10 and 3-1 represent the order of the bits of each word.

## DECODER DECLARATION:

A decoder is a logic network which translates each value of the contants of a register to one and only one of the outputs;

DECO, K(0, 1) = F, L(0, 15) = G(2-5)

This declares the following:

Where F and G have been previously declared.

#### CLOCK DECLARATION:

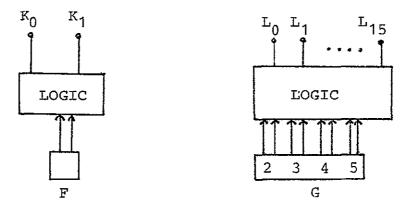

A clock may be specified for event synchronization. CLOCK, P(2)

This declaration defines three clocks, P(0), P(1), P(2). The impulse diagrams are assumed to be the following:

The time intervals between the impulses given by the clocks are the same. A clock may be referenced only in the expression of the label.

During execution, a clock cycle is designated on the simulation printed results as clock time.

#### SWITCH DECLARATION:

SWITCH, STRT (OFF, ON), SENS (P1, P2, P3)

The switch names are STRT and SENS the positions for STRT are OFF and ON and for SENS they are P1, P2, and P3 where OFF and P1 are the respective initial positions.

In later references a switch is either checked for one of its positions, or set to one of its positions. When a switch is checked for a position, it has the form: NAME(POS) e.g. SENS(P2) when setting a switch to a position: NAME=pos e.g. SENS=P2 NOTE: A maximum of 10 switch positions is permitted.

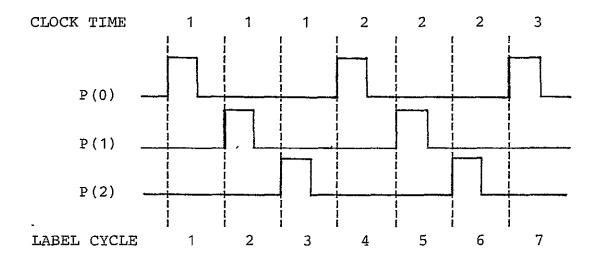

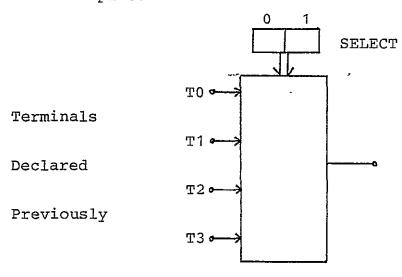

#### TERMINAL DECLARATION:

A terminal statement can rename a terminal or describe a logic network.

or using subscripted terminals

REGISTER, A(0-2)

TERMINAL, B(0-2) = A(0-2)'

Both of these describe the following:

Referring to the decoder example: TERMINAL, ADD=L(0), SUB=L(1), JUM=L(2), etc.

LIGHT DECLARATION

LIGHT, RUN(ON, OFF), FINI(OFF, ON)

The lights RUN and FINI, each have two positions, with the initial position being ON for RUN and OFF for FINI.

A reference where a light is checked for its position,

has the form:

NAME (POSITION) ex: RUN (ON)

When setting the position of a light, the following format is used:

NAME=POSITION ex: RUN=OFF

## BUS DECLARATION

BUS, INTERNAL (15-0), DATA (7-0) This declares INTERNAL bus with 16 lines and DATA bus with 8 lines.

#### BLOCK DECLARATION:

In order to avoid the repeated writing of a group of microstatements, the block statement and do statement are created. The block statement declares the name for a group of microstatements. Whenever these microstatements are declared in an execution statement, a do statement is used to call them.

Example: Serial Complement

| REG          | SISTER,  | T(1-5),A(5-1)              |

|--------------|----------|----------------------------|

| SWI          | TCH,     | START (ON)                 |

| CLC          | CK,      | P                          |

| BLC          | CK,      | SERCOM(A=A(1)'-A(5-2))     |

| /ST          | ART (ON) | /T=20                      |

| /T (         | (1)*P/   | DO/SERCOM,T(1,2)=01        |

| /т (         | 2)*P/    | DO/SERCOM, T(2,3) = 01     |

| /Τ (         | (3)*P/   | DO/SERCOM,T(3,4)=01        |

| /Τ(          | (4)*P/   | DO/SERCOM, T(4,5) = 01     |

| /T (         | (5)*P/   | DO/SERCOM, T(5)=0          |

| DO i = f = 1 |          | -lash1/l and then the DTOC |

NOTE: DO is followed by a slash'/' and then the BLOCK name.

Another example of Block Declaration: BLOCK, PAR(A=B,R=0),CYC(A=A.COUNT., IF (A.EQ.1)THEN(R=1)ELSE(R=0)) All of the microstatements following the block names (PAR,CYC) will be executed when DO/PAR or DO/CYC are called.

### 2.3 CONTINUATIONS

ONLY declaration statements may be continued onto other cards by placing a '1' in column one of the subsequent cards. Label statements and switch statements may be continued on subsequent cards by leaving column one blank.

Declaration and Label statements are limited to 250 terms, where a term is considered to be:

a device name, a variable name, a constant, or any of the following special characters: "+","-","\*","'","\$","/","(",")", or "."

Example:

REGI,A(0-2), 1 B(0-6), 1 C(6-1) /K\*A(2)/ B=B.COUNT. C=C.COUNT.

2.4 COMMENT CARDS

A comment may be made by placing a 'C' in column one. The comment will be ignored by the translator. Comments are not continued in the conventional manner, rather a 'C' in column one of every subsequent card will continue the comment.

Example:

- C SIMULATION OF A SECOND

- C GENERATION COMPUTER

## 2.5 OPERATORS

## STANDARD OPERATORS

The following standard operators are available in CDL:

|     | SYMBOL       | FUNCTION    | EXAMPLE | EXPLANATION                                        |

|-----|--------------|-------------|---------|----------------------------------------------------|

| 1   | (Apostrophe) | Complement  | Α'      |                                                    |

| 1   | (Equal Sign) | Replace     | A=B     | Contents of A are<br>replaced by contents<br>of B. |

| -   | (Dash)       | Concatenate | A-B     | Contents of A & B are placed side by side.         |

| +   | (Plus Sign)  | Logical OR  | A+B     | Bit-wise OR (A and B must be conformal).           |

| *   | (Asterisk)   | Logical AND | A*B     | ······,·                                           |

| • I | 5Q.          |             | A.EQ.B  | Gives '1' if A and B                               |

|     |              |             |         | are equal.                                         |

| .1  | VE.          |             | A.NE.B  | Gives '1' if A and B                               |

|     |              |             |         | are unequal.                                       |

## SPECIAL OPERATORS

Special operators can be established by the user through a separate subprogram. It is referenced by a symbolic name delimited by periods. Example:

\*OPERATOR, X(1-4).COUNT. // IF (X(4).EQ.O)THEN(X(1-3)-1) ELSE (IF (X(3).EQ.O)THEN (X(1-2)-1-0) ELSE (IF(X(2).EQ.O)THEN (X(1)-1-0-0) ELSE (X(1)'-0-0-0))),RETURN

END

The first line is a heading line of the subprogram: \*OPERATOR (or \*OPER) specifies the type of the subprogram, it is followed by a comma and by the name of the first argument, the name of the operator enclosed in a pair of dots, and by the name of the second argument if the operator is binary. If the arguments represent more than one bit, the bit addresses must follow the argument's name in parenthesis, e.g., S(1-4).

The subsequent lines are headed by a blank label, i.e., two slashes. This indicates an immediate execution of the operations when the operator is called. Following the blank label, there must be an expression, which may be a conditional expression, giving the result of the output terminal. The subprogram must be ended with a RETURN and an END statement.

#### **RESTRICTIONS:**

The following special operators are built in for Simulation and they may not be defined by separate subprograms.

| A.ERA.B p | erforms t | he e | exclusi | ve ( | OR | of | A | and | В |  |

|-----------|-----------|------|---------|------|----|----|---|-----|---|--|

|-----------|-----------|------|---------|------|----|----|---|-----|---|--|

- A.ADD.B performs the algebraic sum of A and B, an overflow bit is discarded

- A.SUB.B performs the algebraic sum of A and the complement of B, an overflow bit is discarded

- A.COUNT. Adds one to A, an overflow bit is discarded A.LT.B gives one bit of output: 1 if the conditions A.LE.B algebraically less than, less or equal

A.GE.B greater or equal, greater than, are satis-A.GT.B fied: 0 if the conditions are not met

2.6 MICRO STATEMENTS

An <u>UNCONDITIONAL MICROSTATEMENT</u> consists of a variable representing a storage element, the REPLACE OPERATOR and an expression.

Example:

A=1,B(1,3-5)=C\*D+E(2,0-2)

NOTE: A given device or portion of a device must not appear on the left of a 'replace by' operator more than once in any set of microstatements to be executed during a given label cycle.

A CONDITIONAL MICROSTATEMENT has the following forms:

(a) IF(expression) THEN (microstatements)

IF (expression) has the value '1' then the operations inducated by the (microstatements) will be executed.

#### Example:

IF (A.EQ.B) THEN (R=0)

(b) IF (expression) THEN (microstatements) ELSE (microstatements) if the (expression) is true then the operations indicated by the (microstatements) immediately following THEN will be executed, otherwise the operations indicated by the (microstatements) immediately following ELSE will be executed. Example:

IF (C.NE.D) THEN (R=0) ELSE (R=1)

Conditional statements may be nested in order to form a very powerful decision-making capability. An example of a nested appears in section 5.2. Note that each of the nested IF's must be enclosed in parentheses as shown in the following generalized example:

2.7 SWITCH STATEMENTS

The Switch Statement has the following form: /NAME(POSITION)/microstatements where Name corresponds to a declared Switch Name. Example: SWITCH, STRT(OFF,ON), SENS(S1,S2,S3) /STRT(ON)/A=0,F=1,SENS=S2

The indicated microstatements here would not be executed since STRT(ON) is FALSE.

## 2.8 LABELED STATEMENTS

The Labeled Statement has the following form: /LABEL/microstatements

where;

LABEL = expression \* clock

RESTRICTION;

The expression must not include any clock reference. Example:

/K(O) \* P / A=B, B=A

#### 2.9 END STATEMENT

The physical end of the description of a design is indicated by the word END.

### 2.10 CARD FORMAT

#### HEADING CARD

The main design and the user's defined operators must be preceded by heading cards as follows:

Col. 1-5 \*MAIN

or

Col. 1-...\*OPERATOR...

where no embedded blanks are allowed. The Operator card should contain the arguments and the name of the operator.

#### OTHER CARDS

Declaration cards, Labeled Statement cards, and the End Card may be punched anywhere in columns 2-72. Blanks may be used freely.

## 2.11 TRANSLATOR

The translator accepts the logical design written in CDL from punched cards. It translates the design into a form

suitable for simulation. This consists of various tables and a pseudo program called Polish String. If the \$TRANSLATE card is punched PRIN in columns 14-17, the various tables and Polish String will be printed.

The Translator is called by a special control card having \$TRANSLATE (or \$TRANS) punched in col. 1-10. This card is followed by the deck of cards describing the logical design using CDL. The Translator remains in control until a new control card with \$ in column 1 is read in. A typical deck set-up should appear as follows:

\$TRANSLATE ----Translator is called

\*MAIN

.

.

END

\*OPERATOR,... ----Translator is in control

.

.

.

SIMULATE ----Simulator is called

Simulator is in control

.

.

.

### 2.12 SIMULATOR

The Simulator consists of 5 parts: Loader, Output, Switch, Simulate, and Reset routimes. The Loader accepts test data from punched cards and stores them into memory or into specified registers of the designed computer. The Output routine handles the printout of the contents of the chosen registers, memory words and position of switches during the simulation. The Switch routine simulates the operation of the manual switches. The Simulate routine actually executes the test program. Reset routine reinitializes the Simulator.

The execution of the test program is controlled by a loop which is called the Label Cycle. During each label cycle, the following steps are taken: (a) If a manual switch opera- tion occurs, the corresponding executable statement for the switch operation is carried out. (b) All label values are evaluated. The activated label, i.e., the label expressions having the value TRUE, are accounted for. (c) The microstatements of the activated labels are carried out in two steps. First, all values to be stored in various registers and memory words are evaluated and collected. Then, the collected values are stored one after the other. (d) It is checked whether the simulation should be terminated.

If the Simulation is terminated, the Reset routine can be called and another set of data can be inserted as a test program.

Example: The following is a demonstration of a simula-

CDL Design cards

tion with 2 test programs.

\$TRANSLATE

\*MAIN

....

END

\*OPERATOR, ...

END

\$SIMULATE \*OUTPUT \*SWITCH \*LOAD \*SIM... \*RESET \*LOAD ..... \*SIM...

#### LOAD ROUTINE

The Loader provides the storing of test programs. The data cards should use Col. 2-72, blanks may be inserted anywhere. Only declared full registers and memory words with constant addresses can be loaded with data. The format of the data cards is as follows:

> Data loaded into a register: REG = d Data loaded into memory words M(L)=d or M(L<sub>1</sub>-L<sub>n</sub>)=d<sub>1</sub>,d<sub>2</sub>,...,d<sub>n</sub> or M(L<sub>1</sub>-)=d<sub>1</sub>,d<sub>2</sub>,...,d<sub>n</sub>

Where REG is the name of the register whose contents must be set to the value d. M is the name of the memory and  $L_1$  denotes word addresses. In the first case d is loaded into memory word M(L). In the second case, the words  $d_1-d_n$  are loaded into memory words with addresses  $L_1$  to  $L_n$  consecutively. In the last case, the last address is defined by the number of numbers punched.

A data card may contain any number of lists separated by commas. There is no provision for a continuation card, thus each data card must start with the name of a register or a memory in column 2.

Example:

\*LOAD

R1=0,AC=20,SEP=72,M(0-3)=1,2,3,4,M(77)=345 M(10-)=70,71,72,73,74,75,76,77,100

#### OUTPUT ROUTINE

The output routine provides the printed output of the contents of specified registers, memory words and positions of switches during the simulation. The following format is required:

| Col. 1-7   | *OUTPUT |

|------------|---------|

|            | LABEL   |

| Col. 11-15 | or      |

|            | CLOCK   |

| Col. 16-21 | (n,m) = |

| Col. 22-72 | list    |

Where the label or clock punch specifies the type of output required, n specifies the start of output and m specifies the frequency of the output. The list consists of the names of the registers, switches and memory words whose contents should be printed.

During the simulation, the output may occur at every mth label cycle or at every mth clocktime depending on the type, Label or Clock in Col. 11-15. If the design happens to have one clock, then the two types coincide.

Example:

\*OUTPUT CLOCK (1,10)=RR,START,M(0),M(777),

AC, MQ, M(10), OVER

The list may be continued on the next card(s) provided that column 1 is left blank on the continuation cards. The output of all listed devices is given in hexadecimal, regardless of input format.

#### SWITCH ROUTINE

Manual switch settings are initiated by the Switch routine. The necessary information is given on \*SWITCH cards. For each switch setting, a separate \*SWITCH card is necessary. It has the following format: Col. 1-7 \*SWITCH Col. 11-12 L, Col. 13- NAME=POSITION

Where L specifies the Lth label cycle before which the switch operation occurs. The NAME corresponds to the name of the switch with POSITION as one of its positions declared. During the simulation, an output will occur after every switch setting with a heading stating the interrupt.

#### SIMULATE ROUTINE

The actual simulation starts by calling the Simulate routine using the control card with the following format: Col. 1-4 \*SIM Col. 11- n,r Where n and r are the terminating conditions, n is the maximum number of label cycles allowed, r is the allowed maximum number of consecutive label cycles such that the same group of labels is activated in the CDL program.

Example:

\*SIM 400,3

#### RESET ROUTINE

The Reset routine reinitializes the Simulator to its initial conditions. It is called by a control card with the following format:

| Col. | 1-6          | *RESET    |

|------|--------------|-----------|

| Col. | 1 <b>1</b> – | (options) |

The options may be one or more of the following terms separated by commas:

OUTPUT, resets the output requested previously, it is assumed that another \*OUTPUT card will be given

SWITCH, resets the manual switch operations re-

|        | quested it is assumed that another *SWITCH |

|--------|--------------------------------------------|

|        | card will be given                         |

| CLOCK, | resets the counter of the clock cycle      |

CYCLE, resets the label cycle counter and the clock cycle counter

Example:

| *RESET | CYCLE, OUTPUT |

|--------|---------------|

|        |               |

The reset card then followed by other OUTPUT card, possibly other LOAD card with data, and by a SIM card.

CDL translator and simulator also have an extensive error diagnostics capability.

## 2.13 DESIGN EXAMPLES

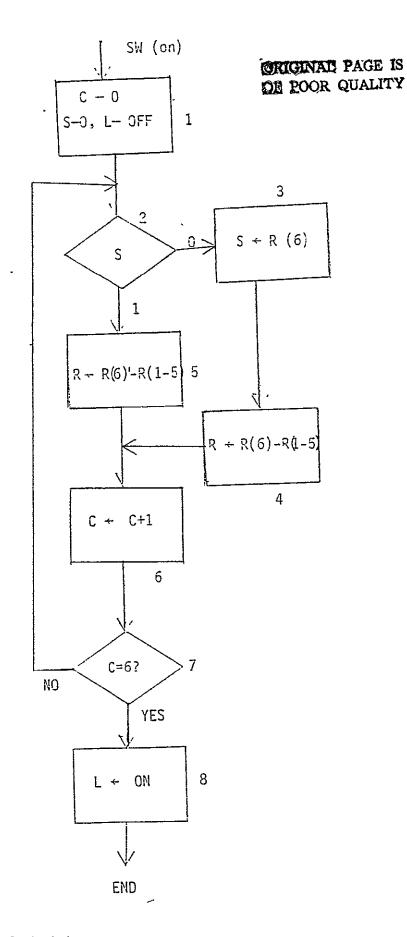

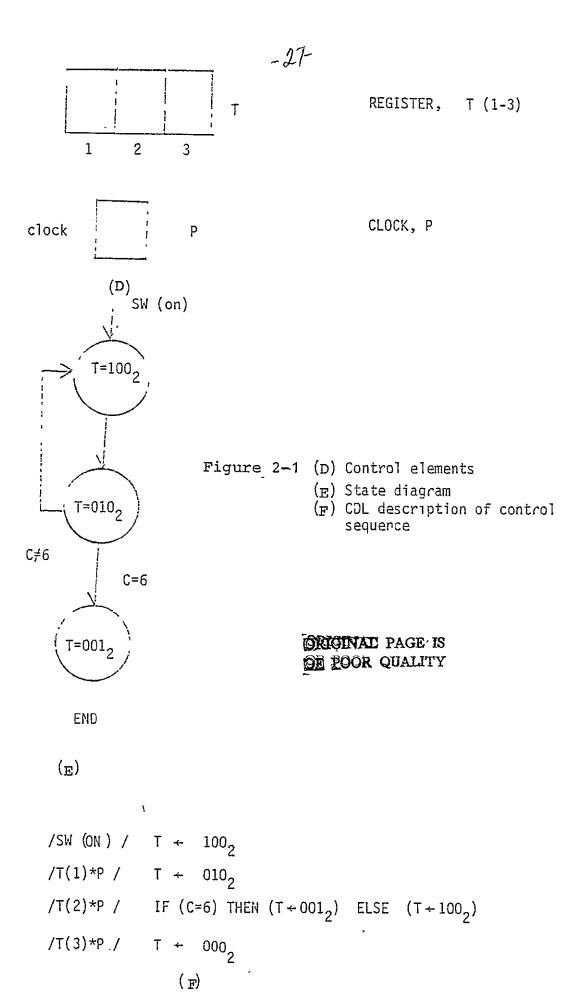

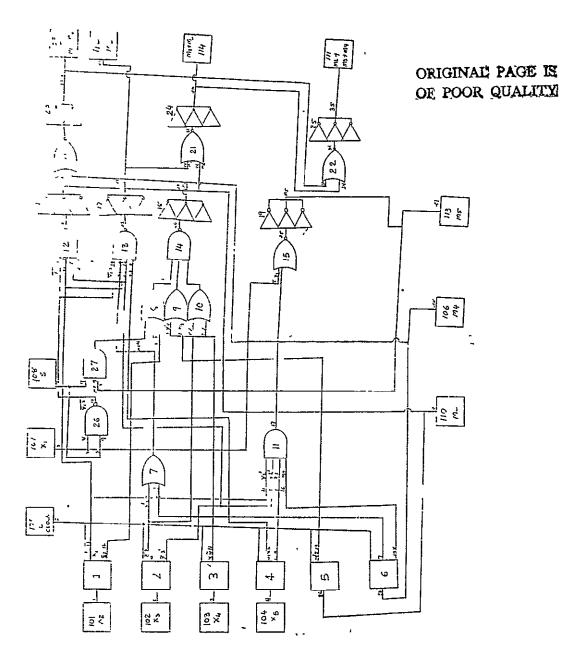

The design process using CDL for a serial two's complementer circuit is illustrated [8] in Figure 2-1. A similar design example is provided in [9]. Several CDL descriptions can be found in [10].

Figure 2-2 shows a sequential circuit along with the CDL description and simulation results.

A CDL description of a variable timer circuit shown in Figure 2-3 is provided in Figure 2-4. CDL is highly suitable for this level of description.

Basically, the circuit consists of a devide by 3600 circuit R along with a counter CT that counts the number of times R goes to zero. CT is compared with the input setting IN. IF IN equals CT an output pulse is given and the START flip-flop is reset to disable the clock. ABORT input clears

# ORIGINAL PAGE IS OF POOR QUALITY

Figure 2-1 Serial Twos Complementer

Figure 2-1 (C): Twos Complementer Sequence Chart

-28-**\$TRANSLATE** ORIGINAL PAGE IS \* MA IN-----OF POOR QUALITY С STORAGE REGISTER, R(1-6), C(2-0), S Ł LIGHT, L(ON, OFF) SWITCH, SATUNI C CONTROL REGISTER, TTI-37 CLOCK, P C-PROCESSOR /SW(ON)/T=;100,C=0,L=0FF,S=0 /T(1)#2/T=;010,0=C.COUNT.,1FTS.EQ.UTTHENTS=R(6),R=(R(6)=R(1=5))] ELSF(R=(R(6)'-R(1-5)))/T(2)\*P/TF(C-EQ.; 110)THEN(T=;001)ELSE(T=;105)-/T(3) \* P/T=;000, L=ON -EMD-\$SIMULATE #0UT?UT---CLOCK(1,1)=R,C,S,T,L 1, SW=ON **¥SWITCH** ≑t0AD-R=5 \*<u>51</u>-4---20,0 -~ - -+ Figure 2-1 (G): - CDL-Complete Deck-Set-Up-•

ORIGINAL PAGE IS

DUIPUT OF SCHULATION

\*\*\*\* SWITCH INTERRUPT \*\*\*\* SH = 0N R = ..05 C = ...0 S = ...0 T = ...4 L = 0FH \*\*\*\*\*\* LABEL CYCLE I TRUE LABELS CLUCK CYCLE 1 /T(1)+P/ R = 3.22 C = 33.1 S = 3.31 S = 3.31 S = 3.32 S = LABEL CYCLE 2 TRUE LABELS CLOCK CYCLE 2 T(2) \* P/R = ...22 C = ...1 S = ...1 T = ...4 L = 0[[ \*\*\*\*\* R = ...31 C = ...2 S = . S = •••1 [ = •••2 L = 0FF \*\*\*\*\*\*\* LABEL CYCLE 4 TRUE LABELS CLUCK CYCLE 4  $/T(2) \neq P/$  R = ...31 - C = ...2 - ...S = ...1 - ... T-=....4 - ...-L-= OFF\*\*\*\*\*\* LABEL CYCLE 5 TRUE LABELS CLUCK CYCLE 5  $/T(1) \neq P/$  R = ...18 C = ...3 S = ...1 T = ...2L = OFF \*\*\*\*\*\* LABEL CYCLE ... 6-----R = ..18 C = ...3 S = ... S = ...1 T = ...41 = 0FF \*\*\*\*\* TRUE LABELS LABEL CYCLE 7 CLUCK CYCL⊢ 7 /T(1)\*P/ \* R = ...2C ---- C-=-...4 ----- S = -...1--- ---T = ...2---- L-= UFF \*\*\*\*\*\* TRUE LABELS CLOCK CYCLE LAUEL CYCLE 8 8 /T(2)\*P/ R = ...2C · C = ...4 S = ...1 J = ...4 L = 0FF \*\*\*\*\*\* /T[1]\*P/ R = ...36 C = ...5 S = . S = ... 1 T = ... 2L = OFF\*\*\*\* LABEL CYCLE 10 TRUE LABELS -CLUCK CYCLE 10 /T{2}\*P/ R = ... 36- - - C = ... 5------ S-= ... L- --- -- T = ... 24 --- -- L = OFF - ----\*\*\*\*\*\* CLUCK CYCLE 11 LABEL CYCLE 11 TRUE LABELS R = ...38 C = ....6 S = ... (T(1) + P)S = ...1 ( = ...2 L = UFF\*\*\*\*\*\*\* LABEL CYCLE - 12 - --- TRUE LABELS - -- -- CLOCK CYCLE 12 /E(2)#P/ R = ...3B C = ...6 S = ...1 T = ...1L = 0FF\*\*\*\*\* LABEL CYCLE 13 TRUE LABELS CLUCK CYCLE 13  $T[3] \neq P/$   $R = ...3B \qquad C = ...6 \qquad S^{-1} = ...1 \qquad I = ...0 \qquad L = (...)$ #### SIMULATION TERMINATED - NO TRUE LABELS #RESET CYCLE,CLUCK \*LOAD R=21 , 10 / AC 144 \*\*\*\*\*\*

Figure 2-1 (H): Simulation Results for R=510

Figure 2-2 (A): A Sequential Circuit

$$M_{2} = (x_{3}' + M_{4}') \cdot x_{2}' \cdot \overline{(x_{1} \cdot s_{1})}$$

$$M_{3} = \overline{(x_{1} \cdot s)} \cdot x_{2}' \cdot \overline{x_{3}'} \cdot x_{5}'$$

$$M_{4} = (M_{5} \cdot s + \overline{x_{2}'}) \cdot (x_{4}' + M_{2}') \cdot (x_{3}' + x_{4}')$$

$$M_{5} = x_{1} + (\overline{x_{2}'} \cdot \overline{x_{3}'} \cdot \overline{x_{5}'} \cdot \overline{M_{4}})$$

| STRANSLATE                                         |

|----------------------------------------------------|

| *MAIN                                              |

| SWITCH, START(ON)                                  |

| REGI, FF(1-6), M2, M4, M5, X(1-6), ST(0-1)         |

| CLOC, P                                            |

| TERM, T1=M2+M4,M3=(X(1)*X(6))'*FF(1)*FF(2)'*FF(4), |

| 1T3=M2+M3, T4= M2+M3+M4                            |

| /START (ON)/ST=1                                   |

| /P*ST(1)/FF=X,ST=2                                 |

| /P*ST(0)/M2=(FF(2)+FF(6))*FF(1)*(X(1)*X(6))*,      |

| M4= (M5*X(6)+(FF(1))*)*(FF(3)+FF(5))*              |

| [FF(2)+FF(4)],                                     |

| M5=X(1)+(FF(1)*(FF(2))**(FF(4))**(FF(6))*),        |

| ST=1                                               |

| END                                                |

| \$SIMULATE                                         |

| *OUTPUT CLOCK(1,1)=FF,M2,M4,M5,X,ST,START          |

| *SWITCH 1,START=ON                                 |

| *LOAD                                              |

| M2=1, M4=1, M5=1                                   |

| *SIM 25,2                                          |

| END OF DATA ON INPUT                               |

|                                                    |

NOTES: S is renamed as X(6) in the above description. Modules 1-6 of the circuit, are named FF (1-6).

Figure 2-2 (6): CDL description of Sequential Circuit

|   |                |   | ORIGIN  | AU PAGE N |

|---|----------------|---|---------|-----------|

| c | UTPUT OF SINUL |   | -OF POC | R QUALITY |

| - |                | • |         |           |

| FF = ++00 H2 = +++1                                                                                                                                                                                                                              | M4 = +++1                                                                                                                                                                                                                                                                                                                                                   | 85 =1                                                                                  | x =00                                                                                                                                                                                                                                                       | ST =1                                                                                                                                                                                                                                                                                                                                 | SIAR = v                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LABEL CYCLE 1                                                                                                                                                                                                                                    | ******                                                                                                                                                                                                                                                                                                                                                      | ******                                                                                 | *************                                                                                                                                                                                                                                               | *****                                                                                                                                                                                                                                                                                                                                 | ************                                                                                                                                                                                                                                                                                                                                                    |

| LABEL CICLE I                                                                                                                                                                                                                                    | /P*ST(1)/                                                                                                                                                                                                                                                                                                                                                   |                                                                                        | CLUCK LILLE                                                                                                                                                                                                                                                 | L                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |

| FF = ++00 M2 = +++1                                                                                                                                                                                                                              | H4 = •••1                                                                                                                                                                                                                                                                                                                                                   | #5 =1                                                                                  | X =00                                                                                                                                                                                                                                                       | ST =2                                                                                                                                                                                                                                                                                                                                 | 5TA- = +/                                                                                                                                                                                                                                                                                                                                                       |

| LABEL CYCLE 2                                                                                                                                                                                                                                    | *****                                                                                                                                                                                                                                                                                                                                                       | *******                                                                                | ********                                                                                                                                                                                                                                                    | *********                                                                                                                                                                                                                                                                                                                             | *******                                                                                                                                                                                                                                                                                                                                                         |

| LABEL CYCLE 2                                                                                                                                                                                                                                    | TRUE LABELS                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | CLOCK CYCLF                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |

| FF =0 M2 =0                                                                                                                                                                                                                                      | /P*ST(0)/                                                                                                                                                                                                                                                                                                                                                   | - ME - 0                                                                               |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |

| ******                                                                                                                                                                                                                                           | ******                                                                                                                                                                                                                                                                                                                                                      | *****                                                                                  |                                                                                                                                                                                                                                                             | ,4************************************                                                                                                                                                                                                                                                                                                | C+++++++++++++++++++++++++++++++++++++                                                                                                                                                                                                                                                                                                                          |

| LABEL CYCLE 3                                                                                                                                                                                                                                    | TRUE LABELS                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | CLOCK CYCLE                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                  | /P*ST(1)/                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |

| FF =0 N2 =0                                                                                                                                                                                                                                      | M4 =0                                                                                                                                                                                                                                                                                                                                                       | 00 =0                                                                                  | X =00                                                                                                                                                                                                                                                       | ST = •++2                                                                                                                                                                                                                                                                                                                             | STAR = UN                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                  | TRUE LABELS                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | CLOCK CYCLE                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                  | /0#57701/                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |

| FF =0 H2 =0                                                                                                                                                                                                                                      | N4 =0                                                                                                                                                                                                                                                                                                                                                       | M5 =0                                                                                  | X =00                                                                                                                                                                                                                                                       | ST =1                                                                                                                                                                                                                                                                                                                                 | STAR = ON                                                                                                                                                                                                                                                                                                                                                       |

| ******                                                                                                                                                                                                                                           | *****************                                                                                                                                                                                                                                                                                                                                           | ********                                                                               |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       | ******                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                  | TRUE LABELS                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | CLOCK CYCLE                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                 |

| FF =0 H2 =0                                                                                                                                                                                                                                      | M4 =0                                                                                                                                                                                                                                                                                                                                                       | N5 =0                                                                                  | X =00                                                                                                                                                                                                                                                       | ST =2                                                                                                                                                                                                                                                                                                                                 | STAR = ON                                                                                                                                                                                                                                                                                                                                                       |

| **********************************                                                                                                                                                                                                               | *************                                                                                                                                                                                                                                                                                                                                               | *********                                                                              | ********                                                                                                                                                                                                                                                    | *********                                                                                                                                                                                                                                                                                                                             | *****                                                                                                                                                                                                                                                                                                                                                           |

| FF =0 HZ =0                                                                                                                                                                                                                                      | TRUE LABELS                                                                                                                                                                                                                                                                                                                                                 |                                                                                        | CLOCK CYCLE                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                 |

| EE =                                                                                                                                                                                                                                             | /P#ST(0)/                                                                                                                                                                                                                                                                                                                                                   | M5 - ^                                                                                 | <u>v - co</u>                                                                                                                                                                                                                                               | CT _ ·                                                                                                                                                                                                                                                                                                                                | CT10 - 0H                                                                                                                                                                                                                                                                                                                                                       |

| - *************************************                                                                                                                                                                                                          | **************                                                                                                                                                                                                                                                                                                                                              | *****                                                                                  | 7 = •=00<br>************                                                                                                                                                                                                                                    | 1+++<br>:*******                                                                                                                                                                                                                                                                                                                      | 101 = XALC<br>*********                                                                                                                                                                                                                                                                                                                                         |