CR-152059

N78-7001.8

#### PRELIMINARY STUDY

#### FOR A

#### NUMERICAL AERODYNAMIC SIMULATION FACILITY

#### FINAL REPORT

BY: N. R. Lincoln

A. A. Vacca

R. A. McHugh

R. W. Johnson

D. B. Bonstrom

#### OCTOBER, 1977

Distribution of this report is provided in the interest of information exchange. Responsibility for the contents resides in the authors or organization that prepared it.

Prepared under Contract No. NAS2-9457 by:

CONTROL DATA CORPORATION 2800 Old Shakopee Road Minneapolis, Minnesota 55440

for

AMES RESEARCH CENTER

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED

FROM THE BEST COPY FURNISHED US BY

THE SPONSORING AGENCY. ALTHOUGH IT

IS RECOGNIZED THAT CERTAIN PORTIONS

ARE ILLEGIBLE, IT IS BEING RELEASED

IN THE INTEREST OF MAKING AVAILABLE

AS MUCH INFORMATION AS POSSIBLE.

#### PREFACE

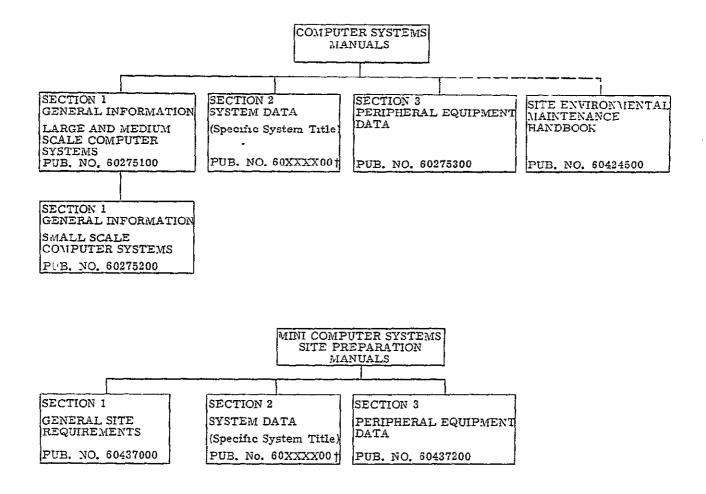

This Final Report presents the findings of the Preliminary Study for a Numerical Aerodynamic Simulation Facility (NASF) as determined by Control Data Corporation. The document consists of six sections. Each section addresses a specific aspect of the Control Data study, and each section includes appendixes, a reference listing, and bibliography where appropriate.

Sections 1 and 2 discuss current and future electronic technology and architecture technology as a basis for valid recommendations. Section 3 gives an analysis of existing flow models and the measurement criteria to be used for benchmarking the project. Section 4 highlights the objectives relative to the design of the facility. Section 5 discusses a preliminary system design which could meet the NASF objective. Section 6 gives an example of a configuration to establish requirements for constructing the site.

In addition to this Final Report, a separate Summary Report presents the salient findings of this preliminary study and summarizes the first phase of a program for the development of a Numerical Aerodynamic Simulation Facility.

# CONTENTS

# SECTION 1. ELECTRONIC TECHNOLOGY SURVEY AND PROJECTIONS

| Introduction                                       | 1-1  |

|----------------------------------------------------|------|

| Objective                                          | 1-2  |

| Scope                                              | 1-2  |

| Technologies Surveyed                              | 1-2  |

| Extent of Investigation                            | 1-2  |

| Methodology                                        | 1-3  |

| Sources of Data                                    | 1-3  |

| Approach Used                                      | 1-3  |

| Observations                                       | 1-4  |

| Charge Coupled Devices                             | 1-4  |

| General Description                                | 1-4  |

| Relative Merits                                    | 1-5  |

| Limitations                                        | 1-6  |

| Cost                                               | 1-7  |

| Risks                                              | 1-7  |

| Operational Implications                           | 1-7  |

| Magnetic Bubble Devices                            | 1-8  |

| General Description                                | 1-8  |

| Merits                                             | 1-10 |

| Limitations                                        | 1-11 |

| Status of Technology                               | 1-12 |

| Prognosis                                          | 1-12 |

| Electron-Beam-Addressed Memory                     | 1-14 |

| General Description                                | 1-14 |

| Relative Merits                                    | 1-14 |

| Limitations                                        | 1-15 |

| Cost                                               | 1-19 |

| Risks                                              | 1-19 |

| Operational Implications                           | 1-19 |

| Large Scale Integration of Semiconductor Circuitry | 1-20 |

| Storage Technology                                 | 1-21 |

| Limits of LSI                                      | 1-22 |

| Reliability of LSI                                 | 1-24 |

| Some Comparative Technologies for the 1980's       | 1-25 |

| Prognosis                                          | 1-34 |

| Josephson Devices                                  | 1-35 |

| General Description                                | 1-35 |

| Relative Merits                                    | 1-36 |

| Limitations                                        | 1-36 |

| Cost                                               | 1-38 |

| Prognosis                                          | 1-38 |

| Advanced Rotating Mass Storage                     | 1-38 |

| General Description                                | 1-38 |

| Canacity                                           | 1_39 |

|            | Media                                                       | 1-40         |

|------------|-------------------------------------------------------------|--------------|

|            | Costs .                                                     | 1-40         |

|            | Access Time                                                 | 1-41         |

|            | Prognosis                                                   | 1-41         |

|            | High Speed Data Channels                                    | 1-42         |

|            | General Description                                         | 1-42         |

|            | Coax Transmission                                           | 1-44         |

|            | Optical Fibers Transmission                                 | 1-54         |

|            | Wireless Transmission                                       | 1-55         |

|            | Advanced Test Equipment                                     | 1-56<br>1-56 |

|            | General Description Functional Test Mode                    | 1-50<br>1-57 |

|            | Pattern Test Mode                                           | 1-57         |

|            | Transition Test Mode                                        | 1-57         |

|            | Test Equipment Configuration                                | 1-58         |

|            | Availability                                                | 1-58         |

|            | Conclusions and Recommendations                             | 1-59         |

|            | Introduction                                                | 1-59         |

|            | Selecting a Technology                                      | 1-59         |

|            | Significant Factors                                         | 1-60         |

|            | The Useful Technologies                                     | 1-61         |

|            | Memories                                                    | 1-61         |

|            | CPU Circuits                                                | 1-66         |

| SECTION 2. | ARCHITECTURAL SURVEY AND PROJECTIONS Outline of the Problem | 2-1          |

|            | Technology Influences                                       | 2-4          |

|            | Standard and Special System Components                      | 2-5          |

|            | Compilers                                                   | 2-6          |

|            | Graphics                                                    | 2-7          |

|            | Communications and Other Utility Functions                  | 2-9          |

|            | Review of Possible Special Processor (SP) Architectures     | 2-12         |

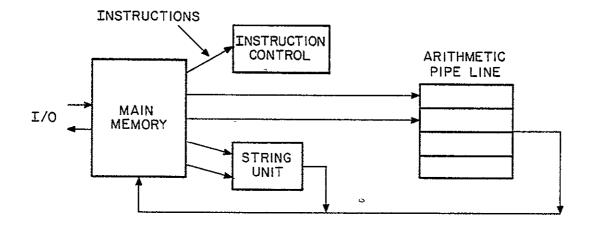

|            | CDC 6600/6500 (MIMD) Approach                               | 2-13         |

|            | Multiple Minicomputers for the MIMD Approach                | 2-15         |

|            | Performance Estimates of Multiple-Minis                     | 2-17         |

|            | Hardware Cost Estimate                                      | 2-19         |

|            | Variable Architecture                                       | 2-22         |

|            | CDC Flexible Processor (MIMD) Approach                      | 2-24         |

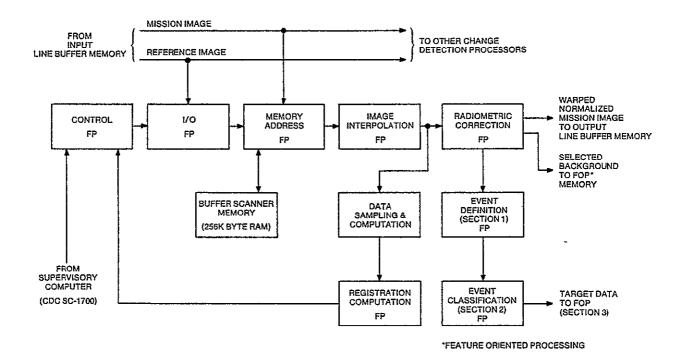

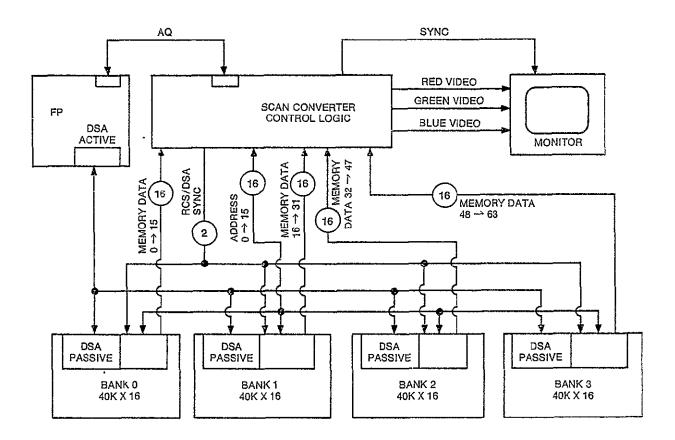

|            | Hardware and Software Description                           | 2-25         |

|            | Related Examples                                            | 2-26         |

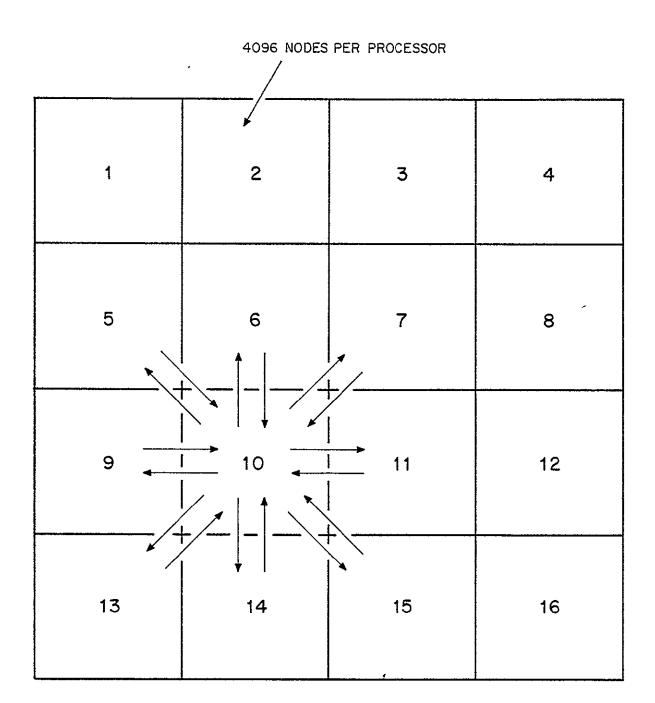

|            | The ILLIAC Structure (SIMD) Approach                        | 2-30         |

|            | Interconnect of Hardware, Interaction of Data               | 2-32         |

|            | Limited Memory Per Processor                                | 2-35         |

|            | Programmability Quotient                                    | 2-35         |

|            | Vector Processing for the SIMD Approach Hybrid Computing    | 2-36         |

|            | Tryot to Compacing                                          | 2-37         |

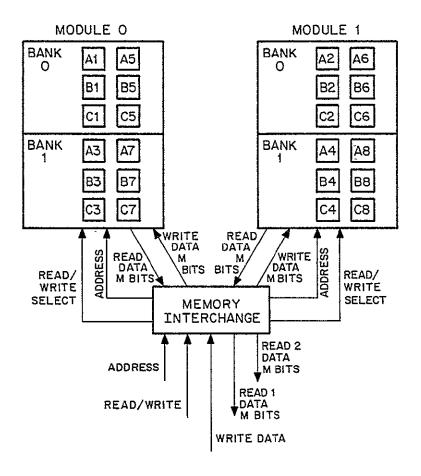

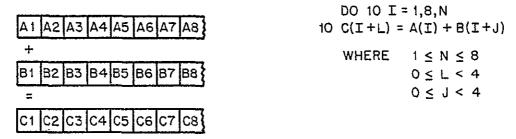

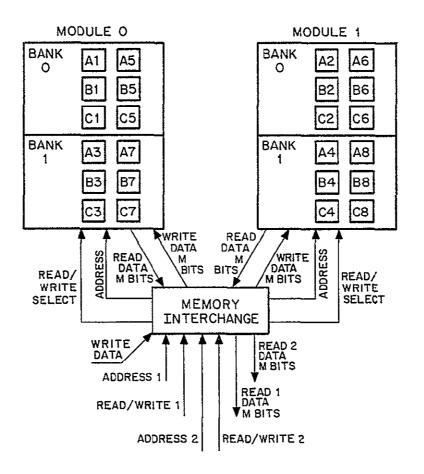

|            | Memory Architecture and Addressing                                                                                                                                                                                                   | 2-37                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

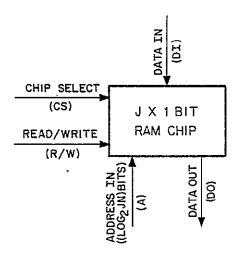

|            | Memory Chip                                                                                                                                                                                                                          | 2-39                                                        |

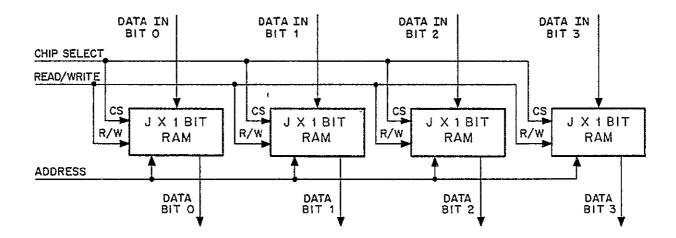

|            | 4-Bit Memory                                                                                                                                                                                                                         | 2-40                                                        |

|            | 2J by 4-Bit Memory                                                                                                                                                                                                                   | 2-41                                                        |

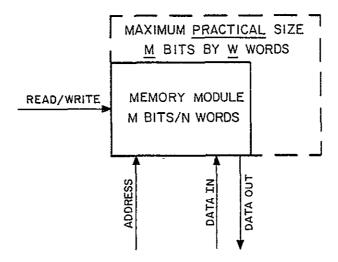

|            | A Single Memory Module                                                                                                                                                                                                               | 2-43                                                        |

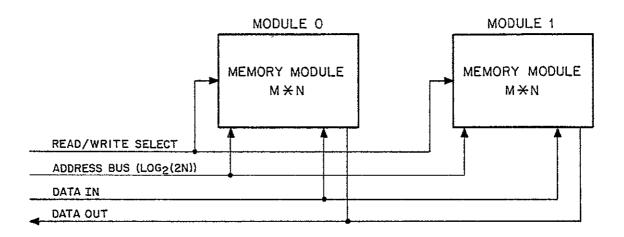

|            | M by 2N Memory on a Bus                                                                                                                                                                                                              | 2-44                                                        |

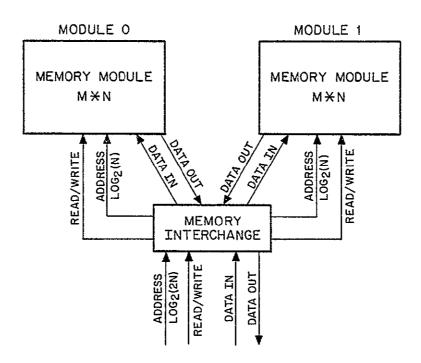

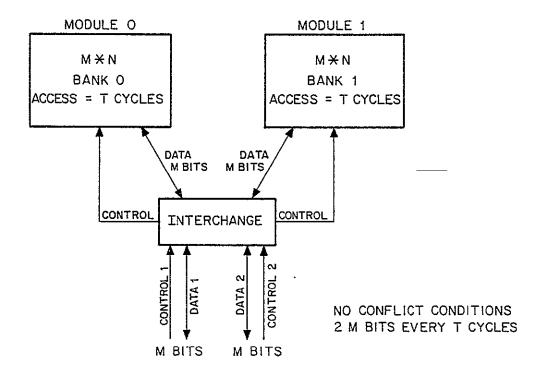

|            | M by 2N Memory Access Via Interchange                                                                                                                                                                                                | 2-46                                                        |

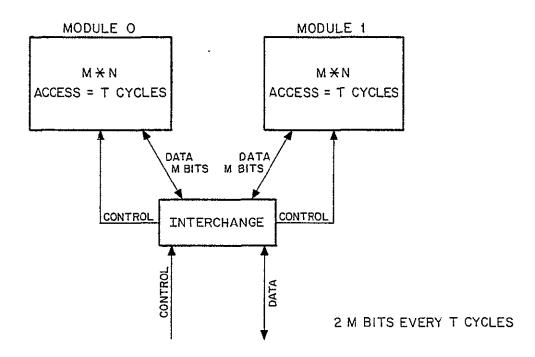

|            | Linear Select - No Banking                                                                                                                                                                                                           | 2-47                                                        |

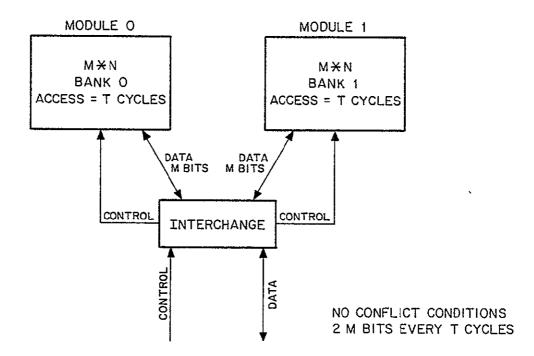

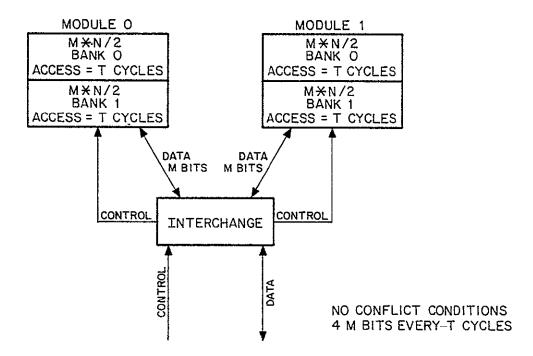

|            | Linear Select - Two Banks                                                                                                                                                                                                            | 2-49                                                        |

|            | Nonlinear Select                                                                                                                                                                                                                     | 2-50                                                        |

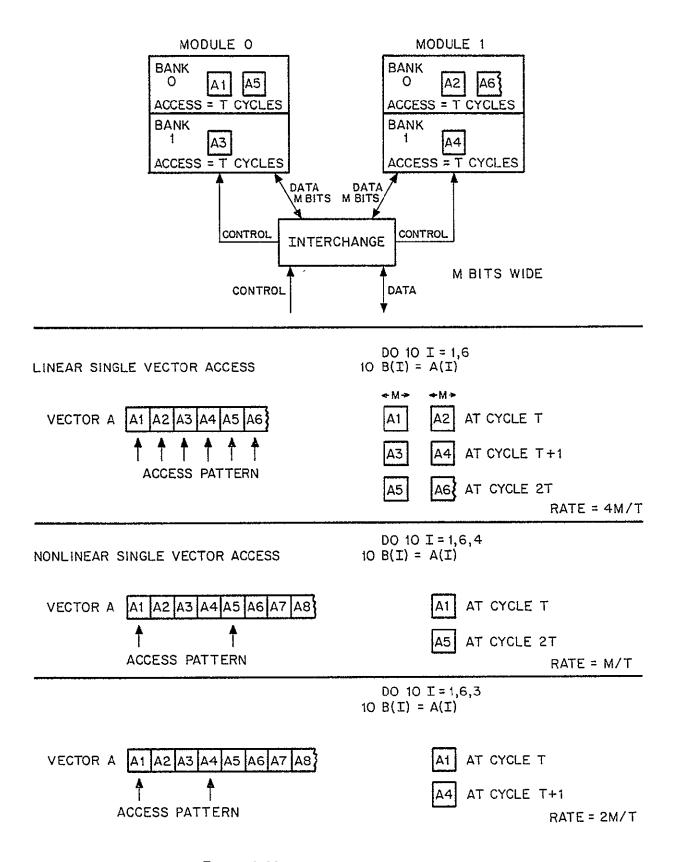

|            | Linear Select - Four Banks                                                                                                                                                                                                           | 2-52                                                        |

|            | Memory Access Patterns                                                                                                                                                                                                               | 2-55                                                        |

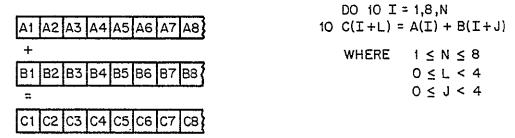

|            | Nonlinear Select, Separate Addressing                                                                                                                                                                                                | 2-59                                                        |

|            | System Architecture Considerations                                                                                                                                                                                                   | 2-63                                                        |

|            | System Balance                                                                                                                                                                                                                       | 2-63                                                        |

|            | I/O System                                                                                                                                                                                                                           | 2-65                                                        |

|            | Memory Hierarchy                                                                                                                                                                                                                     | 2-66                                                        |

|            | Front-Ending                                                                                                                                                                                                                         | 2-68                                                        |

|            | Fault Tolerant Computing                                                                                                                                                                                                             | 2-70                                                        |

|            | Architectural Projections and Conclusions                                                                                                                                                                                            | 2-74                                                        |

|            | CPU                                                                                                                                                                                                                                  | 2-74                                                        |

|            | System                                                                                                                                                                                                                               | 2-76                                                        |

|            | Risks                                                                                                                                                                                                                                | 2-77                                                        |

|            | BENCHMARK DEFINITION/PROJECT MEASUREMENT CRITE  Analysis of Flow Model Programs Procedure Observations of Codes Explicit Code Implicit Code' Relationship of 3-D to 2-D  Measurement Results Evaluation Remarks Benchmark Definition | 3-1<br>3-2<br>3-3<br>3-3<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9 |

| SECTION 4. | CDC DESIGN OBJECTIVES DOCUMENT  Introduction Definition References Planning Justification Interdependent DO and DR Documents                                                                                                         | 4-1<br>4-1<br>4-2<br>4-2<br>4-2                             |

|            | Technical<br>Standards                                                                                                                                                                                                               | 4-3<br>4-3                                                  |

| anament 5  | Objectives Functional and Performance Objectives Compatibility Objectives Acquisition Cost Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-4<br>4-4<br>4-8<br>4-8                                                                                                                                                                                                                                                                       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION 5. | PRELIMINARY SYSTEM DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                |

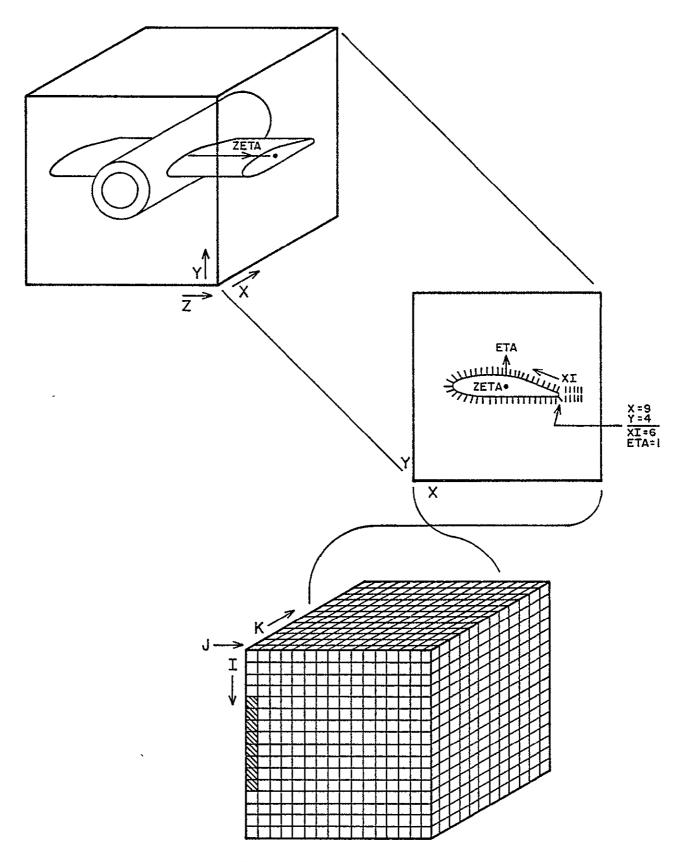

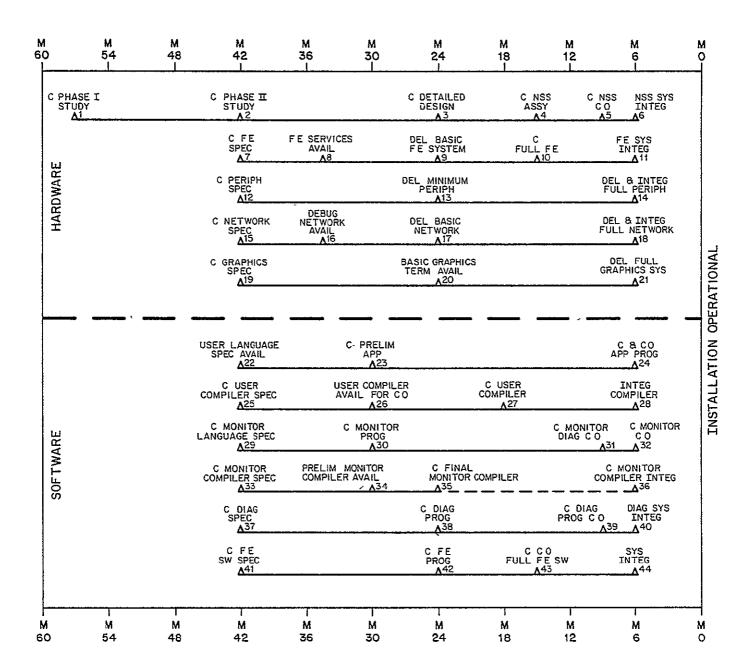

| SECTION 5. | PRELIMINARY SYSTEM DESIGN  Flow Field Simulation Model     Initial Conditions     The Solution     Solution Outline     Storage Implications     Storage Access for the Full Implicit Code The System The Navier-Stokes Solver     Overview of the NSS Hardware     The Units         The Scalar Unit         The Wap Unit         The Map Unit         The Swap Unit         Memory Interchange Unit         NSS Memory         Memory Addressing         NSS I/O System Interface Specifications         Electronic         Logical         User         Programming Considerations Functional Description         System Balance         System Integrity         Conclusions on Integrity         On-Line Maintenance         Expected Failure Rates         Evaluation Against Benchmark         Implicit Code: Left-Hand Side (LHS) Risk Analysis         Hardware Risks         Software Risks         Schedule NASF Schedule | 5-1<br>5-6<br>5-7<br>5-9<br>5-11<br>5-20<br>5-26<br>5-29<br>5-32<br>5-32<br>5-34<br>5-40<br>5-43<br>5-50<br>5-52<br>5-53<br>5-55<br>5-55<br>5-61<br>5-61<br>5-61<br>5-61<br>5-62<br>5-71<br>5-73<br>5-74<br>5-75<br>5-75<br>5-76<br>5-79<br>5-171<br>5-171<br>5-171<br>5-174<br>5-174<br>5-175 |

|            | Costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-182                                                                                                                                                                                                                                                                                          |

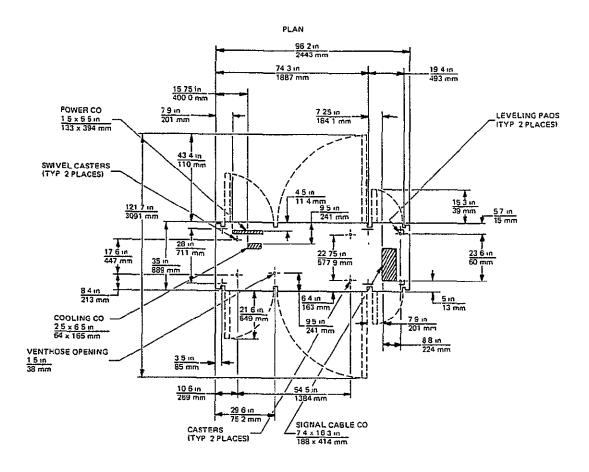

# SECTION 6. PRELIMINARY SITE REQUIREMENTS

| Introduction -                                          | 6-1    |

|---------------------------------------------------------|--------|

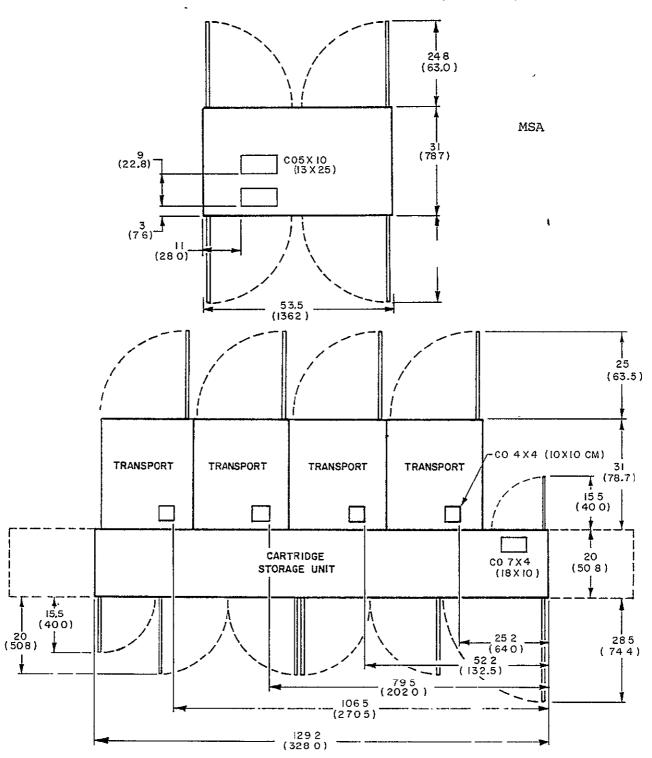

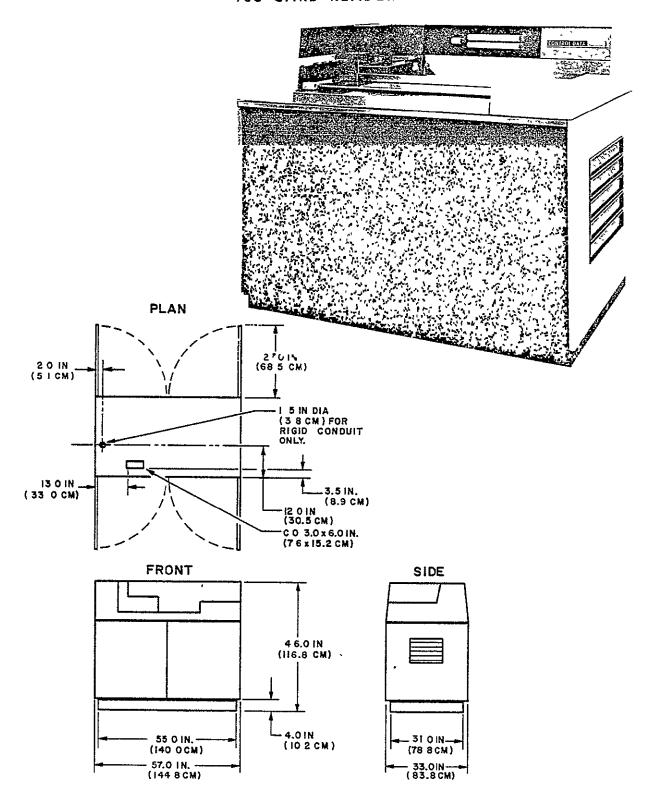

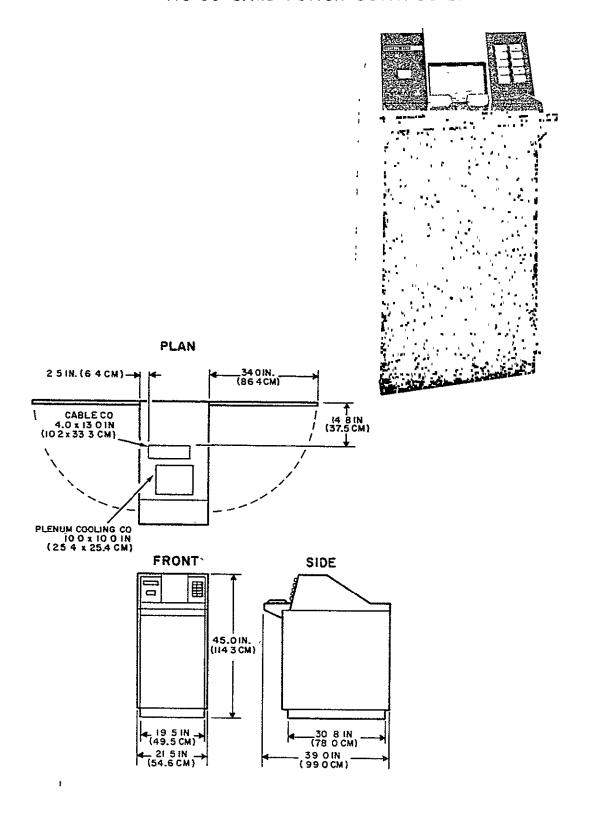

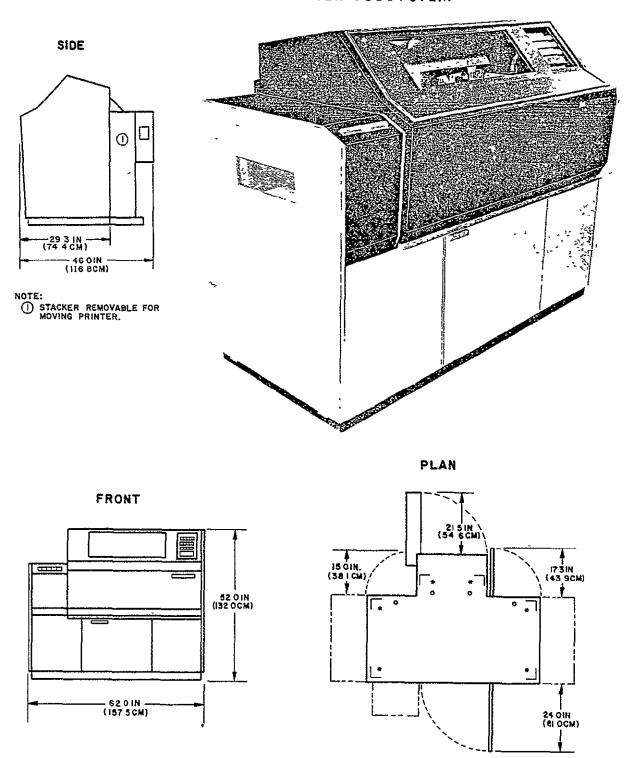

| System Description                                      | 6-1    |

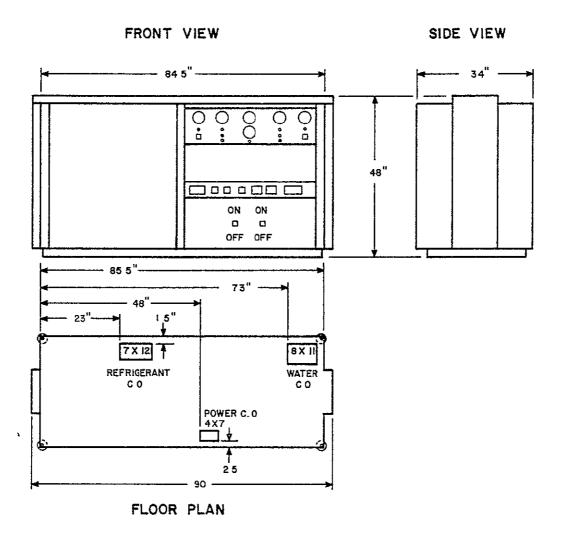

| Central Processor                                       | 6-2    |

| Storage Subsystems                                      | 6-2    |

| Front-End Systems                                       | 6-3    |

| Motor-Generators                                        | 6-6    |

| Refrigeration System                                    | 6-6    |

| Configuration                                           | 6-7    |

| Accommodation Requirements                              | 6-7    |

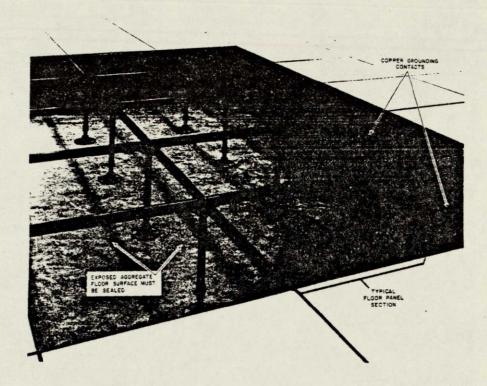

| Floors                                                  | 6-8    |

| Floor Clearance                                         | 6-8    |

| Raised Floor Requirements                               | 6-9    |

| Ceiling                                                 | 6-9    |

| Equipment Clearances                                    | 6-9    |

| Lighting                                                | 6-10   |

| Environmental                                           | 6-10   |

| Dew Point                                               | 6-11   |

| Temperature and Humidity                                | 6-11   |

| Additional Information                                  | 6-12   |

| Power and Cooling Requirements                          | 6 - 12 |

| Electrical Requirements                                 | 6-12   |

| Main Supply Variations                                  | 6-12   |

| Power Factors                                           | 6-13   |

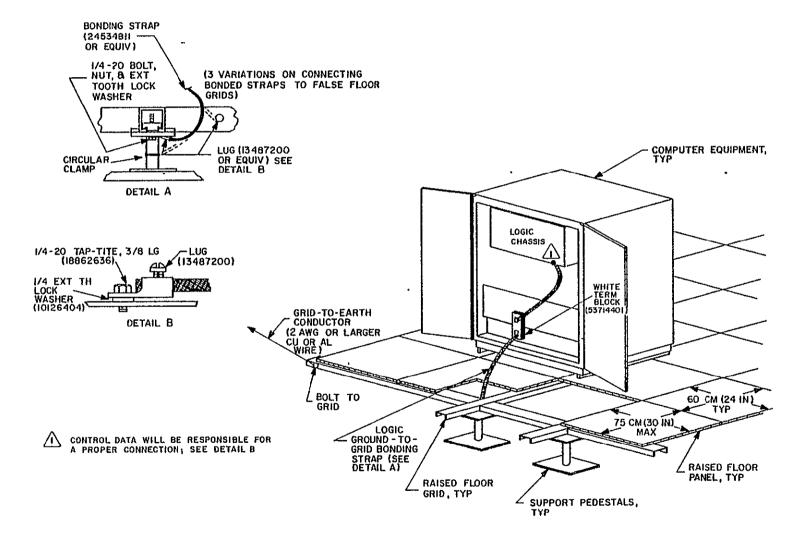

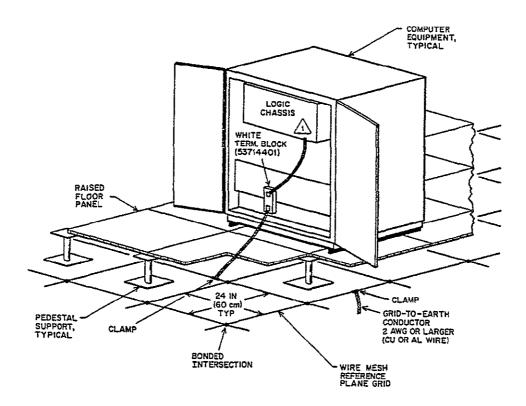

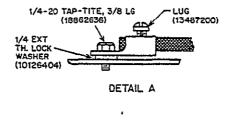

| Grounding Requirements                                  | 6-14   |

| Power Distribution                                      | 6-16   |

| Equipment Cooling Requirements                          | 6-18   |

| Refrigerant-Cooled Equipment                            | 6-18   |

| Air-Cooled Equipment                                    | 6-21   |

| Heat Dissipation                                        | 6-22   |

| Ventilation, Cooling, and Air Conditioning Requirements | 6-22   |

| Special Requirements/Considerations      | 6-23 |

|------------------------------------------|------|

| Cable Layout and Routing                 | 6-23 |

| EMC Grid                                 | 6-23 |

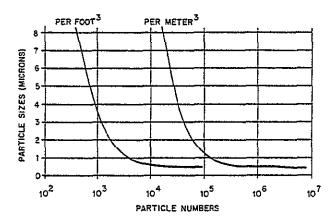

| Recording Media Storage Room             | 6-24 |

| Equipment Room                           | 6-25 |

| Refrigerant Safety Precautions           | 6-25 |

| Hazards of Refrigerant Gas               | 6-26 |

| Calculation of Lethal Refrigerant Levels | 6-26 |

| Pressure Venting Network                 | 6-27 |

| Water Alarm Indicator                    | 6-28 |

| Site Security                            | 6-28 |

| Permissible Radar/Radio Field Strength   | 6-29 |

| Equipment-to-Ground Resistance           | 6-29 |

| Power System (Mains) Neutral Isolation   | 6-29 |

| Raised Floor Panel Surface Covering      | 6-30 |

| Operations and Support Requirements      | 6-30 |

| Operators                                | 6-32 |

| Customer Engineers                       | 6-32 |

| System Programmers                       | 6-32 |

| System Analysts                          | 6-32 |

| Supervisory Personnel                    | 6-33 |

| Supplies                                 | 6-33 |

| Software Lease                           | 6-33 |

| Replacement Parts                        | 6-34 |

| Utilities                                | 6-34 |

| Expenses Not Estimated                   | 6-34 |

#### SECTION 1

#### ELECTRONIC TECHNOLOGY SURVEY AND PROJECTIONS

#### INTRODUCTION

The electronic computer industry, in over 30 years of existence, has enjoyed phenomenal success and growth. Growth has been in virtually all aspects including economics, applications, and technology. The raw computer power has also increased almost beyond comprehension from Eniac to today's supercomputers. As computers become faster and more powerful to meet today's needs and as new and more complex applications are introduced, greater computing power will be required that will lead to tomorrow's supercomputer. The state of the art in designing and building computer components will be a significant factor in the development of these computers.

The early advances in performance were largely attributable to component technology changes and improvements. Vacuum tubes, transistors, and integrated circuits contributed tremendous advances in computer speeds. However, today's computer technology is approaching some, very real limits to such things as reduced component size, faster switching times, and greater component density as primary means of achieving additional computing power.

A problem such as computational aerodynamics challenges computer designers to search for whatever techniques may be found to match the machine to the problem, and to the extent possible, the problem to the machine. The Preliminary Study for a Numerical Aerodynamic Simulation Facility is a project to propose methods to accomplish these matches. This survey and report on electronic technology is the part of this study intended to provide a technology platform on which to base computer architectures proposed for a computational aerodynamics design facility.

#### OBJECTIVE

The objective of this survey is to provide a summary and evaluation of the current state of computer component technologies and projections as to the future of these technologies for possible application to the computational aerodynamics design facility.

#### SCOPE

#### TECHNOLOGIES SURVEYED

A survey of all technologies, which may pertain to such a facility, is not possible because of limited resources nor is it prudent to investigate all, since some are well established and fairly stable. Those technologies which are relatively new and/or were deemed to have potential application in the proposed facility were investigated and are included in this report. They are as follows.

- Charge Coupled Devices (CCD)

- Magnetic Bubble Memories

- Electron Beam Addressed Memory (EBAM)

- Large Scale Integration (LSI) of Semiconductor Circuitry

- Josephson Devices

- Advanced Rotating Mass Storage

- High Speed Data Channels

- Advanced Test Equipment

#### EXTENT OF INVESTIGATION

To the extent possible consistent with time and funds available, the above technologies were investigated to determine the following.

- Relative merit

- Limitations

- Cost

- Risks

- Operational implications

## **METHODOLOGY**

#### SOURCES OF DATA

The amount, types, and sources of data vary considerably by technology and depend on many factors such as age, relative interest to the industry, and the degree to which Control Data has independently pursued the technology. In general, the following sources were used, as applicable, for each technology.

- Control Data project files

- Technical journals, bulletins, and periodicals

- Vendor and industry surveys

- Specialists within Control Data

#### APPROACH USED

The subject technologies were each placed in one of three categories relative to the type and degree of investigation to be applied. The categories and the approach used for each are as follows

• New technologies which have been actively investigated by Control Data for considerable time, these are CCDs, bubble memories, EBAM, and LSI. For this category, a thorough, although nonexhaustive, utilization of all four of the above sources was made. Material was summarized and evaluated by specialists who have been directly involved with a given technology.

- New technologies which are not directly pursued by Control Data; these include Josephson devices and TELD/MESFET portions of LSI. Sources of information for this category were publications and vendor contacts; data was extracted and evaluated by a specialist in a related field.

- Technologies which are not new in themselves but are evolutions of prior art, these are high-speed data channels, advanced rotating mass storage devices, and advanced test equipment. The first two of these technologies were each assigned to a specialist to obtain an assessment of the evolution to date and to project further evolution into the 1980's. Advanced test equipment is an exception in that it is ancillary to the system, yet is very crucial to future high performance devices. Test equipment specialists within Control Data were consulted, and some information was gathered from producers of test equipment.

#### **OBSERVATIONS**

#### CHARGE COUPLED DEVICES

# General Description

Charge coupled device (CCD) memories have been available for over 2 years. Development has progressed to a point where CCDs warrant serious consideration in a storage hierarchy. They are presently available in 16-kbit devices with 65-kbit samples just becoming available. The expectation of 256-kbit chips by the early 1980's is high.

The CCD is a metal-oxide semiconductor (MOS) device. The CCD cell is a MOS capacitor, and a shift register is composed of a series of these capacitors. Data is stored in a cell as the presence or absence of a charge and is moved through the shift register by the application of clock pulses to overlying clock lines.

The manufacturing process is N-channel MOS (NMOS) technology, but for the storage cell, the process is simplified by three factors.

- No metal/oxide contacts

- No diffusions (for source or drain)

#### No metal lines

The peripheral circuitry, however, is normal NMOS technology.

### Relative Merits

Because CCD technology is relatively new and several semiconductor manufacturers are engaged in it, the rapidly increasing user interest and application should cause some fairly rapid advances. Since CCD manufacturing processes are similar to those used for MOS microprocessors and random access memories (RAMs), CCD technology should get impetus from these markets. By the early 1980's, an 18-Gbit memory appears a reasonable expectation. It should operate at a rate better than 1 Gbit/s. Access time is anticipated to be 1 to 2 ms.

Assuming a normal technology improvement pattern for CCDs, the availability of a 256-kbit device by 1980 seems likely. Such a device would make feasible a storage system with the following characteristics. The failure rate projections are based on experience with, and history of, MOS circuits in general since a CCD is an MOS device. Experience with CCDs may reveal different failure mechanisms, but this is not expected to cause a significant difference in overall failure rate.

Capacity 1.8 x 10<sup>10</sup> bits, solid-state, volatile, refresh required

Physical size 1.6 to 2.1 m<sup>3</sup>, dependent on type of packaging and cooling

Power 43 kW, operating

14 kW, standby

Data rate 1.6 x 10 bits per second

Access time 2 ms, worst-case

1 ms, average

Chip 256 kbit, dynamic MOS

1-5

Failure rate 5.8 failure's/month, no SECDED 0.6 failures/month, with SECDED

The size of the basic CCD building block, that is, the chip or integrated circuit, permits flexibility in configuring a memory system. Such a memory can range from bit-serial to many bits in parallel. This also allows increasing total bandwidth of the memory by paralleling bits.

# Limitations

Perhaps one of the biggest drawbacks to utilization of the CCD in a storage system is the dynamic nature of the device. That is, the data which is stored as a charge in a MOS capacitor must be periodically refreshed or the charge dissipates and the data integrity is lost. Typically, refresh is accomplished by cycling the CCD memory at some minimum rate while it is not being accessed, increasing the clock to normal rate for data access. Implemented in this manner, refresh has no effect on data transfer rate after access has been accomplished but adds to the total memory access time analogous to rotational latency in disk storage access. This degrades overall performance somewhat, although proper design can minimize the impact. In addition, the CCD memory is volatile, that is, it loses all data on loss of power unless a back-up power source, such as battery, is provided. Fortunately, the low standby power requirements of the CCDs (about 1  $\mu$ W/bit expected) eases this problem.

The organization of CCDs, at least at present, is a limitation, although to a moderate degree. In order to achieve optimum performance from this type memory, data block size is highly dependent on chip organization. This requires matching system design (block size) to chip organization. Unfortunately, vendors today have little, if any, commonality in chip organization, and it seems that no standard is emerging.

Although CCD technology is relatively new, this can be a limitation since problems generally accompany new technology. It seems inevitable that system implementation of CCDs, in the near future at least, can expect growing pains as the technology matures.

#### Cost

Based on chip cost comparisons, a CCD memory using the 65-kbit devices available today would have an estimated one-third cost, on a per bit basis, versus using 16-kbit devices. Likewise, with the introduction of the 256-kbit chip, expected in the early 1980's, the system cost should have the same ratio when compared to that using the 65-kbit devices.

#### Risks

Because CCD technology is a phase of MOS technology which is relatively well-established, risks are not as great as with a totally new technology. Some potential risks, although not very probable, are in the category of less-than-normal development relative to semiconductor development in general. The above projections of cost, density, data rates, and so on, are based on what have been normal trends in the semiconductor industry. If for some reason CCDs receive less attention, these goals may not be realized.

# Operational Implications

CCD memory is a volatile storage media requiring refresh to maintain data integrity. System implementation must take this into account. For nonvolatile storage, the system design would have to provide auxiliary power for emergency power failure as well as for any normal power-down.

Considering the above characteristics, CCD memory could provide a medium to large storage function. Cost per bit is a limitation on the large-scale end where CCD cannot compete with disks. Speed and access time are limitations on the small-scale end where more suitable RAMs are available. CCDs fall in the gap between high-speed RAM and disk storage, making it a candidate for intermediate or backing storage for a high-speed computational engine.

# MAGNETIC BUBBLE DEVICES General Description

Į

Magnetic bubble devices are a class of integrated circuits which use mobile magnetic domains for digital storage and processing. The basic binary element in such devices is a localized flux reversal in a thin flat film, the magnetic orientation of which is normal to the plane. This localized reversal, termed a bubble, is cylindrically shaped, energetically stable, and can be moved about in the medium with very little expenditure of energy.

Binary data is usually represented as a coded bubble/no bubble pattern. Controlled existence and motion of such patterns are generally provided by metallic overlay patterns deposited on top of the bubble medium. Typical control overlays include conductor patterns, soft magnetic elements, or combinations of both. In each case, the overlay serves to define storage cells and introduce local magnetic field gradients which manipulate the bubbles in coherent fashion. For example, the popular shift register bubble memory uses a rotating in-plane field to activate the magnetic overlay and current pulses to write, erase, and access various locations. Data output can be accomplished in a variety of ways, but magnetoresistors formed in the magnetic overlay layer are most generally used.

Bubble devices may be classified as either logic or memory depending on function. The logic devices utilize the magnetostatic interaction of bubbles to perform prescribed operations on the data. Despite the fact that a complete set of logic functions and even a bubble computer have been described in the literature, such devices tend to be slow and sensitive to their magnetic environment. It is probable that bubble logic will remain a laboratory curiosity in the foreseeable future.

Bubble memory devices are of three general types: conventional linear shift registers, two-dimensional shift registers (for example, lattice devices), and random access memories (RAMs). The RAMs have tended to be cumbersome and complicated, therefore impractical for use in conventional computer systems. They will not be considered here.

Lattice devices are a recent and potentially important development. A closely packed array of bubbles (reminiscent of a hexagonal crystal lattice) is manipulated en masse without a fine featured overlay. Mutual repulsion and a confining border are used to define the lattice positions, and very small bubbles can be used. Since no voids are permissible, information is stored either by varying the wall state of the bubbles or by using multiple layers, one to define the lattice and the second to carry the information. Generally, a single I/O port is provided. Access to individual rows or spots in the lattice is by block movement of the entire storage area. Although these devices offer great potential returns in cost and density, it is unlikely that a large, high-speed version will be available for many years. Several organizations (IBM, Rockwell, and Univac) are investigating them, but no fully functional lattice device has yet appeared in the literature.

This leaves the linear shift register memory as the only viable choice offered by today's bubble technology. The linear register can be organized in a variety of ways including the single serial chain, the serial-parallel-serial (major/minor loop), self-decoding, dynamic ordering, and hierarchical loops. Of these, the major/minor loop organization is the most popular and furthest developed. A complete set of functional elements has been described and the access time is reasonably fast. Additionally, the memory can be made flaw-tolerant quite easily (increasing yields), and the processing and wiring complexity is low.

The major/minor loop organization uses a number of small parallel shift registers (minor loops) for the storage of data. These surround and are interconnected by a primary shift register (major loop) which contains the read/write/erase apparatus. In operation, data is manipulated serially in the major loop but transferred to and from the minor loops in parallel, one bit into each loop. The advantage, of course, is that the access time becomes primarily a function of minor loop length rather than chip capacity. Defective loops can be ignored with the straightforward application of a PROM I/O map.

# Merits

The growing interest in magnetic bubbles may be traced to a number of features which, in some ways, combine the virtues of both magnetic and semiconductor devices. Bubbles are nonvolatile, radiation-resistant, fairly dense, and have solid-state reliability. Power consumption is low (a few  $\mu$ W/bit), and zero standby power is required. The storage medium is inherently digital, and as a result, phenomenally low hard error rates have been measured (10<sup>-14</sup>). Bubble memories also have reasonably fast access when compared with rotating storage, and the cost is projected to be low.

Compared with conventional integrated circuits, bubble devices are extremely simple structurally. The most common circuits require only two delineated layers and one precise mask alignment. Although fine-line lithography is required, there are no complex structures or diffusions, and the processing is free from ionic contamination problems. Further, the completed devices usually require very few external circuit connections. This kind of simplicity generally allows bubble circuits to be very dense, very high capacity, and eventually very low in cost.

Bubble memory technology has reached a point where a large, relatively high performance memory system can be envisioned in the next 2 to 3 years. Feasibility of all components and circuits has been demonstrated. Development of a memory system with the following characteristics is foreseeable, yet represents a significant effort.

Capacity 2 x 10<sup>10</sup> bits, solid-state, nonvolatile

Physical size 1.8 to 3.9 m<sup>3</sup>, dependent on type of packaging and cooling

Power 20 kW, maximum

12 kW, typical 0 kW, standby

Data rate 0.2 x 10 9 bits per second

Access time 5 ms, worst-case

0 to adjacent blocks, or if next block is queued

Chip  $10^6$  bits, major/minor loop, epitaxial garnet, 2- $\mu$ m bubbles

While bubble memories have existed for a relatively long time in the laboratory, they have not been implemented in large configurations sufficiently to enable reasonable error rate estimates. The above reference to 1 error in  $10^{14}$  bits represents laboratory measurement at the bubble device level. While it is an impressive figure, allowance should be made for other system contributions to errors. Nevertheless, bubble technology appears to have a potentially low error rate.

#### Limitations

On the other hand, bubbles have their limitations. Of the three candidates for auxiliary storage (CCDs, EBAMs, and bubbles), bubbles are clearly the slowest both in terms of access time and data rate. High-speed operation (\$\frac{1}{4}\$1 MHz) has been shown to be possible but not practical, given today's packaging and electronic limitations. Low cost, while promised, has never been demonstrated. Wafer production continues to be a costly manual operation and no progress will be made until manufacturing is scaled up. Bubbles also are vulnerable to temperature and magnetic fields but these-problems can be minimized by suitable package design.

The bubble medium itself is relatively complex and costly. The most suitable materials today are the rare earth-substituted iron garnets which are grown epitaxially on single crystal, nonmagnetic garnet substrates. The liquid phase epitaxy process requires high temperatures and very costly materials. Despite excellent control and high growth yields, this type of substrate will always be an order of magnitude more costly than silicon and is two orders of magnitude more costly today. The eventual successor to the garnet films may be the amorphous transitions metal films. These materials, prepared by conventional vacuum deposition, provide a suitable range of bubble properties and are extremely cheap. If the current problems with temperature sensitivity, repeatability, and dielectric integrity can be resolved, the entire technology will be revolutionized. For the present, however, these materials appear to be at least 5 years away.

# Status of Technology

Most skepticism about the viability of bubble technology can be answered by an examination of 1977 activity. More than 20 companies are engaged in bubble development and seven products have been announced. Earlier problems with chip yields, packaging, and reliability appear to be diminishing rapidly and at least 17 memory systems have been described in the literature. Most of these initial offerings have been conservative in performance, but they are serving to test customer acceptance and develop manufacturing techniques.

The laboratory activity is a better reflection of today's state of the art. Recent developments include one million bit chips, working devices at 1 MHz, single level (no mask registration) circuits, and wide temperature (-40°C to +120°C) operation. Smaller and smaller bubbles are becoming practical, particularly with electron beam and X-ray lithography, and cost projections are plummetting. A likely manufacturing cost for garnet film devices is 0.01 cent per bit by 1980.

Table 1-1 summarizes commercial bubble technology today and expectations for 1980. These estimates are based on interviews with bubble development groups and publications in the literature.

## Prognosis

It is obvious that bubble memories are a technical reality, and continuing progress in cost and performance is likely. In spite of this, bubbles have been slow to emerge from the laboratory and the acceptance in the computer industry has been limited. There are a number of reasons for this. First, and most important, a great uncertainty exists in cost. The bubble medium is very expensive and will remain so until production volumes are established. Further, the search for lower cost alternatives will continue at a relatively low profile until a production scale motivation exists. A second factor is performance. Most of the early memory products have been slow and fairly expensive. A favorable point on the cost/performance curve can be reached only with larger, faster chips. Other

TABLE 1-1. BUBBLE TECHNOLOGY TRENDS

| Bubble Medium          | 1977                                       | 1980                                       |

|------------------------|--------------------------------------------|--------------------------------------------|

| Material               | Garnets                                    | Garnets                                    |

| Bubble diameter        | 4 to 6 μm                                  | 1.5 to 3 μm                                |

| Chip Design            | 1977                                       | 1980                                       |

| Organization           | Serial,<br>Major/minor loop                | Major/minor loop                           |

| Fabrication technology | Optical, two-level                         | Optical, one-level                         |

| Chip density           | $1.5 \times 10^5$ bits per cm <sup>2</sup> | $1.5 \times 10^6$ bits per cm <sup>2</sup> |

| Chip capacity          | 10 <sup>5</sup> bits                       | 10 <sup>6</sup> bits                       |

| Shift rate             | 100 to 200 kHz                             | 100 to 500 kHz                             |

| Memory Systems         | 1977                                       | 1980                                       |

| Chips per module       | 1 to 16                                    | 1 to 16                                    |

| Average access time    | 1 to 4 ms                                  | 0.5 to 4 ms                                |

| Data rate/channel      | 50 to 150 kbits/s                          | 100 to 500 kbits/s                         |

| System capacity        | 10 <sup>5</sup> to 10 <sup>7</sup> bits    | 10 <sup>5</sup> to 10 <sup>9</sup> bits    |

| Operating temperature  | 0° to 50°C                                 | -40° to 120°C                              |

| Cost                   | 0.05 to 0.2 cent per bit                   | 0.01 to 0.05 cent per bit                  |

factors include the unavailability of integrated support electronics, lack of standardization and multiple sources, and of course, the lack of a product commitment by IBM. One should also note that bubbles are a dynamically moving technology. Many potential manufacturers have resisted settling upon a specific technical level since improvements are being announced almost routinely.

The future, nonetheless, seems fairly bright for magnetic bubbles. Almost certainly they will settle into that portion of the memory market that requires reliability and nonvolatility. The wide range of capacities, organizations, and performance also suggest that bubbles will have a more universal appeal than other media such as the electron-beam-addressed memory (EBAM) and fixed-head rotating storage. Only time will tell, however, whether this medium offers enough to displace existing technologies from their accepted applications.

# ELECTRON-BEAM-ADDRESSED MEMORY General Description

Electron-beam-addressed memory (EBAM) technology, per se, is not particularly new; it dates back to the 1950's as the Williams tube. This was a 5-inch CRT with a capacitance target and secondary emission detection. The results were relatively low signal levels, short storage lifetime, and little success. By the late 1960's, however, the semiconductor industry had developed MOS technology which was found to provide a good target with high gain for an EBAM.

The data pattern is a two-dimensional array on the target, and it is addressed by deflection of an electron beam. Data is stored as the presence or absence of a positive charge along narrow tracks on the MOS target. Charge storage is accomplished by the application of a bias voltage to the target while the beam is swept along the track during a write or erase cycle. In a subsequent read cycle, the beam is swept over the same track. Where a charge is present, a current is produced to a sense circuit. Where a charge is absent, no significant current is produced.

#### Relative Merits

EBAM technology has been drawing increasing interest, particularly from a technological viewpoint. It is a blend of several technical fields such as semiconductors, vacuum tubes, and high and low voltage electronics. If solutions or improvements for the problem areas

mentioned in the following Limitations paragraph can be found, EBAMs have considerable potential as on-line mass storage devices.

The MOS target is a simple semiconductor which provides high yield and low cost. It is also a relatively nonvolatile storage media. On loss of power, data integrity is retained for a few weeks, sufficiently retrievable. Therefore, this type of storage device would not require backup power, provided it had sufficient capability to shut down in an orderly manner upon loss of power.

Although the basic EBAM storage building block (the tube) has a rather large capacity, some configuration flexibility exists in multitube systems. This permits sharing of electronics for lower cost/bit and paralleling data bits for higher bandwidth, if necessary. However, EBAM transfer rates are about 10 Mbit per second or greater.

Additionally, like the CCD, an EBAM is a totally electronic device. It does not have some of the negative aspects inherent to most electromechanical devices.

#### Limitations

While functional EBAMs exist today, they are not yet sufficiently established for building an economical and reliable system. Cost-effective production must be proved, and quantitative data is needed on reliability, error rates, pattern sensitivity, and so on. In addition, to decrease costs while increasing capacity and performance, three significant problem areas must be addressed.

- The basic target uniformity and life must be improved. The electron beam is a source of radiation, and as such, causes damage to the target with time. In order to avoid this target fatigue, present EBAMs rotate or permute the data to average the usage of the target area.

- The electron optics will require upgrading to accomplish submicron beam diameters in production. The small beam will be necessary to achieve density goals. Also, a two-stage deflection system would have a deflector with a large number of lenslets requiring high-precision tooling.

The cathode needs further development. As the beam is made smaller to achieve greater density, the brightness must be increased. Conventional dispenser cathodes used at present could possibly reach 100 Mbits per tube. To go beyond 1 Gbits as projected, some other technique is required. Field emission cathodes have been applied in a few areas but would need effort to bring this technology to a practical level.

Tubes with a capacity greater than 10 Mbits and an access time better than 30  $\mu$ s have appeared in recent literature (reference 1-1) but have not as yet been demonstrated as viable system components. Future developments could conceivably produce tubes with 1-Gbit capacity by 1980.

Regarding electron beam memory technology in the context of the auxiliary backing storage considered as a requirement for a special computation facility, consider the following major characteristics of this memory technology in a general sense, in order to highlight the attributes of EBAM memories which can be expected to limit system reliability.

Precision high voltage power supplies seem to be an inherent necessity with this memory. The acceleration potential of the electron gun is commonly 10 kV, which must be accurate to about 1 volt. This stable voltage is needed because a spread of only 2 volts in electron energy will cause the beam to assume an elliptical cross-section, radially oriented, at the edges of the target area, since slower electrons are deflected further. The high voltage system, in addition to being physically large, must therefore be constructed of components whose aging characteristics are measured in hundreds of parts per million.

Voltages of a few hundred volts are required in the deflection system as well, with a precision of about 0.01 percent. Together, the relatively high voltages require a large distribution system and constitute a maintenance hazard and reliability limitation.

• The current memory mechanism is one of linear charge storage and linear beam displacement. There is no threshold for the basic memory element as there is for almost every other memory type.

For example, a semiconductor memory latch assumes a minimum energy state in its set (or reset) condition, and a fixed amount of energy must be supplied to reverse its state. A similar condition exists for a magnetic core or a magnetic bubble. An MOS memory cell may employ linear charge storage, but such storage occurs on one element of a transistor, a highly nonlinear device. CCD memories also use linear charge storage but with regularly interposed nonlinear sensing elements to requantize the charge pattern.

The use of a linear storage mechanism means that sneak or stray currents or areas of surface contamination can directly and cumulatively reduce the signal strength by reducing the amount of charge stored.

The lack of a photolithographically defined memory cell has been thought to be an inherent design advantage for EBAM memory, because memory fabrication is simplified and because the memory capacity could in principle be adjusted after assembly to provide an arbitrary signal to noise ratio or to compensate for isolated defects.

In practice, however, this simpler construction may result in more complex operation, since the cell definition is accomplished by beam deflection. Critical definition has thus been made a part of the memory device rather than part of the fabrication system.

It may also result in practice that the cells become defined on the silicon dioxide surface in an EBAM, by virtue of the fact that the cell boundaries are commonly written with charge to form a conducting background grid. There is some evidence that cell boundaries become difficult to redefine with the persistence of this grid.

- Perhaps the most attractive feature of EBAM technology is the promise of very fast access time. The basic beam deflection time should be no greater than 50 microseconds and might well be reducible to about 20. It seems unlikely that all of this promise will be realized inasmuch as the need for data permutation will likely persist. This can be a substantial access time penalty for a memory system which encounters high traffic. In such an application, using a common permute algorithm and sequential uniform reading, the access time penalty could grow to several hundred ms.

- The projected EBAM tube is a high vacuum envelope of large size (50 cm). The

maintenance of a vacuum seal, microphonics, and out-gassing of internal

surfaces are but some of the classic lifetime and reliability limiting character istics of vacuum tubes.

- While erosion of the electron source will limit EBAM tube lifetime, the more critical aging (and reliability) mechanism is target fatigue. At present fatigue rates and beam currents, constant use of a single spot would result in a lifetime of about 5 seconds. Thus, uniform usage must be sought through the permute mechanism. Since the effectiveness of this procedure depends on the program or usage patterns, fatigue is an obvious reliability factor.

The controlled damage of the EBAM target from electron beam radiation is similar to damage done to MOS wafers during electron-beam metal deposition in orthodox semiconductor processing. The fact that this processing problem has persisted in that industry for some time suggests that its understanding is less than complete. The integrity of the EBAM storage media directly depends on it being well understood or at least predictable.

- Because the electron beam can be deflected by stray electromagnetic fields, considerable shielding of the tubes is required. Such shielding may reduce EMI as a reliability consideration but at the expense of volumetric efficiency. The present tube/shield combination is roughly 0.007 m<sup>3</sup>, and the peripheral high voltage system and electronics add significantly to that volume.

- It has been known for some time that EBAM is not well suited for smaller capacity memories. This results from the physical bulk and cost of the elementary memory components. This factor in itself is not a handicap for the NASA-Ames application because a large backing store is needed  $(2 \times 10^{10})$  bits).

- A related performance factor is, however, crucial for this application. The physical bulk of a single tube and the press for reduced costs will drive an EBAM system in the direction of larger capacity tubes. For example, a memory constructed of 2 x 10<sup>4</sup> EBAM tubes (1 Mbit each) is physically too large for this application, whereas one made from 2 x 10<sup>4</sup> bubble or CCD chips is not. The data rate from each tube may not be easily adjustable, since there is only a single beam (a segmented target does not give multiple concurrent signals) and increased sweep rates may be difficult at higher densities where the basic signal energy is reduced. Therefore, one concludes that the ratio of data rate (per second in bits) to memory capacity is about 0.25 to 1.0 at present (Microbit model 700) and will diminish to 0.015 with future generation products (Microbit model 950). This ratio is the maximum attainable by a system, since it is the ratio characteristic of the single EBAM tube.

Corresponding ratios for bubble and CCD chips are approximately 1.56 and 7.8 at the 256-kbit chip capacity, and 0.4 and 2 at the 1-Mbit chip capacity. Volumetric considerations do not exclude the use of either of these chip sizes or types for the present application.

The desired ratio for the backing store, needed for most effective utilization of the complete computational system, is  $(1.6 \times 10^9)/(2 \times 10^{10}) = 0.08$ . Thus, both CCD and bubbles can be made to fit, but 128 Mbit EBAM tubes cannot unless they achieve a data rate of 10.24 Mbits per second. If the 950 tube is built at the 2 Mbit per second expected, a 2 x  $10^{10}$  bit system would have a maximum data rate of only 312 Mbit per second, and this would be attained by operating all of the 156 tubes in such a system simultaneously, so that queuing or permuting of idle tubes could not occur. The transfer time of an 8-kword block would then require 1.64 ms as opposed to 0.32 ms for either CCD or bubbles. The 1.32 ms difference is offset by any access time advantage enjoyed by EBAM, but an overall performance problem will remain.

#### Cost

At the present state of development, EBAM tubes and electronics have a fairly substantial cost. The tube technology needs refinement, and the electronics are complex because of requirements such as restoring and permuting of the data. Multitube systems share these electronics to keep cost/bit down; this dictates large memories. Cost today is on the order of 0.1 cent per bit for a memory of about 100 Mbits. If the problem areas discussed above can be properly resolved, EBAM costs should reach the 0.001 to 0.01 cent per bit range. This is perhaps several years away from production reality.

#### <u>Risks</u>

Control Data is actively pursuing, as well as following, EBAM technology. It appears that system commitment to EBAM at present would be risky from both a cost and technological viewpoint. However, by the time a design freeze is required on a project such as that considered in this study, the stability of this technology should be clearly identified.

# Operational Implications

EBAMs will perhaps always have very large capacity because the basic module, the tube, must have a large capacity, and the electronics must be shared by multiple tubes to make the system cost-effective; this means large capacity memories. On the other hand, EBAMs offer extremely fast access times for their size although not fast enough to replace RAMs.

However, target development to eliminate the problems associated with partially destructive read and fatigue is needed. Until this happens, system usage of an EBAM must take into account the time required to restore data after some number of reads and to permute data blocks periodically.

#### LARGE-SCALE INTEGRATION OF SEMICONDUCTOR CIRCUITRY

Large scale integration (LSI) has become a household phenomenon over the past 10 years with the realization of a host of consumer products such as hand calculators, TV games, various auto components, and so on. However, the high level of integration achieved in these areas (upwards of 1000 gates) was only possible because of the low speeds required (and consequent low power). High performance requirements, particularly as one strives for extremes of performance, cannot trade-off these factors, a priori. It is essential, however, to accomplish the logic functions, given the speed imperative, with as low power as possible because of the implicit limit on the scale of integration imposed by power dissipation. In addition, LSI for high performance has no fallout for broad-based consumer applications. This limits the technology as surely as power dissipation or photolithography in a market-driven economy. The resources needed to push the technology ahead are simply needed elsewhere.

Why bother to push for a larger scale of integration then, when contemplating a super processing engine? The Control Data CYBER 76, which is one current leader in the ability to push jobs out the door, gets by with discrete transistors. The STAR-100, which leads for another class of applications, uses SSI (roughly four gates per package). As one looks to the future, however, it is quite clear, both from experiment and analysis, that significant increases in performance and reliability can only be effected with a move to more integration. The reason, in simplistic terms, is that in order to achieve any significant reductions in propagation time through a logic chain, one must stay on the chip for as many steps as possible. A typical critical logic path (for example, a 48-bit add) requires that a signal pass through 11 to 15 stages of logic. In the case of SSI, the signal must leave the IC and traverse a length of inter-chip pc board wiring for each stage. The total delay is the sum of the gate delays plus the board delays, and the latter typically average 1 to 1.5 ns per run in controlled impedance systems. Thus, a practical limit with SSI, even with zero gate delay, is 15 to 20 ns. Of course, architectural alternatives, such as splitting the cycle or pipelining, can be invoked to accommodate this circuit technology problem. For a given architecture, however, LSI will be inherently faster.

It is also more reliable, and this can easily become the dominant consideration for very large ensembles of electronic parts. The reason for this superiority lies in the reduction of chip bonds, solder joints, and circuit real estate as one goes to a higher scale of integration. In addition, because the internal LSI gates do not have to drive external lines, they can run at lower power with reduced heat dissipation and emitter area per unit of logic.

# Storage Technology

Storage technology can be categorized as a specific case of LSI technology. Its unique structure allows storage to reflect the maximum component density offered by a respective technology.

To date, this technology has resulted in drastic modifications to traditional architectural as well as component selections. With the advent of dynamic RAMs, CCDs and fast registers, system bandwidth objectives have been dramatically increased.

Table 1-2 summarizes both present and projected storage capacity versus performance. 256x1 devices with access delays of less than 10 ns are currently in the final stages of development. A 4X-density improvement is on the drawing boards but with less than 10 ns access delay requirements, it will take time to effectively produce this product. High-performance RAMs (20 to 60 ns access time) are being competed for by several technologies. Dimensional-processing and power-scaling have produced NMOS static RAMs in the sub-60 ns range while conventional bipolar techniques offer 4K RAM candidates in the 20 to 40 ns range. There is reason to believe that during the next 4 to 6 years, product density will increase to 16 kbits.

With respect to moderate performance technology (100 to 200 ns), 16K dynamic RAMs are currently being offered by several suppliers. Most suppliers see visibility to 65K RAMs in the next few years, but methods of achieving the 4X-bit density are not well defined. Scaling, shrinking, and new photolithographic apparatus are deemed necessary to achieve this density as well as improved materials and circuit design techniques.

TABLE 1-2. STORAGE CAPACITY VERSUS SCHEDULE AND ACCESS DELAY

|               | Register<br>File | High<br>Performance<br>Storage | Moderate<br>Performance<br>Storage |

|---------------|------------------|--------------------------------|------------------------------------|

| Device access | 5 to 10 ns       | 20 to 60 ns                    | 100 to 200 ns                      |

| 1976 to 1978  | 256 x 1          | 4K x 1                         | 16K x 1                            |

| 1980 to 1982  | 256 x 4          | 16K x 1                        | 65K x 1                            |

If anything, storage objectives tend to be underestimated while circuit technologies tend to the bullish end of the scale. All agree, however, that 22.6 to 25.8 mm of area still defines producible boundaries to both circuitry and storage. Storage technology continues to more effectively utilize the allocated area. Because of this dynamic density growth, effective system designs must include sufficient addressing capacity while not requiring physical alterations.

# Limits of LSI

The following describes the limits of large-scale integration and the factors that set the limits.

In attempting to increase the scale of integration, semiconductor technologists come upon three major barriers: chip area, photolithography, and power dissipation. All of these barriers manifest themselves as economic hurdles; that is, costs escalate rapidly as one attempts to go beyond them. The slope is not infinite, however, so a group to whom parts cost is not compelling can venture well beyond these limits. If the Republic of Japan or the USSR, for example, were to decide that some aspect of the national honor or security were at stake, application of appropriate resources could be brought to bear and the barriers would yield.

#### Chip Area

Depending on the complexity of the process, there is an upper limit to chip area beyond which the yields drop dramatically. The probability of defects in the semiconductor substrate and epi compounds with that of process flaws due to dust or mishandling in the subsequent steps. Each is area related and the yield typically drops off sharply at areas of 25 to 35 mm<sup>2</sup> for MOS processes (6 or 7 steps) or 12 to 16 mm<sup>2</sup> for bipolar processes (12 to 14 steps). In silicon, there seems to be a skirt on the high end; that is, the probability does not drop to zero for large chips but has some residual value because the defects are not randomly distributed (reference 1-2). But the yield of these very large chips is quite uneconomical and unpredictable. Be that as it may, one reads of examples of good chips which are 10 to 20 mm on a side (for example, in large CCD imaging circuits). A second factor, which mitigates this effect somewhat, is that certain types of defect are ineffective unless they happen to fall in a critical area. The emitter and base regions in bipolar circuits and the gate region in MOS are the most sensitive. Flaws within the bonding pad areas, on the other hand, may be reasonably ignored.

#### Photolithography

The masking and etching steps comprise the most critical steps in most semiconductor processes. Two types of optical limits come into play here, the resolving power of the various photo/etching systems (how fine a line can be formed) and the field over which this resolution is operative. Both factors affect the sensitivity to misregistration, but for LSI, the second type is probably dominant. For example, a sensible yield of individual high speed transistors can be obtained from a photolithography system which is quite intolerable for LSI. Typical production systems today can readily produce  $3-\mu m$  line widths over a 4- or 5-mm field.

The diffraction limits are closer to 1.5  $\mu$ m, but lines of this size only occasionally survive the subsequent processes, primarily because of misregistration. These arts are favored by heavy research and development support by the semiconductor industry, so continual improvement can be expected. But optic systems are up against an increasingly difficult barrier as the diffraction limits are approached.

A number of laboratories are exploring alternative technologies. Reference 1-3 describes the general activity around the world. However, these developments will not become operational for LSI logic for 5 to 10 years.

## Power Dissipation

Power dissipation poses a somewhat different hurdle. If means can be provided to drain off the chip heat, reliable operating temperatures can be maintained. These means become cumbersome to some systems, however, if the power per circuit goes much above 5 W. Air-cooled systems are particularly difficult. The circuits must be spaced less densely, which can offset the speed advantage being sought. Even with well-engineered cooling, however, a high-power chip is less tolerant of flaws in the cooling path, such as bonding flaws or air gaps. This translates to a real but somewhat soft barrier to LSI circuit size. It means that, given an existent cooling system, a lower power technology can use a large scale of integration, or if the scale is fixed, a less elegant cooling system can be used.

# Reliability of LSI

Component failure rates of LSI technology product offerings are expected to maintain the impressive rates of their predecessors (0.1 to 0.05 failures/million hours). Process improvements which improve reliability will be essentially offset by increased complexity. Overall system reliability, however, will be improved significantly due to the total reduction in subassemblies of critical technology.

Current density will become a very critical parameter due to emphasis on die reduction and component shrinking, coupled with high performance requirements. Since current migration has been correlated to temperature (T<sup>4</sup> actually), emphasis on maintaining low operational temperatures, below 65,C to 70,C, is a must. Random defects associated with shallow emitter implantation/diffusion will be reflected as leakages and slow

degrading failures. Breakdown voltages will be lower due to component scaling (in all directions) and impedances will be higher, giving rise to increased concern over static charge.

Just as one begins to believe that all failure modes are known, a new one is uncovered, much like disease control in the medical field. So it will be with semiconductor reliability. As implantation techniques, E-beam mask generation, oxide isolation, and component scaling become commonplace, new failure mechanisms of concern may arise. It is difficult, if not impossible, to predict what they may be. It is probably safe, at this juncture, to assume that they will be related to temperature and dimensional scaling.

#### Some Comparative Technologies For The 1980's

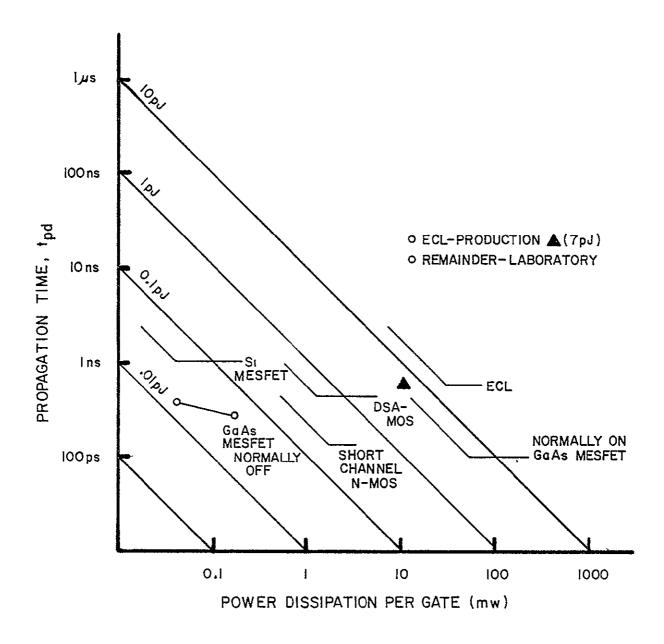

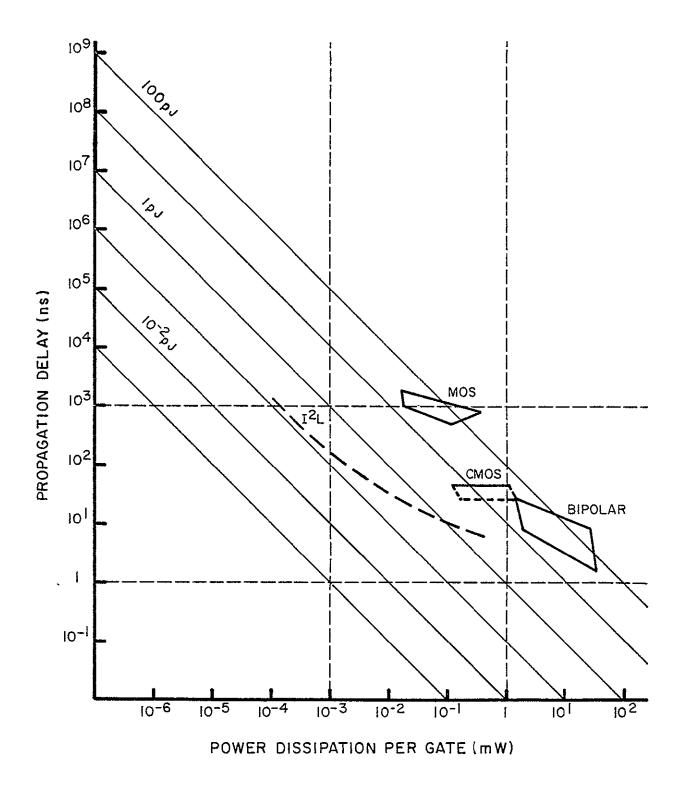

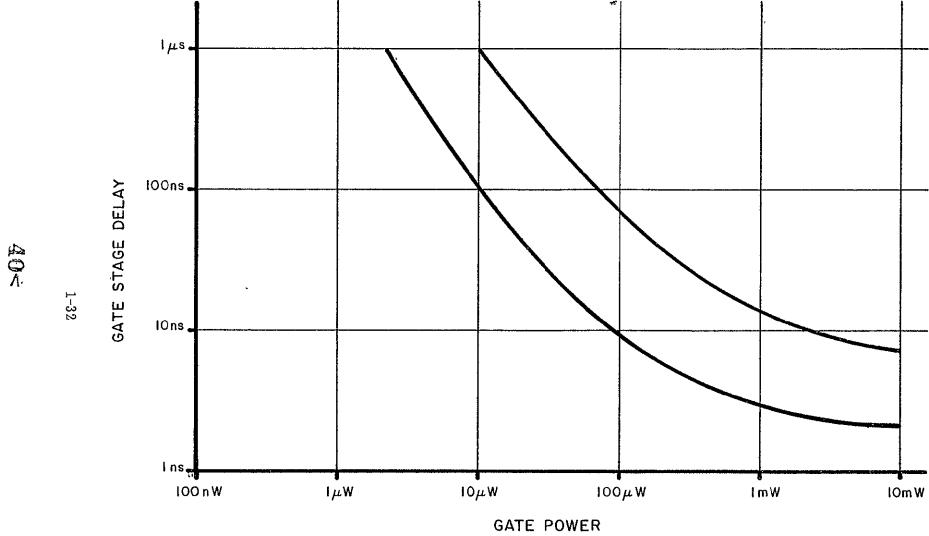

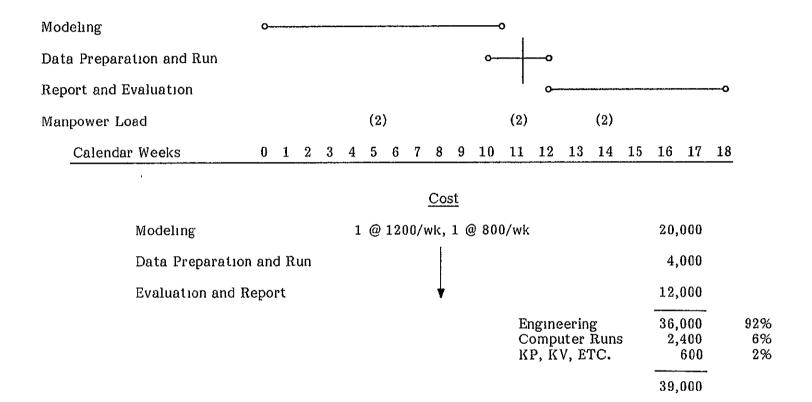

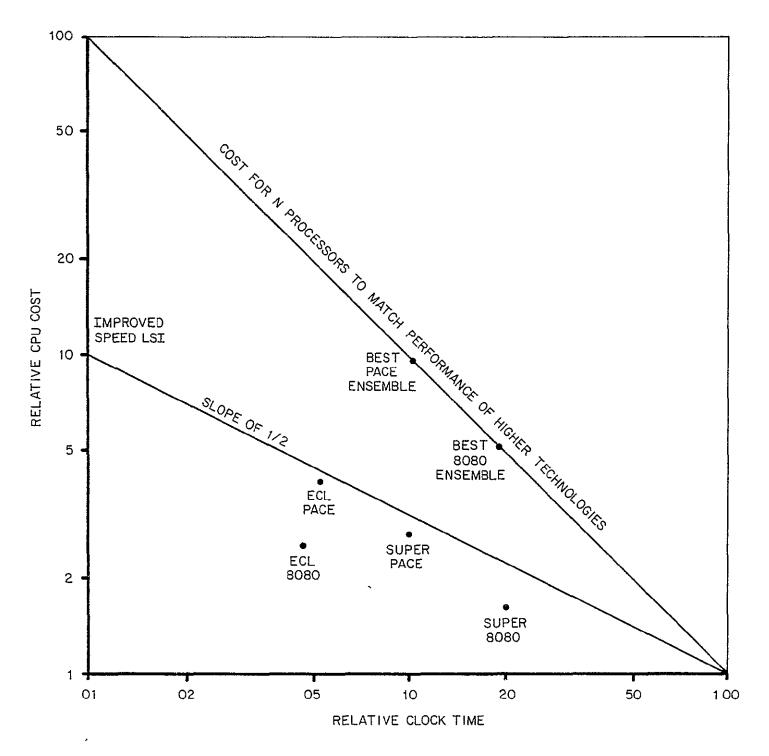

The lead time requirement for development of a large processor, such as this program contemplates, does not allow consideration of any circuit technology which is not now in virtually a production status. Prudence demands, therefore, that the plan implement the high performance technology which is being produced now. The pace of the semiconductor technology requires constant vigilance. However, a lot can happen between now and the hardware design freeze. Technologies which particularly bear watching are the efforts toward realizing high performance circuits in N-MOS, GaAs, and Josephson devices (cryogenics). It is also important to predict the rate and amount of improvement likely to come about in the classic bipolar technology being planned, since this is the most likely implementation circuitry.

#### Field-Effect Transistor (FET) Technologies

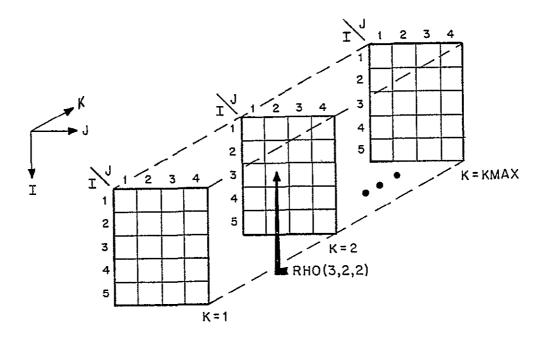

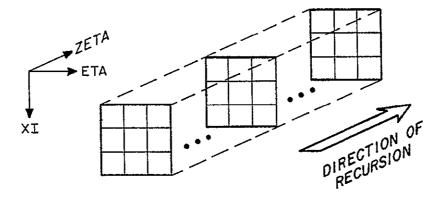

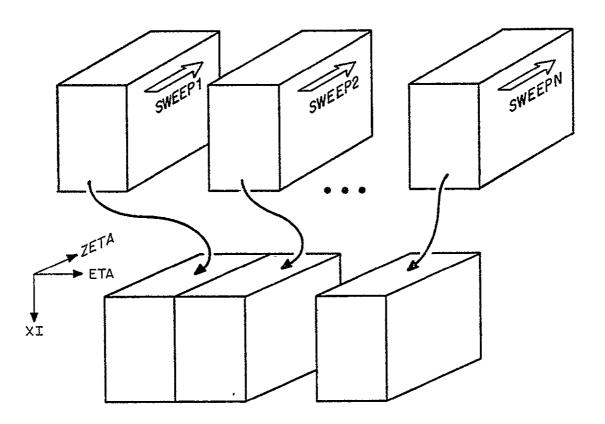

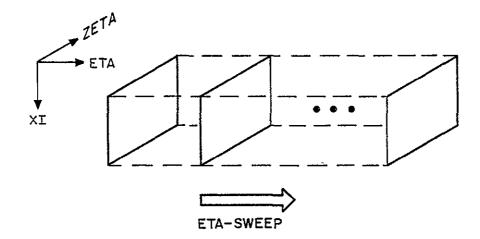

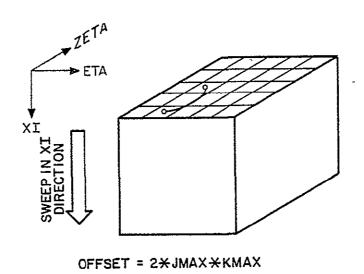

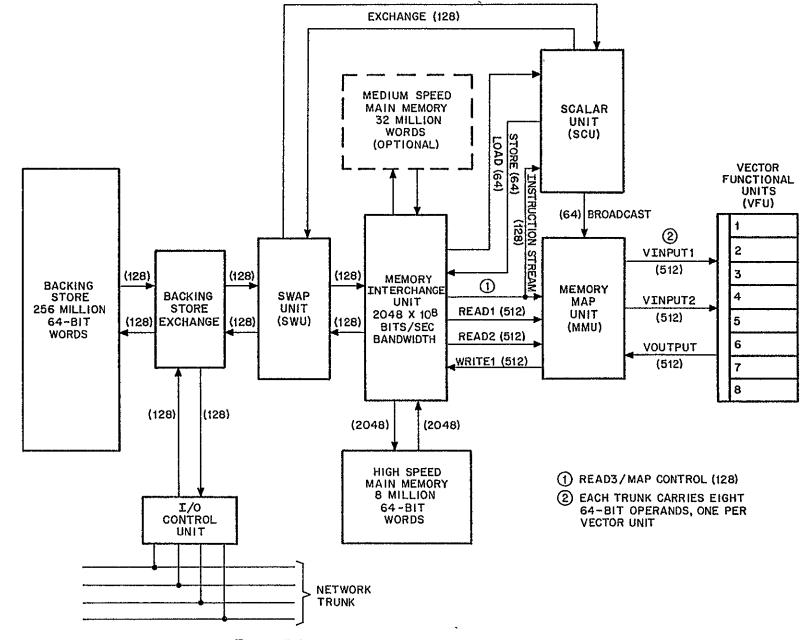

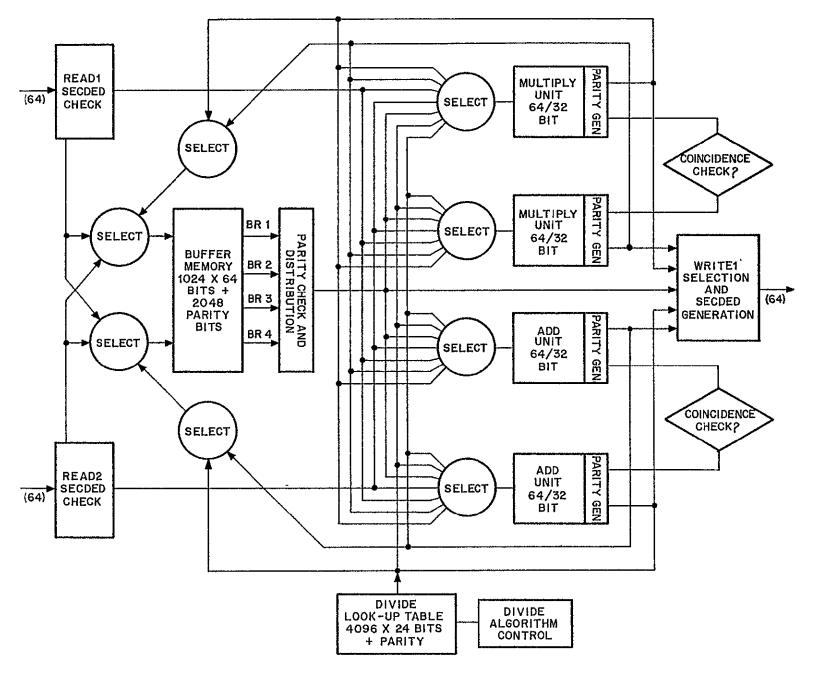

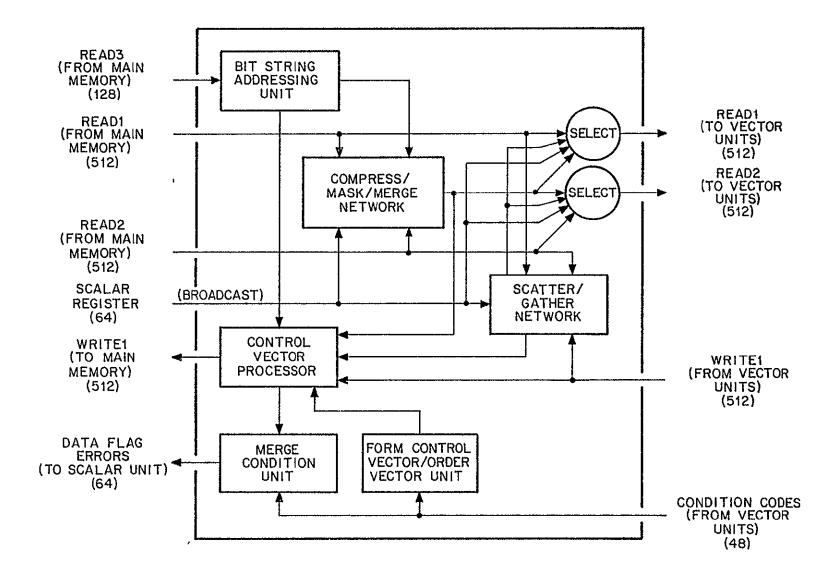

Included in the FET category are metal-oxide-silicon (MOS) as well as field-effect devices which do not use oxide to insulate the gate (MESFETs and JFETs). The most robust, well-developed, and likely-to-be-of-interest MOS technology is N-MOS. The most successful memory and microprocessor products are of this family, and a great deal of research is being invested in its continual improvement. One rarely hears of subnanosecond implementations, however, even though some such activity is known to exist.