# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

N79-19175

(NASA-CR-158370) SILICON ON CERAMIC N/9-19 PROCESS: SILICON SHEET GROWTH AND DEVICE DEVELOPMENT FOR THE LARGE-AREA SILICON SHEET AND CELL DEVELOPMENT TASKS OF THE LOW-COST Unclas SOLAR (Honeywell Corporate Material Sciences G3/31 16687 DOE/JPL 954356-78/4 Distribution Category UC-63

## SILICON ON CERAMIC PROCESS

Silicon Sheet Growth and Device Development for the Large-Area Silicon Sheet and Cell Development Tasks of the Low-Cost Solar Array Project

Quarterly Report No. 10

by

P. W. Chapman

J.D. Zook, J.D. Heaps, C. Pickering B.L. Grung, B. Koepke, and S.B. Schuldt

Period Covered: 9/30/78-12/31/78

Published 31 January 1979

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

The JPL Low-Cost Silicon Solar Array Project is sponsored by the U.S. Department of Energy and forms part of the Solar Photovoltaic Conversion Program to Initiate a major effort toward the development of low-cost solar arrays. This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, by agreement between NASA and DOE.

This report was prepared as an account of work sponsored by the United States Government. Neither the United States nor the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights.

## DOE/JPL 954356-78/4 Distribution Category UC-63

# SILICON ON CERAMIC PROCESS

1.

A REAL PROPERTY AND A REAL

Theorem Control

States.

Crassing and

1

Silicon Sheet Growth and Device Development for the Large-Area Silicon Sheet and Cell Development Tasks of the Low-Cost Solar Array Project

Quarterly Report No. 10

by

P. W. Chapman J.D. Zook, J.D. Heaps, C. Pickering B.L. Grung, B. Koepke, and S.B. Schuldt

Period Covered: 9/30/78-12/31/78

Published 31 January 1979

Honeywell Corporate Material Sciences Center 10701 Lyndale Ave. South Bloomington, Minnesota 55420

The JPL Low-Cost Silicon Solar Array Project is sponsored by the U.S. Department of Energy and forms part of the Solar Photovoltaic Conversion Program to Initiate a major effort toward the development of low-cost solar arrays. This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, by agreement between NASA and DOE.

## TABLE OF CONTENTS

| 아랫 그 바랍니다. 방학은 방학 가장 것이 하는 것이 가지 않는 것이 가지 않는 것이 없는 것이 없는 것이 없다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pag                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                        |

| INTR ODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                        |

| TECHNICAL DISCUSSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                                                                                                        |

| Substrate Development and Characterization<br>Substrate Evaluation<br>Substrate Mechanical Properties<br>Substrate Perforation Techniques<br>Sheet Silicon Growth<br>Dip-Coating Production<br>Experimental Dip Coater<br>Continuous Coating Process<br>Cell Fabrication and Development<br>Performance of SOC Cells<br>Performance of Single-Crystal Cells<br>Average Values<br>Short-Circuit Current-Density Values of Recent SOC Cells<br>Novel Device Development<br>Back Surface Field Metallization<br>Shape of Liquid - Solid Interface<br>Calculation and Observation of Meniscus Shape<br>Thermal Analysis of the Vertical Silicon-on-Ceramic Growth Process<br>Introduction<br>Heat Equations<br>Derivation of Equation (13)<br>Finite Difference Model<br>Interpretation<br>The Role of T <sub>1</sub> and y <sub>F</sub><br>Isotherm Shapes Within the Solid Silicon<br>Summary | $\begin{array}{c} 5\\ 5\\ 6\\ 8\\ 8\\ 10\\ 14\\ 21\\ 23\\ 23\\ 23\\ 23\\ 23\\ 23\\ 26\\ 27\\ 29\\ 31\\ 33\\ 34\\ 37\\ 37\\ 39\\ 43\\ 45\\ 48\end{array}$ |

| CONCLUSIONS AND RECOMMENDATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                                                                                                       |

| Conclusions<br>Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49<br>50                                                                                                                                                 |

| PROJECTION OF FUTURE ACTIVITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                                                                                                       |

| NEW TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52                                                                                                                                                       |

| PROGRAM STATUS UPDATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53                                                                                                                                                       |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                                                                                                                                                       |

羕.

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                          | Page       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1      | Photographs Showing (a) the Front and (b) the Back Side of a<br>McDanel MV-20 Perforated Mullite Substrate that was Dip Coated<br>with Silicon           | 7          |

| 2      | Photograph of New Dip-Coating Facility                                                                                                                   | 11         |

| 3      | Photograph of Heater and Crucible in New Dip Coater                                                                                                      | 11         |

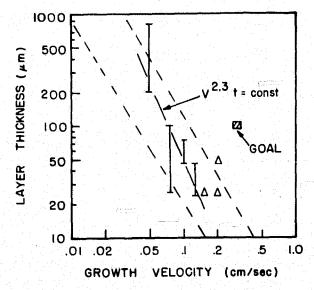

| 4      | SOC Layer Thickness Plotted as a Function of Pull Rate for Coat-<br>ings Produced on Unslotted Coors K Mod Substrates in the New<br>Dip-Coating Facility | 12         |

| 5      | Photograph of Upper Chamber of New Dipper Showing Cooling Shoes                                                                                          | 13         |

| 6      | Photograph of Substrate Dip Coated with Silicon at a Pull Rate of 0.2 cm/sec with Cooling Shoes in Place Near Front and Back Sides of Substrate          | 13         |

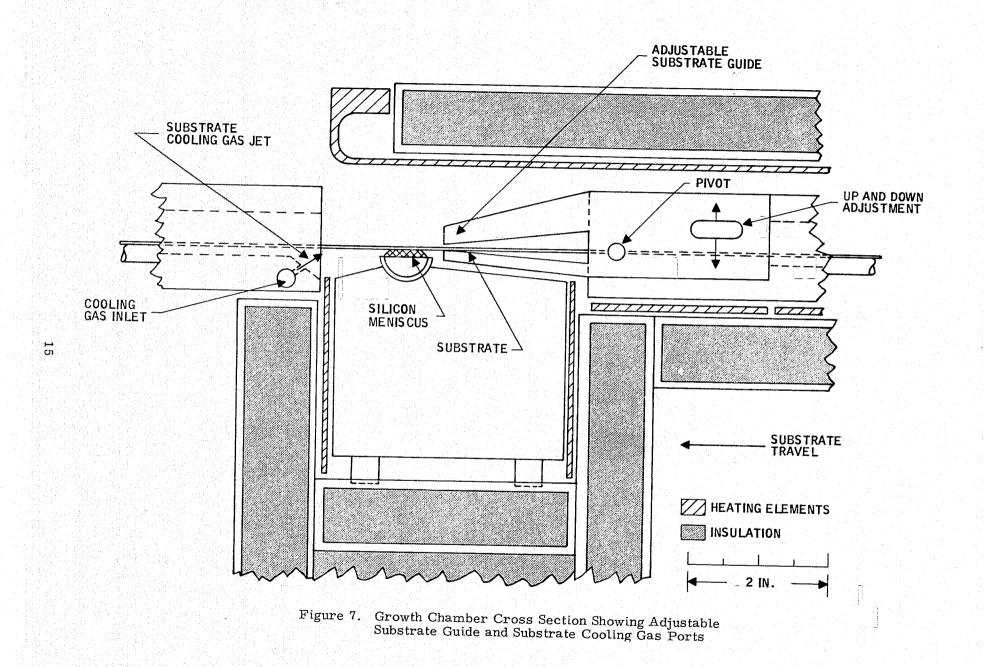

| 7      | Growth Chamber Cross Section Showing Adjustable Substrate Guide<br>and Substrate Cooling Gas Ports                                                       | 15         |

| 8      | Photograph of New Trough/Substrate Heater (Also Showing Quartz Crucible/Trough Piece)                                                                    | 16         |

| 9      | Growth Chamber Cross Section Showing Newly Designed Trough/<br>Substrate Heater                                                                          | 17         |

| 10     | Growth Chamber Cross Section Showing Shorter Upper Substrate<br>Heater                                                                                   | 18         |

| 11     | Photomicrograph of SCIM-Coated Layer Grown at 0.095 cm/sec                                                                                               | 20         |

| 12     | Photomicrograph of SCIM-Coated Layer Grown at 0.23 cm/sec                                                                                                | 20         |

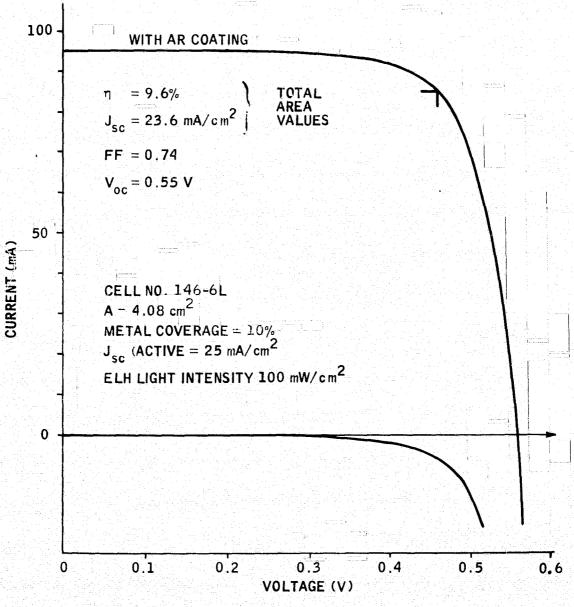

| 13     | Current-Voltage Characteristics of Cell No. 146-6L                                                                                                       | 24         |

| 14     | Shape of As-Grown SOC in the Vicinity of a Triple Junction                                                                                               | 30         |

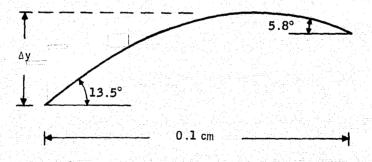

| 15     | Scale Representation of SOC Growth                                                                                                                       | 32         |

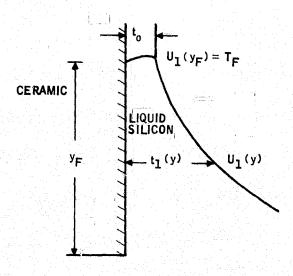

| 16     | Cross-Section View of SOC Growth                                                                                                                         | 33         |

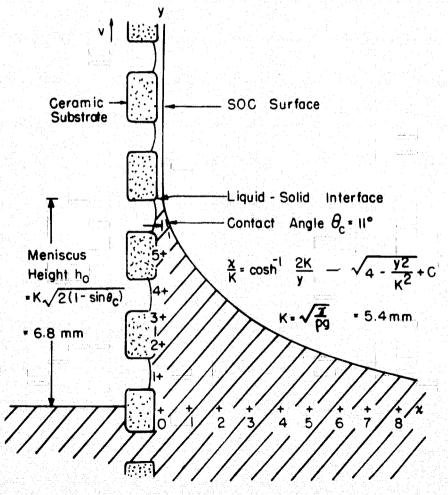

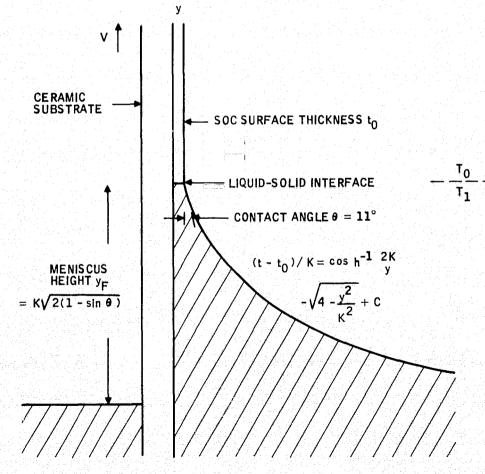

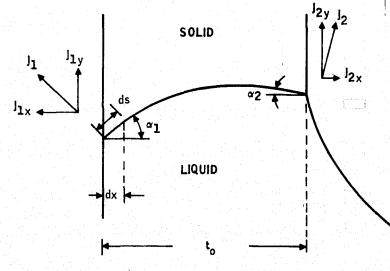

| 17     | Diagram of Meniscus Region                                                                                                                               | 38         |

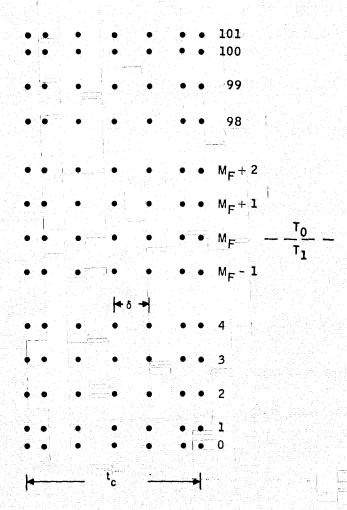

| 18     | Finite Difference Array for Calculating SOC Temperature Profile                                                                                          | <b>3</b> 8 |

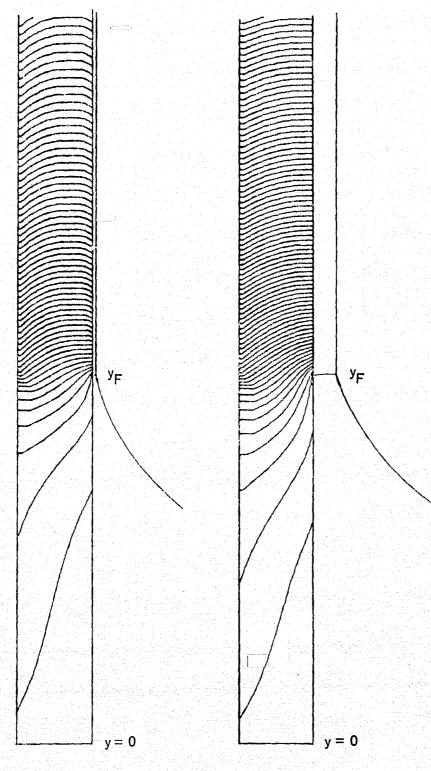

| 19     | Isotherms for T = $T_M$ - 5n, n = 1, 2,, by Two-Dimensional Interpolation                                                                                | 40         |

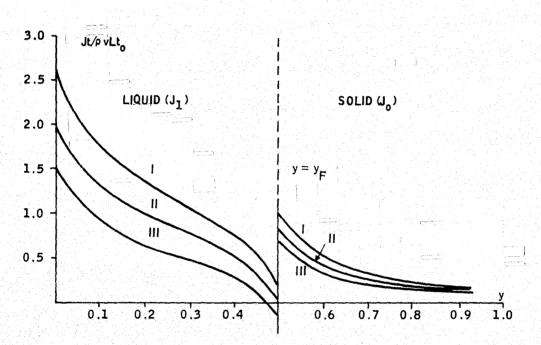

| 20     | Normalized Thermal Flux in Liquid and Solid Parts of the Silicon<br>Layer at Height y Above Melt Surface                                                 | 41         |

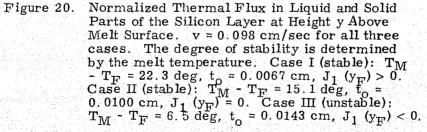

| 21     | Normalized $J_1$ (y <sub>F</sub> ) and Silicon Thickness as Functions of Melt Temperature                                                                | 42         |

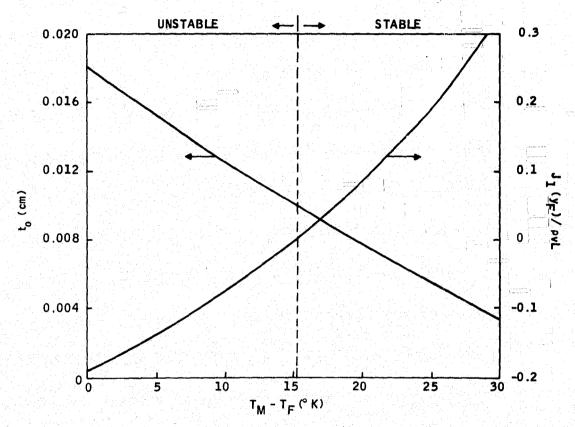

# LIST OF ILLUSTRATIONS (CONCLUDED)

| Figure |                                                                                                                            | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------|------|

| 22     | Normalized $\mathbf{J_1}$ (y <sub>F</sub> ) and Silicon Thickness as Functions of Pull Speed                               | 43   |

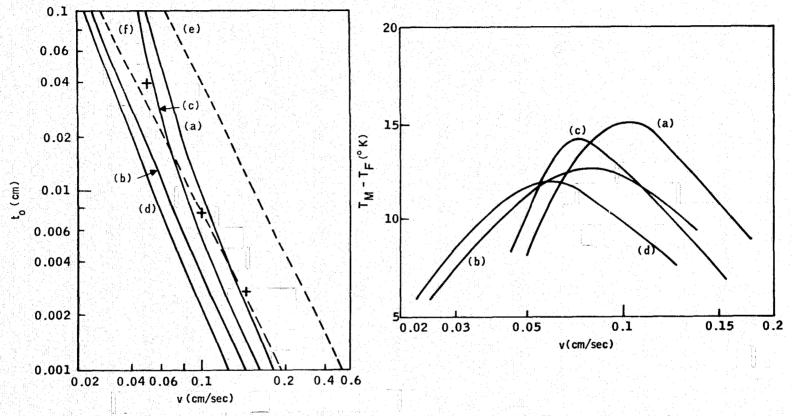

| 23     | Silicon Thickness and Melt Temperature as Functions of Pull Speed for $J_1$ (y <sub>F</sub> ) = 0 [limiting stable growth] | 44   |

| 24     | Analysis of Freezing Point Shape by Means of Heat Flux Components                                                          | 46   |

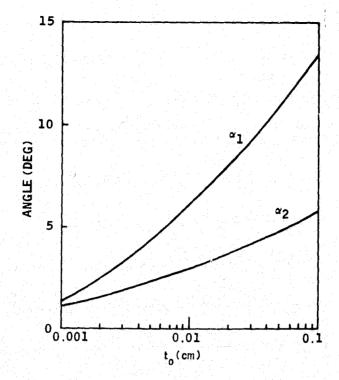

| 25     | Inclinations of Freezing Isotherm versus Silicon Thickness                                                                 | 47   |

| 26     | Updated Program Plan                                                                                                       | 53   |

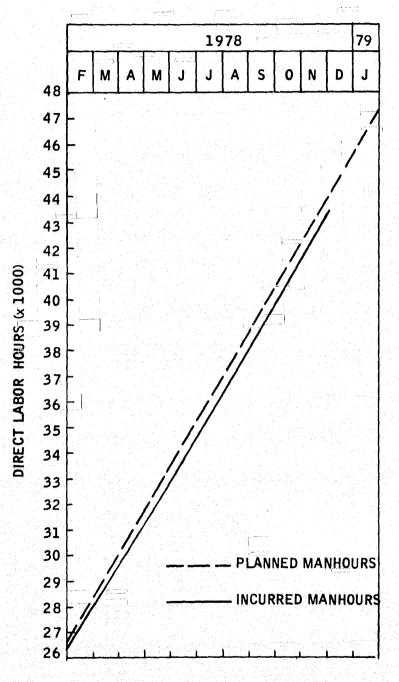

| 27     | Updated Program Labor Summary                                                                                              | 54   |

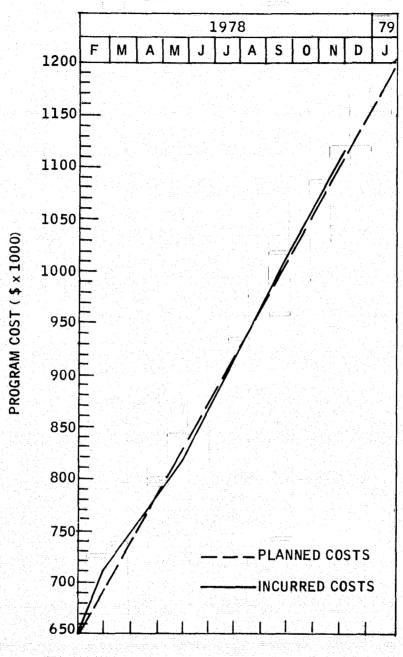

| 28     | Updated Program Cost Summary                                                                                               | 55   |

ν

# LIST OF TABLES

| Table                            |                                                                                                                                                                                                                                                                                                                                        | Page                                         |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1                                | Composition of Various Mullite Bodies                                                                                                                                                                                                                                                                                                  | 5                                            |

| 2                                | Fracture Strengths of Roll-Compacted Substrates                                                                                                                                                                                                                                                                                        | 6                                            |

| 3                                | Slotted SOC Cell Conversion Efficiency                                                                                                                                                                                                                                                                                                 | 21                                           |

| 4                                | Slotted SOC Cell Performance Parameters                                                                                                                                                                                                                                                                                                | 22                                           |

| 5                                | Single-Crystal Cell Performance Parameters                                                                                                                                                                                                                                                                                             | 25                                           |

| 6                                | Performance Parameter Average Values                                                                                                                                                                                                                                                                                                   | 25                                           |

| 7                                | Performance Parameters of 2X-Cells Without IOC Devices                                                                                                                                                                                                                                                                                 | 26                                           |

| 8                                | Performance Parameters of Non-Slotted SOC Cell (No. 126-2)                                                                                                                                                                                                                                                                             | 27                                           |

| 9                                | V <sub>oc</sub> in 16-Mil-Thick Wafer                                                                                                                                                                                                                                                                                                  | 28                                           |

| 10                               | V <sub>oc</sub> in 9-Mil-Thick Wafer                                                                                                                                                                                                                                                                                                   | 278                                          |

| 11                               | Nomenclature and Numerical Data                                                                                                                                                                                                                                                                                                        | 35                                           |

| 4<br>5<br>6<br>7<br>8<br>9<br>10 | Slotted SOC Cell Performance Parameters<br>Single-Crystal Cell Performance Parameters<br>Performance Parameter Average Values<br>Performance Parameters of 2X-Cells Without IOC Devices<br>Performance Parameters of Non-Slotted SOC Cell (No. 126-2)<br>V <sub>oc</sub> in 16-Mil-Thick Wafer<br>V <sub>oc</sub> in 9-Mil-Thick Wafer | 22<br>25<br>25<br>26<br>27<br>28<br>28<br>28 |

## SUMMARY

. 2 - 4

The objective of this research program is to investigate the technical and economic, feasibility of producing solar-cell-quality sheet silicon. We hope to do this by coating one surface of carbonized ceramic substrates with a thin layer of large-grain poly-crystalline silicon from the melt.

Beginning the middle of February 1978, we expanded our program to include activities funded by the Task VI Cell Development Group of the Low-Cost Solar Array (LSA) program at the Jet Propulsion Laboratory. This work is directed toward the solution of unique cell processing/design problems encountered within the silicon-on-ceramic (SOC) material due to its intimate contact with the ceramic substrate.

The Task VI work is contained within this report and is labeled appropriately.

During the quarter, we demonstrated significant progress in several areas:

- The continuous (SCIM or Silicon Coating by an Inverted Meniscus) coater succeeded in producing small-area coatings exhibiting unidirectional solidification and substantial grain size.

- The experimental dip coater was put into operation and succeeded in producing thick, > 500 µm, dendritic layers at coating speeds of 0.2 to 0.3 cm/sec.

- We succeeded in developing a "standard" procedure for producing totalarea SOC solar cells using slotted ceramic substrates. The best conversion efficiency performance to date is 9.6 percent (antireflectivecoated AM1) on a 4-cm<sup>2</sup> total-area cell.

Other results and accomplishments during the quarter can be summarized as follows:

- A standardized process was defined enabling us to fabricate reproducible dip-coated layers for solar-cell processing by the Honeywell Solid State Electronics Center and other JPL contractors.

- A substrate dye-checking procedure was initiated following a suggestion by D. Wirth and J. Sibold of Coors Porcelain Co. This new procedure has increased our yield of silicon-coated slotted substrates.

- Observations were made which seemed to indicate that the liquid solid interface tilts slightly away from the substrate contrary to what was originally thought.

- Remarkably consistent performance was achieved in Honeywell-fabricated SOC solar cells. The average total-area conversion efficiency on these cells was 8.3 (±0.8) percent [AR-coated, AM1].

- Three new mullite compositions were formulated by Coors for evaluation as slotted substrates.

- The fracture strengths of roll-compacted S1SI, J, K, and M Mod mullite substrates were measured.

- Several techniques for producing perforated mullite substrates were investigated by the Honeywell Ceramics Center. A technique for punching 1/8-inch-diameter holes in an MV-20 substrate produced a successful coating.

- Cooling shoes added to the experimental dip coater demonstrated that thick coatings can be achieved at higher pull speeds.

- Better thermal-gradient control at the solidification zone in the SCIM coater was obtained. This resulted in better quality small-area coatings. More-uniform temperature profiles at this critical point in the SCIM coater should produce more-uniform large-area coatings.

- Back Surface Field (BSF) investigations did not produce an effect in either single-crystal or SOC material.

- An analytical thermal analysis of the vertical SOC growth process was conducted. The model obtained suggests that the net lateral heat transfer in the neighborhood of the freezing front is into the ceramic as opposed to out from the free surface as originally thought.

#### INTRODUCTION

This research program began on 21 October 1975. Its purpose is to investigate the technical and economic feasibility of producing solar-cell-quality sheet silicon by coating inexpensive ceramic substrates with a thin layer of polycrystalline silicon. The coating methods to be developed are directed toward a minimum-cost process for producing solar cells with a terrestrial conversion efficiency of 12 percent or greater.

lety of ceramic materials have been dip coated with silicon. The investigation has shown that mullite substrates containing an excess of  $SiO_2$  best match the thermal expansion coefficient of silicon and hence produce the best SOC layers. With such substrates, smooth and uniform silicon layers 25 cm<sup>2</sup> in area have been achieved with single-crystal grains as large as 4 mm in width and several cm in length. Crystal length is limited by the length of the substrate. The thickness of the coating and the size of the crystalline grains are controlled by the temperature of the melt and the rate at which the substrate is withdrawn from the melt.

The solar-cell potential of this SOC sheet silicon is promising. To date, solar cells with areas from 1 to 10 cm<sup>2</sup> have been fabricated from material with an as-grown surface. Conversion efficiencies greater than 9 percent antireflection (AR) coated have been achieved without optimizing cell processing techniques. Such cells typically have open-circuit voltages and short-circuit current densities of 0.54 V and 23 mA/cm<sup>2</sup>, respectively.

The SOC solar cell is unique in that its total area is limited only by device design considerations. Because it is on an insulating substrate, special consideration must be given to electrical contact to the base region. One method which offers considerable promise is to place small slots in the substrate perpendicular to the crystalline growth direction and contact the base region by metallizing the silicon that is exposed through the slots on the back side of the substrate. Smooth, continuous coatings have been obtained on substrates which were slotted in the green state prior to high-temperature firing. The best slotted-cell results indicate a 9.6 percent conversion efficiency (AR-coated) on a  $4-\text{cm}^2$  (total area) cell. This cell was not optimized for device performance.

Development efforts are continuing in such areas as improvement in growth rate, reduction of progressive melt contamination, and optimization of electrical contacts to the base layer of the cell. The investigation has shown that mullite substrates, to a limited extent, dissolve in molten silicon. The impurities from the substrate are believed to adversely affect solar-cell conversion efficiency. A method for reducing substrate dissolution is to reduce the contact area the substrate makes with the silicon melt. Therefore, a silicon coating facility, referred to as SCIM or Silicon Coating by an Inverted Meniscus, has been constructed which is designed to coat large (10-cm x 100-cm) substrates in a continuous manner. It is expected that this facility will not only improve the growth rate, but also minimize the silicon melt contact with the substrate. This should reduce the rate at which the melt becomes contaminated. The facility will also permit a study of possible continued grain growth by accommodating the use of longer substrates. It should also reveal problems that are likely to be encountered in a scaleup process. This machine has succeeded in demonstrating coatings exhibiting unidirectional solidification (desirable and occurring in dip coating) but has yet to achieve continuous coating of a 100-cm-long substrate.

# SUBSTRATE DEVELOPMENT AND CHARACTERIZATION (B. Koepke and K. Jatavallabhula)

During the quarter, substrate activity was concentrated principally in the following three areas: 1) the evaluation of slotted substrates made from two new compositions (M and N modifications) manufactured by Coors Porcelain Co.; 2) characterization of the mechanical properties of these compositions at Honeywell's Corporate Material Sciences Center (CMSC), and 3) investigation of different techniques of perforating substrates carried out by the Honeywell Ceramics Center (HCC). These three areas are discussed below.

## Substrate Evaluation

Three new compositions were produced by Coors Porcelain Co. for substrate evaluation. These compositions, designated L, M, and N modifications, are listed in Table 1.  $^1$

|      |                                                           |       | Approximate Percent Oxide Composition |       |      |       |       |                   |                  | Ratio |                 |

|------|-----------------------------------------------------------|-------|---------------------------------------|-------|------|-------|-------|-------------------|------------------|-------|-----------------|

| Code | Material                                                  | Al2O3 | SiO2                                  | Fe2O3 | CaO  | MgO   | к20   | Na <sub>2</sub> O | TiO <sub>2</sub> | B202  | $Al_2O_3/SlO_2$ |

| 1A   | Std. S1SI Coors<br>composition                            | 57.6  | 38.9                                  | 0.62  | 0.13 | 0.25  | 0, 92 | 0.25              | 1, 12            | 0.00  | 1.48            |

| К    | 184 HRM<br>72. 5% S1SI<br>27. 5% SiO <sub>2</sub>         | 41.4  | 56.2                                  | 0.45  | 0.14 | 0, 18 | 0.66  | 0.18              | 0. 81            | 0.00  | 0. 74           |

| L    | 71.43% SISI<br>28.57% SiO <sub>2</sub>                    | 40.7  | 56.9                                  | 0, 45 | 0.14 | 0, 18 | 0.66  | 0.18              | 0, 79            | 0,00  | 0.715           |

| Μ    | 69% S1SI<br>31% SiO <sub>2</sub>                          | 39.2  | 58.4                                  | 0,43  | 0.14 | 0.17  | 0.64  | 0.17              | 0,77             | 0, 00 | 0.67            |

| N    | Calcined clay plus<br>SiO <sub>2</sub> (K-747 +<br>K-135) | 41.0  | 56.5                                  | 0, 89 | 0.02 | 0.04  | 0. 02 | 0.03              | 1.56             | 0,00  | 0. 73           |

Table 1. Composition of Various Mullite Bodies

Also included in Table 1 are the standard S1SI composition and the most recent batch of K Mod material. The thermal expansion coefficients (RT to 800°C) for the K, L, M, and N modifications were 3.98, 3.78, 4.31, and 3.64 x  $10^{-6}$  °C<sup>-1</sup>, respectively. The high

value for the M material was due to a higher than anticipated  $Al_2O_3/SiO_2$  ratio as detected by chemical analysis of the fired material.<sup>2</sup> The compositions listed in Table 1 are based on initial batch compositions rather than an analysis of fired bodies. The higher expansion of the M Mod material is corroborated by our observation that this material had a greater tendency to fracture during dip coating. The L Mod material had not been delivered to CMSC as of the end of the quarter and thus was not evaluated.

### Substrate Mechanical Properties

The fracture strengths of roll-compacted S1SI, J, K, and M Mod substrates were measured at room temperature in four-point bending and are listed in Table 2. The samples were nominally 0. 04-inch thick and 0. 12-inch wide and were tested over an inner and outer span of 0.5 and 1.25 inches, respectively. The crosshead speed was 0.01 inch/ minute.

| - | Code | Material        | Strength (kpsi) |

|---|------|-----------------|-----------------|

|   | А    | S1SI (155 RCM)  | $17.6 \pm 2.7$  |

|   | J    | J Mod (183 RCM) | 11.1 ± 1.5      |

|   | K    | K Mod (184 RCM) | 14.0±1.6        |

|   | м    | M Mod (218 RCM) | 13.1 ± 2.8      |

Table 2. Fracture Strengths of Roll-Compacted Substrates

The strength of the roll-compacted S1SI is slightly less than the cold-pressed and sintered material (21.7 kpsi as reported in Annual Report No. 3). Increasing the silica content appears to decrease the strength. This is expected because the higher  $SiO_2$  materials contain less mullite. The decrease is apparently not systematically related to the amount of  $SiO_2$  in the material.

#### Substrate Perforation Techniques

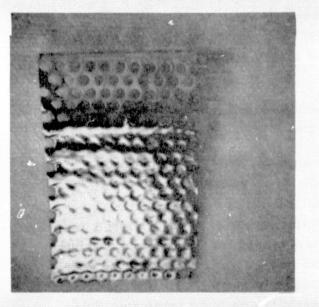

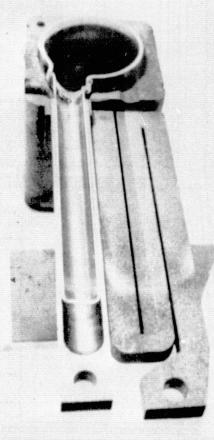

In work carried out at the Honeywell Ceramics Center, W. Harrison and G. Hendrickson have been examining different means to produce perforated mullite substrates. In one attempt, a slurry mix of pure alumina and pure silica was cast on a surface from which metal pins protruded in order to perforate the substrate during initial drying. Due to shrinkage, the cast bodies fractured during drying. In a second attempt, the slurry was cast around pins protruding from a sheet of silicone rubber. The body was removed from the pins and dried; it remained intact but the holes "healed" shut. In a third attempt, extrudable McDanel MV-20 mullite was rolled and then 1/8-inch-diameter holes were punched in the sheet on 1/4-inch centers by hand. This technique was successful and a number of perforated substrates were delivered to the Corporate Material Sciences Center for evaluation.

To date, one punched MV-20 substrate has been dip coaled with silicon. The following points were noted:

- The substrate coated uniformly but the coating contained depressions . corresponding to where the coating bridged a hole.

- The substrate did not crack.

# ORIGINAL PAGE IS OF POOR QUALITY

Many of the holes were filled with silicon.

Photographs of the coated MV-20 substrate are shown in Figure 1. The irregular nature of the surface is shown in the left-hand photograph. The back side of the substrate is shown in the right-hand photograph. Some holes that appear filled with silicon are indicated by arrows. Note that the holes appear filled but in all cases are only coated on the top and bottom with a thin layer of silicon. The mechanism for this behavior is uncertain and is under study. This phenomenon is observed with holes but not with slots. The difference may be due to dynamic effects occurring when the meniscus passes a hole or slot. When it passes a slot, it breaks on the back side but, in some cases, does not break over a hole.

(b)

Figure 1. Photographs Showing (a) the Front and (b) the Back Side of a McDanel MV-20 Perforated Mullite Substrate that was Dip Coated with Silicon. The substrate measures 1.75 x 1.75 x 0.070 inches. The holes are approximately 3/32-inch in diameter and are approximately 3/16-inch apart. Arrows indicate where the holes appeared filled with silicon.

SHEET SILICON GROWTH (J. D. Zook, J. D. Heaps, L. D. Nelson, D. J. Sauve, R. Hegel, and H. Burke)

## Dip-Coating Production

During the quarter, emphasis was placed on increasing the production output of dipcoated SOC material. There were two basic reasons for this: 1) to supply the Honeywell Solid State Electronics Center (SSEC) with material for processing into solar cells, and 2) to supply JPL with substrates to be processed by other contractors -- namely, OCLI and Spectrolab.

A standard procedure was defined, and a production schedule was developed to supply the demand with the original dip-coating system. Due to a number of operational problems, we were not able to meet that schedule with the single system, so the experimental dip-coating system was also used for production.

The standard procedure is described as follows:

- 1) All carbon parts used in the dip-coating system are purified and certified to contain less than 10 ppm of Ti, V, and Fe. Unfortunately, we were not able to maintain all parts to this specification with respect to Fe, but the parts were checked by the Honeywell Chemistry Laboratory by emission spectroscopy, and were found to contain less than 100 ppm Fe in all cases. This is in contrast to the uncertified carbon parts we previously used which contained 1500 ppm Fe, as well as significant amounts of Ti and V.

- 2) The substrates are Coors "type K" mullite-based ceramic with a demonstrated expansion coefficient closely matching that of Si.

- 3) The substrates are dye-checked and baked at 1000°C. This procedure was initiated at the suggestion of ceramics consultants from Coors Porcelain (Dave Wirth and Jack Sibold). During a recent visit, they carefully observed the growth in the experimental dip-coating system (which has excellent viewing access) and noticed that cracks were developing in the ceramic when it was lowered into the melt. These cracks were in all likelihood present in the ceramic before dipping. They suggested the dye-checking procedure which reveals cracks in the substrates, followed by firing at 1000°C in air to burn off the dye and any residual hydrocarbons due to handling. After firing, care is taken not to touch the substrates except with plastic gloves. Results in the experimental dip coater indicate that the new procedure has considerably reduced the substrate cracking.

8

Ż

- 4) Hand-rubbed carbon coatings are applied to the sample using spectrographic carbon. We realize that the hand-rubbed carbon is not ideal because the coverage is not as uniform as with the colloidal graphite paint. However, at present, hand-rubbed carbon is the only method that assures that carbon does not enter the slots. If carbon enters the slots, the silicon wets the slots and does not get forced out during solidification. The latent heat released during solidification upsets the crystal growth conditions, and crystallinity is disturbed.

- 5) Argon is introduced into the system just above the melt surface in the vicinity of the growing crystal to sweep away the SiO particles generated in the melt.

- 6) In addition to the foregoing, the procedure calls for the following:

- a) 600-gram charge

1)

Eliteration

Commission 1

- b)  $600 \times 10^{16}$  atoms boron dopant

- c) 30-minute prebake of substrate just prior to dipping

- d) 1,6 cc/minute argon flow rate

- e) 3-minute preheat at 1/8-inch above melt

- f) 20-second soak time in melt

- g) 0.06 cm/sec pull rate

- h) 2-minute stabilization just after meniscus breaks

- i) 0.06 cm/sec initial withdrawal for 2 inches

With the above procedure, the production yield improved during the quarter. The velocity of 0.06 cm/sec gives layers 200 to 250  $\mu$ m thick. The remaining production problems were associated with the power supply and temperature controllers, availability of substrates, and changes in operator personnel.

There is one yield-limiting factor which is not understood. During some of the runs, some of the samples developed dendrites in the center region of the sample. The dendrites can be eliminated by raising the melt temperature, but this results in a decrease in layer thickness, and the increased possibility of the silicon layer not bridging the slots. The appearance of the dendrites in the middle of a layer suggests some change in the thermal conditions during growth, but the cause of such a change is not apparent.

During the quarter, type M substrates from Coors were also evaluated for dip coating. These substrates have a higher glass content than the type K substrates. They have

suffered significant breakage problems during dipping and appear to be too soft at the melting point of silicon. Further evaluation will be done when we have caught up with the production schedule.

#### Experimental Dip Coater

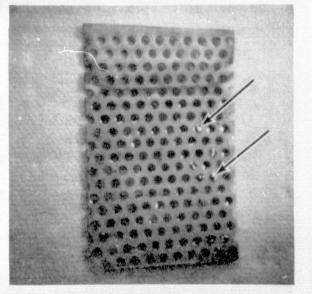

During the quarter, a new dip-coating facility was put in operation at CMSC. A photograph of the dip coater is shown in Figure 2. The unit is basically the same as the existing dip coater but is larger and affords greater accessibility to the molten silicon by the operator. The other dip coater is seen in the background of Figure 2. The power supply is situated between and is shared by both units. There are four access ports in the central section of the new dipper. Two are inclined at 11 degrees to the melt surface and two are at 30 degrees. The melt surface is typically maintained level with the parting line between the lower and middle chambers, and all access ports focus on the center of the crucible at this level. There are four access ports in the top of the chamber inclined at about 60 degrees to the melt surface. The crucible supports and pulling mechanisms in the new dipper are identical with the other unit but the heater is different. In the new unit we have installed a graphite resistance heater with a picket fence design rather than the thin-wall heater used in the other unit.

The new heater assembly is shown in Figure 3. The glass tube on the right side of the heater is used to blow argon gas over the melt surface during some runs to minimize SiO formation on the silicon coating. The picket fence heater is believed to be less susceptible to damage and provide more-uniform heating than the thin-wall heater used in the other system.

In 1979, the new dip-coating facility will be used mainly to determine how the throughput of the SOC process can be optimized. The major goal will be to define conditions under which reasonably thick (i.e.,  $100 \mu m$ ) silicon coatings can be grown at relatively high rates (i.e., 0.15 to 0.3 cm/sec). With the dip-coating geometry used to date, the velocity - thickness relation follows that discussed in Annual Report No. 3, namely  $v^{2}t =$ constant. This behavior has also been found in the new dipper. Figure 4 shows coating thickness plotted as a function of pull rate for a series of coatings made on unslotted Coors K Mod substrates in the new dipper. The dotted lines in the figure show the spread in all the data taken on the other dipper and published as Figure 10 in Annual Report No. 3. The data taken with the new dipper follow the relation  $v^{2} \cdot {}^{3}t$  = constant. The goal of the program to increase the throughput is also shown in the figure.

The data plotted in Figure 4 represent the upper limit in coating thickness expected with the experimental arrangement currently in use (i.e., simply withdrawing a substrate from a crucible of molten silicon). In this case the radiative and convective cooling of the silicon coating is dictated by the melt temperature, the growth velocity, and the thermal conditions of the environment (e.g., the temperature of the walls of the chamber).

[]

0

Figure 2. Photograph of New Dip-Coating Facility

Figure 3. Photograph of Heater and Crucible in New Dip Coater

Figure 4, SOC Layer Thickness Plotted as a Function of Pull Rate for Coatings Produced on Unslotted Coors K Mod Substrates in the New Dip-Coating Facility. The triangles represent data taken with external cooling employed.

If thicker coatings are to be produced at increased pull rates, external cooling will have to be used. Experiments with external cooling have been started. Cooling in the vicinity of the liquid - solid interface is being provided by the two cooling shoes shown in Figure 5. The shoes are mounted or rods that protrude from two of the 30-degree access ports as shown in Figure 2. The shoes are positioned so that both sides of the substrate can be cooled during coating. The cooling shoes are machined from nickel billets and are cooled by water flowing through the rods and into passages drilled in the shoes. One of the shoes has gas jets drilled in it to allow a stream of gas to be directed at the substrate during coating. The gas also enters the shoe through the support rod.

Several preliminary runs were made with the cooling shoes in place. These data are plotted in Figure 4 as triangles. Substrates were pulled at 0.15 and 0.2 cm/sec with the water-cooled cooling shoes positioned 6 mm from both sides of the substrate and about 6 mm above the melt. The cooling shoe on the coating side contained gas jets and allowed a stream of argon to be directed on the silicon coating. Figure 6 is a photograph of an SOC coating made at 0.2 cm/sec under these conditions. Most of the silicon had solidified dendritically, indicating the melt temperature was too low for the conditions used. The upper data point on Figure 4 at 0.2 cm/sec was measured on the smooth portion of the coating existing on the lower right-hand side of the substrate. These are preliminary results and it is expected that improvements will be made in the coating quality as the growth conditions are optimized.

A notable point concerning these early runs with external cooling is that cracking was not observed. This important observation indicates that afterheaters may not be necessary even at high pulling rates. This appears to be a major advantage of supported growth.

Figure 5. Photograph of Upper Chamber of New Dipper Showing Cooling Shoes

Figure 6. Photograph of Substrate Dip Coated with Silicon at a Pull Rate of 0, 2 cm/sec with Cooling Shoes in Place Near Front and Back Sides of Substrate. With the exception of the lower right-hand side of the sample, the coating is dendritic.

## Continuous Coating Process

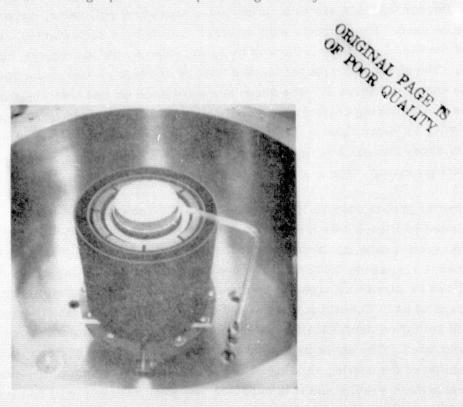

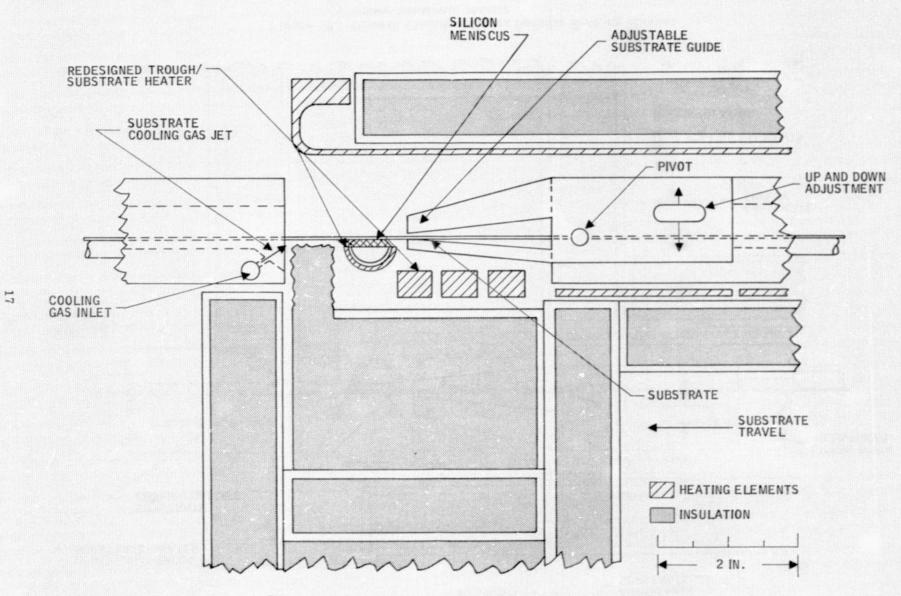

A good part of this reporting period was spent making SCIM coating operational runs. After performing a number of these runs with various heating-element temperature combinations, it became apparent that the trough heating design shown in Figure 7 was not likely to allow the coating on the substrate to solidify at a distance less than 1 inch downstream of the trough. When the liquid - solid interface occurs this far downstream, there is a tendency for molten silicon to be drawn from the trough as the substrate skims over it. This is particularly true at slower (< 0.1 cm/sec) coating speeds where, as with dip coating, more silicon is pulled from the melt to accommodate a subsequently thicker layer. To correct this condition, a new type trough-heater assembly was installed in the coater. The original trough heater also served as a final substrate heater. This was needed to ensure that the substrate would be sufficiently high in temperature before it passed over the molten-silicon meniscus. The new heater assembly also serves this function. The heater is fabricated in such a way that the graphite trough holder itself is an active resistive element of the assembly (see Figure 8). The rectangular legs of this heating assembly fill the final substrate heating requirement. The power density of each leg is graduated in such a way that the substrate temperature never exceeds the melting point of silicon, as shown in Figure 9. Contrary to the original approach, the heating zone now terminates abruptly at the downstream edge of the trough.

Operational runs following this modification revealed that under favorable conditions the solidification interface can be made to occur within 1 cm of the trough. This dimension varied with respect to the temperatures of the trough and upper substrate heaters, as well as with the quantity of cooling gas that can be directed on the silicon-coated face of the substrate.

Runs made with this new heating configuration produced small-area (~  $20 \text{ cm}^2$ ) coatings. As experienced in previous runs, the silicon meniscus was gradually drawn from the trough as the substrate skimmed over it. Since our first attempt to SCIM coat, we have observed that the extent to which molten silicon is drawn from the trough varies with the velocity of the moving substrate. At faster velocities (> 0.1 cm/sec), the substrate travels a greater distance before this withdrawal takes place than is possible at slower speeds. Since coating thickness is a function of substrate speed, this overflow problem makes it difficult to achieve thicker, well-developed crystalline layers of any significant length.

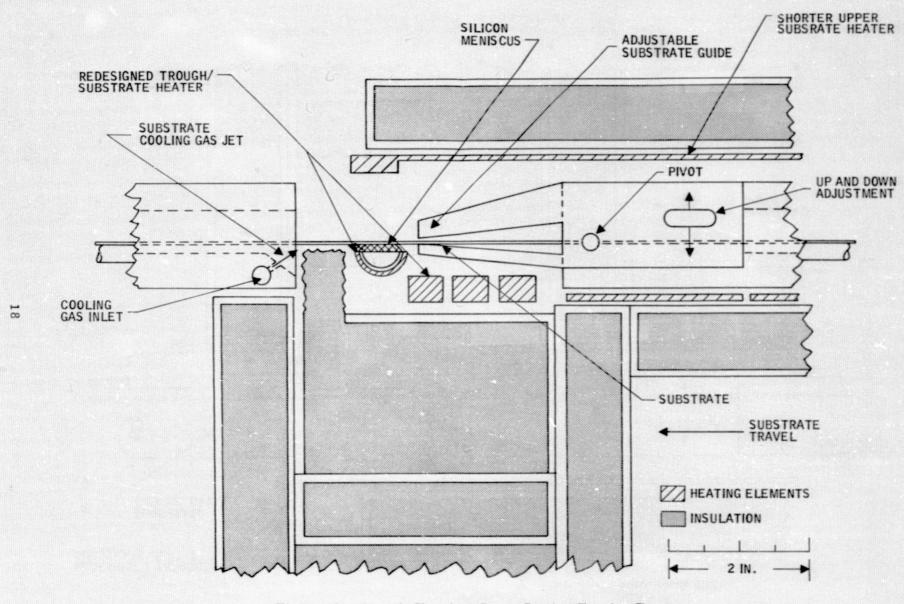

The upper substrate heater could also be a heat source which prevents the solidification front from occurring immediately downstream of the trough (see Figure 9). Note that this heater extends beyond the trough. In a continuing effort to steepen the temperature gradient in this zone, the length of this heater was reduced as shown in Figure 10.

Figure 8. Photograph of New Trough/Substrate Heater (Also Showing Quartz Crucible/Trough Piece)

ORIGINAL PAGE IS OF POOR QUALITY

Figure 9. Growth Chamber Cross Section Showing Newly Designed Trough/Substrate Heater

Figure 10. Growth Chamber Cross Section Showing Shorter Upper Substrate Heater

With this shorter heater, the interface, if desired, can now be shifted until soldification occurs at the edge of the trough. This is the dip-coating equivalent of having the surface of the melt freeze around the substrate as it is being withdrawn from the melt. The temperature of this shorter heater is now a critical coating parameter. If too hot, solidification, as usual, occurs too far downstream. If insufficiently hot, the substrate will freeze to the melt. Using the latter of these two thermal conditions, however, promising layers have been achieved by raising the meniscus height and, consequently, the substrate level as it passes over the meniscus. Apparently the additional heat of fusion contained in this larger volume of silicon prevents the freeze-up which normally occurs with a lower meniscus. Unfortunately, temperature nonuniformity along the trough prevents the solidification front from occurring in a single plane which runs parallel to the trough. The portions of this front which are downstream from the trough continue to allow molten silicon to be pulled from the trough. This temperature non-uniformity was introduced by the new trough heater design and measures must be taken to correct this problem.

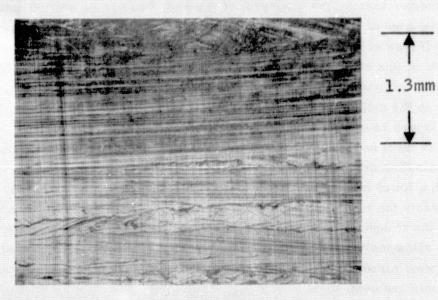

Small-area (10 to 15 cm<sup>2</sup>) coatings have nevertheless been made under these nonuniform thermal conditions. At coating velocities of 0.05 to 0.1 cm/sec, large-grain layers were achieved having thicknesses in the 100 to 200  $\mu$ m range. These layers display the same type of unidirectional solidification experienced in dip coating at these coating rates. Figure 11 is a photomicrograph of one of these layers which was coated at a substrate velocity of 0.95 cm/sec. The layer was 100  $\mu$ m thick and had highly twinned single grains as large as 1.3 mm wide. A faster (0.23 cm/sec) grown coating, on the other hand, produced a larger (~35 cm<sup>2</sup>) layer which was only 10  $\mu$ m thick (see Figure 12). The grain structure here is also very similar to that of dip-coated layers grown under similar conditions.

We are encouraged by the fact that the most recent SCIM-coated layers do indicate that large-grain SOC sheet silicon is possible by this coating technique. The major obstacle to continuous coating remains to be this downstream overflow of molten silicon. An immediate effort will be made to correct the poor trough temperature uniformity which is a suspect for causing the problem. Should this fail to correct it, we are giving consideration to elevating the downstream end of the coater. The coater was designed to be tilted as much as 30 degrees above the horizon. A 30 degree tilt would provide a G/2 downward force on the molten silicon and by doing so could possibly render the temperature uniformity along the trough less critical. Such a change would require only minor modifications to the system.

In summary, we believe that the coating runs performed this reporting period clearly demonstrate that silicon can be coated onto ceramic in continuous manner. To do so in a routine fashion, however, will require much greater temperature uniformity and control than we originally had anticipated.

Figure 11. Photomicrograph of SCIM-Coated Layer Grown at 0.095 cm/sec

**⊲**\_\_\_\_0.1mm

Figure 12. Photomicrograph of SCIM-Coated Layer Grown at 0.23 cm/sec

ORIGINAL PAGE E. OF POOR QUALITY

## Performance of SOC Cells

So far, the best SOC cell has a total-area conversion efficiency of 9.6 percent (AM1, ELH, AR), for a total area of 4.08 cm<sup>2</sup>. The primary characteristics of this cell and 22 other recent SOC cells are given in Tables 3 and 4. The average conversion efficiency after AR coating is 8.3 percent, with a standard deviation of 0.8 percent. All efficiency values were measured using an ELH lamp and a new standard reference cell recently supplied by JPL. The height of the lamp was adjusted to give a light intensity of 100 mW/cm<sup>2</sup>.

| Item          | Cell No.         | Total-Area Conver | rsion Efficiency (%)                                                                                                                                                                                                                                                                                                                                 |

|---------------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item          |                  | Before AR         | After AR                                                                                                                                                                                                                                                                                                                                             |

| 1             | 143-12I          | 5.0*              | 6.1                                                                                                                                                                                                                                                                                                                                                  |

| 2             | 143-12II         | 5.8*              | 7.1                                                                                                                                                                                                                                                                                                                                                  |

| 3             | 143 <b>-</b> 13I | 6.0*              | 9.2                                                                                                                                                                                                                                                                                                                                                  |

| 4             | 143-13II         | 6.5*              | 9.0                                                                                                                                                                                                                                                                                                                                                  |

| 5             | 144-4            | 6.1*              | 8.2                                                                                                                                                                                                                                                                                                                                                  |

| 6             | 147-7            | 4.5               |                                                                                                                                                                                                                                                                                                                                                      |

| 7             | 148-8T           | 5.9*              | 7.9                                                                                                                                                                                                                                                                                                                                                  |

| 8             | 148-8            | 5.7*              | 7.8                                                                                                                                                                                                                                                                                                                                                  |

| 9             | 148-15           | 4.4               |                                                                                                                                                                                                                                                                                                                                                      |

| 10            | 148-16L          | 5.4               |                                                                                                                                                                                                                                                                                                                                                      |

| 11            | 148-16R          | 6.4               |                                                                                                                                                                                                                                                                                                                                                      |

| 12            | 146-6L           | 5.6*              | 9.6                                                                                                                                                                                                                                                                                                                                                  |

| 13            | 146-6R           | 5.2*              | 7.8                                                                                                                                                                                                                                                                                                                                                  |

| 14            | 148-7L           | 6.2               | n de la constante de la consta<br>La constante de la constante de<br>La constante de la constante de |

| 15            | 148-7R           | 6.9               |                                                                                                                                                                                                                                                                                                                                                      |

| 16            | 151-10L          | 6.3               | 8.3                                                                                                                                                                                                                                                                                                                                                  |

| 17            | 151-10R          | 6.6               | 8.4                                                                                                                                                                                                                                                                                                                                                  |

| 18            | 151-13L          | 7.3               | 8.7                                                                                                                                                                                                                                                                                                                                                  |

| 19            | 151-13R          | 6.6               | 9.0                                                                                                                                                                                                                                                                                                                                                  |

| 20            | 151-14L          | 6.0               | 8.2                                                                                                                                                                                                                                                                                                                                                  |

| 21            | 151-14R          | 6.3               | 8.6                                                                                                                                                                                                                                                                                                                                                  |

| 22            | 151-15L          | 6.5               | 8.5                                                                                                                                                                                                                                                                                                                                                  |

| 23            | 151-15R          | 5.9               | 8.2                                                                                                                                                                                                                                                                                                                                                  |

| Avg.<br>Value |                  | 6.0(±0.7)         | 8.3(±0.8)                                                                                                                                                                                                                                                                                                                                            |

Table 3. Slotted SOC Cell Conversion Efficiency

Note: The asterisk indicates values that could not be measured using the new standard cell from JPL. Such values were estimated from previous measurements.

| Cell<br>No.                 | Diffusion<br>No, | V <sub>oc</sub><br>(V) | J <sub>sc</sub><br>(mA/cm <sup>2</sup> )  | Fill<br>Factor | Total-Area<br>Conversion<br>Efficiency<br>(%) |

|-----------------------------|------------------|------------------------|-------------------------------------------|----------------|-----------------------------------------------|

| 143-12I                     | Q46              | 0.54                   | 17.6*                                     | 0.62           | 5.0*                                          |

| After AR coating            |                  | 0.55                   | 22.6                                      | 0.49           | 6.1 (AR)                                      |

| 143-1211                    | Q46              | 0.54                   | 17.3*                                     | 0.62           | 5.8*                                          |

| After AR coating            |                  | 0.55                   | 22,6                                      | 0.62           | 7.7 (AR)                                      |

| 143-131                     | Q46              | 0.54                   | 16.0*                                     | 0.70           | 6.0*                                          |

| After AR coating            |                  | 0.55                   | 22.8                                      | 0.74           | 9.2 (AR)                                      |

| 143-13II                    | Q46              | 0.54                   | 17.0*                                     | 0.71           | 6.5*                                          |

| After AR coating            |                  | 0.54                   | 23.3                                      | 0.71           | 9.0 (AR)                                      |

| 144-4                       | Q46              | 0.54                   | 16.7*                                     | 0.68           | 6.1*                                          |

| After AR coating            |                  | 0.55                   | 23.7                                      | 0.63           | 8.2 (AR)                                      |

| 147-7                       | Q48              | 0.51                   | 17.1                                      | 0.51           | 4.5                                           |

| 148-8T                      | Q48              | 0,53                   | 15,9*                                     | 0,69           | 5.9*                                          |

| After AR coating            |                  | 0.54                   | 21,6                                      | 0,68           | 7.9 (AR)                                      |

| 148-8                       | Q48              | 0.54                   | 16.5*                                     | 0.64           | 5.7                                           |

| After AR coating            |                  | 0.54                   | 22.8                                      | 0.63           | 7.8 (AR)                                      |

| 148-15                      | Q48              | 0,52                   | 15.7                                      | 0.55           | 4.4                                           |

| 148-16L                     | Q48              | 0.53                   | 15.8                                      | 0.65           | 5,4                                           |

| 148-16R                     | Q48              | 0.54                   | 16.3                                      | 0.72           | 6.4                                           |

| 146-6L                      | Q51              | 0.55                   | 18.1*                                     | 0.57           | 5.6*                                          |

| After AR coating            |                  | 0.55                   | 23.6                                      | 0.74           | 9.6 (AR)                                      |

| 146-6R                      | Q51              | 0.53                   | 16.1*                                     | 0.61           | 5.2*                                          |

| After AR coating            |                  | 0.54                   | 22.5                                      | 0.65           | 7.8 (AR)                                      |

| 148-7L                      | Q51              | 0.54                   | 17.5                                      | 0.65           | 6.2                                           |

| 148-7R                      | Q51              | 0.54                   | 17.5                                      | 0,73           | 6.9                                           |

| 151-10L                     | Q53              | 0.53                   | 16.5                                      | 0.72           | 6.3                                           |

| After AR coating            |                  | 0.54                   | 21.6                                      | 0.70           | 8.3 (AR)                                      |

| 151-10R                     | Q53              | 0, 54                  | 16.6                                      | 0.74           | 6.6                                           |

| After AR coating            |                  | 0, 54                  | 21.5                                      | 0.72           | 8.4 (AR)                                      |

| 151-13L                     | Q52              | 0.53                   | 18.7                                      | 0,73           | 7.3                                           |

| After AR coating            |                  | 0.54                   | 23.0                                      | 0.69           | 8.7 (AR)                                      |

| 151-13R                     | Q52              | 0.54                   | 17.1                                      | 0.72           | 6.6                                           |

| After AR coating            |                  | 0.55                   | 22.8                                      | 0.71           | 9.0 (AR)                                      |

| 151-14L                     | Q52              | 0.53                   | 16.8                                      | 0.67           | 6.0                                           |

| After AR coating            |                  | 0.54                   | 22.8                                      | 0.67           | 8.2 (AR)                                      |

| 151-14R                     | <b>ର୍</b> 52     | 0.54                   | 16.8                                      | 0.70           | 6.3                                           |

| After AR coating            |                  | 0.54                   | 23.2                                      | 0.68           | 8.6 (AR)                                      |

| 151–15L<br>After AR coating | <b>Q</b> 53      | 0.54<br>0.54           | $17.4\\23.4$                              | 0.70<br>0.67   | 6,5<br>8.5 (AR)                               |

| 151-15R<br>After AR coating | Q53              | 0.54<br>0.55           | $\begin{array}{c} 16.6\\ 23.3\end{array}$ | 0.66<br>0.64   | 5.9<br>8.2 (AR)                               |

Table 4. Slotted SOC Cell Performance Parameters

Note: All cells have a total area of 4.08 cm<sup>2</sup> and the metallization pattern covers 10 percent of the total area.

All recent SOC cells have a total area of 4.08 cm<sup>2</sup> and a metallization pattern that covers 10 percent of the total area. The cells use slotted mullite-based substrates. The slots provide a way for making electrical contact to the back side of the silicon layer. The mullite-based material has a thermal expansion coefficient that closely matches that of silicon.

The current-voltage characteristics of the best cell are given in Figure 13. This cell has an open-circuit voltage,  $V_{oc}$ , of 0.55 V, a total-area short-circuit current density,  $J_{sc}$ , of 23.6 mA/cm<sup>2</sup>, a fill-factor (FF) of 0.74, and (as already noted), a total-area conversion efficiency of 9.6 percent (AM1, ELH, AR). The active-area short-circuit current density is ~ 26 mA/cm<sup>2</sup>, which is typical of most recent cells (see below).

### Performance of Single-Crystal Cells

The primary characteristics of 10 recent single-crystal cells are given in Table 5. The best cell has a total-area short-circuit current density  $(J_{sc})$  of 30.7 mA/cm<sup>2</sup>, an open-circuit voltage ( $V_{oc}$ ) of 0.58 V, a fill-factor (FF) of 0.77, and a total-area conversion efficiency of 13.7 percent (AM1, ELH, AR), for a total area of 4.08 cm<sup>2</sup>.

## Average Values