# ΝΟΤΙCΕ

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

NASA CR - 159660

N80-14480

BI- DIRECTIONAL FOUF (NASA-CE-159660) QUADRANT (BDQ4) FOWER CONVERIER DEVELOPMENT Final Report (Power Electronics Associates, Unclas CSCL 10B 249 p FC A11/MP A01 Inc.) 46328 G3/44

# BI-DIREC.IONAL FOUR QUADRANT (BDQ4) POWER CONVERTER

DEVELOPMENT

### FINAL REPORT

POWER ELECTRONICS ASSOCIATES, INC.

Round Hill Road, Lincoln, MA 01773

prepared for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATI

NASA LEWIS RESEARCH CENTER

CONTRACT NO. NAS-3-30363

# TABLE OF CONTENTS

. •

đ

| I.  | . INTRODUCTION |                                                  |    | pag | ge |

|-----|----------------|--------------------------------------------------|----|-----|----|

|     | 1.             | The Problem                                      | I  | -   | 1  |

|     | 2.             | The Content of the Study                         | I  |     | 5  |

| II. | CO             | NCEPT FORMULATION                                |    |     |    |

|     | 1.             | Goals of Technology Improvement                  | II | -   | 1  |

|     | 2.             | Definition of a Representative System            | II | -   | 2  |

|     | з.             | Formulation of Needed System Concept             | II |     | 13 |

|     |                | 3.1. Desired Characteristics                     | II | -   | 13 |

|     |                | 3.2. Functional Aspects                          | II |     | 15 |

|     |                | 3.3. Philosophy of Functional Concept            | II | -   | 17 |

|     |                | 3.4. Expected Benefits                           | II | -   | 18 |

|     | 4.             | Functional Concepts for the Planned System       | II | -   | 18 |

|     |                | 4.1. General System Concept                      | II | -   | 18 |

|     |                | 4.2. The Bidirectional Series Capacitor Inverter |    |     |    |

|     |                | Converter                                        | II | -   | 25 |

|     |                | 4.3. Assessment of Significant Physical Features | II | -   | 37 |

|     |                | 4.4. The Control System                          | II | -   | 39 |

|     |                | 4.5. Component Requirements                      | II | -   | 45 |

- ii -

PRECEDING PAGE BLANK NOT FILMED

an é

# table of contents - continued

III.

Ć

Ì

|      | 5.   | System Analysis and Characterization             | II  | - | 46 |

|------|------|--------------------------------------------------|-----|---|----|

|      |      | 5.1. General Aspects                             | II  | - | 46 |

|      |      | 5.2. A numerical Example                         | II  |   | 47 |

|      | 6.   | Engineering Assessment of the Proposed Concept   | II  | - | 65 |

|      |      | 6.1. Critical Aspecto                            | II  |   | 65 |

|      |      | 6.2. Integration of Existing Technology          | II  |   |    |

|      | 7.   | Summay of Concept Formulation                    | II  |   | 69 |

| Refe | erei | nces                                             | II  | - | 71 |

| []]. | COI  | ICEPT VERIFICATION                               |     |   |    |

|      |      |                                                  |     |   |    |

|      | 1.   | Objectives                                       | III | - | 1  |

|      | 2.   | The Doublesided Cyclo-Converter                  | III |   | 8  |

|      |      | 2.1. The Doublesided Three Phase Cyclo-Converter | III |   | 9  |

|      |      | 2.1.1. Selection of the Thyristors for Forward   |     |   |    |

|      |      | Power Transfer                                   | III |   | 15 |

|      |      | 2.1.2. Reconfiguration of the Three Phase Bridge |     |   |    |

|      |      | for Reverse Power Transfers                      | III |   | 21 |

|      |      |                                                  |     |   |    |

page

2.1.3. Protective Suppression and Interlock of Signals III - 25

#### 2.2. The DC Cyclo-Converter III - 36

- iii -

# table of contents - continued

+ \*\*\* \*\* \*

ĥ

ļ

þ,

ì

ł

page

| 2.2.1. Organization of Power Flow                     | III - 36 |  |

|-------------------------------------------------------|----------|--|

| 2.2.2. Reconfiguration of the DC Bridge for           |          |  |

| Reverse Power Transfer                                | III - 38 |  |

| 3. Control System Characteristics                     | III - 40 |  |

| 4. Experimental Verification of Key Circuit Elements  | III - 46 |  |

| 4.1. The Experimental Material                        | III - 47 |  |

| 4.2. Forward Power Transmission                       | III - 49 |  |

| 4.3. Reverse Power Transmission                       | III - 52 |  |

| 4.4. Test Results                                     | III - 54 |  |

| 4.5. Discussion of the Results                        | III - 67 |  |

| 5. Summary of Concept Varification                    | III - 70 |  |

| References                                            |          |  |

|                                                       |          |  |

| IV. PRELIMINARY DESIGN AND PERFORMANCE PREDICTION     |          |  |

| 1. Introduction                                       | IV - 1   |  |

| 2. Engineering Design of a Representative BD4Q System | IV - 3   |  |

| 2.1. System Design                                    | IV - 3   |  |

| 2.2. Thyristor Ratings                                | IV - 9   |  |

| 2.3. Capacitors                                       | IV - 12  |  |

- iv -

# table of contents - continued

.....

----

|    | 2.4   | Magneti | le Components                            | IV | -   | 19 |

|----|-------|---------|------------------------------------------|----|-----|----|

|    |       | 2.4.1   | The Series Inductors                     | IV | -   | 19 |

|    |       | 2,4,2   | The dv/dt Limiting Networks              | IV | -   | 21 |

|    |       | 2.4.3   | Design of the Series Inductor Elements   | IV | -   | 24 |

|    |       | 2.4.4   | The Power Transformer                    | IV | -   | 27 |

|    | 2.5   | Weight  | and Heat Dissipation of the Power Com-   | IV | -   | 31 |

|    | 2.6   | The Cor | ponents ponents trol Electronics         | IV | -   | 36 |

| •  |       |         |                                          |    |     |    |

| 3. | Engin | neerin  | Assessment and Evaluation                | IV | -   | 40 |

|    | 3.1   | Unique  | and Useful External Characteristics      | IV | . • | 40 |

|    |       | 3.1.1   | Power Factor and Harmonic Content in the | IV | -   | 42 |

|    |       |         | AC Supply System                         |    |     |    |

|    |       | 3.1.2   | The Active Filtering Effect              | IV | -   | 61 |

|    |       | 3.1.3   | Speed of Response                        | IV | -   | 63 |

|    | 3.2   | Aspects | s of Technology                          | IV | -   | 66 |

|    |       | 3.2.1   | The Present State of Development         | IV |     | 72 |

|    |       | 3.2.2   | Projections of Applicability             | IV | -   | 74 |

| 4. | Conc] | lusions |                                          | IV | -   | 77 |

|    |       |         |                                          |    |     |    |

References

.

ł

,

1

IV - 83

- v -

| No.  | Caption                                | Chapter I                                                                                                    | page   |

|------|----------------------------------------|--------------------------------------------------------------------------------------------------------------|--------|

| 1.1. |                                        | n of a three phase ac to controlled de<br>the output characteristic of a con-<br>source.                     | I 4    |

| 1.2. |                                        | a of a controlled de to three phase ac<br>ne output characterístics of a current                             | I - 6  |

|      |                                        | Chapter II                                                                                                   |        |

| 2.1. | dc converter with<br>energy with chara | iguration of a three phase ac to<br>unidirectional transfer of electric<br>acteristic wave forms and some of | II - 3 |

|      | their frequency s                      | pectra.                                                                                                      |        |

- 2.2. Symbolic schematic of bidirectional three phase ac II = 5 to de converter used as battery charger.

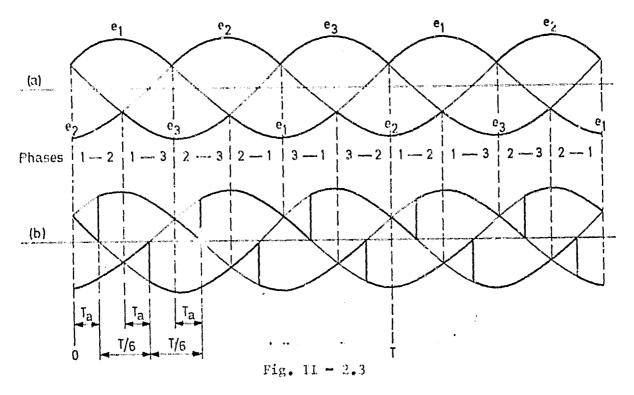

- 2.3. Rectified three phase voltage wave form of (a) full II 6 wave diode bridge and (b) full wave thyristor bridge, with indication of intervals.

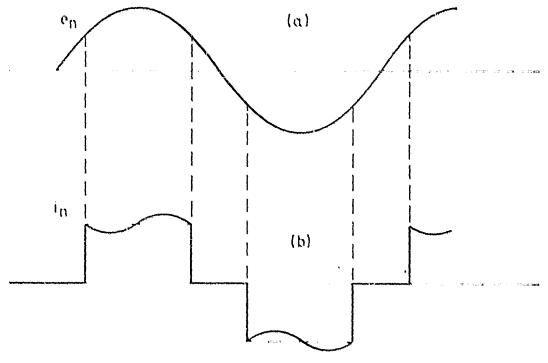

- 2.4. Waveform of (a) voltage  $e_n$  (n = 1, 2, 3) and (b) II 10 typical current  $i_n$  in one of the phases of the three phase supply line for a full wave bridge rectifierfilter.

- vi -

## LIST OF ILLUSTRATIONS

17

Ŷ

þ

ł

)

1

| No.  | Caption Chapter II - continued                                                                                                                                      | page               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

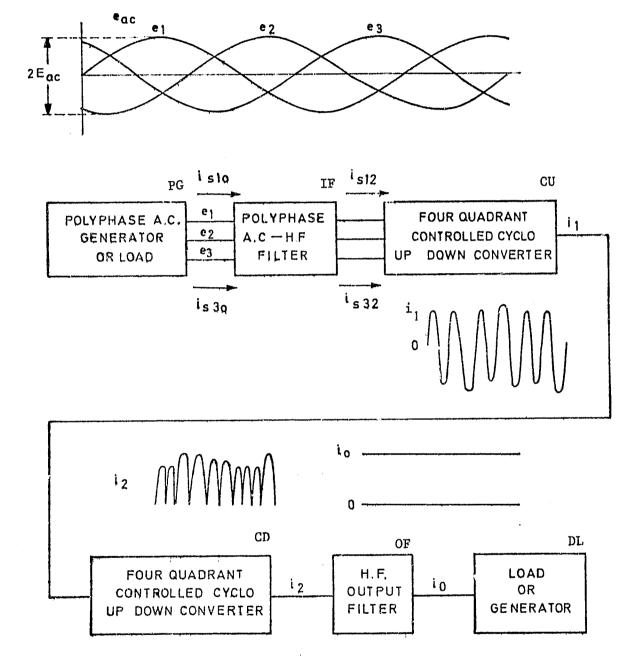

| 4.1. | Symbolic block diagram of bidirectional, four quadrant three phase ac to de converter using a                                                                       | II - 19            |

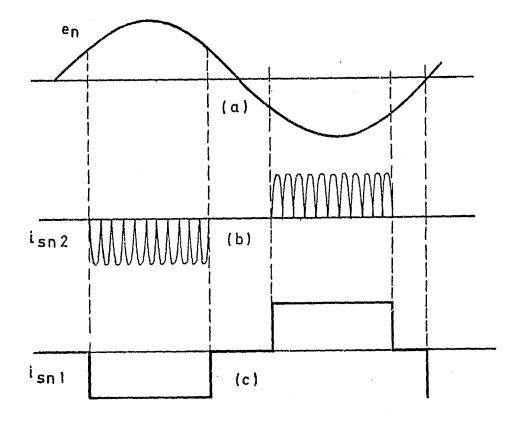

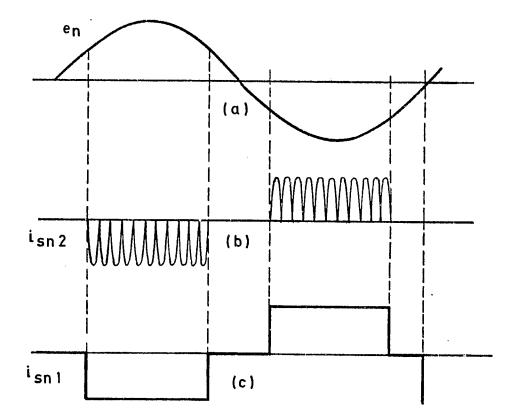

| 4.2. | modulated high frequency corrier link.<br>$P^{i_1}$ se (a) voltage $e_n$ , (b) demodulated carrier<br>current $i_{sn2}$ and (c) filtered current $i_{sn1}$ , during | II - 22            |

| 4.3. | transfer of electric energy to the polyphase line.<br>Symbolic schematic of bilateral four quadrant                                                                 | II - 26            |

| 4.4. | series capacitor inverter-converter.<br>Equivalent circuit of the symbolic schematic of the<br>bidirectional series capacitor inverter-converter                    | II - 27            |

| 4.5. | shown in figure 4.3.<br>Symbolic schematic of the primary circuit of a series                                                                                       | II - 29            |

| 4.6. | capacitor inverter-converter in half bridge<br>configuration.<br>Significant voltage and current waveforms in the                                                   | II - 31            |

|      | series capacitor converter.<br>Antiparallel thyristor bridge and series resonant                                                                                    | II - 36            |

|      | circuit with identification matrix of thyristor<br>firing selections.                                                                                               |                    |

|      | Thyristor bridge associated with dc circuit.<br>Signals for the control logic of the thyristor<br>gating and firing system.                                         | II - 38<br>II - 41 |

LIST OF HLLUSTRATIONS - Continued

| No    | Caption          | Chapter II - continued              | page    |

|-------|------------------|-------------------------------------|---------|

| 4 10  | *11              |                                     | II - 43 |

| 4.10. | fillustration of | representative firing sequence      | 11 - 45 |

|       | emitted by the   | firing pulse generators, FPGij      |         |

|       | and the back bi  | as conditions BBij, associated      |         |

|       | with the thyris  | tors CRij                           |         |

| 4.11. | Block diagram o  | f ASDTIC control system CS with in- | II - 44 |

|       | puts for voltag  | e and current control.              |         |

|       |                  |                                     |         |

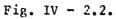

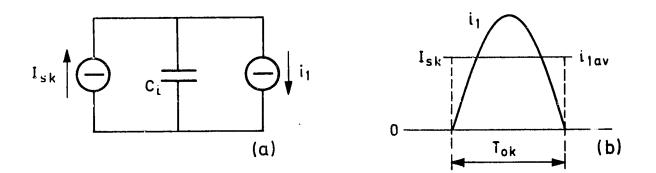

5.1 (a) Input filter capacitor  $C_i$  connected to the "equivalent" current sources  $I_{sk}$  and  $i_1$ ; (b) current II - 57 waveforms  $I_{sk}$  and  $i_1$  during the kth half wave interval  $T_{ok}$  of  $I_1$ .

### Chapter III

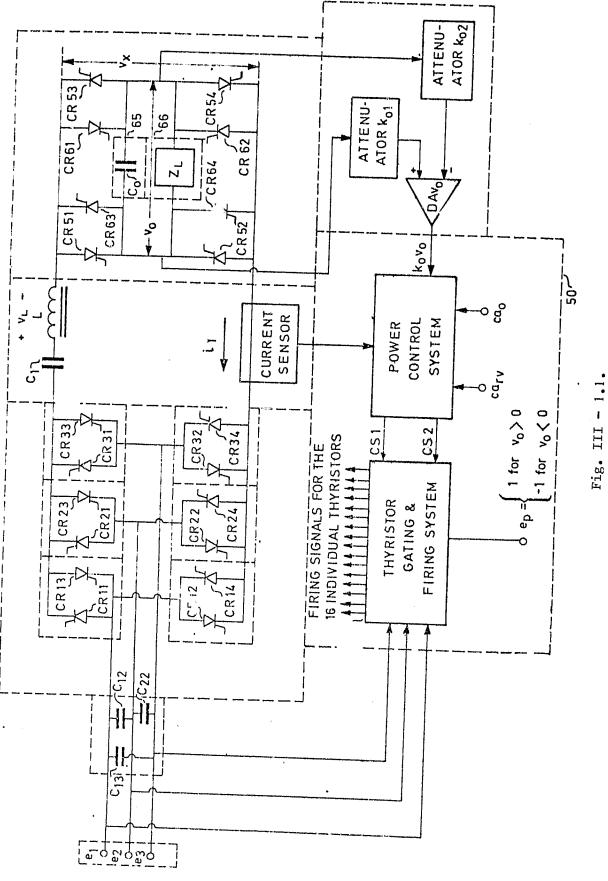

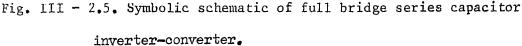

- 1.1. Symbolic schematic of the bidirectional series capacitor Inverter-converter for operation of a dc load with balanced voltage vs. the three phase neutral node.

- 1.2. Significant voltage and current waveforms in the III 3 series capacitor converter.

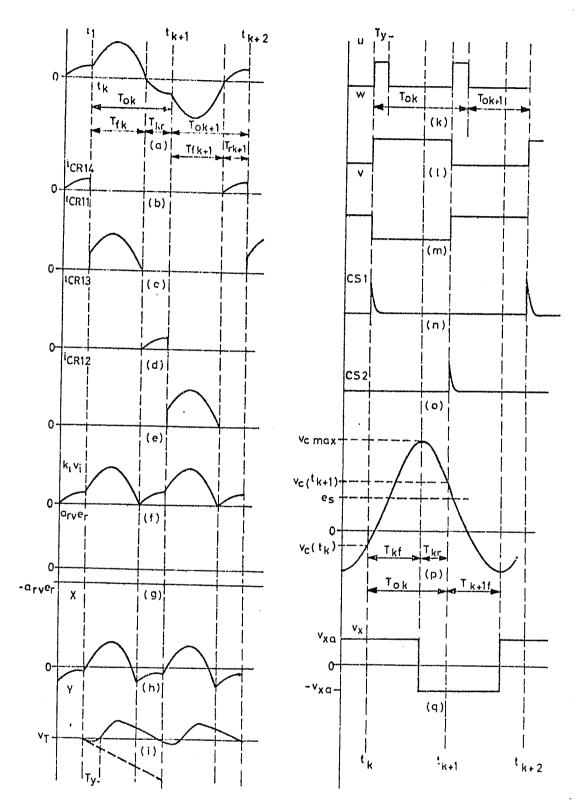

- 1.3. (a) Voltage waveform of a three phase ac system with in- III 6 dication of phases i-j (i,j = 1,2,3) engaged in the rectification process; (b) the resulting rectified voltage  $e_s$ .

- viii -

## LIST OF ILLUSTRATIONS - Continued

| No.  | Caption Chapter I                                | II - continued                                                                                  | page      |

|------|--------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------|

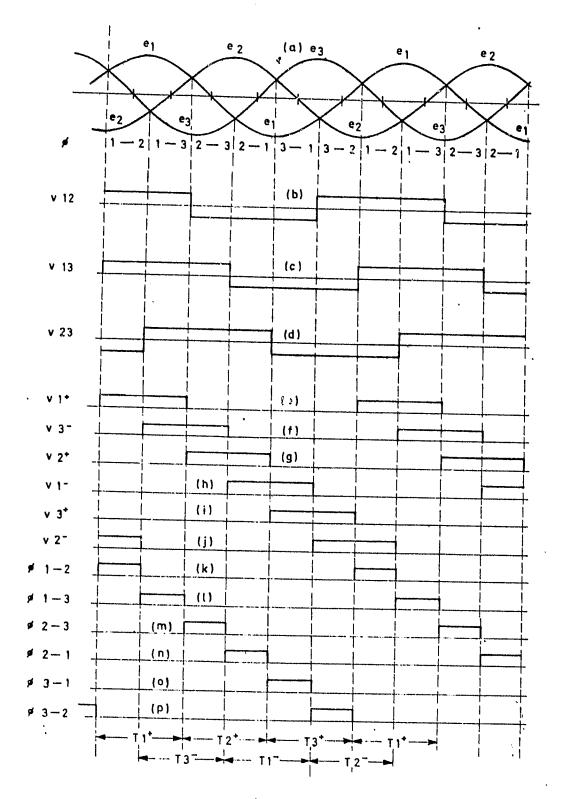

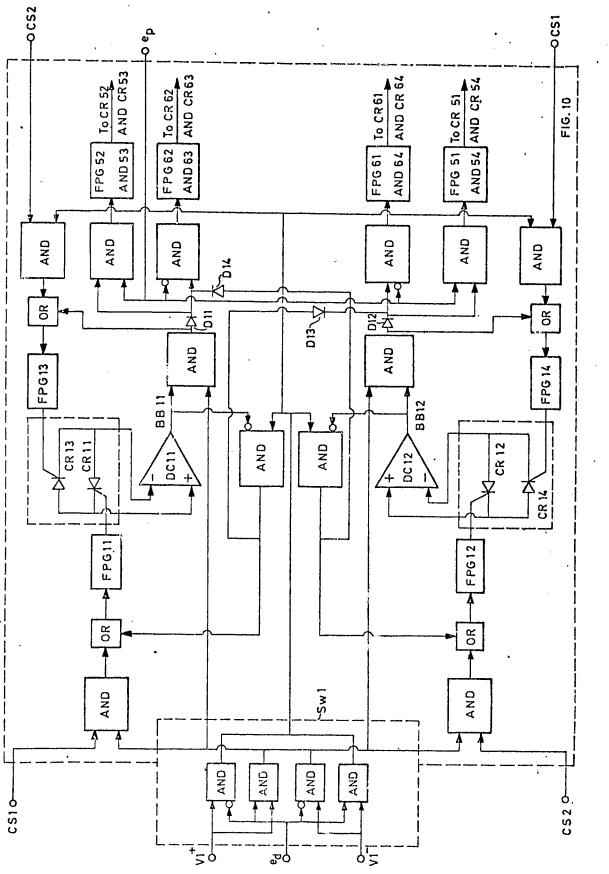

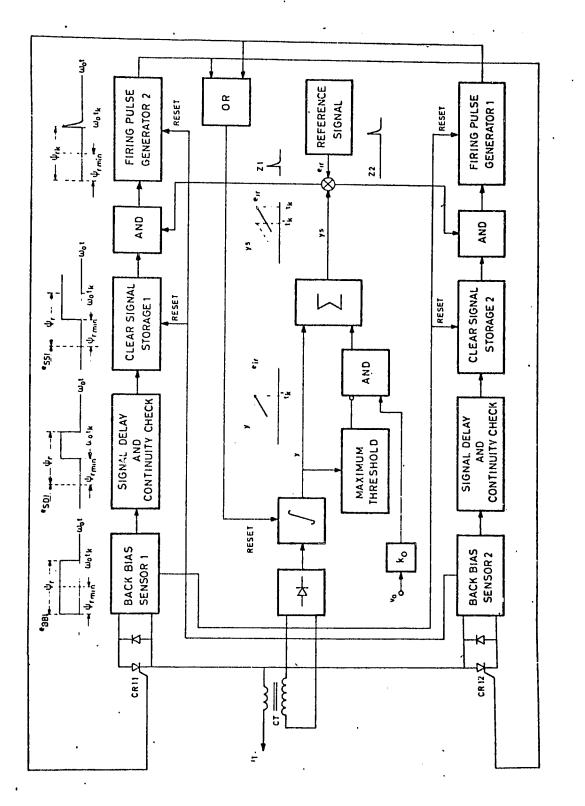

| 2.1. | Signals for the control lo<br>and firing system. | ogic of the thyristor gating                                                                    | II.I - 11 |

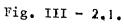

| 2.2. | -                                                | lectronics to provide the                                                                       | III - 12  |

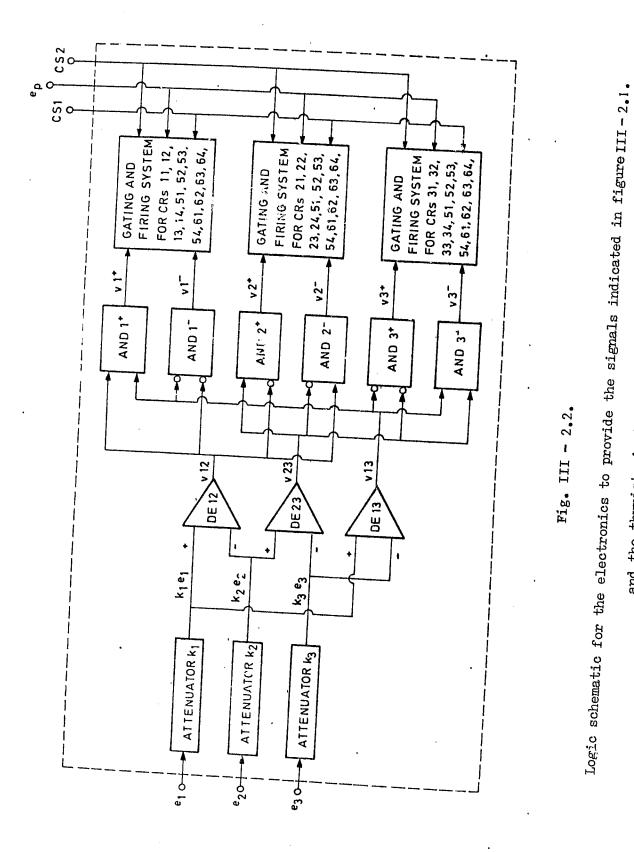

| 2.3. | -                                                | ematic of the logic for the<br>signals for the thyristors of<br>verter.                         | III - 14  |

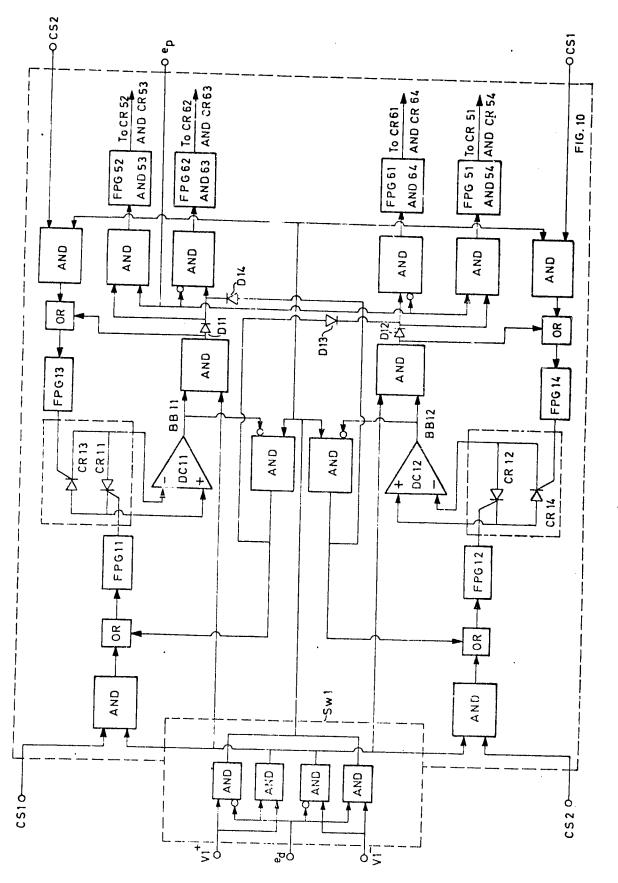

| 2.4. | Functional schematic of or<br>Firing Systems.    | ne of the three Gating and                                                                      | III - 16  |

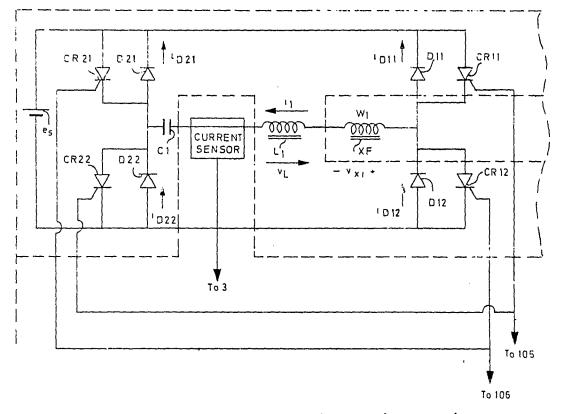

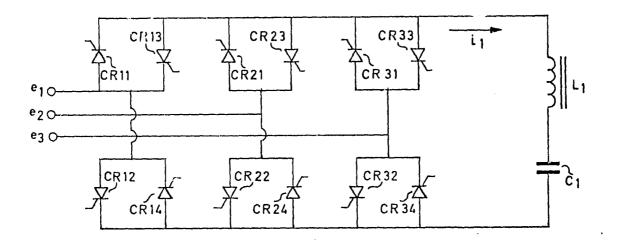

| 2.5. | Symbolic schematic of full inverter-converter.   | bridge series capacitor                                                                         | III - 18  |

| 2.6. |                                                  | demodulated carrier current<br>ent i <sub>snl</sub> , during the trans-<br>the three phase line | III - 22  |

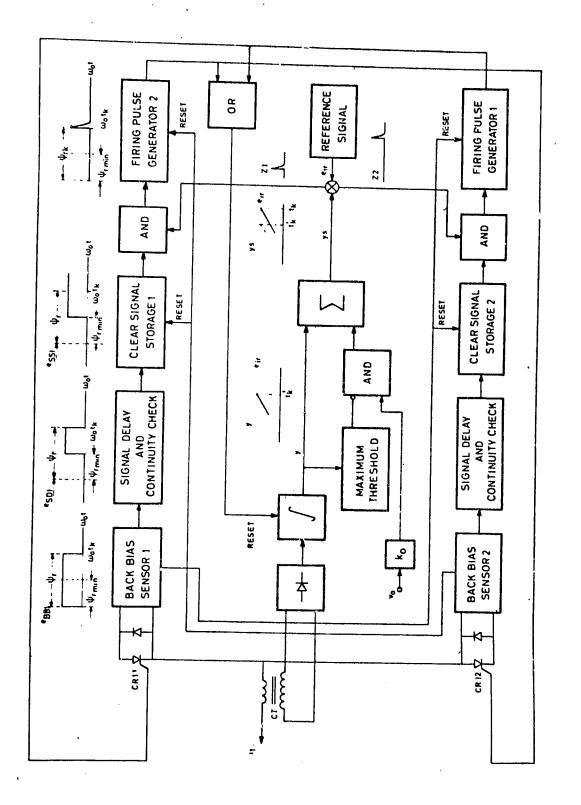

| 2.7. | Functional schematic of th                       | ne control and protection                                                                       | III - 27  |

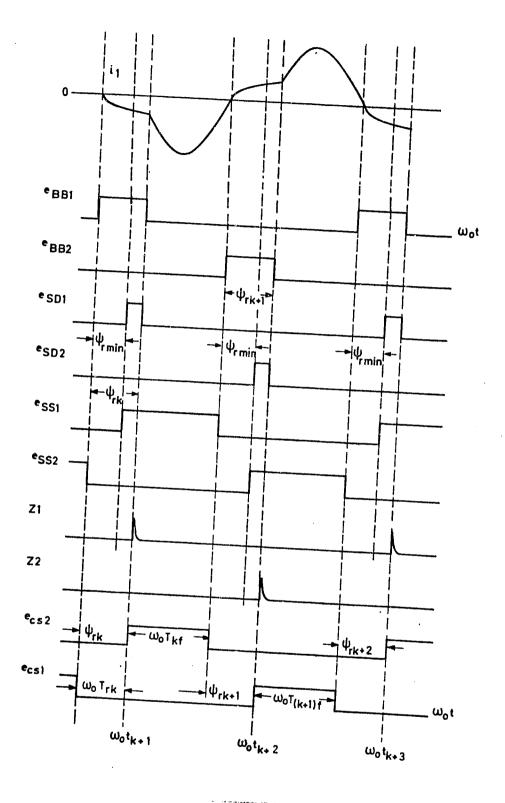

| 2.8  | Significant signal wavefor                       | ms of the protection system.                                                                    | III - 28  |

| 2.9  | The thyristors of the thre<br>functions.         | ee phase bridge and their                                                                       | III - 31  |

- ix -

2

LIST OF ILLUSTRATIONS - Continued

f

Ì

| No.  | Caption Chapter III - continued                                                                                                                                                                                       | page                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

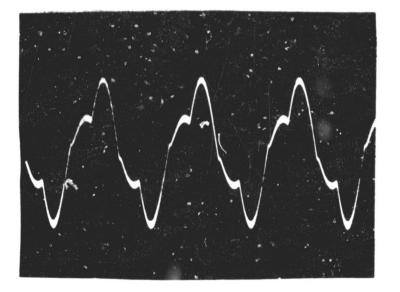

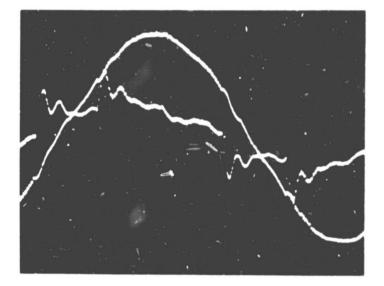

| 4.1. | Traces of the resonant current carrier i <sub>1</sub> at different time scales.                                                                                                                                       | III - 58<br>III - 59 |

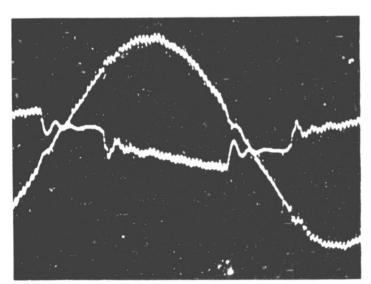

| 4.2. | Voltage $e_i$ and current $i_{1ph}$ in one of the three phases of the a supply line.                                                                                                                                  | III - 62             |

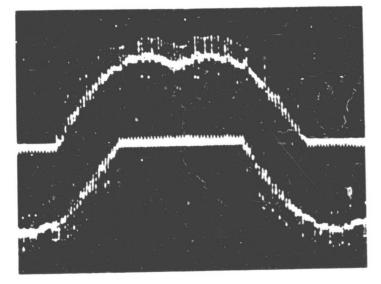

| 4.3. | Phase voltage e and current i for (a) forward and (b)<br>reverse transfer of power through a doublesided cyclo-<br>converter.                                                                                         | III - 65             |

| 4.4. | Voltage across one pair of antiparallel thyristors of the three phase bridge.                                                                                                                                         | III - 66             |

|      | Chapter IV                                                                                                                                                                                                            |                      |

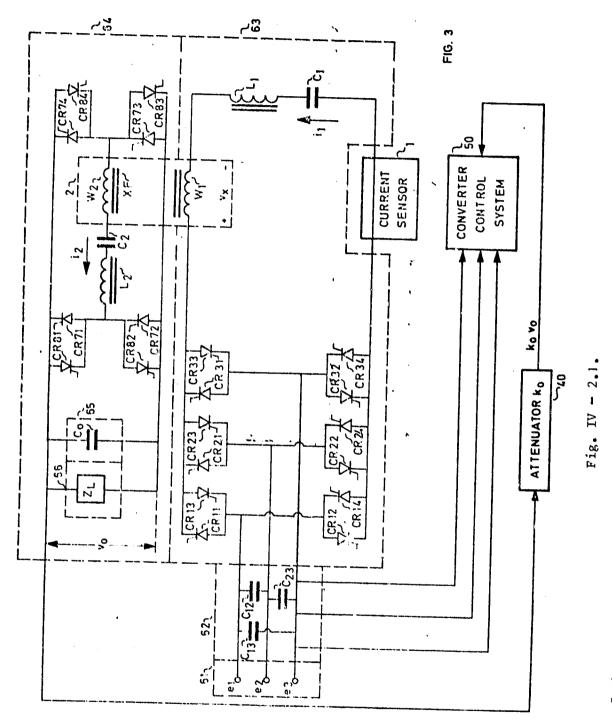

| 2.1  | Symbolic schematic of the bidirectional series capacitor inverter-converter for operation of a dc load (source).                                                                                                      | IV - 5               |

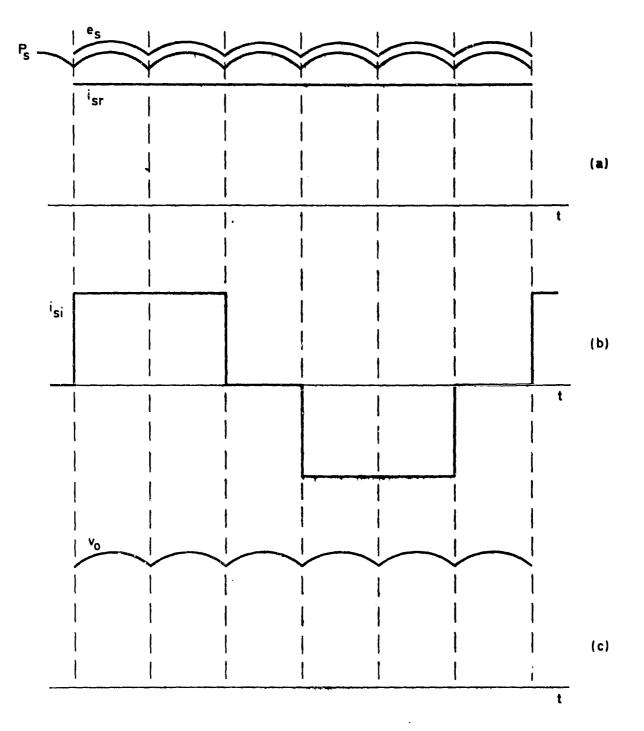

| 2.2  | (a) The output voltage $e_s^*$ of a three phase full wave<br>rectifier, the filter current $i_{sr}$ and the filter input<br>power $P_s$ ; (b) the phase current $i_{si}$ and (c) the filter<br>output voltage $v_o$ . | IV - 6               |

| 2.3. | Equivalent filter capacitor circuit.                                                                                                                                                                                  | IV - 13              |

| 2.4. | The resonant current i                                                                                                                                                                                                | IV - 20              |

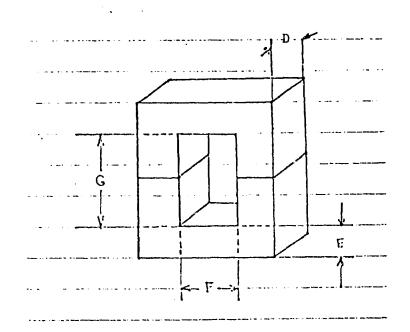

| 2.5. | Symbols for the dimension of a C-core.                                                                                                                                                                                | IV - 25              |

| 2.6  | Functional schematic of one gating and firing system.                                                                                                                                                                 | IV - 37              |

- x -

LIST OF ILLUSTRATIONS - Continued

h

ł

ī

1

| No.  | Caption                                                                                                                                                                                                                                                                                                                                                                                | page    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2.7. | Functional schematic of the control and protection system.                                                                                                                                                                                                                                                                                                                             | IV - 38 |

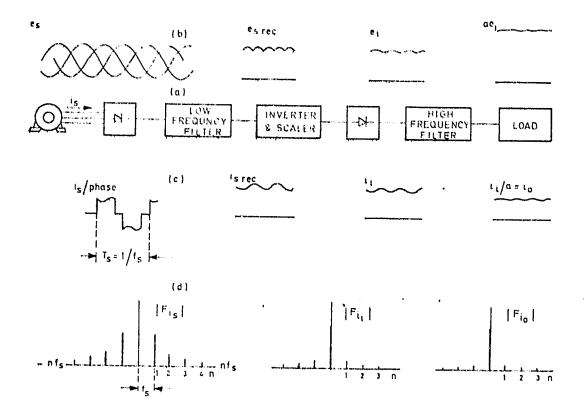

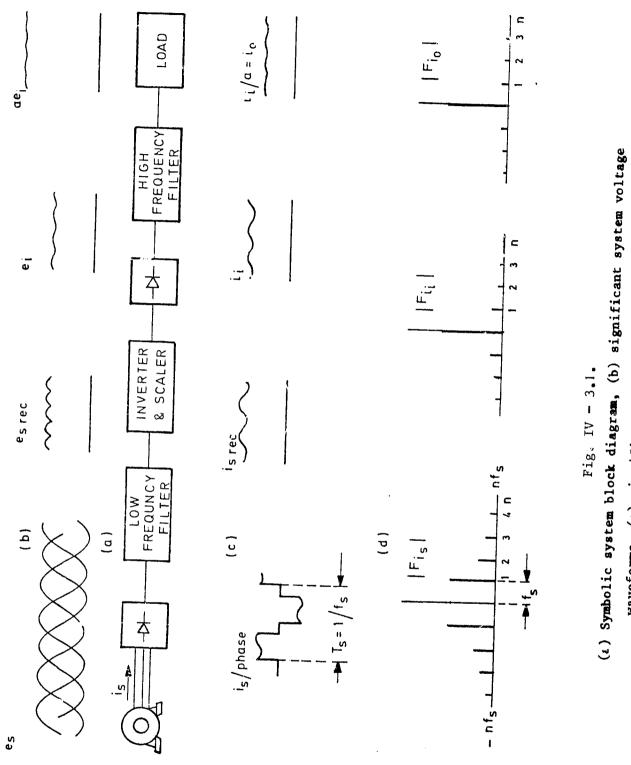

| 3.1. | <ul><li>(a) Symbolic block diagram, (b) significant system</li><li>voltage waveforms; (c) significant system current wave-</li><li>forms, (d) current wavefor frequency spectra.</li></ul>                                                                                                                                                                                             | IV - 41 |

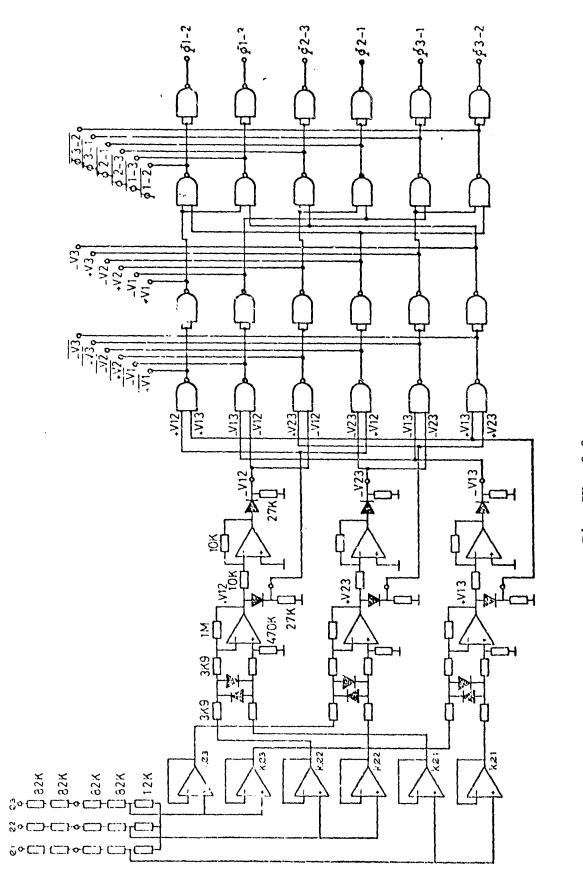

| 3.2. | Simplified electronic schematic of the logic for the generation of selection signals for the thyristors of the three phase cyclo-converter.                                                                                                                                                                                                                                            | IV - 44 |

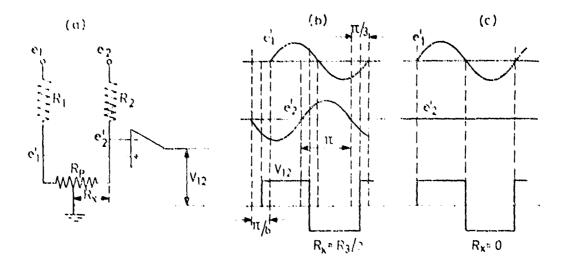

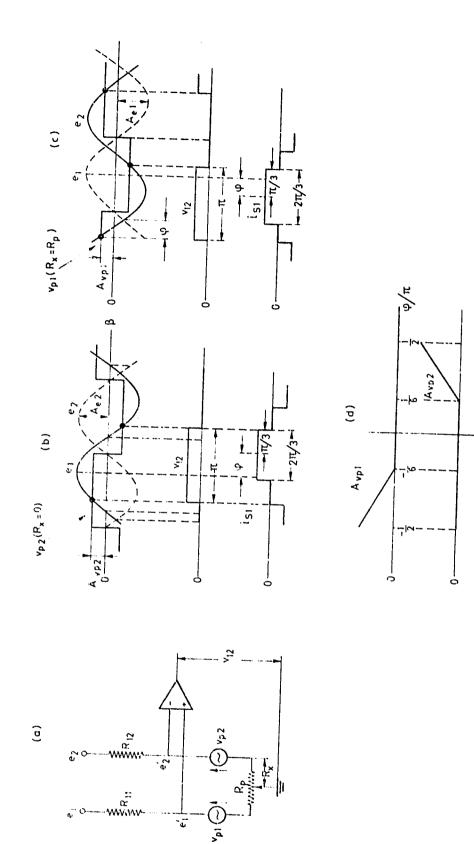

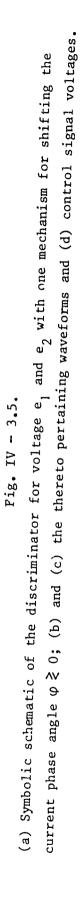

| 3.3. | (a) Symbolic schematic of a controllable phase voltage discriminator; its significant voltage waveforms, (b) for zero phase shift and (c) for 30 degrees ( $\pi/6$ radians) lagging of the phase current $i_{si}$ .                                                                                                                                                                    | IV - 45 |

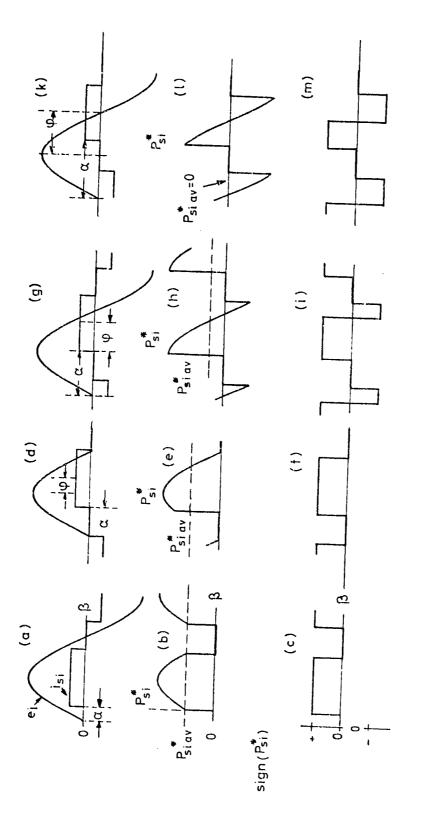

| 3.4. | Stylized waveforms of the voltages $e_i$ (i = 1,2,3), the<br>currents $i_{si}$ . the momentary power $P_{si}$ and the average<br>power $P_{si av}^{*}$ in the individual phases of the ac supply<br>for phase shift angles $0 < \psi < \pi/2$ of the current blocks<br>$i_{si}$ , with indication of the thereto pertaining direction<br>of momentary power flow sign $(P_{si}^{*})$ . | IV - 49 |

| 3.5. | Symbolic schematic of the discriminator for voltage<br>e <sub>1</sub> and e <sub>2</sub> with one mechanism for shifting the current<br>phase angle; (b) and (c) the thereto pertaining wave-                                                                                                                                                                                          | IV - 51 |

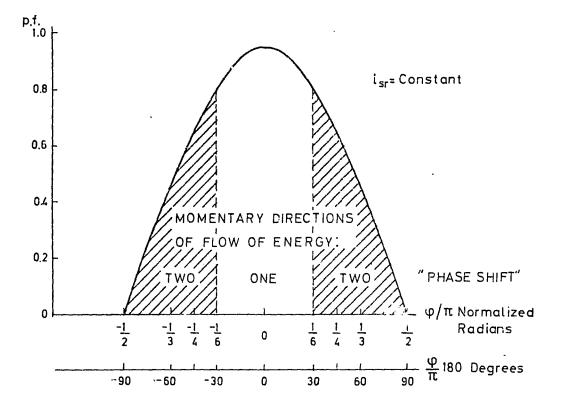

3.6. The power factor p.f. as function of the phase angle. IV - 56

- xi -

forms and (d) control signal voltages.

LIST OF TABLES

1

ŧ

ł

| No. | Title      | Chapter III                              |                            | page       |

|-----|------------|------------------------------------------|----------------------------|------------|

| I   |            | Gating and Firing<br>wer Transfer.       | g of Thyristors for        | III - 24   |

| II  | Gating Con | ditions for the Tl                       | aree Phase Cyclo-Converter | . III - 35 |

| 111 |            | ditions for the Du<br>for Power Transfer | ouble Sided DC Cyclo-      | III - 37   |

| IV  | Characteri | zation of Forward                        | Power Transmission.        | III - 57   |

| v   | Characteri | zation of Reverse                        | Power Transmission.        | III - 57   |

# Chapter IV

| 2.1. | Applicable Apparent Input Voltage e s*.     | IV - 8  |

|------|---------------------------------------------|---------|

| 2.2. | Number of Switching Elements per Phase.     | 1V - 33 |

| 2.3. | Comparative Component Weight and Power Loss |         |

|      | in a $D_{i}$ and AC/DC Converter of 3 kW.   | IV - 35 |

- xii -

#### L. INTRODUCTION

#### I = 1. The Problem

The need for the transformation of polyphase ac power with a given frequency to that of another frequency, including dc, arises in cases such as those involving: the controlled drive of machines, the efficient transfer of electric energy over high voltage dc lines and its temporary storage in secondary batteries, to name a few well known applications. Certain chemical and metallurgical processes require dc or deterministically mixed ac and dc power. Sophisticated equipment as computers or critical signal processors or monitors may require "no-break power". One can add the whole family of supplies of dc power which use the polyphase distribution network as primary source of energy common for communication, x-rays, radar and practically all electronic systems with a power consumption, in excess of several kilowatts.

A subgroup of the above named ac/ac and ac/dc converters requires a reversal of the controlled power flow. A common example is that of a battery charger, used for power "peak sharing" purposes. Low cost excess electric energy is stored in batteries at certain times of the day or night; this energy is then returned to the local or regional three phase network during the hours of peak demand. Valuable and, possibly, scarce fuel can be saved in this manner. The described process

I - 1

can be implemented by the use of two separate pieces of equipment, (1) a controlled rectifier filter and (2) an inverter. The same process can be, preterrable, performed by one single converter with a reversible flow or controlled power. It will be indicated further on that every process involving "reactive" power components requires a recurrent and rapid succession of reversals of the flow of energy in and out of a power converter.

The interface between a polyphase ac and a desystem is, traditionally, envisioned as the connection of two voltage sources with the corresponding characteristics via an appropriate passive low trequency filter. The interposition of this filter between the two voltage sources is necessitated by the requirement to

- a. avoid excessive currents that may arise from even minor and short lived differences between these voltage sources;

- b. allow the coonciliation of character of the concerned sources with the jointly transferred energy;

- c. prevent the "pollution" of either of the interlinked systems by the character of the opposite partner, namely ac or dc.

It is the primary objective of the here presented work to remove the need for a passive low frequency filter between two non-synchronized systems of the same or of different character. The implacable requirement

1 - 2

for an efficient reconciliation of the different characters of two interlinked systems is satisfied by providing the concerned converter with the capability to function as a non-dissipative active filter, concurrent with its performance of the function of transfer and control of the flow of energy in either direction.

The symbolic presentation of a controlled polyphase ac to de converter is shown in Fig. 1 - 1.1. The three phase ac source of supply of energy is presented as a voltage source which "works" into controllable impedances. These controllable impedances are meant to symbolize the "controllability" of power intake by the converter, independent of variations of the impressed voltage and of the character of each of the impedances as "seen" by the feeding phase pairs. The dc output is symbolized as a voltage limited controlled current source.

The chosen presentation implies that the dc output port is short circuit proof and that its voltage will adjust automatically to the load, as seen by the converter. A number of these converters can be, furthermore, parallelled without the peed for any specific precautions.

The main objective is to avoid the harsh conditions which are otherwise caused when two different voltage concrolled systems are interlinked.

1 - 3

rent source.

I -- 4

The converse of the system shown in Fig. I = 1.1, a de to ac inverter, is shown in Fig. 1 = 1.2. Here the power flow emanating from a de voltage source is controlled by the thereto connected variable impedance. The output ports are symbolized by three voltage limited current sources. The direction of transfer of energy is indicated in both figures.

The intended process is the converse of the one described with reference to Fig. L = 1.1. Again, a number of converters can be parallelled without the need for precautions to prevent excessive currents.

Energy can be transferred free of most customary hazards from one voltage source to another without concern for synchronization, momentary voltage excursions within design limits and the character of the linked systems.

An ac to ac converter could consist of a back to back tandem combination of the systems indicated in Figs. I = 1.1 and I = 1.2. A thorough integration of these two systems then removes the need for an internal de link. Such a system adjusts its input-output characteristics in such a manner that those ports which function as output ports assume momentarily the character of current sources.

I = 2. The Content of the Study

The technical problem area as a whole is the subject of this study.

I - 5

I - 6

A philosophy for the improvement of technology is outlined in chapter II of this presentation. This is followed by the experimental verification of the critical aspects of the improved technology in chapter III. An assessment of the significant aspects of the newly acquired improvements is presented in chapter IV.

#### **II. CONCEPT FORMULATION**

II - 1. Goals of Technology Improvement

Presented is an exploratory first approach to the technical problem of controlled bidirectional four quadrant (BD4Q) power transfer between a polyphase ac and a dc system, using high power freugency techniques.

Application of higher internal converter frequencies (10 kHz) is meant to improve the reliability of these devices, and to reduce their cost substantially. This improvement of cost is paired with an appreciable reduction of physical weight and size of the equipment.

In essence, it is intended to extend the power capability of space type equipment to the submegawatt range (order of 100 kW) with potential benefits of this technology for terrestrial use, such as for vehicular and stationary applications.

New characteristics of power conversion are sought, including the capability of extraction of ac power from a polyphase line at an arbitrarily determined power factor, independent of line and load conditions. Conversely, the same can be applied for return of electric energy to the polyphase line. This significant and intrinsic property, which has significant economic implications is not found in the state of the art equipment, even if voluminous and expensive filters were to be used.

11 - 2. Definition of a Representative System

A system that would embody the technology needed for implementation of the bidirectional four quadrant ac to dc converter, as described in A., part III of the Exhibit "A" of subject contract, is chosen for purpose of this study.

This system should, furthermore, be suited to meet the concerned design requirements of this contract as stated in B. part III of the same Exhibit "A".

A system is studied which:

- II 2.1. derives power from a conventional three phase ac supply line and transfers energy to an electric storage battery;

- II 2.2. can reverse the flow of energy so that electric power is delivered from the storage battery to the three phase supply line;

- II 2.3. embodies the potential to be modified and/or expanded to attain a maximum of the design goals stated in C., part III of the same Exhibit "A".

The above described system is devised to also satisfy the desired characteristics and the functional requirements formulated in part 11 - 3 of this report.

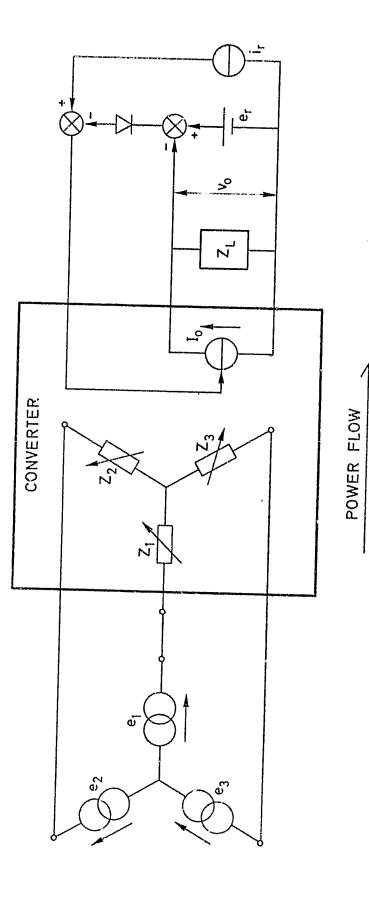

# Fig. 11 - 2.1.

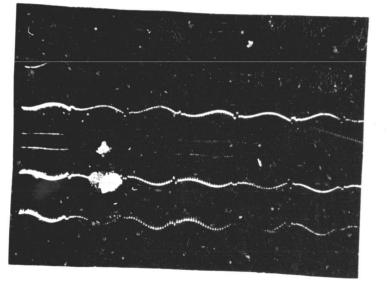

Conventional configuration of a three phase ac to dc converter with unidirectional transfer of electric energy with characteristic wave forms and some of their frequency spectra.

The conventional configuration of a three phase ac to dc converter with unidirectional transfer of electric energy as shown in Fig. II – 2.1. Parts (a) and (b) of this figure are self explanatory. A characteristic current waveform  $i_s$  in one of the phases of the ac supply line is shown in part (c) of that figure. The other sections in the same part (c) show the well known waveforms of the current in the various stages of the transformation process. The frequency spectra which pertain to these current waveforms are qualitativly indicated in part (d) of Fig. II – 2.1.

The above described system is limited in its capability to control the power transformation process in order to:

- (a) control the rate of charge of the battery according to a preset program or in response to appropriate feedback signals;

- (b) shape the frequency spectrum of the currents in the ac feeder lines to desired forms;

- (c) control the power factor as viewed from the three phase supply line.

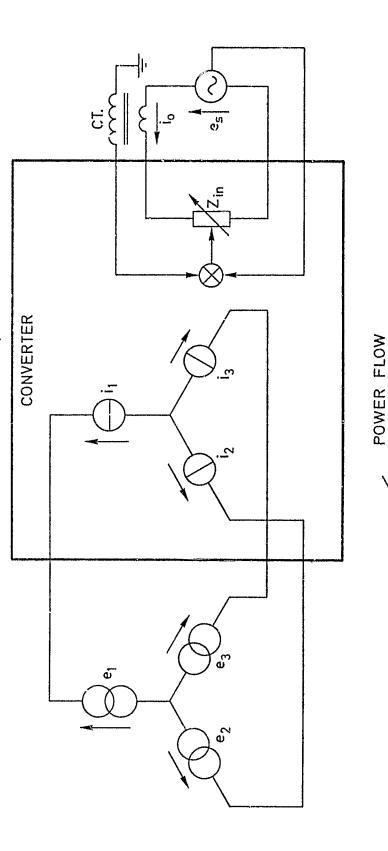

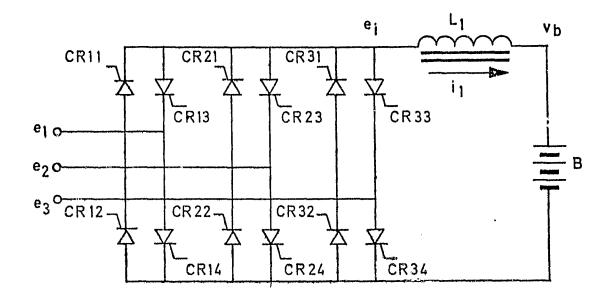

A more sophisticated ac to dc converter system for controlled bidirectional flow of electric energy is shown in Fig. II - 2.2 in the form of a three phase "antiparallel" full wave thyristor bridge. This system and its function is described in the literature [1].

#### Fig. II - 2.2.

Symbolic schematic of bidirectional three phase ac to dc converter, used as battery charger.

The thyristors are selected to conduct current by the application of trigger signals to their gates. These thyristors are selected in pairs according to (1) the relative polarity of the phase voltages  $e_1$ ,  $e_2$  and  $e_3$  and (2) the direction of transfer of energy. Thyristors CRi1 and CRi2 (i = 1, 2, 3) can transfer energy from the ac supply line to the battery B. Conversely, will thyristors CRi3 and CRi4 transfer energy from the battery to the ac supply line. Each of these two groups operates in pairs thus connecting the two of the three phases at one time to the battery or vice-versa. If "full" voltage  $e_i$  is desired, where  $e_i$  av =  $v_b$ , then all thyristors of the group CRi1 and CRi2 are fired in such a manner that this group functions as a full wave diode bridge. This is further discussed with reference to Fig. II - 2.3(a). Operation of a diode bridge is

Rectified three phase voltage wave form of (a) full wave diode bridge and (b) full wave thyristor bridge, with indication of intervals,

performed if phases with voltage  $e_1$  and  $e_2$  are connected to the battery in the interval marked 1-2; phases with voltage  $e_1$  and  $e_3$ in the interval 1-3, and so on. The respective pairs of thyristors are fired accordingly as discussed with reference to Fig. II - 2.2. The firing signals are provided by a control system which does, at this time, not enter the discussion.

If it is desired to reduce the average value  $e_{i av}$  of the voltage  $e_i$ , then this is accomplished by delay of the firing signals beyond the intervals i-j (i, j = 1, 2, 3; i  $\neq$  j) as indicated in Fig. II - 2.3(b). For instance thyristor CR32 which should connect phase No. 3 to the charger system is not fired at the end of interval 1-2. Its firing instant is delayed to a point in the interval 1-3.

The average voltage  $e_i$  av(1-2) in this interval

$${}^{T/6+T}_{a} = {}^{6}_{1} \{f(e_{1} - e_{2})dt$$

$${}^{T/6+T}_{a} = {}^{6}_{T} \{f(e_{1} - e_{2})dt$$

$${}^{T}_{a} = {}^{7}_{a}$$

$$(2.1)$$

with

- T = the period of one cycle of one phase of the ac wave in the three phase supply line;

- $T_a$  = the delay introduced for the firing of thyristors CR11 and CR24 after the start of the interval 1-2 and of CR32 after its termination.

Evidently is  $e_{i av(1-3)T_a}$  a maximum when  $T_a = 0$  and decreases with increasing  $T_a$ . It is envisioned that firing of all thyristors in the "line of firing" is delayed by the same delay time  $T_a$  so that the length of the individual intervals in which two thyristors conduct remains the same, namely T/6, yet all of these intervals are shifted by a delay  $T_a$  to the right compared to the corresponding intervals shown in figure 2.3.

The average voltage  $e_i av(1-3)T_a$  is, eventually, reduced to zero, even though the instantanuous values of  $e_i \neq 0$ , except at isolated

points. This is described in great detail in the literature [1]. Control of the average output voltage  $e_{i av}$  is thus attained as a function of the above discussed delay  $T_a$  of firing instants.

The price for the described process of control is the tolerance of more or less serious deviations of the waveforms of the currents in the individual phases of the supply line from sinusoidal shapes. These deviations give cause to the generation of higher harmonic components and peor power factors in the ac supply line which in turn cause unproductive heating of the supply line and the thereto connected generators |1|. This is a feature which is still being tolerated by the utility companies because of (1) the relative rarity of connected power electronics equipment of appreciable single or cumulative size and (2) the lack of low cost wider band wattmeters and power factor meters to record the actual effort of the supplier of electric energy in order to provide the average power to the battery in its various stages of charging.

The above referred to adverse effects on the supply line can be mitigated, or avoided by having the thyristor bridge shown in Fig. II -2.2. preceded by an ac filter which (1) reduces the higher harmonic content in the phase currents and (2) corrects the power factor. As a corollary it is necessary that the inductor  $L_1$  be sufficiently large as to smoothe the current  $i_1$  in order that the battery would not be, unnecessarily heated by its harmonic content. It is thus necessary to mitigate the distortion of the current waveform

introduced on both sides of the thyristor bridge by its inherent process of operation. The above referred to price is thus translated into appreciable bulk and cost of filters.

Another disadvantage of the described process is the limited speed of response of the system to an externally given or internally gener red command. This limited speed of response is rooted in (1) the minimum switching intervals T/6 or approximately 2.74 msee in a 60 Hz supply line and (2) even more so, the needed heavy filters, referred to above, with time constants far in excess of T/6. This limitation in the speed of response may not be a matter of concern for a battery charger. It becomes, however, a problem when the direction of transfer of energy is reversed.

In the case of de to ac inversion it is necessary that the flow of current into the individual phases is guided by the momentarily present conditions of voltage and current in these phases so that (1) the power factor in the line can be matched, or ever corrected, (2) a minimum of harmonic distortion enter the line and (3) unexpected time varying conditions can be met, such as transient phenomena. Concurrent meeting of the above enumerated requirements cannot be achieved by use of a preprogrammed system. A system is required that adjusts its transfer characteristic almost from instant to instant as to taylor its output to the momentary line conditions. This cannot be achieved by use of a low frequency system which is burdened, furthermore, with heavy filters. The term "low frequency" is used here in the sense that the shortest time intervals for realignement

11 - 9

of the system are not substantially shorter, but are in fact the same as the time intervals during which the current should be taylored, thus reducing the intended task to an impossiblity.

The above described problem area concerning the power factor and the harmonic distortion of current by theristor bridges has its roots in the abrupt switching action of the electronic devices, compounded by thrifty use of materials in friters. This is explained with reference to Fig. 11 < 4.4. The nth phase which feeds a three

Fig. 11 - Carta

Waveform of (a) voltage  $e_n$  ( $n \in 1, 2, 3$ ) and (b) typical current  $i_n$  in one of the phases of the three phase supply line for a full wave bridge coefficientiliter.

phase rectifier-filter bridge "cuts in" at an angle  $\pi/6$  after  $e_n = 0$  and  $de_n/dt \geq 0$ , when its voltage exceeds that of the formerly conducting other phase. Current  $i_n$  which was zero at that instant rises to a level prescribed by current  $i_1$  in the inductor  $L_1$ . The shape of the top of the shown current pulse depends on the size of  $L_1$  and the degree of loading of the system. The most favorable shape is that of a horizontal top which is indicated by a broken line. This condition occurs when  $L_1 \neq \infty$ . Current  $i_n$  terminates at the angle  $5\pi/6$  when another phase "cuts in" and assumes conduction of the current  $i_1$ .

The power factor p.f. in each of the three phases is given by

$$p.f. = \frac{0}{e_n rms^{-1} n rms}$$

(2.2)

when defined in the time domain |2|. This power factor is approximately .955 when  $L_1 \rightarrow \infty$ ; it decreases when  $L_1$  is reduced to manageable sizes and deteriorates rapidly with decreasing  $e_1$  av as explained before.

This deterioration of the power factor is caused by:

the shift of the intervals of current conduction i-j to the right with respect to the voltage sine wave, as explained before;

(2) the increasing "distortion" of the waveform of i<sub>n</sub>, whose individual pulses, eventually, reach into the range of opposite polarity with respect to e<sub>n</sub>. The transfer of energy to the filter-load network ceases eventually since the numerator in question (1.2) becomes zero. The power factor is then reduced to zero.

This deterioration is compounded by the effects that are caused by the limited size of inductor  $L_1$ .

An analogous argument can be made for the reversal of flow of energy, namely from the battery to the three phase line. Here the process of power transfer is also controlled by the firing angles of the thyristors. Yet, the whole process is at the mercy of ac line conditions, the battery voltage, and the desired magnitude of power transfer. There is no degree of freedom left in the system to taylor the harmonic content of the  $i_n$ , which flow now in the reverse direction, and/or to control the contribution of this power transfer to the power factor in the line.

The above described adverse effects on power factor and harmonic content of the current manifest themselves in the form of heat which does not contribute to the transfer and transformation of power.

A suppression of the described effects by use of heavy low frequency filters is possible. The use of filter elements which can store appreciable quantities of electric energy creates the hazard

11 - 12

of unexpectedly high current peaks under dynamic conditions of system operation. These current peaks are difficult to control, to say the least; they can imperil the structural integrity of the thyristors.

The representative system which was defined at the outset of this part of the report should provide substantial improvements and alleviate the problems which exist in the state of the art, as discussed above.

II - 3. Formulation of Needed System Concept

II - 3.1. Desired Characteristics

1

It is intended to improve the technology of the class of electric converters, which comprises the representative system described in II-2. The power range of interest is in the order of 100 kW. Yet, it is intended to clear the way for an expansion of the power level of these converters toward the megawatt range.

The needed system characteristics should include improvements in order to increase the:

a. power density of converter equipment, expressed in kW/kg;

- b. reliability of this equipment by (1) confining the absolute instantanuous and transient stresses on critical components, such as semiconductor switching devices to unconditionally predictible limits, even under the most adverse operating conditions and (2) to minimize the ratio of steady state peak vs. average stresses in the same critical components;

- c. efficiency of power conversion by (1) containment of the current form factors  $\rho_i = i_{1 \text{ rms}}/i_0$  rms where  $i_1$  is the significant internal converter current and  $i_0$  the output current(s) and (2) minimization of power losses in the switching devices by appropriate tayloring of their functions within circuits which are devised to lessen the stress on these devices, also indicated under b.;

- d. dynamic characteristics of these converters, with particular emphasis on reaction speed to externally imposed changing conditions or to applied control signals;

- e. cost effectivness by (1) sparse use of raw materials such as iron and copper causing (1a) lowering of raw material cost, (1b) cost of handling of materials and equipment during manufacturing, transportation, installation and maintenance work, (2) lower frequency of maintenance due to improved reliability and (3) lowering the losses of energy in the equipment, due to improved efficiency, as stated under c.

HI = 3.2. Functional Aspects

A number of functional aspects of converter operation will have to be satisfied on the way in order that the converter acquire the desired characteristics, stated in II - 3.1 above. These functional aspects will be treated in a way that holds the promise for an expansion of the resulting technology to a multitude of electric power transformation processes. This is meant to be, in particular, consistent with the Specifications contained in part III of Exhibit "A" for bidirectional three phase ac to dc conversion.

The functional aspects of the class of converters under considerations which appear to be needed for a materialization of the above listed desirable characteristics require basic functional concepts to;

- a. derive power from a source of three phase ac power with a power factor in excess of 0.85 for all conditions of loading;

- b. confine the power derived as stated under a. at any instant to the first and the third quadrants of the  $V_{AC} - I_{AC}$  plane only;

- c. cause a minimum pollution (current distortion) in the ac feeder lines;

- d. supply regulated de voltage or current with deviations of no

II = 15

more than 1 % from a nominal value to a dc load, such as a battery operating in the first quadrant of the V<sub>DC</sub> - I<sub>DC</sub> plane only;

- e. derive power from a source of dc energy via the same terminals through which power was supplied as stated under c. with a dc power factor of no less than 0.85 in accordance with equation (2.2) and operating in the second quadrant of the  $V_{DC} - I_{DC}$ plane;

- f. supply power emanating from the dc source stated under e. into n three phase ac line, causing a minimum network pollution in doing so; perform that supply of electric power, preferrably, in the second and the fourth quadrants of the  $V_{AC} - I_{AC}$  plane;

- g. provide galvanic isolation between the input and the output terminals of the converters, as viewed from both directions of transfer of energy;

- h. endure progressive overloads and external fault conditions including shorted output terminals without damage to the converter;

- i. be capable of power flow directional changes within no more than 1.0 milliseconds and to apply measures for the stabilization of external conditions within the same time interval.

Efforts were made to incorporate the above enumerated functional aspects in the converter concept which is described in the following part 11 - 4.

II = 3.3. Philosophy of Functional Concept

In order that the system characteristics stated in II - 3.1 and the therewith associated functional aspects stated in II - 3.2 be achieved it appears necessary to introduce the following functional properties. Planned is a converter device which:

- (a) extracts electric energy in pulsating form at a kHz rate directly from the three phase ac line without interposition of a low frequency - 360 Hz - filter;

- (b) functions as a nondissipative active filter in order to:

- (b1) perform the spectral transformation indicated in figure 11 2.1(d);

- (b2) scale and stabilize the system output (load) voltage v;

- (c) has a high degree of reliability, demonstrated by its inherent short circuit capability;

- (d) has a high energy density (kW/kg), or conversly, has a light weight due to the complete absence of low frequency (up to several hundred Hertz) components, because of its high internal

11 - 17

frequency of operation in excess of 10 kHz;

(e) generates little heat because of its inherent efficiency;

The following advantages are expected:

11 - 3.4. Expected Benefits

(a) an adaptation of the waveshaping processes to the requirements of generator and load which is presently not possible in efficient light weight equipment;

(b) ultra light weight of equipment due to:

- (b1) elimination of all low frequency components between generator and load, including the elimination of entire (heavy) functional blocks;

- (b2) use of high internal frequencies of operation in excess of 10 kHz.

11 - 4. Functional Concepts for the Planned System

II - 4.1. General System Concept

þ

A system that appears capable to embody the properties described

## Fig. II - 4.1.

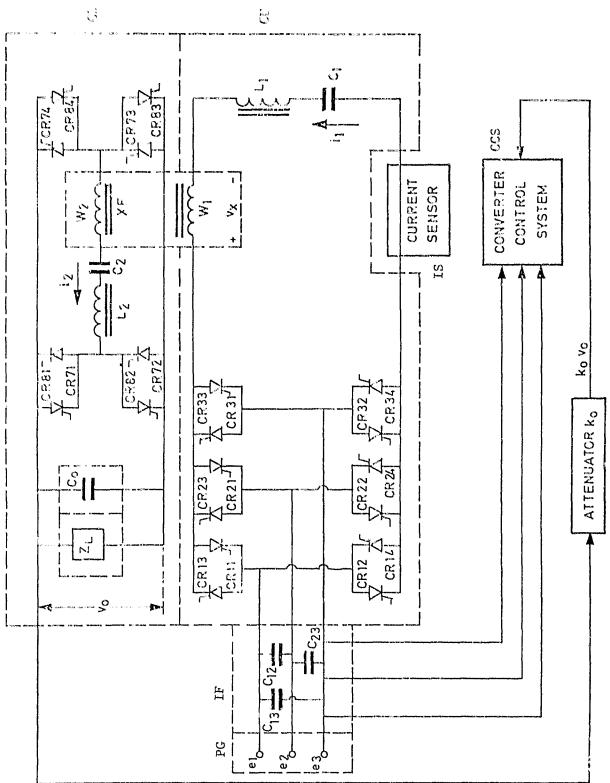

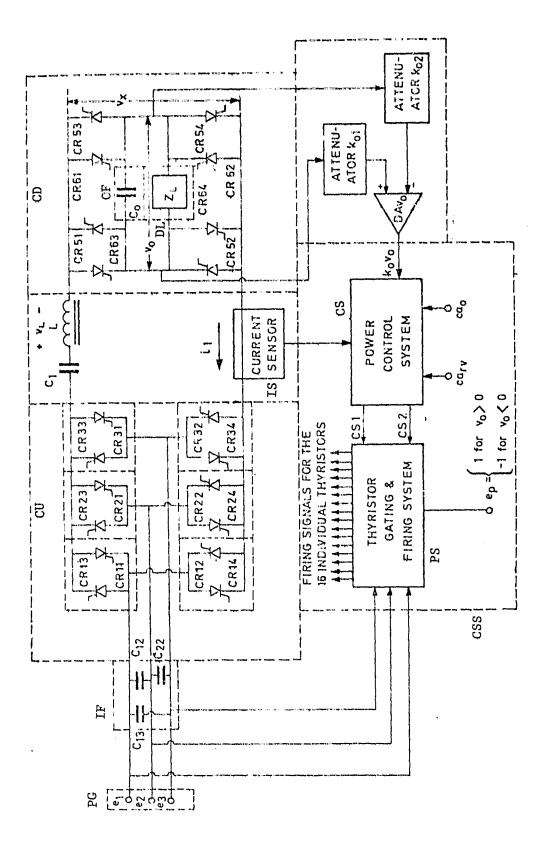

Symbolic block diagram of bidirectional, four quadrant three phase ac to dc converter using a modulated high frequency carrier link. in the preceding part II = 3 of this report, is now described with reference to Fig. II = 4.1. The three phase supply line (PG) is connected via a high frequency low pass filter (IF) to the input stage of the power converter in the form of a four quadrant controlled "cyclo up" converter.

This cyclo up converter extracts energy from the supply line which is used to generate a high frequency (10 kHz) single phase modulated carrier oscillation with current  $i_1$ . The above described transformation process occurs in a nondissipative way with use of a thyristor matrix which will be described further on. The carrier waveform  $i_1$  is both frequency and amplitude modulated to mitigate its own harmonic content with a fundamental 360 Hz frequency, or to accomodate the low frequency spectrum desired in the supply line, or for any other intended purpose, such as power factor correction.

The low frequency content of the above described carrier is then "detected" through rectification by way of a four quadrant controlled cyclo down converter (CD) and by subsequent filtering by a high frequency low pass filter (OF) with a cut off frequency below the lowest frequency of the carrier oscillations.

All operations are being carried out in a nominally nondissipative fashion by use of matrixes of "on-off" thyristor switches supported by filters and other circuits which contain solely reactive elements.

The philosophy for the generation of a modulated high frequency

carrier for purpose of the spectral transformation of the source signal as it appears to the cyclo-converter process is treated in the literature [3, 4, 5, 6].

The two four quadrant controlled cyclo up down converters are equipped for equivalent bidirectional operation. It means that each of these converters can generate a modulated carrier in the above peferred to sense, when viewed from one set of its ports and can selectivly demodulate a modulated carrier when viewed from the other set of ports.

Based on this bidirectional characteristic of these cycloconverters it is possible to reverse the above described flow of energy. A source of electric energy (DL) in form of a battery can energize the four quadrant controlled cyclo up converter (CD) via the (high frequency) low pass filter (OF). A modulated carrier with current i, is generated, which is demodulated by the four quadrant cyclo down converter. The outcome of this demodulation process is distributed in sequence to selected pairs of the three phase line. The electric dc energy emanating from the battery is thus transferred to the ac line.

During the above described dc to three phase ac inversion process it could be advantageous to modulate the carrier with current i in order to (1) convey current with a desired low frequency harmonic content to the individual phases of the polyphase supply line, and

(2) to determine the power factor for this transfer. This is further discussed with reference to Fig. II - 4.2. Illustrated is

#### Fig. II - 4.2.

Phase (a) voltage  $e_n$ , (b) demodulated carrier current  $i_{sn2}$  and (c) filtered current  $i_{sn1}$ , during transfer of electric energy to the polyphase line.

the case in which the carrier is not modulated. The "detected" current  $i_{sn2}$  consists of a succession of uniform pulses which are distributed to the individual phases in such a way, that their smoothed form  $i_{sn1}$  is the replica of the phase currents in a three

II - 22

and the second sec

phase supply line which feeds a full wave rectifier diode bridge, followed by an infinitely large inductor.

The just described mode of operation could be desirable in many cases. Yet, there are three degrees of freedom inherent in this process.

- (a) The time interval T<sub>a</sub> introduced with reference to Fig. II-2.4 with a minimum value of T<sub>a</sub> = 0 can be enlarged or reduced at will. It means that the current blocks shown in Fig. II-4.2(c) can be shifted, arbitrarily, with respect to the voltage sine wave for any polarity. Shifting of these blocks in time does not have an effect on the harmonic content of the current, but provides control on the power factor with which the electric energy is transferred to the polyphase line.

- (b) The uniform amplitude of the current blocks i<sub>snl</sub> can be controlled by adjusting amplitude and frequency of i<sub>l</sub> in a way that a specific amount of charge per second is processed by the detector.

- (c) The shape of each of the blocks of the current i snl can be taylored by appropriate modulation of the carrier.

The advantage of these properties of the presented system is that the waveform of the current  $i_{snl}$  can be taylored at will to control.

- (al) the power factor with which energy is transferred to the polyphase network;

- (bl) the magnitude of the current i and, and

- (c1) the power factor correction in the polyphase line which can be achieved by the combined carrier modulation and current pulse shifting process explained under (a) above.

The preceding argument concerning the transfer of electric energy can be equally applied for the case of "forward" transfer of energy. Control of the average current is attained by adjustment of the average value of each half cycle of the carrier current  $i_1$ . The individual phases carry then the current  $-i_{an1}$  shown in Fig. II-4.2 or the flat top pulses (broken top line) in Fig. II-2.4. These phases "see" thus an imaginary inductor behind the full wave rectifier bridge. This effect is accomplished by appropriate control of the carrier with current  $i_1$ . The freedom to shift the current pulses with respect to the voltage sine wave and to taylor its tops is retained, if so desired, in order to meet specific supply line conditions, such as to improve the power factor in the line concurrent with the charging process.

The advantages of the here described system over the state of the art in form of the "antiparallel" thyristor bridge are rooted in the facts that: (1) the phase currents can be initiated and terminated

at will at any instant of time and (2) form and harmonic content of these phase currents can be deterministically taylored by an active filtering process. A minimum of passive component effort i3 required because of the relativly high frequencies, involved in this process.

The approach for the implementation of the above described system concepts is presented in the following.

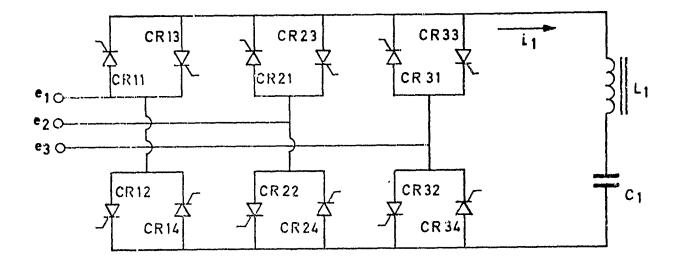

11 - 4.2. The Bidirectional Series Capacitor Inverter Converter

A power circuit which can embody the properties, presented in the preceding section is now discussed with reference to Fig. II-4.3. The thyristor bridge in block CU is fed from a three phase supply line (PG). The just described configuration is identical with the thyristor bridge shown in Fig. II-2.2. This thyristor bridge is connected to the primary winding of a transformer XF, the inductor  $L_1$  and capacitor  $C_1$ , all named elements being arranged in scries. The secondary winding of the transformer is connected via another series resonant circuit  $L_2C_2$  and another thyristor bridge (CO) to the load  $Z_L$  which is parallelled by the filter capacitor  $C_C$  (OF). The secondary circuit can be thought of as being reflected via the transformer back into the primary circuit whereby  $L_1C_1$  and  $L_2C_2$  are thought of as being embodied in one  $LC_1$  combination.

Fig. 11 - 4.3.

Ł

Symbolic schematic of bidirectional four quadrant series capacitor inverter-converter.

Fig. TT - 4.4.

Equivalent circuit of the symbolic schematic of the bidirectional series capacitor inverter-converter shown in Fig. TT - 4.3.

The resulting equivalent circuit is shown in Fig. II-4.4. The further discussion is continued with reference to this figure for purpose of simplicity of presentation. Yet; the circuit shown in Fig. II - 4.3 is meant to be used for the intended purpose.

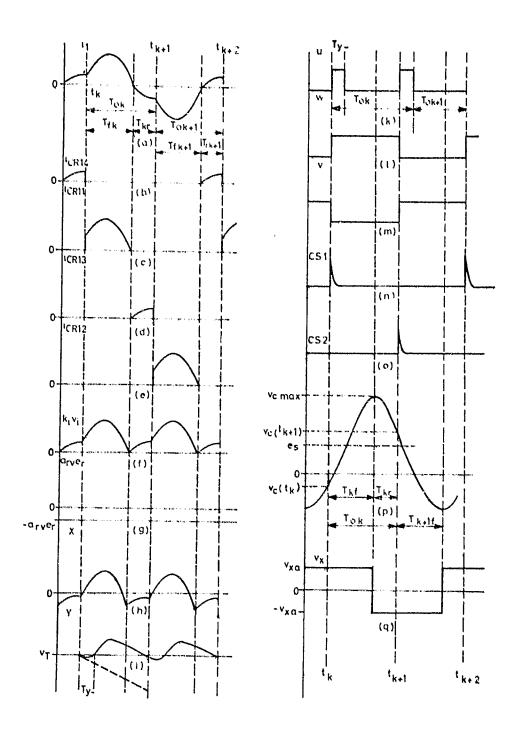

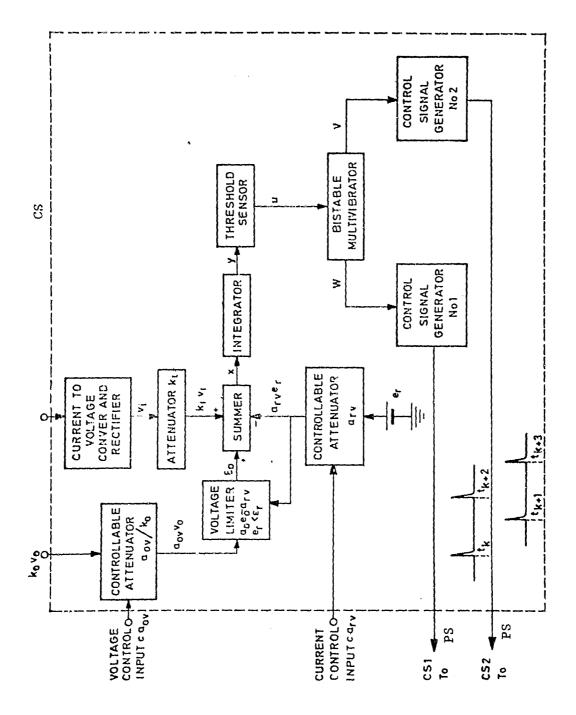

Two phases of the supply line (PG) are, at a given time, connected via two thyristors of bridge CU the series resonant  $LC_1$  link and two thyristors of bridge CD to the load (DL) which is shunted by the filter capacitor  $C_0(OF)$ . All concerned four thyristors will conduct in the discontinuous current mode for one half period of the resonant frequency

(4.1)

$$f_{i} = 1/2\pi\sqrt{LC_{l}} = 1/2T_{o}$$

where

$T_{o}$  = the half period of the resonant circuit.

All four thyristors will open at the termination of this half cycle because current i<sub>1</sub> reverses its direction of flow. It is this process of natural commutation which allows termination of current in any of the supply lines at any time. The expression "any time" is, of course, meant in the sense that

$T_{o} << T/6$  (4.2)

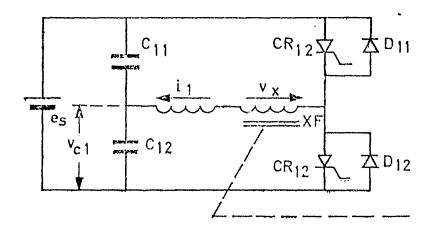

It is assumed that the four thyristors in question were the thyristors CR11, CR51, CR54 and CR24. It means that we operate in the interval 1-2, as discussed with reference to Fig.11-2.3 so that  $e_1 > e_2 < e_3$ . Inequality (4.2) implies that the phase voltages  $e_1$  and  $e_2$ , actually, stand almost "still" in time. If we ignore at this time the moderate variations of  $e_1-e_2$  within the interval 1-2, as referred to before, then the functional philosophy of a de converter of the described class applies [6, 7]. The resonant current  $i_1$  reverses direction when thyristors CR13, CR53, CR52 and CR22 are triggered into conduction. Thyristors CR13 and CR22 now assume the function of the "antiparalle1" diodes D11 and D12 shown in the half bridge configuration of this class of de converters. The just referred to circuit is reproduced here for convenience. All voltage and current waveforms in the LC<sub>1</sub> circuit are analogous to those explained for the circuit shown in Fig.11-4.5.

Fig. 11 - 4.5.

Symbolic schematic of the primary circuit of a series capacitor inverter-converter in half bridge configuration.

11 - 29

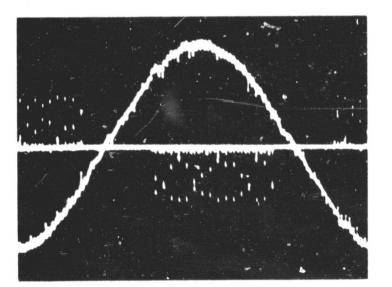

The respective waveforms are reproduced for convenience in Fig. II – 4.6. The role of the various capacitors is now explained. Capacitor  $C_1$  in Fig. 11-4.4 assumes the function of both capacitors C11 and C12 in Fig. 11-4.5 Capacitor  $C_0$  performs the function of the (high frequency) low pass filter (OF), explained with reference to Fig. II – 4.1. Capacitors C12, C13 and C23 perform the function of the (high frequency) low pass filter (IF) explained with reference to the same figure.

One can view the presented system in each time interval i-j, referred to before, as a converter fed from a de source with a moderate voltage ripple. The effects of this ripple are being removed by a control system which embodies an advanced version of the analog signal to discrete time interval converter (ASDTIC) [3, 4, 5, 6].

The "forward" operation of the system thus consists of a succession of time intervals i-j during which it selects two of the three phases with the most appropriate voltage difference in order to perform the customary operation of a dc converter of this class.

A number of simplifications was introduced in the preceding explanation for purpose of simplicity of presentation. The complexity which is needed for purpose of a three phase ac to de operation or its inverse will be gradually indicated as the explanation of the system progresses.

The process of transfer of energy from the battery to the three phase line is analogous to the above described "forward" transfer. In this

11 - 30

11.4

Fig. II - 4.6.

Significant voltage and current waveforms in the series capacitor converter.

. ا

case it is assumed that the battery voltage  $e_b = v_o$ , the voltage over the load  $Z_{1}$  shown in Fig. 11-4.4, since the battery replaces this load. The thyristor bridge (CD) associated with  $Z_{I_{\rm c}}$  becomes now the input of a full bridge series capacitor inverter-converter, whose functional properties are analogous with those of its half bridge version [6]. There are, again, four thyristors in conduction at any time; two thyristors of the "battery bridge" (CD) and two thyristors of the dc/ac bridge (CU), so that the battery is connected during each of the carrier frequency cycles to two selected phases of the three phase power line. Assume that thyristors CR62, CR63, CR13 and CR22 are in conduction in the time interval 1-2. One high frequency current pulse is then generated which enters the phase pair with voltage e, and e2. This pulse can be one of the pulses shown in Fig. II - 4.2 with a polarity which is the opposite of that of the thereto pertaining phase voltage, because of the direction of power flow. When the resonant current has run its course, then thyristors CR11, CR51, CR54 and CR24 are fired in order to back bias the formerly conducting thyristors for an interval

$$T_{\rm kr} \ge t_{\rm off}$$

(4.3)

where

t<sub>off</sub> = the turn off time of the thyristors.

This is also expressed in radians as

$$\Psi_{\mathbf{r}} \stackrel{<}{=} \Psi_{\mathbf{r}} \min \tag{4.4}$$

1

where

$$\psi$$

r min =  $\omega \sigma^{T}$ kr min

Thyristors CR61, CR64, CR14 and CR21 are then fired after elapse of the interval  $T_{kr}$  which is also determined by the control system. The battery feeds again charge in form of one current pulse into the phases with voltage  $e_1$  and  $e_2$ .

The described process goes on with the assumption that, again, time stands "still", that is, the voltage difference  $e_1 - e_2$  changes only moderately within the time interval 1-2. Clearly, the thyristor bridges CU and CD have changed roles. Bridge CU is now the input bridge and CU the output bridge. Instead of a source voltage ripple we have now a load voltage ripple to contend with. Selection of the phase pair is made according to the relative polarities of  $e_1$ ,  $e_2$ , and  $e_3$  which results in a succession of intervals 1-2, 1-3, etc. in which energy is transferred to the respective phases.

The pulse pattern is governed by the same ASDTIC type control system as discussed before with the three degrees of freedom which were previously enumerated in order to satisfy requirements on the harmonic content of phase currents and the power factor of

energy transfer into the polyphase line.

If one looks back on the sequence in which the thyristors of the first phase CR1i (i = 1, 2, 3, 4) operate, then it becomes obvious that, for instance, thyristors CR11 and CR13 change roles depending upon in which direction energy is being transferred. That is, thyristor CR11 carries the main pulse and thyristor CR13 acts as the back biasing "diode" when energy is being transferred from the polyphase line to the battery. Conversely, thyristor CR13 carries the main pulse and thyristor CR13 carries the main pulse and thyristor CR13 carries the main pulse and thyristor CR11 acts as the back biasing "diode" when energy is being transferred from the battery to the polyphase line. This is further explained with reference to Table II-4.1. The sequence (S) of thyristor conduction during "forward"

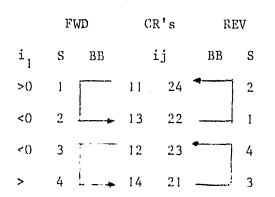

#### Table II = 4.1.

Sequence (S) of conduction of thyristors CRij in the bridge CU during the time interval 1-2 for "forward" (FWD) and "reverse" (REV) transfer of energy, including requesite back bias (BB) conditions.

(FWD) and "reverse" (REV) transmission of energy through the first two "legs" of the bidirectional cycloconverter CU is more detailed indicated. Curved arrows point, furthermore, to the individual pairs of thyristors which are fired once an adequate back bias is ascertained for the thyristor pairs from which these arrows emanate. It appears easy to expand Table II-4.1 to cover all conditions of thyristor conduction in the time intervals i-j to supplement the table shown in Fig. II - 4.7.

The automatic and unfailing mechanization of the therewith associated back bias detection, interpretation and protection against untimely firing of thyristors is one of the important, if not the most important technical feature of this system; it is requesite to its successful materialization.

A summary for the selection of thyristors as function of the phase voltages, the thereto pertaining time interval i-j and of the direction of flow of current  $i_1$  is given in the lower part of Fig. II - 4./.

The upper part of the same figure shows the thyristor bridge CU connected to a closed resonant LC<sub>1</sub> circuit with current i<sub>1</sub> for purpose of identification of the respective switching elements. The abbreviation FWD is used for "forward" and REV for "reverse" transmission of electric energy.

| PHASE VOLTAGES<br>OPERATING PHASES |                    | e1 > e2<br>1 - 2 | e1 > e3<br>1 - 3 |   | e2≯e1<br>2−1     | e3>e1<br>3-1    | e3≯e2<br>3−2     |

|------------------------------------|--------------------|------------------|------------------|---|------------------|-----------------|------------------|

| THYRIS<br>TOR<br>PAIRS<br>CR       | i₁≻0 FWD<br>REV    | 11, 24<br>14, 21 |                  | • | 21, 14<br>24, 11 |                 | 31, 24<br>34, 21 |

|                                    | iii < 0 FWD<br>REV | 13, 22<br>12, 23 | 13, 32<br>12, 33 | • | 23,12<br>22,13   | 33, 12<br>32 13 | 33, 22<br>32, 23 |

# Fig. II - 4.7.

Antiparallel thyristor bridge and series resonant circuit with identification matrix of thyristor firing selections.

II - 36

۱

II - 4.3. Assessment of Significant Physical Features.

The two most important features of the presented system are (1) the natural current commutation of the thyristors by virtue of the series resonant  $LC_1$  circuit and (2) the complete absence of power frequency low pass filters. The first feature allows efficient thyristor operation at frequencies near 10 kHz; the second makes it possible to use capacitors, eclusivly, for purpose of filtering current pulse trains at 10 and 20 kHz.

The functional aspects of the "output" capacitor  $C_0$  are discussed and explained in the literature |6, 7|. The "input" capacitors C12, C13 and C23 appear here in a new light. Their primary purpose is to close the resonant circuit and to shield the polyphase line from the effects of its high frequency operation. These capacitors carry at the same time a low frequency current which is caused by the voltage difference between each of the two lines of the three phase system. The ratio of admittances for the low frequency signal  $Y_s$  and for the pulse repetition rate  $Y_F$ .

$$Y_{\rm F}/Y_{\rm 3} = f_{\rm F}/f_{\rm S} \approx 333$$

(4.4)

for

$$f_{\rm F} = 20 \ 10^3 = 2f_{\rm i} = 1/T_{\rm ok av}$$

$f_s = 60 \text{ Hz}$

The relatively high pulse trequency of approximately 20 kHz makes its possible to place these capacitors between the low frequency power phases, without causing an appreciable leading current effect in the polyphase supply line.

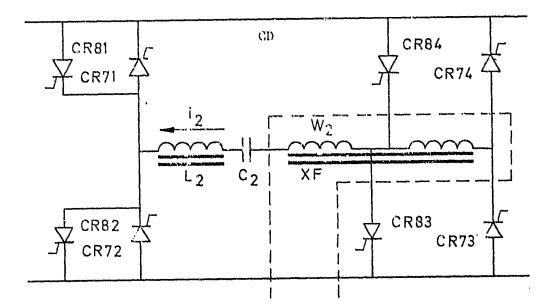

The thyristor bridge (CD) associated with the battery circuit will be modified for purpose of convenient reversal of flow of energy as indicated in Fig. 11-4.8. Transformer XF has a tapped

Fig. 11 - 4.8.

Thyristor bridge associated with de circuit.

secondary winding in order to implement a different turns ratio of the transformer for forward and for reverse transfer of electric energy through the converter. 11 - 4.4. The Control System

The electronic control system (CCS) consists of:

- (a) the thyristor gating and firing system, a protection system (PS) which governs the sequence of firing of thyristors and prevention of accidental "illegitimate" firings;

- (b) the power control system (CS) which governs the process of high frequency carrier generation and its modulation.

The function of the thyristor gating and firing system was described in II-4.2 above. It is in essence, analogous to the protection system used in simple dc converters in this class |8, 9|used for ion propulsion engines. However, there are aspects of considerable added complexity associated with its functions, especially concerning the connections with the ac polyphase line. To use the terminology associated with the half bridge converter of this class of converters shown in Fig. II-4.5, this protection system has to distinguish, unerringly, which two of the three phases of the supply line have to be engaged for power flow in one or the other direction; which of these thyristors will remain in a forward biased condition once it ceases to conduct and thus requires thus a grace period (turn off time) in the form of back bias; which of these thyristors will carry the "main" forward resonant current, whatever the forward direction may be in the sense of energy transfer; and, finally, which of the thyristor assumes the "diode" function in the sense of the half bridge circuit for a given pulse.

The protection system for the dc output or input of the converter is somewhat less complex. Yet, the fact that thyristors for opposite directions of conduction have to work next to each other poses problems that are less severe than those associated with the antiparallel three phase bridge; this type of problems is, of course, completely absent in the case of a simple diode output bridge.

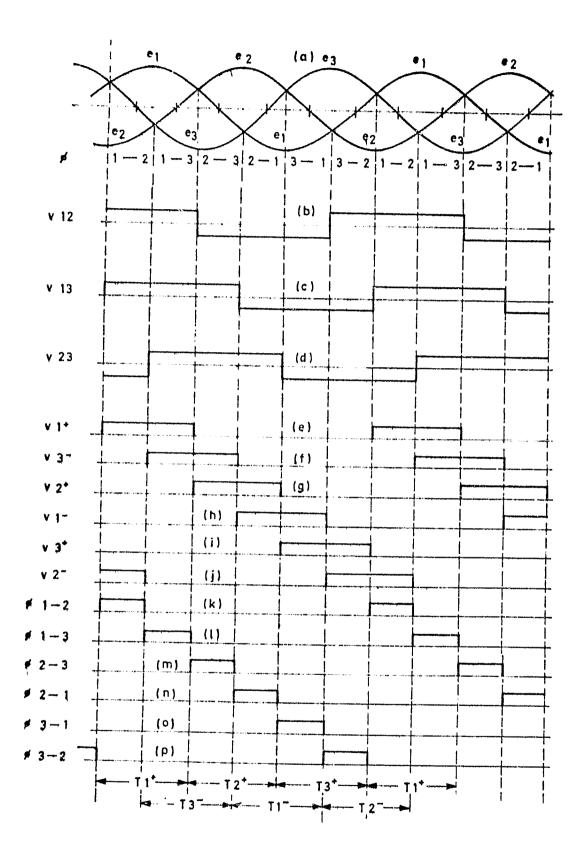

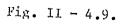

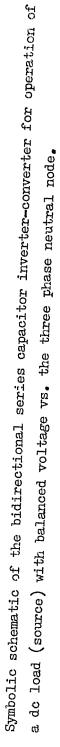

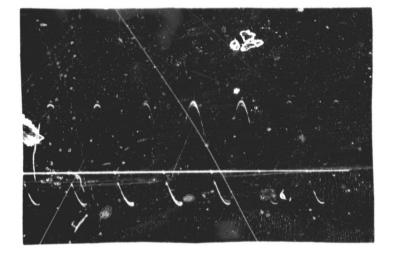

Signals  $e_1$ ,  $e_2$ , and  $e_3$  are fed into a sequence of polarity discriminators which, eventually, generate the signal blocks i-j which identify the relative polarity of phases, as introduced before. The output signals of the discriminatory logic which relates to these intervals i-j is indicated in parts (k) through (p) of Fig. II-4.9. Signals v12, v13, v23 and signals  $v1^+$ ,  $v1^-$ , etc., indicated in parts (b) through (j) of the same figure, signify steps in the process of successive discrimination of the logic process. These blocks i-j are used to clear access to the gates of the eligible thyristors. The actual command for firing comes from the power control system (CS) in the form of signals Cs1 and Cs2 indicated in Fig. II-4.6. These signals Csi fire the thyristors which were selected by the thyristor gating

Signals for the control logic of the thyristor gating and firing system.

and firing system. The referred to selection process includes also a command given to the thyristor firing and gating system, which indicates the direction of power transfer.

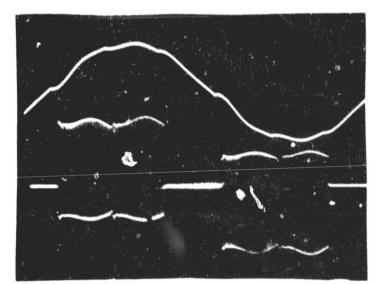

The resulting firing pulse trains and their relative position in time are summarily indicated in parts (c) through q) of Fig. 11 – 4.10. These signals are referred to the time intervals  $T1^+$ ,  $T2^+$ , etc. found at the bottom of Fig. 11-4.4. The significance of this figure appears self explanatory. Back bias detectors BBij and firing pulse generators FPGij are associated with each thyristor CRij.

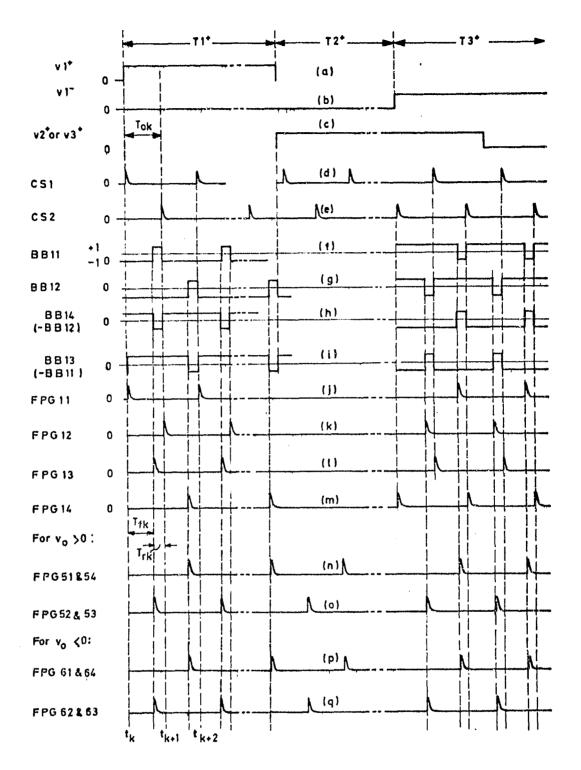

The power control system has, in principle. the structure of the formerly referred to ASDTIC system |3, 4|. It is indicated in its well known form in block diagram form in Fig. II-4.11. Input for signals ca<sub>ov</sub> and c<sub>arv</sub> are provided for application of continuous electric control signals to govern independently the power system output of current and voltage.

Access to the control system's current control and of its voltage limiting capability are necessary in order to achieve the pulse modulation processes which are essential for the materialization of the presented system. The control system receives its inputs from the current sensor (IS) the attenuated output voltage and the two before named signals cars and car.

11 - 42

\*\*\* \* \*\*

)

Fig. II - 4.10.

Illustration of representative firing signal sequence emitted by the firing pulse generators, FPGij and the back bias conditions BBij, associated with thyristors CRij.

2

.

Fig. 11 - 4.11.

Block diagram of ASDTIC control system CS with inputs for voltage and current control. 11 - 4.5. Component Requirements

No other component improvements appear needed than those used for dc converters of this class,

With regard to thyristors, it means that single module converters with power capacitors up to the order of 100 kW could be presently implemented with commercially available components. Expansion to the megawatt range can be implemented with larger thyristors, such as I to 3'kV forward blocking capacity, I kA current carrying capability, with turn off times between 10 and 15 microseconds. Another approach is that of modularization, whereby converters for the megawatt range could be constructed, once the technology is established.

The technology of capacitors has greatly improved in recent years and appears adequate for equipment in the 100 kW range up to the multimegawatt range.

Wire wound devices such as transformers and inductors use increasingly lower cost ferrite cores instead of the more expensive tape wound cores, if physical weight is not at a very high premium. Yet, tape wound cores with an inserted air gap can be used in certain cases. Construction of larger ferrite cores, needed for inductors beyond the submegawatt (100 kW) range does not seem a major hurdle to overcome. Currently available cores can be parallelied or devices arranged in series in order to construct megawatt size converters. 11 - 5. System Analysis and Characterization

II - 5.1. General Aspects

Analysis of the bidirectional three phase ac to dc converter is analogous to the analysis of dc converters of this class.

The operation of the resonant circuit is studied in a succession of time intervals i-j as explained before with reference to Figs. II = 2.3 & II = 4.9. The series resonant  $LC_1$  circuit "sees" on the ac side an input voltage e, which is identical with the output voltage of a loaded full wave diode rectifier bridge, energized by a threee phase line. The difference between the characteristics of a diode bridge and the here presented system lies in the fact that the appropriately selected thyristors sample this voltage  $e_i$  in succession to carry the resonant . current i, in both directions. The ratio between the cumulative charge per unit of time which passes in either of the two directions depends on the intended direction of power transfer. The resonant circuit, thus remains continuously connected to the three phase system, even though only selected thyristors carry high frequency pulses at one time, that is, as long as the resonant current i, is continuous. This current becomes discontinuous for conditions of lighter loading, such as one half of the rated output current or less, depending upon the ratio,  $T_{kr}^{T}/T_{kf}$  indicated in Fig. 11-4.6, and further defined and

explained in the literature [6, 10]. Yet the discontinuity referred to above occurs at a kHz rate, which is (1) usually substantially above 0 Hz rate of ordinary thyristor bridges and (2) concerns, inherently, current pulses with an oscillation frequency of no less than 10 kHz. The low pass filters (IF), (OF) which are part of the conversion process need, therefore, not be designed for the lowest current pulse repetition rate of the LC<sub>1</sub> circuit, but for less than twice the resonant frequency of this LC<sub>1</sub> circuit.

The just described general philosophy of system analysis is now illustrated with a numerical example. A small scale example is chosen for the purpose of simplicity of treatment. Translation of this small scale example to the intended 100 kW range is briefly indicated at the conclusion of this report.

II - 5.2. A Numerical Example.

Assumed is a dc source voltage  $e_s$  with a nominal value  $E_s = 270$  VDC. It is assumed that this source voltage is the average  $e_i_{av}$  of a voltage  $e_i$  which would appear at the output terminals of a full wave diode bridge which is fed from a 117/208 VAC three phase line with corresponding phase voltages  $e_1$ ,  $e_2$  and  $e_3$ . Assumed is, furthermore, that the average  $i_1_{av}$  of the absolute value of the resonant current  $|i_1|$  in a converter of the discussed class is 11 Amperes.

The value of capacitor

$$C_1 = i_{1 \text{ av ok}} / v_{\text{cpp}} = 11.50 \ 10^{-6} / 1100 \approx 0.5 \ \mu\text{F}$$

(5.1)

where

$$T_{ok} = t_{k+1} - t_k = 1/2 f_i$$

; see Fig. II - 4.6(p);

$v_{epp}$  = the peak to peak voltage on capacitor C<sub>1</sub>, which is

in excess of 4e<sub>i</sub> av.

The series inductor

$$L = (T_{ok}/\pi)^2 / C_1 = 340 \ \mu H$$

(5.2)

Consider now the effects that are introduced by the fact that  $e_i \neq E_s$ :

The steady state peak to peak input voltage variation to a converter of the here described class which is caused by a rectified three phase line amounts to approximately 11 percent of  $e_{i av}$ . This is the largest steady state input voltage variation that the converter will "see" under nominal operating conditions, when this input voltage consists of succeding intervals i-j, as discussed above.

One will allow as a rule a certain steady state tolerance of the ac line voltage of, say,  $\pm$  10 percent. The smallest instantaneous input voltage

$$e_{i \min} \approx e_{i av} (1 - 0.1 - 0.06) = 0.84 e_{i av}$$

(5.3)

If it is assumed that the system will operate with an efficiency  $n \approx .95$ , then it can be concluded that [6, 7, 11]

$$v_2 \approx (0.95)(0.84)(270) \approx 215 V$$

(5.4)

where

$v_2$  = the apparent primary transformer voltage amplitude.

L and C<sub>1</sub> are now modified since  $i_{1 \text{ av}} = VA/v_2 = 3000/215 \approx 14 \text{ A}$ :

$$C_1 \simeq 0.6 \ \mu F; L \simeq 280 \ \mu H$$