NAS CR 3215 c.1

# NASA Contractor Report 3215

# Low Power, Compact Charge Coupled Device Signal Processing System

P. W. Bosshart, D. D. Buss, W. L. Eversole, C. R. Hewes, and D. J. Mayer

CONTRACT NAS1-14290 FEBRUARY 1980

# NASA Contractor Report 3215

# Low Power, Compact Charge Coupled Device Signal Processing System

P. W. Bosshart, D. D. Buss, W. L. Eversole, C. R. Hewes, and D. J. Mayer Texas Instruments Incorporated Dallas, Texas

Prepared for Langley Research Center under Contract NAS1-14290

Scientific and Technical Information Office

1980

## TABLE OF CONTENTS

| SECTION |                                                       | <u>PAGE</u> |

|---------|-------------------------------------------------------|-------------|

| I       | INTRODUCTION                                          | . 1         |

|         | A. Frequency Domain Correlation                       | . 3         |

|         | B. Time Domain Correlation                            | . 8         |

| II      | 32-POINT CCD CZT IC                                   | . 14        |

|         | A. Chip Overview                                      | . 14        |

|         | B. CCD Filter                                         | . 22        |

|         | C. Operational Amplifiers                             | . 27        |

|         | 1. Design                                             | . 27        |

|         | 2. Experimental Results                               | . 52        |

|         | D. Multiplying Digital-to-Analog Converters (MDACs) . | . 59        |

|         | 1. Design                                             | . 59        |

|         | 2. Experimental Results                               | . 71        |

|         | E. Read-Only Memory (ROM) and ROM Address             | . 71        |

|         | l. Read-Only Memory                                   | . 71        |

|         | 2. Up/Down Ring Counter (ROM Address)                 | . 82        |

|         | 3. Synchronization                                    | . 87        |

|         | F. Timing Circuitry                                   | . 98        |

|         | 1. Clock Generators                                   | . 98        |

|         | 2. Experimental Results                               | . 109       |

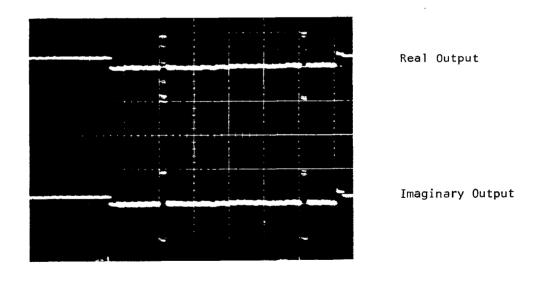

|         | G. Experimental Results                               | . 114       |

|         | H. Applications                                       | . 121       |

| III     | 64-POINT CCD ANALOG/ANALOG CORRELATOR                 | . 125       |

|         | A. Design                                             | . 125       |

|         | B. Performance Limitations in Design                  | . 129       |

|         | l. Multiplier Nonlinearity                            | . 129       |

|         | 2. Offsets                                            | . 132       |

|         | 3. Input Stage Offsets and Nonlinearities             | . 133       |

|         | C. Measured Performance                               | . 133       |

|         | 1. CCD Signal Capacity                                | . 133       |

|         | 2. Feedback Linearized Input Stage                    | . 134       |

#### TABLE OF CONTENTS

| <u>SECTION</u> | •                                                                                                           | PAGE |

|----------------|-------------------------------------------------------------------------------------------------------------|------|

|                | 3. Multiplier Linearity                                                                                     | 136  |

|                | 4. Offsets                                                                                                  | 140  |

|                | 5. Multiplier Scale Factor Matching                                                                         | 148  |

|                | 6. Evaluation                                                                                               | 148  |

|                | D. Directions for Future Designs                                                                            | 150  |

|                | 1. System Organization                                                                                      | 150  |

|                | 2. CCD Design                                                                                               | 152  |

|                | 3. Input Stage Design                                                                                       | 152  |

|                | 4. Buffer Design                                                                                            | 152  |

|                | 5. Multipliers                                                                                              | 153  |

|                | E. Applications and Summary                                                                                 | 153  |

|                | 1. Applications                                                                                             | 153  |

|                | 2. Summary                                                                                                  | 153  |

| ΙV             | CCD BINARY/ANALOG CORRELATOR                                                                                | 155  |

|                | A. Introduction                                                                                             | 155  |

|                | B. Binary/Analog Programmable CCD Correlator Technology                                                     | 159  |

|                | C. Application of Binary/Analog Correlator to Pattern Classification                                        | 171  |

|                | D. Preliminary Design of Matrix Multiplier IC                                                               | 174  |

|                | E. Four-Sensor Demonstration Unit                                                                           | 177  |

| V              | CONCLUSIONS                                                                                                 | 182  |

|                | REFERENCES                                                                                                  | 184  |

|                | LIST OF ILLUSTRATIONS                                                                                       |      |

| FIGURE         |                                                                                                             | PAGE |

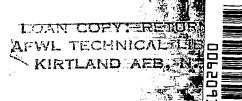

| 1              | Block Diagram of a Transversal Filter Showing Delay Stages D and Weighting Coefficients $h_n$ $n=0$ , $N-1$ | 2    |

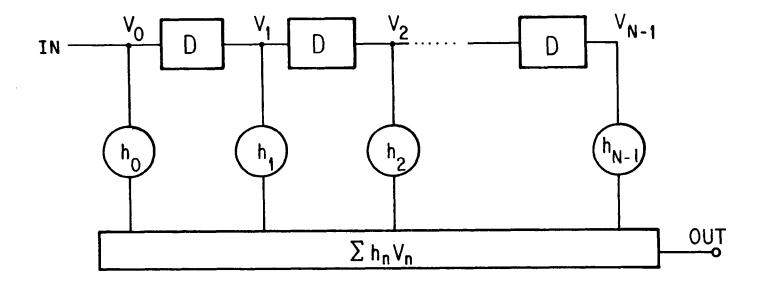

| 2              | Schematic of the CZT Algorithm                                                                              | 5    |

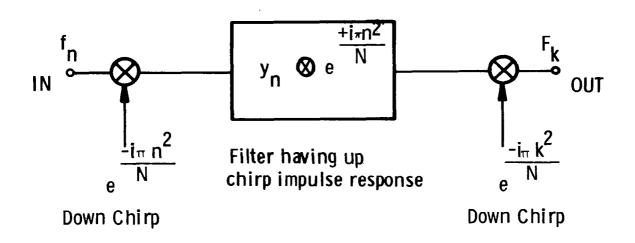

| 3              | Interpretation of the CZT in Terms of Chirp Input Wave-forms in Chirp Filters                               | 6    |

| 4              | Block Diagram of a CCD Programmable Correlator                                                              | 7    |

| 5              | Block Diagram of the Analog/Analog Time Domain Correlator                                                   | 9    |

| 6              | Circuit Schematic of the Four-Quadrant Multiplier Used in the Analog/Analog Correlator of Figure 5          | 10   |

| FIGURE |                                                                      | PAGE |

|--------|----------------------------------------------------------------------|------|

| 7      | Block Diagram of the Binary/Analog Correlator                        | 12   |

| 8      | Block Diagram of 32-Point CZT IC                                     | 15   |

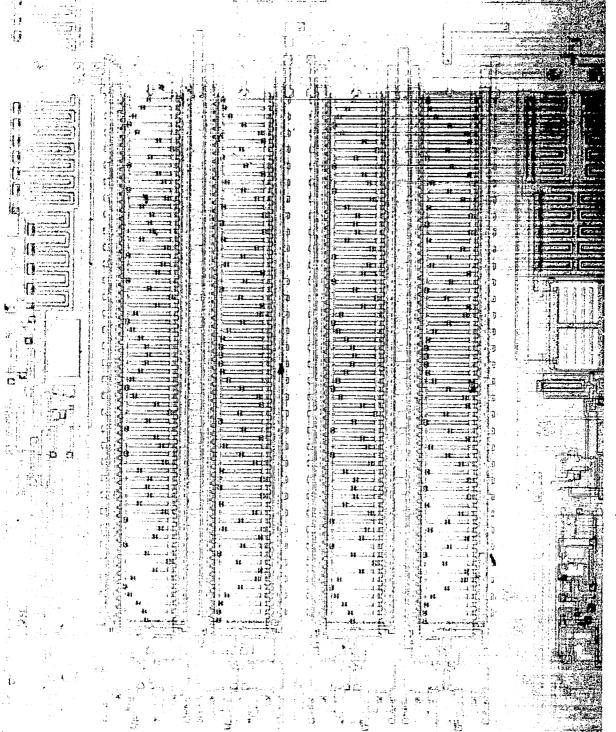

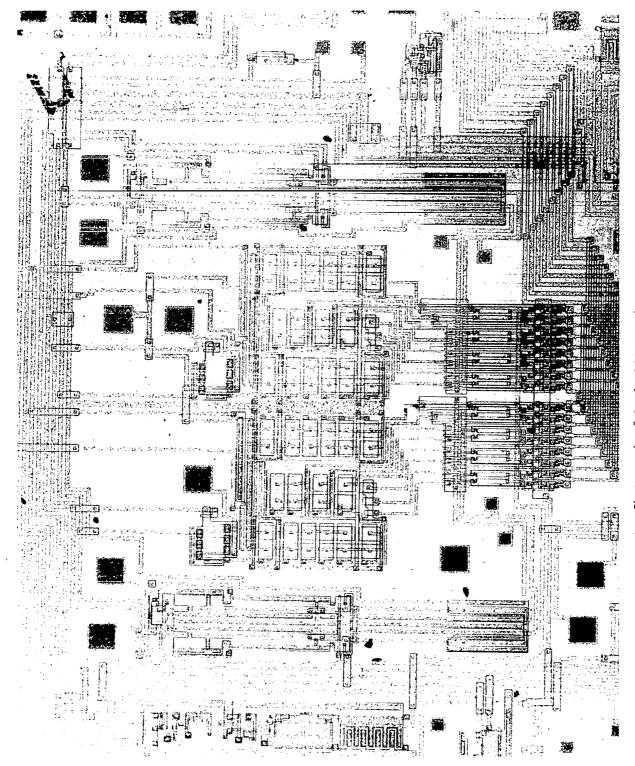

| 9      | Photomicrograph of 32-Point CCD CZT IC                               | 16   |

| 10     | Silicon Gate CCD Coplanar Electrode Structure                        | . 17 |

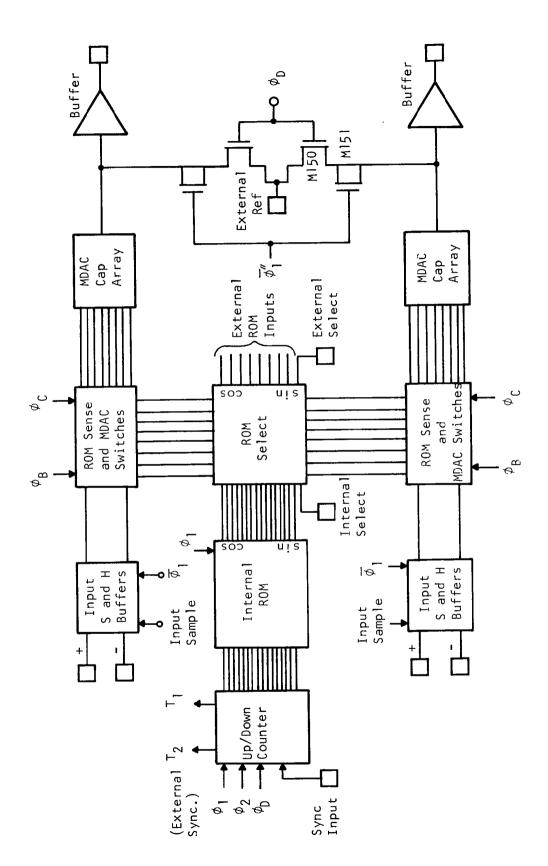

| 11     | Block Diagram of Internal ROM, Up/Down Counter, and Dual MDACs       | 19   |

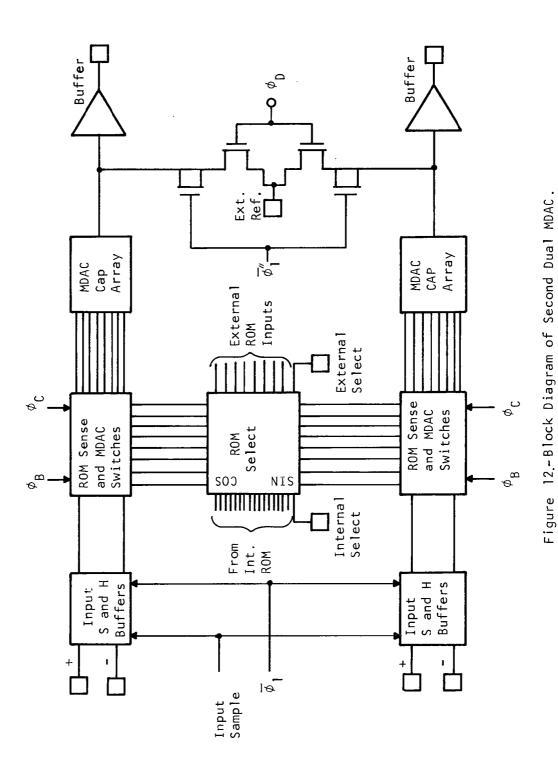

| 12     | Block Diagram of Second Dual MDAC                                    | 20   |

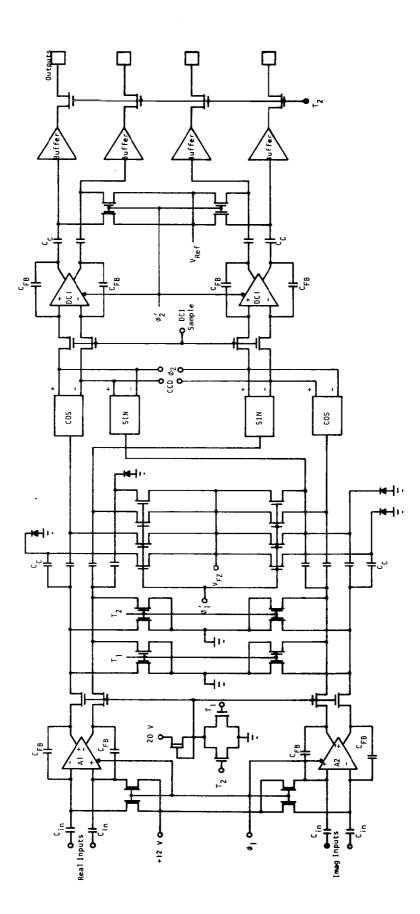

| 13     | Block Diagram of CCD Input Amplifiers, CCDs, DCI, and Output Buffers | 21   |

| 14     | Photomicrograph of CCD Transversal Filters                           | 23   |

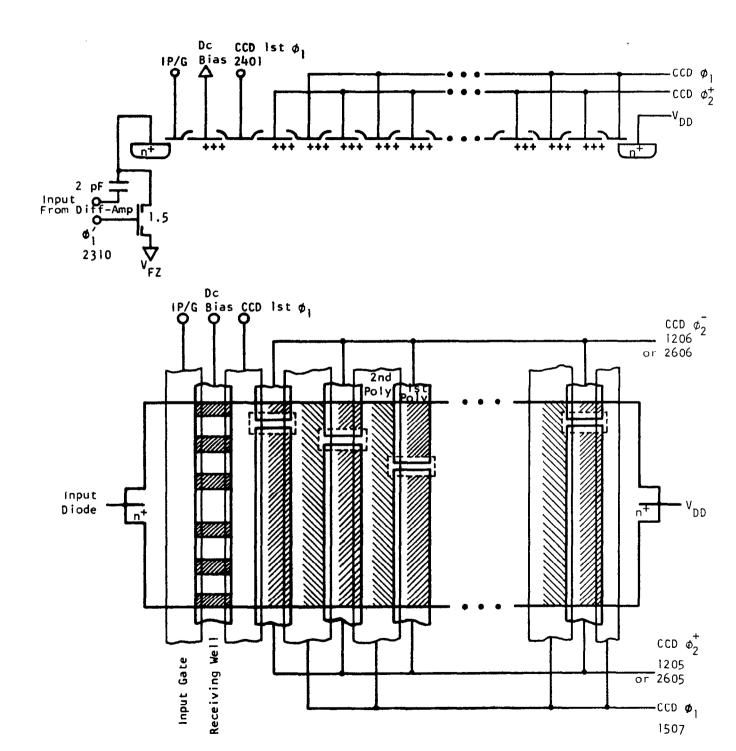

| 15     | Schematic of CCD Filters                                             | 24   |

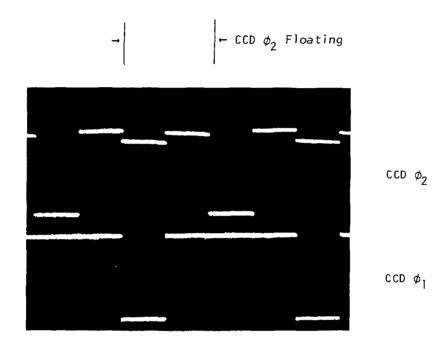

| 16     | CCD Timing                                                           | 26   |

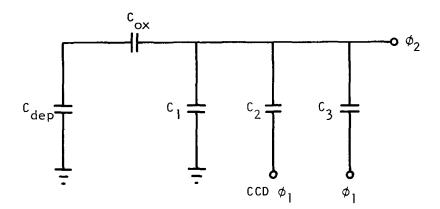

| 17     | CCD Capacitances                                                     | 28   |

| 18     | A Possible Switching Diagram for Figure 17                           | 29   |

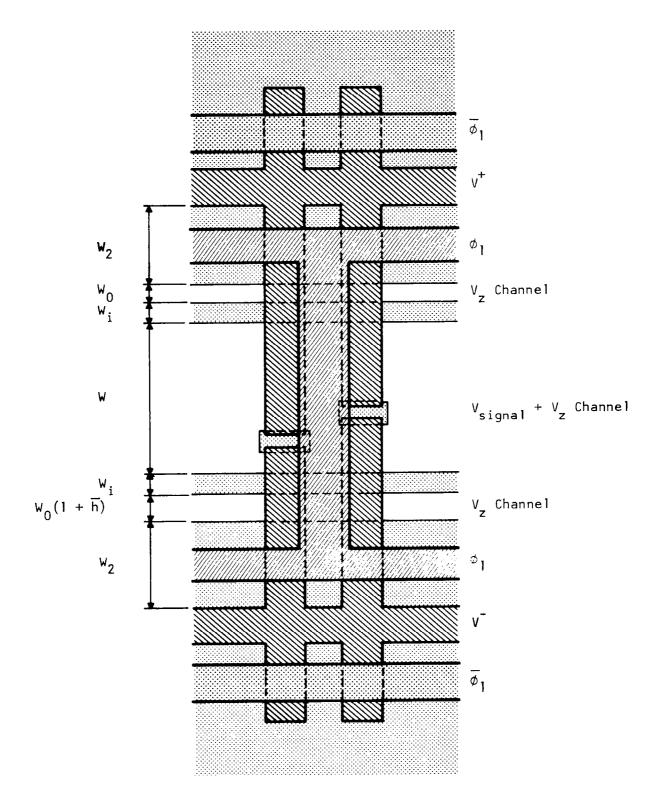

| 19     | Symmetrized and Compensated Two-Phase CCD Layout                     | 32   |

| 20     | DCI Amplifier Compensated for Gain of 30                             | 34   |

| 21     | Photomicrograph of Operation Amplifier Used on CZT IC $\ldots$       | 35   |

| 22     | Block Diagram of Single-Loop Amplifier                               | 40   |

| 23     | Differential Amplifier                                               | 41   |

| 24     | Differential Amplifier Theoretical Open Loop Characteristics         | 43   |

| 25     | Input Amplifier Closed Loop Frequency Response                       | 44   |

| 26     | DCI Amplifier                                                        | 45   |

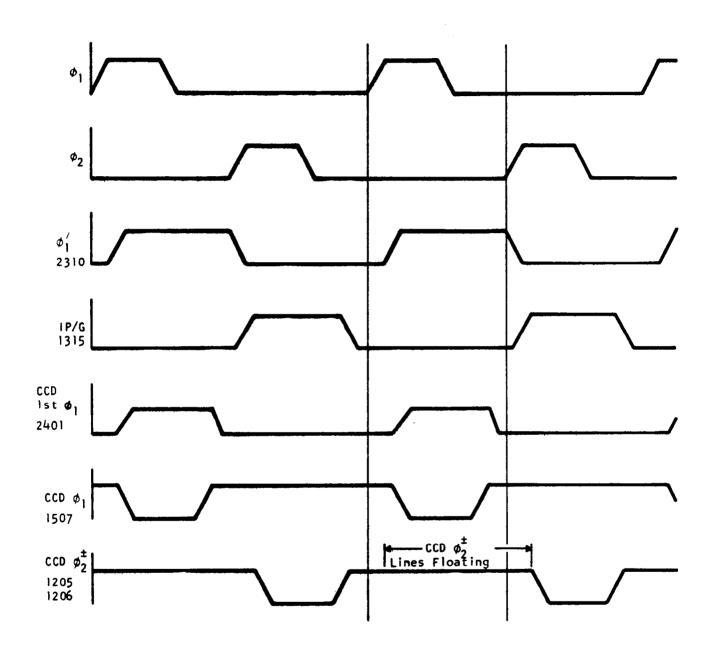

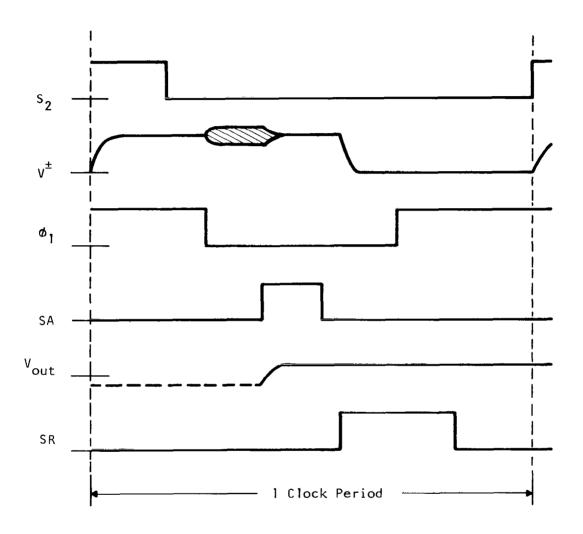

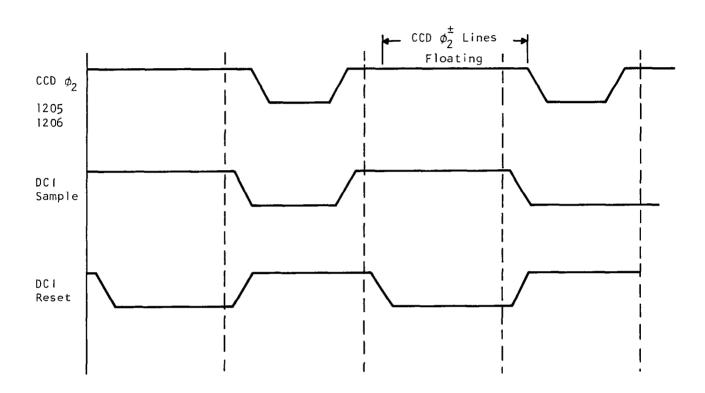

| 27     | DCI Timing                                                           | 46   |

| 28     | CCD Clocks                                                           | 48   |

| 29     | Model for DCI                                                        | 50   |

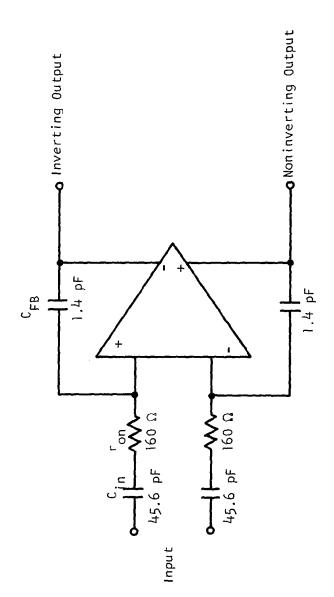

| 30     | Capacitance Model for DCI Input                                      | 51   |

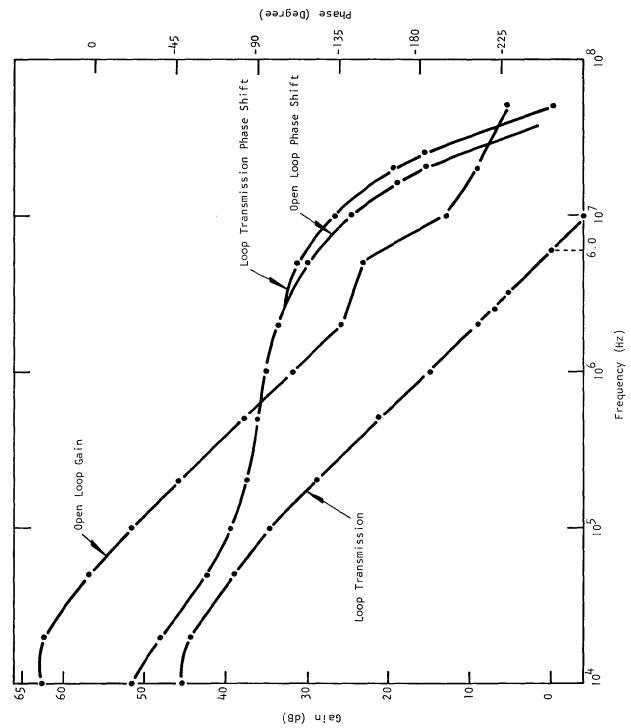

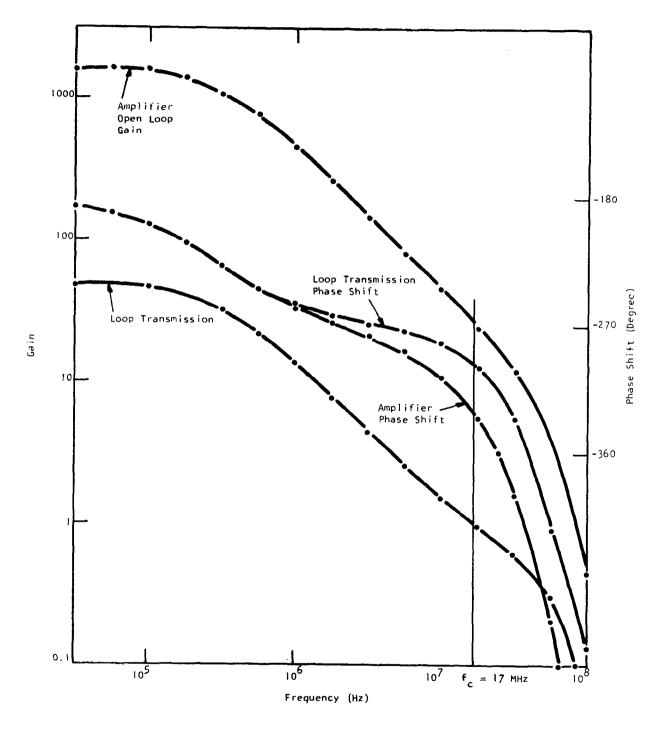

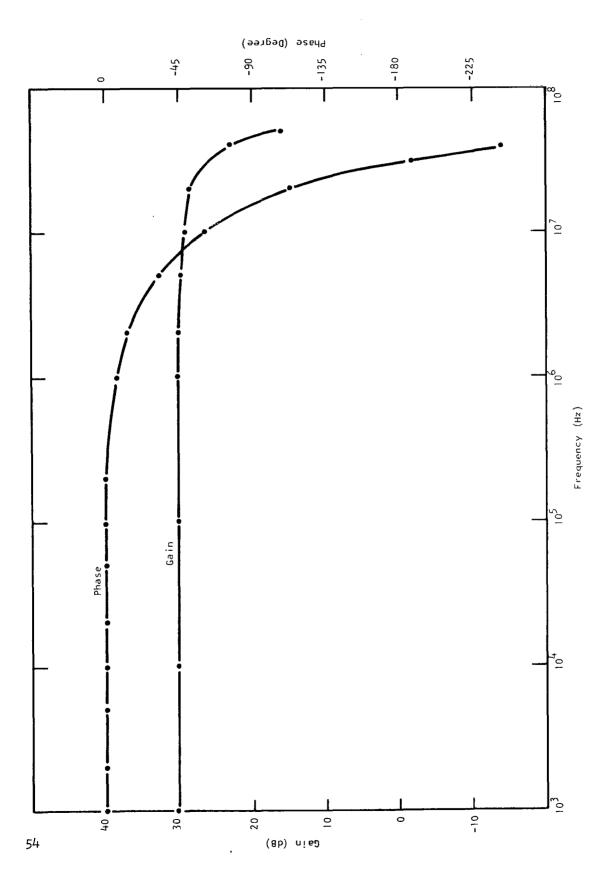

| 31     | DCI Diff-Amp Open Loop Performance                                   | 53   |

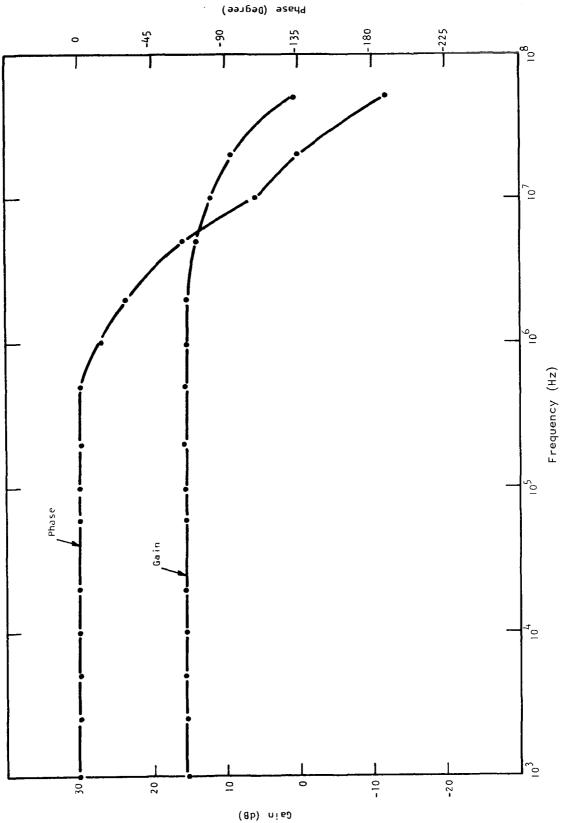

| 32     | Closed Loop Frequency Response of DCI Amplifier                      | 54   |

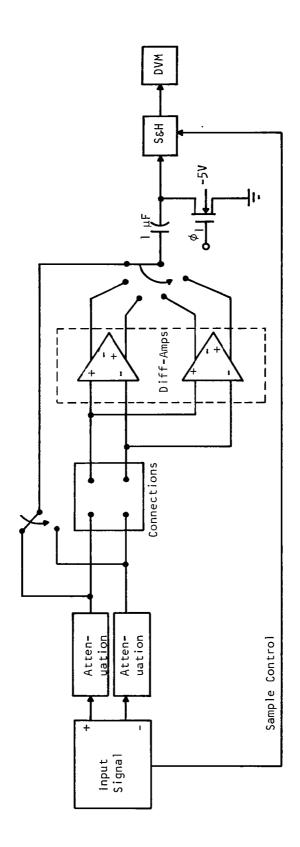

| 33     | Differential Amplifiers Test                                         | 55   |

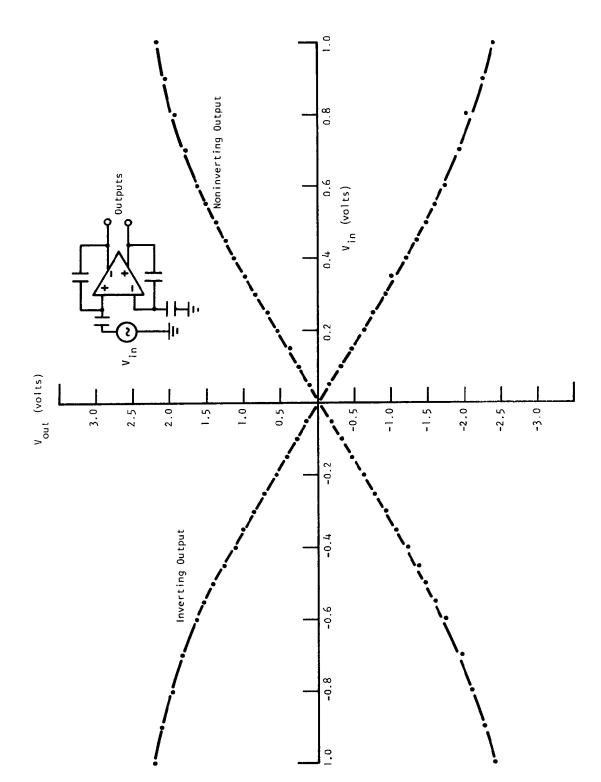

| 34     | Single-Ended Transfer Characteristics of Input Differen-             | 56   |

| <u>FIGURE</u> |                                                                               | PAGE |

|---------------|-------------------------------------------------------------------------------|------|

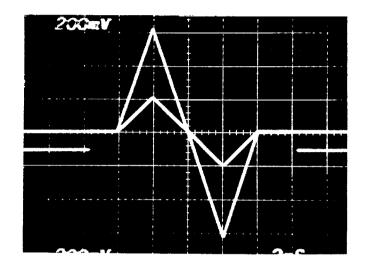

| 35            | Response of Input Differential Amplifier to Common Mode Input                 | 57   |

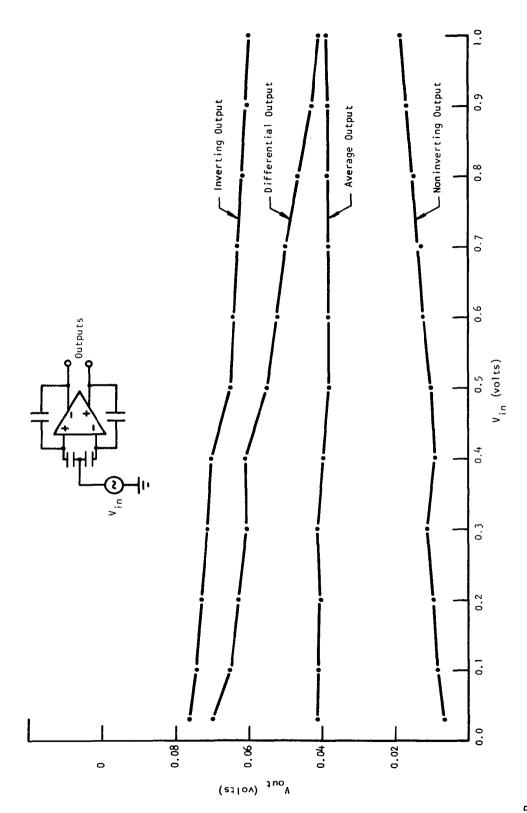

| 36            | Differential Mode Characteristics of Input Amplifier                          | 58   |

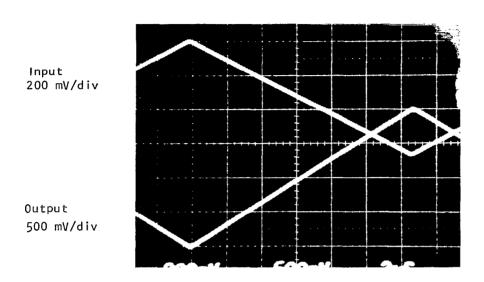

| 37            | Single-Ended Response of Differential Amplifier to Ramp                       | 60   |

| 38            | Photograph Showing the Gain and Linearity of Input Amplifiers                 | 61   |

| 39            | DCI Amplifier Open Loop Characteristics                                       | 62   |

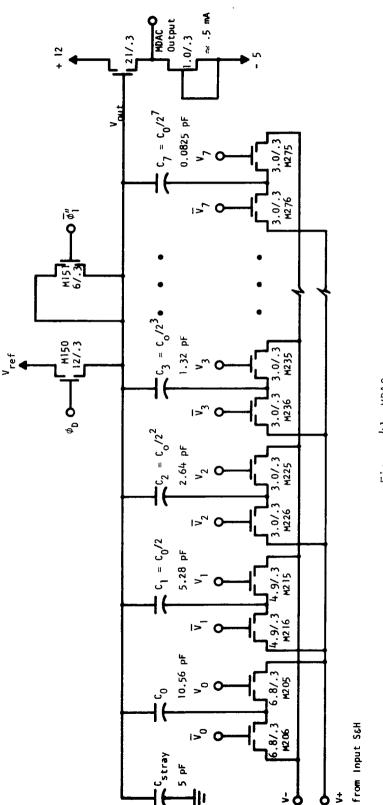

| 40            | Photograph of Dual MDACs Used on CZT IC                                       | 63   |

| 41            | MDAC                                                                          | 64   |

| 42            | Buffered Input Sample-and-Hold                                                | 67   |

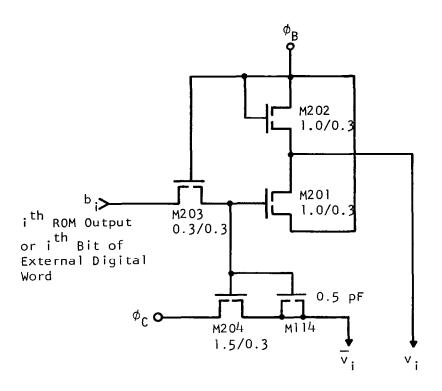

| 43            | ROM Sense and MDAC Drive Circuitry                                            | 69   |

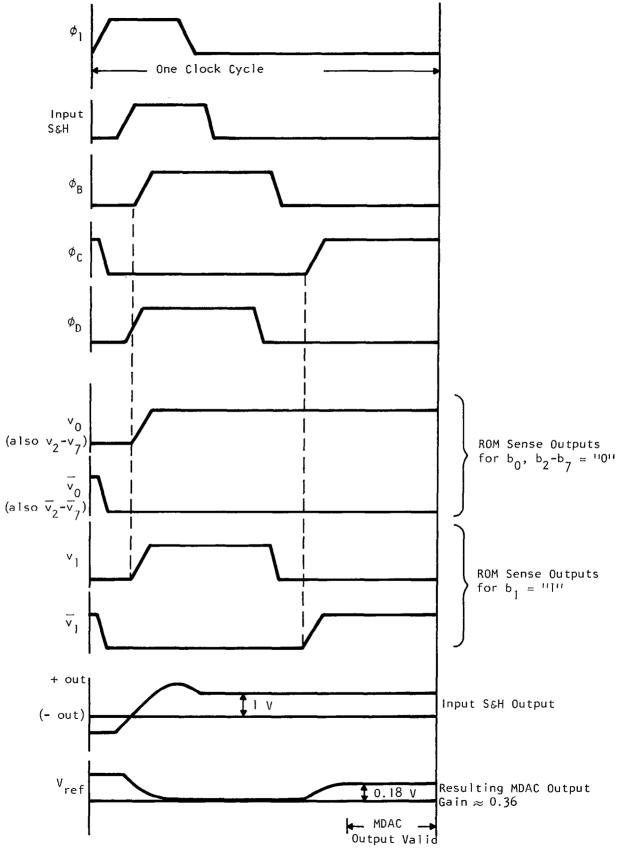

| 44            | Typical MDAC Operation (Multiplication by 0.5)                                | 70   |

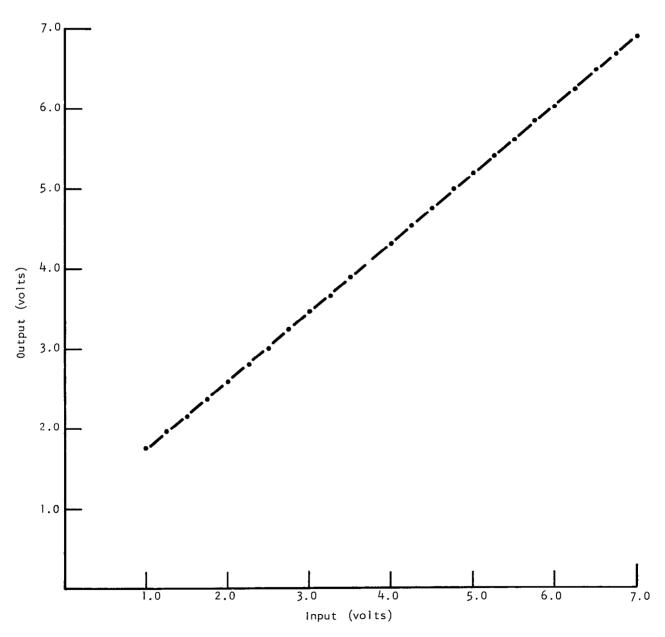

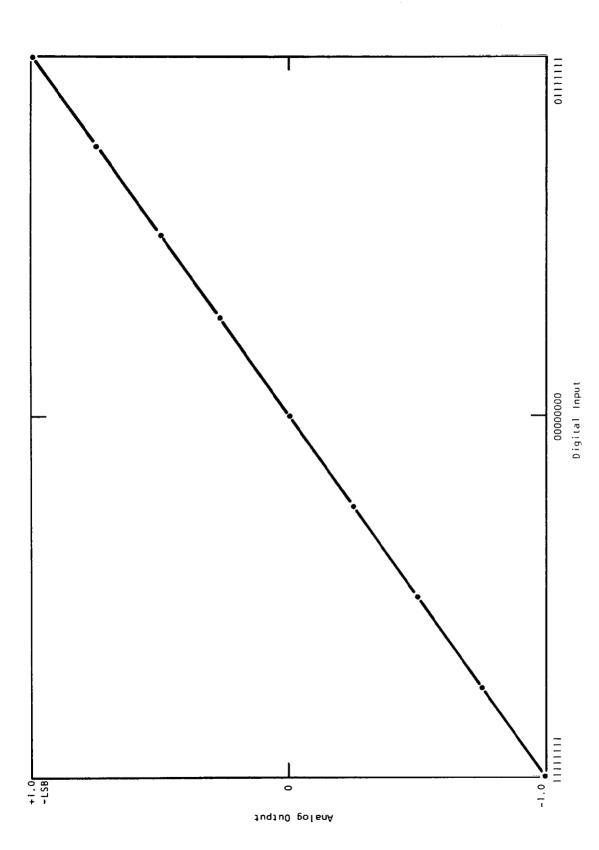

| 45            | Transfer Curve for Input Sample-and-Hold Circuit of MDAC                      | 72   |

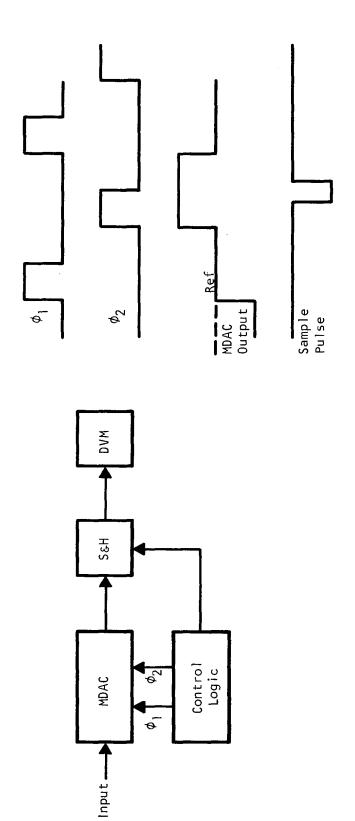

| 46            | Block Diagram of MDAC Test                                                    | 73   |

| 47            | Response of MDAC to dc Input and Sine Chirp of Internal ROM $(V^+ - V^-) < 0$ | 74   |

| 48            | Relative Accuracy of MDACs                                                    | 76   |

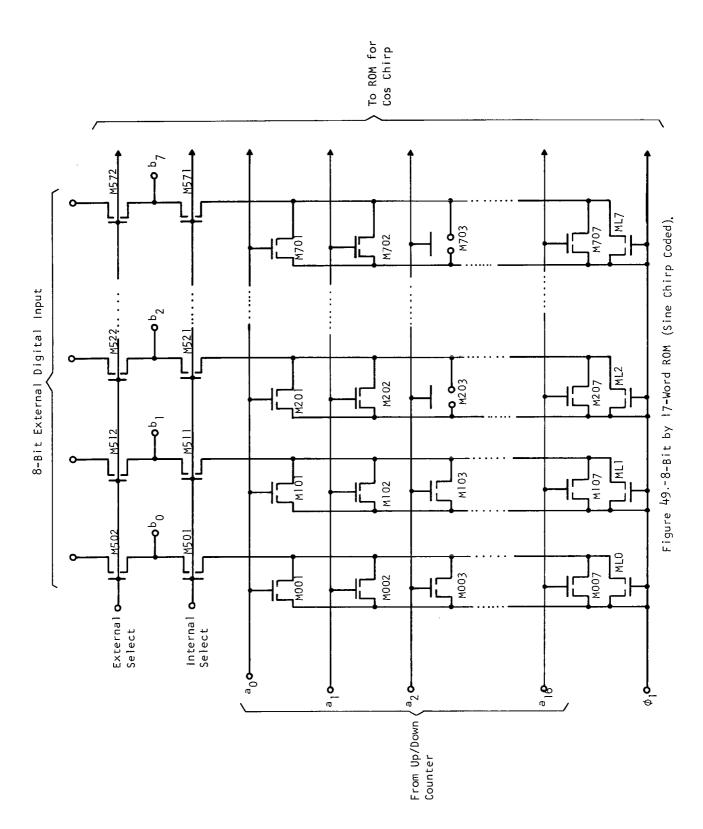

| 49            | 8-Bit by 17-Word ROM (Sine Chirp Coded)                                       | 78   |

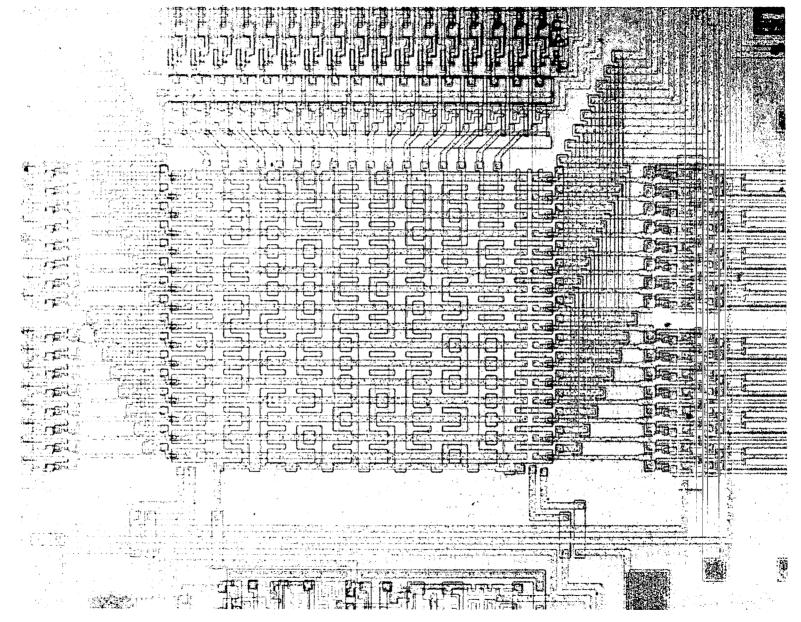

| 50            | Photograph of ROM                                                             | 80   |

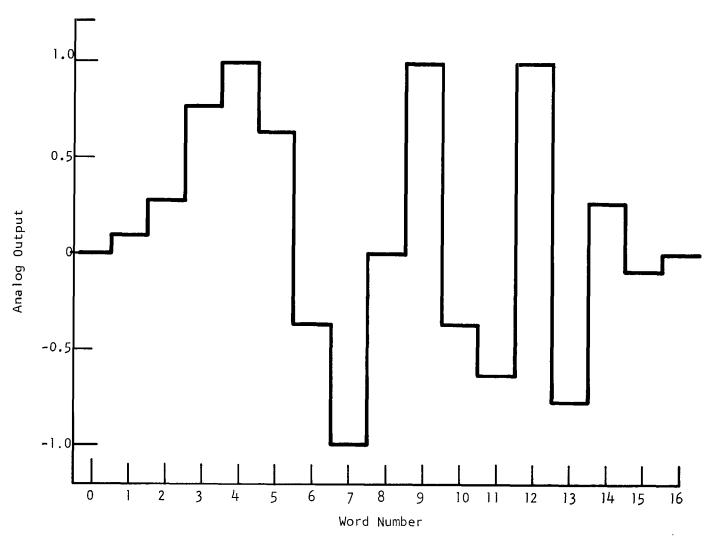

| 51            | Analog Representation of Sine Chirp Coded into ROM                            | 81   |

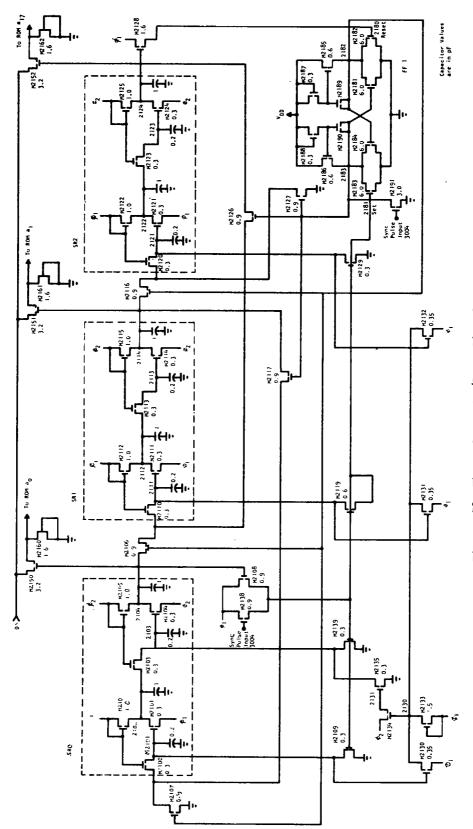

| 52            | Three-Stage Up/Down Ring Counter                                              | 83   |

| 53            | Typical Shift Register Operation (SRO)                                        | 84   |

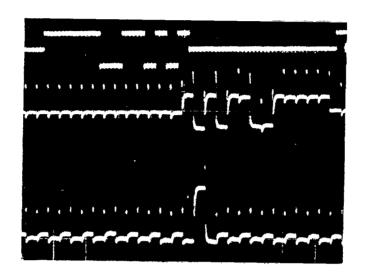

| 54            | Up/Down Counter Waveforms - Normal Operation                                  | 88   |

| 55            | Photograph of Up/Down Counter                                                 | 89   |

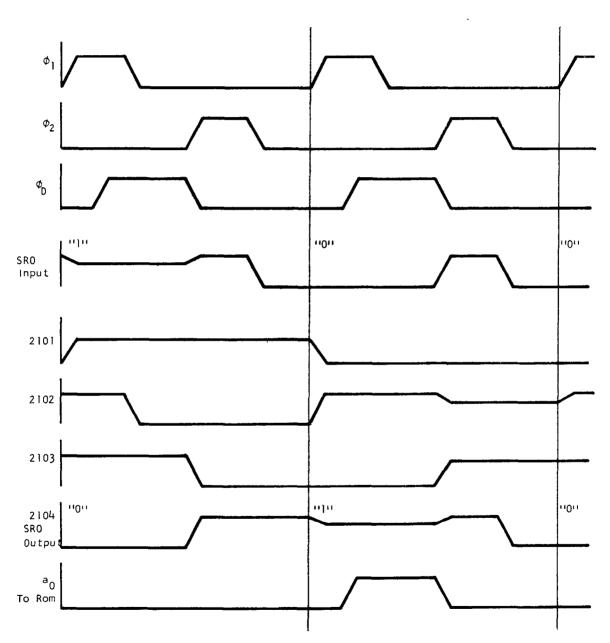

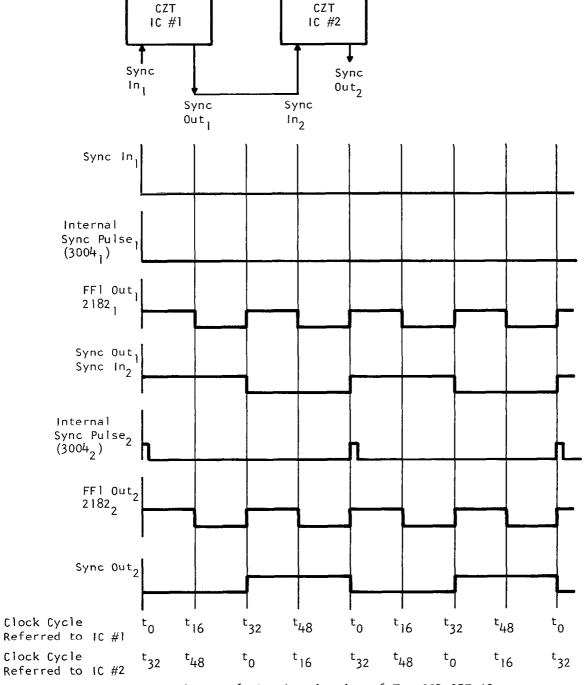

| 56            | Synchronization of Two CCD CZT ICs                                            | 91   |

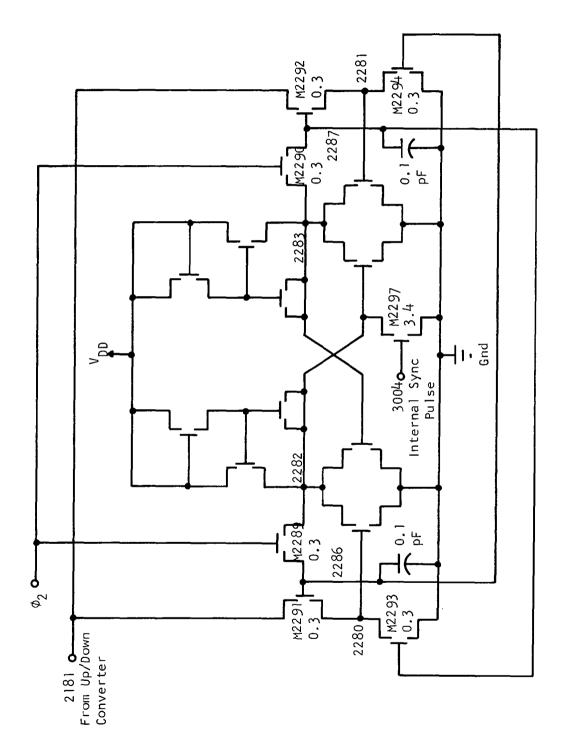

| 57            | External Sync Pulse Generator                                                 | 92   |

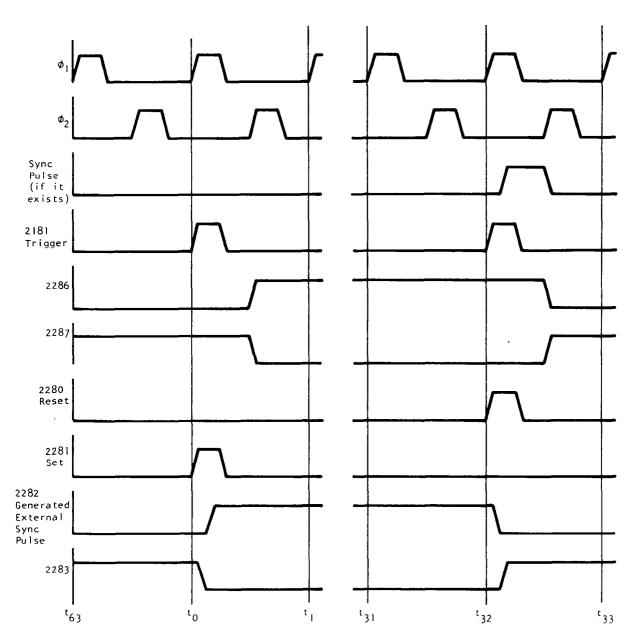

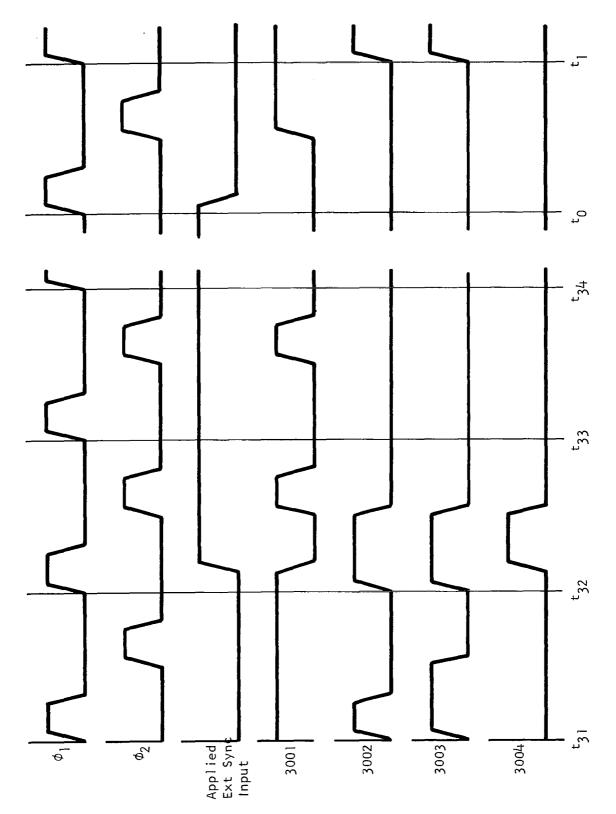

| 58            | External Sync Pulse Generator Timing - Normal Operation                       | 93   |

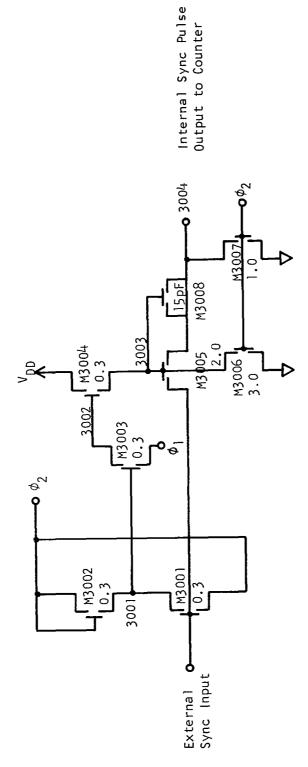

| 59            | GEN 30 (Internal Sync Pulse)                                                  | 95   |

| 60            | GEN 30 Timing                                                                 | 96   |

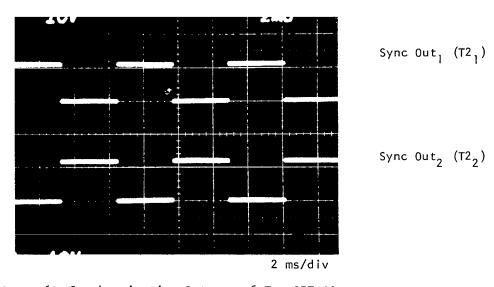

| 61            | Synchronization Outputs of Two CZT ICs Operating Together .                   | 97   |

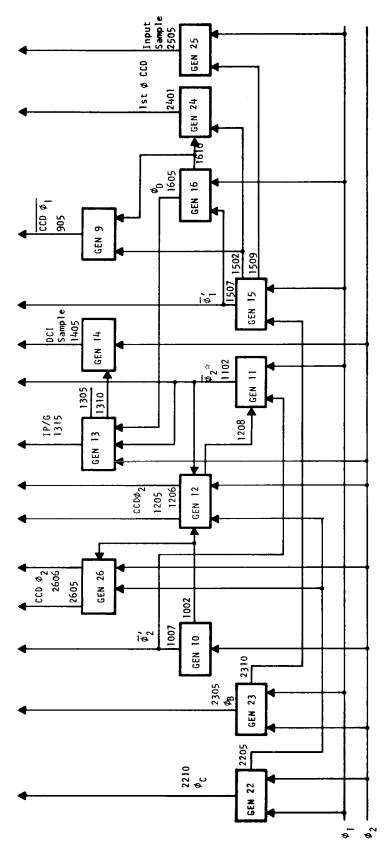

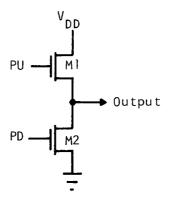

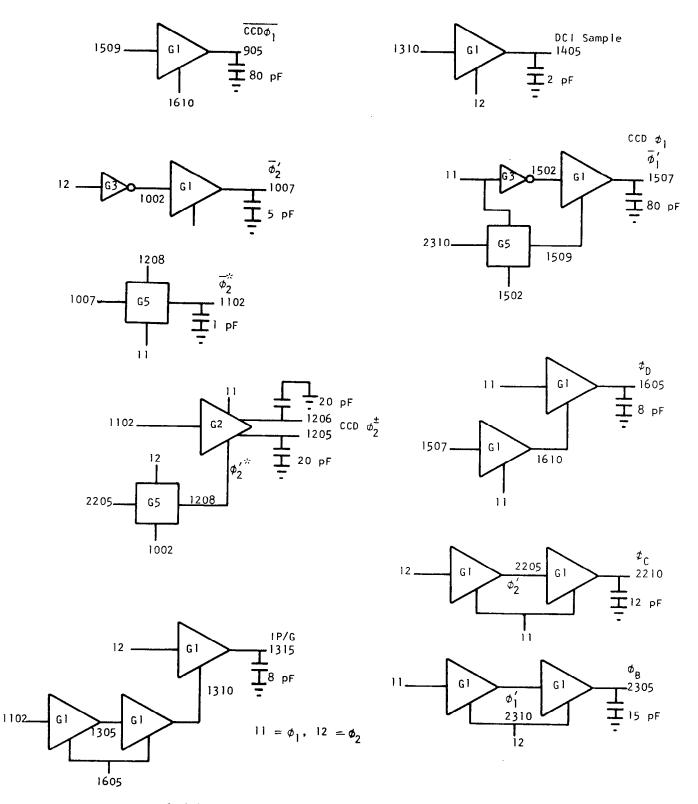

| 62            | Block Diagram of Clock Generators                                             | 99   |

| FIGURE |                                                                                                              | PAGE |

|--------|--------------------------------------------------------------------------------------------------------------|------|

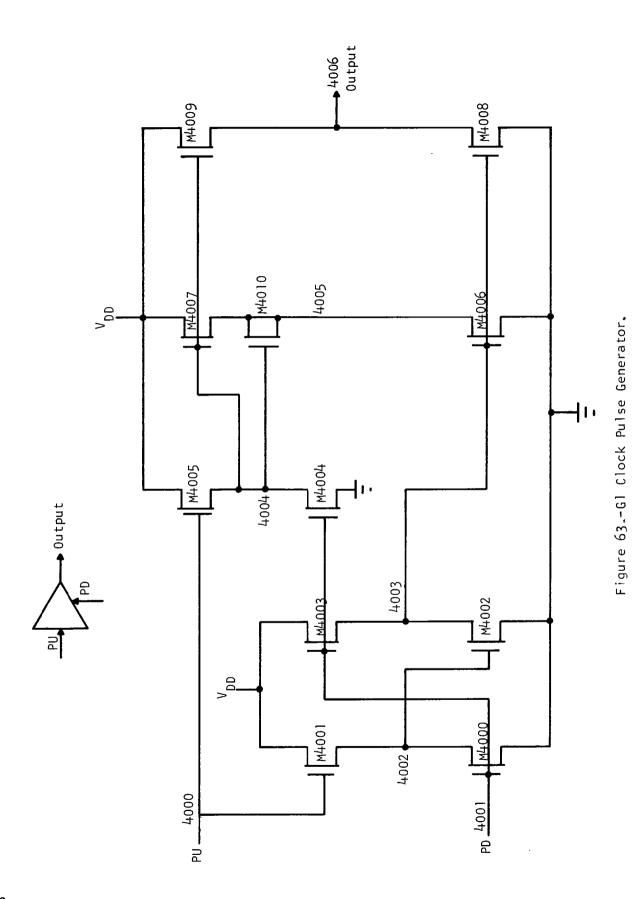

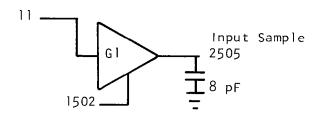

| 63     | Gl Clock Pulse Generator                                                                                     | 100  |

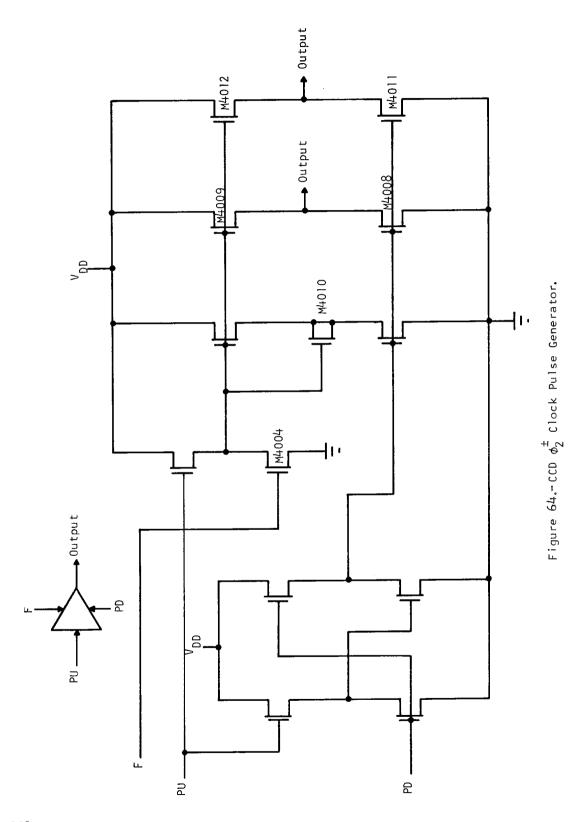

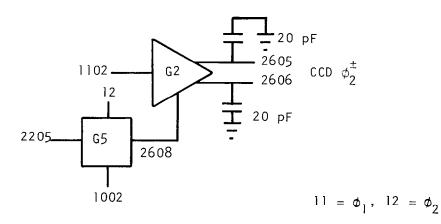

| 64     | CCD $\phi_2^\pm$ Clock Pulse Generator                                                                       | 102  |

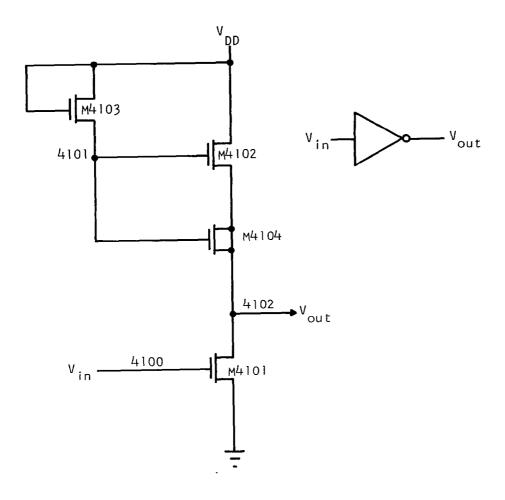

| 65     | G3 Inverter                                                                                                  | 103  |

| 66     | G4 Inverter                                                                                                  | 104  |

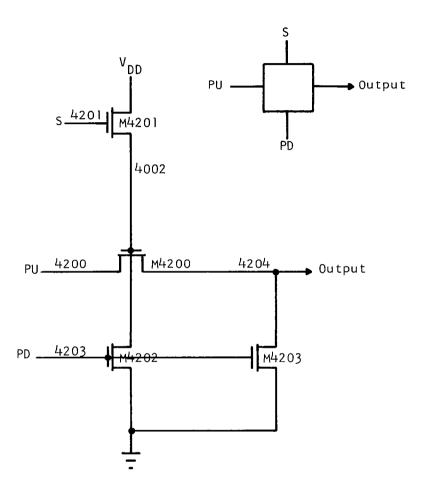

| 67     | G5 Generator                                                                                                 | 105  |

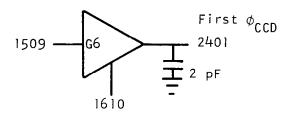

| 68     | G6 Generator                                                                                                 | 106  |

| 69     | Connections of the Clock Generators Showing Capacitive Load of Each Driver                                   | 107  |

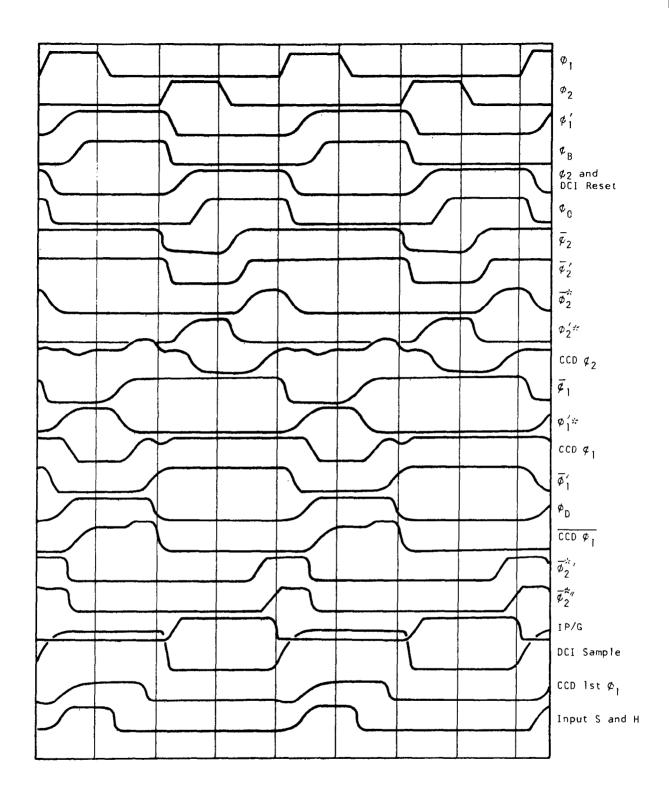

| 70     | System Timing                                                                                                | 110  |

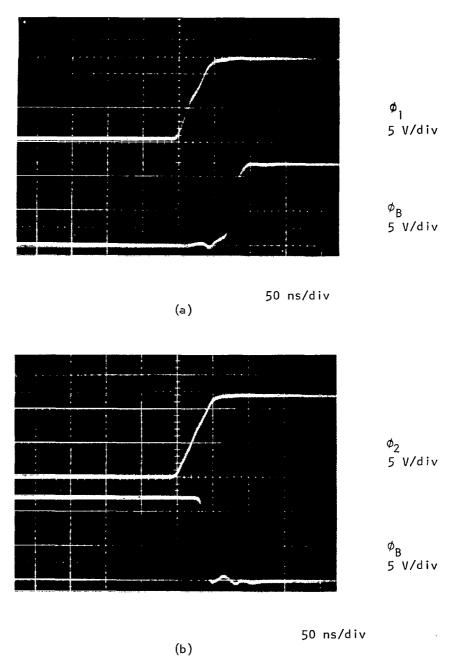

| 71     | Clock Circuit Performance                                                                                    | 111  |

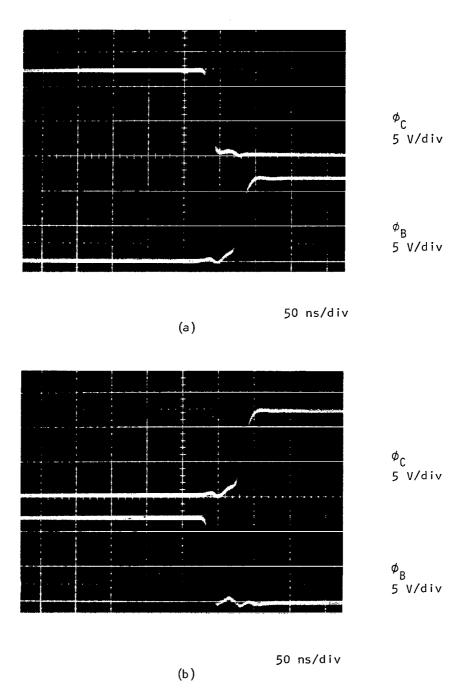

| 72     | Relationship of $\phi_{_{ m B}}$ and $\phi_{_{ m C}}$                                                        | 112  |

| 73     | Photograph of CCD $\phi_2$ Clock Driver                                                                      | 113  |

| 74     | A System for Obtaining Power Density Spectrum of a Real Input Using One CZT IC (50% Input/Output Duty Cycle) | 115  |

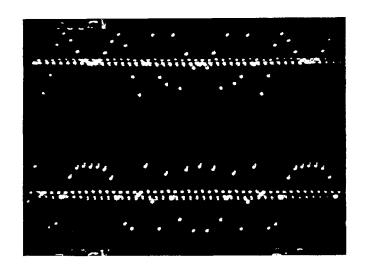

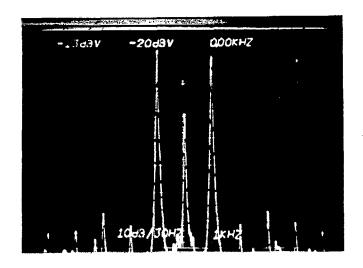

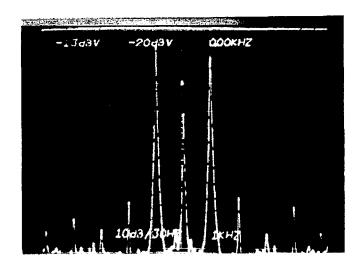

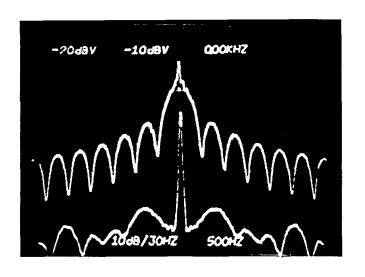

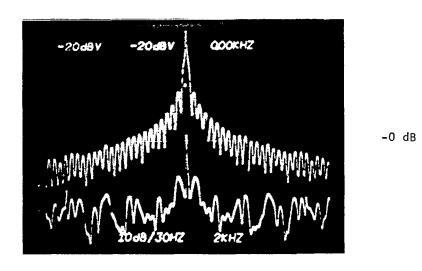

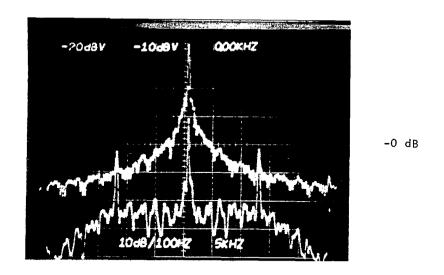

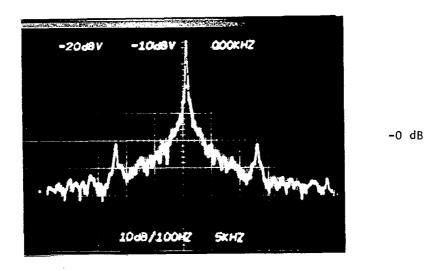

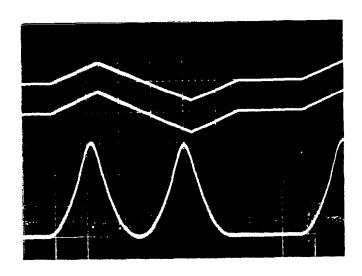

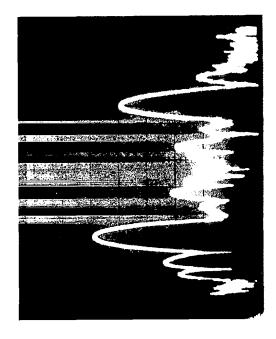

| 75     | Operation of CCD CZT IC with 10 kHz Clocks                                                                   | 116  |

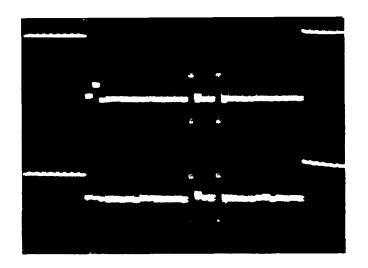

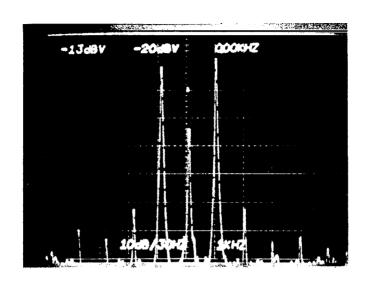

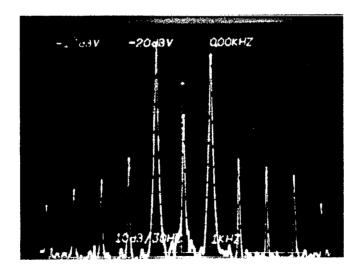

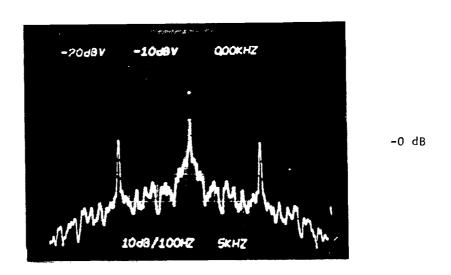

| 76     | Operation of CCD CZT IC with 1 MHz Clocks                                                                    | 117  |

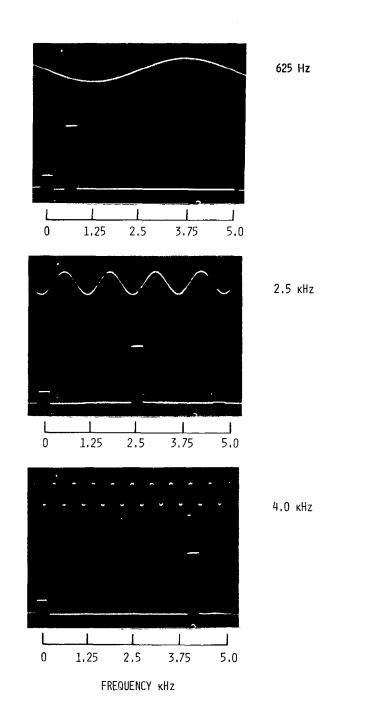

| 77     | Power Density Spectra for Three Sine Waves Obtained Using the 32-Point CCD CZT at a 10 kHz Sample Rate       | 118  |

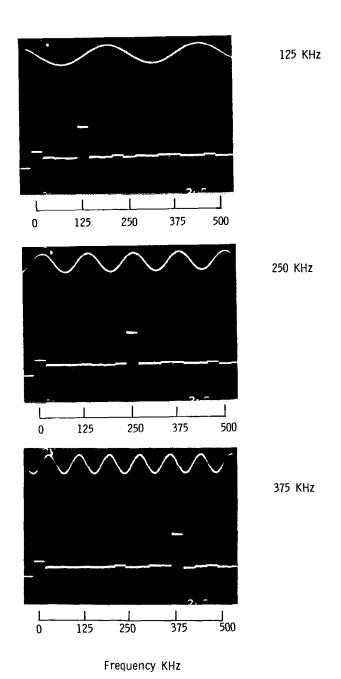

| 78     | Power Density Spectra for Three Sine Waves Obtained Using the 32-Point CCD CZT at   MHz Sample Rate          | 119  |

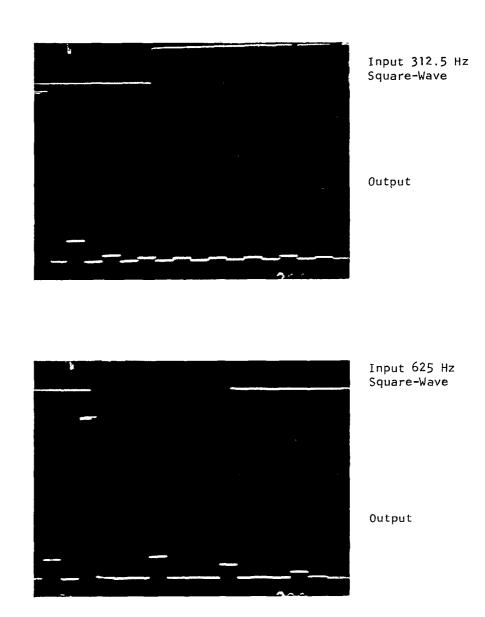

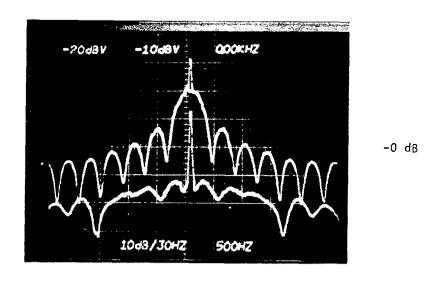

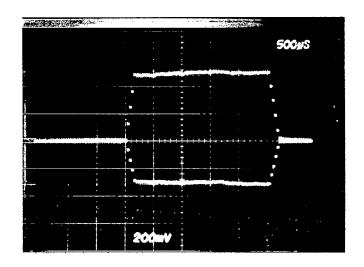

| 79     | Response of CCD CZT IC to Square-Wave Inputs (10 kHz Clock Frequency)                                        | 120  |

| 80     | Realization of Complex I/O CZT with One Chip (50% Duty Cycle)                                                | 122  |

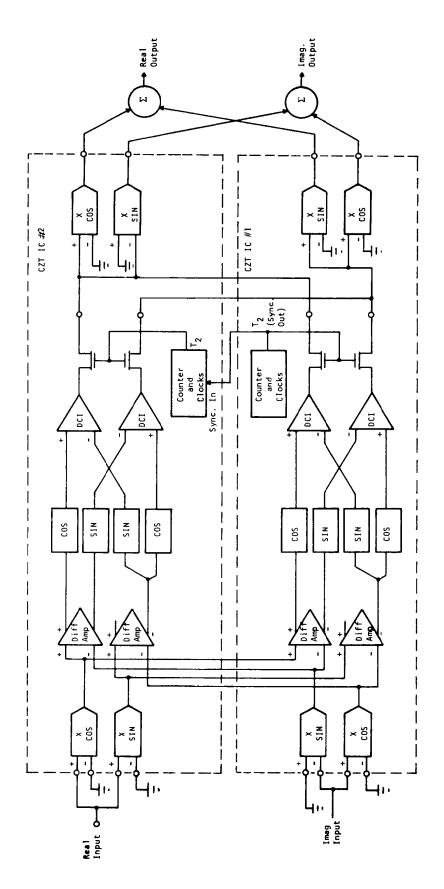

| 81     | Realization of Complex I/O CZT Using Two CZT ICs (100% Duty Cycle)                                           | 123  |

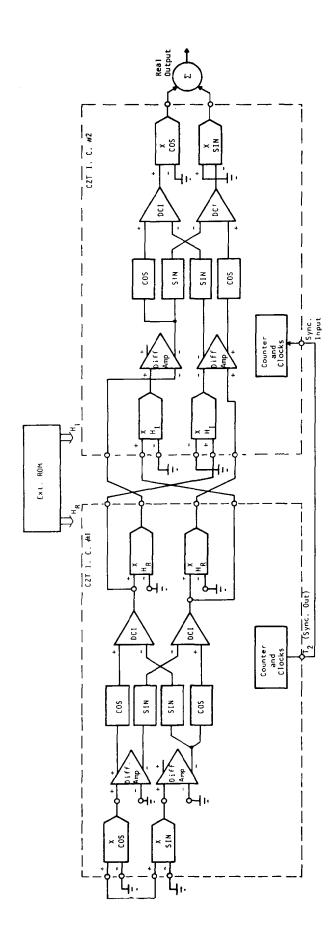

| 82     | Realization of Correlator Using Two CZT ICs (Real 25% Duty Cycle Input, Real 50% Duty Cycle Output)          | 124  |

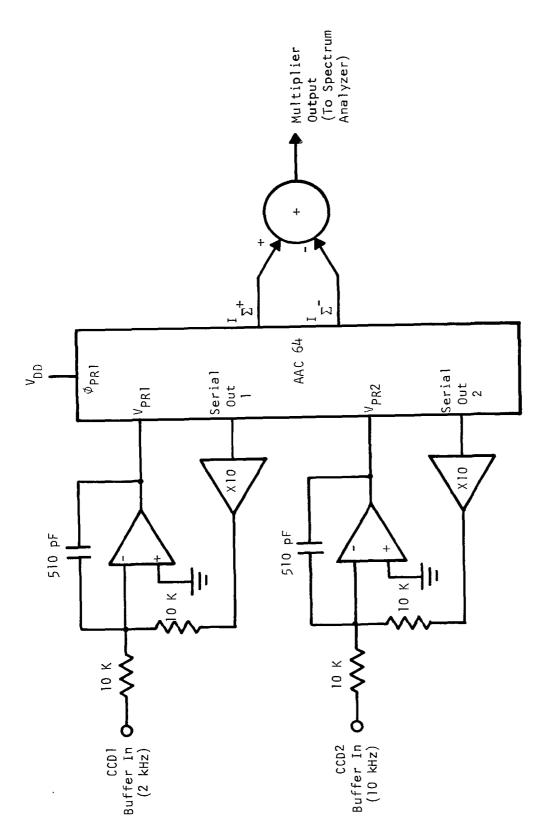

| 83     | Analog Correlator Block Diagram                                                                              | 126  |

| 84     | Floating Gate Reset Technique                                                                                | 127  |

| 85     | Analog Multiplier                                                                                            | 128  |

| 86     | CCD Input Stage                                                                                              | 130  |

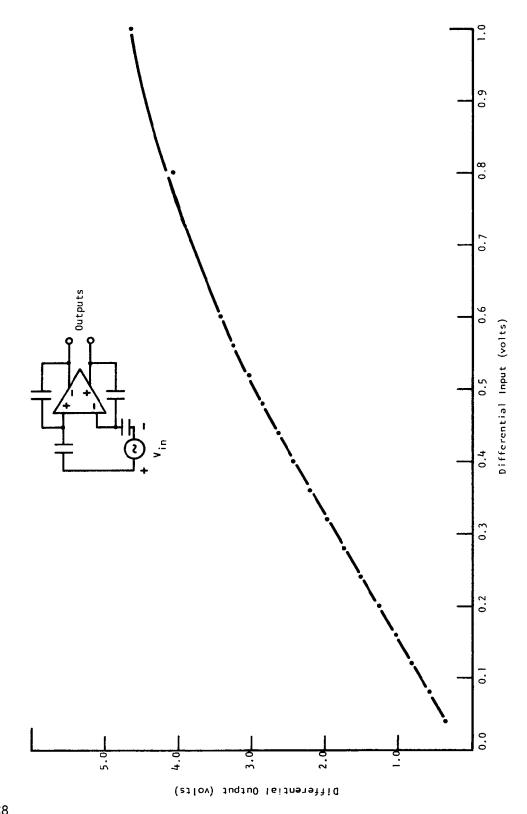

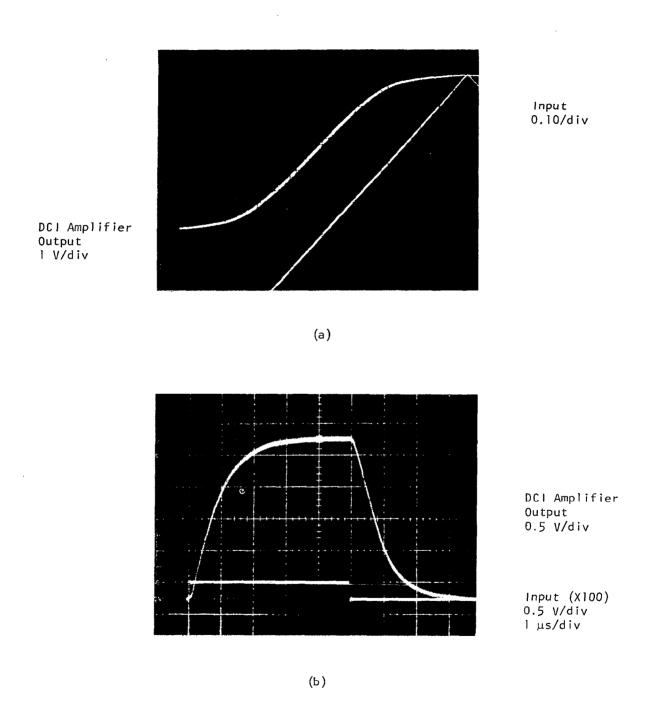

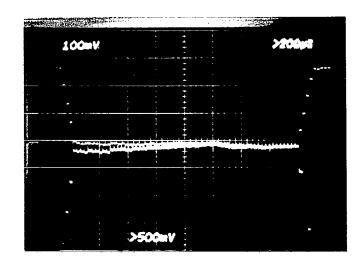

| 87(a)  | CCD Input Stage Feedback-Linearized Output                                                                   | 135  |

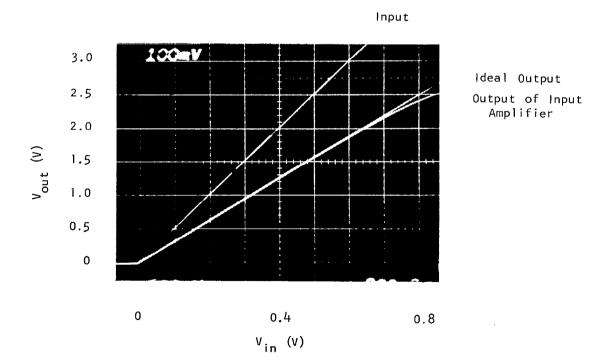

| 87(b)  | CCD Serial Output vs Input                                                                                   | 135  |

| FIGURE |                                                                                                           | PAGE |

|--------|-----------------------------------------------------------------------------------------------------------|------|

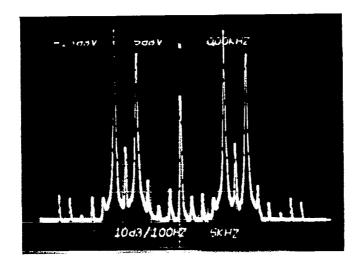

| 88(a)  | CCDl Serial Output Linearity 0.4 V Signal                                                                 | 137  |

| 88(b)  | CCD1 Serial Output Linearity 0.5 V Signal                                                                 | 137  |

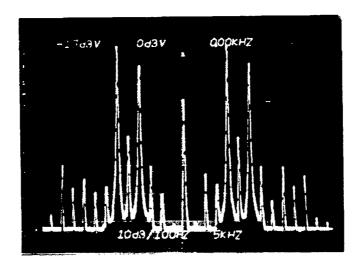

| 89(a)  | CCD2 Serial Output Linearity 0.4 V Signal                                                                 | 138  |

| 89(b)  | CCD2 Serial Output Linearity 0.55 $V_{pp}$ Signal                                                         | 138  |

| 90     | Multiplier Linearity Test Circuit                                                                         | 139  |

| 91 (a) | Multiplier Output $V_{in} = \pm 0.3 V_{pk}$                                                               | 141  |

| 91(b)  | Multiplier Output $V_{in} = \pm 1 \ V_{pk}$                                                               | 141  |

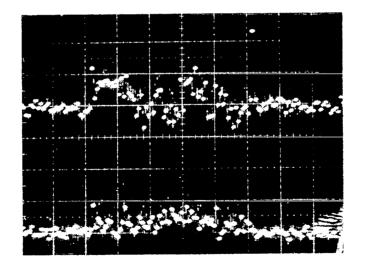

| 92 (a) | Convolution of Two 300 mV Impulses (CCD2 Offsets)                                                         | 142  |

| 92 (b) | Convolution of Impulse with CCD Offsets (CCD1 Offsets)                                                    | 142  |

| 93 (a) | CCD1 Frequency Domain Offset Measurements (Low Pass Output to 2.5 kHz)                                    | 145  |

| 93 (b) | CCD1 Low Pass and Offset Error Outputs to 10 kHz (Offset Error Output)                                    | 145  |

| 94(a)  | CCDI Low Pass and Offset Error Outputs to 2.5 kHz                                                         | 146  |

| 94(b)  | CCD2 Low Pass and Offset Error Outputs to 2.5 kHz                                                         | 146  |

| 95(a)  | CCD2 Low Pass Output to 25 kHz                                                                            | 147  |

| 95(b)  | CCD2 Offset Error Output to 25 kHz                                                                        | 147  |

| 96 (a) | Multiplier Scale Factor Accuracy; Convolution of CCDl (Impulse of Four Samples) with CCD2 (Full Scale Dc) | 149  |

| 96 (b) | Multiplier Scale Factor Accuracy; Multiplier Scale Factor Error                                           | 149  |

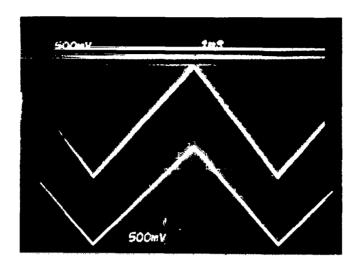

| 97(a)  | 64-Point Convolution of Two Low-Frequency Triangle Waves                                                  | 151  |

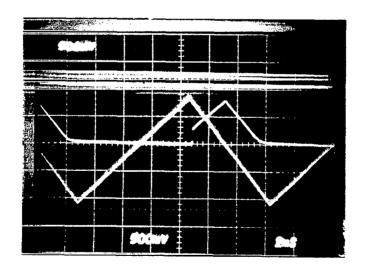

| 97(b)  | 64-Point Convolution of Two Low-Frequency Square Waves                                                    | 151  |

| 98     | Block Diagram of the Binary/Analog Correlator                                                             | 160  |

| 99     | Schematic of the Operation of the Programmable CCD Correlator                                             | 162  |

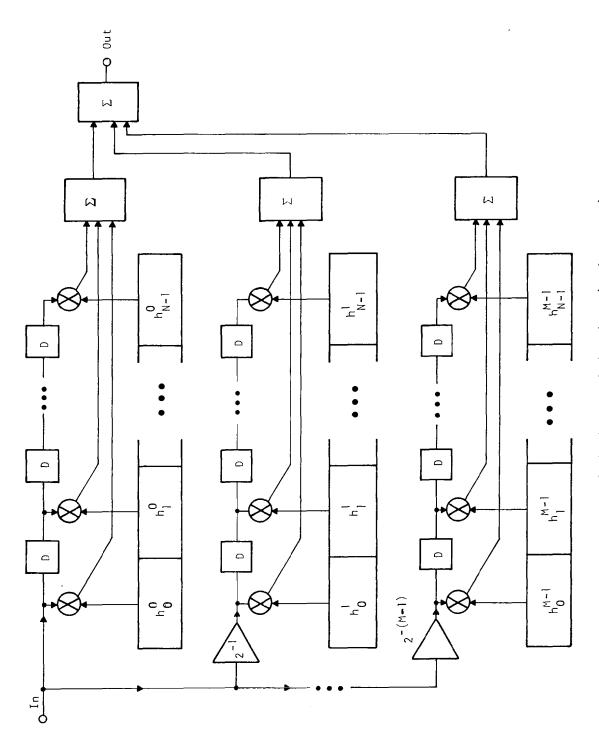

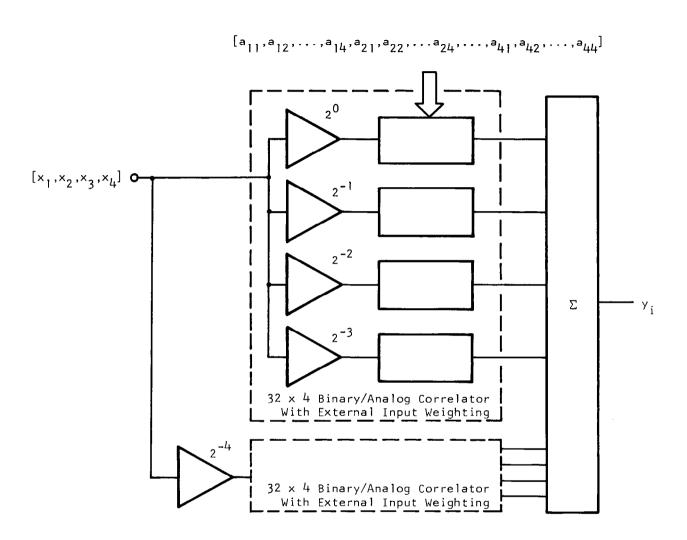

| 100    | Schematic of a Programmable CCD Correlator with M-Bit Accuracy on the Weighting Coefficients              | 165  |

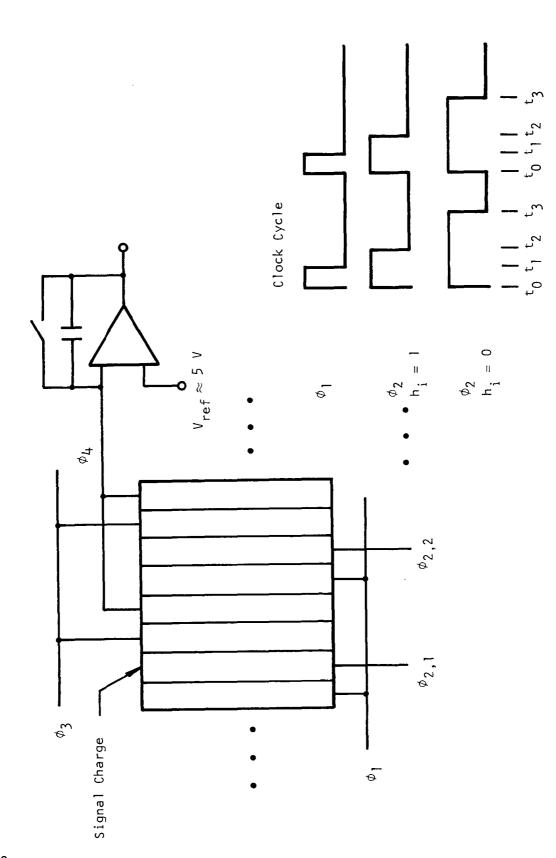

| 101    | Shift Register and Clock Generator for CCD Correlator                                                     | 166  |

| FIGURE      |                                                                                                                  | PAGE |

|-------------|------------------------------------------------------------------------------------------------------------------|------|

| 102         | Photograph of a 32-Stage Binary/Analog Correlator with Four-Bit Weighting Coefficients                           | 167  |

| 103         | Experimental Impulse Response of 32-Stage Binary/Analog Convolver                                                | 168  |

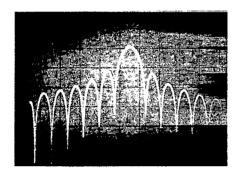

| 104         | Response of the Test Device Operated as a Bandpass Filter                                                        | 169  |

| 105         | Frequency Response of the Binary/Analog Correlator Programmed to Give a Bandpass Filter with Passband at 125 kHz | 170  |

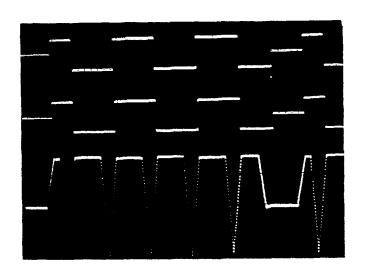

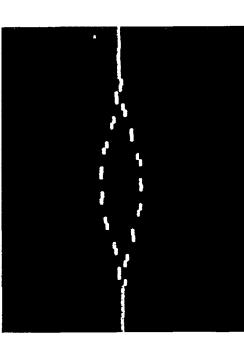

| 106         | Matched Filter Operation of the Test Device Using a 13-Bit Barker Code                                           | 172  |

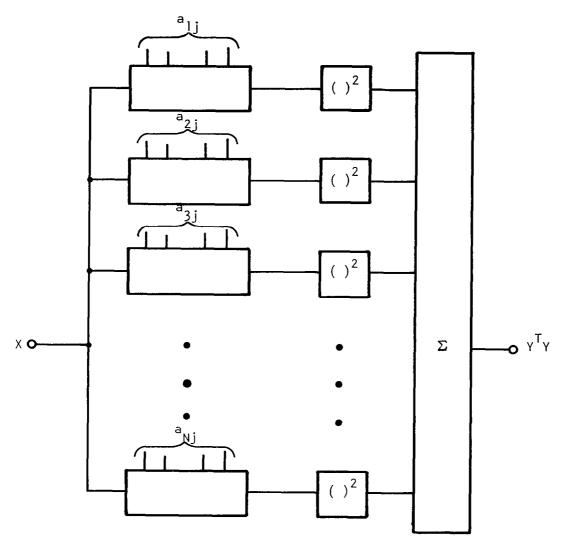

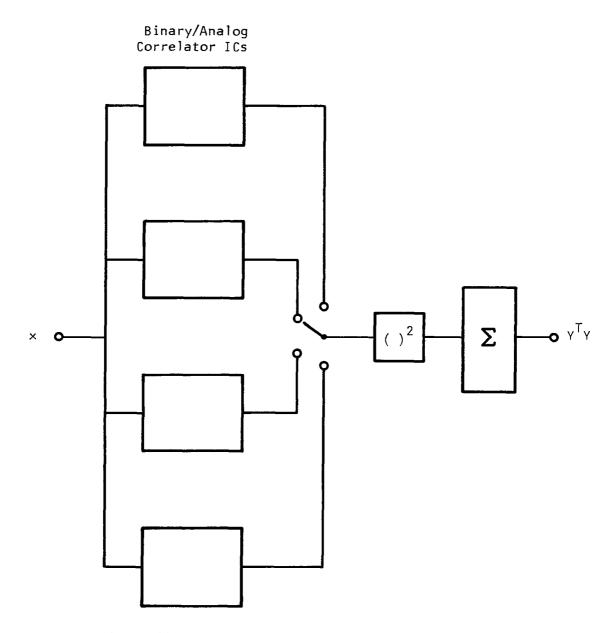

| 107         | Block Diagram for Computing $Y^{T}Y$                                                                             | 173  |

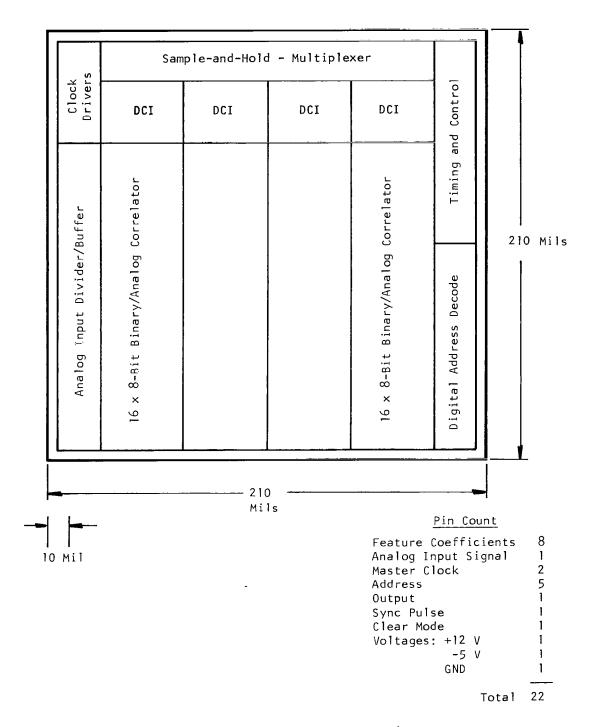

| 108         | Block Diagram of Binary/Analog Correlator IC                                                                     | 175  |

| 109         | Preliminary Design of Four-Column by 16-Stage by Eight-Bit CCD Matrix Multiplier IC                              | 176  |

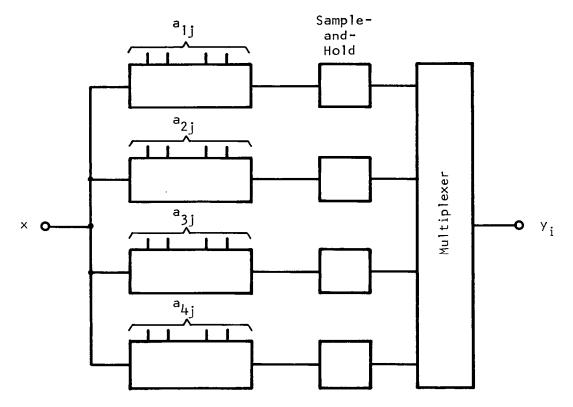

| <b>1</b> 10 | System Block Diagram for Pattern Classifier                                                                      | 178  |

| 111         | Block Diagram of Pattern Classifier Using 32 x 2-Bit Binary/Analog Correlator                                    | 179  |

| 112         | Illustration of 8-Bit Accuracy of the Binary/Analog Correlator                                                   | 181  |

|             | LIST OF TABLES                                                                                                   |      |

| TABLE       |                                                                                                                  | PAGE |

| I           | FET Geometries and Supplies                                                                                      | 36   |

| ΙΙ          | MDAC Error                                                                                                       | 75   |

| III         | MDAC Characteristics                                                                                             | 77   |

### SECTION I INTRODUCTION

The mathematical operation of convolution is a very important function in many of the pattern recognition or pattern classification algorithms that are used to synthesize useful information about the earth from the electrical outputs of satellite-borne environmental sensors. Since charge coupled devices (CCDs) are so well suited to performing convolution, it is not surprising that substantial interest has arisen within NASA in developing CCDs for preprocessing environmental sensor data preparatory to its transmittal to the ground.

The one complication that limits the immediate usefulness of CCDs is the fact that the satellite preprocessors are learning machines and must adapt to the terrain they are observing. In terms of CCD hardware, this means that the convolutions must be programmable; i.e., the impulse responses of the filters must be electronically variable.

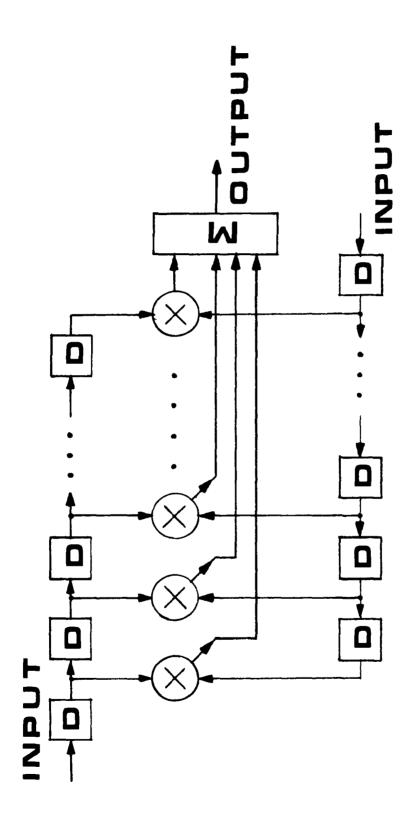

The canonical CCD transversal filter, illustrated in Figure 1, has fixed weighting coefficients  $h_n$  n=0, N-1 that are coded into the photomask with which the device is made. The impulse response is determined by the  $h_n$  and is not electrically alterable. Various approaches have been tried to construct filters with electronically alterable  $h_n$ , but all such attempts have failed to maintain the electronic simplicity of the fixed weighting coefficient transversal filter.

This program addresses two different techniques for performing programmable correlation

- Frequency domain correlation using the CCD chirp z-transform (CZT).

- Time domain correlation using direct analog/analog correlation and binary/analog correlation.

Two separate ICs have been developed under the program:

• 32-point CCD CZT IC.

Figure 1.-Block Diagram of a Transversal Filter Showing Delay Stages D and Weighting Coefficients  $h_n$  n=0, N-1.

32-point CCD analog/analog correlator.

These two ICs are discussed in Sections II and III, respectively. In addition, a prototype IC capable of correlating a digital reference word with an analog input signal was evaluated under this program. The evaluation of the binary/analog correlator is discussed in Section IV.

#### A. Frequency Domain Correlation

This approach to programmable correlation is based on the fact that correlation in the time domain is equivalent to multiplication in the frequency domain. Consequently, the frequency domain correlator is based on taking the discrete Fourier transform (DFT) of the input signal.

The discrete Fourier transform operation can be performed using the chirp z-transform algorithm. 4 The CZT gets its name from the fact that it can be implemented in an analog manner by (1) premultiplying the time signal with a chirp (linear FM) waveform, (2) filtering in a chirp convolution filter, and (3) postmultiplying with a chirp waveform.

When implemented digitally, the CZT has no advantages over the conventional fast Fourier transform algorithm.  $^4$  However, the algorithm lends itself naturally to implementation with CTD transfersal filters.  $^{5,6}$

Starting with the definition of the DFT

$$F_{k} = \sum_{n=0}^{N-1} f_{n} e^{-i2\pi n k/N}$$

(1)

and using the substitution

$$2nk = n^{2} + k^{2} - (n - k)^{2} , \qquad (2)$$

the following equation results.

$$F_{k} = e^{-i\pi k^{2}/N} \left[ \sum_{n=0}^{N-1} \left( f_{n} e^{-i\pi n^{2}/N} \right) e^{i\pi (k-n)^{2}/N} \right] .$$

(3)

This equation has been factored to emphasize the three operations that make up the CZT algorithm. It is illustrated in Figure 2.

To implement the conventional N-point CZT, the CCD filters are chirp filters of length 2N-1 that chirp from -f to +f, and the premultiply waveform has a time duration N/f and chirps from zero to -f. A physical interpretation in terms of correlation of the input chirp with the filter is given in Figure 3. When the input signal has zero frequency, the product with the premultiply chirp results in an input waveform to the filter that chirps from 0 to  $-f_c$ . The samples corresponding to frequencies near f = 0 are clocked into the filter first, and those near  $f = -f_c$  are clocked in last. This sequence of samples results in a correlation peak at  $t = t_0$ , when the product waveform has been clocked into the first half of the filter. When the input frequency is  $f_1 \neq 0$ , the product with the premultiply chirp results in an input to the filter that chirps from  $f_1$  to  $-f_c + f_1$ . The input waveform ( $V_{in} \times chirp$ ) in Figure 3 corresponds to an input signal at a frequency  $f_1$  at time  $t = t_0$ . This waveform is shifted to the right as t increases, resulting in a correlation peak at  $t_1$ . The shift in time relative to the dc correlation peak is

$$t_{1} - t_{1} = \frac{N}{f_{c}^{2}} f_{1} . \tag{4}$$

In this way, the time axis of the output is calibrated in frequency.

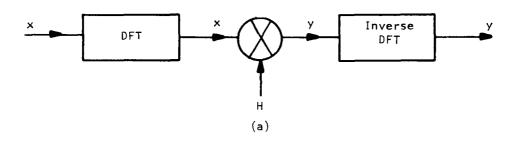

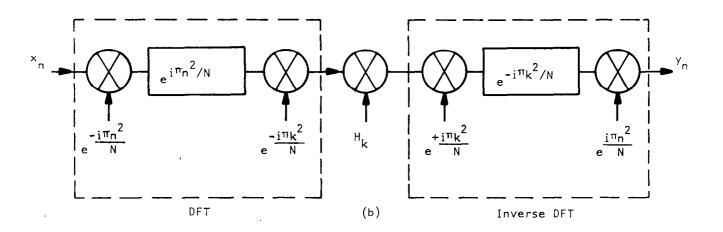

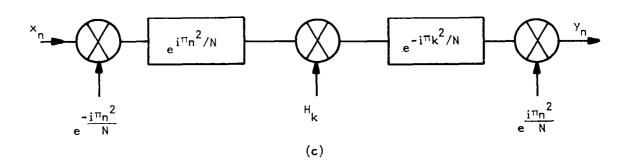

The CZT is very convenient for performing programmable correlation. Figure 4(a) shows that correlation of x(t) with h(t) can be accomplished by (1) performing the discrete Fourier transform (DFT) of x(t) to obtain X(f); (2) multiplying X(f) by H(f), where H(f) is the DFT of h(t); and (3) performing the inverse DFT on  $Y(f) = X(f) \cdot H(f)$ .

Figure 2.-Schematic of the CZT Algorithm.

Figure 3.-Interpretation of the CZT in Terms of Chirp Input Waveforms in Chirp Filters.

Figure 4.-Block Diagram of a CCD Programmable Correlator.

Figure 4(b) is obtained from 4(a) by replacing the DFT and inverse DFT blocks with their CCD CZT equivalents, and 4(c) is obtained by simplifying 4(b). Figure 4(c), therefore, represents an economical and useful way to perform programmable correlation in pattern classification machines, and this program had as one of its goals the development of CCD CZT ICs to perform spectral analysis for a broad range of NASA requirements including programmable correlation.

The 32-point CCD CZT IC developed under this program is discussed in Section II.

#### B. Time Domain Correlation

An alternate approach to achieving programmable correlation is the direct time domain correlator. The analog/analog correlator is illustrated in Figure 5. It is similar in operation to the transversal filter illustrated in Figure 1, except that the weighting coefficients are electronically programmable by clocking an analog reference signal into the device. It operates by first loading CCD1 with a reference signal and then clocking a second signal through CCD2. Since the charge is stored dynamically in CCD1, it decays due to thermal leakage and must be refreshed after 10 ms to 100 ms.

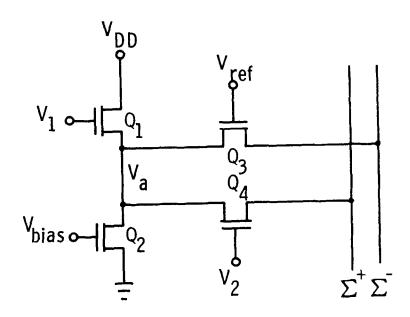

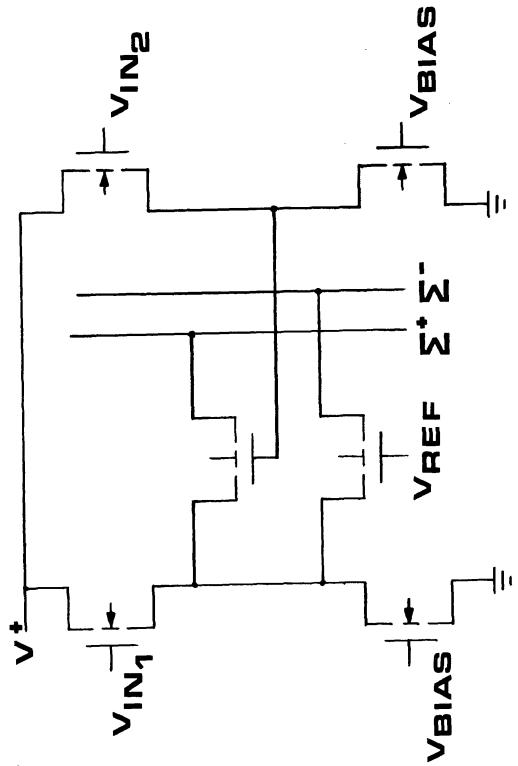

Each stage of the CCD is tapped with a diffusion whose potential takes on a value approximately proportional to the signal charge, and four-quadrant multiplication is accomplished using the circuit of Figure 6. Transistors  $Q_3$  and  $Q_4$  act as voltage-controlled resistors, and the balanced configuration overcomes the inherent nonlinearity of MOS transistors used as resistors. The output  $V_2$  from CCD2 is applied to the gate of  $Q_4$ , and the gate of  $Q_3$  is biased to  $V_{\rm ref}$ , which is equal to the value of  $V_2$  when CCD2 has the zero level of charge (half-full well). The output from CCD1 is buffered by a sourcefollower whose output  $V_3$  is applied to the drain of  $Q_3$  and  $Q_4$ . The sources of  $Q_3$  and  $Q_4$  are connected to virtual ground current buses  $\Sigma^-$  and  $\Sigma^+$  whose currents are differenced in an off-chip differential amplifier.

Ž

Figure 5.-Block Diagram of the Analog/Analog Time Domain Correlator.

Figure 6.-Circuit Schematic of the Four-Quadrant Multiplier Used in the Analog/Analog Correlator of Figure 5.

The currents flowing in  $\mathbf{Q_3}$  and  $\mathbf{Q_4}$  are

$$I_3 = \beta \left( V_{\text{ref}} - V_t - \frac{1}{2} V_a \right) V_a , \qquad (5)$$

and

$$I_{\mu} = \beta (V_2 - V_t - \frac{1}{2}V_a) V_a$$

(6)

The difference current

$$I_4 - I_3 = \beta (V_2 - V_{ref}) V_a$$

(7)

contains no nonlinear terms.

The 64-point analog/analog time domain correlator designed, fabricated, and tested under this contract is discussed in detail in Section III.

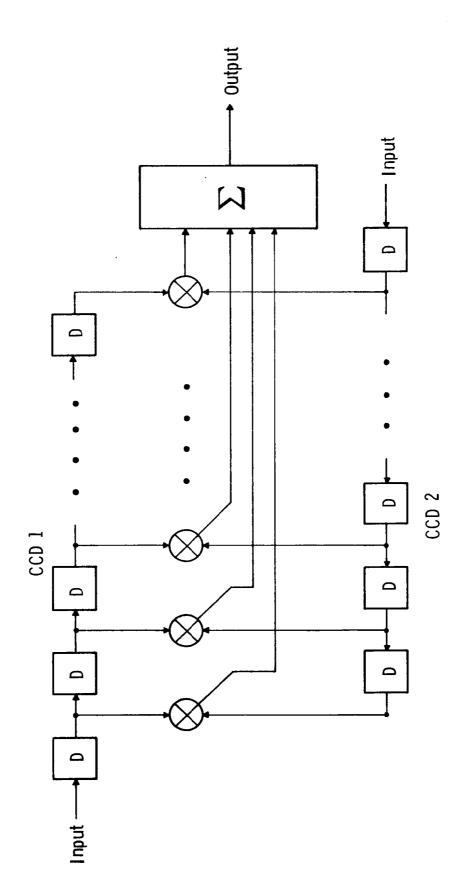

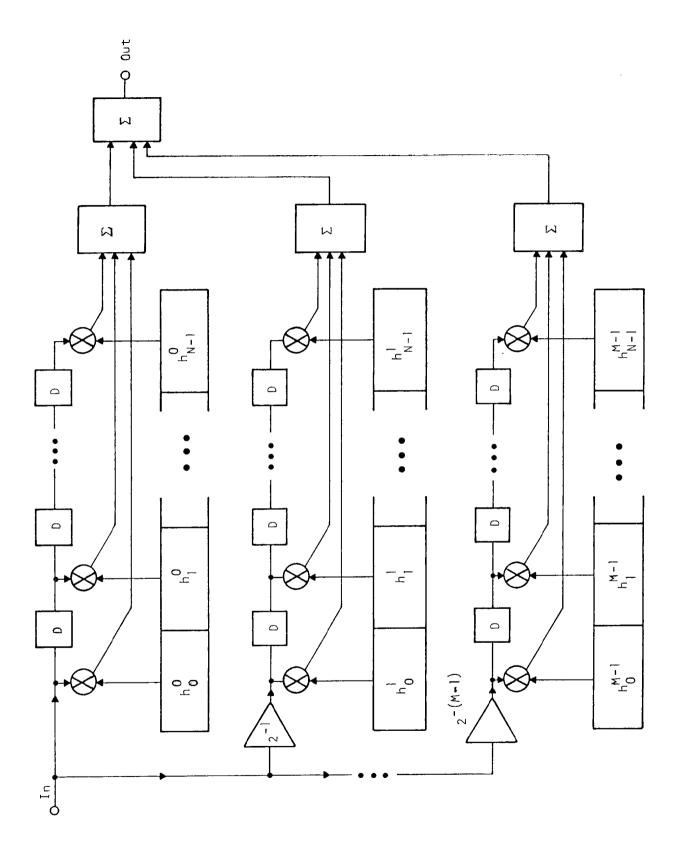

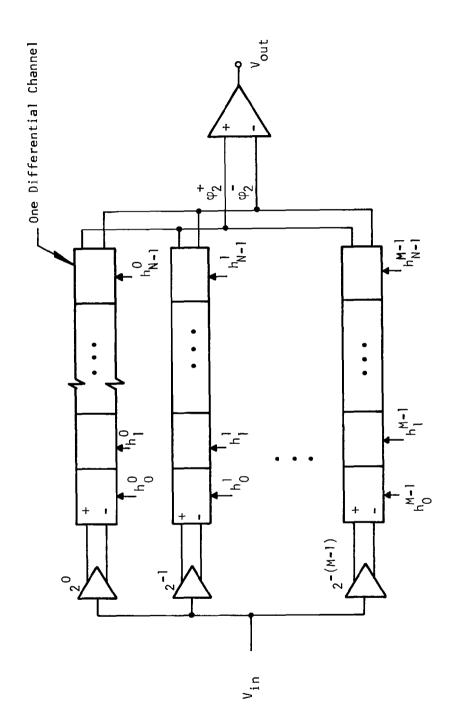

An alternate approach to the analog/analog correlator is the binary/analog correlator. The concept of the binary/analog correlator is illustrated in Figure 7. The weighting coefficients ( $^{\rm h}_{\rm o}$ ,  $^{\rm h}_{\rm N-1}$  of Figure 1) are made electronically programmable by decomposing each one into a binary representation.  $^{\rm h}_{\rm n}$  is represented with M-bit accuracy by

$$h_{n} = \sum_{k=0}^{M-1} h_{n}^{k} 2^{-k} . \tag{8}$$

For M-bit accuracy, M parallel CCD binary/analog correlators are put on a chip as shown in Figure 7. The most significant bit  $h_n^0$  of each coefficient is loaded into the static shift register (coefficient store) shown as elongated rectangles in the filter at the top of the figure. The second most significant bit  $h_n^1$  of each coefficient is loaded into the second coefficient store, and the least significant bit  $h_n^{M-1}$  is loaded into the coefficient store shown at the bottom of the figure. The analog input signal to be filtered is applied without

Figure 7.- Block Diagram of the Binary/Analog Correlator.

attenuation to the top filter (most significant bit). The input is attenuated by a factor of two at the input of the second filter (second most significant bit), and it is attenuated by a factor of  $2^{M-1}$  at the input to the bottom filter (least significant bit). This attenuation is performed using capacitive ratio techniques similar to those employed in MOS MDAC technology. The coefficients stored in the static shift registers then control the weighting of the transversal filters, and when the outputs of each filter are summed together as shown, the result is

$$H(z) = \frac{V_{out}(z)}{V_{in}(z)} = \sum_{n=0}^{N-1} h_n^0 z^{-n} + 2^{-1} \sum_{n=0}^{N-1} h_n^1 z^{-n} + \dots + 2^{-(M-1)} \sum_{n=0}^{N-1} h_n^{M-1} z^{-n}$$

(9)

$$= \sum_{n=0}^{N-1} \left[ \sum_{k=0}^{M-1} \left( h_n^k 2^{-k} \right) \right] z^{-n}$$

(10)

$$= \sum_{n=0}^{N-1} h_n z^{-n} .$$

(11)

The binary/analog correlator is discussed in detail in Section IV.

# SECTION II 32-POINT CCD CZT IC

This section describes in detail the design and operation of the frequency domain correlator. The design of each component of the CZT IC is discussed, and applications and experimental results are described.

#### A. Chip Overview

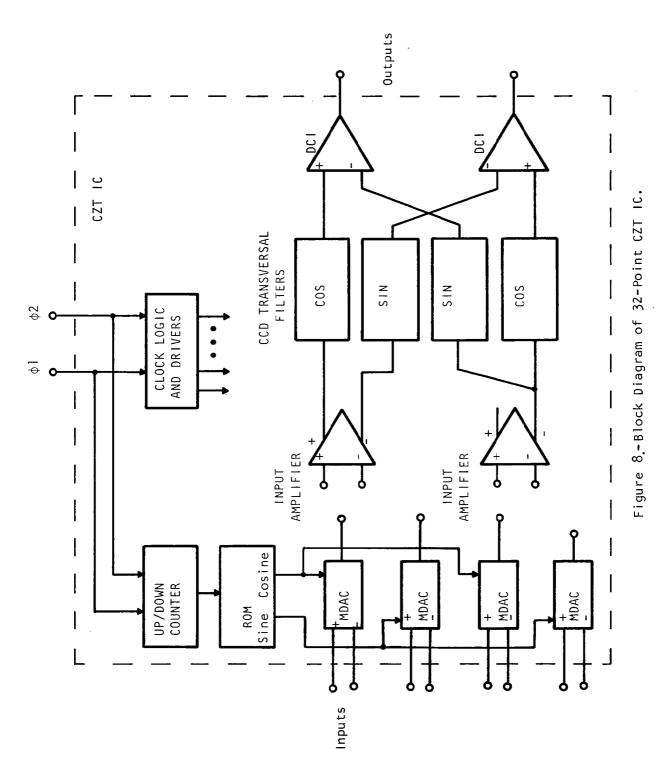

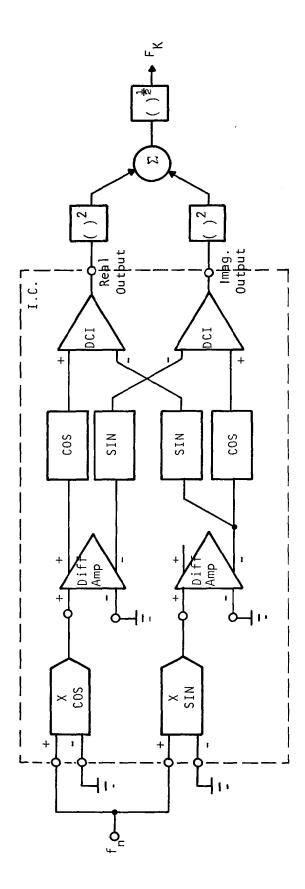

The frequency domain correlator contains all the hardware needed to implement a 32-point CZT, as discussed in the introduction and shown schematically in Figure 4. The IC, shown in block diagram form in Figure 8, is composed of the following:

- ROM

- Up/down counter

- Four MDACs

- Four operational amplifiers

- Eight output buffers

- Clock generators

- Four 64-stage CCD filters.

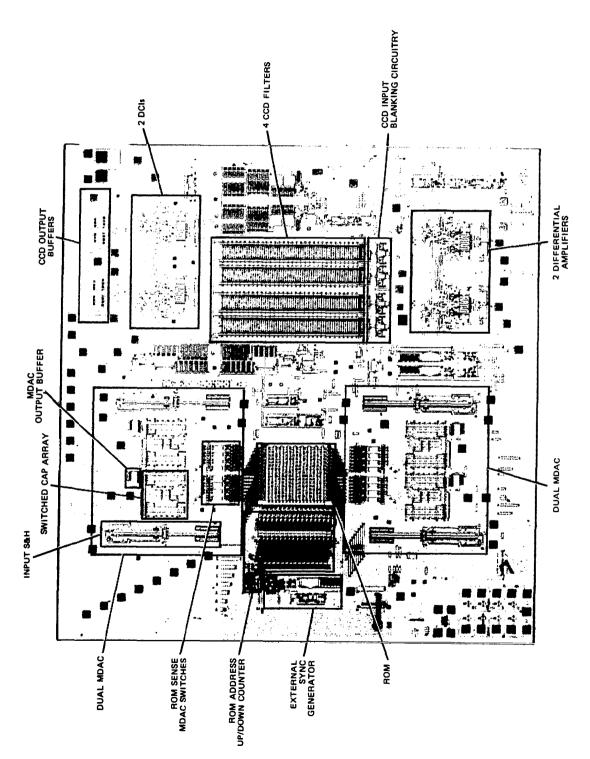

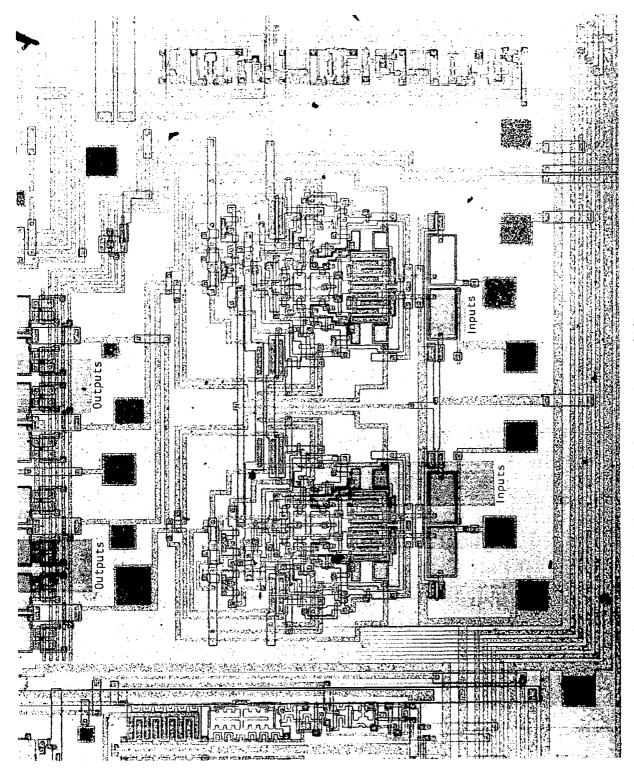

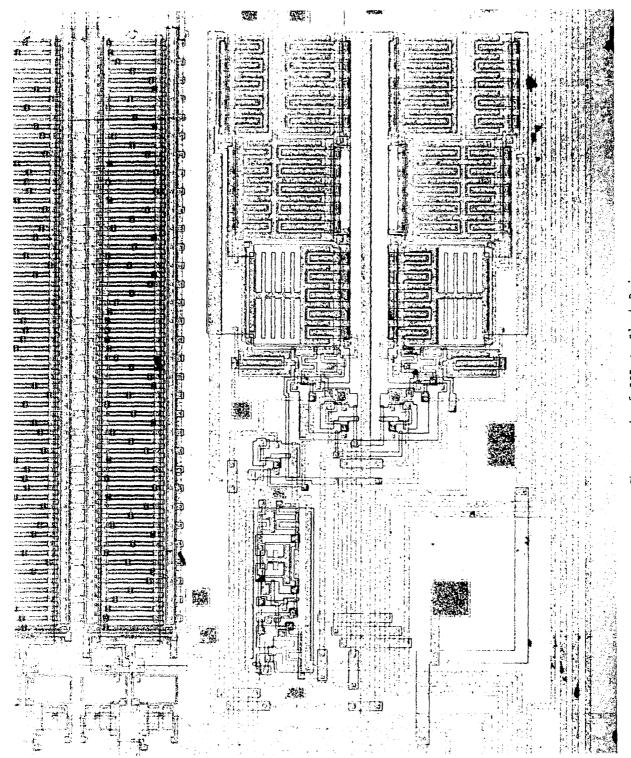

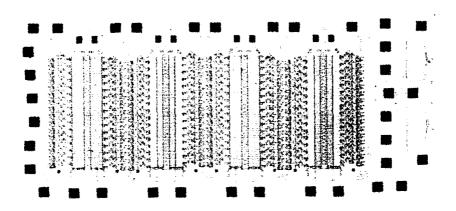

A photomicrograph of the IC is shown in Figure 9.

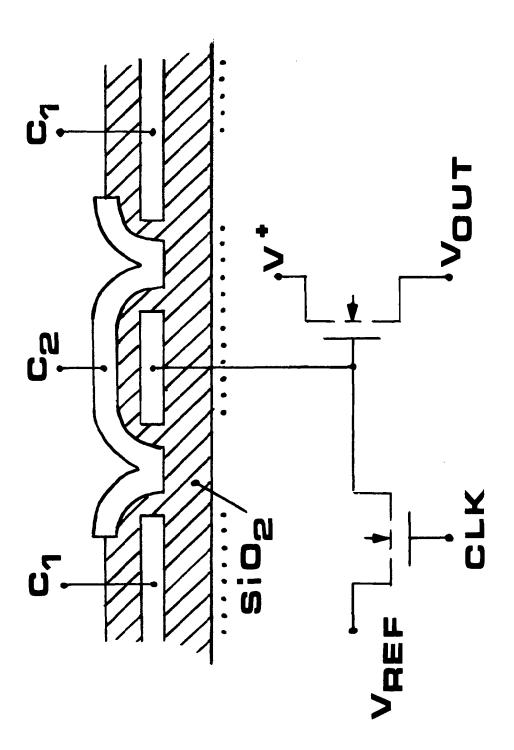

The IC measures  $6.04 \times 5.69 \text{ mm}^2$  ( $238 \times 224 \text{ mils}^2$ ) and was fabricated using TI's two-phase silicon gate coplanar electrode structure, shown in Figure 10. To provide storage and directionality, n-type ion implants (wells) are diffused under the two clock electrodes. As seen in Figure 10, when both the  $\phi_1$  and  $\phi_2$  clocks are off, charge (signal) resides in the wells (under the  $\phi_1$  electrode for this example). When  $\phi_2$  is turned on, a potential energy gradient is formed, forcing the charge to move under the  $\phi_2$  electrode. Next, both clocks are turned off, and the charge remains in the  $\phi_2$  well. When  $\phi_1$  is turned on, the charge moves under the  $\phi_1$  electrode and has moved one bit down the CCD structure.

Figure 9,-Photomicrograph of 32-Point CCD CZT IC.

Figure 10.-Silicon Gate CCD Coplanar Electrode Structure.

Because of the complexity of the analog circuits surrounding the CCD filters, much circuit modeling and MOSFET modeling was needed. To obtain accurate MOSFET models for use in the circuit modeling, data were taken on MOSFETs from previously processed ICs. These data were tabulated and fitted to the Shichman-Hodges MOS equations using the computer, and parameter values were extracted for circuit modeling. This procedure allowed the design of the peripheral circuitry to be accomplished with a high degree of confidence.

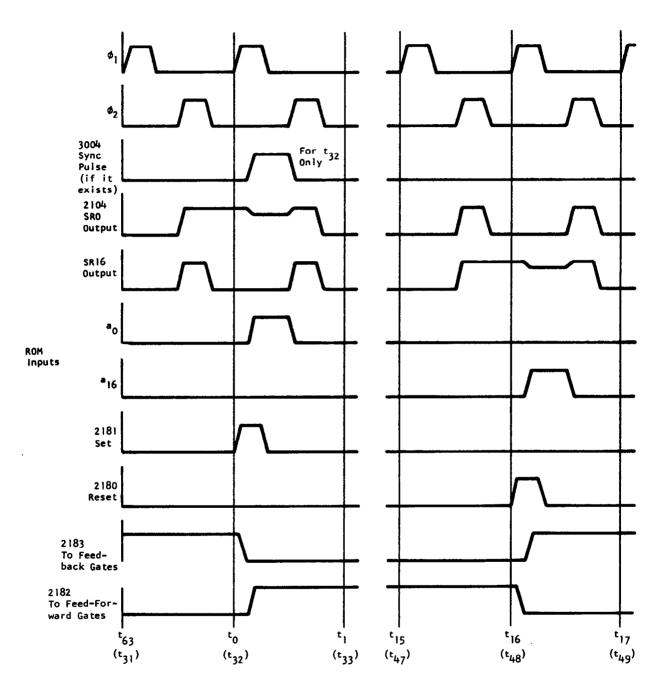

In an effort to provide the greatest possible flexibility, the IC was partitioned into three main signal processing sections. The first two sections are both dual MDACs. The MDACs and their associated circuitry are shown in Figures 11 and 12. The ROM is common to both sets of MDACs and has 16 output lines, 8 for the sin chirp words and 8 for the cosine chirp words. chirp is available to one MDAC in each figure, and the cos chirp is available to the other two MDACs. The eight-bit external word is available to all four MDACs and may be individually selected for each set of dual MDACs. consists of an input sample-and-hold buffer, ROM sense and MDAC drive circuitry, the MDAC capacitor array, and an output buffer. The third section of the partition, shown in Figure 13, consists of two CCD input amplifiers  $(A_1 \text{ and } A_2)$ , CCD input blanking circuitry, four 64-stage CCD transversal filters, two differential current integrators (CCD output amplifiers), and four output buffers. The CCD input amplifiers make the inverse of the signal available to the CCDs so that both CCD outputs to the DC! may be summed the same way. The CCD input blanking circuitry uses the T $_{

m l}$  and T $_{

m 2}$  pulses from the up/down counter to load "zeros" into the CCD for appropriate periods. The  $\mathsf{T}_2$  pulse is always used. The  $T_1$  pulse is used only to implement the noncircular correlation function and must be stitch-bonded on-chip if it is required.

Each of the three partitioned sections utilizes output buffering circuits so that the sections can be connected in several configurations using one or more ICs. Also, each section has the circuitry required to process real and

Figure 11,-Block Diagram of Internal ROM, Up/Down Counter, and Dual MDACs.

Figure 13.-Block Diagram of CCD Input Amplifiers, CCDs, DCI, and Output Buffers.

imaginary signal components. In addition to the three partitioned sections described above, the chip contains clock-generating circuitry. The clock generators derive all the internal timing pulses from the two-phase clocks input to the IC.

#### B. <u>CCD Filter</u>

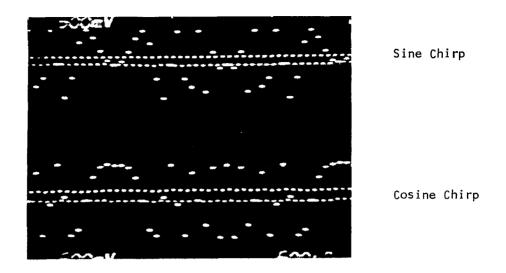

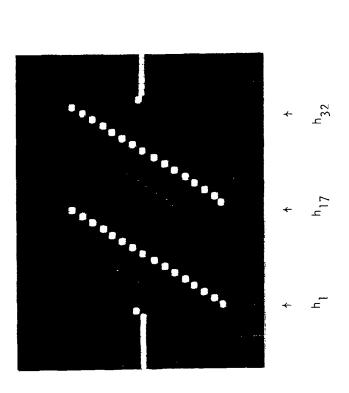

The four filters needed to implement the CZT algorithm are chirp convolution filters with 2N-1 stages. A photograph of the four CCD filters is shown in Figure 14. The weighting coefficients for the sine and cosine chirp filters are

$$h_k^{\cos} = \cos \frac{\pi k^2}{32}$$

$k = 0.31$

$$h_k^{\sin} = \sin \frac{\pi k^2}{32}$$

$k = 0.31$ .

The coefficients were realized using the split-electrode technique, and because the CZT IC was designed to perform the true CZT, the filter tapweights were repeated for the remaining N-1 stages of the filters.

The CCD filter structure is illustrated in Figure 15. Each filter is surface channel and uses two-phase clocking. Each stage is 25.4  $\mu m$  (1 mil) long and consists of a 12.7  $\mu m$  (0.5 mil) long first poly electrode and a second poly electrode that is effectively 12.7  $\mu m$  (0.5 mil) long. The barriers are 5.1  $\mu m$  (0.2 mil) each, and the wells are 7.6  $\mu m$  (0.3 mil) each. The channel width is 155  $\mu m$  (6.1 mils). The split electrodes are the first poly electrodes. The split electrode gaps are 5  $\mu m$  (0.2 mil), and the channel stop beneath each gap is 12.7  $\mu m$  (0.5 mil) wide.

The channel stop beneath each gap serves two purposes. The first is to prevent the electrons of the signal charge packets from being trapped in these

Figure 14.-Photomicrograph of CCD Transversal Filters.

24

Figure 15.-Schematic of CCD Filters.

areas and causing serious degradation of the charge transfer efficiency. The second reason for the channel stop is that the position of the weighting coefficients is defined by the same photomask that defines the CCD channel. Thus, the weighting coefficient accuracy is determined by the accuracy with which the photomask is made and is not dependent on alignment of different photomask levels in the device fabrication process. With this approach approximately 0.16% accuracy in the weighting coefficients is possible with a 155  $\mu$ m (6.1 mil) wide channel in the CCD. This gives an area for the first well area of 7.6 x (1.55 - 12.7) = 1084  $\mu$ m<sup>2</sup> [0.3 x (6.1 - 0.5) = 1.68 mil<sup>2</sup>].

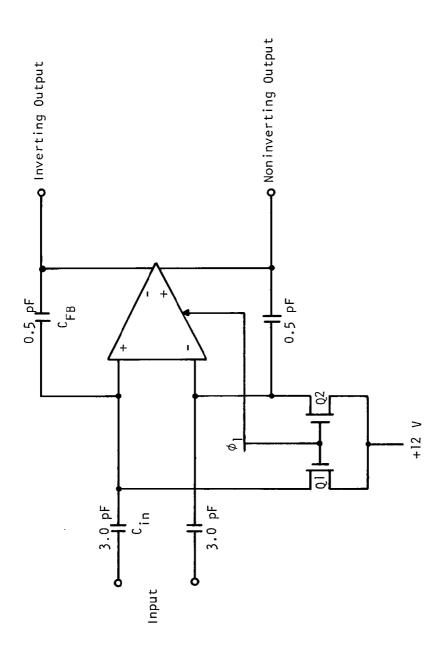

The CCD clocking sequence is illustrated in Figure 16 relative to the two-phase input clocks  $\phi_1$  and  $\phi_2$ . The analog input to the CCD is capacitively coupled to the input diode. The fat-zero level on the diode is set to  $V_{FZ}$  when  $\phi_1'$  comes up. After  $\phi_1'$  falls, the CCD input signal is allowed to change and the IP/G signal pulls up, dumping signal charge into the receiving well, which is controlled by a dc bias. The total receiving well area is  $710~\mu\text{m}^2$  (1.1 mil $^2$ ), making the capacity of this well 65% as large as the capacity of the following wells. This prevents saturation of the filter. The signal is sampled when IP/G falls. Next, the CCD first  $\phi_1$  clock rises and falls, dumping the sampled signal charge under the first split electrode. The CCD first  $\phi_1$  electrode rises to a level less than that of the CCD  $\phi_2^\pm$  clock lines to make sure that all charge is transferred. At the same time, the CCD  $\phi_1$  electrodes fall, transferring the charge packets under the CCD  $\phi_1$  electrodes to the remaining split electrodes. These split electrodes must be floating when this occurs in order to sense the charge packets.

The capacitive coupling of the CCD  $\phi_1$  line to the CCD  $\phi_2^\pm$  lines is compensated for by another clock,  $\overline{\text{CCD}\phi_1}$ , which is capacitively coupled to the CCD  $\phi_2^\pm$  lines by approximately the same amount. The  $\overline{\text{CCD}\phi_1}$  clock comes up when CCD  $\phi_1$  clock falls. The output signal is sampled before the CCD  $\phi_1$  line rises

Figure 16.-CCD Timing.

again. When the CCD  $\phi_2^\pm$  electrodes are pulled down, the charge packets are transferred to the following CCD  $\phi_1$  electrodes. When each charge packet reaches the end of the CCD, it is dumped onto the output diode, which is tied to  $V_{DD}$ . An effort was made in laying out the four CCDs and their interconnects to match the capacitance on all four output lines. Consideration was given both to capacitance to the substrate and to capacitance to the other clock lines.

#### C. Operational Amplifiers

#### 1. Design

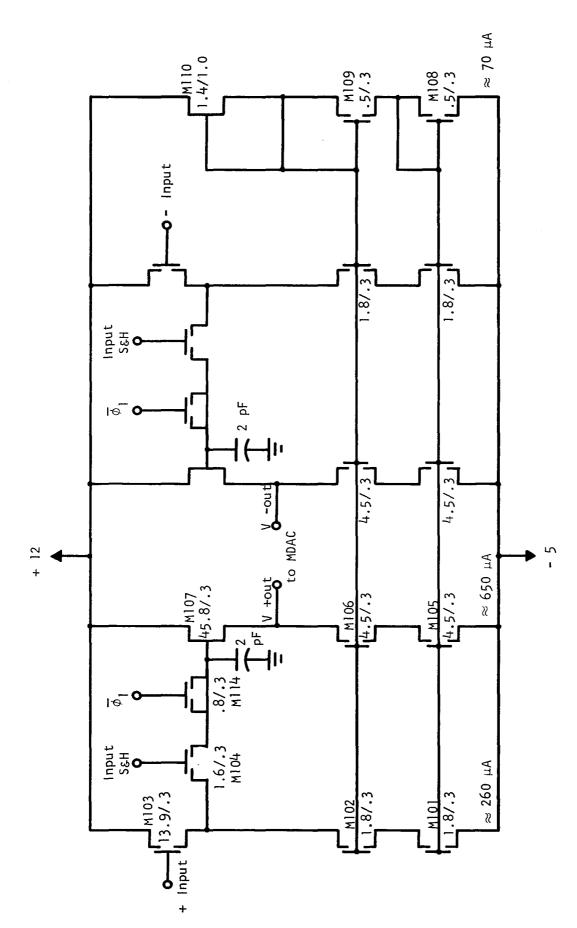

In the realization of the 32-point CZT, four operational amplifiers are needed to perform two functions. The first function is to provide gain and the inverse of the signal to the inputs of the CCDs. These amplifiers are called the input diffamps and are designated as Al and A2 in Figure 13. The need for the inverse of the signal can be understood best by considering the function of the differential current integrator (DCI).

The general DCI scheme and the capacitances associated with the CCD are shown in Figure 17. The following capacitances are indicated in the figure:

$C_S$  = stray to substrate, made equal on  $V^\pm$  nodes.  $C_{OF}$  = fixed overlaps from phase I ( $\phi_I$ ) to  $V^\pm$  nodes, also made equal.  $C_{OL}$  ( $I \pm h_i$ )/2 = overlap to  $\phi_I$  for each stage, depends on  $h_i$ .  $C_{OF}$  + N/2  $C_{OL}$  = a coupling to  $\overline{\phi_I}$ , equal for each node  $V^\pm$ .  $C_{OX}$  ( $I \pm h_i$ )/2 =  $V^\pm$  electrode to channel capacitance for each stage.  $C_D$  ( $I \pm h_i$ )/2 = depletion layer capacitance for each stage.

A possible timing scheme is shown in Figure 18. The operation is as follows. The split electrode nodes  $V^{\pm}$  are clocked to the voltage  $V_2$  via the series switches  $S_2$ , while the phase I  $(\phi_1)$  clock is high. The switches  $S_2$  are then turned off, and nodes  $V^{\pm}$  are left floating. The next point in the timing

Figure 17.-CCD Capacitances.

28

Figure 18.-A Possible Switching Diagram for Figure 17. A high voltage on a switch turns it on.

diagram is the turn-off of phase l. At this point the charge transfers under the split electrodes. The nodes  $V^{\pm}$  are isolated, and feedthrough from  $\phi_1$  via the overlap capacitance could reduce the voltage  $V^{\pm} \cong V_2$  to a value low enough so that incomplete transfer could take place. To prevent this, a capacitive coupling to  $\overline{\phi}_1$  is provided, which is approximately equal to the coupling to  $\phi_1$ .

As the signal charge  $Q_S$  flows under the split electrodes, the node voltages  $V^\pm$  change in proportion to the sum of the tap weights  $(l \pm h_i)$ . The node voltages then are

$$v^{\pm} = v_{2} - v_{\phi_{1}} \left[ c_{0F} + \sum_{i=1}^{N} (1 \pm_{h} i) c_{0L} \right] / 2c^{\pm}$$

$$+ v_{\phi_{1}} \left( c_{0F} + \frac{N}{2} c_{0L} \right) / 2c^{\pm} + \sum_{i=1}^{N} c_{0X} (1 \pm h_{i}) (v_{i} + v_{z}) / 2c^{\pm} , \quad (12)$$

where

$$C^{\pm} = C_S + 2C_{0F} + C_{0L} \frac{N}{2} (2 \pm \overline{h}) + C_E \frac{N}{2} (1 \pm \overline{h}) ,$$

(13)

and  $C_E = C_{OS}$ ,  $C_D$  in series, and

$$\frac{\overline{h}}{h} = \sum_{i=1}^{N} h_i/N,$$

$V_7$  = bias voltage for zero signal (fat zero),

V<sub>i</sub> = signal voltage sampler.

The node voltages  $V^{\pm}$  are to be sensed by the differential feedback amplifier A when the switches SA are turned on at the next stage in the timing diagram. The negative feedback of the amplifier causes its output to change until the input voltages  $V^{\pm}$  and  $V^{\mp}$  are equal.

The output voltage  $V_{\mbox{out}}$  is proportional to the difference:

$$V^{+} - V^{-} = -V_{\phi_{1}} N\overline{h} c_{0L}/c + V_{z} N\overline{h} c_{0X}/c + c_{0X} \sum_{i=1}^{N} h_{i}V_{i}/c$$

, (14)

where  $C^{\dagger}$  and  $C^{\dagger}$  have been made equal by the addition of  $(C_{0L} + C_{E})$  Nh to node  $V^{\dagger}$ . In practice, the addition may have to be made to  $V^{\dagger}$  if h is negative.

Only the third term in Equation (14) is the desired output of the convolution filter. The first two terms need to be eliminated. This can be accomplished in two ways. The first involves an additional channel in parallel with the signal channel. This new channel is of width  $\left|\overline{h}\right| \cdot W_S$  if  $W_S$  is the signal channel width, and is located on the side of the  $V^-$  electrode if  $\overline{h}>0$ . The new channel only carries a signal equal to  $V_Z$ . Again, in practice, two such channels may be required, one on each side of the main signal channel. Their widths are then adjusted so that they differ by  $\left|\overline{h}\right|$   $W_S$ . A possible layout of such a structure is shown in Figure 19. The addition not only cancels the two unwanted parts in the output [Equation (14)], but also adds just the required capacitances to equalize  $C^+$  and  $C^-$ .

A second way the two additional terms in Equation (14) can be cancelled is appropriate to the chirp z-transform. Here the output of a cos and a sin chirp are added. However, the values of  $\overline{h}$  for the sin and cos chirp are equal, at least for an even number of stages. Even when apodization is added to the CCD chirp filter, as may be done for a sliding transform, the values of  $\overline{h}$  differ by only a small amount. For example, for even N,  $\overline{h}$ (cos) =  $\overline{h}$ (sin) =  $1\sqrt{2N}$ . For a Hamming weighted filter we calculate

Figure 19.-Symmetrized and Compensated Two-Phase CCD Layout.

| <u>N</u> | h (cos) | $\frac{\overline{h}(sin)}{}$ | $\frac{1}{h}$ (cos - sin) |

|----------|---------|------------------------------|---------------------------|

| 512      | 0.0313  | 0.0311                       | $1.7 \times 10^{-4}$      |

| 256      | o.0444  | 0.0439                       | 5.0 x 10 <sup>-4</sup>    |

| 128      | 0.0632  | 0.0618                       | $1.4 \times 10^{-3}$      |

| 64       | 0.0903  | 0.0863                       | $4.0 \times 10^{-3}$      |

| 32       | 0.130   | 0.119                        | 1.1 x 10 <sup>-2</sup>    |

| 16       | 0.189   | 0.158                        | 3.1 x 10 <sup>-2</sup>    |

| 8        | 0.274   | 0.193                        | 8.1 x 10 <sup>-2</sup>    |

The difference is small for the larger transforms.

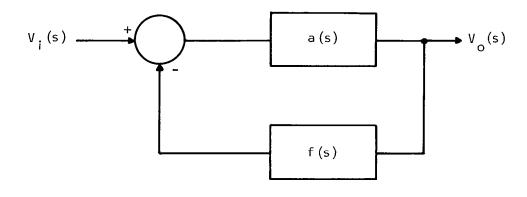

The required equalization of capacitances and cancellation of unwanted signals can then be obtained by substracting the output of a cos and sin chirp filter. In practice, this subtraction is achieved by cross-connecting the  $V^+$  (cos) and  $V^-$  (sin) nodes. No additional channel is needed. However, one of the input signals has to be available in both normal and inverted form. Since the length of our transform was small and gain was needed at the inputs to the CCD filters, we chose to use the second approach. Two operational amplifiers are used at the input to the filters and two amplifiers are used as DCIs at the output of the filters. The designs of the two diffamps are identical except for the values of the compensation capacitors and the feedback capacitors.

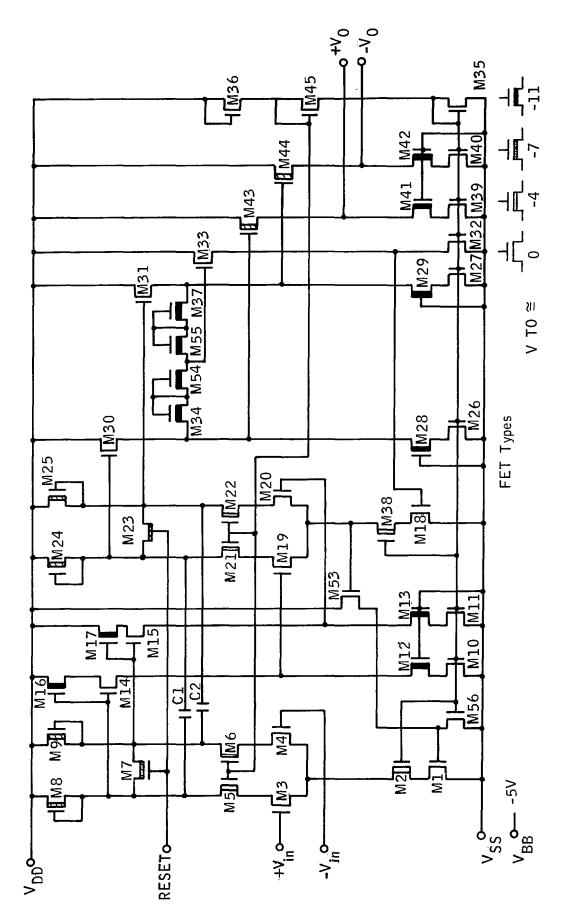

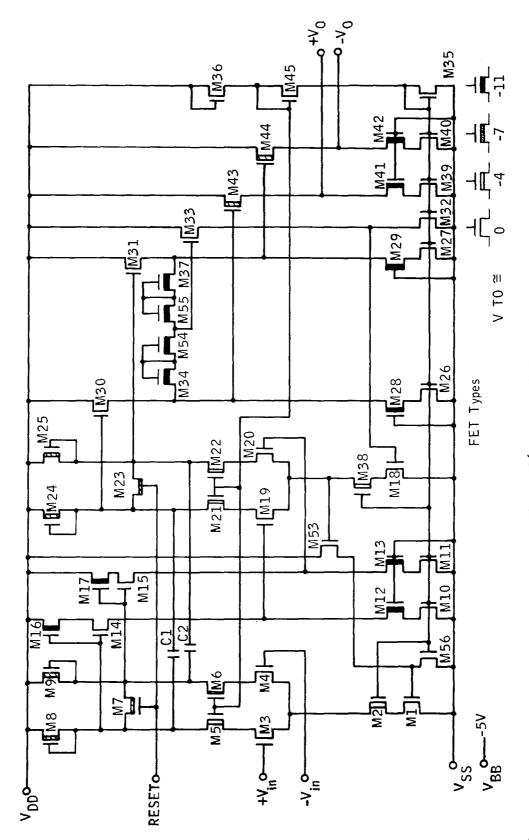

The basic amplifier is shown in Figure 20 with the design parameters listed in Table I. A photomicrograph of the amplifier is shown in Figure 21.

The amplifier has two stages of differential gain. Each stage is cascaded and uses depletion loads. Between the first and second stages are buffers (M14 and M15) which also serve as level translators. After the second gain stage, the outputs are double-buffered by M30 and M31, and then by M33 and M34. The current source biases of all buffers are cascaded to provide a

Figure 20.- DCI Amplifier Compensated for Gain of 30.

Figure 21.- Photomicrograph of Operation Amplifier Used on CZT 1C.

$\frac{ \text{Table I}}{\text{FET Geometries and Supplies}}$

| V <sub>SS</sub> = 0         C1 = C2 = 0.075 pF           FETS         W/L (mils)         W/L (µm)           M1, M7, M23         0.35/0.3         8.9/7.6           M2         1.25/0.3         32/7.6           M3, M4         18/0.3         457/7.6           M5, M6         1.30/0.3         33/7.6           M8, M9         0.35/0.7         8.9/17.8           M10,M11         0.7/0.3         17.8/7.6           M12, M13         0.75/0.5         19/12.7           M14, M15         1.5/0.3         38/7.6           M16, M17, M21, M22         0.45/0.5         11.4/12.7           M18         0.6/0.3         15.2/7.6           M19, M20         2.45/0.3         62/7.6           M24, M25         0.35/0.5         8.9/12.7           M26, M27         0.5/0.3         12.7/7.6           M28, M29         0.55/0.5         14/12.7           M30, M31         0.95/0.3         24/7.6           M32         0.7/0.5         17.8/12.7           M34, M37         0.35/0.65         8.9/16.5           M35         0.75/1.0         19/25.4           M36         0.65/0.3         16.5/43           M38         0.8/0.4         < | $V_{DD} = +20 \text{ at } 3.5 \text{ mA}$ |            | V <sub>RB</sub> = <b>-</b> 5 at 1.5 nA |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------|----------------------------------------|

| M1, M7, M23       0.35/0.3       8.9/7.6         M2       1.25/0.3       32/7.6         M3, M4       18/0.3       457/7.6         M5, M6       1.30/0.3       33/7.6         M8, M9       0.35/0.7       8.9/17.8         M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M45       0.75/1.7       19/43                                                                                    |                                           |            | 0.0                                    |

| M2       1.25/0.3       32/7.6         M3, M4       18/0.3       457/7.6         M5, M6       1.30/0.3       33/7.6         M8, M9       0.35/0.7       8.9/17.8         M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43 </td <td><u>FETS</u></td> <td>W/L (mils)</td> <td>W/L (µm)</td>                        | <u>FETS</u>                               | W/L (mils) | W/L (µm)                               |

| M3, M4       18/0.3       457/7.6         M5, M6       1.30/0.3       33/7.6         M8, M9       0.35/0.7       8.9/17.8         M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.3       12.7/7.6         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6                                                                                    | M1, M7, M23                               | 0.35/0.3   | 8.9/7.6                                |

| M5, M6       1.30/0.3       33/7.6         M8, M9       0.35/0.7       8.9/17.8         M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M45, M55       0.35/0.85       8.9/22                                                                                                                                | M2                                        | 1.25/0.3   | 32/7.6                                 |

| M8, M9       0.35/0.7       8.9/17.8         M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/0.3       16.5/43         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                  | M3, M4                                    | 18/0.3     | 457/7.6                                |

| M10,M11       0.7/0.3       17.8/7.6         M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                         | M5, M6                                    | 1.30/0.3   | 33/7.6                                 |

| M12, M13       0.75/0.5       19/12.7         M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                      | M8, M9                                    | 0.35/0.7   | 8.9/17. <b>8</b>                       |

| M14, M15       1.5/0.3       38/7.6         M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                       | M10,M11                                   | 0.7/0.3    | 17.8/7.6                               |

| M16, M17, M21, M22       0.45/0.5       11.4/12.7         M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                                                                                                                | M12, M13                                  | 0.75/0.5   | 19/12.7                                |

| M18       0.6/0.3       15.2/7.6         M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                                                                                                                                                                          | M14, M15                                  | 1.5/0.3    | 38/7.6                                 |

| M19, M20       2.45/0.3       62/7.6         M24, M25       0.35/0.5       8.9/12.7         M26, M27       0.5/0.3       12.7/7.6         M28, M29       0.55/0.5       14/12.7         M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                                                                                                                                                                                                                   | M16, M17, M21, M22                        | 0.45/0.5   | 11.4/12.7                              |

| M24, M250.35/0.58.9/12.7M26, M270.5/0.312.7/7.6M28, M290.55/0.514/12.7M30, M310.95/0.324/7.6M320.7/0.517.8/12.7M33, M41, M420.65/0.516.5/12.7M34, M370.35/0.658.9/16.5M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | м18                                       | 0.6/0.3    | 15.2/7.6                               |

| M26, M270.5/0.312.7/7.6M28, M290.55/0.514/12.7M30, M310.95/0.324/7.6M320.7/0.517.8/12.7M33, M41, M420.65/0.516.5/12.7M34, M370.35/0.658.9/16.5M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M19, M20                                  | 2.45/0.3   | 62/7.6                                 |

| M28, M290.55/0.514/12.7M30, M310.95/0.324/7.6M320.7/0.517.8/12.7M33, M41, M420.65/0.516.5/12.7M34, M370.35/0.658.9/16.5M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | M24, M25                                  | 0.35/0.5   | 8.9/12.7                               |

| M30, M31       0.95/0.3       24/7.6         M32       0.7/0.5       17.8/12.7         M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | M26, M27                                  | 0.5/0.3    | 12.7/7.6                               |

| M320.7/0.517.8/12.7M33, M41, M420.65/0.516.5/12.7M34, M370.35/0.658.9/16.5M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M28, M29                                  | 0.55/0.5   | 14/12.7                                |

| M33, M41, M42       0.65/0.5       16.5/12.7         M34, M37       0.35/0.65       8.9/16.5         M35       0.75/1.0       19/25.4         M36       0.65/1.7       16.5/43         M38       0.8/0.4       20/10         M39, M40       0.65/0.3       16.5/7.6         M43, M44       5.1/0.3       130/7.6         M45       0.75/1.7       19/43         M53       0.45/0.3       11.4/7.6         M54, M55       0.35/0.85       8.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M30, M31                                  | 0.95/0.3   | 24/7.6                                 |

| M34, M370.35/0.658.9/16.5M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M32                                       | 0.7/0.5    | 17.8/12.7                              |

| M350.75/1.019/25.4M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | M33, M41, M42                             | 0.65/0.5   | 16.5/12.7                              |

| M360.65/1.716.5/43M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M34, M37                                  | 0.35/0.65  | 8.9/16.5                               |

| M380.8/0.420/10M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | M35                                       | 0.75/1.0   | 19/25.4                                |

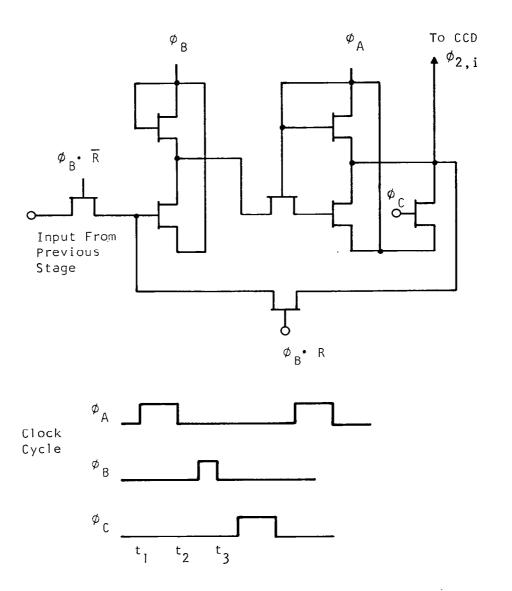

| M39, M400.65/0.316.5/7.6M43, M445.1/0.3130/7.6M450.75/1.719/43M530.45/0.311.4/7.6M54, M550.35/0.858.9/22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | M36                                       | 0.65/1.7   | 16.5/43                                |