NASA CR 3235

## NASA Contractor Report 3235

AFWL TECHNICABLIB KIRTLAND AFB, NO

InSb Charge Coupled Infrared Imaging Device - 20-Element Linear Imager

R. D. Thom, T. L. Koch, W. J. Parrish, J. D. Langan, and S. C. Chase

CONTRACT NAS1-14922 FEBRUARY 1980

## NASA Contractor Report 3235

## InSb Charge Coupled Infrared Imaging Device - 20-Element Linear Imager

R. D. Thom, T. L. Koch, W. J. Parrish, J. D. Langan, and S. C. Chase Santa Barbara Research Center Goleta, California

Prepared for Langley Research Center under Contract NAS1-14922

Scientific and Technical Information Office

1980

## CONTENTS

| Section |                                                                                   | Page         |

|---------|-----------------------------------------------------------------------------------|--------------|

| 1       | INTRODUCTION                                                                      | 1-1          |

| 2       | DEVICE DESIGN AND FABRICATION                                                     | 2-1          |

|         | InSb Material Characteristics                                                     | 2 - 1        |

|         | 8585 Chip Design and Description                                                  | 2-8          |

|         | Process Description                                                               | 2-12         |

|         | Mask and Process Modifications                                                    | 2-15         |

| 3       | TWO-ELEMENT InSb CCIRID                                                           | 3 - 1        |

|         | Device Description                                                                | 3 - 1        |

|         | Gate Oxide Witness Evaluation                                                     | 3 - 3        |

|         | CCD Gate Capacitance and Flatband Voltage                                         | 3 - 8        |

|         | Surface Potential and Charge Storage Capacity                                     | 3 - 10       |

|         | Channel Stop Metal Bias Requirements                                              | 3-13         |

|         | Two-Element InSb CCIRID Operation                                                 | 3 - 18       |

| 4       | 20-ELEMENT InSb CCIRID                                                            | 4-l          |

|         | Device Description                                                                | 4 - 1        |

|         | Gate Oxide Witness Evaluation                                                     | 4-4          |

|         | Gate Capacitance, Flatband Voltage, and Surface Potential Diagram for 8585 Lot 8B | 4-14         |

|         | Test Equipment Configuration                                                      | 4-19         |

|         | Test Results                                                                      | 4-29         |

| 5       | DISCUSSION OF TEST RESULTS                                                        | 5 <b>-</b> 1 |

|         | Charge Transfer Efficiency                                                        | 5-1          |

|         | LTCVD Reactor Differences                                                         | 5-10         |

|         | Device Operating Temperature                                                      | 5 - 11       |

|         | Improvements in Photogate Yield                                                   | 5-20         |

| 6       | APPLICATIONS FOR MONOLITHIC InSb CCD ARRAYS                                       | 6-1          |

|         | Earth Resources Applications                                                      | 6-1          |

## CONTENTS (Cont)

| Section |                                       | Page  |

|---------|---------------------------------------|-------|

|         | Meteorological Satellite Applications | 6-3   |

|         | Geological Applications               | 6-4   |

| 7       | SUMMARY                               | 7 - 1 |

| •       | REFERENCES                            | R-1   |

## ILLUSTRATIONS

| Figure |                                                                                                                                  | Page   |

|--------|----------------------------------------------------------------------------------------------------------------------------------|--------|

| 2-1    | InSb CCIRID Wafers                                                                                                               | 2-2    |

| 2-2    | Interband Tunneling in MOS Structure                                                                                             | 2-4    |

| 2-3    | Interband Tunnel Current versus Surface Potential for InSb                                                                       | 2-6    |

| 2-4    | Monolithic InSb CCIRID Chip (SBRC 8585)                                                                                          | 2-9    |

| 2-5    | Cross Section Perpendicular to Channel for CCIRIDs on SBRC 8585 Chip                                                             | 2-11   |

| 2-6    | I-V Characteristic of Implanted Planar InSb p-n Junction (T = 77 K, $N_D$ = 4.5 × $10^{14}/cm^3$ ; 2 volts/div; 10 $\mu a/div$ ) | 2-12   |

| 2-7    | Process Flow Chart for 8585 InSb CCIRID                                                                                          | 2-13   |

| 2-8    | SEM Photograph of Etched Diode Contact Window Showing Undercutting of Gate Oxide Layer                                           | 2-16   |

| 2-9    | p-n Junction Contacts on 8585 Chip (Dimensions for 20-Element Imager, in mils)                                                   | 2-17   |

| 2-10   | SEM Photograph of Diode Contact Using Nested Oxide<br>Etch Masks (2-Element CCIRID No. 498-20-B5,<br>Lot 8B, 40°, 3500X)         | 2-18   |

| 3 – 1  | Two-Element, 4¢ InSb CCIRID on 8585 Chip                                                                                         | 3 - 1  |

| 3 - 2  | Schematic Diagram of Two-Element and 20-Element InSb CCIRIDs                                                                     | 3-2    |

| 3 - 3  | SBRC Capacitance Measurement System                                                                                              | 3 - 5  |

| 3-4    | Low-Frequency and High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 4; Sample 486A-10A                                  | 3-5    |

| 3 - 5  | Surface State Density of Gate Oxide Witness; 8585 Lot 4; Sample 486A-10A                                                         | 3-7    |

| 3-6    | Surface Potentials for One Bit of 40 CCD                                                                                         | 3 - 11 |

| 3 – 7  | Surface Potential versus Gate Voltage for 8585 Lot 4                                                                             | 3 - 13 |

| 3 - 8  | Effect of Surface Conditions on Breakdown Voltage of InSb Planar p-n Junctions                                                   | 3-15   |

| 3-9    | Surface Effect, Intermediate Case                                                                                                | 3 - 16 |

| 3 - 10 | InSb CCD Floating Diffusion Output (Showing Negligible Output Diode Leakage                                                      | 3-17   |

| Figure |                                                                                                                                               | Page          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

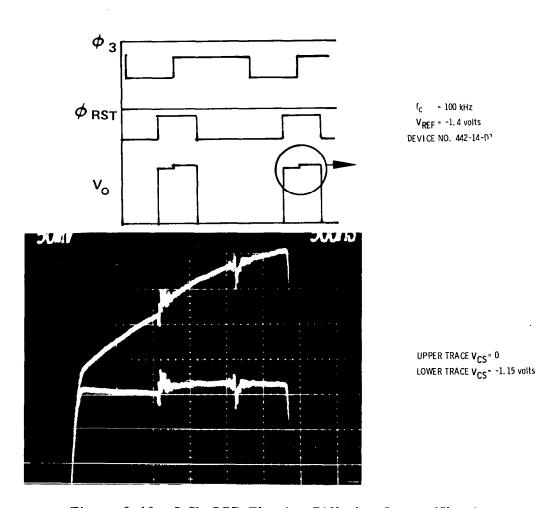

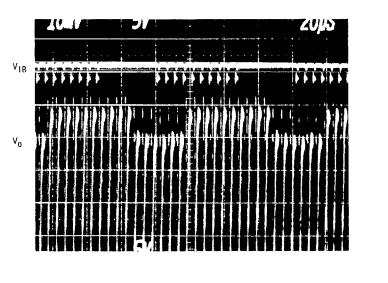

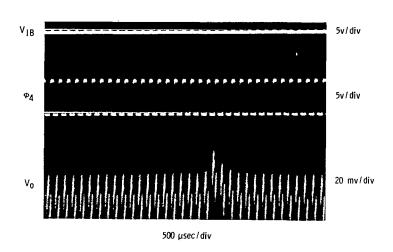

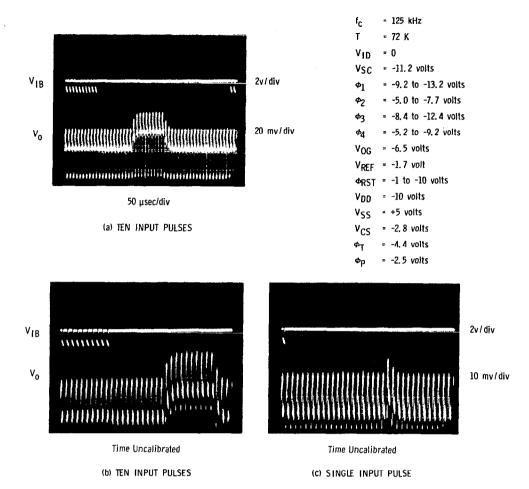

| 3-11   | Output of Two-Element ( $3\frac{1}{2}$ Bit) InSb CCIRID with Ten Input Pulses (Device No. 442-14-G2)                                          | 3-19          |

| 3-12   | Output of Two-Element $(3\frac{1}{2} \text{ Bit})$ InSb CCIRID with Single Input Pulse (Device No. 442-14-G2)                                 | 3-20          |

| 3-13   | Output of Two-Element $(3\frac{1}{2}$ Bit) InSb CCIRID<br>No. 442-14-Dl with Six Input Pulses                                                 | 3-23          |

| 3-14   | Output of Two-Element $(3\frac{1}{2} \text{ Bit})$ InSb CCIRID<br>No. 442-14-D1 with Ten Input Pulses                                         | 3-23          |

| 3 - 15 | Output of Two-Element $(3\frac{1}{2}$ Bit) InSb CCIRID No. 442-14-G2 without Fat Zero and with Parameters Adjusted for Maximum Output Voltage | 3-27          |

| 3-16   | Two-Element InSb CCIRID No. 442-14-Dl Operating in Optical Mode                                                                               | 3 <b>-</b> 29 |

| 4-1    | 20-Element InSb CCIRID                                                                                                                        | 4-2           |

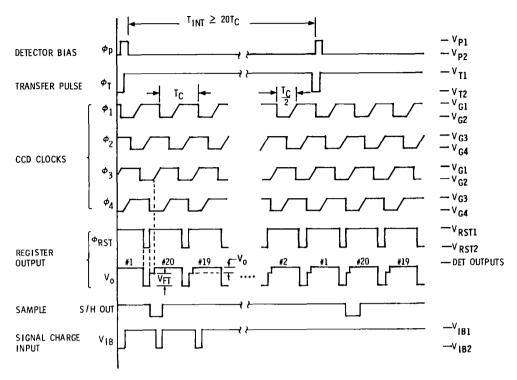

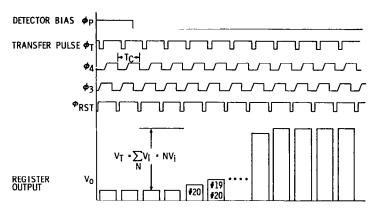

| 4-2    | 20-Element CCIRID Timing Diagram                                                                                                              | 4-3           |

| 4-3    | High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 1)                                                        | 4-6           |

| 4-4    | High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 2)                                                        | 4-7           |

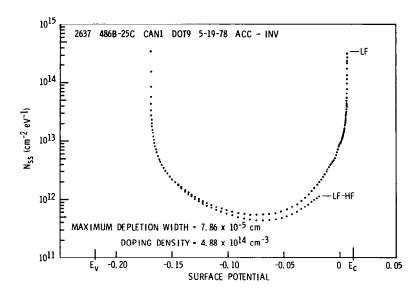

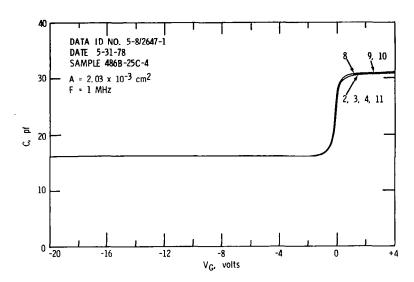

| 4-5    | Low-Frequency and High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 1, Dot 3)                               | 4-7           |

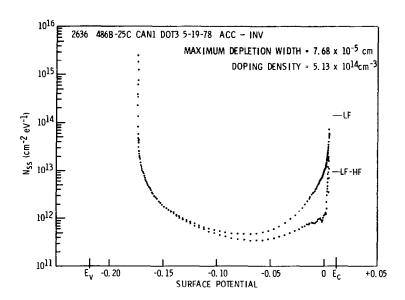

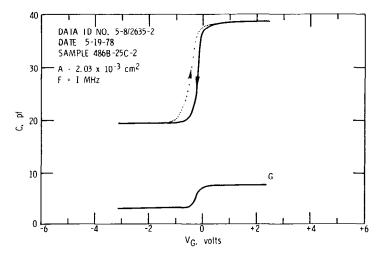

| 4-6    | Surface State Density by Quasistatic Technique of Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 1, Dot 3)                             | 4-8           |

| 4-7    | Surface State Density by Quasistatic Technique of Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 1, Dot 9)                             | 4-9           |

| 4-8    | High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 4)                                                        | 4-10          |

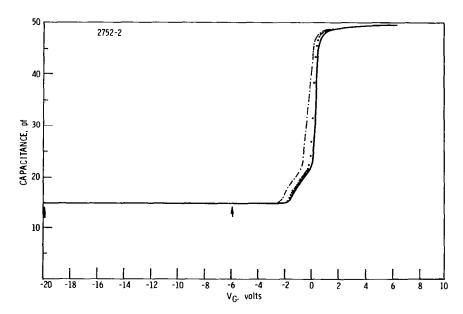

| 4-9    | Hysteresis of Gate Oxide Witness; 8585 Lot 8B; Sample 486B-25C (Can 2, Dot 11)                                                                | 4-10          |

| Figure |                                                                                                                  | Page |

|--------|------------------------------------------------------------------------------------------------------------------|------|

| 4-10   | Low-Frequency and High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 11B; Sample 532-2A (Can 2, Dot 3)   | 4-12 |

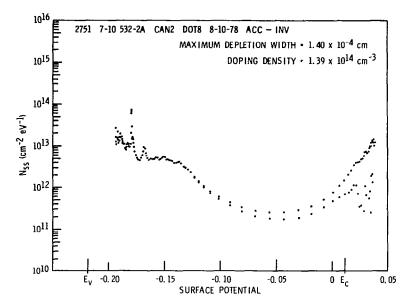

| 4-11   | Surface State Density by Quasistatic Technique of Gate Oxide Witness; 8585 Lot 11B; Sample 532-2A (Can 2, Dot 3) | 4-12 |

| 4-12   | Surface State Density by Quasistatic Technique of Gate Oxide Witness; 8585 Lot 11B; Sample 532-2A (Can 2, Dot 8) | 4-13 |

| 4-13   | Hysteresis of Gate Oxide Witness; 8585 Lot 11B; Sample 532-2A (Can 2, Dot 3)                                     | 4-13 |

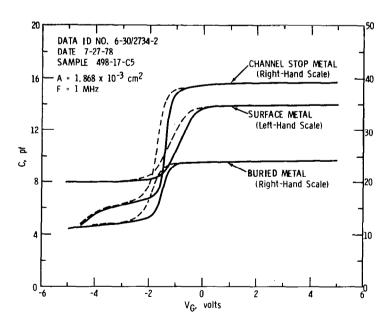

| 4-14   | C-V Characteristics of Channel Stop, Buried, and Surface<br>Metal Capacitors; Wafer 498-17; 8585 Lot 8B; Chip C5 | 4-16 |

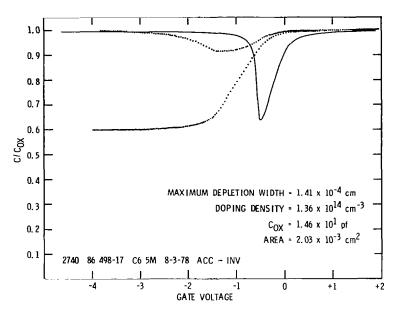

| 4-15   | Low-Frequency and High-Frequency C-V Curves for Surface Metal Capacitor; Wafer 498-17; 8585 Lot 8B; Chip C6      | 4-17 |

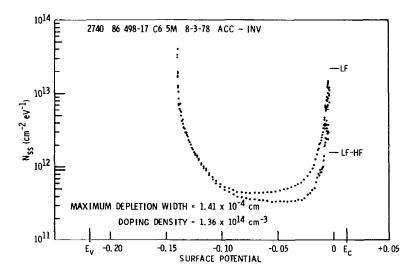

| 4-16   | Surface State Density by Quasistatic Technique of Surface Metal Capacitor; Wafer 498-17; 8585 Lot 8B; Chip C6    | 4-17 |

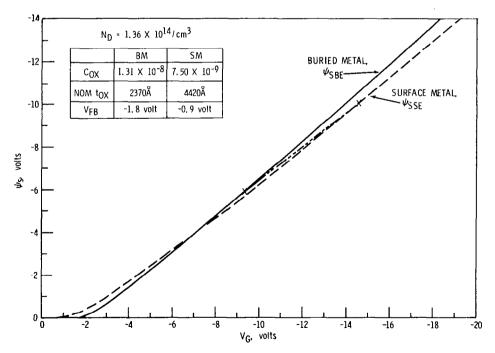

| 4-17   | Surface Potential versus Gate Voltage for Wafer 498-17, 8585 Lot 8B                                              | 4-18 |

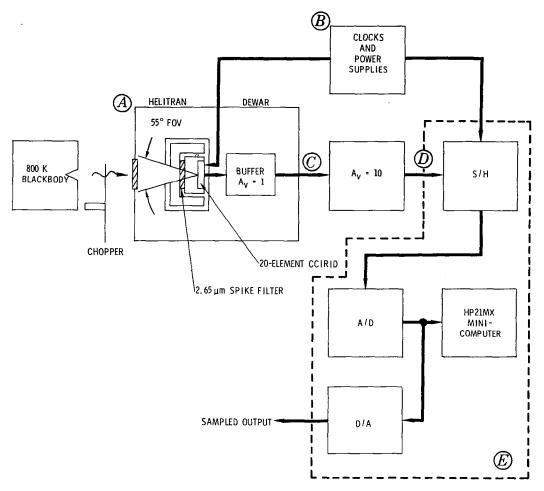

| 4-18   | General Test Configuration for 20-Element InSb CCIRID                                                            | 4-20 |

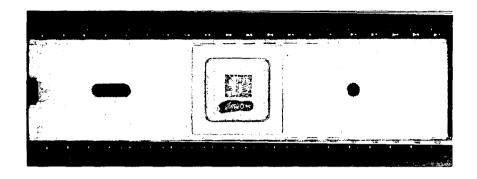

| 4-19   | 20-Element InSb CCIRID in 40-Lead Dual-Inline Package, with Sapphire Window Sealed Over Well                     | 4-22 |

| 4-20   | 20-Element InSb CCIRID Mounted in Dual-Inline Package, Prior to Sealing of Sapphire Window                       | 4-22 |

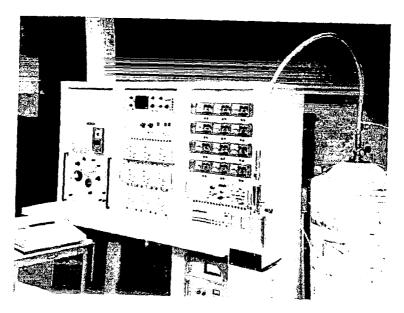

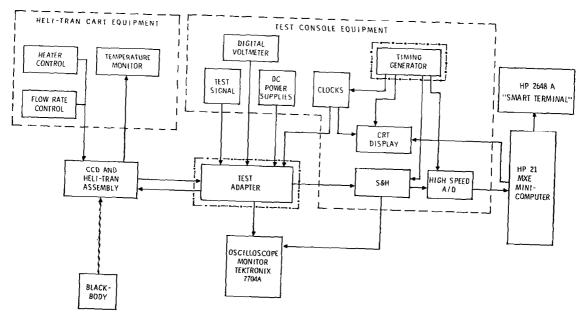

| 4-21   | CCD Array Test Set No. 2                                                                                         | 4-23 |

| 4-22   | Block Diagram of CCD Array Test Set No. 2 and Heli-Tran Cart Equipment                                           | 4-23 |

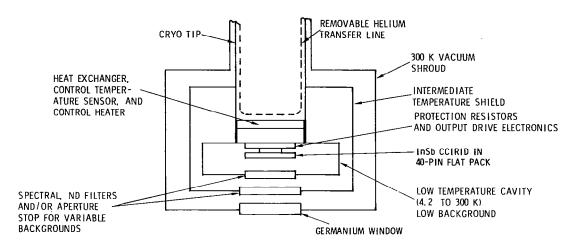

| 4-23   | Sketch of Low-Temperature Cavity, Shields, and . Windows in Heli-Tran System                                     | 4-25 |

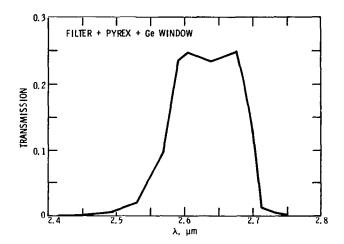

| 4-24   | Transmission Curve for 2.65-µm Narrow Bandpass Filter, Pyrex Plate, and Germanium Outer Window                   | 4-27 |

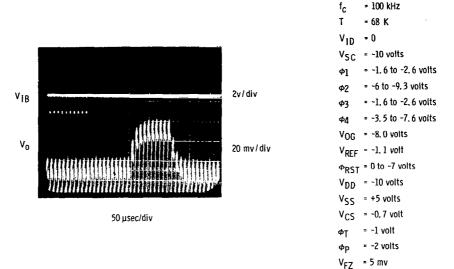

| 4-25   | Output of 20-Element InSb CCIRID No. 498-17-A3 with Ten Pulses Applied to FZ Input; CTE = $0.992 \pm 0.002$      | 4-30 |

| Figure |                                                                                                                          | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------|------|

| 4-26   | Output of 20-Element InSb CCIRID No. 498-17-A3 (Retest, Four Months after Packaging); CTE = 0.9955 ± 0.0005              | 4-31 |

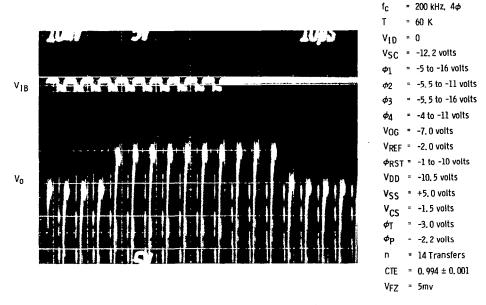

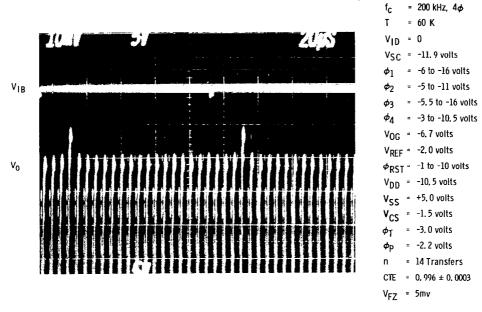

| 4-27   | Output of 20-Element InSb CCIRID No. 522-20-B4 with Signal Pulses Applied to FZ Input; CTE = 0.994 ± 0.001               | 4-32 |

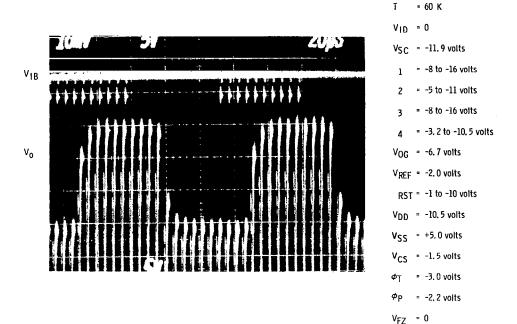

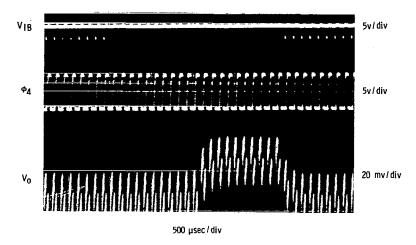

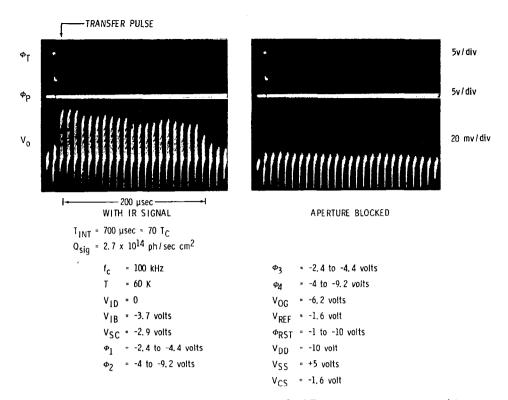

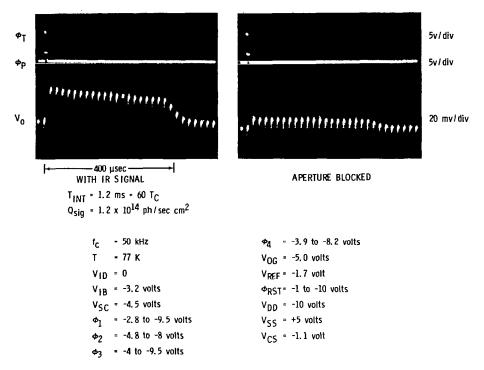

| 4-28   | 20-Element CCIRID No. 498-17-A3 Operating at 60 K in Multiplexing Mode with Chopped IR Signal Input                      | 4-40 |

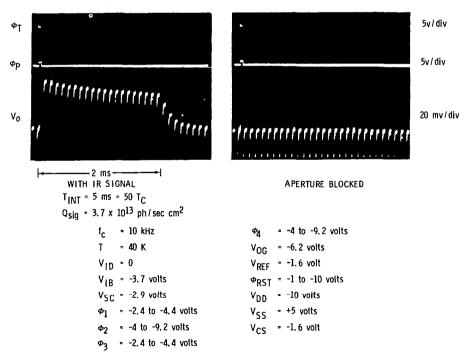

| 4-29   | 20-Element CCIRID No. 498-17-A3 Operating at 40 K in Multiplexing Mode, $T_{\rm INT} > N_{\rm B}T_{\rm C}$               | 4-40 |

| 4-30   | 20-Element CCIRID No. 498-17-A3 Operating a 77 K in Multiplexing Mode, $T_{\rm INT} > N_{\rm B}T_{\rm C}$                | 4-41 |

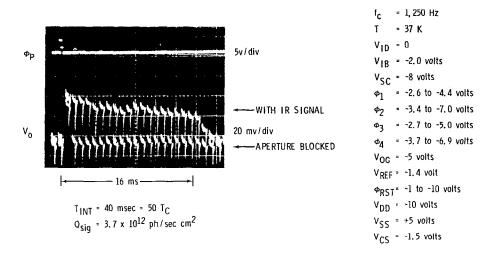

| 4-31   | 20-Element CCIRID No. 498-17-B2 Operating at 37 K in Multiplexing Mode, T <sub>INT</sub> > N <sub>B</sub> T <sub>C</sub> | 4-42 |

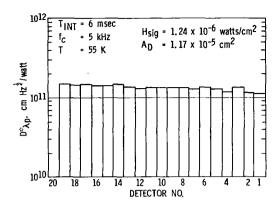

| 4-32   | Measured D* of 20-Element CCIRID 498-17-B2 in Multiplexing Mode                                                          | 4-44 |

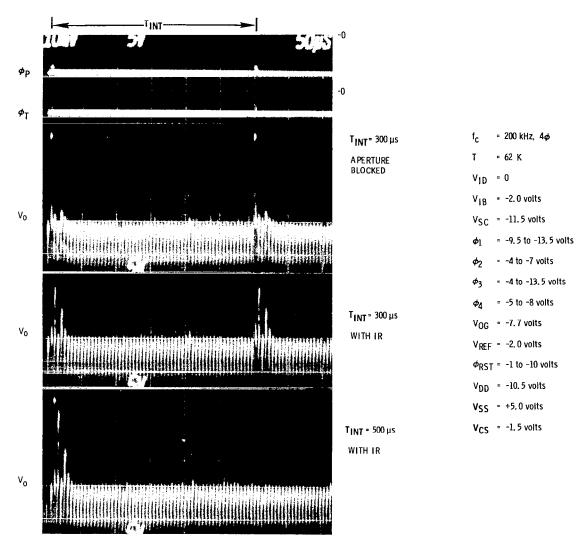

| 4-33   | InSb CCIRID Timing Diagram for Demonstration of Time-Delay-and-Integration Mode ( $T_{INT} = T_C$ )                      | 4-45 |

| 4-34   | TDI Operation of 20-Element CCIRID 498-17-B2                                                                             | 4-46 |

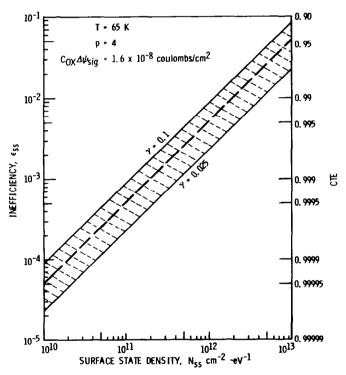

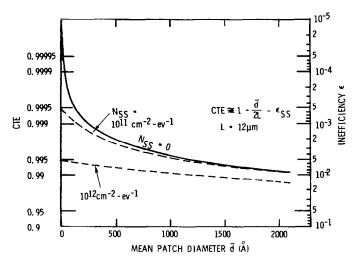

| 5 - 1  | Calculated Inefficiency Range versus $N_{\text{ss}}$ for Parallel-Edge Surface State Loss                                | 5-2  |

| 5-2    | Measured C-V Characteristics of InSb MOS Sample with Gate Oxide Deposited in Horizontal-Flow CVD Reactor                 | 5-5  |

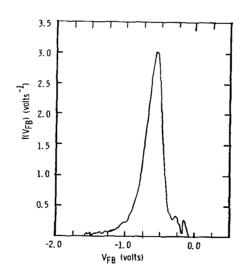

| 5-3    | Measured Flatband Voltage Distribution for Sample in Figure 5-2                                                          | 5-5  |

| 5-4    | SEM Photo of LTCVD SiO <sub>2</sub> Granularity Resulting from a Horizontal CVD Reactor, Showing Mean Size of 1500Å      | 5-6  |

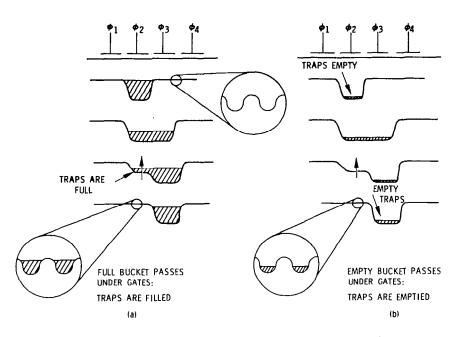

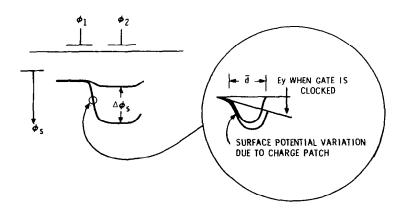

| 5-5    | Charge Transfer Inefficiency Mechanism due to Trapping by Localized Surface Potential Variations                         | 5-7  |

| 5-6    | Release of Trapped Charge from Trap in Region of Large Lateral Field                                                     | 5-7  |

| 5-7    | Calculated CTE versus Mean Patch Diameter                                                                                | 5-9  |

| 5-8    | Dark Current in a 4¢ CCD                                                                                                 | 5-12 |

| Figure | ı                                                                                                          | Page |

|--------|------------------------------------------------------------------------------------------------------------|------|

| 5-9    | Clock Frequency and Integration Time versus Storage Time                                                   | 5-15 |

| 5-10   | Etch Pits on <111>B Face of CZ InSb Wafer after Etching to Reveal Defects (2X)                             | 5-17 |

| 5 - 11 | Etch Pits on CZ InSb Wafer at Higher Magnification (40X)                                                   | 5-17 |

| 5-12   | <pre>&lt;111&gt;B Face of LPE InSb Layer after Defect Etching (Phase Contrast Photomicrograph) (40X)</pre> | 5-18 |

| 5-13   | MOS Storage Time at 77 K for LPE InSb Layer                                                                | 5-19 |

| 5-14   | 8585 InSb CCIRID Transparent Gate Structure                                                                | 5-21 |

|        |                                                                                                            |      |

## TABLES

| Table |                                                                  | Page |

|-------|------------------------------------------------------------------|------|

| 2 - 1 | InSb Wafer Specification Summary                                 | 2-2  |

| 2-2   | 8585 Chip Design Rules                                           | 2-10 |

| 2-3   | 8585 CCIRID Fabrication Steps                                    | 2-14 |

| 3 - 1 | Oxide Parameters, 8585 Lot 4                                     | 3-9  |

| 4-1   | Nominal Design and Process Parameters for 20-Element InSb CCIRID | 4-1  |

| 4-2   | Oxide Parameters, 8585 Lot 8B                                    | 4-15 |

| 4-3   | Calculated Charge Transfer Efficiency                            | 4-33 |

#### SYMBOLS

parallel edge inefficiency parameter γ = inefficiency per transfer of CCD € = free space permittivity,  $8.854 \times 10^{-14}$  f/cm substrate permittivity, f/cm = inefficiency due to surface states € 55 λ = wavelength, μm = transmission of spectral filter at wavelength  $\lambda$  $\tau_{(\lambda)}$ = generation lifetime in depletion region, seconds  $oldsymbol{ au}_{arphi}$ = metal-semiconductor work function difference, volts Ø<sub>MS</sub>  $\psi_s$ = surface potential, volts = field-of-view (FOV), degrees  $\Omega$ = blackbody source aperture area, cm<sup>2</sup> Aaper = CCD bit area. cm<sup>2</sup>  $A_B$ = detector area, cm<sup>2</sup>  $A_{D}$ = area contributing to dark current. cm<sup>2</sup>  $A_{DK}$ = channel edge area, cm<sup>2</sup>  $A_{E}$ = area swept by fat zero charge, cm<sup>2</sup>  $A_{EZ}$ = gate area, cm<sup>2</sup>  $A_{G}$ = junction area, cm<sup>2</sup>  $A_{T}$ = total area swept by charge packet, cm<sup>2</sup>  $A_{\varsigma}$ = trap area, cm<sup>2</sup> A,  $A_{x}$ = voltage gain вv = junction breakdown voltage, volts  $C_{CSM}$ = output diode to channel stop metal capacitance, farads  $C_{FB}$ = flatband capacitance per unit area. f/cm<sup>2</sup>  $C_{gs}$ = gate-to-source capacitance, farads CIDI. = ideal capacitance of MOS capacitor, farads  $C_{0}$ = CCD output capacitance, farads COD = output diode capacitance, farads

$C_{OX}$  = oxide capacitance per unit area, f/cm<sup>2</sup>

C<sub>PAD</sub> = pad capacitance, farads

CSF = source-follower input capacitance, farads

C<sub>stray</sub> = stray capacitance, farads

CTE = charge transfer efficiency (efficiency per transfer)

$\overline{d}$  = mean diameter of trap, cm

D = distance from blackbody aperture to device, cm

D\* = detectivity, cm  $Hz^{\frac{1}{2}}$ /watt

E<sub>B</sub> = field in bulk depletion region, volts/cm

$E_g$  = bandgap, eV (joule)\*

E<sub>s</sub> = surface electric field, volts/cm

E<sub>v</sub> = lateral electric field magnitude, volts/cm

f<sub>c</sub> = CCD clock frequency, Hz

F<sub>sc</sub> = electric field in tunneling calculation, (volts/m)

$\hbar$  = reduced Planck's Constant, 1.0554  $\times$  10<sup>-34</sup> joule second

$H_{sig}$  = signal irradiance at plane of array, watts/cm<sup>2</sup>

I<sub>R</sub> = junction reverse current, amp

I<sub>sc</sub> = photodiode short-circuit current, amp

$J_D$  = dark current density, amps/cm<sup>2</sup>

$J_g$  = thermal generation current, amps/cm<sup>2</sup>

$J_T$  = current density due to interband tunneling, amps/cm<sup>2</sup>

(amps/m<sup>2</sup>)

k = Boltzmann's Constant,  $1.38 \times 10^{-23}$  joule/K

K<sub>OX</sub> = oxide dielectric constant

L = CCD gate length, cm

$m*_{i}$  = effective mass, i = x, y, z, (kg)

n = number of transfers

N = number of detectors in TDI

$N_B$  = number of CCD bits

<sup>\*</sup>The interband tunneling calculations in Section 2 are facilitated through use of mks units, which are listed in parentheses in the list of symbols.

$N_D$  = substrate net impurity concentration, cm<sup>-3</sup>

$N_{fc}$  = number of oxide charges per unit area =  $Q_{fc}/q$ , cm<sup>-2</sup>

$N_G$  = number of gates in CCD

n<sub>i</sub> = intrinsic carrier concentration, cm<sup>-3</sup>

n<sub>e</sub> = surface electron concentration, cm<sup>-3</sup>

$N_{ss}$  = surface state density, #/cm<sup>2</sup>-eV

p = number of CCD phases

P = interband matrix element, (joule-meter)

q = electron charge,  $1.6 \times 10^{-19}$  coulombs

$Q_{\lambda}(T)$  = spectral radiant photon emittance of blackbody at temperature

T, phot sec<sup>-1</sup> cm<sup>-2</sup>  $\mu$ m<sup>-1</sup>

Q<sub>B</sub> = background photon flux at plane of array, phot/sec-cm<sup>2</sup>

$Q_{bb}(T)$  = radiant photon emittance of blackbody at temperature T,

phot/sec-cm<sup>2</sup>

Q<sub>D</sub> = dark charge, coulombs

$Q_{fc}$  = oxide fixed charge density, coulombs/cm<sup>2</sup>

QFILT(T) = radiant photon emittance of blackbody at temperature T trans-

mitted by a specified filter, phot/sec-cm<sup>2</sup>

$Q_{FZ}$  = fat zero charge, coulombs

$Q_{\rm p}$  = stored charge density, coulombs/cm<sup>2</sup>

Q<sub>s</sub> = signal charge, coulombs

$Q_{sig}$  = signal irradiance at plane of array, phot/sec-cm<sup>2</sup>

Q<sub>trap</sub> = trapped charge, coulombs

$R_{\lambda}$  = responsivity at wavelength  $\lambda$ , volts/watt

T = temperature, degrees Kelvin

$T_C$  = CCD clock period, seconds

T<sub>INT</sub> = detector integration time, seconds

$t_{OX}$  = oxide thickness, cm

$T_S$  = storage time, seconds

VBI = junction built-in voltage, volts

V<sub>FB</sub> = flatband voltage, volts

V<sub>FT</sub> = feedthrough voltage at output, volts

V<sub>FZ</sub> = output voltage due to fat zero charge, volts

$v_{\mathbf{G}}$  $v_n$ = noise voltage, volts = V<sub>s</sub> + V<sub>FZ</sub>, total output voltage, volts  $v_{o}$  $v_R$ = junction reverse bias, volts  $V_s$ = output voltage due to signal charge, volts = CCD gate width, cm w W = depletion region width, cm = spectral radiant emittance of blackbody at temperature T, watts cm  $^{-2}\ \mu\text{m}^{-1}$  $W_{\lambda}(T)$  $W_{bb}(T)$ = radiant emittance of blackbody at temperature T, watts/cm<sup>2</sup> W<sub>FILT</sub>(T) = radiant emittance of blackbody at temperature T transmitted

by a specified filter, watts/cm<sup>2</sup>

= gate voltage, volts

#### Section 1

#### INTRODUCTION

For new generations of infrared sensors in the 1980s, the development of integrated focal plane arrays (FPAs) will allow considerable improvements in sensor performance while reducing the weight, volume, and power requirements of the FPA and associated subsystems. An optimal type of integrated FPA is a charge-coupled infrared imaging device, or CCIRID, which combines, monolithically, detector elements and charge transfer devices for multiplexing or other signal processing functions in a common, infrared semiconductor material. Such CCIRIDs may be configured in either linear or area (two-dimensional) arrays.

Monolithic integration of detectors and CCDs in an intrinsic IR semiconductor material is an attractive approach for next-generation line and area IR arrays. The monolithic intrinsic structure offers higher operating temperature and quantum efficiency compared to its monolithic extrinsic (Si:X) counterpart having the same cutoff wavelength, but gains these advantages without the need for the hundreds or thousands of individual interconnections required in the hybrid IR array concept, a sandwich of an intrinsic detector array and silicon CCD chip. Because the intrinsic or fundamental absorption is utilized, potentially high quantum efficiencies may be realized with suitable device design, and optical crosstalk effects, particularly important in dense arrays, will be small.

The long range objective of this work is to develop this new concept in monolithic infrared imaging. The semiconductor material used in this development is indium antimonide (InSb), an excellent choice for a CCIRID with photon detection capability in the 1- to 5.5-µm spectral region. The immediate goal is to fabricate prototype InSb CCIRIDs that will be used to establish applications and operational characteristics of the infrared imaging sensors. The monolithic infrared CCIRID imagers being developed on this program are

#### Section 2

#### DEVICE DESIGN AND FABRICATION

#### InSb MATERIAL CHARACTERISTICS

#### InSb Wafers

Starting material for CCIRID processing was n-type InSb grown by M. C. P. Electronics Limited (England) and distributed by Metal Specialties, Inc., Fairfield, Connecticut. The InSb ingots, grown by the Czochralski technique, were cut into wafers oriented to within  $\frac{1}{2}^{\circ}$  of the (111) plane, and subsequently final-polished to a thickness of 635  $\mu m$ . The (111) B face was used throughout this program for device processing. The wafers used for CCIRID processing were undoped (n-type) with a net carrier concentration at 77 K ranging from  $6 \times 10^{13}$  to  $2 \times 10^{14}/\text{cm}^3$ , as determined by Hall measurements. The wafers utilized during the program had dislocation densities (as measured by etch pit density on the A face) ranging from 0 to  $1000/\text{cm}^2$ . Later in the program the E. P. D. specification was tightened to  $\leq 100/\text{cm}^2$ .

The wafers were shaped (by M. C. P.) to a uniform diameter of 3.2 cm, followed by cutting of a nonoriented flat. The uniform diameter and flat allow the slices to be handled conveniently in conventional processing equipment and are necessary for pattern orientation in the projection mask aligner that is used. An ultrasonic cutting tool was first used to shape the InSb wafers, but edge chipping led to the present technique of shaping by means of a diamond hole cutter. Figure 2-1 shows, on the left, an InSb wafer that has been shaped and final-polished on the B-face, ready for CCIRID processing; and on the right, a completely processed wafer. Approximately 50 8585 chips/wafer are obtained on the 3.2-cm diameter slices.

A summary of the InSb material specifications is given in Table 2-1.

Figure 2-1. - InSb CCIRID Wafers.

Table 2-1. InSb Wafer Specification Summary

| TYPE                            | CZOCHRALSKI SINGLE CRYSTAL, n-TYPE                                |

|---------------------------------|-------------------------------------------------------------------|

| DOPANT                          | UNDOPED                                                           |

| DIAMETER                        | 32 ± 0.25 mm                                                      |

| FLAT LENGTH                     | 21.17 ± 0.25 mm                                                   |

| THICKNESS                       | 635 ± 25 μm                                                       |

| PARALLELISM                     | FACES PARALLEL TO WITHIN 25 μm                                    |

| FLATNESS                        | FLAT TO WITHIN 5 μm WITHIN 28 mm<br>CENTRAL DIAMETER              |

| LINE DISLOCATIONS               | <6 mm IN LENGTH                                                   |

| ETCH PIT DENSITY                | ≤100/cm <sup>2</sup>                                              |

| ORIENTATION                     | WITHIN 1/20 OF (111)                                              |

| SURFACE POLISH                  | <0.1 μm FINISH, B FACE<br><5 μm FINISH, A FACE                    |

| EDGE CHIPS                      | ≤2 PER WAFER FACE                                                 |

| CARRIER CONCENTRATION ND (77 K) | 5.0 x 10 <sup>13</sup> TO 2.0 x 10 <sup>14</sup> /cm <sup>3</sup> |

| ELECTRON MOBILITY He (77 K)     | ≥525, 000 cm <sup>2</sup> /volt-sec                               |

#### Interband Tunneling Considerations

Several factors influence the choice of  $N_D$ . The most important is tunnel current which motivates use of low carrier concentration material. It is generally realized that, for materials with bandgap below about 0.2 eV, interband tunneling presents a potentially important factor in device design and performance. InSb with its 0.228 eV energy gap represents a borderline case where tunneling is usually considered to be unimportant in, for example, InSb PV detectors where the impurity concentration of the substrate is sufficiently low to prevent tunnel diode characteristics and where the detector is operated with zero applied bias. However, the relatively high fields resulting at the surface when deep depletion conditions are established in an InSb CCD or CID can produce significant tunnel currents, particularly when the impurity concentration is high. For a given surface potential, the maximum surface electric field increases as  $\sqrt{N_D}$  and, since the tunnel current density varies exponential with this electric field, a strong dependence of tunnel current on  $N_D$  results.

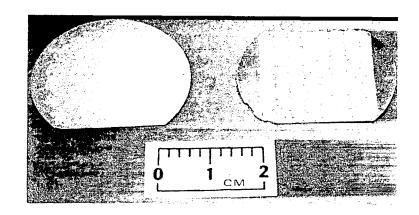

This tunneling current has been considered in detail by Anderson<sup>3</sup>. Referring to Figure 2-2, which shows an MOS structure with n-type substrate biased into a deep depletion condition, tunneling from the valence to the conduction band is possible for electrons with energy between  $E_{vo}$  and  $E_{cw}$ . After introduction of several approximations which, however, do not introduce errors of more than a few percent for tunnel current densities  $\leq 0.1$  amp/cm<sup>2</sup>, the tunnel current may be written in the form

$$\frac{J_{T}}{q} \approx \frac{\left(q\psi_{s} - \frac{E_{g}}{2}\right) qF_{sc}}{\pi^{3}\sqrt{2} h^{2}} \left(\frac{m*_{y}m*_{z}}{E_{g}^{2}}\right)^{\frac{1}{2}} \left(\frac{E_{g}}{m*_{x}}\right)^{\frac{1}{2}} \times \frac{\left(\frac{b}{a}\right)^{\frac{1}{2}} exp\left(-\frac{\sqrt{a/b} \pi}{2\sqrt{2}qF_{sc}h} \sqrt{\frac{m*_{x}}{E_{g}}} E_{g}^{2}\right)}{\left\{4 + \frac{\sqrt{a/b} \pi}{2\sqrt{2}qF_{sc}h} \cdot \sqrt{\frac{m*_{x}}{E_{g}}} E_{g}^{2}\right\}}$$

(2-1)

Figure 2-2, - Interband Tunneling in MOS Structure.

where

$$\frac{a}{b} \equiv \frac{q\psi_s}{q\psi_s - E_g/2} , \qquad (2-2)$$

$\rm E_g$  is the bandgap,  $\rm F_{SC}$  is the electric field and h the reduced Planck's Constant. The effective mass is isotropic in InSb with

$$\sqrt{\frac{m_i^*}{E_g}} = \frac{\sqrt{3} h}{2P}$$

(2-3)

where i = x, y, z and P is an interband matrix element which, for InSb, is equal to

$$P = 1.440 \times 10^{-28}$$

joule-meter. (2-4)

Evaluating the constant terms in equation (2-1):

$$C_{1} = \frac{q}{\pi^{3}\sqrt{2} \, h^{2}} \left( \frac{m^{*}y^{m^{*}z}}{E_{g}^{2}} \right)^{\frac{1}{2}} \left( \frac{E_{g}}{m^{*}x} \right)^{\frac{1}{2}}$$

$$= \frac{q}{\pi^{3}\sqrt{2} \, h^{2}} \frac{\sqrt{3} \, h}{2P}$$

(2-5)

=  $2.084 \times 10^{41}$  coul/joule<sup>2</sup>-sec-m

and

$$C_2 = \frac{\pi}{2\sqrt{2} q \hbar} \sqrt{\frac{m^*_x}{E_g}} \cdot E_g^2$$

(2-6)

=  $5.563 \times 10^7 \text{ volts/meter}$

for  $E_g$  = 0.228 eV = 3.6526  $\times$  10<sup>-20</sup> joule, allows rewriting (2-1) as

$$\frac{J_{T}}{q} \cong C_{1} \left( q \psi_{s} - \frac{E_{g}}{2} \right) F_{sc} \cdot \frac{\left( \frac{b}{a} \right)^{\frac{1}{2}} \exp\left( - C_{2} \sqrt{a/b} / F_{sc} \right)}{\left\{ 4 + \left( C_{2} \sqrt{a/b} / F_{sc} \right) \right\}}$$

(2-7)

To express  $J_T$  with  $\psi_s$  as the independent variable, use is made of the relation:

$$F_{sc} = C_3 \left( q \psi_s \right)^{\frac{1}{2}} \tag{2-8}$$

where

$$C_3 = \left(2N_D/\epsilon_s\right)^{\frac{1}{2}}.$$

(2-9)

Substituting (2-2) and (2-8) into equation (2-7) leads to the final result:

$$\frac{J_{T}(\psi_{s})}{q} \cong \frac{C_{1}C_{3}\left(q\psi_{s} - \frac{E_{g}}{2}\right)^{3/2}}{\left\{4 + \frac{C_{2}}{C_{3}}\left(q\psi_{s} - \frac{E_{g}}{2}\right)^{-\frac{1}{2}}\right\}} \exp\left\{-\frac{C_{2}}{C_{3}}\left(q\psi_{s} - \frac{E_{g}}{2}\right)^{-\frac{1}{2}}\right\}$$

(2-10)

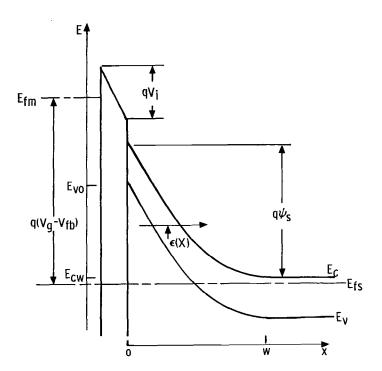

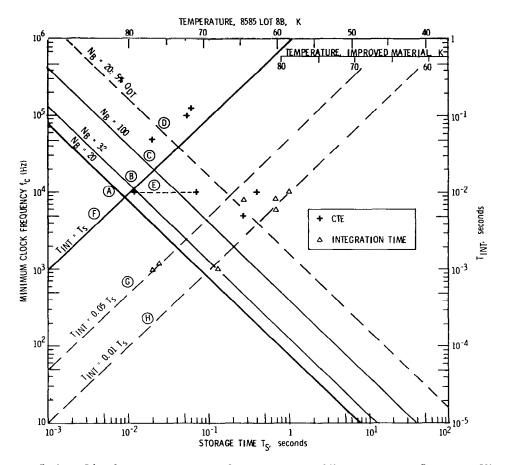

InSb tunnel current density versus surface potential for four values of impurity concentration  $N_D$ , calculated using equation (2-10), is plotted in Figure 2-3. The tunnel current is expressed as a carrier flux density (log scale) on the left-hand ordinate, and a current density on the right-hand ordinate. The extreme variation with  $N_D$  is apparent. At  $|\psi_s|=2$  volts, for example, the tunnel current varies 21 orders of magnitude between  $2\times 10^{14}$  and  $2.5\times 10^{15}/\mathrm{cm}^3$  carrier concentrations. For the latter value of  $N_D$ ,  $J_T$  increases rapidly as  $\psi_s$  only slightly exceeds the bandgap  $E_g$ . This is analogous to the rapid increase in reverse current of a backward diode. For  $N_D=2\times 10^{14}/\mathrm{cm}^3$ , however, surface potentials of several volts are possible before appreciable tunneling occurs.

It is now necessary to relate the results of Figure 2-3 to limits on CCD operation. Although several relationships between dark current, clock frequency, and CCD performance can be developed, the most straightforward approach is to compare the tunnel current,  $J_T$ , with the thermally-generated current  $J_g$  in the device. The particular criterion applied is to determine the surface potential at which  $J_T = J_g$ .

Figure 2-3. - Interband Tunnel Current versus Surface Potential for InSb.

With appropriate processing to minimize surface generation, it has been shown that thermal generation in InSb MOS devices at 77 K is determined by bulk current sources and, in particular, by generation within the volume of the depletion region. This current is given by

$$\frac{J_g}{q} = \frac{n_i W}{\tau_g} = \frac{n_i}{\tau_g} \left( \frac{2\epsilon_s |\psi_s|}{qN_D} \right)^{\frac{1}{2}}$$

(2-11)

where  $\pmb{\tau}_g$  is the generation lifetime in the depletion region.  $\pmb{\tau}_g$  has been obtained from Zerbst-plot analysis of InSb MOS capacitance-time plots, and is typically 0.2 µsec. Using this value in equation (2-11), the thermal generation currents have been plotted in Figure 2-3 for the two extreme values of  $N_D$  considered. Since  $J_g \propto \sqrt{\psi}_s$ , the thermal currents are nearly horizontal lines on the log plot of Figure 2-3.

The surface potentials at which  $J_T = J_g$  are:  $|\psi_s| = 1$  volt for  $N_D = 1$ 2.5  $\times$  10<sup>15</sup>/cm<sup>3</sup>;  $|\psi_s|$  = 11.4 volts for N<sub>D</sub> = 2  $\times$  10<sup>14</sup>/cm<sup>3</sup>; and intermediate values for  ${\rm N}_{\rm D}$  between these two cases. These potentials represent the upper limit to surface potential in a CCD fabricated on InSb of that impurity concentration. Consider, for example, an InSb CCD fabricated on  $N_{\overline{D}}$  = 2.5  $\times$  $10^{15}/\mathrm{cm}^3$  material. Assume that a clock voltage is applied to a CCD gate with a magnitude so as to instantaneously establish an empty-well surface potential exceeding the potential at which  $J_T = J_g$ . For example, take  $|\psi_s|$  = 2 volts, point A in Figure 2-3. At this potential, tunnel current exceeds the thermal generation rate by four orders of magnitude, and the minority carriers generated will rapidly accumulate at the interface until the surface potential is reduced to 1 volt (point B), at which point the normal thermal process is resumed. Therefore, for this particular impurity concentration, attempts to clock the CCD so as to produce  $|\psi_s| > 1$  volt under any gate will produce large tunnel currents which will quickly return the potential to 1 volt. For the low concentration  $N_D = 2 \times 10^{14}/\text{cm}^3$ , a wide range in CCD surface potentials (about 11 volts) is possible before the tunneling process begins.

Since charge storage capacity is directly related to maximum surface potential, as  $\rm N_D$  is increased progressively smaller charge capacity results until charge transfer ceases completely (the specific limiting impurity concentration depending on whether the CCD is  $2\phi$  or  $4\phi$ ). Based on these calculations, which have been verified by experimental determination of the onset of tunneling in InSb MOS capacitors, material with  $\rm N_D$  no higher than 2  $\times$   $10^{14}/\rm cm^3$  was used for device fabrication. Resulting CCD charge capacities are in excess of  $10^6$  holes. Since tunneling is a basic quantum mechanical limitation, it is not unique to InSb, and comparable tunnel currents occur in other direct gap materials having the same bandgap.

#### 8585 CHIP DESIGN AND DESCRIPTION

In earlier work<sup>1,2</sup> shift registers were fabricated in InSb to demonstrate the feasibility of CCDs in this material. These made use of the then-available processing technology, one based on gold metallizations and SiO dielectric layers. Due to the relative difficulty in etch delineation of these materials, device dimensions were limited. CCDs with 50-µm and 25-µm gate lengths were fabricated for which CTEs of 0.9 and 0.975 per transfer, respectively, were measured. A further limitation was encountered with the on-chip p-n junctions, which were formed by a mesa technique; the non-planarity of the diodes prevented their reduction to the required size and reduced yields in the dielectric deposition steps.

In this program, a new InSb CCIRID chip was successfully fabricated based on an improved process which eliminates the limitations inherent with the earlier techniques. This process includes planar junction formation and an aluminum and SiO<sub>2</sub> material system which is amenable to state-of-the-art delineation techniques.

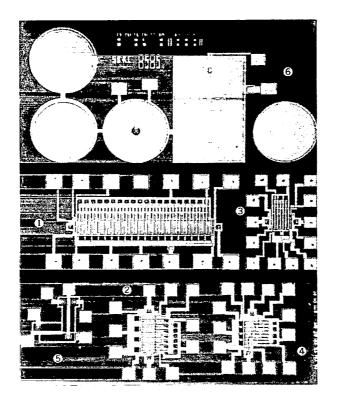

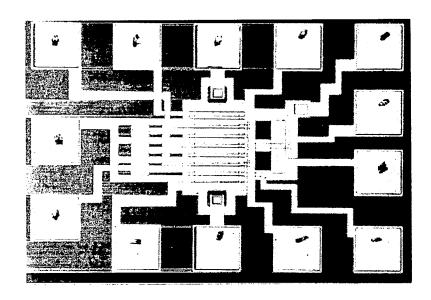

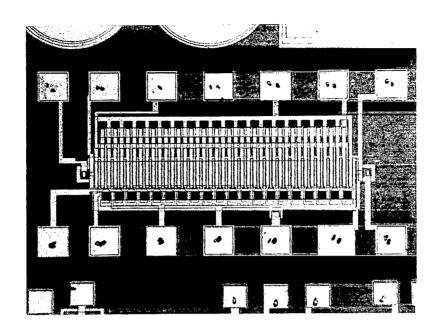

The monolithic InSb chip is designated the SBRC 8585; a photomicrograph of a die from a completed wafer is shown in Figure 2-4. The principal device on the chip is a 20-element CCIRID (center). Smaller complementary

Figure 2-4. - Monolithic InSb CCIRID Chip (SBRC 8585).

devices are two- and four-element CCIRIDs, which differ in design details, and a four-element TDI array with tapered register. The balance of the chip contains MOS capacitors and gate-controlled diodes for process diagnostics. The various devices are numbered in Figure 2-4 as follows:

- l. 20-element linear imager

- 2. 4-element linear imager

- 3. 2-element linear imager

- 4. 4-element TDI array

- 5. Monolithic Gated Charge Integrator (GCI)

- 6. Test devices

Device numbers 1, 3, and 4 are all  $4\phi$  devices, with 12.5- $\mu$ m (0.5-mil) gate lengths in the cases of 1 and 4; device 3 has 10.0- $\mu$ m (0.4 mil) gate lengths. Device number 2 is a  $2\phi$  structure with 12.5- $\mu$ m gate lengths. The test

devices consist of three capacitors with different gate metal - either channel stop, buried, or surface metal. There are, in addition, two gated diodes to aid in evaluating process parameters. The 8585 chip dimensions are 2388  $\mu$ m (94 mils) by 2896  $\mu$ m (114 mils). The design rules for the 8585 chip are shown in Table 2-2.

Table 2-2. - 8585 Chip Design Rules.

| DIMENSION                                      | MINIMUM DIMENSION ON<br>SBRC 8585 (mils) |

|------------------------------------------------|------------------------------------------|

| CHANNEL STOP WIDTH                             | 0. 20                                    |

| ALUMINUM LINE WIDTH (ANY LEVEL)                | 0. 20                                    |

| AL-TO-AL GAP (ANY LEVEL)                       | 0. 20                                    |

| SM-TO-BM OVERLAP                               | 0. 125                                   |

| GATE LENGTH                                    | 0. 40                                    |

| CONTACT WINDOWS                                | 0.3 X 0.8                                |

| SOURCE-DRAIN IMPLANT WIDTH<br>FOR ARRAY DIODES | 2. 0                                     |

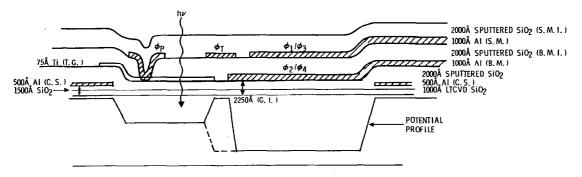

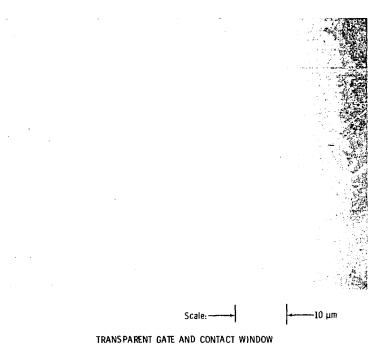

A schematic cross section perpendicular to the channel for the CCIRIDs on the 8585 chip is shown in Figure 2-5. The design/dimensions of the 20-element CCIRID are specified here, but the design of all the devices on the 8585 is similar. The 20-element CCIRID incorporates an array of 20 MOS detectors. The accumulated detector charges are transferred laterally into an opaque InSb shift register by means of a surface metal transfer gate ( $\phi_T$ ). A separate detector array rather than detection in the CCD channel provides greater flexibility since detector integration times may be varied independently of CCD clock frequency. The MOS photogates are 35 by 32.5  $\mu$ m on 50- $\mu$ m centers and are biased via a common bus bar ( $\phi_p$ ). 75Å of evaporated titanium was used as the semitransparent photogate material. The IR transmittance of the thin Ti gate structure was measured to be 38% including

Figure 2-5. - Cross Section Perpendicular to Channel for CCIRIDs on SBRC 8585 Chip.

reflection losses associated with the oxide layers above and below it. Ti was used for convenience and an improved transparent gate structure having lower loss is being developed.

The 20-bit shift register is a  $4\phi$ , surface channel, overlapping gate CCD. The gate oxide of the CCD is  $1000\text{\AA}$  of  $SiO_2$  grown on the InSb wafers by low-temperature chemical vapor deposition (LTCVD) using silane and oxygen at  $\sim 200\,^{\circ}$ C. An additional  $500\text{\AA}$  thick layer of  $SiO_2$  is sputter deposited over the LTCVD  $SiO_2$  layer, which passivates the gate oxide and serves as a transition layer between the LTCVD oxide and the other oxide and aluminum layers in the CCD structure, which are all sputtered. Aluminum gates and oxide contact cuts are delineated by chemical and plasma etching, respectively. The gate length on the 20-element device is 12.5  $\mu m$ .

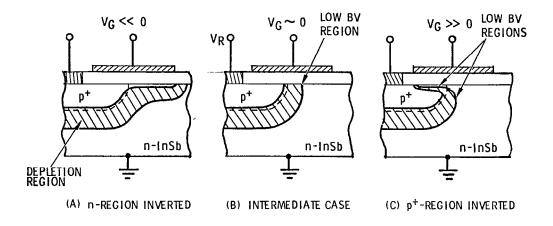

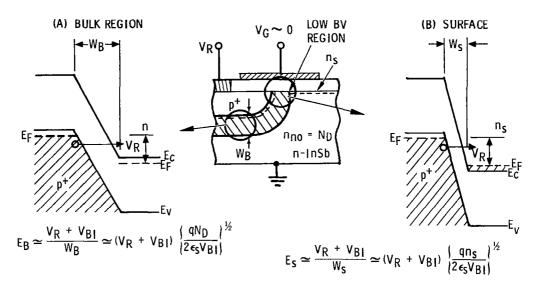

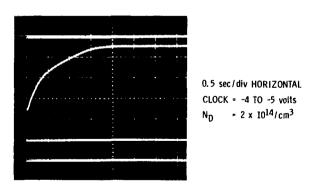

The 8585 chip incorporates planar p<sup>+</sup>-n junctions formed by ion implantation of beryllium for FZ input and charge output. The availability of a compatible junction technology may enable additional features to be incorporated in future chip designs such as overload protection or ac-coupled detector inputs. The implanted InSb junctions have sufficiently high breakdown voltage and low leakage for use in infrared CCD devices. Their breakdown voltage increases as  $N_D^{-1}$  and is greater than 5 volts for the impurity concentrations considered. Figure 2-6 shows a 77 K I-V characteristic for a Be-implanted diode on InSb with  $N_D = 4.5 \times 10^{14}/cm^3$ , with breakdown

Figure 2-6. - I-V Characteristic of Implanted Planar InSb p-n Junction (T = 77 K,  $N_D$  = 4.5  $\times$  10<sup>14</sup>/cm<sup>3</sup>; 2 volts/div; 10  $\mu$ a/div).

voltage of 8 volts. The forward and reverse currents of the implanted InSb junctions have been analyzed and found to follow the usual theory for abrupt junctions, with recombination-generation current dominating at 77 K. At 1-volt reverse bias, the 77 K reverse current density is  $5 \times 10^{-7}$  amp/cm<sup>2</sup>. This low leakage permits use of the Be-implanted junctions as the output diode in a floating diffusion output circuit.

#### PROCESS DESCRIPTION

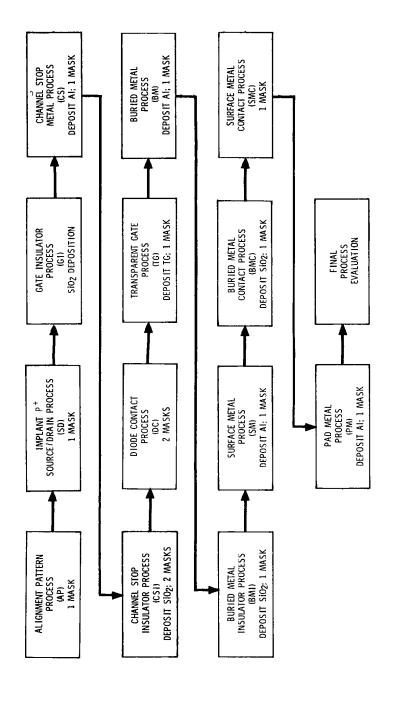

A total of fourteen mask levels is used to fabricate the 8585 CCIRID devices. The block diagram of Figure 2-7 illustrates the processing steps for the 8585 InSb CCIRID chip. The processes designated in Figure 2-7 are explained according to process step, layer designation, process description, and the process control methods used in Table 2-3.

As can be seen in Table 2-3, processing of the CCIRID devices requires the use of five different metal depositions: sputter deposition of aluminum for the channel stop, buried, surface and pad metal layers; and the use of thermally-deposited titanium for the semitransparent gates. The insulating layers in the CCIRID structure require five different oxide depositions.

Figure 2-7. Process Flow Chart for 8585 InSb CCIRID.

Table 2-3. 8585 CCIRID Fabrication Steps

| PROCESS STEP                                      | STEP<br>DESIGNATION | PROCESS DESCRIPTION                                                                                                                                                                                                                                                                          | PROCESS CONTROL METHODS                                                                                                                                                                                         |

|---------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A:<br>ALIGNMENT PATTERN                           | АР                  | ETCH BASIC ALIGNMENT MARKS INTO SUBSTRATE                                                                                                                                                                                                                                                    | MICROSCOPIC INSPECTION FOR SIZE AND EDGE DEFINITION.                                                                                                                                                            |

| SOURCE/DRAIN p <sup>+</sup><br>IMPLANT            | SD                  | ION IMPLANT p <sup>+</sup> BERYLLIUM THROUGH<br>PHOTORESIST PATTERN                                                                                                                                                                                                                          | MICROSCOPIC INSPECTION OF STAINED WITNESS SAMPLES.                                                                                                                                                              |

| B:<br>GATE INSULATOR                              | GI                  | DEPOSIT SILICON DIOXIDE GATE INSULATOR                                                                                                                                                                                                                                                       | CAPACITANCE VERSUS VOLTAGE TO CHARACTERIZE ELECTRICAL PROPERTIES OF SILICON DIOXIDE – INDIUM ANTIMONIDE INTERFACE, INCLUDING: SURFACE STATE DENSITY, STORAGE TIME, FLAT BAND SHIFT, HYSTERESIS AND CAPACITANCE. |

| C:<br>CHANNEL STOP METAL                          | cs                  | SPUTTER DEPOSIT ALUMINUM METALLIZA-<br>TION AND ETCH                                                                                                                                                                                                                                         | SURFACE PROFILOMETER MEASUREMENT OF<br>THICKNESS. MICROSCOPIC INSPECTION<br>OF GEOMETRY AFTER ETCHING.                                                                                                          |

| CHANNEL STOP<br>INSULATOR OR<br>FIELD OXIDE       | CSI<br>OR<br>FO     | SPUTTER DEPOSIT SILICON DIOXIDE INSULATOR AND ETCH                                                                                                                                                                                                                                           | GEOMETRY AFTER ETCHING; THICKNESS<br>MEA SUREMENTS.                                                                                                                                                             |

| DIODE CONTACT                                     | DC                  | ETCH INSULATORS TO IMPLANTED InSU<br>SURFACE AND FORM DIODE CONTACT                                                                                                                                                                                                                          | GEOMETRY AFTER ETCHING; ELECTRICAL SHORT PROBE TESTS; 77°K DIODE PROBE TESTS.                                                                                                                                   |

| TRANSPARENT GATE                                  | TG                  | THERMALLY DEPOSIT TITANIUM THROUGH PHOTORESIST MASK                                                                                                                                                                                                                                          | GEOMETRY: TRANSMISSION, ABSORPTION, AND REFLECTIVITY OF WITNESS SAMPLES.                                                                                                                                        |

| BURIED METAL                                      | BW                  | SPUTTER DEPOSIT FIRST ALUMINUM CCD<br>GATE METALLIZATION AND ETCH                                                                                                                                                                                                                            | GEOMETRY AFTER ETCHING; THICKNESS MEASUREMENTS.                                                                                                                                                                 |

| BURIED METAL<br>INSULATOR                         | ВМІ                 | SPUTTER DEPOSIT BURIED, AND SURFACE<br>GATE INSULATOR AND ETCH CONTACT<br>WINDOWS                                                                                                                                                                                                            | GEOMETRY AFTER ETCHING; THICKNESS MEASUREMENTS.                                                                                                                                                                 |

| SURFACE METAL                                     | SM                  | SPUTTER DEPOSIT SECOND ALUMINUM CCD<br>GATE METALLIZATION AND ETCH                                                                                                                                                                                                                           | GEOMETRY AFTER ETCHING; THICKNESS MEASUREMENTS.                                                                                                                                                                 |

| SURFACE METAL<br>INSULATOR AND<br>BURIED CONTACTS | ВМС                 | SPUTTER DEPOSIT SURFACE METAL SILICON<br>DIOXIDE INSULATOR AND ETCH BURIED<br>METAL GATE CONTACTS                                                                                                                                                                                            | GEOMETRY AFTER ETCHING: THICKNESS<br>MEASUREMENTS OF INSULATOR.                                                                                                                                                 |

| SURFACE METAL CONTACTS                            | SMC                 | ETCH SURFACE METAL GATE CONTACTS                                                                                                                                                                                                                                                             | GEOMETRY AFTER ETCHING.                                                                                                                                                                                         |

| PAD METAL                                         | PM                  | SPUTTER DEPOSIT ALUMINUM AND ETCH<br>BOND PADS                                                                                                                                                                                                                                               | GEOMETRY AFTER ETCHING; THICKNESS MEASUREMENTS.                                                                                                                                                                 |

| D:<br>FINAL PROCESS<br>EVALUATION                 |                     | MECHANICAL AND ELECTRICAL INTEGRITY DETERMINED BY MICROSCOPIC INSPECTION, ELECTRICAL PROBE TESTS, SURFACE C-V TESTS. AND DIODE C-V TESTS. SCANNING ELECTRON MICROSCOPE FOR HIGH-MACNIFICATION INSPECTION OF MULTILAYER STRUCTURE, VOLTAGE CONTRAST EVALUATION, AND VOLTAGE BREAKDOWN STUDIES |                                                                                                                                                                                                                 |

These include the deposition of LTCVD SiO<sub>2</sub> for the gate insulator to obtain the required low surface state density. The LTCVD SiO<sub>2</sub> layer is sealed with an overcoating of sputtered SiO<sub>2</sub>. Sputtered SiO<sub>2</sub> is also used for the channel stop, buried metal and surface metal insulating layers.

The process utilizes positive photoresist (Shipley AZ1300 series) and 2:1 reduction projection mask aligning to delineate the CCD devices. Etching of the aluminum gate patterns is done chemically while contact cuts through the oxide layers are etched with a plasma etcher/asher.

#### MASK AND PROCESS MODIFICATIONS

The original 8585 mask design had some features which were found to be incompatible with the actual processing sequence for fabricating the CCIRIDs as it developed during the program. These design changes led to new photomasks being fabricated for the channel stop insulator, surface metal insulator, and diode contact levels.

The first mask change required was to separate the channel stop metal contact window cuts from the channel stop insulator etch process (CSI). In the CSI etch step, the total thickness of the oxide is reduced in the CCD channel region. In this operation only a fraction of the oxide is removed and no absolute stop point (i. e., an underlying metal layer) is reached. The CSI step is intended to reduce the oxide thickness in the channel so as to decrease the clock voltage magnitudes required to operate the CCD. A result of the CSI etch is that some oxide remains in the channel stop metal contact window. By adding a new mask designated CSC, these contacts are now separately etched through to the metal stop to assure continuity.

The second mask change required separation of the BMC and SMC contact window cuts in place of the original SMI etch mask. This change was found to be necessary because of the different oxide thicknesses involved. The oxide overlying the surface metal is 0.2  $\mu$ m thick while the oxide over the buried metal is 0.4  $\mu$ m thick. When both sets of contact cuts were etched

simultaneously with the original mask, the surface metal contact cuts were severely overetched while clearing the buried metal contact cuts.

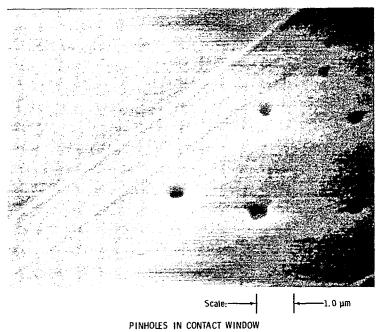

CCIRID wafers which were processed early in the contract were found to have a high number of "open" p-n junctions (input and output diodes) which were due to various degrees of contact degradation. This degradation varied from oxide lifting around the contact windows, to windows which appeared visually acceptable but were electrically open. Junctions tested for contact continuity at room temperature showed contact resistances which ranged from > 1000 M $\Omega$  (opens) to ~  $40\Omega$ . When cooled to 77 K, all were found to either open or show very poor forward characteristics.

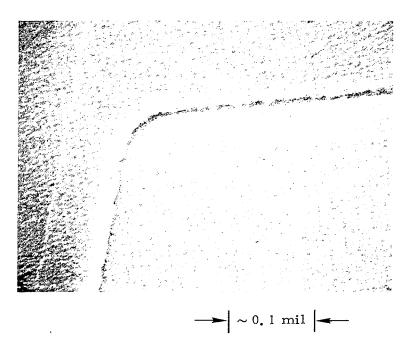

The scanning electron microscope (SEM) was used to determine why the diode contacts were opening. The SEM photograph shown in Figure 2-8 illustrates the origin of the contact failures. The photograph clearly shows that while the overlying aluminum conductor is continuous over the upper oxide

Figure 2-8. ~ SEM Photograph of Etched Diode Contact Window Showing Undercutting of Gate Oxide Layer.

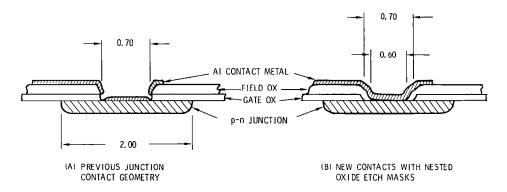

edge, it is discontinuous at the bottom edge indicating that the oxide layer is undercut at the InSb/SiO<sub>2</sub> interface. This was found to result from differential etch rates of the LTCVD SiO<sub>2</sub> gate insulator and the overlying sputtered SiO<sub>2</sub> field oxide. For the early wafer lots the diode contact windows were formed by etching through both oxide layers to the p-n junction surface in a single etching operation. The reason for this etch variation is that the LTCVD SiO<sub>2</sub> etches faster than the overlying sputtered SiO<sub>2</sub> (approximately 250Å/min versus 90Å/min, respectively. This variation in etch rate allows the gate oxide to etch faster laterally than the field oxide layer, thus creating an undercut profile at the lower oxide edge. This edge profile is shown schematically in Figure 2-9(A).

Figure 2-9.- p-n Junction Contacts on 8585 Chip (Dimensions for 20-Element Imager, in mils).

The solution to the diode contact problem required fabricating a new photomask which is identical to the original diode contact window mask except that the window dimensions are smaller by 0.10 mil per side, as shown in Figure 2-9(B). The process was changed so that following the channel stop metal delineation process, the original mask is used to etch contact windows through the gate oxide. Then the field oxide is deposited and the new smaller contact windows are etched. The "nested" etch masks result in a window geometry illustrated schematically in Figure 2-9(B). Since each oxide layer is etched separately, the lateral undercutting which occurs does not effect the

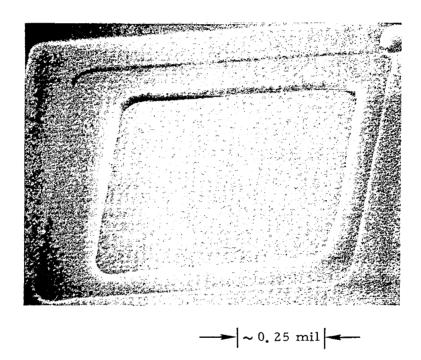

overall contact window. A SEM photograph of a typical contact processed with the nested oxide etch mask procedure is shown in Figure 2-10, showing continuous Al metal coverage of the window edges. Since implementation of the nested contact process, the yield of good diode contacts has exceeded 90%.

With these mask and process changes having been made, testable InSb CCIRIDs were produced beginning with 8585 Lot 4. The following sections describe the test results.

Figure 2-10.- SEM Photograph of Diode Contact Using Nested Oxide Etch Masks (2-Element CCIRID No. 498-20-B5, Lot 8B, 40°, 3500X).

# Section 3 TWO-ELEMENT InSb CCIRID

#### DEVICE DESCRIPTION

The first device on the 8585 chip successfully processed and tested was the two-element, 4¢ InSb CCIRID. This CCD is at the center right in Figure 2-4. It is a smaller version of the 20-element CCIRID and is basically similar to it in design. The two-element device was included on the chip to take advantage of its higher yield due to its smaller device area, optimizing the possibility of obtaining CCD data from the 8585 chip as early as possible.

A photomicrograph of the two-element CCIRID is shown in Figure 3-1. The CCD register is at the center of the photograph and the two dark square regions to the right of the CCD channel are the MOS detectors (photogates). The input and output p-n junctions are at the top and bottom of the photograph, respectively.

Figure 3-1. - Two-Element, 40 InSb CCIRID on 8585 Chip.

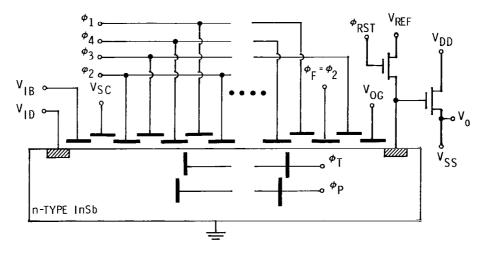

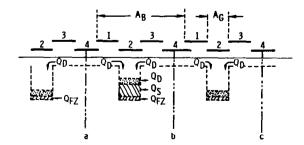

The schematic diagram for the two-element CCIRID is shown in Figure 3-2. The schematics for the two-element and 20-element CCIRIDS are identical and this figure will be referenced again in Section 4. The shift register in the two-element array is an overlapping-gate,  $4\emptyset$  device with 14 clocked gates (3-1/2 bits, 4 gates/bit). The first clocked gate is  $\emptyset_2$  and the last clocked gate is  $\emptyset_3$ . The fat zero input (which can be also used to electrically input signal charge into the register) consists of a diode ( $V_{ID}$ ), an input buried gate ( $V_{IB}$ ), and an input surface gate ( $V_{SC}$ ). The output elements consist of a diode, a buried metal output gate ( $V_{OG}$ ), and a floating gate ( $V_{F}$ ) which may be optionally used.

Figure 3-2. - Schematic Diagram of Two-Element and 20-Element InSb CCIRIDs.

Either the output p-n junction or the floating gate can be used for charge detection; in testing to date, the former approach has been taken, using the output junction in a floating diffusion output circuit. The circuit utilizes two 3N163 p-channel enhancement-type silicon MOSFETS, mounted in the flatpack adjacent to the InSb chip, for the source follower and switch transistors shown in Figure 3-2. An identical arrangement was used for the 20-element evaluation described in Section 4. All CCDs on the 8585 chip,

including the two-element device, also have a floating clock output option. Operating with the floating diffusion output, the isolated gate  $\phi_F$ , which lies between a  $\phi_1$  and  $\phi_3$  gate, was tied to its appropriate phase  $(\phi_2)$  and clocked normally.

The device has two photogate detectors biased through a common bus  $(\phi_P)$  and a surface metal transfer gate  $(\phi_T)$ . The photocharge from the detectors enters the register through two ports in the channel stop metal beneath  $\phi_4$  gates. The ports are one and three bits away from the output; i. e., there is an empty (isolation) bit between detector inputs. This differs from the 20-element CCIRID which has one CCD bit/detector. The CCD gate length in the two-element device is 10  $\mu$ m, slightly smaller than that in the 20-element device (12.5  $\mu$ m). With these exceptions the device layouts are identical.

#### GATE OXIDE WITNESS EVALUATION

Several two-element CCIRIDs were tested from wafer number\* 442-14, 8585 Lot 4. Each wafer lot includes a witness wafer for evaluating the gate oxide characteristics after deposition but prior to subsequent CCD processing, and p-n junction characteristics. The gate oxide witness for 8585 Lot 4 was sample number 486A-10A. The witness is processed simultaneously with the CCIRID wafers up through sputtering of the 500Å SiO<sub>2</sub> overlayer. In the deposition of the first device metal layer (the channel stop metal layer) the CCIRID wafers are removed from the system after 500Å of A1 is deposited. The witness wafer remains to receive a total of 2000Å for ease of wirebonding to the test capacitors. In this manner the witness undergoes identical process conditions through the first gate level. The witness wafers are drawn from the inventory of wafers not suitable for CCIRID processing (e.g., those with

<sup>\*</sup>The device identification system used throughout this report is as follows: Each CCD chip is identified by a seven-digit number as: XXX-XX-XX. The first three numbers represent the InSb ingot number; the second two the wafer number; and the last pair (alphanumeric) identifies the particular chip or die.

scratches or too high an impurity concentration). The 2000Å of aluminum on the witness wafer is photoetched into a pattern of 20-mil diameter dots. After dicing into groups of nine dots, chips are mounted in TO-5 packages which adapt to specially-designed MOS capacitor evaluation dewars.

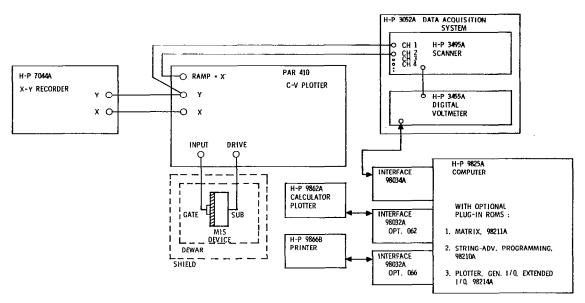

The witness capcitors are evaluated for flatband voltage, surface state density, and other parameters pertinent to the CCIRIDs. To allow rapid accumulation of the necessary C-V and other MOS diagnostic data, a computer-aided surface analysis system has been used in this program. A survey to determine the optimum Nss measurement technique for InSb and other infrared semiconductors, resulting in selection of the quasi-static technique, and design and setup of the automated C-V system, was accomplished on a related contract (F04701-76-C-0174). The system has been continually improved and its capabilities expanded under SBRC's Two-Dimensional Infrared Array IR&D Project. Its present configuration is shown in Figgure 3-3. In addition to its principal output, Nss versus surface potential, software for  $N_{\text{SS}}$  measurement by the conductance method, substrate impurity concentration calculation, and C-t data acquisition and analysis has been implemented. Not shown in Figure 3-3 are a PAR 135 Electrometer, an HP 3310A Function Generator, and a Tektronix 7403N Oscilloscope which are used in obtaining the quasi-static (low-frequency) capacitance characteristics and the pulsed capacitance (C-t) data.

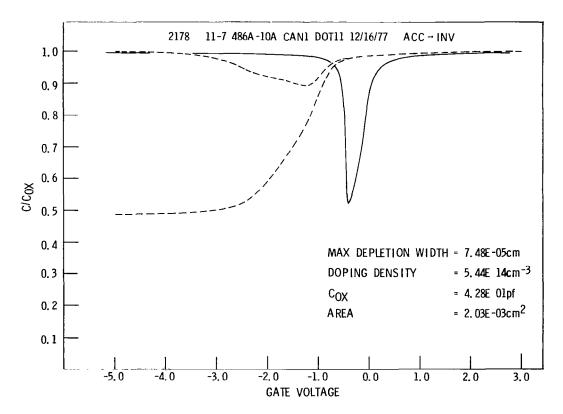

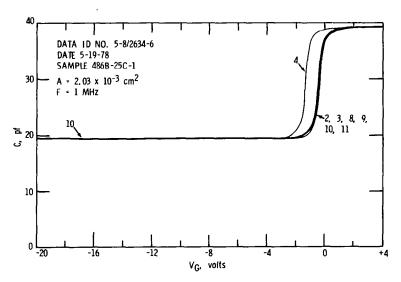

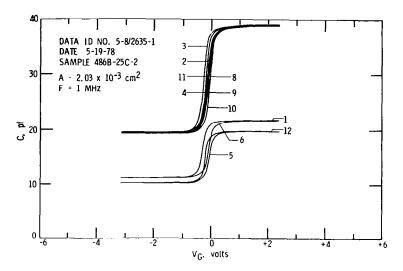

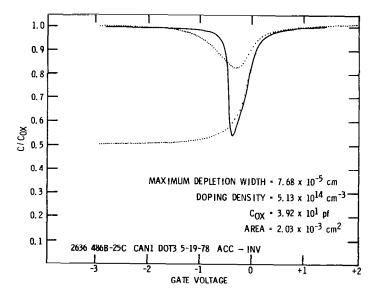

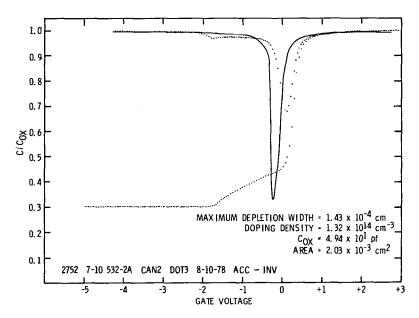

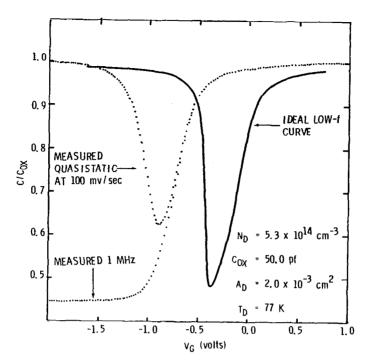

Figure 3-4 shows the measured low-frequency and high-frequency C-V characteristics (dashed curves) for one (typical) capacitor from the Lot 4 witness sample. The solid curve is the ideal low-frequency C-V characteristic calculated by the computer for the particular impurity concentration and oxide capacitance of the witness sample. The oxide capacitance from the accumulation region of the curve is 43pf giving  $C_{\rm OXW} = 43 {\rm pf}/2$ .  $03 \times 10^{-3} {\rm cm}^2 = 2$ .  $12 \times 10^{-8} {\rm f/cm}^2$ . The measured thickness of the LTCVD SiO<sub>2</sub> plus sputtered overlayer was  $1650 {\rm \AA}$  giving for the calculated dielectric constant of the witness gate oxide:

Figure 3-3. - SBRC Capacitance Measurement System.

Figure 3-4. - Low-Frequency and High-Frequency C-V Curves for Gate Oxide Witness; 8585 Lot 4; Sample 486A-10A.

$$K_{OXW} = \frac{C_{OXW} t_{OXW}}{\epsilon_{O}} = 3.95$$

(3-1)

in excellent agreement with the expected dielectric constant of SiO2.

The flatband capacitance can be obtained from the C-V computer program or the equation

$$\frac{C_{FB}}{C_{OX}} = \left[1 + C_{OX} \left(\frac{kT}{N_D \epsilon_s q^2}\right)^{\frac{1}{2}}\right] - 1$$

(3-2)

which gives  $C_{\rm FB}$  = 0.87  $C_{\rm OX}$  for the witness sample parameters. For the capacitor of Figure 3-4, the flatband voltage is -1.0 volt. Average  $V_{\rm FB}$  of all samples was -1.15 volts. The net fixed charge density at the interface may be then calculated as

$$N_{fc} = Q_{fc}/q \cong C_{OXW} (-V_{FB})/q = +1.5 \times 10^{11} \text{ charges/cm}^2$$

(3-3)

This low fixed (positive) charge density is characteristic of the LTCVD  $\mathrm{SiO}_2$ -InSb interface, and leads to relatively low clock voltage requirements for the CCIRIDs. Note that the calculation (3-3) assumes zero metal-semiconductor work function difference ( $\phi_{\mathrm{MS}}$ ). Taking handbook photoelectric work functions for Al and InSb indicates that  $\phi_{\mathrm{MS}}$  may be as large as -0.5 volt, but our data indicate that it is closer to zero (photoelectric work functions must be viewed as an estimate only of the actual work function difference in an MOS structure). The work function difference is expected to be negative, however, leading to an even lower  $\mathrm{N}_{\mathrm{fC}}$  than calculated in (3-3).

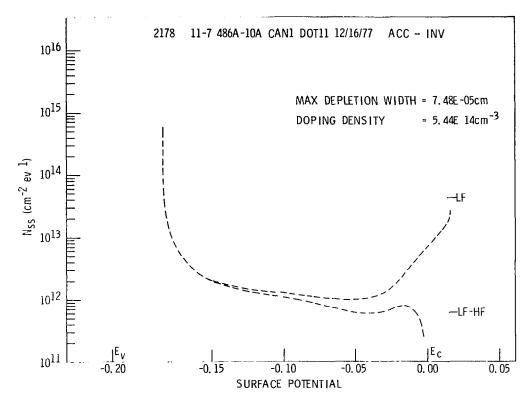

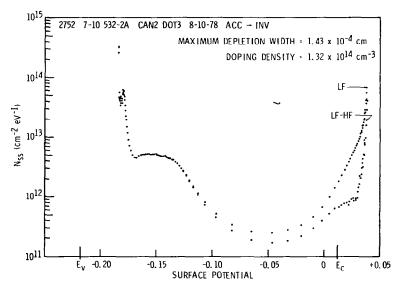

Referring again to Figure 3-4, the dispersion of the measured high-frequency capacitance curve relative to the ideal curve, and the small dip in the measured low-frequency curve, both indicate that  $N_{\rm ss}$  is relatively high. Figure 3-5 shows the results of the quasi-static calculation of  $N_{\rm ss}$ , showing a midband value of  $10^{12}/{\rm cm}^2$ -eV. The LTCVD SiO<sub>2</sub> for 8585 Lot 4 was deposited in a vertical-flow configuration reactor, and this surface state density is to date typical of this particular reactor. CVD reactor comparisons

Figure 3-5.- Surface State Density of Gate Oxide Witness; 8585 Lot 4; Sample 486A-10A.

and a more detailed discussion of InSb gate oxide characteristics will be found in Section 5 and cited references.

Finally, although the witness sample dots were not stressed to destruction to determine ultimate breakdown strength, all dots withstood 20 volts bias, or  $1.2 \times 10^6$  v/cm. Scaling this result to the nominal oxide thicknesses under the BM and SM of the CCD (2750Å and 4750Å respectively) these gate levels should withstand biases (with respect to substrate) of 33 and 57 volts respectively. This assumes no process-related degradation of oxide quality.

#### CCD GATE CAPACITANCE AND FLATBAND VOLTAGE

After completion of CCD processing, three MOS capacitors on each 8585 die are available for evaluation (see Figure 2-4). These capacitors are on the channel stop metal, buried metal, and surface metal levels so that the characteristics of each gate level may be determined. Flatband voltages of each gate level are measured to determine starting points for setting the clock voltages. The oxides beneath each of these three capacitors undergo the same processing conditions (e.g., etching) as their corresponding oxide levels in the CCD structures. Therefore, the capacitors provide an accurate measure of the CCD gate characteristics.

The oxide parameters for 8585 Lot 4, determined from the test capacitors, are tabulated in Table 3-1. Listed are the measured characteristics for the three gate levels along with the gate oxide witness sample. Row (a) in the table lists the nominal oxide thicknesses (total) under each gate level. The thicknesses for the various layers in the CCD are determined by Dektak stylus profilometer measurement of a step etched through the oxide layer. To provide a substrate which is inert to the oxide etch for accurate oxide thickness determination, single-crystal sapphire substrates are used for these witness parts. The density and thickness of the SiO<sub>2</sub> sputtered on the sapphire may differ slightly from that deposited on the InSb wafers; consequently, these thicknesses are "nominal" but close to the actual thicknesses on the InSb.

Row (b) in Table 3-1 gives the measured capacitance per unit area determined from the capacitor C-V curves and the known area of each dot. Using the dielectric constant (3.95) determined for the gate oxide witness sample and assuming\* it is constant for each SiO<sub>2</sub> layer in the CCD, the oxide thicknesses may be calculated from the measured capacitances in row (b). The values so obtained should agree well with the nominal thick-

<sup>\*</sup>This is a valid assumption based on independent measurements of the dielectric constant of our sputtered SiO<sub>2</sub> films in MIM structures.

Table 3-1. Oxide Parameters, 8585 Lot 4.

|           |                                               | GATE OXIDE<br>WITNESS    | CHANNEL<br>STOP METAL    | BURIED<br>METAL         | SURFACE<br>METAL        |

|-----------|-----------------------------------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| WAFER NO. |                                               | 486A -10A                | 442-14                   | 442-15                  | 442-14                  |

| (a)       | NOMINAL OXIDE<br>THICKNESS (Å)                | 1650                     | 1650                     | 2750                    | 4750                    |

| (b)       | MEASURED C <sub>OX</sub> (f/cm <sup>2</sup> ) | 2. 12 x 10 <sup>-8</sup> | 2. 13 x 10 <sup>-8</sup> | 1.36 x 10 <sup>-8</sup> | 7.79 x 10 <sup>-9</sup> |

| (c)       | DIELECTRIC CONSTANT                           | 3. 95                    | (3. 95)                  | (3, 95)                 | (3. 95)                 |

| (d)       | CALCULATED OXIDE<br>THICKNESS (Å)             |                          | 1640                     | 2580                    | 4490                    |

| (e)       | ERROR (d) TO (a)<br>(%)                       |                          | ~0. 6                    | -6. 2                   | -5.5                    |

| (f)       | FLATBAND CAPACITANCE (CFB/COX)                | 0. 87                    | 0. 80                    | 0.87                    | 0. 92                   |

| (g)       | MEASURED V <sub>FB</sub> (volts)              | -1. 15                   | -0.8                     | -2.0                    | -4.0                    |

| (h)       | Nfc (charges/cm <sup>2</sup> )                | +1.5 x 10 <sup>11</sup>  | +1.1 x 10 <sup>11</sup>  | +1.7 x 10 <sup>11</sup> | +1.9 x 10 <sup>11</sup> |

nesses in row (a). These are listed in row (d) and are seen to be quite close to the nominal values.

The flatband capacitances and measured flatband voltages for the CCD gate levels are listed in rows (f) and (g) of Table 3-1. Using equation 3-3,  $N_{fc}$  was calculated for each level [row (h)] and is seen to be in the 1 to 2 ×  $10^{11}/cm^2$  range consistent with the gate oxide witness sample. It should be noted that, for the LTCVD SiO<sub>2</sub>-InSb interface, we have found that the flatband voltage can be shifted either positive or negative by biasing the gate with respect to substrate prior to and during cooldown of the device to 77 K. These bias stress studies indicate the fixed charge results from injection from the semiconductor into the oxide. However, once cooled to 77 K, the

fixed charge remains constant under normal operating biases. The flatband voltages and corresponding fixed charge values given in Table 3-1 were measured with the gates floating during cooldown, rather than with any bias applied. In the InSb CCD testing throughout the program, the device terminals were also floated during cooldown so that the "intrinsic" fixed charge levels listed in Table 3-1 are the values that apply to the device as tested.

### SURFACE POTENTIAL AND CHARGE STORAGE CAPACITY

Having determined the CCD oxide parameters given in Table 3-1, the surface potential versus gate voltage relationships may be calculated for the 8585 Lot 4 devices. The relationship between the surface potential  $\psi_{\rm S}$ , stored charge  ${\rm Q_p}$ , and applied gate voltage  ${\rm V_G}$  is

$$\psi_{s} = V + V_{O} - V_{O} \left(1 + \frac{2V}{V_{O}}\right)^{\frac{1}{2}}$$

(3-4)

where

$$V \equiv V_G - V_{FB} + \frac{Q_p}{C_{OX}}$$

(3-5)

and

$$V_O = -\epsilon_s q N_D / c_{OX}^2$$

(3-6)

$C_{\mbox{OX}}$  is the oxide capacitance/unit area appropriate to the gate being considered.

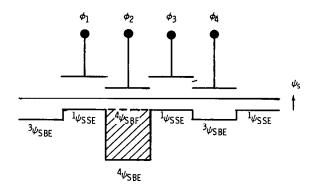

To define nomenclature, Figure 3-6 shows one bit of an overlapping-gate,  $4\phi$  CCD. Consistent with Figure 3-2,  $\phi_1$  and  $\phi_3$  are surface gates and  $\phi_2$  and  $\phi_4$  are buried gates. On the 8585 chip, the surface and buried gates are equal in area as shown in Figure 3-6. The surface potentials are shown in Figure 3-6 appropriate to the one-quarter of the clock period during which time the charge is stored beneath the buried  $\phi_2$  gate. We consider here simple  $4\phi$  clocking but other clocking modes are possible such as simulated  $2\phi$  or  $4\phi$  double-clocking.

The clock voltages applied to the surface gates ( $\phi_1$ ,  $\phi_3$ ) are  $V_{G1}$  and  $V_{G2}$  and to the buried gates ( $\phi_2$ ,  $\phi_4$ )  $V_{G3}$  and  $V_{G4}$ . (These are identified in

Figure 3-6. - Surface Potentials for One Bit of 4¢ CCD.

the 20-element CCIRID clock diagram in Section 4, Figure 4-2.) The high or "on" voltages are  $V_{G2}$  and  $V_{G4}$  with  $V_{G2} < V_{G1}$  and  $V_{G4} < V_{G3}$ . The surface potential notation used is that the subscripts refer to B = buried gate, S = surface gate, E = empty, F = full, and the superscripts 1, 2, 3, 4 denote the potentials appropriate to clock voltages  $V_{G1}$ ,  $V_{G2}$ ,  $V_{G3}$ , and  $V_{G4}$  respectively.

Referring to Figure 3-6, the  $\phi_2$  gate is on (clock voltage  $V_{G4}$ ) and the other three gates are clocked off.  $\phi_1$  and  $\phi_3$  are therefore at their off surface potential  $^1\psi_{\rm SSE}$  and are empty. The buried gate  $\phi_4$  is also empty, at potential  $^3\psi_{\rm SBE}$ . When no charge is being transferred in the CCD, the potential under  $\phi_2$  is  $^4\psi_{\rm SBE}$ . The criterion for maximum charge storage in the CCD is evident from Figure 3-6 and occurs when

$$^{4}\psi_{\text{SBF}} = ^{1}\psi_{\text{SSE}} \tag{3-7}$$

Any less-negative surface potential under gate  $\phi_2$  resulting from additional charge stored will clearly produce spillover across the  $\phi_1$  and  $\phi_3$  gates. The maximum charge that can be stored under  $\phi_2$  is therefore

<sup>\*</sup>Signs and notation appropriate to a p-channel CCD are used throughout. When considering the inequalities, recall that gate voltages and surface potentials are negative for a p-channel device in normal operation.

$$Q_{pB} \text{ (max)} \cong C_{OXB} \left( {}^{4}\psi_{SBF} - {}^{4}\psi_{SBE} \right)$$

$$\cong C_{OXB} \left( {}^{1}\psi_{SSE} - {}^{4}\psi_{SBE} \right) \tag{3-8}$$

Considering in a similar manner the fraction of the clock period during which the charge is stored beneath a surface gate (e.g.,  $\phi_3$ ) one obtains for the maximum charge storage

$$Q_{pS} \text{ (max)} \cong C_{OXS} \left(^2 \psi_{SSF} - ^2 \psi_{SSE}\right)$$

$$\cong C_{OXS} \left(^3 \psi_{SBE} - ^2 \psi_{SSE}\right) \tag{3-9}$$

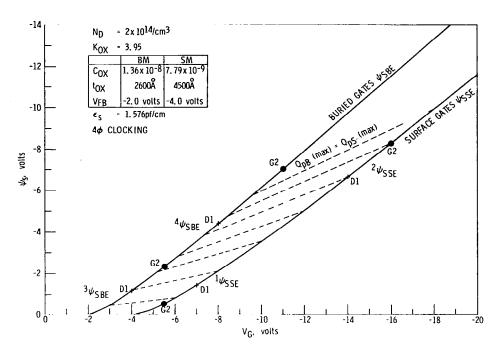

Equations (3-8) and (3-9) show that the charge storage capacity may be estimated for a given set of clock voltages from the empty-well surface potentials of the buried and surface gates. Using equations (3-4) through (3-6), with  $Q_p = 0$ , the  $\psi_S$  versus  $V_G$  curves appropriate to 8585 Lot 4 were calculated and are plotted in Figure 3-7. These curves give the surface potential beneath the gate when empty for any applied  $V_G$ .

A further criterion for simple 4¢ clocking and for the case of equal gate area is

$$Q_{pB} (max) = Q_{pS} (max)$$

(3-10)

which using (3-8) and (3-9) leads to

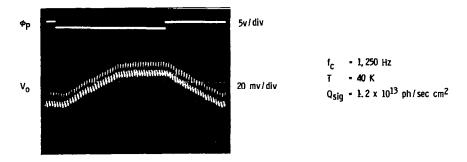

$${}^{4}\psi_{\text{SBE}} = {}^{2}\psi_{\text{SSE}} \left(\frac{C_{\text{OXS}}}{C_{\text{OXB}}}\right) \tag{3-11}$$