## NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM MICROFICHE. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE

# MASA CR- 160004

(NASA-CR-160004) IC KU-BAND IMPATT

AMPLIFIER Final Report, 1 Jun. 1977 - 31

Jan. 1979 (Texas Instruments, Inc.) 111 p

HC A06/HF A01 CSCL 09A

N80-27601

Unclas G3/33 25333

#### IC KU-BAND IMPATT AMPLIFIER

V. Sokolov

M. R. Namordi

F. H. Doerbeck

W. R. Wisseman

Texas Instruments Incorporated

Central Research Laboratories

13500 North Central Expressway

Dallas, Texas 75265

March 1979

Final Project Report for Period 1 June 1977 - 31 January 1979

Prepared for

GODDARD SPACE FLIGHT CENTER

Greenbelt, Maryland 20771

Ş

# TABLE OF CONTENTS

| SECTION |                                                                 |                                                                          | PAGE |  |  |  |  |

|---------|-----------------------------------------------------------------|--------------------------------------------------------------------------|------|--|--|--|--|

| I       | INTRODUCTION AND SUMMARY                                        |                                                                          |      |  |  |  |  |

| II      | KU-                                                             | BAND IMPATT DEVELOPMENT                                                  | 5    |  |  |  |  |

|         | Α.                                                              | Device Design                                                            | 5    |  |  |  |  |

|         | В.                                                              | GaAs Epitaxial Growth                                                    | 11   |  |  |  |  |

|         | C.                                                              | Device Fabrication Process                                               | 16   |  |  |  |  |

|         |                                                                 | 1. Test Slice Characterization                                           | 16   |  |  |  |  |

|         |                                                                 | 2. Slice Uniformity Characterization                                     | 20   |  |  |  |  |

|         |                                                                 | a. Surface Quality                                                       | 20   |  |  |  |  |

|         |                                                                 | b. Substrate Evaluation                                                  | 20   |  |  |  |  |

|         |                                                                 | c. Anodic Thinning for Uniformity Evaluation                             | 22   |  |  |  |  |

|         |                                                                 | d. Uniformity Evaluation                                                 | 22   |  |  |  |  |

|         |                                                                 | 3. Final Processing                                                      | 22   |  |  |  |  |

| ,       | D.                                                              | Device Waveguide Performance                                             | 27   |  |  |  |  |

|         | E.                                                              | Device Evaluation and Performance in Microstrip                          | 32   |  |  |  |  |

| III     | AMPLIFIER DEVELOPMENT                                           |                                                                          |      |  |  |  |  |

|         | Α.                                                              | General                                                                  | 35   |  |  |  |  |

|         | В.                                                              | FET Preamplifier Design and Performance                                  | 39   |  |  |  |  |

|         | C.                                                              | IMPATT Driver Amplifier Design and Performance                           | 49   |  |  |  |  |

|         | D. IMPATT Balanced Power Amplifier Stage Design and Performance |                                                                          |      |  |  |  |  |

|         | Ε.                                                              | Design, Integration, and Performance of Spacecraft Transmitter Amplifier | 60   |  |  |  |  |

|         |                                                                 | l. Amplifier Housing                                                     | 60   |  |  |  |  |

|         |                                                                 | 2. Bias Shutdown Circuit                                                 | 60   |  |  |  |  |

|         |                                                                 | 3. Integrated Amplifier Performance                                      | 62   |  |  |  |  |

| IV .    | IMPA                                                            | ATT RELIABILITY STUDIES                                                  | 71   |  |  |  |  |

|         | Α.                                                              | Introduction                                                             | 71   |  |  |  |  |

JUANUS HOT FILMED

# TABLE OF CONTENTS

(continued)

| SECTION |                                                                                                   | PAGE |

|---------|---------------------------------------------------------------------------------------------------|------|

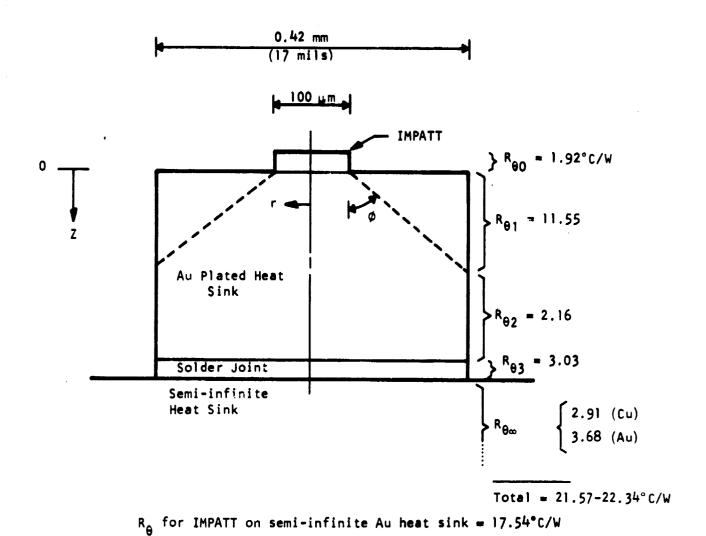

|         | B. Thermal Impedance, R <sub>0</sub>                                                              | 73   |

|         | 1. Thermal Circuit Model                                                                          | 73   |

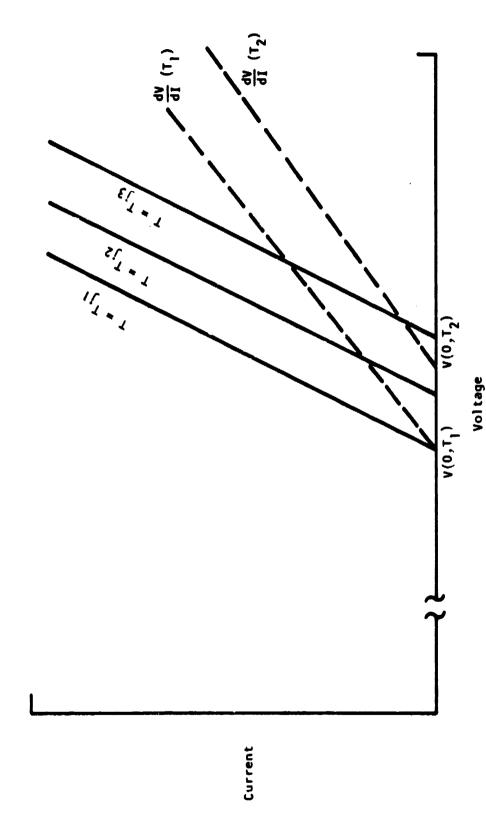

|         | <ol> <li>Determination of R<sub>0</sub> using the Reverse Bias</li> <li>Characteristics</li></ol> | 76   |

|         | 3. R <sub>0</sub> Experiments                                                                     | 79   |

|         | C. Temperature Stress Test                                                                        | 82   |

|         | D. Non-Rf Bias-Temperature Stress Test                                                            | 84   |

|         | E. Rf Bias-Temperature Stress Test                                                                | 85   |

| ٧       | CONCLUSIONS AND RECOMMENDATIONS                                                                   | 100  |

|         | REFERENCES                                                                                        | 104  |

|         | LIST OF TABLES                                                                                    |      |

| TABLE   |                                                                                                   | PAGE |

| 1       | Performance Requirements                                                                          | 2    |

| 2       | Representative Waveguide Circuit Results                                                          | 31   |

| 3       | Driver Stage Performance                                                                          | 53   |

| 4       | Balanced Stage Performance                                                                        | 59   |

| 5       | Locking Bandwidth Characteristics of Spacecraft Transmitter Amplifier                             | 69   |

| 6       | Activation Energy of GaAs IMPATTs with Different Barrier Metallizations                           | 72   |

| 7       | Thermal Impedance Measurements by Different Techniques                                            | 80   |

| 8       | Microwave Test Results of Temperature-Stressed Diodes (Lot 79III)                                 | 83   |

|         | •                                                                                                 |      |

# LIST OF TABLES

# (continued)

| TABLE  |                                                                                       | PAGE |

|--------|---------------------------------------------------------------------------------------|------|

| 10     | IMPATT Oscillators for Reliability Life Test                                          | 93   |

| 11     | Behavior of Oscillator #8 During rf BTS Life Test                                     | 94   |

| 12     | Equivalent Time Accumulated by Each IMPATT                                            | 96   |

|        | LIST OF ILLUSTRATIONS                                                                 |      |

| FIGURE |                                                                                       | PAGE |

| 1      | Idealized Low-High-Low Structure                                                      | 6    |

| 2      | Calculated Intrinsic Efficiency of GaAs LHL Using Idealized Structure                 | 7    |

| 3      | $\eta_{\text{max}}$ Dependence on Q and N <sub>D</sub> when $X_p = X_{p \text{ opt}}$ | 9    |

| 4      | Maximum Efficiency Achieved from Various Slices                                       | 12   |

| 5      | Epitaxial Growth System with Sliding Substrate Reactor                                | 13   |

| 6      | Schematic Diagram of Sliding Substrate, Abrupt Junction Epitaxial Reactor             | 15   |

| 7      | Low-High-Low IMPATT Device Fabrication Flow Chart                                     | 17   |

| 8      | Composite Profile Obtained from Step-Etched Test Slice                                | 19   |

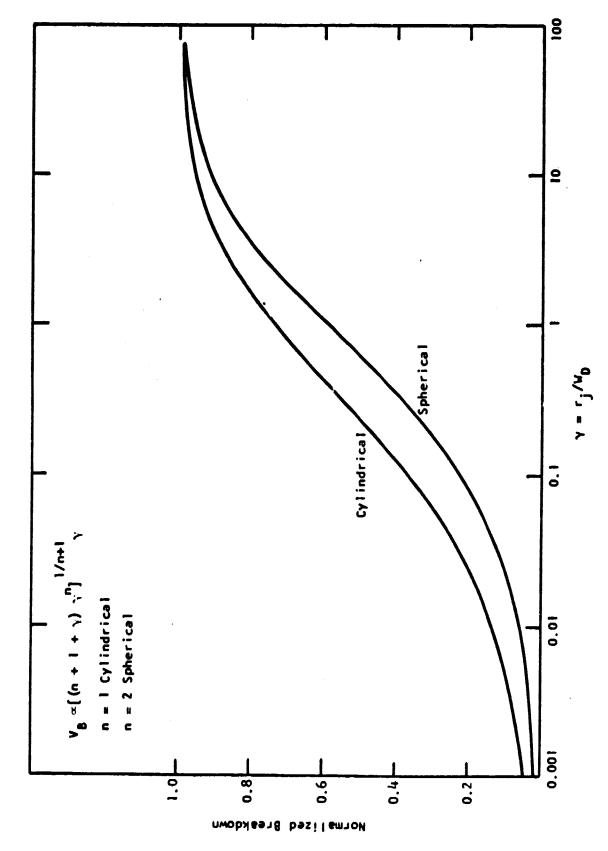

| 9      | Normalized Breakdown as a Function of Junction Curvature                              | 21   |

| 10     | Procedure for Fabricating GaAs Low-High-Low IMPATT Diodes                             | 24   |

| 11     | Voltage Map of a Slice Exhibiting Good Uniformity                                     | 25   |

| 12     | Breakdown Characteristics of a Diode from a Slice with a Good Surface                 | 26   |

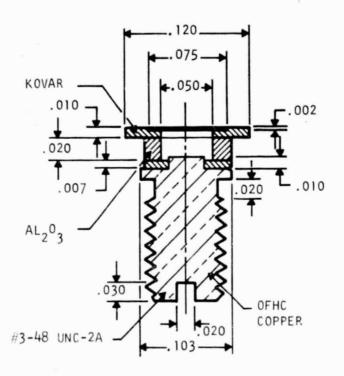

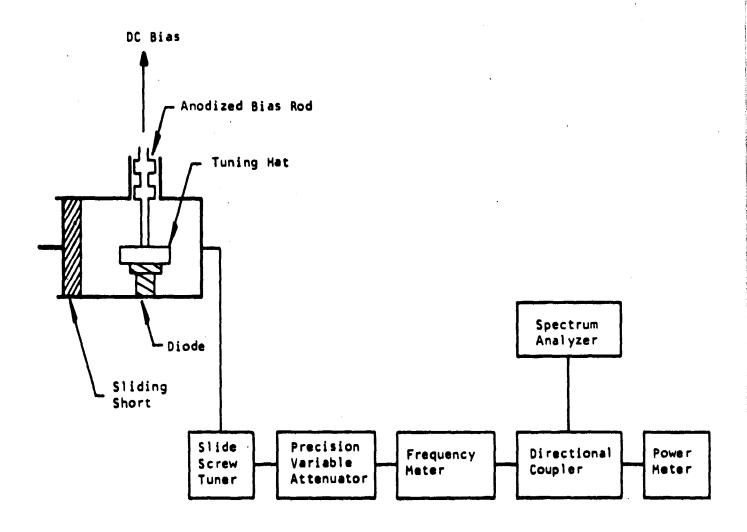

| 13     | Detail of Package Used for Testing in Waveguide Hat Circuit                           | 28   |

| 14     | Ku-Band Waveguide Test Circuit                                                        | 29   |

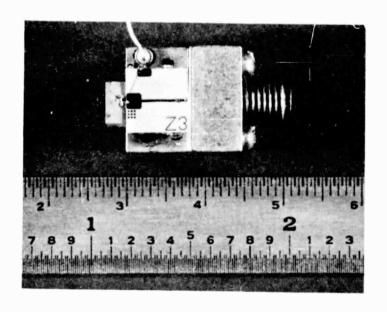

| 15     | IMPATT Microstrip Oscillator Test Fixture                                             | 33   |

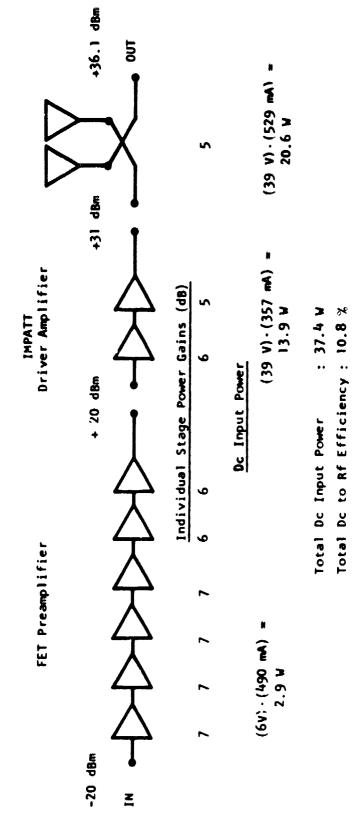

| 16 .   | Block Diagram of Spacecraft Transmitter Amplifier                                     | 36   |

| 17     | FET Mounting Scheme to Reduce Parasitic Losses                                        | 41   |

|        |                                                                                       |      |

# LIST OF ILLUSTRATIONS

(continued)

| FIGURE |                                                                                                              | PAGE |

|--------|--------------------------------------------------------------------------------------------------------------|------|

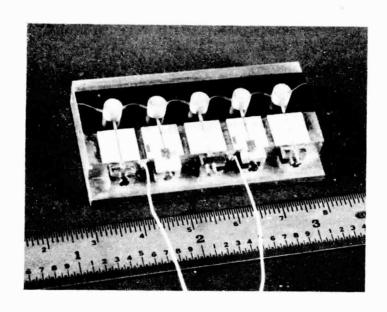

| 18     | Single and Multistage 15 GHz FET Breadboard Amplifiers                                                       | 42   |

| 19     | Gain Compression Curve For 15 GHz Preamplifiers                                                              | 43   |

| 20     | Six-Stage FET Preamplifier Ready for Testing                                                                 | 45   |

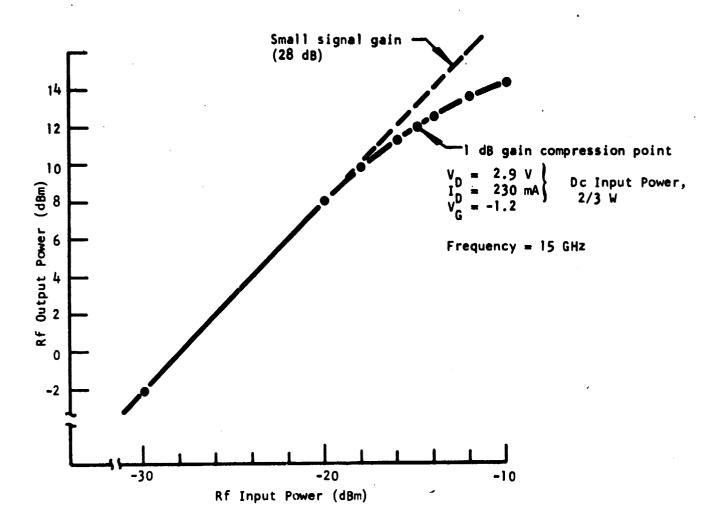

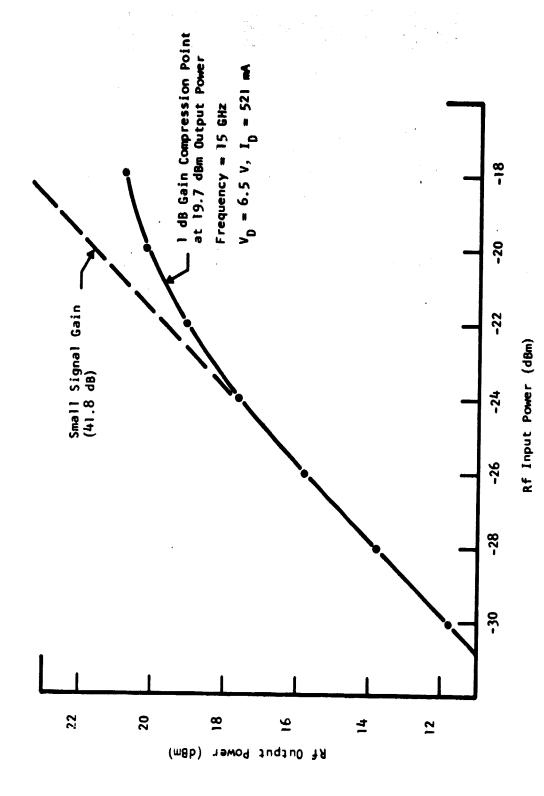

| 21     | Gain Compression Characteristic for 15 GHz Six-Stage Preamplifier                                            | 46   |

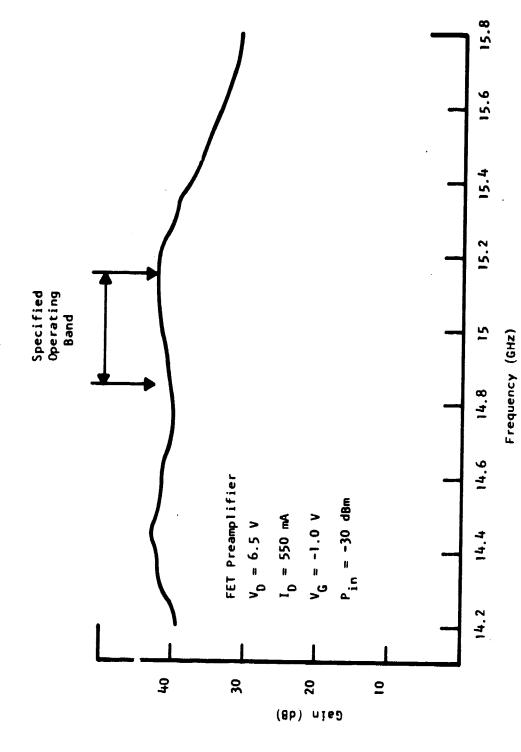

| 22     | Gain versus Frequency Characteristic for 15 GHz Six-Stage Preamplifier                                       | 47   |

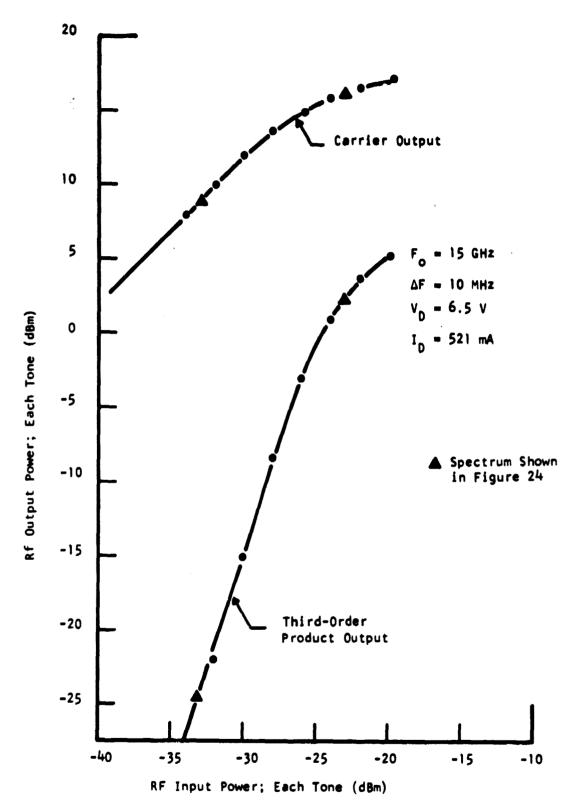

| 23     | Third-Order Intermodulation Product vs Input Level at Band Center of the Six-Stage FET Preamplifier          | 48   |

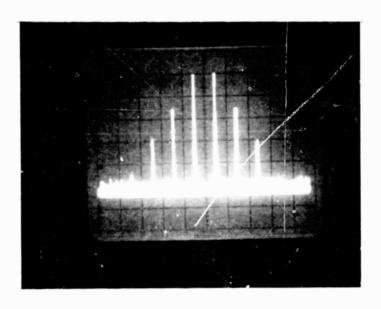

| 24     | Spectrum Analyzer Display of FET Preamplifier Output                                                         | 50   |

| 25     | IMPATT Driver Amplitier Chassis                                                                              | 51   |

| 26     | Preamplifier, Driver, and Balanced Power Amplifier Chassis                                                   | 56   |

| 27     | Estimated Balanced Power Stage Performance                                                                   | 58   |

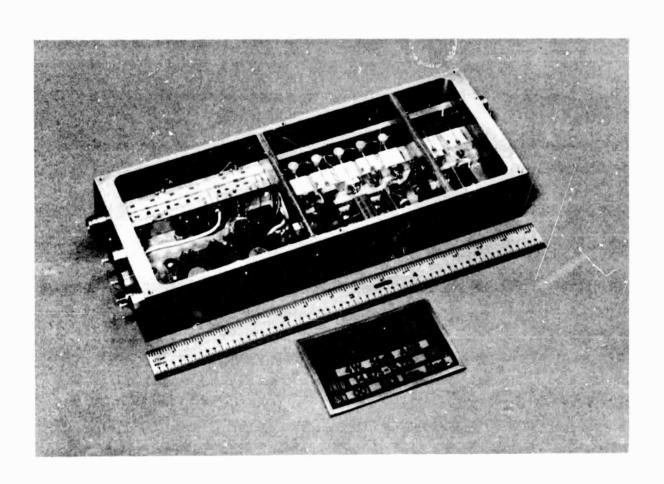

| 28     | Integrated Spacecraft Transmitter Amplifier                                                                  | 61   |

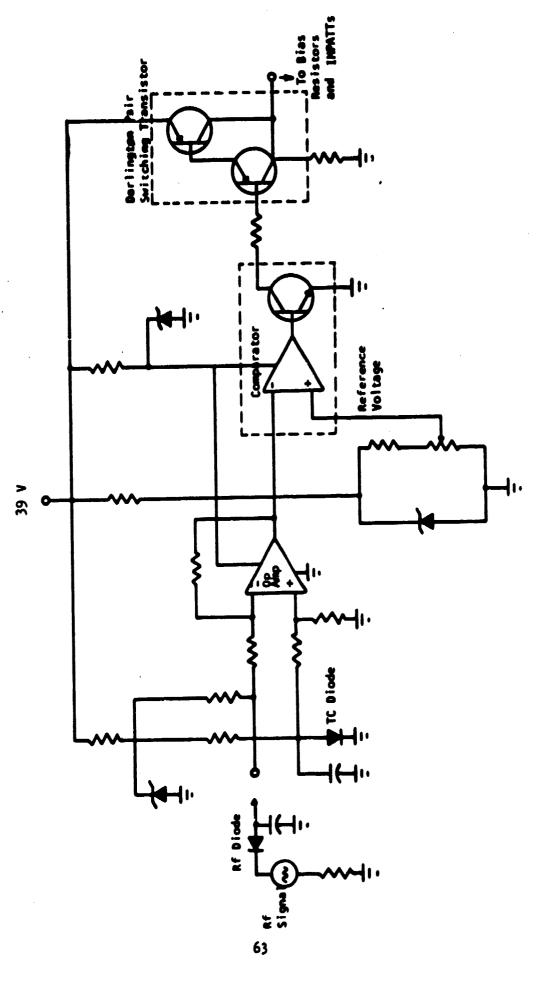

| 29     | Automatic Shutdown Circuit and Detector Diode Temperature Compensation Circuit for NASA Amplifier            | 63   |

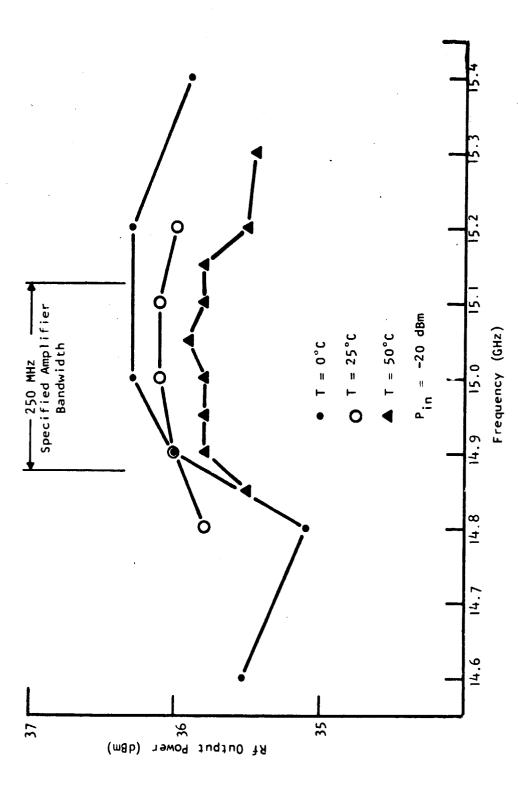

| 30     | Output Power vs Frequency Characteristic For 4 W Amplifier for Baseplate Temperatures of 0°C, 25°C, and 50°C | 65   |

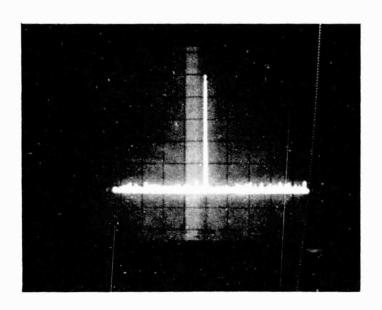

| 31     | Spacecraft Transmitter Amplifier Output Spectrum at 50°C<br>Baseplate Temperature                            | 67   |

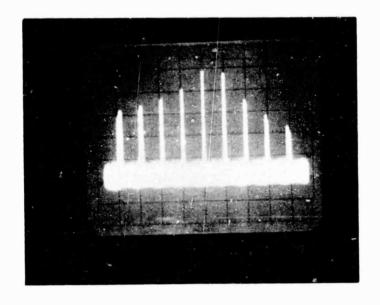

| 32     | Spectrum Analyzer Display of 4 W Amplifier Output                                                            | 68   |

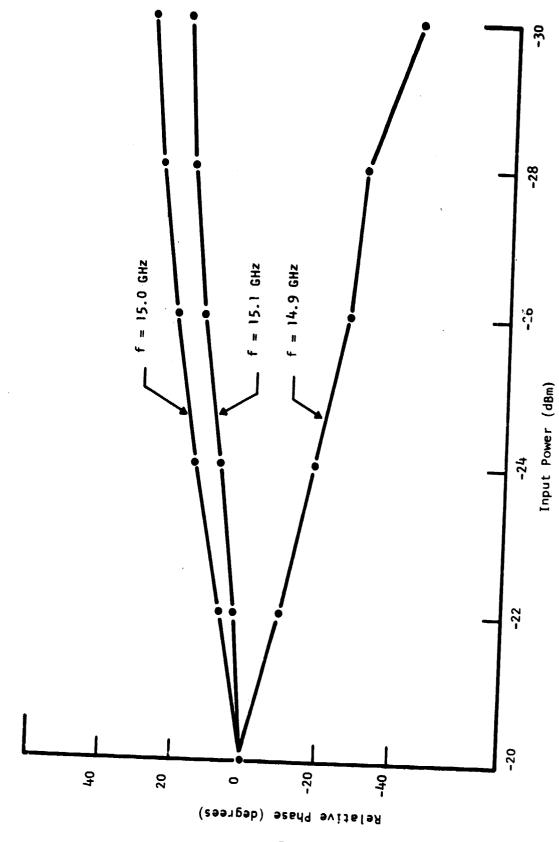

| 33     | AM-to-PM Conversion Characteristics for Spacecraft Transmitter Amplifier                                     | 70   |

| 34     | Thermal Circuit Model for Thermal Impedance Calculation                                                      | 75   |

| 35     | Idealized Reverse Bias Characteristics of an IMPATT                                                          | 77   |

| 36     | Results of Bias-Temperature Stress Under Non-Oscillating Conditions                                          | 86   |

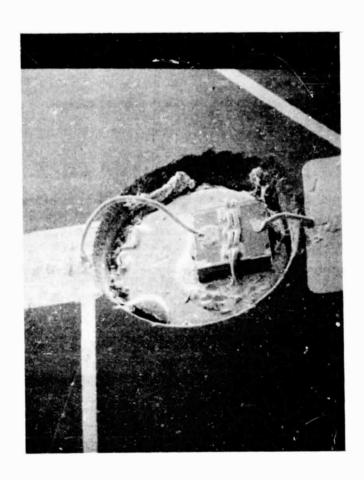

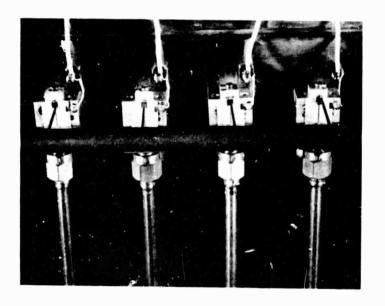

| 37     | Photographs of RF Life-Test Station                                                                          | 87   |

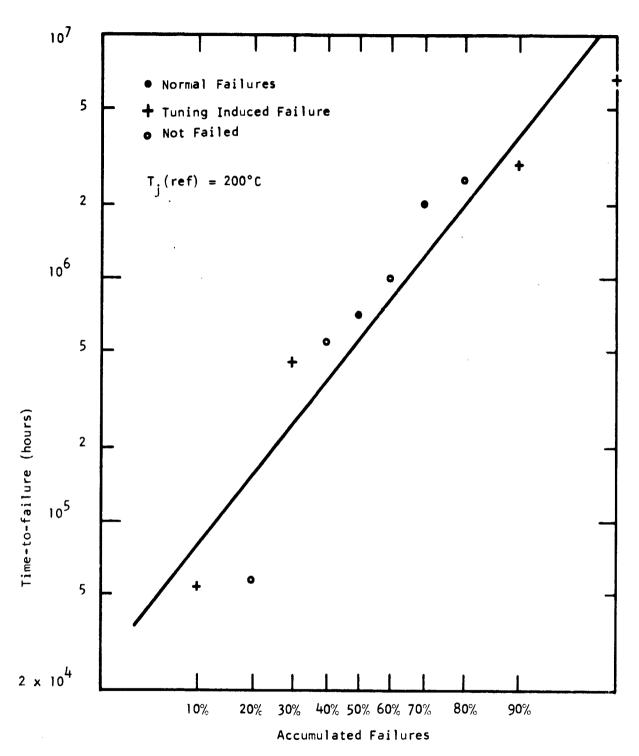

| 38     | Results of Rf Bias-Temperature Stress Life Test                                                              | 97   |

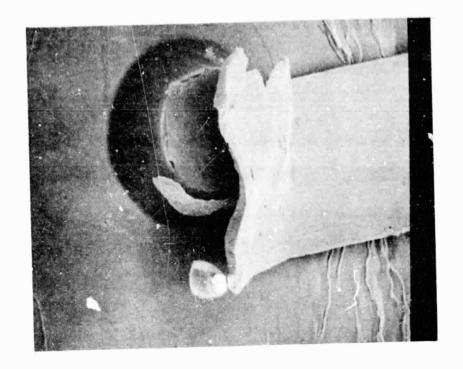

| 39     | SEM Photographs of Failed Oscillator IMPATTs                                                                 | 98   |

## SECTION I INTRODUCTION AND SUMMARY

This report presents the results of work performed under Contract No. NASS-24182 to develop a Ku-band Solid State Spacecraft Transmitter. Under a previous two-year NASA contract, NAS5-20894, a breadboard version of an all-IMPATT spacecraft transmitter was developed. The accomplishments made during the earlier program formed part of the technology base for the next phase of development under the current contract. The principal difference in the programs under the two contracts is that under Contract NASS-24182 the center operating frequency was shifted from 13.525 GHz to 15.085 GHz, and increased emphasis was placed on transmitter reliability. The program goal was to achieve an operating lifetime of five years. In response to these new requirement qoals and to the need for further transmitter performance improvement, significant changes in both device and circuit design were implemented during the development of the transmitter amplifier delivered to NASA under the current contract. These included: (1) implementation of high power, high efficiency, and high reliability GaAs Schottky-Read IMPATTs; (2) incorporation of a six-stage FET preamplifier; (3) incorporation of a two-way power combiner in the final power output stage; and (4) more complete microstrip circuit integration of preamplifier, driver, and power amplifier chassis, resulting in substantial transmitter size reduction.

Table 1 shows the performance requirements as specified at the beginning of the contract. Two of the requirements were later modified with the consent of the NASA contract monitor. First, the restriction of having the amplifier powered from an unregulated 28 V power supply was removed, and instead it was decided to establish the bias requirements during the course of the amplifier development. Second, OSM connectors rather than waveguide signal connectors were used in the delivered amplifier.

Key accomplishments and progress made toward the achievement of the performance goals include the following:

#### Table I

#### Performance Requirements

63 dB min

15. 085 GHz Center Frequency:

250 MHz Bandwidth (1 dB):

± 0.4 dB max Bandpass Ripple:

Gain: (Threshold to - 30 dBm) (- 20 dBm) 57 dB min

> < 0.2 dB/10 MHz (Rate of Change)

28 ± 1 V dc unregulated Voltage Available:

Overall Amplifier Efficiency (including power supply interface): 10% min

All intermodulation products generated Intermodulation:

by two - 33 dBm cw signals separated by 10 MHz at any frequency in the passband must be no greater than + 18 dBm at the amplifier output when operating

in the normal full gain condition.

$0^{\circ}C$  to  $+50^{\circ}C$ Operating Temperature Range:

Operaing Lifetime: 5 years

< - 20 dBm for input signals Spurious Output Radiation:

< - 20 dBm or absence thereof

Cooling: Conducting heat sink only

1000 cm<sup>3</sup> Total Volume:

Waveguide Signal Connectors:

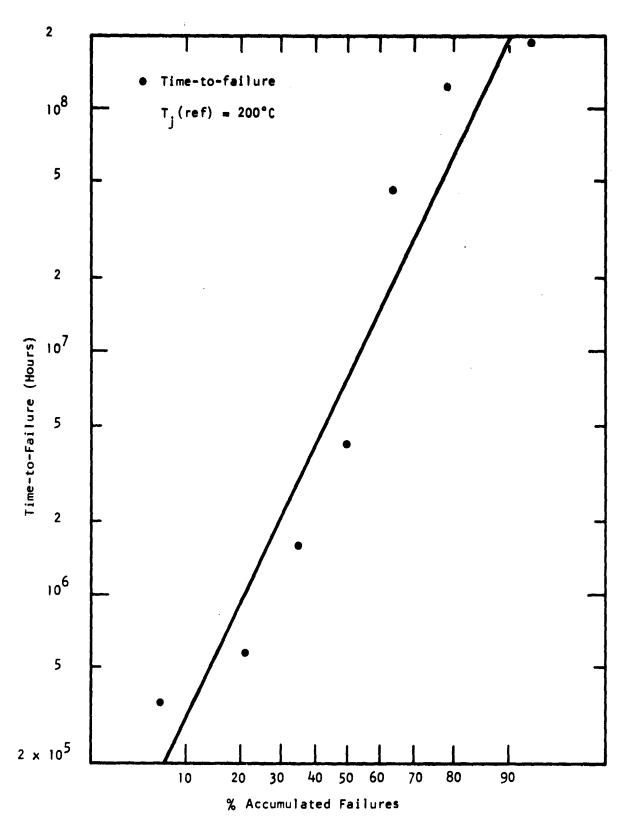

- Development and fabrication of high power Schottky-Read IMPATTs with low-high-low doping profiles incorporating titanium tungsten barrier metallization in the Schottky junction for high reliability. Output powers of up to 2 W with dc-rf conversion efficiencies of 23% have been obtained for single-mesa diodes operating at 15.7 GHz as free-running oscillators in waveguide. For these devices an extrapolated mean time to failure (MTTF) of greater than 5 x 10<sup>5</sup> hours (as determined from extensive life testing) is obtained for typical junction operating temperatures of 200°C.

- Development of a six-stage FET preamplifier with a 1 dB gain compression point of 20 dBm and a linear gain of 41 dB at 15 GHz. An output third-order intermodulation intercept point of 25 dBm was achieved with this amplifier.

- Development of a balanced power output stage incorporating two single-mesa IMPATTs yielding an output power of 4.2 W, with 52 dB gain and an intrinsic power-added efficiency (i.e., excluding bias distribution circuits) of 15.7%.

- Delivery of an all-solid-state, 4.1 W, 56 dB gain, 15 GHz amplifier with an overall dc-to-rf efficiency of 10.8%. The amplifier has greater than a 250 MHz 1 dB bandwidth, operates over the 0° to 50°C (base plate) temperature range with less than 0.5 dB change in the power output, weighs 444 grams, and has a volume of 220 cm<sup>3</sup>.

Although the 5 W power output goal was not achieved, it is considered that the realization of a 4 W amplifier using proven high reliability, high efficiency GaAs diodes is indeed a significant accomplishment. It demonstrates the development of an essentially laboratory experimental device into one that is feasible for use in an important engineering application.

The remainder of this report is organized as follows. Device design and materials growth are discussed in Section II. Amplifier design and development are covered in Section III. The results of the IMPATT device reliability studies are presented in Section IV. Section V discusses conclusions drawn from the results of the work carried out during the course of the program, as well as recommendations for future work.

# SECTION II KU-BAND IMPATT DEVELOPMENT

In this section we describe low-high-low GaAs IMPATT device design, GaAs epitaxial growth, the IMPATT fabrication process, the device rf performance in a waveguide cavity, and the device rf performance in microstrip.

#### A. <u>Device Design</u>

GaAs IMPATTs with low-high-low (LHL) and high-low (HL) impurity profiles have been shown to have the potential for high efficiency operation because of a shortened avalanche region. However, the LHL structure has a lower surface field than the HL structure and therefore a lower field emission (tunneling) current component. Since the field emission current component is not in proper phase relationship with the rf voltage, the LHL structure potentially has higher efficiency than the HL structure. Accordingly, all our efforts in this program were focussed on optimization of the LHL structure.

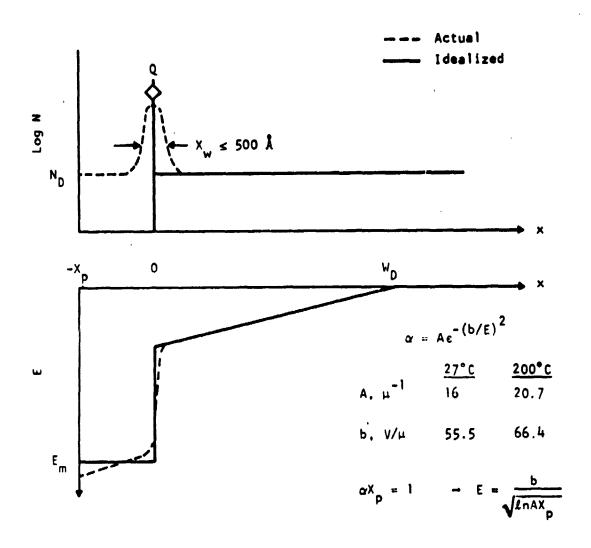

In the design of LHL Read diodes, three parameters are of primary importance to the device designer: (a) the drift doping,  $N_D$ ; (b) the charge in the pulse clump, Q; and (c) the distance from the Schottky barrier interface to the pulse clump peak,  $X_D$ . Provided the half-width of the pulse clump,  $X_W$ , is less than 1/3  $X_D$ , then the physical device can be idealized as shown in Figure 1. Using this model, together with the relationship between the ionization coefficient,  $\alpha$ , and electric field, E, it is possible to calculate breakdown voltage, depletion width, and efficiency for the device. A series of nomographs for various  $N_D$ , with Q as parameter, has been constructed; a typical example is shown in Figure 2.

These nomographs are calculated using the following material parameters:

(a) GaAs dielectric constant,  $\epsilon_r = 12.4$  (Reference 1)

Figure 1 Idealized Low-High-Low Structure

Figure 2 Calculated Intrinsic Efficiency of GaAs LHL Using Idealized Structure

(b) Saturated drift velocity at 200°C,

$$v_0 = 6.88 \times 10^6$$

cm/sec (Reference 2)

(c)

$$\int_{\alpha}^{0} dx = 1$$

$$= X_{p}$$

(d)

$$\alpha = AE^{-(b/E)^{2}}$$

(Reference 3)

where the values for A and b employed are shown in Figure 1.

(e) The efficiency, T, is computed by the equation

$$\pi = \frac{1}{\pi} \frac{V_d}{V_a + V_d} \frac{\sin \left[ (\pi/2) \left( \frac{W_D}{W_D} \right) \cos t \right]}{W_D/W_D \cot t}, \tag{1}$$

where  $V_d$  is the voltage across the drift region,  $V_a$  is the voltage across the avalanche region,  $W_D$  opt  $= \frac{V_O}{2f}$ , and f is the frequency.

This equation reduces to Read's equation when  $W_D = W_{D\ opt}$ . The sin term in the numerator results from the Fourier series analysis of a rectangular pulse train when the pulse width is varied; the term in the denominator results from dc current considerations. Further, as is conventional, Equation (1) assumes 50% voltage modulation.

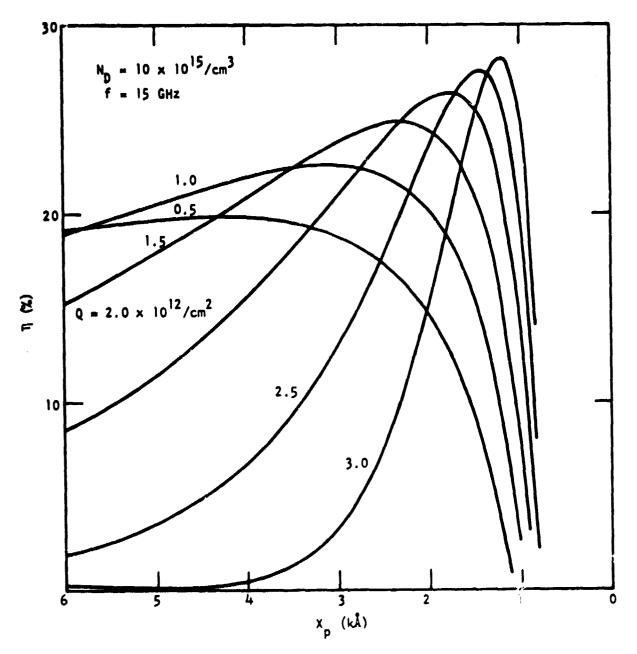

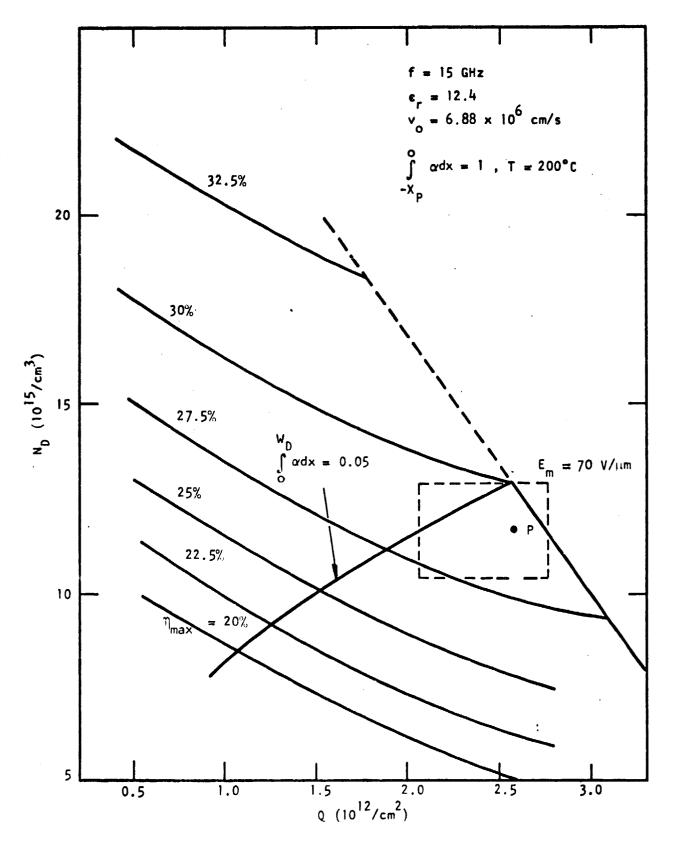

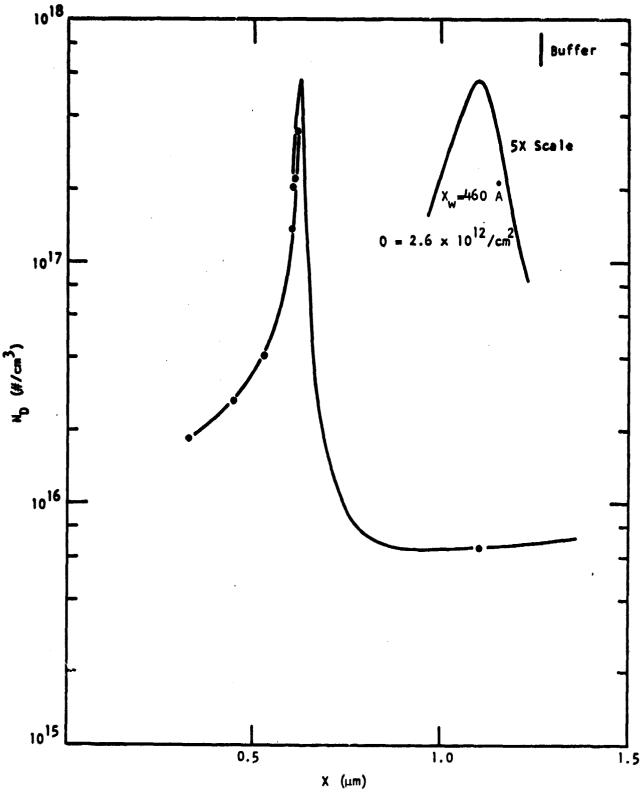

Associated with each curve in Figure 2 is a value of  $X_p$ ,  $X_{p \text{ opt}}$ , at which the efficiency is a maximum,  $\eta_{max}$ . These nomographs are then used to generate a plot of  $\eta_{max}$  vs Q with N<sub>D</sub> as a parameter, from which Figure 3 is obtained. This figure identifies the appropriate range of values for N<sub>D</sub> and Q for high efficiency operation.

Two additional constraints must be imposed: (a) the maximum field must not exceed  $\sim 70 \text{ V/}\mu\text{m}$  in order to avoid a significant tunneling current component.

Figure 3  $\eta_{\text{max}}$  Dependence on Q and  $N_{\text{D}}$  when  $X_{\text{P}} = X_{\text{P}}$  opt

This defines the right-hand bound of the design window. (b) The ionization integral in the drift space must be < 5%. Accordingly, the left-hand bound of the design window is defined by

$$\int_0^{W_D} \alpha dx = 0.05.$$

If point P is defined as  $N_D$  (P) = 0.9  $N_D$  apex, then the optimum Ku-band window results as:

$$N_D = 11.6 \times 10^{15}/\text{cm}^3 \pm 10\%$$

$Q = 2.57 \times 10^{12}/\text{cm}^2 + 7\%$

It should be noted that this window is essentially unchanged under any reasonable choice of saturation drift velocity, length of drift space, and/or ionization integral value over the avalance zone. In fact, any reasonable choice will result in a change in point P which is  $<\pm3\%$  on Q and  $<\pm5.5\%$  on N<sub>D</sub>. The only parameter that significantly affects the location of the window is  $\varepsilon_r = 10.9$ ; this value of  $\varepsilon_r$  will reduce both N<sub>D</sub> and Q by  $\sim$  13% over that depicted in Figure 3.

Three further observations with respect to Figure 3 should be made. First, the figure should be viewed as a three-dimensional plot. Its shape is that of a steep hill whose gradient decreases as the left and right boundaries are approached; the gradient becomes negative somewhere in the vicinity of these boundaries and is probably followed by a relatively steep drop. Second, the efficiencies shown are intrinsic device efficiencies that would be observed only in loss-less systems. Consideration of skin depth, operating voltage and current, cavity dimensions, and the reactive energy circulating in the cavity indicate that cavity losses vary between  $f^{5/2}$  and  $f^{7/2}$ . The observed efficiency,  $\eta_{o}$ , is

$$\eta_o = \eta_{intrinsic} (1 - \kappa_c)$$

,

where  $K_c$  is the percent cavity loss (expressed in decimal units). Using low limit estimates of  $K_c$  of 0.015 - 0.025 at 10 GHz,  $K_c$  values of 0.060 to 0.165 are obtained at 15 GHz. These two items considered together therefore imply that the maximum observable efficiency possible in the Ku-band will be in the 23 to 26% range. Finally, the values of  $X_p$  opt and  $\Delta X_p$  opt (defined as the allowable variation in  $X_p$  opt wherein the intrinsic efficiency is reduced by 1%) for the indicated design window are:

| Upper right-        | hand corner | Lower left-hand corner |  |  |  |

|---------------------|-------------|------------------------|--|--|--|

| X <sub>p opt</sub>  | 1150 A      | 1700 A                 |  |  |  |

| Δχ <sub>p opt</sub> | ±160 Å      | ±330 Å                 |  |  |  |

It is the achievement of  $\mathbf{X}_{p}$  opt to within the tight tolerance required that makes this device particularly difficult to fabricate.

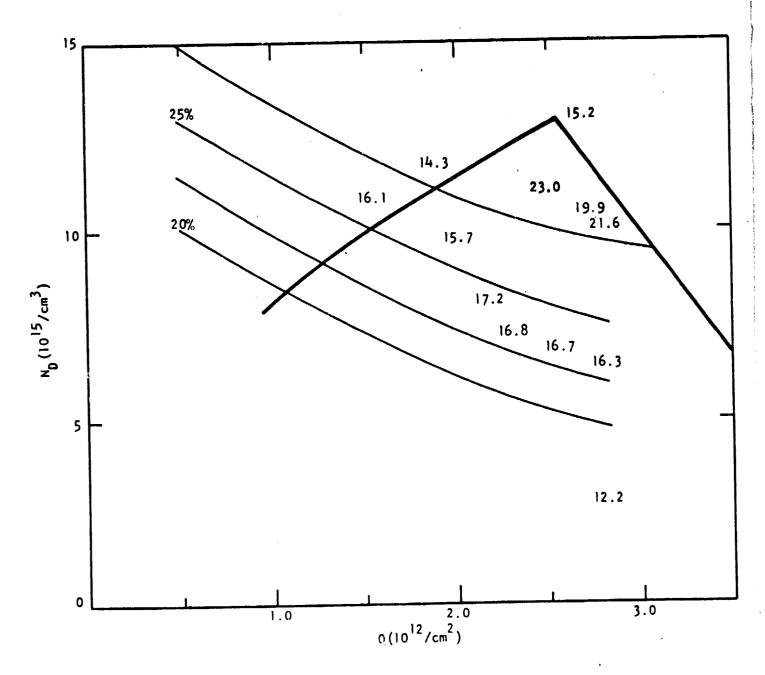

To confirm the validity of our GaAs LHL IMPATT model, the maximum efficiency achieved from various slices is superimposed on the design window as shown in Figure 4. These results are for slices processed since June 1977 for which X p is close to its optimum value. Even though there are uncertainties associated with the profiler measurements, variation of material parameters across the slice, and waveguide circuit optimization, it is clear that the experimental results indicate the model is of reasonable utility for LHL IMPATT design.

#### B. GaAs Epitaxial Growth

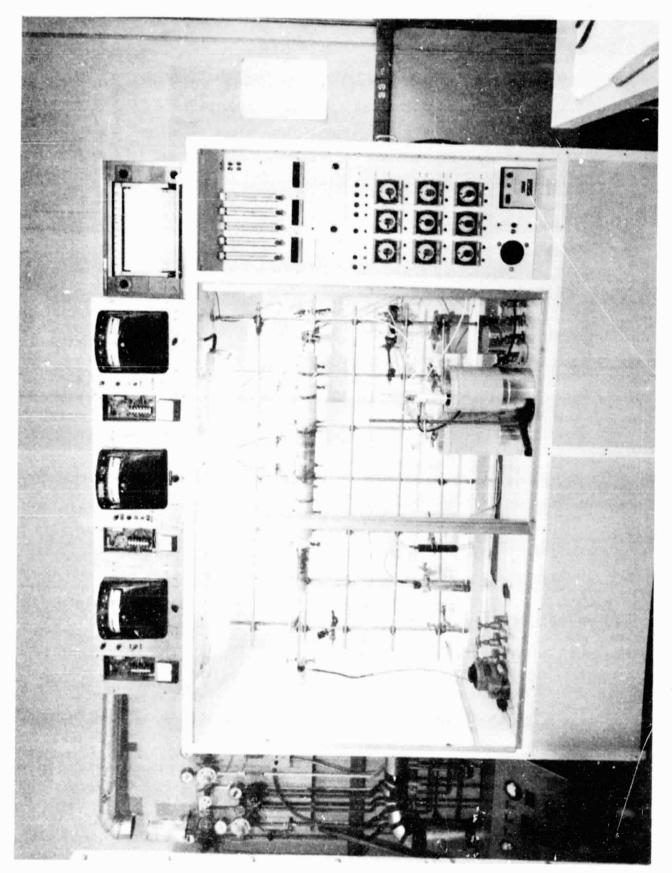

The GaAs Read structures were grown by vapor phase epitaxy, using the well-established Ga-AsCl<sub>3</sub>-H<sub>2</sub> process. Microwave device material is routinely produced by this technique at Texas Instruments. From the start of this program, the emphasis was placed on growing high-low-high structures having material parameters defined by the window described in Section II.A. Figure 5 shows the reactor system.

Figure 4 Maximum Efficiency Achieved from Various Slices

Figure 5 Epitaxial Growth System with Sliding Substrate Reactor

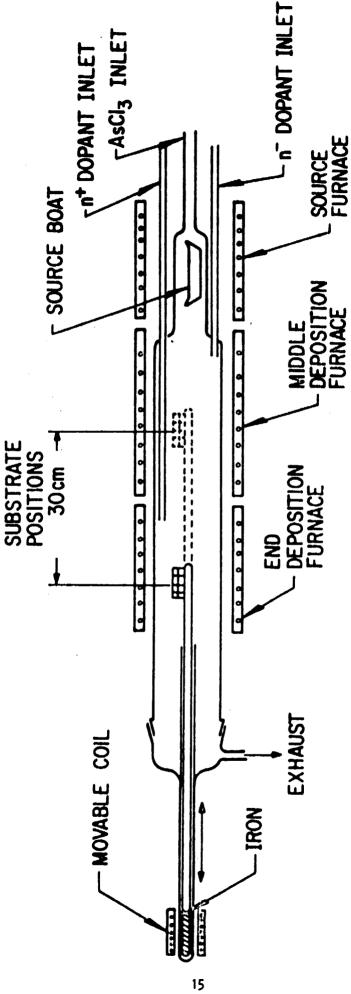

Because of the toxicity of the arsenic compounds, the reactor is mounted in a well-ventilated hood. The gas flow and the temperature cycles are controlled by electric clocks. Details of the reactor design are depicted in Figure 6.

The horizontal reactor exhibits two growth zones. In the upstream growth zone the doping concentration is controlled by the doping gas concentration entering the zone via the  $n^-$  dopant inlet. Higher carrier concentration is obtained in the downstream growth zone which is controlled via the  $n^+$  dopant inlet.

The LHL material requirements call for the following structure, starting from a high quality, high conductivity GaAs substrate:

- Buffer layer: doped 5 x  $10^{17}$  to  $10^{18}$  cm<sup>-3</sup>, about 5  $\mu$ m thick

- Drift layer, doped 7 x 10  $^{16}$  to 1.3 x 10  $^{17}$  cm  $^{-3}$ , 2.5  $\mu m$  to 4.0  $\mu m$  thick.

- A doping pulse with a halfwidth < 500 Å, containing a charge of 2.0 to 2.6 x  $10^{12}/\text{cm}^2$ . Good device performance was obtained with doping pulses having a peak doping of 5 x  $10^{17}$  cm<sup>-3</sup> and a halfwidth of 300 Å.

- $\bullet$  A surface layer, greater than 1500 Å thick, with the same doping level as the drift layer.

A complete doping profile is presented in the next section (Figure 8).

To extend the capabilities of the epitaxial growth system to pulse doping, an additional doping line had to be incorporated. With the help of a gas injection valve, such as that used for gas chromatography, a small volume, 0.5 cc, of high

Schematic Diagram of Sliding Substrate, Abrupt Junction Epitaxial Reactor Figure 6

concentration doping gas can be injected into the gas that enters the reactor through the n dopant line. The growth sequence for the complete LHL structure was then as follows:

- (1) Growth of the buffer layer in the downstream n+ zone.

- (2) Moving of the slice into the n zone and growth of the drift layer.

- (3) Injection of doping pulse.

- (4) Continuation of growth until desired n surface layer thickness was achieved.

Evaluation of the grown epitaxial structures included thickness measurements by cleaving, staining, microscopic examination of the cross section, and C-V profiling after application of gold Schottky barriers.

#### C. Device Fabrication Process

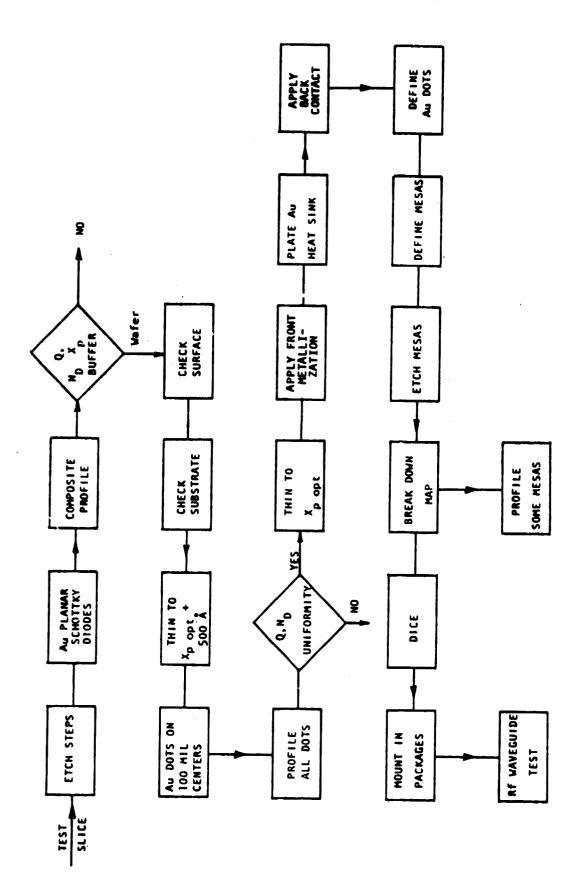

The fabrication process flow chart is shown in Figure 7. In brief, it consists of three parts. First, the material is characterized to determine whether its parameters are such that high efficiency devices can reasonably be expected. Second, the slice is processed to determine whether Q,  $N_D$ , and  $X_p$  are of sufficient uniformity. Finally, the slices that pass all acceptance criteria are processed to completion.

#### 1. Test Slice Characterization

A  $\sim$  3 x 20 mm test slice is cleaved off the  $\sim$  13 x 20 mm wafer for slice characterization. This test slice is always cleaved off the wafer from the bottom (referring the slice orientation during VPE growth); experience has shown that this piece accurately reflects the material parameters of the slice committed to device fabrication. The test slice is step-etched so that the first two steps etch into the substrate and buffer, respectively; the last steps, 10 to

Figure 7 Low-High-Low IMPATT Device Fabrication Flow Chart

15 in number, successively remove 500 to 1000 Å from the surface. Circular Au planar Schottky diodes are formed on the step-etched surface via standard photolithography and electroplating, together with a uniform Au contact layer on the back surface. The profile is then obtained with an analog impurity profiler. A typical example is shown in Figure 8. This profile is a composite obtained from information from many diodes on the test slice.

To ensure accuracy in the material characterization, a second operator obtains further data from the test slice. These data consist of determining (a) the accurate value of  $X_p$ , (b) the maximum value of the  $X_p$  that permits profiling over the clump and into the drift region, (c) the value of Q measured for a number of diodes, and (d) the slope of  $N_p$  so that the effective drift doping can be ascertained. (d)

Our estimates of Q, effective  $N_D$ , and  $X_p$  are determined from these data. Calibration of our analog impurity profiler against a digital profiler indicates an accuracy of  $\pm 15\%$ . In addition, experience has shown that a typical good slice will exhibit the following variations over its area:

$$N_d \pm 10\%$$

, Q ± 10%,  $X_p \pm 300 \text{ Å}$ .

These uncertainties make it difficult to precisely ascertain material parameters. Consequently, all slices that have parameters within  $\pm 30\%$  of point P, as defined in Figure 3, are accepted for further processing; about 15% of the slices grown fulfill this acceptance criterion.

$<sup>\</sup>star$  This is usually a reliable indicator of the quality of a slice; good device performance has frequently been obtained when this value is in the 1500 to 2400 Å range, provided that N $_{\rm D}$  is near its optimum value.

$<sup>\</sup>dot{\tau}$  Typically, the drift doping increases toward the buffer with a slope of 10 to 50% per micrometer. Sufficient data are not available at present to correlate device performance and N<sub>n</sub> slope.

Figure 8 Composite Profile Obtained from Step-Etched Test Slice

#### 2. Slice Uniformity Characterization

This procedure is employed to determine material parameter uniformity across the slice and to thin the wafer to the vicinity of  $X_{p}$  opt. In addition, the slice surface and substrate qualities are inspected. Typically, the 1 x 2 cm slice is cleaved in two, with one part held in reserve for use if some processing failure should occur.

#### a. Surface Quality

The sample is inspected under a microscope. A mirror-like finish with only a few discernible features over 70% of the sample's surface is acceptable. Samples with scaly or haze finishes, or with many pits, are rejected.

The reason for this inspection is clarified by Figure 9, which shows the normalized breakdown voltage as a function of junction curvature. Since Ku-band diodes have  $W_D=2~\mu m$ , a pit with a spherical curvature of 1  $\mu m$  will have a breakdown of 50% that of the surrounding area. Defects of this type, which are practically unavoidable, can be tolerated provided their aggregate area is < 1% of the total device area. This is because the current-carrying capability of the defects is thermally limited; thus, the out-of-phase current carried by the defects is only a small part ( $\sim$  2%) of the total diode current so that the efficiency of the device is not seriously degraded. The size and number of these defects are manifested by the sharpness or lack of sharpness of the diode's reverse characteristic; obviously, sharp breakdowns are preferable. Experience has shown that when the VPE reactor is leak-free, more than 80% of the slices pass this inspection.

#### b. Substrate Evaluation

Substrate evaluation is accomplished simply by removing  $\sim 6 \, \mu m$  from the back surface of the slice and anodically oxidizing the substrate at 40 V while protecting the epitaxial front surface. A uniform purple-colored oxide should result, indicating a substrate with a high doping concentration; otherwise, the slice is rejected. More than 90% of the slices pass this test.

Figure 9 Normalized Breakdown as a Function of Junction Curvature

#### c. Anodic Thinning for Uniformity Evaluation

Using the material parameters obtained from the test slice, a plot of both the breakdown voltage and the efficiency as a function of  $X_p$  is generated via a computer. The difference between  $X_p$  opt as obtained from the plot and the measured value of  $X_p$  from the test slice determines the amount of thinning required. The thinning is then scheduled to obtain  $X_p$  opt + 500 Å for uniformity evaluation.

Thinning is accomplished by anodic oxidation<sup>5</sup> by alternately growing and stripping the oxide. Careful attention is paid to oxide color uniformity; thinning is terminated before the scheduled point if the oxide becomes nonuniform.

#### d. Uniformity Evaluation

Circular planar Au Schottky barrier diodes are formed on 2.54 mm (100 mil) centers on the slice via standard photolithography and electroplating, together with a uniform Au contact layer on the back surface. All diodes of the typically  $4\times4$  matrix are profiled to determine both the quality of the test slice data and the uniformity of the material parameters. In most cases (>70%), all the test slice material parameters are confirmed to within  $\pm20\%$ ; a new computer efficiency plot is generated to determine  $X_p$  opt using these new material parameters. Variations of material parameters across a typical good slice were noted earlier in Section II.C.1; slices with greater variation are usually processed, provided that high efficiency devices can be expected from >25% of the slice area. About 70% of the slices reaching this stage are committed for final processing.

#### 3. Final Processing

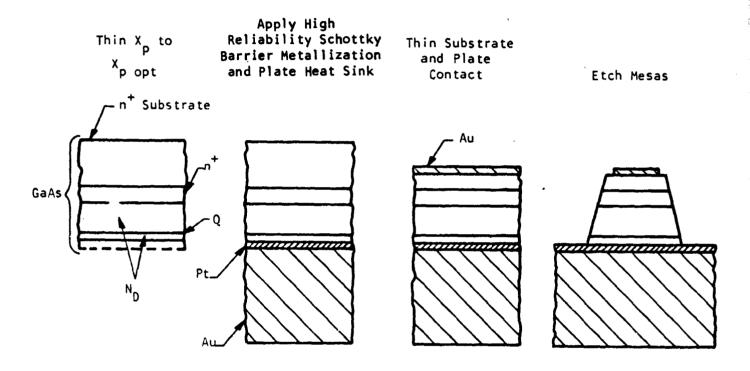

The Au dots are etched off with a minimum of GaAs removal (estimated as <100 Å). The slice is given a final thinning to obtain  $X_p = X_p$  via anodic oxidation. The remainder of the fabrication procedure employs the standard TI

IMPATT process whose main features are illustrated in Figure 10. After final thinning, a high reliability metallization system is applied to the front (junction) side, consisting of 400 Å  $\pm$  100 Å Pt/2250 Å  $\pm$  250 Å TiW (90% W by weight)/1000 Å  $\pm$  200 Å Pt. The metallization system is serially deposited by sputtering in one pumpdown after a brief sputter etch of the GaAs surface. This metallization system is employed because the reaction of a Pt/GaAs interface is known to proceed fairly rapidly, thereby degrading the reliability and performance of high-efficiency, Read-type, Schottky barrier GaAs IMPATTs. By employing a thin Pt layer for Schottky barrier formation, followed by a barrier layer, the deleterious Pt/GaAs reaction is terminated when the Pt is consumed. The final 1000 Å Pt layer is included to protect the barrier layer from the atmosphere upon exposure.

After front-side metallization, a 0.25 mm (10 mil) thick gold heat sink is electroplated onto the Pt. Next, the substrate is thinned by lapping and etching to  $\sim 25~\mu m$ , and a Au/Ge ohmic back contact is evaporated, followed by an additional 1 to 2  $\mu m$  of plated Au. After mesa etch, the ohmic contacts are alloyed at  $460^{\circ}\text{C}$  for 1 minute in a He atmosphere. These ohmic back contacts are employed to counteract possible unreliability due to current crowding and thermal runaway. Mesas are then defined and etched using standard lithographic techniques; typical mesa diameters for Ku-band applications are 125  $\mu m$ . The heat sink is  $\sim 0.50~\text{mm}$  (20 mils) square after sawing. The final step in device fabrication is lapping of the gold heat sink to a smooth finish that will ensure good wetting of the solder between the heat sink and the bonding pedestal of the package.

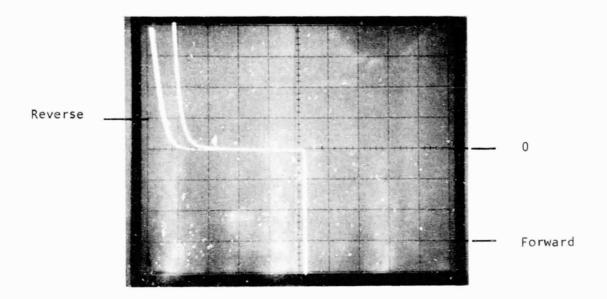

Before the slice is diced, a breakdown voltage map of the slice is obtained. A typical map for a slice that exhibited good uniformity during profiling is shown in Figure 11. The voltage reading is that obtained at a reverse current of 10 mA; diode spacing is on 0.50 mm (20 mil) centers. A typical breakdown characteristic of a diode from this slice is shown in Figure 12. Such characteristics are frequently obtained from slices with good surfaces.

Figure 10 Procedure for Fabricating GaAs Low-High-Low IMPATT Diodes

| X    | X  | 21 | 25 | 27 | 27 | 28  | 14 | X  |

|------|----|----|----|----|----|-----|----|----|

| X    | 20 | 24 | x  | 28 | 27 | 2.7 | 28 | 28 |

| 21   | 16 | 25 | 28 | 29 | 25 | 28  | x  | 28 |

| 20   | 26 | 30 | 31 | 33 | 34 | X   | 33 | 34 |

| . 16 | 21 | 26 | 26 | 27 | 27 | 27  | 28 | 27 |

| 15   | 19 | 22 | 23 | 24 | 25 | 25  | 24 | 23 |

| X    | 17 | 19 | 21 | 21 | 22 | 22  | 19 | 20 |

Figure 11 Voltage Map of a Slice Exhibiting Good Uniformity

V = 1 and 10 mA/div H = 5 V/div

Figure 12 Breakdown Characteristics of a Diode from a Slice with a Good Surface

ORIGINAL PAGE IS OF POOR QUALITY

Profiling of mesas at this stage met with very limited success. The mask set was designed to create 0.23 mm (9 mil) diameter profiling mesas located on 2 mm (80 mil) centers. (These mesas are located at heat sink edges and are destroyed during dicing.) For profiling, these mesas must be made ohmic. The application of solder at  $\sim 300^{\circ}\text{C}$  to these mesas usually makes them leaky so that proper profiling cannot be accomplished. Usually, only information concerning the value of  $X_D$  could be obtained.

After dicing, mesas with the proper breakdown voltage are mounted in microwave packages for testing in the waveguide hat circuit. This package is illustrated in Figure 13. Diodes are soldered into the package by flowing a eutectic Au-Sn solder preform onto the package pedestal and placing the heat sink on the wetted solder pool under gentle pressure. The solder is then frozen, and the unit becomes securely bonded to the package. The mesa top is connected to the package flange with a crossed 0.13 mm (5 mil) Au ribbon; wire mesh straps have also been employed. Tailoring of mesa area with a high-speed jet etch can be done with either arrangement.

The yield obtained in final processing is > 80%. Yield losses are generally due to problems encountered during plating, which result in poor interfaces and therefore in devices with high thermal impedance.

#### D. Device Waveguide Performance

Packaged diodes are tested in the waveguide hat circuit shown in Figure 14. Bias is supplied from a constant voltage source through a  $100 \, \Omega$  resistor. Bias is increased to  $10 \, \text{mA}$  and the bias voltage recorded; this voltage is referred to as the breakdown voltage. The bias is increased to  $\sim 150 \, \text{mA}$ , and the diode is tuned for maximum output power; power, bias, and frequency are recorded. Bias current is then increased in  $\sim 25 \, \text{mA}$  increments, and the diode is retuned for maximum power. This process is continued until a maximum in efficiency or power is achieved.

Figure 13 Detail of Package Used for Testing in Waveguide Hat Circuit

Figure 14 Ku-Band Waveguide Test Circuit

Best performance is obtained from a diode when the diode is held securely in position in the test circuit. This ensures good electrical contact between the package flange and the waveguide hat, as well as forcing intimate contact between the package screw threads and those in the heat sink; this minimizes the parasitics associated with those contacts. Further, the cavity is periodically cleaned and fresh Au electroplated as needed to ensure minimum cavity losses.

The optimum hat and diode position in the waveguide for Ku-band operation is determined by trial and error. Once these parameters are optimized, they are generally not changed; it is assumed that the configuration is near optimum for other LHL Ku-band diodes. The dimensions of the optimum hat for the Ku-band waveguide circuit used in this work are:

Diameter = 5.08 mm (200 mils) Height = 2.54 mm (100 mils).

Some representative waveguide circuit results for the LHL device lots are presented in Table 2; the rf performance data is that exhibited by the best device from the particular lot. Also included in the table are material parameters and breakdown voltage map reults. Except for the possible mix-up of slices 63 II and 64 II, high confidence is placed in the reliability of these data. The device lots shown represent 60% of the lots that have efficiency > 15%. The other 40% of the device lots processed either failed due to processing errors or were experimental slices (with material parameters considerably removed from the design window) intended to test the validity of the idealized model. These latter slices, as expected, exhibit efficiency < 10%.

It is highly likely that this mix-up did in fact occur, though proof of this is, of course, not available. Assuming that there was a mix-up, then the rf performance data of 64 II and 63 II should be interchanged.

Table 2

# Representative Wavequide Circuit Results

|    |        | Comments                             | Poor surface | Leaky breakdown    | Poor slice uniformity | Slice mix-up with<br>64 II may have occurred |              | Poor Pt/Au interrace,<br>low yield | High yield. Good slice uniformity |           |              |                          |

|----|--------|--------------------------------------|--------------|--------------------|-----------------------|----------------------------------------------|--------------|------------------------------------|-----------------------------------|-----------|--------------|--------------------------|

|    |        | Hardiness                            | Fair-Poor    | Fair               | Fair                  | Fair                                         | Very Good    | Poor                               | Fair-Good<br>Fair-Good            | Fair-Good | Fair-Good    | Excellent Excellent      |

|    | 4-     | (GHz)                                | 7.71<br>7.71 | 15.7<br>15.3       | 15.6<br>15.6          | 15.1<br>15.6                                 | 15.5         | 15.7                               | 15.0<br>15.0                      | 15.0      | 15.7<br>15.7 | 15.7                     |

|    | Prf    | 3                                    | 1.30         | 2.00               | 1.41                  | 2.50                                         | 1.60<br>2.25 | 1.50                               | 1.90                              | 2.60      | 0.82         | 1.8 <del>4</del><br>2.10 |

|    | F      | প্ত                                  | 16.7<br>16.3 | 16.0<br>14.5       | 15.2<br>14.4          | 17.2<br>16.6                                 | 19.9         | 2i.6<br>19.1                       | 21.0<br>20.4                      | 18.0      | 16.3         | 23.0<br>22.0             |

|    | BV     | <del>Na</del> p                      | 17-26        | 24-29              | 10-21                 | 19-31                                        | 24-29        | 15-21                              | 19-27                             | 17-30     | 32-43        | 14-30                    |

| ×° | Final  | €                                    | 1600-2400    | ~1350              | 1500-2500             | 1500-2100                                    | 1            | 1350-1850                          | 1500-1700                         | 1750-2250 | 2400-2700    | 2300-2900                |

|    | 9      | (10 <sup>12</sup> /cm <sup>2</sup> ) | 1.7-2.0      | 1.8-2.3            | 2.2                   | 2.1-2.3                                      | 3.4          | 2.4-2.8                            | 2.3-2.7                           | 2.0       | 9.1          | 2.1-2.8                  |

|    | ND 3   | (1015/cm <sup>2</sup> )              | 6-8          | 13                 | ~12                   | 8 <b>-</b> 9                                 | 10-12        | 7-7.5                              | 9.6                               | 6.6-8.5   | 6.7          | 7-10                     |

|    | Device | Lot                                  | 29 II        | 111 6 <del>4</del> | 61 II                 | 63 11                                        | 11 45        | 70 11                              | 70 111                            | 71 II     | 76 111       | 111 62                   |

Notes: First line corresponds to best efficiency achieved; second to maximum power. Hardiness refers to ability to withstand electrical abuse.

### E. <u>Device Evaluation and Performance in Microstrip</u>

A conventional waveguide test circuit can be used as the initial step for microwave evaluation of the diodes to be incorporated in a microstrip amplifier circuit. However, to design an optimum amplifier circuit, it is essential to characterize the diode in a microstrip circuit for large-signal operation. The main concerns for high power applications are to achieve the required circuit resistance for an optimum impedance match and the necessary bond lead inductance for the desired operating frequency.

The Read diode is evaluated as a free-running oscillator in a microstrip test fixture. The basic microstrip circuit consists of a 50  $\Omega$  transmission line, a 10 pF beam lead capacitor for dc blocking, and a  $\lambda/4$  transformer section to reduce the real part of the impedance to  $\sim 3 \,\Omega$  at the input to the diode. The microstrip circuit is fabricated on 0.25 mm thick polished alumina and mounted on a gold-plated aluminum block. The diode, which has an integral plated heat sink, is alloyed onto a gold-plated copper block  $(0.50 \times 0.50 \times 0.25 \text{ cm})$  and attached to the microstrip circuit block with a small screw. The diode mounting scheme used in the test fixtures is identical to that employed in the final amplifier assemblies. Figure 15 shows the microstrip oscillator test fixture.

For initial evaluation the circuit is tuned only for maximum power from the device as a free-running oscillator (i.e., no rf input). Several microstrip circuits employing transformed impedances ranging from 3  $\Omega$  to 11  $\Omega$  were investigated. Input impedance levels less than 3  $\Omega$  are difficult to produce on 0.25 mm thick alumina because the width of the transforming section becomes greater than the length ( $\lambda/4$ ). It becomes difficult to predict the actual impedance presented to the diode in this situation. For the Ku-band Read diodes tested, the impedance level required for a 0.10 to 0.13 mm diameter mesa is approximately 3  $\Omega$  to obtain maximum power output. If two mesas are combined in parallel on a chip, the required impedance presented to the device must be approximately halved ( $\approx 1.5 \Omega$ ). At the 3  $\Omega$  level, the microstrip transformer is already a square ( $\lambda/4 \times \lambda/4$ ), and thus a 50-to-1.5  $\Omega$  transformer is not easily achievable.

Figure 15 IMPATT Microstrip Oscillator Test Fixture

For high-power performance from a Read diode, one would like to employ as large a mesa as possible. The larger the area, however, the greater the capacitance. This necessarily requires a correspondingly smaller lead inductance to the device to cause it to resonate at the desired frequency. To obtain the optimum condition, the shortest possible 0.13 mm wide gold ribbon is bonded from the microstrip circuit to the diode. The diode is then etched until the desired operating frequency is achieved. Often the diode will require a considerable amount of etching to increase the frequency of oscillation. The lead inductance has been minimized ( $_{\infty}$  0.25 nH), and the diode capacitance must be reduced to achieve the frequency required. In the case of double mesas (parallel combination on a single chip), the individual capacitances add, necessitating an even further reduction in the input inductance or the diode capacitance. Doublemesa operation was found to be difficult to repeat from chip to chip. Many bonding configurations were implemented with the double mesas, with most schemes yielding unpredictable results. The reactive parasitics appeared to predominate.

It was found that to achieve the highest possible output power, either a single-mesa diode with a large junction area or a multiple-mesa with the same total area must be used. The thermal advantage gained by a multiple-mesa approach appeared to be outweighed by the difficulties encountered with lower impedance levels, unpredictable results obtained with various bonding configurations, and local parasitics. From slice 79 III a single-mesa Read diode (0.10 to 0.13 mm) produced 1.8 W at 15.6 GHz as a free-running oscillator in a microstrip test circuit. Efficiency was 23%. Another single mesa delivered 1.4 W at 15.6 GHz with 19% efficiency.

# SECTION III AMPLIFIER DEVELOPMENT

### A. General

Figure 16 shows a block diagram of the three main amplifier chassis: the FET preamplifier, the IMPATT driver amplifier, and the IMPATT balanced power stage. The power gain of each stage, as well as the dc input power and corresponding rf power output along the chain of amplifiers, is also indicated. The amplifier operates from 39 V, 6 V, and -1 V commercial dc power supplies. (The -1 voltage is necessary for biasing the FET gates.) All dc power losses due to biasing networks are included in the dc input values shown. The nominal rf input power to the amplifier ranges from threshold (< -30 dBm) to -20 dBm. Below threshold, amplification is no longer needed (as determined by transmitter requirements), and the driver and power amplifiers are made idle by removing bias from the IMPATT diodes. This is accomplished by a detector-activated "squelch" circuit, which monitors the output power level of the FET preamplifier.

Although it is possible to develop stable amplifiers (i.e., stable under zero of drive) using flat profile IMPATTs, it is not practical to do so with amplifiers employing high efficiency GaAs IMFATTs with low-high-low doping profiles, 9-11 because for these diodes a large increase in negative resistance accompanies reduced of drive levels. As a consequence, an amplifier tuned for maximum output power at a high input drive level (i.e., the real part of the circuit impedance presented to the diode is low) will oscillate at reduced or zero drive levels (because the magnitude of the diode's negative resistance has increased to a value greater than the real part of the circuit impedance). For this reason, the low-high-low GaAs IMPATTs are much more appropriate for injection-locked oscillator (ILO) operation than for stable amplifier application. Other advantages of the ILO approach include: (1) higher amplifier efficiency due to higher gain ( and therefore fewer) ILO stages, (2) easier and faster tuning procedure (more cost effective), and (3) improved overall amplifier gain stability with respect to changes in ambient temperature. This is because the output power

IMPATT Belanced Power Amplifier

Figure 16 Block Diagram f Spacecraft Transmitter Amplifier

36

of an ILO stage is not directly proportional to its input power and, in fact, can be very insensitive to it. Consequently, the amplifier gain variation due to temperature changes is affected primarily by the temperature characteristics of the final ILO stage rather than by the cumulative gain variation of all preceding stages.

The primary disadvantages of an injection-locked oscillator approach are:

(1) operation mar power saturation over most of the input power range; (2) reduced bandwidth capability as compared to a broadband stable amplifier; (3) a locking bandwidth that is dependent on the input rf drive level; and (4) spurious output during zero input conditions. In light of the transmitter amplifier requirements however, it was possible to overcome the latter three disadvantages, as discussed later in this section. The problem of power-saturated operation results in poorer third-order intermodulation suppression at lower drive levels, e.g., at -30 dBm input power. Nevertheless, when put in perspective with the overall transmitter requirements, especially the efficiency and power output goals, the advantages of the ILO design far outweigh the disadvantages. As a consequence, the ILO approach was implemented in the IMPATT stages of the delivered amplifier.

An FET rather than an IMPATT preamplifier was chosen because of several key advantages that the former design provides. The FET preamplifier is easier to design and tune for stable operation. (Even flat profile IMPATTs are difficult to simultaneously tune for high efficiency and stable operation under zero drive conditions.) Furthermore, an FET amplifier is intrinsically less sensitive to changes in ambient temperature. Both the gain and the center band of operation drift significantly with temperature in an all-IMPATT preamplifier. The FET design is more cost-effective because of a simpler, more compact MIC configuration; no ferrite material or permanent magnets are required. Finally, the FET preamplifier provides at least two orders of magnitude improvement in the noise figure, as well as improved linearity performance as compared to the IMPATT counterpart.

The FET preamplifier is designed on the basis of small signal S-parameters. Because six stages of FET are used, attention is given to compact design to maintain the small preamplifier dimensions. Holes, I mm in diameter, drilled in the alumina substrate accommodate the FET chips, which are mounted on 0.15 mm thick gold discs. The FET preamplifier provides 41 dB of small signal gain and yields a 1 dB gain compression point of 100 mW.

The driver amplifier consists of two IMPATT stages of circulator-coupled reflection amplifiers operating in the ILO mode. Three of the five MIC-fabricated circulators serve as isolators at the input and output of the driver and between the two stages. The driver stage has a gain of 11 dB at an output power of 1.2 W.

The power amplifier consists of two single-mesa diodes power-combined via a 3 dB interdigitated coupler fabricated on a quartz substrate. This approach, rather than one using a single-ended amplifier with multiple-mesa chip-level power-combining, was implemented for two reasons. First, high-power multiple-mesa operation is difficult to achieve in a microstrip circuit 10,11 at mid Ku-band. Second, a balanced, circuit-power combined design is potentially a more reliable configuration, since there is more complete isolation both electrically and thermally between the combined mesas. Thus, a higher probability of optimum efficiency operation from both devices is achieved. The power amplifier stage provides an output power of 4.2 W at 5 dB gain.

All three amplifier chassis are integrated in a housing whose volume is  $220~{\rm cm}^3$ . Because of the high gain of the spacecraft transmitter amplifier, metal partition walls incorporating short sections of  $50~\Omega$  transmission line feedthroughs separate the three chassis to suppress potential signal feedback and spurious oscillation in the preamplifier. Also included in the housing are the bias distribution circuits, as well as the detector-activated IMPATT "squelch" circuit. This circuit ensures zero rf output from the amplifier for input signals below the threshold level (< -30 dBm).

### B. FET Preamplifier Design and Performance

Because of the narrow bandwidth requirements of the spacecraft transmitter (fractional bandwidth of 1.7%), the circuit design for the FET preamplifier is quite straightforward. Small signal S-parameters are measured on the devices to be used, and simple single-section  $\lambda/4$  microstrip transformers are designed to transform from a 50  $\Omega$  impedance level down to the required value as determined from the S-parameters. Bond wires connecting the device to the circuit provide the necessary inductance to cancel the capacitive reactance of the devices. Simple, conjugate impedance matching at 15 GHz is used for both gate and drain circuits.

The FETs are TI devices having 0.5 µm long, electron beam defined gates with total gate widths of 300 μm (four gate fingers, 75 μm each). For S-parameter measurements the FET devices are mounted in test circuits in the same manner used for the preamplifier. To minimize parasitic circuit elements associated with the device mounting scheme and to reduce the overall length of the multistage amplifier, a different mounting method was used from that usually employed at Texas Instruments for power devices. Instead of sandwiching a copper carrier block (on which the FET is soldered) between input and output microstrip circuits, a hole is drilled through the alumina substrate containing the etched circuit, and the device is mounted inside the hole and fixed to the same carrier to which the alumina microstrip circuit is attached. The FET device is soldered to a gold disc, 0.9 mm in diameter and 0.15 mm thick, and wire bond connections are made between the source pads and this disc. The disc serves two purposes: (1) it allows the ground connection to the source pads via the wire bonds, and (2) it serves as a pedestal for the device when it is placed in the hole to position the top surface of the 0.1 mm high chip leve! with the 0.25 mm thick alumina substrate. The disc is placed in the hole and attached to the substrate carrier block by conductive silver epoxy or solder. Wire bonds are then attached to the gate and drain pads and connected to the input and output microstrip lines, respectively.

Figure 17 FET Mounting Scheme to Reduce Parasitic Losses

ORIGINAL PAGE IS OF POOR QUALITY

### \*\*S PARAM. PROG.

FREQ. IN GHZ = 15.0000 MAGN. S11? 0.6800 ANGLE S11? -165.0000 MAGN. 812? 0.1000 ANGLE S12? 45.0000 MAGN. 821? 1.7000 ANGLE S21? 80.0000 MAGN. 822? 0.4200 ANGLE S22? -155.0000 K= 1.3624 MAG IN DB=

(a)

8.7107

(b)

(c)

Figure 18 Single and Multistage 15 GHz FET Breadboard Amplifiers. (a) S-parameters for a 300  $\mu m$  FET. (b) Single-stage amplifier with 8 dB gain.

- (c) Four-stage amplifier with 28 dB gain.

Figure 19 Gain Compression Curve For 15 GHz Preamplifiers

stages, such that the six-stage preamplifier is mounted on one carrier plate. For improved heat sinking the gold discs on which the FET chips are mounted and soldered to the carrier plate in the case of the 600  $\mu$ m devices. To facilitate testing, the carrier plate is designed such that OSM connectors can be attached at three places for testing the first four, last two, or all six cascaded stages.

Figure 20 shows the FET preamplifier ready for testing the first four stages. A ribbon bonding scheme enables one to test either the first four or the last two stages. When checked out, the test microstrip line is made idle, and the main amplifier chain is connected. Also seen in Figure 20, at the extreme right of the alumina substrate, is the 10 dB coupler, which senses part of the input power and directs it to a detector for activating the shutdown circuitry for the IMPATT bias supply.

Figure 21 shows the gain compression curve for the actual preamplifier used in the final spacecraft transmitter amplifier measured at 15 GHz. A small signal gain of 42 dB and a 1 dB gain compression point of 20 dBm are achieved. Figure 22 shows the small signal gain versus frequency characteristic. Across the specified operating band a gain variation of 1.5 dB is observed for the preamplifier. For these measurements the last two stages operated at a drain voltage of 6.5 V, and the first four stages operated at a 4 V drain bias. A voltage dropping resistor was used so as to power the entire six-stage preamplifier from a single drain power supply of 6.5 V (in the final amplifier integration, the preamplifier power supply voltage for the drain was lowered to 6 V).

To further assess the linearity characteristics of this preamplifier, third-order intermodulation distortion measurements were performed at 15 GHz. Two signals separated in frequency by 10 MHz were applied to the preamplifier, and the level of the third-order products was measured. Figure 23 shows the level of the

Figure 20 Six-Stage FET Preamplifier Ready for Testing

Figure 21 Gain Compression Characteristic for 15 GHz Six-Stage Preamplifier

Gain versus Frequency Characteristic for 15 GHz Six-Stage Preamplifier Figure 22

Figure 23 Third-Order Intermodulation Product vs Input Level at Band Center of the Six-Stage FET Preamplifier

third-order products as a function of input power. Figures 24(a) and (b) show the corresponding spectrum analyzer displays for input power levels of -33 dBm and -23 dBm, respectively. It is seen that for the former case the third-order products are 33 dB below the carrier level. This corresponds to at least a 12 dB improvement in third-order intermodulation performance over an all-IMPATT preamplifier operating at a lower frequency of 13.3 GHz.

### C. IMPATT Driver Amplifier Design and Performance

The driver amplifier consists of two stages of circulator coupled reflection amplifiers operating in the injection-locked oscillator mode. Three additional MIC circulators serve as isolators at the input and output and between stages. The driver stage design follows closely that used previously at Texas Instruments for development of similar amplifiers. 8,10,11 A photograph of the driver chassis is shown in Figure 25. Simple  $\lambda/4$  transformers (50  $\Omega$  to  $\sim$  3  $\Omega$ ) and bonding ribbon inductance ( $\sim$  0.13 mm  $\times$  0.2 mm  $\times$  25  $\mu$ m) are used for impedance matching to the diodes. The matching circuits are fabricated on 0.25 mm alumina substrates, while the circulator discs are etched on TT1-390 0.5 mm thick ferrite. SmCo permanent magnets (6.25 mm in diameter and 3.13 mm thick) mounted beneath the ferrite directly underneath the disc resonators bias the ferrite for circulator action. 11 For circulator optimization 0.38 mm thick shims are placed between the magnet and the bottom surface of the ferrite substrate. For additional control of the magnetic fringing field lines and circulator optimization, iron 'pucks' are placed on the top surface of the ferrite. The circulator resonator disc etched on the ferrite has a diameter of 3.75 mm. A single quarter-wave transformer with a characteristic impedance of 31.6  $\Omega$  (with the ferrite demagnetized) is used for impedance matching the circulator to 50  $\Omega$ . The three isolators use the same circulator design, except that the magnets are reversed in polarity, and the circuit etched on the alumina is simply a terminated (by a thin-film resistor) 50  $\Omega$  line.

(a)

(b)

Vertical: 10 dB/div Horizontal: 10 MHz/div Center Frequency: 15 GHz

Figure 24 Spectrum Analyzer Display of FET Preamplifier Output With

- (a) Two -33 dBm Input Signals(b) Two -23 dBm Input Signals

Figure 25 IMPATT Driver Amplifier Chassis

To check the total insertion loss of all circulators between 14 and 16 GHz, the magnets were positioned identically (with the same polarity) underneath the ferrite such that the signal passed only once through each disc, essentially traversing the driver chassis from input to output in a straight line. From 14 to 15.75 GHz the total insertion loss, including a pair of OSM connectors, was between 2.5 and 3.2 dB. The return loss from 14 to 15.2 GHz was greater than 20 dB, and greater than 12 dB from 15.2 to 16 GHz. Generally, the adjacent-port isolation of these circulators is also greater than 20 dB over at least a 1 GHz bandwidth for mid Ku-band center frequencies.

The driver amplifier is designed to increase the power level to greater than 1 W, and yet maintain a locking bandwidth considerably in excess of 250 MHz to ensure the bandwidth performance over temperature. Because the locking bandwidth for a single-stage ILO is nominally proportional to the square root of the input power, the critical design operating point occurs at the lower input levels. Consequently, it is necessary to obtain a locking bandwidth of greater than 250 MHz at a driver input level of +10 dBm (~ -30 dBm input to the preamplifier), and yet maintain 10 or 11 dB gain at an input drive level of 20 dBm. This was achieved for the driver amplifier using single-mesa diodes (79 III) in each stage and the same impedance matching circuits used in the oscillator test fixture (Figure 15, Section II).

Table 3 summarizes the driver amplifier's performance, as well as the operating characteristics of the actual diodes used. An output power of 1.3 W and an added-power efficiency of 10% were achieved for the amplifier, including the losses in the series bias resistors. These resistors are necessary to stabilize the IMPATTS against low frequency bias oscillations. The performance of the actual devices, as characterized in the microstrip oscillator test circuit, is shown at the bottom of Table 3. Note that the efficiencies in this case include the losses in the microstrip line and OSM connector (0.2 to 0.3 dB) and do not include the losses in the bias line series resistor.

Table 3 Driver Stage Performance

| Diode Operating Voltage and Current<br>and 10 mA Breakdown Voltage<br>First Stage Second Stage | 35 V, 211 mA               | V <sub>B</sub> = 23 V |  |

|------------------------------------------------------------------------------------------------|----------------------------|-----------------------|--|

| Diode Operating V<br>and TO mA Bre<br>First Stage                                              | 26 V, 147 mA               | V <sub>B</sub> = 17 V |  |

| Output<br>Power<br>(dBm)                                                                       | 31.0                       | 31.2                  |  |

| Locking<br>Limits<br>(15 GHz ± MHz)                                                            | -160, + 260<br>-340, + 480 | -660, + 840           |  |

| Locking<br>Bandwidth<br>(MHz)                                                                  | 420<br>820                 | 1500                  |  |

| Input<br>Power<br>(dBm)                                                                        | + 10<br>+15                | +20                   |  |

Driver Stage Operating Voltage: 38 V Series Bias Resistors: First Stage - 82  $\Omega$

Second Stage - 13.3 n

Total Dc Input Power: 13.6 W

Power-Added Efficiency: 10%

| -                                                           |               | 9                       |

|-------------------------------------------------------------|---------------|-------------------------|

| Performance of Diodes in Microstrip Oscillator Test Circuit | ode           | 1.4 W, 18.9% at 15.6    |

| Circ                                                        | <u>a</u>      | %<br>a                  |

| sst                                                         | econd Stage   | 9.9                     |

| Ţ                                                           | P             |                         |

| ato                                                         | eco           | 4.                      |

| cil                                                         | 0,1           | _                       |

| 000                                                         |               |                         |

| tri                                                         |               |                         |

| cros                                                        |               |                         |

| Mi                                                          |               |                         |

| in                                                          |               | CH2                     |

| ode                                                         |               | .1 W, 14.5% at 15.5 GHz |

| F Di                                                        | ode           | at 1                    |

| 0                                                           |               | %                       |

| ance                                                        | tage          | 14.5                    |

| Form                                                        | irst Stage Di | `€                      |

| Per                                                         |               | -                       |

|                                                             | -             |                         |

Although a 10% power-added efficiency was realized for this amplifier, a more careful pairing up of diodes, so that the operating voltage of both would be closer to the 35 V value, would result in still higher efficiency, since less power would be dissipated in the series bias resistors.

### D. IMPATT Balanced Power Amplifier Stage Design and Performance

A 3 dB microstrip interdigital hybrid coupler, the so-called Lange 12 coupler. is used to power-combine the outputs of two IMPATT diodes as shown schematically in Figure 16. Both the coupled and the direct ports of the coupler are terminated with an identical matching circuit and diode combination. Ideally, the voltage reflection coefficients looking into the diode circuits are equal in both magnitude and phase. Because of the 90° phase properties of the hybrid, the two reflected waves add in phase at the normally isolated port and cancel at the input port, resulting in the necessary isolation between input and output signals. Since the frequency of interest is mid Ku-band, the substrate chosen for fabrication of the coupler circuit is  $0.25 \pm 0.013$  mm thick, fused quartz (GE 125) with a 60-40 surface finish. This choice of substrate for the coupler fabrication. rather than alumina, was made primarily because of the potential for lower loss due to the resulting wider line widths and smoother surface finish for the quartz substrate. The disadvantage of such thin quartz substrates, however, is that they are more fragile than equally thin alumina substrates, and extra care must be exercised during fabrication and assembly. The etched circuit dimensions for the coupler are: line widths in the coupling section, 0.075 mm; gaps between lines, 0.02 mm.

The original design and performance of this coupler were described in detail elsewhere. Optimization of the coupler continue under this contract. In an attempt to reduce losses, plated-up silver (flashed with gold to prevent tarnishing)

approximately 2.5  $\mu$ m thick, was used for the metallization. The pattern itself was defined by etching a thin nichrome/Au base metallization, approximately 200 Å thick. The insertion loss for a single pass for this coupler at 15 GHz is between 0.25 and 0.35 dB over and above the nominal 3 dB power split. Amplitude tracking over the range of 14 to 16 GHz is better than 0.25 dB.

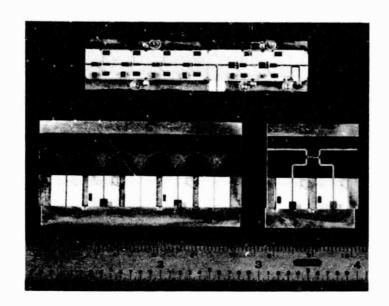

Figure 26 shows the balanced power stage (minus the IMPATT diodes) alongside the other two component chassis prior to final assembly and tuning. Also shown in the photograph is the Ku-band Lange coupler etched on a 22.5 x 10 x 0.25 mm fused quartz substrate. The matching circuits consisting of the single section  $\lambda/4$  transformer, tuning pads, and 50  $\Omega$  line are all fabricated on the 7.5 x 7.5 x 0.25 mm alumina substrate.

Tuning of the balanced stage begins with careful selection of a pair of nearly identical diodes. Diodes are matched to have nearly equal breakdown and operating voltages, power output, and frequency of operation when tuned with close to identical matching circuits. The selected pair of diodes is then simultaneously tuned in the balanced stage to realize maximum combined output power from the output port of the coupler, with a nominal input power of 31 dBm. As in the case of the driver stage, both diodes are single-mesa devices that operate in the injection-locked oscillator mode. However, since the driver stage output power stays nearly the same at 31 dBm, the balanced stage locking bandwidth is determined by this one input level. That is, the gain of the balanced stage (and hence the locking bandwidth) remains constant at about 5 dB. For the diodes and matching circuits used, the locking bandwidth at these drive levels is well over 1 GHz.

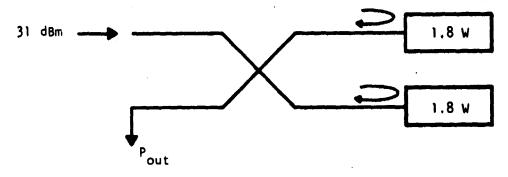

From the coupler insertion loss measurements and from the single-mesa diode characterization studies in the microstrip oscillator test circuits it is possible

Figure 26 Preamplifier, Driver, and Balanced Power Amplifier Chassis

ORIGINAL PAGE IS OF POOR QUALITY to estimate the anticipated balanced-stage power output performance. The assumption is made that the rf power added from each diode in the balanced ILO configuration is just equal to the oscillator output power when the diodes are tested separately in the microstrip oscillator test fixture. Figure 27 shows the calculation given a 3 dB coupler with an insertion loss of 0.3 dB (single pass) and two 1.8 W single-mesa diodes tested as free-running oscillators. An input to the balanced stage of 31 dBm is assumed. The output power is simply the addition of the available power output exhibited during free-running oscillator operation from each diode, plus the input power, minus the losses in the coupler. Note that the input power "passes" twice through the coupler, while the added power from the diodes suffers the loss corresponding to one pass through the coupler. As the figure shows, the result of the calculation is a power output of 4.5 W and a gain of 5.5 dB. To achieve the 5 W goal, diodes with microstrip oscillator powers of at least 2 W must be incorporated in the balanced stage and in the second stage of the driver amplifier.

Table 4 shows the balanced stage performance. An output power of 4.2 W at a gain of 5.2 dB and an intrinsic power-added efficiency of 16% was achieved at 15 GHz. A locking bandwidth of about 1.5 GHz was obtained. The operating characteristics of one of the diodes in the microstrip oscillator test fixture are listed at the bottom of the table. This diode yielded 1.8 W at an efficiency of 23% at 15.6 GHz. The second diode had nearly the same characteristic, with slightly less dc-to-rf efficiency (~ 20%).

In the final incorporation of the balanced stage into the spacecraft transmitter amplifier, series resistors are used to bias the two diodes from a 38 V dc source. A 9  $\Omega$  and an 11  $\Omega$  resistor are employed.

### Given:

Two 1.8 W diodes (as free oscillators)

One 1.3 W driver amplifier

One 3 dB coupler with 0.3 dB loss (single pass)

$$P_{\text{out}} = 1.3 (10^{-0.06}) + 2(1.8)(10^{-0.03}) = 4.5 \text{ W}$$

$$Gain = 5.5 \text{ dB}$$

Figure 27 Estimated Balanced Power Stage Performance

Table 4

Balanced Stage Performance

|             |                     |        |                   | t Power           |

|-------------|---------------------|--------|-------------------|-------------------|

| Input Power | Output Power        | Gain   | Diode A           | Diode B           |

| 31 dBm      | 36.2 dBm<br>(4.2 W) | 5.2 dB | 35.5 V,<br>279 mA | 35.4 V,<br>242 mA |

Power-Added Efficiency: 16%

Center Frequency: 15 GHz

Locking Bandwidth: ~ 1.5 GHz

# Operating Characteristics of Diode B as a Free-Running Microstrip Oscillator

10 mA Breadkown Voltage: 23.6 V

Operating Voltage, Current: 35 V, 224 mA

Frequency: 15.6 GHz

Output Power: 32.5 dBm (1.8 W)

Dc-to-rf Efficiency: 23%

## E. Design, Integration, and Performance of Spacecraft Transmitter Amplifier

### 1. Amplifier Housing