Metadata, citation and similar papers at core.ac.uk

#### FAME—A MICROPROCESSOR BASED FRONT-END ANALYSIS AND MODELING ENVIRONMENT

CORE

#### Jacob D. Rosenbaum and Edward B. Kutin Higher Order Software Jericho, New York

FAME, (Front-End Analysis and Modeling Environment) is a microprocessor based interactive computer aided design aid, for designers and developers of computer-based systems. FAME is especially useful in microprocessor applications where systems complexity has increased the need for more rigorous approaches to the development process.

A variety of techniques and methods are being proposed by government and industry to meet the extensive need for better approaches to development, documentation and verification of systems. Some of the more widely used include; formal specification of system requirements and designs, static analysis of related models, and simulation to insure that the system to be developed meets the intended objective. To date, support of these activities involve large, costly computerized systems or extensive manual procedures.

Higher Order Software (HOS) is a methodology for the specification and verification of large scale, complex, real-time systems. An emphasis in its development has been the aerospace environment. Typical systems applications include guidance and control, navigation, communications, radar imaging, satellite tracking and many others. The methodology integrates Functional Decomposition, Abstract Data Types, and Control Structures in accordance with a set of axioms that describe decomposition rules, nodal relationships and responsibilities. The systems models produced can be verified statically using small amounts of computer resources and time.

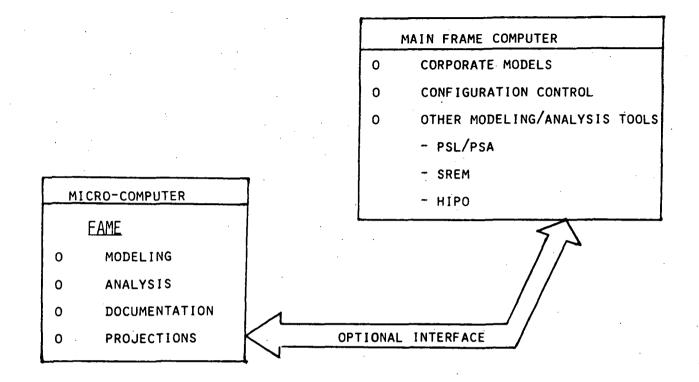

The HOS methodology has now been implemented as FAME (Front-End Analysis and Modeling Environment), a microprocessor based system for interactively developing, analyzing and displaying system models in a low cost user-friendly environment. The nature of the model is such that when completed it can be the basis for projection to a variety of forms such as Structured Design Diagrams, Petri-Nets, Data Flow Diagrams, PSL/PSA Source Code etc. The user's interface with the analyzer is easily recognized by any current user of a structured modeling approach; therefore extensive training is unnecessary. Furthermore, when all the system capabilities are used one can check on proper usage of Data Types, Functions and Control Structures and thereby add a new dimension to the design process that will lead to better, and more easily verified software designs.

FAME is now available on a range of computer systems as well as on any Microprocessor with 64K of memory and dual floppy disks that can use the CP/M operating system. It is especially useful on Microprocessor Development Systems where one would now be able to combine the requirements, documentation analysis, verification and code development activities on a single device.

Preceding Page Blank

## FAME CAPABILITIES

## BENEFITS OF HOS

0 MODELS ARE VERIFIABLE STATICALLY

O MODELS INTEGRATE

- FUNCTIONS

- DATA TYPES

- LIBRARIES OF OPERATIONS & STRUCTURES

- RULES FOR MODEL CREATION

O SUPPORTS ALL PHASES OF DEVELOPMENT

0 MODELS CAN SUPPORT DIRECT SIMULATION

Martin Andrew Contraction

MODELS CAN PROVIDE EXTRACTS TO SATISFY OTHER METHODS

O AN HOS ANALYSIS REQUIRES KNOWLEDGE OF ONLY A PARENT & ITS OFFSPRING

# COST BENEFITS OF FAME ON MICRO

- O OFFLOADS MAINFRAME T/S SYSTEMS

- O PROVIDES GOOD RESPONSE @<\$4/HOUR

- O MINIMUM LINE CHARGES

0

HOS MODELING & ANALYSIS COSTS ESTIMATES (ON 8080 MICROCOMPUTER)

| MODELING PHASE | CLOCK MINUTES/NODE | NODES INVOLVED |

|----------------|--------------------|----------------|

| DECOMPOSITION  | 15 MIN             | PARENTS        |

| ANALYSIS       | 1.5 MIN            | PARENTS        |

| DISPLAY        | 1,0 MIN            | PARENTS        |

|                |                    |                |

# CURRENT STATUS

| 0 | prototype (c basic) on 8080 micro-computers (cpm) |

|---|---------------------------------------------------|

| 0 | PROTOTYPE (C BASIC) ON INTEL MDS                  |

| 0 | PASCAL VERSION ON MICRO (IN DEVELOPMENT)          |

| 0 | pascal version on vax 11/780                      |

| 0 | CURRENTLY REHOSTING TO:                           |

|   | - HARRIS                                          |

|   | - CONTROL DATA (CYBERNET)                         |

|   | - MULTICS                                         |

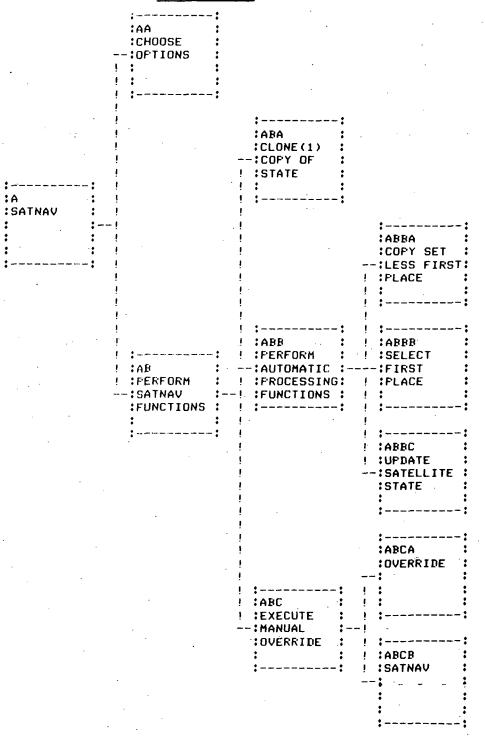

### PARENT/OFFSPRING DIAGRAM

HOS/ FRONT-END ANALYSIS AND MODELING ENVIRONMENT

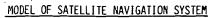

## SATELLITE NAVIGATION

MODEL NAME: SATNAV AUTHOR: EN DATE/TIME: 7/14

| OUTPUTS | • .                                                                                 | INFUTS                               |

|---------|-------------------------------------------------------------------------------------|--------------------------------------|

| YSATST  | : ABB<br>: PERFORM<br>: AUTOMATIC<br>: PROCESSING<br>: FUNCTIONS<br>:<br><br>O=PROC | XSAIST<br>SSETIM<br>LSETPL<br>CSTSIM |

|         |            | ··          |           | ·:            |  |  |

|---------|------------|-------------|-----------|---------------|--|--|

| : ABBC  | :COJ0IN    | : ABBB      | :COINCLUD | : ARBA :      |  |  |

| UPDATE  | :          | SELECT      | <b>:</b>  | COPY SET :    |  |  |

| SATELLI | TE :       | FIRST       | :         | LESS FIRST:   |  |  |

| STATE   | <b>;</b> . | :PLACE      |           | :FLACE :      |  |  |

| :       | 1 <b>1</b> | :           | :         | : :           |  |  |

| :       | :          | :           | :         | : :           |  |  |

| :       | :          | :           | :         | ::            |  |  |

|         | SATST      | LSETPL 1 LS | SETPL L   | SETPL 2 LSETP |  |  |

| S       | SETIM      |             |           |               |  |  |

| r -     | CICIN      |             | -         |               |  |  |

CSISIN LSETPL 1 LSETPL 2

|        |    | STATE OF  | SATELLITES   |            | •          | STATE  |   |

|--------|----|-----------|--------------|------------|------------|--------|---|

|        |    |           | SATELLITES   |            | -          | STATE  |   |

| SSETIM | >  | ORDERED   | SETS OF      | IMAGES     |            | ORDSFT |   |

| LSETPL | >  | ORDERED   | SETS OF      | PLACES     |            | ORDSET | • |

| CSTSIM | >  | ORDERED S | SETS OF (ORI | DERED SETS | OF INAGES) | ORDSET |   |

| LSETPL | 2> | ORDERED   | SET OF       | PLACES 2   |            | ORDSET |   |

| LSETPL | 1> | ORDERED   | SET OF       | FLACES 1   |            | ORDSET |   |

O=PROC ---> EQUAL(0,PROCEED)

A>

## TYPICAL PROMPTED SCENARIO

```

HOW MANY OFFSERING DO YOU WANT TO ADD? 2

FOR NODE ABBCA

EN NAME (8 ): AUIDCOR_

OF NAME (8 );

LONG NAME (10): AUTOMATIC_

LONG NAME (10 ): CUREELATIO

LONG NAME (10 ): +

CONNECTOR (8):

INFUT(8): 2_____

INFUT(8): 4_____

INFUT(8): 8_____

INFUT(8): 6_____

INFUT(8): .....

OUTFUT(8): XSAISI11

FOR OUTPUT XSATST ( /

DATA TYPE(8): SIAIE_.

LONG NAME(10): STATE_DE__

LONG NAME(10): SATELLITES

LONG NAME (10):

OUTFUT(8): ____

```

```

CONDITION (8):

FOR NODE ABBCB

FN NAME (8): SAINACCU

DF NAME (8):

LONG NAME (10): SAINAU

LONG NAME (10): 1

CONNECTOR (8): COJOIN

INFUT(8): XSAISI''

```

INFUT(8): 4\_\_\_\_\_ INFUT(8): 10\_\_\_\_\_ INFUT(8): 6\_\_\_\_\_ OUTFUT(8): 1\_\_\_\_\_ OUTFUT(8): 1\_\_\_\_\_ DUTFUT(8): \_\_\_\_\_ DO YOU WANT TO MAKE ANY CHANGES TO INFUTTED INFORMATION?N FILES CLOSED---RUNNING UPDATE PASSWORD NUMBER

UPDATE COMPLETED

### TREE DIAGRAM