# **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

#### A STUDY OF HIGH DENSITY BIT TRANSITION

#### **REQUIREMENTS VERSUS THE EFFECTS ON BCH**

ERROR CORRECTING CODING

Interim Final Report Covering the Period July 1, 1980 - September 30, 1981

Submitted to:

Mr. Russ Coffee EF-13 George C. Marshall Space Flight Center National Aeronautics and Space Administration Marshall Space Flight Center, Alabama 35812

Submitted by:

Mississippi State University Engineering and Industrial Research Station Department of Electrical Engineering Mississippi State, Mississippi 39762

(NASA-CR-161881) A STULY OF HIGH DENSITY N82-10753 BIT TRANSITION REQUIREMENTS VERSUS THE HC. A05 MF A01 EFFECTS ON BCH ERROR CORRECTING CODING HC. A05 MF A01 Interim Final Report, 1 Jul. 1980 - 30 Sep. 1981 (Mississippi State Univ., Mississippi G3/61 27730

> Principal Investigator: Frank Ingels Associate Investigator: William O. Schoggen

> > Contract No. NAS8-33887

#### EXECUTIVE SUMMARY

Digital data streams using non-return-to-zero-level encoding (NRZ-L) as the signalling waveform are subject to periods of no level change. The signalling waveform with not changing levels has energy content that is rich about the origin and of course does not contain any edges in the waveform.

Proper operation of the ground station receiving such digital data streams depends upon satisfactory bit synchronization. Bit synchronizers typically require a certain minimum percentage of edges in the received signalling waveform. This requirement is not always satisfied by NRZ-L waveforms.

The purpose of this investigative study has been to determine a satisfactory method of providing sufficient bit transitions (edges) in the signalling waveform for the 2 MHz data link of the Space Shuttle High Rate Multiplexer (HRM) unit.

The system design already in existence places several constraints on any method used to ensure the desired bit transition density of at least 1 bit transition in every 64 bits and at least 64 bit transitions in every 512 bits.

These constraints are:

- The method chosen must produce at least 1 bit transition in every 64 bits and at least 64 transitions in every 512 bits.

- The method chosen must not increase the present bandwidth nor decrease the present information rate.

- 3. The method chosen must be compatible with the existing BCH code.

- The method chosen should have a minimal design impact on the present system.

- 5. The method chosen must pass unaltered any data stream whose data rate is greater than 2 MHz.

- The method chosen should resolve the bit phase ambiguity problem inherent in the Channel 2 return link of the KU-Band system.

1

Many methods for increasing bit transition densities in a data stream exist. These methods have been summarized, discussed in detail and compared one against another and against the constraints mentioned above.

These methods include use of alternate Pulse Code Modulation (PCM) waveforms, data stream modification by insertion, alternate bit inversion, differential encoding, error encoding and use of bit scramblers. (Bit scramblers come in many different versions such as: self synchronizing, multi and single count, serial, cascaded and parallel scramblers).

Of all the methods discussed, one method satisfied the desired objective, met all constraints and had advantages that outweighed disadvantages when compared against the remaining methods. This method was chosen - the reset scrambles or simply the Psuedo-Random Cover Sequence Generator (PN-CSG). This technique is fully analyzed and a design implementation is proposed.

The method consists of modulo-2 addition of a PN sequence to the data stream before the modulations of the Radio Frequence (RF) transmitter. It is recommended that only the data streams and the 4 bit frame synchronization Identity Count (ID) be so modified. It is recommended that there be no change in the 28 bit frame synchronization word.

If the PN sequence is added to the frame synchronization word, it is very likely that the special properties chosen for frame synchronization patterns would be violated. Furthermore, the decoder must then search for four frame synchronization patterns if it is desired to correctly detect the presence or absence of the PN cover sequence, and to alleviate any phase ambiguity.

The probability of failing to provide the required bit transition density is less than  $2.44 \cdot 10^{-17}$ . A computer simulation program was developed which tests the truncated PN sequence with random data streams. The computer results indicate that the output sequence to be transmitted by the RF modulator will have a transition density of approximately 50%. This should improve the overall KU Band system performance considerably in the presence of low signal-to-noise ratios by increasing the bit synchronizer's capability to stay locked to the incoming bit clock.

ii

## TABLE OF CONTENTS

| Chapter |       |         |        |     |      |               |             |      |     |     |      |      |      |     |     |    | Page    |

|---------|-------|---------|--------|-----|------|---------------|-------------|------|-----|-----|------|------|------|-----|-----|----|---------|

|         | EXEC  | UTIVE S | UMMARY | •   | •    | • •           | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | i       |

|         | LIST  | OF FIG  | URES   | •   | •    |               | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | v       |

|         | LIST  | OF TAB  | LES    | •   | •    |               | •           | •    | •   | •   | •    | •    | •    | •   | • . | •  | vi      |

|         | LIST  | OF SYM  | BOLS   | •   | • •  |               | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | vii     |

| 1       | INTRO | DUCTIO  | N      | •   | •    |               | •           | •    | •   | •   |      | •    | •    | •   | •   | •  | 1       |

| 2       | STAT  | ement o | F PROB | LEM | ANI  | ) CO          | STR         | AINT | S   | •   | •    | •    | •    | •   | •   | •  | 7       |

|         | 2.A   | THE PR  | OBLEM  | •   | •    |               | ٠           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 7       |

|         | 2.B   | PRIMAR  | Y SYST | em  | CONS | STRA          | INTS        | •    | •   | •   | •    | •    | •    | •   | •   | ٠  | 7       |

|         | 2.C   | SECOND  | ARY SY | STE | M CO | )<br>NST      | RAIN        | rs   | •   | •   | •    | •    | •    | •   | •   | •  | 11      |

| 3       | DIFF  | erent m | ethods | AV. | AILA | BLE           | TO A        | ALLE | VIA | TE  | THE  | 2    |      |     |     |    |         |

|         | PI    | ROBLEM  | • •    | •   | •    |               | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 13      |

|         | 3.A   | ALTERN  | ATE PU | LSE | COL  | )e mo         | DUL         | ATIO | N W | AVE | FOR  | MS   | •    | •   | •   | •  | 13      |

|         |       | 3.A.1   | Bi-PH  | ASE | •    |               | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 13      |

|         |       | 3.A.2   | DELAY  | MO  | DULA | TIO           | ι.          | •    | •   | • • | •    | •    | •    | •   | •   | •  | 13      |

|         | 3.B   | DATA S  | TREAM  | MOD | IFIC | ATI           | DN •        | •    | •   | •   | •    | •    | •    | •   | •   | •  | 16      |

|         |       | 3.B.1   | ALTER  | NAT | E BI | T II          | IVERS       | SION | •   | •   | •    | •    | •    | •   | •   | ٠  | 17      |

|         |       | 3.B.2   | DIFFE  | REN | TIAI | . ENG         | CODI        | NG   | •   | •   | •    | •    | •    | •   | •   | •  | 17      |

|         |       | 3.B.3   | BIT I  | NSE | RTIC | )N •          | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 18      |

|         |       | 3.B.4   | ERROR  | EN  | CODI | NG            | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 19      |

|         |       | 3.B.5   | BIT S  | CRA | MBLE | rs.           | •           | •    | •   | •   | •    | •    | •    | •   | •   | •  | 25      |

|         |       |         | 3.B.5  | .a  | SEL  | .F-SY         | NCHI        | RONI | ZIN | G S | CRA  | MBL  | ERS  | }   | •   | •  | 25      |

|         |       |         |        |     | 3.E  | 1.5.8         | 1.1         | MUL  | TI- | COU | NTE  | R S  | CRA  | MBL | ER  | •  | 29      |

|         |       |         |        |     | 3.B  | 1.5.8         | a.2         | SIN  | GLE | -00 | UNI  | ER   | SCR  | AMB | LER |    | 30      |

|         |       |         |        |     | 3.B  | <b>5.</b> 5.a | a.3         | TRA  | NSI | TIO | n d  | FNS  | ITY  | FO  | R   |    |         |

|         |       |         |        |     |      |               |             | SEL  | F-S | YNC | HRO  | NIZ  | ING  | DES | CRA | MB | LERS 30 |

|         |       |         |        |     | 3.B  | 1.5.8         | <b>a.</b> 4 | SEL  | F-S | YNC | HRO  | NIZ  | ING  | ;   |     |    |         |

|         |       |         |        |     |      |               |             | DES  | CRA | MBL | ERS  | •    | •    | •   | •   | •  | 31      |

|         |       |         |        |     | 3.B  | 1.5.8         | ı.5         | THE  | SP  | ECT | RUM  | I OF | ' TH | E   |     |    |         |

|         |       |         |        |     |      |               |             | SCR  | AMB | LER | l OU | TPU  | T    | •   | •   | •  | 34      |

|         |       |         |        |     | 3.B  | i.5.e         | 1.6         | SER  | IAL | , C | ASC  | ADE  | D,   | AND | )   |    |         |

|         |       |         |        |     |      |               |             | PAR  | ALL | EL  | SCR  | AMB  | LER  |     | •   | •  | 35      |

|         |       |         | 3.B.5  | .Ъ  | NON  | -SEI          | LF-S        | YNCH | ron | 121 | NG   | (RE  | SET  | :)  |     |    |         |

|         |       |         |        |     | SCR  | AMBI          | <b>ERS</b>  | •    | •   | •   | •    | •    | •    | ٠   | •   | •  | 38      |

#### TABLE OF CONTENTS (Continued)

#### Chapter Page 4 41 PSEUDO-NOISE COVER SEQUENCE (RESET SCRAMBLER) . . . 41 4.B THE PARTICULAR PN SEQUENCE FOR THE COVER 44 SEQUENCE FOR THE COVER SEQUENCE GENERATOR (CSG) . 4.C PROBABILITIES ASSOCIATED WITH THE SEQUENCE . . . 47 5 CONCLUSIONS AND RECOMMENDATIONS . 54 • . . . • . . 6 REFERENCES 57 • • • • • . . . . • . . . . • 7 59 7.A COMPUTER SIMULATION PROGRAM • 60 . 7.B SPECIFICATION DOCUMENT FOR PN CSG ENCODER/DECODER . 76 7.C NOVEMBER 1980 MONTHLY REPORT . . . . . . . . . 86

# LIST OF FIGURES

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

| 1.1    | KU Band Return Link                              | . 2  |

| 1.2    | HRM - KUSP Interface                             | . 4  |

| 1.3    | General User's Format                            | . 6  |

| 3.1    | PCM Waveforms                                    | . 14 |

| 3.2    | 1/3 Convolutional Encoder with Alternated Bit    |      |

|        | Invertion Employed by Space Telescope            | . 21 |

| 3.3    | Periodic Convolutional Interleaver and           |      |

|        | Deinterleaver Employed by Space Telescope        | . 24 |

| 3.4    | Basic Self-Sync Scrambler                        | . 26 |

| 3.5    | Multi-Counter Scrambler                          | . 27 |

| 3.6    | Single-Sounter Scrambler                         | . 28 |

| 3.7    | Multi-Counter Descrambler                        | . 32 |

| 3.8    | Single-Counter Descrambler                       | . 33 |

| 3.9    | Cascading of N M-bit Scramblers                  | . 36 |

| 3.10   | Parallel Scrambler Configuration                 | . 37 |

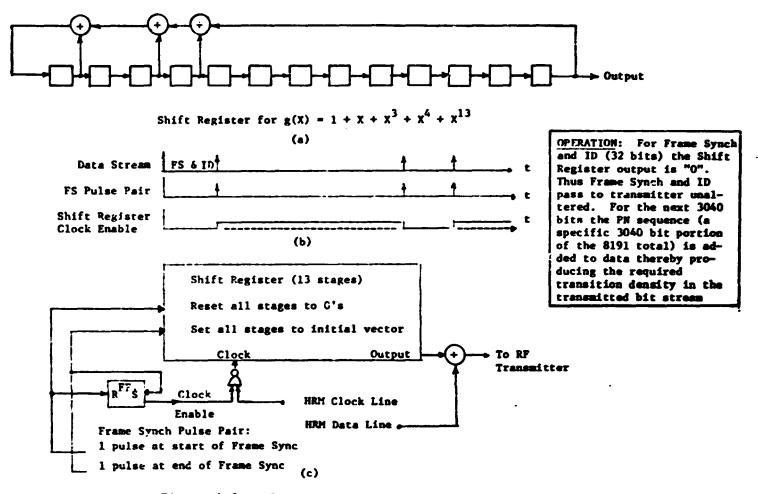

| 3.11   | Reset Scrambler and Descrambler                  |      |

|        | (PN Conver Sequence Generater)                   | . 39 |

| 4.1    | General PN Cover Sequence Generator              | . 42 |

| . 4.2  | CSG Encoder Using Shift Register Implementation. | . 45 |

| 4.3    | CSG Encoder Using ROM Implementation             | . 46 |

| B.1a   | CSG Encoder Functional Location                  | . 79 |

| B.1b   | CSG Decoder Functional Location                  | . 79 |

| B.2    | HRM Data Stream                                  | , 80 |

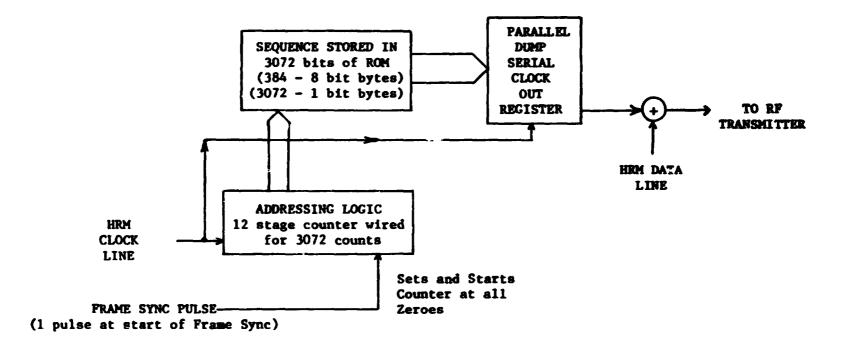

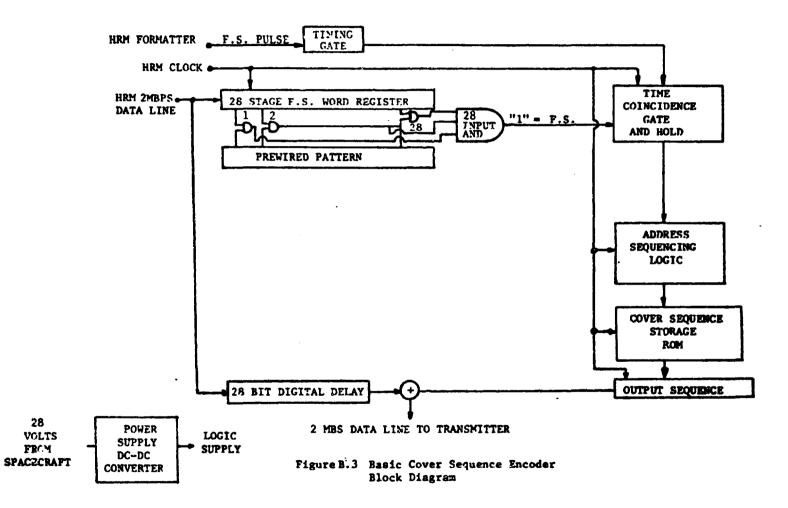

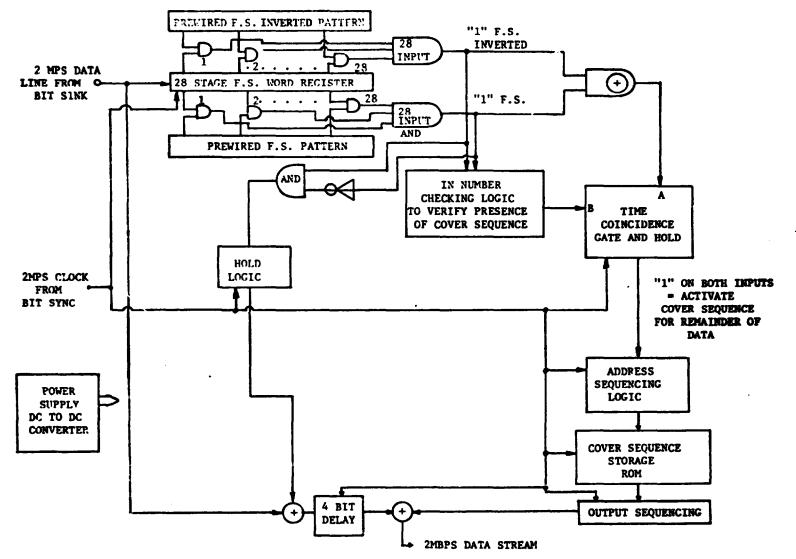

| B.3    | Basic Cover Sequence Encoder Block Diagram       | . 82 |

| B.4    | Cover Sequence Decoder Block Diagram             | . 83 |

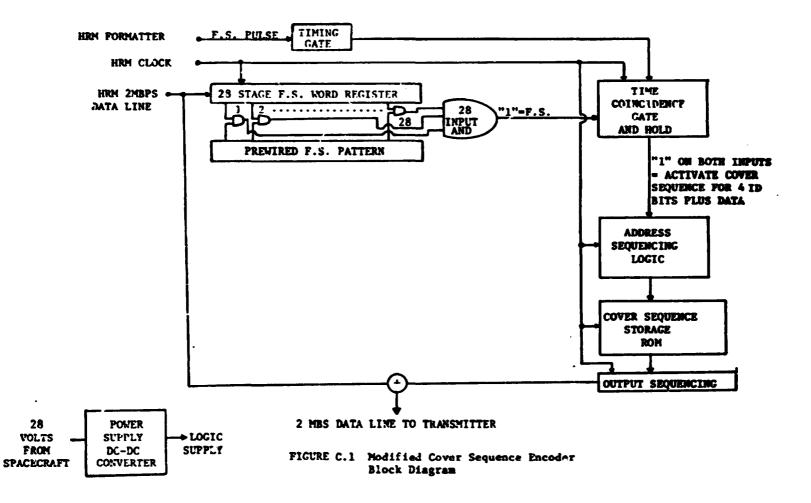

| C.1    | Modified Cover Sequence Encoder Block Diagram    | . 89 |

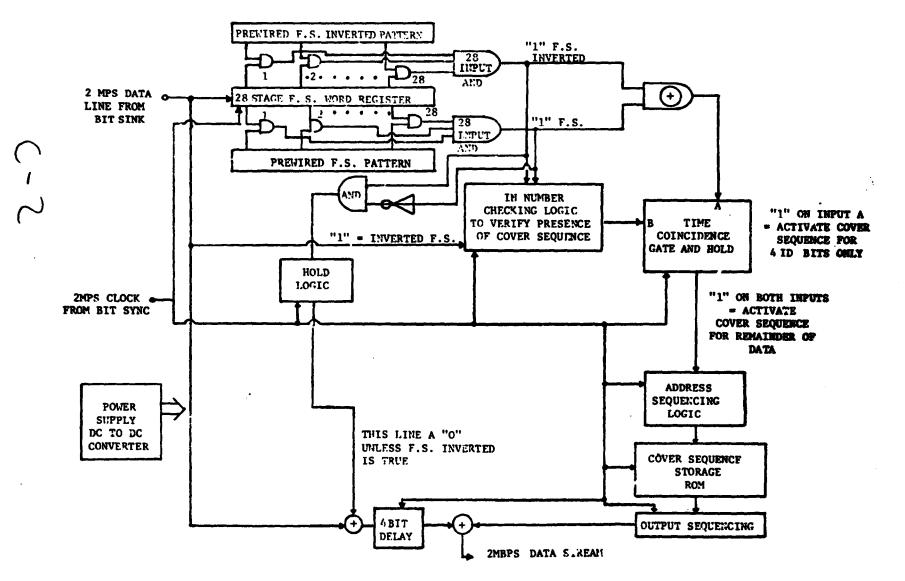

| C.2    | Modified Cover Sequence Decoder Block Diagram    | . 90 |

# LIST OF TABLES

Table

| 1.1 | Available Input Data via KU-Band Link 2             |    |

|-----|-----------------------------------------------------|----|

| 2.1 | Main System Constraints                             |    |

| 2.2 | Secondary System Constraints                        | ,  |

| 3.1 | Bit Transition Density Coding Choices 40            | I  |

| 4.1 | Zero-One Distribution for n=13 Maximal              |    |

|     | Length PN Sequence                                  | I. |

| 4.2 | Truncated Sequence for the CSG                      |    |

| 4.3 | Zero-One Distribution for the Truncated Sequence 51 |    |

| 4.4 | Alternate One-Zero Distribution for the             |    |

|     | Truncated Sequence                                  |    |

| 5.1 | Comparison of CSG With System Constraints           | 1  |

Page

# LIST OF SYMBOLS

| BCH   | Base-Chanduri-Hocquenghem                 |

|-------|-------------------------------------------|

| BER   | Bit-Error-Rate                            |

| BSR   | Bit-Slip-Rate                             |

| BSS   | Basic Self-Sync Scrambler                 |

| CSG   | Cover Sequence Generator                  |

| DM    | Delay Modulation                          |

| FBSRG | Feedback Shift Register Generator         |

| FM    | Frequency Modulation                      |

| HBTD  | High Bit Transition Density               |

| HRAA  | High Rate Acquisition Assembly            |

| HRDM  | High Rate Demultiplexer                   |

| HRM   | High Rate Multiplexer                     |

| KUSP  | Space Shuttle KU-Band Signal Processor    |

| LCM   | Least Common Multiple                     |

| Mbps  | Mega Bits Per Second                      |

| MCS   | Multi-Counter Scrambler                   |

| ML    | Maximal Length                            |

| PCM   | Pulse Code Modulation                     |

| QPSK  | Quadrature Phase Shift Keying             |

| SCS   | Single-Counter Scrambler                  |

| SL    | Spacelab                                  |

| SR    | Shift Register                            |

| ST    | Space Telescope                           |

| TDRSS | Tracking and Delay Relay Satellite System |

|       |                                           |

#### CHAPTER 1

#### INTRODUCTION

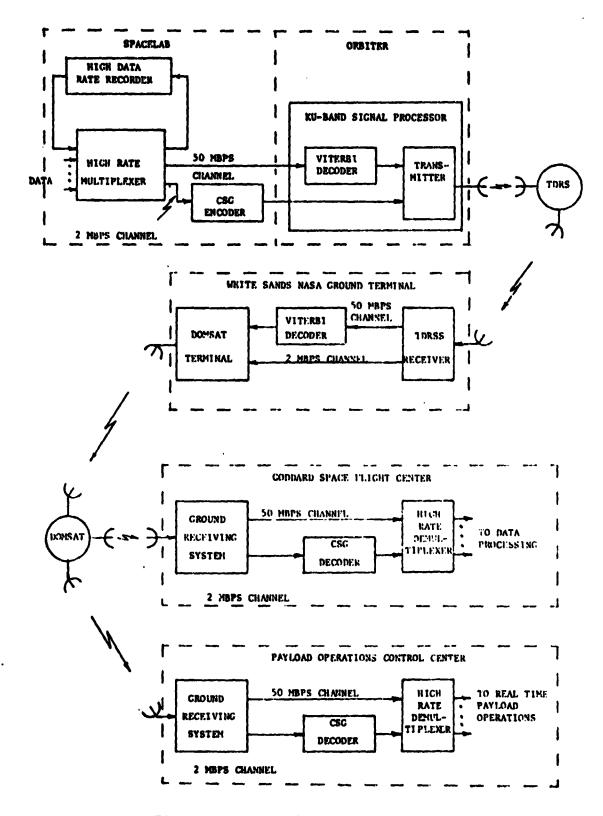

The Spacelab (SL) is an orbital laboratory which remains attached to the Space Shuttle for the duration of a mission. The SL will utilize the KU-Band communication system of the Shuttle for communication with the ground. Figure 1.1 is a simplified sketch of the return link. The following paragraphs give a brief description of the SL return link, for further information the reader is referred to References 1, 2, 3, and 4.

The onboard experiment data is collected by the High Rate Acquisition Assembly (HRAA). The HRAA consists of the onboard High Rate Multiplexer (HRM) plus associated High Rate Links, and the ground based High Rate Demultiplexer (HRDM). The return link, connecting the HRM and HRDM, utilizes the Shuttle KU-Band Signal Processor (KUSP) and the Tracking and Delay Relay Satellite System (TDRSS) which includes the receiving station, and the bit synchronizer. The return link will provide a bit-error-rate (BER) of at least  $1 \times 10^{-5}$  with a Bit-Slip-Rate (BSR) of less than  $1 \times 10^{-15}$  provided certain system constraints are met. Herein lies the problem; the SL data stream violates the transition requirements of the bit synchronizer. This will be further reviewed in Chapter II.

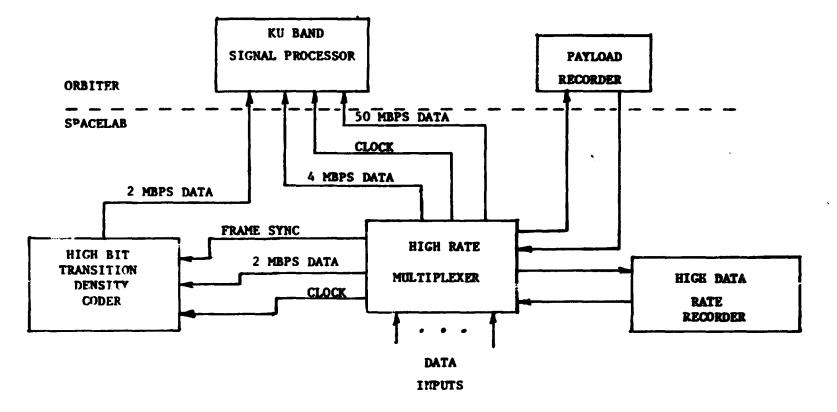

The HRM receives data from 18 experiments, 2 I/O units and 2 records, and outputs data to the KUSP and the 2 recorders. Sixteen of the 18 experiment channels are switchable and the other 2 are direct. The HRM time multiplexes these 16 channels with the other data including playback data from the recorders and serially transmitts the data to the KUSP.

The SL employs the KU-Band Link of the Shuttle and this link utilizes the two operation modes of the KUSP; Mode 1 - Quadrature Phase Shift Key (QPSK) modulation and Mode 2-FM modulation. The KUSP has three channels of input data in each mode. Table 1.1 lists the available input data in both modes. Figure 1.2 illustrates the interface between the HFM and the KUSP.

The HRM uses several different format structures for its output. Only the general user format, for frequencies less than 32 Mbps, will

Figure 1.1 KU Band Return Link

# TABLE 1.1 AVAILABLE INPUT DATA VIA KU-BAND LINK

PM MODE 1:

CHANNEL 1 - SAME AS FM Mode CHANNEL 2 - SAME AS FM MODE CHANNEL 3 - PAYLOAD DIGITAL OUTPUT, 2-50 MBPS WITH CLOCK, NRZ-L, M, OR S

FM MODE 2:

- CHANNEL 1 192 KBPS BI-PHASE-L PCM AND VOICE FROM NSP

- CHANNEL 2 SELECT ONE OF FOUR INPUTS

- PLI (NARROW BAND BENT PIPE FROM DETEACHED PAYLOAD)

- PAYLOAD DIGITAL OUTPUT, 16 KBPS-2MEPS, NRZ-L, M, OR S, OR 16 KBPS - 1.024 MBPS B1-PHASE L, M, OR S

- OPERATIONAL RECORDER DUMP

- PAYLOAD RECORDER DUMP

- CHANNEL 3 SELECT ONE OF FOUR INPUTS

- TV

- PAYLOAD DIGITAL OUTPUT, 16 KBPS-4 MBPS, NRZ-L, M, OR S

- PAYLOAD ANALOG OUTPUT, DC-4.5 MHz

- PLI (WIDE BAND BENT PIPE FROM DETACHED PAYLOAD)

Figure 1.2 High Rate Multiplexer to KU-Band Signal Processor Interface

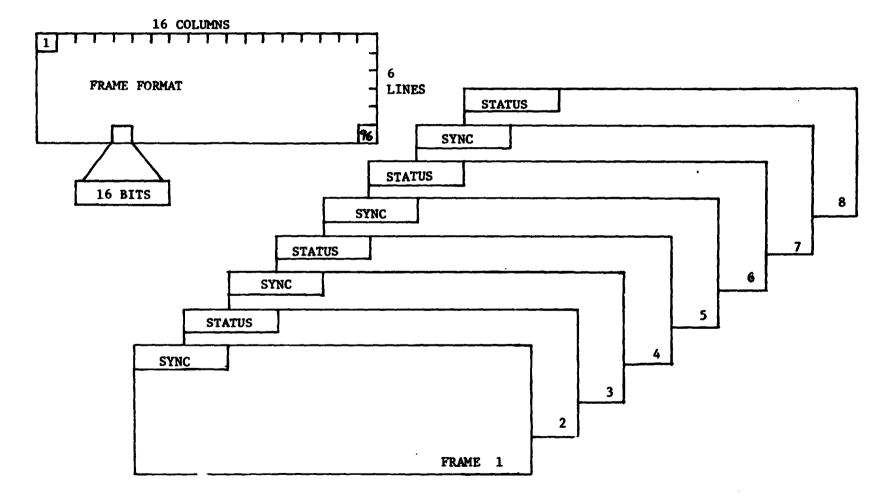

be discussed. For further information concerning the HRM formats; see references 1 and 2. The user format consists of eight frames of 96 words each (768 words), each frame beginning with a sync or a status word. The normal frame is composed of 6 lines by 16 words. Since each of the 21 inputs to the HRM operate at bit rates assynchronous to the output bit rate, fill data is required. The 16th or last word of each line is a fill data indicator. The HRM employs a unique method to provide the necessary fill data words. When a line of data requires fill, all the valid data words to the right of the fill word are shifted to the left thus making the fill word the 15th word of the data line. The system requires that the fill data (stuffing) indicator shall be constructed such that the probability of error in interpreting the indicator is less than  $10^{-10}$ . The HRM utilizes a (31,16,3) BCH code to satisfy the required BER for the stuffing indicator. The HRM encodes the 16 bit stuffing indicator into a 31 bit BCH code word capable of correcting 3 errors per word. When more than one fill word is needed, the valid data words are again shifted left and the 14th word of the previous line is inserted into the 14th word of the present line.

The general input data format is illustrated in Figure 1.3. The input data to the HRM is as follows:

| 18 experiments | NRZ-L         |                                 |

|----------------|---------------|---------------------------------|

| HDRR           | NRZ-L         | Reverse playback 2 Mbp only     |

| PLR            | Manchester II | Reverse 1Mbp only               |

|                |               | (Must be playback through HRDM) |

Figure 1.3 General User Format

#### **CHAPTER 2**

#### STATEMENT OF PROBLEM AND CONSTRAINTS

#### 2.A THE PROBLEM

An investigation of the effect of low bit transition density on the performance of the Channel 2 KU-Band return link was conducted. The results of this investigation indicated the SL will not meet the minimum specifications of the TDRSS Users' Guide with respect to the bit synchronizer. The end result of this failure to meet the bit synchronizer (sync) specifications is loss of lock by the bit sync and subsequent loss of data for an undefined period of time (Reference 5). To alleviate this problem the SL must increase the bit transition density on the Channel 2 KU-Band return link to a minimum of one bit transition every sixty-four bits and sixty-four bit transitions within five-hundredtwelve bits.

There are several different methods that may be employed to provide the data stream with the macessary bit transition density. These methods are discussed in more detail in Chapter III. This chapter deals mainly with the problem and the constraints caused by the system. There are four main constraints placed on the HBTD coder. They are listed in Table 2.1 and discussed in the following paragraphs.

#### 2.B PRIMARY SYSTEM CONSTRAINTS

The primary objective of the HBTD modification is to increase the bit transition density of the data stream to at least one bit transition every sixty-four channel symbols and sixty-four bit transitions every five-hundred-twelve channel symbols. This is the absolute minimum requirement by the TDRSS bit synchronizer at White Sands, New Mexico to provide the desired BSR of  $10^{-15}$  with the SL signal characteristics.

Since the 2Mbit channel is expected to operate at the maximum rate of 2 Mbps for maximum utilization, the modification must not increase the channel errors. The system requires that the fill indicator must be able to locate the fill data with an accuracy of no less than  $10^{-10}$ . The fill indicator is a (31,16,3) BCH code. A (31,16,3) BCH code takes 16 information bits and converts them into a 31 bit code word capable of correcting 3 errors. Since the channel bit error rate affects the fill TABLE 2.1 HIGH BIT TRANSITION DENSITY (HBTD) CODE CONSTRAINTS

- 1. THE HBTD CODE MUST HAVE AT LEAST ONE TRANSITION EVERY 64 BITS AND AT LEAST 64 TRANSITIONS WITHIN 512 BITS

- 2. THE CODE MUST NOT INCREASE THE PRESENT BANDWIDTH, NOR DECREASE THE INFORMATION RATE.

- 3. IT MUST BE COMPATIBLE WITH THE EXISTING BCH CODE. (IMPLIES A SCHEME WHICH PRODUCES MULTIPLE DECODER ERRORS PER DISCRETE CHANNEL ERRORS WOULD BE INCOMPATIBLE WITH BCH CODE.)

- 4. THE HARDWARE IMPLEMENTATION MUST HAVE MINIMAL DESIGN IMPACT ON THE PRESENT SYSTEM.

indicator word, any modification that increases the channel error would degrade the fill indicator. For example, if the system modification produced only one additional error per channel error, then the reliability of the fill indicator, as shown below, would be  $4.6 \times 10^{-8}$ , which is unacceptable.

To illustrate the problem consider the effects of differential encoding on BCH word error probability. Assuming the RF channel has an average random error rate, due to additive white gaussian noise, corresponding to 1 bit in 100,000 (that is an average bit error rate of  $1 \times 10^{-5}$ ) one may calculate the probability of an erroneous decoding of a BCH coded word with use of NRZ-L code and also with use of a differental encoding such as NRZ-M or NRZ-S.

The model to be used is:

#### Using NRZ-L Coded Data Stream

A single error on the RF channel in the BCH code word will result in a single error in the data input to the BCH decoder. The BCH code word can correct up to and including 3 errors out of 31 bits.

Thus the probability of erroneous decoding of the BCH word (PEBCH) is

$$PEBCH = 1 - [P(0) + P(1) + P(2) + P(3)]$$

(2.1)

where:

| P(0) = | Probability of no errors in the 31 bit word |

|--------|---------------------------------------------|

| P(1) = | Probability of 1 error in the 31 bit word   |

| P(2) = | Probability of 2 errors in the 31 bit word  |

| P(3) = | Probability of 3 errors in the 31 bit word  |

In general P(X) is expressed as

$$P(X) = \begin{pmatrix} N \\ X \end{pmatrix} p^{X} q^{N-X}$$

(2.2)

where

p is the probability of an RF channel error

q is the l - p

X is the number of errors in the word

N is the number of bits in the word.

The expression  $\begin{pmatrix} N \\ X \end{pmatrix}$  relates to the number of different ways in which X errors occur in an N bit word and

$$\binom{N}{X} = \frac{N!}{(N-X)!X!}$$

(2.3)

#### Using NRZ-M or NRZ-S (Differential Encoding) Coded Data Stream

A single error on the RF channel in the BCH code word will result in two adjacent errors on the data stream input to the BCH decoder. (Reference is any text in communications, in particular: Reference 16, page 324.)

Thus we have as the probability of erroneous decoding of the BCH word with Differential Encoidng (PEBCHDE)

$$PEBCHDE = 1 - [P(0) + P(1)]$$

(2.4)

Where the expressions P(0) and P(1) are as defined in the previous case. Note this expression for PEBCHDE reflects the fact that 2 RF channel errors in the BCH word will result in 4 errors presented to the BCH decoder and this will result in erroneous decoding.

These calculations were performed using a double precision digital computer program.

The results are

PEBCH =  $3.01841884819964434 \times 10^{-16}$ PEBCHDE =  $4.64910190316402087 \times 10^{-8}$

One sees a significant difference in the error performance due to erroneous decoding of BCH words!

For a 50 Mbps data stream the average length of time between erroneous decoding of the BCH word would be approximately

160 seconds average between erroneous decoding of BCH words using differential encoding (NRZ-M or NRZ-S)

16,000,000,000 seconds average between erroneous decoding of BCH words using NRZ-L encoding.

The unacceptability of adding additional errors to the system is obvious.

The fourth criterion, minimal impact on the present system, results from the fact that the system is in the production stage and any major changes would be very costly. Approximately \$100,000 cost results from a minor change alone due to the paper work required.

#### 2.C SECONDARY SYSTEM CONSTRAINTS

Additional criteria, dealing with the implementation, results from the expected characteristics of the data stream. The modification must pass unaltered data emanating from any source other than the HRM and data rates greater than 2 Mbps from the HRM. These constraints result from the physical location of the modifications and the operational functions of the HRM. All data emitted from the HRM via the 2 Mbit channel will be NRZ-L. The above stated constraints apply to both the encoder and decoder. There decoder must also resolve the phase ambiguity problem which results when a Bi-Phase NRZ-L data is used. Since NRZ-L employs a high level to represent a one and low level to represent a zero, it is possible for the data stream to become inverted. That is to say a transmitted one is received as a zero and vice versa. Therefore the decoder must be capable of detecting and correcting the inverted data stream. These secondary system constraints are listed in Table 2.2.

#### TABLE 2.2 SECONDARY SYSTEM CONSTRAINTS

-

.

- 1. HBTD CODE MUST PASS UNALTER ANY DATA STREAM WHOSE RATE IS GREATER THAN 2 MBPS.

- 2. THE CODE MUST PASS UNALTER ALL DATA STREAMS WHICH EMANATE FROM SOURCES OTHER THAN THE HRM REGARDLESS OF THE DATA RATE.

- 3. THE HBTD ENCODER MUST HAVE A BYPASS MODE.

.

4. THE HBTD CODE MUST RESOLVE THE "BIT AMBIGUITY" PROBLEM INHERENT TO THE CHANNEL 2 RETURN LINK. .

.

#### CHAPTER 3

#### DIFFERENT METHODS AVAILABLE TO ALLEVIATE THE PROBLEM

Two basic types of modifications exist to improve the Bit Transition Density of the Channel 2 data stream to the minimum requirements of the bit synchronizer. They are: (1) Use an alternative PCN waveform or (2) modify the data stream. The remainder of the section is devoted to describing several methods for accomplishing these modifications.

#### **3.A ALTERNATE PCM WAVEFORM**

The 2 Mbit channel presently employs a NRZ-L waveform. There are several other binary waveforms available. Several of the most common are shown in Figure 3.1. The most frequently used waveforms, for high bit transition density applications, are the Bi-Phase and Delay Modulation waveforms. Both are widely used in the tape recording industry.

### 3.A.1 Bi-Phase

The three main types of Bi-Phase waveforms are; Bi-Phase Level, Bi-Phase-Mark, and Bi-Phase-Space. Bi-Phase Level is also called Split Phase or Manchester Code. All three waveforms provide at least one transition for each bit cell. They produce single output errors for a single input or channel error. The hardware required to implement each is moderate in complexity. All three Bi-Phase waveforms are self-synchronizing. The main disadvantage of all three is that Bi-Phase modulation requires twice the bandwidth of the present NRZ-L to provide the same information rate. Therefore the use of Bi-Phase would require either an increase in the present bandwidth or a decrease in the information rate. Neither case is acceptable since it violates one of the main system constraints.

#### 3.A.2 Delay Modulation

Delay Modulation (DM) is a procedure for encoding binary data into rectangular waveforms of two levels according to the following rules for DM-M:

| CODE<br>DESIGNATIONS  | LOGIC<br>WAVEFORM<br>LEVELS | CODE WAVEFORMS |

|-----------------------|-----------------------------|----------------|

| <b>NRZ -</b> L        | "1"<br>"0"                  |                |

| NRZ – M               | "1"<br>"0"                  |                |

| NRZ - S               | "1"<br>"0"                  |                |

| BI¢ - L               | "1"<br>"0"                  |                |

| BI - R <sup>(1)</sup> | "1"<br>"0"                  |                |

| BI - S <sup>())</sup> | "1"<br>"0"                  |                |

| DM – M                | "t"<br>"1"                  |                |

| DM – S                | "1"<br>"0"                  |                |

. ....

| NON-RETURN-TO-ZERO-LEVEL                     |

|----------------------------------------------|

| "One" is represented by one level.           |

| "Zero" is represented by the other level.    |

| NON-RETURN-TO-ZERO-MARK                      |

| "One" is represented by a change in level.   |

| "Zero" is represented by no change in level. |

| NON-RETURN-TO-ZERO-SPACE                     |

| "One" is represented by no change in level.  |

CODE DEFINITIONS

# <u>%</u>

"Zero" is represented by a change in level.

#### BI-PHASE LEVEL (SPLIT PHASE)

Level change occurs at center of every bit period.

- "One " is represented by a "one" level with the transition to the "zero" level.

- "Zero" is represented by a "zero" level with the transition to the "one" level.

#### "BI-PHASE-MARK

Level change occurs at the beginning of very bit period. "One" is represented by a midbit level change. "Zero" is represented by no midbit level change.

#### BI-PHASE-SPACE

Level change occurs at the beginning of every bit period. "Onc" is represented by no midbit level change. "Zero" is represented by a midbit level change.

#### DELAY MODULATION-MARK (MILLER CODE)

"One" is represented by a level change midbit time.

"Zero" followed by a "zero" is represented by a level change at the end of the first "Zero" bit. No level change occurs when a "zero" is preceded by a "one".

#### DELAY MODULATION-SPACE (MILLER CODE)

- "Zero" is represented by a level change at midbit time.

- "One" followed by a "one" is represented by a transition at the end of the first "one" bit. No level change occurs when a "one" is preceded by a "zero".

- 1. A one is represented by a transition from one level to the other at the midpoint of the bit cell.

- 2. A zero is represented by no transition unless it is followed by another zero. The case of consecutive zeros is represented by a transition at the end of the leading zero bit cell.

In the case of DM-S the rules for ones and zero are enterchanged. These rules are illustrated in Figure 3.1.

Delay Modulation has several attractive properties:

- The majority of the signalling energy lies in frequencies less than one-half the symbol rate.

- The power spectrum is small in the vicinity of f = 0 (that is at D.C.).

- 3. DM provides at most one transition per bit cell and at the least 2 bit transitions every 3 bit cells; thus, providing a bit stream with 3 very high bit transition density.

These properties provide DM with the advantage of inherent selftiming information using phase modulation which is not present in NRZ-L, while requiring approximately the same bandwidth as NRZ-L. DM is also suitable for use with tape recorders, especially when higher packing density is required, or with systems which require high bit transition densities.

DM requires a given 3 bit sequence to assure proper bit sync. This sequence is 101 for DM-M. This sequence has a high probability of occurring one or more times in any random data bit stream. The probability that one or more 101 bit sequences will occur increases rapidly as the number of bits in the data sequence increases. The following equation may be used to obtain a close approximation of the probability of 101 occurring n or more times in m bits (the number of bits per sequence).

$$P_{m}(101 \ge n) = 1 - P_{m}(101 \le n) = 1 - (P_{m}(101 = 0) + P_{m}(101 = 1) + \dots$$

$$P_{m}(101 = (n-1))$$

(3.1)

Where:

$$P_{m}(101=r) = {k \choose r} {q_{0}^{k-r}} {p_{0}^{r}}$$

$$q_{0} = \text{ the probability of any 3 bits not being 101 = \frac{7}{8}$$

$$p_{0} = \text{ the probability of any 3 bits being 101 = \frac{1}{8}}$$

$$k = m - 2$$

$${k \choose r} = \frac{k!}{(k-r)!r!}$$

For example, let m be 16 (for 14 binary bits) then the probability of a 101-bit sequence occurring one or more times is:

$$P_{16}(101=1) = 1 - P(101=0)$$

=  $1 - {\binom{14}{0}} {\binom{7}{8}}^{14} {\binom{1}{8}}^1 = 1 - \frac{14}{14!0!} {\binom{7}{8}}^{14} = 1 - {\binom{7}{8}}^{14} = 1 - .154 = .846$

In other words, there is a 84.6% probability of a 101 pattern occurring and hence providing bit sync within a 16 bit sequence. Thus, one should expect a bit sync lock within a very short time upon the start up of a DM encoded sequence. The main disadvantage of Delay Modulation is that single errors into the decoder will yield double errors out of the decoder. This results from the comparison of the present and most recent bit to determine the value of the previous bit. Thus the property that produces the improved bit transition density also makes DM incompatible with the BCH code used by the fill indicator.

#### 3.B DATA STREAM MODIFICATION

There are several means of modifying the present data stream to meet the bit transition requirements. The first method that comes to mind is to simply invert every other bit or alternate bit inversion. Other means such as differential encoding, a bit insertion technique or error correcting encoding techniques are commonly used to improve

(3.2)

the bit transition density of a data stream. Bit scrambling is another technique which is employed to increase the bit transition in a sequence. Each of these methods are discussed in the following paragraphs.

All the aforementioned techniques require the same bandwidth for the same information rate as the present system.

#### 3.B.1 Alternate Bit Inversion

Alternate bit inversion is probably the simplest method for increasing the transition density. This technique inverts every other bit of the data stream. It yields excellent results in the case of long sequences of bits of the same value. The implementation is very simple except for the synchronization with the data stream and a bit slip will result in the inversion of the original data stream. Single channel errors produce single output errors. The main disadvantage of this technique is the inability to guarantee the bit transition density. In the case of an alternating input data stream, this procedure will produce an output sequence of bits of the same value equal in length to the input sequence. Since the SL data stream is excepted to contain long runs of alternating bits this method must be discarded. Additional logic could be added to the encoder and decoder to prevent this occurrence but the logic required would be quite complex and require additional considerations.

#### 3.B.2 Differential Encoding

The use of differential encoding as a means of improving the bit transitions density has received considerable use in other systems, especially when the data stream contains long strings of bits having the same value; all ones or all zeros. This technique has advantage over alternate bit inversion in that an alternating bit sequence retains half of the original transitions. There are two types of differential coding, NRZ-M and NRZ-S as illustrated in Figure 3.1. NRZ-M uses a change of state to indicate a one and no change for zero, while NRZ-S indicates a zero by a change in level and no change for a one. Differential encoding provides a 50% transition density for an alternating input data stream and a 100% transition density for by a change of state, one for NRZ-M and zero for NRZ-S. If the values is the level represented by no change, nothing is gained by different encoding. Therefore one must design for the level which is most dominant in the data stream and know that the sequence lengths of the other level will not result in a loss of lock by the bit sync. Another disadvantage of differential encoding is that single input errors produce double output errors. Since the difrematial encoding propagates the number of channel errors and can be designed for only a single case of bit sequence of the same value instead of for both, it must be eliminated as a possible solution.

#### 3.B.3 Bit Insertion

Bit insertion technique are also commonly used to increase bit transition density. There are several different types of bit insertion techniques. Some add bits to the data stream while others use blocks of bits to replace certain data sequences. However, all of these techniques share the need for a complex timing and counting circuitry. The basic concept for all insertion techniques is the need to recognize when to insert and when to remove their speicfied patterns. For example, assume a bit replacement technique is to be used to meet the six:y-four in five-hundred-twelve requirement. The obvious way to guarantee that the data stream would meet this requirement would be to have at least one transition every eight bits. This would mean that an eight bit pattern would have to be inserted in place of any eight bit sequence of the same value. The selection of the particular pattern to be used for insertion must be chosen in a manner similar to that of a synchronization pattern for frame sync. The insertion sequence must meet the following:

- The probability of it occurring naturally in the data stream must be extremely small. Since it is very desirable to avoid false recognition at the receiver, which would result in a misinterpretation of valid data for inserted data.

- The inverse of the sequence must also be available. Since the bit sequence of the same value may be either ones or zeros, two separate sequences are needed.

18

3. The effects of channel errors must be considered. Should the ground receiver accept no errors, one error, two errors, etc? If a short sequence such as the eight bit one used in the example is selected, then the no error case would probably be best. The probability of no errors in any 8 bits is .99992 thus the probability of not recognizing the inserted pattern due to channel error would be about  $8 \times 10^{-5}$ , slightly greater than the channel error rate of  $1 \times 10^{-5}$ . In the one error case the probability of false synchronization detection would be much higher than the gain in recognizing a valid insertion with a single error.

By employing this simple insertion technique, one does not take advantage of the natural transition that might occur prior to and following the sequence of the same value. As stated above the timing and clocking circuitry would be complex even for this simple case. For this reason bit insertion is not the most favorable method although it can be designed to meet the system constraints given in Chapter 2. But it should be noted that only the replacement type can be employed. The inserting of additional bits would decrease the information rate and therefore this type is not acceptable. Since the amount of additional bits cannot be predetermined.

#### 3.B.4 Error Encoding

Telecommunication systems often employ different types of error correcting codes to improve their bit transition density. In this manner, the error correcting codes provided two services. First, they improve the channel bit error rate and second, they provide an increase transition density. This type of method is employed by the 50 Mbit channel of the shuttle as well as by many other systems. All these systems add addition bits to the data and thus decrease the information rate. Therefore they are not viable candidates for the HBTD modification, but are included in the following for completeness.

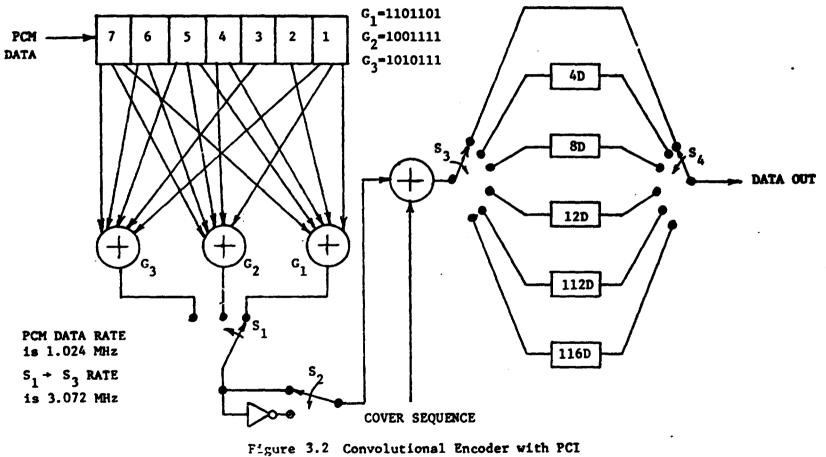

The folio-ing discussion concerning the output symbol transition density of the 1/3 convolutional encoder with alternate symbol inversion is based on the material by M.K. Simon and J.F. Smith in Reference 6 and

19

illustrated in Figure 3.2. Simon and Smith have determined, for a particular class of convolutional codes, that alternate symbol inversion assures a maximum transition-free run of output symbols, and hence its minimum transition density. This maximum length is independent of the data source model, independent of the code connections, and dependent only on the code constraint length and rate. Simon and Smith separate all 1/vconvolutional codes into three classes of codes: Veven, Vodd for transparent codes, and v odd for nontransparent codes. A transparent code is one which provides the complement of the output sequence for the complement of the input sequence. A simple test to determine if a code is transparent is each row of the generator matrix <u>C</u> has an odd number of ones then the code is transparent.

The generator matrix  $\underline{C}$  for the 1/3 convolutional code employed by the Space Telescope (ST)

$$\underline{\mathbf{c}} = \begin{bmatrix} 1 & 1 & 0 & 1 & 1 & 0 & 1 \\ 1 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 & 1 & 1 \end{bmatrix}$$

(3.3)

where the right hand column represents the present input and the left hand column represents the oldest (content of the last shift register K, the code constraint length) input.

Since v = 3, odd and each row of <u>C</u> contains an odd number of ones, the convolutional code is a member of case 2. Simons and Smith state for v odd and transparent codes, the only input bit sequence that will produce an output alternating sequence longer than N<sub>max</sub> symbols, where N<sub>max</sub> is defined as

$$N_{max} = K + \left[\frac{K-1}{V-1}\right] - 1 + V$$

(3.4)

K = the code constraint length; [X] denotes the smallest integer greater than or equal to X.

is the alternating sequence. Furthermore, if the encoder is such that the alternating input sequence produces the alternating output sequence, then this output sequence can continue indefinitely, i.e., alternate symbol inversion will not produce a finite transition-free symbol sequence.

and Cover Sequence

Reference 6 provides a test to determine if a case 2 code will produce an alternating output for an alternating input. Split the generator matrix <u>C</u> into two matrices  $\underline{C}_{odd}$  and  $\underline{C}_{even}$  where  $\underline{C}_{odd}$ is composed of all the odd columns of <u>C</u> and <u>C</u><sub>even</sub> all the even columns. If the number of ones in each row of the matrix formed by stacking  $\underline{C}_{odd}$  on top of  $\underline{C}_{even}$  alternates even, odd, even, ... or vice versa, then an alternating input sequence will produce an alternating output sequence. Testing the generator matrix, it is found the number of ones in each row of the test matrix does not alternate even, odd or vice versa. Therefore the maximum number of transition-free output symbols from the 1/3 convolution encoder with alternate symbol inversion is

$$N_{\text{max}} = K + \left[\frac{K-1}{v-1}\right] - 1 + v$$

= 7 +  $\left[\frac{7-1}{3-1}\right] - 1 + 3$

= 12. (3.5)

The maximum number of transition-free output symbols was also determined to be 12 in References 7 and 8. Magnavox in Reference 7 utilized an extensive computer analysis to arrive at a maximum of 12 Baument, et al., Reference 8, used a slightly different mathematical approach to obtain 12 as the maximum bits between transitions and therefore the system is guaranteed to meet the 1 in 64 requirement.

Simon and Smith also prove in Reference 6 the 11-bit input sequence Oll10100100 yields the output Ol000000000001. Neither this output sequence nor its compliment can be repeated within the next 33 output symbols. The next input will produce at least one additional bit transition therefore the average bit transition for this worse case plus one additional input is 2 transitions per 16 output symbols which yields an average of 1 transition every 8 output symbols. Therefore the output of the 1/3 convolutional encoder with alternate bit inversion and generator matrix given in Equation 3.3 will meet both the 1 transition per 64 bits and 64 transitions in 512 or 3n average of 1 transition every 8 bits. If the 12-bit input sequence is 01110100100 the output will be 01000000000001100.

If the 12-bit input sequence is 01110100101 the output will be 010000000000001011.

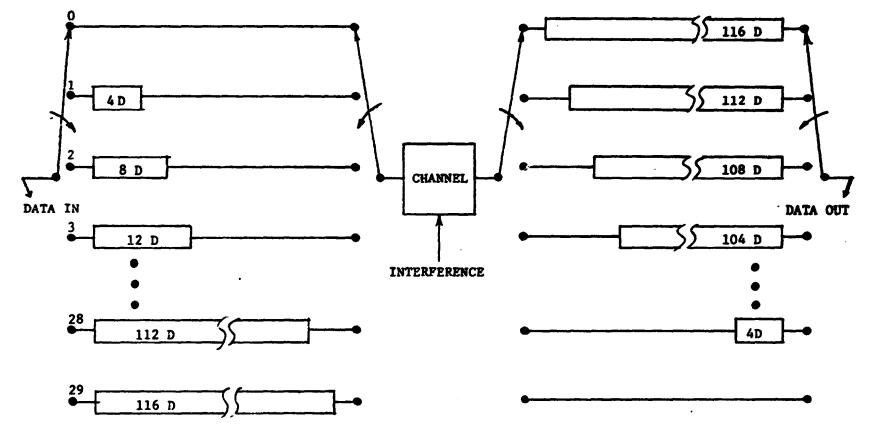

Since the output of the 1/3 rate convolutional encoder will have a transition at least every 13 bits independent of the data input, it is not necessary to examine the equipment preceeding the encoder. However if the channel interleaver is utilized it is necessary to determine if it is possible to obtain 64 or more symbols out of the interleaver without a transition. The channel interleaver is shown in Figure 3.3. This interleaver will take any two symbols within 30 of each other and separate them by at least 119 bits. Equation 3.6 may be used to express a typical output symbol  $b_i$ in terms of the input symbols  $a_i$ .

$$b_{j+i} = a_{j+i-4x30} = a_{j+i-120_i} = a_{j-119_i} \frac{j \ge 119_i}{j \le 119_i}$$

(3.6a)

$b_{j+i} = 0$   $j \le 119_i$  (3.6b)

where

j = 0, 30, 60, 90, 120, ... i = 0, 1, 2, 3, ..., 29

Therefore, a typical output sequence of the interleaver would resemble a sampling of the input sequence with the samples being taken every 119<sup>th</sup> bit for sequences up to 30 bits in length. In order for the interleaver to have an output of 64 consecutive symbols of the same value, the input data must be such that samples of the input sequence separated by 119 symbols be of the same value. The length of input symbols corresponding to 64 output symbols is approximately 3511. Also noting that the output of the interleaver is combined with a PN cover sequence of length 30, it would appear highly unlikely that a string of 64 ones or zeros will occur, however due to the systematic construction of the components of the system, it is possible that a

*r*

1

٠

Figure 3.3 Periodic Convolutional Interleaver and Deinterleaver

,

.

1.00 10 10 10 10

sequence of data does exist that will yield a string of 64 output symbol without a transition. Since the actual structure of the data is presently unavailable it is not possible to examine this problem more closely. It would be necessary to examine very closely the structure of the data and how that structure is effected by the various components of the system.

#### 3.B.5 Bit Scramblers

A bit scrambler is a digital machine which maps a data sequence into a channel sequence and with the special mapping of a periodic data sequence into a periodic channel sequence with period much greater than the data period. For periodic source, the channel sequence produced by the scrambler, also, has many transitions.

The basic element of all scramblers is a feedback shift register generator (FBSRG) with tap polynomial h(x); where h(x) is a primitive polynomial over the field GF(p), p is prime. The manner in which this element is connect determines whether the scramblers is self-synchronizing or not. The self-synchronizing group utilizes the data sequence to drive the FBSRG. The non-self synchronizing group, often call reset, utilizes the FBSRG as a maximal length (ML) generator and modulo adds the ML sequence to the data. Each group is discussed in the following paragraphs.

#### 3.B.5.a Self-Synchronizing Scramblers

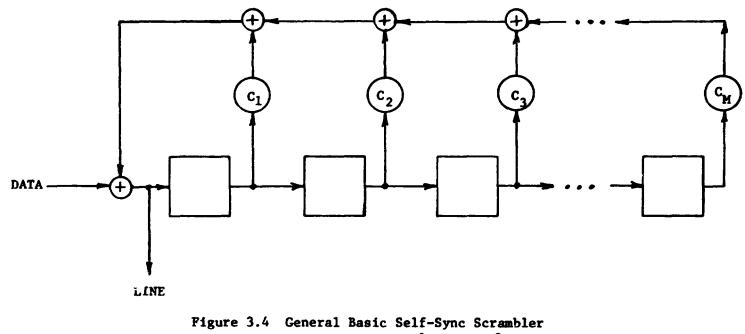

The self synchronizing group maybe subdivided into two types called multi-counter scramblers (MCS) and single-counter scramblers (SCS). Both types consists of a "basic self-sync scrambler" and a "monitoring logic". Figure 3.4 illustrates the "basic self-synchronizing scrambler" (BSS). The logic circuit determines the scrambler type Figures 3.5 and 3.6 show the MCS and SCS respectively.

The BSS when excited by a periodic sequence of period \* 's' will respond with a periodic line sequence which has either period 's' or a period which is the least common multiple (LCM) of 's'

<sup>\*</sup>A sequence has period 's' if it is the smallest period in the sequence.

h(x) =  $X^{m}$  +  $C_{1}X^{m-1}$  +  $C_{2}X^{m-2}$  + ... +  $C_{m}$

where  $C_i = 1$  or 0 and h(x) is a primitive polynomial over GF(2) of degree M. C must equal one.

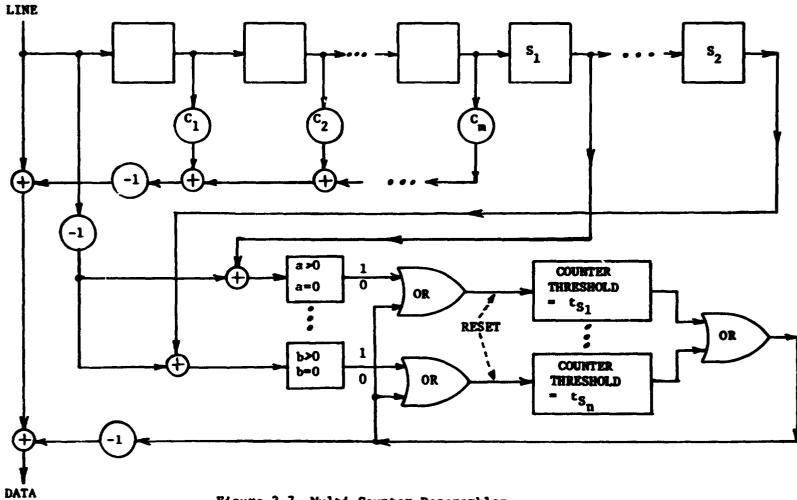

Figure 3.5 Multi-Counter Scrambler

.

•

•

.

•

Figure 3.6 Single Counter Scrambler

and  $p^{m-1}$  (denoted by LCM(s,  $p^{m}$ -1). The period with which the scrambler responds is a function of the initial values stored in the scrambler storage elements, (its initial state) and there is only one such state (for each phase of input sequence) for which the line sequence has period 's'. For all other such initial states the line sequence has the larger period. The preceding statements are Savage's Theorem 1 for BSS (See Reference 9 for proof).

The logic circuit employed by the MCS and SCS are used to detect the presence of a periodic sequence of low period on line and alter the starting state of the BSS to insure the line sequence has period of LCM  $(s,p^m-1)$ .

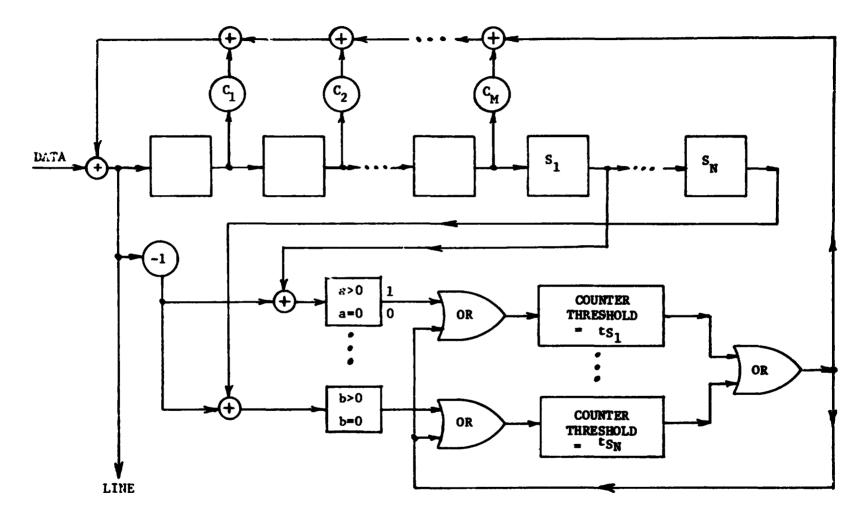

# 3.B.5.a.l Multi-Count Scrambler

The logic used by the MCS is more general than the SCS and allows for the simultaneous detect of sequences of several periods. The MCS employs N counters, one for each period 's<sub>i</sub>',  $1 \le i \le N$ , and the i<sup>th</sup> counter will generate +1 if it reaches its threshold  $t_{s_i}$ . The counter is reset whenever the reset lead is nonzero so that  $t_{s_i}$ consecutive zeros on the reset lead of the i<sup>th</sup> counter will cause it to reach its threshold. Whenever a counter reaches its threshold a '1' is added to the feedback line of the BSS, thereby change the state of the BSS. Thus, the line sequence will then be changed from period 's<sub>i</sub>' to period  $LCM(S_i, p^m-1)$  where the i<sup>th</sup> counter was the one reaching threshold. At the same time, all counters are reset.

Thus, the MCS shown in Figure 3.5 will scramble a periodic sequence of period 's' if 's' divides ' $s_i$ ' (denoted by 's'/' $s_i$ ') for some i,  $1 \le i \le N$ , and will produce a periodic line sequence of period LCM (' $s_i$ ',  $p^m$ -1) if the following two conditions are met:

1) The tap polynomial h(x) of degree m is primitive over GF(p) where data sequences have components from GF(p).

2) The thresholds  $t_{s_1}$ ,  $1 \le s_1 \le N$  are chosen as

$p^m-1$  is the period of the maximal length sequence generated by BSS in the absence of an input.

$$t_{e_{\underline{i}}} \geq (m-1) + \max 'e_{\underline{i}}' . \qquad (3.7)$$

$$l \leq j \leq N$$

$$j \neq i$$

If all input periods divide 's ', then the statement holds when condition (i) is met and a threshold of  $t_{s} \ge m$  is used. The above is Savage's MCS theorem. (See Reference 9 for proof.)

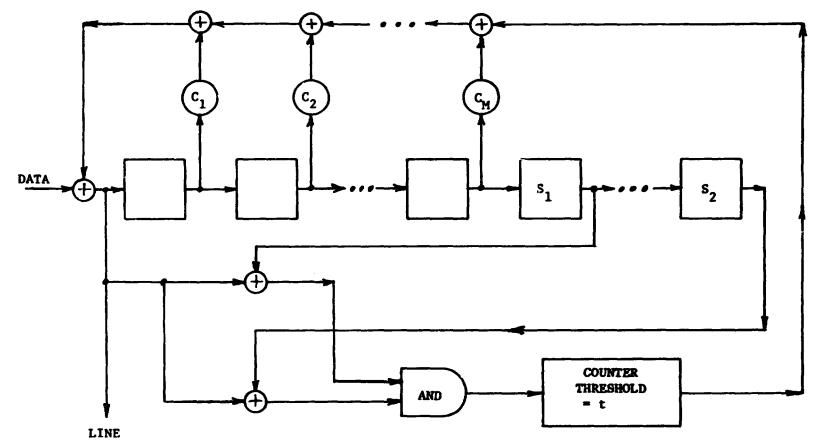

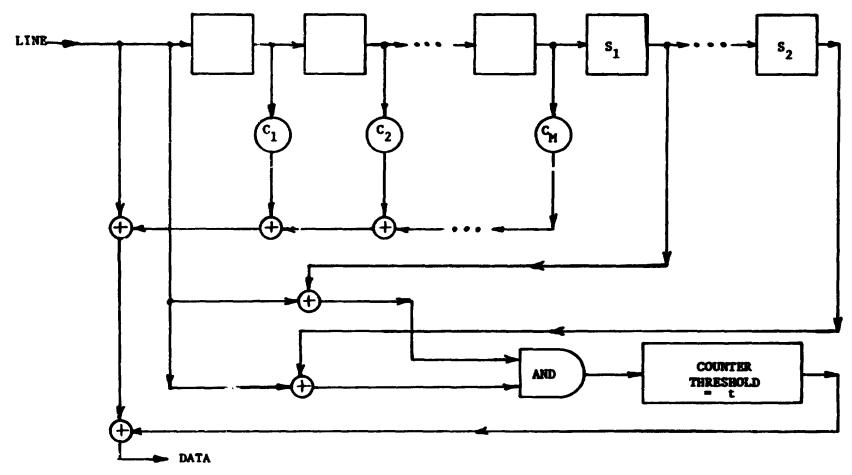

### 3.B.5.a.2 Single-Counter Scramblers

The SCS is designed to scramble periodic binary sequences whose periods divide either  $s_1$  or  $s_2$  or both. Since the SCS utilizes only one counter, it may be less costly to build than the MCS in some case. The SCS operates in the same manner as the MCS.

Savage's SCS theorem states that a SCS exists which will scramble all periodic binary sequences with periods which divide  $s_1'$  or  $s_2'$  where  $s_1 < s_2$  and  $s_1$  does not divide  $s_2$  (denoted by  $s_1 \ge s_2$ ) if

the tap polynomial h(x) of degree 'm' is primitive over GF(2).

2)  $s_1$  and  $s_2$  are relatively prime to  $2^m-1$ , and

3) a counter threshold, t,  $t \le s_2(2^m - 1) - 2^{m-1} + 2$  is chosen. See Reference 9 for proof.

### 3.B.5.a.3 Transition Density for Self-Synchronizing Scramblers

Transitions occur frequently in a scrambled periodic sequence and in one period of a scrambled sequence there are approximately half as many transitions as there are digits. These have been illustrated in Reference 9 when the source is binary and the scrambler input periods are relatively prime to  $2^{m}$ -1, where m is the size of the BSS.

Assuming the BSS generates a line sequence with period 'l' when the input has period 's', the source is binary, the BSS has 'm' stages, and 's' is relatively prime to 2<sup>-1</sup>-1; then 'l' is an 's'(2<sup>m</sup>-1) component vector. If the binary line sequence is converted into a line signal by the mapping l + 1, 0 + -1 and if it is linear modulated, then Savage's Transition theorem states "The binary vector '*t*' of length  $s(2^{m}-1)$  representing the response of a binary scrambler to an input of period 's', when 's' and  $2^{m}-1$  are relatively prime, has at least one transition every 's' + 'm' digits and has a total of Tr(*t*) transitions where

$$\frac{1}{2} \left(\frac{2^{\mathbf{m}}-2}{2^{\mathbf{m}}-1}\right) \leq \frac{\mathrm{Tr}(L)}{\mathfrak{s}(2^{\mathbf{m}}-1)} \leq \frac{1}{2} \left(\frac{2^{\mathbf{m}}}{2^{\mathbf{m}}-1}\right)$$

(3.8)

This theorem may hold for reset scrambler also, but Savage's proof does not take into count the reset scrambler. Therefore prior to applying these bounds to the reset scrambler further evaluation is needed.

### 3.B.5.a.4 Self-Synchronizing Descramblers

The descramblers for the MCS and SCS are shown in Figures 3.7 and 3.8, respectively. The descrambler is said to be out of synchronism with the scrambler if either (1) the values in the BSS and the delay elements differ from those stored in the corresponding sections of the scrambler or (2) if the counters in the monitoring logic are not at the same levels as those at the scrambler or both. Examining Figure 3.7 or 3.8, it can be seen that the delay elements of the descrambler will be purged after  ${}^{*}s_{N}{}^{*}$  clock intervals, provided  ${}^{*}s_{N}{}^{*}$  is the largest expected period (number of delay elements). The monitoring logic at the scrambler and descrambler will be at the same level after an additional  ${}^{*}s_{N}{}^{*}$  clock intervals provided no line errors have occurred. Therefore the descrambler will require at most 2 x  ${}^{*}s_{N}{}^{*}$  clock intervals free of error (channel errors or bit slip) to recover sync.

The primary effect of a channel error on the descrambler is to introduce additional errors. If the effect on the monitoring logic is neglected, the descrambler will produce approximately w(h) as many output errors as channel errors, where w(h) is the number of nonzero terms in the tap polynomial h(x).

.

Figure 3.7 Multi-Counter Descrambler

Figure 3.8 Single-Counter Descrambler

### 3.B.5.a.5 The Spectrum of the Scrambler Output

Assume a linearly modulated carrier, a binary source, and the source is converted into a waveform such that 0 = -1, 1 = +1. Let  $T_0$  be the time interval alloted to each binary digit and let  $\hat{\ell}(t)$  be the waveform generated by the binary sequence  $\ell$ .

If l is the output of the scrambler for an equiprobable, independent source input, then l is a sequence of independent, equiprobable, binary digits. Thus the autocorrelation function of l(t) is

$$R_{f}(\tau) = \begin{cases} 1 - \frac{|\tau|}{T_{o}}, |\tau| \le T_{o} \\ 0, |\tau| > T_{o} \end{cases}$$

(3.9)

and the power density spectrum for  $\hat{l}(t)$  is

$$S(f) = T_{o} \left( \frac{\sin \pi f T_{o}}{\pi f T_{o}} \right)^{2}$$

(3.10)

Now let the source be periodic, with period 's' such that the line sequence has period  $T_o(LCM(s, 2^m-1))$ ; then the power density spectrum for  $\hat{\ell}(t)$  is

$$S(f) = \frac{1}{p} \delta(f) + T_{o} \left( \frac{\sin \pi f T_{o}}{\pi f T_{o}} \right)^{2} \left\{ \frac{u}{sPT_{1}} \int_{j=-\infty}^{\infty} \delta(f - \frac{j}{PT_{1}}) + (1 - \frac{u}{s} - \frac{1}{p}) \frac{1}{PT_{o}} \int_{j=-\infty}^{\infty} \delta(f - \frac{j}{PT_{o}}) \right\}$$

(3.11)

where  $P = 2^m - 1$

u is a function of the scrambler input (the number of 1's in  $l + l_k$ , k a multiple of P, depends on the input;  $l_K$  represents k cyclic shifts of l).

In other words the principle effect of scrambling is to decrease the number of tones in a given bandwidth by a factor which is approximately P and to decrease the level of each tone by approximately the same factor. The bandwidth is unchanged.

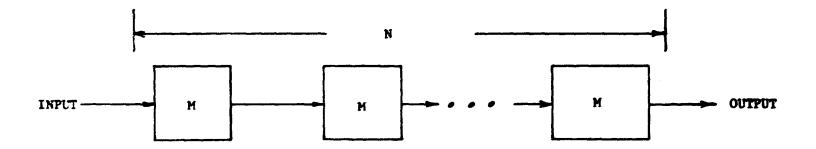

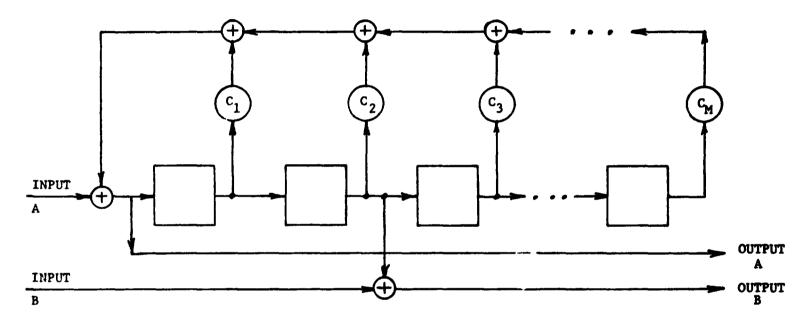

# 3.B.5.a.6 Serial, Cascaded, and Parallel Scramblers

Self-synchronizing scramblers may be classed in subgroups depending on the inter connects between the scramblers. A single scrambler with m delays is called a serial scrambler. The scramblers described in the above were serial.

Scramblers may also be connected in cascaded, meaning the output of one is fed to the input of the next scrambler. Cascade scramblers are inferior to serial scramblers with the same number of delay elements. For example 4 serial scramblers connected in cascade (see Figure 3.9) has a longest output period (output of the 4<sup>th</sup> scrambler) of only the LCM(s,4(2<sup>m</sup>-1)) and a probability of occurance of  $(1-2^{-2m})$ where as a single scrambler with 4m delays has a maximum output period of LCM(s,2<sup>4m</sup>-1) with a probability of occurance of  $(1-2^{-4m})$ . Therefore a serial scrambler is preferred to a cascaded scrambler.

Scramblers may also be connected in parallel. The main advantage of parallel scramblers is the reduction of the number of output errors to input errors. Parallel scramblers use two inputs thereby requiring additional components for series input sequences. Figure 3.10 shows the configuration for parallel scramblers. Examining Figure 3.10, if an error occurs on input 'a', w(h) + 1 errors will be produced by the output, but if an error occurs on input b only one will be produced in the output. Therefore, in the case of parallel inputs, the output errors will be reduced for line b. This technique provides little improvement for random errors occurring in serial data; however.

References 9 and 10 provide additional information on selfsynchronizing scramblers. The main point concerning self-synchronizing scramblers is that the principal effect of infrequent channel errors on the descrambler is to multiply the number of channel errors by w(h), where w(h) is the number of non-zero terms in the tap polynomial h(x).

35

Figure 3.9 Cascading of N M-bit Scramblers

.

Figure 3.10 Parallel Scrambler Configuration (Monitoring Logic Omitted)

### 3.B.5.b Non-Self Synchronizing (Reset) Scramblers.

The reset scrambler is simple, consisting of a maximal-length sequence generator modulo 2 added to the data sequence prior to modulation. The reset scrambler must be provided with synchronizing pulses in order to relock on sync. Since the ML sequence is independent of the data stream there is no multiplication of output errors relative to input errors.

At present the number of transition for a given sequence length is unknown. It is possible that the reset scrambler may provide the same Tr(l) as the self-synchronizing scrambler, but the proof utilized by Savage<sup>9</sup> cannot be directly applied to the reset scrambler.

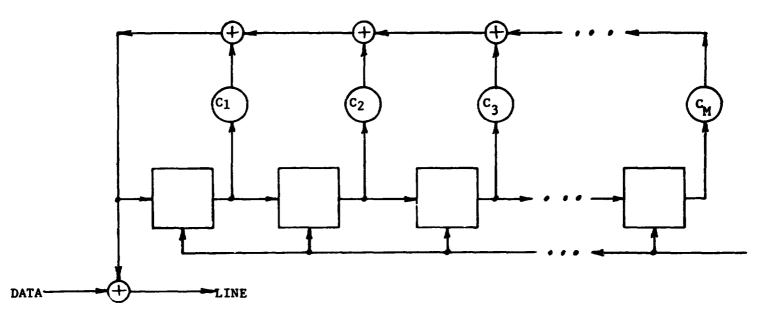

The scrambler and descrambler for the reset group are identical maximal-length sequence generator for binary data. Figure 3.11 shows the reset scrambler. The synchronizing pulse may be obtained from the frame sync or another sync pattern found in the data stream. Since the sync pattern would be utilized to reset and start the MLsequence, it would not be scrambled.

The self-synchronizing scramblers are poor candidates for the SL due to the multiplication of channel errors. The reset group is a better candidate provided a lower bound can be determined for the number of transitions for a given sequence length, and is discussed in the next Chapter. (See Reference 12 for a brief summary on scramblers.)

Table 3.1 summarizes the possible methods discussed in this section for improving bit transition density of the 2 Mbit SL Link. Only the reset scrambler remains as a viable option. The reset scrambler is actually a PN Cover Sequence which is modulo-2 added to the data stream. This technique is examined in further detail in Chapter IV.

. .

$$h(X) = X^{m} + C_{1}X^{m-1} + \dots + C_{m}$$

where  $C_{1} = 1$  or 0 and  $h(X)$  is a primitive

polynomial over GF(2) of degree M

39

.

|    | Technique                                                                                 | SPECTRAL BY                 | ERROR CHARACTERISTICS                                                                   | SYNCHROWIZATION                                                         | HARDWARE COMPLEXITY                                | TRANSITION PROPERTIES                                              | CONSTRAINTS<br>VIOLATED |

|----|-------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|-------------------------|

| 1. | Pit Scrambler<br>Self Synchronizing<br>a. Serial                                          | Same as<br>Data Stream      | Error propagation<br>and multiple output<br>errors for single<br>error input            | Self Synchronising                                                      | Encoder-Moderate                                   | A Guaranteed<br>Performance can<br>be Provided                     | 43                      |

|    | b. Parallei                                                                               | Same as<br>Data Stream      | Some as la.                                                                             | Self Synchronizing                                                      | Encoder-Hoderate                                   | A Guaranteed<br>Performence can<br>be provided                     | 83                      |

| 2. | Delay Modulation<br>a. Miller                                                             | Same as<br>Data Stream      | Double errors out<br>for single error in                                                | Must Provide<br>Synchronization                                         | Encoder-Moderate<br>Decoder-More Complex           | 2 Transitions in<br>every 3 bit cells                              | . #3                    |

|    | b. Miller <sup>2</sup>                                                                    | Saue as<br>Data Stream      | Double errors out<br>for single error in                                                | Must Provide<br>Synchronization                                         | Encoder-Moderate<br>Decoder-More Complex           | ] Transition in<br>every ] bit cells                               | 13                      |

| 3. | Bi-Phase Modulation<br>(Manchester, Man-<br>chester II, Bi-Phase<br>Mark, Bi-phase Space) | Double<br>Data<br>Bandwidth | l error out for<br>l error in                                                           | Self Synchronizing                                                      | Encoder-Moderate<br>Decocer-Moderate to<br>Complex | l transition for<br>every bit cell                                 | <b>#</b> 2              |

| 4. | Alternate<br>Bil Version                                                                  | Some as<br>Data             | l bit slip yields<br>inverted bit stream.<br>l error out for l<br>error in.             | Hust Provide<br>Synchronization                                         | Encoder-Hoderate<br>Decoder-Moderate               | Data Pattern<br>Sensitive. No<br>Guarantees.<br>Statistically Good | 13                      |

| 5. | Sequence Insertion<br>(Includes Error<br>Codes)                                           | Same 49<br>Deta             | Possible error multi-<br>plication due to channel<br>errors and data convolu-<br>tions. | Hust Provide<br>Synchronization<br>Sensitive to Inverted<br>Data Stream | Timing and Counting<br>Complex-                    | Can be Designed<br>to Heet Specifics-<br>tions.                    | 13                      |

| 6. | PK Cover Sequence<br>(Reset Scrambler)                                                    | Same as<br>Data             | l error out for<br>l error in.                                                          | Must Provide<br>Synchronisation                                         | Encoder-Simple<br>Decoder-Moderate                 | Can be Designed<br>to Neet Specifics-<br>tions.                    | BONE                    |

# TABLE 3.1 BIT TRANSITION DENSITY CODING CHOICES

.

•

:

### CHAPTER 4

### PSEUDO-NOISE COVER SEQUENCE (Reset Scrambler)

In the preceding chapter, different techniques were examined to determine their capability of resolving the bit transition density problem of the SL 2 Mbit Return Link and these techniques are summarized in Table 3.1. Only the PN Cover Sequence (or Reset Bit Scrambler) was capable of meeting all the system constraints listed in Tables 2.1 and 2.2. This chapter deals primarily with the particular PN sequence chosen for the SL, however a brief general discussion of PN sequences is also given.

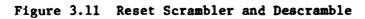

### 4.A PSEUDO-NOISE (PN) SEQUENCES

Pseudo-Noise Sequences are binary-valued, noise-like sequences in that they are purely random. That is any bit in the sequence may be a one or a zero with equally likely probability. However their primary advantages are that they are deterministic, easily generated by feedback shift registers, and they have a correlation function which is highly peaked for zero delay and approximately zero for other delays. By proper selection of the tap polynomial, which indicates the feedback connections, a maximal linear (ML) sequence or m-sequence is generated. Figure 4.1 illustrates a general ML sequence generator. A ML sequence has a length,  $L = 2^{n}-1$ , where 'n' is the number of stages in the shift register (SR). The number of ones in the sequence equals the number of zeros plus one. There are

$$\begin{bmatrix} \frac{2^n-1}{2} \end{bmatrix} \text{ zeros and } \begin{bmatrix} \frac{2^n-1}{2} \end{bmatrix} + 1 \text{ ones.}$$

The number of transitions within the sequence is approximately half the number of bits in the sequence. The number of transition equals

$\left\lfloor \frac{2^n-1}{2} \right\rfloor$  . The maximum number of bits without a transition is

equal to the number of stages in the SR, 'n'. The statistical

٠

Figure 4.1 PN Cover Sequence. The  $d_1(i = 1, 2, ..., n)$  are either one or zero, depending on the tap polynomial, h(x), where h(x) is a primitive polynomial over the field GF  $(2^n)$  and h(x) = 1 + d,  $X + d_2 X^2$  $+ d_3 X^3 + ... + d_n X^n$ .

,

,

.

distribution of ones and zeros is well defined and always the same. There are exactly  $2^{n-(p+2)}$  runs of length 'p' for both ones and zeros in every maximal sequence where 'p' is any positive integer less than 'n', including zero. However, the relative positions of their runs vary from ML sequence to ML sequence depending on the tap polynomial and the method of connection. The main properties of ML sequences are listed below.

- 1. The number of ones in a sequence equals the number of zeros within one bit.

- 2. The statistical distribution of ones and zeros is well defined and always the same. Relative positions of their runs vary from code sequence to code sequence, depending on the tap polynomial and the method of connection, but the number of each run length does not.

- 3. Autocorrelation of a maximal linear code sequence is such that for all values of phase shift the correlation value is -1, except for the 0 to 1 bit phase shift area, in which correlation varies linearly from the -1 value to  $2^n$ -1 (the sequence length).

- 4. A modulo-2 addition of a maximal linear code with a phase shifted replica of itself results in another replica with a phase shift different from either of the originals.

- 5. Every possible state, or m-tuple, of a given n-stage generator exists at some time during the generation of a complete code cycle. Each state exists for only one clock pulse. The exception is that the all-zeros state does not normally occur and cannot be allowed. (For additional information concerning ML sequences, see Reference 13, pp. 53-72 and Reference 14.)

The particular ML sequence, the reasons for choosing it, and a statistical statement of the probability of not incurring sufficient transitions are discussed in the following paragraphs.

### 4.B THE PARTICULAR PN SEQUENCE FOR THE COVER SEQUENCE GENERATOR (CSG)

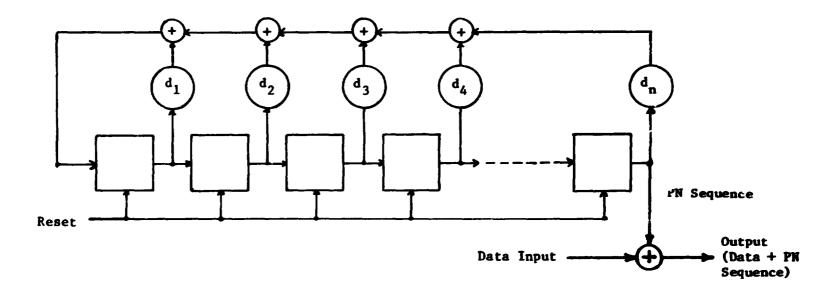

It is a common engineering practice to select a ML sequence whose length is at least equal to the number of bits between synch words, since the sync pattern in better left alone. The SL general user format contains 3040 bits between each 32 bit sync word (28 bit sync pattern and a 4 bit ID word), therefore the sequence generated by the CSG should have a length equal to or greater than 3040. Although a  $12^{th}$  degree polynomial yields a ML sequence length of 4095 bits and is the smallest sequence that could be used, it is not a Mersenne prime sequence and is therefore susceptible to interperodicty. For this reason a  $13^{th}$  degree polynomial was chosen. It will generate a  $2^{13}$ -1 = 8191 bit sequence before repeating itself; its composition will vary depending upon the tap polynomial used. A 13 stage PN generator is a Mersenne prime generator. Various tap polynomials are available for use and some are listed as follows:

$$g(x) = 1 + x + x^{3} + x^{4} + x^{13}$$

$$g(x) = 1 + x^{4} + x^{5} + x^{7} + x^{9} + x^{10} + x^{13}$$

$$g(x) = 1 + x + x^{4} + x^{7} + x^{8} + x^{11} + x^{13}$$

etc.

The first polynomial listed yields the fewest number of connections which would be desirable if a shift register implementation was used for producing the code.

Since the sequence generated is 8191 digits long and only 3040 digits exist between the frame synchronization patterns, a truncation of the sequence is desirable.

Deciding upon the particular 3040 bit piece of the sequence is dependent upon the structure of the sequence. It is highly desirable to avoid long strings of alternating 1's and 0's due to the very likely prospect of these strings occurring in the data. Factors which enter into the sequence structure are the initial condition (or contents) of the PN sequence shift register and the tap polynomial.

Figures 4.2 and 4.3 illustrate the methods of modifying the data stream emanating from the HRM. Figure 4-2 illustrates the shift

Figure 4.2 CSG Encoder Using Shift Register Implementation

\$

•

•

٠

•

Figure 4.3 HDBT Encoder Using ROM Implementation

•

•

register type of encoder for HDBT and Figure 4.3 illustrates the ROM type of encoder for HDBT. In either case the same sequence will be utilized. It should be noted that the frame sync and ID portion are not altered.

The sequence will have the run length distributions, shown in Table 4.1, for all tap polynomials and initial start vectors (the arrangement of these various runs will vary of course or there would be no difference in the sequences).

In general there are  $2^{n-(p+2)}$  runs of length p for both ones and zeros in every maximal sequence, except that there is only one run of length n (ones) and one run of length n-1 (zeros).

A computer program based on an algorithm presented by Robert Gold in Reference 14 was used to generate the complete sequence of 8191 bits. This sequence was examined and the particular portion of 3040 bits was selected. This sequence is shown in Table 4.2. The zero-one distribution for this truncated 13 stage PN sequence is illustrated in Table 4.3. An examination of Table 4.3 reveals that this truncated sequence maintains the properties of a ML sequence. Although they are not perfectly retained, it is very close. Since the SL data stream is expected to contain long runs of alternate ones and zeros, the truncated sequence must be examined for these also. Table 4.4 lists the number and lengths of all alternating runs contained in the truncated sequences.

### 4.C PROBABILITIES ASSOCIATED WITH THE SEQUENCE

Now let us investigate some probabilities of not achieving the transition density requirements.

In order for failure to achieve a transition in 64 bits to occur it must have a data sequence that exactly matches the PN sequence for 64 bits. Since the PN sequence is statistically independent of the data sequence in bit by bit as well as string by string fashion we have

> Prob (of more than 63 bits with no transition) =  $(.5)^{64} = 5.4210108 \times 10^{-20}$ .

The requirement that 64 transition in 512 bits occur may be thought of from the following viewpoint:

# TABLE 4.1ZERO-ONE DISTRIBUTION FOR n = 13MAXIMAL LENGTH PN SEQUENCE

| TOTAL | NUMBER | OF   | ONES  | 4096        |

|-------|--------|------|-------|-------------|

| TOTAL | NUMBER | OF   | ZEROS | <u>4095</u> |

|       | TC     | DTAI | BITS  | 8191        |

•

| RUN LENGTH | NUMBER OF RUNS<br>CONSECUTIVE ONES | NUMBER OF RUNS<br>CONSECUTIVE ZEROS | NUMBER OF BITS<br>INCLUDED |

|------------|------------------------------------|-------------------------------------|----------------------------|

| 13         | 1                                  | 0                                   | 13                         |

| 12         | 0                                  | 1                                   | 12                         |

| 11         | 1                                  | 1                                   | 22                         |

| 10         | 2                                  | . 2                                 | 40                         |

| 9          | 4                                  | 4                                   | 72                         |

| 8          | 8                                  | 8                                   | 128                        |

| 7          | 16                                 | 16                                  | 224                        |

| 6          | 32                                 | 32                                  | 384                        |

| 5          | 64                                 | 64                                  | 640                        |

| 4          | 128                                | 128                                 | 1024                       |

| 3          | 256                                | 256                                 | 1536                       |

| 2          | 512                                | 512                                 | 2048                       |

| 1          | 1024                               | 1024                                | 2048                       |

|            |                                    | TOTAL                               | BITS 8191                  |

**48**

| 10100001011111001                                         | 0010100001111110                                         | 01 00 10 1 1 1 1 0 1 1000               |

|-----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------|

| 1000010600000111                                          | 0010010010111001                                         | C00 1 10 1 0 20 1 1 0 1 10              |