## **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

# LSI/VLSI Design for Testability Analysis and General Approach

Albert Y. Lanı

(NASA-CR-169145) LSI/VLSI DESIGN FOR TESTABILITY ANALYSIS AND GENERAL APPROACH (Jet Propulsion Lab.) 141 p HC A07/MF A01 CSCL 09C

N82-29541

Unclas G3/33 28444

June 1, 1982

Pasadena, California

Prepared for

Naval Ocean Systems Center

San Diego, California

through an agreement with

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory

California Institute of Technology

# LCI/VLSI Design for Testability Analysis and General Approach

Albert Y. Lam

June 1, 1982

Prepared for

Naval Ocean Systems Center

San Diego, California

through an agreement with

National Aeronautics and Space Administration

by

Jet Propulsion Laboratory

California Institute of Technology

Pasadena, California

The research described in this publication was carried out by the Jet Propulsion Laboratory, California Institute of Technology, and was sponsored by the Naval Ocean Systems Center, San Diego, California, through an agreement with NASA.

ļ

#### ABSTRACT

For many years since the advent of large-scale integrated circuit technology, digital system testing has been a challenging problem. Intensive research efforts are directed towards the discovery of techniques (systematic and/or ad hoc) for designing digital systems with good testability and maintainability. This report presents a survey of most major contributions to the theory and practice of digital design for testability. Detailed analysis of each of the contributions is also presented, providing the reader with necessary background materials for the main objective of this report — from the comparison of all design for testability techniques studied, some conclusions may be drawn to establish a general guideline/approach to designing testable circuits for large scale integration and very large scale integration.

PRECEDING PAGE BLANK NOT FILMED

111

ORIGINAL PAGE IS OF POOR QUALITY

#### ACKNOWLEDGMENT

This study was initiated by the Naval Ocean Systems Center, Code 923, and represents a facet of a block-funded program entitled Integrated Circuit Technology, sponsored by the Naval Electronics Systems Command, Technology Division. The work was performed by agreement with NASA under Contract NAS7-100 at the Jet Propulsion Laboratory of the California Institute of Technology. This program is continuing under NASA sponsorship, and related system studies are being conducted at the University of California, Los Angeles under sponsorship of the Office of Naval Research.

#### ACRONYMS

AC Accumulator ac (AC) alternating current ALU Arithmetic Logic Unit ATE Automatic Test Equipment BIT Built-In Test BITE Ruilt In Test Equipment CM Control Module CPU Central processing unit CUT Circuit Under Test DC Direct Current DFT Design For Testability DMAR Data Memory Address Register Department of Defense DoD DP Diagnostic Processor EXOR Logical Exclusive-or Function FR Flag Register GLF General Logic Function GLS General Logic Structure HFPH Hazard Free Polarity Hold IC Integrated Circuit **I/0** Input/Output IR Instruction Register ITSC Input Test Set Complex LNCR Liaison Network Control Registers LSI Large Scale Integration LSSD Level Sensitive Scan Design MM Memory Module MOS Metal Oxide Silicon MSI Medium Scale Integration MUX Multiplexer NAND Logical And-Not Function N-channel Metal Oxide Silicon NMOS Logical Or-Not Function NOR OR Logical Or Function OTSC Output Test Set Complex PC Program Counter

Partition Control Register

PCR

PFF Parasitic Flip Flop

PLA Programmable Logic Array

PM Processing Module

PMOS P-channel Metal Oxide Silicon

PU Processing Unit

RAM Random Access Memory

ROM Read Only Memory

s-a-0 stuck-at-zero s-a-1 stuck-at-one

SEC/DEC Single Error Correction/Double Error Detection

SSI Small Scale Integration SRL Shift Register Latch

SSRL Stable Shift Register Latch

TSC Totally Self Checking

ULM Universal Logic Modules

UUT Unit Under Test

VDD Main Power Supply

VLSI Very Large Scale Integration

# CONTENTS

| 1   | INTRODUCTION                                            | 1-1        |

|-----|---------------------------------------------------------|------------|

|     | 1.1 TESTABILITY AND GOOD TESTABILITY                    | 1-2        |

|     | 1.2 PREREQUISITES OF DESIGNING FOR TESTABILITY          |            |

|     | 1.2.1 Well Specified Design Framework                   | 1-3        |

|     | 1.2.2 Well Defined Failure Universe                     | 1-5        |

|     | 1.2.3 Implementation Technology                         | 1-6        |

|     | 1.3 HARDWARE PAILURES, MOS CIRCUIT FAULTS AND ERRORS    | 1-6        |

|     | 1.4 INTRODUCTION TO DESIGN FOR TESTABILITY              | 1-1/       |

|     | 1.4.1 On-Line on-Chip Testing                           | 44         |

|     | 1.4.2 On-Line off-Chip Testing                          | 1-1        |

|     | 4 ji 3 Oge Line on Opin Minerine                        | 1-14       |

|     | 1.4.3 Off-Line on-Chip Tasting                          | 1-1:       |

|     | 1.4.4 Off-Line off-Chip Testing                         | 7-74       |

|     | 1.4.5 General Approach                                  | 1-15       |

| 2   | OVERVIEW OF MAJOR DESIGN FOR TESTABILITY TECHNIQUES     | 21         |

| B-0 | 2.1 CLASSICAL APPROACH - DUPLICATE AND COMPARE          | Z- 1       |

|     |                                                         | <b>~</b> 4 |

|     | TECHNIQUE                                               | 2-1        |

|     | 2.1.1 Morphic Boolean Algebra and Morphic AND           |            |

|     | gate                                                    | 2-3        |

|     | 2.1.2 Totally Self-Checking Code Checkers and           |            |

|     | Comparators                                             | 2-9        |

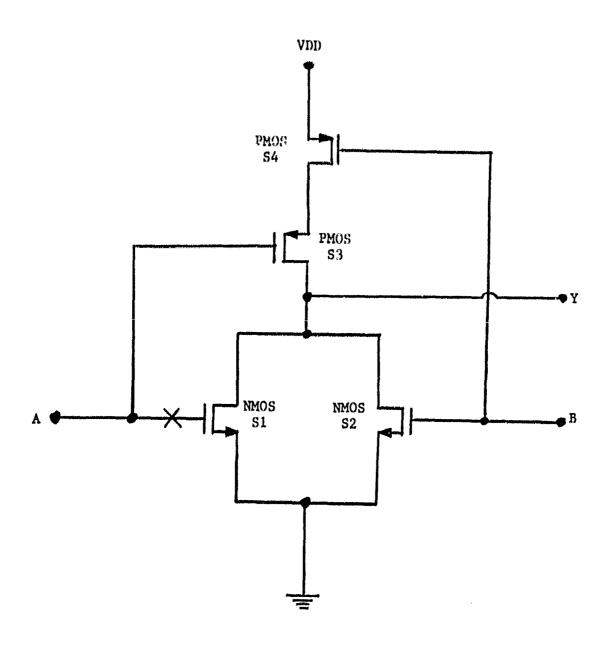

|     | 2.1.3 Simple CMOS Implementation of Morphic AND         |            |

|     | Gate                                                    |            |

|     | 2.2 LEVEL SENSITIVE SCAN DESIGN (LSSD)                  | Ž-12       |

|     | 2.2.1 Hazard-Free Polarity-Hold Latch and               |            |

|     | Shift Register Latch                                    | 2-15       |

|     | 2.2.2 Design Structure                                  |            |

|     | 2.2.3 Fundamental Testing Techniques of LSSD-           |            |

|     | Structured Circuits and Systems                         | 2-18       |

|     | 2.2.4 Advanced Testing Techniques of LSSD-              |            |

|     | Structured Circuits and Systems                         | 2-21       |

|     | 2.2.4.1 LSSD to NON-LSSD Interface                      |            |

|     | 2.2.4.2 Utilization of Existing Latches                 | - m        |

|     | in LSSD Logic                                           | 2-25       |

|     | 2.2.4.3 LSSD Parity Checking                            | 2-27       |

|     | 2.2.4.4 On-Line Dynamic Scan                            |            |

|     | 2.2.4.5 On-Line Error Detection in Memory               |            |

|     |                                                         |            |

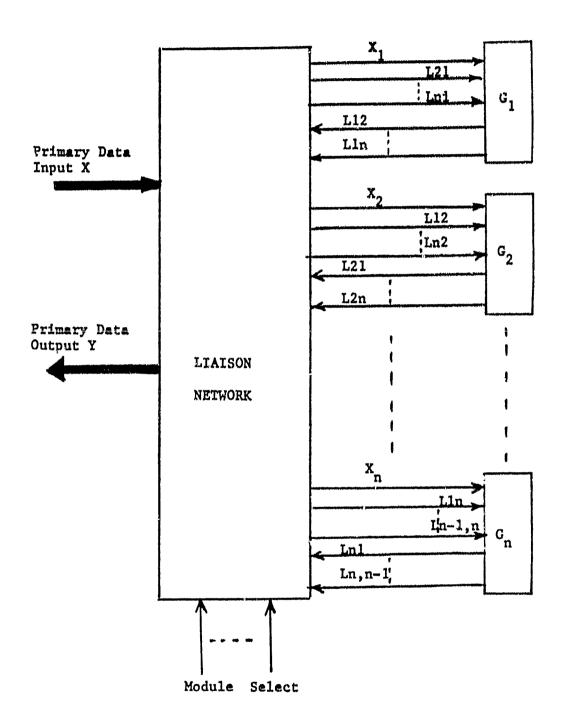

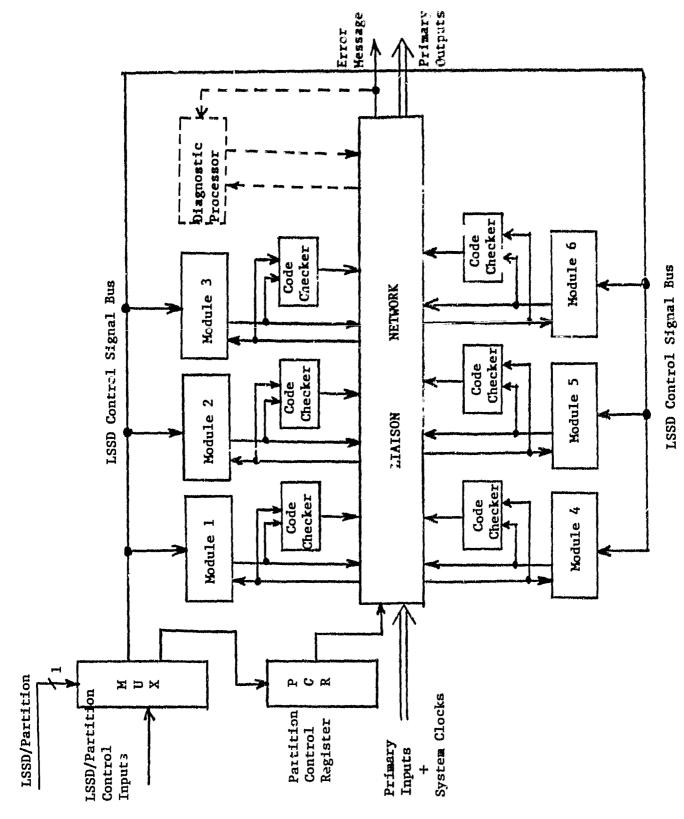

|     | 2.3 MODULARIZED DECOMPOSITION VIA MULTIPLEXED ROUTING . |            |

|     | 2.3.1 Basic Circuit Decomposition Scheme                |            |

|     | 2.3.2 Generalized Routing Scheme                        | 2-3        |

|     | 2.3.3 Reliability and Testability of Liaison            |            |

|     | Network                                                 | 2-32       |

| _   | COMPANIAN OF THE RESIDENCE                              |            |

| 3   | COMPARISON OF DFT TECHNIQUES                            |            |

|     | 3.1 SELF-CHECKING TECHNIQUE                             |            |

|     | 3.2 LEVEL SENSITIVE SCAN DESIGN TECHNIQUE               |            |

|     | 3.3 MULTIPLEXED ROUTING TECHNIQUE                       | 3-8        |

|     |                                                         |            |

| 4   | A GENERAL APPROACH TO DESIGN FOR TESTABILITY            | 4-1        |

|     | 1 1 GENERAL DESTGN FOR TESTABLISTY GUIDELINES           | h_2        |

|      | 4.2 A GENERAL DFT STRUCTURE                           |                                          |

|------|-------------------------------------------------------|------------------------------------------|

| 5    | CONCLUSIONS                                           | 5-1                                      |

| 6    | REFERENCES                                            | 6-1                                      |

| APPE | DIXES                                                 |                                          |

|      | A. PARASITIC FLIP FLOP CAUSES                         | A-1                                      |

|      | B. CIRCUIT FAULT EFFECTS ON TSC CIRCUITS              |                                          |

| Figu |                                                       |                                          |

|      | 1.1 Trend of Fault Coverage Obtained in Practical     |                                          |

|      | Cases Versus Network Sixe                             | 1-20                                     |

|      | 1.2a Nearest Neighbor Fault Model                     |                                          |

|      | 1.2b Neighborhood Fault Model                         |                                          |

|      | 1.3 On-Line On-Chip Testing Block Diagram             |                                          |

|      | 1.4 On-Line Off-Chip Testing Block Diagram            |                                          |

|      | 1.5 Off-Line On-Chip Testing Block Diagram            | 1-23                                     |

|      | 1.6 Micro/Macrocell Structure Development             | 1-24                                     |

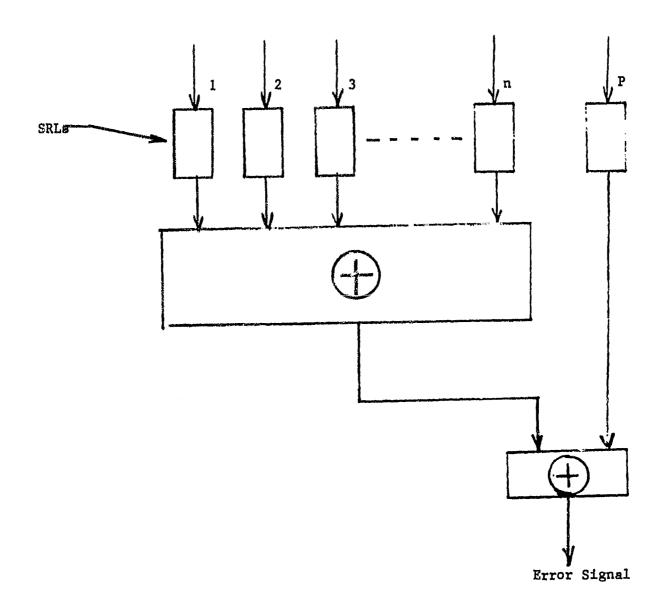

|      | 2.1 Block Diagram of TSC Circuit                      |                                          |

|      | 2.2 2-Level NAND-NAND Logic Implementation of         |                                          |

|      | Morphic-AND Function                                  | 2-35                                     |

|      | 2.3 2-Level NOR-NOR Logic Implementation of           |                                          |

|      | Morphic-AND Function                                  | 2-35                                     |

|      | 2.4 Morphic-AND Function Truth Table                  | 2-36                                     |

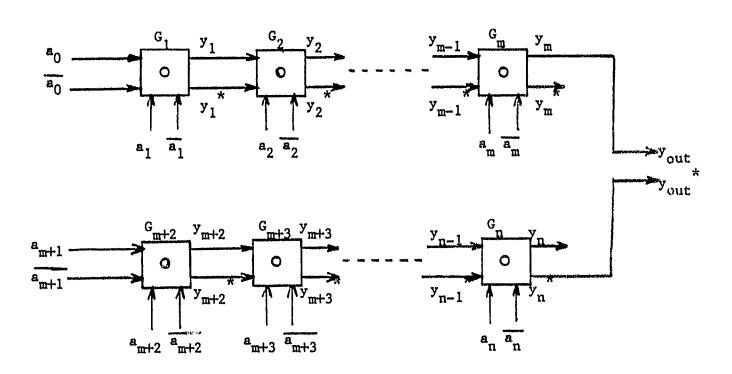

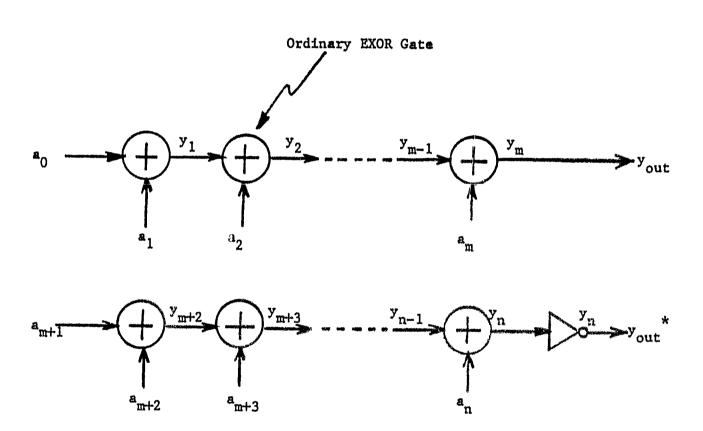

|      | 2.5 n-bit TSC Even Parity Checker                     | 2-37                                     |

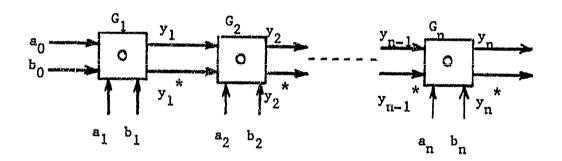

|      | 2.6 n-bit TSC Comparator                              |                                          |

|      | 2.7 CMOS Morphic-AND Gate                             | 2-39                                     |

|      | 2.8 n-bic TSC Parity Checker                          |                                          |

|      |                                                       | 2-41                                     |

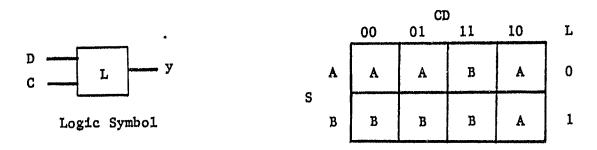

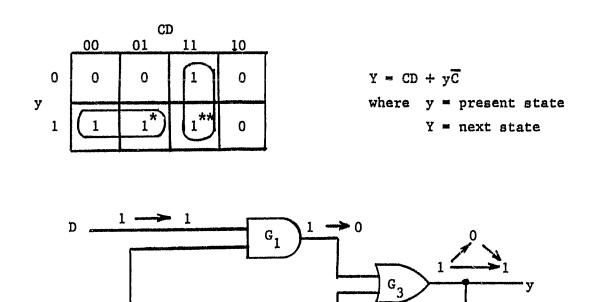

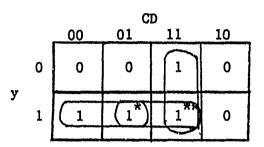

|      | 2.9b Excitation Table, Excitation Equation, and Logic | <b>.</b>                                 |

|      | Implementation of a Level-Sensitive Latch             | 2-41                                     |

|      | 2.90 Excitation Table, Excitation Equation, and Logic | a 4a                                     |

|      | Implementation of an HFPH Latch                       | 2-42                                     |

|      | Logic Implementation of a Shift Register Latch 2      | oko                                      |

|      | 2.11 Interconnection of SRLs for Scan-in/Scan-out 2   |                                          |

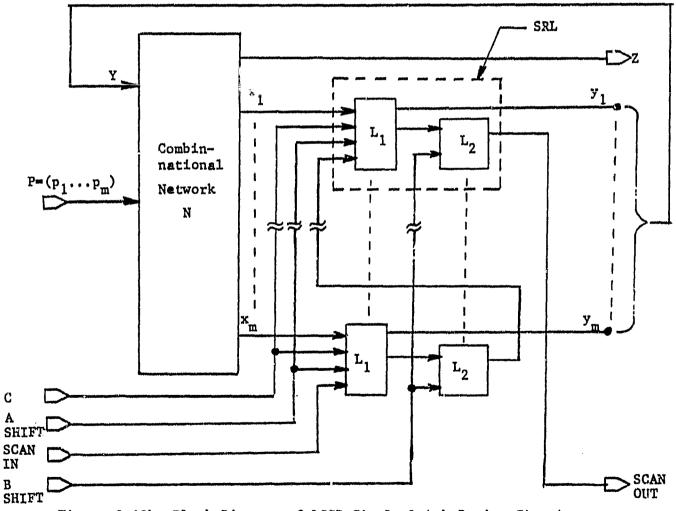

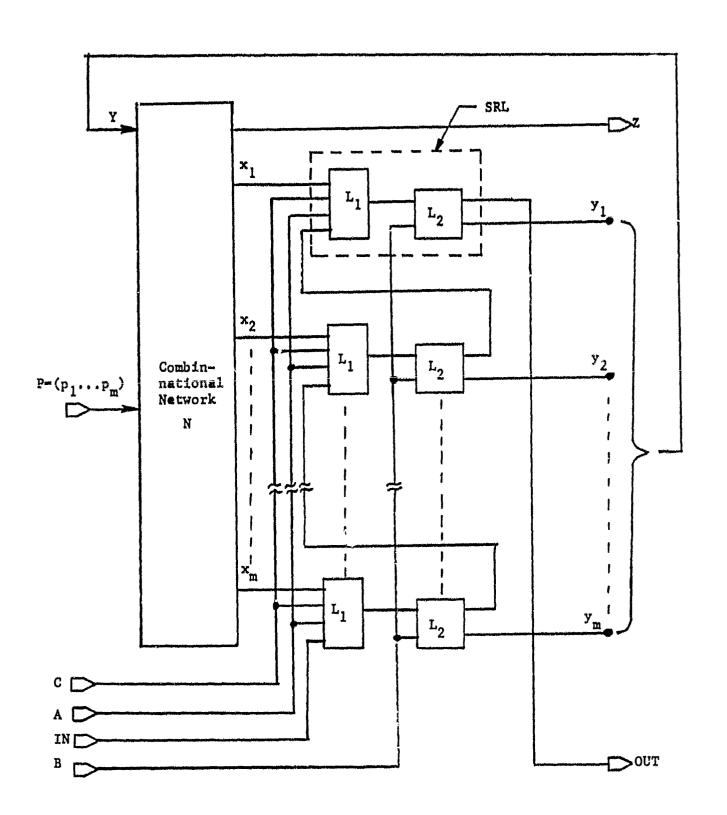

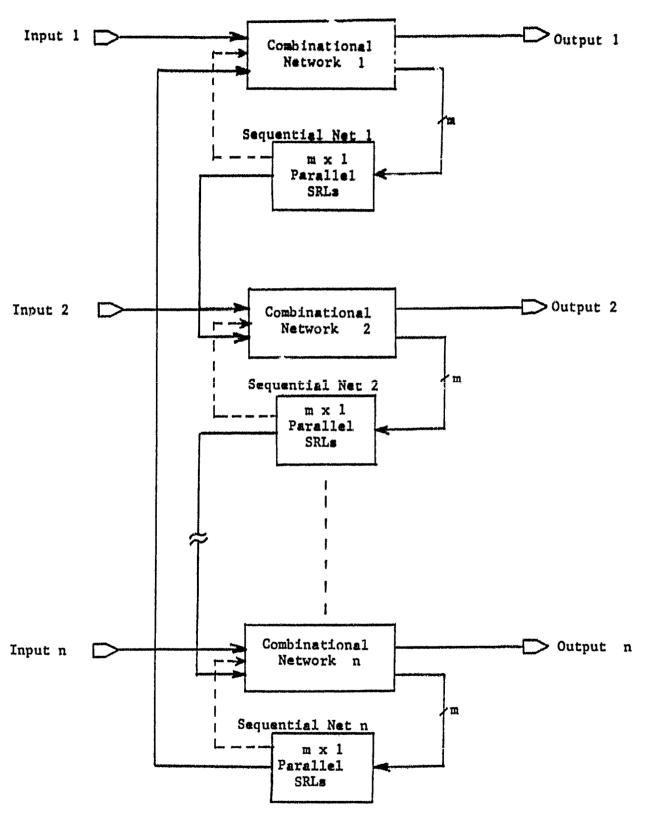

|      | 2.12a Basic Sequential Network Structure: Type 1 2    |                                          |

|      | 2.12b Block Diagram of LSSD Single Latch Design       | L-4,                                     |

|      | Structure                                             | 2_15                                     |

|      | 2.12c Block Diagram of LSSD Double Latch Design       | ري ۱۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰۰ |

|      | Structure                                             | 2-46                                     |

|      | 2.13 Basic Sequential Network Structure: Type 2       | 47                                       |

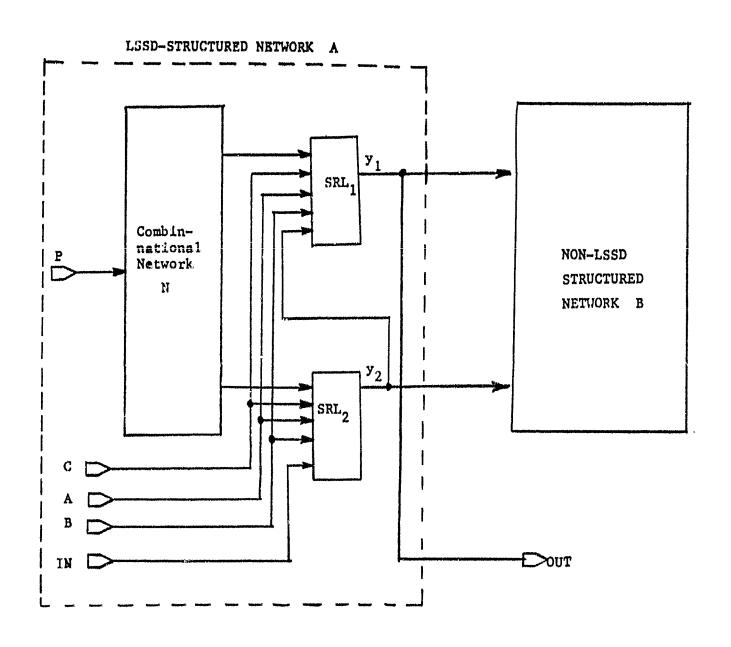

|      | 2.14 Block Diagram of LSSD to non-LSSD Network        | · , ,                                    |

|      | Interface                                             | 2-48                                     |

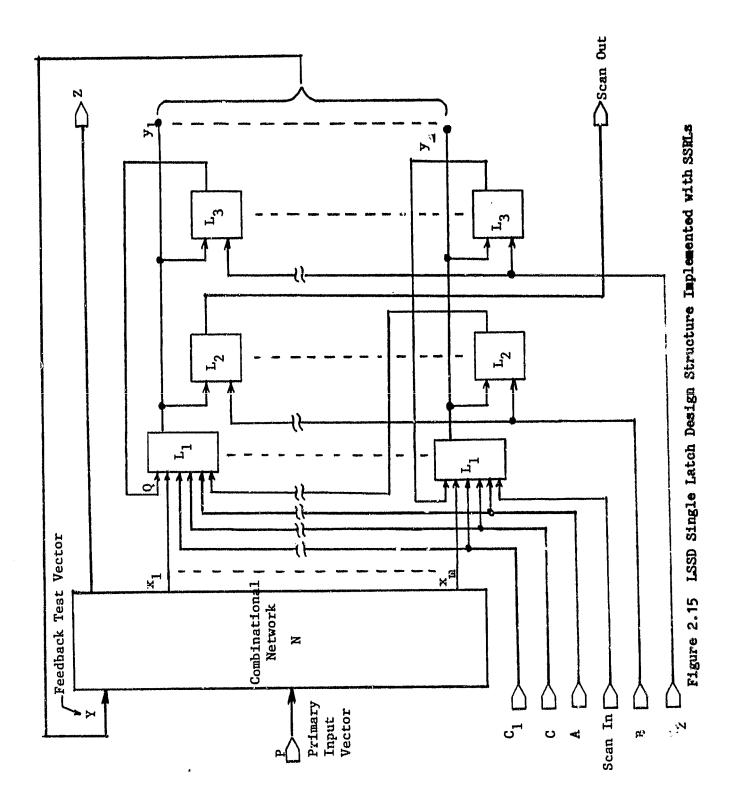

|      | 2.15 LSSD Single Latch Design Structure Implemented   |                                          |

|      | with SSRLs                                            | 2-49                                     |

|      | 2.16 Logic Implementation of a Stable Shift Register  |                                          |

|      | Latch                                                 | 2-50                                     |

|      | 2.17 Original SSRL Implementation                     | 2-51                                     |

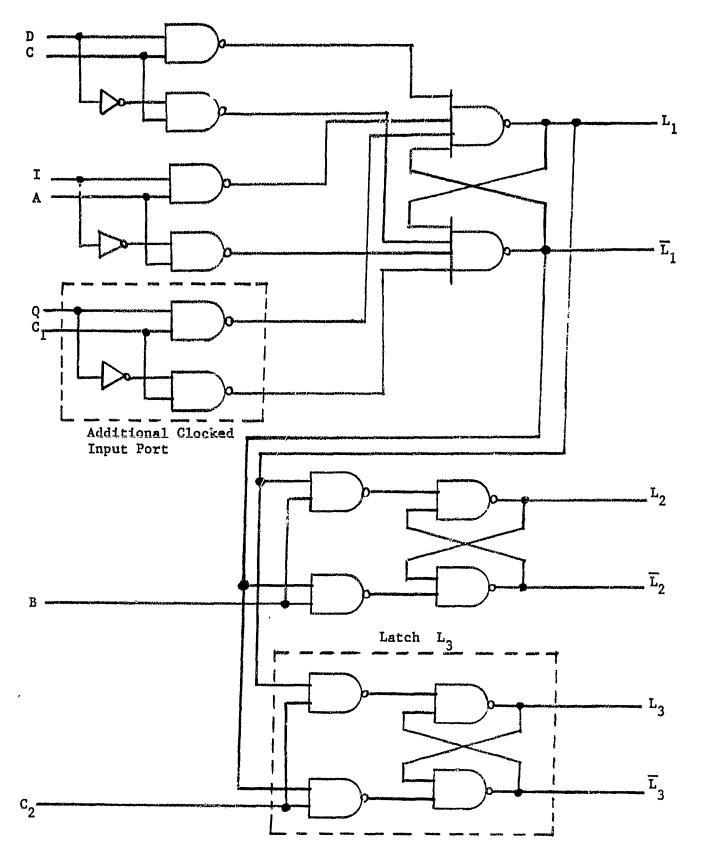

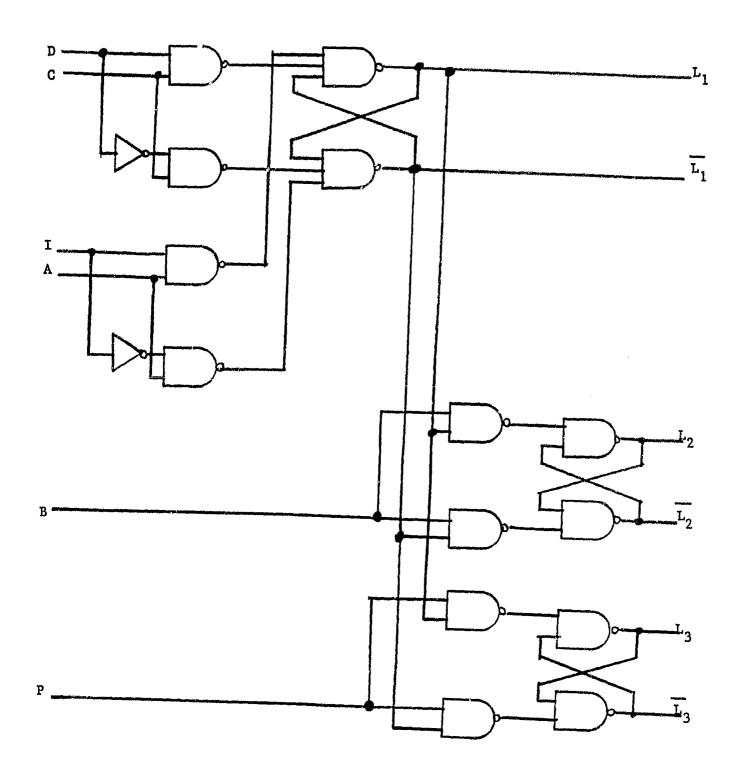

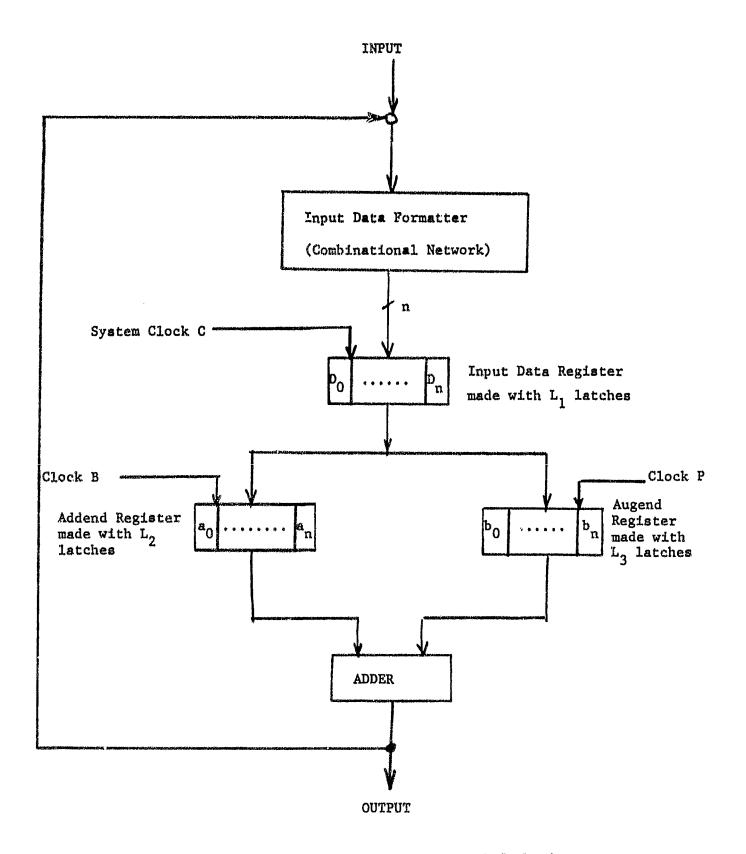

| 2.18       | Example of Use of SSML in LSSD Logic               | 2-52       |

|------------|----------------------------------------------------|------------|

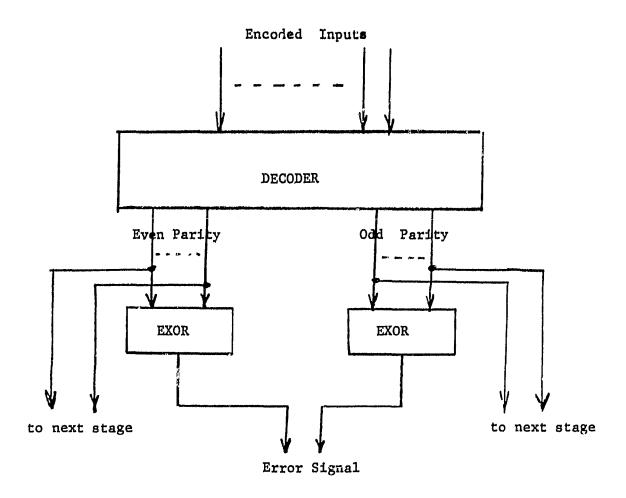

|            | LSSD Parity Checker Implementation                 |            |

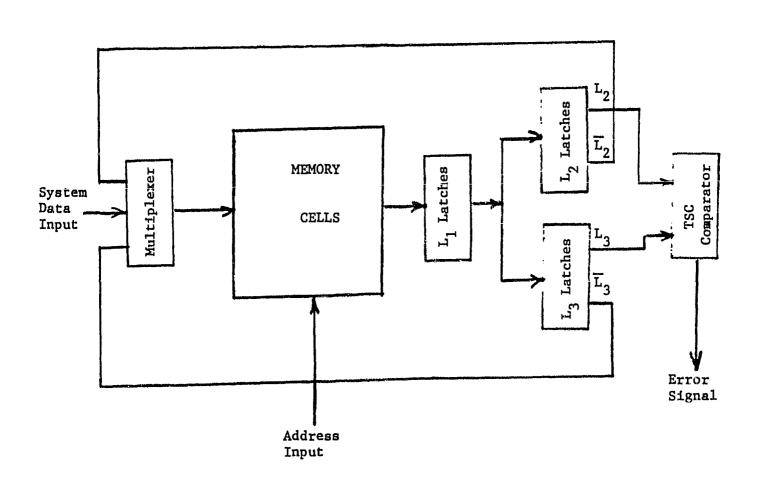

| 2.20       | LSSD On-Line Memory Error Detection                | 2-54       |

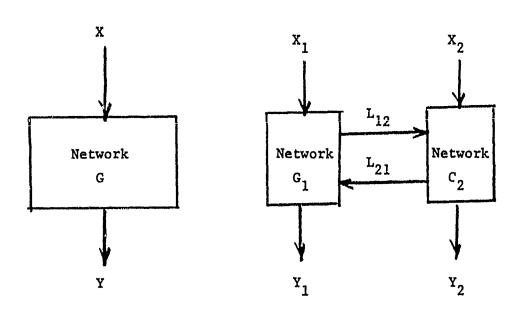

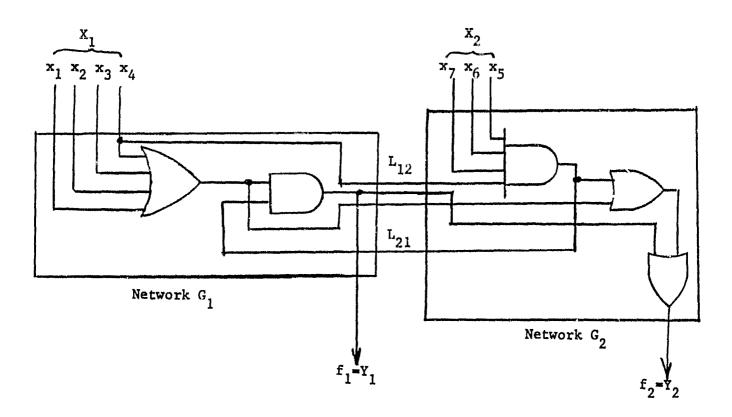

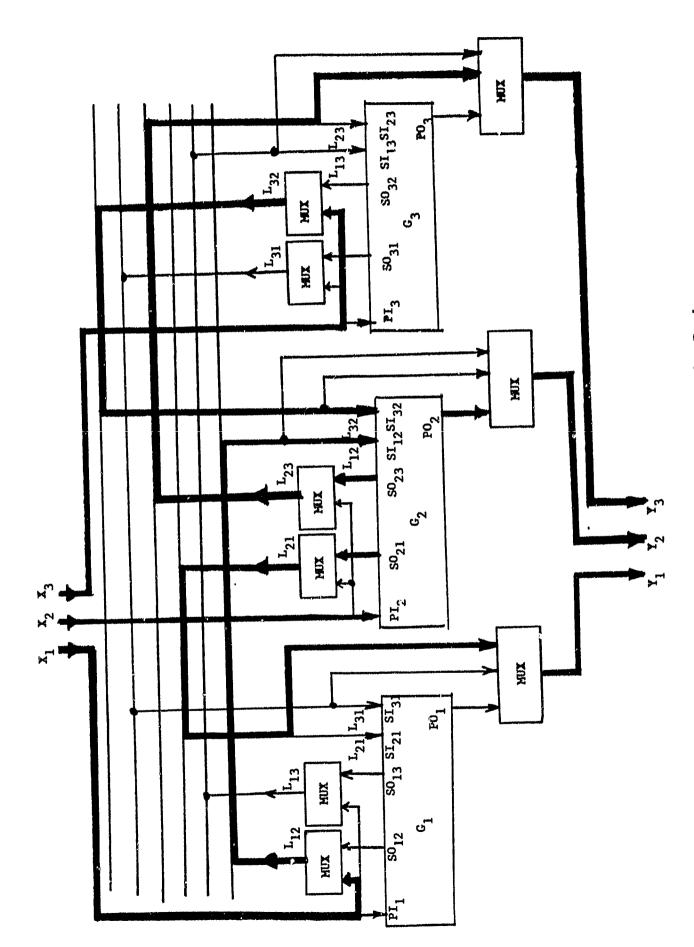

| 2.21       | Basic Network Decomposition 2-Module Partitioning  | 2-55       |

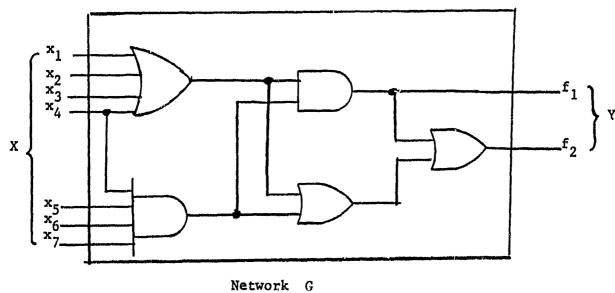

| 2.22       | An Example of Network Partition                    | 2-56       |

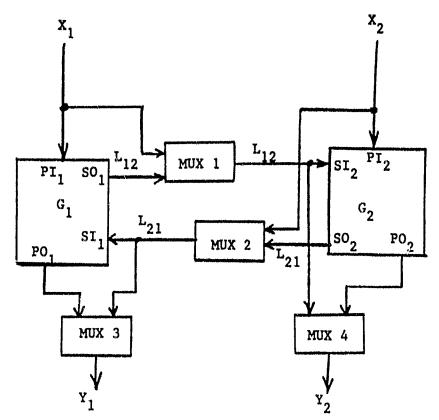

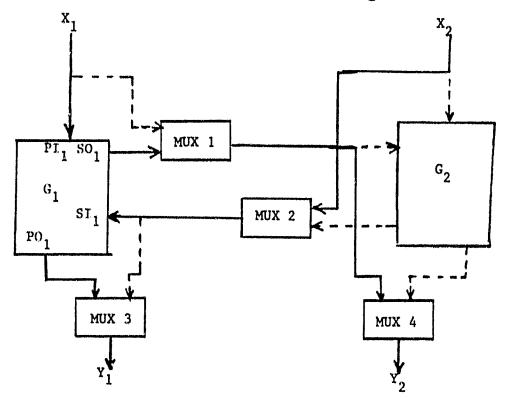

| 2.234      | A 2-Module Routing Scheme                          | 2-57       |

| 2.231      | Blook Diagram of Input/Output Buses Routing -      |            |

|            | G1 under Test                                      | 2-57       |

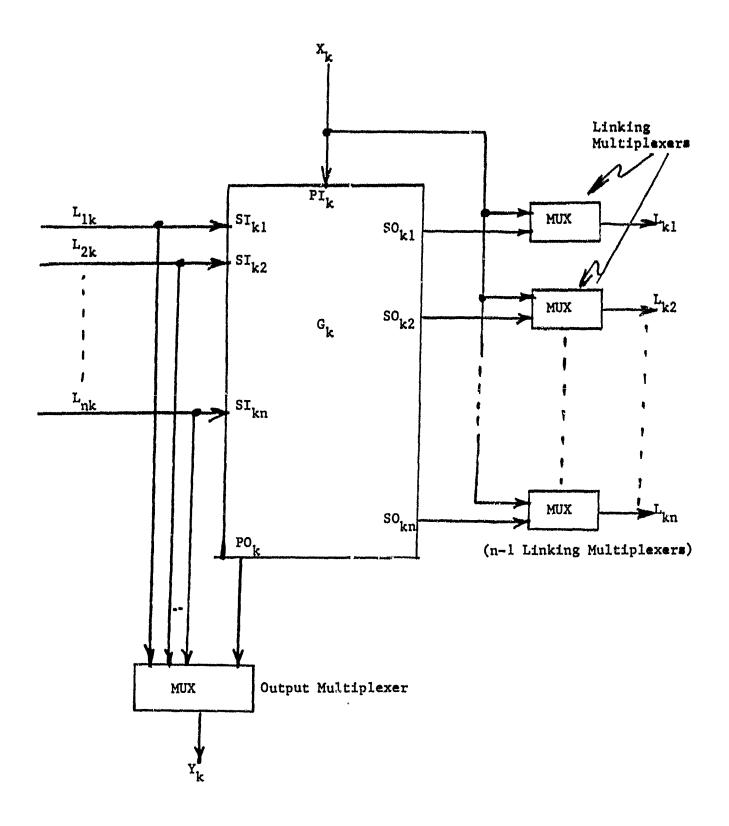

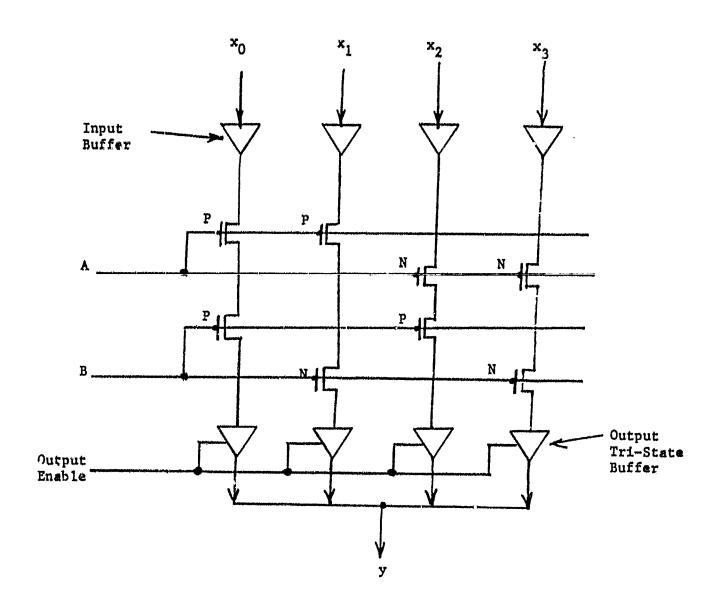

| 2.24       | Protocol of a Routing Circuit of a Single Module . | 2-58       |

| 2.25       | Block Diagram of a 3-Module Routing Design         | 2-59       |

| 2.26       | A Generalized Routing Model                        | 2-60       |

| 2.27       | An Implementation of a 1-out-of-4 Multiplexer      | 2-61       |

| 3.1        | Block Diagram of an IBM S/360 Processing Unit      | 3-14       |

| 3.2        | Scheme for Decoder Checking                        | 3-15       |

| 3.3        | DFT Techniques Comparison Table                    |            |

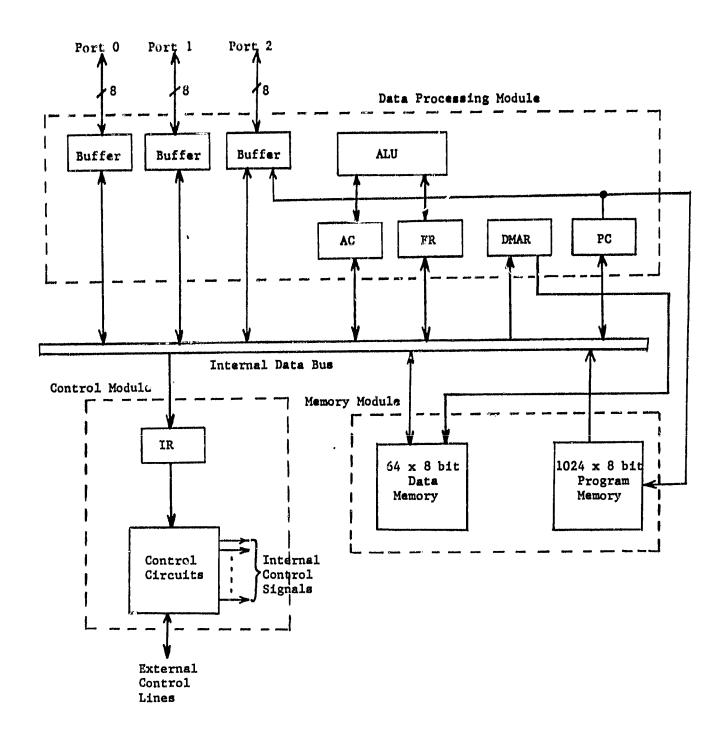

| 4.1        | A General DFT Structure                            | 4-12       |

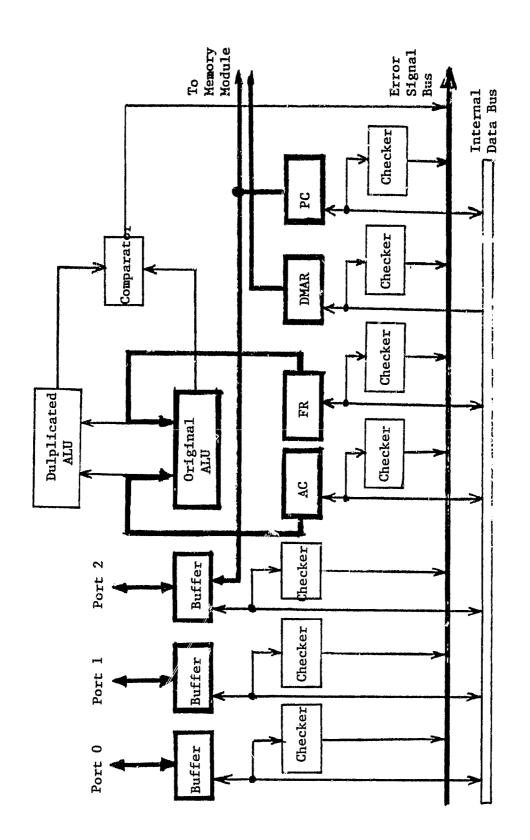

| 4.2        | Block Diagram of the Structure of Intel 8080       |            |

|            | Mioroprocessor                                     | 4-13       |

| 4.3        | Real-Time Monitoring of Critical Module, an        |            |

|            | Example                                            | 4-14       |

| 4.4        | General "Store/Generate and Compare" Technique     | 4-15       |

| 4.5        | General "Store and Generate Built-in Testing"      | 4-15       |

| 4.6        | Block Diagram of Test Set "Store and Generate"     |            |

|            | Scheme                                             |            |

| 4.7        | Block Diagram of Syndrome-Test Scheme              | 4-17       |

| A1         | Two-Input CMOS NOR Gate                            | <b>X-3</b> |

| <b>B</b> 1 | NOR Gate Parasitic Flip Flop Fault Detection vs.   |            |

|            | Innut Patterns                                     | R          |

| 1. Report No. JPL Pub 82-50 2. Government Accession No.                           | 3. Recipient's Catalog No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Title and Subtitle LSI/VLSI Denign for Tenterility                             | 5. Report Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Analysis and General Approach                                                     | 8. Performing Organization Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7. Author(s) Albert Y. Lam                                                        | 8. Performing Organization Report No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9. Performing Organization Name and Address                                       | 10. Work Unit No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| JET PROPULSION LABORATORY California Institute of Technology 4800 Oak Grove Drive | 11. Contract or Grant No. NAS 7-100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pasadena, California 91109                                                        | 13. Type of Report and Period Covered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12. Sponsoring Agency Name and Address                                            | JPL Publication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NATIONAL AERONAUTICS AND SPACE ADMINISTRATION Washington, D.C. 20546              | 14. Sponsoring Agency Code X141-40-00-01-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15. Supplementary Notes                                                           | A STANDARD CONTRACTOR OF THE STANDARD CONTRACTOR |

# 16. Abstract

For many years since the advent of large-scale integrated circuit technology, digital system testing has been a challenging problem. Intensive research efforts are directed towards the discovery of techniques (systematic and/or ad hoc) for designing digital systems with good testability and maintainability. This report presents a survey of most major contributions to the theory and practice of digital design for testability. Detailed analysis of each of the contributions is also presented, providing the reader with necessary background materials for the main objective of this geport — from the comparison of all design for testability techniques studied, some conclusions may be drawn to establish a general guideline/approach to designing testable circuits for large scale integration and very large scale integration.

|     | enteres de la companya de la compan<br>La companya de la co | <b>.</b>       | 10.                    | ranger (m. 1945)<br>1940 - Paris Marie (m. 1946)<br>1941 - Paris Marie (m. 1946) |           |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|----------------------------------------------------------------------------------|-----------|

| 17. | Key Words (Selected by Author(s))                                                                                                                                                                                                |                | 18. Distribution State | ment                                                                             | 0         |

|     | Integrated Circuits Electronics and Electrical Eng Computer Operations and Hardwa Computer Systems                                                                                                                               |                | Unclassified           | - Unlimited                                                                      |           |

| 19. | Security Classif. (of this report) 20                                                                                                                                                                                            | ). Security Cl | assif. (of this page)  | 21. No. of PagUs                                                                 | 22. Price |

|     | Unclassified                                                                                                                                                                                                                     | Unclassif      | Eied                   | 126                                                                              |           |

#### SECTION 1

#### INTRODUCTION

Integrated circuit technology is moving from SSI/MSI to LSI/VLSI. The problem of circuit testing (at chip, board, and system levels) is thus aggravated not proportionally but exponentially. Since the advent of SSI, fault modeling techniques have been exclusively used for test generation/fault simulation, and exhaustive explicit testing of SSI/MSI devices has been possible and practical. For LSI/VLSI devices, however, fault modeling and exhaustive testing are clearly impractical if not impossible. For instance, as many as 30 defects could be associated with a two input AND gate and a 10,000-gate chip could contain 300,000 defects, each of which may be a fault cause. This large number of faults, plus the multiplicity of fault occurrences, tremendously complicates the modeling problem. As for exhaustive testing, the total number of test vectors N, the number of inputs m, and the number of storage elements n have the following relationship:

$N = 2^{m+n}$ .

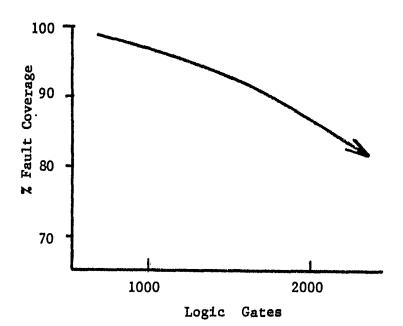

Therefore, an LSI chip with 40 inputs and 140 storage elements may require 2<sup>180</sup> test vectors. If these vectors are run at a rate of 10<sup>7</sup> vectors per second (10 MHz), it will take 10<sup>47</sup> seconds or  $3\times10^{39}$  years to run an exhaustive functional test on the chip once [1]. Figure 1.1 shows the trend of fault coverage obtained in practical cases versus network size [2]. We see that if the network (sequential) contains 2000 or more elements, the ability

of Automatic Test Equipment (ATE) to generate tests decreases to unacceptable levels.

Therefore, incorporating testability characteristics into a digital design such that the final product (the device) can be tested cost-effectively should be the basic guideline to reliable IC design.

#### 1.1 TESTABILITY AND GOOD TESTABILITY

Let us define the terms "Testability" and "Good Testability".

"Testability" may be defined as the ability to determine the status (functioning as specified or not functioning as specified) of the unit under test (UUT) within a prescribed time period.

A testing or design technique that leads to "Good Testability" of the UUT should provide the following desirable features [3]:

- (1) Contains no logical redundancy;

- (2) Reasonable test set size;

- (3) Test set can be derived fairly easily;

- (4) Results of the test are easily observable at the outputs;

- (5) Results of the test can be interpreted fairly easily;

- (6) Good fault coverage for a specified fault set;

- (7) Faults locatable to the desired degree.

If additional hardware and I/O's are used to enhance testability, the following features are also desirable :

- (8) Reasonable hardware overhead;

- (9) Minimal additional I/O pins;

- (10) Minimal functional processing speed interference.

Although not quantitative, the above features of "Good Testability" give some means for measuring and evaluating the testability of a digital design. We will use these features as a benchmark to qualitatively measure and evaluate the effectiveness and efficiency of the DFT techniques discussed in sections 2 and 3.

# 1.2 PREREQUISITES OF DESIGNING FOR TESTABILITY

Design for testability can become an accepted practice only if the following prerequisites are established and well understood: 1.2.1 Well Specified Design Framework

- (i) What design techniques are to be employed?

- (a) On chip testing only:

- Hardware built-in test (BIT)

- Hardware/Software BIT

- (b) Off chip testing only:

- Design for easily testable logic functions

- Architectural design to enhance testability

- Modularized design approach

- Design for ATE compatibility

- (c) On chip and Off chip testing:

- A combination of part or all of the above techniques.

In order to achieve good testability and optimal lifecycle cost, on chip hardware/software BIT is a must. For

\* See section 1.4 for descriptions.

instance, operation/support costs may run as high as 50% of its total life-cycle cost for a typical weapon system over its life-cycle (about 20 years), (Engineering evaluation 3-4%, Prototype/Preproduction 12%, Production 35%)[3]. Hence operation/support of the system represents the primary cost factor. Moreover, DoD studies [3] show that systems designed with built-in testability achieve up to 70% of life-cycle cost reduction. Therefore, incorporating built-in testability into the design of a system not only enhances its testability but also reduces its ownership cost.

(ii) What are the standards for measuring and evaluating testability?

A standard tool is needed to relate testability measures to system availability and life-cycle cost, to calculate the testability of a design, and to relate a design in progress to the requirements. The testability measures can be defined in terms of the "CONTROLLABILITY" and "OBSERVABILITY" of the circuit. A paper by Stephenson and Grason [4] gives formulae for assigning weights to these parameters. Also, an IBM 360 program which is based on this paper has been written at Bell Telephone Laboratories as a tool for measuring the testability of an arbitrary circuit. This program is also reported to be able to indicate the difficulty of test generation. A circuit,

if shown difficult to test, can be modified before being released for test generation.

#### 1.2.2 Well-defined Failure Universe

It is very important to specify a finite and realistic "failure universe" (fault set) to serve as the basis of testability design and evaluation. For LS1/VLSI circuit (including memory circuits), stuck-at, bridging, floating, parasitic flip flop, and pattern sensitive faults are the common circuit faults that may produce error(s) at the output(s). All of these faults originate from two types of hardware failures: Manufacturing Defects and Wear-out Mechanisms. In the following subsection, we will discuss hardware failures, MOS LSI/VLSI circuit faults and errors in greater detail.

Different fault sets accepted as a coverage basis often result in different approaches to designing for testability. The more types of faults the product (the device) is expected to cover (i.e., the occurrence of any of the specified fault types can be detected in accordance with the prescribed testability requirement(s)), the less is the possibility of achieving such expectation.

\* A chain of faults may originate from the source of hardware failure. As the fault propagates and affects the circuit output(s), we say an error results.

#### 1.2.3 Implementation Technology

It is critical for the circuit designer to be able, while considering all design and testability specifications, to determine what implementation technology is to be employed for the realization of his/her design. For example, with increasing integration (SSI/MSI to LSI/VLSI), both the memory and general purpose logic device manufacturers recognize the inadequacy of the classical stuck-at fault model for characterizing their new products. Neighbor intraction and interaction are becoming more of a problem. Hence guidelines for DFT, fault model(s), and testing techniques all have to be revised. Further, as will be shown in the following subsection, the CMOS implementation and the NMOS implementation of a design have different impacts on DFT. Different approaches have to be employed to fulfill the same testability requirements.

#### 1.3 HARDWARE FAILURES, MOS CIRCUIT FAULTS AND ERRORS

Hardware failures are mainly due to (1) manufacturing defects such as lithographic misalignment, wafer imperfection, etc. and (2) wearout mechanisms, such as metal migration and ion contamination. Hardware failures may result in the following kinds of circuit faults common in MOS circuits [5]:

- (1) Stuck-at Fault the logical value of a line is always stuck at 1 or 0. This kind of fault is caused by (1) oxide pinhole,

- (2) missing or defective pull-down transistors, (3) pull-down

- transistors source-to-drain shorts, and (4) pull-up transistors source-to-drain shorts.

- (2) Bridging Fault two adjacent conducting layers or overlapping layers short together. Lithographic misalignment is one of the causes of this fault type.

- (3) Floating Fault a conducting wire is separated or broken and may "float" between logic 1 and logic 0 depending on the physical geometry and electrical environment of its neighborhood. Missing or defective pull-up transistors; missing contact cut or metal cover; and metal, polysilicon, and diffusion opens are the causes of this fault type.

- (4) Parasitic Flip Flop (PFF) Fault This fault has five potential causes as listed in appendix A. The occurrence of this fault in a combinational gate (a NOR gate, for example) can turn the gate into a D flip flop type sequential circuit. Hence, the logic function of the affected circuit is altered in a very unpredictable fashion. Interestingly, CMOS circuits may have PFF faults, but NMOS circuits may not have them unless implemented with enhancement mode pass transistors only. Therefore, in the design for testability of CMOS devices, one may have to consider this PFF fault preblem. A method is presented in appendix B to eliminate the undesirable effects due to PFF faults. This method is effective but somewhat disadvantageous in the sense that its implementation in a circuit may slow down the processing speed significantly.

- (5) Pattern Sensitive Fault this type of fault occurs in high density memory circuits (a 64K RAM chip, for example). It may also occur in high density general logic devices such as microprocessors. In high density general logic circuits, switching of a conducting wire (master wire) may cause switching of a neighboring wire (slave wire) to the same logic value, depending on the current density in the master wire. Hence this fault may be viewed as an intermittent bridging fault. For memory circuits, there are two pattern sensitive fault models:

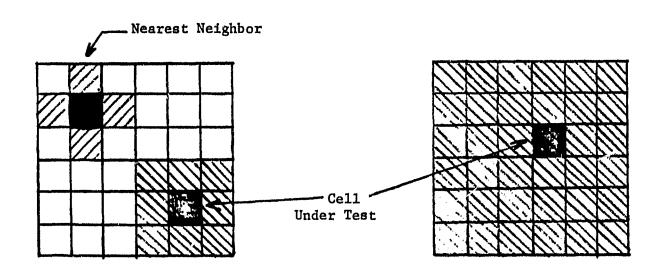

- (a) Nearest Neighbor fault model (figure 1.2a) when the content of a memory cell (master cell) is switched, the contents of any one or all of its nearest neighboring cells (slave cells) are inductively switched.

- (b) Neighborhood fault model (figure 1.2b) this model is similar to the nearest neighbor fault model except that the affected neighboring (slave) cells cover a wide area of the master cell.

The following shows the test pattern requirements for a 64K RAM for the stuck-at, nearest neighbor, and neighborhood fault models with N representing the number of memory cells [1].

| Fault Model      | Pattern         | Number of Test Vectors  |

|------------------|-----------------|-------------------------|

| Stuck At         | 2N              | 1.311 × 10 <sup>5</sup> |

| Nearest Neighbor | 2N3/2           | 3.355 × 10 <sup>7</sup> |

| Neighborhood     | 2N <sup>2</sup> | 8.590 x 10 <sup>9</sup> |

The neighborhood model requires almost five orders of magnitude more test vectors than the stuck at model. To fully test a 64K RAM with test cycle rate of 375 ns, it takes 49ms/3221sec if the stuck-at/neighborhood model is used [1].

It is seen that MOS LSI circuit faults fall into five catagories, namely, CLASSICAL STUCK-AT, BRIDGING, FLOATING, PARASITIC FLIP FLOP, and PATTERN SENSITIVE faults. These faults are, however, caused not only by manufacturing defects but also sometimes by wearout mechanisms in field use. There are two major wearout mechanisms:

- (1) METAL MIGRATION -- which eventually results in wire separation. Electrical current in aluminum conductors induces movement of aluminum material in the conductors and eventually leads to separation of conducting wires. A metal wire disconnected from a signal source can result in a floating fault. This natural migration process can be reduced by reducing the current density in the conductors.

- (2) SODIUM ION CONTAMINATION -- which eventually results in an oxide pinhole at the input of a n-channel enhancement mode transistor. Sodium ions tend to move towards and accumulate in regions of relatively high electrical field (for example, under transistor control input ports). Continuous accumulation of

sodium ions in a region will eventually result in that region being shorted to ground and equivalently stuck at zero. Sodium ion contamination has been found to be the cause of 35% of field failures [6].

Since the above postulated circuit faults are the most common faults in MOS LSI/VLSI devices, they may be considered as the elements of our "Fault Set" or "Failure Universe". Every DFT technique that we will discuss later on deals with these fault elements only. However, multiple, random occurrence of any or all of these faults in a circuit is assumed and considered. Some of the techniques have the restrictions that in the circuit under test, the fault is single and/or the errors at the output(s) are unidirectional.

#### 1.4 INTRODUCTION TO DESIGN FOR TESTABILITY

In section 2 of this report, we will present an overview of most of the major DFT techniques developed in the academic and industrial sectors. Here we first introduce the general concepts of testing of digital systems, networks and devices. Also we want to discuss some basic problems of design for testability and some general approaches to these problems.

<sup>\*</sup>A unidirectional error is a random, symmetric, multiple error where all the fault bits fail to the same direction. Here "symmetric" means that both 0->1 and 1->0 are possible.

It is generally known that the cost and level of difficulty of circuit testing is an exponential function of the complexity of the circuit under test. The following shows the cost to detect and diagnose a fault at different circuit levels [2].

Cost to detect and diagnose a fault at different levels

| CHIP          | BOARD         | SYSTEM         | FIELD           |  |

|---------------|---------------|----------------|-----------------|--|

| <b>\$0.30</b> | <b>\$3.00</b> | <b>\$30.00</b> | <b>\$300.00</b> |  |

|               |               |                |                 |  |

We see that if a fault can be detected at the earliest stage, then the cost per fault detection can be substantially reduced. Further, as we have stated earlier, testing of VLSI devices is far from a fully solved problem. Testing of systems of a good quantity of VLSI devices at this stage would not only be infeasible but impossible. Therefore, much attention should be given to the level of testability at the chip and sometimes, board levels.

Chip testing techniques can be grouped into two categories: (1)

On-Line Testing and (2) Off-Line Testing. Both of these categories have two subcategories: (1) On-Chip Testing (Built-In Test)

and (2) Off-Chip Testing.

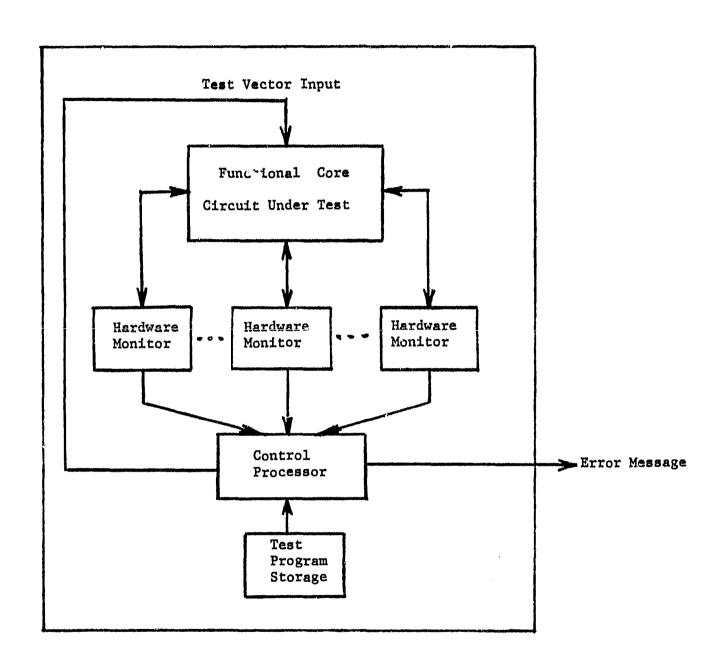

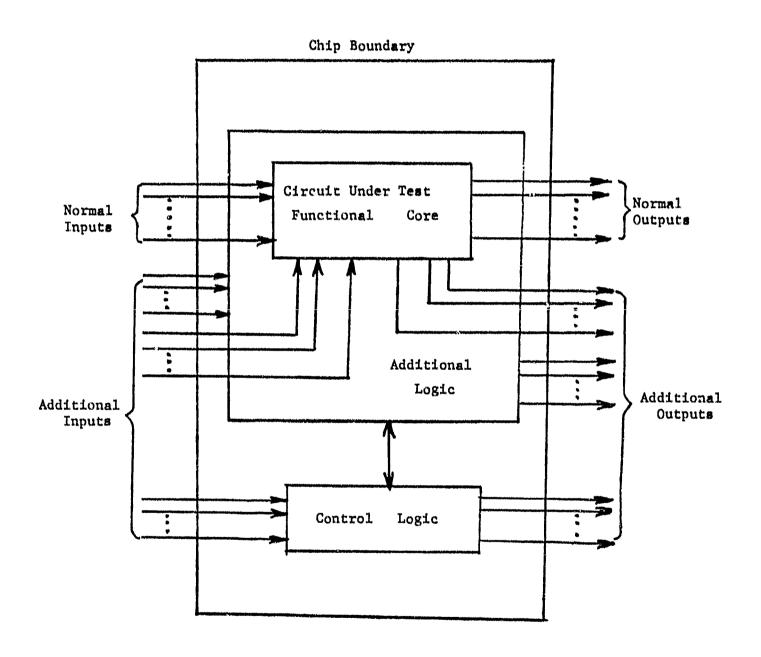

1.4.1 On-Line on-Chip Testing [7,8,9] (Figure 1.3):

All testing is concurrently performed while the chip is in normal

operation or in idle state. All or most of the supporting facilities for the self-testing, may they be hardware and/or software, are built into the chip. This means that additional hardware (monitors, microprocessors, etc.) and/or additional non-volatile memory for test/diagnosis programs storage have to be installed into the chip which may result in a substantial increase of chip area overhead. The employment of this technique is most justifiable and beneficial to the performance/reliability of totally self-supporting systems such as space-borne digital systems.

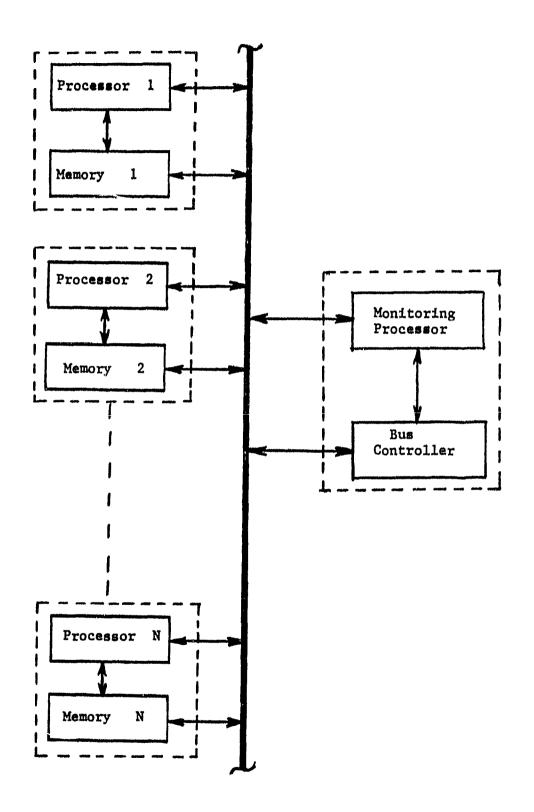

# 1.4.2 On-Line off-Chip Testing [10,11] (Figure 1.4):

This is also concurrent testing, but the monitoring/testing hardware/software are all built off the chip. A self-testing distributed multiprocessor network is an example. Processors in different chips test/check each other periodically. In case of error occurrence, according to some predetermined algorithms and sequences, the majority processors "out-vote" the minority processor(s) (usually a single processor) which is then subject to some rollback and recovery attempts. If such attempts are unsuccessful, the minority processor is cut off from the network, and the majority processors may take over and share the tasks of the "cast-away" processor(s). In this case, the processing speed is decreased. Another way is to use "spare" processor(s) to replace the "abandoned" one(s). But this has the disadvantage of in-

creased hardware cost and redundancy. This testing scheme has some other disadvantages which will be discussed in section 3.

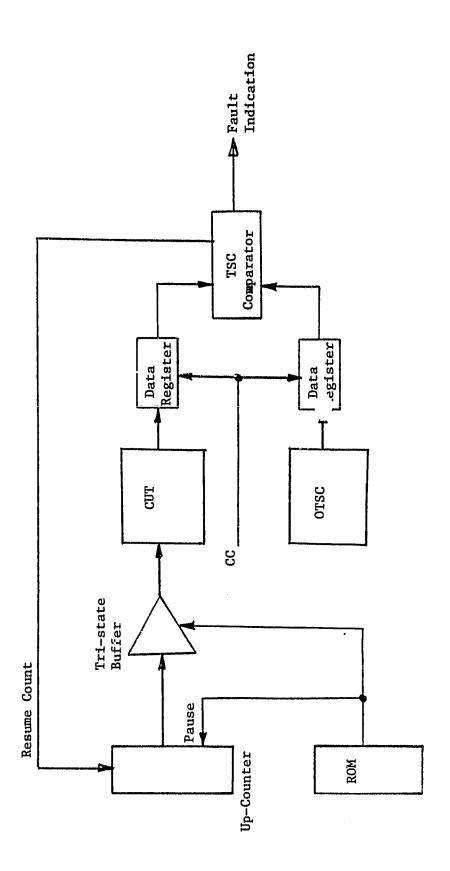

1.4.3 Off-Line on-Chip Testing [12,13,14,15,16,17,18] (Figure 1.5): This testing scheme is generally known as "Built-In-Test/Built-In-Test Equipment" testing and is viewed as the most useful and promising technique(s) to improve and enhance testability of LSI/VLSI devices. In this scheme, additional logic is first built into the chip to monitor the functional core (circuit under test (CUT)), to increase controllability and observability of the CUT, and/or to allow for testing with reduced/compressed test data sec. With the help of automatic test equipments (ATE), the testing process is greatly simplified. Also in some designs, the additional built in logic which is in the form of totally self-checking (TSC) checkers, will inform the outside world of most functional or signal transmission errors, thus enhancing the diagnosibility of the device.

One of the drawbacks of this scheme is that the checking and testing of the device is not quite spontaneous (concurrent), which may aggravate the error latency problem in some critical systems. This problem is intrinsic even in systems with concurrent self-testing/self-checking capabilities. Integrated carcuit manufacturers, however, favor this scheme because of its good cost-effectiveness and excellent fault coverage of their prescribed fault set. They can minimize the error latency problem of their products in field use by specifying stringent dynamic

specifications such as maximum clock cycle time and by recommending automated dynamic diagnostics of critical systems.

In sections 2 and 3 we will study some "BIT/BITE" testing techniques and discuss their advantages and disadvantages.

## 1.4.4 Off-Line off-Chir Testing

In this scheme, very little is done to the original functional core. The only additional logic that may be built in are circuits at the two ends (input and output ports) of the CUT for the enhancement of ATE compatibility. Very complex testing algorithms and data sets may be required and for LSI/VLSI devices, the testing process, if effective, is usually very time-consuming and costly.

As will be discussed in section 4 of this report, different design, performance, and testability requirements would call for different DFT techniques and strategies. The following lists some basic problems of DFT and some general approaches to these problems.

#### Basic Problem

1. The complexity of the device - the vast number of gates in LSI/VLSI devices ranges from 500 to 50,000. This poses problems for the ATE to assume its diagnostic role as a general IC testing equipment.

- 2. The inaccessibility of individual cells limited pin-to-gate ratio restricts the accessibility of cells in a chip. Testing the cells individually would simplify the test generation and cesting processes.

- 3. The irregular structure of general purpose logic devices the more irregular the structure of a device, the more difficult and complex test generation/fault simulation and testing procedures are.

- 4. Limited availability of pind the incorporation of a good quantity of built-in testing logic may be impossible due to the shortage of pins available for the primary inputs and outputs of these additional logic.

- 5. The difficulties in testing sequential logic no adequate and efficient test generation algorithms for LSI/VLSI sequential devices exist. Some alorithms, however, are useful for testing large combinational (latch free) circuits (e.g. >5000 gates) [19,20].

- 6. Checking the checker problem Additional circuits (checkers) are often built into the devices to monitor the operations and signal propagations. Hence correct functioning of these checkers is vital. To aviod the checking the checker problem, the monitoring circuits must at least be built self-checking.

#### 1.4.5 General Approach

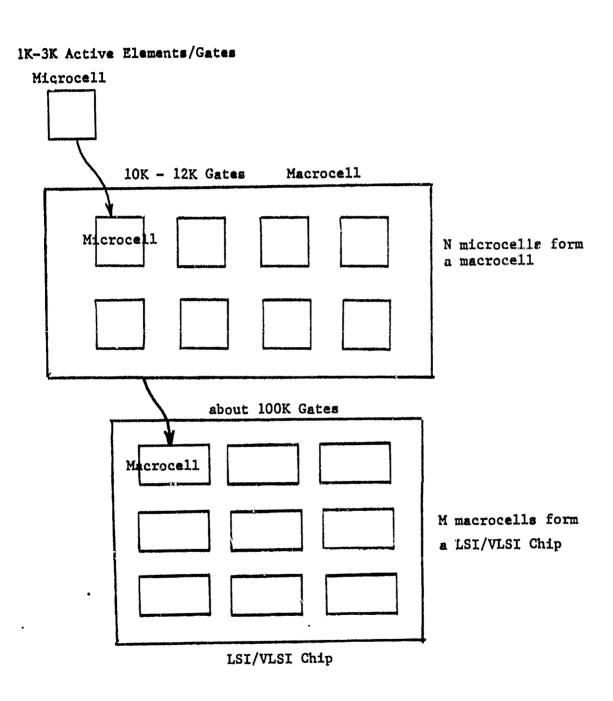

1. Modularization - To ease the problem of employing ATEs as general testing equipment for complex LSI/VLSI devices,

modularized design of the functional core may be a good approach. The functional core is divided into several subfunctional logic entities called macrocells. Each of these macrocells consists of several modules called microcells which may be identical or readily available from the microcell libraries of the CAD system (figure 1.6). The upperbound of the microcell baseline may be restricted to 800-1200 gates [3]. The microcells may be PLAs (programmable logic arrays [21]), GLSs (general logic ptructures [22]), GLFs (general logic functions [23]), ULMs (universal logic modules [24]), and cellular arrays [24]. Each of the macrocells may contain up to 12,000 gates [3] and should be made accessible and observable through the primary inputs and outputs of the device, either directly or indirectly through multiplexed routes. This technique not only eases the problems of automatic testing and fault simulation but also facilitates the design process. The irregular structure of the general logic devices can be 'ade regular by implementing the defined circuit functions with the aforementioned general microcall circuit structures.

2. Multiplexed Routing - The accessibility of each of the cells of a device can be drastically increased by putting in multiplexed signal propagation routes between primary inputs/outputs and individual cells [16]. Bus multiplexers are placed at the input and output buses of each cell such that the primary inputs/outputs can be directly connected(routed)

- to the inputs/outputs of the cell. If the device can be partitioned into many cells such that each cell has only a few inputs and outputs, exhaustive testing can be performed on each cell, and test generation is virtually eliminated.

- 3. Level Sensitive Scan Design (LSSD) [12] The enormous number of internal states of a large sequential network makes it impossible to effectively test such a network. The LSSD technique, first proposed by IBM, not only can be used as an effective tool for the structured design of easily testable sequential devices but also for "System Bring-up" and for field serviceability. Basically, this technique allows a sequential network, while switched to the "Test" mode, to be physically converted into a combinational (latch-free) network. Therefore, along with the employment of the multiplexed routing and modularization design techniques, a large combinational/sequential device can be cost-effectively tested.

- 4. Totally Self-Checking (TSC) Checkers/Comparators and Fault Monitors The incoporation of signal flow checkers and circuit fault monitors into a design is essential to the upgrading of the reliability and testability of such a design. It is clear that these checkers and monitors should be, if not failure-proof, totally self-checking for reliable performance. It has been shown [25] that a class of totally self-checking circuits, which can be used as checkers and monitors, can be designed using a very simple coding scheme cailed the "1-out-

- of-2 code" (see section 2). Basically, if there is any single fault in a TSC circuit, the output will be a non-code word which is interpreted as an error, indicating malfunctioning.

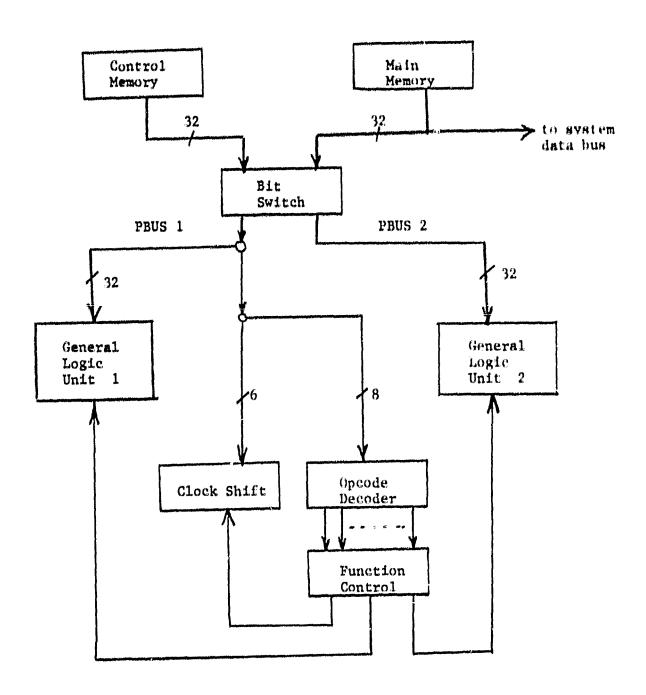

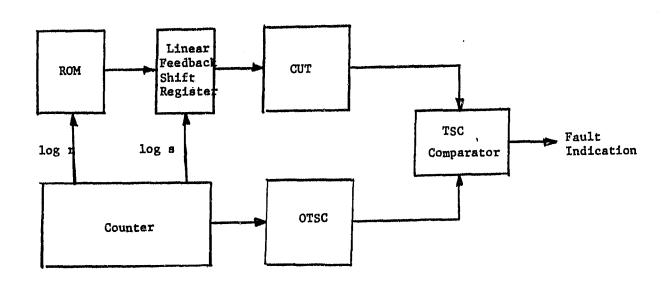

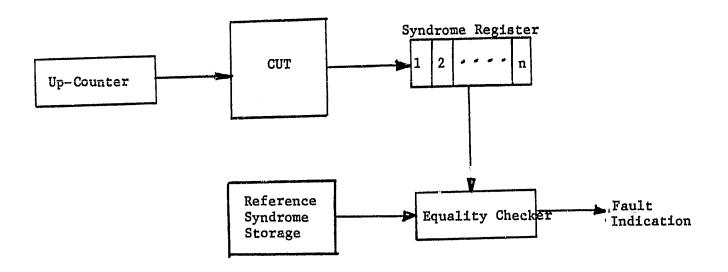

- 5. A General Structured Approach to Design for Testability All of the aforementioned DFT techniques are somewhat non-general in the sense that their applications are only practically suited for some specific circuit structures. To provide a general scheme for the design for testability, a general structured approach is needed. At the present time, no such approach has been proposed. A DFT technique called the "Store and Jenerate" technique, proposed by Agarwal and Cerny [18], may be by far the most promising scheme ever proposed. Although several unresolved problems still exist, as mentioned in their paper, this scheme provides a general circuit design structure which, with little modifications, can be adapted to any set of DFT specifications and requirements.

As suggested by its name, this technique has the test set and the calculated test response either stored and/or generated on chip. Thus, periodic real-time testing of the CUT is possible. The CUT is first divided (with additional hardware as described in (2) of subsection 1.3) into several macrocells. All sequential elements in each macrocell are converted into latch-free combinational elements (using LSSD), and thus, full testing of each macrocell becomes possible and practical. Using TSC checkers and comparators, the actual test response

of the CUT is compared with the pre-stored/generated calculated response. Any errors resulting from circuit faults and/or signal transmission errors in the CUT are detected. Quite clearly, this technique can achieve a relatively large fault coverage.

There are still several unresolved problems. The main problem is the large storage requirement for the test set and the calculated response set. Although the test set can be generated on chip without much difficulty, the on-chip generation of the calculated response set is non-trivial. Trade-offs between the storage and generation of the test and response sets have to be made. Scheme(s) for lossless compression of these two data sets should also be investigated.

In the following section (section 2), we will present an overview of several useful techniques and schemes for the enhancement of testability and maintainability of LSI/VLSI devices. In section 3, we will discuss the relative strong and weak points of these techniques. In section 4, we will try to merge some of these techniques together to form a general structured approach to designing testable LSI/VLSI devices.

Figure 1.1 Trend of Fault Coverage Obtained in Practical

Cases Versus Network Size

Fig. 1.2a Nearest Neighbor

Fault Model

Fig. 1.2b Neighborhood

Fault Model

Figure 1.3 On-Line on-Chip Testing Block Diagram

Figure 1.4 On-Line off-Chip Testing Block Diagram

Figure 1.5 Off-Line on-Chip Testing Block Diagram

Figure 1.6 Micro/Macrocell Structure Development

#### SECTION 2

### OVERVIEW OF MAJOR DESIGN FOR TESTABILITY TECHNIQUES

In this section we will discuss the design principles of most major DFT schemes and techniques.

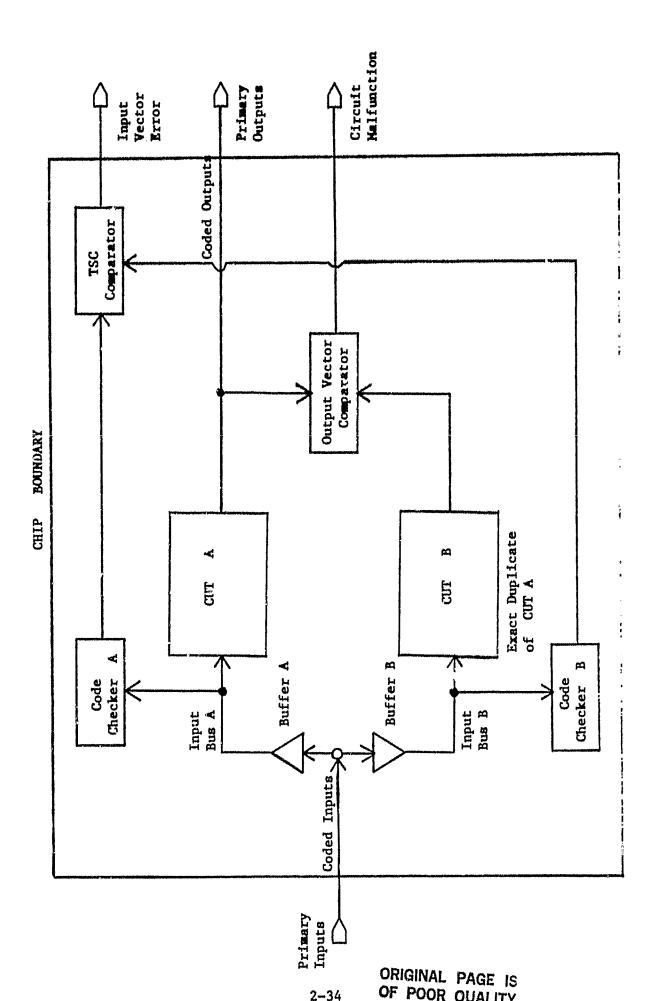

2.1 CLASSICAL APPROACH - DUPLICATE AND COMPARE TECHNIQUE

Quite clearly, it is desirable that if a device is to be designed

for testability and maintainability, it should be made capable of

informing the user of any malfunctions or errors during

operation. The classical approach to achieving this desirable

feature is very simple in principle:

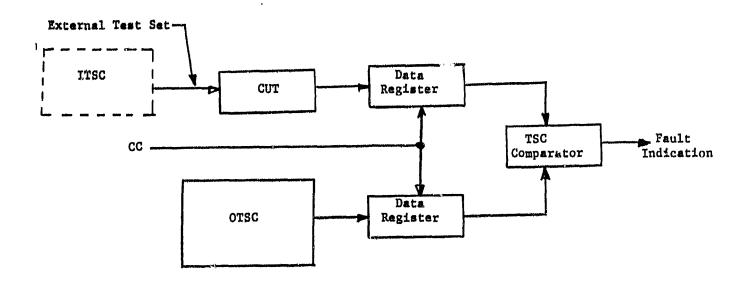

The circuit under test is duplicated on chip (figure 2.1). During normal operation, the input vectors are applied to both circuits. The responses of the circuits are then compared for identicalness, otherwise circuit malfunction or error is said to have occured.

Clearly this scheme has a major disadvantage - hardware redundancy. Nevertheless, there are also some <u>technical</u> problems to be resolved before this scheme becomes applicable:

1. The assurance of valid input vectors to both of the circuits under test - Since the input vectors from the primary input port of the device are split and sent to the inputs of the two CUTs, they might be erroneous due to transmission problems or circuit faults on input buses A and/or B. Hence, both of the input vectors should be checked for validity just before they

first encoding all input vectors according to some selected coding scheme (parity coding, for instance) and then having these input vectors checked by some code-checkers, as shown in figure 2.1. If there is an erroneous input vector to either one or both of the CUTs, the code-checkers should flag this error to the user at the "Input Vector Error" pin. In the following subsection (2.1.2), we will present a design of such code checkers.

2. The assurance of correct functioning of the checkers and comparators - As mentioned in section 1.4, the checkers and comparators should be designed to be totally self-checking to guarantee the validity of the error flags (i.e. the "Input Vector Error" flag and the "Circuit Malfunction" flag). At all times, if there are no circuit faults inside the checkers and comparators, then the checkers will be fully capable of examining the input words for code-validity and so will the comparators in determining the identicalness of its two input vectors. If there are some circuit faults inside the checkers and the comparators, then the checkers and comparators may still be functioning for most of the time. The properties of the sequence of the input vectors to these TSC circuits diversely affect the checking capabilities of these TSC circuits under the influence of circuit faults.

Nevertheless, in this SELF-CHECKING design scheme, the checkers should be able to flag internal circuit faults as well as

input vector errors, provided there are no circuit faults. As for the output comparator, it should also be able to flag internal circuit faults as well as output errors from either or both of the CUTs.

The design principles and techniques of TSC circuits are shown in the following subsection.

## 2.1.1 Morphic Boolean Algebra and Morphic-AND Gate

A mapping from the two-valued Boolean variable to Morphic Boolean variable is defined as follows:

$$M : [(e1,e2),(\overline{e1},\overline{e2})] \rightarrow 0$$

$[(e1,e2),(\overline{e1},e2)] \rightarrow 1$

where ej and e2 are elements of the set  $\{0,1\}$ .

Hence while in the positive Boolean algebra, TRUE and FALSE are represented by 1 and 0 respectively, Morphic TRUE  $(1_{\rm M})$  and Morphic FALSE  $(0_{\rm M})$  are represented by either (0,1) or (1,0) and (0,0) or (1,1) respectively. Morphic Boolean operations are defined exactly as those of the two-valued Boolean algebra. For example: Morphic-AND Function

$$1_{\text{M}} * 0_{\text{M}} = 0_{\text{M}} <---> (0,1) * (1,1) = (1,1)$$

$$1_{\text{M}} * 1_{\text{M}} = 1_{\text{M}} <---> (1,0) * (0,1) = (1,0)$$

where \* is the AND function.

It is not difficult to see that the mapping of the two-valued Boolean algebra into morphic Boolean algebra can be used to solve

the detection problem of stuck-at faults of a single line which is semi-passive, i.e., a line that has a constant value under normal operation. Suppose in some digital network there is a line, A, whose logic value is always 1 under normal operation. There is no way, under normal operation, to detect the stuck-at-1 fault of this line. However if the network is designed with morphic logic instead, then line A will be apped into two lines A1 and A2. Since (A1,A2) can take on either (0,1) or (1,0) under normal operation, if the same type of fault occurs at line A1 or line A2, it will eventually be detected because sooner or later, even under normal operation, (A1,A2) will become (1,1) or (0,0), which represents error if we assume a 1-out-of-2 code.

Definition 2.1 : 1-out-of-2 Code. A codeword (valid) is defined as Morphic logic 1 (1 $_{

m M}$ ) while a non-codeword (invalid) is defined as Morphic logic 0 (0 $_{

m M}$ ).

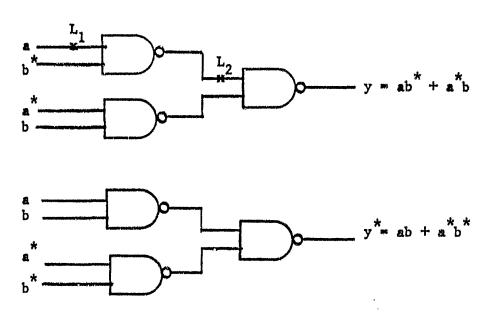

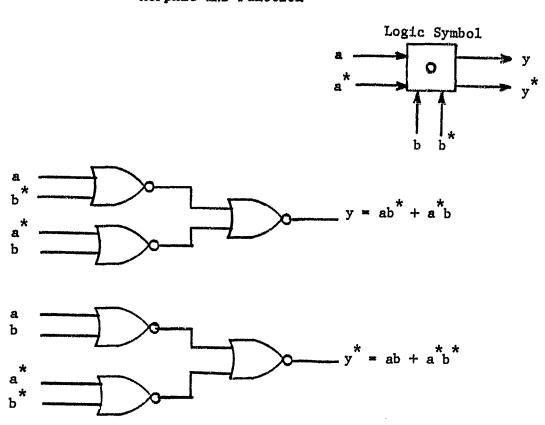

One of the logical elements that can be used as the basic building block of morphic circuits is called the <u>Morphic-AND</u> gate. Let  $A=(a,a^{\#})$  and  $B=(b,b^{\#})$  be two morphic variables and  $Y=(y,y^{\#})$  be a morphic function of A and B, then the Morphic-AND function is defined as follows:

$$[Y \times (y, y^{\#})] \times [A \times (a, a^{\#})] + [B \times (b, b^{\#})]$$

where  $y \times ab^{\#} + a^{\#}b$

$y^{\#} \times ab + a^{\#}b^{\#}$

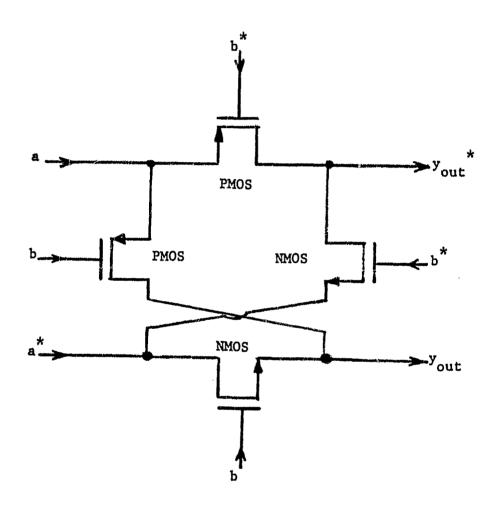

Figures 2.2 and 2.3 show the 2-level NAND-NAND logic and NOR-NOR logic implementations of the Morphic-AND function. Figure 2.4 shows the truth table of the Morphic-AND function. From the truth

table we can see that if we restrict all input vectors as being 1-out-of-2 codewords only ( the last four cases in the truth table), the output of the gate will be a valid codeword. Any non-codeword input (the remaining twelve cases) resulting from a transmission problem or bus faults will generate a non-codeword at the gate output, which indicates error.

The Morphic-AND gate also self-checks for any single internal stuck-at fault, as proved in the following:

Definition 2.2: Let X, Y, and F represent the sets of valid codeword inputs, valid codeword outputs, and prescribed faults.

Let  $x_1$ . X be a codeword input,  $y_1$ . Y be a codeword output, and  $f_1$ . F be a fault. A circuit is said to be FAUL. SECURE if for every correct input  $x_1$ ,  $y_1$  is the correct fault-free output and  $y_1$  is the output in the presence of a fault  $f_1$ , then  $y_1$  =  $y_1$  if  $y_1$  is a valid codeword or else  $y_1$  is an invalid non-codeword. A circuit is said to be SELF-TESTING if for every fault  $f_1$ , there exists at least one valid input  $x_1$  for which the resulting output,  $y_1$ , is a non-codeword.

Definition 2.3: A circuit is said to be TOTALLY SELF-CHECKING if and only if it is both FAULT-SECURE and SELF-TESTING.

To prove that this Morphic-AND gate is totally self-checking for

any single internal stuck-at fault. it suffices to show that if there is a stuck-at fault on either line L1 or L2 in figure 2.2, the circuit remains fault-secure and self-testing.

Line L1 s-a-0 case:

$$y^t \times a^{\#}b$$

From the truth table in figure 2.4, we see that there are, out of the sixteen input patterns, four valid codeword patterns. The output of the faulty circuit ( $y^t$  and  $y^{ht}$ ) due to these four input patterns are shown in the following table:

| Input | Pattern |   | <b>a</b> ,** | b | <b>b</b> * | y' | y*, | Output Pattern |

|-------|---------|---|--------------|---|------------|----|-----|----------------|

|       | 1       | 0 | 1            | 0 | 1          | 0  | 1   | 1              |

| 7     | 2       | 0 | 1            | 1 | 0          | 1  | 0   | 2              |

|       | 3       | 1 | 0            | 0 | 1          | 0  | 0   | 3              |

|       | 4       | 1 | 0            | 1 | 0          | 0  | 0   | 4              |

Input patterns 1 and 2 yield output patterns 1 and 2 which are the same outputs as if the circuit is fault-free. Input patterns 3 and 4 yield invalid non-codeword outputs. Hence the circuit is both fault-secure and self-testing.

Line L1 s-a-1 case:

$$y'*b^{\#}+a^{\#}b$$

$$y^{\#'}*y^{\#}$$

The responses of the faulty circuit are shown as follows:

# OFFICE PACE IS OF POUR QUALITY

|               | * |   |   |   |    | ıl          |    |   | ,              |

|---------------|---|---|---|---|----|-------------|----|---|----------------|

| Input Pattern | Ĺ | 8 | * | þ | b# | $\parallel$ | y' | • | Output Pattern |

| 1             |   | 0 | 1 | 0 | 1  | ea o        | 1  | 1 | 1              |

| 2             |   | 0 | 1 | 1 | 0  |             | 1  | 1 | 2              |

| 3             |   | 1 | 0 | 0 | 1  |             | 1  | 0 | 3              |

| 4             |   | 1 | 0 | 1 | o  |             | 0  | 1 | 4              |

Output patterns 1 and 2 show that the circuit is self-testing.

Output patterns 3 and 4 show that the circuit is fault-secure.

Hence the circuit is totally self-checking.

Line L2 s-a-0 case:

In this case, y' is always 1. Hence the responses are:

| Input | Pattern | å | 8.# | b | b* | y' | y*, | Output Pattern |

|-------|---------|---|-----|---|----|----|-----|----------------|

|       | 1       | 0 | 1   | 0 | 1  | 1  | 1   | 1              |

|       | 2       | 0 | 1   | 1 | 0  | 1  | 0   | 2              |

| !     | 3       | 1 | 0   | 0 | 1  | 1  | 0   | 3              |

| 1     | 4       | 1 | 0   | 1 | 0  | 1  | 1   | 4              |

Output patterns 1 and 4 show that the circuit is self-testing.

Output patterns 2 and 3 show that the circuit is fault-secure.

Line L2 s-a-1 case:

This fault is equivalent to line Li s-a-0.

Since by symmetry, the stuck-at faults of lines L1 and L2 represent all possible single stuck-at fault in the circuit, the circuit is thus proved to be totally self-enecking for any single stuck-at fault.

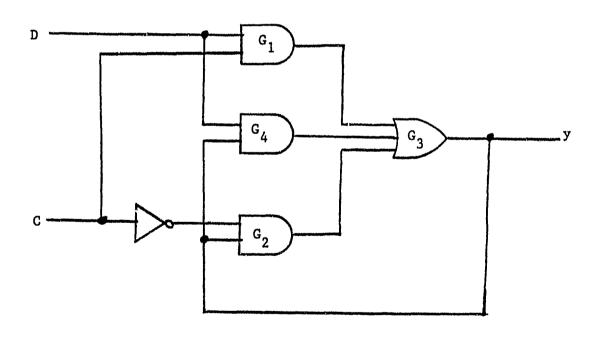

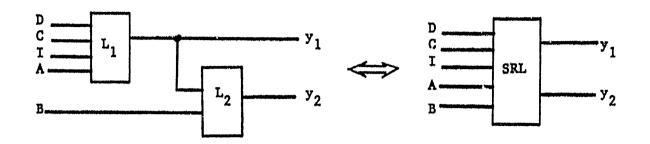

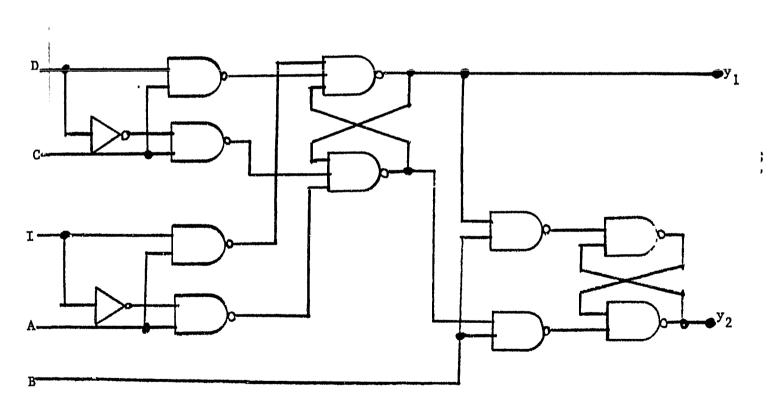

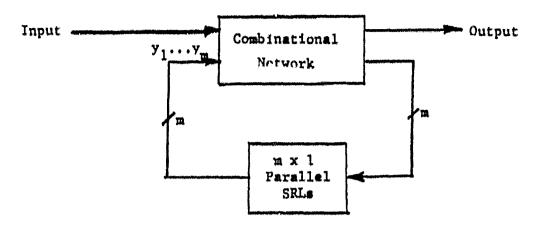

Note that Morphic-AND gates are not only totally self-checking for single stuck-at faults but also for single bridging, floating, and parasitic flip flop faults. The effect of circuit faults on TSC circuits is dicussed in appendix B.