## **General Disclaimer**

## One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some of the material. However, it is the best reproduction available from the original submission.

Produced by the NASA Center for Aerospace Information (CASI)

### TECHNICAL MEMORANDUM (NASA) 84

(NASA-CR-169691) A RF FRONT END INTERFACE AND AGC MODIFICATION (Ohio Univ.) 16 p HC A02/MF A01 CSCL 17G

N83-15276

Unclas G3/04 08097

<del>5</del> - 6

RF FRONT END INTERFACE AND AGC MODIFICATION

The Mini-L-82 RF front end has been interfaced to the Ohio University LORAN-C receiver utilizing a modified AGC system.

by

Stephen R. Yost

Avionics Engineering Center Department of Electrical Engineering Ohio University Athens, Ohio 45701

December 1982

Prepared for

NASA Langley Research Center Hampton, Virginia 23665

(Contract NGR 36-009-017)

1 1

### TABLE OF CONTENTS

| ι.   | INTRODUCTION                     | 1  |

|------|----------------------------------|----|

| II.  | RF FRONT END DESCRIPTION         | 1  |

| III. | AGC CIRCUIT DESIGN               | 1  |

| IV.  | RESULTS AND FURTHER OPTIMIZATION | 10 |

| ۷.   | ACKNOWLEDGEMENTS                 | 10 |

| VI.  | REFERENCES                       | 14 |

うり

PAGE

#### I. INTRODUCTION

The latest RF front end built by Burhans (Mini-L-82) has been successfully interfaced to the Ohio University LORAN-C receiver (Figure 1). In order for the front end to operate optimally, modifications were made to existing automatic gain control (AGC) circuitry already developed for the Ohio University LORAN-C receiver. This AGC circuit is described in reference 1. This technical memorandum will describe the hardware modifications to the AGC and other interface circuitry, as well as some preliminary results.

#### **II.** RF FRONT END DESCRIPTION

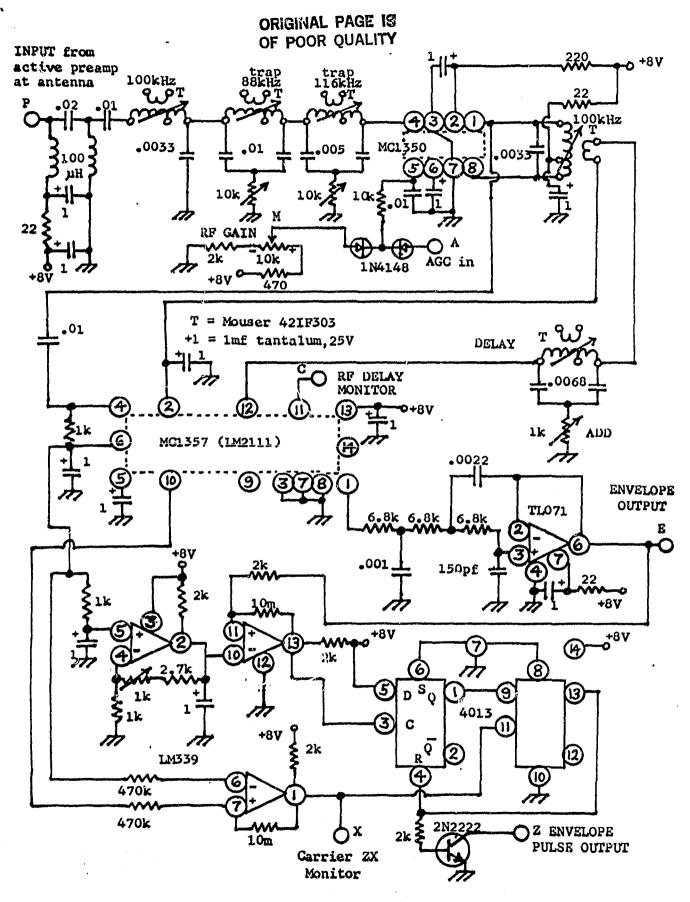

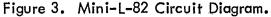

The Mini-L-82 RF front end (refer to Figures 2 and 3) is similar in overail design to the previous front end used with the Ohio University receiver but it has a much narrower bandwidth. Also, the Mini-L-82 has a much improved response to lower input signal levels. The output of the front end is a negative-going zero crossing pulse which is 10 microseconds long (Figure 4). In order for the receiver to operate properly, this pulse is inverted using a 7404 TTL inverter. The front end output is also open collector; therefore, an external pull-up resistor is provided. The positive-going 10 microsecond pulse is applied to the existing receiver circuitry which extends the pulse to 70 microseconds using a 74123 monostable. This 70-microsecond pulse is the optimum value for the search and track software routines. Efforts were made to adjust search and track software parameters to use the 10-microsecond pulse. However, it was found that this increased search time substantially and also created difficulties for the tracking loops because of the LORAN-C phase code which causes the zero crossing pulse to shift five microseconds with each phase reversal. Therefore, the interface between the Mini-L-82 and the receiver is essentially the same as that for the old front end.

#### III. AGC CIRCUIT DESIGN

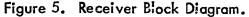

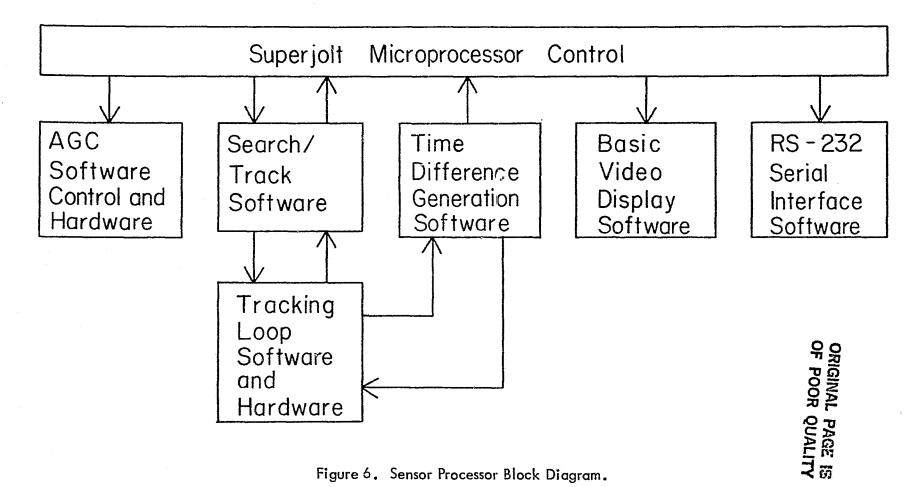

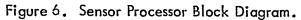

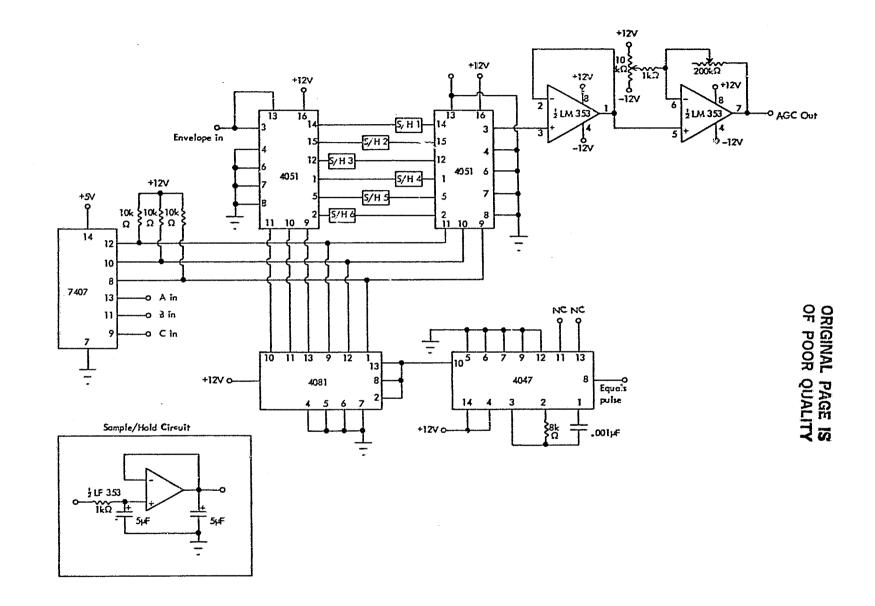

The AGC circuit is based roughly on the circuit designed for use with the old front end, and it is part of the sensor processor section of the Ohio University LORAN-C receiver (Figures 5, 6, and 7). The envelopes of all the tracked LORAN-C stations are sampled individually with the sampled voltages stored on capacitors. Each tracked station has its own "channel" in the AGC circuit (Figure 8). Channel address control is provided by the microcomputer. Since the magnitude of the sampled voltage often exceeds five volts, all of the AGC circuit components are CMOS integrated circuits with a twelve-volt power supply.

Even though the basic circuit design is similar to the previous AGC circuit, there are important differences to optimize performance with the new front end. The front end is designed to optimize performance at low signal levels. The AGC will "turn down" the gain on the LORAN-C stations until the region of best front end performance is reached. Since the various LORAN-C stations in a given chain are received at various signal amplitudes, it is the function of the AGC to reduce the gain on each

-2-

Figure 1. Ohio University Loran-C Reseiver.

್ಕ್,

· · San Anta

2.0

59.1

-4-

## Figure 4. Loran-C Chain Parameters.

-5-

-7-

# H

Figure 7, AGC Block Diagram.

-8-

### Figure 8. AGC Circuit Diagram.

-9-

1202

# ORIGINAL PAGE IS OF POOR QUALITY

station proportionate to that station's received signal level. The end result is that all of the LORAN-C stations are processed at a constant signal level. This condition is essential to the proper operation of an envelope-detector front end such as the Mini-L-82.

In the previous AGC circuit, the envelope was sampled during a 20- microsecond sampling window that was delayed 40 microseconds from the zero crossing. It was determined that this sampling area could possibly contain some sky wave contamination. In the current AGC design, the envelope is sampled during a 20-microsecond window starting at the zero crossing. The sampled voltage is dependent on the slope of the envelope at that point. Strong stations have a large slope; hence, a larger sample voltage is stored for that station. The sampled voltages are stored on their respective channels and adjusted for optimum front end performance by the gain and offset adjustment op-amp in the circuit. The AGC amplifier is an integral part of the Mini-L-82 front end design, it provides up to 60 dB of gain.

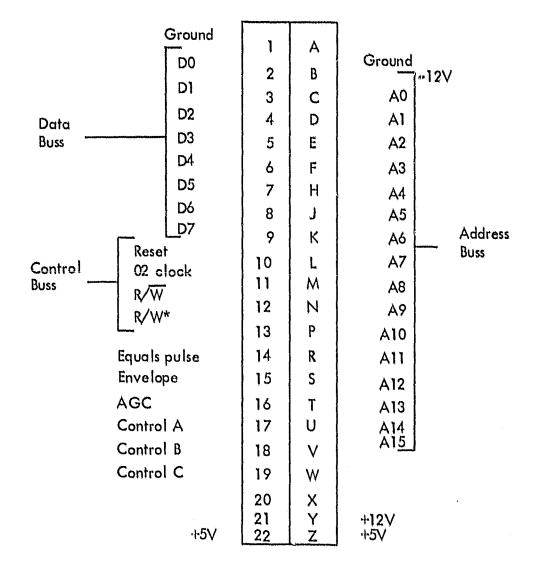

The AGC circuit was built on a Vector (tm) circuit card in the receiver that also contains 8K bytes of ROM/RAM memory and the serial interface (Figures 9, 10, and 11). Tantalum capacitors were used for the sample and hold circuits because of their low leakage characteristic.

#### IV. RESULTS AND FURTHER OPTIMIZATION

Preliminary results indicate that the new front end AGC combination perform satisfactorily. Side-by-side bench tests with Trimble 10A and Texas Instruments 9900 LORAN-C receivers have proven that the proper time differences are being obtained. Extensive bench tests and flight tests will follow as time permits.

Further optimization of the AGC circuit will occur as software to track all of the stations in a LORAN-C chain is developed. The AGC circuit was designed to sample up to six separate LORAN-C stations. Along with expanded station tracking software, a more sophisticated search routine is also under development. It is also planned to develop a printed circuit board for the AGC and enclose it with the RF front end in a sealed enclosure to reduce interference from the other digital circuits of the microcomputer.

#### V. ACKNOWLEDGEMENTS

The design, construction, and testing of the Mini-L-82 and the AGC circuitry has been funded by the NASA Joint University Program for air transportation research as a part of the continuing development of Ohio University's LORAN-C receiver. The author would like to thank Mr. Ralph Burhans for continuing his quest for a better front end for the Ohio University LORAN-C receiver. His advise and expertise were of great help in this project. Also providing invaluable assistance were Mr. Jim Nickum, Dr. Robert Lilley, Mr. Daryl McCall, and Ms. Fujiko Oguri. Mr. Nickum took all of the photographs that appear in this report.

Figure 9. AGC/Memory/Interface Board.

- - -

Figure 10. AGC/Memory/Interface Board Components.

OF POOR QUALITY

# ORIGINAL PAGE IS OF POOR QUALITY

~**~.....**₹a' []

Figure 11. Edge Connector Pin Assignments.

-13-

## ORIGINAL PAGE IS OF POOR QUALITY

124

### VI. REFERENCES

- Yost, Stephen R., "Commutated Automatic Gain Control System", OU NASA TM-81, Avionics Engineering Center, Department of Electrical Engineering, Ohio University, Athens, Ohio, 45701, November 1981.

- Lilley, Dr. R.W. and Daryl McCall, "A LORAN-C Prototype Navigation Receiver for General Aviation", OU NASA TM-80, Avionics Engineering Center, Department of Electrical Engineering, Ohio University, Athens, Ohio, 45701, August 1981.