# NASA CR-172,159

# NASA Contractor Report 172159

NASA-CR-172159 19840002697

# Feasibility Study For A Generalized Gate Logic Software Simulator

John G. McGough Flight Systems Division Bendix Corporation

Contract NAS1-15946 July 1983

# LIBRARY GOPY

1.0710 (983

LANGLEY RESEARCH CENTER LIBRARY, NASA HAM2JOH, VIRGINIA

NF02035

NALIONAL Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23665

# TABLE OF CONTENTS

a.

2

. ن

.

| 1.0 | 1.1        | ARY AND CONCLUSIONS<br>Summary<br>Conclusions                                   | 5<br>5<br>7      |  |  |  |

|-----|------------|---------------------------------------------------------------------------------|------------------|--|--|--|

| 2.0 | 2.1<br>2.2 | ODUCTION<br>Objectives of BGLOSS<br>BGLOSS Requirements<br>Objectives of GGLOSS | 8<br>8<br>9<br>9 |  |  |  |

| 3.0 |            | LATION TECHNIQUES                                                               |                  |  |  |  |

| 2.0 |            | The Prototype Network                                                           | 10<br>10         |  |  |  |

|     | 3.2        | Simulation Techniques                                                           | 15               |  |  |  |

|     | 5.2        | 3.2.1 Unit-Delay Simulation                                                     | 15               |  |  |  |

|     |            | 3.2.2 Event-Driven Simulation                                                   | 17               |  |  |  |

|     |            | 3.2.3 Zero-Delay Simulation                                                     | 17               |  |  |  |

|     |            | 3.2.4 Summary of Simulation Techniques                                          | 18               |  |  |  |

|     |            | 3.2.5 Application To GGLOSS                                                     | 19               |  |  |  |

|     | 3.3        | Other Key Design Issues                                                         | 20               |  |  |  |

|     |            | 3.3.1 2-Valued Versus Multi-Valued Logic                                        | 20               |  |  |  |

|     |            | 3.3.2 Network Initialization                                                    | 22               |  |  |  |

|     |            | 3.3.3 Gate Operations And Alternate Network                                     | 22               |  |  |  |

|     |            | Representations                                                                 |                  |  |  |  |

|     |            | 3.3.4 Parallel Versus Serial Mode Simulation                                    | 24               |  |  |  |

|     |            | 3.3.5 Fault Modelling                                                           | 26               |  |  |  |

|     |            | 3.3.5.1 Proposed Fault Model                                                    | 27               |  |  |  |

|     |            | 3.3.5.2 Validity of The Proposed Fault Model                                    | 28               |  |  |  |

|     |            | 3.3.5.3 Implementation of The Proposed Fault<br>Model                           | 30               |  |  |  |

|     |            | 3.3.5.4 Fault Collapsing                                                        | 32               |  |  |  |

|     | <b>.</b>   | 3.3.6 Extension to Multiprocessor Systems                                       | 32               |  |  |  |

|     | 3.4        | Simulation Timing                                                               | 32               |  |  |  |

|     |            | 3.4.1 Simulation Speed                                                          | 33               |  |  |  |

| •   |            | 3.4.2 Simulation Efficiency                                                     | 34               |  |  |  |

| 4.0 |            | SS CHARACTERISTICS AND APPROACH                                                 | 37               |  |  |  |

|     |            | Salient Characteristics                                                         | 37               |  |  |  |

|     | -          | Rationale                                                                       | 37               |  |  |  |

|     | 4.3        | Simulation Techniques                                                           | 38               |  |  |  |

|     |            | 4.3.1 Functional-Level Networks<br>4.3.2 Gate-Equivalent Circuits               | 38               |  |  |  |

|     |            | 4.3.3 The Prototype BDX-930 Network Model                                       | 38               |  |  |  |

|     |            | 4.3.4 Fault Models                                                              | 39               |  |  |  |

|     |            | 4.3.5 Method of Identifying Detected Faults                                     | 39<br>40         |  |  |  |

|     | 4.4        | Preprocessor/Postprocessor Characteristics                                      | 41               |  |  |  |

|     |            | 4.4.1 Statistical Methods                                                       | 41               |  |  |  |

|     | 4.5        | Simulation Timing                                                               | 41               |  |  |  |

|     |            | Problem Areas 42                                                                |                  |  |  |  |

|     | 4.7        | BGLOSS in Retrospect                                                            | 42               |  |  |  |

|     |            |                                                                                 |                  |  |  |  |

## TABLE OF CONTENTS (CONT'D)

| 5.0                                | GGLOSS |        |                                    | 43 |

|------------------------------------|--------|--------|------------------------------------|----|

|                                    | 5.1    | Introd | uction                             | 43 |

|                                    |        | 5.1.1  | Summary Review of BGLOSS           | 43 |

|                                    |        | 5.1.2  | BGLOSS's Deficiencies              | 43 |

|                                    |        | 5.1.3  | Conclusions                        | 43 |

|                                    | 5.2    | Overvi | ew of GGLOSS                       | 43 |

|                                    |        | 5.2.1  | General Characteristics            | 45 |

|                                    |        | 5.2.2  | Specific Characteristics           | 45 |

|                                    |        |        | GGLOSS Modes of Operation          | 45 |

|                                    | 5.3    | -      | ed Tasks                           | 46 |

|                                    |        |        | User Tasks                         | 46 |

|                                    |        | -      | GGLOSS Tasks                       | 47 |

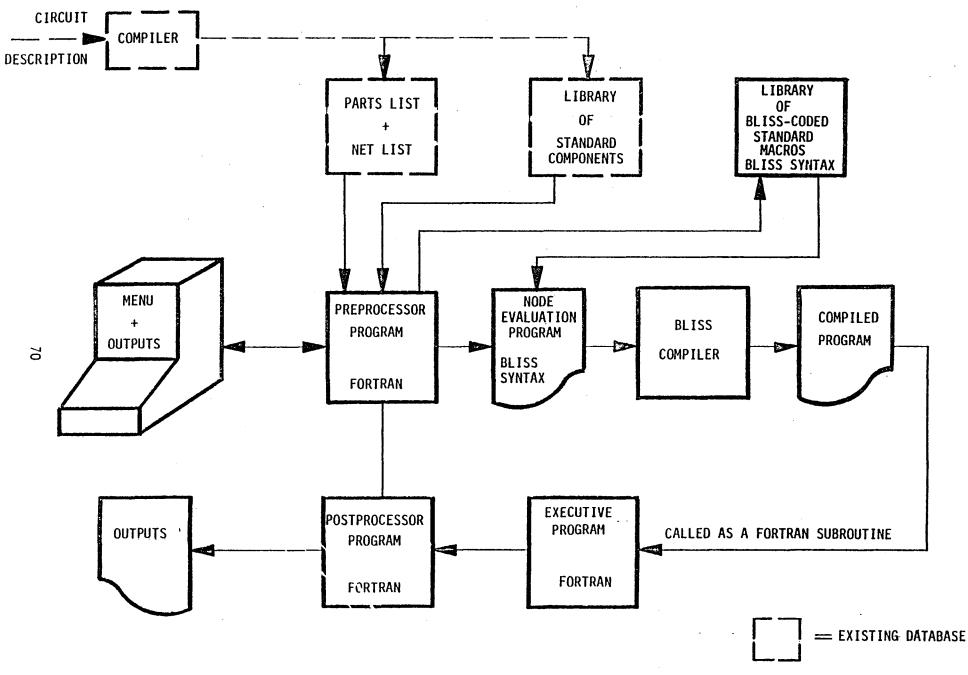

|                                    | 5.4    |        | ure of GGLOSS                      | 47 |

|                                    |        |        | Preprocessor Tasks                 | 47 |

|                                    |        |        | Postprocessor Tasks                | 47 |

|                                    |        |        | Executive Tasks                    | 48 |

|                                    |        |        | Library of Bliss-coded Macros      | 48 |

|                                    |        |        | Overview of The Simulation Process | 48 |

|                                    |        | I/O Op |                                    | 49 |

|                                    | 5.6    | Estima | ited Tasks                         | 49 |

| 6.0                                | REFE   | RENCES |                                    | 51 |

| APPE                               | NDIX   | A PRO  | PPERTIES OF LOOP-FREE NETWORKS     | 71 |

| APPENDIX B SPECIAL DIGITAL DEVICES |        |        |                                    | 74 |

| APPE                               | NDIX   | с ан   | HYPOTHETICAL SIMULATION            | 98 |

\$

ţ,

# LIST OF ILLUSTRATIONS

| FIGURE      | TITLE                                                            | PAGE       |

|-------------|------------------------------------------------------------------|------------|

| 1           | Realization of a Simple Clocked Node                             | 52         |

| 2           | Realization of a Compound Clocked Node                           | 53         |

| 3           | R-S Flip Flop                                                    | 54         |

| 4           | Realization of a Sequential Network                              | 55         |

| 5           | Prototype Network Models For Unit-Delay and                      | 56         |

|             | Zero-Delay Simulations                                           |            |

| 6           | Node Evaluations in U And Z Simulations                          | 57         |

| 7           | Common Gates                                                     | 58         |

| 8           | Equivalence of an n-Input "OR" Gate And n-1<br>Binary "OR" Gates | 59         |

| 9           | Parallel/Serial Mode Simulations                                 | 60         |

| 10          | Typical Parallel/Serial Interfaces                               | 61         |

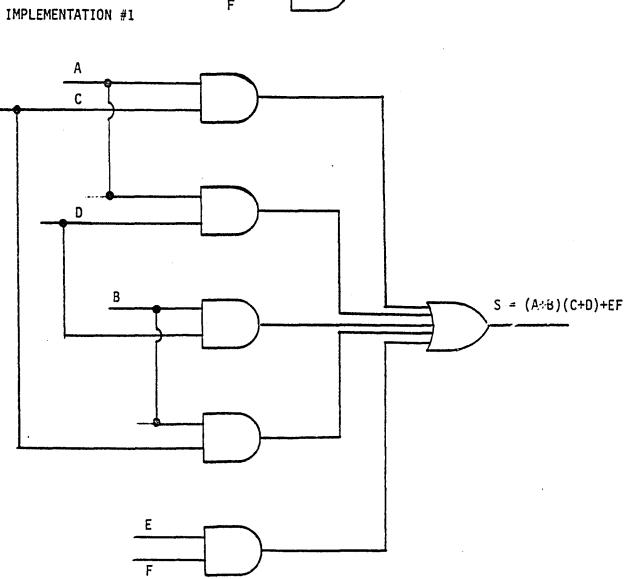

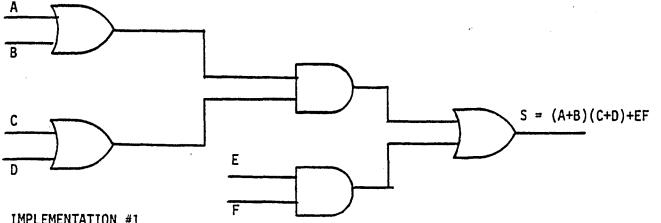

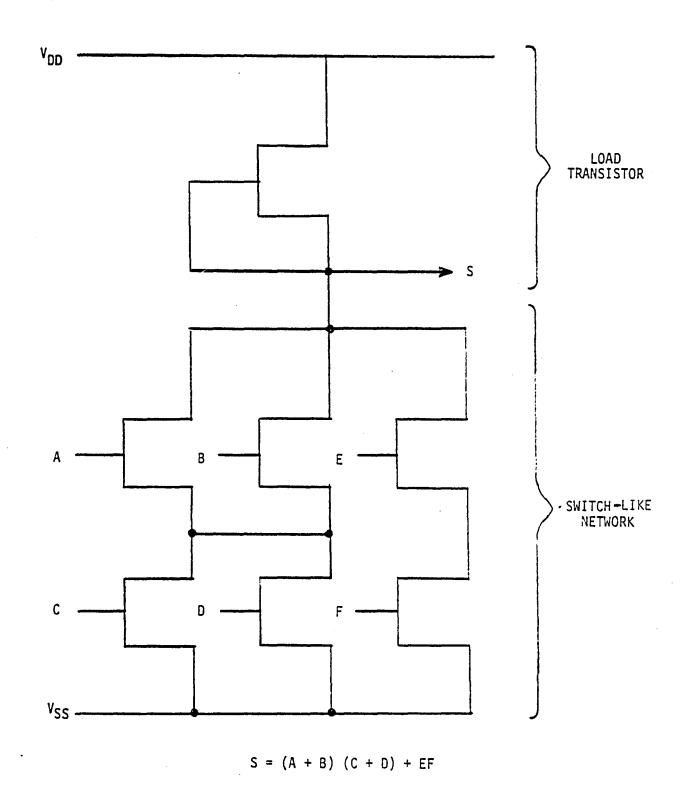

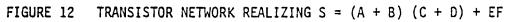

| 11          | Gate-Equivalent Imlementations of                                | 62         |

|             | S=(A+B)(C+D)+EF                                                  |            |

| 12          | Transistor Network Realization of<br>S=(A+B)(C+D)+EF             | 63         |

| 13          | Fault Correspondences in Gate-Equivalent                         | 64         |

|             | Circuits                                                         | -          |

| 14          | Procedure For Simulating Faults in a Functional -                | 65         |

|             | Level Device                                                     |            |

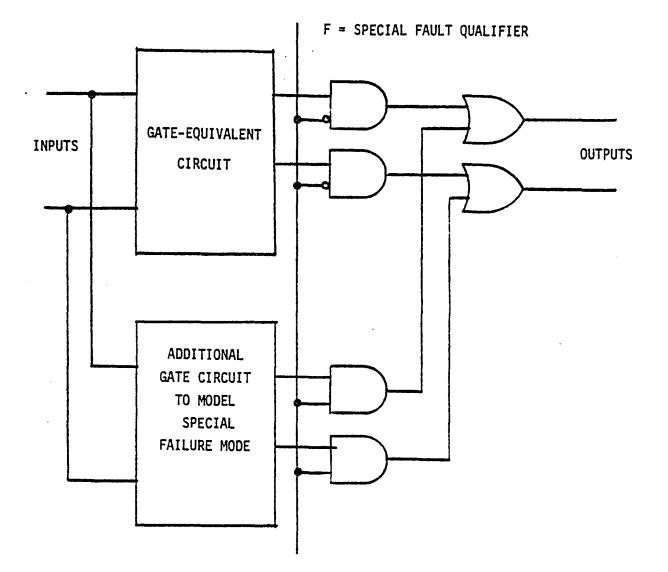

| 15          | A Method of Parallel Simulation Of Special                       | 6 <b>6</b> |

|             | Failure Modes                                                    |            |

| 16          | Standard Fault Model of a Gate                                   | 67         |

| 17          | Combinational Networks of Different Structure                    | 68         |

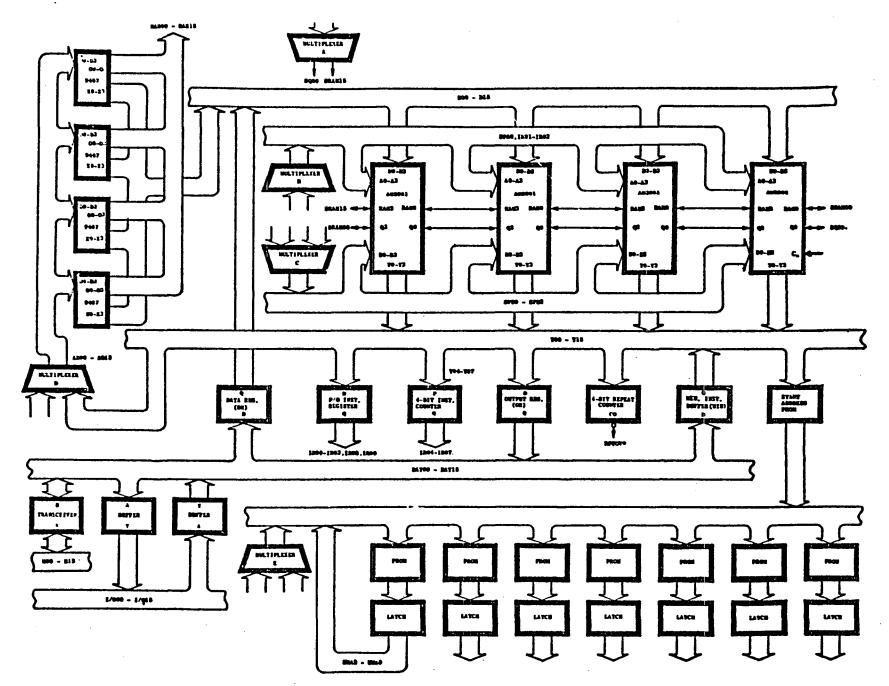

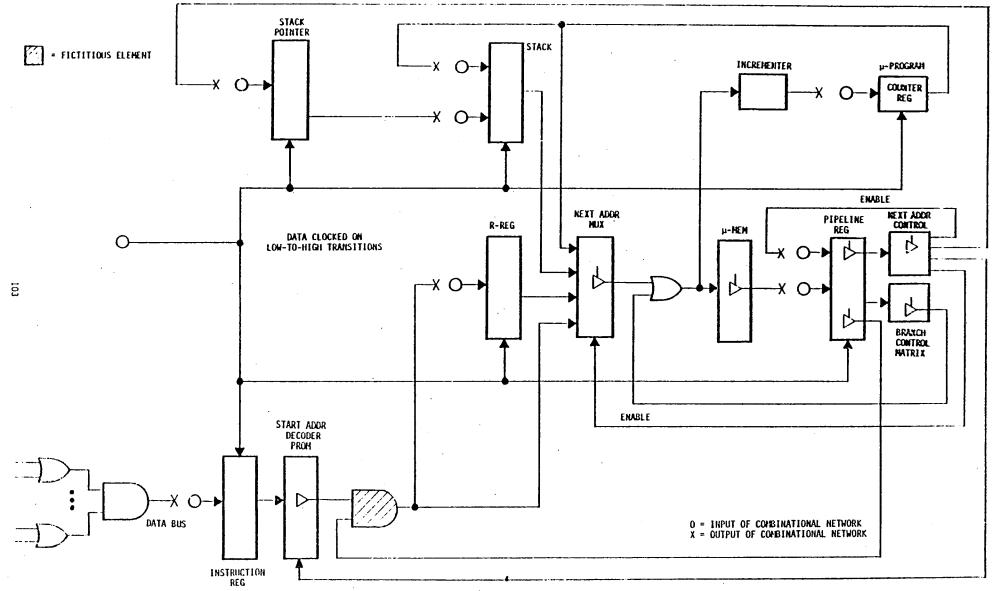

| 18          | BDX-930 Processor                                                | 69         |

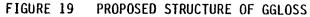

| 19          | Proposed Structure of GGLOSS                                     | 70         |

| A-1         | Example of Rank-Ordering                                         | 73         |

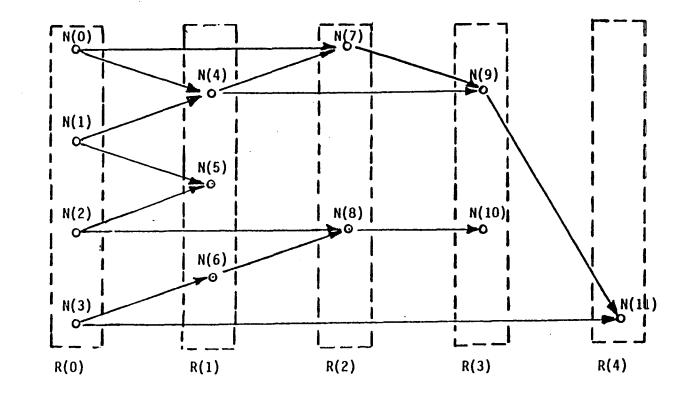

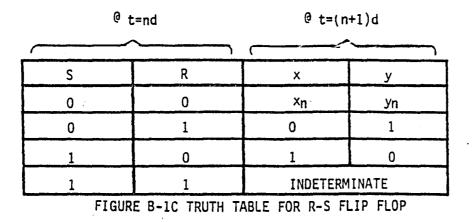

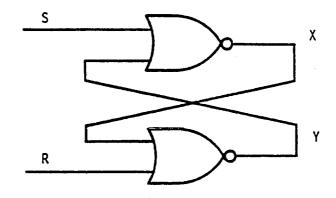

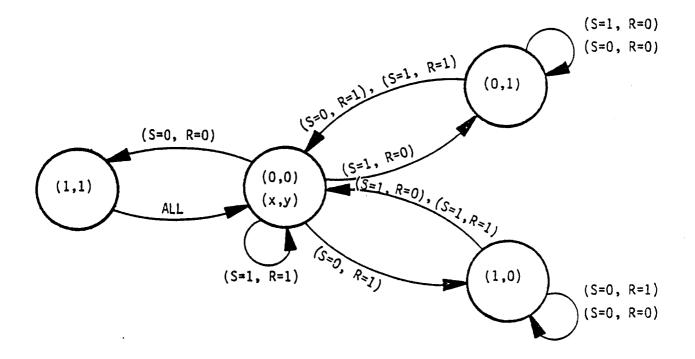

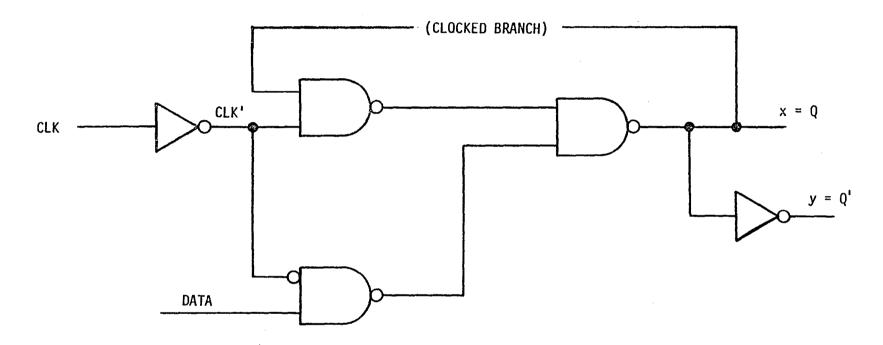

| B-1         | R-S Flip Flop, Nand Gate Representation                          | 82         |

| B-2         | R-S Flip Flop, Nor Gate Representation                           | 83         |

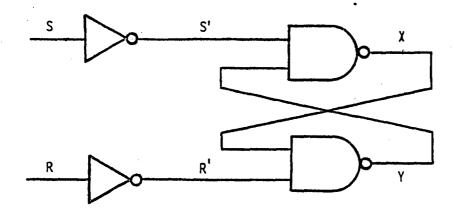

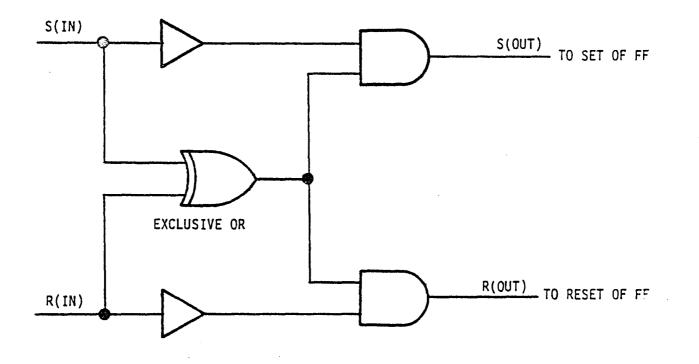

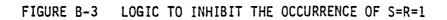

| B-3         | Logic to Inhibit The Occurrence of S=R=1                         | 84         |

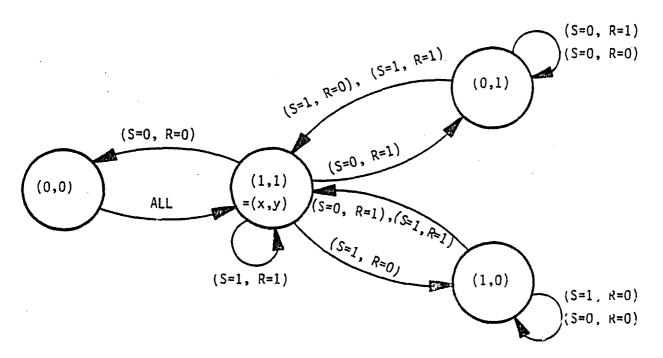

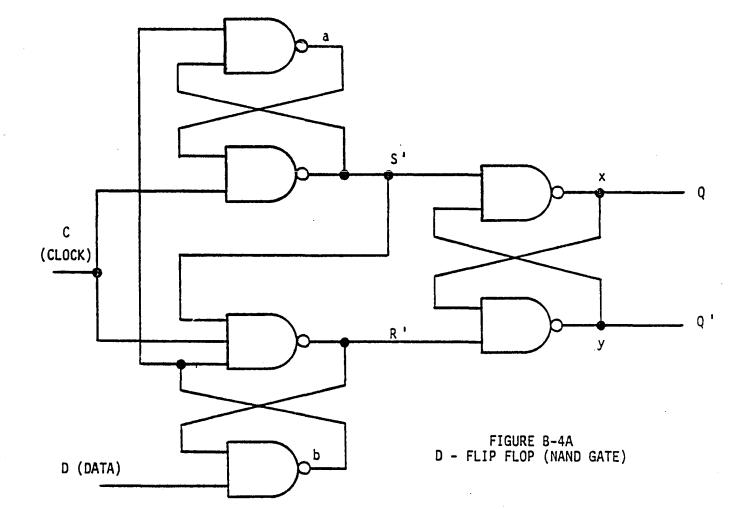

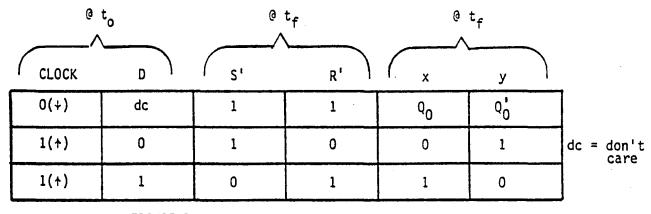

| B-4<br>B-5  | D-Flip Flop<br>State Diagram of D-Flip Flop                      | 85<br>86   |

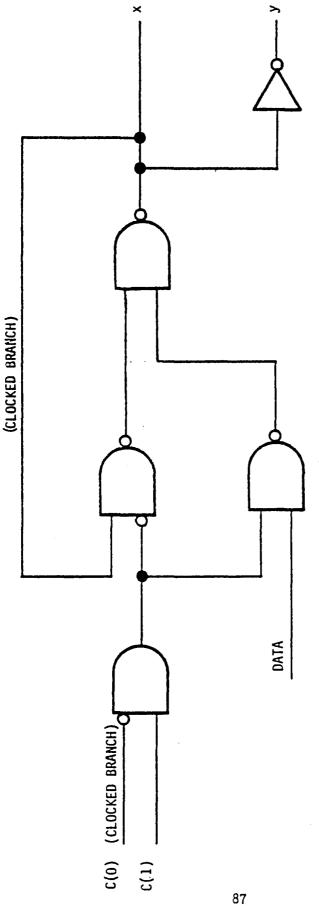

| B-6         | State Diagram of D-Flip Flop<br>Simplified Model of D-Flip Flop  | 87         |

| 0-0         | (Requiring Clock Transition Through Zero)                        | 07         |

| B-7         | Simplified Model of D-Flip Flop                                  | 88         |

| <b>D</b> -, | (Clock Transition Through Zero Not Required)                     | 00         |

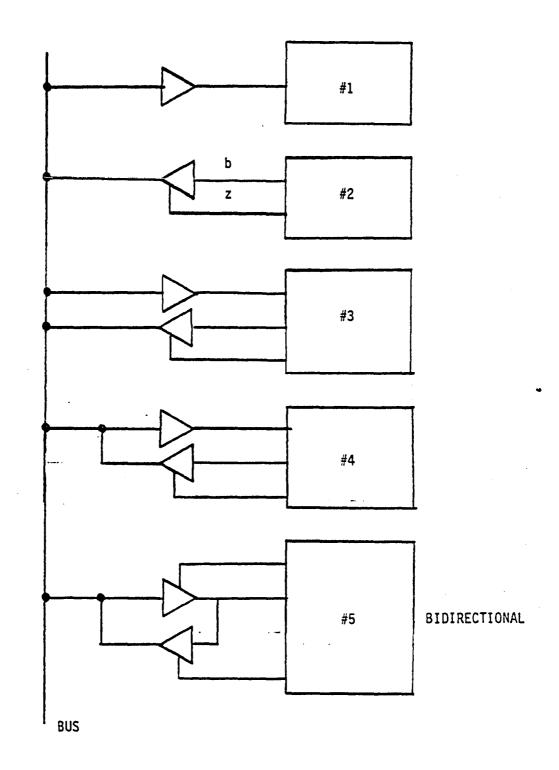

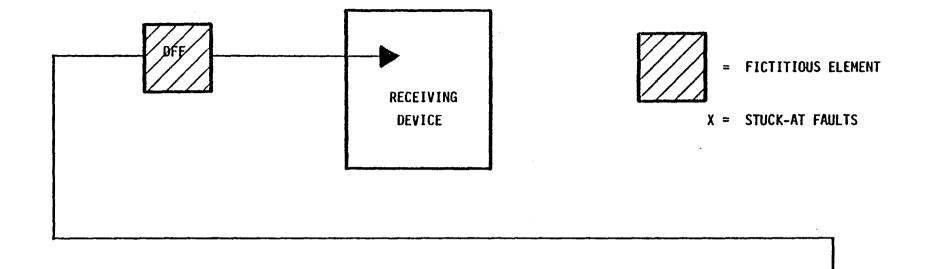

| B-8         | Typical Tristate Transmitter/Receiver                            | 89         |

| - •         | Arrangements                                                     |            |

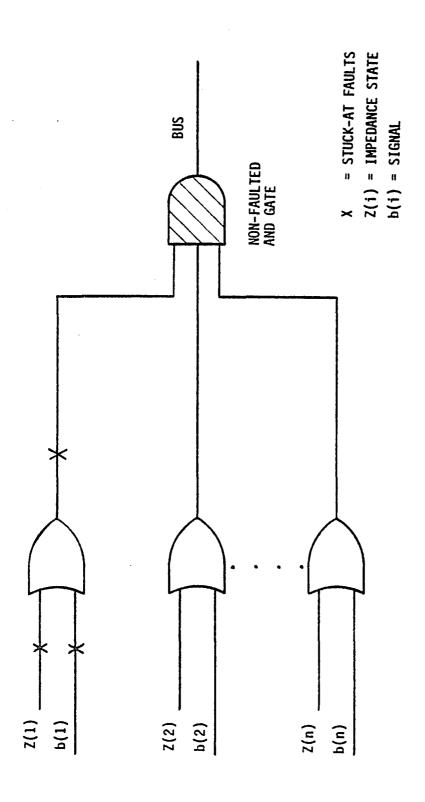

| B-9         | Gate-Equivalent Circuit, Tristate Bus of BGLOSS                  | 90         |

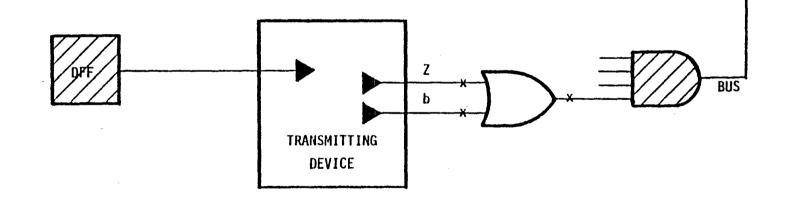

| B-10        | Typical BGLOSS Model of a Transmitter/Receiver                   | 91         |

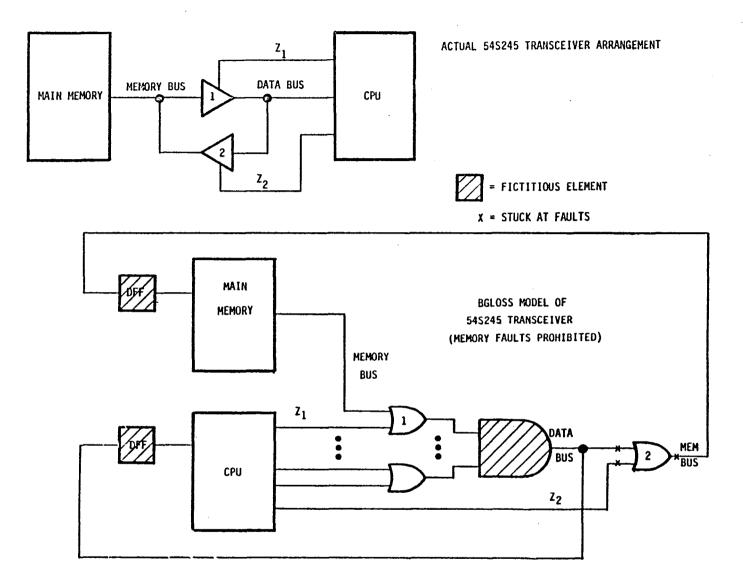

| B-11        | Model of Bidirectional Transceiver Used in BGLOSS                | 92         |

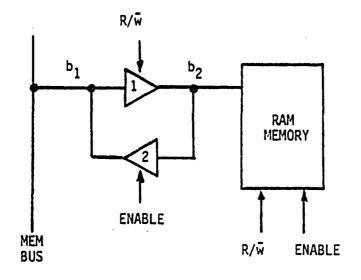

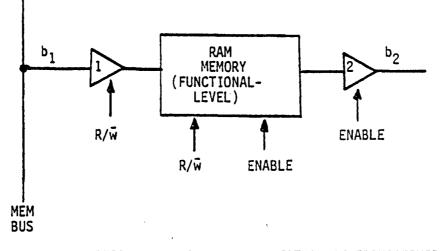

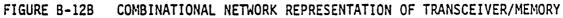

| B-12        | Memory to Memory Bus Transceiver Models                          | 93         |

| B-13        | Prototype Network Model of Memory to Memory Bus                  | 94         |

| _           | Transceiver                                                      |            |

| B-14        | Gate-Level To Register-Level Conversion Algorithm                | 95         |

PAGE

2

4

# LIST OF ILLUSTRATIONS (CONT'D)

| FIGURE | TITLE                                                           | PAGE |

|--------|-----------------------------------------------------------------|------|

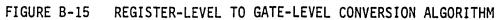

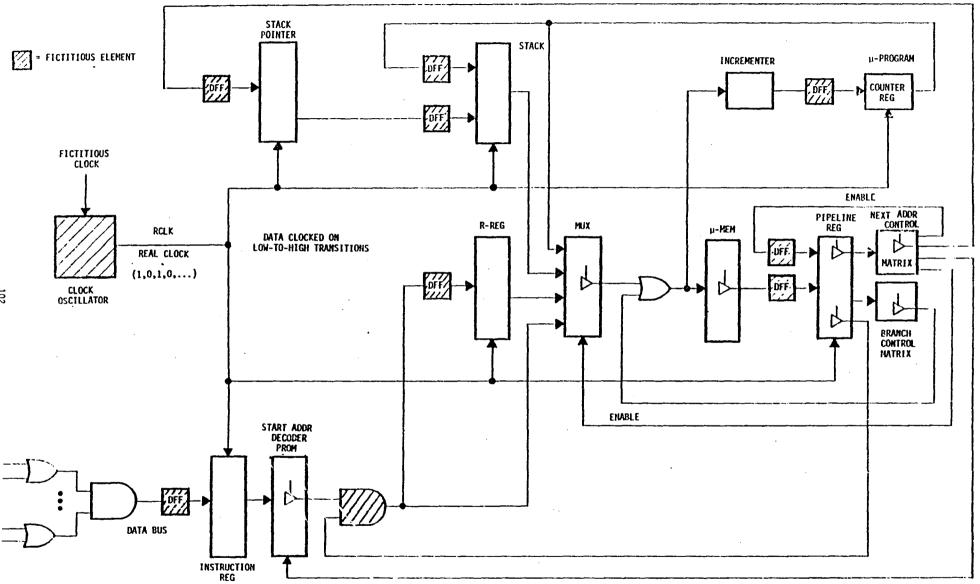

| B-15   | Register-Level To Gate-Level Conversion Algorithm               | 96   |

| C-1    | A Generalized Computer Architecture                             | 101  |

| C-2    | A Typical Computer Control Unit                                 | 102  |

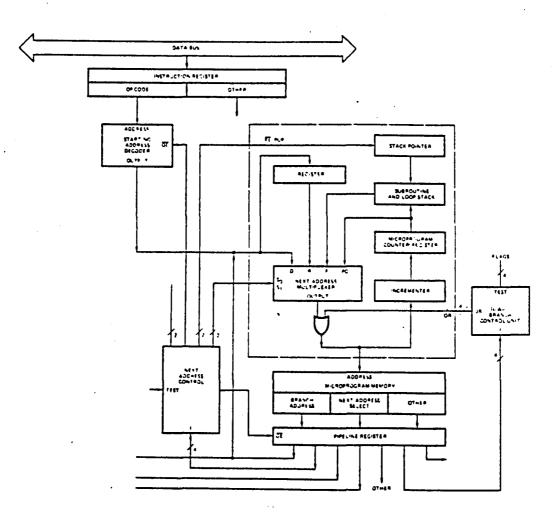

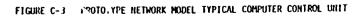

| C-3    | Prototype Network Model of a Typical Computer<br>Control Unit   | 103  |

| C-4    | Construction of Combinational Networks Within<br>Compound Nodes | 104  |

# LIST OF TABLES

| TABLES | TITLE                                | PAGE |

|--------|--------------------------------------|------|

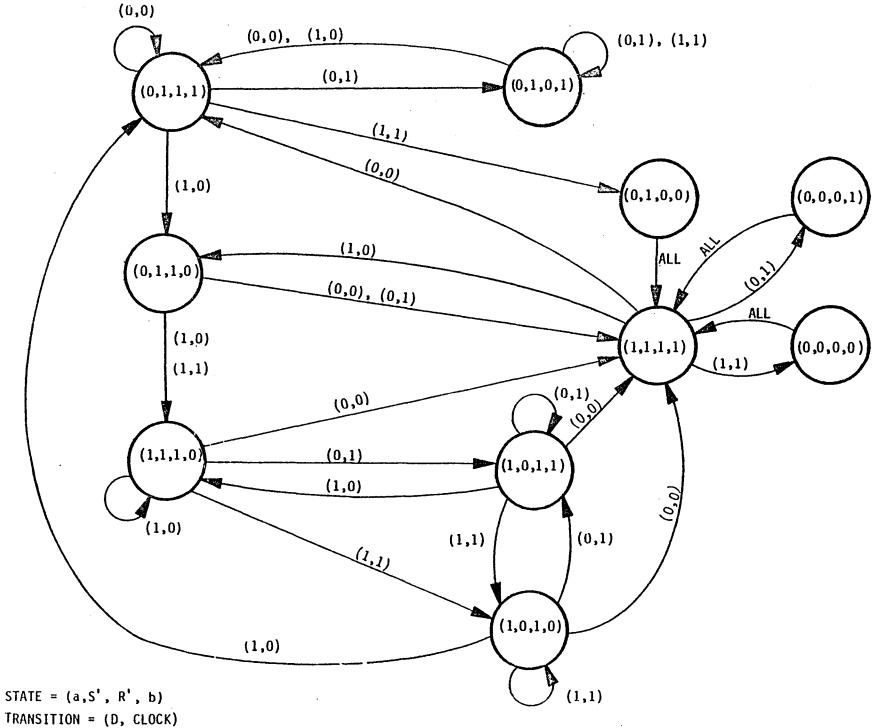

| B-1    | Excitation Table for the D-Flip Flop | 97   |

4

1

łe,

#### FEASIBILITY STUDY FOR A GENERALIZED GATE LOGIC SOFTWARE SIMULATOR

#### 1.0 SUMMARY AND CONCLUSIONS

#### 1.1 SUMMARY

Past experience has shown that commercial gate logic software simulators are several orders of magnitude too slow to perform practicable fault experiments which require simulation of digital hardware and software. In 1979 Bendix developed a very high speed gate-level simulation of the Bendix BDX-930 digital computer cpu (hereafter referred to as "BGLOSS"). The simulation was used to perform fault experiments to determine fault latency and to validate coverage of self-test programs. The success of BGLOSS in these programs resulted in a follow-on contract to determine the feasibility of developing a generalized version of BGLOSS (hereafter referred to as "GGLOSS") which would retain the high speed feature of BGLOSS and, in addition, be applicable to a wide variety of digital circuits and computers.

#### SECTION SUMMARY

Section 2.

The objectives and requirements of BGLOSS are reviewed and extended to GGLOSS.

Objectives of BGLOSS

- o To conduct failure modes and effects analyses

- o To assist in the design and validation of self-test

- o To obtain fault latency data such as was obtained in (refs.1,2)

Requirements of BGLOSS

- o Capable of simulating software

- o High speed

- o Capable of simulating multiple cpu's operating concurrently

Section 3.

A hypothetical network is defined which represents the prototype of all networks to be simulated. The network features a fictitious clock which, effectively, discretizes the time scale. The User constructs a prototype network by

- o defining the gate operations of the network

- o selecting a fictitious clock period

- o designating which branches are clocked

It is shown that this procedure produces a network of combinational circuits whose inputs are clocked. GGLOSS then evaluates each combinational circuit once in every clock cycle. It is shown that the clocked combinational circuits can be evaluated in any order but the gates within each combinational circuit must be evaluated in a definite order. GGLOSS computes the correct order.

Other key design issues are examined, including

- o 2-valued versus multi-valued logic

- o network initialization

- o gate operations and alternate network representations

- o parallel versus serial mode simulation

- o fault modelling

- o extension to multiprocessor systems

It is concluded that, to obtain high speed, GGLOSS should employ

- o 2-valued logic

- o parallel mode simulation

- o a low-level programming language for gate evaluations

This section concludes with a discussion of simulation speed and efficiency. It is shown that BGLOSS achieved an effective speed of 2.86x10\*\*6 gates/sec as compared with 1000 gates/sec for commercially available simulators.

Section 4.

The salient characteristics of BGLOSS are reviewed for possible incorporation into GGLOSS.

Characteristics of BGLOSS

- o Gate logic software simulator

- o Programmed in Bliss

- o Vax 11/780 host computer

- o parallel mode simulation, exclusively

- o fixed order of node evaluations

- o 2-valued logic, exclusively

- o Requires User-initialization of the network

- o Stuck-at faults, exclusively

- o Collapses faults

- o Capable of simulating software

- o 2.86x10##6 gates/sec

#### Section 5.

After a review of BGLOSS an overview of GGLOSS is given.

Proposed Characteristics of GGLOSS

- o gate logic software simulator

- o hosted on Vax 11/780

- o parallel mode simulation

- o serial mode simulation, optional

- o fixed order of node evaluations

- o 2-valued logic, exclusively

- o requires User-initialization of the network

- o stuck-at faults, exclusively

- o collapses faults

GGLOSS will be implemented in such a way as to make maximum use of an existing computer-aided circuit design facility. In particular, the method of defining gate-level circuits, peculiar to the existing database, will be retained. GGLOSS will be designed to interface with existing netlist and partslist formats. Simulation specifications and data not normally on file in the database, such as failure rates and input/output options, will be input via the menu.

Appendix A

A brief discussion of an algorithm for computing the proper order of gate evaluations is given.

Appendix B

Techniques of modelling basic digital devices, such as flip flops, tristate busses and Rom memory, are described.

Appendix C

To illustrate the methodology of GGLOSS a simulation of a hypothetical Computer Control Unit is described.

#### 1.2 Conclusions

- A high speed generalized gate logic software simulator is feasible. Speeds of the order of 2x10##6 gates/sec can be achieved.

- The fidelity of fault simulation is at least as good as that of an event-driven commercial simulator.

- The simulator can, albeit at reduced speed, simulate circuit timing.

- The simulator can be designed to utilize the existing resources of a computer-aided circuit design facility. It will not be necessary to reprogram existing gate-level circuits which are on file in the database.

- A reasonable degree of transportability can be obtained by programming the control and executive functions of GGLOSS in Fortran.

- For high speed it is necessary to use a low-level programming language for gate evaluations. The recommended language is Bliss.

#### 2.0 Introduction

In the Fall of 1979 Bendix was awarded a contract by NASA Langley Research Center to perform a fault simulation study to determine fault latency in a digital avionics processor(ref.1). Prior to the award, Bendix had developed a gate logic software simulator(BGLOSS) for its BDX-930 digital computer. The study provided the opportunity to not only establish fault latency statistics but to test BGLOSS in a variety of scenarios, not the least of which included the simulation of software programs and their interaction with hardware faults. Prior simulation experience lead to the conclusion that, next to reasonable accuracy, simulation speed was the most important characteristic of a simulator. Current, commercially available varieties are too slow for the types of fault experiments envisioned, being of the order of 1000 gates/sec of host computer cpu time. The impact of such speeds can readily be appreciated by considering an application in which it is desired to determine the detectability of a fault by a self-test program consisting, typically, of 1000 assembly language instructions. In the BDX-930, an assembly language instruction requires, on the average, four passes through the cpu, which consists of 5000 equivalent gates. Thus, a single fault. together with a complete execution of self-test, requires the simulation of 20 million gates. At 1000 gates/sec it would require 5.55 hours of cpu time! Subsequently, after thousands of simulated faults, the speed of BGLOSS was established at 2.86 million gates/sec on a Vax 11/780 host computer. As a consequence of the success of BGLOSS in the context of the Fault Latency Study, NASA Langley Research Center awarded Bendix a follow-on contract to determine the feasibility of developing a generalized gate logic software simulator (GGLOSS) based upon the BGLOSS model.

#### 2.1 Objectives of BGLOSS

BGLOSS was designed to simulate faults in large scale digital systems for the purpose of

- conducting failure modes and effects analyses

- designing and validating self-test programs

- \* obtaining fault latency statistics such as were obtained in (refs. 1, 2).

#### 2.2 BGLOSS Requirements

Based on the above objectives and intended applications a set of minimal design requirements was established for the planned simulator:

- A) The simulator must be capable of simulating software. This was a basic requirement since the objectives included the design and validation of self-test and the evaluation of fault latency when comparison-monitoring is the method of fault detection.

- B) The simulator must yield results in a timely manner. The simulation of self-test and flight control applications programs requires many passes through the cpu. Considering the quantity of faults that were to be simulated it was the judgement of the BGLOSS design team that the simulation time, on whatever computer EGLOSS was hosted on, should not exceed 25000 times real time. Assuming 5000 gates in the cpu, at a clock cycle of 250 nanoseconds, this would be equivalent to simulating 801,753 gates/second (In any event, EGLOSS, simulated on a Vax 11/780, did not exceed 7000 times real time, which was equivalent to 2.86x10\*\*6 gates/second).

- C) The simulator must be capable of simulating multiple cpu's, with different software programs, concurrently. Because many of the envisioned simulation experiments involved redundant channels of a flight control system it was desired that the simulation should be capable of modelling the concurrent operation of synchronous and asychronous channels, i.e., processors which, effectively, execute different software programs concurrently.

#### 2.3 Objectives of GGLOSS

The eventual success of BGLOSS was an indication that a more general simulator could be designed which met the same design requirements. In summary, these are:

- 1) The simulator must be capable of simulating software

- 2) The simulator must yield results in a timely manner

- 3) The simulator must be capable of simulating multiple cpu's, operating sycnchronously or asynchronously with each, possibly, executing different software programs.

In concluding this Introduction, it must be emphasized that GGLOSS is intended solely as a fault simulator. In particular, it is not intended as a circuit design tool. As a consequence, the reader will observe, subsequently, that it lacks certain features that are normally contained in state-of-the-art commercial simulators. These features and the rationale for their ommission will be described in later sections.

#### 3.0 Simulation Techniques

During the early phase of the study it became evident that a prerequisite for understanding the issues involved in the design of BGLOSS and the rationale for selecting many of its features was a broad knowledge of gate logic simulation techniques and the key issues involved in the selection of a simulator. Thus, this Report begins with a general survey of gate logic simulation techniques and related design issues. It is hoped that the subsequent treatment of BGLOSS is more comprehensible, as a result.

#### 3.1 The Prototype Network

Before discussing simulation techniques it is desirable to define a hypothetical network which will represent the prototype of all non-faulted networks to be simulated.

Terminology

A graph is a set, (V,E,f), where

- V = a set of elements called "vertices"

- E = a set of elements called "edges"

- f = a mapping from E to the set of unordered pairs of elements of

A graph is "directed" if the edges are given a direction. The vertices of a directed graph are called "nodes" and the edges, "branches". To be more precise, a directed graph is a set, (N,B,f), where

N = a set of elements called "nodes" B = a set of elements called "branches" f = a mapping from B to NxN.

The node pair

۷.

f(b)=(u,v), b in B, (u,v) in NxN

directs the branch from node u to node v. Nodes u and v are the "initial" and "terminal" nodes of b, respectively.

The number of branches which terminate at a node is called the "in-degree" of the node.

A "path" is a sequence of branches  $b(1),b(2),\ldots,b(n)$  such that there is a sequence of nodes  $N(0),N(1),\ldots,N(m)$  with the property that the initial and terminal nodes of b(k) are N(k-1), N(k), respectively. The path is said to "join" N(0) to N(m).

The "length" of a path is the number of branches in the path.

A path is a "loop" if it joins a path to itself.

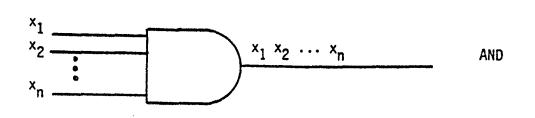

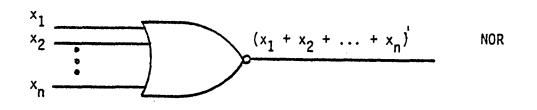

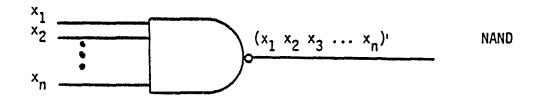

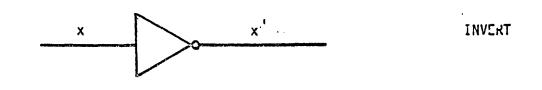

A "network" is a directed graph. In our applications the nodes will represent logic elements (e.g., AND, OR, INVERT ) and the branches, transmitted signals. Signals will assume the values of logic 0 and logic 1, exclusively. Since a branch is always associated with a node we associate a fictitious node with each external input. We call such nodes "E-nodes".

A "primitive" network is a network whose nodes consist of single logic elements, e.g., AND, OR, INVERT. A node of a primitive network is called a "simple" node. A node which is not simple is called a "compound" node.

A "combinational" network is a primitive network with no loops.

A node N is called a "predecessor" of node M if there exists a path joining N to M ( If the network has no loops then N and M cannot be predecessors of each other). An ordering, N(1), N(2),...,N(m), of the network nodes is called a "p-ordering" if N(k) is not the predecessor of any node N(j) where j < k. We note that, since some nodes are not related by the predecessor relation, there will generally exist many p-orderings of a network. In this connection we have

Theorem. In a network with no loops there exists at least one p-ordering of the nodes ( see Appendix A ).

#### Clocked Networks

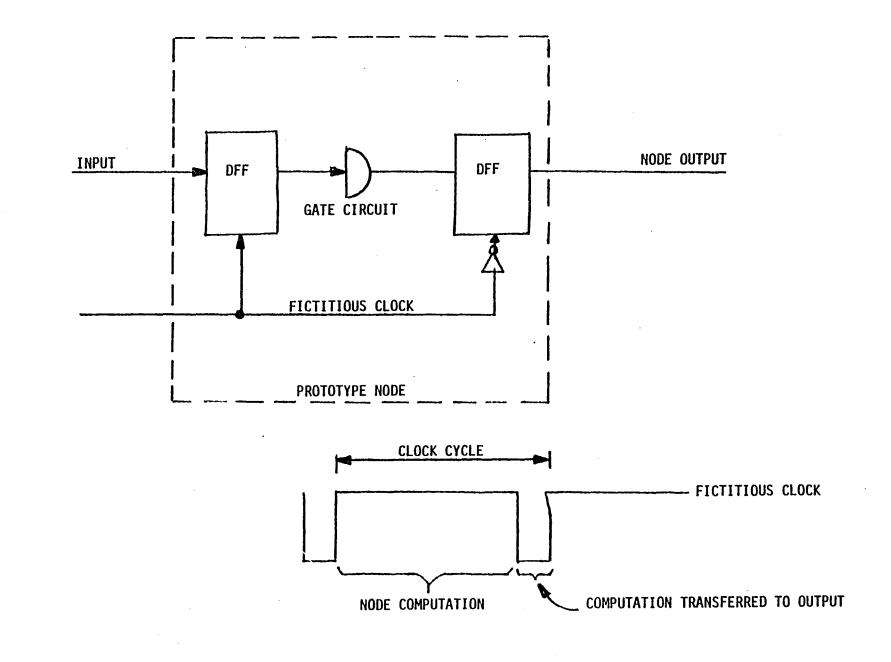

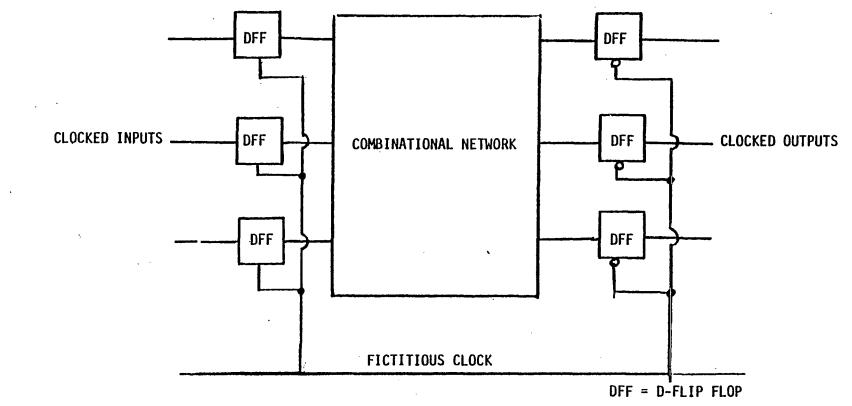

The prototype network will consist of compound nodes with each node representing a combinational network. In order to model the network for digital simulation it is necessary to introduce a discrete time scale. For this purpose we introduce a fictitious clock. The clock generates a periodic train of pulses which are transmitted to all nodes without delay. Upon receipt of a pulse a node activates its inputs and computes a set of outputs. The outputs, however, are only transmitted to other nodes at the descending edge of the pulse. As a consequence, node inputs and outputs do not change while a clock pulse is present. A realization of a simple clocked node, using D-flip flops, is shown in Figure 1. A similar realization of a compound clocked node is shown in Figure 2. In connection with a clocked node it will be assumed that

- 1) all gates have the same propagation delay. d;

- 2) each clock cycle is a multiple of d;

- 3) the propagation delay through the combinational network does not exceed the clock period.

As a consequence of this latter assumption, for all intents and purposes, the propagation delay of the combinational network may as well be zero.

Constructing The Prototype Network

We assume, for the present, that the network is a primitive network which may contain feedback loops. In our principal applications the network will represent a digital processor, in which case, the network is a true, clocked network. In constructing the prototype network we take the position that the User fully understands the dynamics of the constituent circuits in regard to normal and faulted performance. It is our view that a Simulator cannot be expected to model a universal circuit. It will be shown, subsequently, through numerous examples, that a network model can be constructed at many hierarchical levels, depending upon the objectives of the User. In addition, the failure modes of digital components can be exceedingly complex and, in any case, will generally be a function of the unique characteristics of the circuit. Only the knowledgeable User can supply this information.

Briefly, the procedure for constructing a prototype network is as follows:

- Select a fictitious clock cycle. The clock cycle represents the smallest distinguishable time increment. As a consequence, the clock frequency is the maximum frequency of any network input, internal state or output. For example, if it is desired to model a flip flop and observe potential high frequency oscillations then the clock cycle should be equal to the delay of a single gate. In a true, clocked network, on the other hand, the clock cycle should not be greater than the true clock cycle.

- 2) Identify clocked signals. The User must designate which signals, i.e., branches, are to be clocked. Effectively, this is the equivalent of inserting a fictitious D-flip flop in the branch. It is not necessary to identify the output flip flops, as shown in Figures 1 and 2. These are superfluous, if it is assumed that an output flip flop always terminates at a clocked node. In designating clocked branches the following rules must be followed:

- 1) All external inputs are clocked.

- 2) All loops must contain at least one clocked branch.

- 3) If A and B are the initial and final branches of a path and if A and B are clocked and no clocked branches intervene, then the propagation delay between A and B must not exceed the clock period.

If each clocked branch is cut the result is a set of disconnected, combinational subnetworks. The inputs to each subnetwork are clocked and the outputs are either inputs to a fictitious D-flip flop or network outputs that are terminated. As a result of this construction the network will consist of clocked, compound nodes of the type shown in Figure 2.

## Multiple Clocks

The preceding network employed a single clock. It is desirable, either to improve computational efficiency (see Example 6, following) or to model certain high speed networks, to employ multiple clocks or a single clock with multiple phases. In these arrangements the User associates a clock, clock frequency and phase with branches. The rules governing this designation are the same as before, i.e.,(1), (2) and (3).

As a result of this construction the network will consist of clocked, compound nodes except that the fictitious D-flip flops are triggered by different clocks. If we make the assumption, as we do, that all clock cycles are multiples of some primary clock cycle with period equal to unity, then the network is evaluated as follows:

- 1) Each clocked branch is cut, as before, to form combinational subnetworks. The inputs to each subnetwork are clocked, possibly by different clocks.

- 2) Each subnetwork is evaluated every time at least one input D-flip flop is triggered, irrespective of whether or not the input changed at this time. The triggering is activated by the associated fictitious clock. Thus, for example, if all inputs are clocked by clocks of period m and in phase with each other then the subnetwork will be evaluated once in every m primary clock cycles.

#### **Observations**

Despite its appearance as a clocked network the prototype can model a wide variety of networks, as the following examples demonstrate:

Example 1. Asynchronous Network With Unit Gate Delays

The network is modelled by a primitive clocked network in which the clock cycle is equal to the proagation delay of a single gate.

Example 2. Asynchronous Network With Variable Delays

All gate delays are assumed to be multiples of the delay, d, of a single gate. If the gate delay is viewed as a transport lag then a gate with delay md can be modelled by inserting m-1 fictitious gates, each with delay, d, in series. The network is otherwise modelled as in Example 1.

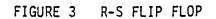

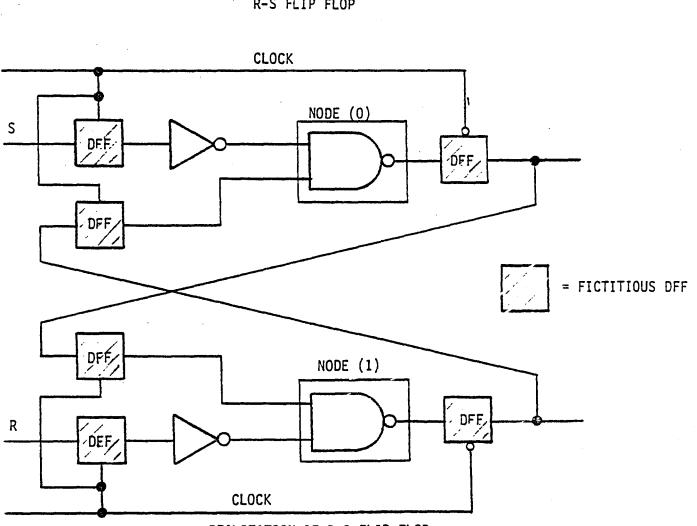

### Example 3. Realization of an R-S Flip Flop

The circuit is shown in Figure 3. The prototype network consists of two nodes, N(0), N(1), also shown in the figure.

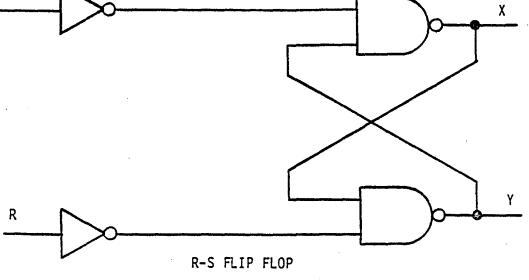

Example 4. A Sequential Network

It is shown in (ref.3) that every sequential network can be realized by a combinational network with unit delay feedback. A realization, using a prototype network, is shown in Figure 4.

Example 5. Simulating a True, Clocked Network

In a true, clocked network the network may experience a change of state following the descending edge of a clock pulse. One example of this is the D-flip flop, which requires that the clock return to zero before the next data input----otherwise no output change is possible. There are two approaches that can be taken when simulating a true, clocked network, depending on the desired accuracy and level of detail of the circuit model:

- 1) The nodes are evaluated only at the rising edge of the true clock. In this case the circuit models implicitly assume that a clock transition has occurred prior to each rising edge(see, for Example, the D-flip flop model of Figure B-7).

- 2) The nodes are evaluated at both the rising and descending edges of the true clock. The circuit models should be constructed to reflect differences in the responses, otherwise the extra net evaluation in each cycle is wasted.

In (1) the fictitious clock may coincide with the true clock. In (2) the fictitious clock should be twice the frequency of the true clock, e.g., the nodes should be evaluated once at the rising edge and once at the descending edge. Node outputs are transferred to the global memory after all nodes have been evaluated, irresective of whether the evaluation corresponds to a rising or descending edge.

Example 6. Use of multiple clocks to improve efficiency

Consider a true clocked network which is combinational except that it contains an R-S flip flop. While the inputs are clocked at, possibly, true clock cycles it may be desired to observe the outputs of the flip flop at higher frequencies. This could be achieved by evaluating the total network at a higher frequency but this would be computationally very inefficient since the combinational circuit inputs do not change between true clock cycles. A better approach would be to clock the inputs of the flip flop at the higher frequency. This creates an independent subnetwork which can be evaluated at high frequencies without requiring a corresponding evaluation of the total network.

#### 3.2 SIMULATION TECHNIQUES

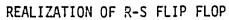

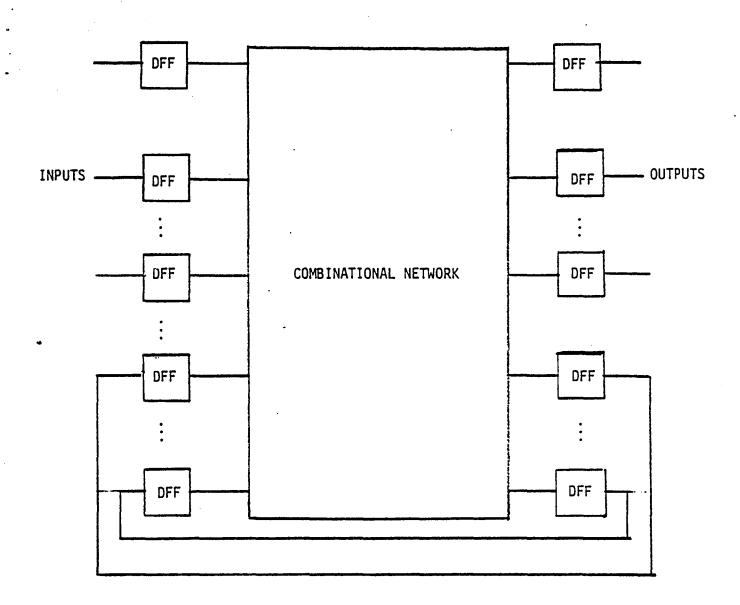

In this section it will be assumed that the network to be simulated is a primitive network. The results, however, can be extrapolated to networks with compound nodes in an obvious way. For illustrative purposes we consider the primitive network of Figure 5A.

There are essentially two techniques used to simulate the prototype network: the "Unit-Delay" and "Zero-Delay" simulations hereafter referred to as the "U" and "Z" simulations, respectively. These differ in the way that data is transmitted between simulated nodes. Specifically, each node accesses a dedicated, "local" memory into which is stored computed outputs. This memory can only be accessed by its associated node. When data is to be made available to other nodes it is transferred, by the simulation executive program, to a "global" memory whence it can be accessed by all nodes. Thus, at the start of each node evaluation the inputs are fetched from the global memory and the resultant, computed outputs are stored in local memory.

- 1) In the U simulation the contents of all local memories are transferred to the global memory after all nodes have been evaluated.

- 2) In the Z simulation, on the other hand, upon completion of each node evaluation the associated local memory is transferred immediately to the global set where it is used as input data in subsequent node evaluations.

#### 3.2.1 Unit-Delay Simulation

The procedure is as follows:

- 1) Define an arbitrary ordering of the nodes.

- 2) Initialize the network ( which is necessary because of the use of 2-valued logic ).

Then, at each clock pulse,

- 3) Evaluate every node in the selected order.

- 4) Transfer the computed output to the global set from whence it can be accessed by other nodes.

- 5) Repeat (3),(4) at the next clock cycle.

Observations

- The U simulation evaluates all nodes in every clock cycle. Thus, if the network consisted of n nodes( excluding E-nodes) it could require n\*\*2 node evaluations to propagate a signal through the network.

- 2) The U simulation gives correct node outputs for any ordering of node evaluations.

- 3) The U simulation is recommended when

- a) it is desired to simulate the effects of propagation delays, as in a feedback circuit; or

- b) it is desired to observe the response of each node in each clock cycle, as in a true, clocked network; or

- c) it is inconvenient to determine a p-ordering of the nodes.

The disadvantages of the U simulation technique are:

- 1) It requires a large number of node evaluations to propagate a signal through the network. This is wasteful if the propagation delays are small relative to the time between successive input events. For example, consider a combinational network of n nodes within a higher-level node, as in a true, clocked network. In a good design the propagation delay of the circuit is never larger than the clock cycle and, in most cases, very much smaller. Consequently, the circuit is always stable before the onset of the next clock pulse. In this scenario the U simulation would require n<sup>##2</sup> node evaluations to propagate each input event when actually n would suffice. Moreover, most of the n<sup>##2</sup> evaluations result in no change in the circuit elements.

- 2) Even when it is desired to observe the outputs of each node in each cycle, in many applications only a subset of nodes see changing inputs or outputs and, hence, require evaluation in each clock cycle. The U simulation, however, evaluates all nodes irrespective of whether or not the evaluation yields different results.

#### 3.2.2 Event-Driven Simulation

To overcome this last disadvantage a variation of the U simulation can be used: the Event-Driven simulation. In this approach only those nodes are evaluated whose inputs, outputs or internal state have changed from those of the preceding clock cycle. This is the most commonly employed simulation technique. Unfortunately, it requires considerable software overhead to maintain and this frequently offsets any advantage gained in reducing the number of node evaluations. In addition, it does not lend itself to parallel simulation (See Section 3.3.4).

#### 3.2.3 Zero-Delay Simulation

This technique is used to overcome the former disadvantage of the U simulation. The procedure is as follows:

- 1) External input branches are clocked.

- 2) A p-ordering of node evaluation is selected, e.g., N(0),N(1), N(2),...,N(n-1).

- 3) The network is initialized.

Then, at the kth clock pulse, k=0,1,2,..., DO

Evaluate N(k(modn)) and transfer its local outputs to the global set.

#### Observations

- 1) The order of node evaluations is critical: the ordering must be a p-ordering.

- 2) In a combinational network with n nodes(excluding E-nodes) the Z simulation can propagate a signal through the network after, at most, n node evaluations.

- 3) The Z simulation is recommended when

- a) the outputs of intermediate nodes are of no interest; or

- b) the propagation delays of the network are small relative to the time between successive input events; or

- c) the circuit is a subset of a node of a true, clocked network.

- 4) The Z simulation employs an invariant order of node evaluations. This is a benefit in parallel mode simulation.

The disadvantages of the Z simulation are:

- 1) It requires a p-ordering of the nodes.

- 2) It assumes that the propagation delays of the network are small relative to the time between successive input events, i.e., a node, once evaluated, does not see a change in input or internal state until all nodes have been evaluated.

- 3) It is not easily applicable to sequential circuits unless the time delay associated with feedback elements is large relative to the propagation delay of the straight-through elements.

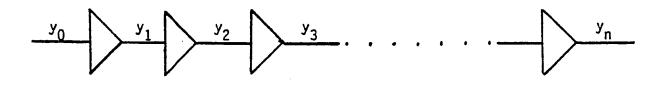

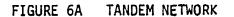

As a comparison of the U and Z simulation techniques consider the simulation of a simple network consisting of tandem gates, as shown in Figure 6A. The resultant node evaluations of the U and Z simulations are shown in Figures 6B,6C, respectively. From Figure 6B it can be seen that the U simulation evaluates n nodes (excluding E-nodes) in each clock cycle, for a total of  $n^{#*2}$  to propagate the input. The Z simulation, on the other hand, evaluates a single node in each clock cycle (see Figure 6C), requiring only n node evaluations to propagate the input to the output. In so doing, however, it assumes implicitly that the input did not change during these cycles then both techniques would require the same number of node evaluations. We note that an Event-Driven simulation of this network would have resulted in the same order and quantity of node evaluations as in the Z simulation.

#### 3.2.4 Summary of Simulation Techniques

The U simulation technique is conceptually simple, easy to program, independent of the order of node evaluations and yields the states and outputs of each node in each clock cycle. It is ideal for parallel mode simulation. The technique is recommended for simulating the compound nodes in a clocked network, as in a cpu. Its main disadvantage is the large number of node evaluations required to propagate a signal through the network.

The Z simulation technique is extremely efficient computationally when the time between successive inputs is large compared with the propagation delay of the network. It is ideal for parallel mode and combinational circuit simulations.

The Event-Driven simulation is potentially computationally more efficient than the U simulation. However, the overhead may offset this advantage. In any case, the Event-Driven simulation does not lend itself to parallel mode simulation.

F .

## 3.2.5 Application To GGLOSS

Both the U and Z simulation techniques will be used in GGLOSS. Briefly, the procedure will be as follows:

- 1) Starting with a given network the User creates a clocked, Prototype Network model consisting of compound nodes of the type shown in Figure 2.

- 2) The compound nodes are evaluated at each clock cycle, concurrently, using the U simulation technique.

- 3) The combinational networks within the compound nodes are p-ordered and evaluated using the Z simulation technique.

ER127

#### 3.3 OTHER KEY DESIGN ISSUES

Other key design issues associated with the selection of the simulator are:

- o 2-valued versus multi-valued logic

- Network initialization

- o Gate operations and alternate network representatons

- Parallel versus serial mode simulation

- o Fault modelling

- o Extension to multiprocessor systems

#### 3.3.1 2-Valued Versus Multi-Valued Logic

In the prototype network all signals assume binary values, 0 and 1. In many commercial simulators, however, signals are permitted to assume, in addition, pseudo values such as

- X: unknown state

- E: error state

- Z: high impedance state

The rationale for this multi-valued logic is

X: Under certain conditions circuits may assume unknown states and outputs. A signal value is denoted by an "X" until its value is known without ambiguity.

There are, principally, three scenarios in which the X designation has been found useful:

- 1) Power-On. At power-on the circuit elements may assume random bit patterns. These are designated by X's until they stabilize to unambiguous values.

- 2) Entry Into Self-Test. At the initiation of a self-test program the contents of accumulators and scratchpad memory may be unknown. The constituent bits are designated by X's until they are explicitly set by the test.

- 3) Failure Conditions. Certain failures may result in unknown or ambiguous conditions such as when all of the transmitters of a tristate bus are in the high impedance state. The resultant bus value is designated by X's.

- E: In some devices, such as flip flops, certain combinations of inputs and internal states are not permissible since they may result in ambiguous or unintended outputs. When such a condition arises the affected output is denoted by "E".

- Z: This state distinguishes between high/low impedance states of a transfer gate and the binary values of logic signals.

It will be shown, subsequently, that the use of multi-valued logic greatly reduces the real time efficiency of parallel mode operations. However, the issue, at present, is whether or not multi-valued logic is necessary.

The Unknown State, X

GGLOSS is not intended as a circuit design tool: it will always be assumed that the non-faulted circuit is well-designed. As a consequence, a standard input sequence will always result in a correct and unambiguous state, independently of the initial state. In a clock synchronized cpu, for example, the circuits stabilize to unambiguous values after power-on. To obtain the correct initial conditions it is only necessary to simulate the power-on conditions for a random selection of initial states of the network. In the fault scenarios it will always be assumed that the network has stabilized to an unambiguous state prior to the injection of a fault. It will be shown, subsequently, that fault models are, themselves, logic networks which merely replace the non-failed network. As a consequence, unless the fault model is, itself, ambiguous a stuck-at fault cannot introduce an ambiguous signal in the network. The absence of the X designation requires that memory elements be initialized to known values. If this is inconvenient or impracticable random bit patterns can be selected. Upon entry into self-test or any program, for that matter, it is good design procedure to initialize all pertinent memory elements. The X state alerts the User to non-initialized memory elements which may influence the outcome of the test. In summary, the unknown state provides the following benefits:

- 1) It relieves the User of the burden of determining initial network states and outputs.

- 2) It flags non-initialized states whose values may influence the outcome of a test procedure.

- 3) It can be used to flag unknown or ambiguous signal values due to failures. In the context of a fault simulator it does not appear to be unreasonable to expect the User to provide the initial conditions for the network especially since these conditions will have a unique effect on failure modes. Replacing the initial states and outputs by X's defeats the purpose of the simulation which is, after all, to identify failure modes and effects. The case of unknown or ambiguous effects of failures is a different matter. Here it may not be practicable to ascertain the precise effects of a failure. However, even in this context the use of the X state merely alerts the User to this uncertainty. In any case the detectability of the fault cannot be determined until the uncertainty is removed.

The Error State, E

It will always be assumed that the prototype network is defined at the level of detail necessary to unambiguously model the network's response to all combinations of inputs and internal states. Admittedly, this imposes a heavy burden on the user, requiring a detailed knowledge of the fault modes of all devices in the circuit including those represented at the functional-level. The use of "E" values alerts the user to an error condition without detailing the resultant response. However, since the purpose of GGLOSS is fault simulation and the determination of detection coverage the use of "E" values gives very little information regarding the subsequent detection of this condition and, consequently, should be eliminated from the simulation.

The High Impedance State, Z

It will be demonstrated in Appendix B that a special state to denote high impedance is unnecessary. In general, high/low impedance devices can be modelled by gates with the high/low impedance states replaced by binary values of 0 and 1.

#### 3.3.2 Network Initialization

In a well-designed network means are provided to stabilize the internal states, usually at power-on. By simulating this condition the proper network initialization can always be obtained and stored for future reference. Proper network initialization can always be obtained by simulating a sample program of sufficient length to arrive at an unambiguous network state.

#### 3.3.3 Gate Operations And Alternate Network Representations.

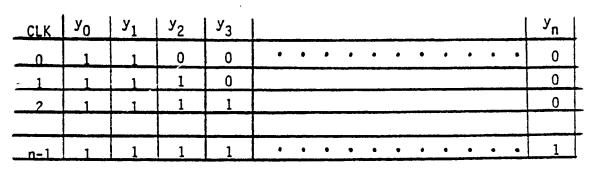

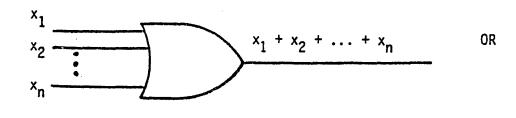

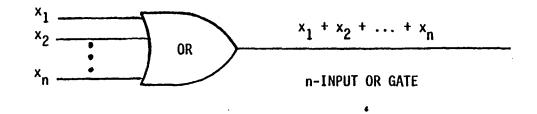

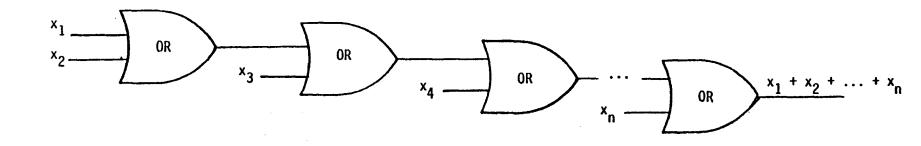

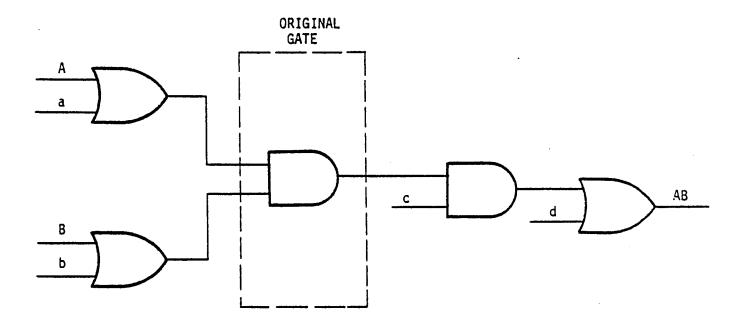

In Section 1 the prototype network was defined in terms of AND, OR and INVERT gates. In this section we will consider alternate gate representations. Figure 7 identifies the most common gates used to either simulate or implement a digital network. It is well-known ( see (ref. 3), for example) that a sequential network can be realized by a combinational network with loops. As a consequence, the sufficiency of a gate set depends upon its ability to represent arbitrary combinational net-In the prototype network the gates are assumed to be n-input works. This, however, is merely a convenience since each n-input gate gates. could have been defined, recursively, in terms of binary gates of the same type by making use of the associative properties of the AND and OR operations. Thus, for example, an n-input OR gate could have been represented by n-1, binary OR gates, as shown in Figure 8. As a consequence, we may say that the gate operations of the prototype, combinational network constitute a two-element( i.e., 0 and 1) Boolean Algebra with binary operations of multiplication and addition and the unary operation of complementation. The devices which perform these operations are called "AND" gates, "OR" gates and "INVERT" gates, respectively.

Definition 1. A Boolean function of n variables is a mapping of n-tuples of binary variables into the set  $\{0,1\}$ .

Every Boolean function can be realized by a combinational network consisting of AND, OR and INVERT gates, exclusively. However, this is not the only set of gates that can realize a Boolean function.

Definition 2. A set of gates (i.e., gate-types) is "complete" iff. every Boolean function can be realized by a combinational network constructed from gates of the set.

It can be shown (ref.4) that the following sets are complete:

S1) ( AND, OR, INVERT ) S2) ( AND, INVERT ) S3) ( OR, IMVERT ) S4) ( NAND ) S5) ( NOR )

Since S1 is a complete set the prototype network of Section 1 is complete in the sense that it can realize any Boolean function and, consequently, any sequential network. On the other hand, since { NOR } is also a complete set, a complete prototype network could be realized by employing NOR gates, exclusively.

Example. A prototype network is realized by binary gates of the set { AND, OR, INVERT }. It is desired to realize the network using binary NOR gates. The network can be transformed as follows: Let the symbol, "/", represent the NOR operation. Then

replace x' by x/x

replace x+y by (x/y)/(x/y)

replace xy by (x/x)/(y/y)

In summary, we may say that any prototype network can be realized by any one or a combination of the gate sets, S1 through S5. The only requirement is that the selected gate-set must be complete.

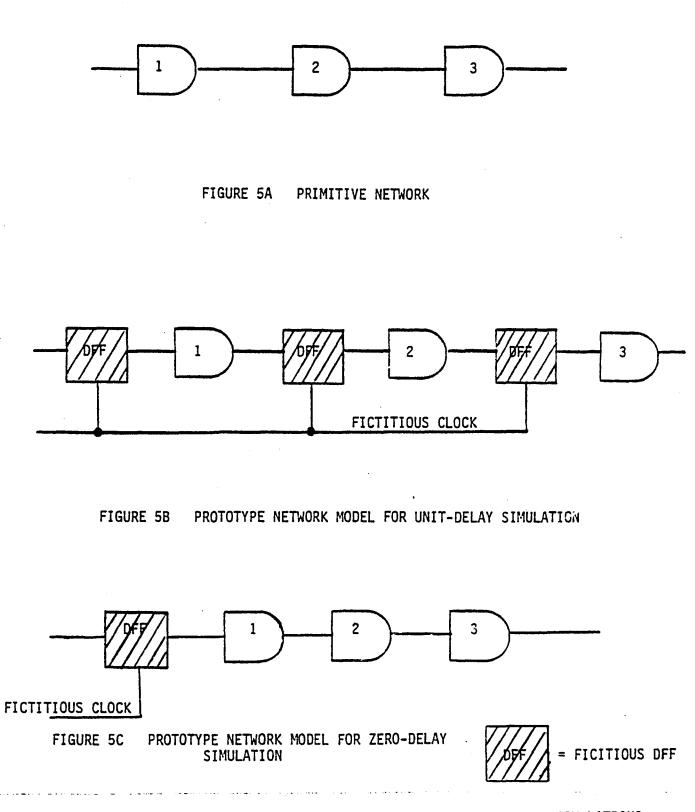

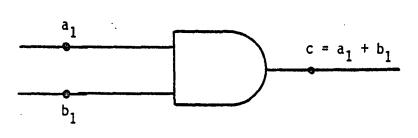

## 3.3.4 Parallel Versus Serial Mode Simulation.

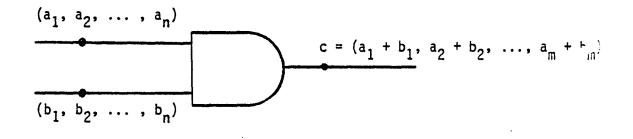

In order to achieve good simulation speed and efficiency careful attention must be given to the efficiency of the logical constructs of the programming language. Typically, the host computer will contain, at the assembly language level, logical constructs of the form, AB, A+B, and A', where A and B are whole words. Because they constitute the basic logical operations of the computer these constructs are among the most efficient in the instruction repertoire. Moreover, and equally important from the standpoint of simulation, these instructions perform the same logical operation on corresponding bits of the operands. Thus, if A and B are the words

A = (a(1),a(2),...,a(m))B = (b(1),b(2),...,b(m))

I

where a(k),b(k) = kth bit valuesand m = number of bits in a word

then the construct . A+B, yields the result

$C = (c(1), c(2), \dots, c(m))$

where c(k) = a(k) + b(k), k=1,2,...,m.

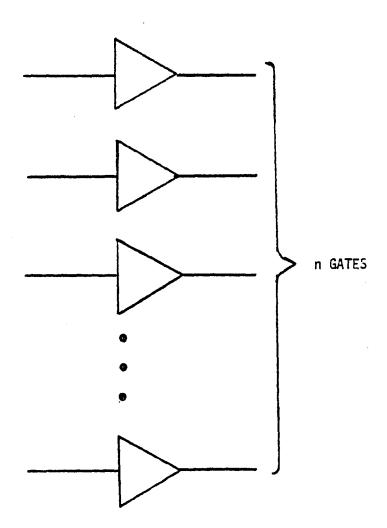

Effectively, m gate evaluations are performed, in parallel, at the cost of a single instruction. By exploiting this property the speed and efficiency of the Simulator can be increased by a factor of m, approximately. Specifically, the simulation is that of m, identical networks which differ from each other in that they have different fault sets or they are responding to different software programs. Each gate node is represented by a full, m-bit word of the host computer, with the kth bit value representing the kth network. A single pass through the network yields the responses of the m networks in their respective scenarios. This method of simulation is called "parallel mode simulation".

Hereafter, logical constructs which are

- 1) highly efficient in real time and

- 2) perform the same operation on corresponding bits of the operands will be referred to as "primitive logical constructs".

High-Level Programming Language. Typically, high-level languages such as Fortran and Pascal avoid the use of primitive constructs. In these languages the logical operands are Boolean variables(i.e.,TRUE or FALSE) so that, in effect, an entire word of the host computer is reserved for a single bit value. Thus, in these languages, to obtain the output of a binary gate for m sets of inputs requires the execution of m, logical constructs. This method of simulation (i.e.,one gate at a time) is called "serial mode simulation". Parallel and serial mode simulations are illustrated in Figure 9 for the construct, A+B. Macro Language. Macro languages provide the user with the basic capabilities of assembly language while reducing some of the tediousness of assembly language programming. They do this, typically, by allowing the user to call-up strings of commonly used assembly language instructions with a single instruction(i.e., a macro instruction). Macro languages almost always retain the primitive logical constructs of assembly language and, consequently, they are ideal for parallel mode simulation.

Example. It is desired to simulate a multiprocessor system with m, identical processors, each with a different software program. The cpu is simulated in the parallel mode using a simulation technique that employs an invariant order of node evaluations. Each processor is represented by a fixed bit position in the words of the host computer, e.g., processor #k is represented by bit position #k,  $k=1,2,\ldots,m$ . The fact that the resultant event sequences may be different for the m processors is immaterial since the order of node evaluations is invariant for any event sequence. As a consequence, a single pass through the cpu (in a clock cycle) gives the network states for the m processors.

Disadvantages of Parallel Mode Simulation

The use of parallel mode simulation imposes certain constraints on the Simulator: It limits the use of

- 1) high-level programming languages

- 2) multi-valued logic

- 3) Event-Driven simulation

- 4) and restricts modularization.

1) To fully capitalize on the benefits of parallel mode simulation the programming language must contain primitive constructs. This precludes the use of most high-level languages such as Fortran and Pascal. The use of low-level languages( e.g., assembly and macro languages) severely limits the transportability of the Simulator.

2) The use of multi-valued logic values, 0,1,X,E or Z, requires two or more bits to represent a signal value. Moreover, and more significantly, the logical operations involving these bits are not simple, logical functions of pairwise bits of the input words. This negates the advantage of primitive constructs, which operate on pairwise bits.

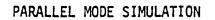

3) The efficient use of parallel mode simulation demands an invariant order of node evaluations. If m networks are simulated in parallel, each subject to different software, inputs or faults, it is to be expected that they will experience different event sequences. As a consequence, an event-directed simulator would eventually reach a condition that required, at the same instant of time, a different order of node evaluations for two or more of the m networks. 4) To achieve maximum simulation speed and efficiency the network should be modelled at the gate-level, since these operations corresond directly to primitive constructs of the programming language. Functional-level representations, such as registers, memory devices or IC chips, must be evaluated serially. Thus, when a gate interfaces with a functional-level device it is necessary to convert from parallel to serial mode formats or vice versa, depending upon the device. In addition, the functionallevel device must be evaluated repeatedly to obtain the appropriate parallel oututs. The process is illustrated in Figure 10. Referring to the figure, the inputs to the functional-level device are in parallel mode format. The functional-level device, however, must be evaluated serially, perhaps using a truth table or some other high-level evaluation procedure. The procedure can be summarized as follows:

- The parallel inputs are converted to serial formats, (a(k), b(k)), k=1,2,...,m.

- 2) The functional-level device is evaluated serially to obtain the outputs, c(k)=f((a(k),b(k)), k=1,2,...,m.

- 3) The outputs are converted to parallel format, i.e., to the whole word (c(1),c(2),...,c(m)).

Despite the relative inefficiency of this procedure it is unreasonable and impracticable to proscribe functional-level representations. Since some functional-level representation is unavoidable it is recommended that the number of such devices be kept to a minimum and efficient conversion algorithms be used.

#### 3.3.5 Fault Modelling

It has been demonstrated, thus far, that the prototype network has the flexibility and capability to model a wide variety of digital networks under non-faulted conditions. In this section techniques of mcdeling failure modes are considered. At the present time there is little or no data available regarding either the mode or frequency of failures of MSI Despite this deficiency of data, failure mode and or LSI devices. effects analyses are regularly performed for avionics and flight control systems. The conventional approach is to assume a set of failure modes for each device. These are usually restricted to faults at single pins although, occasionally, multiple faults may be considered. In most cases the failure rate of a device is assumed to be uniformly distributed over the pins or over the set of postulated failure modes. Except for special devices, faults are assumed to be static, being either S-a-O or S-a-1. The point to be made here is that failure modes and their frequency of occurrence are necessarily conjectural and the credibility of any fault model proposed here will suffer no less from this deficiency of data than the conventional "model".

#### 3.3.5.1 Proposed Fault Model

The proposed fault model is essentially the same as that used in BGLOSS. The following assumptions regarding failure modes of digital devices are assumed:

- 1) Every device can be represented, from the standpoint of performance and failure modes, by the manufacturer-supplied, gate-level equivalent circuit (a " gate-equivalent" circuit is a logic circuit that models the non-faulted performance of the device).

- 2) Every fault can be represented as either a S-a-0 or S-a-1 fault at a gate node.

- 3) The failure rate of the device is uniformly distributed over the gates of the equivalent circuit.

- 4) The failure rate of a gate is uniformly distributed over the nodes of the gate.

- 5) S-a-O and S-a-1 faults are equally likely.

- 6) Faults remain active indefinitely.

- 7) A fault at an output node propagates to all nodes and devices that are physically connected to the failed node.

- 8) A fault at an input node does not propagate back to the driving node.

This latter assumption, while unrealistic from the standpoint of modeling shorts, provides a wider variety of failure modes than would otherwise be possible if propagation were allowed.

The method of selecting faults is implicit in the above model. Each S-a-O and S-a-1 is assigned a probability of occurrence proportional to the prescribed failure rate. The resultant fault set is then randomly sampled with each fault weighted by its probability of occurrence. Thus, faults in devices with high failure rates will be selected more frequently than faults in devices with lower failure rates. The above procedure does not distinguish between gate-level and pin-level faults; the method automatically assigns failure rates to pins. If only pin-level faults are considered an alternative selection procedure is to assume that

"the failure rate of the device is uniformly distributed over the pins".

While this assumption violates the prescribed fault model it is consistent with the conventional method of assigning a probability of occurrence to pin faults. In summary, the essential assumptions of the proposed fault model are:

- All faults can be represented by single S-a-O and S-a-1 faults of gate nodes of the non-faulted, gate-equivalent circuit.

- The failure rate of the digital device is uniformly distributed over the gates of the gate-equivalent circuit.

Advantages of the Proposed Model.

- o Faults are single, stuck-at faults.

- The model provides a simple and systematic procedure for modeling a wide variety of faults including data-dependent faults.

- The model provides a systematic procedure for associating a probability of occurrence with each fault.

- o The model accommodates parallel mode simulation.

#### 3.3.5.2 Validity of the Proposed Fault Model

The proposed fault model is based on the fundamental assumption that the failure modes of the digital device can be modelled by stuck-at faults of a gate-equivalent circuit. The fact that it may be necessary to inject multiple faults, whereas the proposed model employs only single stuck-at faults, is a relatively minor difference since the proposed model could just as easily accommodate multiple faults, as well. The major effect of introducing multiple faults is the difficulty of assigning probabilities of occurrence to the multiple fault sets.

The point at issue here is

- Does a gate-equivalent circuit, which was selected to model nonfaulted performance, correctly model failure modes when subjected to stuck-at faults?

- o More specifically, can every failure mode be produced by a set of stuck-at faults in the gate-equivalent circuit? Conversely, does every set of stuck-at faults produce a realizable failure mode?

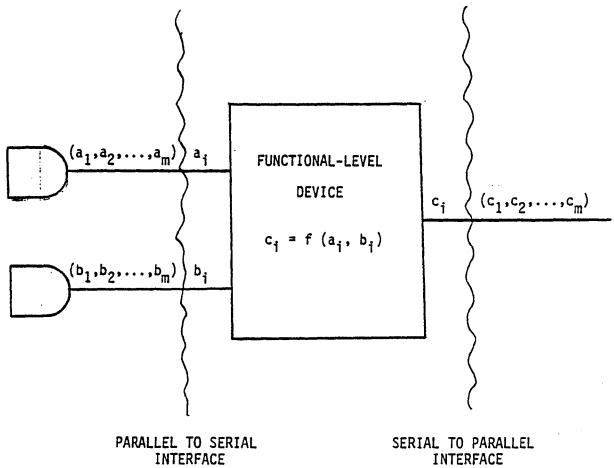

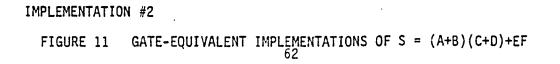

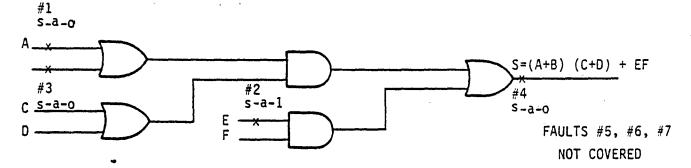

Example. Consider a circuit that implements the logic, S=(A+B)(C+D)+EF. Figure 11 illustrates two possible gate-level representations. In the non-faulted case both representations are equivalent. It is apparent, however, that the failure modes of stuck-at faults are quite different in the two representations.

From this example it may be concluded that a gate-equivalent circuit does not necessarily model the failure modes of the device. The question is, does any gate-equivalent circuit do so? In several recent publications (refs. 5,6) the assumption that failure modes can be modelled by stuck-at faults of a gate-equivalent circuit is challenged. The authors assert that

- 1) All failures cannot be modelled by stuck-at faults.

- 2) Stuck-at faults are satisfactory for modelling small-scale circuits but inadequate for large-scale circuits.

- 3) Faults should be opens and shorts, referenced to the physical layout of the circuit.

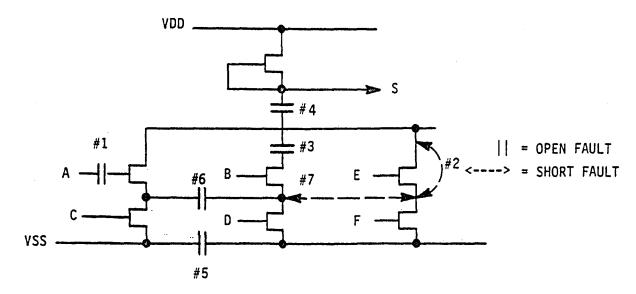

In support of this thesis the authors exhibit the gate circuit of Figure 12. The switch-like network consists of a load transistor and a set of command transistors which act like switches. By applying input patterns, e.g., A, B, C, D, E, F, a set of conduction paths are determined between the output node and the VSS power supply node. A conduction path is activated when all of its command transistors are on; a conduction path is blocked when at least one of its command transistors is blocked. When a conduction path between output node and the VSS node is activated the output is at the VSS potential(logic state 0); when all conduction paths are blocked the output is at the VDD potential(logic state 1). The network realizes the function S=(A+B)(C+D)+EF.

Two possible gate-level representations of the function were given previously in Figure 11. Figure 13 shows a set of open and short faults of the transistor network and the corresponding stuck-at faults in the gate circuits. Of the seven faults selected, gate circuit #1 can model four as stuck-ats; gate circuit #2 can model six, provided that multiple stuck-ats are allowed. Fault #7, which shorts two paths, cannot be modeled by either gate circuit. The reason is that this fault creates a new logic circuit which realizes the function

S=(A+B+E)(C+D+F).

From this example it becomes clear why the failure modes of small-scale devices can be modelled by gate-equivalent circuits with stuck-at faults: they consist of relatively few multiple conduction paths.

Based on the above observations we conclude that::

- 1) The proposed model is adequate to model failure modes of SSI devices.

- 2) The proposed model should accommodate multiple stuck-at faults.

- 3) The selection of an appropriate gate-equivalent circuit, which most closely models the failure modes of the device, should be based on a failure modes analysis of the transistor circuit. Based on this analysis the user must select a realistic set of open and short faults and their associated stuck-at faults. The User should be cognizant, however, that not every combination of stuck-at faults corresponds to a realizable failure mode.

The above procedure will result in a gate-equivalent circuit that will model normal performance and a subset of realizable failure modes. Each failure mode not modellable by the gateequivalent circuit will undoubtedly require a unique gate circuit to model. Thus,

1

4) The user must select a set of "representative" faults and determine, for each fault, a unique gate circuit to model the resultant failure mode.

In summary, the fault model will consist of

المتعادية المعادية

- 1) A gate-equivalent circuit which models normal performance and some failure modes.

- 2) A set of gate circuits which model the failure modes of representative faults not modellable by the gate-equivalent circuit.

#### 3.3.5.3 Implementing the Fault Model

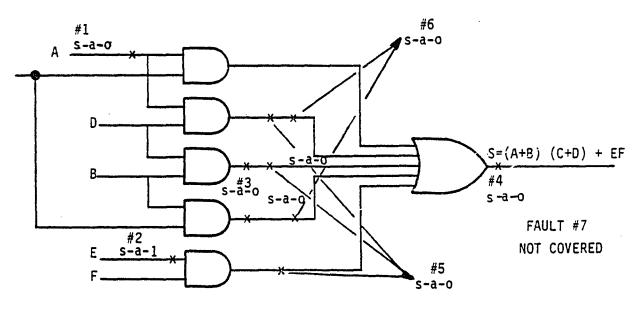

The Simulator must be capable of simulating faulted and non-faulted network performance in either the serial or parallel modes of simulation. When a device is represented at the functional-level it is necessarily simulated in the serial mode. Implementing fault modes associated with a functional-level device is a relatively straightforward procedure: The database contains a non-faulted device representation at the functional-level and a set of fault models (see Figure 14). When a fault is to be injected the Simulator Executive identifies 1) the fault and 2)the network, i.e., one of the m, parallel networks to be faulted. The Simulator then evaluates the appropriate network responses and, after all parallel inputs have been serviced, converts the outputs to the appropriate parallel format.

The procedure is more delicate when the device is represented at the gate-level. Here, the concern is speed and to achieve speed it is necessary to maintain parallel mode simulation at all times. The efficient use of parallel mode simulation requires:

R1) A single gate circuit which models both faulted and non-faulted performance.

R2) Every gate must be evaluated for each of the m, parallel networks and in an invariant order.

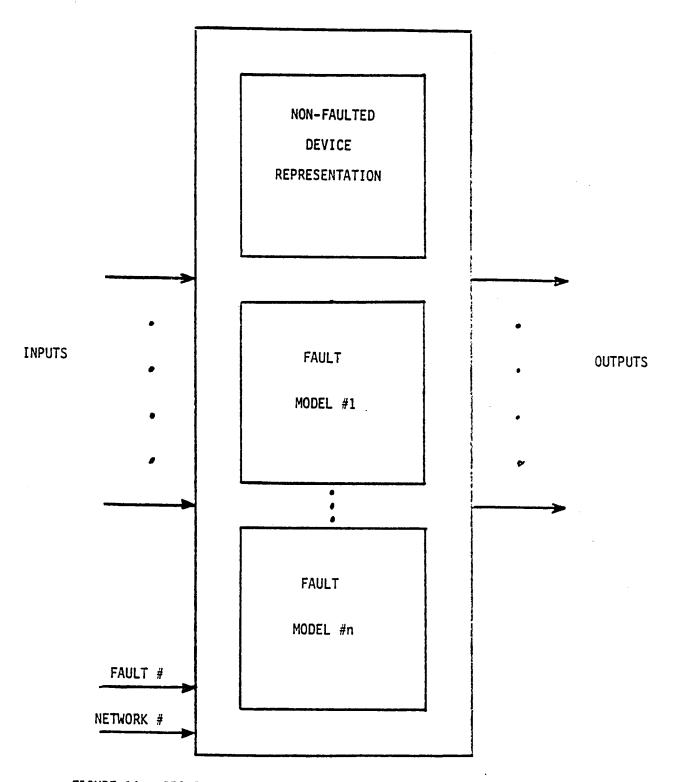

The major advantage of the proposed fault model in this context is that it employs a single gate circuit which models both faulted and nonfaulted performance. As we have seen, however, it may be necessary to employ several different circuits for this purpose. In any case it is necessary to comply with requirements R1 and R2 if efficient parallel mode simulation is to be achieved. Example. A gate-equivalent circuit is given which models normal performance and some failure modes. It is necessary to create an additional circuit to model a special failure mode. To comply with R1 and R2 the circuits are simulated as shown in Figure 15. During each clock cycle both circuits are evaluated. The special failure mode is activated by a discrete qualifier,F. In the parallel mode F is represented by an m-bit word in the host computer. When it is desired to activate this failure mode in, say network #k, the kth bit is set to a logic 1, all other bits remaining at logic 0. The logic 1 state causes the transfer of the outputs of gate circuit #1 to the outputs of the device. Naturally the extra gates introduced for this purpose are never faulted.

#### Modelling Failure Modes in The Gate-Equivalent Circuit

The method of parallel mode simulation depicted in Figure 15 can be relatively costly in simulation speed and efficiency since it requires the evaluation of the gates in both the gate-equivalent and special gate circuits during each pass. In this section more efficient simulations are described.

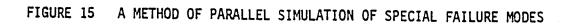

The gate-equivalent circuit is used to model non-faulted performance and some failure modes which are the result of stuck-at faults. To model stuck-at faults each gate is expanded in a manner illustrated in Figure 16, for an AND gate. Referring to the figure

a = 1 models a S-a-1 of A b = 1 models a S-a-1 of B c = 0 models a S-a-0 of A or B or AB d = 1 models a S-a-1 of AB

It is noted that stuck-at faults are modelled by selecting appropriate values of inputs, a,b,c, and d. Moreover,when a=b=d=0 and c=1 the circuit models non-faulted performance. Thus, in the parallel mode the circuit of Figure 16B can be used in all m networks, whether faulted or not. The circuit, however, requires 5 gate evaluations whereas the non-faulted gate required a single gate evaluation. If every gate where replaced by a similar circuit the simulation speed would decrease fivefold! To avoid this penalty it was found expedient, in BGLOSS, to partition the network and insert faults in one partition at a time.

#### Modelling Special Failure Modes

When it is neccessary to model special failure modes a special gate circuit must be included, as illustrated in Figure 15. However, the gate-equivalent circuit then consists of non-faulted gates, only. Thus, there is relatively little reduction in simulation speed. Naturally it is advisable to incorporate a single special gate circuit, at a time.

#### 3.3.5.4 FAULT COLLAPSING

Another technique used to increase simulation speed in BGLOSS was "fault collapsing". It was recognized that not all stuck-at faults were distinguishable at a gate output. For example, a S-a-O fault on an input node of an AND gate is indistinguishable from a S-a-O fault on the output node. As a consequence, if two indistinguishable faults of the same gate were selected, only one fault was simulated.

#### 3.3.6 Extension To Multiprocessor Systems

Parallel mode simulation is ideal for simulating multiprocessor systems although it may, under certain conditions, result in a decrease in simulation speed. As an illustration, consider a multiprocessor system such as SIFT (ref. 7), consisting of 8 processors. Each SIFT processor is assigned a set of computing tasks, some of which are redundantly executed, depending upon the criticality of the task. Non-critical tasks are normally assigned to a single processor. As a consequence, it may be assumed that, for the most part, the processors are executing different programs. Assuming that a 32-bit word of the host computer represents a single gate node, the bits are subdivided into 4 segments, of 8 bits. Each segment represents a different version of the multiprocessor system. A fault would then be injected into one of the 8 bits in each segment (If faults are limited to the same processor then it is only required to simulate the 7 memories of the non-faulted processors and 4 memories corresponding to the faulted processors). In this approach only 4 faults can be simulated in a single run as compared with 31 if a single processor system is simulated. This results in an 8-fold decrease, approximately, in simulation speed. An apparently attractive alternative approach would be to simulate 7, non-faulted processors and 25, faulted processors in a single run. The problem here is that the action taken by the multiprocessor system may be different for different faults. Effectively, the system operates like an event-criven simu-As a consequence, when a fault is injected it is necessary to lator. simulate the non-faulted processors for the duration of the run in order to determine the resultant action taken by the system. In summary, when the action taken by a multiprocessor system (e.g., dual, triplex, etc.) is dependent on the fault then it is necessary to simulate all of the non-faulted processors during a run.

#### 3.4 SIMULATION TIMING

An important figure of merit of a simulator is the cpu time required by the host computer to simulate a network. This is particularly important when it is desired to simulate a software program in a miniprocessor. In these applications a typical miniprocessor might consist of 5k or more equivalent gates and a single instruction could require 4 or more passes through the cpu. If the entire software program is executed for a single fault, as in self-test, then it is obvious that even a modest number of faults would require a very large number of gate evaluations.

#### 3.4.1 Simulation Speed

Definition 1.

Given a class of combinational networks, each with n gates. If the host computer requires T seconds of cpu time, on the average, to propagate a single input vector through a network then we define

"simulation speed" = n/T gates per second.

Example. In the parallel mode of operation, if

m = number of bits per word and T = cpu time for a single pass then simulation speed = nm/T gates /sec

Thus, parallel mode operations improve simulation speed by a factor of m.

#### Observations

1) The figure of merit is independent of the number of gates actually evaluated by the simulator.

Example. In a tandem combinational network of n gates a Z simulation will propagate a signal after n node evaluations whereas a U simulation would require n<sup>##</sup>2 node evaluations. If the host computer cpu time was 1 second for each then the simulation speed would be n gates/sec for each simulation.

- 2) Simulation speed is a function of the speed of the host computer. For our purposes all simulation speeds will be referenced to the Vax 11/780 computer(0.8 MIPS).

- 3) The figure of merit, when applied to either a U or Z simulation is independent of the structure of the network since each of these simulations evaluates a fixed number of gates, e. g., n\*\*2 and n, respectively. However, when applied to the Event-driven simulator the figure of merit is a strong function of network structure. Consider, for example, the two networks of Figure 17. Each contains n gates but the figure of merit applied to network #2 will tend to favor the Event-Driven simulation over the Z simulation since the former could propagate some inputs after only a single node evaluation. In general "simulation speed" will always favor the Event-Driven over the Z simulation.

4) It is desirable to obtain the relative simulation speeds of the U and Z simulations. While each method evaluates a fixed number of gates the problem is that some gates have more than two inputs. Thus, the desired relationship is a function of the

1) average number of inputs/gate;

2) cpu time required for each gate;

3) average number of gates in the network.

If the gate constructs correspond to 2-input gates and if

n = average number of gates in the network

i = average number of inputs/gate,

then

n(i-1) = average number of equivalent, 2-input gates and

anu

Z simulation speed = n(i-1)x(U simulation speed).

#### 3.4.2 Simulation Efficiency

ч. Г

Definition 2.

Let t = real time to propagate a signal through a network T = average cpu time required by the host computer to simulate a single pass through the network.

We define

"simulation efficiency" = t/T.

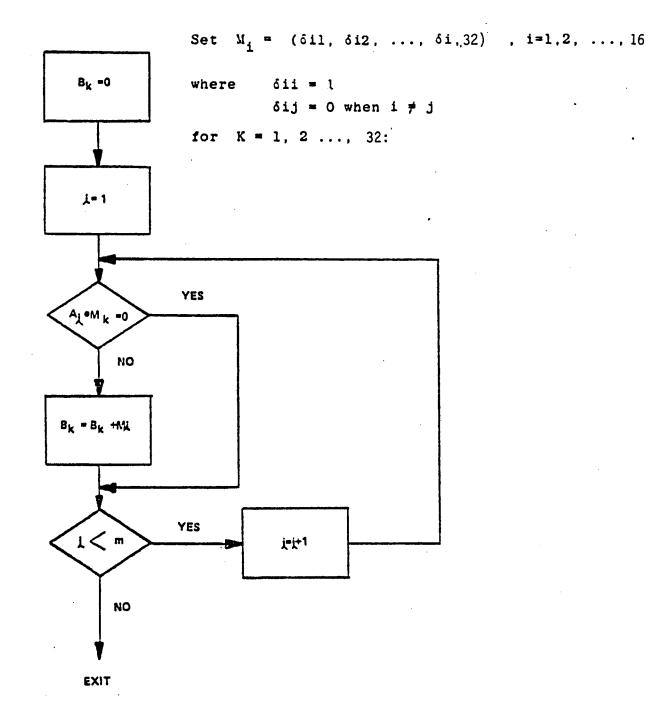

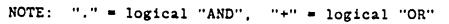

This figure of merit will be applied principally to a miniprocessor  $c_{\mu}u$  where t = true, clocked cycle.