https://ntrs.nasa.gov/search.jsp?R=19840018892 2020-03-20T21:59:07+00:00Z

# N84-26960

Progress Report RSC-4242-4-2

# DEVELOPMENT OF LAND BASED RADAR

# POLARIMETER PROCESSOR SYSTEM

by

C. W. Kronke

A. J. Blanchard

September 1983

#### Supported by

National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland 20771

TEXAS A&M UNIVERSITY REMOTE SENSING CENTER COLLEGE STATION, TEXAS

## DEVELOPMENT OF LAND BASED RADAR POLARIMETER PROCESSOR SYSTEM

by

C. Kronke

A. J. Blanchard

September 1983

Supported by

National Aeronautics and Space Administration Goddard Space Flight Center Greenbelt, Maryland 20771

Contract No. NAG 5-31

#### ABSTRACT

The processing subsystem of a land based radar polarimeter was designed and constructed. This subsystem is labeled the Remote Data Acquisition and Distribution System (RDADS). The radar polarimeter, an experimental remote sensor, incorporates the RDADS to control all operations of the sensor. The RDADS uses Original Equipment Manufacturers (OEM) industrial standard components including an 8-bit microprocessor based single board computer, analog input/output (I/0)boards, a dynamic Random Access Memory (RAM) board, and power supplies. A high-speed digital electronics board was specially designed and constructed to control range-gating for the radar. A complete system of software programs was developed to operate the RDADS. The software uses a powerful real-time, multi-tasking, executive package as an operating system. The hardware and software used in the RDADS is presented here in detail. Also, recommendations for future system improvements are made.

### TABLE OF CONTENTS

•

.

Page

| ABSTRACT                           |

|------------------------------------|

| TABLE OF CONTENTS                  |

| LIST OF TABLES                     |

| LIST OF FIGURES                    |

| PROJECT BACKGROUND                 |

| Remote Sensing                     |

| The Radar Polarimeter System       |

| STATEMENT OF WORK 8                |

| Radar Electronics                  |

| Microwave Transceivers             |

| IF Section and Multiplexer         |

| Other RDADS Interfaces             |

| HARDWARE                           |

| Design Approach                    |

| RDADS Computer                     |

| Central Processor                  |

| Serial I/O, Timers, and Interrupts |

| Parallel I/O                       |

| Analog I/O Interface               |

| Random Access Memory               |

| RDADS Chassis and Power Supply     |

| IF Controller                      |

.

•

## TABLE OF CONTENTS (Continued)

Page

| Processor I/O Interface               |

|---------------------------------------|

| Timing Network                        |

| Cycle Control                         |

| Programmable Transmit Pulse Generator |

| Fixed Delay Generator                 |

| Programmable Range Delay Generator    |

| Programmable Gate Pulse Generator     |

| I/O Expansion in the IFC              |

| SOFTWARE                              |

| Structured Programming                |

| Modular Programming                   |

| Limited Constructs                    |

| Development Support                   |

| Software Design                       |

| Problem Statement                     |

| Radar Control and Data Acquisition.   |

| RDADS Communication                   |

|                                       |

| Design Approach                       |

| ROU Commands                          |

| LOCAL Command                         |

| TXPOL and RXPOL Commands              |

| MODE Command                          |

| HEAD or BAND Command                  |

| RANGE and GATE Commands               |

## TABLE OF CONTENTS (Continued)

|                                                                                           | age |

|-------------------------------------------------------------------------------------------|-----|

| IFGAIN Command                                                                            | 74  |

| Radar Task                                                                                | 75  |

| Radar Task Operation                                                                      | 75  |

| Digital Automatic Gain Control Implementation                                             | 78  |

| Real-Time Multi-Tasking                                                                   | 81  |

| The RMX-80 Executive Package                                                              | 83  |

| RMX-80 Nucleus                                                                            | 86  |

| RMX-80 Terminal Handler                                                                   | 88  |

| RMX-80 Command Line Interpreter                                                           | 90  |

| Analog Input Handler                                                                      | 93  |

| Utility Packages and Libraries                                                            | 94  |

| RDADS Utilities Library                                                                   | 95  |

| System Utilities Library                                                                  | 97  |

| Remote Operations Command Tail Interpreter                                                | 99  |

| Remote Operations Data Formatting and Transmission                                        | 101 |

| Remote Operations Main Utility                                                            | 103 |

| PROJECT SUMMARY                                                                           | 105 |

| Future Consideration and Recommendations                                                  | 106 |

| REFERENCES                                                                                | 110 |

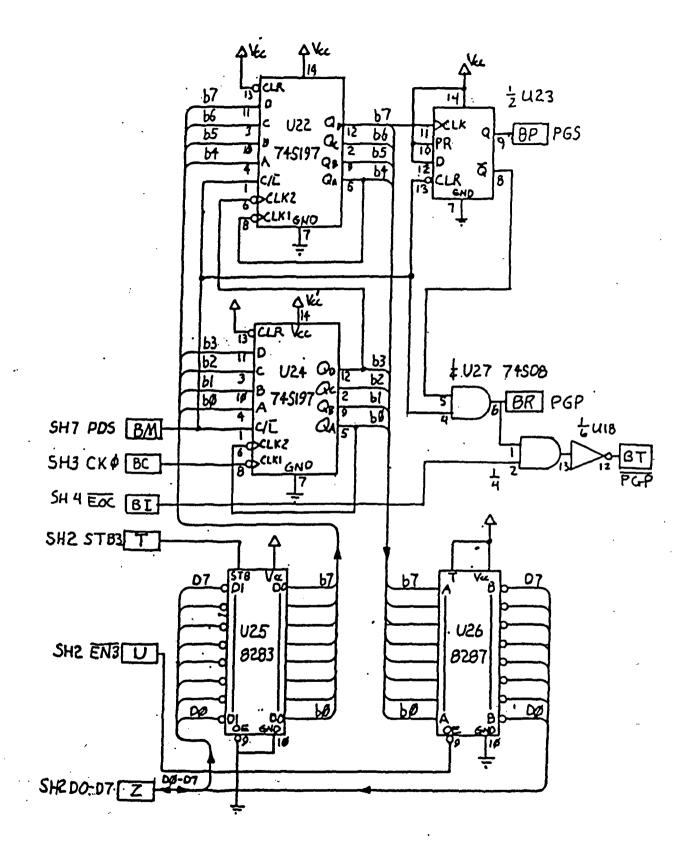

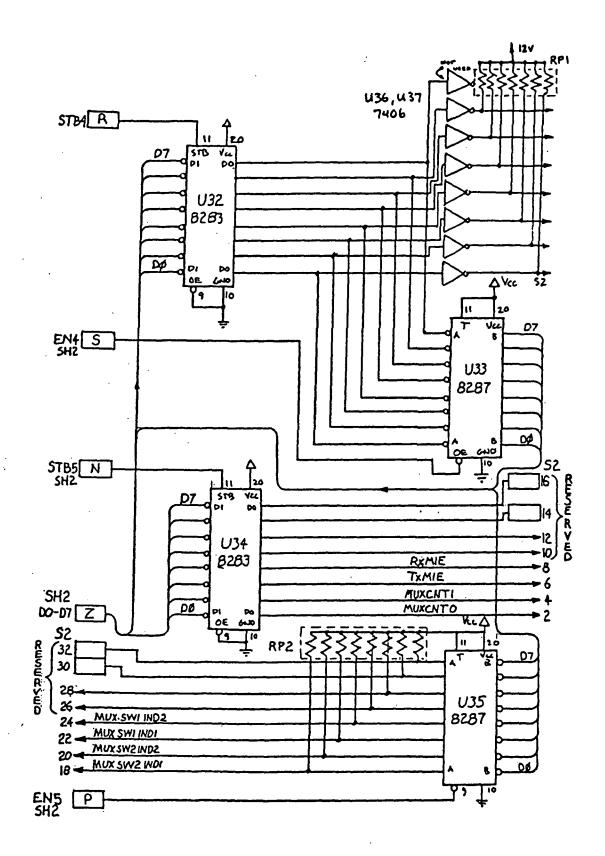

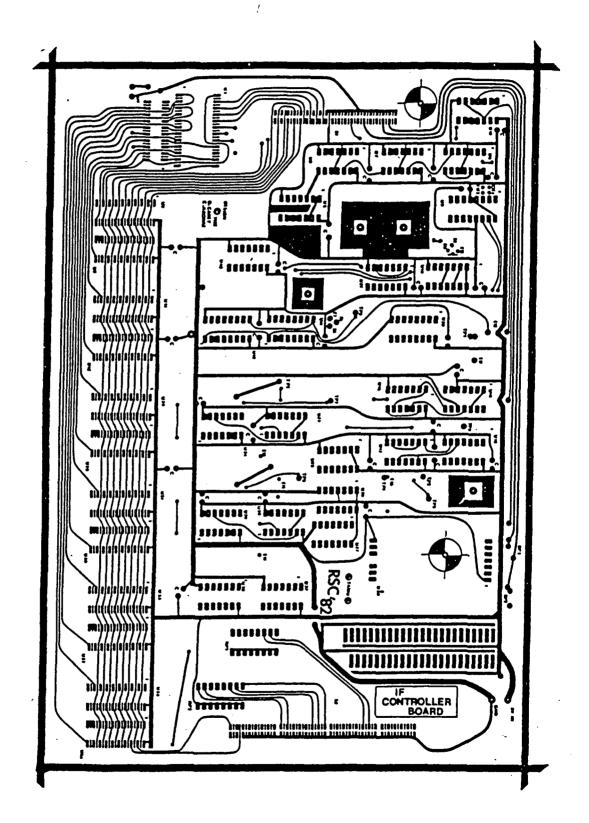

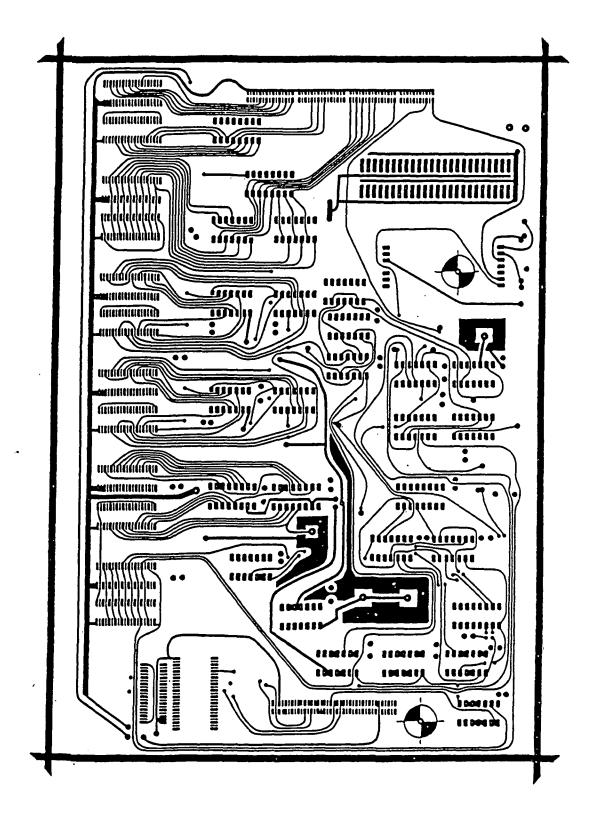

| APPENDIX A. IF CONTROLLER CIRCUIT BOARD ELECTRICAL DIAGRAMS<br>AND PRINTED CIRCUIT LAYOUT | 112 |

| APPENDIX B. RDADS SOFTWARE SOURCE LISTINGS                                                |     |

| THE HEAT DE READE OF THIRE SOURCE EIGTINGS & & & & & & & & & & & & & & & & & & &          | 467 |

~

LIST OF TABLES

| TABLE |  |

|-------|--|

|-------|--|

ι.

| 1  | Port Addresses for the 80/24's Parallel I/O (Hex) |

|----|---------------------------------------------------|

| 2  | Cal/Op Control Port Signal Assignments            |

| 3  | Indicator Enable Port Signal Assignments          |

| 4  | Indicator Circuit Read Port Assignments           |

| 5  | Interpretation of Indicator Circuit Data          |

| 6  | RF Head Common Control Port Signal Assignments    |

| 7  | iSBC-80/24 Parallel I/O Summary                   |

| 8  | iSBX-311 Analog Input Signal Assignments          |

| 9  | Memory Map for the RDADS iSBC-80/24 Processor     |

| 10 | Processor Port Assignments for IFC Interface 40   |

| 11 | IFC Channel Assignments                           |

| 12 | IFC Control Channel (2) Signals                   |

Page

### LIST OF FIGURES

.

• .

٠

•

| FIGU | RE                                                                     | Pa | age |

|------|------------------------------------------------------------------------|----|-----|

|      | · ·                                                                    |    |     |

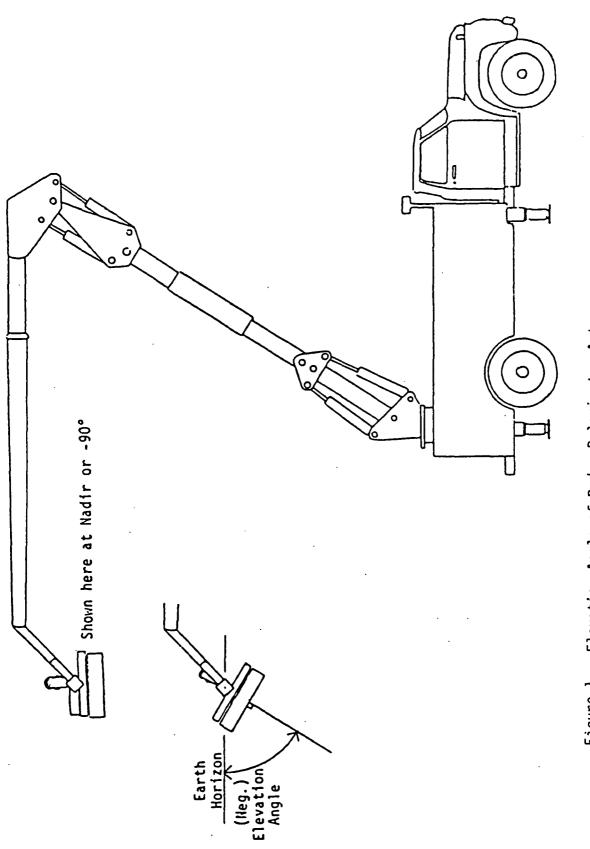

| 1    | Elevation Angle for Radar Polarimeter Antennas                         | •  | 4   |

| 2    | Azimuthal Angle of Radar Polarimeter Boom                              | •  | 5   |

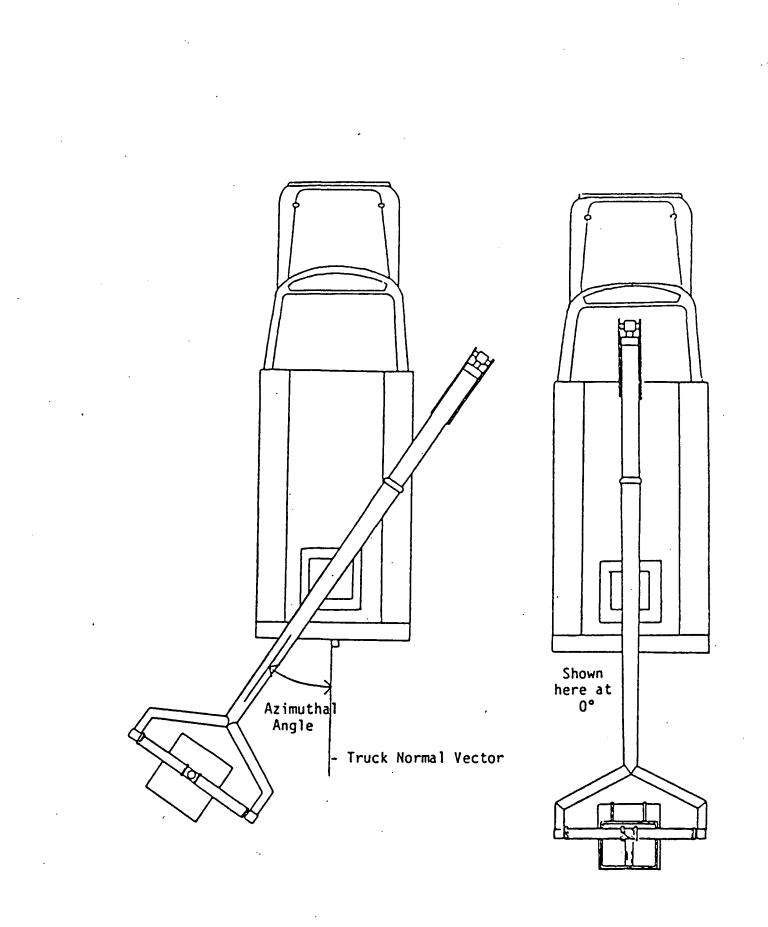

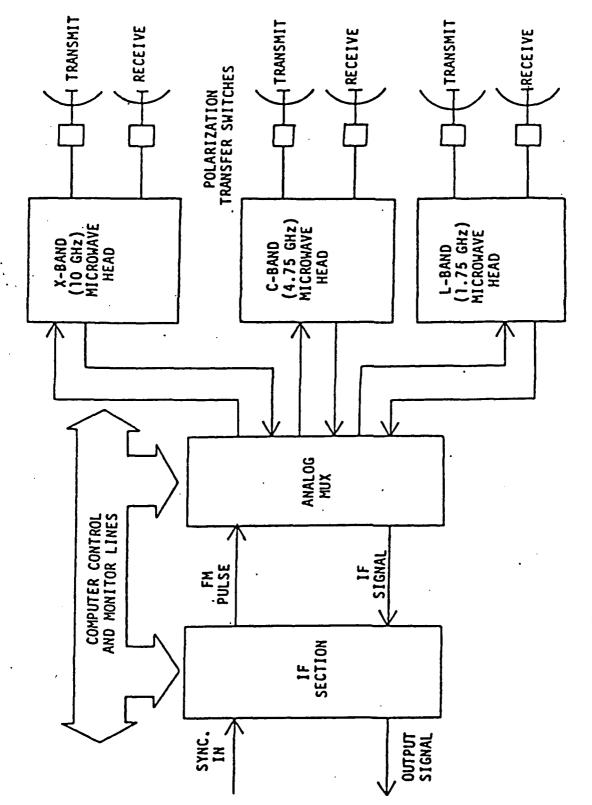

| 3    | Block Diagram of the Radar Polarimeter System                          | •  | 6   |

| 4    | Block Diagram of Radar Hardware                                        | •  | 10  |

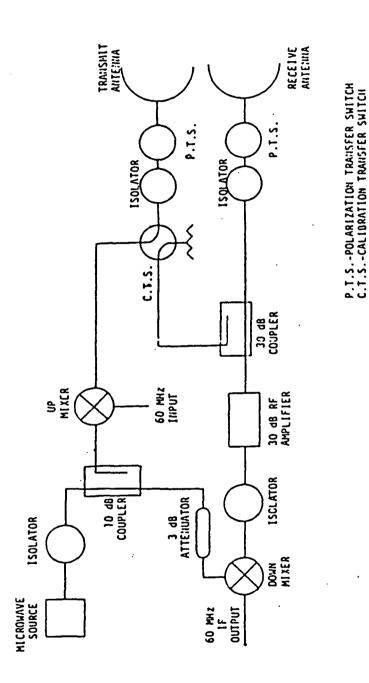

| 5    | Microwave Transceiver Circuit Transfer Switches<br>Controlled by RDADS | •  | 12  |

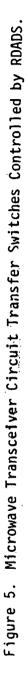

| 6    | Block Diagram of IF Section of the Radar                               | •  | 13  |

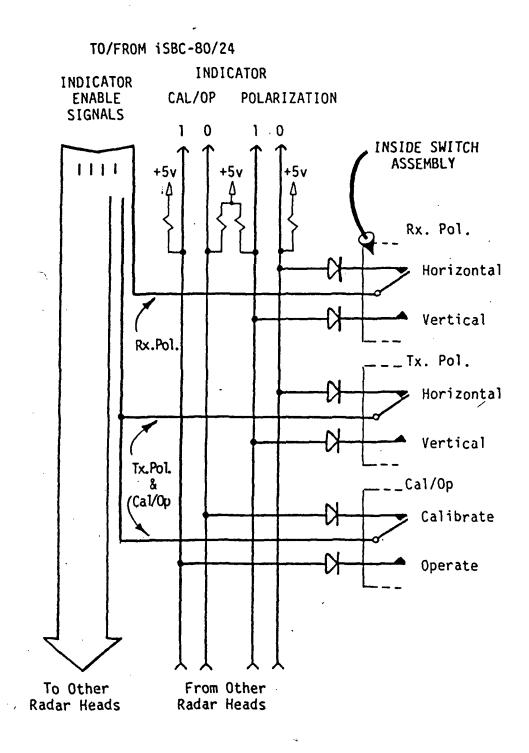

| 7    | Indicator Circuits for a Single Radar Head                             | •  | 28  |

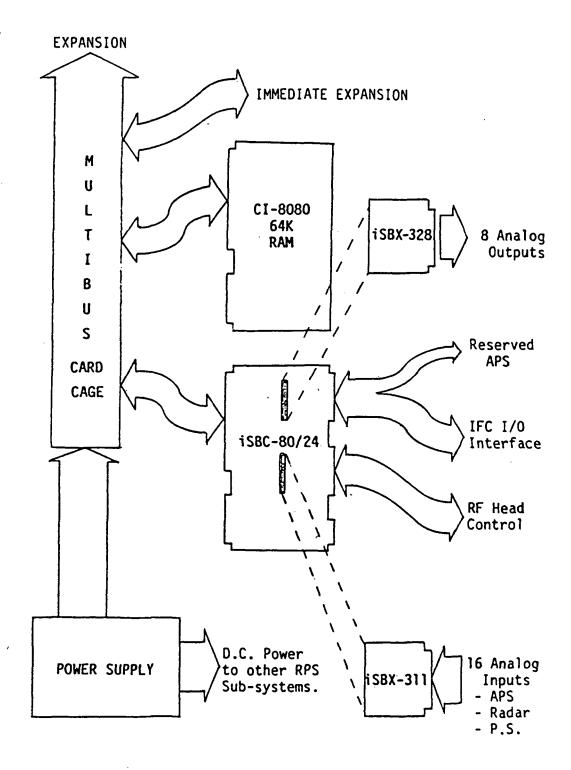

| 8    | RDADS Computer Block Diagram                                           | •  | 38  |

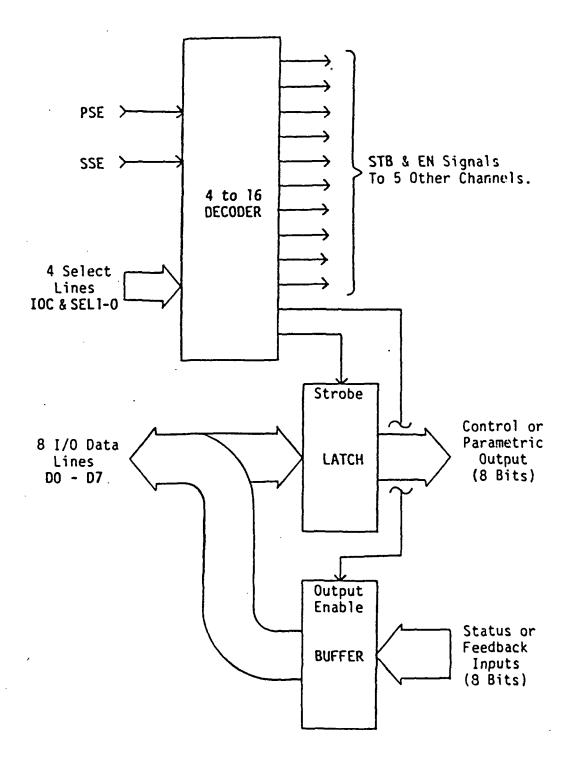

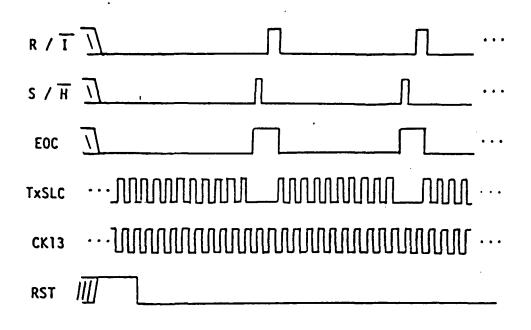

| 9    | Processor I/O Interface on the IFC                                     | •  | 42  |

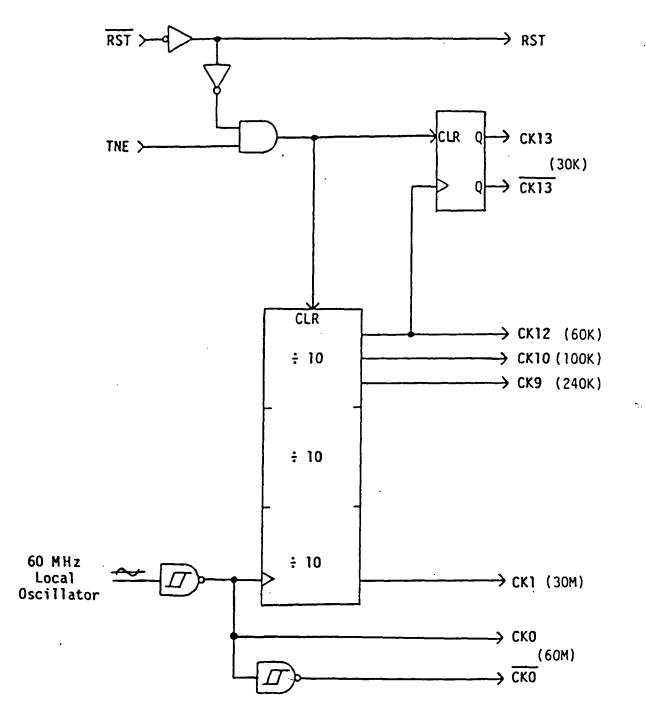

| 10   | IFC Timing Network                                                     | •  | 45  |

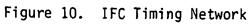

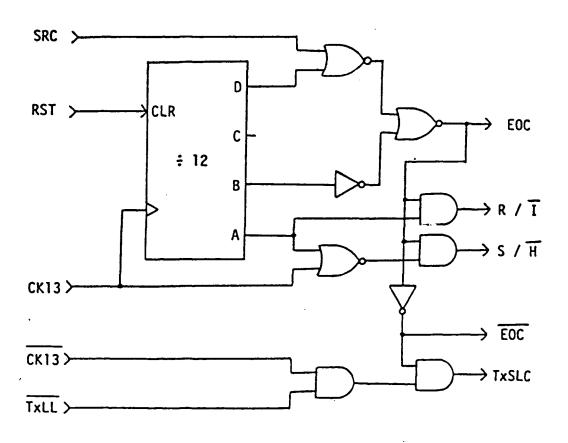

| 11   | Cycle Controller for the IFC                                           | •  | 46  |

| 12   | IFC Programmable Transmit Pulse Generator                              | •  | 49  |

| 13   | IFC Fixed Delay Generator                                              | •  | 51  |

| 14   | Programmable Range Delay Generator                                     | •  | 53  |

| 15   | Programmable Gate Pulse Generator                                      | •  | 55  |

| 16   | Simple Block Structure Diagram                                         | •  | 58  |

| 17   | Structure Diagram for the Remote Operations Utility<br>Package         | •  | 64  |

,

#### **PROJECT BACKGROUND**

The Remote Sensing Center (RSC) at Texas A&M University was contracted by NASA Goddard Space Flight Center to design, build, and put into operation a mobile land based radar polarimeter [1]. The formal name of this experimental remote sensor is the Radar Polarimeter System (RPS). The sensor was constructed for use in soil moisture and other agricultural remote sensing experiments. An integral component of the RPS is an electronic control and data acquisition system. This major RPS subsystem receives commands from and sends information to a master processing computer. The control and data acquisition electronics will hereafter be referred to as the Remote Data Acquisition and Distribution System or RDADS. It was the objective of this effort to design and construct the RDADS.

#### Remote Sensing

Remote Sensing is a science dealing with obtaining information about objects through measurements made without coming into contact with the objects. Currently this science is providing valuable information to those involved in agriculture, forestry, hydrology, mineral exploration, and land use management. For many years theorists and scientists have been interested in the depolarization effects of

. .

natural terrain on electromagnetic energy (Blanchard [2], Fung [3] Leader [4], Rouse [5], Beckman [6], Blanchard [7], etc.). The phenomenon of the depolarization of radar backscatter has been established as having potential application in the remote sensing of soil moisture content (Blanchard [8], Hirosawa [9], Ulaby [10], etc.). There is, however, a need for controlled experimentation investigating the effect of target parameters on cross polarized radar measurements. The ground based radar polarimeter was constructed for use in this type of experimentation.

#### The Radar Polarimeter System

The RPS consist of two vehicles, a computer data van and a radar boom truck. The data van houses and transports a computer used for automatic control of the RDADS, data acquisition and storage, and computational support. Data van subsystems are all part of the main processor. These subsystems include the Central Processor Unit (CPU), program and data storage equipment, and the Operator's I/O console.

The radar truck is a flatbed truck with a tandem boom mounted on the bed. The boom is used to position the polarimeter radar equipment and antennas over a test site. Subsystems of the radar boom truck include the radar, the Antenna Positioning System (APS), and the Remote Data Acquisition and Distribution System (RDADS). The radar subsystem acquires polarized microwave backscatter measurements. Antenna orientation and position are controlled by the APS. The radar and APS are both controlled by the RDADS. Moreover, the RDADS acts as the smart interface between the RPS subsystems and the data van computer.

Because of the nature of the radar polarimeter and the measurements to be made with it, the radar antennas must be translated over an azimuthal arc during operation. This azimuthal scan is accomplished by turning the boom at its base. In addition, data must be acquired at different elevation angles in order to observe the effect of incidence angle on radar backscatter measurements. Figures 1 and 2 present drawings of the radar boom truck from two different views to illustrate the two angular freedoms of movement. Each of these angular position parameters (azimuth and elevation) is controlled by the RDADS through the APS interface hardware.

Microwave measurements are made by radar hardware mounted on the boom truck. The radar is composed of the RF, IF, and video electronics required to make the microwave backscatter measurements. The radar operates at frequencies in three different bands (X, L and C). This allows effects of frequency on target sites to be studied. Individual, dual-polarized transmit and receive antennas for each microwave band are part of the radar's RF equipment. These antennas allow measurements to made for four different combinations of transmit and IF and video electronics are used for range receive polarization. gating and integration of radar measurement signals. All radar circuitry is controlled and monitored by the RDADS.

Figure 3 presents a block diagram of the entire Radar Polarimeter System showing each of the subsystems mentioned above. This document describes the design and development of the RDADS. The next section covers the interface and operational requirements of the system. The design and development are then covered in two sections, one on

Figure 1. Elevation Angle of Radar Polarimeter Antennas.

Figure 2. Azimuthal Angle of Radar Polarimeter Boom.

Figure 3. Block diagram of the Radar Polarimeter System.

hardware and one on software. A final section summarizes the design and recommends future work.

#### STATEMENT OF WORK

The objective of this project was to design, implement, and document the Remote Data Acquisition and Distribution System (RDADS). This effort included the hardware required to interface and control the radar equipment and the APS electronics. Hardware was also required for communicating with the main processor. The work also included all software required to operate the radar and to communicate with the main processor. Development of the APS hardware and the RDADS software used to control it were not a part of this work. The development of radar RF, IF, and video electronics were also not a part of this project.

The primary function of RDADS was to control and monitor the functions of the radar electronics. The system allows for automatic operation of the radar under the data van computer's direction. This section will review the radar electronics of the RPS to identify the interface and control requirements for the RDADS.

#### Radar Electronics

Radar Hardware mounted on the boom truck accomplishes the actual microwave measurements performed by the RPS. This hardware consists of three separate microwave transceivers multiplexed into a single Intermediate Frequency (IF) processing section. Each RF head operates at a specific frequency, namely 1.6 GHz for L-band, 4.75 GHz for C-band, and 10.0GHz for X-band. The radar system uses a pulse compression technique to achieve high range resolution. The IF section generates an

FM signal centered at 60 MHz. This phase coded expanded pulse is up converted to microwave frequencies in each radar head. The IF section also accepts the signal received by the RF head once it has been converted back to the 60 MHz IF range. Pulse compression, video amplification, range-gating, and integration are performed in sequence on the return signal by the IF receiver. The RDADS computer controls and monitors the operation of these radar components. Figure 4 presents a block diagram of the radar hardware.

#### Microwave Transceivers

The RF heads transmit electromagnetic microwave energy to the target through dual polarized antennas. Identical antennas are used to receive the microwave energy reflected by the target. For each of the microwave transceivers there is a pair of antennas, one transmit and one receive. Each antenna has two coaxial feed connections, one for vertical polarization and one for horizontal polarization.

A mechanical microwave switch is used to select which feed, and therefore which polarization, is used for the transmit and receive antenna. These switches, referred to as Polarization Transfer Switches (PTS), are controlled by the RDADS. They are controlled by a single TTL level signal such that a high level selects the vertical feed and a low level selects the horizontal feed.

A four-port microwave switch is used in each RF head to allow an internal calibration measurement to be made. This Calibration Transfer Switch (CTS) is used to bypass the head's antennas by feeding the transmit signal directly into the receiver circuit. This switch is

Figure 4. Block Diagram of Radar Hardware

controlled by the RDADS through two TTL signal lines. A pulse on one signal line causes the CTS to switch to the internal calibration loop. A pulse on the other line switches the CTS to allow transmission through the antennas. Each transfer switch has an internal singlepole, double-throw indicator switch that operates in conjunction with the microwave switch. These electrical indicator switches are used by the RDADS to monitor the state of each Polarization Transfer Switch and Calibration Transfer Switch.

Placement of the RF switches in the microwave circuitry is shown in Figure 5. This figure is a circuit diagram for a single RF head. The microwave source for each head determines its frequency of operation. The individual components in each head are either broadband devices or designed for operation in the frequency range of that head.

IF Section and Multiplexer

The IF section of the radar generates a swept frequency pulse that is directed to a selected RF head through the analog multiplexer. This FM pulse is then up converted by the selected head to the proper RF frequency and transmitted to the target. The reflected signal received by the RF head is down converted back to the IF range. The IF section will receive this down converted signal via the analog multiplexer and estimate the return energy. An analog signal whose voltage level is a function of return energy is output by the IF section.

Figure 6 shows a block diagram of the IF section of the radar. The transmitter portion generates the swept frequency pulse that is centered at 60 MHz. A square pulse of approximately 50 nS duration is

:

Figure 6. Block Diagram of IF Section of the Radar

required as an input to the IF transmitter. This pulse is used to generate a 60 MHz tone burst of the same duration. When the 60 MHz pulse is applied to the SAW filter device a Frequency Modulated (FM) pulse is produced. This swept frequency pulse is then upconverted by the RF transmitters.

The receiver portion of the IF section requires several input signals for proper operation. The 7-bit digital attenuator is used to control the gain of the IF receiver. This attenuator is controlled automatically by the RDADS. A range-gating pulse must be input to the IF receiver to control the gating of received signals into the Video Integrator. By providing the range-gating signal at the proper time and duration, the receiver can reject unwanted reflections and noise. The time of occurrence of the gate signal with respect to the occurrence of the IF transmit pulse will vary depending on the distance to the target and for internal calibration measurements. In addition, the duration of the gate signal varies with changes in the incidence angle of the electromagnetic energy on the target. The RDADS provides the range-gating signal at the proper time and of the proper duration, dependent on elevation angle and when the RF head is in calibrate mode.

The RDADS also supplies a "sample-and-hold" control signal and an "integrator reset" signal to the IF receiver. These signals are applied to allow integration of several received pulses and sampling of the resulting integrator output which is held as the IF section's analog output. The RDADS measures the analog output by converting it to a digital count.

The analog multiplexer used to select between radar heads uses mechanical switches identical to those used for polarization control. Two switches with the common port of one connected to one of the switched ports of the other are used to multiplex three lines to one. One switch pair is used for switching the IF transmitter's output to one of the three RF heads. The return signal of each head is connected to another switch pair to multiplex these into the IF receiver. Two TTL level signals, one for each switch, are required for each pair. These switches also have indicators that are used to monitor their state. The RDADS controls and monitors both multiplexer switch pairs.

#### Other RDADS Interfaces

The RDADS must also provide interface capability for use by the APS. Both analog input and output are required for the control and monitoring of antenna position. Analog outputs are used to signal D.C. motor control drive circuits to set the motor speed. Angular position information is input as an analog signal. Digital control lines are also used by the APS to control direction of movement and braking functions. The RDADS has provisions for these analog I/O and digital output signals.

The RDADS computer communicates with the data van computer through a serial RS232 data link. The RDADS has an asychronous communications channel used for this purpose. The main processor sends instructions for controlling the operations of the RPS to the RDADS through this link. The RDADS provides automatic functions that support and simplify the control operations. Data obtained by the RDADS are transmitted to the data van over the same serial data link. D.C. power for the boom

truck sub-systems is provided by the RDADS. This power is generated using D.C. power supplies that operate off of a 115 volts 60 Hz power source.

The interface and operational requirements of the RDADS have been identified. Of these, the most important is the radar interface since it is the means by which the polarimeter measurements are made. Provisions were identified for interfacing to the APS hardware developed external to this project. Operations controlled by the RDADS are done so under direction of the main processor in the data van. Instructions from the main processor and data returned by the RDADS are passed through a serial data link between the two systems. The next section will describe the hardware used to implement the RDADS.

#### HARDWARE

This section presents the design and implementation of the RDADS hardware. A short presentation of the design philosophy adopted for this project will be given. Following this, a complete description of the hardware installation will be given with details on interfaces to other RPS subsystems.

#### Design Approach

To obtain the best time wise execution of this project and still maintain high degrees of reliability and flexability, proven components and technology were utilized wherever possible. Industrial grade components were chosen from available "off-the-shelf" hardware to meet the RDADS operational requirements. These Original Equipment Manufacturer (OEM) designated products simplified the design by providing flexible, high level functions. Whenever a requirement could not be met with available industrial products, an original design was implemented.

A single board, microprocessor based, computer is the center of the system's hardware. This computer controls the operations of the RDADS under direction by the data van computer. The RDADS computer board also provides capability for interfacing directly to other RDADS, Radar, and APS hardware. Since the design uses a microprocessor, most of the system's operation was defined in software. This allowed a large degree of flexibility in the design. In addition, operations

that would be complex or difficult to implement in hardware were more easily accomplished in software. Other OEM products utilized in the design were analog I/O boards, a memory expansion board, a cardcage providing a bus backplane, and several D.C. power supplies. Collectively, these components were labeled the RDADS Computer.

The range gating function of the IF receiver presented a special design problem for the project. The required speed of operation for a controller could not be met using any available OEM products. An original design utilized Schottky TTL integrated circuit devices (ICs) to accomplish high speed control functions. The design was implemented on a single printed circuit board labeled the IF Controller or IFC. This circuit also expanded the RDADS Computer's parallel I/O capability in the IF section.

#### RDADS Computer

The Remote Data Acquisition and Distribution System computer controls the operation of boom truck subsystems. This stand alone processor has the following duties:

- o Communicate with the data van CPU.

- o Control the IF and RF hardware.

- o Control the antenna elevation and boom scan.

- o Acquire radar data.

Interfaces to other RPS subsystems are an integral part of the RDADS hardware. These interfaces required the computer to have both digital and analog I/O capabilities. The hardware of the RDADS

computer can be broken down into the following components:

o Central Processor with digital I/O capabilities.

o Analog I/O Interface.

o Random Access Memory.

o Chassis and Power Supply.

Selections made for each of these components will be discussed in the following sections.

Central Processor

The central processor controls all activity of the RDADS. Intel Corporation's iSBC-80/24 Single Board Computer System was chosen for use as the central processor. The 80/24 is a single printed circuit board that uses an Intel 8085A-2 microprocessor. Since the 80/24 is designed for general applications, it is very versatile and can be configured in a number of different ways. The board has many jumper selectable component interconnects and set-up options. Several I.C. components on the board have software programmable functions. The 80/24 also accommodates connection directly to special configuration circuit boards.

The 80/24 is compatible with the IEEE-796 Bus Standard (known commonly as the Multibus). The board provides a system clock, parallel data communications lines, a serial communications channel, firmware (EPROM) sockets, programmable interval timers and event counters, and interrupt control circuitry. General specifications for the iSBC-80/24 are as follows:

o Complete computer system on a single 6.75 by 12.0

inch printed circuit board.

- An Intel 8085A-2 microprocessor operating at 4.8

MHz.

- Sockets for 4K bytes (using 2708 or 2758), 8K bytes (using 2716), 16K bytes (using 2732), or 32K bytes (using 2764) of EPROM.

- o 4K bytes of Random Access Memory on board.

- o Multimaster-Multibus bus arbitration logic.

- o Bus addressable to 64K.

- o USART with RS232C line drivers and receivers for serial I/O up to 38,400 baud.

- o Three programmable BCD or binary timers and event counters.

- o 19.35, 9.68, 4.84, 2.15 and 1.075 MHz on board clock signals.

- Programmable control logic for up to 12 levels of vectored interrupts.

- o Forty-eight programmable parallel I/O lines with sockets for I/O line drivers and terminators.

- o Two iSBX bus Multimodule interface connectors.

For complete details on operation and use of the board see the "iSBC-80/24 Single Board Computer Hardware Reference Manual" [11].

The 8085 microprocessor controls all functions of the 80/24. The board was configured for installation of up to four 2732 EPROMs through jumper selections. Three 2732 EPROMs were used to store a control program for the 8085. This resident software directs all operations of

the RDADS. It utilizes the 4K on-board RAM of the 80/24 for variable storage. The 64K bus addressing capability of the 80/24 was used to install an expansion RAM board. With this set-up, the processor has up to 16K bytes of constant program memory and 48K bytes of dynamic read/write storage.

#### Serial I/O, Timers, and Interrupts

The serial channel of the 80/24 was used for communicating with the Data Van CPU. This channel was configured for a standard RS232 set up so that no special interfaces were required for connection of the serial data link. On-board line drivers and receivers convert 0 to +5 (TTL) voltage levels to and from the standard RS232 +12 to -12 voltage levels. The serial interface was set up for loop-back of all RS232 hand-shaking signals, thus it required only three connections. These were Transmit Data (TxD), Receive Data (RxD) and a signal ground. Serial communication is controlled by an 8251A Programmable Communications Interface (PCI) I.C. The 8085 sends and receives data through the 8251 in a parallel format. Conversion of the parallel data to and from serial data formats is handled by the 8251 PCI.

An 8253 Programmable Interval Timer (PIT) chip on the 8024 provides three independent programmable timers. Timer 2 of this device is used as a baud rate generator for the serial communications channel. The input to Timer 2 is the on-board 1.075 MHz clock signal. The timer is programmed for square wave, divide by 7, operation so that it outputs a 153.6 KHz clock signal. This signal is applied to both the receive and transmit clock inputs of the 8251 PCI. The 8251 was

programmed for an asynchronous communications rate multiplier of 16 so that the baud rate of the serial interface is 9.6 KHz or 9600 Baud. Since both the 8251 and the 8253 are software programmable the baud rate for the system can easily be adjusted.

The 1.075 MHz clock signal was also input to Timer 0 of the 8253 PIT. This timer was programmed to divide the input by 53,750 in order to produce a pulse output rate of 20 Hz. The output of Timer 0 was tied to the IR1 pin of the 8259A Programmable Interrupt Controller (PIC). This provided a Level 1 Hardware Interrupt every 50 mS for timing various system functions. Again, since the PIT is software programmable, this real time clock rate can be modified.

An output from the IF section is used to syncronize the RDADS processor's data acquisition with the analog output from the radar. This output was the IF Service Request (IFSR) signal. IFSR tells the processor when the analog output of the receiver is ready for conversion. To reduce the radar data rate, IFSR is input to Timer 1 of the Timer 1's output was then applied to IR2 of the 8259A PIC. The 8253. timer was programmed for divide by 21 operation. IFSR cycled at a fixed rate of 2.5 KHz so that a Level 2 interrupt occurred every 8.4 mS when enabled. During radar data acquisition the Level 2 interrupt triggers the analog data conversion done by the processor. The analog data acquisition rate is approximately 119 samples per second. The software that programs the operation of Timer 1 of the 8253 can easily be changed to obtain a different data acquisition rate.

Two other interrupt levels are used in the RDADS processor. These are utilized for interrupt driven serial I/O: Level 6 interrupt for

serial input and Level 7 for serial output. The Receiver Ready (RxR) signal output by the 8251A PCI was tied to IR6 of the PIC. Transmitter Ready (TxR) from the PCI was connected to IR7 of the PIC. With these two interrupts, the processor did not have to poll the PCI during I/O operations. Instead the processor could send data to the 8251A and then do other work while the 8251A output the data. The processor could also be interrupted during non-critical operations when data was received by the 8251A.

#### Parallel I/O

Parallel I/O lines of the 80/24 were used for hardware control and monitoring. This parallel communications is accomplished on the 80/24 by two 8255A Programmable Peripheral Interface I.C.s. Each 8255A PPI has three 8-bit programmable I/O ports. Ports A and B can be programmed independently as either input or output. Port C is programmed independently as either input, output, half input and half output, or as handshaking signals for I/O operations of Ports A and B. Also, when programmed for output, signals from Port C can be controlled individually through bit set/reset commands issued to the 8255A's control port. The two 8255A's on board the 80/24 provide a total of 48 parallel I/O lines divided into six ports. Port addresses for all six ports are summarized in Table 1.

Ports E8, E9, and EA were used for communicating with the RF hardware. Port E8 was programmed as output and used to control the calibrate/operate (Cal/Op) transfer switches in the RF heads. A Cal/Op switch has two positions and requires two signals to control it. A

| 8255A No. 1 | 8255A No. 2 |

|-------------|-------------|

| E4          | E8          |

| E5          | E9          |

| E6          | EA          |

|             | E4<br>E5    |

Port Addresses for the 80/24's Parallel I/O (Hex)

TABLE 1

pulse on the switch Control O signal would set the switch to the calibrate position. Likewise, a pulse on Control 1 would place the switch in the operate position. Each had to be controlled independently so that only one selected head would be in operation at any given time. Designating Port E8's eight bits for Cal/Op control allowed for connection to the three existing radar heads and one additional backup or expansion connection. The assignment of the output signals for Port E8 are given in Table 2.

The two control signals for a Cal/Op switch energize two respective coils internal to the switch. The switch assembly has an internal electronic circuit that automatically turns either coil off after it accomplishes its internal mechanical operation. This means that the controlling signal can be a level rather than a pulse which simplifies the algorithm used to drive the port. The only requirement is that the two signals applied to a Cal/Op switch must never both be high at the same time. This approach also supports the use of transfer switches that have a single level sensitive control input.

The radar head numbers specified in Table 2 were used during

| Port E8 1 | Bit  | Assignme | ent     |    |

|-----------|------|----------|---------|----|

| 0         | Head | 1 Cal/Op | Control | 0  |

| 1         | Head | 1 Cal/Op | Control | 1. |

| 2         | Head | 2 Ca1/Op | Control | 0  |

| 3         | Head | 2 Ca1/Op | Control | 1  |

| 4         | Head | 3 Ca1/Op | Control | 0  |

| 5         | Head | 3 Cal/Op | Control | 1  |

| 6         | Head | 4 Ca1/Op | Control | 0  |

| 7         | Head | 4 Cal/Op | Control | 1  |

|           |      |          |         |    |

TABLE 2

Cal/Op Control Port Signal Assignments

development when the actual microwave band assignment was of no concern. These head numbers were assigned to particular bands in the final system as follows:

Head 1 - X Band (10.0 GHz). Head 2 - L Band (1.75 GHz). Head 3 - C Band (4.75 GHz). Head 4 - Reserved for future use.

This assignment was purely a matter of choice and had no impact on the design. It is presented here for clarity.

I/O Port E9 on the 80/24 was used in monitoring the status of all microwave switches in the radar heads. This port was programmed for output operation and used to control the multiplexing of switch state indicator circuits. Each switch assembly has an electrical single-

pole, double-throw indicator switch that is set according to the current state of the microwave switch. Output signals from Port E9 drive the common pole of individual indicator switches or pairs of switches. Within an RF head the common poles of both the Cal/Op and the Transmit Polarization (Tx. Pol.) switches are connected to the same output bit of Port E9. Each pair was connected to a different bit, one bit for each head. The common pole for each Receive Polarization (Rx. Pol.) switch is connected to other bits of port E9, again one for each head. These signals out of Port E9 are called the Indicator Circuit Enables and the specific assignments are given in Table 3.

| T | A | В | L | Ë | 3 |

|---|---|---|---|---|---|

|---|---|---|---|---|---|

Indicator Enable Port Signal Assignments

| Port E9 Bit | Indicator Circuit Assignment |

|-------------|------------------------------|

| 0           | Head 1 Tx. Pol. and Cal/Op   |

| 1           | Head 1 Rx. Pol.              |

| 2           | Head 2 Tx. Pol. and Cal/Op   |

| 3           | Head 2 Rx. Pol.              |

| 4           | Head 3 Tx. Pol. and Cal/Op   |

| 5           | Head 3 Rx. Pol.              |

| 6           | Head 4 Tx. Pol. and Cal/Op   |

| 7           | Head 4 Rx. Pol.              |

| 6           | Head 4 Tx. Pol. and Cal/Op   |

The upper half (Bits 4 through 7) of Port EA was programmed for input and used to read the status of the microwave switches. Assignments for these input lines are given in Table 4. Two are used for polarization switch indicator monitoring and two for Cal/Op switch indicator monitoring. Each pair consist of one line labeled Indicator O and one line labeled Indicator 1. The polarization indicator pair connects to both the Tx. Pol. and Rx. Pol. indicator switches in every radar head. Likewise, the Cal/Op indicator pair connects to the Cal/Op indicator switch in each head. All connections to indicator switch terminals are made through a signal diode, one diode for each terminal, with the anode end tied to the terminal. The cathode end of the diode ties to either Indicator 0 or 1 dependent on how the switch's RF ports are connected. The upper four bits of Port EA are pulled to a high level through 1K ohm resistors on-board the 80/24. Indicator circuits for a single radar head are illustrated in Figure 7.

#### TABLE 4

Indicator Circuit Read Port Assignments

| licator Read Function |

|-----------------------|

| arization Indicator O |

| arization Indicator 1 |

| Cal/Op Indicator O    |

| Cal/Op Indicator 1    |

|                       |

Figure 7. Indicator Circuits for a Single Radar Head

Normally, the Indicator Circuit Enable outputs are at a high level. An indicator circuit can be read by the processor to determine the status of any switch in the radar heads as follows:

- o The Indicator Circuit Enable output for the desired head and desired switch (or switch pair) is driven low. Only one output of Port E9 should be low at any time or results of the read are unspecified.

- o The Indicator Read Port (upper half of Port EA) is input to the processor. The status of the selected switch is then determined from the data read.

The Indicator Read data can be divided into two separate 2 bit binary values, one for polarization and one for Cal/Op. Indicator 0 would be the least significant bit of the 2 bit value and the value would range from 0 to 3. Table 5 defines the meaning of data returned by an indicator circuit read. This table shows an open circuit failure as Failure I and a short circuit failure as Failure II.

The lower half of Port EA was programmed for output operation. Bits 2 and 3 were used to control the transmit and receive polarizations. Polarization switches required a single TTL level control signal. The microwave antennas were connected so that a low level signal corresponded to horizontal polarization and a high level signal corresponded to vertical. Since only one RF head can be operating (transmitting) at a time, the polarization transfer switches in each head were controlled simultaneously. This was accomplished using the two signals (bits 2 and 3) of Port EA. Bit 2 controls all transmit

| INDICAT | OR LINE | INDICAT    | OR PAIR      |

|---------|---------|------------|--------------|

| 1       | 0       | Cal/Op     | Polarization |

| L       | L       | Failure II | Failure II   |

| L       | н       | Calibrate  | Horizontal   |

| н       | L       | Operate    | Vertical     |

| Н       | Н       | Failure I  | Failure I    |

Interpretation of Indicator Circuit Data

TABLE 5

polarization switches and Bit 3 controls all receive polarization switches. The two remaining output bits of Port EA were also routed to every radar head. These bits provide spare common control signals to the RF heads reserved for future expansion or modification. The bit assignments of the lower half of Port EA are summarized in Table 6.

## TABLE 6

RF Head Common Control Port Signal Assignments

| Port EA Bit | Control Function      |

|-------------|-----------------------|

| ·           |                       |

| 0           | Reserved RF Control O |

| 1           | Reserved RF Control 1 |

| 2           | Transmit Polarization |

| 3           | Receive Polarization  |

|             |                       |

Parallel Ports E4 and E6 of the 80/24 were used for monitoring and control of the IF section. Port E4 was utilized as a bidirectional data port for I/O operations to the IF Controller board. Port E6 was programmed for output and used primarily to control the I/O operations of Port E4. Both of these ports and their assignments will be discussed in more detail in the second part of this section that covers the IFC.

Port E5 was reserved for use by the Antenna Positioning System. Interfaces to the APS were developed external to this project. For information on the use and assignment of signals of Port E5, documentation on the APS should be consulted. The use of all parallel I/O ports on the 80/24 is summarized in Table 7.

# Analog I/O Interface

A unique feature of the 80/24 is that it is Multimodule compatible. The two iSBX bus interface connectors allow two iSBX Multimodule boards to be mounted directly on the 80/24 board. The 80/24 can be specially configured for different applications through the use of available Multimodule boards. Intel currently supplies several Multimodule boards for a variety of applications. Two such boards where obtained for analog I/O functions.

This part of the RDADS processor actually consists of two components: an analog input board and an analog output board. Each of these boards are Intel Multimodule boards that mount directly on the iSBC-80/24 board. This requires the use of both of the 80/24's Multimodule connectors.

| TABL | Ε. | 7 |

|------|----|---|

|------|----|---|

iSBC-80/24 Parallel I/O Summary

| Port Address | Assigned Function |

|--------------|-------------------|

| E4           | IFC Data I/O      |

| E5           | Reserved (APS)    |

| E6           | IFC I/O Control   |

| É8           | Cal/Op Control    |

| E9           | Indicator Control |

| EA Lower     | RF Head Control   |

| EA Upper     | Indicator Read    |

The analog input board selected for use in the RDADS was the iSBX-311 Analog Input Multimodule board. The specifications for this board are as follows:

- o Eight differential or sixteen single-ended analog inputs.

- o Resistor selective gain (1X-250X).

- o -5 to +5 volt bipolar or 0 to +5 volt unipolar input range.

- o 12 bits Resolution (11 bits plus sign for +/volts).

- o Accuracy of +/-0.035% of full scale range +/- 1/2

LSB.

- o 20 megohms input impedence with input protection to

30 volts.

o Typical conversion time of 50 microseconds.

o 18K conversions per second sample rate.

The iSBX-311 was used in its factory configuration of single ended, bipolar operation with a 1X gain setting. This set-up provided 16 analog inputs with an input range of -5 to +5 volts and input resolution of 2.44 millivolts. Complete details on the iSBX-311 can be found in the board's hardware reference manual [12].

The analog inputs provided by the 311 are used to measure the radar output signal, antenna elevation angle, and supply voltage levels. Some of the inputs to this board were left unused and are reserved for future expansion or modifications. The signal assignments for the 311 are itemized in Table 8. All D.C. supply voltage levels were divided down using trimming potentiometers (trimpots) to produce the monitor levels input to the analog converter. The 117 volt A.C. level was conditioned using a low voltage transformer, single wave rectifier, and R-C filter. This produced a D.C. voltage level corresponding to the average peak magnitude of the A.C. line voltage. The peak level signal was also divided down using a trimpot before input to the iSBX-311. The trimpots are adjusted to calibrate supply voltage monitoring.

The iSBX-328 Analog Output Multimodule board was chosen for use as the analog output interface. The 328's specifications are listed below:

- o Eight independent analog voltage level or current loop (individually selectable) outputs.

- o Output ranges of -5 to +5 volts bipolar level, 0 to

| TABLE 8 | TA | BL | .Ε | 8 |

|---------|----|----|----|---|

|---------|----|----|----|---|

iSBX-311 Analog Input Signal Assignments

| Channel | Input Signal              |

|---------|---------------------------|

| 0       | IF Analog Data Signal     |

| 1       | APS Position Signal 1     |

| 2       | APS Position Signal 2     |

| 3-6     | Reserved (Not Connected)  |

| 7       | 117 Volt A.C. Monitor     |

| 8       | Reserved IF Analog Signal |

| 9       | +5 Volt Supply Monitor    |

| 10      | -5 Volt Supply Monitor    |

| 11      | +15 Volt Supply Monitor   |

| 12      | -15 Volt Supply Monitor   |

| 13      | +12 Volt Supply Monitor   |

| 14      | -12 Volt Supply Monitor   |

| 15      | +28 Volt Supply Monitor   |

|         |                           |

+5 volts unipolar level, and 4 to 20 milliampere current loop.

- o 12 bit resolution.

- o Accuracy of at least 0.17% of full scale voltage range.

- o Output slew rate of 0.1 volt per microsecond

minimum.

- o 5 KHz single channel and 800 Hz eight channel

through put rates.

o Voltage mode current output +/- 5 milliamperes

maximum.

This board provides analog output for APS motor control functions. All outputs are reserved for use by the APS and future modification or expansion. For details on the operation and use of the iSBX-328 consult the hardware reference manual [13]. This project did not use any outputs from the 328.

## Random Access Memory

Chrislin Industries' CI-8080 64K Dynamic Random Access Memory (RAM) board is used to provide the RDADS processor with additional program and data storage space. This board contains 64K bytes of RAM and is Multibus compatible. Due to on-board memory of the iSBC-80/24 the processor can address only 44K bytes of the CI board. The remaining 20K bytes can be used by other boards (added in the future) that are connected to the Multibus. Table 9 gives a breakdown of the 80/24's address space in terms of on-board memory and memory on the CI-8080.

TABLE 9

Memory Map for the RDADS iSBC-80/24 Processor

| Address Range | Location | Storage Function       |

|---------------|----------|------------------------|

| 0 - 3FFF      | 80/24    | Constant Program       |

| 4000 - EFFF   | CI-8080  | Dynamic Program & Data |

| F000 - FFFF   | 80/24    | Program Variables      |

RDADS Chassis and Power Supply

The Multibus boards discussed above where installed in a card cage chassis. Electronic Solution's ESBC-604G was used for this purpose. The 604 is a four slot card cage with a Multibus backplane. It allows connection of a power supply directly to the bus backplane for power distribution to all cards installed in the chassis. Use of the four slots in the ESBC-604G was as follows:

> Slot 1 - iSBC-80/24 Computer with two iSBX Multimodule boards mounted on it.

Slot 3 - CI-8080 64K RAM board.

Slot 4 - Available for future use.

Note that there is an extra slot available for future needs. The 604 also has an expansion connector on the bus backplane that allows an expansion card cage to be mounted directly to the 604.

Power is supplied to the card cage by Power One's CP-291A computer grade D.C. power supply. The 291 supplies all power needed by the 80/24, the Multimodule boards, and the CI-8080. Power from the 291 is also used by other subsystems of the RDADS. This supply outputs +/-5 volts and +/-12 volts. Three additional power supplies are used to provide +/-15 volts and +28 volts to the RDADS. Lambda's LUS-10-15 switching power supply is used for a +15 volt power source. Power One's HA15-0.5 D.C. power supply provides -15 volts. And Electrostatic's Model 30-28 supplies +28 volts to the RDADS.

Figure 8 presents the component breakdown of the RDADS Computer. The figure shows how the components interconnect to each other and to other parts of the RDADS and RPS subsystems. The sections above have described the components of the RDADS computer. The next part of this section will present the IF Controller design.

## IF Controller

A special function board was designed and developed by this project for controlling the radar range gating in the IF section of the RPS. The IF Controller (IFC) is a high speed (60 MHz) digital circuit with many programmable features. The IFC inherently controls the radar transmission and receiver data acquisition in the IF section. In addition the board provides the RDADS processor with expanded I/O capability in the IF section.

The IFC circuit board can be broken down into the following major subdivisions:

- o Processor I/O Interface

- o Timing Network

- o Cycle Control

- o Programmable Transmit Pulse Generator

- o Fixed Delay Generator

- o Programmable Range Delay Generator

- o Programmable Gate Pulse Generator

- o Digital Attenuator I/O Interface

- o Band Multiplexer Control Interface

Each of these IFC sub-circuits will be discussed in the next sections.

Figure 8. RDADS Computer Block Diagram.

## Processor I/O Interface

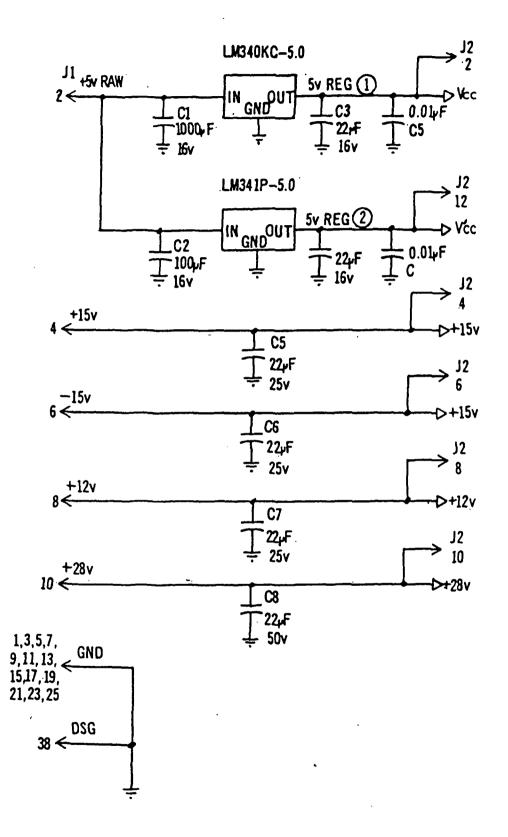

As noted in the section on the RDADS processor's parallel I/O, Ports E4 and E6 are used for communicating with the IFC. Port E4 is used as a bidirectional bus port for data I/O to and from the IFC. Before the processor can perform an I/O operation through Port E4, it must first program the port for either input or output operation, whichever is appropriate. Port E6 is used to control the I/O operations to the IFC. Three bits of port E6 are used to select between different register pairs on the IFC board. Another bit is used to tell the IFC whether the processor is doing input or output. Two other bits are used to enable IFC output or strobe IFC data latching. Of the remaining two bits, one is used as a master reset output by the processor to the IFC and the other is reserved for future needs. Table 10 presents the IFC/Processor Interface parallel I/O assignments.

The names listed under "Signal" in Table 10 are the formal signal names used in the circuit diagrams. Processor communication to the IFC is either to a data latch or from a tri-state buffer. Latches and buffers are arranged as register pairs on the IFC and each pair is referred to as a channel. There is a total of 6 channels used in the circuit. The three select lines are used to choose one of the 6 channels. The IOC signal is used to select either the latch or buffer of the selected channel. These four signals combined are input into a 74154 4-to-16 Decoder I.C. on the IFC board. Six of the outputs of the 74154 are used as strobe signals to the six latches. Six others are used as output enable (OE) signals to the six tristate buffers. The remaining four outputs are not used. The PS/E and SS/E signals are

| TA | BL | E | 1 | 0 |

|----|----|---|---|---|

|    |    | - | _ | - |

!

Processor Port Assignments for IFC Interface

| Port | Bit | IFC Function            | Si gna l |

|------|-----|-------------------------|----------|

| E4   | 0   | Data I/O - Bit O        | DO       |

| E4   | 1   | Data I/O - Bit 1        | D1       |

| Ε4   | 2   | Data I/O - Bit 2        | D2       |

| E4   | 3   | Data I/O - Bit 3        | D3       |

| E4   | 4   | Data I/O - Bit 4        | D4       |

| E4   | 5   | Data I/O - Bit 5        | D5       |

| E4   | 6   | Data I/O - Bit 6        | D6       |

| E4   | 7   | Data I/O - Bit 7        | D7       |

| E6   | 0   | Data I/O Control        | 10C      |

| E6   | 1   | Channel Select - Bit 1  | SEL1     |

| E6   | 2   | Channel Select - Bit 2  | SEL2     |

| E6   | 3   | Channel Select - Bit 3  | SEL3     |

| E6   | 4   | Reserved Control Bit    | n.a.     |

| E6   | 5   | Reset Signal            | RST      |

| E6   | 6   | Secondary Strobe/Enable | SS/E     |

| E6   | 7   | Primary Strobe/Enable   | PS/E     |

|      |     |                         |          |

÷

applied to the G1 and G2 enable inputs of the 74154. The outputs of the 74154 are all high until the device is enabled by the PS/E and SS/E signals. When enabled the selected output goes low to strobe or enable the proper device. With this configuration the IFC registers all share a common data bus connection to the processor through Port E4. Figure 9 details the I/O interface for the IFC. The assigned select addresses for each IFC channel are given in Table 11.

Channel 2 was used for general control in the IFC. Control information written to Latch 2 is used by various other parts of the IFC circuit. The outputs of this latch are also tied to the inputs of the tristate buffer it is paired with. The processor can read the contents of the latch through the buffer. Output bits from the latch are listed in Table 12 along with their assigned signal name. These signals are explained in the discussion on the sub-circuit identified in this table.

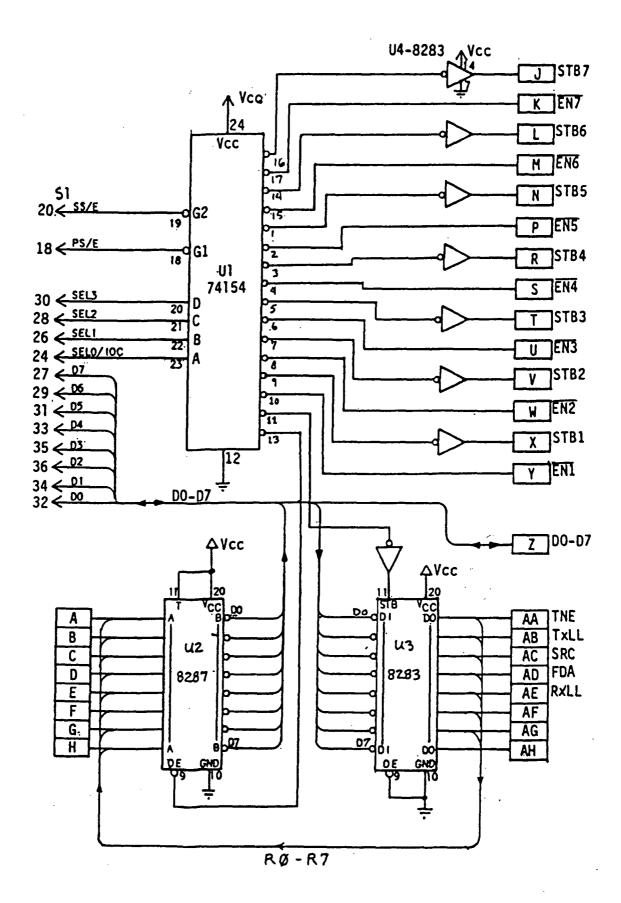

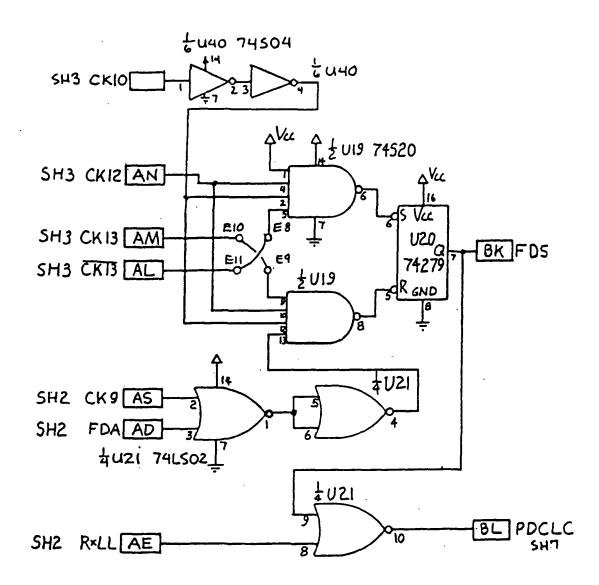

## Timing Network

To provide synchronous operation with the other parts of the IF section, the IFC's clock signal is derived from the 60 MHz IF oscillator. The oscillator's output is brought on-board the IFC through an SMA connector. This signal is applied to a Schmitt Trigger Inverter to provide a clock signal of sufficient amplitude to the rest of the board. This signal is buffered once again to provide a clock signal of opposite phase. For lower frequency timing functions on the IFC, the buffered 60 MHz clock is sent through a set of cascaded 74S196 Divide-by-10 Counters. Three 74S196's are used to give a total clock

# Figure 9. Processor I/O Interface on the IFC.

# TABLE 11

IFC Channel Assignments

| Channel | Register Selected  |

|---------|--------------------|

| 0-1     | Not used.          |

| 2       | General Control    |

| 3       | Transmit Pulse     |

| 4       | Range Delay        |

| 5       | Gate Width         |

| 6       | Digital Attenuator |

| 7       | Multiplexer        |

|         |                    |

.

TABLE 12

IFC Control Channel (2) Signals

| Bit | Signal | Sub-circuit    |

|-----|--------|----------------|

| 0   | TNE    | Timing Network |

| 1   | TxLL   | Cycle Control  |

| 2   | SRC    | Cycle Control  |

| 3   | FDA    | Fixed Delay    |

| 4   | RxLL   | Fixed Delay    |

| 5-7 |        | Not Used       |

|     |        |                |

frequency division of 1000. Each counter in the timing network has four outputs, all at a different frequency.

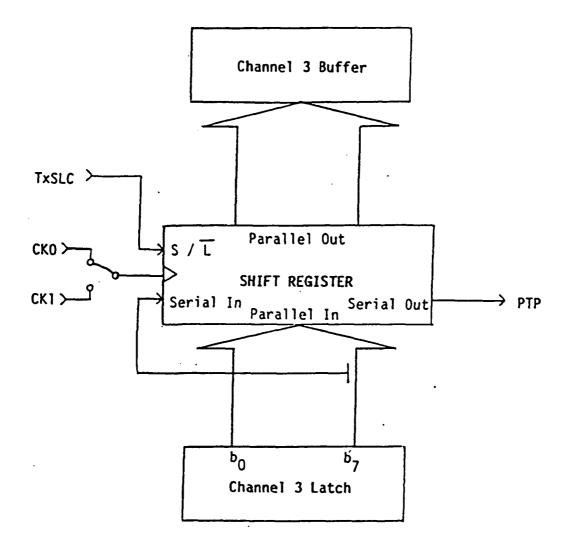

The 60 MHz buffered clock was labeled CKO and the twelve outputs from the Divide-by-1000 counter were labeled CK1 through CK12 (CK1 = 30 MHz and CK12 = 60 KHz). A two phase 30 KHz signal (CK13) was produced by clocking a toggle Flip/Flop (F/F) with the 60 KHz CK12 signal. Figure 10 shows the timing network of the IFC. Note that CK1, CK9, CK10, and CK12 are the only clock signals output by the Divide-by-1000 counters that are used. Figure 10 also shows the introduction of the Reset (RST) signal into the IFC. This signal is buffered to provide reset signals to the timing network and other parts of the circuit. The Timing Network Enable (TNE) from the control latch, must be high for the circuit to operate.

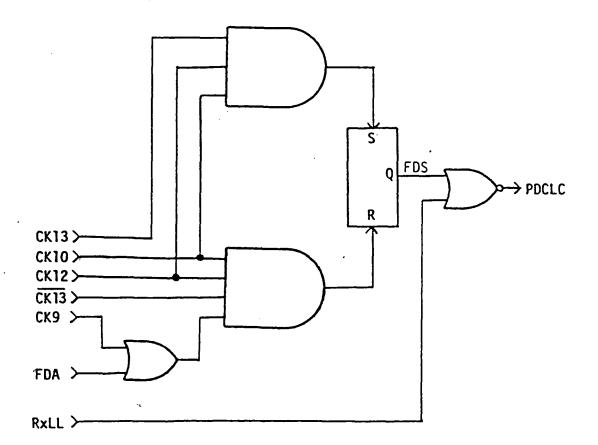

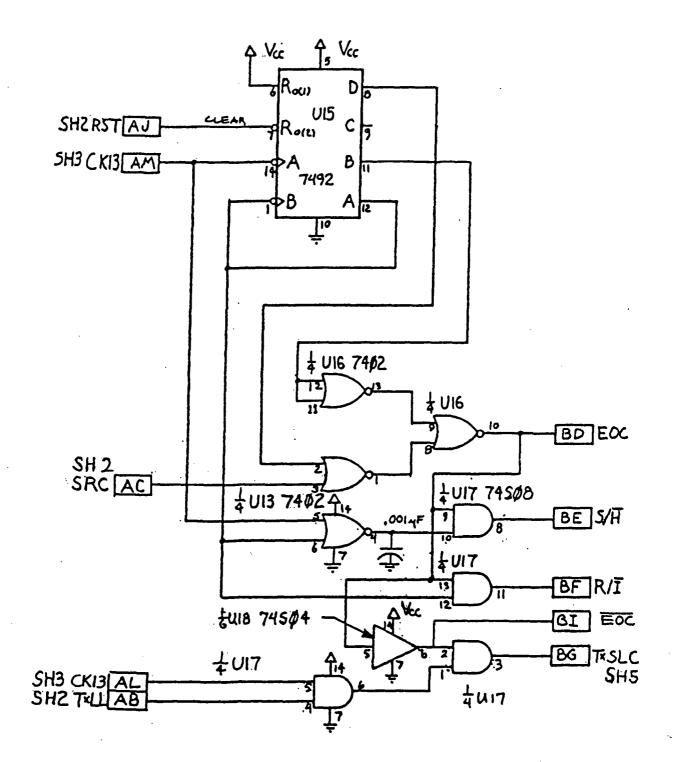

Cycle Control

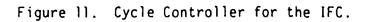

To control the cycling operations performed by other parts of the IFC, a Cycle Control circuit was designed. This circuit is presented in Figure 11. This circuit performs the following functions period-ically:

- o Tell the Transmit Pulse Generator when to load and when to run (TxSLC).

- o Provide a service request interrupt signal to the processor (EOC).

- o Tell the Analog Sample and Hold device when to sample and when to hold (S/H).

- o Tell the Analog Integrator when to reset and when to integrate (R/I).

•

The circuit uses the bi-phase clock signal CK13 as a base clock for its operation. The divide-by-twelve counter is used to generate an overall cycle timing function for the IFC.

The cycle control circuit sends pulses to the Transmit Pulse Generator at the rate of CK13 or 30 KHz. The integrator will normally integrate ten radar return pulses to obtain each analog output data value. The circuit allows the processor to select either ten or four integration cycles per datum with the SRC, Sample Rate Control, signal. SRC originates from the general control register (Channel 2). The four integration cycle selection could prove useful if return signals are too large and saturate the integrator when ten cycles are used. In addition to these integrator cycles, two more cycles of CK13 are used for sampling the integrator output and resetting the integrator. When SRC is low, selecting ten integrator cycles (12 overall), the IFC's overall cycle rate is 2.5 KHz which corresponds to an analog sample available every 0.4 mS. SRC high selects four cycles (6 overall) for a cycle rate of 5 KHz or a 0.2 mS cycle time.

Figure 11 also presents a timing diagram for the cycle controller. Note that during integrator sampling and reset operations, the Transmit Shift Load Control (TxSLC) is inhibited to prevent radar output. TxSLC also may be inhibited by a low level on Transmit Load Lock (TxLL). TxLL is another signal from the general control register. The inverse of the End of Cycle (EOC) signal is used to enable the range gating function of the IFC. This way, range gating is inhibited during the integrator sampling and reset operations. The timing diagram also shows that the Sample/Hold control signal (S/H)

precedes the Integrator Reset Signal, (R/I), by half a cycle of CK13 or 16 microseconds. This gives the Sample and Hold device time to enter the HOLD mode. Note from the timing diagram that the number of integration cycles is unspecified for the first IFC cycle after a board reset (RST). The first EOC interrupting the processor after a reset should therefore be ignored. All cycles after the first are valid.

# Programmable Transmit Pulse Generator

The IF transmitter requires a signal from the IFC to tell it when to transmit a radar pulse and for how long. The Transmit Pulse Generator does just that. Figure 12 is a block representation of the generator circuit. The 8-bit shift register in the circuit is parallel loaded with a pattern obtained from the latch of IFC Channel 3. The pattern is shifted out of the register serially to produce the transmit pulse. The shift register can be clocked at either 60 MHz or 30 MHz depending on which clock signal is jumper selected, CKO or CK1. Normal configuration is 60 MHz. The circuit is told when to load and when to shift by the TxSLC (Transmit Shift Load Control) signal output by the Cycle Controller. The register is loaded when TxSLC is low and begins to shift after the rising edge.

The processor must load the Channel 3 latch with the proper pattern for the circuit to operate. By using a programmable shift register the generated transmit pulse can be adjusted to accommodate switching characteristics of the mixer used to produce the 60 MHz radar pulse. The processor has the ability to read the contents of the shift register through the buffer of Channel 3. The shift register can

Figure 12. IFC Programmable Transmit Pulse Generator.

be read "on the fly" or if TxLL is low the loaded value can be read and confirmed. TxLL is set low through the general control latch (Channel 2).

Fixed Delay Generator

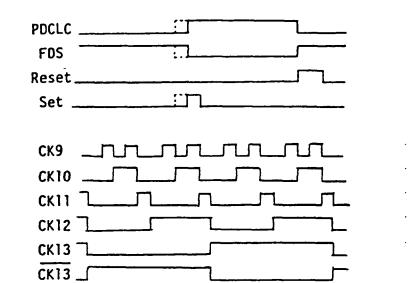

After generation of a transmit pulse, the IFC must wait a fixed amount of time corresponding to the minimal delay before the radar signal is returned to the input of the integrator. The Fixed Delay Generator accomplishes this function. The CK9, CK10, CK12 and CK13 clock signals are combined to produce this fixed delay output signal, FDS. Figure 13 shows the Fixed Delay Generator circuit and the timing of its output with respect to TxSLC.

The FDS signal is "OR"ed with Receiver Load Lock (RxLL) to produce the output signal Programmable Delay Count Load Control (PDCLC). PDCLC is applied to the next stage of the IFC, the Programmable Range Delay Generator. RxLL is one of the general control bits from IFC Channel This gives the processor a way of stopping the action of 2's latch. the next two stages of the IFC (Range Delay and Gate Pulse generation). The Fixed Delay Adjust signal (FDA) also originates from the control latch. This gives the processor a way of adjusting the fixed delay that is generated by the circuit. When FDA is low CK9 is included in the generator circuit and the fixed delay is approximately 13 microseconds. If FDA is high CK9 is ignored and the generated delay is approximately 11 microseconds. Note also that the two biphase CK13 clock signals can be switched by jumper selection to choose whether the falling or rising edge of CK13 starts the fixed delay. Fine

Figure 13. IFC Fixed Delay Generator.

adjustments are handled by the programmable feature of the Range Delay Generator.

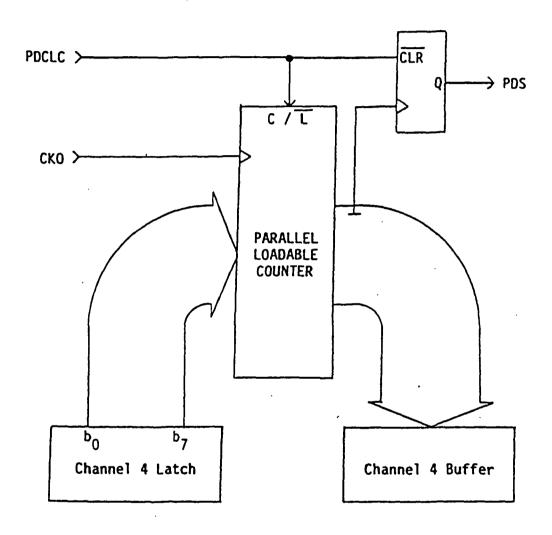

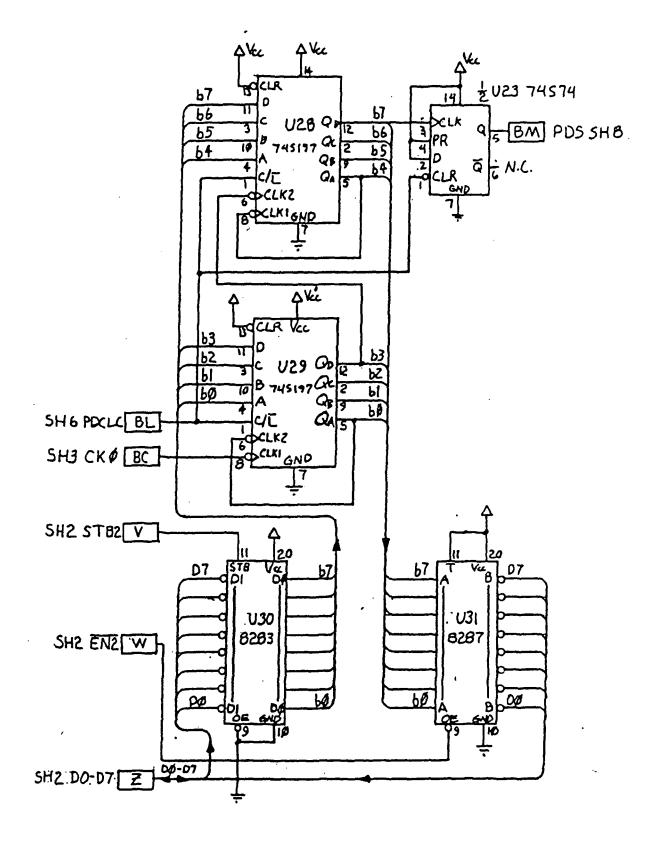

Programmable Range Delay Generator

Operation of the radar system at varying elevation angles has two effects on the radar return signal in terms of range gating. The return signal delay varies with changes in distance to the target due to the electromagnetic waves propagation time. In addition, the width of the return radar pulse varies due to changes in the incidence angle of the wave on the target. The signal is spread through time as the target scene area increases. To accommodate for such changes and still provide a good noise rejection to the receiver, the range gate signal must be as narrow as possible and must occur at the proper time to "catch" all of the return signal. The Programmable Range Delay and Gate Pulse Generators allow the proccessor to adjust the range gating function for such changes.

The range delay generator is shown in Figure 14. This circuit uses a programmable counter that is loaded from the output by the latch of IFC Channel 4. The counter is clocked by CKO at 60 MHz. The F/F in the circuit catches the rising edge of the most significant bit out of the counter. The output of this F/F is the generated delay signal, PDS. By writing the proper value out to Channel 4 of the IFC, the processor can adjust the range delay that is generated. The generator's operation cycle is based on the signal provided by the Fixed Delay Generator, PDCLC (Prog. Delay Count Load Control). When PDCLC is low the counter is loaded and the F/F is cleared. After the rising

Figure 14. Progammable Range Delay Generator.

edge of PDCLC, the counter begins operation marking the start of the programmed delay. Note that the output of the counters can be read by the processor through the buffer of Channel 4. As with the Tx. Pulse Generator, the read is either "on the fly" or if RxLL is high the loaded value is read.

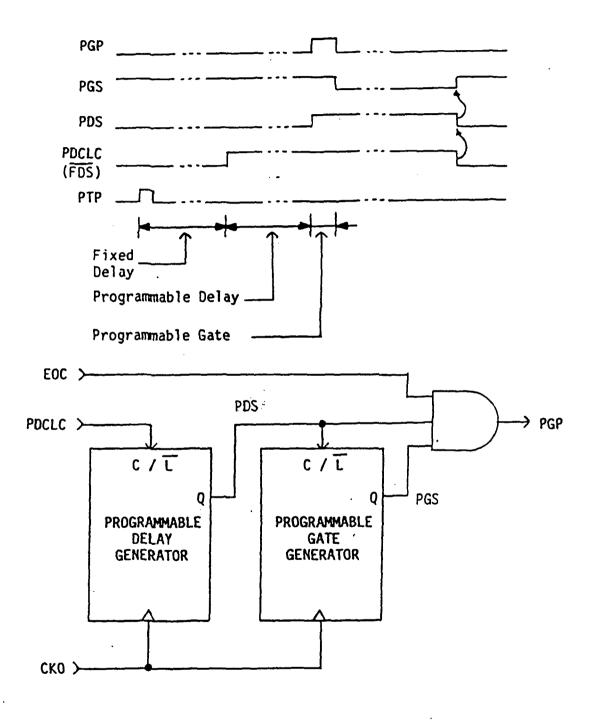

# Programmable Gate Pulse Generator

The Programmable Gate Pulse Generator function is produced using the same circuit used for range delay. The only difference is that the circuit's function is controlled by PDS rather than PDCLC. PDS acts as the count load signal for the gate pulse generator. The rising edge of the Programmable Gate Signal (PGS) that is produced actually marks the end of the gate pulse. The rising edge of PDS marks the start of the gate pulse. By ANDing the PDS signal with the inverse of the PGS signal, the desired Programmable Gate Pulse signal, PGP, is generated. This signal is ANDed with EOC and inverted to produce the actual signal used to control the integrator gating circuit. Including EOC in the signal inhibits range gating while the integrator is being sampled and reset. Figure 15 presents the combined Range Delay and Gate Generator circuits and a timing diagram that illustrates how the circuits produce the gate pulse. The gate width is programmed and checked through IFC Channel 5. For reading the loaded value of the Gate Generator, the RxLL signal should be high.

Figure 15. Programmable Gate Pulse Generator.

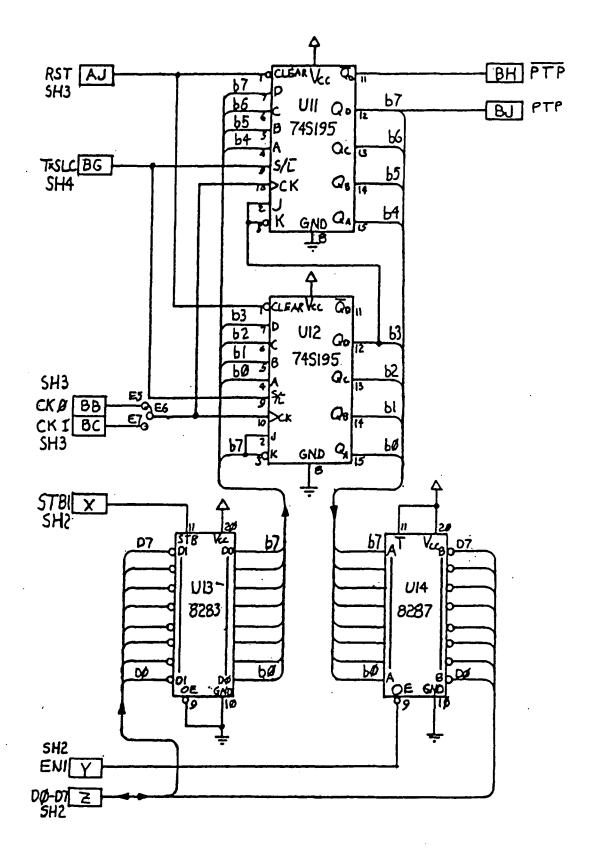

I/O Expansion in the IFC

The processor interface scheme used in the IFC provided an easy way to expand the processor's I/O capability in the IF section. Two additional IFC Channels are used to accomplish this expansion. Channel 6 is used for controlling the Digital Attenuator in the IF receiver. The output of Channel 6's latch is returned through the buffer of that channel to allow the processor a method of checking the attenuator's setting. Channel 7 is used to control and monitor the RF Head Multiplexer in the IF section. Switches identical to those used in the RF polarization control are used for the multiplexing function in the IF section. Monitoring of the multiplexer switches is accomplished the same way that monitoring of RF polarization switches was done.

A complete set of detailed circuit diagrams for the IF Controller circuit board can be found in Appendix A. The IFC was first prototype on a special Schottky TTL wire wrap board. Once made operational, the final circuit was produced in the form of a printed circuit board. A print of the circuit layout can also be found in Appendix A along with a component placement diagram.

When combined, the RDADS Processor and the IF Controller provided all the hardware needed to control and operate the RPS. Since most of the hardware functions are under software control, the operation of the RPS can easily be adjusted or modified. The next section presents the software developed for the RDADS.

#### SOFTWARE

RDADS hardware was selected and designed to permit flexibility in the system's implementation. This flexibility was achieved through a microprocessor based system design. The polarimeter's functional operation was defined primarily through the microprocessor software. This section presents the design and development of the RDADS software.

The RDADS is a complex processing system that performs a number of functions during operation. The software design problem had to be divided into smaller problems and organized for development. A structured programming approach was taken for the design and development of RDADS software. This section will begin by briefly presenting the programming techniques that were chosen and how they fulfill the project requirements. Emphasis and elaboration will follow in a discussion of the actual software.

## Structured Programming

Appearance of a computer program, its readability, comprehensibility, and "style", is the principal aspect of "structured programming" [14]. Structured programs are readable, easily understood, and well organized. Modular programming and limitation of program constructs are two important concepts used in developing programs that are structured.

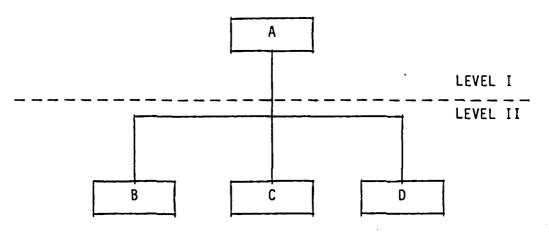

Modular Programming

Modular design and implementation breaks the programming problem down into levels and blocks. Levels refer to hierarchical divisions within an installation. At each level the entire installation can be divided into blocks with independent characteristics. Blocks and their hierarchical levels are commonly illustrated by block structure diagrams. An example of a structure diagram is shown in Figure 16. Here the entire problem is represented by Block A at Level I and is broken down into Blocks B, C, and D at Level II. The problem breakdown can be carried through as many levels as required. This modular breakdown allows the problem and solution to be viewed in terms of simpler components and in an organized fashion.

Figure 16. Simple Block Structure Diagram.

## Limited Constructs

A second requirement for structured programming is the concept of limiting the number of basic program constructs [14, 15, 16, 17]. A program construct can be defined as a structure element or pattern used to express logic in a program. There are three basic constructs necessary to fulfill all programming requirements. These basic constructs, referred to as sequence, selection, and iteration, can be combined in any fashion to accomplish any logical task [18].

The construct of sequence is a succession of selection structures, iteration structures, and individual process steps. To express sequence, statements are written one after the other, as follows:

Input X and Y

Add X and Y

### Output result

Selection is a construct in which a process is broken into options. The execution of these options is dependent on a specified condition. To illustrate selection, terms like IF, THEN, and ELSE are commonly used, as in:

IF X > Y THEN MAXVAL is X

## ELSE MAXVAL is Y

Repetition of a process is accomplished using the third construct, iteration. A DO loop is the common example of iteration such as:

DO I from 1 to 10 Add X(I) to SUM End DO

With these basic programming patterns any logical process can be implemented. Processes more complex than those illustrated above are effected by combining these basic constructs.

Development Support

Both of the above conceptual components are fundamental to the

structured programming philosophy. Many available software development and programming languages directly support the design and tools implementation of structured programs through the use of these Programming languages usually provide a means of directly concepts. implementing the three basic constructs required. This allows the design portion of the development process to be virtually language independent. A software design can be entirely depicted in pseudo-code which is an informal method of expressing the steps of a process in terms of the basic constructs. Since these constructs are supported directly in most languages, the implementation phase is accomplished through simple conversion of pseudo-code to actual source code. A programming language can be chosen at the time of implementation without affecting the logical design of the program.

Modularity is promoted not only in languages but also by support tools such as program library facilities, module linkers, and predeveloped modular process utilities. Most all languages directly support modularity by providing for some type of subprogram, function, or procedure implementation. Once developed, program modules can be stored as individual units or as part of a library of modules. An entire software installation is obtained by combining individual modules together through the use of an object linker. The linker also provides the function of "looking-up" and extracting needed modules from libraries. Commercially available process utilities can be also linked with user modules to provide the complete system installation. These and other software design tools and products support and simplify the development of structured programs.

#### Software Design

In this section a statement of the software problem will be given. Some of the specific requirements on the software installation will be itemized. This will be followed by a general description of the design approach taken. Refinement of the design problem and descriptions of solution implementations will be given later in this section.

Problem Statement

RDADS software was required to perform three basic functions. These were:

o Communicate with the main computer in the data van,

o Control radar operation and data acquisition,

. o Position the RPS antennas.

The first two functions are explained here. Antenna positioning software was developed external to this project.

Radar Control and Data Acquisition

Radar operations can be divided into three categories. Two of these are the microwave transceiver control operations and the IF section control operations. The third is the acquisition of data from the radar.

Transceiver operation is controlled with RF switches. There are three RF switches under computer control in each microwave transceiver. These are the CAL/OP switch and the transmit and receive

polarization transfer switches. All microwave switches are controlled and monitored through parallel I/O operations from the processor.

IF section operations include setting and checking the control and parametric registers of the IF Controller. IF Controller registers include a general control/status register, a transmit pulse register, the range and gate width registers, a digital attenuator register, and a transceiver multiplexer register. IFC communications are also performed through parallel I/O by the processor.

Radar data acquisition is accomplished primarily through conversion of the analog signal output by the IF section. The IF Controller board signals the computer when the analog signal is ready for conversion. The computer then converts the analog signal to a digital count. It can determine from this measurement if the Digital Attenuator should be adjusted. Control of the attenuator is performed automatically by the processor to implement a Digital Automatic Gain Control (DAGC) function for the receiver.

**RDADS** Communication

Operation of the RDADS is normally controlled by the data van CPU. The RDADS can also be controlled directly by the user. RDADS communication was designed to allow for two different operational set-ups. The first is the normal set-up of communicating with the data van in a remote fashion. The second is a local set-up using a console terminal in place of the data van CPU. Using a terminal to communicate with the RDADS allows the system to operate in a stand alone configuration instead of being a slave device to the main CPU. This local set-up was

devised to provide for testing, maintenance, and calibration. Communication software was designed not only for the basic operational requirements, but also for flexibility and utility in testing and maintaining the RPS.

### Design Approach

The approach to the design of the software installation was to develop an operating system that allowed interactive control of predefined functions. Interaction was to be either directly through a console terminal or indirectly through the data van CPU. A general command list was defined that would provide for all the required operations. Each command task was broken down into steps needed in accomplishing the overall function. By breaking each level of tasks down into a subordinate level, the actual operational requirements of each task were divided into simpler components. This breakdown continued until the sub-divisions of a task reached a point where they could be implemented easily.

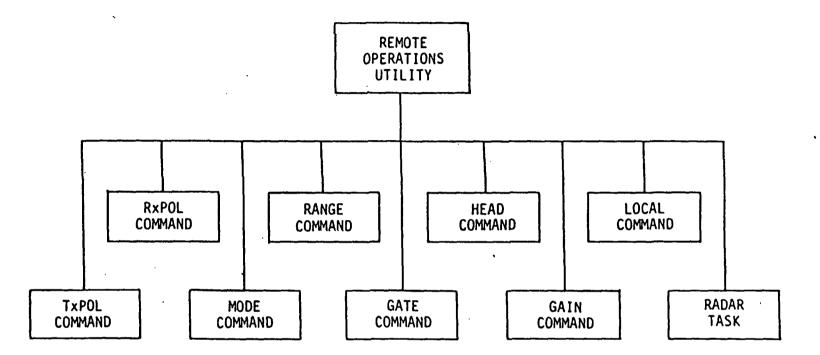

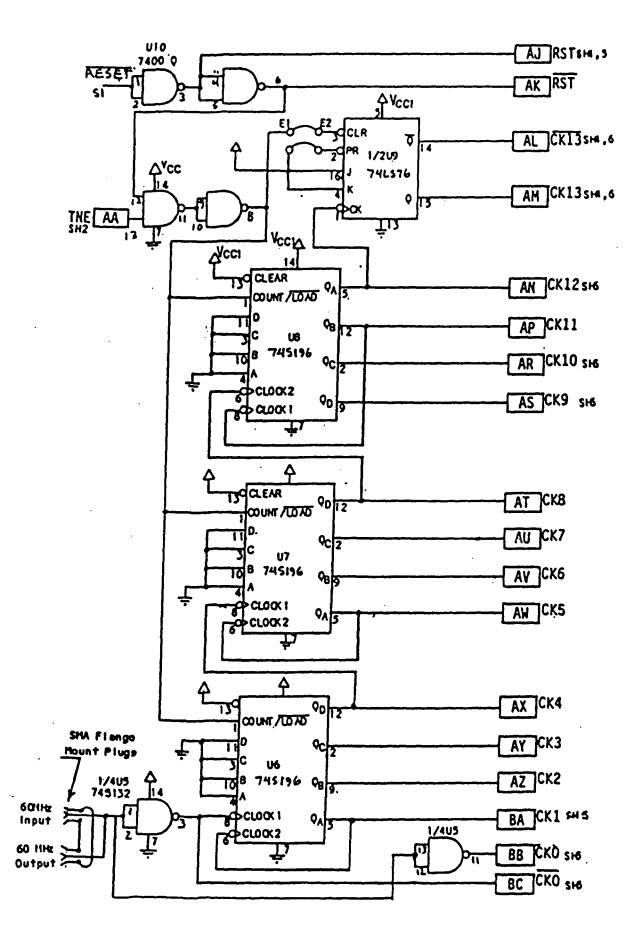

The operating system for the RDADS is called the Remote Operations Utility (ROU). Figure 17 presents a task structure diagram of the ROU. Each task performs a command function except for the Radar Task which is a free running task used to acquire the radar measurement data. Each of the command tasks will be presented here by describing the format of the command entries and the actions they perform. This will be followed by a discussion of the radar task's logical operation.

•

.

.

.

ï

#### **ROU Commands**

The following rules apply to all the descriptions of the Remote Operations Utility commands:

- 1. Keywords are shown in upper case and must be entered as Any abbreviation of the keyword is acceptable but shown. should contain at least enough characters to distinguish it from any other keyword used in the command. Command keywords may be abbreviated but also must contain enough characters to distinguish them from other commands. Failure to do this may cause unwanted results. Ambiguity among keyword entries is resolved by order of appearance in the format description. Ambiguity among command keywords is resolved by order of appearance in the command table. Abbreviations are formed by entering the first characters of a keyword in the same order that they appear in the keyword. Any number of characters is acceptable as long as no intermediate characters are omitted.

- 2. Command keywords are always the first keyword in a command format. Everything that follows the command keyword is referred to as the command tail. The command keyword and its command tail constitute a command string or command entry.

- All keywords, symbols, and variable entries must be separated from other keywords, symbols, and variable entries with one or more spaces.

- 4. Braces, " { } " group alternatives in which one and only one alternative must be chosen.

- Parenthesis, "() " group alternatives in which one or more must be chosen. At least one alternative must be chosen but two or more can be used.

- 6. Brackets, "[] " group options which may be omitted entirely. Underlined options are assumed if all options of the group are omitted.

- 7. The "or" symbol, " " separates command options or alternatives.

- 8. Braces, parenthesis, brackets, and the "or" symbol are used to identify options or alternatives only and are not intended to be entered as part of the command string during operation.