### **General Disclaimer**

### One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

# ELECTRON LITHOGRAPHY STAR DESIGN GUIDELINES

PART III of IV: The Mosaic Transistor Array

**Applied to Custom Microprocessors**

PART IV of IV: Stored Logic Arrays - SLAs

Implemented with Clocked CMOS

(NASA-CR-170767) ELECTRON LITHOGRAPHY STAR DESIGN GUIDELINES. PART 3: THE MOSAIC

TRANSISTOR ARRAY AFFLIED TO CUSTOM MICROPROCESSORS. PART 4: STORES LOGIC

(Mississippi State Univ., Mississippi

NE5-31842

Unclas G3/60 16022

ENGINEERING & INDUSTRIAL RESEARCH STATION

**ELECTRICAL ENGINEERING**

FINAL REPORT - PARTS III & IV

Submitted to:

National Aeronautics and Space Administration George C. Marshall Space Flight Center

Principal Ivestigator

Date of general release 1 hay, 1985

SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered)

| REPORT DOCUMENTATION                                                                                        | READ INSTRUCTIONS BEFORE COMPLETING FORM                                 |                                                                |  |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|--|

| MSSU-EIRS-EE-83-4                                                                                           | 2. GOV: ACCESSION NO.                                                    | 3. RECIPIENT'S CATALOG NUMBER                                  |  |

| 6. TITLE (and Subside) Electron Lithography STAR Designant 3: The Mosaic Transistor A                       | 5. TYPE OF REPORT & PERIOD COVERED<br>Final Report<br>Parts 3 and 4 of 4 |                                                                |  |

| to Custom Microprocessor Part 4: Stored Logic Arrays - S                                                    |                                                                          | 6. PERFORMING ORG. REPORT NUMBER                               |  |

| 7. AUTHOR(a)                                                                                                |                                                                          | 8. CONTRACT OR GRANT NUMBER(#)                                 |  |

| J. Donald Trotter, Principal Ir                                                                             | NAS8-33450                                                               |                                                                |  |

| PERFORMING ORGANIZATION NAME AND ADDRESS Mississippi State University Drawer EE Mississippi State, MS 39762 |                                                                          | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |  |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                                                                     |                                                                          | 12. REPORT DATE                                                |  |

| NASA/MSFC                                                                                                   |                                                                          | August 31, 1982                                                |  |

| MSFC, AL 35812                                                                                              | 13. NUMBER OF PAGES                                                      |                                                                |  |

| ATTN: Harley R. Hope AP29-C                                                                                 | 73                                                                       |                                                                |  |

| ONRRR, Georgia Institute of Technology  206 O'Keefe Building                                                |                                                                          | Unclassified                                                   |  |

| Atlanta, GA 39332                                                                                           | ISA. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                            |                                                                |  |

16. DISTRIBUTION STATEMENT (of this Report)

17. DISTRIBUTION STATEMENT (of the abstract entered in Block 20, if different from Report)

18. SUPPLEMENTARY NOTES

OF POOR QUALITY

19. KEY WORDS (Continue on reverse side if necessary and identify by block number)

Part 3: STAR, Semicustom microprocessor, Data path

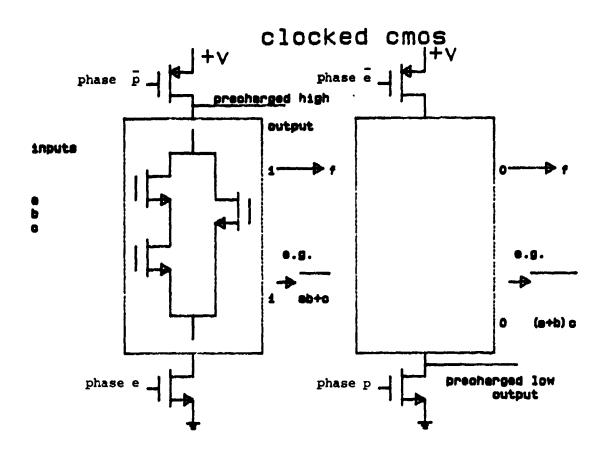

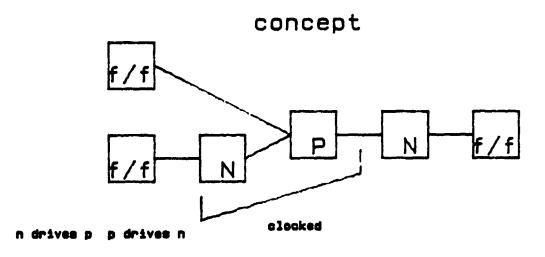

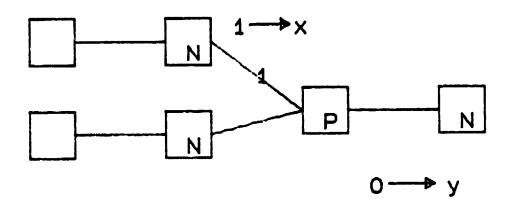

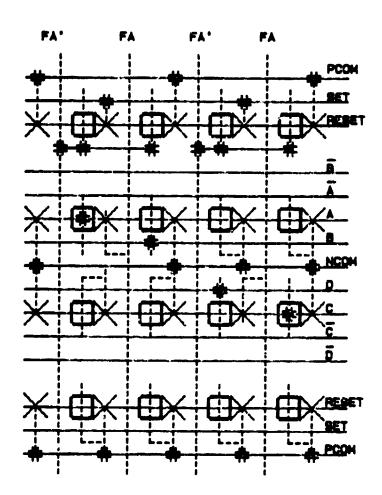

Part 4: Stored Logic Array (SLA), Programmable Logic Array (PLA), Clocked CMOS, STAR, Mosaic Transistor Array (MTA)

20. ABSTRACT (Continue on reverse side if necessary and identify by block number)

Part 3: The Mosaic Transistor Array is an extension of the STAR system developed by NASA which has dedicated field cells designed to be specifically used in semicustom microprocessor applications. The basic logic functions for a data path are designed with compatible interface to the STAR grid system.

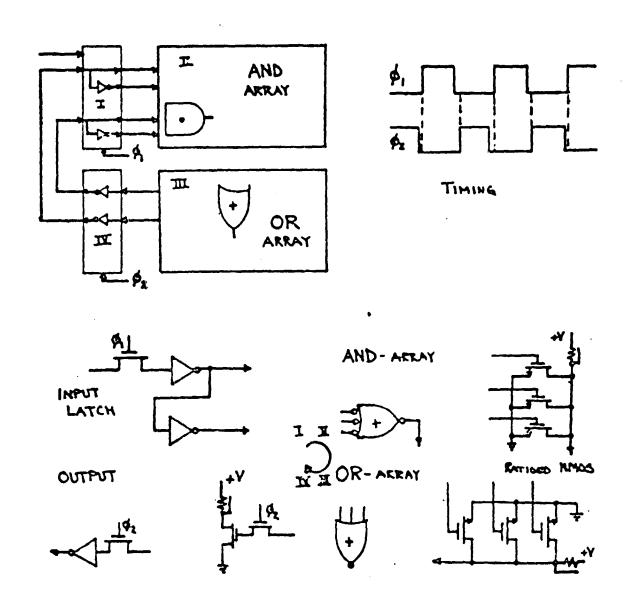

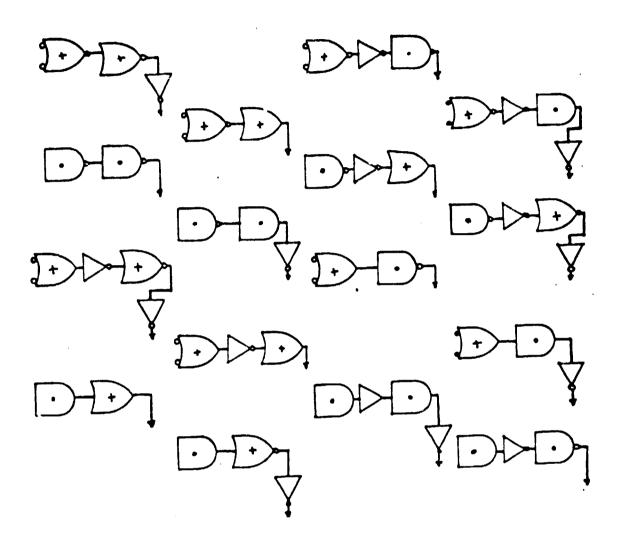

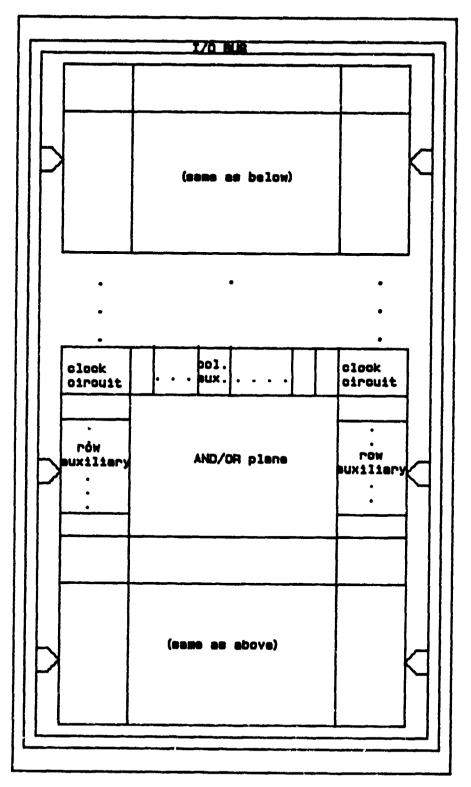

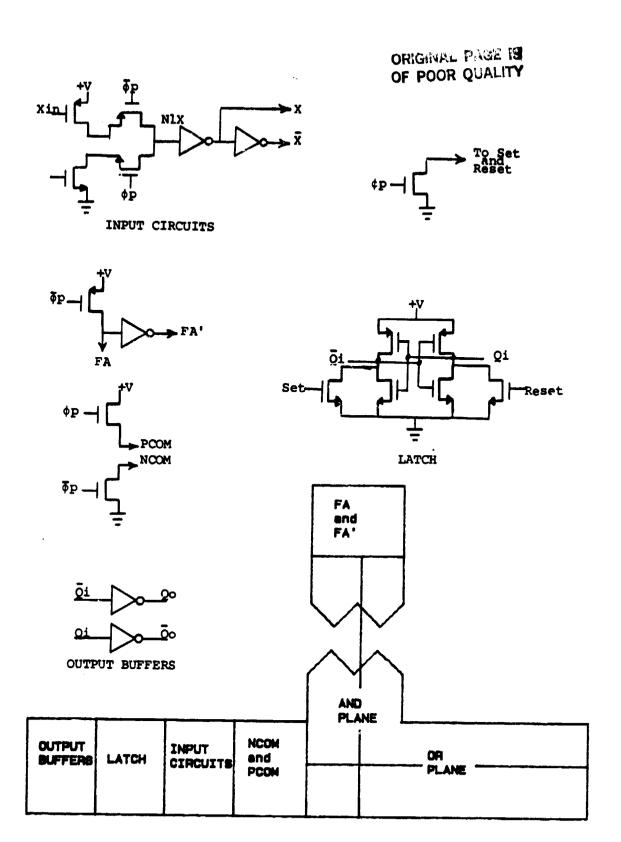

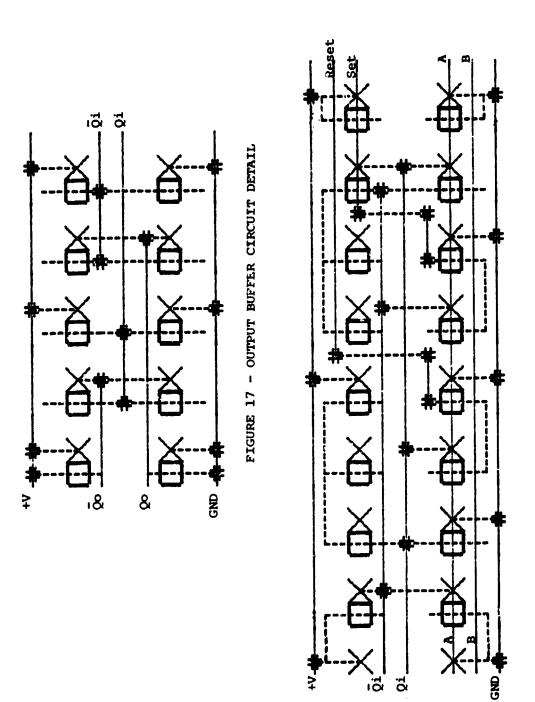

Part 4: Stored logic arrays are folded PLAs with the AND and OR planes merged into one physical space. The structure is shown to be compatible

#### FINAL REPORT

#### CONTRACT NAS8-33450

#### ELECTRON LITHOGRAPHY STAR DESIGN GUIDELINES

Part 3: THE MOSAIC TRANSISTOR ARRAY APPLIED TO CUSTOM

**MICROPROCESSORS**

Part 4: STORED LOGIC ARRAYS - SLAS IMPLEMENTED WITH CLOCKED CMOS

Principal Investigator

J. Donald Trotter

Mississippi State University Department of Electrical Engineering Mississippi State, Mississippi 39762

August 31, 1982

for

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION Marshall Space Flight Center, AL 35812

### ELECTRON LITHOGRAPHY STAR DESIGN GUIDELINES

Part 3: The Mosaic Transistor Array Applied to Custom Microprocessors

Principal Investigator

J. Donald Trotter

# THE MOSAIC TRANSISTOR ARRAY APPLIED TO CUSTOM MICROPROCESSORS

### Outline

| 1.   | Introduction                                    | 1  |

|------|-------------------------------------------------|----|

| 11.  | The Sandia CMOS Process with Double Layer Metal | 3  |

| 111. | The Design Approach                             | 12 |

| IV.  | The Data Path Circuitry                         | 17 |

| ٧.   | Additional Comments                             | 29 |

| Vī   | Appendix                                        | 30 |

### LIST OF FIGURES

| Figure   | 1   | Process Cross-Sections        | 6, |

|----------|-----|-------------------------------|----|

| Figure   | 2 a | CMOS Inverter                 | 14 |

| Figure   | 2 b | Three Types of Switches       | 14 |

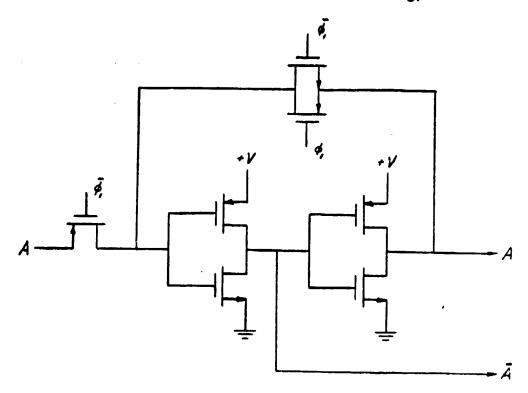

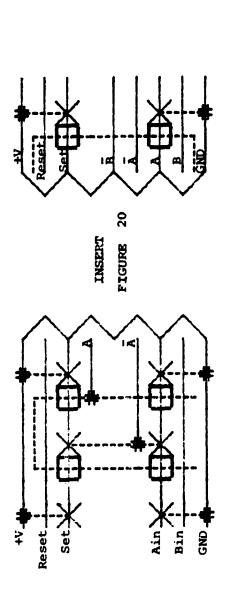

| Figure   | 3   | A CMOS Latch                  | 15 |

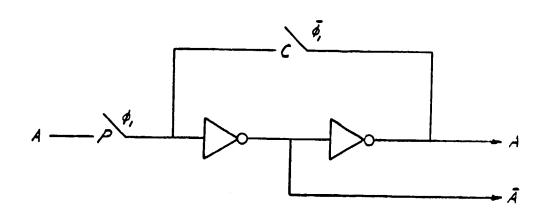

| Figure   | 4   | Block Diagram of Latch        | 16 |

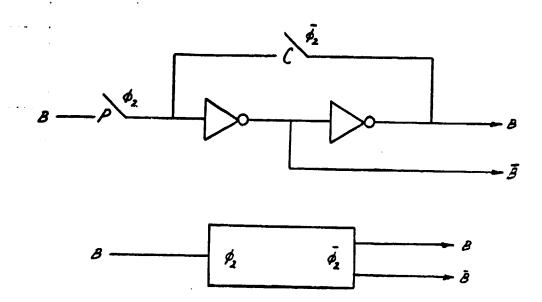

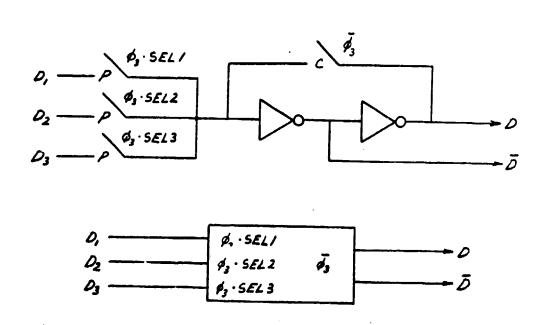

| Figure   | 5   | Latch with Multiple Inputs    | 16 |

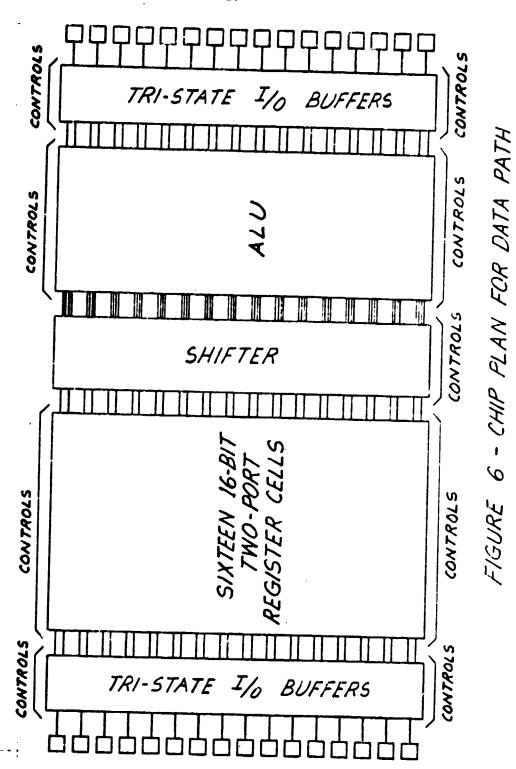

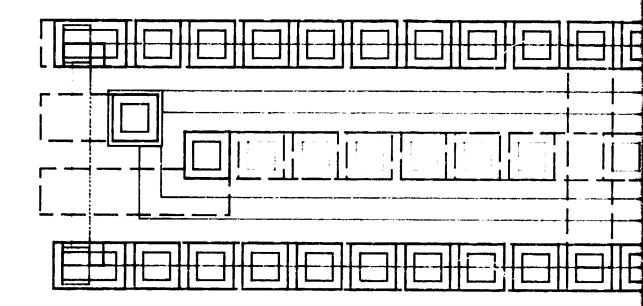

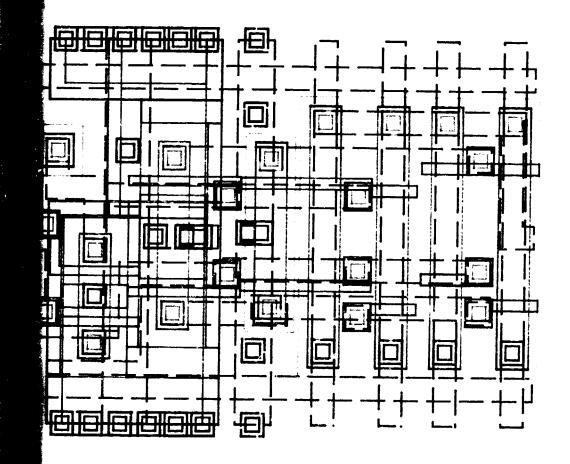

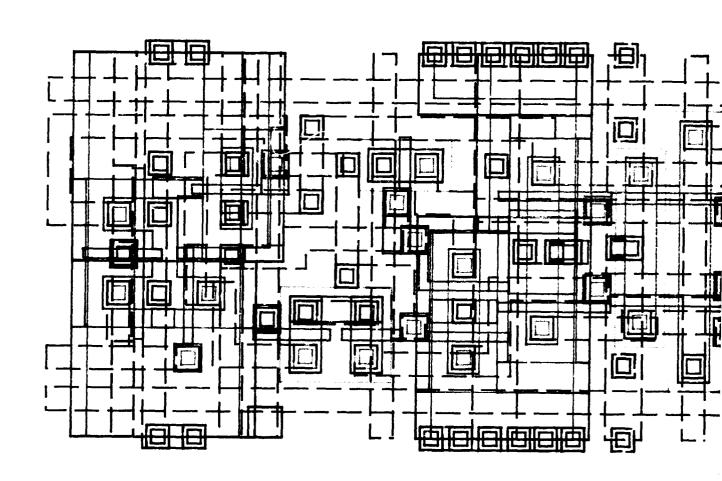

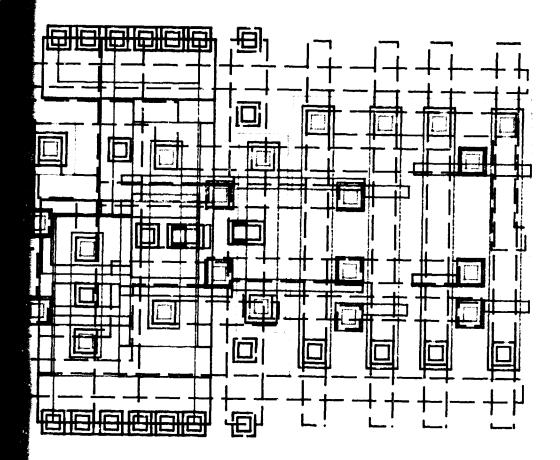

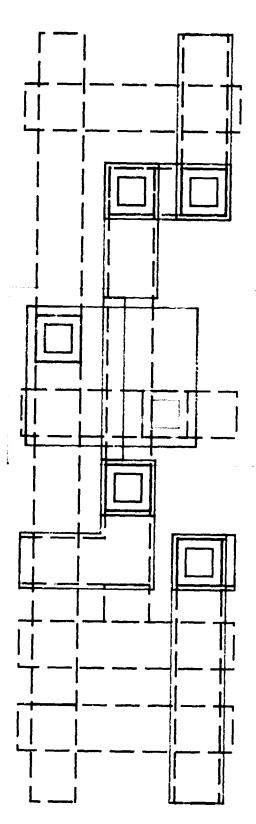

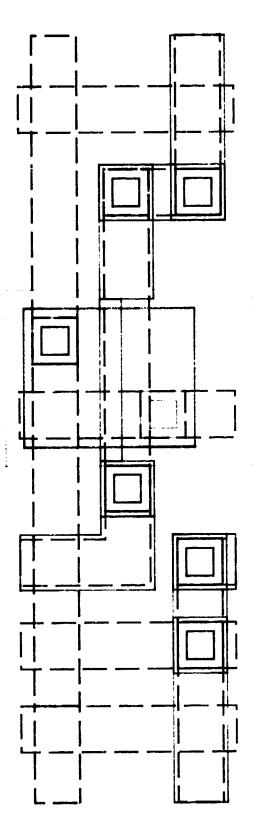

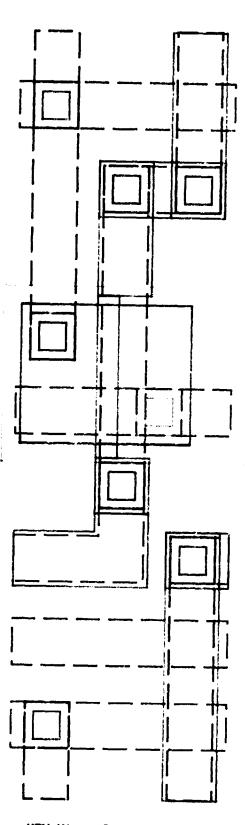

| Figure   | 6   | Chip Plan for Data Path       | 19 |

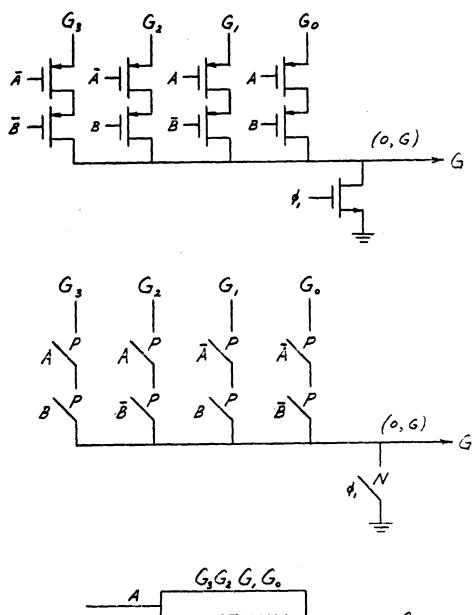

| Figure   | 7   | Generalized Functional Block  | 20 |

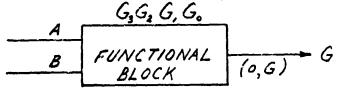

| Figure   | 8   | Block Diagram for a 1 Bit ALU | 21 |

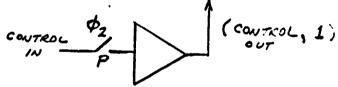

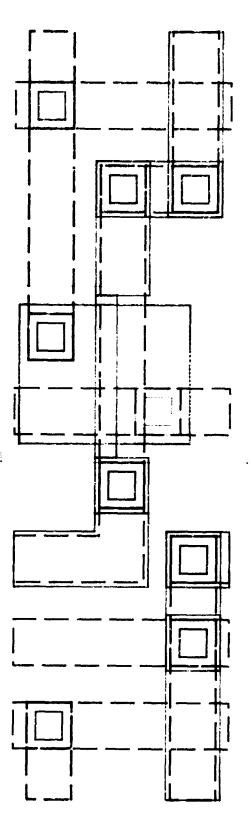

| Fi gur e | 9   | Control Buffers               | 22 |

| Figure   | 10  | Two Port Register             | 23 |

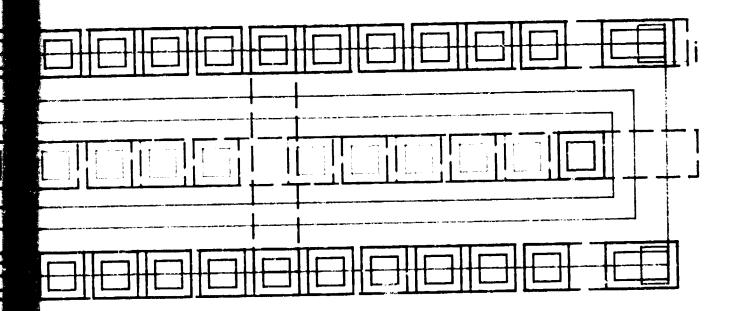

| figure   | 11  | A 4x4 Barrel Shifter          | 24 |

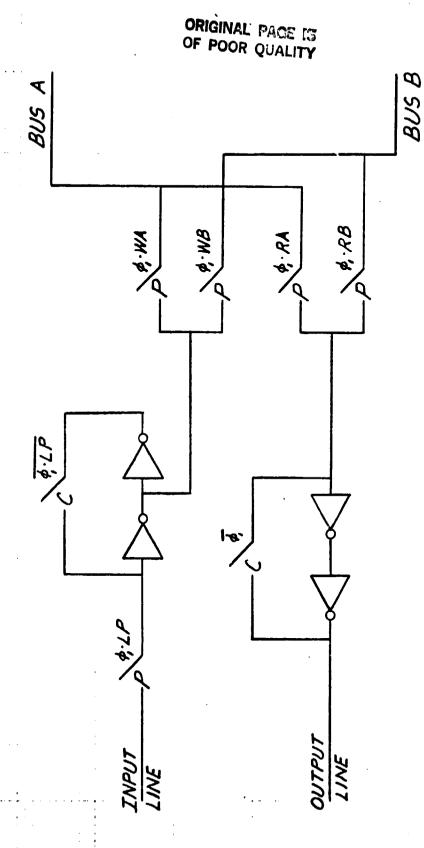

| Figure   | 1 2 | Bus Circuitry and Timing      | 25 |

| Fipure   | 1 3 | Literal Buffer                | 26 |

| Figure   | 14  | Input/Output Latches          | 27 |

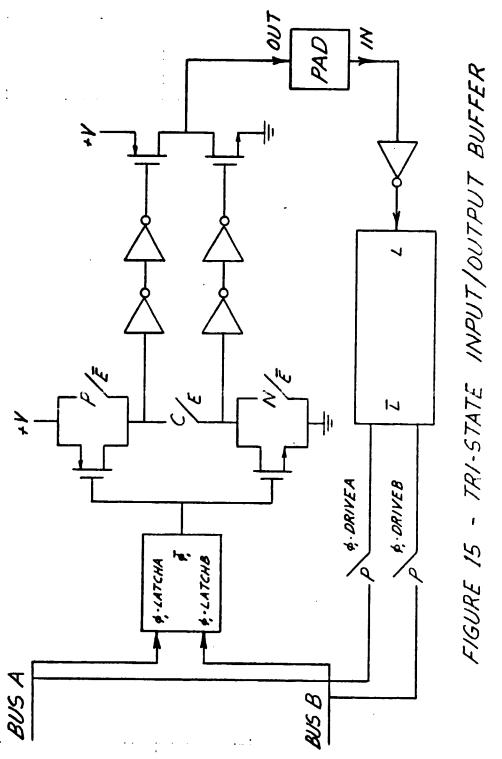

| Figure   | 15  | Tri-State I/O                 | 28 |

### LIST OF TABLES

| Table | Ia | NASA | Design | Rules | for | Sandia | Process | 8  |

|-------|----|------|--------|-------|-----|--------|---------|----|

|       | Ib |      |        |       |     |        |         | 9  |

|       | Ic |      |        |       |     |        |         | 10 |

|       | Id |      |        |       |     |        |         | 11 |

#### SUMMARY

The Mosaic Transistor Array is an extension of the STAR system developed by NASA which has dedicated field cells designed to be specifically used in semicustom microprocessor applications. The Sandia radiation hard bulk CMOS process is utilized in order to satisfy the requirements of space flights. A design philosophy is developed which utilizes the strengths and recognizes the weaknesses of the Sandia process. A style of circuitry is developed which incorporates the low power and high drive capability of CMOS. In addition the density achieved is better than that for classic CMOS, although not as good as for NMOS.

The basic logic functions for a data path are designed with compatible interface to the STAR grid system. In this manner either random logic or PLA type structures can be utilized for the control logic.

v

# THE MOSAIC TRANSISTOR ARRAY APPLIED TO CUSTOM MICROPROCESSORS

#### I. Introduction

NASA at Marshall Space Flight Center has developed the Standard Transistor Array (STAR) as a means of providing quick turn-around to the design-fabrication cycle for custom integrated circuits. It is in essence a semicustom approach utilising two levels of metal interconnect for customizing a chip to an application. It provides a means for fabrication of the diffused understructure at one location while the customizing double-layer metal can be applied at another. This allows organizations with proficiency in the thin film hybrid field to place the turn-around of custom I.C. development under their own control.

The associated STAR software allows for any mix of automatic layout and hand layout desired. Since the interconnections are regimented into a vertical-horizontal format, a reasonable display of the chip design can be mapped onto the column-row oriented line printer output. The STAR software system therefore does not demand an interactive graphics capability as a prerequisite for efficient operation.

Due to the double-layer metal aspect, STAR provides higher density than former automatic layout schemes which utilize only one layer of metal. The chip understructure is packed with transistors and the interconnections are handled overhead in the metal layers. The STAR scheme calls for all metal to be routed over a rigid grid structure. interconnect points of the understructure transistors to the metalization layer, i.e., the grid points, are also fixed. The nature of the layout and fabrication of the understructure can be varied in all other aspects. Thus, the STAR approach can be suited to variations of technology. The intent is to separate the chip logic (in terms of interconnections of grid points) from the technology (in terms of solid state devices which feed through up to the grid). Logic, once defined, can easily be transferred from one technology to another or scaled up or down as desired. understructure consists for the most part of two complementary transistors that are replicated over the whole

ORIGINAL PAGE IS

OF POOR QUALITY ohip. The task of changing tachnologies is reduced to redesigning two transistors. The accommodation within a technology to a specific vendor's desires on design rules also be handled easily by redesigning the two can transistors.

The STAR format dedicates certain of the horisontal and vertical lames to the task of converting transistors into standard logic cell designs in order to ease the burden on automatic layout computation. This leaves clear lanes, unused cell lane segments, for the global interconnection of cells into the final chip design. STAR provides an excellent solution for custom integrated circuit needs in the area of random logic. There is a considerable need for such capability in the interfacing of a standard off-the-shelf microprocessors and their associated chips out to the real world. The STAR approach is not area efficient, however, in actual development of new microprocessors or similar ohips.

The Mosaic Transistor Array (MTA), the subject of research effort, is an approach aimed at reducing the turn-around time in the development of microprocessor or similar chips. Such chips tend to have segments devoted to RAM, ROM, PLA, and register activities. The STAR format, is optimized for random logic, provides more interconnect lanes than are needed for these very regular The MTA provides a small variety of structures. understructures to accommodate each such activity. These understructures or field cells still maintain the same grid for compatibility with the random logic field cell, but the density of transistors may increase by a factor of four. The MTA loses the semioustom capability of the STAR. Prudent inclusion of extra random logic and/or PLA field cells into a design provides elbow room for mistakes or changes in control section. In concept one only has to revise the metal level masks. Wafers having the previous understructure processing would still be good for the new chip logic design.

A requirement for "total dose" radiation hardness constrains the design to be compatible with an available "hard" process. The Sandia silicon gate bulk CMOS process has been selected. This process presents interesting consequences for VLSI type designs. Channeling over the p-well is minimised by requiring the poly gate to extend over thin oxide into the P+ guard ring. This constraint compromises the normal CMOS circuit density -- much less compared with NMOS microprocessors.

The goal of this research project is to develop at . first generation set of cells suitable for least implementing the basic computer functions. In order to achieve flexibility for various applications, a customized structure is visualized, possibly control microprogramming. In addition an organised approach to the

assembly of the system building blocks from both circuit and topology points of view is required. A generalised data path (bit-slice) structure with a finite-state machine controller offers such an approach. Furthermore, the data flow through the bit-slice can be optimised for performance.

### II. The Sandia CMOS Process with Double-Layer Metal

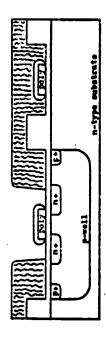

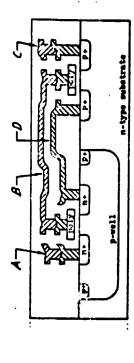

The Sandia process has been chosen since it represents a bulk silicon, radiation-hard process suitable for low-power space applications. Double layer metal add-on processing is assumed for this design — just as in the case for the STAR program. The Sandia process is a p-well process with a separate P+ guard-ring diffusion. Consequently, the all N+ poly interconnection/gate layer is permitted to cross the field and p-well boundary. The fabrication steps required for n-type and p-type devices in the Sandia process are explained with the aid of a series of cross-sectional drawings in Figure 1.

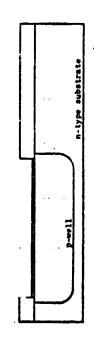

The fabrication process begins with the growth of a thermal oxide on an n-type silicon wafer. Figure 1a shows the cross-section of the wafer after the thermal oxide has been grown. The next set of steps develops the p-well which is necessary for the isolation of the NMOS devices. In order to create the p-well, a hole must be made in the thermal oxide; this is done by a masking process. The p-well mask allows the thermal oxide to be removed in regions where a p-well is desired. The p-well is implanted and driven-in. A thin oxide is grown over the well in conjunction with the drive-in. The end result is indicated in Figure 1-b.

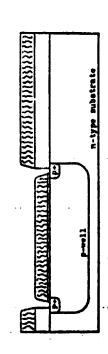

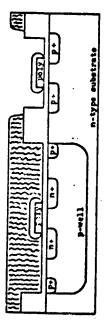

The P+ guard ring is the next addition. This guard ring serves to prevent the formation of a n-type channel over the lightly doped p-well -- even with the trapped positive charges in the oxide due to high doses of radiation. It also serves to inhibit SCR latch-up. The placement of the guard ring is controlled by a mask. Figure 1-0 displays the wafer after a boron diffusion has produced the P+ guard ring. The guard ring mask (photoresist), indicated by the region enclosing the wavy lines, is shown in the figure.

A thick oxide, referred to as the field oxide, is then grown over the entire wafer. A mask is used to remove the thick oxide in regions where a thin oxide is desired. Figure 1-d illustrates the results.

The philosophy of the Sandia process is to have a thin oxide cover the entire p-well, including the guard ring and the PMOS devices. The other regions are covered by a thick oxide. It should be noted that the exposure to radiation creates hole-electron pairs in the oxide. The

## ORIGINAL PAGE IS

electrons move relatively freely with moderate electric fields and are drained off by the positive potential interconnections. The holes are trapped at the oxide interface, resulting in an effective accumulation of positive charge which attracts electronic charge in the silicon below. The charge trapped is related to the oxide thickness to the second power, as a minimum. Consequently, over lightly-doped p-regions, only thin gate oxide is used in order to prevent channeling between "unrelated" N+ nodes.

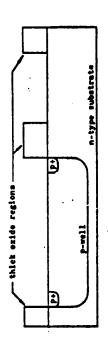

The thin oxide is provided by growing an oxide over the entire wafer. This oxide growth does not appreciably change the thickness of the thick oxide already present. A uniform polysilicon (poly) deposition follows the thin oxide growth. The poly is doped N+ and will be used as the gates for all the transistors, both NMOS and PMOS. A mask referred to as the poly mask is used to remove the unwanted poly. The poly that remains is covered by growing a layer of thin oxide. Figure 1-e shows the cross-section of the wafer at this point in the fabrication process.

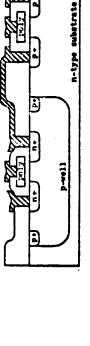

The wafer is now ready to be implanted with an Namaterial which will provide the sources and drains of all the NMOS devices. The Name implant mask (photoresist) is placed on the ohip and the Name material implanted. The results from this Name implant step are indicated in Figure 1-f. The mask is still in place as indicated by wavy lines. It is obvious from the figure that the placement of the source and drain regions in the pawell for the NMOS devices is controlled by the implant mask and the poly. This provides a self-alignment of the NMOS transistors which is vital for proper operation of the device. One notes that a Name of the device of the name of the n

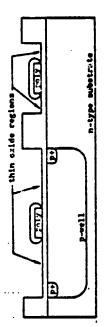

Similar to the NMOS devices, the PMOS devices are also self-aligned. The P+ implant mask is used with a boron implant to dope the P+ regions. Figure 1-g illustrates the results. From the figure it is seen that the placement of the source and drain regions of the PMOS devices is controlled by the thick oxide and the poly. The P+ implant mask does not allow the P+ material to be implanted inside the p-well except in regions for chmic contact to the p-well.

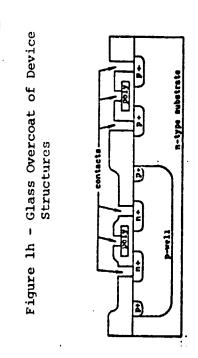

The removal of the P+ implant mask is followed by a glass coating. The cross-section of the wafer after this step appears as in Figure 1-h. It is seen in the figure that once the NMOS and PMOS devices have been constructed it remains only to provide the metal interconnections between devices.

As mentioned previously, double-layer metal processing is assumed. Before the first layer of metal is deposited on the chip, holes are out into the glazs that is present on the chip. This is done through another masking

step; the mask is this case referred to as the contact mask. Figure 1-i illustrates the chip after this masking step. The holes produced in the glass are called contacts, and the chip is ready for the first layer of metal.

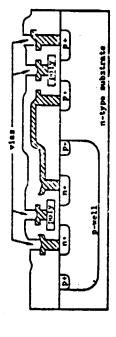

The first layer of metal, sometimes a silicide, is deposited on the chip. A mask is used to remove the metal in locations where it is unwanted. This technique was used when the poly was laid on the chip and will be used again for the second layer of metal. After the first metal processing steps, the chip appears as in Figure 1-j. The metal is indicated in the figure by the cross-hetched area. In the figure the drain of the NMOS device has been connected to the drain of the PMOS device. Other connections between devices can be made by use of the metal.

The first metallisation is followed by another glass coating similar to the glass coating step which followed the P+ implant. Before connections are made using the second metallisation, holes are out in the glass. Again a mask (called a via mask) is used. The resulting holes in the glass are known as vias. The cross-section of the chip after the vias have been stohed is indicated in Figure 1-k.

The second layer of metal, appropriately referred to top metal, is deposited on the chip. Once again a mask is used during the etching process to remove undesirable top This second metallisation step provides the metal. remaining device connections that could not be completed A final glass overcoat is placed on the with first metal. as shown in Figure 1-1. The top metal has been cross-hatched opposite to that of first metal. According to the figure the connection of the gates of the NMOS and PMOS devices has been made by the top metal. This second metallisation completes the process except for a pad mask step that allows terminal connections of the packaged chip to the integrated circuit.

The Sandia process can be quickly summarised by reviewing the different masks required during fabrication. Ten masks excluding the final pad mask comprise the complete set of required masks. These masks are in order: p-well, P+ guard ring, thin exide, poly gate, N+ implant, P+ implant, contact, first metal, via, and second (top) metal.

The design rules used for the MTA project are the same as those developed for the radiation-hard STAR design. These rules are repeated in the following Table for the reader's conveniency.

Figure la - Thermal Oxide on Wafer

Figure 1b - Creating the p-well

Figure 1c - Masking the p+ Guard Ring

Figure 1d - Field Oxide on Chip

Figure le - Thin Oxide Growth and Poly Deposition

Figure 1f - Masking the n+ Implant Region

Figure lg - Masking the p+ Implant Region

Figure 1j - First Metallization

Figure 1k - Making Vias

Figure 11 - Top Metal

Figure 1i - Making Contacts

n-type substrate

P-111

112

Kica

Ė

| MASK     | DESCRIPTION                        | NASA<br>(MILS) | SANDIA<br>(MICRONS) |

|----------|------------------------------------|----------------|---------------------|

| LAYER 1: | P-WELL                             |                |                     |

| 1.1.1    | MINIMUM WIDTH                      | .2             | 5                   |

|          | MINIMUM SPACE                      | 1.0            | 25                  |

| LAYER 2: | P+ GUARD-BAND                      |                |                     |

| 2.2.1    | MINIMUM WIDTH                      | .2             | 5                   |

| 2.2.2    | MINIMUM SPACE                      | .6             | 15                  |

| 2.2.3    | MINIMUM WIDTH AROUND WELL          | .3             | 7                   |

| 2.1.1    | INSIDE EDGE OF GUARD BAND          | _              |                     |

|          | OVERLAP TO OUTSIDE OF P-WELL       | 0              | 0                   |

| LAYER 3: | THICK OXIDE (ALIGNED TO P+ GUARD-I | BAND)          |                     |

| 3.3.1    | MINIMUM THICK OXIDE WIDTH          | .3             | 7                   |

| 3.3.2    | MINIMUM THIN OXIDE SPACE           | .3             | 8                   |

| 3.3.3    | MINIMUM SPACE (P+ TO P+)           | .5             | 12                  |

| 3.2.1    | MINIMUM THIN OXIDE OVERLAP         |                |                     |

|          | OF GUARD BAND EDGE                 | .2             | 5                   |

| 3.2.2    | MINIMUM THICK OXIDE TO             |                |                     |

|          | GUARD BAND WHEN USED TO            |                |                     |

|          | DEFINE N+                          | .325           | 8                   |

| 3.2.3    | MINIMUM THICK OXIDE TO             |                |                     |

|          | GUARD BAND WHEN USED TO            |                |                     |

|          | DEFINE P+ DRAIN                    | .65            | 17                  |

| 3.2.4    | SAME AS 3.2.3 EXCEPT               |                |                     |

| :        | P+ SOURCE                          | .5             | 13                  |

| 3.1.1    | MINIMUM THICK OXIDE TO             |                |                     |

|          | P-WELL WHEN USED TO                | 2.22           |                     |

|          | DEFINE P+ DRAIN                    | .85            | 21                  |

| 3.1.2    | SAME AS 3.1.1 EXCEPT               |                |                     |

|          | P+ SOURCE                          | .675           | 17                  |

| 3.3.3    | MINIMUM THIN OXIDE TO              | <b>.</b> -     |                     |

|          | SCRIBE LINE                        | 2.0            | 50                  |

Table Ia - NASA Design Rules For Sandia Process

| MASK     | DESCRIPTION                       | NASA<br>(MILS) | SANDIA<br>(MICRONS) |

|----------|-----------------------------------|----------------|---------------------|

| LAYER 4: | POLY SILICON (ALIGNED TO THICK OF | KIDE)          |                     |

|          | MINIMUM LINE                      | .25            | 6                   |

| 4.4.2    | MINIMUM SPACE                     | . 25           | 6                   |

| 4.4.2    | MINIMUM PMOS GATE LENGTH          | .25            | - 5                 |

| 4.4.3    | MINIMUM NMOS GATE LENGTH          | .2             | 8                   |

| 4.3.1    | MINIMUM POLY TO THICK             |                |                     |

|          | OXIDE                             | .075           | 1                   |

| 4.2.1    |                                   |                |                     |

|          | WHEN POLY DEFINES N+              | . 35           | 9                   |

| 4.2.2    | SAME AS 4.2.1 EXCEPT POLY         |                |                     |

|          | DEFINES P+ DRAIN                  | .7             | 18                  |

| 4.2.3    | SAME AS 4.2.2 EXCEPT POLY         |                |                     |

|          | DEFINES P+ SOURCE                 | .6             | 14                  |

| 4.3.2    | MINIMUM POLY GATE OVERLAP         |                |                     |

|          | OF THICK OXIDE                    | .2             | 5                   |

| 4.2.4    | MINIMUM POLY OVERLAP OF           |                |                     |

|          | GUARD RING                        | .25            | 6                   |

| 4.1.1    |                                   |                |                     |

|          | POLY DEFINES P+ DRAIN             | .9             | 22                  |

| 4.1.2    | SAME AS 4.1.1 EXCEPT POLY         |                |                     |

|          | DEFINES P+ SOURCE                 | .7             | 18                  |

| LAYER 5: | N+ IMPLANT (ALIGNED TO THICK OXII | DE)            |                     |

| 5.5.1    | MINIMUM WIDTH                     | .2             | 5                   |

| 5.5.2    | MINIMUM SPACE                     | .2             | 6                   |

| 5.2.1    | MINIMUM N+ TO P+ GUARD            | .4             | 10                  |

| LAYER 6: | P+ IMPLANT (ALIGNED TO THICK OXII | DE)            |                     |

| 6.6.1    | MINIMUM WIDTH                     | .2             | 5                   |

| 6.6.2    | MINIMUM SPACE                     | .5             | 12                  |

| 6.2.1    | MINIMUM P+ DRAIN TO               | •••            |                     |

|          | P+ GUARD                          | .75            | 19                  |

| 6.2.2    | MINIMUM P+ SOURCE TO              |                |                     |

| ,        | P+ GUARD @ VDD                    | .6             | 15                  |

| 6.2.3    | MINIMUM P+ DRAIN TO               |                |                     |

|          | P+ GUARD @ VDD                    | .6             | 15                  |

| 6.3.1    | MINIMUM P+ TO THICK OXIDE         |                | <del></del>         |

|          | WHICH DEFINES P+                  | .2             | 5                   |

| 6.1.1    | MINIMUM P+ TO P-WELL              | .9             | 23                  |

| 6.1.2    | MINIMUM P+ TO P-WELL              |                | _ <del>-</del>      |

|          | @ VDD                             | .75            | 19                  |

| 6.5.1    | MINIMUM P+ OVERLAP OF             |                |                     |

|          | N+ FOR SHORTING                   | .05            | 1                   |

Table  ${ t Ib}$  -(Continued). NASA Design Rules For Sandia Process

|                                       | NASA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SANDIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESCRIPTION                           | (MILS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (MICRONS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CONTACT (ALIGNED TO THICK OXIDE)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MINIMUM CONTACT                       | $.3 \times .3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6 x 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | . 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | .15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | . 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| · · · · · · · · · · · · · · · · · · · | . 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The sound control                     | . 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| METAL (ALIGNED TO CONTACT)            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MINIMUM METAL WIDTH                   | .5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MINIMUM METAL SPACE                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MINIMUM METAL CONTACT                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OVERLAP                               | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MINIMUM METAL TO SCRIBE               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LINE                                  | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VIA (ALIGNED TO FIRST METAL)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MINIMUM VIA                           | .3 x .3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6 x 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MINIMUM VIA INSIDE METAL              | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                       | MINIMUM CONTACT MINIMUM CONTACT INSIDE THICK OXIDE DIFFUSION MINIMUM CONTACT INSIDE POLY TO EDGE MINIMUM CONTACT OUTSIDE POLY TO EDGE MINIMUM CONTACT INSIDE N+ DIFFUSION MINIMUM CONTACT INSIDE P+ DIFFUSION MINIMUM CONTACT FROM OXIDE STEP MINIMUM CONTACT FOR SHORT- ING OVERLAP DIFFUSIONS MINIMUM P+ GUARD CONTACT  METAL (ALIGNED TO CONTACT)  MINIMUM METAL WIDTH MINIMUM METAL SPACE MINIMUM METAL CONTACT OVERLAP MINIMUM METAL TO SCRIBE LINE  VIA (ALIGNED TO FIRST METAL)  MINIMUM VIA | CONTACT (ALIGNED TO THICK OXIDE)  MINIMUM CONTACT .3 x .3  MINIMUM CONTACT INSIDE  THICK OXIDE DIFFUSION .2  MINIMUM CONTACT INSIDE  POLY TO EDGE .15  MINIMUM CONTACT OUTSIDE  POLY TO EDGE .2  MINIMUM CONTACT INSIDE  N+ DIFFUSION .2  MINIMUM CONTACT INSIDE  P+ DIFFUSION .2  MINIMUM CONTACT FROM  OXIDE STEP .2  MINIMUM CONTACT FOR SHORT- ING OVERLAP DIFFUSIONS .3  MINIMUM P+ GUARD CONTACT .3  METAL (ALIGNED TO CONTACT)  MINIMUM METAL WIDTH .5  MINIMUM METAL CONTACT .3  MINIMUM METAL CONTACT .3  VIA (ALIGNED TO FIRST METAL)  MINIMUM VIA .3 x .3 |

Table Ic - (Continued). NASA Design Rules For Sandia Process

| MASK      | DESCRIPTION                   | NASA<br>(MILS) | SANDIA<br>(MICRONS) |

|-----------|-------------------------------|----------------|---------------------|

| LAYER 10: | SECOND METAL (ALIGNED TO VIA) |                |                     |

| 10.10.1   | MINIMUM METAL WIDTH           | .5             | 8                   |

| 10.10.2   | MINIMUM METAL SPACE           | .3             | 7                   |

| 10.9.1    | MINIMUM METAL OVERLAP         |                |                     |

|           | OF VIA                        | .1             | 1                   |

| 10.3.1    | MINIMUM BONDING PAD TO        |                |                     |

|           | THIN OXIDE                    | 1.5            | 40                  |

| 10.10.3   | MINIMUM BONDING PAD TO        |                |                     |

|           | SECOND METAL                  | 1.5            | 40                  |

| 10.8.1    | MINIMUM BONDING PAD TO        |                |                     |

|           | FIRST METAL                   | 1.5            | 40                  |

| 10.10.4   | MINIMUM UNBUFFERED .          |                |                     |

|           | PAD SPACING                   | 8.5            | 220                 |

| 10.10.5   | MINIMUM BUFFERED PAD          |                |                     |

|           | TO PAD SPACING                | 12.5           | 320                 |

| 10.10.6   | MINIMUM PAD SIZE              | 4 x 4          |                     |

| 10.10.7   | MINIMUM VSS & VSS BUS         |                |                     |

|           | WIDTH                         | .6             | 16                  |

| 10.3.1    | MINIMUM METAL TO              |                | 50                  |

|           | SCRIBE LINE                   | 2.0            | 50                  |

| 10.11.1   | PAD MASK INSIDE METAL PAD     | .175           | 4                   |

Table Id -(Continued). NASA Design Rules for Sandia Process

bit-slice structure generalized finite-state machine controller is visualized to offer the flexibility objectives of this work. Mead and Conway suggest such an approach in their design text. However, their circuit philosophy is based on silicon gate NMOS with depletion devices -- a technology not suitable for the radiation environment of space flights. implementation of logic by means of register-to-register transfer paths through combination logic with each register being gated with a particular clock phase is not new; however, their extensive use of pass transistor logic to implement the combinational logic is unusual. Raticed logic is principally restricted to the latches and registers; the ratioless pass transistor logic achieves the extended AND function at essentially zero stand-by power with the only performance compromise being fan-in. In this case the pass transistors are bi-lateral switches supplying current as a source-follower and sinking current as common source device. The source follower configuration has two short-comings:

- 1) Its final output value (pull-up) is limited by the body-effect to approximately 3.5 volts from a 5 volt supply -- even for a high performance NMOS process.

- 2) The time for the 0 to 3.5 volt transition is approximately five times longer than for the 3.5 to 0 volt transition (operating as a common source device).

Nevertheless, the simplicity of pass transistor logic is very attractive, particularly for VLSI designs. Precharging "high" can minimize transition delays in many cases.

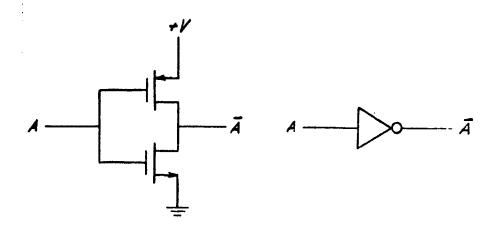

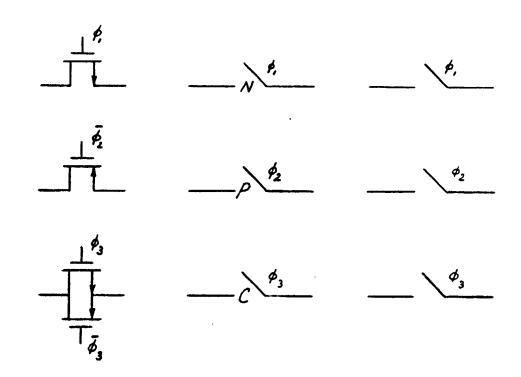

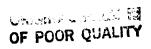

Attempting to apply these concepts to CMOS technologies presents some interesting dilemmas. Replacing the ratioed inverters in the latches and registers by CMOS inverters is a straight-forward decision; however, "structured" combinational logic poses a problem. Pass transistor switches, historically, in CMOS are implemented with pairs of devices, one NMOS and one PMOS for each switch, in order to avoid using a device in its compromised source-follower configuration. A bulk CMOS process with the AMOS devices built in a p-well, such as the Sandia process, NMOS devices with poor device characteristics provides compared with standard NMOS devices. The high p-well doping in the Sandia process (higher than normal for radiation hardness) produces a greater body-effect and reduced channel mobility compared with the standard. Consequently, the Sandia NMOS device is particularly unsuitable as a rourge-follower. As a result a direct implementation of the pass-transistor logic utilized by Mead and Conway is not practical in this design effort.

On the other hand classical CMOS is not practical for VLSI either. The CMOS device count for combinational logic is approximately twice that for NMOS. Further, implementing pass-transistor logic with classical CMOS requires true and compliment signals to drive the NMOS and PMOS pair — thus requiring roughly twice the number of control signals and drivers as for NMOS.

One alternative approach remains: implement pass-transistor logic with PMOS only, utilizing the fact that the PMOS devices in the Sandia process have a relatively low body-effect. In addition the P+ guard ring diffusion can be used as a diffusion tunnel under poly interconnections to provide a much needed cross-under capability.

Consider a CMOS latch with a PMOS pass-transistor serving 's a multiplexing switch. The PMOS pass-gate will provide a output swing from about 1.5 volts to the power supply. Adjusting the ratio of the first inverter in the latch can provide the necessary level shifting. However, an additional NMOS device is required with the PMOS feedback transistor to supply the full voltage swing after "latch-up", thus providing the full gate drive signals, facilitating the full output drive from the inverters.

In this design philosophy the NMOS transistors, which require the extra area for channel stops, are utilized only where necessary. The NMOS device is an effective switch in the common-source configuration; however, a PMOS device is required for pull-up either in a classical CMOS fashion or precharged in a clocked scheme.

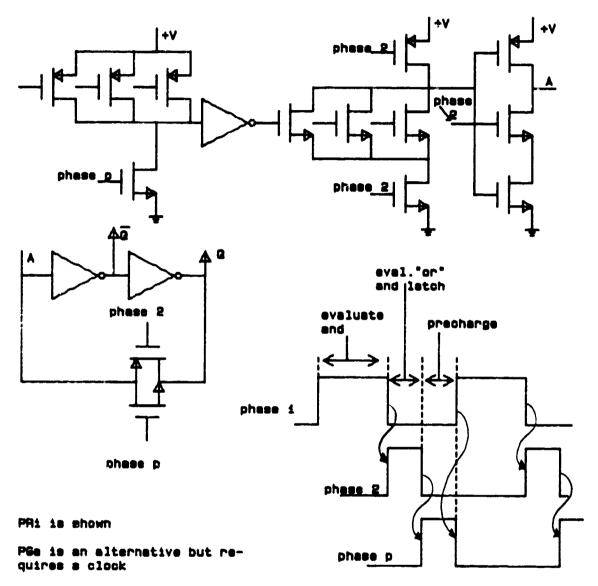

FIGURE 2a - CMOS INVERTER

FIGURE 26 - THREE TYPES OF SWITCHES

FIGURE 3 - A CMOS LATCH

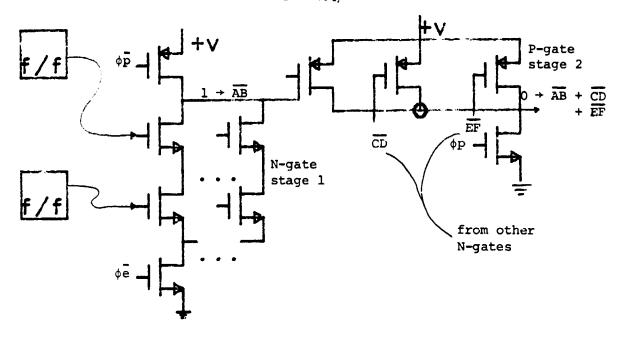

FIGURE 4 - BLOCK DIAGRAM OF A LATCH

FIGURE 5 - LATCH WITH MULTIPLE INPUTS

#### The Data Path Circuitry

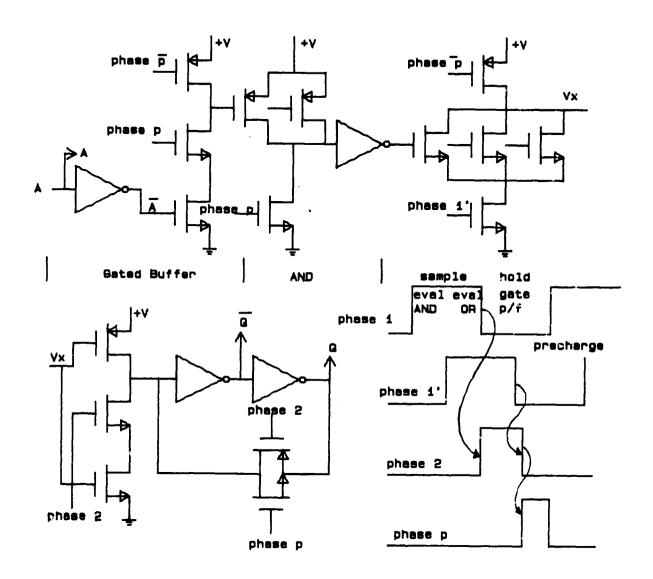

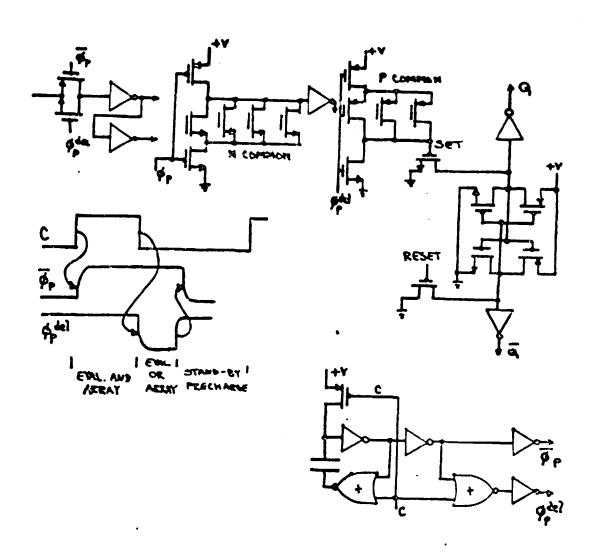

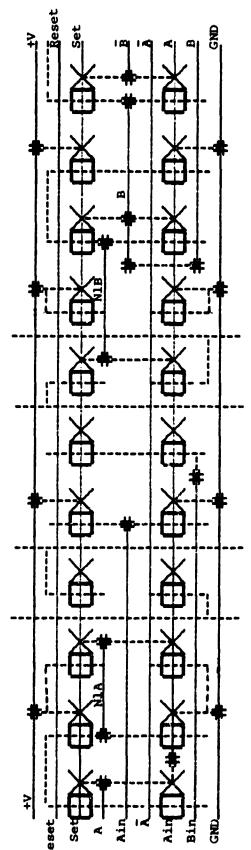

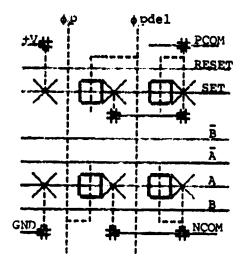

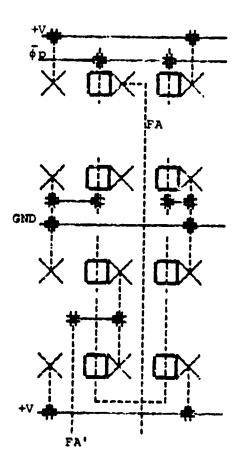

Following the philosophy of Mead and Conway the data path is organized as parallel bit-slices from one port to another port as illustrated in Figure 6. Two different buses run between the two I/O ports and pass through the dual port register array, the barrel shifter, and the ALU. The ALU is built around a Manchester-type carry circuit. The carry-out signal is precharged high prior to logic evaluation (phase 2) and remains high unless the kill signal (K) is true or P\*Cin' is true where P is the pass signal and Cin' is compliment of the carry-in signal.

#### Cout' = K + P\*Cin'

The kill and pass signals are generated by generalised function blocks, Figure 7. Each block contains four control signals and is driven by true and compliment signals from two data sources, e.g.,

Gout = G0\*A'\*B' + G1\*A'\*B + G2\*A\*B' + G3\*A\*B

where  $A \in B$  are data signals and G0 - G3 are control signal, determined by the interpretation of the instruction.

The ALU is illustrated in Figure 8. The carry chain circuitry is implemented in NMOS since it is precharged high during phase 1 and conditionally discharged low during phase 2. The NMOS device is faster in this mode than the PMOS device. In addition the K and P function blocks can be precharged low during phase 1 and conditionally charged high during the evaluation of the logic, phase 2 -- thus achieving a ripple-through effect and saving one signal inversion and two logic gates.

The ALU is preconditioned for logic evaluation (precharged) during phase 1 and the logic is evaluated during phase 2. The data is transferred over the buses during phase 1 with the buses precharged low during phase 2. The two input latches, A and B, have multiplexing gates which select signals from three sources: 1) For latch A the possible signals are Bus A, the shifter output, and the shift-control signal. 2) For latch B the possible signals are Bus B, the shifter output, and the shift control signal. These signals are selected during phase 1 and latched during phase 2. The two output latches sample only the output of the R block during phase 2. Either output latch can drive either bus during phase 1.

The carry-chain output drives the carry input for the next bit-slice. After several bit-slices are added together, the discharge delay through the several pass-transistors can become excessively long. By utilizing

the Cin signal generated to drive the R block as the drive signal for the carry propagation gate on a periodic basis, the pass-gate logic is buffered to minimize the carry propagation delay.

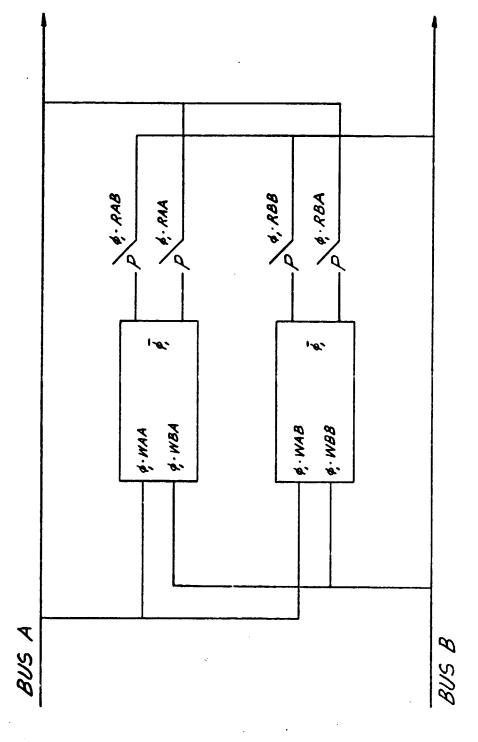

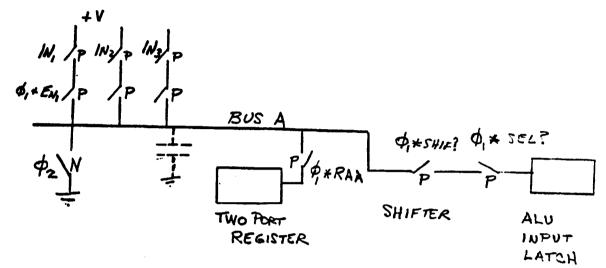

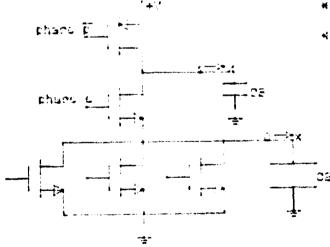

The data buses are precharged low during phase 2 and conditionally charged high through the enabled PMOS pass-gate as illustrated in Figure 12. The two port register cell with its PMOS drivers to either bus is shown in Figure 10.

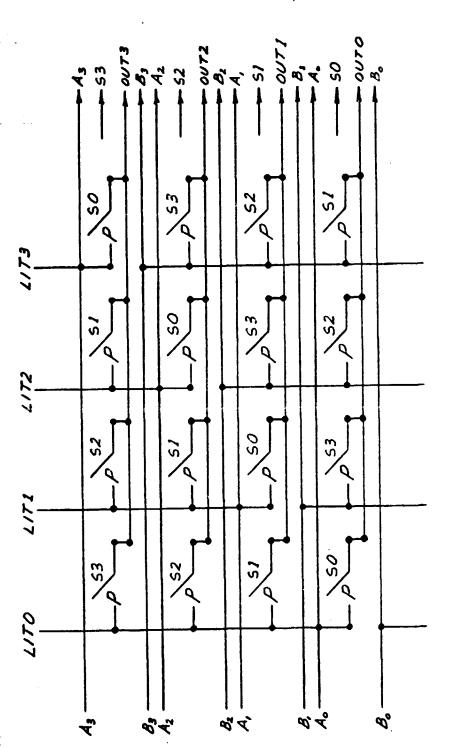

Between the register and the ALU is a barrel shifter which concatenates the two buses with bus B being in the lower significant bit politions. With the shift constant equal to sero the shifter output corresponds to the A bus. With a non-sero shift constant, he output is shifted down the corresponding number of bits. The most significant bits from the A bus are omitted and the most significant bits of the B bus are included. Figure 11 illustrates the pass-gate logic used in a 4 x S bit barrel shifter. For the Sandia process the shifter is implemented in PMOS with the shift output precnarged low in phase 2. If data is read out of a register to an input latch, the transfer occurs in phase 1 through three PMOS pass-gates: a dual port read switch, a shifter switch, and the multiplexer at the latch input.

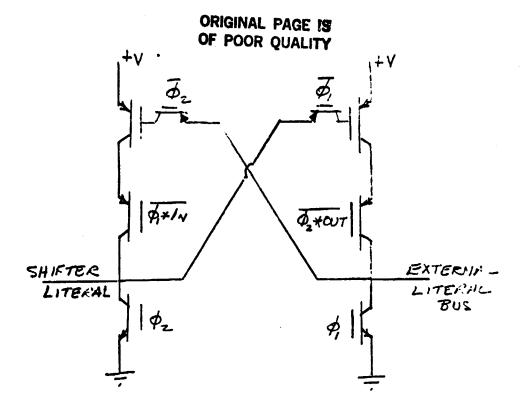

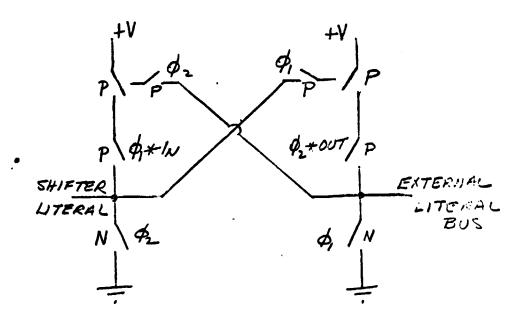

The shifter also accommodates data transfers between hus A and a literal -port to the controller. The controller can supply a literal in phase 1. Data transfer in the reverse direction is possible in the opposite phase. Figure 13 illustrates the bi-lateral buffer.

A tri-state I/O buffer is given in Figures 14 and 15. The output is latched from either bus and enabled with an asynchronous signal with the latch driving either bus during phase 1. An appropriate number of inverter stages is included in the buffer to achieve the necessary capacitance driving capability.

FIGURE 7 - GENERALIZED FUNCTIONAL BLOCK

# ORIGINAL PAGE IS

٠<u>٠</u>.

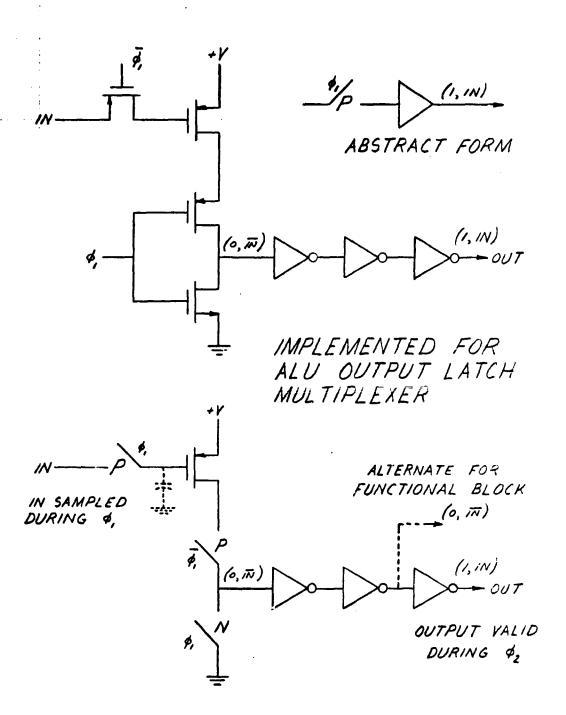

FIGURE 9 - CONTROL BUFFER

FIGURE 10 - TWO-PORT REGISTER CELL

YGURE 11 - A 4 x 4 BARREL SHIFTER

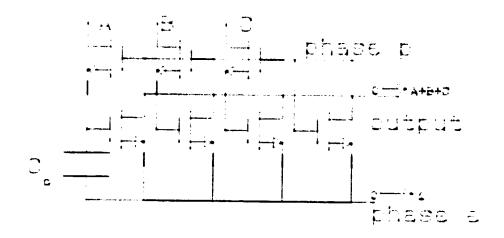

- · BUS DISCHARGED LOW IN \$2

- . BUS CONDITIONALLY CHARGED HIGH IN O

- . CONTROL BUFFERS

- NON- INVERDING

- SAMPLE INPUTS IN \$2

- OUTPUTS ARE PRECHARGED HIGH IN OZ

FIGURE 12 BUS CIRCUITRY AND TIMING

FIGURE 13 LITERAL BUFFER

, . ,

FIGURE 14 - INPUT/OUTPUT LATCH

27

#### ORIGINAL PAGE 13 OF POOR QUALITY

٠).

#### V. Additional Comments

This design of the functional elements for a data path logic provides the foundation for implementing a microprocessor with the MTA concept. In this regard either the structured SLA described in another part of this report and/or conventional STAR cells can be used to implement the control logic.

The data path or bit-slice approach is quite flexible and is compatible with the concept of microprogramming with a PLA type structure. Electrically reprogrammable PLAs could even provide field changes in the basic instruction. The popularity of the bit-slice approach is exemplified by recent announcements from Hewlett-Packard and Bell Laboratories. It should also be noted that the Bellmac32 from Bell Laboratories is a 32 bit processor implemented with CMOS which uses their poly cell (standard cells) structures in conjunction with a data path function.

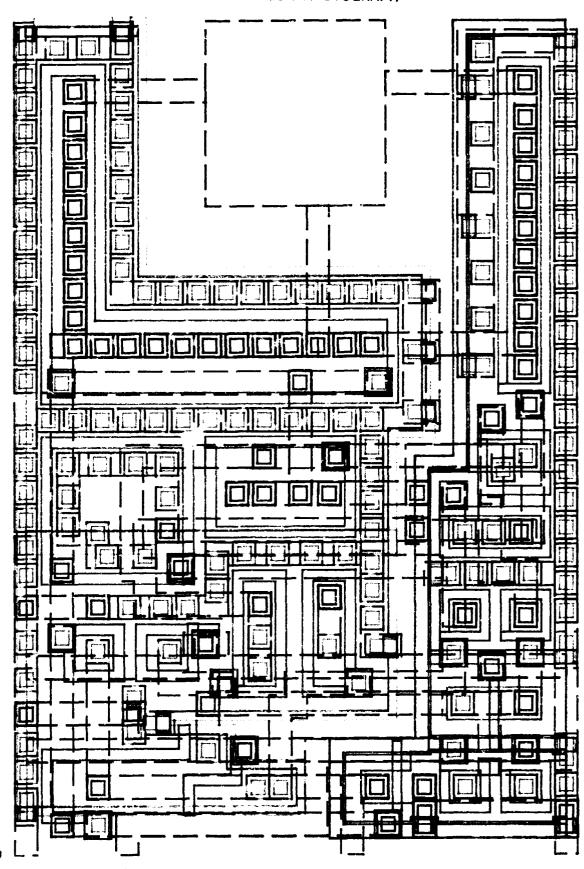

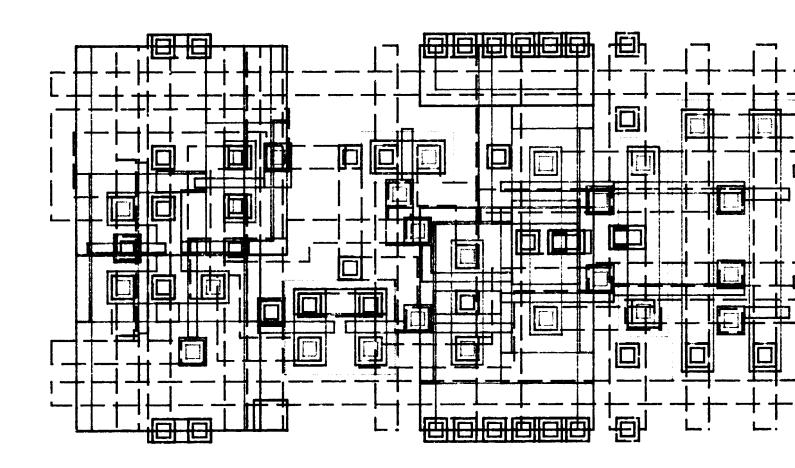

The detail drawings of the functional cells for the data path are provided in the appendix.

#### REFERENCES

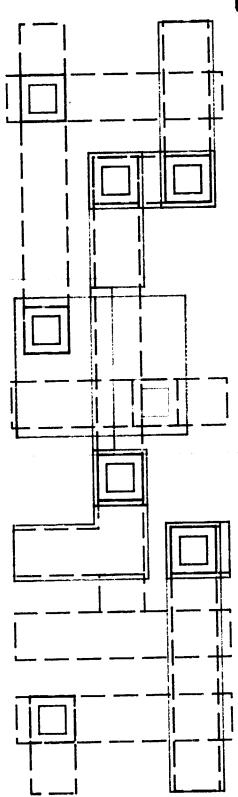

1. Carver Mead and Lynn Conway, <u>Introduction to VLSI Systems</u>, Addison-Wesley Publishing Company, 1980. BASIC LATCH (no silicide)

1001

scale: 1001X

ODD LATCH ( gate added )

1002

scale: 1001X

ORIGINAL PAGE

EVEN LATCH (gate added )

1003

scale: 1001X

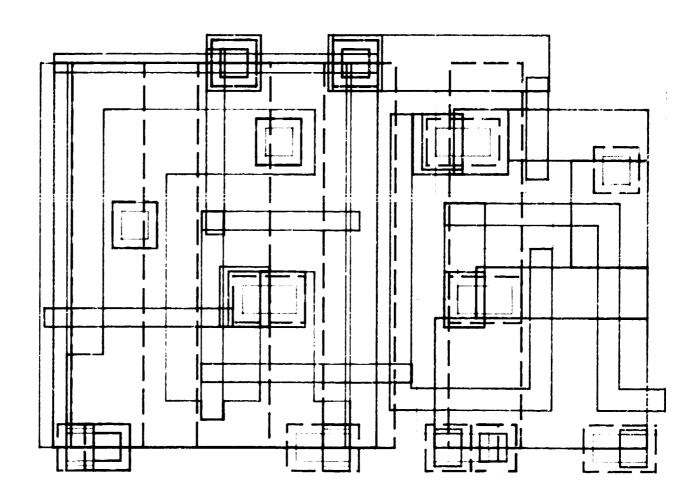

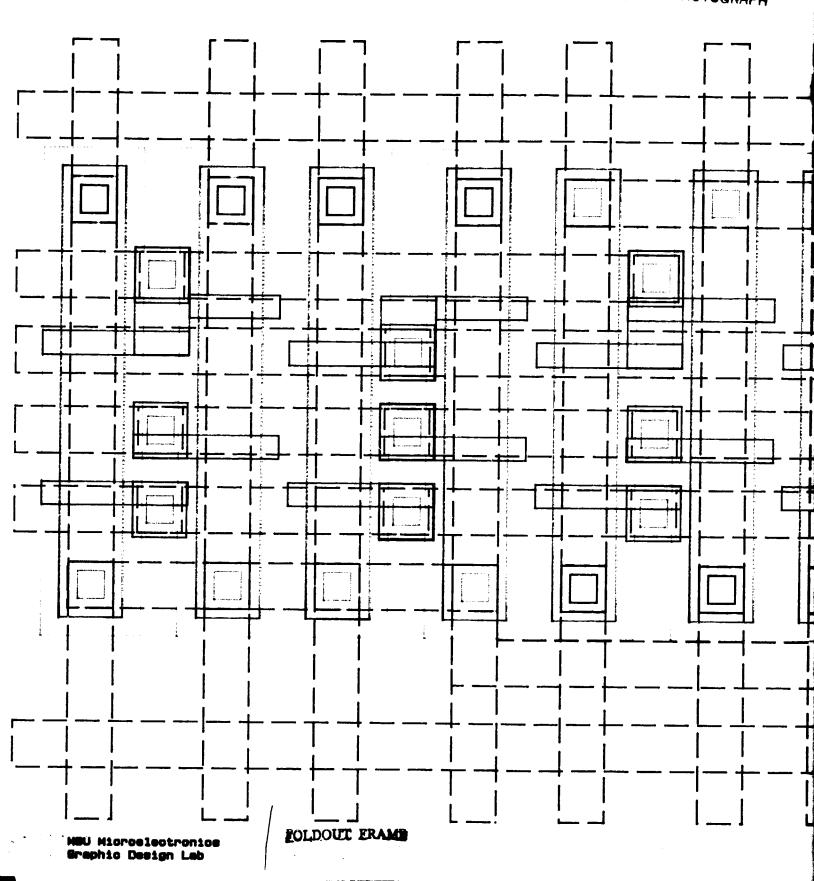

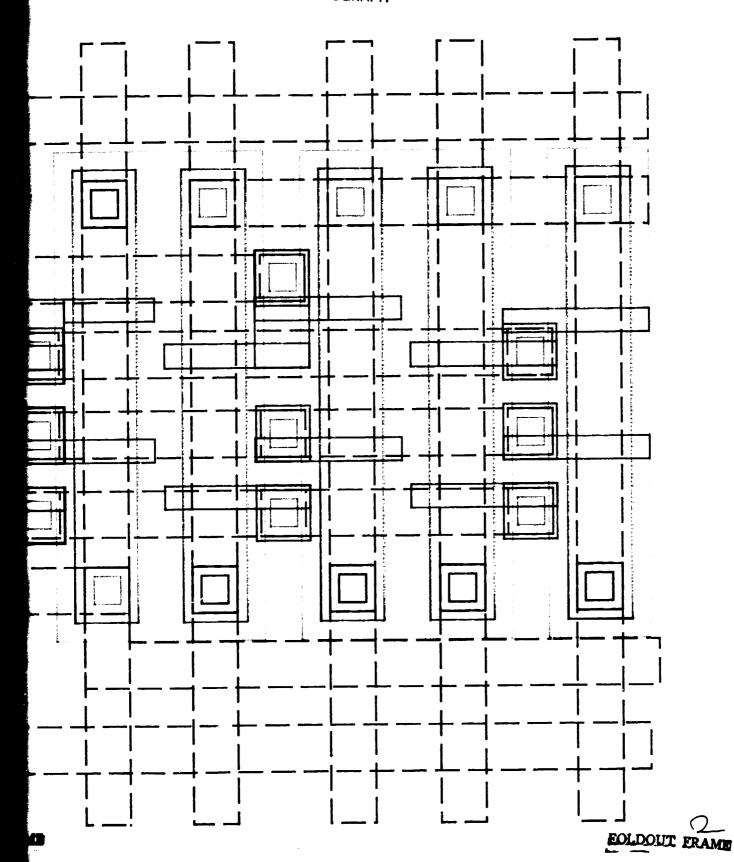

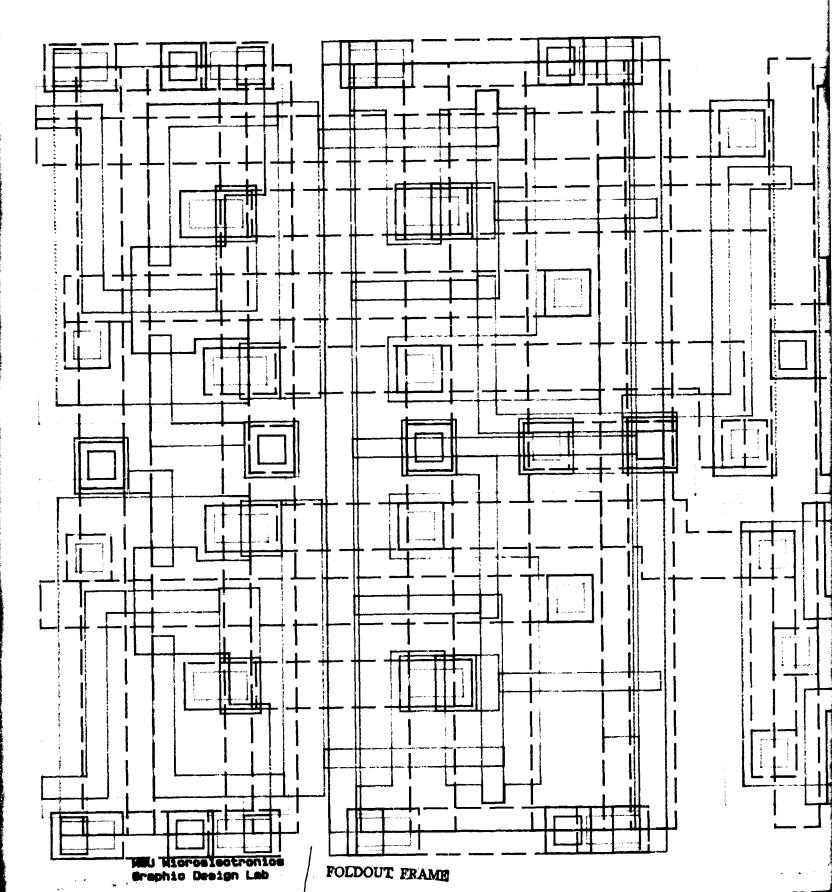

ODD CELL 1004 scale: 1001X

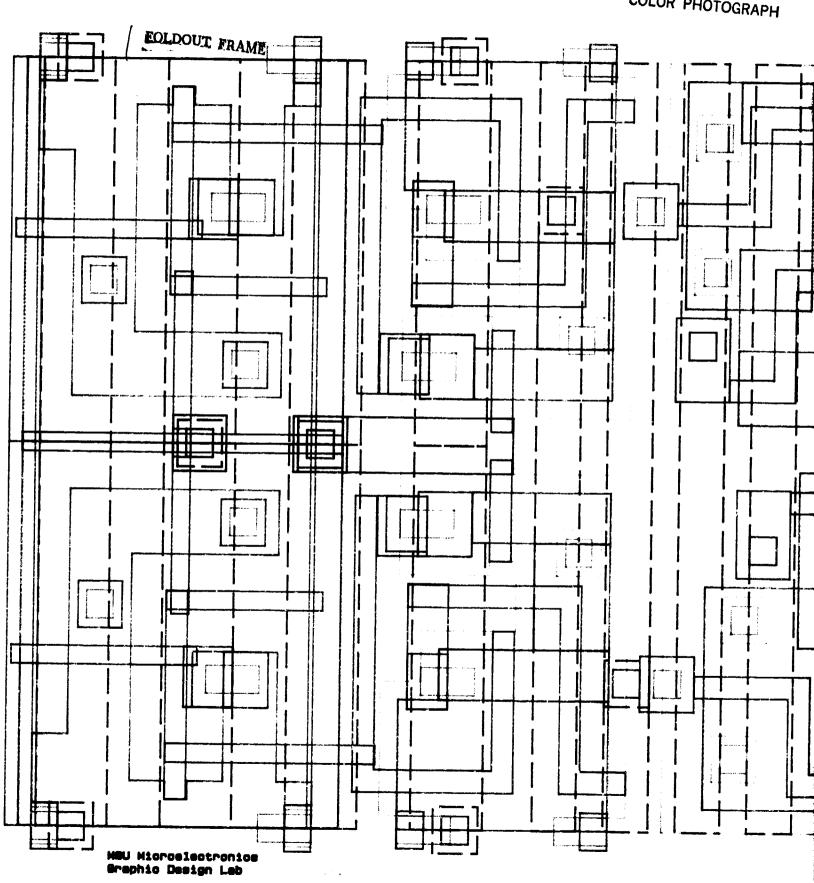

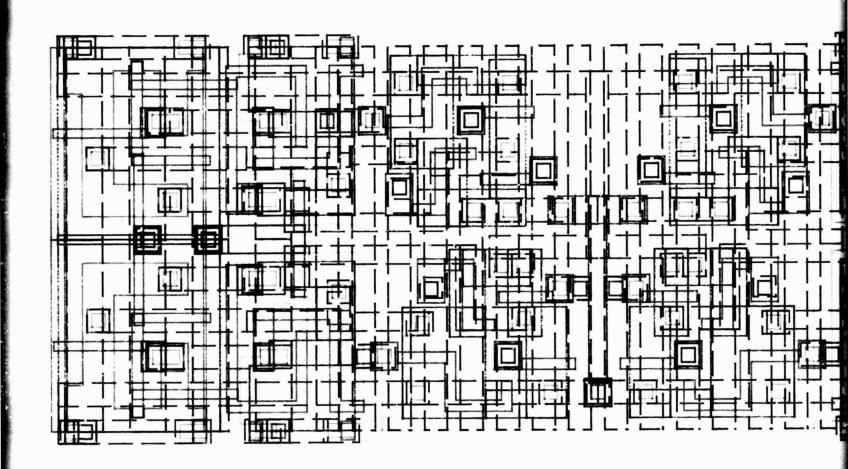

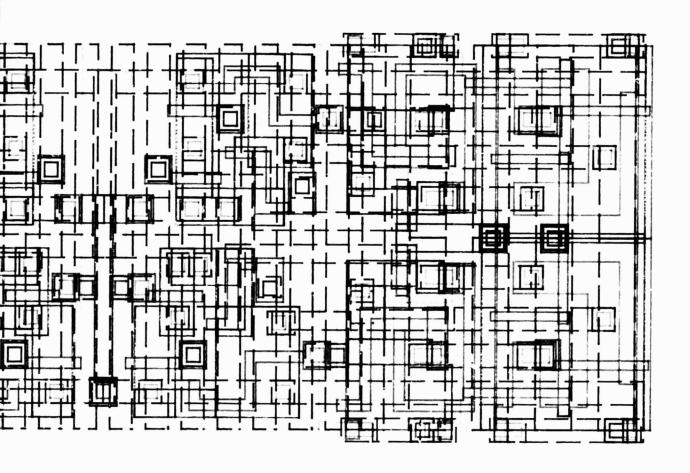

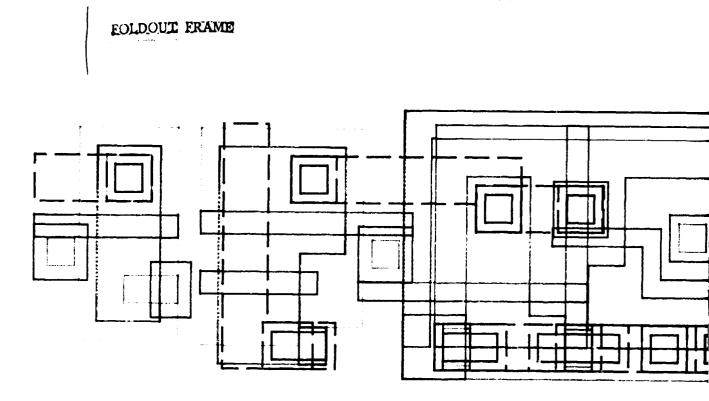

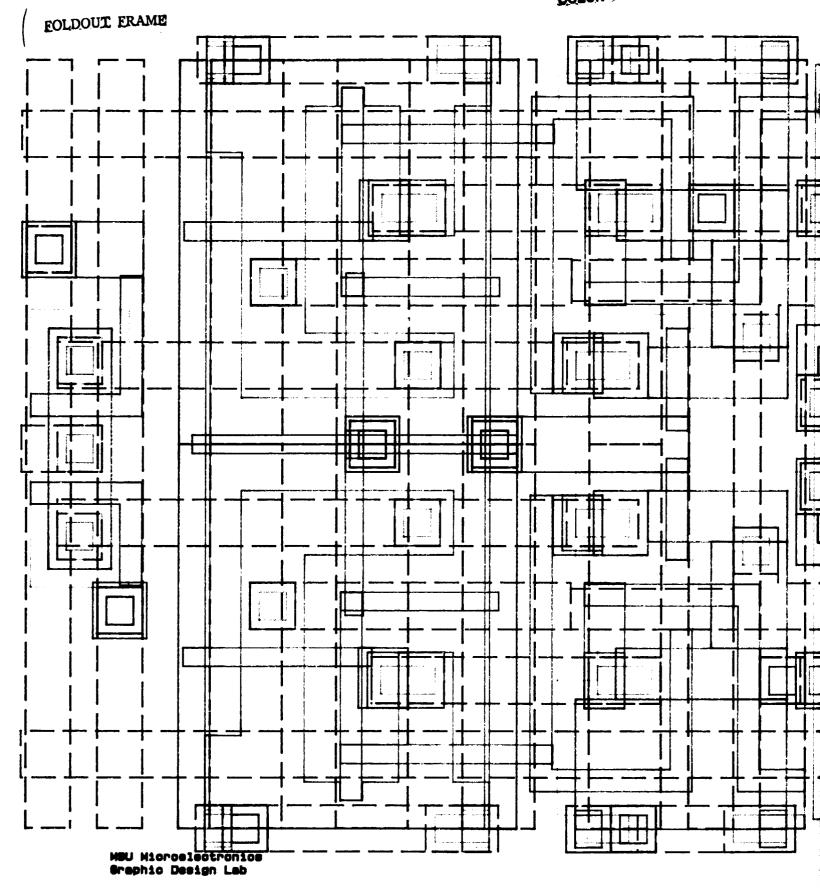

ORIGINAL PAGE COLOR PHOTOGRAPH CEOLDOUT FRAME EVEN CELL 1005

FOLDOUT FRAME SCale: 1001X

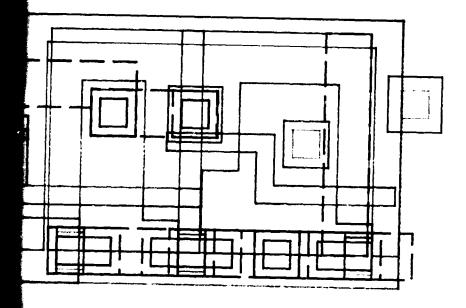

DUAL CELL 1006

scale: 500X

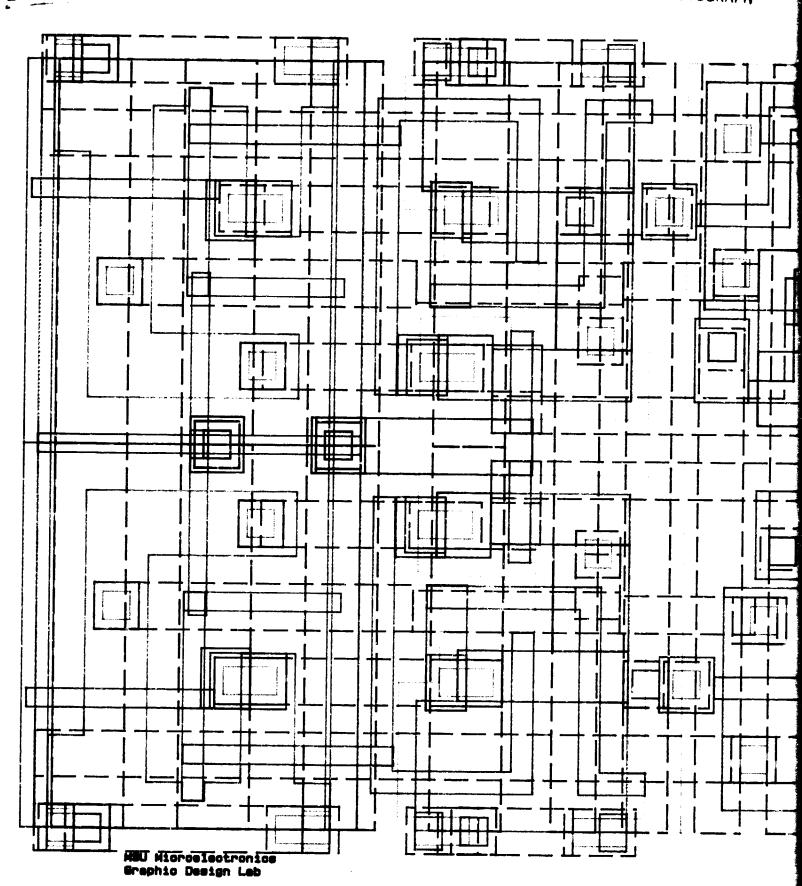

ORIGINAL PAGE COLOR PHOTOGRAPH

( ) E.

FOLDOUT FRAME

MSU Microelectronics Graphic Design Lab

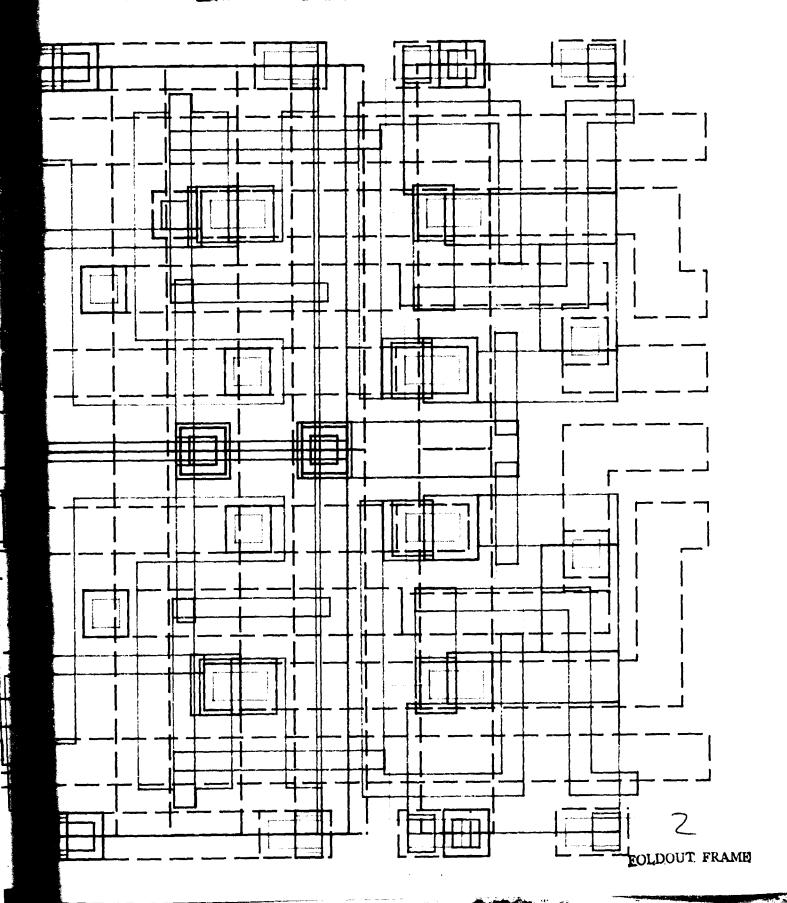

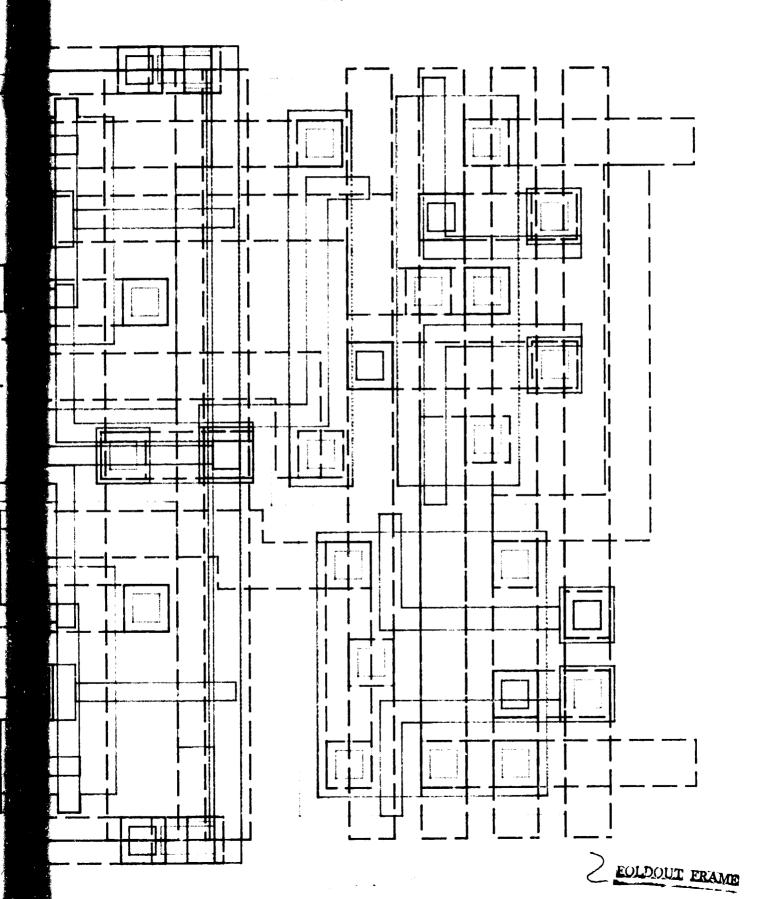

#### ORIGINAL PAGE COLOR PHOTOGRAPH

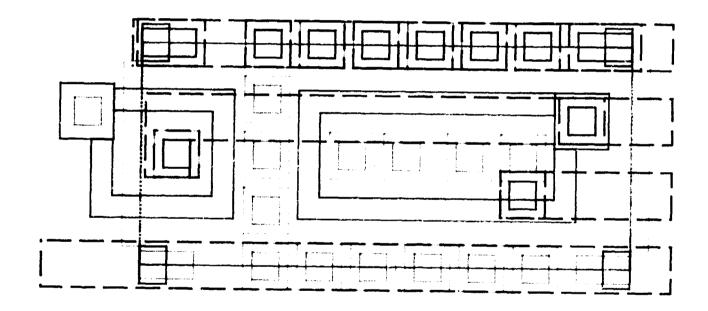

FUNCTIONAL BLOCKS P & K

1007

scale: 1001X

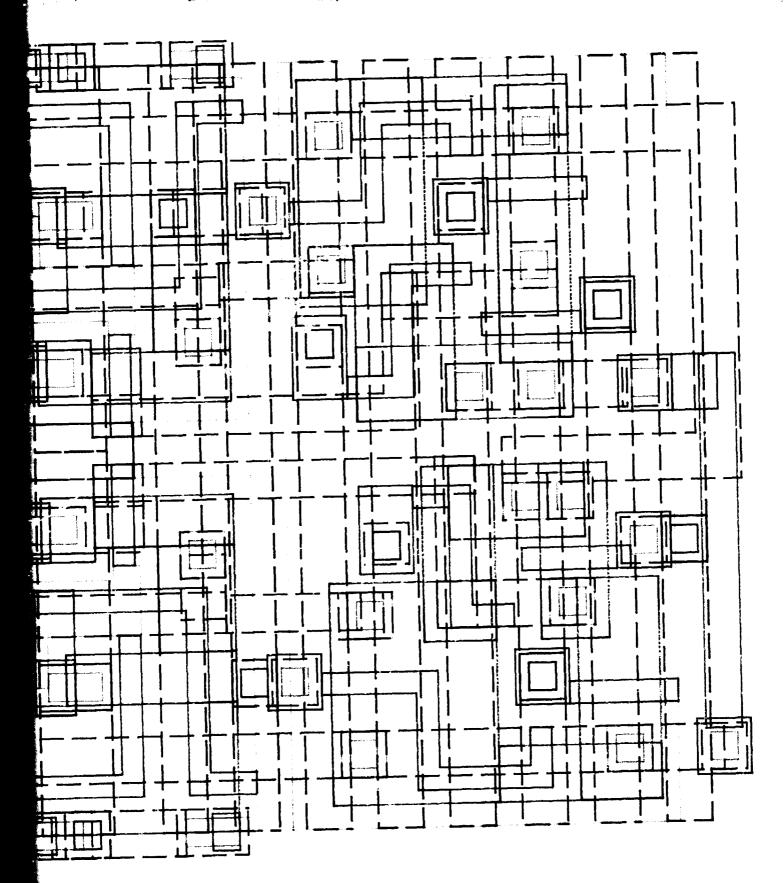

ORIGINAL PAGE COLOR PHOTOGRAPH

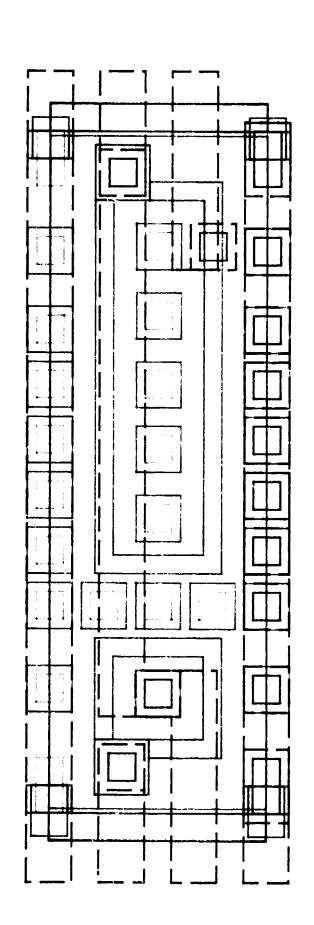

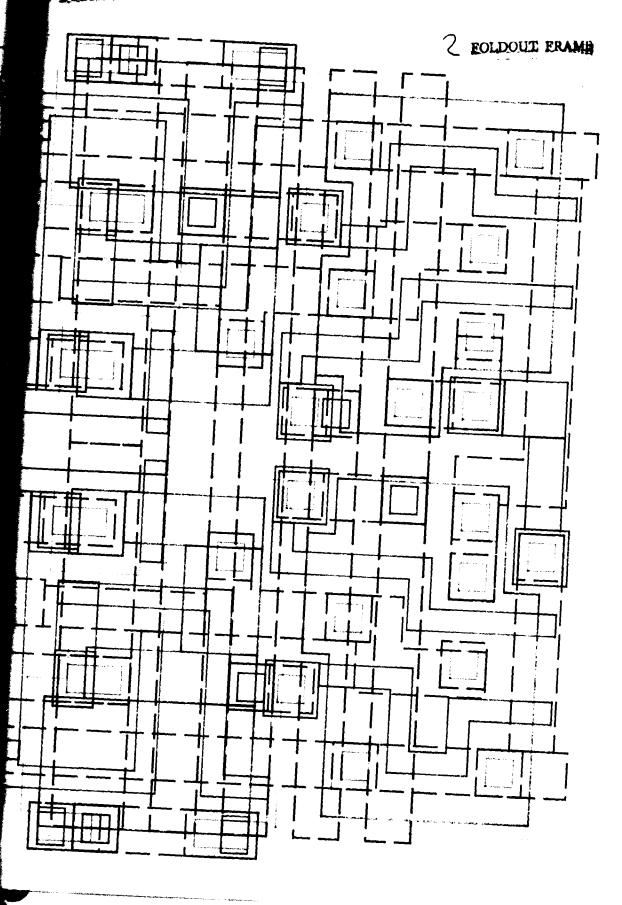

CONTROL BUFFER [ from Y=0 to Y=85 ]

10081

scale: 1001X

## ORIGINAL PAGE COLOR PHOTOGRAPH

9 EDIDOUT ERAME

CONTROL BUFFER [ from Y=85 to Y=150 ]

10082

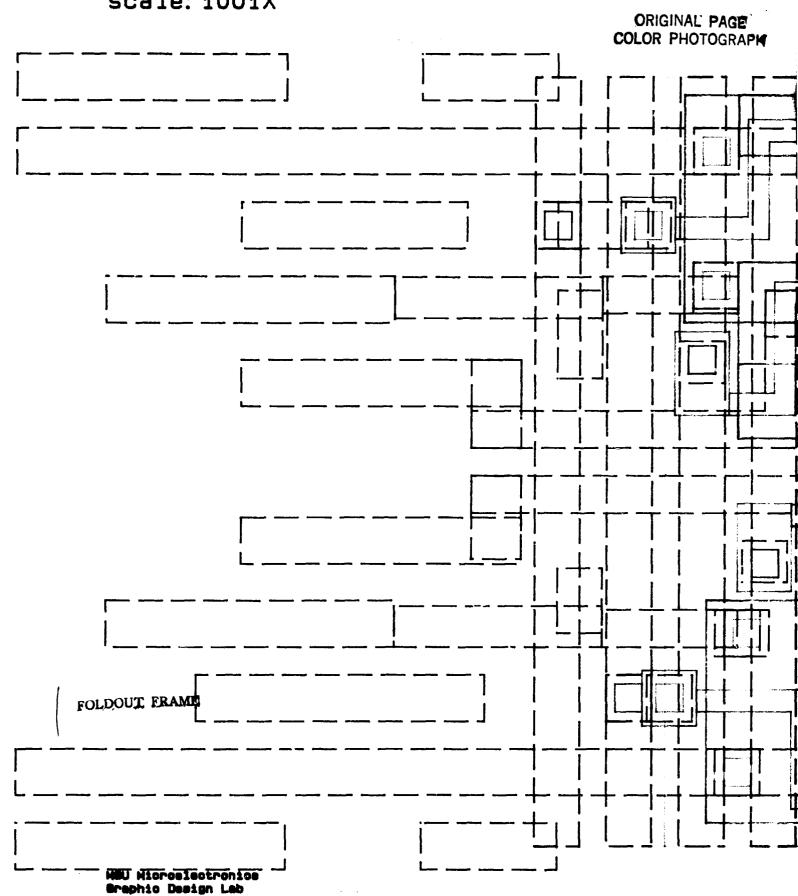

scale: 1001X

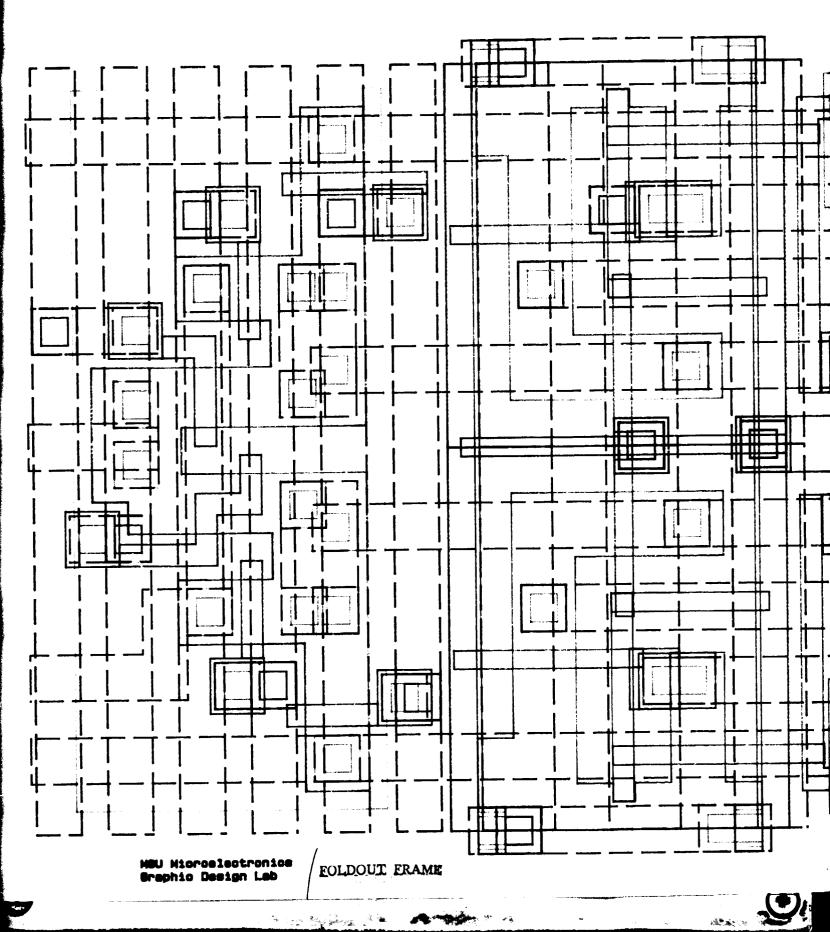

[ from Y=150 to Y=235 CONTROL BUFFER

10083

scale: 1001X

CONTROL BUFFER [ Y=235 to Y=340 ]

10084

scale: 1001X

EOLDOUT FRAME

### ORIGINAL PAGE COLOR PHOTOGRAPH

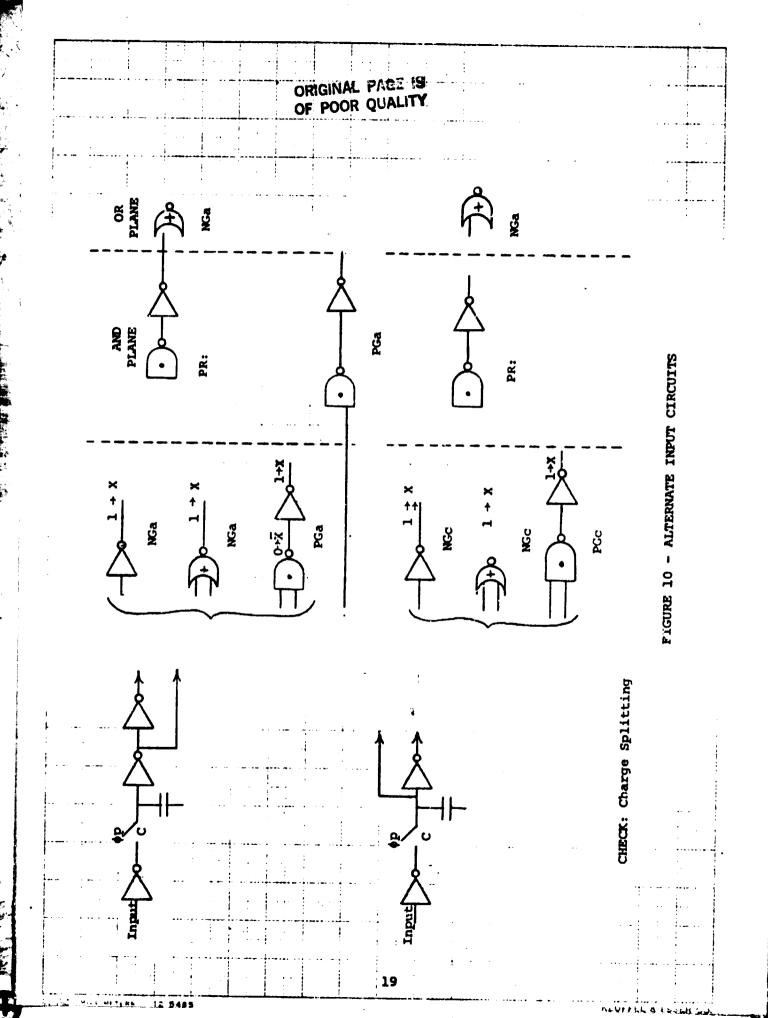

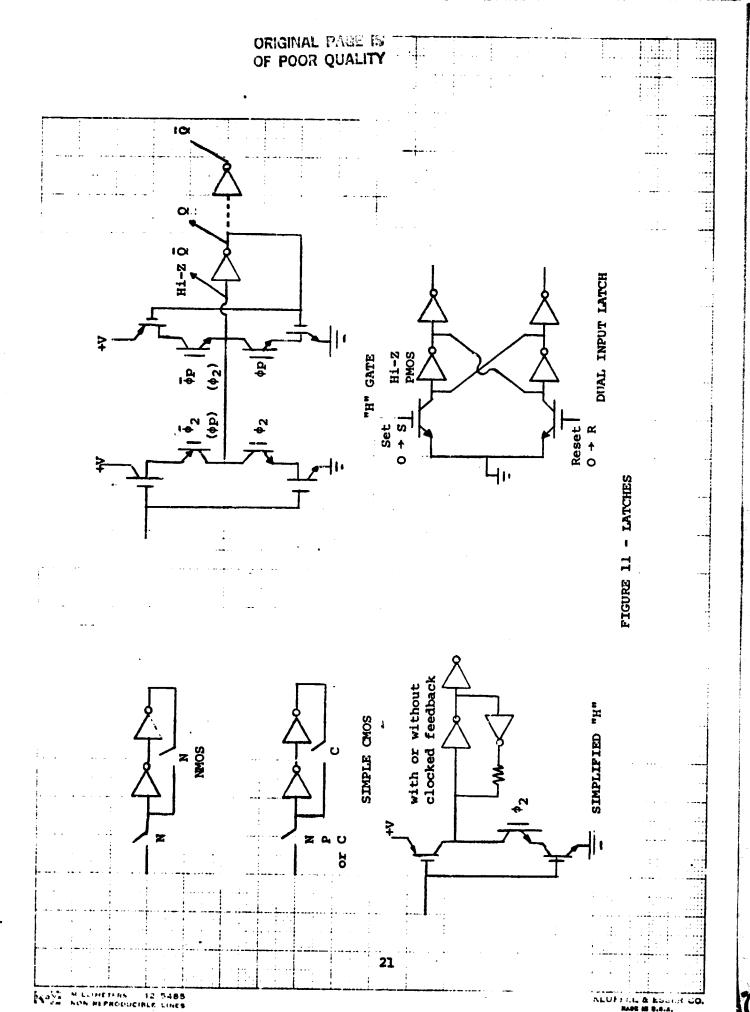

7 EOLDOUT ERAMIN