https://ntrs.nasa.gov/search.jsp?R=19860011001 2020-03-20T15:19:59+00:00Z

**MDC H1343A**

DECEMBER 1985

IBM

(NASA-CR-177839)SPACE STATION DATA SYSTEMN86-20472ANALYSIS/ARCHITECTURE STUDY.TASK 2:OPTIONS DEVELOPMENT DR-5.VCLUME 1:TECHNOLOGY OPTIONS (McDonnell-DouglasUnclasAstronautics Co.)379 p HC A17/MF A01G3/18

NASA CR- 177839

### SPACE STATION DATA SYSTEM ANALYSIS/ARCHITECTURE STUDY

RСЛ

Task 2 – Options Development, DR-5 Volume I – Technology Options

MCDONNELL DOUGLAS ASTRONAUTICS COMPANY-HUNTINGTON BEACH 5301 Bolsa Avenue Huntington Beach, California 92647 (714) 896-3311

### PREFACE

The McDonnell Douglas Astronautics Company has been engaged in a Space Station Data System Analysis/Architecture Study for the National Aeronautics and Space Administration, Goddard Space Flight Center. This study, which emphasized a system engineering design for a complete, end-to-end data system, was divided into six tasks:

- Task 1. Functional Requirements Definition

- Task 2. Options Development

- Task 3. Trade Studies

- Task 4. System Definitions

- Task 5. Program Plan

- Task 6. Study Maintenance

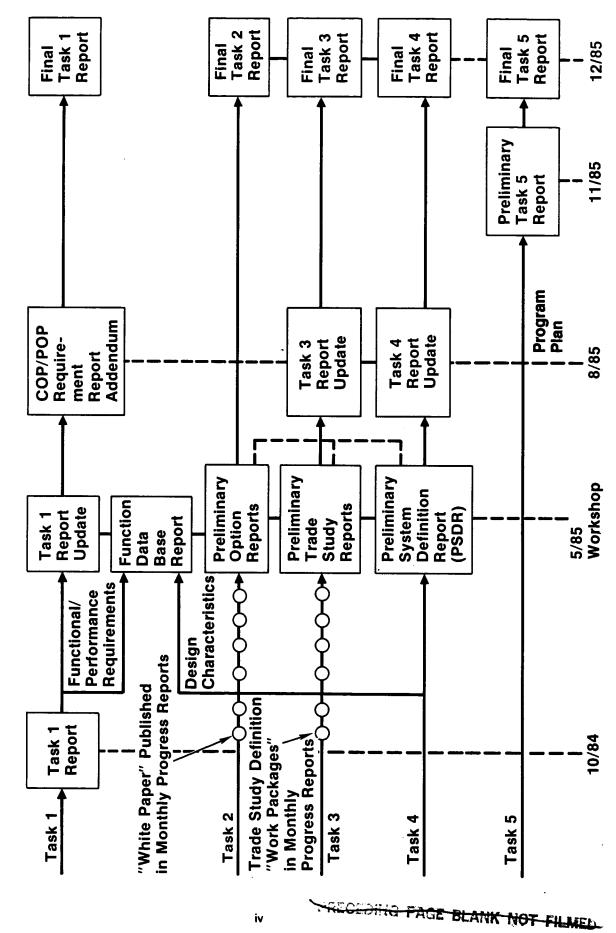

McDonnell Douglas was assisted by the Ford Aerospace and Communications Corporation, IBM Federal Systems Division and RCA in these Tasks. The Task inter-relationship and documentation flow are shown in Figure 1.

This report was prepared for the National Aeronautics and Space Administration Goddard Space Flight Center under Contract No. NAS5-28082

Questions regarding this report should be directed to:

Glen P. Love Study Manager McDonnell Douglas Astronautics Company Huntington Beach, CA 92647 (714) 896-2292

### PRECEDING PAGE BLANK NOT FILMED

**SUSE** MDAC

Figure 1

# SSDS A/A DOCUMENTATION SCHEDULE CO IBM RCA

VHG598

iv

### Task 2, Volume I TABLE OF CONTENTS

- ----

| I                            | ntroduction                          | 1   |

|------------------------------|--------------------------------------|-----|

| 1.0 T                        | echnology Options                    | 6A  |

| 1.1 M                        | ass Storage                          | 7   |

| 1.1.1                        | On-Line Storage (Space)              | 7   |

|                              | 1.1.1.1 Description                  | 7   |

|                              | 1.1.1.2 Option Characterization      | 9   |

|                              | 1.1.1.3 Projected Capabilities       | 18  |

|                              | 1.1.1.4 Comparisons                  | 21  |

|                              | 1.1.1.5 Application                  | 25  |

| 1.1.2                        | On-Line Storage (Ground)             | 27  |

|                              | 1.1.2.1 Description                  | 27  |

|                              | 1.1.2.2 Option Characterization      | 27  |

|                              | 1.1.2.3 Projected Capabilities       | 33  |

|                              | 1.1.2.4 Comparisons                  | 34  |

|                              | 1.1.2.5 Application                  | 36  |

| 1.1.3                        | Off-Line Storage                     | 36  |

|                              | 1.1.3.1 Description                  | 36  |

|                              | 1.1.3.2 Option Characterization      | 37  |

| 1.1.4                        | References                           | 40  |

| 1.2 Man/Machine Interface 45 |                                      |     |

| 1.2.1 Output                 |                                      | 45  |

|                              | 1.2.1.1 Display                      | 45  |

|                              | 1.2.1.2 Speech Synthesis             | 69  |

| 1.2.2                        | Input Controls                       | 80  |

|                              | 1.2.2.1 Manual                       | 80  |

|                              | 1.2.2.2 Speech Recognition           | 98  |

| 1.3 [                        | Data Processing Hardware             | 107 |

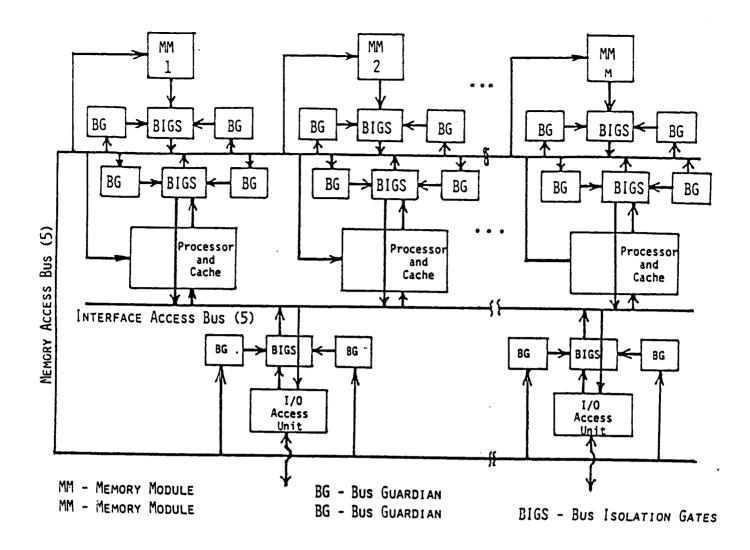

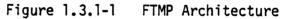

| 1.3.1                        | Fault Tolerant Computer Architecture | 108 |

|                              | 1.3.1.1 Description                  | 108 |

|                              | 1.3.1.2 Option Characterization      | 109 |

|                              | 1.3.1.3 Projected Capabilities       | 116 |

|                              | 1.3.1.4 References                   | 118 |

۷

| TOPIC |  |

|-------|--|

| ر     |  |

| PA | GΕ |

|----|----|

|----|----|

.

| 1.3.2  | Special Purpose Computers                      | 119  |

|--------|------------------------------------------------|------|

| 1.3.2. | 1 Option Characterization                      | 119  |

| 1.3.3  | General Purpose Computers                      | 135  |

|        | 1.3.3.1 Description                            | 135  |

|        | 1.3.3.2 Option Characterization                | 137  |

|        | 1.3.3.3 Projected Capabilities                 | 152  |

| 1.3.4  | Flight Computers                               | 155  |

|        | 1.3.4.1 Description                            | 155  |

|        | 1.3.4.2 Option Characterization                | 158  |

|        | 1.3.4.3 Projected Capabilities                 | 168  |

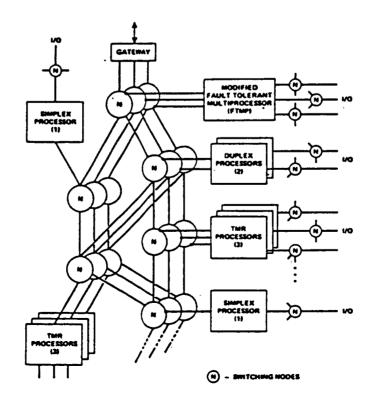

| 1.3.5  | Advanced Computer Architecture                 | 172  |

|        | 1.3.5.1 Discussion                             | 172  |

|        | 1.3.5.2 Options                                | 173  |

|        | 1.3.5.3 References                             | 179  |

| 1.4 S  | oftware                                        | 179A |

| 1.4.1  | Advanced Algorithms                            | 181  |

|        | 1.4.1.1 Data Compression                       | 181  |

| 1.4.2  | On-board Space Station High Order Language     | 219  |

|        | 1.4.2.1 On-board Source Language               | 219  |

| 1.4.3  | Deleted                                        | 241  |

| 1.4.4  | Advanced Tools                                 | 243  |

|        | 1.4.4.1 Automated Code Generation              | 243  |

|        | 1.4.4.2 Automated Code Evaluation/Verification | 248  |

|        | 1.4.4.3 Expert System Builders                 | 250  |

| 1.5 0  | eleted                                         | 253  |

| 1.6 A  | rtificial Intelligence                         | 255  |

| 1.6.1  | Implementation Technology                      | 255  |

|        | 1.6.1.1 Hardware                               | 255  |

|        | 1.6.1.2 Kernel Languages                       | 269  |

|        | 1.6.1.3 Support Environments                   | 271  |

| 1.6.2  | Applications                                   | 279  |

|        | 1.6.2.1 Expert Systems and Problem Solving     | 279  |

|        | 1.6.2.2 Image and Speech Recognition           | 291  |

|        | 1.6.2.3 Natural Language Software              | 294  |

| 1.6.3  | Summary ·                                      | 296  |

| TOPIC                                           | PAGE |

|-------------------------------------------------|------|

| 1.7 Communications                              | 305  |

| 1.7.1 Hard-Wired Communications                 | 307  |

| 1.7.1.1 Network Media for Space Station Program | 309  |

| 1.7.1.2 Network Interface Unit                  | 325  |

| 1.7.2 Deleted                                   | 353  |

### GLOSSARY

| A       | Automatic                                    |

|---------|----------------------------------------------|

| A&R     | Automation and Robotics                      |

| A/A     | Analysis/Architecture                        |

| A/D     | Advanced Development                         |

| A/L     | Airlock                                      |

| A/N     | Alphanumeric                                 |

| AC&S    | Attitude Control System                      |

| ACA     | Attitude Control Assembly                    |

| ACO     | Administrative Contracting Officer           |

| ACS     | Attitude Control and Stabilization           |

| ACS/COM | Attitude Control System/Communications       |

| ACTS    | Advanced Communications Technology Satellite |

| AD      | Ancillary Data                               |

| AD      | Advanced Development                         |

| ADOP    | Advanced Distributed Onboard Processor       |

| ADP     | Advanced Development Plan                    |

| AFOSR   | Air Force Office of Scientific Research      |

| AFP     | Advanced Flexible Processor                  |

| AFRPL   | Air Force Rocket Propulsion Laboratory       |

| AGC     | Automatic Gain Control                       |

| AGE     | Attempt to Generalize                        |

| AI      | Artificiál Intelligence                      |

| AIE     | Ada Integrated Environment                   |

| AIPS    | Advanced Information Processing System       |

| ALI     | Air Lock One                                 |

| ALS     | Alternate Landing Site                       |

| ALS/N   | Ada Language System/Navy                     |

| AMIC    | Automated Management Information Center      |

| ANSI    | American National Standards Institute        |

| AOS     | Acquisition of Signal                        |

| AP      | Automatic Programming                        |

| APD     | Avalanche Photo Diode                        |

| APSE    | Ada Programming Support Environment          |

| ARC     | Ames Research Center                         |

ix

PRECEDING PAGE BLANK NOT FILMED

PAGE WIT INTENTIONALTY BEAM

| ART              | Automated Reasoning Tool                          |

|------------------|---------------------------------------------------|

| ASCII            | American Standard Code for Information Exchange   |

| ASE              | Airborne Support Equipment                        |

| ASTROS           | Advanced Star/Target Reference Optical Sensor     |

| ATAC             | Advanced Technology Advisory Committee            |

| ATC              | Air Traffic Control                               |

| ΑΤΡ              | Authority to Proceed                              |

| ATPS             | Advanced Telemetry Processing System              |

| ATS              | Assembly Truss and Structure                      |

| AVMI             | Automated Visual Maintenance Information          |

| AWSI             | Adoptive Wafer Scale Integration                  |

| В                | Bridge                                            |

| BARC             | Block Adaptive Rate Controlled                    |

| BB               | Breadboard                                        |

| BER              | Bit Error Rate                                    |

| BIT              | Built-in Test                                     |

| BITE             | Built-in Test Equipment                           |

| BIU              | Buffer Interface Unit                             |

| BIU              | Bus Interface Unit                                |

| BIU              | Built-in Unit                                     |

| BMD              | Ballistic Missile Defense                         |

| BTU              | British Thermal Unit                              |

| BW               | Bandwidth                                         |

| ເຼ               | Constrained                                       |

| c <sup>2</sup>   | Command and Control                               |

| c <sup>3</sup>   | Command, Control, and Communication               |

| c <sup>3</sup> i | Command, Control, Communication, and Intelligence |

| C&DH             | Communications and Data Handling                  |

| C&T              | Communication and Tracking Subsystem              |

| C&T              | Communications and Tracking                       |

| C&W              | Control and Warning                               |

| C/L              | Checklist                                         |

| CA               | Customer Accommodation                            |

| CAD              | Computer-Aided Design                             |

| CAE              | Computer-Aided Engineering                        |

| CAIS             | Common APSE Interface Set                         |

| CAM              | Computer-Aided Manufacturing                      |

.

×

| CAMAC             | Computer Automatic Measurement and Control                        |

|-------------------|-------------------------------------------------------------------|

| CAP               | Crew Activities Plan                                              |

| CASB              | Cost Accounting Standard Board                                    |

| CASE              | Common Application Service Elements                               |

| CATL              | Controlled Aceptance Test Library                                 |

| CBD               | Commerce Business Daily                                           |

| CBEMA             | Computer and Business Equipment Manufacturing Association         |

| CCA               | Cluster Coding Algorithm                                          |

| ССВ               | Contractor Control Board                                          |

| ССВ               | Configuration Control Board                                       |

| CCC               | Change and Configuration Control                                  |

| CCD               | Charge-Coupled Device                                             |

| CCITT             | Consultive Committee for International Telegraph and Telephone    |

| CCITT             | Coordinating Committee for International Telephony and Telegraphy |

| CCMS              | Checkout Control and Monitor System                               |

| CCR               | Configuration Change Request                                      |

| CCSDS             | Consultative Committee for Space Data System                      |

| CCTV              | Closed-Circuit Television                                         |

| cd/M <sup>2</sup> | Candelas per square Meter                                         |

| CDG               | Concept Development Group                                         |

| CDMA              | Code Division Multiple Access                                     |

| CDOS              | Customer Data Operations System                                   |

| CDR               | Critical Design Review                                            |

| CDS               | Control Data Subsystem                                            |

| CE                | Conducted Emission                                                |

| CEI               | Contract End-Item                                                 |

| CER               | Cost Estimating Relationship                                      |

| CFR               | Code of Federal Regulations                                       |

| CFS               | Cambridge File Server                                             |

| CG                | Center of Gravity                                                 |

| CIE               | Customer Interface Element                                        |

| CIL               | Critical Item List                                                |

| CIU               | Customer Interface Unit                                           |

| CLAN              | Core Local Area Network                                           |

| CM                | Configuration Management                                          |

| CM                | Center of Mass                                                    |

| CMDB              | Configuration Management Data Base                                |

xi

| CMG        | Control Moment Gyro                                             |

|------------|-----------------------------------------------------------------|

| CMOS       | Complementary Metal-Oxide Semiconductor                         |

| CMS        | Customer Mission Specialist                                     |

| CMU        | Carnegie-Mellon University                                      |

| CO         | Contracting Officer                                             |

| COF        | Component Origination Form                                      |

| COL        | Controlled Operations Library                                   |

| COMM       | Commercial Missions                                             |

| СОР        | Co-orbital Platform                                             |

| COPCC      |                                                                 |

| COPCC      | Coorbit Platform Control Center                                 |

|            | COP Operations Control Center                                   |

| COTS       | Commercial Off-the-Shelf Software                               |

| CPCI       | Computer Program Configuration Item                             |

| CPU        | Central Processing Unit                                         |

| CQL        | Channel Queue Limit                                             |

| CR         | Compression Ratio                                               |

| CR         | Change Request                                                  |

| CR&D       | Contract Research and Development                               |

| CRC        | Cyclic Redundancy Checks                                        |

| CRF        | Change Request Form                                             |

| CRSS       | Customer Requirements for Standard Services                     |

| CRT        | Cathode Ray Tube                                                |

| CS         | Conducted Susceptibility                                        |

| CSD        | Contract Start Date                                             |

| CSDL       | Charles Stark Draper Laboratory                                 |

| CSMA/CD/TS | Carrier-Sense Multiple with Access/Collision Detection and Time |

|            | Slots                                                           |

| CSTL       | Controlled System Test Library                                  |

| CTA        | Computer Technology Associates                                  |

| CTE        | Coefficient of Thermal Expansion                                |

| CUI        | Common Usage Item                                               |

| CVSD       | Code Variable Slope Delta (Modulation)                          |

| CWG        | Commonality Working Group                                       |

| D&B        | Docking and Berthing                                            |

| DADS       | Digital Audio Distribution System                               |

| DAIS       | Digital Avionics Integration System                             |

| DAR        | Defense Acquisition Regulation                                  |

|            |                                                                 |

| DARPA  | Defense Advanced Research Projects Agency         |

|--------|---------------------------------------------------|

| DB     | Data Base                                         |

| DBA    | Data Base Administrator                           |

| DBML   | Data Base Manipulation Language                   |

| DBMS   | Data Base Management System                       |

| DCAS   | Defense Contract Administrative Services          |

| DCDS   | Distributed Computer Design System                |

| DCR    | Data Change Request                               |

| DDBM   | Distributed Data Base Management                  |

| DDC    | Discipline Data Center                            |

| DDT&E  | Design, Development, Testing, and Engineering     |

| DEC    | Digital Equipment Corp.                           |

| DES    | Data Encryption Standard                          |

| DFD    | Data Flow Diagram                                 |

| DGE    | Display Generation Equipment                      |

| DHC    | Data Handling Center                              |

| DID    | Data Item Description                             |

| DIF    | Data Interchange Format                           |

| DMA    | Direct Memory Access                              |

| DMS    | Data Management System                            |

| DoD    | Department of Defense                             |

| DOMSAT | Domestic Communications Satellite System          |

| DOS    | Distributed Operating System                      |

| DOT    | Department of Transportation                      |

| DPCM   | Differential Pulse Code Modulation                |

| DPS    | Data Processing System                            |

| DR     | Discrepancy Report                                |

| DR     | Data Requirement                                  |

| DRAM   | Dynamic Random-Access Memory                      |

| DRD    | Design Requirement Document                       |

| DS&T   | Development Simulation and Training               |

| DSDB   | Distributed System Data Base                      |

| DSDL   | Data Storage Description Language                 |

| DSDS   | Data System Dynamic Simulation                    |

| DSIT   | Development, Simulation, Integration and Training |

| DSN    | Deep-Space Network                                |

| DTC    | Design to Cost                                    |

v

-

xiii

| DTC/LCC | Design to Cost/Life Cycle Cost                         |

|---------|--------------------------------------------------------|

| DTG     | Design To Grow                                         |

| E/R     | Entity/Relationship                                    |

| EADI    | Electronic Attitude Direction Indicator                |

| ECC     | Error Correction Codes                                 |

| ECLSS   | Environmental Control and Life-Support System          |

| ECMA    | European Computers Manufacturing Assoc.                |

| ECP     | Engineering Change Proposals                           |

| ECS     | Environmental Control System                           |

| EDF     | Engineering Data Function                              |

| EEE     | Electrical, Electronic, and Electromechanical          |

| EHF     | Extremely High Frequency                               |

| EHSI    | Electronic Horizontal Situation Indicator              |

| EIA     | Electronic Industry Association                        |

| EL      | Electroluminescent                                     |

| EM      | Electromagnetic                                        |

| EMC     | Electromagnetic Compatibility                          |

| EMCFA   | Electromagnetic Compatibility Frequency Analysis       |

| EME     | Earth Mean Equator                                     |

| EMI     | Electromagnetic Interference                           |

| EMR     | Executive Management Review                            |

| EMS     | Engineering Master Schedule                            |

| EMU     | Extravehicular Mobility Unit                           |

| EMUDS   | Extravehicular Maneuvering Unit Decontamination System |

| EO      | Electro-optic                                          |

| EOL     | End of Life                                            |

| EOS     | Earth Observing System                                 |

| EPA     | Environmental Protection Agency                        |

| EPS     | Electrical Power System                                |

| ERBE    | Earth Radiation Budget Experiment                      |

| ERRP    | Equipment Replacement and Refurbishing Plan            |

| ESR     | Engineering Support Request                            |

| ESTL    | Electronic Systems Test Laboratory                     |

| EVA     | Extravehicular Activity                                |

| F/T     | Fault Tolerant                                         |

| FACC    | Ford Aerospace and Communications Corporation          |

| FADS    | Functionally Automated Database System                 |

xiv

| FAR     | Federal Acquisition Regulation                             |

|---------|------------------------------------------------------------|

| FCA     | Functional Configuration Audit                             |

| FCOS    | Flight Computer Operating System                           |

| FCR     | Flight Control Rooms                                       |

| FDDI    | Fiber Distributed Data Interface                           |

| FDF     | Flight Dynamics Facility                                   |

| FDMA    | Frequency-Division Multiple Access                         |

| FEID    | Flight Equipment Interface Device                          |

| FETMOS  | Floating Gate Election Tunneling Metal Oxide Semiconductor |

| FF      | Free Flier                                                 |

| FFT     | Fast Fourier Transform                                     |

| FIFO    | First in First Out                                         |

| FIPS    | Federal Information Processing Standards                   |

| fl      | foot lambert - Unit of Illumination                        |

| FM      | Facility Management                                        |

| FMEA    | Failure Modes and Effects Analysis                         |

| FMECA   | Failure Mode Effects and Criticality Analysis              |

| FO      | Fiber-Optics                                               |

| FO/FS/R | Fail-Operational/Fail Safe/Restorable                      |

| FOC     | Fiber-Optic Cable                                          |

| FODB    | Fiber-Optic Data Bus                                       |

| FODS    | Fiber Optic Demonstration System                           |

| FPR     | Federal Procurement Regulation                             |

| FQR     | Formal Qualification Review                                |

| FSD     | Full-Scale Development                                     |

| FSE     | Flight Support Equipment                                   |

| FSED    | Full Scale Engineering Development                         |

| FSIM    | Functional Simulator                                       |

| FSW     | Flight Software                                            |

| FTA     | Fault Tree Analysis                                        |

| FTMP    | Fault Tolerant Multi-Processor                             |

| FTSC    | Fault Tolerant Space Computer                              |

| GaAs    | Gallium Arsenide                                           |

| GaAsP   | Gallium Arsenic Phosphorus                                 |

| GaInP   | Gallium Indium Phosphorus                                  |

| GaP     | Gallium Phosphorous                                        |

| GAPP    | Geometric Arithmetic Parallel Processor                    |

|         |                                                            |

.

- ----

•

,

xv

| Gbps       | Gigabits Per Second                           |

|------------|-----------------------------------------------|

| GBSS       | Ground Based Support System                   |

| GEO        | Geosynchronous Earth Orbit                    |

| GEP        | Gas Election Phosphor                         |

| GFC        | Ground Forward Commands                       |

| GFE        | Government-Furnished Equipment                |

| GFP        | Government-Furnished Property                 |

| GFY        | Government Fiscal Year                        |

| GIDEP      | Government/Industry Data Exchange Program     |

| GMM        | Geometric Math Model                          |

| GMS        | Geostationary Meteorological Satellite        |

| GMT        | Greenwich Mean Time                           |

| GMW        | Generic Maintenance Work Station              |

| GN&C       | Guidance, Navigation, and Control             |

| GPC        | General-Purpose Computer                      |

| GPP        | General-Purpose Processor                     |

| GPS        | Global Positioning System                     |

| GRO        | Gamma Ray Observatory                         |

| GSC        | Ground Service Center                         |

| GSE        | ground Support Equipment                      |

| GSFC       | (Robert H.) Goddard Space Flight Center       |

| GTOSS      | Generalized Tethered Object System Simulation |

| H/W        | Hardware                                      |

| HAL        | High-Order Algorithmic Language               |

| HDDR       | Help Desk Discrepancy Report                  |

| HDDR       | High Density Digital Recording                |

| HEP        | Heterogeneous Element Processor               |

| HFE        | Human Factors Engineering                     |

| HIPO       | Hierarchical Input Process Output             |

| HIRIS      | High Resolution Imaging Spectrometer          |

| HMI        | Habitation Module One                         |

| HM         | Habitation Module                             |

| HOL        | High Order Language                           |

| HOS        | High Order Systems                            |

| <b>HPP</b> | High Performance Processors                   |

| HRIS       | High Resolution Imaging Spectrometer          |

| I          | Interactive                                   |

xvi

| I/F    | Interface                                                |

|--------|----------------------------------------------------------|

| 1/0    | Input/Output                                             |

| IBM    | IBM Corporation                                          |

| IC     | Intercomputer                                            |

| ICAM   | Integrated Computer-Aided Manufacturing                  |

| ICB    | Internal Contractor Board                                |

| ICD    | Interface Control Document                               |

| ICOT   | Institute (for new generation) Computer Technology       |

| ICS    | Interpretive Computer Simulation                         |

| ID     | Interface Diagram                                        |

| ID     | Identification                                           |

| IDM    | Intelligent Database Machine                             |

| IDMS   | Information and Data Management System                   |

| IEEE   | Institute of Electrical and Electronic Engineers         |

| IEMU   | Integrated Extravehicular Mobility Unit                  |

| IF     | Intermediate Frequency                                   |

| IFIPS  | International Federation of Industrial Processes Society |

| ILD    | Injector Laser Diode                                     |

| IMU    | Inertial Measurement Unit                                |

| INS    | Inertial Navigation System                               |

| IOC    | Initial Operating Capability                             |

| IOP    | Input/Output Processor                                   |

| IPCF   | Interprocess Communications Facility                     |

| IPC    | Interprocesses Communication                             |

| IPL    | Initial Program Load                                     |

| IPR    | Internal Problem Report                                  |

| IPS    | Instrument Pointing System                               |

| IR     | Infrared                                                 |

| IR&D   | Independent Research and Development                     |

| IRN    | Interface Revision Notices                               |

| ISA    | Inertial Sensor Assembly                                 |

| ISA    | Instruction Set Architecture                             |

| ISDN   | Integration Services Digital Network                     |

| ISO    | International Standards Organization                     |

| ITAC-0 | Integration Trades and Analysis-Cycle O                  |

| ITT    | International Telegraph and Telephone                    |

| IV&V   | Independent Validation and Verification                  |

xvii

| IVA             | Intravehicular Activity                 |

|-----------------|-----------------------------------------|

| IWS             | Intelligent Work Station                |

| JPL             | Jet Propulsion Laboratory               |

| JSC             | (Lyndon B.) Johnson Space Center        |

| KAPSE           | Kernal APSE                             |

| KEE             | Knowledge Engineering Environment       |

| KIPS            | Knowledge Information Processing System |

| KOPS            | Thousands of Operations Per Second      |

| KSA             | Ku-band, Single Access                  |

| KSC             | (John F.) Kennedy Space Center          |

| Kbps            | Kilobits per second                     |

| Kipc            | Thousand instructions per cycle         |

| LAN             | Local-Area Network                      |

| LaRC            | Langley Research Center                 |

| LCC             | Life-Cycle Cost                         |

| LCD             | Liquid Crystal Display                  |

| LDEF            | Long-Duration Exposure Facility         |

| LDR             | Large Deployable Reflector              |

| LED             | Light-Emitting Diode                    |

| LEO             | Low Earth Orbit                         |

| LeRC            | Lewis Research Center                   |

| LIDAR           | Laser-Instrument Distance and Range     |

| LIFO            | Last In First Out                       |

| LIPS            | Logical Inferences Per Second           |

| LISP            | List Processor                          |

| LisP            | List Processor                          |

| LLC             | Logical Link Control                    |

| LMI             | LISP Machine Inc.                       |

| LN <sub>2</sub> | Liquid Nitrogen                         |

| LNĂ             | Low-noise Amplifier                     |

| LOE             | Level of Effort                         |

| LOE             | Low-earth Orbit Environments            |

| LOS             | Loss of Signal                          |

| LPC             | Linear Predictive Coding                |

| LPS             | Launch Processing System                |

| LRU             | Line-Replaceable unit                   |

| LSA             | Logistic Support Analysis               |

|                 | - · · · · ·                             |

xviii

| MMU    | Manned Maneuvering Unit                       |

|--------|-----------------------------------------------|

| MNOS   | Metal-Nitride Oxide Semiconductor             |

| MOC    | Mission Operations Center                     |

| MOI    | Moment of Inertia                             |

| MOL    | Manned Orbiting Laboratory                    |

| MOS    | Metal Oxide Semiconductor                     |

| MPAC   | Multipurpose Application Console              |

| MPS    | Materials, Processing in Space                |

| MPSR   | Multi-purpose Support Rooms                   |

| MRMS   | Mobile Remote Manipulator System              |

| MRWG   | Mission Requirements Working Group            |

| MSFC   | (George C.) Marshall Space Flight Center      |

| MSI    | Medium-Scale Integration                      |

| MSS    | Multispectral Scanner                         |

| MTA    | Man-Tended Approach                           |

| MTBF   | Mean Time Between Failures                    |

| MTTR   | Mean Time to Repair                           |

| MTU    | Master Timing Unit                            |

| NASA   | National Aeronautics and Space Administration |

| NASCOM | NASA Communications Network                   |

| NASPR  | NASA Procurement Regulation                   |

| NBO    | NASA Baseline                                 |

| NBS    | National Bureau of Standards                  |

| NCC    | Network Control Center                        |

| NFSD   | NASA FAR Supplement Directive                 |

| NGT    | NASA Ground Terminals                         |

| NHB    | NASA Handbook                                 |

| NISDN  | NASA Integrated System Data Network           |

| NIU    | Network Interface Unit                        |

| NL     | National Language                             |

| NLPQ   | National Language for Queuing Simulation      |

| 'NMI   | NASA Management Instruction                   |

| NMOS   | N-Channel Metal-Oxide Semiconductor           |

| NMR    | N-Modular Redundant .                         |

| NOS    | Network Operating System                      |

| NS     | Nassi-Schneidermann                           |

| NSA    | National Security Administration              |

|        |                                               |

xx

| NSF         | National Science Foundation                                  |

|-------------|--------------------------------------------------------------|

| NSTS        | National Space Transportation System                         |

| NTDS        | Navy Tactical Data System                                    |

| NTE         | Not To Exceed                                                |

| NTRL        | NASA Technology Readiness Level                              |

| NTSC        | National Television Standards Committee                      |

| Nd:YAG      | Neodynium Yttrium Aluminum Garnet (laser type)               |

| M&O         | Operations and Maintenance                                   |

| 0/B         | Onboard                                                      |

| OASCB       | Orbiter Avionics Software Control Board                      |

| OCN         | Operations and Control Network, Operational Control Networks |

| ODB         | Operational Data Base                                        |

| ODBMS       | Onboard Data Base Management System                          |

| OEL         | Operating Events List                                        |

| OES         | Operating Events Schedule                                    |

| OID         | Operations Instrumentation Data                              |

| OLTP        | On Line Transaction Processing                               |

| OMCC        | Operations Management and Control Center                     |

| OMV         | Orbital Maneuvering Vehicle                                  |

| ONR         | Office of Naval Research                                     |

| ORU         | Orbital Replacement Unit                                     |

| <b>0</b> S  | Operating System                                             |

| OSE         | Orbit Support Equipment                                      |

| <b>0</b> 51 | Open Systems Interconnect                                    |

| OSM         | Orbital Service Module                                       |

| OSSA        | Office of Space Science and Applications                     |

| OSTA        | Office of Space and Terrestrial Application                  |

| OSTDS       | Office of Space Tracking and Data Systems                    |

| ΟΤν         | Orbital Transfer Vehicle                                     |

| P&SA        | Payload and Servicing Accommodations                         |

| P/L         | Payload                                                      |

| PA          | Product Assurance                                            |

| PAM         | Payload Assist Module                                        |

| PASS        | Primary Avionics Shuttle Software                            |

| PBX         | Private Branch Exchange                                      |

| PC          | Personal Computer                                            |

| PCA         | Physical Configuration Audit                                 |

|             |                                                              |

| LSAR     | Logistic Support Analysis Report                            |

|----------|-------------------------------------------------------------|

| LSE      | Language Sensity Editors                                    |

| LSI      | Large-scale Integration                                     |

| LTV      | LTV Aerospace and Defense Company, Vought Missiles Advanced |

|          | Programs Division                                           |

| LZPF     | Level O Processing Facility                                 |

| M        | Manual                                                      |

| μP       | Microprocessor                                              |

| MA       | Multiple Access                                             |

| MA       | Managing Activity                                           |

| MAPSE    | Minimum APSE                                                |

| Mbps     | Million Bits Per Second                                     |

| MBPS     | Million Bits Per Second                                     |

| MCAIR    | McDonnell Aircraft Company                                  |

| MCC      | Mission Control Center                                      |

| MCC      | Microelectronics and Computer Technology Corp.              |

| MCDS     | Management Communications and Data System                   |

| MCM      | Military Computer Modules                                   |

| MCNIU    | Multi-compatible Network Interface Unit                     |

| MDAC-HB  | McDonnell Douglas Astronautics Company-Huntington Beach     |

| MDAC-STL | McDonnell Douglas Astronautics Company-St. Louis            |

| MDB      | Master Data Base                                            |

| MDC      | McDonnell Douglas Corporation                               |

| MDMC     | McDonnell Douglas Microelectronics Center                   |

| MDRL     | McDonnell Douglas Research Laboratory                       |

| MFLOP    | Million Floating Point Operations                           |

| MHz      | Million Hertz                                               |

| MIMO     | Multiple-Input Multiple-Output                              |

| MIPS     | Million (machine) Instructions Per Second                   |

| MIT      | Massachusetts Institute of Technology                       |

| MITT     | Ministry of International Trade and Industry                |

| MLA      | Multispectral Linear Array                                  |

| MMI      | Man Machine Interface                                       |

| MMPF     | Microgravity and Materials Process Facility                 |

| MMS      | Module Management System                                    |

| MMS      | Momentum Management System                                  |

| MMU      | Mass Memory Unit                                            |

|          |                                                             |

xix

| PCA    | Program Change Authorization                       |

|--------|----------------------------------------------------|

| PCM    | Pulse Code Modulation                              |

| PCR    | Program Change Request                             |

| PDP    | Plazma Display Panel                               |

| PDR    | Preliminary Design Review                          |

| PDRD   | Program Definition and Requirements Document       |

| PDRSS  | Payload Deployment and Retrieval System Simulation |

| PILS   | Payload Integration Library System                 |

| PIN    | Personal Identification Number                     |

| PLA    | Programmable Logic Array                           |

| PLAN   | Payload Local Area Network                         |

| PLSS   | Payload Support Structure                          |

| PMAD   | Power Management and Distribution                  |

| PMC    | Permanently Manned Configuration                   |

| PN     | Pseudonoise                                        |

| POCC   | Payload Operations Control Center                  |

| POP    | Polar Orbiter Platform                             |

| POPCC  | Polar Orbit Platform Control Center                |

| POPOCC | POP Operations Control Center                      |

| PRISM  | Prototype Inference System                         |

| PSA    | Problem Statement Analyzer                         |

| PSA    | Preliminary Safety Analysis                        |

| PSCN   | Program Support Communications Network             |

| PSL    | Problem Statement Language                         |

| PTR    | Problem Trouble Report                             |

| QA     | Quality Assurance                                  |

| R      | Restricted                                         |

| R&D    | Research and Development                           |

| R&QA   | Reliability and Quality Assurance                  |

| R/M/A  | Reliability/Maintainability/Availability           |

| R/T    | Real Time                                          |

| RAD    | Unit of Radiation                                  |

| RAM    | Random Access Memory                               |

| RAP    | Relational Associative Processor                   |

| RC     | Ring Concentrator                                  |

| RCA    | RCA Corporation                                    |

| RCS    | Reaction Control System                            |

|        |                                                    |

xxii

| RDB  | relational Data Base                           |

|------|------------------------------------------------|

| RDC  | Regional Data Center                           |

| REM  | Roentgen Equivalent (man)                      |

| RF   | Radio Frequency                                |

| RFC  | Regenerative Fuel Cell                         |

| RFI  | Radio Frequency Interference                   |

| RFP  | Request for Proposal                           |

| RGB  | Red-Green-Blue                                 |

| RID  | Review Item Disposition                        |

| RID  | Revision Item Description                      |

| RISC | Reduced Instruction Set Computer               |

| RMS  | Remote Manipulator System                      |

| RMSE | Root Mean Square Error                         |

| RNET | Reconfiguration Network                        |

| ROM  | Read Only Memory                               |

| ROTV | Reuseable Orbit Transfer Vehicle               |

| RPMS | Resource Planning and Management System        |

| RS   | Reed-Solomon                                   |

| RSA  | Rivest, Skamir and Adleman (encryption method) |

| RTX  | Real Time Execution                            |

| S&E  | Sensor and Effector                            |

| S/C  | Spacecraft                                     |

| S/W  | Software                                       |

| SA   | Single Access                                  |

| SA   | Structured Analysis                            |

| SAAX | Science and Technology Mission                 |

| SAE  | Society of Automotive Engineers                |

| SAIL | Shuttle Avionics Integration Laboratory        |

| SAIS | Science and Applications Information System    |

| SAR  | Synthetic Aperture Radar                       |

| SAS  | Software Approval Sheet                        |

| SASE | Specific Application Service Elements          |

| SATS | Station Accommodations Test Set                |

| SBC  | Single Board Computer                          |

| SC   | Simulation Center                              |

| SCR  | Software Change Request                        |

| SCR  | Solar Cosmic Ray                               |

|      |                                                |

| SCS    | Standard Customer Services                        |

|--------|---------------------------------------------------|

| SDC    | Systems Development Corporation                   |

| SDP    | Subsystem Data Processor                          |

| SDR    | System Design Review                              |

| SDTN   | Space and Data Tracking Network                   |

| SE&I   | Systems Engineering and Integration               |

| SEI    | Software Engineering Institute                    |

| SESAC  | Space and Earth Scientific Advisory Committee     |

| SESR   | Sustaining Engineering System Improvement Request |

| SESS   | Software Engineering Standard Subcommittee        |

| SEU    | Single Event Upset                                |

| SFDU   | Standard Format Data Unit                         |

| SI     | International System of Units                     |

| SIB    | Simulation Interface Buffer                       |

| SIFT   | Software Implemented Fault Tolerance              |

| SIMP   | Single Instruction Multi-Processor                |

| SIRTF  | Shuttle Infrared Telescope Facility               |

| SLOC   | Source Lines of Code                              |

| SMC    | Standards Management Committee                    |

| SMT    | Station Management                                |

| SNA    | System Network Architecture                       |

| SNOS   | Silicon Nitride Oxide Semiconductor               |

| SNR    | Signal to Noise Ratio                             |

| SOA    | State Of Art                                      |

| SOPC   | Shuttle Operations and Planning Complex           |

| SOS    | Silicon On Saphire                                |

| SOW    | Statement of Work                                 |

| SPC    | Stored Payload Commands                           |

| SPF    | Software Production Facility                      |

| SPF    | Single-Point Failure                              |

| SPR    | Spacelab Problem Reports                          |

| SPR    | Software Problem Report                           |

| SQA    | Software Quality Assurance                        |

| SQAM   | Software Quality Assessment and Measurement       |

| SQL/DS | SEQUEL Data System                                |

| SRA    | Support Requirements Analysis                     |

| SRAM   | Static Random Access Memory                       |

••

·

.

-

| SRB    | Software Review Board                                       |

|--------|-------------------------------------------------------------|

| SRC    | Specimen Research Centrifuge                                |

| SREM   | Software Requirements Engineering Methodology               |

| SRI    | Stanford Research Institute                                 |

| SRM&QA | Safety, Reliability, Maintainability, and Quality Assurance |

| SRMS   | Shuttle Remote Manipulator System                           |

| SRR    | System Requirements Review                                  |

| SS     | Space Station                                               |

| SSA    | Structural Systems Analysis                                 |

| SSA    | S-band Single Access                                        |

| SSCB   | Space Station Control Board                                 |

| SSCC   | Station Station Communication Center                        |

| SSCR   | Support Software Change Request                             |

| SSCS   | Space Station communication system                          |

| SSCTS  | Space Station communications and tracking system            |

| SSDMS  | Space Station data management system                        |

| SSDR   | Support Software Discrepancy Report                         |

| SSDS   | Space Station data system                                   |

| SSE    | Software Support Environment                                |

| SSEF   | Software Support Environment Facility                       |

| SSIS   | Space Station Information System                            |

| SSME   | Space Shuttle Main Engine                                   |

| SS0    | Source Selection Official                                   |

| SSOCC  | Space Station Operations Control System                     |

| SSOCC  | Space Station Operations Control Center                     |

| SSOL   | Space Station Operation Language                            |

| SSON   | Spacelab Software Operational Notes                         |

| SSOS   | Space Station Operating System                              |

| SSP    | Space Station Program                                       |

| SSPE   | Space Station Program Element                               |

| SSPO   | Space Station Program Office                                |

| SSSC   | Space Station Standard Computer                             |

| SSST   | Space Station System Trainer                                |

| STAR   | Self Test and Recovery (repair)                             |

| STARS  | Software Technology for Adaptable and Reliable Software     |

| STDN   | Standard Number                                             |

| STI    | Standard Technical Institute                                |

xxv

~

| STO              | Solar Terrestrial Observatory                   |

|------------------|-------------------------------------------------|

| STS              | Space Transportation System                     |

| SUSS             | Shuttle Upper Stage Systems                     |

| SYSREM           | System Requirements Engineering Methodology     |

| Si               | Silicon                                         |

| SubACS           | Submarine Advanced Combat System                |

| TAI              | International Atomic Time                       |

| TBD <sup>.</sup> | To Be Determined                                |

| TBU              | Telemetry Buffer Unit                           |

| TC               | Telecommand                                     |

| TCP              | Transmissions Control Protocols                 |

| TCS              | Thermal Control System                          |

| TDASS            | Tracking and Data Acquisition Satellite System  |

| TDM              | Technology Development Mission                  |

| TDMA             | Time-Division Multiple Access                   |

| TDRS             | Tracking and Data Relay Satellite               |

| TDRSS            | Tracking and Data Relay Satellite System        |

| TFEL             | Thin Film Electrolumenescent                    |

| THURIS           | The Human Role in Space (study)                 |

| TI               | Texas Instruments                               |

| ТМ               | Technical Manual                                |

| ТМ               | Thematic Mapper                                 |

| TMDE             | Test, Measurement, and Diagnostic Equipment     |

| TMIS             | Technical and Management Information System     |

| TMP              | Triple Multi-Processor                          |

| TMR              | Triple Modular Redundancy                       |

| TMS              | Thermal Management System                       |

| TPWG             | Test Planning Working Group                     |

| TR               | Technical Requirement                           |

| TRAC             | Texas Reconfigurable Array Computer             |

| TRIC             | Transition Radiation and Ionization Calorimeter |

| TSC              | Trade Study Control                             |

| TSIP             | Technical Study Implementation Plan             |

| TSP              | Twisted Shielded Pair                           |

| TSS              | Tethered Satellite System                       |

| TT&C             | Telemetry, Tracking, and Communications         |

| TTC              | Telemetry Traffic Control                       |

|                  |                                                 |

| TTR   | Timed Token Ring                     |

|-------|--------------------------------------|

| TWT   | Traveling-Wave Tube                  |

| U     | Non-restrictive                      |

| UCC   | Uniform Commercial Code              |

| UDRE  | User Design Review and Exercise      |

| UIL   | User Interface Language              |

| UON   | Unique Object Names                  |

| UPS   | Uninterrupted Power Source           |

| URN   | Unique Record Name                   |

| UTBUN | Unique Telemetry Buffer Unit Name    |

| UTC   | Universal Coordinated Time           |

| V&V   | Validation and Verification          |

| VAFB  | Vandenberg Air Force Base            |

| VAX   | Virtual Address Exchange             |

| VHSIC | Very High-Speed Integrated Circuit   |

| VLSI  | Very Large-Scale Integration         |

| VLSIC | Very Large-Scale Integrated Circuit  |

| VV&T  | Validation, Verification and Testing |

| WAN   | Wide Area Network                    |

| WBS   | Work Breakdown Structure             |

| WBSP  | Wideband Signal Processor            |

| WDM   | Wavelength Division Multiplexing     |

| WP    | Work Package                         |

| WRO   | Work Release Order                   |

| WS    | Workstation                          |

| WSGT  | White Sands Ground Terminal          |

| WTR   | Western Test Range                   |

| XDFS  | XEROX Distributed File System        |

| YAPS  | Yet Another Production System        |

| ZOE   | Zone Of Exclusion                    |

| ZONC  | Zone Of Non-Contact                  |

| ZnS   | Zinc Sulfide                         |

|       |                                      |

٠

### Volume I TASK 2 - OPTIONS DEVELOPMENT

### INTRODUCTION

The primary objective of Task 2 is the development of an information base that will support the conduct of trade studies (Task 3) and provide sufficient data to make key design/programmatic decisions (Tasks 4 & 5). This includes: (1) the establishment of option categories that are most likely to influence SSDS definition; (2) the identification of preferred options in each category; and (3) the characterization of these options with respect to performance attributes, constraints, cost and risk.

The definition of option categories was accomplished using hierarchial structures derived primarily from technology, system design, or programmatic perspectives. Technology option categories include advanced materials. processes and techniques that can be used to enhance the implementation of SSDS design structures. Design option categories include alternative structures, configurations and techniques that can be used to develop designs that are responsive to the SSDS requirements. Programmatic option categories include methods used to administrate/manage the development operation and maintenance of the SSDS. Programmatic options are important in that they tend to constrain design/technology decisions to cost-effective and timely solutions. It should be noted that with this method of option categorization, certain disciplines may be split across technology, design and programmatic areas. For example, software categories are included in all three. Technology oriented categories for software include such items as advanced tools and algorithms while design oriented categories include data base management and operating systems. Software development is addressed under programmatic options. The MDAC study team categorization approach and its structure is summarized in Table 1. It is intended to facilitate completeness, avoid replication, and support ease of use. The technology, design and programmatic options are each bound in separate volumes for ease of review. This draft is a collection of "white papers" each of which addresses a single option subject. This volume (I) addresses the generic approach and

### TABLE 1

## SSOS OPTIONS

3.1 Standardization/Commonality

3.2 System Management

3.0 PROGRAMMATIC OPTIONS

| VOLUME I                                        | VOLUME II                          | VOLUME III     |

|-------------------------------------------------|------------------------------------|----------------|

| 1.0 TECHNOLOGY OPTIONS                          | 2.0 DESIGN OPTIONS                 | 3.0 PROGRAMMA1 |

| l.l Mass Storage                                | 2.1 Software                       | 3.1 Standard   |

| 1.2 Man/Machine Interface                       | 2.1.1 Data Base Management         | 3.2 System Má  |

| 1.3 Data Processing Hardware                    | 2.1.2 Resource Management          | * 3.3 Deleted  |

| 1.4 Software                                    | 2.2 System Architecture            | * 3.4 Deleted  |

| 1.4.1 Advanced Algorithms                       | 2.2.2 Autonomy/Automation          | 3.5 System De  |

| 1.4.2 High Order Languages                      | 2.2.3 System Growth                | 3.5.1 Hardwai  |

| *1.4.3 Deleted                                  | * 2.2.4 Deleted                    | 3.5.2 Softwai  |

| 1.4.4 Advanced Tools                            | 2.2.5 System Interfaces            | 3.5.3 System   |

| -14                                             | 2.2.5.1 SSDS/Payload               | Verlfic        |

| <pre>&gt;&gt; 1.6 Artificial Intelligence</pre> | * 2.2.5.2 Deleted                  |                |

| 1.7 Communications                              | 2.2.5.3 Man/Machine I/F            |                |

| 1.7.1 Hard-Wired Communications                 | (Workstations)                     |                |

| 1.7.1.1 Network Media                           | * 2.2.5.4 Deleted                  |                |

| 1.7.1.2 Network I/F Devices                     | 2.3 System Security/Privacy        |                |

| *l.7.2 Deleted                                  | 2.4 Time Management                |                |

|                                                 | 2.5 Communications                 |                |

|                                                 | 2.5.1 Space Communications         |                |

|                                                 | 2.5.2 Wide Area Communications     |                |

|                                                 | 2.5.3 Local Area Networking        |                |

|                                                 | 2.6 Network Performance Assessment | nt             |

|                                                 |                                    |                |

System Integration Test &

Verification

**3.5.1 Hardware Procurement**

3.5 System Development

Software Development

\* These items have been deleted or incorporated into other sections.

methodology for the Technology Options listed in Table 1. Volumes II and III address the detailed options development for the Design and Programmatic Options, respectively.

The options which were identified within each major category are those considered most likely to influence SSDS design/programmatic decisions and/or enhance SSDS capabilities. This screening process is based on an assessment of the key driving requirements (Task 1) as well as the emerging architectural needs (Task 4). The level of option characterization varies across the different categories depending on study needs and perceived criticality. Some categories are much easier to characterize in terms of quantitative parameters than others. For example, most technology options are more conducive to quantitative measurement (i.e., size, power, reliability, capacity, throughput, cost, etc.), however, the characterization of these categories must include projected capabilities for both IOC and growth phases.

### TASK APPROACH

The Task 2 options development activity was initiated early in the study to: (1) facilitate data gathering in high-technology areas that require long-lead-time efforts; (2) provide supporting design and technology perspective to Task 1 activities; and (3) support an early extraction of design/development drivers. However, options development should be done within the context of a system design structure that is derived from a comprehensive understanding of the requirements. This provides a firm basis for focusing options development on the more critical architectural needs. To accommodate the evolving needs of the study from requirements definition to the initial phases of system design while allowing early data gathering efforts to be initiated, required a highly adaptive approach.

This section will describe the following steps that define the task methodology and approach. The key steps include:

- 1. Establish an early baseline options list structure.

- 2. Establish a prioritized options list structure.

- 3. Identify options in high-priority categories.

- 4. Characterize options.

- 5. Document option categories.

- 6. Review and validation.

Early in the study a baseline options list structure was developed. The intent was to create a broad hierarchial framework that would not preclude potential solutions merely by omission. This required a somewhat independent and innovative viewpoint that did not introduce pre-conceived biases. This "baseline" structure also provided a highly visible mechanism to force conscious decisions as to the applicability and criticality of the various option categories. The top-level outline of this "baseline" structure has been retained even though study needs have dictated changes at the lower levels.

A "prioritized" options list structure was then derived form the "baseline" that recognized the needs of Tasks 3 & 4 in terms of their schedule, areas of emphasis, and key characterization parameters. This required significant interaction with these tasks to insure that a sufficient options data base will be available at the appropriate time. This is an evolving and continuing process that provides the basis for "bounding" and time phasing task 2 activities.

Initially, representative options were identified within the baseline options list structure to illustrate the intent of each category. This supported the refinement of the structure and supported the prioritization process. Once efforts were initiated for a high-priority category, the list of options was refined and screened to focus on driving requirements and evolving architectural needs. This process is essentially a coarse filter applied to a broad spectrum of alternatives to derive a "manageable" subset that can support key design decision extraction or provide the basis for a detailed trade study.

Once a refined set of options had been established for a prioritized category, option characterization and data gathering efforts were initiated. The characterization parameters vary significantly for different categories and were established/coordinated based on study needs (Tasks 3 & 4). Data gathering was based on a multitude of input sources including the following:

- Literature Searches

- Team-wide Expertise

- Technical Conferences

- NASA System and Technology Study Documentation

- Industry/Government Standards

- Team Research and Development

- NASA R&D and Testbed Activities

- Personal contacts with NASA, Industry and DoD Experts

- Review of Major DoD Initiatives (VHSIC, Ada/APSE, STARS, DARPA activities, etc.)

- Academia Programs

A key factor in characterizing technology options is the need to include realistic projections of capabilities that are likely to exist for IOC and future growth potential. This provides the foundation to develop SSDS designs that: (1) minimize the "technology gap" for initial development; (2) accommodate technological growth during the life time of the Space Station; and (3) support planned transitions to more autonomous/automated operations. In addition, such projections will play a key role in overall technology assessments that will result in specific recommendations for SSDS technology development and/or enhancement. Related technology development programs currently in process or planned for the near future will be of particular interest and provides valuable near-term insight. Long-term projections are more difficult and uncertain but are no less important because of their influence on growth and technology accommodation planning.

All major option categories have been documented in the form of preliminary "white papers" and included in the monthly progress reports for NASA review and comment. This form of documentation is based on a generic format that

included the identification of key driving requirements, a brief description of the options, option characterization and projected capabilities. We used this method of documentation and review to accomplish the following objectives:

- a. Facilitate Team coordination and review.

- b. Solicit contributions from all available sources including related NASA activities.

- c. Identify areas of deficiency for which specialized support may be required.

- d. Provide a mechanism to support early NASA review and allow maximum visibility.

Most option categories have been documented and submitted to NASA for review. The material provided in this appendix is a compilation of these preliminary "white papers" incorporating those NASA comments received prior to April 1, 1985.

### SUMMARY

The preliminary task 2 (options development) documentation included in this Appendix has been organized using the outline and numbering scheme of the options list structure provided in Table 1. However, some sections have been deleted or incorporated within other sections during the course of the study and are so identified. This documentation was previously provided to NASA in the form of individual "white papers" (monthly progress reports) for preliminary review. The material contained in Volumes I, II, and III of this report represents a partial update to the preliminary "white papers". That is, attempts have been made to update sections to reflect those NASA review comments that were received in time for incorporation. This material is still considered to be preliminary in nature and will be updated prior to the formal Task 2 submittal.

1.0 TECHNOLOGY OPTIONS

1.1 MASS STORAGE

This section describes the technology options for mass storage and includes the major categories of (1) on-line storage (space), (2) on-line storage (ground), and (3) off-line storage (archive). On-line storage is divided into space/ground categories because of significant differences in both the driving requirements and the applicable technologies. As used here, "on-line storage" refers to devices that provide on-line computer access to mass storage capabilities without direct human intervention. "Off-line storage" implies some level of long-term data archiving, generally requiring intermediate processes before data can be stored or retrieved. Not included in this section is the memory storage that is considered to be an integral part of a processing element. However, memory devices may be included as an option if they provide sufficient shareable resources to be considered as "mass storage."

1.1.1 On-Line Storage (Space)

1.1.1.1 <u>Description</u>. This category includes the onboard storage technology that is potentially applicable in one or more of the following areas:

- a. High speed/capacity buffering of downlink data to accommodate link bandwith and availability.

- b. Rapid access storage for on-board data base management capability.

- c. Recording capability for media that can be transported to space or to ground via Shuttle Transport System (STS).

- d. High speed, moderate capacity devices that can be used for temporary storage, caches, or other specialized needs.

The onboard operational environment imposes additional unique requirements for mass storage systems. This includes space radiation, electro-magnetic interference, reliability, and constraints on physical size, weight, and power consumption. The option characteristics developed in this section reflect the importance of these environments (i.e. size, weight, power, radiation hardness, etc.).

Of particular importance is the radiation environment. While most mass storage media (i.e. magnetic tape, optical disk, magnetic disk, magnetic bubble) are inherently hard for anticipated levels, required support electronics might be more susceptable and need to be designed for radiation hardness or shielded in order to insure data quality.

The radiation environment consists of cosmic rays, the Van Allen Belt, and other sources of charged particles that significantly influence the selection of space qualified mass storage devices. This environment will result in total dose and single event (SEU) phenomena that can cause performance degradation, failure or logic "upset" in commercial components. This environment varies considerably with platform altitude and inclination and is statistical in nature due to the variations in proton flux of solar flares. The total dose environment is highest for a polar orbit (POP). The total dose per year is expected to be between 2000 and 25,000 Rads/year depending on solar conditions. Therefore, a reasonable total dose specification would be approximately 100,000 Rads for equipment expected to operate for 10 years. Lower levels of total dose may be specified if natural or intentional shielding is provided.

Heavy ions and energetic protons can cause upset of single locations in electronic circuitry, most notably in memory devices. These upsets are expected to become more critical as the feature size of the devices decrease and the complexity of the device increase. The degree to which these single event errors can be tolerated depends largely of the criticality of the application. For most mass storage applications, design/cost tradeoffs will determine the appropriate mechanism for operation in this enviroment (i.e. decreased component/media susceptability, error detection and correction coding, etc.). Expected upset rates can be calculated and designed around with reasonable confidence. Refer to section 3.5.1 for details on the space radiation environment model and appropriate alternatives for hardware space qualification.

The options described in this category are not restricted to current space qualified technology and includes those areas where such technology development has been initiated or significant potential is indicated for future development. The options in this category include:

- Magnetic Tape

- Magnetic Disk

- Optical Disk

- Bubble Memory

- Semiconductor

### 1.1.1.2 Option Characterization

### 1.1.1.2.1 Magnetic Tape (HDDR)

"High Density Digital Recording" (HDDR) is an option because it provides data storage at high density and at high speed on the magnetic tape media. These are characteristics appropriate for certain SSDS onboard mass storage requirements (i.e. buffering, etc.).