January 1987

DAA/ LANGLEY

UILU-ENG-87-2209 CSG-60

COORDINATED SCIENCE LABORATORY

110-61

College of Engineering

64833 TOR

P.86

# A PARALLEL SIMULATED ANNEALING ALGORITHM FOR STANDARD CELL PLACEMENT ON A HYPERCUBE COMPUTER

Mark Howard Jones

(NASA-CR-180676) A PARALLEL SIMULATED

ANNEALING ALGORITHM FOR STANDARD CELL

PLACEMENT ON A HYPERCUEE CONFUTER (Illinois

Univ.) 86 p Avail: NTIS HC A05/MF A01 Unclas

CSCL 09B G3/61 0064833

| 1月547432 UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

# A PARALLEL SIMULATED ANNEALING ALGORITHM FOR STANDARD CELL PLACEMENT ON A HYPERCUBE COMPUTER

BY

# MARK HOWARD JONES

B.S., Michigan State University, 1985

# THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1987

Urbana, Illinois

#### ABSTRACT

A parallel processing algorithm for standard cell placement suitable for execution on a hypercube computer is presented. In the past there have been proposed several parallel algorithms for performing module placement that are suitable for execution on a two-dimensional array of processors. These algorithms had several limitations; namely, they got stuck at local minima, were susceptible to oscillation, could not handle variable size modules (standard cells), and allowed only nearest neighbor exchanges. Recently, simulated annealing, a general purpose method of multivariate optimization, has been applied to solve the standard cell placement problem on conventional uniprocessor computers. These algorithms do not get stuck at local minima and can handle modules of various sizes, but take an enormous amount of time to execute. In this thesis, a parallel version of the simulated annealing algorithm is presented which is targeted to run on a hypercube computer. A strategy for mapping the cells in a two-dimensional area of a chip onto processors in an n-dimensional hypercube is proposed such that both small and large distance moves can be applied. Two types of moves are allowed: cell exchanges and cell displacements. The computation of the cost function in parallel among all the processors in the hypercube is described along with a distributed data structure that needs to be stored in the hypercube to support parallel cost evaluation. A novel tree broadcasting strategy is used extensively in the algorithm for updating cell locations in the parallel environment. Studies on the performance of the algorithm on example industrial circuits show that it is faster and gives better final placement results than the uniprocessor simulated annealing algorithms. An improved uniprocessor algorithm is proposed which is based on the improved results obtained from parallelization of the simulated annealing algorithm. This enhanced algorithm, through the use of nonuniformly distributed moves and slightly outdated placement data, is found to be less likely to get stuck at local minima, and is found to converge to a better final placement for a variety of industry standard circuits.

PAGE INTENTIONALLY BLANK

# **ACKNOWLEDGEMENT**

I wish to acknowledge the help of my advisor, Prithviraj Banerjee, in critiquing and providing helpful insight and information in the development of this thesis.

# TABLE OF CONTENTS

| CHAPTER                                     | PAGE |

|---------------------------------------------|------|

| 1. INTRODUCTION                             | 1    |

| 1.1. Motivation                             | 1    |

| 1.2. Previous Research                      | 2    |

| 1.3. Thesis Outline                         | . 5  |

| 2. HYPERCUBE CONCURRENT PROCESSORS          | 6    |

| 2.1. Introduction                           | . 6  |

| 2.2. Hypercube Message-Passing Architecture | . 8  |

| 2.2.1. Hypercube interconnection network    | . 8  |

| 2.2.2. Processing nodes                     | . 11 |

| 2.2.3. Distributed software                 | . 12 |

| 2.3. Current and Future Hypercube Systems   | . 13 |

| 2.3.1. Commercial systems                   | . 14 |

| 2.3.2. Experimental systems                 | . 16 |

| 2.3.3. Comparison and benchmarks            | . 17 |

| 2.4. Hypercube Simulator                    | . 18 |

| 3. PARALLEL ALGORITHM FOR CELL PLACEMENT    | . 21 |

| 3.1. Simulated Annealing Algorithm          | . 21 |

| 3.2. Overview of Parallel Algorithm         | . 23 |

| 3.3. Cell Assignment to Processors          | 2.4  |

| CHAPTER                                        | PAGE |

|------------------------------------------------|------|

| 3.4. Distributed Data Structure                | . 25 |

| 3.5. Cost Function                             | . 27 |

| 3.6. Move Generation                           | . 29 |

| 3.7. Discussion of Moves                       | . 29 |

| 3.7.1. Mastership selection                    | . 29 |

| 3.7.2. Selection of move                       | . 29 |

| 3.7.3. Cost calculation of exchange class move | . 32 |

| 3.7.4. Cost calculation for displacements      | . 33 |

| 3.8. Annealing Schedule                        | 33   |

| 3.9. Broadcasting New Cell Locations           | 37   |

| 4. ALGORITHM IMPLEMENTATION AND PERFORMANCE    | 40   |

| 4.1. Implementation                            | 40   |

| 4.2. Placement Results                         | 40   |

| 4.3. Timing Estimates                          | 41   |

| 4.3.1. Computation                             | 44   |

| 4.3.2. Communication costs                     | 44   |

| 4.3.3. Expected speedup                        | 46   |

| 5. IMPROVED UNIPROCESSOR ALGORITHM             | 49   |

| 5.1. Introduction                              | 49   |

| 5.2. Overview of New Algorithm                 | 49   |

| 5.3. Use of Pseudoparallel Moves               | 50   |

# LIST OF TABLES

| Tabl         | le                                                                                   | Page |

|--------------|--------------------------------------------------------------------------------------|------|

| 2.1.         | Hardware capability comparison for various systems                                   | 18   |

| 3.1.         | Variation of alpha with temperature                                                  | 34   |

| 3.2.         | Suggested attempts per cell for various size circuits                                | 36   |

| 3.3.         | Broadcast steps for three-dimensional hypercube on a message from nodes 1, 2, and 7  |      |

|              |                                                                                      | 39   |

| 4.1.         | Placement wiring length comparison                                                   | 43   |

| 4.2.         | Move timing requirements on MC68020 in milliseconds                                  | 44   |

| 4.3.         | Move timing requirements on 80286 in milliseconds                                    | 45   |

| 4.4.         | Memory usage for standard circuits                                                   | 46   |

| 4.5.         | Estimate of time to complete the four types of moves in milliseconds using Intel hy- |      |

|              | percube                                                                              | 47   |

| 4.6.         | Time to complete 32 moves in milliseconds                                            | 48   |

| 5.1.         | Example window specifications                                                        | 53   |

| 5.2.         | Cost vs number of multiple moves for 64-cell circuit                                 | 55   |

| 5.3.         | . Comparison of final cost for using or not using 16 multiple moves                  | 56   |

| 5.4.         | . Comparison of cost vs distribution for (1:4) double window                         | 56   |

| 5.5.         | . Comparison of cost vs distribution for (1:1/2) double window                       | 56   |

| 5.6.         | . Comparison of cost vs distribution for (1:%) double window                         | 57   |

| <b>5.7</b> . | . Comparison of cost vs distribution for (1:1/3) double window                       | 57   |

| 5.8.         | . Comparison of cost vs distribution for (1:2/3) double window                       | 57   |

|              | . Comparison of cost vs distribution for (1:2/3:1/3) triple window                   | 58   |

| Table |                                                                          | Page |  |

|-------|--------------------------------------------------------------------------|------|--|

| 5.10. | Comparison of cost vs distribution for (1: 4: 1/2: 1/4) quadruple window | 58   |  |

| 5.11. | Comparison of cost vs windowing scheme for industry standard circuits    | 61   |  |

# LIST OF FIGURES

| Figu | re                                                               | Page |

|------|------------------------------------------------------------------|------|

| 1.1. | Example standard cell VLSI layout                                | 2    |

| 2.1. | Three-dimensional hypercube                                      | 8    |

| 2.2. | Four-dimensional hypercube (16 processing nodes)                 | 9    |

| 2.3. | Six-dimensional hypercube (64 processing nodes)                  | 10   |

| 2.4. | Subnetworks of four-dimensional hypercube                        | 11   |

| 3.1. | Area map of 64-processor hypercube                               | 26   |

| 3.2. | Example net and corresponding memory structure                   | 28   |

| 3.3. | Cost function evaluation                                         | 30   |

| 3.4. | Parallel moves in the hypercube                                  | 31   |

| 3.5. | Three-dimensional hypercube                                      | 39   |

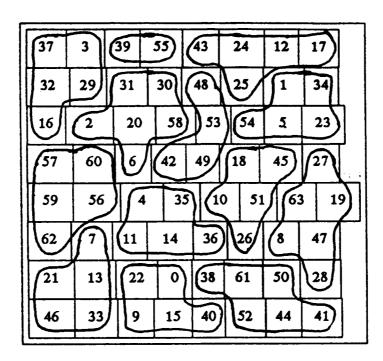

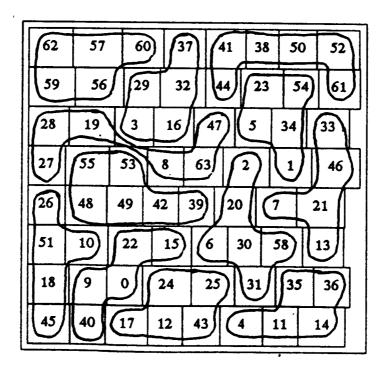

| 4.1. | Cell placement with 16-processor hypercube                       | 42   |

| 4.2. | Cell placement with uniprocessor TimberWolf                      | 42   |

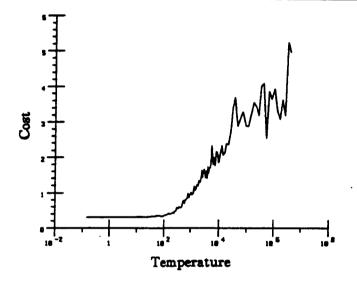

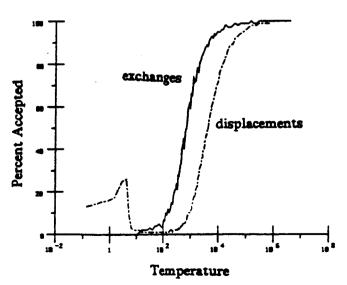

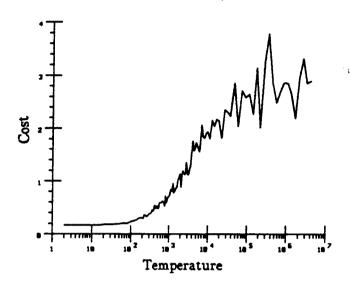

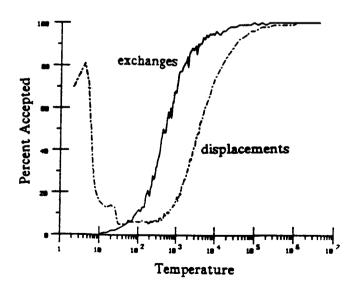

| 4.3. | Temperature vs cost                                              | 43   |

| 4.4. | Temperature vs percentage accepted moves                         | 43   |

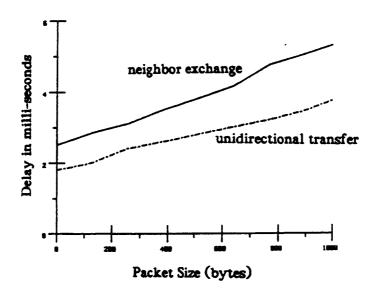

| 4.5  | Link delay for various packet sizes                              | 45   |

| 5.1. | Improved simulated annealing algorithm                           | 50   |

| 5.2  | Original net placement                                           | 51   |

| 5.3  | Placement after initial acceptance                               | 51   |

| 5.4  | Example use of windowing in determining cell movement for cell M | 53   |

| 5.5  | . Temperature vs cost                                            | 60   |

| 5.6  | . Temperature vs percentage accepted moves                       | 60   |

| Figure                                                              |    |

|---------------------------------------------------------------------|----|

| 5.7. Cell placement with windowing and multiple moves               | 62 |

| 5.8. Cell placement with conventional simulated annealing algorithm | 62 |

|                                                                     |    |

.

e ann

#### CHAPTER 1

#### INTRODUCTION

#### 1.1. Motivation

As the complexity of digital systems implemented in VLSI increases, there is a greater need for automating the design of the layout for these systems. One of the areas of VLSI design automation which has received substantial attention in recent years is in researching algorithms for determining the placement of simple cells or modules in a VLSI design. The placement problem consists of finding an optimum assignment of N modules on a board with respect to some criterion prescribed on the interconnections of these modules, such as minimal wire length or signal propagation delays. The terms "module" and "board" are used as generic terms and apply equally well to all circuit levels. The physical design of computers includes several distinct categories of placement problems, depending on the type of packages involved.

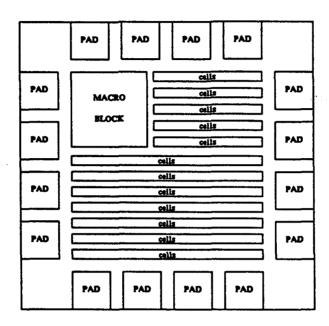

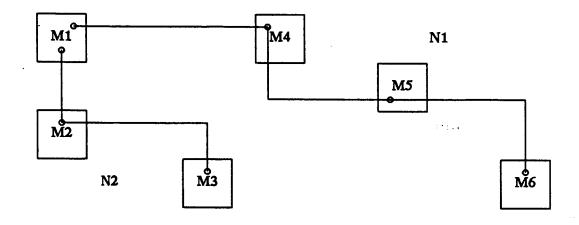

The simplest placement problems arise in designing chips with structured layout rules. In these "gate array" chips, standard logic circuits, such as three- or four-input NOR's, are preplaced in a regular grid arrangement [1, 2]. The designer specifies only the signal wiring, which occupies the final, highest layers of the chip. In more general VLSI design, the standard cell layout is such that a set of standard cells of constant height and variable width are arranged in horizontal rows with pads placed around the periphery of the chip. These standard circuits may all be identical, or they may be described in terms of a few standard groupings of two or more adjacent cells. Furthermore, macro blocks may also be present on the chip. An example typical standard cell layout is shown in Figure 1.1.

Given a set of standard cells and a net list which describes the interconnections among the cells, the objective is to place the cells so as to minimize the total length of wires interconnecting the cells and to minimize the total area of the chip. Manual placement generally results in area and

Figure 1.1. Example standard cell VLSI layout.

performance efficiency for small circuits. However, for very large circuits, not only is the design time prohibitively long, but the area and performance suffer. The problem that arises in automating this process is that like many combinatorial optimization problems this problem is NP-complete [3]. The time required to perform an algorithmic solution, which surveys all possible solutions of a given placement problem, grows exponentially with the number of cells. Fortunately, in practice one needs merely a good solution and some sort of assurance that the absolute minimum solution is not significantly better than the one found. Several heuristic methods which attempt to accomplish this have been developed that find good solutions with acceptable computational cost.

#### 1.2. Previous Research

There are two basic strategies for heuristics: "divide-and-conquer" and "iterative improvement." In divide-and-conquer algorithms such as min cut [4], one recursively divides the problem

into subproblems of manageable size, then solves these subproblems individually. The solutions to these subproblems must then be patched back together. For this method to produce very good solutions, the subproblems must be naturally disjoint, and the divisions made must be appropriate ones so that errors made in patching do not offset gains obtained in applying more powerful methods to the subspaces.

Iterative improvement algorithms such as force-directed interchange, pairwise interchange, neighborhood interchange, and forced-directed pairwise relaxation [5, 6, 7] start with the system in a known configuration. A standard rearrangement operation is applied to all parts of the system in turn, until a rearranged configuration is observed which improves the cost function. The rearranged configuration then becomes the new configuration of the system, and the process is continued until no further improvement can be found. Iterative improvement consists of a search in the coordinate work space for rearrangement steps which lead "down hill," i.e., reduce the prescribed cost function. Since this search usually has a tendency to get stuck at a local and not the global minima of the objective cost function, the process normally has to be carried out several times, starting from several different randomly generated initial configurations, and then the best placement obtained is used. In addition to these problems, conventional heuristic algorithms usually do not allow for the amount of flexibility and extensibility desired by users.

To avoid the problems associated with conventional heuristic placement algorithms, a family of heuristic optimization algorithms have been devised based on simulated annealing [8]. These algorithms generate the next placement configuration randomly and can climb hills, i.e., changes that generate configurations of higher cost than the present configuration are sometimes accepted. These "hill climbing" changes are only accepted according to a certain criterion which takes the state-of-the-search process into consideration.

The simulated annealing technique has been proposed and applied to the standard cell placement problem in a program called TimberWolf [9, 10], which by applying all displacements, exchanges, and orientations of cells randomly, avoids getting stuck at local minima and thus

achieves near-optimal placement.

Recently, some researchers have started to investigate speeding up simulated annealing algorithms by running them on parallel processor systems. Aarts et al. have proposed schemes for parallelizing simulated annealing algorithms for several general classes of problems and have discussed theoretical convergence characteristics [11]. A parallel algorithm for the Traveling Salesman Problem based on simulated annealing has been reported for the hypercube [12]. Parallel algorithms for partitioning and routing have been proposed by Chung and Rao [13].

Two multiprocessor-based simulated annealing algorithms for the standard cell problem have been reported by Rutenbar and Kravitz [14, 15]. The first scheme, called Move Decomposition, partitions the computations of the individual move across processors and thus allows the cooperating parallel subtasks to evaluate the effects of this move more rapidly. The second scheme, called the Parallel Moves strategy, allows multiple-move evaluation in parallel but accepts only one of the moves. In this thesis, we propose a parallel simulated annealing algorithm that is targeted to run in a local memory message-passing parallel processing environment, namely the hypercube computer.

There are a number of basic differences in the three approaches to parallelize simulated annealing. In the first two cases, the parallel algorithms are based on a shared memory model, whereas the third uses a local memory model. The first is basically simulating a serial-simulated annealing environment, but evaluating each individual move faster. The second algorithm evaluates multiple moves in parallel but accepts only one move. Hence, its convergence characteristics are identical to the uniprocessor algorithm. In the third case proposed in this thesis, the moves are evaluated in parallel and accepted/rejected in parallel on the basis of changes in the cost function for each move, assuming that the other moves are not made. The theoretical considerations of whether the annealing properties are still preserved when the cost calculations are based on slightly outdated information and when only a restricted set of moves are allowed, is a subject of future research. Experimentally, we have verified that our algorithm works.

#### 1.3. Thesis Outline

In this this, we present a parallel algorithm using simulated annealing on the hypercube computer. The basic idea used in the algorithm involves parallel exchange and displacement moves in different dimensions of the hypercube, and acceptance/rejection of the moves on the basis of changes in cost functions, ignoring the effects of other moves.

In Chapter 2, a detailed description of the hypercube architecture and an overview of the Intel hypercube simulator, which was used for program development, will be presented. In Chapter 3, we will briefly describe conventional simulated annealing, and then discuss a parallel version of the algorithm. We will describe the data structures that are necessary to support various parallel move evaluations and discuss how the subtasks for evaluating the acceptability of parallel moves are assigned. We will present a novel tree broadcasting strategy for the hypercube that is used extensively in our algorithm for updating cell locations in the parallel environment. In Chapter 4, we will describe the implementation of the algorithm on an Intel hypercube simulator. We will report on the performance of the proposed algorithm for several actual standard circuits used in industry and present some accurate estimates of the execution time for the algorithm. We will show that the parallel algorithm gives about 10-20% better final placements than conventional uniprocessor simulated annealing algorithms. Finally, in Chapter 5, an improved uniprocessor simulated annealing algorithm, based on the benefits observed from parallelizing the conventional simulated annealing algorithm, will be presented. We will demonstrate that this improved algorithm is less likely to get stuck at the local minima of the objective function, and thus converges to a final placement which is better than the final placement generated by the conventional uniprocessor algorithm.

#### CHAPTER 2

#### HYPERCUBE CONCURRENT PROCESSORS

#### 2.1. Introduction

Supercomputers such as the IBM 3081/3084. CRAY-2, and Burroughs D-825 normally achieve their high performance by increasing the raw speed of the electronic components and logic circuits. For these mammoth computers, the switching and propagation delays are measured in nanoseconds, and data are propagated at speeds close to the speed of light. Unfortunately, these uniprocessors are nearing the limits imposed by physical and electrical constraints. Electronically, uniprocessor computers are reaching their speed limit. To increase the computing speed further, pipelining and parallelizing of operations must be exploited at the circuit level, making these supercomputers very large and very expensive.

An alternative approach to supercomputing is through parallelism at the processor level. We are on the verge of a revolution in computing spawned by advances in computer technology. Progress in very large-scale integration (VLSI) is leading not so much to faster computers, but to much less expensive and much smaller computers, i.e., computers contained on a few chips. These chips make it practical to build very high-performance computers, or supercomputers, consisting of a large number of smaller computers combined to form a single concurrent processor.

The concept of interconnecting multiple, small, inexpensive microcomputers is not new. A number of multiprocessing systems of differing configurations are in existence. Multiple processors communicating with each other via single or time shared bus architecture, such as DCS [16], are very common. In this architecture, several computers are connected to the bus and communicate with each other through token messages. A time shared bus is easy to construct, but the processor-to-processor communications are limited because only one information exchange is allowed at any one time. In another approach, STARAN [17] uses a complete point-to-point con-

nection between processors. This speeds up processor communications and allows simultaneous data transfer; however, the number of interconnection lines increases rapidly as the number of processors increases. C:mmp [18], a multi-miniprocessor at Carnegie-Mellon University, uses crossbar switches between a bank of memories and a bank of processors. This causes only slightly degraded simultaneous transfer ability; however, just like the STARAN, the crossbar network increases in complexity too fast as the number of functional units increases. More recently, Jordon [19] designed a FEM machine, which is a two-dimensional array, that allows any processor to communicate directly with its eight nearest neighbors. Tuazon [20] added more flexibility by providing a switching network that allows a processor to create a communication path to any other processor.

The advent of cost-effective VLSI components in the past few years has made feasible the commercial development of massively parallel computers with upwards of 1024 or more processors. Many different parallel architectures are under development, but the most commercially successful large-scale parallel architecture to date has been the Boolean hypercube, implementations of which are available from at least four different vendors. In the brief time since their introduction, these machines have already gone from experimental prototype status to near-commercial supercomputer performance and have done so at a relatively modest cost.

A significant difference between hypercubes and most other parallel processors is that these multiple-instruction, multiple-data machines (MIMD) use message-passing instead of shared variables for communication between concurrent processes. Each processor has only a small private local memory. Activities with other processors are coordinated by sending messages through an interconnection network. This type of architecture is more readily scaled up to very large numbers of processors than multiprocessor designs based on globally shared memory. The hypercube network is connected densely enough to support efficient communication between arbitrary sets of processors, yet sparsely enough to be relatively simple and inexpensive to build. Another virtue of the hypercube network is its flexibility; many other interconnection topologies (rings, grids, trees, etc.), are subnetworks of the hypercube; hence the hypercube is an ideal test bed for experimenta-

tion with parallel algorithms intended for many different types of distributed-memory, messagepassing multiprocessors.

#### 2.2. Hypercube Message-Passing Architecture

#### 2.2.1. Hypercube interconnection network

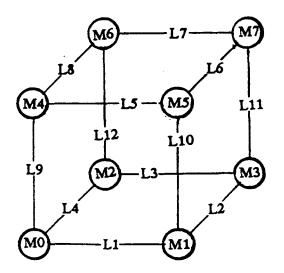

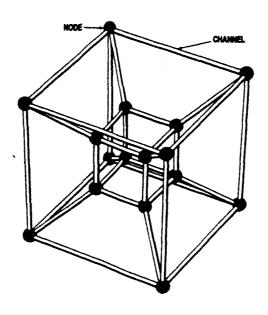

A hypercube consists of  $2^N$  processors that are connected by the binary N-cube interconnection. The processors are consecutively numbered or tagged by binary integers, i.e., bit strings of length N, from 0 through  $2^N-1$ . In a hypercube interconnection network each processor is directly connected to N other processors whose binary tags differ from its own by exactly one bit. Topologically, this arrangement places the processors at the vertices of the N-dimensional cube. For example, in Figure 2.1, a 3-cube is pictured which has  $2^3$  processors placed at each of the vertices and communication links, which directly connect the processors, represented by the twelve edges of the 3-cube. Simultaneous communications between several pairs of nodes can therefore occur with

Figure 2.1. Three-dimensional hypercube.

Figure 2.2. Four-dimensional hypercube (16 processing nodes).

this type of interconnection network.

Higher-order (hyper) cubes are more difficult to visualize. Figure 2.2 shows a four-dimensional hypercube which can be described as a cube within a larger cube with corresponding corner nodes connected. Hypercubes of arbitrary dimensions can be constructed by replicating the one of next-lower dimension, then connecting corresponding nodes. One of the advantages of the hypercube network is that as the number of processors increases, the number of connecting links per processor grows only logarithmically, so that very large numbers of processors connected in a hypercube network become both feasible and attractive.

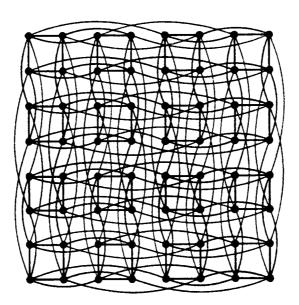

In practice, the actual physical layout of the hypercube's processors is a linear arrangement in a card cage or a planar arrangement on a printed circuit board. Cube connections are then made by wires, conducting layers, or backplane. A planar view of a six-dimensional hypercube is shown in

#### Figure 2.3.

If a message needs to be sent between a pair of nodes that are not directly connected, then they are routed from node to node until they reach their destination. The routing path can be easily derived by inverting one bit at a time of the bits in the source address which differ from corresponding bits of the destination address until it exactly matches the destination address. For example, to route data from node 0101 to node 1010 in a four-dimensional hypercube, the intermediate nodes, 0100, 0110, and 0010, would be used. It can be easily verified that for an N-dimensional hypercube, the furthest node from any starting node is only  $\log_2 N$  away. For every pair of nodes there are  $(\log_2 N)!$  possible routes. This redundancy can be exploited to enhance communication bandwidth and fault tolerance of the hypercube network.

Figure 2.3. Six-dimensional hypercube (64 processing nodes).

Through software, a hypercube can be adapted to model other interconnection configurations by ignoring some of the interconnects. For example, in the four-dimensional hypercube, by ignoring some of the interconnects one can arrive at the variations shown in Figure 2.4 a, b, and c as the 3D cube, 2D plane, and toroidal mesh. The data routing requirements will affect the particular variation used. For example, problems which are normally represented in array form, such as matrix operations and sets of linear equations, etc., can be implemented using a 2D configuration. Analysis of three-dimensional structures can use the 3D topology.

#### 2.2.2. Processing nodes

An attractive feature of the hypercube is its homogeneity. Because of this, all the processing nodes are normally designed to be identical. Nevertheless, with any distributed system, a need usually arises, either by necessity or by convenience, to have a separate processor that acts as master controller or manager of the remaining processors. This special processor, usually called the host, is generally not part of the main hypercube interconnection network, whose processors are

- a) Three-dimensional cube

- b) Two-dimensional plane

- b) toroidal mesh

Figure 2.4. Subnetworks of four-dimensional hypercube.

referred to as node processors or simply nodes. The role of the host is to initiate a computation, collect results upon completion, and serve as the input/output (IO) link to the outside world. The host must be directly connected to at least a subset of the nodes in the hypercube and, preferably, to all of them, perhaps by a global bus that is used only for host/node communications as opposed to node/node communications.

Because the hosts need to do more powerful operations such as IO, program down loading, and system diagnostics, the architecture of the host is normally faster and more powerful. Because this processor is a critical link in the hypercube, i.e., its loss would disable all IO, the host is normally made to be more fault tolerant.

Each of the hypercube's processing nodes is composed of three separate components: the CPU, local memory, and communications circuitry. Some system designs have a separate communications coprocessor to handle node-to-node communications thus allowing for simultaneous computation and communication. Physically, each processing node is built from as few VLSI chips as possible in order to increase speed and to keep space requirements low.

#### 2.2.3. Distributed software

The hardware structure of the hypercube when viewed at the level of nodes and channels is a difficult target for programming any but the most highly regular computing problems. Most hypercube resident operating systems create a more flexible and machine-independent environment for concurrent computation. Instead of formulating a problem to fit on the nodes and on the physical communication channels that exist only between certain pairs of nodes, the programmer can formulate problems in terms of processes and logical communication channels between processors. This process model of computation is quite similar to the hardware structure of the hypercube but is usually abstracted from it.

Processes are the basic unit of computations and can be described as a sequential program that sends and receives messages. A single node may contain many processes. All processes execute concurrently, whether by virtue of being in different nodes or by being interleaved in execution within

a single node. Multitasking in such an environment is quite feasible. Each process has a unique global identification that arises as an address for messages. All messages have headers containing the destination and the sender identification and a message type and length. Messages are queued in transit, but message order is preserved between any pair of processes.

Because it has only local memory, the hypercube needs to employ a distributed operating system. An operating kernel will reside in each node processor to supervise user processes running on the node and to handle message traffic. In particular, the kernel in a given node sends, receives, and queues messages for processes running on its node, and may also automatically forward incoming messages intended for processes running on other nodes, freeing the main node processor of much of the communication overhead. A variety of operating systems, compilers, and other parallel processing development tools have been designed and implemented for use on the hypercube architecture [21, 22, 23, 24]. Processor scheduling is an important area which has received substantial research in recent years [25, 26, 27].

The host is responsible for compiling application programs and loading the resulting object code into the appropriate node processors. Once the host has initiated a computation, the host and node processors all proceed asynchronously, coordinated only by the exchange of messages containing problem data or control information.

#### 2.3. Current and Future Hypercube Systems

A hypercube of computers was often discussed in the mid 1970's as a practical means to implement a concurrent processing environment [28, 29]. The Russians [30] built a 32-node hypercube in the late 1970's with positive results. Many references have appeared in literature since then concerning the construction or use of hypercube computers [31, 32]. The pioneering work was finally brought to practical fruition in 1983 with the Mark I "cosmic cube" [33] at the California Institute of Technology, where it has since been in regular use for solving a wide variety of important scientific problems. Transfer of this new technology into the commercial sector has been relatively swift. Intel Scientific Computers Corp. announced the first commercially available

hypercube, the Intel Personal Super Computer (iPSC) [34], in early 1985. Several other commercial vendors soon followed: Ametek Computer Research's Ametek [35], NCUBE Corp. [36] with the NCUBE/ten, and Floating Point Systems Inc. with their T series. Further joint development by Caltech and the Jet Propulsion Laboratory has since created a new generation of hypercubes, the Mark II and Mark III.

The availability of these machines is making possible widespread experimentation of large-scale parallel computing for realistic applications. Moreover, these machines are moving quickly from experimental prototypes to genuine supercomputer performance and doing so at a relatively modest cost.

#### 2.3.1. Commercial systems

Several commercially hypercube systems have become available recently. Even though they are all built around the same hypercube message-passing architecture, their actual hardware and software implementation and performance vary considerably from system to system. Three of the systems have already been delivered to customers. These systems include the Intel iPSC, the Ametek Computer Research's Ametek, and the NCUBE Corporation's NCUBE/ten.

Primarily to reduce development time, the first systems introduced used proven widely available VLSI circuits as the backbone of each of the node processors. The Intel and Ametek systems use the 16-bit Intel 80286 [37] to perform all general purpose computations. In addition to its high computational ability, the 80286 was selected for its built-in support of a custom coprocessor, the 80287. The coprocessor interface provides a very low overhead mechanism for a client program to invoke task management functions that are implemented concurrently. By using widely available technology, both systems were able to use existing hardware and software development tools and thus reduce system development time.

The communications hardware in both systems is rather simple and slow. Node-to-node communications are run over links controlled by an Intel ethernet chip at peak rates of 10 megabits/second. Because of this relatively simple communications hardware and the need to

perform a large part of the communications overhead in software, link delays for even very simple messages are in the milliseconds range for both systems [38]. This makes communication very expensive in comparison to computation time. This means that for an algorithm to be feasible for significant speedup on these systems, the ratio of computation to communication has to be rather large. Both systems also tend to have limited amounts of local memory, on the order of 512K bytes.

The Ametek system's communication system is small-packet based, which means that small packets take significantly less time to traverse the links than do larger ones. The Intel iPSC's use of ethernet with standard 1K byte packets enables it to have constant delay for packets of less than 1K bytes. For larger packets, multiple packets have to be sent.

Both of these systems were designed to allow for easy expansion with configurations from 16 to 128 nodes available in both systems. Additionally, recent developments in the Intel iPSC allows for up to 4 megabytes of RAM at each node and to have array processors and accelerators attached to node processors to enhance performance.

These initial systems were primarily designed as a quick implementation of the hypercube architecture for commercial use. Systems which followed these initial entries, primarily the NCUBE/ten, strived to develop special purpose hardware specifically targeted for hypercube use. In most of the parallel systems being proposed or manufactured, each node consists of many chips, often more than 100. In contrast, the NCUBE/ten node has only 7 chips, and 6 of them are memory. The NCUBE/ten uses state-of-the-art VLSI to integrate most of the system (except memory) at each node onto a single chip. Each node is designed to have 128K bytes of local memory with local groups of processors connected to a global 500M byte disc. The NCUBE/ten-node processor is a complex chip of about 160,000 transistors that integrates memory interface, communications links, and a high-speed 32-bit processor with 64-bit floating point. Each node is capable of performing at a peak rate of 0.5 megaflops. A broad range of error-correcting mechanisms in the data paths is incorporated to insure reliability. The NCUBE/ten is expandable from 16

to 1024 processors, and unlike the iPSC and Ametek allows for extremely high-speed IO at each of the processing nodes without the need to transfer information to the host processor first.

#### 2.3.2. Experimental systems

The first experimental hypercube implementation to get significant recognition was the Mark I built at Caltech, commonly known as the cosmic cube [33]. This system consisted of at most 64 processing nodes based on the Intel 8086 microprocessor as data processor and 8087 coprocessor as the floating-point processor. Each node was equipped with 128K bytes of RAM. Full duplex communication channels running at a slow 2 megabits/second were utilized for node-to-node communications. Because of the slow processor and communications speeds and the limited 128K bytes of local memory, the system was definitely not in the supercomputer range, but even with these slow microelectronic technologies, the 64-node machine was found to be quite powerful for its cost and size. The performance of the Mark I encouraged Caltech to develop an enhanced model.

The follow-up to the Mark I was the Mark II system [39]. The Mark II was built in cooperation with the Jet Propulsion Laboratory. This system can be configured up to a 128-node network. Intel 8086 processors and 8087 coprocessors were again used, and RAM was increased to 256K bytes per node, with additional external IO incorporated into groups of node processors. Enhanced hardware and software have significantly increased the systems' performance over that of the Mark I. A follow-up system, the Mark III [40], will be a vastly more powerful machine, constructed from nodes, each of which has two MC68020s, floating point accelerator chips, and 4 megabytes of memory [41]. These powerful nodes, along with equally powerful node-to-node communications hardware, are expected to allow the Mark III to match or surpass the performance of most standard supercomputers available today.

Several other systems are in various stages of research in a number of universities throughout the country. The most ambitious system being developed is at the Los Alamos National Laboratory in connection with the University of New Mexico [42]. This system will be primarily hardware-oriented. Rather than approaching the hypercube problem by using nodes with minimal computing

resources, the engineers at Los Alamos have elected to implement the architecture, using nodes with sufficient computing resources to address interesting problems. A variety of off-the-shelf and specially designed VLSI circuits will be used in an attempt to allow for upwards of 20 megaflops of computational power at each node. A small local memory of between 16K and 64K bytes, along with a large disk with a capacity in excess of 300K bytes, is incorporated into each processing node. Fast node-to-node links with rates in excess of 40 megabits/second will also be incorporated. This system is expected to have a peak performance in excess of 20,000 megaflops

#### 2.3.3. Comparison and benchmarks

The performance of a concurrent processing program depends on the hardware, architecture, and programming algorithm used. The maximum number of concurrent megaflops of computational power is a commonly used yardstick. This number as normally quoted is obviously only "potential" performance, which can only be achieved through efficient programming. Because of the nature of the hypercube architecture, several other factors have to be taken into account. The hardware factors effected by a particular hypercube implementation are

#### 1) Memory Size

Invariably, as the node memory increases, the performance of the system also improves. Unfortunately, large memories can be very expensive. Secondary memory or dual port memories which allow simultaneous communication and computation may be used in some cases.

#### 2) Processing Speed

Since scientific applications are the primary users of hypercubes, it is essential that the floating-point operational speed be as large as possible to solve these computationally intensive problems.

#### 3) Communication Speed

High-speed communication is very important in a message-passing environment. Not only does the link transfer rate have to be high, but the time spent in doing the overhead associ-

ated with transmitting, routing, and receiving has to be kept low.

Table 2.1 gives a comparison of the hardware capabilities of the various systems discussed in the preceding two sections.

Table 2.1. Hardware capability comparison for various systems.

| System     | Max Number<br>Processors | Type of CPU | Memory<br>Size (bytes) | Computational Mflops (peak) | Communication Mbits/Second |

|------------|--------------------------|-------------|------------------------|-----------------------------|----------------------------|

| Mark I     | 64                       | Intel 8086  | 128K                   | 8                           | 2                          |

| Mark II    | 128                      | Intel 8086  | 256K                   | 15                          | 8                          |

| Mark III   | 1024                     | MC68020     | 4M                     | >1000                       | _                          |

| iPSC       | 128                      | Intel 80286 | 512K-4M                | 20                          | 10                         |

| Ametek     | 128                      | Intel 80286 | 512K                   | 20                          | 10                         |

| NCUBE/ten  | 1024                     | Custom VLSI | 128K/500M              | 512                         | 10                         |

| Los Alamos | 1024                     | Custom VLSI | 64K+300K               | >20000                      | 40                         |

#### 2.4. Hypercube Simulator

Due to the present unavailability of an actual Intel hypercube at the University of Illinois, initial testing of the algorithm to be presented in the next chapter has been completed using the Intel iPSC Simulator running on a SUN 3/50 work station system under UNIX 4.2 [43]. This simulator was chosen because of assurances that programs which executed properly under the simulator could be transferred to an actual iPSC system and operate with only minimum or no modification required.

The simulator package consists of a simulator program and a set of libraries which simulate hypercube operations in a sequential processing environment. This event-driven simulator provides an interactive interface to the user, which simulates a large portion of the iPSC's host node commands. These commands allow the user to load executable code into each of the nodes of the hypercube and to initiate execution. Nodal processes are simulated in the uniprocessor environment by forking off UNIX processes.

The major difference between hypercube algorithms and uniprocessor algorithms is the need to do message-passing between concurrently operating processors. The primary responsibility of the simulator is to model these message transfers in such a way that ordering of messages is preserved. In order to remove the programmer as far as possible from requiring an understanding of the exact communication routing requirements for a given message, a system of logical channels is adopted in the iPSC system and its simulator. A channel, as used in the iPSC system, is a 64-byte block of memory that contains information about a message to be sent or received. Typical information contained in this block of memory is the source node and process id, the destination node and process id, and the message length. A sending process needs to establish a channel to contain this information before a message can be sent. Likewise, a receiving process must also establish a channel to receive this information before the message can be received. Once an operation (send or receive) has been completed, the information is no longer needed, and the channel can be used again by another message. If a process needs to send/receive more than one message simultaneously, the process needs to open a channel for each of the simultaneous send/receive operations. Because of the nature of these logical channels, the programmer is relieved of determining the actual path over which a message travels. The operating kernel at each node of the hypercube will determine the optimal path between the two nodes connected by the logical channel.

A typical message transfer in software requires a call to a procedure send by the node processor wishing to send a message. Procedure send initiates the transmission of a message to another node processor. The caller can wait for this transmission to complete or simultaneous computation can be taking place. A typical call to send is of the form:

#### send(ci. type, buf, len, node)

where

ci : Channel identifier of channel over which message is to be transmitted

type: User specified integer value referring to type of message. The

receiving node uses this value to distinguish multiple incoming messages.

buf: Pointer to the continuous block of memory (buffer) that contains

the message to be sent.

len: Number of bytes in buffer to be transmitted.

node: Physical address of node to receive message.

In a similar manner the node processor which is to receive the message calls a receive procedure. A typical receive call is of the form

### receive(ci, type, buf, &cnt, &node)

where

ci : Channel identifier of channel over which message is to be received.

type: Integer value referring to the type of message wanting to receive.

buf: Pointer to the buffer where the received message is to be stored.

cnt: Upon reception of a message of the proper type,

cnt will contain the number of message bytes received.

node: Upon reception of a message of the proper type, node will contain the identification of the processor which sent the message.

Through the exchange of data by sending and receiving of messages to and from other processors in this manner, nodes can exchange required data and coordinate activities.

#### **CHAPTER 3**

#### PARALLEL ALGORITHM FOR CELL PLACEMENT

#### 3.1. Simulated Annealing Algorithm

Simulated annealing, as proposed by Kirkpatrick [8], is a popular Monte Carlo algorithm for combinatorial optimization. Simulated annealing is a variation on an algorithm introduced by Metropolis [44] for approximate computation of mean values of various statistical-mechanical quantities for a physical system in equilibrium at a given temperature. The Metropolis method, combined with Kirkpatrick's "several temperature" method, is collectively called simulated annealing.

The search for a minimum cost function in a simulated annealing algorithm has a close analogy to the physical process by which a material changes state while minimizing its energy. When a material is crystalized from the liquid phase, it must be cooled slowly if it is to assume its highly-ordered, lowest-energy state. At each temperature during the annealing process, the material is in equilibrium, i.e., the likelihood of its being in a given state is governed by the Boltzman distribution for that temperature. As the temperature decreases, the distribution becomes concentrated on the lower-energy states until, when the temperature finally reaches zero, only the minimum-energy state(s) have nonzero probability. However, if the cooling is too rapid, the material does not have time to reach equilibrium. Instead, various defects become frozen into the structure.

Because conventional iterative improvement algorithms forbid changes of state which increase the cost function, they are much like rapidly reducing a physical system to zero temperature in a very small period of time. Simulated annealing is thus a variation of the conventional iterative improvement algorithms in which uphill moves are permitted in the cost function under the control of a slowly reducing temperature parameter.

A simplified algorithmic structure of the simulated annealing algorithm is given below:

```

PROGRAM SIMULATED ANNEALING

T = T<sub>0</sub>;

X = X<sub>0</sub>;

While (stopping criteria not satisfied)

While (inner loop criteria not satisfied)

X' = Generate(X);

evaluate cost(X');

If( accept(cost(X'), cost(X)))

X = X';

ENDIF;

ENDWHILE;

update(T);

ENDWHILE;

ENDWHILE;

END PROGRAM

```

This algorithm is characterized by three main functions: accept, generate, and update. The function accept is used to determine if a proposed new configuration of the circuit should be accepted. While several accept functions can be used [45, 46, 47], a probabilistic exponential function is normally used for standard cell placement optimization because of its proven ability in other similar optimization problems. The accept function is given below:

```

FUNCTION accept( cost(X'), cost(X))

\Delta C = cost(X') - cost(X);

If( \Delta C <= 0)

Return(TRUE);

else

y = exp(-\Delta C/T);

r = random(0,1);

If( r < y)

Return(TRUE);

else

Return(FALSE);

ENDIF;

ENDIF;

END FUNCTION:

```

New configurations characterized by a negative change in the cost function ( $\Delta C < -0$ ) always satisfy the acceptance criterion. However, for new configurations characterized by  $\Delta C > 0$ , the

temperature parameter T and a random number generator play fundamental roles. If T is very large, then r is likely to be less than y, and a new state is almost always accepted irrespective of  $\Delta C$ . If T is small, close to zero, then only new configurations which are characterized by very small  $\Delta C > 0$  have any chance of being accepted. In general, all states with  $\Delta C > 0$  have smaller chances of satisfying the test as the temperature decreases.

The generate function selects a new configuration of the circuit. This means randomly moving cells within the circuit. These moves can either be the exchange of cells, the displacement of a single cell, or an orientation or mirroring change in a cell. In the presented simulated annealing algorithm, the program variable X represents the present placement of cells and X' represents a new candidate cell configuration created by the generate function.

The update function, also called the annealing or cooling schedule, determines a new value for the temperature after completion of the inner loop. The update function is very important in determining the convergence properties of the simulated annealing algorithm. A broad range of update functions which return monotonically decreasing values of temperature have been found to guarantee convergence of the simulated annealing algorithm to an optimal or a near optimal solution [48, 49, 50, 51, 52, 53].

#### 3.2. Overview of Parallel Algorithm

The simulated annealing technique has been proposed and applied to the placement problem in a program called TimberWolf [9, 10], which by applying displacements, exchanges, and orientation changes randomly, avoids getting stuck at local minima and thereby achieves near-optimal final placement results. TimberWolf has been shown to provide substantial chip area savings in comparison to existing standard cell layout methods. We now describe an algorithm for performing the standard cell placement using a variation of the TimberWolf algorithm on a hypercube of log(P)-dimensions connecting P processors. Let us suppose that we are given the problem of placing N standard cells where N >> P. An outline of this algorithm is shown below. Each of the steps in the algorithm will be described in the following subsections.

STEP 1. Perform initial cell assignments in P processors.

STEP 2. Determine initial temperature.

STEP 3. While "Stopping criteria": temperature < 0.1 not reached

STEP 4. Generate new temperature

STEP 5. For inner\_loop\_count = 1 to NA

/\* NA =  $(N \times \text{attempt}_p\text{arameter}) / (\log(P) \times P/2)$ \*/

STEP 6. For each dimension i=0 to log(P)-1 do

STEP 7. Randomly select P/2 moves (exchange or displace) in parallel among pairs of PEs connected in dimension i.

STEP 8. Check "range-limiter" function in dimension i.

STEP 9. Evaluate change in cost for each move between pairs of PEs independently.

STEP 10. Accept/reject moves using exponential function independently.

STEP 11. Broadcast new cell locations to all other processors.

STEP 12. ENDFOR:

STEP 13. ENDFOR:

STEP 14. ENDWHILE:

#### 3.3. Cell Assignment to Processors

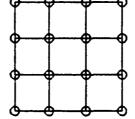

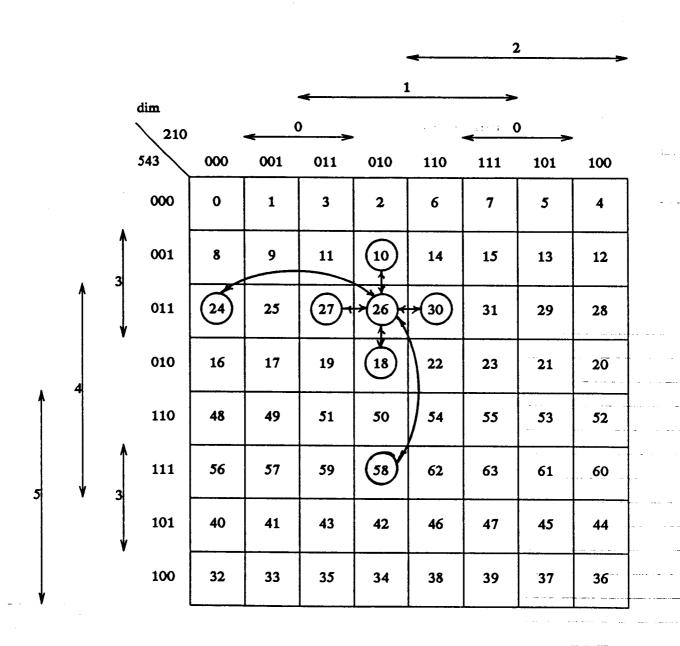

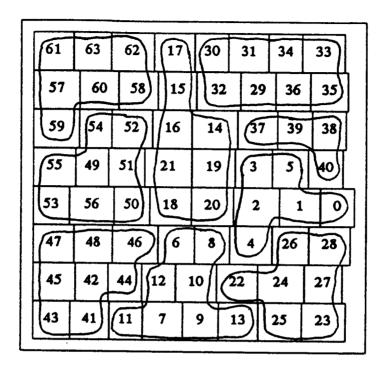

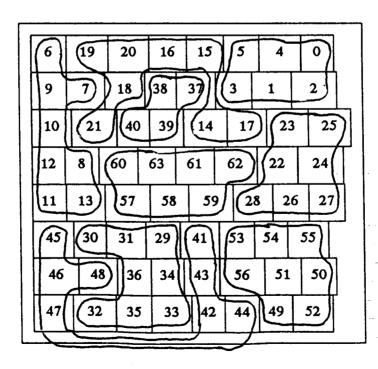

We now describe a technique for mapping a log(P)-dimensional hypercube onto a two-dimensional area using an example six-dimensional hypercube. The results can be generalized to other dimensions. In the 64-processor hypercube, a processor having a binary address  $p_5p_4\cdots p_i\cdots p_0$  is connected to processor  $p_5p_4\cdots p_i\cdots p_0$  via a link in dimension i. We propose that each processor be assigned an approximately equal area portion of the total chip area which can be viewed as a virtual  $8\times 8$  square grid. Each virtual grid corresponds to a horizontal portion of a number of rows. (For example, for a standard circuit with 16 rows of cells, each processor in a 64-processor hypercube will be in charge of one-eighth the horizontal length of two of the rows.)

The cells are initially assigned randomly to different processors such that each processor has an approximately equal number of cells assigned to it. The cells within each processor are also randomly placed with no regard to area overlaps. We also tested with a strategy of cell assignment such that the sums of areas of cells assigned to each processor is approximately equal to

$$A_{average} = \frac{1}{64} \sum_{m=1}^{N} A_m.$$

where  $A_m$  is the area of the  $m^{th}$  cell. But because of the large number of moves that are accepted at high temperatures in the initial stages of the annealing process, it does not make any difference which strategy is used since the cells get randomly dispersed anyway. Since all cells have constant height, each processor therefore is assigned a rectangular portion of the chip area. The correspondence between processor addresses and virtual grid regions on the physical chip area is shown in Figure 3.1. By choosing such a map, we guarantee that the processors that are adjacent in a predetermined set of four dimensions of the hypercube allow for all nearest North-South-East-West neighbor displace/exchanges. The other two dimensions of the hypercube are used for displace/exchanges across larger distances in the area map. For example, in Figure 3.1, processor 26, which controls grid location (3.4), has a a 4-link to processor 10, a 3-link to processor 18, a 2-link to processor 30, and a 0-link to processor 27, which correspond to the nearest neighbors in the North(2.4), South(4.4), East(3.5) and West(3.3) directions; in addition, the 1-link to processor 24 and the 5-link to processor 58 control grid locations (3.1) and (6.4), that are distance 3 away from (3.4).

#### 3.4. Distributed Data Structure

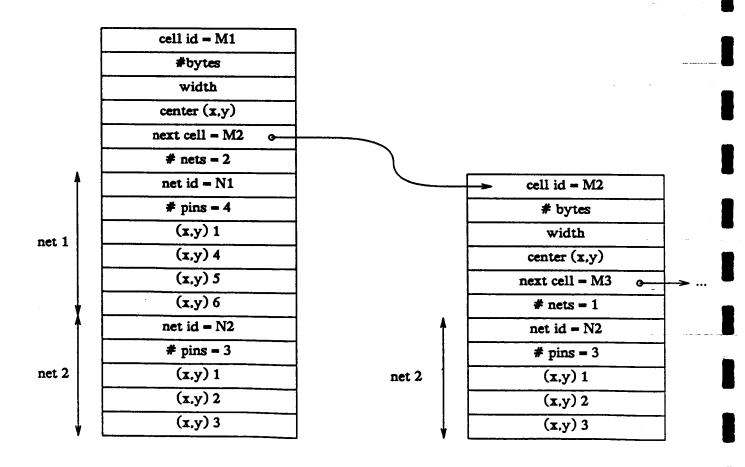

We assume that each processor contains a list of cells currently assigned to this processor along with the following information for each cell to aid in the computation of the cost function in parallel among processors in the hypercube:

- (1) The width of the cell

- (2) The (x,y) coordinate location at which the center of the cell is currently placed

- (3) A list of nets to which this cell is connected

Figure 3.1 Area map of 64-processor hypercube

(4) For each net listed in (4), a list of other cells, to which the net is connected, along with the (x,y) pin location(s) within these cells

The state of any particular cell is composed of the information in (1) through (4) and is packed within a continuous block of memory to allow for easy packet transfer of information between nodes. Also, a list of (x,y) locations and widths of all cells that are assigned to processors that are adjacent in the two dimensions of the hypercube corresponding to the East-West nearest neighbors in the physical area map is also maintained in each processor. Figure 3.2 shows an example of the blocked memory data structure for typical cells.

### 3.5. Cost Function

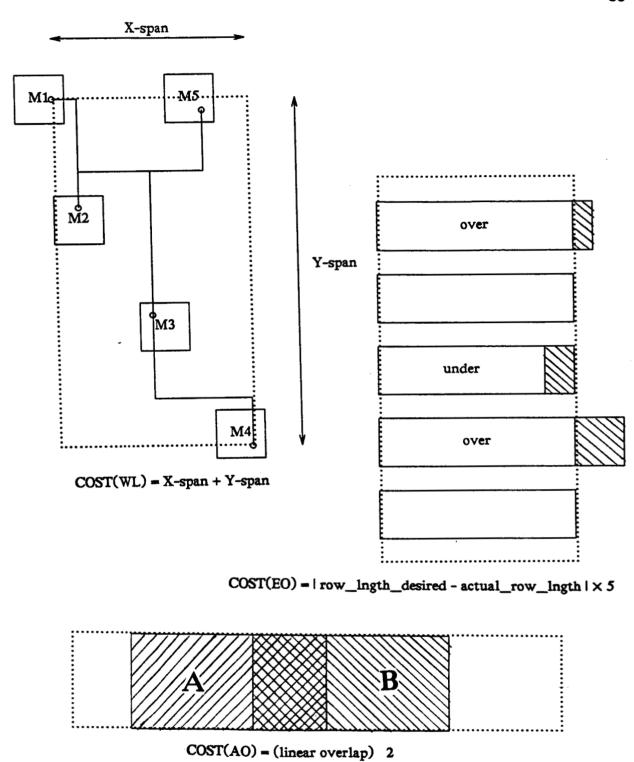

Because of the nature of the simulated annealing algorithm, a very complex cost function can be used which takes into account many different aspects of a particular circuit configuration. The cost function for the standard cell placement problem consists of three parts:

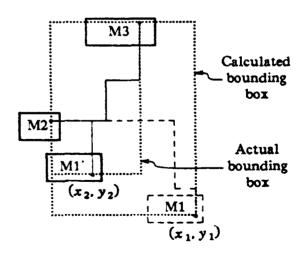

- (1) Estimated wire-length using half the perimeter of the bounding box rule

- (2) Overshoot or undershoot of each row length over or under the desired row length

- (3) Linear area overlap between cells in the same row

These are graphically shown in Figure 3.3 with corresponding cost functions. The horizontal work space length is calculated to be equal to 110% of the desired length of every row. The cells for a

Figure 3.2. Example net and corresponding memory structure.

given row, therefore, have at least an additional 10% of length in which to move in each row. However, the cost penalty associated with going over or under the desired row length is calculated using the desired length and not the 110% length of each row.

### 3.6. Move Generation

After the cells have been distributed among the processors of the hypercube, each processor repeatedly interacts with its neighboring processors in each of the d dimensions of the hypercube. The set of steps involved in a parallel set of moves is outlined in Figure 3.4. At each time step, P/2 pairs of processors participate in the evaluating P/2 moves.

### 3.7. Discussion of Moves

### 3.7.1. Mastership selection

For each pair of processors (p,q) connected in dimension i, one of them is chosen to be the Master and the other to be the Slave using the criteria listed in STEP 1 of Figure 3.4 to ensure that the mastership of the pair alternates between processors in alternate iterations. The choice is not random as in [54] because it would then involve an extra synchronization message between the processors, and we wish to reduce the communication overhead as much as possible. We alternate mastership between iterations because otherwise, in a fixed scheme, we would bias the displacements of cells from the Master to the Slave processor resulting in the Master processor having no cells after several iterations.

### 3.7.2. Selection of move

At each iteration of the TimberWolf algorithm the generate function is performed with one of two types of cell movements randomly chosen to create a new circuit configuration for analysis. These moves are:

- (1) Displacement of a single randomly selected standard cell from its present position to a randomly selected point anywhere within the physical work space

- (2) Exchange in position of two randomly selected standard cells

Figure 3.3. Cost function evaluation.

### PROCEDURE PARALLEL MOVES:

- STEP 1 For each pair of processors (p,q) connected in dimension i, if the inner\_loop\_count is even and if p < q, then p is chosen to be the Master, q to be the Slave, otherwise vice versa.

- STEP 2 Master randomly decides if next move will be an exchange or a displacement, favoring the latter by a factor of 5 to 1. The Master also decides randomly with equal probability if the move will be an intraprocessor or interprocessor exchange/displace.

- STEP 3.1 If MOVE = INTER-PROCESSOR EXCHANGE, processor p (Master) randomly selects a cell CELL(p) with (x,y)-position POS(p) within its allocated area map and sends the data structure of CELL(p) to processor q. Meanwhile processor q (Slave) also randomly selects a cell CELL(q) with (x,y)-position POS(q) within its allocated area map, and sends the data structure of CELL(q) to processor p.

```

STEP 4.1 Compute \Delta_{exchange}(CELL(p),CELL(q)) = \Delta_1(WL,CELL(p),POS(q),p) + \Delta_2(WL,CELL(q),POS(p),q) + \Delta_3(AO,CELL(p),POS(p),p) + \Delta_4(AO,CELL(p),POS(q),q) + \Delta_5(AO,CELL(q),POS(q),q) + \Delta_6(AO,CELL(q),POS(p),p) + \Delta_7(EO,CELL(p),POS(p),p) + \Delta_8(EO,CELL(p),POS(q),q) + \Delta_9(EO,CELL(q),POS(q),q) + \Delta_{10}(EO,CELL(q),POS(p),p)

```

STEP 5.1 Processor q sends the portion of the cost function it computed to processor p.

STEP 6.1 Go to STEP 7

STEP 3.2 If MOVE = INTRA-PROCESSOR EXCHANGE, processor p (Master) randomly selects two cells,  $CELL_1(p)$  and  $CELL_2(p)$ , both within its allocated area map.

```

STEP 4.2 Compute \Delta_{exchange} (CELL<sub>1</sub>(p),CELL<sub>2</sub>(p)) = \Delta_1(WL,p) + \Delta_2(AO,p) + \Delta_3(EO,p)

```

STEP 5.2 Go to STEP 7

STEP 3.3 If MOVE = INTER-PROCESSOR DISPLACEMENT, processor p (Master) selects a cell CELL(p) with position POS(p) within its allocated area map and sends the data structure for CELL(p) along with the portion of the cost function it has computed to processor q (Slave). Processor q selects a random position POS(q) within its area map and computes the remainder of the cost function.

```

STEP 4.3 Compute \Delta_{displace} (CELL (p), POS (q)) = \Delta_1(WL, CELL (p), POS (q), q) + \Delta_2(AO, CELL (p), POS (p), p) + \Delta_3(AO, CELL (p), POS (q), q) + \Delta_4(EO, CELL (p), POS (p), p) + \Delta_5(EO, CELL (p), POS (q), q)

```

STEP 5.3 Go to STEP 7.

STEP 3.4 If MOVE = INTRA-PROCESSOR DISPLACEMENT, processor p randomly selects a cell, CELL(p), and a position, POS(p), within its allocated area map.

STEP 4.4 Compute

$$\Delta_{displace}(CELL(p),POS(p)) = \Delta_1(WL,p) + \Delta_2(AO,p) + \Delta_3(EO,p)$$

STEP 7 Master accepts/rejects move using exponential function ACCEPT (DELTA, T) END PROCEDURE;

Figure 3.4. Parallel moves in the hypercube.

A move can be either an exchange or a displacement. Which of these is actually executed is randomly chosen by the Master in STEP 2 of Figure 3.4. The ratio of single-cell displacements to cell exchanges has a profound effect on the quality of the final placement. The best results were observed to occur when the random selection favors displacements in a ratio of approximately 5 to 1 similar to the result reported in [10]. In addition, the Master decides if the exchange or displacement move will be an intraprocessor (completely within the Master) or interprocessor (between the Master and the Slave). The best results were observed to occur when the number of intraprocessor moves is equal to the number of interprocessor moves. Orientation mirroring of cells was not implemented.

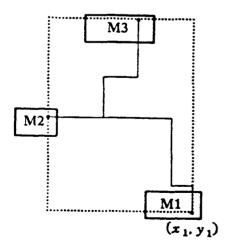

# 3.7.3. Cost calculation of exchange class move

We now discuss the cost function calculation for an interprocessor exchange, i.e., STEP 4.1. of Figure 3.4, which is the most complicated of all the move types. (The case of an intraprocessor exchange, STEP 4.2, is very simple.) We break up the task of calculating the cost of an interprocessor exchange move into 10 subtasks that are distributed equally among the Master and Slave processors. The first term,  $\Delta_1(WL,CELL(p),POS(q),p)$  deals with the change in the wire length due to the movement of CELL(p) from POS(p) to POS(q). This is calculated by estimating the change in half the perimeter of the bounding box of each net. This term can be calculated by processor p alone, since it keeps information about all the nets to which CELL(p) is connected, along with all the (x,y) locations of cells that are on the same nets, and can read POS(q) (which is the new (x,y) location CELL(p)) from the message by processor  $\Delta_2(WL,CELL(q).POS(p),q)$  relates to the change in wire length due to the movement of CELL(q) from POS(q) to POS(p), and is computed in an identical manner by processor q. The term  $\Delta_3(AO.CELL(p).POS(p),p)$  deals with the change in the area overlap of cells due to the movement of CELL(p) out of POS(p) and is calculated by processor p since it has information about all the cells that are near a given (x,y) location within processor p's area map. When CELL(p) is moved out of location POS(p), it may remove area overlapping of cells. The term  $\Delta_4(AO,CELL(p),POS(q),q)$  deals with the change in the cell area overlap due to the movement of CELL(p) into POS(q) and is calculated by processor q since it has information about all the cells that are near a given (x,y) location within processor p's area map. When CELL(p) is moved into location POS(p), it might create additional cell area overlap. The terms  $\Delta_5$  and  $\Delta_6$  are similar calculations for CELL(q). The term  $\Delta_7(EO,CELL(p),POS(p),p)$  deals with the change in actual row length compared to desired row length (edge overshoot or undershoot) when CELL(p) is moved out of POS(p), and is calculated by processor p. The term  $\Delta_8(EO,CELL(p),POS(q),q)$  deals with the change in edge overshoot/undershoot when CELL(p) is moved into POS(q), and is calculated by processor q. The terms  $\Delta_9$  and  $\Delta_{10}$  are similar calculations for CELL(q).

### 3.7.4. Cost calculation for displacements

We now discuss how the cost function is calculated for an interprocessor displacement class move, STEP 4.3. (The intraprocessor displacement calculation in STEP 4.4 is relatively straightforward.) We break up the task into 5 subtasks that are shared between the Master and the Slave processors. The term  $\Delta_1(WL,CELL(p),POS(q),q)$ , computed by processor q, is the change in wire length due to the movement of CELL(p) from POS(p) to POS(q). The term  $\Delta_2(AO,CELL(p),POS(p),p)$ , computed by processor p, is the change in cell area overlap caused by the movement of CELL(p) out of POS(p). The term  $\Delta_3(AO,CELL(p),POS(q),q)$ , computed by processor q, is the change in cell area overlap caused by the movement of CELL(p) into POS(q). The term  $\Delta_4(EO,CELL(p),POS(p),p)$ , computed by processor p, is the change in edge overshoot/undershoot caused by the movement of CELL(p) out of POS(p). The term  $\Delta_5(EO,CELL(p),POS(q),q)$ , computed by processor p, is the change in edge overshoot/undershoot caused by the movement of CELL(p) into POS(q).

### 3.8. Annealing Schedule

In any simulated annealing algorithm, two important criteria are the choice of the initial temperature and the rate of decrease of the temperature. For the choice of the initial temperature, we

adopted the heuristic that at the initial temperatures, we should accept 95% of all moves for which there is an increase in the cost function. Hence, prior to starting the actual annealing algorithm, we calculate the change in cost functions for  $10 \times N$  (N = number of standard cells in circuit) single moves within the hypercube. The average change,  $\Delta$ , is calculated for those moves in which the change in cost is positive. This average cost is then used to find a proper initial temperature using the following formula:

$$T_{init} = -\frac{\Delta}{\ln{(0.95)}}$$

The temperature of the system is then reduced after each stage of the algorithm according to the cooling schedule given by

$$T_{i+1} = \alpha(i)T_i$$

where  $\alpha$  varies from 0.80 to 0.94 and decreases to 0.1 during the final stages of the algorithm. This variation is table-driven, as shown in Table 3.1. By using this strategy, during the initial stages of the algorithm virtually every new state is accepted and the temperature is reduced quite rapidly.

Table 3.1. Variation of alpha with temperature.

| For Temperature<br>Greater Than | α    |

|---------------------------------|------|

| 40,000                          | 0.80 |

| 20,000                          | 0.84 |

| 10,000                          | 0.88 |

| 5,000                           | 0.91 |

| 200                             | 0.94 |

| 100                             | 0.90 |

| 50                              | 0.85 |

| 5                               | 0.80 |

| 1.5                             | 0.70 |

| 0                               | 0.10 |

During the intermediate stages of the algorithm, the temperature is reduced in such a way that the average change in cost  $\Delta C$  for proposed moves is approximately equal from iteration to iteration. When the temperature is reduced below 1.5, rapid reduction in temperature is initiated in order for the system to firmly converge to a local minimum of the cost function. The final stopping criterion is satisfied when the temperature reaches a minimum value of 0.1.

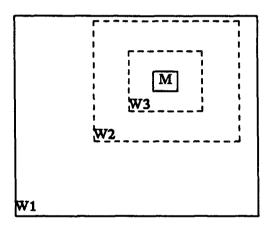

In order to enhance convergence during the later stages of the algorithm, a range limiting mechanism is incorporated similar to TimberWolf [10]. For single intraprocessor displacements, a rectangular window is centered at the center of the cell to be displaced. A row is randomly selected which intersects the window and is within the locally allocated work space. A random position is then selected within that row and within the window or locally allocated work space, which ever is smaller. For proposed pairwise cell exchanges and interprocessor displacements, a move is attempted only if (1) the vertical distance between the change in movement of cell(s) is less than or equal to the vertical span of the range limiter window and (2) the horizontal distance between the change in movement of cell(s) is less than or equal to the horizontal span of the range limiter window.

Initially when the temperature is at its maximum value, the horizontal and vertical span of the range limiter window are equal to twice the span of the corresponding dimension of the physical work space. After the initial temperature is determined, the approximate number of decades, d, from zero is determined. Because it is desirable to have the window size shrink slowly, the horizontal and vertical window spans are made proportional to the logarithm base 10 of the value of the temperature. The actual formula controlling the respective window dimensions are shown below.

$$\frac{windowX}{2} = MAX[3, \frac{1}{d}xspan \log_{10}(0.2temperature)]$$

$$\frac{windowY}{2} = MAX[3, \frac{1}{d}yspan \log_{10}(0.2temperature)]$$

Regardless of row separation, the vertical range limiter is restricted from reducing below the distance needed for inter-row movement until the temperature of the system drops below 5.

At high temperatures during the simulated annealing process, we do not restrict the distance over which exchanges and displacements of cells can occur. Gradually, as the temperature is decreased for each processor, the range limit is also decreased accordingly until eventually certain dimensions of the hypercube are "frozen," i.e., changes between pairs of processors connected via those dimensions are effectively inhibited.

At each new temperature, the system is allowed to stabilize. This is accomplished by collectively attempting to generate a user-specified number of new states per cell at each stage/temperature of the system. For example, given a 1000 cell circuit for which a user wishes 300 attempts per cell, 300000 new states per stage/temperature will be attempted. The number of attempts per cell is directly proportional to the running time of the algorithm, and is the only user specified parameter which influences the run time. Large numbers of attempts per cell will give better placement but at the cost of excessive execution times. In general, to get the best performance to execution time ratio, Table 3.2 should be used as a guideline for various size circuits.

Table 3.2. Suggested attempts per cell for various size circuits.

| Number of Cells in Circuit | Suggested Number of<br>Attempts per Cell |

|----------------------------|------------------------------------------|

| <300                       | 100                                      |

| 500                        | 200                                      |

| 1000                       | 300                                      |

| 1500                       | 400                                      |

| 2000                       | 500                                      |

| 2500                       | 600                                      |

| 3000                       | 700                                      |

# 3.9. Broadcasting New Cell Locations

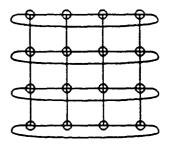

Once the cells have been moved to new locations, these updated locations have to be sent to all processors so that they can update all net and pin information affected by the move. Two schemes for performing this task were investigated.

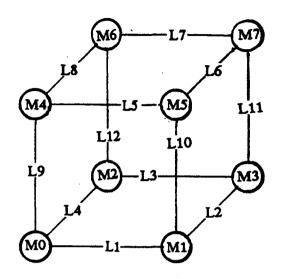

The first one uses uses the property of the existence of Hamiltonian circuits in the hypercube topology [55]. This scheme operated in the following manner. Each processor which has an updated cell location informs its Hamiltonian circuit successor of the updated value of the cell location. This processor would then inform its Hamiltonian circuit successor which would do the same. It can be easily seen that if all P processors contained updated cell locations, it will take P-1 time steps for all the updated cell locations to be available at all the processors. Figure 3.5 shows a three-dimensional hypercube with labels on processing nodes and links. Using this simple scheme, if processor 0, which is labeled M0, has an updated cell location to broadcast throughout the hypercube, a possible Hamiltonian circuit is M0, M1, M3, M2, M6, M4, M5, M7. This broadcast uses links L1, L2, L3, L12, L8, L5, and L6 requiring 7 time steps. Since each message transfer is extremely expensive, we decided to abandon this simple scheme and adopt a more complicated but extremely efficient one.

In the second scheme, each processor having a set of new cell locations broadcasts this information to all its log(P) neighbors in the first time step along its links in log(P) dimensions. In the next time step, the processors that have just received these messages from the first time step forward the messages to their own neighbors connected via links in the higher-most log(P)-i-1 dimensions where i equals the dimension of the link along which a message was received during the first time step. In the  $j^{th}$  time step, all processors receiving messages from the  $j-1^{tt}$  time step forward the messages to their neighbors in the higher most log(P)-i-1 dimensions where i again equals the dimension of the link along which a message was received during the  $j-1^{tt}$  time step. In the case of multiple initial processors wanting to broadcast modified cell locations, the messages are combined where needed at intermediate nodes before forwarding. This scheme guarantees that the

broadcasting is completed in log(P) time steps without conflicts for links. Figure 3.5 shows a three-dimensional hypercube with labels on processing nodes and links. Table 3.3 shows the steps involved in broadcasting updated cell locations from processors 1, 2, and 7 which are labeled as M1, M2, and M7 in Figure 3.5.

The entries in Table 3.3 are of the form Mi(j,k) which represents a message which originated from processor  $P_i$  during the first time step and moves from processor  $P_j$  to  $P_k$  during the current time step. For example, in time step 2, message M7(6,4), which has originated from  $P_7$ , is transmitted from processor  $P_6$  to  $P_4$  along a dimension 1 link. It can be verified that all messages reach all processors within 3 time steps. In case of conflicts for using a particular link at a particular time step, messages are combined. For example, in time step 2, link L9 has two messages M1(0,4) and M2(0,4) which represent messages originating from processors  $P_1$  and  $P_2$  but moving from  $P_0$  to  $P_4$  during time step 2.