(NASA-CR-178390) A FAULT INJECTION N88-20895 EXPERIMENT USING THE AIRLAE FLAGNOSTIC FEULATION FACILITY (Research Triangle Inst.) 130 p CSCL 09B Unclas G3/62 0134590

### NASA Contractor Report 178390

## A FAULT INJECTION EXPERIMENT USING THE AIRLAB DIAGNOSTIC EMULATION FACILITY

Robert Baker, Scott Mangum, and Charlotte Scheper

Center for Digital Systems Research Research Triangle Institute Research Triangle Park, North Carolina 27709

Contract NAS1-17964 Task Assignment No. 5 March 1988

Langley Research Center Hampton, Virginia 23665

## NASA Contract Report 178390

# A FAULT INJECTION EXPERIMENT USING THE AIRLAB DIAGNOSTIC EMULATION FACILITY

Robert Baker Scott Mangum Charlotte Scheper

Center for Digital Systems Research Research Triangle Institute Research Triangle Park, North Carolina 27709

> Contract NAS1-17964 Task Assignment No. 5

> > March 1988

## TABLE OF CONTENTS

| List of Figures and Tablesii                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Introduction and Scope1                                                                                                                                |

| 2. Overview of the Data Communicator/Interstage and the<br>Associated Gate Level Model4                                                                   |

| 2.1 Functional Description42.2 Circuit Description and Modeling Issues                                                                                    |

| 3. Experiment Preparation19                                                                                                                               |

| <ul> <li>3.1 Introduction</li></ul>                                                                                                                       |

| Testing of Software Items                                                                                                                                 |

| 27<br>3.6 Validation of the C/I Emulation Model                                                                                                           |

| 4. Diagnostic Emulation Experiment Description and Results40                                                                                              |

| 4.1 General Plan404.2 The Experiment444.3 Analysis of Experiment Results524.4 Review of Undetected Faults704.5 Inferences Drawn from Experiment Results73 |

| 5. Conclusions, Observations and Recommendations74                                                                                                        |

| 6. References                                                                                                                                             |

| Appendix A. Listing of the Diagnostic Tests77                                                                                                             |

| Appendix B. Diagnostic Emulation Outputs for Non-faulted C/I                                                                                              |

### LIST OF FIGURES AND TABLES

-----

| Figure 1.1. Experiment Diagram                               |

|--------------------------------------------------------------|

| Figure 2.1. Fault Tolerant Processor (Quadriplex Version)    |

| Figure 2.2. C/I Exchange Network                             |

| Table 2.1.   Data Communicator Operations                    |

| Figure 2.3. FTP Communicator                                 |

| Figure 2.4. Actual Circuitry for Cross Channel Links         |

| Figure 2.5. More Accurate Model Used for Cross Channel Links |

| Figure 2.6. Simplified Model Used for Cross Channel Links    |

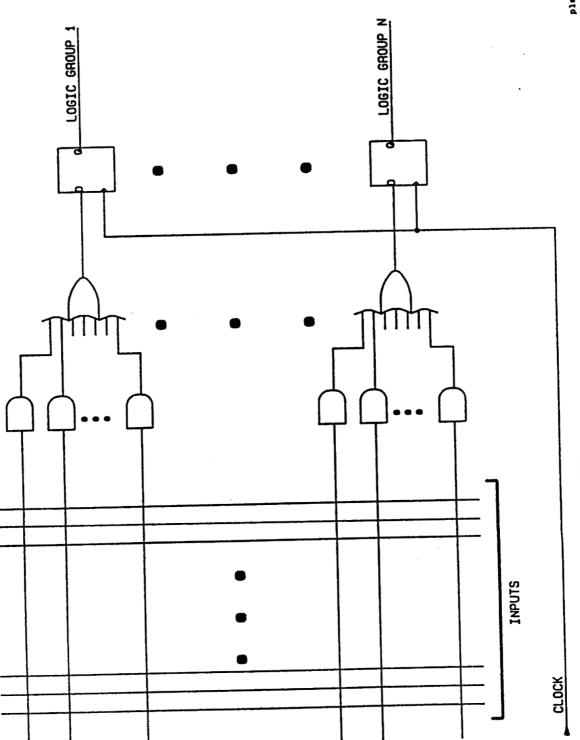

| Figure 2.7. Programmable Logic Array15                       |

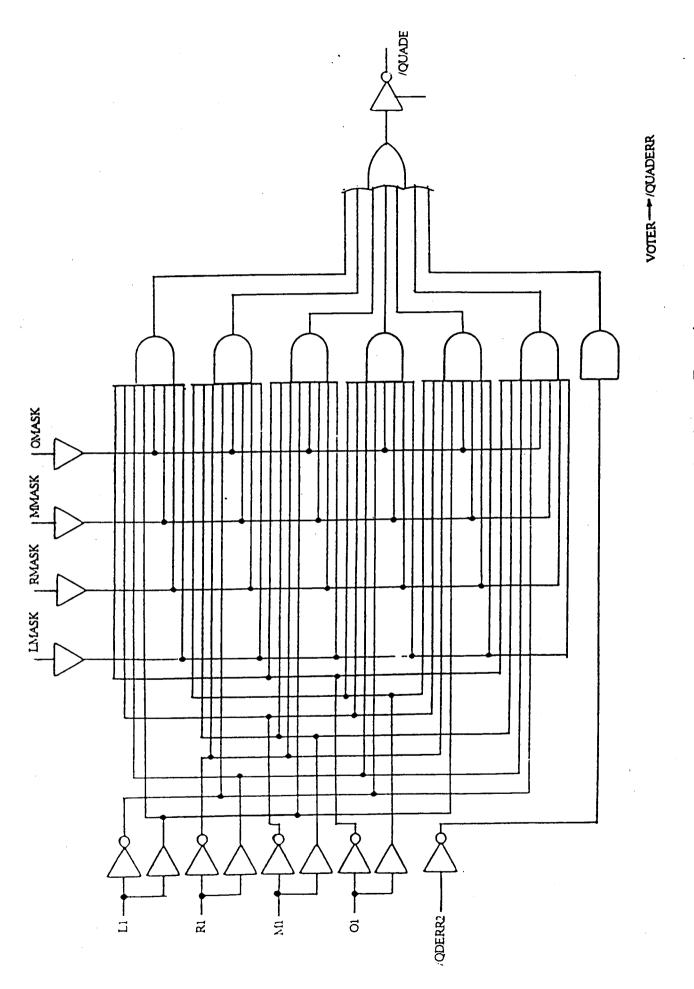

| Figure 2.8. Voter Syndrome Quaderror Function16              |

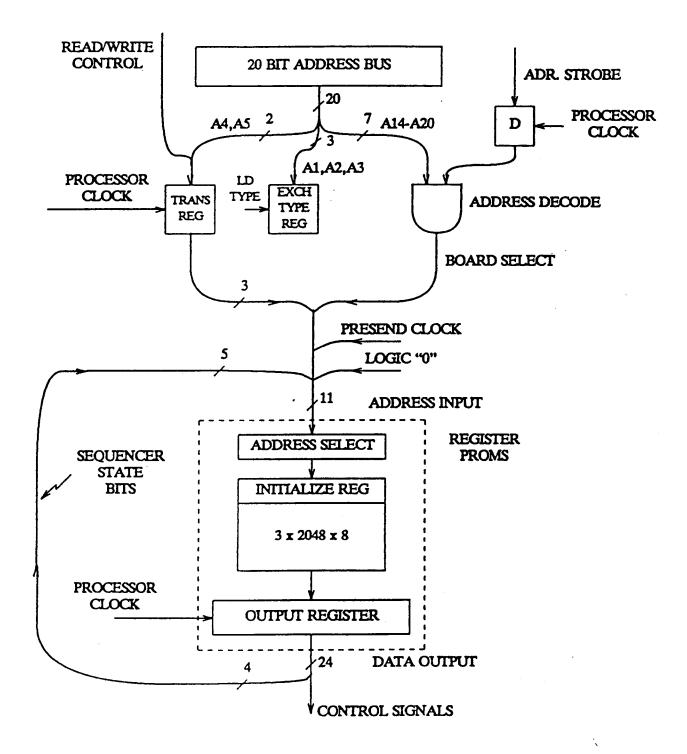

| Figure 2.9. Communicator Control Sequencer                   |

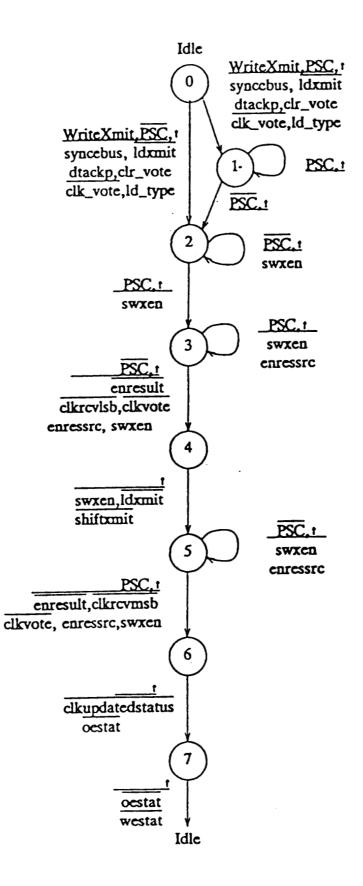

| Figure 2.10 Write XMIT State Diagram                         |

|                                                              |

| Figure 3.1. System Flow Diagram20                            |

| Figure 3.2. Network Initialization                           |

| Figure 3.3. Emulation Process                                |

| Table 3.1.    C/I Instruction Mnemonics    25                |

| Figure 3.4. Block Diagram of Test Circuit                    |

| Figure 3.5. Network Model Preparation (Desired)              |

| Figure 3.6. Network Model Preparation (Actual)               |

| Figure 3.7. Communicator/Interstage Exchange Network         |

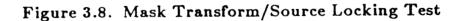

| Figure 3.8. Mask Transform/Source Locking Test               |

| Figure 3.9. Error Logging/Masking Network                    |

| (One Network for Each Processor)                             |

| Figure 3.10. Typical C/I Self Test Sequence for a            |

| Single Test Vector35                                         |

| Figure 3.11. Tests Used for Experiment                       |

| Figure 3.12. Diagnostic Sequences                            |

|                                                              |

| Figure 4.1. Communicator/Interstage Model41                  |

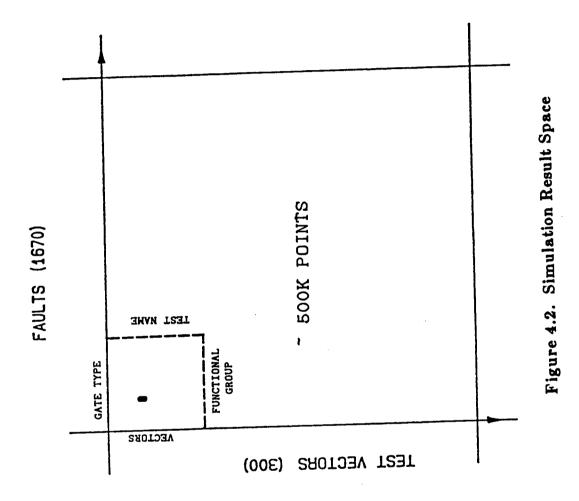

| Figure 4.2. Simulation Result Space42                        |

| Figure 4.3. Diagnostic Sequences43                           |

| Figure 4.4. Fault Sets by Functional Group45                 |

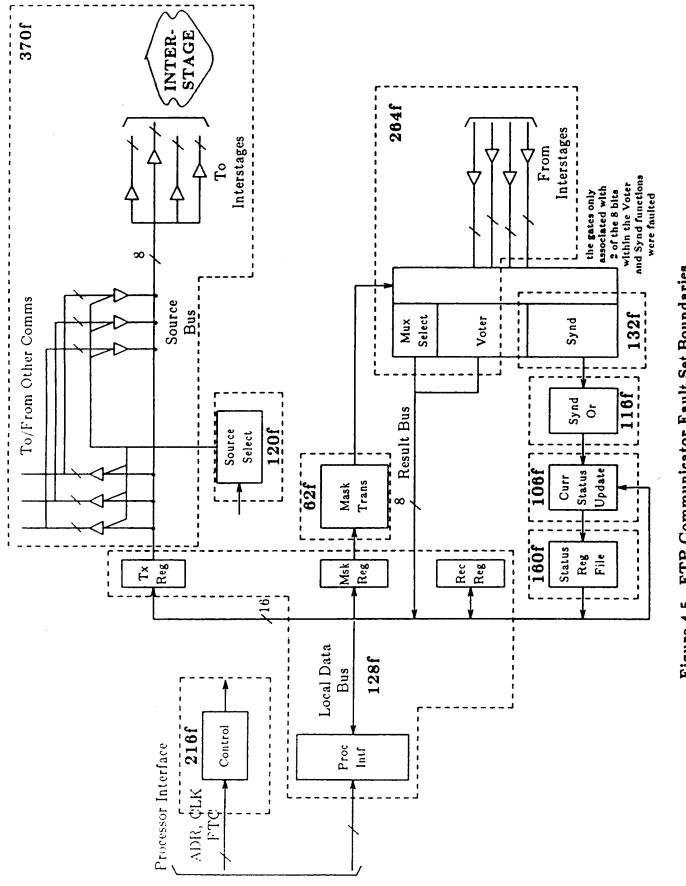

| Figure 4.5. Communicator Fault Set Boundaries46              |

| Figure 4.6. Typical Good Circuit Output47                    |

| Figure 4.7. Typical Post-Processing Output48                 |

| Figure 4.8. Emulation CPU Time49                             |

| Figure 4.9. Some Diagnostic Emulation Experiment Numbers     |

| Figure 4.10, Summary of Diagnostic Emulation Speed51         |

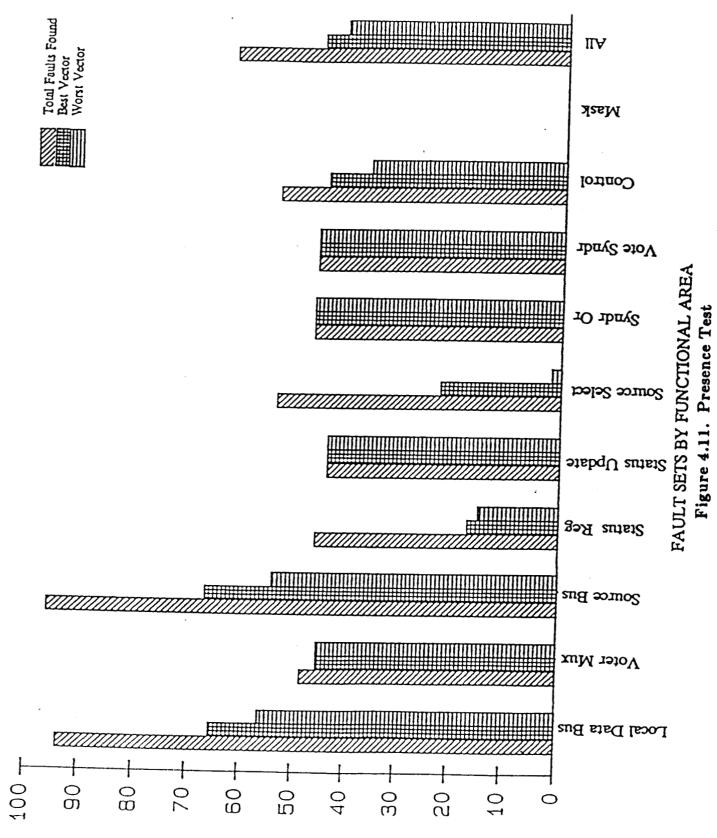

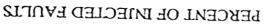

| Figure 4.11. Presence Test53                                 |

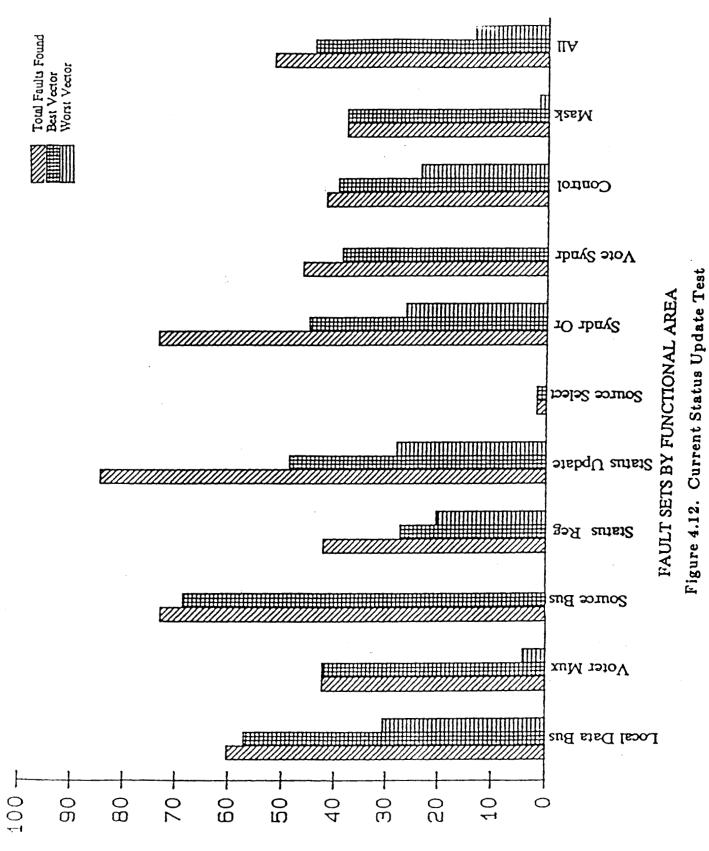

| Figure 4.12. Current Status Update Test                   | 55  |

|-----------------------------------------------------------|-----|

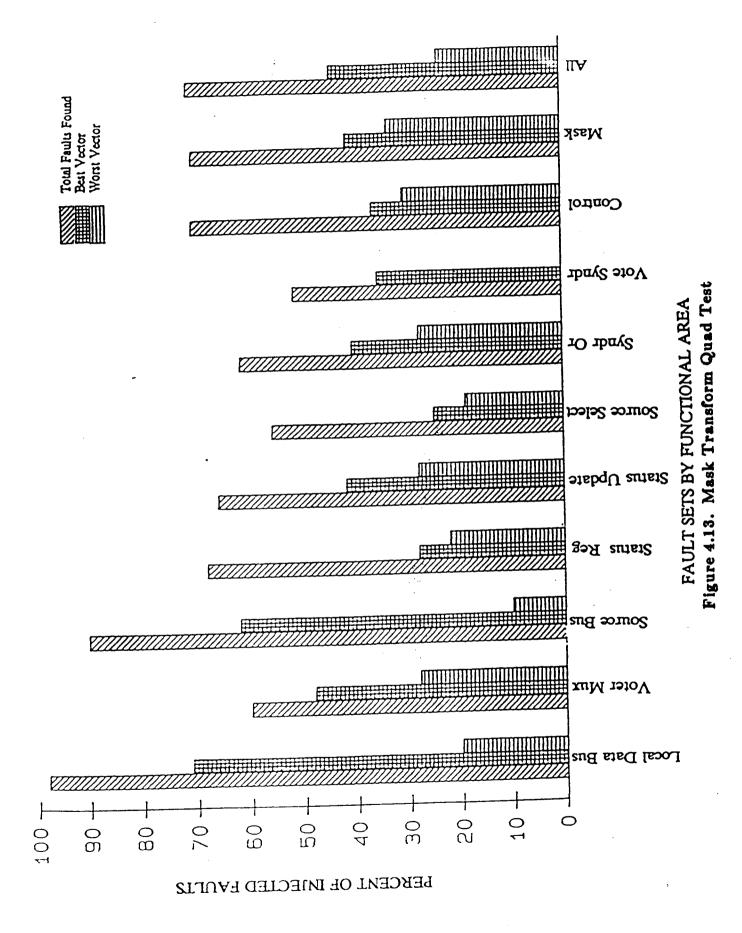

| Figure 4.13. Mask Transform Quad Test                     | 56  |

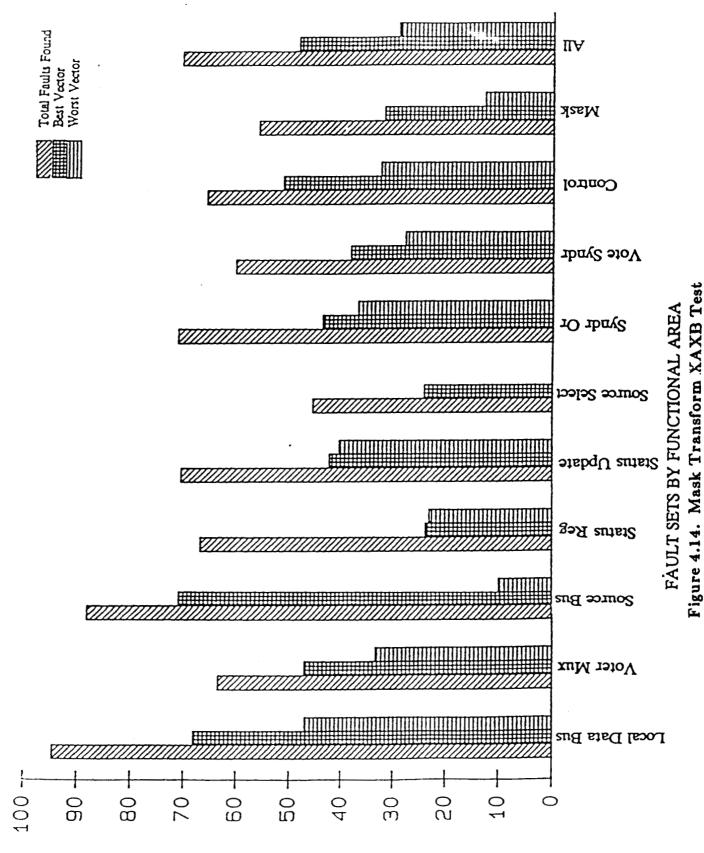

| Figure 4.14. Mask Transform XAXB Test                     | 57  |

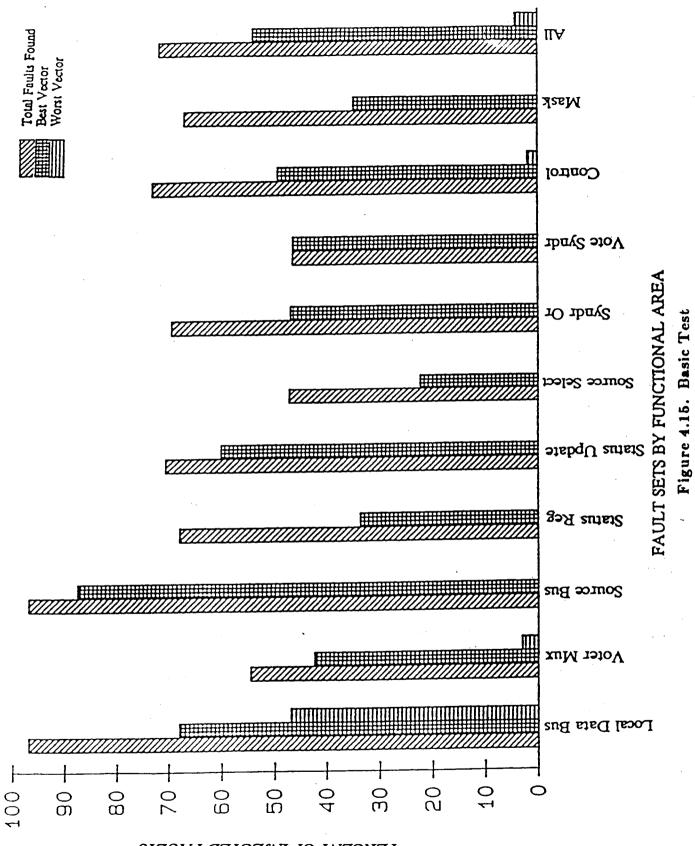

| Figure 4.15. Basic Test                                   | 58  |

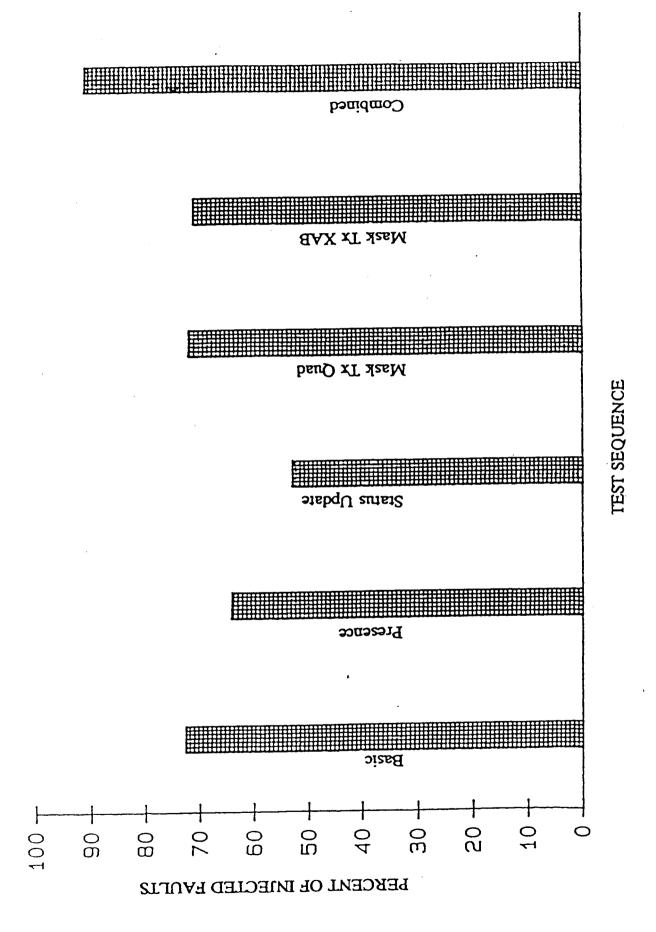

| Figure 4.16. Diagnostic Test Performance                  | 60  |

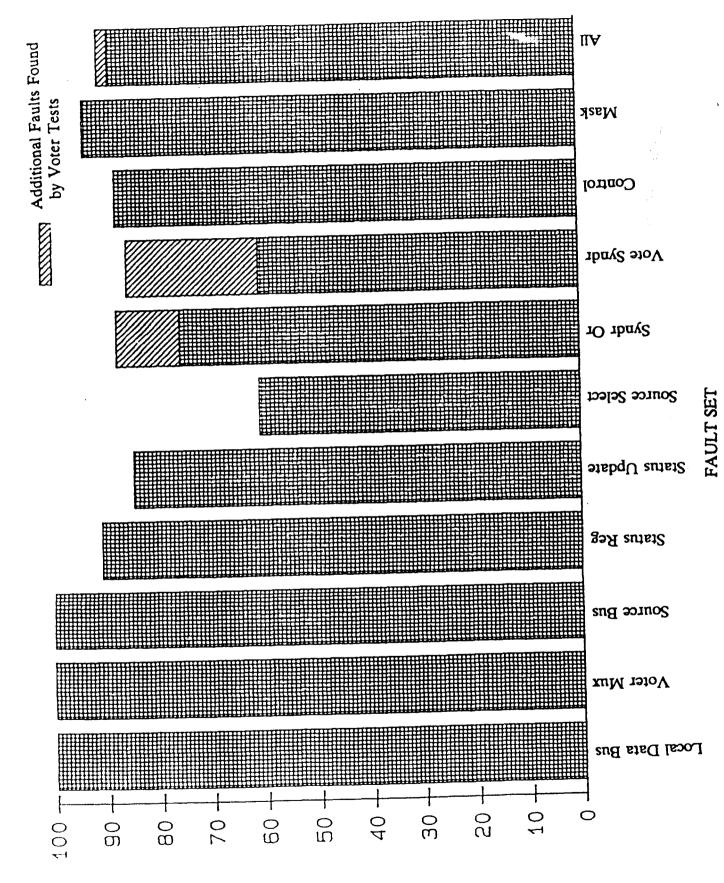

| Figure 4.17. Combined Performance of all Non-voter Tests  | 61  |

| Figure 4.18. Performance of Best Test for A               |     |

| Given Fault Set                                           | 62  |

| Figure 4.19. Performance of Worst Test for A              |     |

| Given Fault Set                                           | 63  |

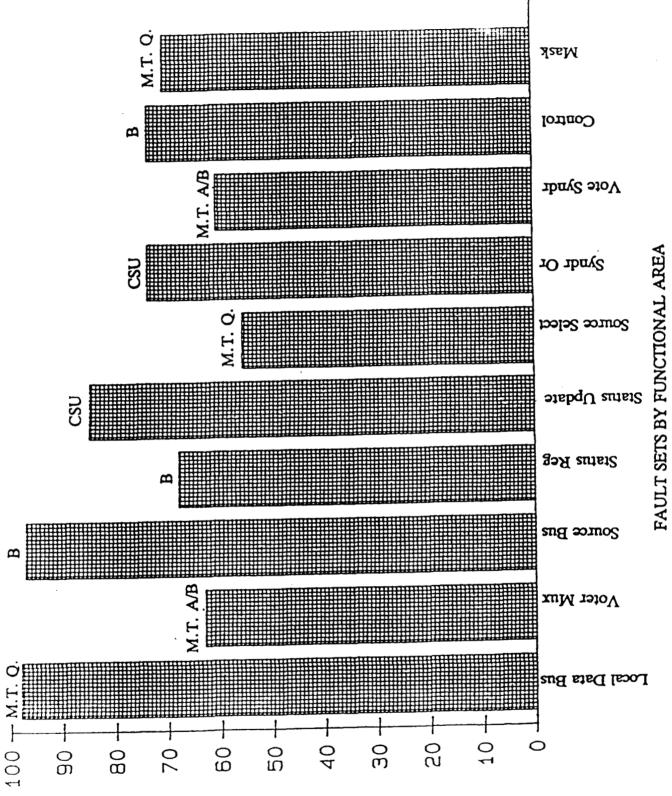

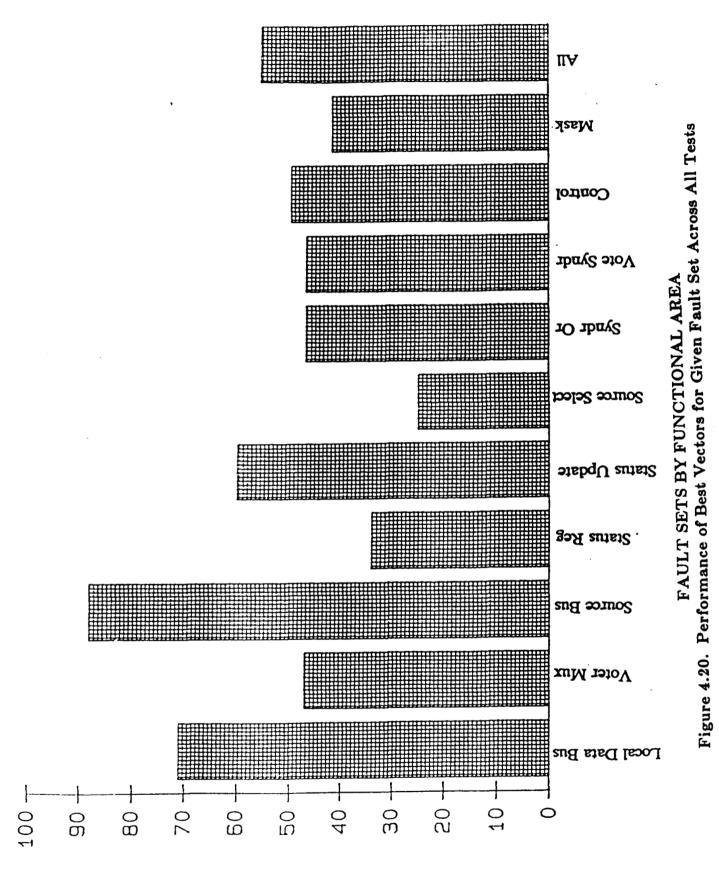

| Figure 4.20. Performance of Best Vectors Across All Tests | 64  |

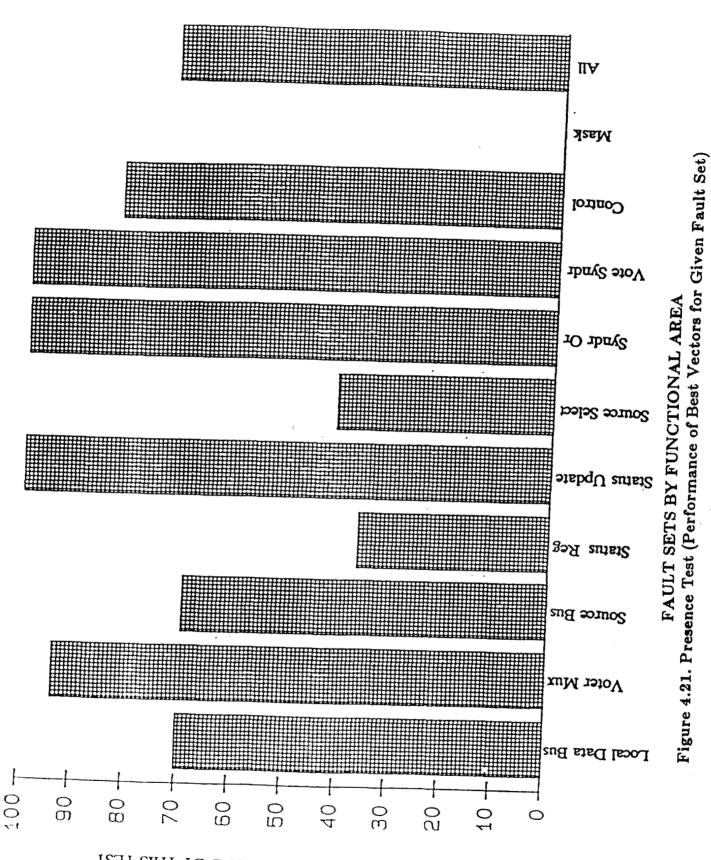

| Figure 4.21. Presence Test (Best Vectors)                 | 65  |

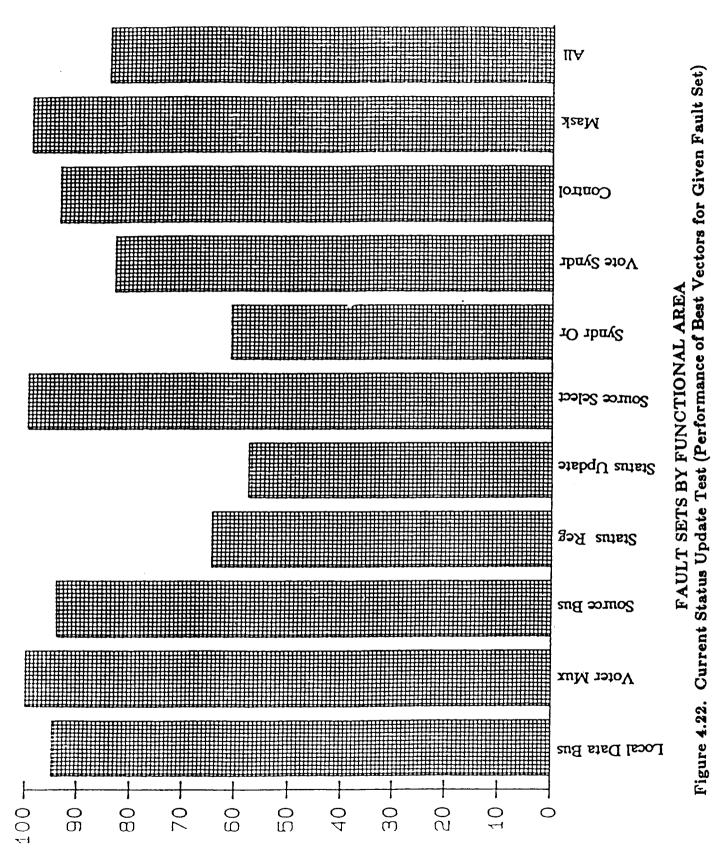

| Figure 4.22. Current Status Update Test (Best Vectors)    | .66 |

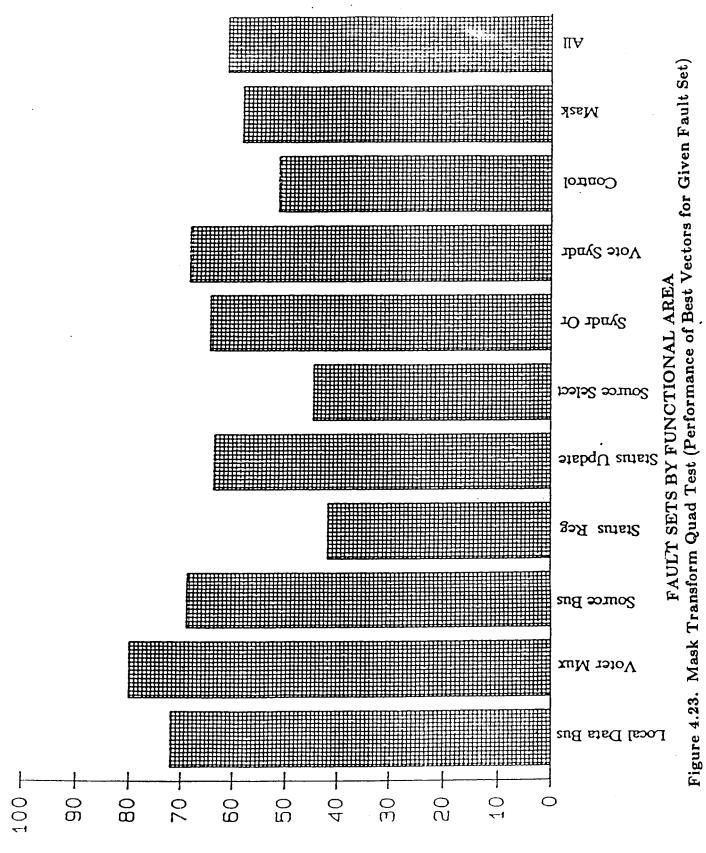

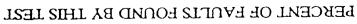

| Figure 4.23. Mask Transform Quad Test (Best Vectors)      | 67  |

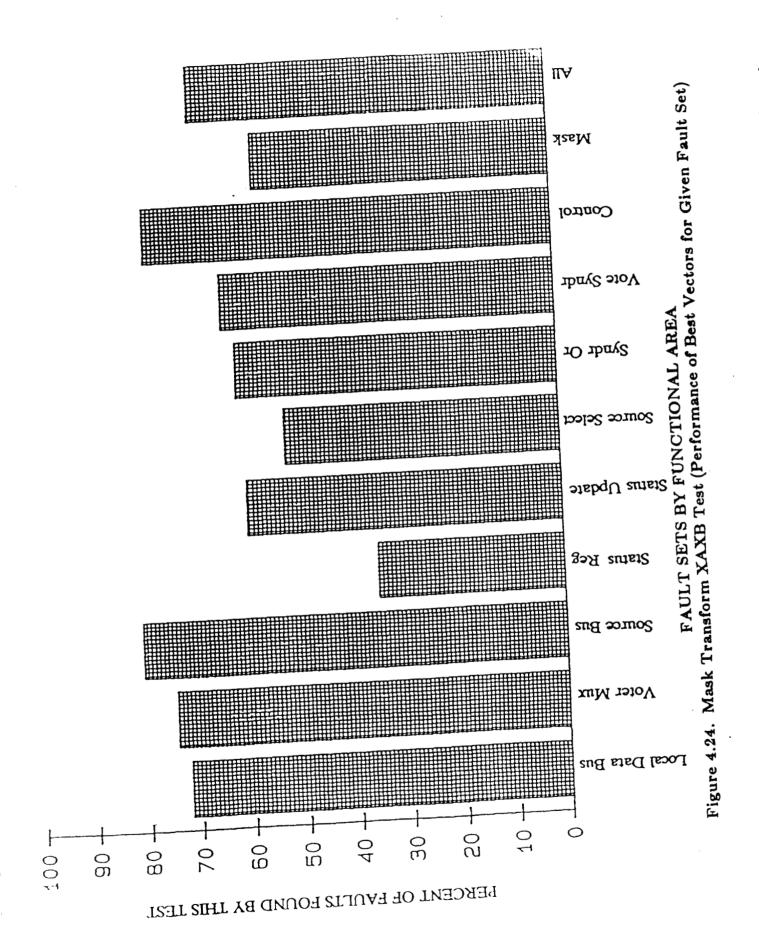

| Figure 4.24. Mask Transform XAXB Test (Best Vectors)      |     |

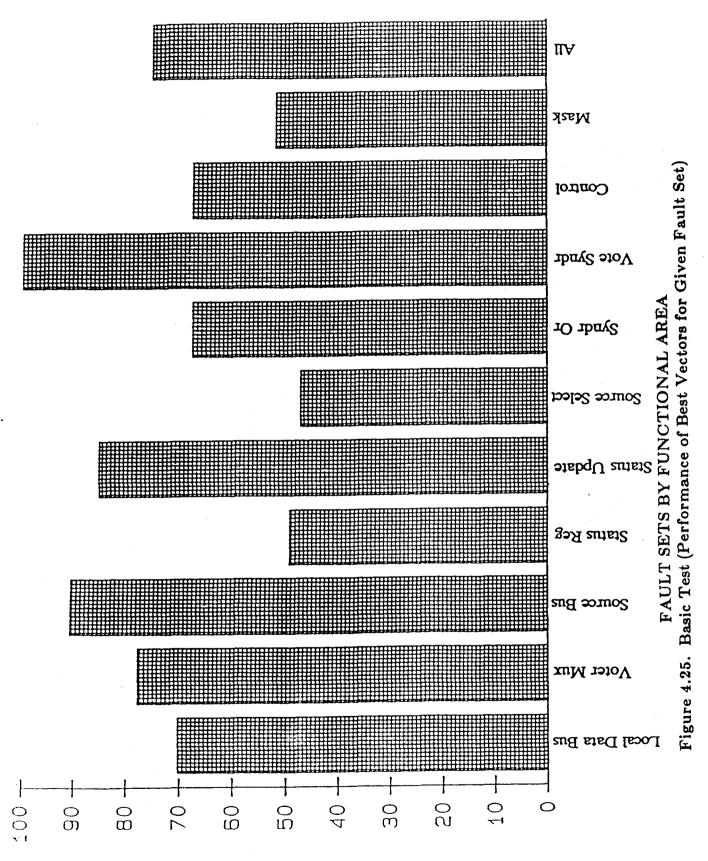

| Figure 4.25. Basic Test (Best Vectors)                    | 69  |

| Table 4.1. Summary of Undetected Faults                   | 72  |

Ŷ

#### 1. Introduction and Scope

Digital flight control systems for aircraft and spacecraft perform life or mission critical functions. Extremely high reliability requirements must be established and demonstrated for these systems. To meet the reliability and performance requirements, systems become complex. Complexity and demanding requirements combine to render the validation of system reliability difficult. Testing, sufficient to establish the high reliability of these systems, is not feasible. Consequently, sophisticated reliability modeling tools based on analytic models are needed to predict and validate reliability for both the design and development phases of fault tolerant systems. Reliability modeling tools depend upon the accurate determination of various model parameters such as fault coverage and fault latency. When system testing to determine such parameters is precluded, computer simulations can be used in some circumstances to stand-in for a system. This report describes the preparation for, conduct of, and results of a simulation-based fault injection experiment conducted using the AIRLAB Diagnostic Emulation (DE) facilities.

The primary objective of this experiment was to determine the effectiveness of the diagnostic self test sequences used to uncover latent faults in a logic network providing the key fault tolerance features for a flight control computer. Since this experiment resulted in the most extensive use of the AIRLAB Diagnostic Emulation facilities to date, a secondary, but essential, objective was to develop methods, tools, and techniques for conducting the experiment.

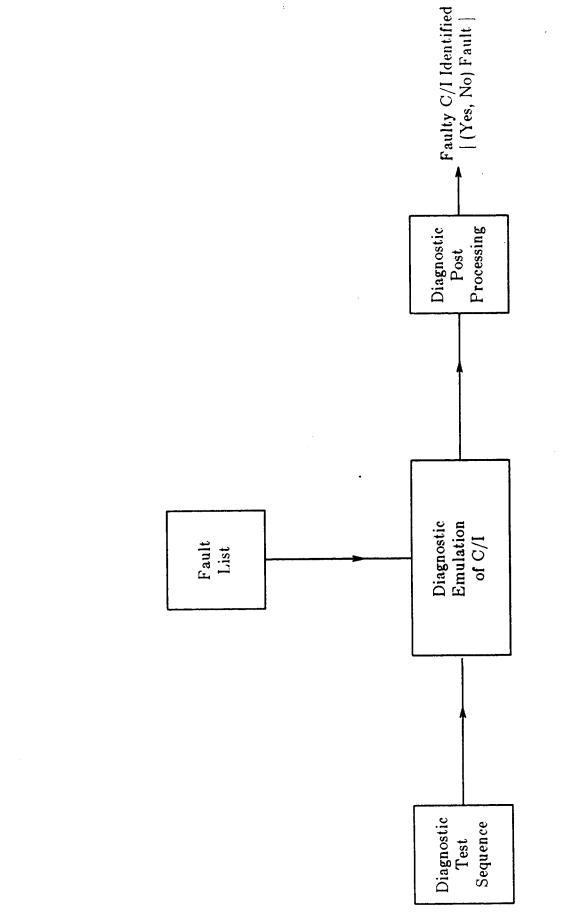

In this experiment, more than 1600 faults were injected into a logic gate level model of the Data Communicator/Interstage (C/I), a key component in the Charles Stark Draper Laboratories (CSDL) Fault Tolerant Processor (FTP). For each fault injected, diagnostic self test sequences consisting of over 300 test vectors were supplied to the C/I model as inputs. For each test vector within a test sequence, the outputs from the C/I model were compared to the outputs of a fault free C/I. If the outputs differed, the fault was considered detectable for the given test vector. These results were then analyzed to determine the effectiveness of various test sequences, to identify latent faults, and to identify opportunities for improving the performance of the diagnostic test sequences. Figure 1.1 diagrams the essential elements of the experiment design.

The Data Communicator/Interstage of the FTP was selected because of the following:

- 1. the C/I network provides for the critical fault tolerance features of input source congruency, error masking, error reporting and system reconfiguration,

- 2. the quadriplex C/I network used the full capacity of the AIRLAB Diagnostic Emulator,

- 3. documentation for the C/I design at the logic gate level was available, and

4. the results of the experiment could provide valuable information about the FTP design.

To prepare for and complete this experiment, several major issues had to be considered. Chief among these were design capture for a complex network; validation of the model derived from the design capture; analyses and decisions that reduced the required simulation time while preserving essential information; the design of test sequences for a complex state network; the applicability of fault models for LSI technology; the complexity management issues associated with modeling, validating, and simulating a large network; CAD tools and procedures to handle the complexity management problems; techniques to maintain data integrity for extended simulations; techniques for improving fault coverage and latency; and performance measures and techniques for analyzing the effectiveness of test vectors. Each of these issues can develop into significant problem areas as system complexity increases with the advancement of integrated circuit and computer architecture technology. Specifically, simulation methods, techniques, and associated tools will have to advance to meet the demands of computer technology. Moreover, validation research in general will be significantly impacted by some of these issues.

Section 2 of this report provides an overview of the C/I design and discusses the gate model used for various parts of the C/I. Section 3 describes the various activities involved in the experiment preparation process. Among the activities discussed are design capture, test sequence design, and model validation. In section 4, the conduct of the experiment is reviewed and the results are presented and analyzed. Section 5 provides a summary of experiment results, a review of lessons learned from conducting the experiment and a discussion of extensions to this experiment.

ĩ

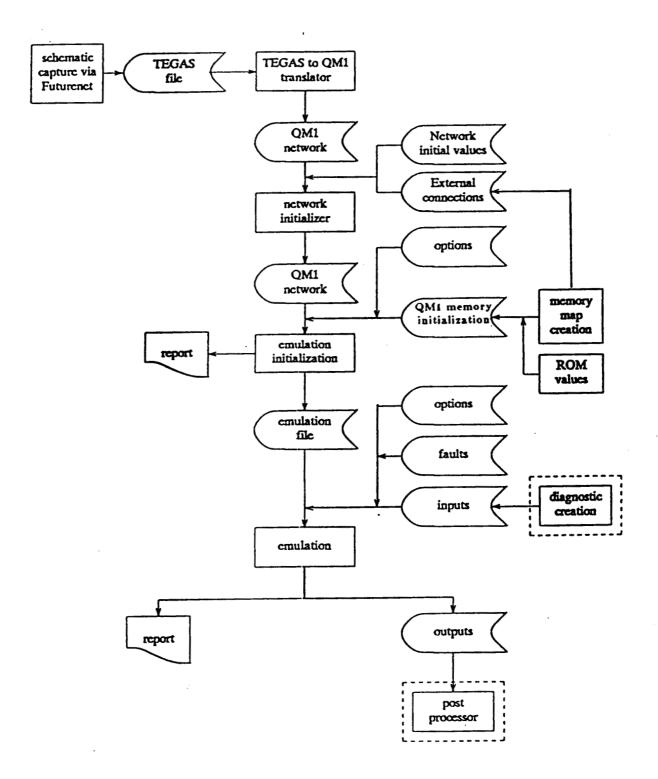

Figure 1.1. Experiment Diagram

# 2. Overview of the Data Communicator/Interstage and the Associated Gate Level Model

### 2.1. Functional Description[1] [2] [3]

The Data Communicator/Interstage (C/I), which was modeled in this experiment, provides the Fault Tolerant Processor (FTP) with certain key fault tolerance mechanisms. These mechanisms include circuitry to support the correct replication of simplex source data in all good FTP channels, to detect and mask errors in a single FTP channel, and to support FTP reconfiguration by blocking out faulty channels.

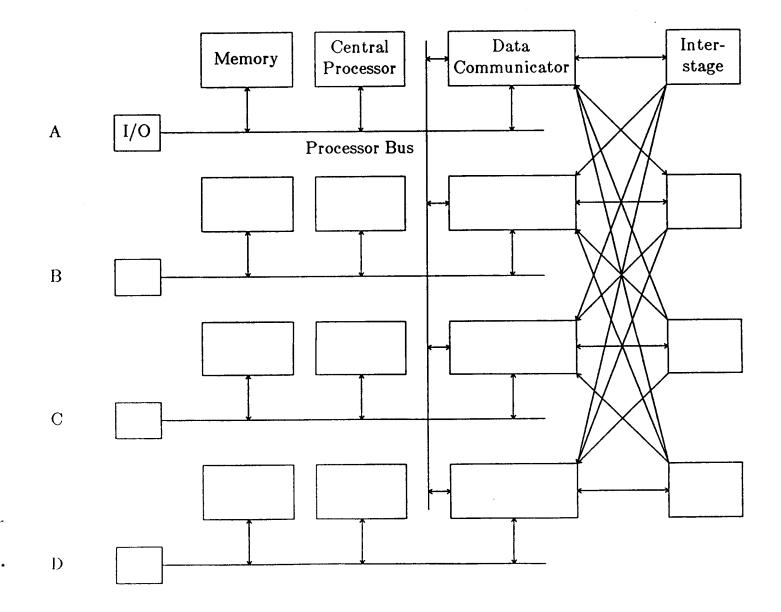

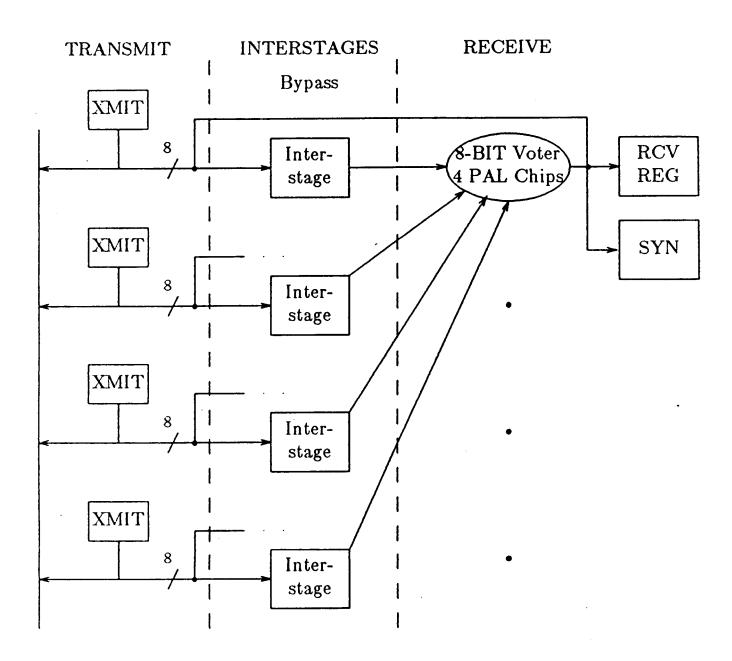

Figure 2.1 shows a quadriplex FTP.

Figure 2.2 shows the data exchange network associated with a quadriplex FTP. Each channel, A, B, C, or D, has a transmit and receive register which can be accessed by the input/output processor (IOP) or computational processor (CP) via a shared memory bus.

Simplex source data, that is, data available to one FTP channel may be distributed correctly to all good FTP channels by using a FROM X exchange. Referring to figure 2.2, a FROM A exchange, for example, will cause the data word in the communicator transmit register of channel A to be distributed to all other data communicators via the cross channel links. Data transfers between communicators and interstages are byte serial with two bytes comprising a data word. Data distributed to each communicator are passed to associated interstages.

Each interstage replicates the data and passes a copy to each communicator. Each communicator votes the data received from each interstage and writes the voted data into the Receive Register. The Receive Registers are then read by the associated channel processor. In this matter, simplex source data from channel A is replicated in all good processor channels. FROM B, FROM C, and FROM D exchanges occur in a similar manner except that the source channel is B, C, or D respectively.

If each channel has data which requires voting for fault masking, a FROM OWN exchange can be executed. Each channel places its copy of the data to be voted into its respective Transmit Registers. Data words are transmitted to the respective interstages which in turn replicate the data and distribute the copies to each communicator. Each communicator votes all copies of the data and returns the voted result to the Receive Register for subsequent reading by its associated computer.

Errors detected during the voting process of an exchange are recorded in the Status Registers of each communicator. The Status Registers of each communicator can be read by their associated processors. It is intended that these error reports be used by the FTP to determine and isolate faulty channels.

A write only Mask Register allows a channel to be excluded from the voting process.

The capability to execute exchanges which by-pass the interstage and voter is provided for network testing.

# FAULT TOLERANT PROCESSOR (Quadriplex Version)

Figure 2.1

# C/I EXCHANGE NETWORK

Figure 2.2

Table 2.1 lists the transactions on operating that can be executed by the communicator.

> FROM A Exchange FROM B Exchange FROM C Exchange FROM D Exchange FROM OWN Exchange READ Receive Register WRITE Receive Register WRITE Mask Register READ FROM A Status Register READ FROM B Status Register READ FROM D Status Register READ FROM D Status Register READ FROM D Status Register

Table 2.1. Data Communicator Operations

#### 2.2. Circuit Description and Modeling Issues

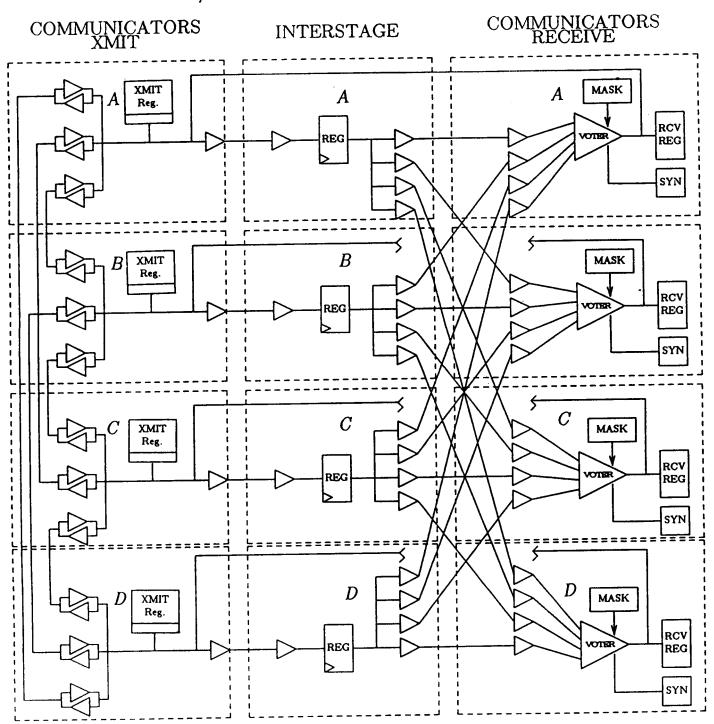

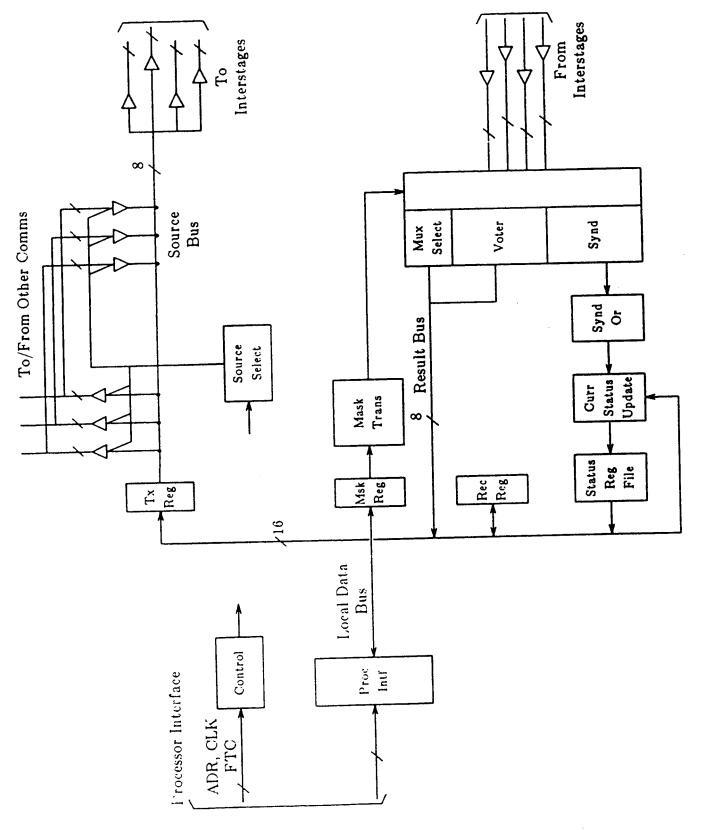

Figure 2.3 is a functional block diagram for the C/I. Each area and the associated gate level models will be described in the following paragraphs.

The processor interface consists of receivers for the 20 bit processor address bus; 16 bit bidirectional tri-state data bus driver/receivers; and receivers or drivers as required for processor control signals, data acknowledge, read/write, system reset, system clock and fault tolerant clock.

For purposes of simplifying the simulation model, the processor address bits associated with the base address for the memory mapped data communicator were consolidated into a single communicator select bit. This consolidation reduced the size of the input files for the simulation and speeded the simulation run time. A single *and* gate (address decoder) and the several address bit receivers were modeled as a single receiver. No essential fault coverage information was lost by this simplification.

The bidirectional processor data bus was modeled as separate input and output ports because the Diagnostic Emulator had capability for either input or output connections. No essential fault coverage information was lost due to this modeling restriction.

Figure 2.3. FTP Communicator

The Local Data Bus is a 16 bit tri-state bus used to communicate as follows: From Processor Bus to Transmit Register

From Processor Bus to Mask Register (5 bits)

From Processor Bus to Receive Register

From Receive Register to Processor Bus

From Status Register (5 bits) to Processor Bus

From Status Register (5 bits) to Current Status Update Logic

From Result Bus to Receive Register Most Significant Byte

From Result Bus to Receive Register Least Significant Byte

From Transmit Register Most Significant Byte to Transmit Register Least Significant Byte

This bus was modeled by use of and gates at each data source, enabled by the appropriate source enable signal, and by an or gate to combine the various data sources to one signal line. The resulting model was functionally equivalent to a tristate bus. The or function is a phantom gate in that there is no identifiable device in the network to which it can be associated. Despite its phantom nature, stuck-at zero faults were asserted on these devices during simulation to cover certain kinds of bus faults.

The Transmit Register, Mask Register and Receive Register are all implemented with 74LS374 octal D-type latches with tri-state outputs. The storage portion of these devices were modeled directly as D-type flip-flops and the tri-state output portion were modeled as *and* gates feeding an appropriate bus *or* gate as indicated in the previous paragraph.

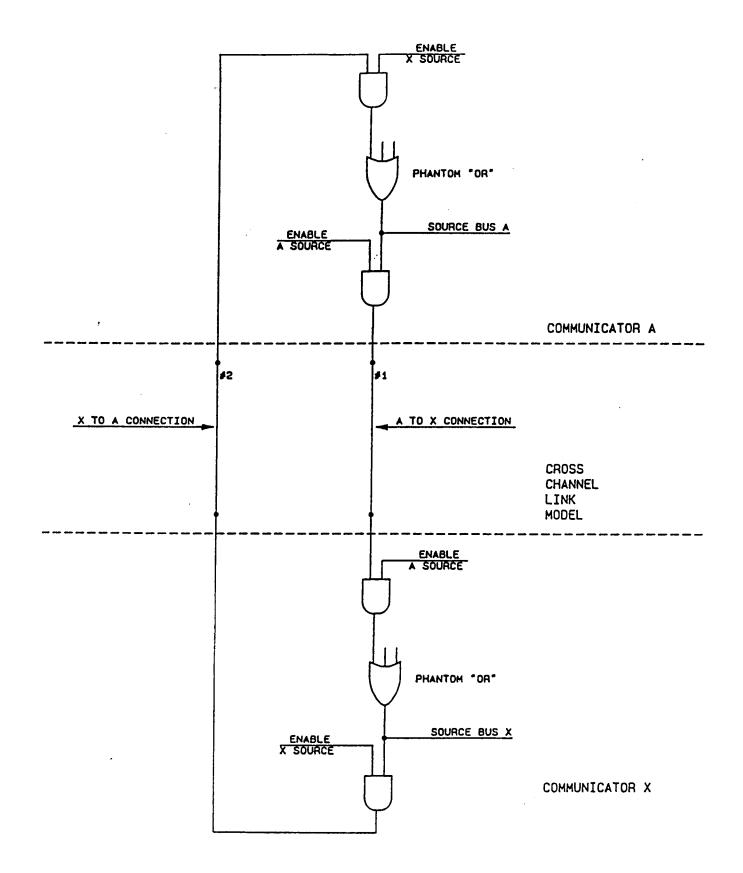

The Source Bus communicates data bytes from the Transmit Register to cross channel links and to the interstages. Also, data bytes from cross channel links can be transferred to the interstages. This bus was modeled with *and* gates and phantom *or* gates similar to the Local Data Bus.

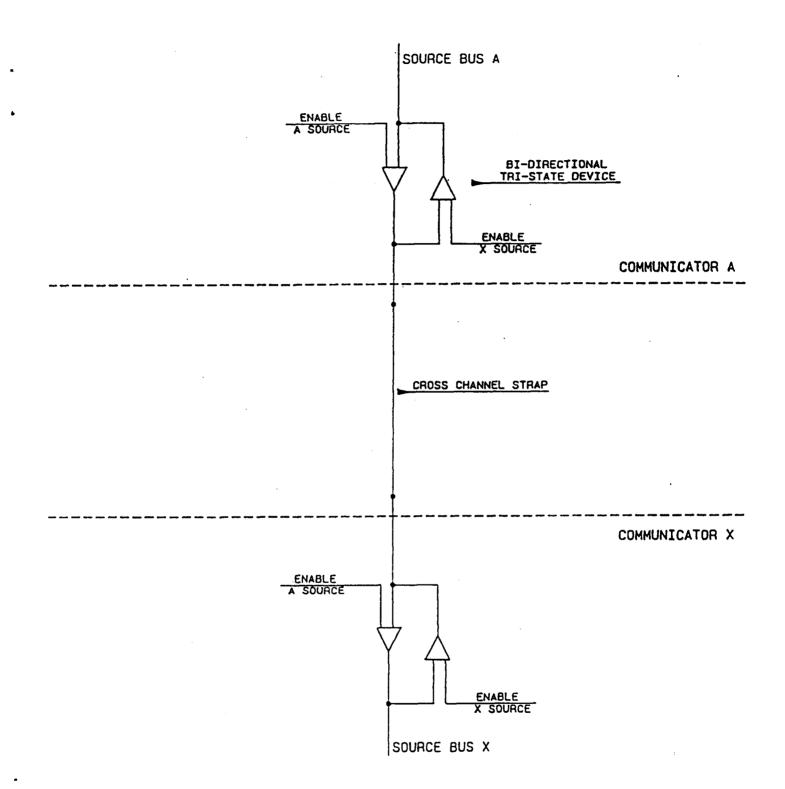

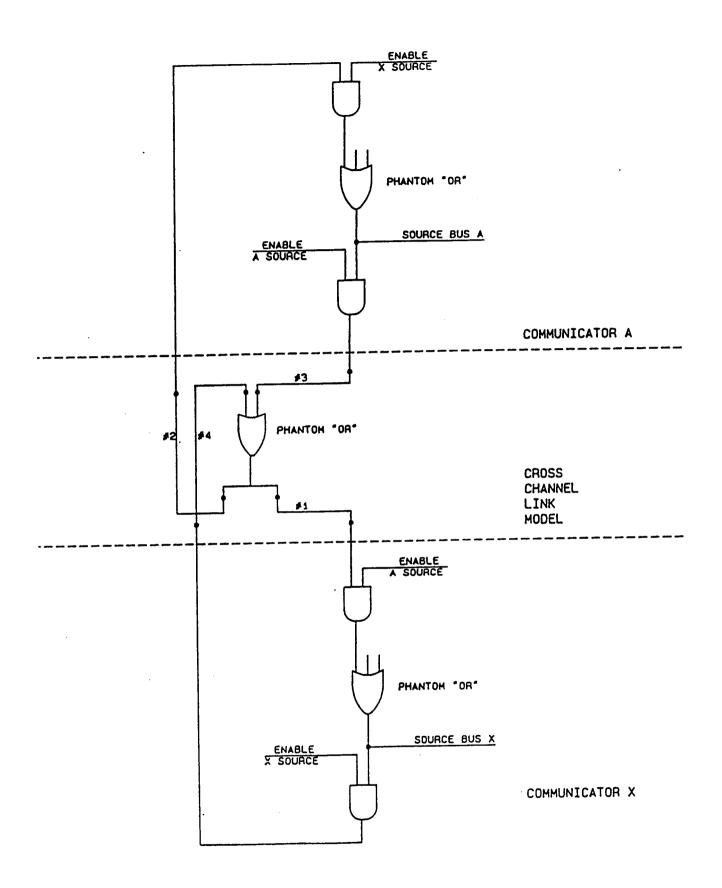

The cross channel links which distributes data from each communicator Source Bus to all other communicators' source busses is a bidirectional tri-state bus. The circuitry is diagrammed in figure 2.4. An adequate model for this is shown in figure 2.5. Since this model required a significant number of connections (384) and phantom gates (96) and since these particular connections had to be hand edited into the network, the simpler model (192 connections and 0 gates) shown in figure 2.6 was used. This decision was based on incomplete analysis which indicated that the model adequately captured the network behavior. While data is handled properly by this model, the effects of faults in the Source Select logic which supplies the enable signals for the cross channel links were not accurately modeled. Consequently, certain gate faults were not found by the C/I diagnostics. As discussed in a later chapter, these faults would have been found had the more complex and accurate model been used for the cross channel links.

The States Register file is implemented with two 74LS189  $4 \times 16$  bit RAM chips. Only 5 status bits, A error, B error, C error, D error and Quad error, are recorded in each of the 5 exchange types. Thus, only  $5 \times 5$  of the potential  $8 \times 16$  bits are used for the Status Register file. The Status Register was modeled with five, five-bit D-type flip-flop registers and with the address decoder and selection logic necessary to direct five bits of data to and from these registers.

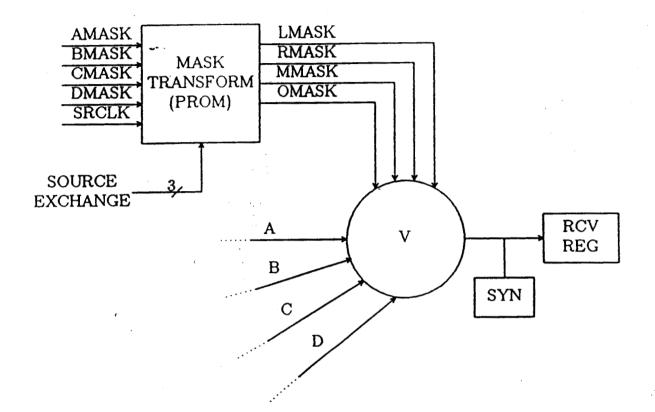

The Mask Transform block receives the Mask Register bits (Mask A, Mask B, Mask C, Mask D, and Source Lock), the two channel identification (ID) bits, and the three exchange type bits to determine which, if any, channel to block from the voter logic and to select the source of data to be routed to the Receive Register. This function is implemented with a  $2048 \times 8$ -bit registered programmable read only memory. To model this device directly required that a Diagnostic Emulator overhead feature be used. This feature assigns a block of memory outside normal device simulation which can be used to store the contents of the memory being modeled. Memory address and data bit connections are associated with and determined by designated nodes within the network being simulated. To access this memory, a change on a designated control line will stop normal simulation of the network and will invoke an action which uses the state of the designated address nodes to select a particular location in the assigned memory block and to impose the state of the bits in this memory location on the designated data bit nodes.

Since this operation is generally slower than gate simulation and since validation of the operation of this PROM was judged to be more difficult than validating an equivalent gate network for this case, a decision was made to model this block with a simple gate network at least until the rest of the C/I network could be validated.

The interstages consist of drivers, receivers, and D-type flip-flops. These devices were modeled using the Diagnostic Emulator gate and flip-flop primitives.

The Source Select, Current Status Update, Syndrome Or, Voter, and Voter Syndrome blocks are implemented using programmable logic arrays (PLA). A diagram of a typical PLA is shown in figure 2.7. The logic equations programmed for each function were modeled directly. Figure 2.8 illustrates one of these functions. The adequacy of *stuck-at* gate fault models for these devices is questionable since certain bridging faults between conductors carrying the input functions and a cell with the array cannot be accurately represented by such a simple model. A more elaborate gate model which would better represent these faults was beyond the scope of this effort.

The Source Select block shown in figure 2.3 uses exchange type bits and channel ID bits to control the cross channel links. The Voter and Voter Syndrome block

Figure 2.4. Actual Circuitry for Cross Channel Links

Figure 2.5. More Accurate Model Used for Cross Channel Links

.

performs the bit-for-bit voting of non-masked data copies and detects and reports errors for non-consistent data copies. These voter related functions are implemented in four PLA's with two data bits (dibits) processed by each PLA. The Syndrome Or block consolidates errors (syndromes) reported by each Voter Syndrome dibit. The Current Status combines these consolidated errors with the contents of the Status Register.

The final major block is the Control. This block provides the timed control signals to direct the operation of the Data Communicator. It is implemented using three  $2048 \times 8$ -bit registered programmable read only memory devices. Since these devices

are connected so that particular processor interface control signals, processor interface address bits, and certain of their own output bits are used to control their address inputs; a classical state machine with inputs, outputs, and internal states is implemented. This state machine is depicted in figure 2.9. The circuit is modeled using D flip-flops for the PROM register and the external memory feature of the Diagnostic Emulator. However, it was found that the contents of the PROM were highly redundant and that its size could be reduced to 512 words instead of 2048 words without losing any capability. Further reductions were possible but were not carried out. Figure 2.10 shows the state diagram for the the Write Xmit operation controlled by this state machine. Review of this design indicated that, as a result of the redundancy in the contents of the PROM, the state machine would require substantial additional testing to establish functionality. The redundancy likely resulted from the use of a high level design tool. This observation has implications regarding the use of high level design tools for fault tolerant systems.

Except for the Control block, four complete C/I's were modeled. Only two Control blocks were modeled. One Control block provided control signals for channels B, C, and D. The other provided control signals for channel A. The Channel A C/I was the only C/I module faulted in the experiment. In addition to the four C/I's, support logic which generated fault tolerant clock and processor clock had to be modeled. These signals were generated by a simple ring oscillator and a divide by counter. A ring counter was used to create a clock whose period in gate delays or event units is approximately equal to the actual processor clock frequency. The divide by counter used to generate the fault tolerant clock was set at 12 processor clock pulses instead of 40 as used in the FTP. This change reduced the required simulation time without losing essential information.

Every flip-flop in the C/I model has a pseudo-gate connected in line with its output so that the flip-flop output can be faulted. The addition of the pseudo-gate circumvented a Diagnostic Emulator constraint which does not allow flip-flop outputs to be directly faulted. The fault gate was automatically inserted into the netlist by the netlist translator software on each occurrence of a flip-flop. Pseudo-gates were inserted into the model for each external input to the C/I that went to a flip-flop. These inserted gates were used to satisfy a Diagnostic Emulator requirement that no external input be directly connected to a flip-flop. Finally, external output devices which had no internal connections were connected to sink gates. The sink gate

plasys.dv0

Figure 2.8. Voter Syndrome Quaderror Function

-16-

Figure 2.9. Communicator Control Sequencer

Figure 2.10. Write XMIT State Diagram

connection satisfied the restriction that all devices must have at least one internal connection. The output of each *sink* gate was in turn connected to one of its own inputs to meet this requirement.

### 3. Experiment Preparation

### **3.1.** Introduction[4] [5]

Most of the effort expended in the experiment was directed toward developing and validating the Data Communicator/Interstage (C/I) gate level model and the associated experiment support software. This experiment preparation process can be divided into several general areas of activity. These areas are

1. the development and testing of experiment support software,

- 2. the activities associated with learning to use the diagnostic emulator,

- 3. the development of a gate level model of the C/I,

- 4. the development of C/I input sequences that would test the C/I in accordance with the C.S. Draper Laboratories C/I diagnostic software description, and

- 5. the validation of the C/I model.

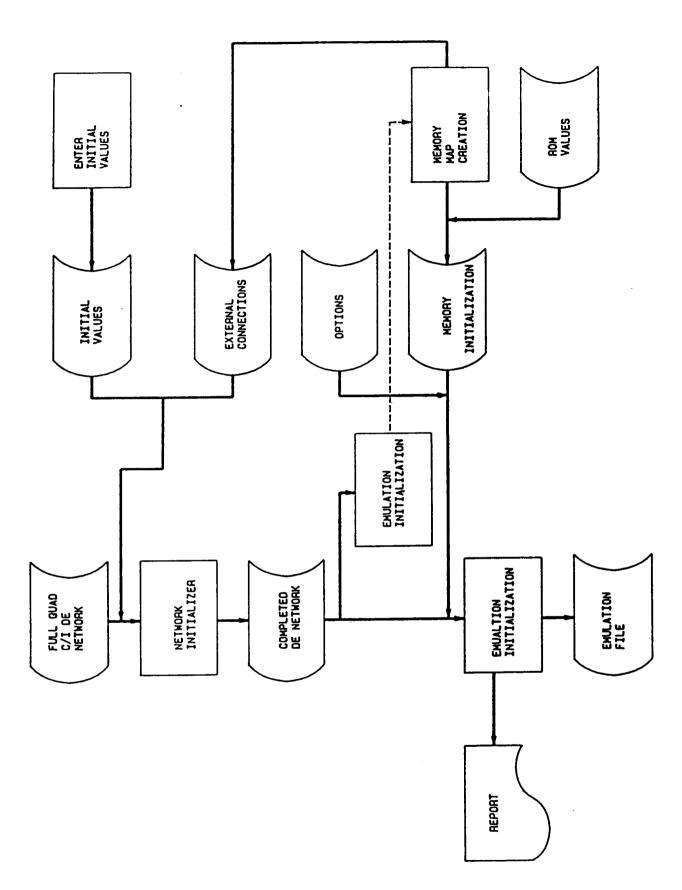

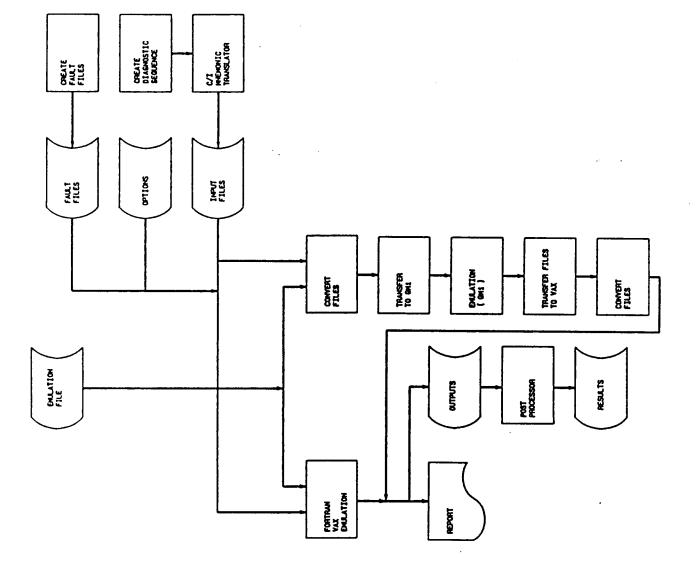

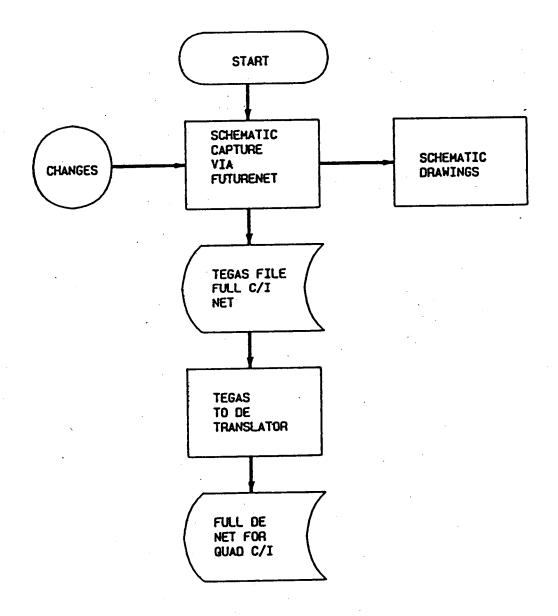

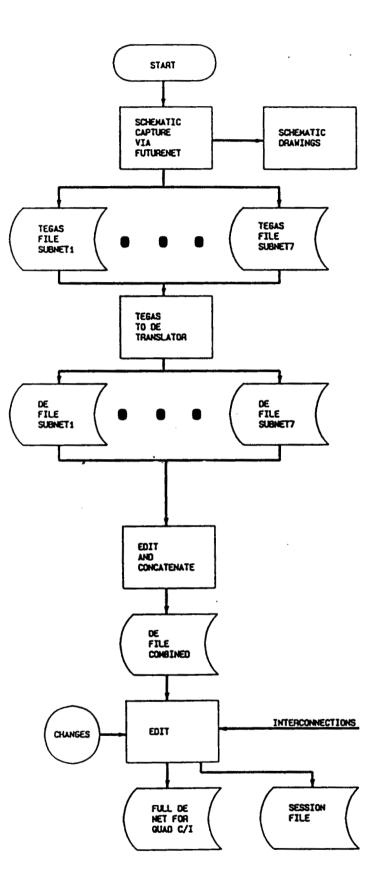

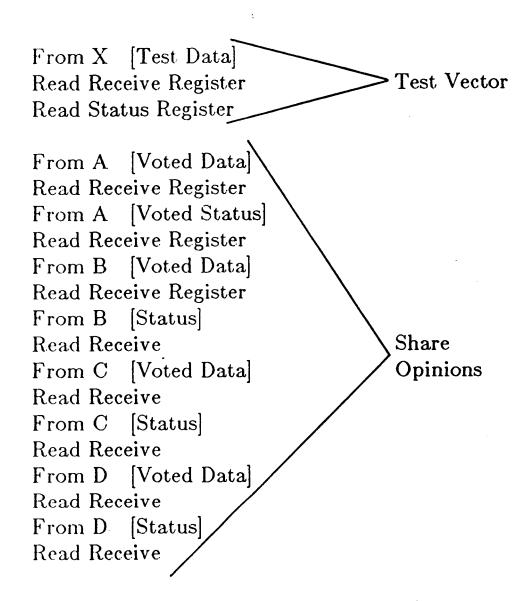

A brief description of the process used to set up and use a Diagnostic Emulation model will be given in this paragraph. A complete description of the Diagnostic Emulation portion of this process is given in the user manual.[4] Figure 3.1 diagrams the process. A description of the C/I logic network was created by using FUTURENET, a logic schematic capture computer-aided design tool. The resulting network description file was translated to a format suitable for input to the NASA-LaRC Diagnostic Emulation network initializer. This file, labeled QM-1 network, combined with files describing initial values for network nodes and files establishing external connections to the network such as network input and memory data connections, was supplied to a network initializer program. The resulting initialized network file, combined with an emulation options file and external memory initialization files, was processed by an emulation initialization program. The resulting emulation file, along with option files, fault description files, and external input data files, was used as input to the emulation. If the FORTRAN Diagnostic Emulation program was to be used, these files were used directly. If the QM-1 emulation was to be used, these files were converted and then transferred to the NANODATA QM-1 machine for execution. The output of the emulation process was used to examine the behavior of the model during the debug and validation phase and to provide the inputs for post-processing during the experiment phase.

The process described above is shown in more detail in figures 3.2 and 3.3. Note that in figure 3.2 there is a loop through the network initializer, emulation

Figure 3.1. System Flow Diagram

initialization, memory map creation, external connections, and back to the network initializer. This loop is necessary to establish the address references required to define the external connections file. This part of the process is done once, provided the network does not change. Also note that in figure 3.3 the difference between a VAX FORTRAN emulation and a NANODATA QM-1 emulation is detailed.

#### 3.2. Experiment Support Software

To use the existing Diagnostic Emulator to the extent required by the experiment, a number of new software utilities and tools had to be developed or procured. These items included the following:

- 1. a FUTURENET schematic capture computer-aided design tool;

- 2. a translator to convert FUTURENET netlists to a format suitable for the Diagnostic Emulation process;

- 3. an expanded set of primitive control features for the Diagnostic Emulator;

- 4. a set of programs to facilitate the preparation of Diagnostic Emulation options, connection, fault lists, input, memory, and initialization files;

- 5. a C/I mnemonic instruction translator to aid the preparation of C/I diagnostic test sequences; and

- 6. a program to analyze the outputs of the Diagnostic Emulation.

At the start of this project, gate level models of hardware to be emulated had to be created using a hardware description language. The large text file that resulted was then translated to a netlist suitable for Diagnostic Emulation. Creating, maintaining, changing, and verifying this large test file was a tedious, time-consuming, and errorprone process. The FUTURENET computer-aided schematic capture tools were purchased to facilitate the creation of the C/I emulation model or any other hardware models. It was felt that these tools would reduce the effort required for creating, maintaining, and verifying the C/I model. Since the schematic level is the natural level at which design engineers work with and document designs, it was felt that models created at this level would be less subject to errors.

A software program to convert FUTURENET/TEGAS netlists to the netlist format for the Diagnostic Emulator was written by RTI personnel. For the purposes of minimizing the resources dedicated to this conversion software, the devices used in the C/I schematic were restricted to those used by the Diagnostic Emulator. Adding the capability to accept more general devices, which in turn would be translated to Diagnostic Emulator devices, is not precluded by this restriction.

Figure 3.2. Network Initialization

.

-

-

To meet the needs of a fault insertion experiment, new control primitives were required for the Diagnostic Emulator. The new primitives added were as follows:

- 1. the capability to assert a stuck-at logic one or zero fault on any device output for a defined number of emulation steps,

- 2. the capability to provide external logic inputs from an input data file at designated emulation event numbers,

- 3. the capability to direct the output of designated logic nodes to an output file,

- 4. the capability to assert a fault on a bit in external memory arrays, and

- 5. the capability to define the length of an emulation run and to recycle the emulation using the next fault defined in a fault list.

The capability to provide each of these primitive control features had been planned but had not been implemented at the beginning of this effort. These capabilities were added to both the VAX FORTRAN emulation and the NANODATA QM-1 emulation. The implementation of these software features was done by NASA personnel.

A C/I mnemonic instruction translator was written to simplify the preparation of test sequences for the experiment. This translator provided the conversion of mnemonic representations for each C/I instruction into the proper bit pattern. In addition, *pseudo* instructions that allowed for defining iterative loops were provided. This latter capability simplified the creation of long test sequences consisting of iterative data values. Table 3.1 shows the mnemonics used.

| NAME | DEFINITION                                                                                                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| VECB | Pseudo op to define start of a new test vector                                                                                                    |

| VECE | Pseudo op to define end of a test vector                                                                                                          |

| LOOP | Pseudo op to set up a repetitive sequence of C/I operations.<br>Arguments specify the level of nesting and the iteration<br>increments and limits |

| END  | Pseudo op to define the end of a loop                                                                                                             |

| RDRR | Read receive register                                                                                                                             |

| WRCV | Write receive register; arguments are data for each C/I                                                                                           |

| WXMR | Write transmit register; arguments indicate source for each $C/I$ (A, B, C, D) and data for each                                                  |

| WMSR | Write mask register; arguments indicate mask to be written for each C/I                                                                           |

Table 3.1. C/I Instruction Mnemonics

Emulation outputs from the experiment were processed to determine the faults detected by each test vector.

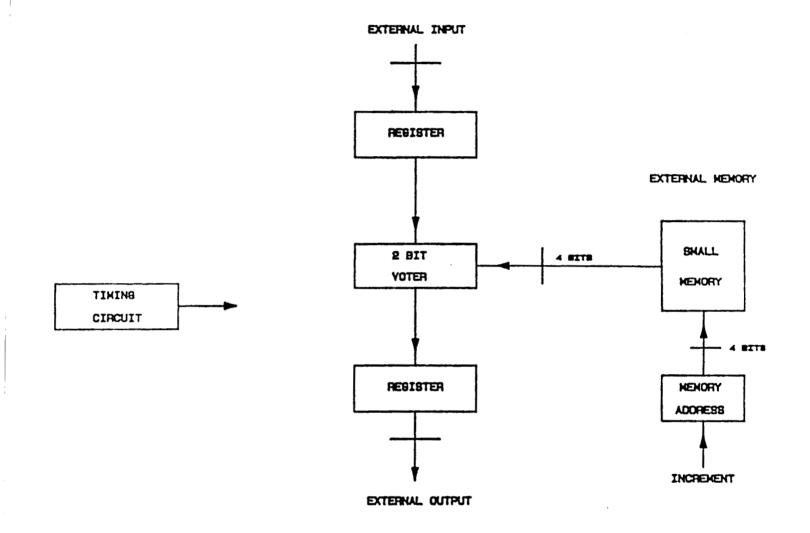

### 3.3. Learning Use of the Diagnostic Emulator and Testing of Software Items

A simple logic network was used as a vehicle to learn the use of the Diagnostic Emulator and to test the various new software items. In addition to simplicity, the network was designed to be similar to the C/I and to require the use of all Diagnostic Emulator primitives in the C/I model. These primitives include fault insertion, external inputs, external outputs, external memory arrays, and each type of logic device. Successful setup and emulation of this network was an essential first step in learning the use of the Diagnostic Emulator and for validating the new software development items.

A block diagram of this network is given in figure 3.4. The network was first analyzed on a simple IBM PC-based simulator, EZCAD. The EZCAD results were used as a basis for comparing Diagnostic Emulator results.

### 3.4. Development of a C/I Gate Level Model

Some of the circuit details of the C/I gate level model are discussed in section 2. The desired process for creating the model is shown in figure 3.5. In this process, a schematic of the entire quad C/I network would be captured using FUTURENET.

Figure 3.4. Block Diagram of Test Circuit

The resulting netlist would then be converted to a form suitable for the Diagnostic Emulator. Changes to the model would take place at the schematic entry level and would be followed by the translation process.

An attempt was made to carry out this process. However, the full quad C/I network was too large for certain of the FUTURENET support tools. Consequently, another less desirable process had to be employed. The actual process used is shown in figure 3.6. In this process, the full quad C/I was broken into smaller subnets. Each subnet was translated and these subnets were concatenated into a larger net. The interconnections between subnets were handled by editing these interconnections into the translated net file. While the number of interconnections was small relative to the total network, the editing process to produce these interconnections was prone to error. Further, this step made it difficult to return to the schematic level for model checking and for any model changes. This limitation of FUTURENET and the manner in which the model was created made it difficult to realize the full potential of computer-aided design capture. Unanticipated model network configuration control problems had to be solved, and checking of certain parts of the model was rendered much more difficult since it had to be done at the netlist level.

An indicator of the potential for difficulties is found in the network size information. The full quad C/I network consisted of more than 5000 nodes (devices) and 15,000 connections. About 20,000 lines of text, or more than 300 pages, were required to list the network.

This network is relatively small compared to most VLSI designs. The only effective way to deal with such designs is with effective CAD tools.

### 3.5. Diagnostic Test Sequences for the Data Communicator/Interstage[6] [7] [8] [9]

The C/I plays a critical role in FTP fault tolerance by ensuring that all good processors receive identical data values (source congruency), by masking errors, and by providing for FTP reconfiguration after faults are detected. An important part of FTP operation is the use of diagnostic test sequences for the C/I for both pre-mission and in-mission testing. These test sequences are used to uncover latent faults. This experiment was directed toward determining the effectiveness of proposed diagnostic test sequences.

A fault detection, isolation, and reconfiguration (FDIR) program is used in FTP. FDIR provides for hardware implemented fault detection and error reporting, software implemented fault isolation based on the analysis of error reports, software implemented reconfiguration by disabling failed channels, and software implemented self tests to uncover latent faults. The C/I is tested with self tests that operate within the FDIR function. FDIR tests the C/I with a frequently executed high priority limited scope test, called Presence, and a somewhat exhaustive low priority test sequence, which is executed with a much lower frequency.

## Figure 3.5. Network Model Preparation (Desired)

# Figure 3.6. Network Model Preparation (Actual)

The Presence test is a simple test that is executed at the beginning of a processing frame to determine the *presence* of each processing channel of the FTP. During this test, unique data values from each channel are exchanged via the C/I. Correct. exchange of a channel's unique values establishes presence.

The low priority C/I self tests of the FDIR assume that a certain class of C/I faults, such as hard errors in the data path, will be detected in the normal course of processing and/or by the Presence test. Those areas of the C/I logic not stimulated in the normal course of operation are the focus of the self tests. These areas include error detection, error reporting, fault masking, and reconfiguration logic.

The main components of the low priority C/I self tests are as follows:

1. the Voter PAL Test,

2. the Mask Transform Test,

3. the Voter Syndrome Or Test, and

4. the Current Status Update Test.

The C/I voter is implemented using programmable logic array chips. The voting and error detection logic is contained in the voter PAL chips. Two bits of a data byte from each FTP channel are voted within a single PAL package. Four voter PAL packages are required for each communicator. The inputs to these PAL chips include dibits from each channel and a mask bit for each channel, as shown in figure 3.7. The Voter PAL Test consists of sequencing through all combinations of inputs to each voter PAL chip for both the least and most significant byte of a data exchange. This exhaustive test is used because certain failure modes of a PAL can result in any input to the chip coupling to any PAL output. This is true even if the gates associated with a given output are not programmed to accept all input signals. The total number of test vectors required for this test are  $2^{16}$ .

The Mask Transform Test targets the channel mask or blocking logic (see figure 3.8). This logic provides the capability to exclude a channel from the voting process. This component of the self test requires 192 test vectors.

The Voter Syndrome Or Test targets the two PAL chips associated with combining the error outputs of the 4 voter PAL chips. The test is intended to test only those gates not previously tested by the Voter PAL Test. This test was not completely defined at the time of the fault injection experiment.

The Current Status Update Test is intended to uncover faults in the current status update PAL chips (see figure 3.9). In this test, all combinations of data exchange errors are stimulated by selection of appropriate test vectors. Stimulated errors are logged into the Status Registers. These test vectors are followed by test vectors that stimulate additional data exchange errors. The Status Register is then checked to determine if it is properly updated.

Figure 3.7. Communicator/Interstage Exchange Network

Tests For Each PROM Input:

|         | Test Number |   |   |   |   |   |  |

|---------|-------------|---|---|---|---|---|--|

| Channel | 1           | 2 | 3 | 4 | 5 | 6 |  |

| A       | A           | D | A | В | A | С |  |

| В       | В           | C | A | В | В | D |  |

| С       | В           | С | C | D | A | С |  |

| D       | A           | D | С | D | В | D |  |

(Number of Mask Transfer PROM Test Vectors) =  $6 \cdot 32 = 192$

Figure 3.9. Error Logging/Masking Network (One Network for each Processor)

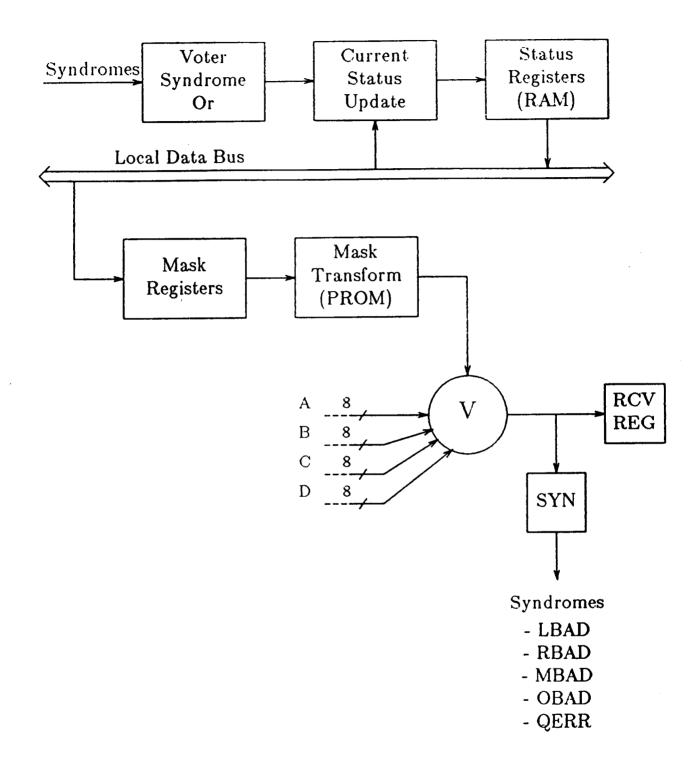

Figure 3.10 illustrates a typical sequence of C/I transactions associated with a single test vector. Three transactions are required to exchange data, read the results, and retrieve the associated error report. This does not include any special setup of the Mask Registers and Status Registers. Once exchange results and error reports are obtained, it is necessary for all channels to exchange this data. This allows all good channels to arrive at a consensus on the results of a test vector. A total of nine exchange and read transactions are required for each vector. Each exchange/read transaction pair requires about 10  $\mu$ sec to complete in real time.

Assuming that the C/I self test requires approximately  $2^{16}$  test vectors, and that the self test is constrained to use only five percent of the C/I throughput capacity, the C/I self test will require approximately two minutes to execute. This time sets a bound on the fault latency time for faults detectable via the C/I self tests.

Estimates of the time required to conduct a fault injection experiment using the Diagnostic Emulator are of interest. Consider an experiment that requires the injection of 2000 faults and requires that the C/I self test sequence (about  $2^{16}$  test vectors) be executed completely for each fault. Assume that the NANODATA QM-1 is used. Also assume that only the self test transactions must be executed, i.e., the C/I throughput is 100% dedicated to self test for the experiment. The QM-1 version of the Diagnostic Emulator will execute approximately 50,000:1 slower than real time for the C/I network. The total simulation time required would be approximately 19 years. If the VAX FORTRAN version was used at  $10^6$ :1 slower than real time, the simulation would require approximately 3.8 centuries!

The unacceptably long run times cited in the preceding paragraph provide motivation for restricting the extent of an experiment. If the simulation time requirements are reduced by a factor of about 1000, 200 QM-1 hours would be required. Such a simulation time requirement would be well within the feasible range.

In the planning stage of this experiment, the self test for the C/I used substantially fewer test vectors. The number of test vectors used by C.S. Draper Laboratories (CSDL) at that time would have resulted in reasonable simulation time requirements. The exhaustive test implemented by the new self tests greatly expanded the simulation time.

A reduction in simulation time by a factor of 9 can be obtained by recognizing that the exchanges required to share opinions in an actual FTP would not be required in an experiment. An additional factor of about 100 was needed and was obtained by reducing the number of test vectors.

Recall that the exhaustive testing addressed certain PAL failure modes. It was determined that these failure modes would not be reflected in a direct gate level model of the PAL logic. Consequently, the large set of test vectors could be reduced and not change the outcome of an experiment based on a gate level model. Further, it was decided to test the C/I voters only for the quadriplex and triplex configurations and only for one of the voter PAL chips.

9 Exchanges about 10  $\mu$ sec each

The tests prepared for the experiment are summarized in figures 3.11 and 3.12. Tests are characterized by the number of test vectors within a test, by the number of C/I transactions or instructions required for the test, and by the number of DE simulation steps required for the test. These tests include about 600 test vectors that are in the desired range. Appendix A gives detailed listings of these tests.

#### 3.6. Validation of the C/I Emulation Model

The purpose of the validation process was to establish, to the greatest extent possible, that the C/I emulation model accurately reflected the behavior of the C/I. Most of the funding for this emulation experiment was directed toward this effort. In general, the validation of a complex model would be difficult. For this experiment, several factors further complicated the validation process.

Ideally, the emulation model for a network would be created automatically from a design data base using well-established software programs, and the design verification data base of test vectors and results would be available for use. In this experiment, design information used to create the emulation model was in the form of a schematic drawing and a design description. Furthermore, access to the C/I designer was limited. To create the emulation model, the schematic was manually entered into a computer using a CAD schematic capture tool. The devices used in the design were replaced with Diagnostic Emulation gate primitives prior to schematic capture. The translation of the netlist for the captured schematic to a form suitable for Diagnostic Emulation was accomplished using a software program developed for this experiment. As described in section 3.5, certain of the network model interconnections had to be established by editing the translated netlist text files. Additional experiment software, described in section 3.3, was developed to support the experiment. This software included modifications to the Diagnostic Emulator.

When discrepancies were found during testing/debugging of the model, errors in the design capture, errors in the new software, errors in the changes to the Diagnostic Emulator, errors in the use of the Diagnostic Emulator, and errors related to modeling issues were all candidates for the source of the problem. Engineering analysis based on limited design documentation was required to devise tests for the model, to determine the correctness of the responses, and to devise additional tests for isolating the source of detected errors.

The additional complications of the validation process for the C/I can be attributed to the following:

- 1. the status of the Diagnostic Emulation facilities in AIRLAB (i.e., changes, limitations, and documentation) at the start of the experiment,

- 2. the design capture process that was employed,

- 3. the development of software to facilitate model development, and

Voter Tests Tested a single voter PAL chip (2 bits) in the quad and triplex configurations. Used both upper and lower bytes to give two test vectors per vote.

Mask Transform Tests Tested mask transform *logic* for quad and duplex configurations

Current Status Update Test Tested the current status update PAL

Presence Test Equivalent to CSDL "Presence"

Basic Test RTI test which tested a range of C/I functions beyond "Presence"

### Figure 3.11. Tests Used for Experiment

| TEST                     | · · · · · · · · · · · · · · · · · · · | NBR     | NBR    | SIM   |

|--------------------------|---------------------------------------|---------|--------|-------|

| NAME                     | ABBREV                                | VECTORS | INSTRS | STEPS |

| Presence                 | presence                              | 10      | 62     | 8400  |

| Current Status<br>Update | cstupd                                | 10      | 64     | 11900 |

| Basic                    | basic                                 | 16      | 112    | 11900 |

| Mask Transform<br>Quad   | msktrnq                               | 12      | 84     | 9900  |

| Mask Transform<br>XAXB   | msktrn <b>xaxb</b>                    | 24      | 160    | 19200 |

| Mask Transform<br>XCXD   | msktrnxcxd                            | 24      | 160    | 19200 |

| Voter Test<br>Quad1      | vb0lquad1                             | 128     | 772    | 98000 |

| Voter Test<br>Quad2      | vb01quad2                             | 128     | 772    | 98000 |

| Voter Test<br>B01 3XA    | vb013xa                               | 64      | 388    | 48700 |

| Voter Test<br>B01 3XB    | vb013xb                               | 64      | 388    | 48700 |

| Voter Test<br>B01 3XC    | vb013xc                               | 64      | 388    | 48700 |

| Voter Test<br>B01 3XD    | vb013xd                               | 64      | 388    | 48700 |

Figure 3.12. Diagnostic Sequences

4. the absence of a design verification data base of test vectors and responses.

The effort to validate a model could have been reduced considerably by the appropriate use of well-established CAD tools that were integrated into the hardware design data base. The uncertainty as to the possible sources of model discrepancies encountered in this first AIRLAB Diagnostic Emulation experiment would be reduced for additional experiments. Integration of the design data base into the Diagnostic Emulation facilities would eliminate problems associated with design recapture. Finally, integration of the design data base would permit the use of the design verification test vectors and responses and would reduce the need for the validator/experimenter to fully understand the operation of the network modeled and to analyze the detailed responses of the network.

The validation process for the C/I model relied to some extent on the software testing afforded by the emulation of the simple network described in section 3.3. The approach to verifying the C/I model was to verify the C/I microsequencer logic and to then add additional C/I functions. The C/I microsequencer model was verified using a simple IBM PC-based simulator, EZCAD. This simulator provided easy-to-use graphical *logic analyzer*-type outputs. The microsequencer was verified against its documented state transition diagram for each operation type. A microsequencer model was prepared for the VAX FORTRAN Diagnostic Emulator and was verified for each state transition and output. This provided a source of correct control signals for subsequent testing of the C/I model.

The full C/I model that incorporated the verified microsequencer model was prepared for the VAX FORTRAN Diagnostic Emulator. This model was tested for each operation type with various data inputs. Numerous design recapture errors were found and corrected. Next, sequences of operations with various data values were emulated. Errors were found and corrected. Finally, all the diagnostic test sequences, except for the non-voter tests, were used as the emulator inputs. The emulator output for each test sequence was verified for correctness.

The QM-1 version of the Diagnostic Emulation was not available when the model verification was complete. Consequently, the experiment was started using the VAX FORTRAN version. Once the QM-1 version became available, a QM-1 C/I model was prepared. This model was verified against extensive emulation results from the VAX FORTRAN version for both good circuit and faulted circuit conditions. Non-faulted C/I outputs for each diagnostic test sequence are included in appendix B.

Errors stemming from each of the possible sources enumerated above were found during the validation process. However, most errors, including the most difficult errors to isolate, were traced to the manual editing of interconnections into the large netlist text file.

As noted earlier, the validation part of this experiment required the most effort. Without appropriate CAD tools integrated into the design data base, it would be difficult to justify the cost of experiments using other designs of similar complexity. This experiment involved a network of relatively modest complexity (5000 gates) relative to modern VLSI (50,000 to 100,000 gates). Standards for verifying the accuracy of network models are much higher for highly reliable fault tolerant systems. The only costeffective way to manage the complexity of modern VLSI designs for a highly fault tolerant system will be with the use of well-established validated CAD tools that are integrated into a common design data base.

#### 4. Diagnostic Emulation Experiment Description and Results

#### 4.1. General Plan

The general plan for this experiment is to do the following:

- 1. emulate at the gate level the Charles Stark Draper Laboratories (CSDL) Fault Tolerant Processor's Communicator/Interstage (C/I) hardware using the AIRLAB Diagnostic Emulator facilities,

- 2. insert single faults into the gate level model,

- 3. for each inserted fault, use the CSDL diagnostic self test sequence for the C/I as inputs for the emulation model,

- 4. determine if observable errors are produced in the emulation model output for each fault inserted, and

- 5. evaluate the results of the experiment.

Figure 4.1 diagrams the emulation setup. Test vectors from the C/I diagnostic self test sequence were used as input to a gate level model of the C/I network. Faults that model *stuck-at-one* and *stuck-at-zero* gate output failures were inserted into the gate level model. Each fault was inserted for a complete pass through the diagnostic self test sequence, only one fault was present in the network during any pass through the self test sequence, and faults were only inserted into the channel A portion of the C/I. For each fault and test vector, outputs from the C/I model and both data and error reports were compared against the outputs produced by a fault-free C/I model. If the outputs differed, the fault was designated as detectable for the test vector in question.

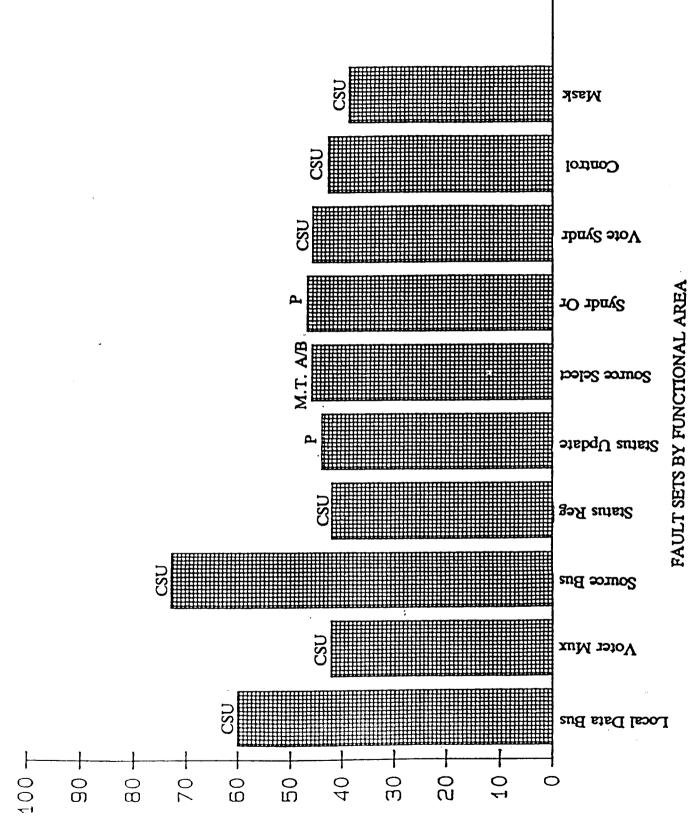

Figure 4.2 diagrams the output space for this experiment. Originally, 600 test vectors were planned (see section 3.5), but only 328 were used. These test vectors were grouped into tests associated with a particular purpose or functional area within the C/I. These tests are listed in figure 4.3 along with their associated parameters. Faults were grouped into sets associated with a particular functional area. Figure 4.4 lists the fault groupings, and figure 4.5 diagrams the functional areas associated with these fault sets. Note that within Voter and Voter Syndrome fault sets, devices associated with 2 of the 8 bits were faulted. Excluding these faults reduced the experiment

Figure 4.1. Communicator/Interstage Model

-42-

| TEST                     |            | NBR     | NBR    | SIM   |

|--------------------------|------------|---------|--------|-------|

| NAME                     | ABBREV     | VECTORS | INSTRS | STEPS |

| Presence                 | presence   | 10      | 62     | 8400  |

| Current Status<br>Update | cstupd     | 10      | 64     | 11900 |

| Basic                    | basic      | 16      | 112    | 11900 |

| Mask Transform<br>QUAD   | msktrnq    | 12      | 84     | 9900  |

| Mask Transform<br>XAXB   | msktrnxaxb | 24      | 160    | 19200 |

| Mask Transform<br>XCXD   | msktrnxcxd | 24      | 160    | 19200 |

| Voter Test<br>Quad1      | vb0lquad1  | 128     | 772    | 98000 |

| Voter Test<br>Quad2      | vb01quad2  | 128     | 772    | 98000 |

| Voter Test<br>B01 3XA    | vb013xa    | 64      | 388    | 48700 |

| Voter Test<br>B01 3XB    | vb013xb    | 64      | 388    | 48700 |

| Voter Test<br>B01 3XC    | vb013xc    | 64      | 388    | 48700 |

| Voter Test<br>B01 3XD    | vb013xd    | 64      | 388    | 48700 |

Figure 4.3. Diagnostic Sequences

duration. Since the network topology for the remaining 6 bits was the same as for the 2 bits where faults were injected, the results for the 2 bits could be used to determine the results for the remaining 6 bits. This grouping of faults and test vectors was found to be a useful way to interpret experiment results and to draw conclusions regarding the effectiveness of particular test vectors. Figure 4.6 shows a typical output from the emulation. The single number on a line is the simulation time step and the four numbers on a line are the outputs from the four channels of the C/I model. Figure 4.7 is a typical post-processing output. For each vector in a self test sequence and for each fault in a fault set, the faulty circuit emulation output values are compared to good circuit emulation output values. If the outputs differ, the fault is considered to be detected by that test vector. The "1" entry in figure 4.7 indicates that the fault was detected. The score (the number of faults found) for each vector is given at the bottom of the fault list, and the number of vectors in the designated test detecting a particular fault is given in the right hand column. The first run and additional runs within the fault list are for fault-free conditions. Emulator outputs from the first run were used as the reference for subsequent faulted outputs. Emulation runs required large amounts of computer execution time and complex setup procedures. The opportunity for errors was of concern. Consequently, additional fault-free runs were included to help ensure consistent results. This precaution did, in fact, result in finding several problems during the experiment.

#### 4.2. The Experiment

Originally, the NANODATA QM-1 version of the Diagnostic Emulator was to be used for this experiment and the VAX FORTRAN version was to be used for validating the model. Since the changes to the QM-1 version were not completed when the model validation was complete, the experiment was started using the AIRLAB VAX computers. After the QM-1 version became available, it was used to complete the experiment. Figure 4.8 summarizes the use of AIRLAB computing resources during the experiment. It should also be noted that more than 300K blocks of disk storage were in use at various points during the experiment. Figure 4.9 details some interesting experiment-related numbers. One interesting observation is that the total amount of real time operation of the C/I that was simulated was only two seconds. Another interesting number is the average stack size (12 devices) for the emulation algorithm. This number indicates the average number of devices whose outputs change during a given simulation step. It is indicative of the potential savings in processing time that could be realized by an event-driven simulation versus a simulation that must compute all device outputs for each event time. The ratio of average stack size to total network size (12;5000) is substantial and represents a considerable reduction in device computations. However, it is also indicative of a design that has low device activity. A ratio of 1:20 should be more typical. From the numbers in figure 4.9, it is possible to estimate the average device computations per second required for an equivalent non-eventdriven simulation of this network. Figure 4.10 summarizes these calculations. It should be noted that for fault simulation, a time resolution equivalent to 1/2 or 1 clock cycle is often sufficient. It was found that the QM-1 version operated about 60K:1 slower than real time for this network, and that the VAX 11/780 was about  $1.2 \times 10^{\circ}$

| Group                    | Number of Faults |

|--------------------------|------------------|

| Local Data Bus           | 128              |

| Source Bus               | 370              |

| Status Register          | 160              |

| Current Status Update    | 106              |

| Source Select            | 120              |

| Syndrome Or              | 116              |

| Voter/MUX/Result Bus     | 264              |

| Voter Syndrome           | 132              |

| Mask Transform           | 62               |

| Microsequencer & Control | 216              |

| Fan-out                  |                  |

|                          | 1674             |

Figure 4.4. Fault Sets by Functional Group

.

| TEST SEQUENCE                                           |        | NXAXB          | GOOI   | O CIRCUIT 🛶 | - FAULT CONDITION |

|---------------------------------------------------------|--------|----------------|--------|-------------|-------------------|

|                                                         | 0      | 12 0           | 0      | 0           |                   |

|                                                         | 0      | 100 0          | 0      | 0           |                   |

|                                                         | 0      | 244<br>0       | 0      | 0           |                   |

|                                                         | 0      | 388<br>0       | 0      | 0           |                   |

|                                                         | 0      | 532<br>0       | 0      | 0           |                   |

|                                                         | 0      | 658<br>0       | 0      | 0           |                   |

| These numbers represent simulation time step for        | 0      | 766 0          | 0      | 0           |                   |

| which the following C/I                                 |        | -1270          |        | -           |                   |

| oupus were sampled.                                     | X      | 1396           | 146063 |             |                   |

|                                                         | 11     | 11<br>1522     | 11     | 11          |                   |

| These data are outputs <b>*</b><br>from the four C/I's. | 0      | 0<br>2026      | 0      | 0           |                   |

|                                                         | 34307  | 34307<br>2152  | 34307  | 34307       |                   |

|                                                         | 11     | 11<br>2278     | 11     | 11          |                   |

|                                                         | 0      | 0<br>2782      | 0      | Ο.          |                   |

|                                                         | 143470 |                | 143470 | 143470      |                   |

|                                                         | 3      | 3<br>3034      | 3      | 3           |                   |

|                                                         | 0      | 0              | 0      | 0           |                   |

|                                                         | 31714  | 3538<br>31714  | 31714  | 31714       |                   |

|                                                         | 5      | 3664 5         | 5      | 5           |                   |

|                                                         | 0      | 3790<br>0      | 0      | 0           |                   |

|                                                         | 107760 |                | 107760 | 107760      |                   |

|                                                         | 3      | 4420<br>3      | 3      | 3           |                   |

|                                                         | 0      | 4546<br>0      | 0      | 0           |                   |

|                                                         | 107760 | 5050<br>107760 | 107760 | 107760      |                   |

|                                                         |        | 5176<br>5      | . 5    | 5           |                   |

|                                                         |        | 5302 0         | 0      | 0           |                   |

|                                                         |        | 5410 0         | 0      | 0           |                   |

|                                                         |        | 5914           |        | -           |                   |

|                                                         |        | 6040           | 34307  |             |                   |

|                                                         | 11     | 11<br>6166     | 11     | 11          |                   |

|                                                         |        |                |        |             |                   |

\_

# Figure 4.6. Typical Good Circuit Output

Fault file: CSTUP1FAULT.DAT Vector file: CSTUPD.VEC Data file: CSTUP10UT.DAT

2 = no fault3 = stuck at "0"

4 =stuck at "1"

· ..... Onaisions

| Run number<br>Device                        | *<br>Fault<br>Condition                                                      |                 | tor nu          | mber<br>3 | -      | 5                   |             |             |             |        |        |                                                     |

|---------------------------------------------|------------------------------------------------------------------------------|-----------------|-----------------|-----------|--------|---------------------|-------------|-------------|-------------|--------|--------|-----------------------------------------------------|

| 2, APA1G01<br>3, APA1G01                    | 4<br>3<br>4                                                                  | 1<br>  1<br>  1 | 1<br>  1<br>  1 | 1<br>1    | 1      | 1<br>1<br>1         | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 | 1      | 1<br>1 | 10<br>10<br>6                                       |

| 4, APA1G02<br>5, APA1G02<br>6, APA1G03      | , 3<br>, 4                                                                   | 1               | 1               | 1<br>1    | 1<br>1 | 1                   | 1           | 1           | 1           | 1      | 1      | 4<br>6<br>4<br>6                                    |

| 7, APA1G03<br>8, APA1G04<br>9, APA1G04      | , 3<br>, 4<br>, 3                                                            | 1               | 1               | i         | 1      | 1                   | 1           | 1           | 1           | 1      | 1      | 646                                                 |

| 10, APA1G05<br>11, APA1G05<br>12, APA1G06   | , 4<br>, 3<br>, 4                                                            | 1               |                 | 1         | 1<br>1 | 1<br>1              | 1<br>1      | 1<br>1      | 1<br>1      | 1      | 1      | 4                                                   |

| 13, APA1G06<br>14, APA1G07                  | 34343434343434<br>343434343434<br>34343434343                                | 1               | 1               | 1         | 1      | 1                   | 1           | 1           | 1           | 1      | 1      | 2<br>8<br>1                                         |

| 15, APA1G07<br>16, APA1G08<br>17, APA1G08   | , 4<br>, 3                                                                   | 1               | 1               | 1         | 1<br>1 | 1                   | 1           | 1<br>1      | 1           | 1      |        | 6<br>2<br>6                                         |

| 18, APA1G09<br>19, APA1G09<br>20, APA1G10   | 3                                                                            | 1               | 1               |           | T      | 1<br>1              | 1           | 1           | 1           | 1<br>1 |        | 464828162626262                                     |

| 21, APA1G10<br>22, APA1G11<br>23, APA1G11   | , 3<br>, 4<br>, 3                                                            | 1               |                 | 1<br>1    | 1      | 1                   | 1           | 1           | 1           | 1      |        | 6<br>2<br>0                                         |

| 24, APA1G12<br>25, APA1G12<br>26, APA1G13   | 4<br>3<br>4<br>3                                                             | 1               | 1               | 1<br>1    | 1<br>1 | 1<br>1              | 1<br>1      | 1<br>1      | 1<br>1      | 1      | 1      | 10<br>8<br>0                                        |

| 27, APA1G13<br>28, APA1G14<br>29, APA1G14   | , 3<br>, 4<br>, 3                                                            | 1               | 1               | 1         | 1      | 1                   | 1           | 1           | 1           | 1      | 1      | 0<br>10                                             |

| 30, APA1G15<br>31, APA1G15                  | , 4<br>, 3<br>, 4<br>, 3<br>, 4<br>, 3                                       | l               | 1               | 1         | 1      | 1 <sup>.</sup><br>1 | 1           | 1           | 1           |        |        | 8<br>0<br>3                                         |

| 32, APA1G16<br>33, APA1G16<br>34, APA1G17   | . 4                                                                          | 1               | 1               | 1<br>1    | 1<br>1 | î<br>1              | 1<br>1      | 1           | 1<br>1      | 1      | 1      | 10<br>6<br>4                                        |

| 35, APA1G17<br>36, APA1G18<br>37, APA1G18   | , 3<br>, 4<br>, 3                                                            |                 | 1               | 1         | 1      | 1                   | 1           | 1           | 1           |        | _      | 4<br>6<br>0<br>6                                    |

| 38, APA1G19<br>39, APA1G19<br>40, APA1G20   | 4<br>3<br>4                                                                  |                 |                 | 1         | 1<br>1 | 1                   |             | 1           | 1           |        |        | 06                                                  |

| 41, APA1G20<br>42,                          |                                                                              |                 |                 | 1         | 1      | 1                   | 1           | ı ı         | 1           |        |        | 0<br>0<br>6                                         |

| 43, APA1G21<br>44, APA1G21<br>45, APA1G22   | , 3<br>, 4                                                                   | 1               |                 | 1         | 1      | 1                   | 1           | 1           | 1           | 1      | 1      | 2<br>6<br>4                                         |

| 46, APA1G22<br>47, AFPPA1F(<br>48, AFPPA1F( | , 3<br>)0, 4<br>)0, 3                                                        |                 | 1               | 1         | 1      | 1                   | 1           | 1           | 1           | 1      | 1      | 0<br>6<br>2<br>6<br>4<br>6<br>4<br>6<br>4<br>6<br>0 |

| 49, APA1G23<br>50, APA1G23<br>51,           | 3<br>2<br>4<br>3<br>4<br>3<br>0<br>0<br>4<br>0<br>0<br>3<br>0<br>2<br>0<br>2 | 1               | 1               | 1         | 1      | 1                   | 1           | 1           | 1           |        | 1      | 60                                                  |

|                                             |                                                                              | 22              | 20              | 26        | 24     | 26                  | 24          | 26          | 24          | 20     | 14     | 1                                                   |

## Figure 4.7. Typical Post-Processing Output

| Test                     | VAX 11/750 | VAX 11/780 | QM-1     |

|--------------------------|------------|------------|----------|

| Presence                 |            | 34 hrs.    |          |

| Basic                    | 84 hrs.    |            |          |

| Current Status<br>Update |            | 38 hrs.    |          |

| Mask Transform<br>XAXB   |            | 65 hrs.    |          |

| Mask Transform<br>Quad   | 72 hrs.    |            |          |

| Voter XA                 |            |            | 6.6 hrs. |

| Voter XB                 |            |            | 6.6 hrs. |

| Voter XC                 | 244 hrs.   |            |          |

| Voter XD                 |            | 122 hrs.   |          |

|                          | 400 hrs.   | 259 hrs.   | 13.2 hrs |

### Figure 4.8. Emulation CPU Time\*

\*Does not include post-processing

3

. •

| Network size                                     | >5000 devices<br>>15000 interconnections |

|--------------------------------------------------|------------------------------------------|

| Simulation resolution                            | 1 gate delay – 5ns                       |

| Gate delays per clock                            | 18 — 120 ns                              |

| Clocks/Fault tolerant clock                      | 12*                                      |

| Average stack size of<br>Event-driven simulation | 12 devices                               |

| Maximum stack size of<br>Event-driven simulation | $\sim$ 500 devices                       |

| Total faults                                     | 1670                                     |

| Total C/I transactions cycles/fault              | 2034                                     |

| Transaction cycles in experiment                 | $\sim 3 \times 10^{6}$                   |

| Simulation steps                                 | $\sim 3.6 \ge 10^8$                      |

| Total real time                                  | $\sim 2$ seconds                         |

\*Actual fault tolerant clock has 40 processor clock periods. The simulation was scaled to 12 to reduce run time.

Figure 4.9. Some Diagnostic Emulation Experiment Numbers

| Processor  | Gate Events/Sec  | Real Time Ratio               |

|------------|------------------|-------------------------------|

| VAX 11/750 | $1 \times 10^3$  | $2.4 \times 10^6$ : 1 slow    |

| VAX 11/780 | $2 \times 10^3$  | $1.2 \times 10^6$ : 1 slow    |

| QM-1       | $37 \times 10^3$ | 60 x 10 <sup>3</sup> : 1 slow |

- Establishing equivalence to a non-event-driven simulation is difficult

- If equivalent time resolution is required for the nonevent-driven simulation, the comparable speeds are

| VAX 11/750 | 500k Gates/Sec                 |

|------------|--------------------------------|

| VAX 11/780 | 1 x 10 <sup>6</sup> Gates/Sec  |

| QM-1       | 20 x 10 <sup>6</sup> Gates/Sec |

• If 1/2 clock period time resolution is required, then the comparable speeds are

| VAX 11/750 | 50k Gates/Sec                 |

|------------|-------------------------------|

| VAX 11/780 | 100k Gates/Sec                |

| QM-1       | 2 x 10 <sup>6</sup> Gates/Sec |

Figure 4.10. Summary of Diagnostic Emulation Speed

slower than real time.

#### 4.3. Analysis of Experiment Results

The experiment data presented in this section are not adjusted or modified to account for certain modeling problems identified after the experiment was complete. These problems will be discussed in a later section. Primarily, results are organized by diagnostic test and fault set. For each self test/fault set pair, the percentage of faults detected relative to the number of faults injected within the fault set are presented. Test vectors with the best and worst scores for each test/fault set pair are identified. The relative and combined performance results of the self tests are presented. Finally, the percentage of faults found by the best vector within a test relative to the number of faults detected by the test are examined.

Before reviewing these results, it should be noted that conclusions and observations are subject to the following:

- 1. There are limitations due to the adequacy of a gate level fault model for the C/I implementation technology;

- 2. Faults were only injected in a single emulated C/I;

- 3. The number of faults within a fault set varies;

- 4. Self tests reflect RTI's understanding of the CDSL self test description;

- 5. Faults were injected in devices associated with two of the eight voter bits.