الله https://ntrs.nasa.gov/search.jsp?R=19880013218 2020-03-20T06:16:12+00:00Z (۲) المراجع الم

GRANT

Grant Number NAG8-093 /N-62-22

141226 137P.

# A DIRECT-EXECUTION PARALLEL ARCHITECTURE FOR THE ADVANCED CONTINUOUS SIMULATION LANGUAGE (ACSL)

(NASA-CR-182809) A DIRECT-EXECUTION PARALLEL ARCHITECTURE FOR THE ADVANCED CONTINUOUS SIMULATION LANGUAGE (ACSL) (Alabama Univ.) 137 p CSCL 09B N88-22602

Unclas G3/62 0141226 by

Chester C. Carroll Cudworth Professor of Computer Architecture Department of Electrical Engineering College of Engineering The University of Alabama Tuscaloosa, Alabama

and

Jeffrey E. Owen Graduate Research Assistant

## **Prepared for**

**National Aeronautics and Space Administration**

Bureau of Engineering Research The University of Alabama May 1988

BER Report No. 424-17

The University of Alabama College of Engineering Bureau of Engineering Research P.O. Box 1968 University, Alabama 35486 Telephone: (205) 348-1591

# THE UNIVERSITY OF ALABAMA COLLEGE OF ENGINEERING

The College of Engineering at The University of Alabama has an undergraduate enrollment of more than 2,300 students and a graduate enrollment exceeding 180. There are approximately 100 faculty members, a significant number of whom conduct research in addition to teaching.

Research is an integral part of the educational program, and research interests of the faculty parallel academic specialities. A wide variety of projects are included in the overall research effort of the College, and these projects form a solid base for the graduate program which offers fourteen different master's and five different doctor of philosophy degrees.

Other organizations on the University campus that contribute to particular research needs of the College of Engineering are the Charles L. Seebeck Computer Center, Geological Survey of Alabama, Marine Environmental Sciences Consortium, Mineral Resources Institute—State Mine Experiment Station, Mineral Resources Research Institute, Natural Resources Center, School of Mines and Energy Development, Tuscaloosa Metallurgy Research Center of the U.S. Bureau of Mines, and the Research Grants Committee.

This University community provides opportunities for interdisciplinary work in pursuit of the basic goals of teaching, research, and public service.

#### BUREAU OF ENGINEERING RESEARCH

The Bureau of Engineering Research (BER) is an integral part of the College of Engineering of The University of Alabama. The primary functions of the BER include: 1) identifying sources of funds and other outside support bases to encourage and promote the research and educational activities within the College of Engineering; 2) organizing and promoting the research interests and accomplishments of the engineering faculty and students; 3) assisting in the preparation, coordination, and execution of proposals, including research, equipment, and instructional proposals; 4) providing engineering faculty, students, and staff with services such as graphics and audiovisual support and typing and editing of proposals and scholarly works; 5) promoting faculty and staff development through travel and seed project support, incentive stipends, and publicity related to engineering faculty, students, and programs; 6) developing innovative methods by which the College of Engineering can increase its effectiveness in providing high quality educational opportunities for those with whom it has contact; and 7) providing a source of timely and accurate data that reflect the variety and depth of contributions made by the faculty, students, and staff of the College of Engineering to the overall success of the University in meeting its mission.

Through these activities, the BER serves as a unit dedicated to assisting the College of Engineering faculty by providing significant and quality service activities.

Grant Number NAG8-093

## A DIRECT-EXECUTION PARALLEL ARCHITECTURE FOR THE ADVANCED CONTINUOUS SIMULATION LANGUAGE (ACSL)

by

## Chester C. Carroll Cudworth Professor of Computer Architecture

and

Jeffrey E. Owen Graduate Research Assistant

## Prepared for

The National Aeronautics and Space Administration

Bureau of Engineering Research The University of Alabama May 1988

BER Report No. 424-17

# LIST OF ABBREVIATIONS

- ACSL Advanced Continuous Simulation Language

- AMD Advanced Micro Devices

- CISC Complex Instruction Set Computer

- CPU Central Processing Unit

- EPROM Erasable Programmable Read Only Memory

- FPU Floating Point Unit

- HLL High Level Language

- I/O Input/Output

- MIPS Million Instructions Per Second

- PE Processing Element

- RAM Random Access Memory

- RISC Reduced Instruction Set Computer

- ROM Read Only Memory

- TI Texas Instruments

ii

# TABLE OF CONTENTS

| LIST OF ABBREVIATIONS                                 | ••• | ii  |

|-------------------------------------------------------|-----|-----|

| LIST OF TABLES                                        | ••• | v   |

| LIST OF FIGURES                                       | • • | vi  |

| ABSTRACT                                              | ••  | vii |

| Chapter                                               |     |     |

| 1. INTRODUCTION                                       | ••• | 1   |

| The Advanced Continuous Simulation language, ACSL     |     | 2   |

| A Direct-Execution Architecture                       |     | 2   |

| Parallel Processing                                   |     | 4   |

| How to Improve the Current ACSL Computer Design       |     | 5   |

| now co improvo ono ourrond nord comprose per-Bar a se |     |     |

| 2. PARALLEL PROCESSING DESIGN CONSIDERATIONS          | ••• | 7   |

| Rive Crained on Course-Crained Architecture           |     | 7   |

| Fine-Grained or Course-Grained Architecture           |     | 8   |

| Shared Memory or Private Memory                       |     |     |

| Interconnection Network                               | ••• | 9   |

| 3. REAL-TIME INSTRUCTION EXECUTION WITH ACSL          |     | 13  |

| Parallelism on the Construct Level                    |     | 14  |

|                                                       |     | 14  |

| Parallelism on the Program Level                      |     |     |

| Allocater Requirements                                |     | 19  |

| Resource and Construct Allocation                     | • • | 19  |

| Expression Reduction and Factoring                    |     | 20  |

| Interprocessor Communication Scheduling               |     | 20  |

| Real-Time Data Transfer                               |     | 21  |

| Program Execution with Direct-Execution Architectures |     | 22  |

| Program Execution with Direct-Execution Architectures | ••• | ~~  |

| 4. PROCESSING ELEMENT CONFIGURATION                   | ••• | 24  |

| Execution Flow in the Processing Element              |     | 24  |

| CPU                                                   |     | 29  |

| Microprocessor Survey                                 |     | 29  |

|                                                       |     | 30  |

| Inmos Transputer                                      | ••• | 30  |

| •                                                     |     | 31  |

| Fairchild Clipper                                     |     |     |

| VLSI 86C010                                           | • • | 32  |

| TI 74AS88XX and AMD 29300                             | • • | 32  |

| Microprocessor Selection                              |     |     |

| Understanding the AMD 29000                           |     | 35  |

| Microprogram Timing Analysis                          |     |     |

| Assumptions used in Analysis                          |     |     |

| An Optimal CPU/FPU                                    |     |     |

|                                                       |     | 40  |

| Input/Output Processor                                | ••  |     |

| Intelligent versus Nonintelligent I/O Processors      | 5.  | 41  |

|       | Packet Formats                        |     |     |     |   |   |   |   |   |   |   |   | 42  |

|-------|---------------------------------------|-----|-----|-----|---|---|---|---|---|---|---|---|-----|

|       | Interprocessor Communication Times    | •   | •   | •   | • | • | • | • | • | • | • | • | 44  |

| 5.    | ARCHITECTURAL EVALUATION              | •   | •   | •   | • | • | • | • | • | • | • | • | 46  |

|       | The Armstrong Cork Benchmark          | •   | •   | •   | • | • | • | • | • | • | • |   | 46  |

|       | Dragster Benchmark                    |     |     |     |   |   |   |   |   |   |   |   | 49  |

| 6.    | DISCUSSION OF RESULTS                 |     |     |     |   |   |   |   |   |   |   |   | 55  |

|       | Parallel versus Serial Execution .    |     |     |     |   |   |   |   |   |   |   |   | 55  |

|       | Armstrong Cork Program                |     |     |     |   |   |   |   |   |   |   |   | 57  |

|       | Dragster Program                      |     |     |     |   |   |   |   |   |   |   |   | 57  |

|       | Conclusions                           | •   | •   | •   | • | • | • | • | • | • | • | • | 58  |

| Appen | dix                                   |     |     |     |   |   |   |   |   |   |   |   |     |

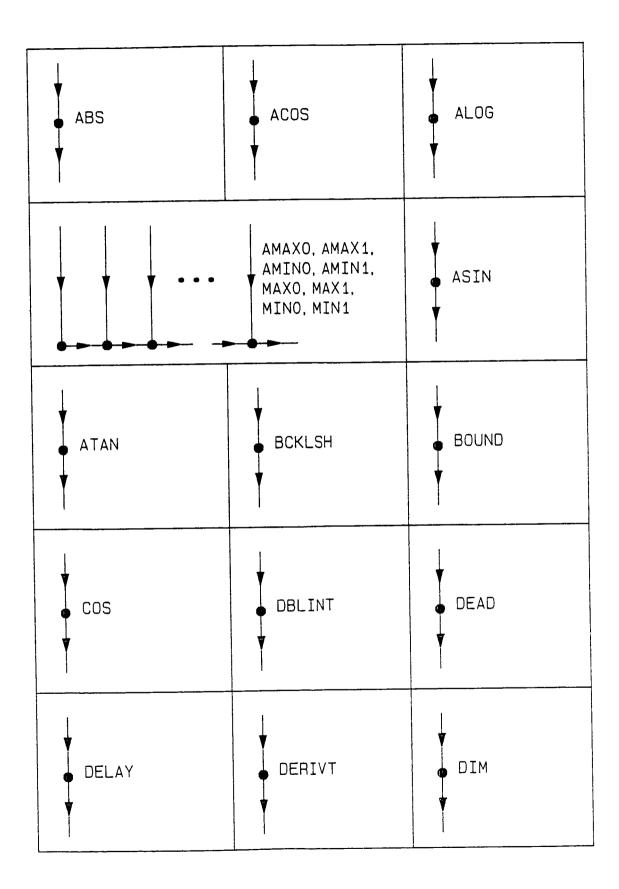

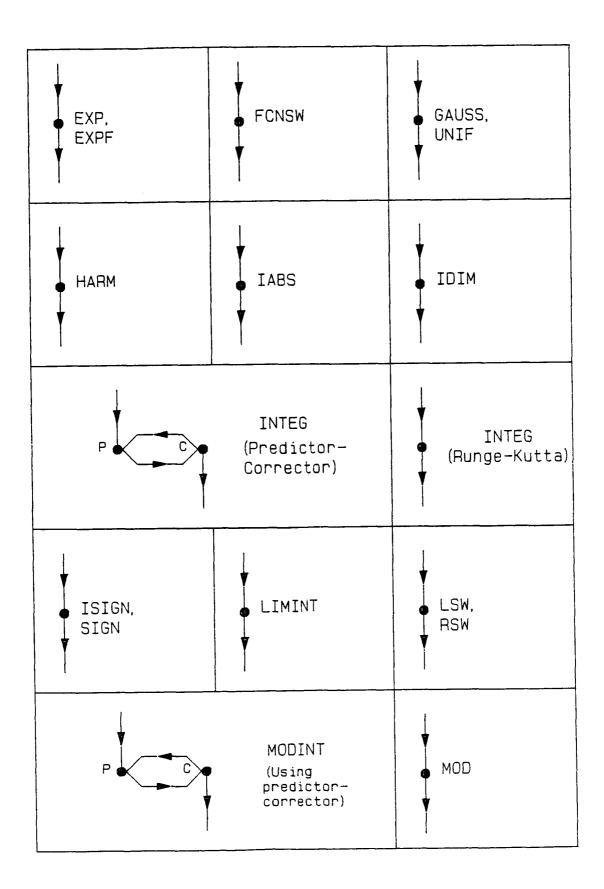

| Α.    | DATA FLOW GRAPHS FOR ACSL CONSTRUCTS  | •   | •   | •   | • | • | • | • | • | • | • | • | 60  |

| в.    | MICROPROGRAMMED ROUTINES FOR ACSL CON | STI | RUC | CTS | 5 | • | • | • | • | • | • | • | 64  |

| LIST  | OF REFERENCES                         |     |     |     |   |   |   |   |   |   |   |   | 129 |

# LIST OF TABLES

.

| [abl | e                                                           | Page |

|------|-------------------------------------------------------------|------|

| 1.   | Categorized ACSL Constructs                                 | 15   |

| 2.   | Armstrong Cork Benchmark                                    | 17   |

| 3.   | Comparing 32 Bit RISC Microprocessors                       | 30   |

| 4.   | Average Instruction Access Times for Clipper                | 34   |

| 5.   | Microprogram Timing Results                                 | 37   |

| 6.   | Intracluster Communication Analysis                         | 45   |

| 7.   | Armstrong Cork Cluster Activity                             | 48   |

| 8.   | Dragster Program                                            | 50   |

| 9.   | Dragster Program Cluster Activity                           | 54   |

| 10.  | Comparisons Between Sequential and Parallel Implementations | 56   |

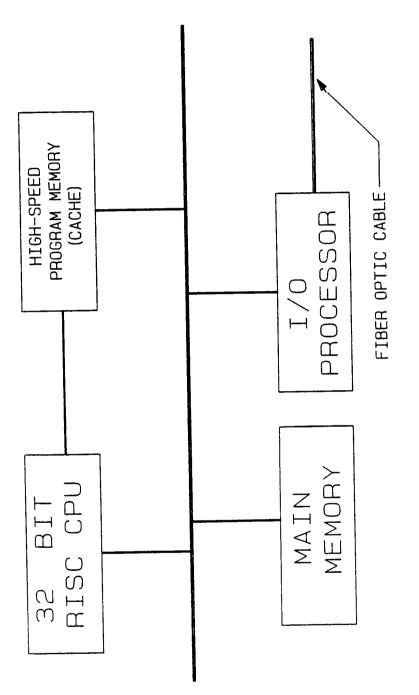

# LIST OF FIGURES

| Figu | re                                                       | Page |

|------|----------------------------------------------------------|------|

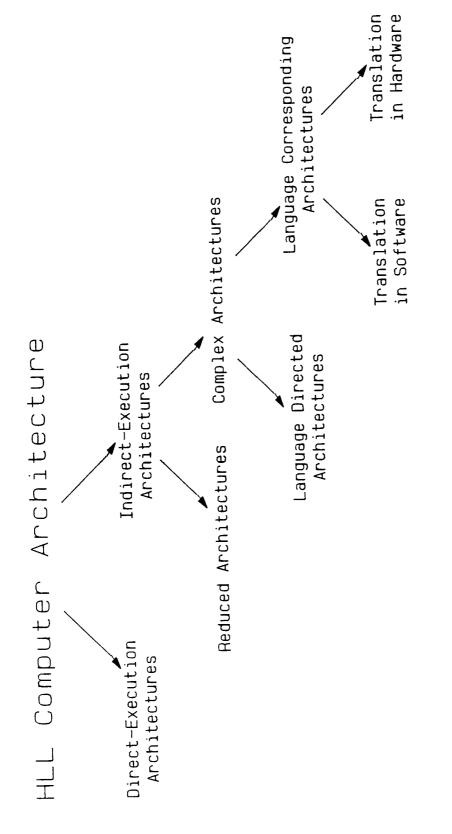

| 1.   | HLL Computer Architecture Classifications                | 3    |

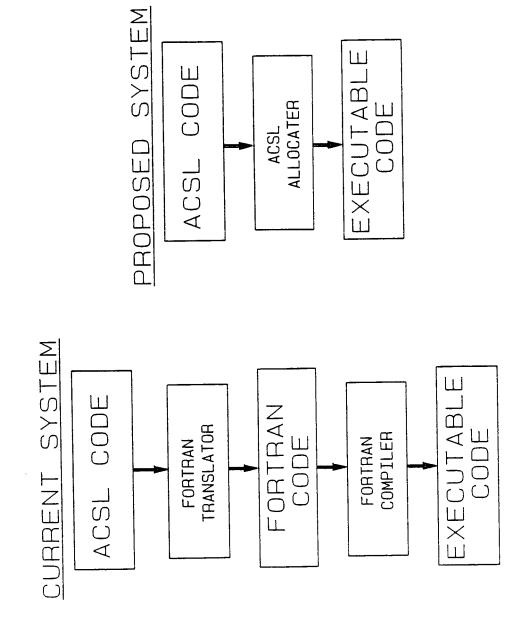

| 2.   | Current System versus Proposed System                    | 6    |

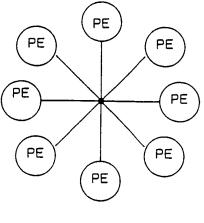

| 3.   | Possible Interconnection Networks                        | 10   |

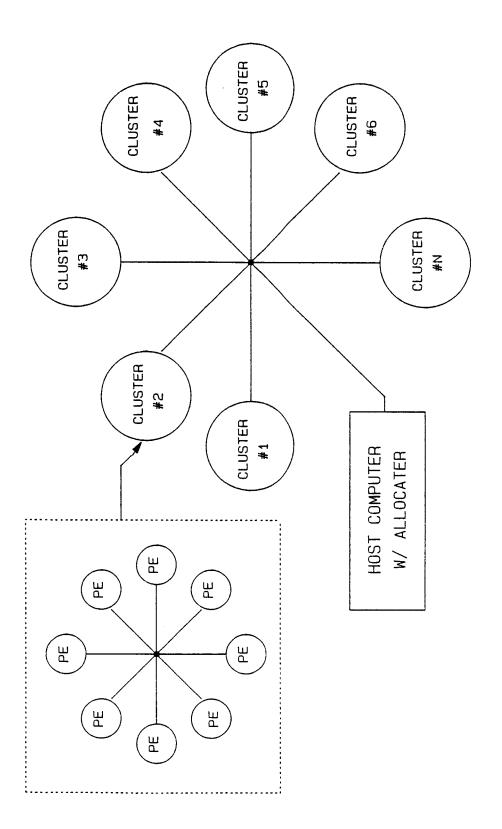

| 4.   | Clustered Network using Fiber Optic Stars                | 12   |

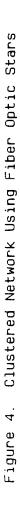

| 5.   | Data Flow Graph of Armstrong Cork Program                | 18   |

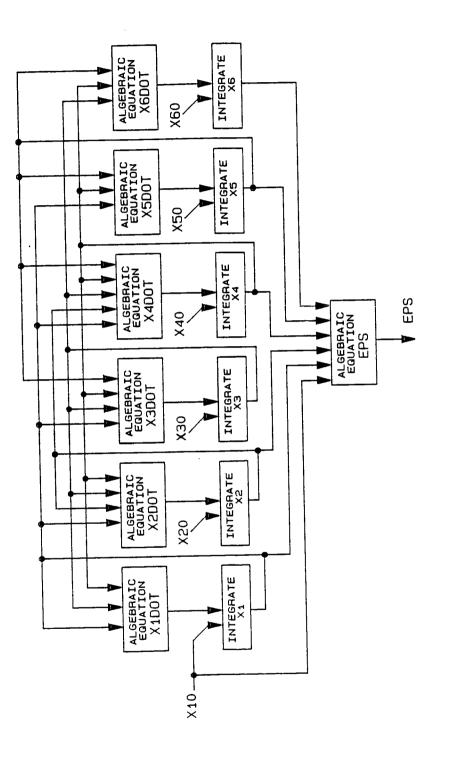

| 6.   | Processing Element                                       | 25   |

| 7.   | The University of Maryland Direct-Execution Architecture | 26   |

| 8.   | Instruction Execution Flow                               | 28   |

| 9.   | AMD 29000 Based PE                                       | 36   |

| 10.  | Packet Formats                                           | 43   |

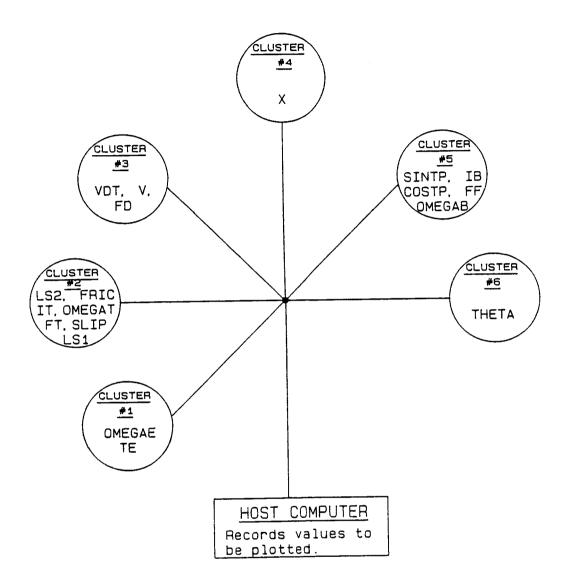

| 11.  | Cluster Allocation for Armstrong Cork Program            | 47   |

| 12.  | Cluster Allocation for Dragster Program                  | 52   |

#### ABSTRACT

A direct-execution parallel architecture for the Advanced Continuous Simulation Language (ACSL) is presented which overcomes the traditional disadvantages encountered when simulations are executed on a digital computer. The incorporation of parallel processing allows the mapping of simulations onto a digital computer to be done in the same inherently parallel manner as they are currently mapped onto an analog computer. The direct-execution format maximizes the efficiency of the executed code since the need for a high level language compiler is eliminated. Resolution is greatly increased over that which is available with an analog computer without the sacrifice in execution speed normally expected with digital computer simulations.

Although this report covers all aspects of the new architecture, key emphasis is placed on the processing element configuration and the microprogramming of the ACSL constructs. The execution times for all ACSL constructs are computed using a model of a processing element based on the AMD 29000 CPU and the AMD 29027 FPU. The increase in execution speed provided by parallel processing is exemplified by comparing the derived execution times of two ACSL programs with the execution times for the same programs executed on a similar sequential architecture.

vii

## CHAPTER 1

## INTRODUCTION

Analog computers have traditionally been chosen over digital computers for the simulation of physical systems because analog computer architectures are tailor-made for solving systems of simultaneous differential equations in an inherently parallel fashion. The main drawback of an analog computer is the low resolution of its outputs which will degrade the accuracy of the simulation. The traditional Von Neumann digital computer is capable of higher resolution, but it requires more computational time due to the sequential nature of its architecture. This report will present a digital computer architecture that overcomes the slow execution problem of a Von Neumann machine while providing greater resolution than normally possible with an analog computer.

This paper will examine a specific simulation language, ACSL, and use two techniques to improve its execution speed in order to simulate systems in real-time. These two techniques are the use of a directexecution architecture to bypass the compiler, thereby increasing system efficiency and speed, and the incorporation of parallel processing in the system architecture to further maximize execution speed.

All aspects of the architecture will be examined, including the microprogramming of the ACSL constructs, the processing element configuration, the interconnection network, the I/O processor, and the functions performed by the allocater. From this analysis execution

times of two example ACSL programs will be derived in terms of the minimum real-time calculation interval.

With the addition of appropriate sensors and actuators, this architecture could be used to simulate physical systems while they interact with other physical systems in real-time. Assuming the modeling equations are accurate, the results of the simulation will be precisely the same as if the actual component had been used. Furthermore, if the system being simulated is a type of computer controlled system, then the same architecture used to model it could also be used to implement the component being simulated.

## The Advanced Continuous Simulation Language, ACSL

The Advanced Continuous Simulation Language (ACSL) is used to model dynamic systems by time dependent, non-linear differential equations and/or transfer functions (Mitchell and Gauthier, Associates 1986). Simulation of physical systems is a standard and useful analysis tool used to test the design of a system prior to the actual construction of the proposed system. For example, a program written in ACSL to determine whether or not a pilot ejecting from his aircraft will strike the plane's vertical stablilizer is a much better approach than actually ejecting a test pilot to see if he clears the tail fin of the aircraft.

## A Direct-Execution Architecture

There are several ways high-level languages can be implemented. Some architectures concentrate on hardware, some on software, and still others on implementation technology. In general, computer architectures to implement high-level languages fall into one of the classifications shown in the tree diagram in figure 1 (Milutinovic 1988). Indirect-

Figure 1. HLL Computer Architecture Classifications

execution architectures use software or hardware to translate or compile the high-level language program in to a form suitable for machine execution. Direct-execution architectures bypass the translation step by incorporating hardware or software functions to execute high-level language programs directly.

When a compiler is used to convert a high-level language to machine code, inefficiencies are introduced into the newly created machine code. These inefficiencies cause the system to operate below the maximum possible execution speed and cause the system to utilize more memory than would be required if the high-level language constructs were programmed in a more efficient manner. A direct-execution architecture can help solve these problems since each processing element is microprogrammed to execute HLL constructs directly, thereby eliminating the need for a compiler and the inefficiencies associated with it.

## Parallel Processing

Parallel processing will be incorporated in the new architecture to increase execution speed. There is always a need in industry for faster execution speeds when modeling dynamic systems. The sequential machines used today simply cannot perform complex high-speed simulations in a real-time environment. With the introduction of parallel processing into a simulation language architecture, the simulation speeds for complex tasks will increase greatly over currently available simulation speeds. This has already been demonstrated at The University of California at Berkeley where the Department of Electrical Engineering and Computer Science is working on the Msplice parallel simulator for analog circuits. For some circuits a 32 processor version of Msplice runs as much as 25 times faster than a uniprocessor version (Howe 1987).

Parallel processing principles apply to any type device technology, so if it is stated that a parallel processing architecture is not needed because a higher speed technology (such as optical computers) will soon be available, please note that parallel processing can increase the speed of these devices in the same manner it is used to increase the performance of silicon devices.

## How to Improve the Current ACSL Computer Design

To compile an ACSL program today, one first converts the ACSL source code to FORTRAN with a FORTRAN translator. The FORTRAN code is then compiled to create executable machine code. Each step taken to compile an ACSL program introduces inefficiencies into the resulting machine code. This process is illustrated in figure 2. Another problem with the current method is the fact that the vast majority of variables used in FORTRAN reside in main memory, thus making FORTRAN a memory intensive language. Even if the memory variables are residing in a data cache, execution would proceed at a higher rate if the variables were contained in internal CPU registers rather than in memory locations.

The direct-execution process rids an architecture of the problems stated above. The need for a FORTRAN translator and compiler is eliminated since the ACSL constructs are microprogrammed at each processing element (PE). This approach will result in more efficient code than could be achieved with a compiler. The memory access problem will be reduced by selecting a microprocessor with a large internal register file permitting program variables to reside in internal CPU registers.

Figure 2. Current System versus Proposed System

## CHAPTER 2

## PARALLEL PROCESSING DESIGN CONSIDERATIONS

When designing a parallel processing architecture, there are several decisions to be made that are not considered when designing a typical sequential computing system. These decisions include the choice between a fine or course grained system, the method employed to organize memory, and what type interconnection network to use. These choices can either make an architecture fast and efficient, or they can bog down an architecture with inefficiencies to the point that a single high-speed processor can out-perform the parallel processing system.

## Fine-grained or Course-grained Architecture

The granularity of an architecture describes the complexity of the functions that each PE performs. A fine-grained system's PE would perform simple functions such as an addition or multiplication. Conversely, a course-grained system's PE would be capable of more complex tasks, such as the evaluation of an entire equation with multiplications, additions, subtractions, divisions, etc. Granularity also expresses the ratio between computation and communication in a parallel program (Howe 1987). Fine-grained systems are typically characterized as having more communication overhead than course-grained systems.

The system under consideration will be implementing high-level language constructs, some of which are fairly complex; therefore, a course grained architecture will be employed in order to keep a moder-

ately complex construct microprogram executable within a single PE. Doing so will minimize communication requirements between PEs and decrease possible communication bottlenecks.

## Shared Memory or Private Memory

In a shared memory system, multiple processors are connected to multiple memory banks through one or more buses. All memory in the system is contained in every processors memory map making all memory equally accessible by every processor. To access a memory location, the processor simply initiates a memory read or write cycle to the desired memory location. If no contention is present from the other processors, the requesting processor is allowed to access memory. This method provides the highest memory bandwidth but creates bottlenecks when several processors need access to the same memory bank at once.

In a private memory system, variables are passed to and from processors by way of a message passing scheme. To read a variable from another processor, the requesting processor sends a message to the processor holding the desired variable, and that processor sends a message back containing the variable. In general, private memory systems are usually efficient when the interactions between tasks are minimal, but shared memory systems can tolerate a higher degree of interaction between tasks without significant deterioration in performance (Howe 1987). With this in mind, if an architecture has a high degree of communication between tasks, a shared memory approach would be more efficient; but if the tasks had a low degree of inter-communication, a private memory approach would be better.

If a construct microprogram is considered to be a task in this ACSL architecture, there is then only a moderate amount of communication

between tasks. This is primarily due to the fact that very few of the ACSL constructs contain significant amounts of parallelism; therefore, it appears that a private memory architecture would be the most efficient.

## Interconnection Network

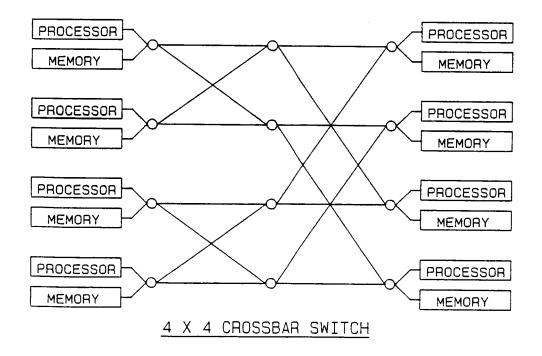

The two types of interconnection networks or topologies to be considered are the non-blocking crossbar switch and the fiber optic star. Crossbar switches offer the highest communication bandwidth and the most complex and costly design. Fiber optic stars offer higher communication bit rates than crossbar switches but only one PE may use the star network at a time. These interconnection networks are illustrated in figure 3.

If a system has a high degree of intercommunication between PEs, then a crossbar switch will offer the highest efficiency; on the other hand, if communication between PEs is low a fiber optic star will offer the best solution. As stated earlier, there is relatively little communication between tasks and what communication is present tends to be broadcast-type transfers to update state variables in the system; therefore, a fiber optic star would probably offer a more nearly optimal solution than the crossbar switch when all variables such as transmission format, cost, complexity, and transfer rates are considered.

Clustering is a technique in which PEs are grouped together with a dedicated interconnection network, and these groups or clusters of PEs are connected by a dedicated interconnection network. By creating levels in the interconnection network, clustering allows PEs in a cluster to operate on shared data with low communication overhead and provides hardware facilities for multiple groups of PEs to execute a

A FIBER OPTIC STAR

# Figure 3. Possible Interconnection Networks

tightly coupled process within their cluster without affecting the communications outside their cluster (Briggs and Hwang 1984). Figure 4 shows an interconnection network that uses fiber optic stars within a cluster and a fiber optic star connecting the clusters.

#### CHAPTER 3

## REAL-TIME INSTRUCTION EXECUTION WITH ACSL

In order to simulate complex systems in real-time, parallel processing will be incorporated into the architecture to boost execution rates to maximum levels. Parallelism will be implemented on two levels: the construct level and the program level. After examining the data flow graphs in appendix A, it does not take long to realize that very few of the ACSL constructs contain parallelism. Fortunately, one of the most important constructs in ACSL can be implemented with a parallel algorithm; that construct is the INTEG or integration instruction.

Parallelism on the program level is much more accommodating than parallelism on the construct level. Considering the fact that simulations executed on an analog computer are programmed in an inherently parallel manner, then it becomes clear that simulation programs written in ACSL can be mapped onto a parallel architecture in the same manner that simulations are mapped onto an analog computer architecture.

A direct-execution architecture offers several advantages over the traditional compiler approach to high-level language implementation with the largest advantage being in the form of more efficient code which results in faster program execution. In a direct-execution architecture, the compiler is eliminated altogether, and in its place an allocater is used to allocate segments of ACSL programs to the various PEs in the system. Resident at each PE are the hand-written assembly language routines to execute all ACSL constructs which will

result in the most efficient programming possible. Although it is beyond the scope of this paper to design the allocater, an attempt will be made to specify its requirements and describe its basic operation.

## Parallelism on the Construct Level

ACSL constructs have been classified into one of three different categories. These categories are constructs with no inherent parallelism, constructs approximated with a finite term series (such as trigonometric functions), and constructs with inherent parallelism. Table 1 shows all constructs in their appropriate category. Their data flow graphs and microcoded routines can be found respectively in appendix A and appendix B.

Constructs in category I offer no parallelism and are executable on one PE; in fact, several of these construct routines may be allocated to one PE without overfilling that PE's program memory. Constructs in category I range from simple boundary checks to simple calculations.

Constructs in category II again offer no parallelism in a coursegrained system but can be computed very efficiently by the use of a floating point processor that is optimized for factored polynomial evaluation. This point is discussed further in chapter 4.

Constructs in category III have useful amounts of inherent parallelism which are exploitable in a course-grained system. The most important construct in this category is the integrate instruction. In order to take advantage of parallelism, the integrate construct will use a second order parallel predictor-corrector algorithm. This algorithm is simply a restructuring of the traditional predictor-corrector method to allow predicting of the n+1 value while at the same time correcting

## TABLE 1

## CATEGORIZED ACSL CONSTRUCTS

#### CATEGORY I

ACSL INSTRUCTIONS WITH NO PARALLELISM PRESENT IN A COURSE-GRAINED SYSTEM.

ABS - ABSOLUTE VALUE. AMOD - REMAINDER OF MODULUS. BCKLSH - BACKLASH OR HYSTERICES. BOUND - LIMIT A FUNCTION. DBLINT - LIMIT DISPLACEMENT TERM OF FUNCTION. DEAD - CREATE DEADSPACE. DELAY - DELAY WITH RESPECT TO TIME. DERIVT - 1ST ORDER DERIVATIVE. DIM - POSITIVE DIFFERENCE. FCNSW - FUNCTIONAL SWITCH. GAUSS - CREATE NORMALLY DISTRIBUTED RANDOM VARIABLE. HARM - CREATE A SINUSOIDAL FUNCTION. IABS - ABSOLUTE VALUE OF AN INTEGER. IDIM - POSITIVE DIFFERENCE OF INTEGERS. INT - INTEGERIZE F.P. VALUE. ISIGN - APPEND A SIGN. LIMINT - LIMIT INTEGRATION. LSW, RSW - LOGICAL AND REAL SWITCH FUNCTIONS. MOD - REMAINDER OF AN INTEGER DIVISION. PTR - POLAR TO RECTANGULAR CONVERSION. PULSE - GENERATE A PULSE TRAIN. QNTZR - QUANTIZE A VARIABLE. RAMP - LINEAR RAMP FUNCTION GENERATOR. RTP - RECTANGULAR TO POLAR CONVERSION. SIGN - APPEND A SIGN. STEP - GENERATE A STEP FUNCTION. UNIF - UNIFORM RANDOM NUMBER SEQUENCE. ZHOLD - ZERO ORDER HOLD.

## CATEGORY II

#### ACSL INSTRUCTIONS APPROXIMATED WITH A FINITE TERM SERIES.

ACOS - ARC COSINE. ALOG - NATURAL LOGARITHM. ASIN - ARC SINE. ATAN - ARC TANGENT. COS - COSINE. EXP - NATURAL EXPONENT. EXPF - SWITCHABLE EXPONENTIAL. SIN - SINE. SQRT - SQUARE ROOT. TAN - TANGENT. TABLE 1--Continued

#### CATEGORY III

#### ACSL INSTRUCTIONS WITH PARALLELISM:

AMAXO, AMAX1, MAXO, MAX1 - INTEGER AND FLOATING POINT MAXIMUM VALUE ROUTINES.

AMINO, AMIN1, MINO, MIN1 - INTEGER AND FLOATING POINT MINIMUM VALUE ROUTINES.

INTEG - INTEGRATION.

for the n value (Liniger, Werner, and Miranker 1966). Using this method, a speed increase factor close to two can be realized.

In addition to a parallel predictor-corrector method, a fourth order Runge-Kutta integration method will also be programmed (Ralston and Wilf 1965). Although basically a sequential process, the coefficients K1, K2, K3, and K4 of the Runge-Kutta algorithm can be computed for sets of simultaneous equations concurrently, thereby making the execution time for a system of N equations on a parallel processing computer approximately equal to the execution time for a system with a single equation on a sequential machine.

#### Parallelism on the Program Level

As stated at the beginning of this chapter, ACSL programs can be mapped directly onto a parallel architecture since simulations are typically executed on an analog computer, and analog computers tend to incorporate a large amount of parallelism. This is best demonstrated with an example using the Armstrong Cork Benchmark (Hannaver 1986).

An ACSL program called the Armstrong Cork Benchmark is shown in table 2. A restructured data flow graph of this program is shown in

#### TABLE 2

ARMSTRONG CORK BENCHMARK

#### INITIAL

CONSTANT TEND = 50.0E-6CONSTANT K1 = 1.0E-14, K2 = 1.0E6, K3 = 1.0E3, K4 = 1.0E6CONSTANT K5 = 1.0E-2, K6 = 1.0E-5, K7 = 1.0E5, K8 = 1.0E6CONSTANT K9 = 1.0E-3CONSTANT X10 = 24., X20 = 0., X30 = 0., X40 = 0.CONSTANT X50 = 0., X60 = 0.MINTERVAL MINT = 1.0E-7MAXTERVAL MAXT = 1.0

# END

## DYNAMIC

| DERIVATIVE                                           |

|------------------------------------------------------|

| X1DOT = -K1*X1 - K3*X1*X4 - K7*X1*X3                 |

| X2DOT = -K2*X2 + K1*X1 + K3*X1*X4 + K7*X1*X3 + K9*X4 |

| X3DOT = K6*X5*X5 - K7*X1*X3 - K8*X3*X4               |

| X4DOT = K2*X2 - K3*X1*X4 - K4*X4*X4 + K6*X5*X5 -     |

| K8*X3*X4 - K9*X4                                     |

| X5DOT = K3*X1*X4 - K5*X5*X5 - K6*X5*X5               |

| X6DOT = K4*X4*X4 + K5*X5*X5 + K8*X3*X4               |

|                                                      |

| X1 = INTEG(X1DOT, X10)                               |

| X2 = INTEG(X2DOT, X20)                               |

| X3 = INTEG(X3DOT, X30)                               |

| X4 = INTEG(X4DOT, X40)                               |

| X5 = INTEG(X5DOT, X50)                               |

| X6 = INTEG(X6DOT, X60)                               |

|                                                      |

| EPS = (X1 - X10) + X6 + (X2 + X4 + X5)               |

|                                                      |

| TERMT(T.GT.TEND)                                     |

| END                                                  |

|                                                      |

|                                                      |

TERMINAL END

END

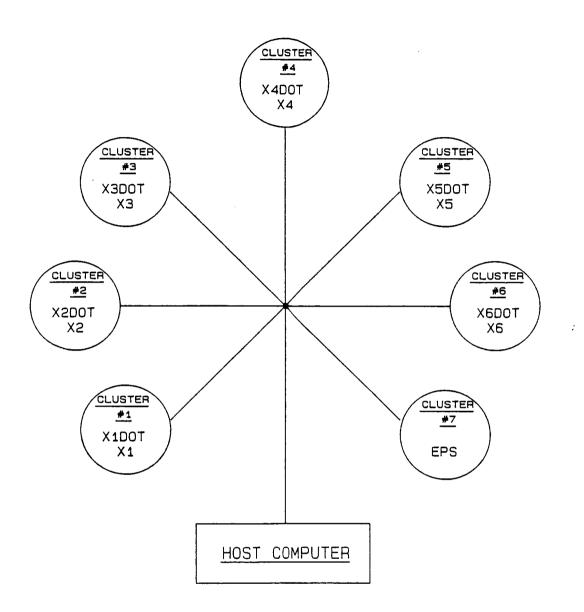

figure 5. The graph in figure 5 can be thought of as a set of 6 integrators operating in parallel. One possible allocation algorithm might be to allocate the algebraic equation X1DOT and the integrator X1

to a cluster of PEs, the equation X2DOT and the integrator X2 to another cluster of PEs, and so on until all six equations and integrators are allocated. These six clusters of processors would then compute their equations, perform their integrations, and update their results at the appropriate communication interval all in parallel. An additional PE would be required to accumulate the program output EPS. With this configuration and the use of parallel integration methods, an execution speed increase of up to twelve could be realized over the usual uniprocessor approach.

## Allocater Requirements

For real-time operation, the allocater has to allocate ACSL constructs in the most efficient manner, reduce and factor equations for maximum execution speed, and optimally schedule the interprocessor communications.

## Resource and Construct Allocation

System resources must be allocated in an optimum manner to obtain maximum system throughput. Instead of using main memory locations to hold variables, the allocater will assign internal CPU and FPU registers to frequently used variables. Doing so will allow maximum execution speeds since most variables will be immediately available to CPU.

To maximize execution speed, ACSL constructs must be allocated on the cluster level and the PE level in the most efficient manner. In general, independent functions should be allocated in a way to allow them to be executed in parallel; in addition, tasks with a moderate to high degree of processor intercommunications should be allocated to a cluster of PEs, thus allowing the required communications between

processors to proceed without hindering other processor's intercommunications. An example of this would be to allocate an integration and its associated equation to a cluster of PEs as described in the section <u>Parallelism on the Program Level</u>. Two or more PEs in the cluster could be used on a parallel integration algorithm and one or more of the PEs could be used to evaluate the derivative function. The optimum number of PEs in a cluster would depend on the complexity of the program.

#### Expression Reduction and Factoring

The allocater will be responsible for reducing algebraic expressions down to the form that will allow maximum execution speed. This process may include factoring a polynomial to allow rapid multiply/accumulate sequences. The constructs involving finite term series approximations are programmed in this manner. To illustrate factoring, examine the following equation for the exponential function (Beyer 1984):

$EXP[X] = 1 + X + A0 \times X \times 2 + A1 \times X \times 3 + A2 \times X \times 4 + A3 \times X \times 5 + A4 \times X \times 6 + A5 \times X \times 7.$

It may be factored to allow computation without generating higher powers of X in the following manner:

EXP[X] = 1 + X[1 + X[A0 + X[A1 + X[A2 + X[A3 + X[A4 + X[A5]]]]]].

This form allows rapid computation of an exponential with floating point units that incorporate a multiply/accumulate ALU.

## Interprocessor Communication Scheduling

The allocater will be responsible for determining what time periods the PEs will have data ready to transmit. Using this information, the

allocater will schedule the order in which intracluster PEs will transmit to other intracluster PEs and the order in which clusters will transmit data to other clusters. The allocater is able to schedule data transfers, because the execution times of all the construct routines are known. Once the order of all data transfers is known, the allocater loads information into every I/O processor telling it which data words to use, what order they arrive, and where the data words go in the PEs memory. For example, the allocater might tell a particular I/O processor that the fourth word seen on the star after the start of a calculation interval is state variable X1 which it needs for its calculations. The I/O processor would read X1 (and any other variables it required) and ignore all others. This process would repeat every calculation period.

The reason this complex scheduling scheme was devised is to minimize the communication overhead associated with transferring a word of data between PEs. If data packets were used that contained addressing or destination information, it would significantly increase the communication delays in the system. Using the scheduling technique allows the use of data packets that contain little or no overhead characters, only 32 bits of data.

## Real-Time Data Transfer

In order for a PE to transmit a word of data to another PE, the only action taken by the transmitting PE is to write the data word to the I/O processor. The I/O processor knows which data word it just received from the predetermined order assignments. The I/O processor then formats the data into a packet, waits for that data word's scheduled turn on the network, and then places it on the fiber optic

star network. If the data is scheduled to be received by an intracluster PE, that PE's I/O processor reads the data word and deposits it into the proper location in that PE's memory. If the transfer is intercluster, it will be read by the cluster I/O processor and placed on the intercluster fiber optic star for reception by the proper cluster at the scheduled time.

When a data word is received by the I/O processor for use by the PE, the I/O processor writes the data word to a predetermined memory location and signals the PE by activating an interrupt line. The interrupt causes the PE to retrieve the data word atomically with the LOADSET instruction. The LOADSET instruction reads a word of memory and writes back all ones to the same location after the read. With this technique, the I/O processor can determine if the PE has read the data word before updating the memory location with a new value. When all the operands have been received and loaded by the interrupt routine, the interrupt routine signals the executing task by setting a condition code to the boolean true value. The executing task simply checks this condition code, and when true, continues with the program execution.

### Program Execution with Direct-Execution Architectures

Direct-execution architectures offer several advantages over other architectures that use translators and compilers in that the directexecution architecture has no compilation overhead, offers single-copy program storage, and has a high degree of interactiveness (Milutinovic 1988). A disadvantage of a direct-execution architecture is its lack of flexibility. Most direct-executions languages are implemented entirely in hardware thus representing a nonoptimal hardware/software tradeoff, except in specific applications. For example, it would not be advan-

tageous to use a direct-execution architecture developed for Ada in a system used to execute FORTRAN code. Although the architecture discussed in this thesis was designed to execute ACSL, it is flexible enough to implement other host languages by simply re-writing the microcoded routines to execute whatever high-level language desired.

#### CHAPTER 4

## PROCESSING ELEMENT CONFIGURATION

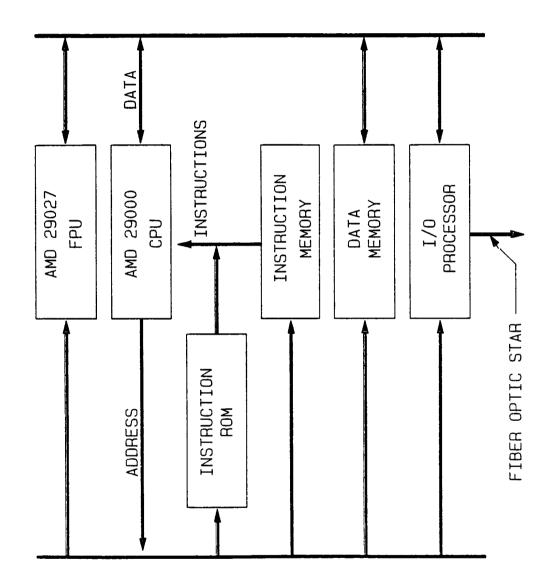

A processing element (PE) will be composed of a CPU, a FPU, highspeed instruction memory, main memory, and an I/O processor. The CPU will be a state-of-the-art microprocessor capable of sustained high MIPS rates. The FPU (floating point unit) will be required due to the numerically intensive tasks associated with ACSL. The high-speed instruction memory will hold the microcoded ACSL construct routines the CPU will execute, allowing the CPU to execute at full speed without wait states. Main memory will be made up of dynamic RAM and EPROM which will hold the microcoded routines for all ACSL constructs. The I/O processor is responsible for monitoring the interconnection bus and relieving the CPU from the overhead associated with interprocessor communications. A block diagram of a PE is shown in figure 6.

## Execution Flow In The Processing Element

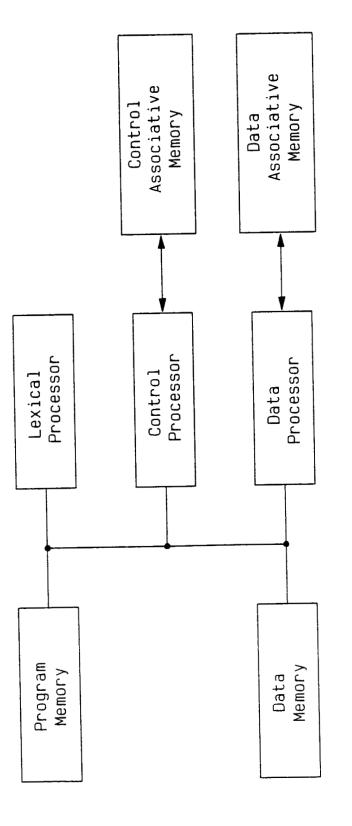

Before an intelligent choice can be made as to what type processing element to use, there must be an understanding as to the execution environment the PE will be operating in. Figure 7 shows a typical direct-execution architecture known as the University of Maryland approach. Code to be executed is stored in the program memory, and data variables are stored in the data memory. At execution, the lexical processor scans the program memory to determine what high-level language tokens it is to execute. The lexical processor then places the tokens

Figure 6. Processing Element

i

into a token register for execution by the control processor or data processor. The data processor will execute tokens corresponding to data manipulations such as multiplication and shifting, and the control processor executes tokens that change program flow such as GOTO and IF THEN instructions (Milutinovic 1988).

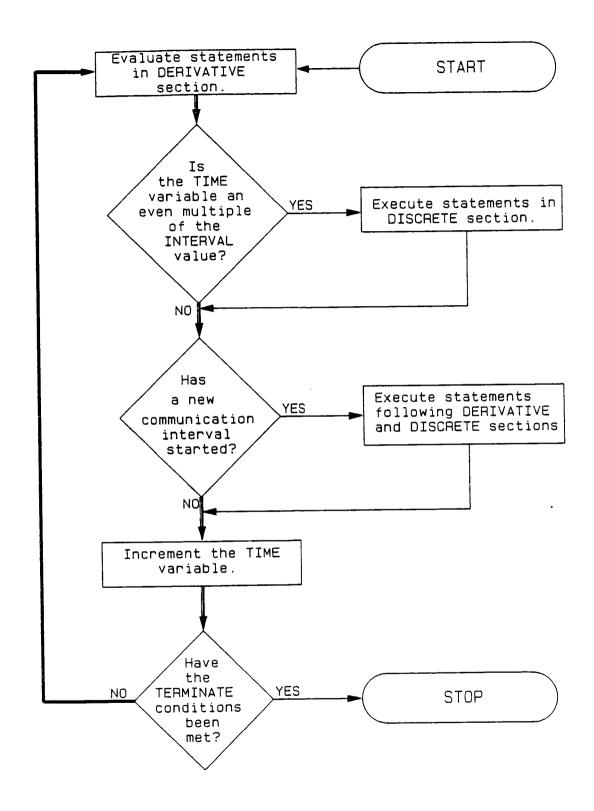

The architecture designed to implement ACSL will be similar to the University of Maryland approach, but will deviate from it in several ways in order to simplify the design and increase program execution. The ACSL direct-execution architecture will use only one processor to execute program control instructions as well as data manipulation instructions, although a floating point processor will be included to assist in the calculation of floating point operands. To obtain the maximum execution speeds, all lexical analysis will be performed by the allocater prior to the start of execution. The tokens to be executed will be resident in the CPU when execution starts. This is possible due to the fact that ACSL programs execute the same code repetitively as shown by the bold line (the primary loop) in figure 8. The code in the DERIVATIVE section is simply executed over and over, incrementing the time variable each pass until the terminate conditions are met. Performing lexical analysis before execution starts eliminates the need for a lexical processor in hardware, thus simplifying the design and increasing throughput by eliminating any delays associated with having the CPU wait for tokens.

When a PE receives (in the preprocessing stage) an ACSL construct it is to execute or an operand it will use in execution, that PE transfers the microcoded routine from main memory into high-speed static RAM or deposits the operand into an internal CPU register. When program

Figure 8. Instruction Execution Flow

execution begins, the PE will be executing instructions entirely from high-speed RAM with all operands contained in internal CPU registers, thus allowing the fastest possible execution by eliminating access to slow main memory.

## CPU

Microprocessors examined will be limited to the new families of 32 bit machines in order to obtain the most performance per processing element (PE). Of the available 32 bit microprocessors there are two basic types, complex instruction set (CISC) or reduced instruction set (RISC) microprocessors. Our search will concentrate on RISC type processors since they are characterized as having a large register set, being able to execute one instruction per clock cycle and having a high MIPS rate. RISC processors usually use a hard-wired instruction decoder that allows it to execute one instruction per clock cycle; on the other hand, CISC processors usually pay a performance penalty for supplying more complex instructions in the form of multiple clock cycles per instruction. In most cases it simply takes longer to decode and execute complex variable length instructions, and this inefficiency causes even simple operations in a CISC processor to take multiple clock cycles to execute--operations that a RISC processor would execute in one clock cycle (Toy, Wing, and Zee 1986).

### Microprocessor Survey

All the microprocessors listed in table 3 have one feature in common, except the 86C010 ARM, and that is they all use a dual bus Harvard architecture. Harvard architectures significantly improve performance by allowing data and instruction accesses simultaneously.

| TABLE | 3 |

|-------|---|

|-------|---|

| MANUF.     | CLOCK<br>SPEED                                 | CPU<br>REGISTERS                                                                                    | MIPS                                                                                         |

|------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| AMD        | 25 MHz                                         | 192                                                                                                 | 25.0                                                                                         |

| INMOS      | 20 MHz                                         | 3                                                                                                   | 10 - 20                                                                                      |

| FAIRCHILD  | 33 MHz                                         | 32                                                                                                  | 5 - 33                                                                                       |

| VLSI TECH. | 8 MHz                                          | 25                                                                                                  | 4.0                                                                                          |

| AMD        | 11.11 MHz                                      | 65                                                                                                  | 11.11                                                                                        |

| TI         | 20 MHz                                         | 65                                                                                                  | 20.0                                                                                         |

|            | AMD<br>INMOS<br>FAIRCHILD<br>VLSI TECH.<br>AMD | MANUF. SPEED<br>AMD 25 MHz<br>INMOS 20 MHz<br>FAIRCHILD 33 MHz<br>VLSI TECH. 8 MHz<br>AMD 11.11 MHz | MANUF.SPEEDREGISTERSAMD25 MHz192INMOS20 MHz3FAIRCHILD33 MHz32VLSI TECH.8 MHz25AMD11.11 MHz65 |

### COMPARING 32 BIT RISC MICROPROCESSORS

#### AMD 29000

The AMD 29000 has built-in support for both a data and an instruction cache with the cache memory located externally from the processor. It is said to be targeted toward general purpose CPU applications such as workstations and personal computers. Operating at 25 MHz, Advanced Micro Devices claims the 29000 offers about 12 times the performance of a VAX-11/780 for integer and systems code. The generous 192 register file acts as a data cache for a moderate number of operands while giving the ability to read-modify-write data in a single clock cycle. The AMD 29000 has a 32 bit fixed width instruction set. Large, fixed length instructions encode programs less efficiently (in terms of memory used) than small, variable-length instructions, but they can be processed much faster. The AMD29027 FPU is available to increase floating point computations greatly over software routines (Johnson 1987b).

### Inmos Transputer

The Inmos Transputer was designed with parallel processing in mind.

It is a high-integration machine which has four high-speed (20M bps) serial channels for communication with other processors, two timers, an 8 channel DMA controller, and a dynamic ram controller on chip. Systems have been built using over 100 Transputers that showed a linear increase in computing speed for each Transputer added. A disadvantage of the Transputer architecture for this application is the fact that the I/Oprocessor is located internally in the CPU and must be explicitly programmed. For maximum speed, an external I/O processor should be used to relieve the CPU of the overhead associated with formatting the message/data, computing where the data is to be send, etc. The Transputer must take time to program the serial I/O channels with such information--time that could have been spent by the CPU in executing an ACSL program. A new upgraded Transputer with a built-in floating point processor has been announced by Inmos and should be available soon. This will make the Transputer family more attractive to number-crunching applications, but for now it will not be considered further in this application (Cushman 1987).

# Fairchild Clipper

The Fairchild Clipper represents to some the state of the art in 32 bit microprocessors. This three chip set is actually a blend between CISC and RISC in that it contains a microprogram ROM to execute complex instructions, but this ROM is by-passed when the Clipper executes a more primitive instruction. This offers the high MIPS rate of RISC processors while still enjoying the sophisticated instructions of a CISC. Another feature of the Clipper is that it contains a complete 4K byte data cache, a 4K byte instruction cache, and a floating point processor on-board. The Clipper's register file contains 32 general

purpose registers that can be used for data or addressing, and eight 64 bit registers that are dedicated to floating point calculations. The Clipper instruction set contains 101 hardwired single clock cycle instructions and 67 microprogrammed complex instructions. Instruction lengths vary from 16 to 64 bits wide in multiples of 16 bits (Hunter 1987).

### VLSI 86C010

١

The VLSI 86C010 is intended to be a low cost RISC 32 bit microprocessor. Due to its standard von Neumann architecture, slow clock speed, and small register file, it will be a low performance device as well and will not be considered for this architecture (Cushman 1987).

# TI 74AS88XX and AMD 29300

The remaining two processor families, the TI 74AS88XX and the AMD 29300, are very similar architectures, and many designers mix and match various family members from both manufacturers when designing a system. Both of these processors are fixed-width 32 bit bit-slice microprocessors. A bit-slice CPU is composed of various parts that let a user configure his architecture for his application. Using a bit-slice CPU does increase your parts count, but this is offset by the fact that a bit slice system usually offers superior performance to that of a fixed architecture microprocessor. As in a classic RISC machine, a bit slice processor executes one microinstruction per clock cycle. The designer has the option of including complex instructions in the architecture by writing a microprogram (with the primitive microinstructions) to implement the complex function (Cushman 1987).

#### Microprocessor Selection

The three most impressive microprocessors in the survey are the AMD 29000, the Fairchild Clipper, and the TI 74AS88XX family. All three offer similar instruction sets. The Clipper does offer more complex instructions than the others, but this is offset by the fact that these instructions take multiple clock cycles to execute. As far as register files are concerned, all three processors offer a large number of registers with the Clipper having 32, the 74AS88XX having an expandable 65 word register file, and the AMD 29000 boasting an impressive 192 general purpose 32 bit registers. The last factor to consider before selecting a microprocessor is the execution speed or MIPS rate of each processor. Given that all three processors can execute a simple instruction in one clock cycle, the limiting factor in performance becomes the access time to the instruction cache or instruction memory. A processor cannot execute instructions faster than it fetches them.

The Clipper contains a 4K byte instruction cache configured as a four-way set associative cache with a quadword line buffer. If the total access time for the quadword line buffer is 60nS and the total access time for the main cache memory is 120nS, then depending on the instruction length (16 to 64 bits), the average access time for in-line code would be given by table 4 (Hunter 1987).

Examining these calculations shows that even if all the Clipper instructions were 16 bits long, the highest MIPS rate possible would be 15 MIPS. This figure does not take into account the time necessary to load the quadword line buffer or the main cache memory. Unless the cache mechanism can be disabled and the Clipper allowed to fetch one instruction word per clock cycle, it appears that in this application

#### TABLE 4

| INSTRUCTION<br>SIZE | ACCESSES TO<br>LINE BUFFER<br>@60nS EACH | ACCESSES TO<br>MAIN CACHE<br>@120nS EACH | TOTAL AVG.<br>ACCESS TIME |

|---------------------|------------------------------------------|------------------------------------------|---------------------------|

| 16 BIT              | 8                                        | 1                                        | 66.67nS                   |

| 32 BIT              | 4                                        | 1                                        | 72nS                      |

| 64 BIT              | 2                                        | 1                                        | 80nS                      |

|                     |                                          |                                          |                           |

### AVERAGE INSTRUCTION ACCESS TIMES FOR CLIPPER

(where the program will be executed totally out of high-speed static RAM) the cache system will deteriorate performance rather than enhance it.

The AMD 29000 offers several access protocols: simple access, pipelined access, and burst-mode access. All of the access protocols will fetch instructions at a 25MHz rate, but the burst-mode is easier to implement, since there are not as many address transfers or decodes to perform (Johnson 1987b).

The TI 74AS88XX uses a simple pipelined approach to access program memory. A microsequencer places an address on the microprogram memory, and the same clock edge that updates the microsequencer address output latches the previously addressed output from the microprogram memory into the instruction register. This allows instructions to be executed and fetched at a maximum rate of 20MHz (Texas Instruments, Inc. 1985).

After examining the results of the above analysis and the features contained in each of the microprocessors, it appears that the AMD 29000, with its 192 general purpose registers and 25 MIPS execution rate, offers the best solution. A block diagram of a PE constructed with an AMD 29000 is shown in figure 9 (Johnson 1987a). The TI bit-slice processor family offers approximately the same performance (or possibly slightly higher, depending on the efficiency of its FPU) as the AMD 29000, but due to the complexity and size of this bit-slice CPU, it was not selected. The Clipper performs at its best when used in systems with several layers of memory hierarchy, ranging from very fast to extremely slow. The Clipper's elaborate cache and memory management unit decreases the effective access time from 500nS for dynamic RAM to around 100nS, a 500% improvement in performance, but, the Clipper does not seem well suited to this particular application (Hunter 1987).

### Understanding The AMD 29000

For those not familiar with the AMD 29000, there are a few details about its programming that should be understood. Due to its pipelined architecture, the AMD 29000 uses a delayed branch mechanism. With a delayed branch, the instruction immediately following a branch instruction will always be executed. In the case where a useful instruction can be placed after a branch instruction, the branch instruction has an execution time of one clock cycle; otherwise, a NOP instruction will have to follow the branch, giving the branch instruction an effective execution time of two clock cycles.

The AMD 29000 has a unique way of handling conditional instructions. Instead of having a flag register which all conditional instructions use, the AMD 29000 allows conditions for instructions to come from any general purpose register. Certain instructions set true or false boolean values in a general purpose register, values that conditional branch instructions can use at a later time to determine whether to take a branch or to continue execution (Johnson 1987b).

Figure 9. AMD 29000 Based Processing Element

# Microprogram Timing Analysis

The following paragraphs will examine the execution times of the AMD 29000 assembly language ACSL construct routines, shown in Appendix B, and specify the assumptions and conditions used to obtain these speeds. A summary of the execution times and the average MIPS rates for the ACSL construct routines is shown in table 5.

## TABLE 5

## MICROPROGRAM TIMING RESULTS

| CONSTRUCT   | INSTRUCTIONS<br>EXECUTED | AVERAGE<br>MIPS | EXECUTION<br>TIME (nS) |

|-------------|--------------------------|-----------------|------------------------|

| ABS         | . 1                      | 25              | 40                     |

| ACOS        | 35                       | 12.5            | 2800                   |

| AINT        | 7                        | 12.5            | 560                    |

| ALOG        | 62                       | 12.8            | 4840                   |

| AMAXO       | 7*CNT+12                 | varies          | (7*CNT+21)*40          |

| AMAX1       | 7*CNT+12                 | varies          | (10*CNT+21)*40         |

| AMINO       | 7*CNT+12                 | varies          | (7*CNT+21)*40          |

| AMIN1       | 7*CNT+12                 | varies          | (10*CNT+21)*40         |

| AMOD        | 40                       | 12.99           | 3080                   |

| ASIN        | 31                       | 12.5            | 2480                   |

| ATAN        | 77                       | 12.5            | 6160                   |

| BCKLSH      | 24                       | 15.38           | 1560                   |

| BOUND       | 20                       | 16.67           | 1200                   |

| COS         | 28                       | 12.5            | 2240                   |

| DBLINT      | 18                       | 16.08           | 1120                   |

| DEAD        | 21                       | 14.58           | 1440                   |

| DELAY       | 12                       | 21.42           | 560                    |

| DERIVT      | 41                       | 13.31           | 3080                   |

| DIM         | 10                       | 15.63           | 640                    |

| EXP         | 31                       | 12.5            | 2480                   |

| EXPF        | 39                       | 13.0            | 3000                   |

| FCNSW       | 15                       | 21.43           | 700                    |

| GAUSS       | 153                      | 15.61           | 9800                   |

| HARM        | 47                       | 13.06           | 3600                   |

| IABS        | 5                        | 12.5            | 400                    |

| IDIM        | 4                        | 25              | 160                    |

| INT         | 5                        | 12.5            | 400                    |

| INTEG:      |                          |                 |                        |

| RUNGE-KUTTA | 43+4*FUNCTION            | 12.5            | 3280+4*FUNCTION        |

| PREDICTOR   | 14+FUNCTION              | 12.5            | 960+FUNCTION           |

| CORRECTOR   | 16+FUNCTION              | varies          | 1160+FUNCTION+DELAY    |

| ISIGN       | 5                        | 12.5            | 400                    |

| LIMINT      | 16                       | 15.39           | 1040                   |

| CONSTRUCT | INSTRUCTIONS<br>EXECUTED | AVERAGE<br>MIPS | EXECUTION<br>TIME (nS) |

|-----------|--------------------------|-----------------|------------------------|

| LSW       | 3                        | 25              | 120                    |

| MAXO      | 7*CNT+9                  | varies          | (7*CNT+15)*40          |

| MAX1      | 7*CNT+16                 | varies          | (10*CNT+29)*40         |

| MINO      | 7*CNT+9                  | varies          | (7*CNT+15)*40          |

| MIN1      | 7*CNT+16                 | varies          | (10*CNT+29)*40         |

| MOD       | 55                       | 25              | 2200                   |

| PTR       | 70                       | 12.5            | 5600                   |

| PULSE     | 31                       | 16.15           | 1920                   |

| QNTZR     | 60                       | 17.05           | 3520                   |

| RAMP      | 10                       | 15.63           | 640                    |

| RSW       | 3                        | 25              | 120                    |

| RTP       | 353                      | 13.81           | 25560                  |

| SIGN      | 5                        | 12.5            | 400                    |

| SIN       | 32                       | 12.5            | 2560                   |

| SQRT      | 245                      | 15.09           | 16240                  |

| STEP      | 10                       | 16.67           | 600                    |

| TAN       | 32                       | 12.5            | 2560                   |

| UNIF      | 17                       | 14.66           | 1160                   |

| ZHOLD     | 3                        | 25              | 120                    |

# TABLE 5--Continued.

# Assumptions Used In Analysis

The following assumptions were made in the analysis of the ACSL

construct routines:

- 1. Operands (except where noted) are contained in internal registers in the AMD 29000.

- 2. There will be a 100% hit ratio in the Branch Target Cache.

- 3. Instruction memory will accommodate one cycle accesses.

- 4. Load and store instructions require two clock cycles for execution, and all other instructions used require only one clock cycle.

- 5. All floating point operands are 32 bit single precision values.

Since there are 192 general purpose registers in the AMD 29000 and for a large number of PEs there will be a relatively small number of operands per PE, the assumption that all operands will be held in internal CPU registers is not unreasonable. This assumption is verified by examining the microcoded routines in appendix B. There is not a single routine that uses more than a ten registers.

The AMD 29000 contains a Branch Target Cache which holds information regarding the 32 most recent branches. The first time a branch is executed the four instructions at the target location are saved in the Branch Target Cache. When the branch is executed again, the processor pipeline is filled with instructions from the Branch Target Cache, allowing the processor to proceed without having to wait for the pipeline to refill. Since ACSL programs execute the same code in the derivative section repetitively and the construct routines tend to contain in-line code, it is safe to say that branches taken will be contained in the Branch Target Cache.

In order to have memory fast enough to allow one-cycle accesses, static RAM memory with access speeds of 20nS or less will have to be used. This does not present a problem since there are several memory devices on the market today with speeds of 15nS to 20nS.

All AMD 29000 instructions (except LOADM and STOREM) are designed to execute in one clock cycle. Unfortunately, the LOAD and STORE instructions will require two clock cycles to execute when instructions are being fetched at a rate of 25 MHz (one per clock cycle), because the address bus is shared between data operations and instruction fetches. The processor will require one clock cycle to generate the LOAD or STORE instruction address and another clock cycle to generate the operand address. In applications where multiple clock cycles are required to access memory, the loading and storing of data operands will be transparent, since the operand address generation will be performed during the the time periods (referred to as wait states) the CPU is waiting for instruction memory.

Using 32 bit floating point operands will provide sufficient resolution and accuracy for the majority of applications. If double precision operands are required, execution times will not significantly increase, since the AMD 29027 FPU performs double precision operations in the same amount of time as single precision operations. The only additional requirements will be the time necessary to load and unload the extra words to and from the FPU and the extra storage required for the larger operands.

# An Optimal CPU/FPU

After examining the characteristics of the AMD 29000 microprocessor, it becomes obvious that a theoretical processor with different features could significantly improve the performance of this architecture. Possible improvements to the processor include the following:

1. Separate address buses for instructions and data.

2. Integral floating point unit.

3. Non-pipelined operation, both in the CPU and the FPU.

The only factor keeping all construct routines from operating at 25 MIPS is the fact that two clock cycles are required for a LOAD and a STORE operation. If separate address buses for instructions and data were used, an instruction could be fetched and a data value stored in one clock cycle, thus bringing the average MIPS rates in table 5 to 25 MIPS.

An integral floating point unit could improve system performance by reducing the burden of loading and unloading operands to and from the FPU. Currently, two clock cycles are required to load or unload 32 bit

operands; but with an integral FPU, external accesses could be eliminated by sharing internal registers.

Pipelining is a common technique used to improve the throughput of a CPU; unfortunately, it can cause additional delays when branches are encountered. The optimal CPU for this architecture will not be pipelined in order to avoid the branch problem. The AMD 29027 FPU is also pipelined for maximum execution speed. The data in the FPU must be pushed through the unit with instruction or operand writes until the result is present at its outputs. This fact significantly increases execution time for floating point operands by causing the FPU to take up to 400nS to compute a result when it is capable of performing the same operation in 200nS. For the optimal FPU, pipeline advancement would not be dependent on two cycle LOAD or STORE instructions.

# Input/Output Processor

In order for a parallel processing system to operate at peak performance levels, the interprocessor communication structure must be fast and efficient. The I/O processor must be able to retrieve variables from the interconnection bus network and deposit them into the CPUs memory as fast as possible to minimize the communication overhead of the parallel processing system. Although it is beyond the scope of this paper to design an I/O processor, the following paragraphs will attempt to describe a possible I/O processor in sufficient detail to derive realistic times for the communication delays.

### Intelligent versus Nonintelligent I/O Processors

There are two basic extremes when it comes to I/O processor design, the intelligent I/O processor and the nonintelligent I/O processor.

The intelligent I/0 processor is characterized as having a programmable CPU and the nonintelligent I/0 processor is characterized as being a collection of dumb, hardwired state machines.

The intelligent I/O processor has the advantage of being able to handle errors intelligently, perform more complex tasks, and make the system architecture flexible in terms of packet length, content, and format. The nonintelligent or hardwired I/O processor has a speed advantage over a programmable I/O processor since it simply reacts to conditions instead of analyzing them first.

Perhaps the optimal solution is an I/O processor that is a blend of the two extremes. It could contain intelligence in the form of a microprocessor which would monitor the communication process, including the complex scheduling of interprocessor transfers. As long as processes were proceeding normally, the microprocessor would do nothing, and the hardwired data transfer circuitry could proceed at a maximum rate. If an error was detected or some unusual condition occurred, the microprocessor could step in and conduct error recovery or tell the hardware how to handle the unusual condition.

### Packet Formats

Now that an I/O processor configuration has been decided upon, a data communication format may be chosen. Figure 10 shows various packet formats that could be used. To simplify the I/O processor design, all packets will use a 32 bit fixed length with one extra bit on the start of the packet to designate what type packet it is, and an extra bit on the end for parity checking. If the prefix bit is a zero, that packet contains a data word; if the prefix bit is a one, that packet contains a command that is directed to one or more PEs.

| ACKET           |

|-----------------|

|                 |

|                 |

| $\triangleleft$ |

|                 |

| $\triangleleft$ |

| $\Box$          |

| РАНІТҮ                  | 4    |

|-------------------------|------|

| DATA WORD               | 32   |

| PACKET<br>TYPE<br>(C/D) | 1    |

| DESCRIPTION             | BITS |

| PACKET  |  |

|---------|--|

| COMMAND |  |

| PARITY                                               |      |

|------------------------------------------------------|------|

| COMMAND                                              | 16   |

| P.E.<br>ADDRESS                                      | 8    |

| PACKET CLUSTER P.E.<br>TYPE ADDRESS ADDRESS<br>(C/D) | ω    |

| РАСКЕТ<br>ТҮРЕ<br>(С/ <u>D</u> )                     | 1    |

| DESCRIPTION                                          | BITS |

Figure 10. Packet Formats

## Interprocessor Communication Times

Using the model of the fiber optic star interconnection network shown in figure 3, the model of the I/O processor discussed in the I/O processor sections, and the model of the communication structure shown in figure 10, an approximation of the time to transfer data from one PE to another can be determined as shown in table 6.

Table 6 gives a total time of 51 clock cycles at the fiber optic star bus frequency and 7 clock cycles at the CPU clock frequency to transfer a data word to an intracluster PE. Using a fiber optic star bus frequency of 300MHz and a CPU frequency of 25MHz, the communication delay time for intracluster transfers will be 450nS. Assuming there is no waiting for access to the intercluster fiber-optic star, no additional delay will be added to the communication delay time for an intracluster transfer.

# TABLE 6

# INTRACLUSTER COMMUNICATION ANALYSIS

CLOCK CYCLE

# FUNCTION PERFORMED

| TRANSMITTING PE |                                                      |  |  |

|-----------------|------------------------------------------------------|--|--|

| 1               | PE writes a data word to I/O processor.              |  |  |

| 2               | I/O processor forms a data packet.                   |  |  |

| 3-36            | I/O processor shifts data onto the fiber optic star. |  |  |

|                 |                                                      |  |  |

# RECEIVING PE

| 3-36    | I/O processor receives data packet and converts to parallel.                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 37-40   | I/O processor computes destination address with look-<br>up table.                                                                          |

| 41-51   | I/O processor performs a read/check/write memory cycle<br>to deposit received data word into PE memory and<br>activates CPU interrupt line. |

| 7 (CPU) | CPU responds to interrupt, writes data word to CPU register location, and sets data received flag.                                          |

|         |                                                                                                                                             |

### CHAPTER 5

### ARCHITECTURAL EVALUATION

Chapter 5 will attempt to give a better understanding of the performance of this direct-execution parallel architecture by evaluating two ACSL programs in terms of execution speeds and computing resources required.

# The Armstrong Cork Benchmark

The Armstrong Cork benchmark, shown in table 2, will now be evaluated to determine the minimum real-time calculation interval possible (Hannaver 1986). The first step in analyzing an ACSL program is to allocate the program constructs to the various PEs and clusters in the system. One such allocation of clusters is shown in figure 11. In order to insure maximum execution speed, equations should be factored for ease of computation. The resulting factored equations that will be integrated every calculation interval are listed below:

X1DOT = X1\*(-K1-K3\*X4-K7\*X3)

$$X2DOT = -K2 \times X2 + X1 \times (K1 + K3 \times X4 + K7 \times X3) + K9 \times X4$$

$X3DOT = K6 \times X5 \times X5 + X3 \times (-K7 \times X1 - K8 \times X4)$

X4DOT = X4\*(-K3\*X1-K4\*X4-K8\*X3-K9)+K2\*X2+K6\*X5\*X5

X5DOT = X5\*X5(-K5-K6)+K3\*X1\*X4

X6DOT = X4\*(K4\*X4+K8\*X3)+K5\*X5\*X5.

Using the allocation of computing tasks shown in figure 11, the

.

# Figure 11. Cluster Allocation for Armstrong Cork Program

calculation times and resources required at each cluster were derived and shown in table 7. The corrector routine of the parallel predictorcorrector method will always take longer to execute than the predictor routine; therefore, only the corrector routine will be analyzed. For the sake of simplicity, it will be assumed that the derivative function is evaluated entirely on one PE. Cluster 7 will be used to evaluate the equation for the output function EPS. The equation for EPS will require five additions which can be evaluated in 1.2uS.

ļ

### TABLE 7

### ARMSTRONG CORK CLUSTER ACTIVITY

| CLUSTER   | DERIVATIVE<br>EVALUATION<br>TIME | CORRECTOR<br>EVALUATION<br>TIME | PEs<br>USED |

|-----------|----------------------------------|---------------------------------|-------------|

| Cluster 1 | 0.880uS                          | 2.49uS                          | 2           |

| Cluster 2 | 1.6uS                            | 3.21uS                          | 2           |

| Cluster 3 | 1.52uS                           | 3.13uS                          | 2           |

| Cluster 4 | 2.24uS                           | 3.85uS                          | 2           |

| Cluster 5 | 1.2uS                            | 2.81uS                          | 2           |

| Cluster 6 | 1.44uS                           | 3.05uS                          | 2           |

|           |                                  |                                 |             |

To obtain the minimum calculation interval possible with this configuration, the communication delay times of all the state variables must be considered. Since all state variables are used in other equations, their values must be updated every calculation interval. The updating of values will be done after the derivative function is integrated and will result in an additional delay of 1.34uS. The output function EPS will be transmitted to the host computer every calculation

interval for recording. The minimum calculation interval can now be determined by taking the worst execution time for the clusters and adding it to the update delay, 1.34uS. The slowest executing cluster is cluster 4 (3.85uS); therefore, the minimum real-time calculation interval is found to be 5.19uS. This value could possibly be lowered by dividing the function X4DOT among two or more PEs for evaluation. If this method is taken, care should be taken to insure that communication bottlenecks to not occur due to excessive task division.

## Dragster Benchmark

The DERIVATIVE portion of an ACSL program named Dragster is shown in table 8 (Hannaver 1986). The Dragster program will be analyzed in the same fashion the Armstrong Cork program was examined. Figure 12 shows several clusters of PEs connected by the intercluster fiber optic star and the various functions allocated to each cluster.