# NASA Contractor Report 185126

# Advanced Modulation Technology Development for Earth Station Demodulator Applications

R.C. Davis, J.V. Wernlund, J.A. Gann, J.F. Roesch, T. Wright, and R.D. Crowley Harris Corporation GCSD Melbourne, Florida

July 1989

Prepared for Lewis Research Center Under Contract NAS3-24681

National Aeronautics and Space Administration

N89-26880

(NASA-CR-185126) ADVANCED MODULATION TECHNOLOGY DEVELOPMENT FOR EARTH STATION DEMODULATOR APPLICATIONS Final Report (Harris Corp.) 282 p CSCL 09F

Unclas 0224576

G3/17

### INTRODUCTION

This report is prepared by Harris Government Communications Systems Division for NASA Lewis Research Center under contract NAS3-24681. This report is written in response to SOW paragraph 3.7.3, Final Report. The purpose of this document is to provide a summary of the entire contractual efforts, pertinent results, and a compilation of the task reports.

## 1.0 <u>Task I Report</u>

The Task I Report describes the refinement of the proposed downlink modulation system design concept. It develops in detail the specific modulation scheme used, the conceptual design for the Earth station demodulator hardware implementation, and an assessment of the impact of future technology on system performance.

### 2.0 <u>Task III Breadboard Evaluation Report</u>

This report describes the test results for the A/D converter breadboard developed during Task III and was written in response to SOW paragraph 2.3.5. Task III was the breadboard development phase of the program.

# 3.0 <u>Task V Design Review Package</u>

This section contains the material presented at the Task V final design review. This material is in vu-graph format and describes the POC Model Demodulator and the Special Test Equipment (STE) detailed design. Included are descriptions of the design and layout, functional performance, size, weight, power, and results of functional performance analyses.

# 4.0 <u>Coded 16-ary CPFSK Coherent Demodulator Paper</u>

This section contains a paper which was published in the Proceedings of the Mobile Satellite Conference, sponsored by the Jet Propulsion Laboratory. It is a summary of the conceptual design and design implementation for the modulation system developed in response to the requirements of this contract.

# 5 0 Task VII Report

The Task VII Report provides the results of POC Model Testing and Analyses. The purpose of this document is to present the results of the tests conducted in accordance with the POC Model Test Plan and Procedure developed in response to SOW subtask 2.5.3. The POC Model Test Plan and Procedure is included in the Task VII Report. This report also provides recommendations for the development of an engineering model demodulator using further advanced implementation technology, based on analyses of test results.

# CONTENTS

|                                                                                                      | Page |

|------------------------------------------------------------------------------------------------------|------|

| TASK I REPORT by Richard D. Crowley                                                                  | 1    |

| HIGH SPEED A/D CONVERTER BREADBOARD EVALUATION REPORT by James F. Roesch, Jr                         | 54   |

| TASK V REVIEW by Richard D. Crowley, Robert C. Davis, and James A. Gann                              | 18   |

| DEVELOPMENT FOR A CODED 16-ARY CPSFK COHERENT DEMODULATOR by Ken Clark, Robert Davis, and Jim Roesch | 178  |

| TASK VII REPORT                                                                                      | 184  |

# NAS3-24681 ADVANCED MODULATION TECHNOLOGY DEVELOPMENT TASK I REPORT APRIL 4, 1986

P. O. BOX 91000 MELBOURNE, FL 32902

SUBMITTED BY: RICHARD D. CROWLEY

PREPARED FOR: NASA LEWIS RESEARCH CENTER CLEVELAND, OH 44135

## CONTENTS

| 1.   | DETAILED DEVELOPMENT OF THE MODULATION SCHEME                        | 3  |

|------|----------------------------------------------------------------------|----|

| 1.1  | Modulation Scheme Comparisons                                        | 3  |

| 1.2  | Rationale for the Scheme Selected                                    | 14 |

| 1.3  | Detailed Description of the Modulation Scheme Developed · · · · · ·  | 17 |

| 1.4  | A Description of the Method and Estimated Speed of Independent Burst |    |

|      | Acquisitions                                                         | 21 |

| 2.   | CONCEPTUAL DESIGN OF DOWNLINK MODULATION HARDWARE                    | 33 |

| 2.1  | Downlink Modulation System Conceptual Design                         | 33 |

| 2.2  | Theoretical Performance Characteristics and Operating Conditions of  |    |

|      | the Downlink Modulation System Design Concept                        | 35 |

| 2.2. | .l Bandwidth Efficiency                                              | 36 |

| 2.2. | .2 Power Efficiency                                                  | 37 |

| 2.2. | .3 Bit Error Rate Performance                                        | 38 |

| 2.3  | "Ility" Data                                                         | 41 |

| 2.3. | .l Producibility - Special Features for Lowering Costs when Produced |    |

|      | in Quantity                                                          | 41 |

| 2.3. | .2 An Estimate of Recurring Costs                                    | 44 |

| 2.3. | .3 Reliability                                                       | 45 |

| 2.3. | .4 Maintainability                                                   | 45 |

| 2.4  | Overview of Special Test Equipment                                   | 46 |

| 3.   | TECHNOLOGY ASSESSMENT AND DESIGN IMPACT                              | 47 |

| 3.1  | Current Versus Future Technology                                     | 47 |

| 3.2  | Hardware Techniques which Represent an Advancement in the            |    |

|      | State-of-the-Art in Modulation Technology                            | 49 |

| 3.3  | The Impact of Technology on System Performance                       | 50 |

| 3.4  | Advantages and Disadvantages of Implementation Technologies          | 51 |

#### 1. DETAILED DEVELOPMENT OF THE MODULATION SCHEME

This section of the task one report details the development of the modulation scheme chosen to fulfill the requirements given in the Statement of Work (SOW).

### 1.1 Modulation Scheme Comparisons

The selection of the modulation/coding scheme proposed by Harris, and the corresponding implementation thereof has been based primarily on:

- 1. Demodulator simplicity

- Achieving a transmitted spectral shape whose power outside of the

bit rate point is 20 dB down from the desired signal power

- 3. Achieving a 5 x  $10^{-7}$  bit error rate performance with the required Eb/No as close as feasibly possible to that of QPSK

- 4. Operating through a non-linear TWT

- 5. Utilizing a coding scheme that creates minimal spectral spreading and yet is powerful enough to meet the  $5 \times 10^{-7}$  bit error rate

Careful attention has been paid to perform proper tradeoffs based on these criteria that would substantiate the proposed modulation/coding scheme and its implementation. The intent of this section is to summarize the most important of these tradeoffs.

A wide assortment of bandwidth efficient modulation techniques exist within the industry [1]. Some of these, like Minimum Shift Keying (MSK), have been developed [2] within the industry in general whereas others like Continuous Phase Frequency Shift Keying (CPFSK) have been specifically developed at Harris [3].

The first categorization of these techniques occurs when considering the envelope variations of the transmitted waveform. Techniques that impart data onto a carrier through its phase or frequency, are constant envelope signals whereas a signaling scheme that imparts data onto the carrier amplitude clearly exhibits envelope variations. A candidate in the latter category is M-ary Quadrature Amplitude Modulation (MQAM) which has been shown [3] to have greater power efficiency than schemes such as CPFSK or M-ary Phase Shift Keying (MPSK) which are in the constant envelope category. However, time-varying envelope signals require a linear RF channel which proves to be power inefficient in a satellite TWT that must be backed-off to provide such linearity. In this present TDMA downlink the minimization of signal distortion may require a 10 dB backoff which in our opinion is too great a price to pay in lost link margin for the increased bandwidth efficiency. Therefore this first tradeoff concluded that only constant envelope signals would be acceptable because of the power inefficiencies caused by the TWT backoff.

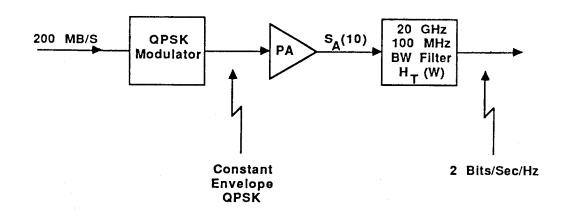

Another technique that was considered is to generate a constant envelope signal that is amplified by the transmit TWT and then filtered to shape the spectrum. The modulation scheme shown in Figure 1.1-1 was considered relative to the Statement of Work (SOW) requirements. As shown, a 200 Mb/s QPSK constant envelope modulation is employed through the power amplifier (PA) so that the nonlinear AM/AM and AM/PM characteristics given in the SOW can be tolerated.

Figure 1.1-1 An Alternative Modulator Approach

After the amplifier, the spectrum is of course still that of QPSK, i.e.,

$$S_{A}^{(w)} = \frac{\sin(2\pi f/f_{B})}{2\pi f/f_{B}}$$

(1)

where, f = frequency removed from the carrier

$$f_B = Bit rate = 200 Mb/s$$

The first nulls of this spectrum are at  $\pm$  .5 Bit rate, i.e., in the center of the adjacent channel and consequently the main lobe will cause too much adjacent channel interference. Thus, additional filtering is required after the PA.

An approach that is attractive at first glance is to duobinary shape the spectrum after the amplifier. There are several ways of performing this spectral shaping. Irregardless of how it is done, the overall combination of transmit and receiver filtering must result in a net filter of:

$$H_{dB}(w) = \cos 2\pi \frac{f}{f_B}, \quad |f| < .25f_B$$

$$= 0, \quad \text{elsewhere}$$

(2)

One way to perform the filtering is to do the full duobinary shaping at the transmitter, i.e., squeeze the spectrum of eq. (1) to give  $H_{\overline{\text{dB}}}(w)$  in eq. (2). This requires a transmit waveguide filter after the PA with the transfer function:

$$H_{T}(w) = \frac{2\pi(f/f_{B})}{\sin(2\pi f/f_{B})} \cos(2\pi f/f_{B}), \quad | f | < .25f_{B}$$

$$= 0, \quad \text{elsewhere}$$

(3)

The transmit filter in eq. (3) causes 3 dB of power loss just due to spectral truncation of the (sinx)/x spectrum out of the PA. In addition, there is power loss due to midband insertion loss of the filter. The sum of the 3 dB spectral loss and the insertion loss is a loss in link margin and reduces the efficiency of prime power consumption that can be critical in the satellite environment.

In addition, if the full duobinary shaping is done at the transmitter, the receive filter theoretically must have an ideal sharp cutoff at  $\pm$  .25  $f_B$  with a flat response across the band. Consequently, the effects, on performance and on adjacent channel interference rejection, of a more realistic receiver filter needs to be carefully considered.

Another approach to obtaining the duobinary shaping after the PA is to equally divide the filtering between the transmitter and the receiver. This leads to a transmit filter of,

$$H_{T}(w) = \frac{2\pi(f/f_{B})}{\sin(2\pi f/f_{B})} \left[\cos(2\pi f/f_{B})\right]^{1/2}, |f| < .25f_{B}$$

(4)

and a receive filter of:

$$H_{R}(w) = [\cos(2\pi f/f_{B})]^{1/2}$$

, | f | < .25f<sub>B</sub> (5)

With the transmit filter of eq. (4), 2 dB of spectral truncation loss occurs, plus the filter midband insertion loss.

If well-known duobinary precoding techniques are used and simple "slicer" receivers are used to receive the duobinary signal created at the receiver, 3 dB of theoretical performance loss occurs relative to QPSK occurs with full duobinary shaping at the transmitter (given one can build a reasonable approximation to the ideal sharp cutoff filter required at the receiver without much additional loss). The performance loss for the equal filter division case with the simple slicer receiver is 2.2 dB theoretical.

Making use of Viterbi algorithm demodulation concepts, it is possible to recoup most of the performance losses relative to QPSK (3 dB and 2.2 dB in the full and equal filter division cases, respectively). Such an approach would involve building two 100 MHz (= symbol rate) 2-state Viterbi processors (one for each of the quadrature detector outputs).

Table 1.1 shows the summarizing data concerning the performance of employing duobinary signaling to meet the SOW objectives. From the columns showing degradation in received signal-to-noise ratio (SNR) requirement relative to QPSK, the simpler slicer receivers do not provide the needed performance. This leaves the Viterbi receivers, which obtain the required performance, but require 100 Mb/s 2-state Viterbi demodulators on each of the quadrature detector outputs. The 100 Mb/s high rate may be a bit of an implementation problem, but the 2-state Viterbi demodulator is not conceptually complex.

Table 1.1 Duobinary Summary Data

| Duobinary<br>Filter<br>Division | S <sub>T</sub><br>Spectral<br>Truncation<br>Loss, dB | Filter<br>Insertion<br>Loss, dB | S <sub>T</sub> +L <sub>I</sub><br>Net Link<br>Margin<br>Loss, dB | RCVR<br>Type | Theory:<br>QPSK<br>Degrad.<br>Loss, dB |

|---------------------------------|------------------------------------------------------|---------------------------------|------------------------------------------------------------------|--------------|----------------------------------------|

| Full Xmit                       | 3                                                    | 1-2                             | 4-5                                                              | Viterbi      | -0                                     |

| Full Xmit                       | 3                                                    | 1-2                             | 4-5                                                              | Slicer       | -3                                     |

| Equal<br>Xmlt/RCVR              | 2                                                    | 1-2                             | 3-4                                                              | Viterbi      | -0                                     |

| Equal<br>Xmit/RCVR              | 2                                                    | 1-2                             | 3-4                                                              | Slicer       | -2.2                                   |

The desirability of this constant envelope QPSK through the PA followed by tight filtering reduces to consideration of the importance of these factors:

- 1. At best, 3 to 5 dB of link margin will be lost due to the transmit filters.

- 2. The modulator required is a 200 Mb/s QPSK modulator.

- 3. The demodulator is a 100 MHz symbol rate quadrature demodulator followed by 100 Mb/s 2-state decoders on each rail.

- 4. Additional filters are required at the downlink modulators.

Other such filtering techniques can be done, but based on link margin losses, these techniques do not meet the objectives of power efficiency and thus our efforts are directed to constant envelope modulation waveform signals.

Rased on this constant envelope decision, attention was then focused on those signaling schemes that modulate data unto the phase or frequency of a carrier. One of the more widely used forms of modulation is Phase Shift Keying (PSK). It's utility arises in power limited channels where binary PSK provides good Eb/No performance for a given bit error probability. However it's capability in bandlimited channels is remarkably poor because the first sidelobe, which peaks at 1.5 x bit rate, is only 13 dB down from the main lobe. In order to achieve the spectrum requirement of 20 dB down power outside of the .5 x bit rate point, an M-ary PSK scheme with M > 32 would be required. Assuming no intersymbol interference, signal power efficiency would drop some 18 dB from QPSK if M = 64. This power efficiency loss is deemed too severe, and thus eliminates PSK from further consideration. Attention was then turned toward Frequency Shift Keying (FSK) signaling schemes.

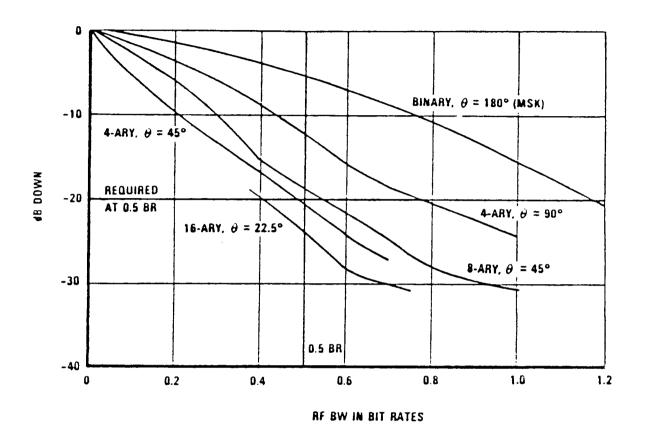

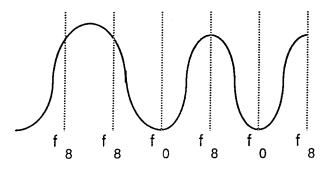

Conventional FSK signaling (conventional in that the tonal separation is equal to an integer multiple of the symbol rate) is by itself not a spectrally efficient modulation scheme. However, two modifications to the conventional FSK scheme can be made to minimize this inefficiency. The first is to reduce the tonal separation, or frequency deviation, thus compressing the spectrum and necessitating a coherent receiver. Secondly, instead of permitting phase jumps at the symbol transitions, phase may be forced to be continuous across the transition boundary. The latter modification produces what is well known to be continuous phase FSK, or CPFSK. A subset of this class of signaling schemes is MSK which is merely binary CPFSK with a frequency deviation ratio of .5. As seen in Figure 1.1-2 the only M-ary CPFSK schemes that have a chance of meeting the out-of-band requirements is one where M  $\geq$  16. Both 8-ary CPFSK and 4-ary CPFSK (otherwise known as

FIGURE 1.1-2 Spectral Characteristic of Uncoded CPESK

MSK/2) have out-of-band powers greater than the required 20 dB down from the desired signal power. Excluding intersymbol interference, the power efficiency loss relative to QPSK performance for 16-ary CPFSK is 13 dB. In comparison to PSK, CPFSK achieves the spectral requirement without filters but does so with a smaller power efficiency. Therefore, 16-ary CPFSK was chosen as the most likely signaling scheme capable of successfully meeting the QPSK performance when coding is added.

It is unfortunate that when forward error correcting coding is required in many systems, it is applied only as an afterthought by appending it to an already defined modulation format. For instance, the application of a rate 1/2 convolutional code, which is quite common, to an 8-ary FSK modulation format, seems congenial on the surface. However, each FSK symbol contains 3 coded bits thus making soft decision generation somewhat unhandy. On the other hand if a rate 1/3 code where used, the soft decision generation is now quite straight-forward, and if desired, more powerful symbol decoding could be performed in the decoder. This latter case is an example of a conscious marrying of a coding technique to a modulation format. Applying such a conscious effort to the bandlimited/power limited channel is an extremely high priority design focus. In fact we believe it is one of the most novel approaches toward consciously marrying modulation and coding in that we do not waste precious bandwidth to squeeze out tenths of dB's in performance. On the contrary, we use a moderate amount of coding (33% band spreading) but place it in that part of the modulation waveform where it is going to yield the greatest coding gain. This novel and Harris-patented (License rights owned by the Government) approach codes only the LSB's of a CPFSK symbol since errors are usually made to nearby signals in the signal space. Any coding to correct extremely low probability noise events (those

that cause errors in distant signals in the signal space) is a waste of bandwidth. An additional benefit of this coding technique is the hardware savings it provides by not requiring a decoder sync since symbol timing coincides with the decoder timing.

The coding technique which we developed on the 1979 RADC-sponsored Study [5] is almost identical to that investigated by researchers at the University of Virginia [6,7] in conjunction with M-PSK modulation on a study sponsored by NASA/LeRC. Unlike the MPSK schemes, however, our approach using coded 16-CPFSK modulation requires no additional spectrum shaping filters to achieve 2 bits/sec/Hz adjacent channel operation. In addition, the shaped spectrum signal of our coded 16-CPFSK modulation is of constant envelope, and thus avoids all nonlinear amplifier problems.

For the same number of coder states, the coded 16-PSK approach is theoretically 2 dB more power efficient than our coded 16-CPFSK approach solely on the basis of received SNR. However (and this is very important) the 16-PSK scheme will have to use post amplifier filtering to trim the (sinx)/x spectrum to meet the adjacent channel operability requirements of the SOW. If pre-amplifier filtering is proposed with the coded 16-PSK signal, the backoff required to prevent sidelobe restoration after the nonlinear PA will be excessive from a link power efficiency standpoint. Even with post amplifier filtering, the 2 dB theoretical advantage of the coded 16-PSK approach will be offset by the insertion loss of the required filter. We believe our constant envelope coded 16-CPFSK approach, in requiring no filtering, is the better approach from the overall link power efficiency and equipment simplicity standpoints and thus will be adopted as our baseline.

The final trade-off area to be discussed is the demodulator implementation. When using CPFSK it is possible to perform data detection

over multiple symbols because of the memory introduced into the waveform by forcing phase continuity during symbol transitions. While this multiple-symbol detection provides greater power efficiency [8], it carries along with it the necessity to perform a large number of matched filter correlations in a Viterbi-like, maximum-likelihood, sequence estimator algorithm [9]. For 16-ary CPFSK with a detection over just 2 symbols, 256 (16<sup>2</sup>) individual correlations would need to be performed. This is contrary to the objective of demodulator simplicity and furthermore it only gains about 2 dB at an uncoded error rate of 10%. Therefore we have chosen to perform a simpler multi-symbol observation phase detection. Now, once we made this decision we further discovered that we could use a simple, Harris proven [10] technique of phase sampling and thus eliminate the need for 16 separate matched filters. A negligible performance difference at low error rates further enhances this phase sampling technique over the matched filter approach.

Listed below is a summarization of what these major tradeoffs have produced:

- 1. 16-ary CPFSK is the least complex, bandwidth efficient modulation format capable of meeting the out-of-band power requirement.

- 2. Multiple symbol detection with a Viterbi-like, maximum likelihood sequence estimator is not warranted from a complexity viewpoint although it does slightly increase power efficiency.

- 3. Multi-symbol observation detection is performed with a simple, and Harris proven, phase detector technique.

- 4. A Harris patented, bandwidth efficient coding technique has been creatively matched with 16-ary CPFSK to provide coding gain where it is needed most.

#### 1.2 Rationale for the Scheme Selected

The selection of our approach was driven by key factors from both the SOW and the evaluation of system requirements for optimizing overall modulation technique performance. The key considerations in the selection of the signaling scheme are given below.

- 1. Constant envelope signaling provides maximum transmit TWT efficiency

- 2. Any filter at the satellite will dissipate power by spectral truncation and insertion losses, and will thus reduce link margin since the TWT is peak limited

- 3. Coding gain is necessary, but must be applied efficiently

- 4. Hardware simplicity is critical for cost effective implementations in the 1990's

Any combination amplitude and phase modulation scheme will require backoff of the TWT from its saturation point and will decrease the overall link efficiency. Therefore, the only parameters left for the modulation are the phase and/or frequency of the signal.

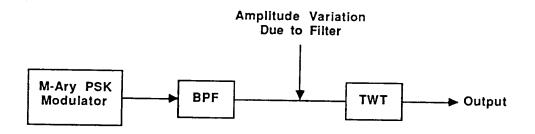

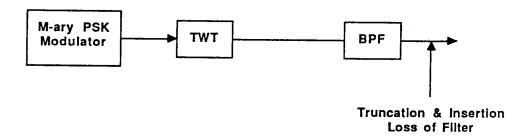

M-ary PSK has been considered by Harris and other researchers [6] for applications such as this. With proper coding, near-QPSK level performance can be attained. The difficulty with PSK is that the rapid changes in phase result in bandspreading of the energy which must then be filtered for adjacent channel performance. The energy loss of the required filtering process is directly applied to link margin and must be considered when evaluating the modulation scheme. To illustrate this consider Figure 1.2-1. In A the signal is filtered prior to the input to the TWT. However, the signal now has amplitude variation due to the filter and the TWT must operate in the linear region (i.e., backoff from saturation) which decreases the average power and efficiency of the satellite output. In B the input to

the TWT is a constant envelope signal; the filtering is accomplished at the output. The filter truncates the spectrum and dissipates the power from insertion losses. In either case  $\underline{A}$  or  $\underline{B}$ , the power transmitted from the satellite is reduced by several dB and the overall system link margin is decreased.

A. Filtering Prior to TWT

B. Filtering After TWT

Figure 1.2-1 Transmit Filtering

The bandwidth problem of PSK is solved by utilizing a CPFSK approach. As shown in Figure 1.1-2, the modulated spectrum is adequate for transmission with no filter and the only remaining selection is the size of the transmit alphabet for bandwidth compression. Additionally, a unique

constraint of the phase progression of the signal resulted in a powerful coding gain for system performance.

Knowledge of the good spectral properties of our proposed CPFSK signaling is, of course, not unique to Harris. Many efforts have been directed here and elsewhere at trying to improve the performance obtainable with CPFSK modulation. These efforts have involved attempts to shape the phase trajectories and an exploitation of the coding-like gains available with multisymbol observation optimum receivers. Multisymbol observation is available with CPFSK because of the continuity of RF phase in the transmitted waveform that makes the present time symbol depend on previously transmitted symbols. Impressive, tantalizing performances are obtained for some of the CPFSK schemes. Their only drawback is the complexity of the optimum Viterbi algorithm demodulators required to get at the performance.

The uniqueness of the Harris demodulation approach resides primarily in the way we have managed to sidestep the complexity of the optimum demodulator, yet still retain most of its performance. We have done this by developing a multisymbol observation phase detection receiver that is simple, yet obtains performance within 2 dB of the optimum multisymbol observation Viterbi type of demodulator. Our simple phase detector approach (see the Harris proprietary addendum) allows relatively narrowband filtering (1/2 bit rate EW) ahead of the phase detector, and needs no intersymbol interference corrector to obtain its impressive performance relative to the complicated optimum receiver. Thus our coherent phase detector technique exploits the coding-like gains inherently available in the CPFSK signaling format.

The way in which we apply coding with low (33%) bandspreading, yet still obtain impressive coding gain is another unique feature of our

approach. We developed this coding strategy on a 1979 study for RADC [5]. Essentially the same coding approach in connection with M-ary PSK modulation is proposed in 1982 [6] and 1984 [11] papers by researchers at the University of Virginia. Their work was at least in part sponsored by NASA/LeRC. We prefer our coded 16-CPFSK approach over a coded 16-PSK approach for reasons detailed in paragraph 1.1.

Conceptually, we believe our approach of overlaying coding on the spectrally compact CPFSK signal to improve its performance is a practically important and enlightened one. Unlike some other ongoing research efforts that attempt to circumvent the limitations of simple CPFSK through the choice of more complicated phase trajectories (multimod index, cosine shaping instead of linear shaping of the trajectories, partial response shaping on the trajectories, etc.), our approach simply lives with the distance structure inherent in standard CPFSK and then improves it with coding. From the implementation standpoint, we believe our approach is superior.

### 1.3 Detailed Description of the Modulation Scheme Developed

The technique for accomplishing the performance requirements of the SOW is a 'modulation scheme pioneered by Harris and known as Continuous Phase Frequency Shift Keying (CPFSK). The scheme is a refinement of the well-known Frequency Shift Keying (FSK). CPFSK is a modification of FSK which provides spectral efficiency by reducing the frequency deviation and constraining the phase to be continuous across symbol transition boundaries. At the beginning of a symbol, the transmitted frequency is chosen at the modulator to be 1 of 16 possible transmit frequencies (for 16-CPFSK). This resulting frequency is transmitted for the duration of the symbol and the process is repeated for

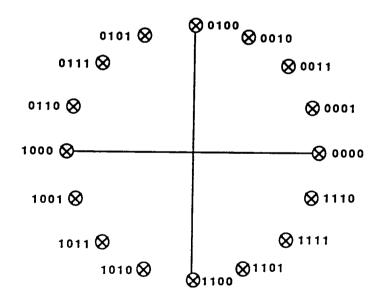

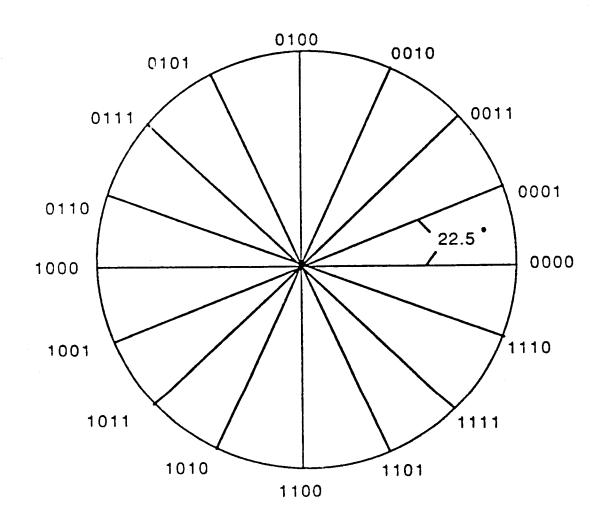

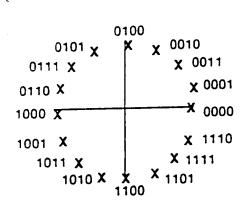

each symbol transmitted. Because of the memory induced into the waveform by forcing the phase continuity, a mapping function that relates the modulator four bit (1 of 16) input to the transmitted phase value at the end of a symbol time can be generated. By computing a running count on phase, the modulator can project what frequency must be transmitted to force the output phase to exactly hit the desired phase node (value) at the end of a symbol time. This frequency is then sent across the link and a demodulated phase constellation such as shown in Figure 1.3-1 is generated. This variation on the transmit frequency selection is transparent to the overall performance of 16-ary CPFSK but is the key to the application of coding for performance improvement.

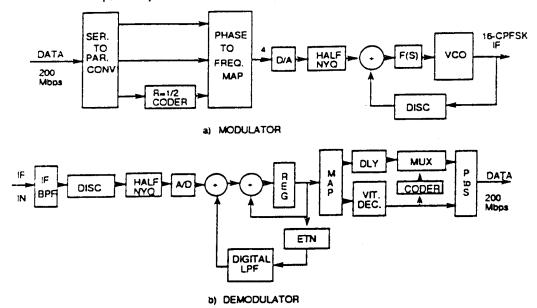

Figure 1.3-1 Demodulated Phase Constellation

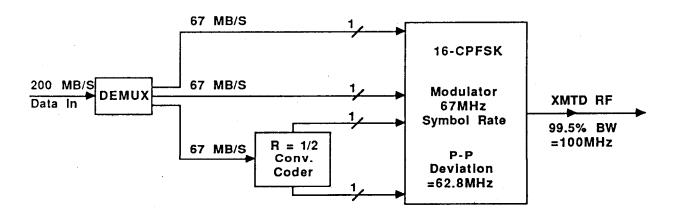

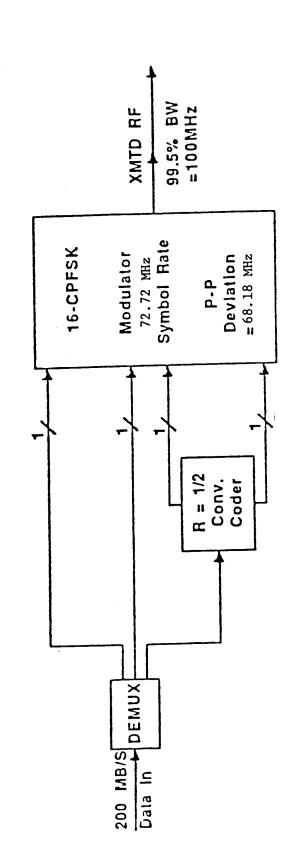

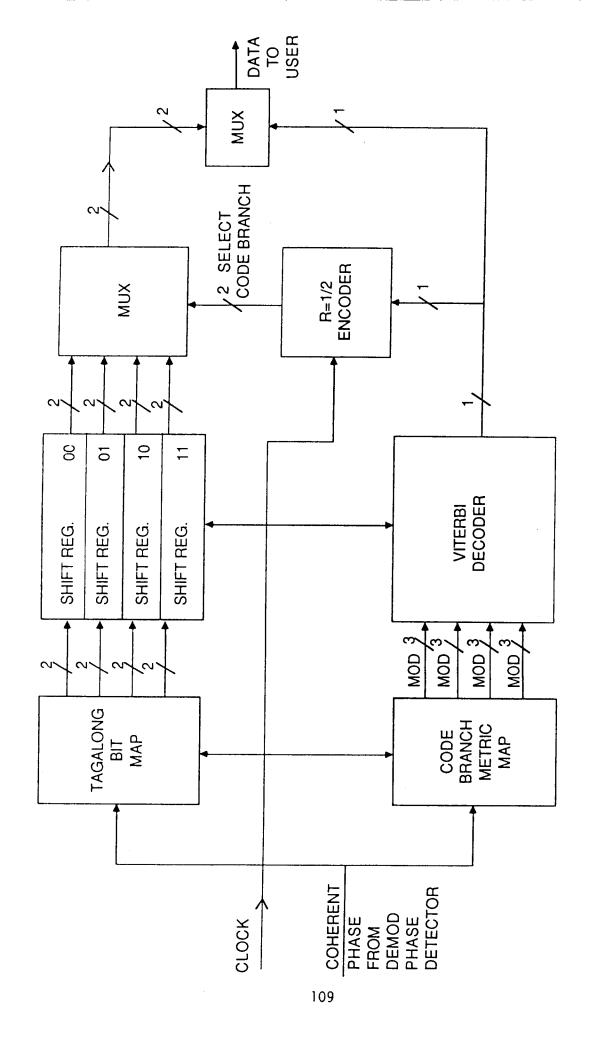

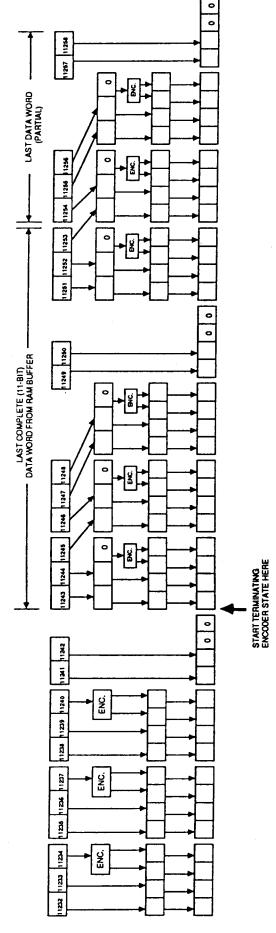

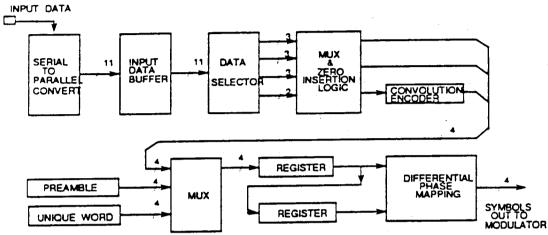

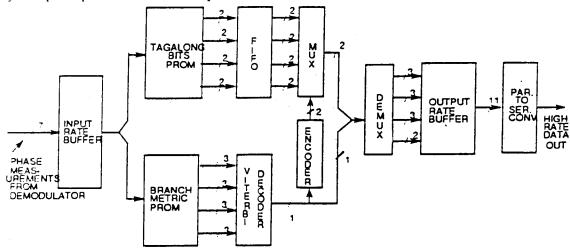

The input data stream is demultiplexed, in the modulator, into three data streams (see Figure 1.3-2) in which the Least Significant Bit (LSB) is convolutionally encoded R=1/2, K=7. The corresponding four bit output

determines the frequency that will be sent by computing the necessary frequency deviation to arrive at the desired phase node. From this, it can be seen that the two Most Significant Bits (MSB's) determine the quadrant of the transmitted phase (at the end of a symbol) and the LSB's determine the position within a quadrant. For the bit assignments shown in Figure 1.3-1, any group of 4 adjacent phases contain all possible combinations for the two bits from the coder (i.e., LSB's). Further, within the set of any four adjacent phases, antipodal code branches (e.g., 00 and 11, or 10 and 01) produce phases differing by 45° and orthogonal branches (e.g., 00 and 01, or 10 and 11) produce phases differing by at least 22.5°. These properties are used in the Harris approach to provide coding gain that results in near QPSK performance.

Figure 1.3-2 CPFSK Modulator

The spectral output power density versus bandwidth is shown in Figure 1.1-2 for 4-ary (also known as MSK/2), 8-ary, and 16-ary CPFSK. From the SOW, it can be derived that adjacent and co-channel interference requirements equate to a spectrum shaping requirement that the energy outside of the 0.5 bit rate bandwidth, be -20 dB relative to the total

signal power. As can be seen in Figure 1.1-2, 16-ary will provide the spectral shaping performance without transmit filtering. In addition, the 16-ary exceeds this requirement by a sufficient amount to allow 20-30% bandspreading to accommodate coding for overall system performance gain.

The combination of information coding in both the transmitted frequency and the phase state at the end of a symbol time, results in a signal that makes maximum use of the occupied system bandwidth. This unique spectral efficiency also supports maximum system power efficiency in two aspects. First, the resulting signal is constant envelope and thus the transmit TWT can be saturated for peak performance. Secondly, the transmit spectral shaping is inherent in the scheme and requires no filter which conserves power that would be lost in filtered spectrum truncation and insertion losses. This holds true whether the transmit filters are incorporated before or after the TWT since peak power available determines the link margin.

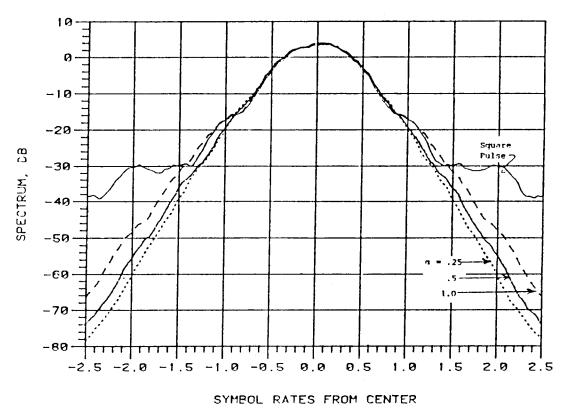

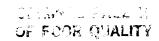

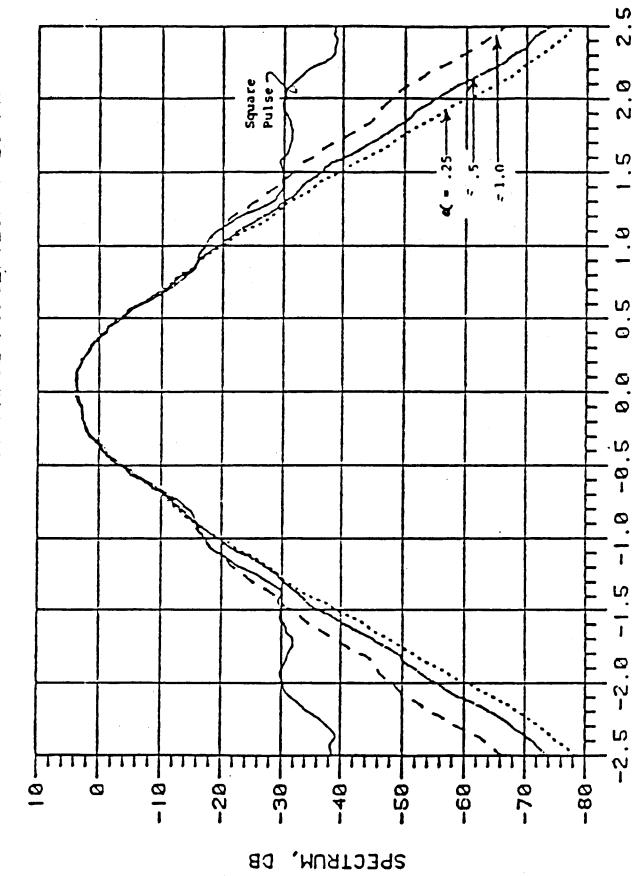

If baseband pulse shaping is incorporated into the modulator, further increases in spectral efficiency may be achieved at the modulator output without spectral filtering of the IF. In figure 1.3-3 we show the spectra produced at the modulator output for different choices of the modulator baseband pulse shaping filter. The curve for square pulses corresponds to standard 16-CPFSK signalling with 16 equispaced frequencies at a spacing of 1/16 of the symbol rate. The other curves are for various alphas on a square root of Nyquist filter with a raised cosine frequency characteristic. The far sidelobes are significantly reduced with the non-square pulse shaping baseband filters. The adjacent channel is located at 1.5 symbol rates from center (or .5 bit rate for our 3 information-bit/symbol scheme). We are contemplating the use of an  $\alpha = .25$  baseband filter to control adjacent channel interference.

Figure 1.3-3 16-ary CPFSK Modulation Spectra for Various Baseband Filters

1.4 A Description of the Method and Estimated Speed of Independent Burst Acquisitions

Here we will provide answers to the TDMA burst acquisition problems. The problems to be addressed are as follows:

- 1. How is the coherent phase detector circuitry jammed to the correct value at the beginning of a burst?

- 2. What are the effects of frequency offsets on the acquisition strategy?

- 3. How is the symbol timing derived for each burst?

- 4. How is the lmsec. TDMA frame timing derived?

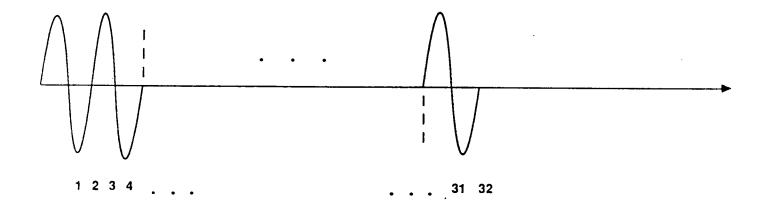

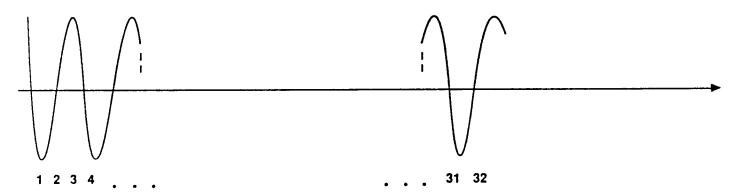

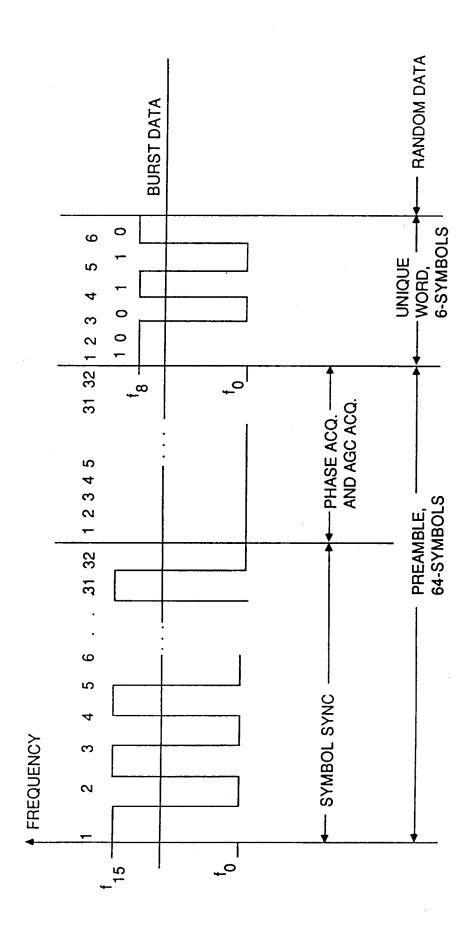

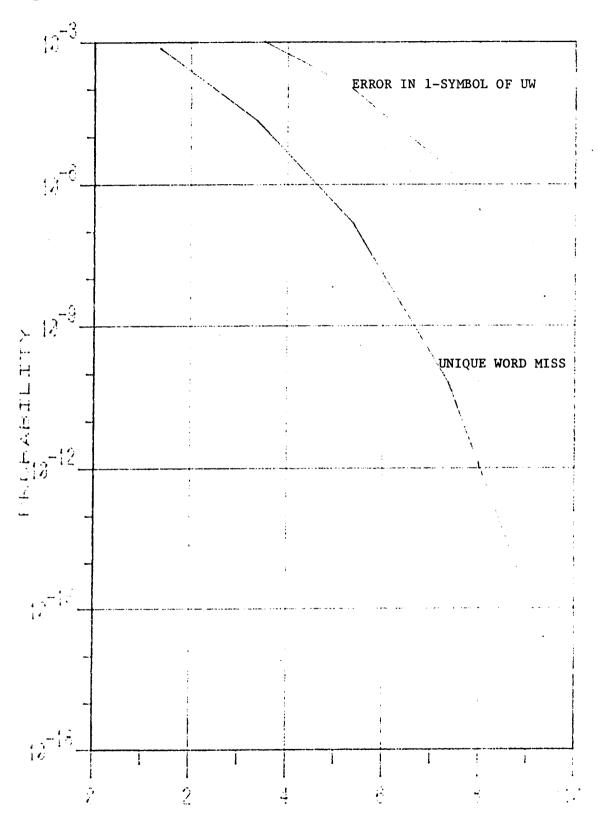

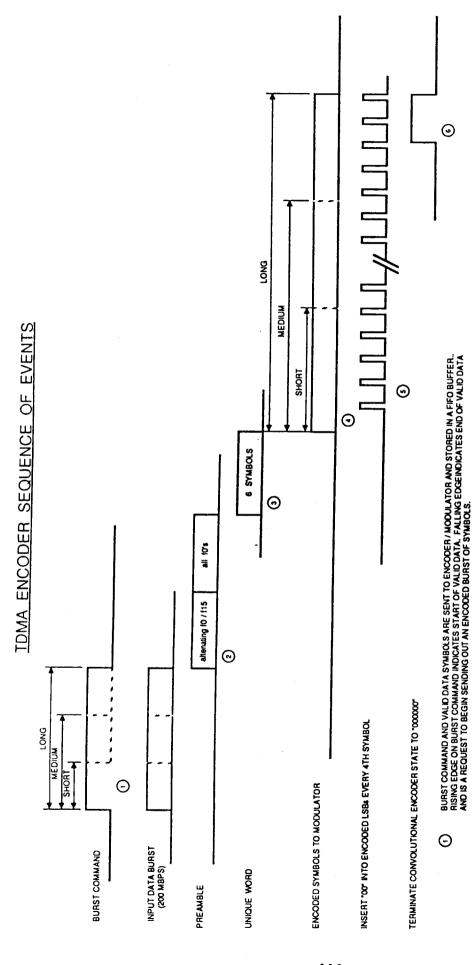

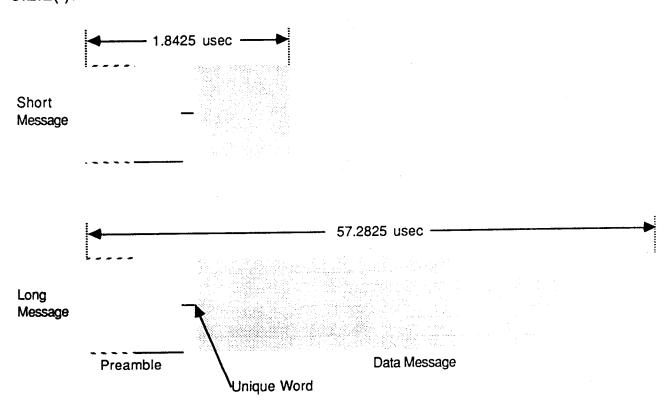

Figure 1.4-1 illustrates our concept of a single TDMA burst (a TDMA frame, which lasts 1 msec. in time, may consist of one or more bursts). As can be seen by Figure 1.4-1 a single TDMA burst consists of three components; a preamble (32 symbols = 96 bits), a unique word (6 symbols = 18 bits), and data ( $\geq$  32 symbols). The answers to the above questions all hinge on the special preamble we are considering to support all the timing functions.

| PREAMBLE   | UNIQUE WORD | DATA         |

|------------|-------------|--------------|

| 32 Symbols | 6 Symbols   | ≥ 32 Symbols |

| 96 Bits    | 18 Bits     | ≥ 96 Bits    |

Figure 1.4-1 A Single TDMA Burst

The preamble must provide for initial phase acquisition, and initial symbol timing. In the following paragraphs we will address the methods by which phase and timing are acquired.

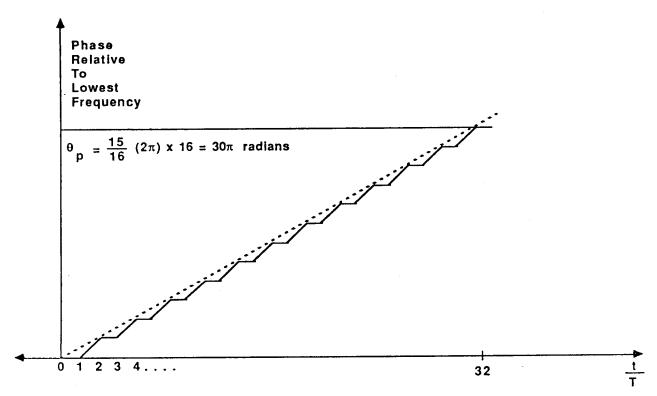

Figure 1.4-2 shows the phase modulation applied during the preamble we have selected. As shown, the preamble corresponds to an alternating frequency modulation between  $\pm$  peak deviation =  $\pm$  15/32 symbol rate. The dotted line shows the rise that will occur for the center frequency input with no frequency offset. We will simply sum the 32 samples of this phase error over the preamble and divide by 32 to get the average phase error relative to the lowest frequency reference.

Figure 1.4-2 Phase Modulation During Preamble

There remain questions about how well does this "phase jam" strategy work in the face of noise and initial frequency offset. First, how accurately can the initial phase be acquired in the face of channel noise? Since we are averaging 32 samples to arrive at an estimate of initial phase error, the variance of the phase jitter on the estimate is 1/32 of the variance on each of the individual phase measurements over the preamble. Thus the phase jam procedure will have only a small impact on overall performance, causing about  $10 \log_{10}(1 + 1/32) = .13$  dB degradation in noise performance. Secondly, what is the impact of initial IF frequency offset on the phase jam strategy? For a 30 GHz uplink, 10 GHz satellite translation, a 20 GHz downlink, and negligible doppler, assuming  $5 \times 10^{-7}$  L.O. stabilities everywhere, the initial frequency offset is:

$$F = (30 + 10 + 20) \times 10^9 \times 5 \times 10^{-7} = 30 \text{ kHz}.$$

The effect of this 30 kHz offset is to cause the preamble phase given by Figure 1.4-2 to ramp linearly up (or down, depending on the sign of the offset) over the 480 nsec. preamble, from zero to:

$$\Delta \theta = 30 \times 10^3 \times 480 \times 10^{-9} = .0144 \text{ cycle} = 5.2^{\circ}$$

Since the phase error increases linearly from 0 to 5.2°, the average of phase over the preamble is changed by 2.6°. This means that when peak frequency offset occurs, our phase jam is 2.6° in error. Whether or not this is of concern depends on which SNR at which we are operating. At 12 dB Eb/No, the SNR in the half-bit rate IF is 15 dB. The noise caused phase jitter on our signal at that point is:

$$\theta_{\rm S}^2 = \frac{1}{2({\rm SNR})} = \frac{1}{2(31.6)} = .0158 \text{ rad.}^2$$

or

$$\theta_s = 7.2^{\circ}$$

RMS.

Thus, 2.6° of error in the phase jam due to frequency offset is not negligible, but should be tolerable with no more than about .5 dB degradation before the baseband loop removes it, which for a 1 MHz loop bandwidth or more, takes less than lusec., or < 64 symbols.

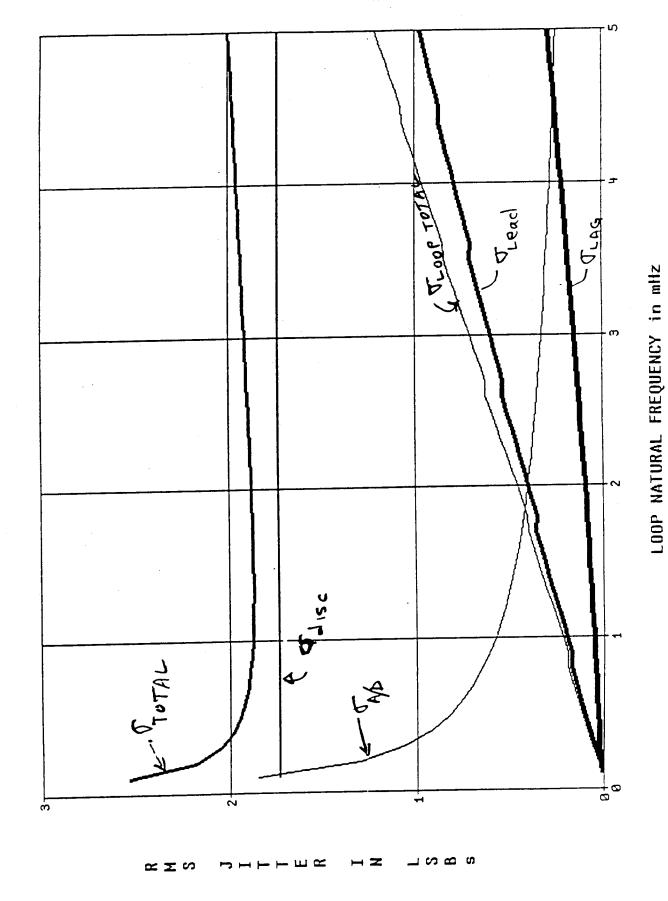

We have already described above a technique for acquiring initial phase for our loop during the special preamble. However, that technique does not acquire initial frequency offset, which is approximately 30 kHz. Therefore, the second order phase lock loop is left with the task of acquiring this 30 kHz frequency offset after the phase is jammed by the procedure described above. We will make use of Figure 1.4-3 to specify a loop bandwidth,  $F_{\rm N}$ , that will acquire the 30 kHz of frequency offset with little phase pull during such acquisition.

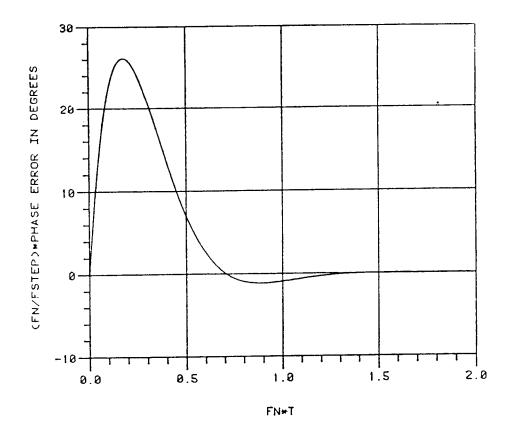

Figure 1.4-3 Transient Phase Error for a Frequency Step In Versus FN\*T for a Second Order PLL with Zeta = .707

As shown in Figure 1.4-3, the peak phase error induced by the offset,  $F_{\rm STEP}$ , in a  $\xi$  = .707, natural frequency =  $F_{\rm N}$  loop is described by:

$$\frac{F_{N}}{F_{CDED}} \theta_{e,pk} = 26^{O}$$

(6)

From eq. (6), it can be seen that the key to holding peak phase error,  $\theta_{e,pk}$ , to a small value is to choose  $F_N$  large relative to  $F_{STEP}$ . If we choose, during the acquisition of a 30 kHz frequency offset, to hold peak phase error to  $1^{\circ}$  (which will have a negligible impact on the performance of our modem), then  $F_N$  must be:

$$F_N = \frac{F_{STEP}}{\theta_{e,pk}} \times 26^O = \frac{30 \times 26}{1} \text{ kHz} = 780 \text{ kHz}$$

(7)

As a baseline, we will assume an  $F_N=1$  MHz. Of course, the wider the loop bandwidth, the larger the channel noise induced phase jitter. The noise bandwidth of a second order loop is given by:

$$B_{L} = \frac{W_{N}}{2} \left( \xi + \frac{1}{4 \xi} \right) = \frac{W_{N}}{2} \left( .707 + \frac{1}{4 (.707)} \right) = 3.33 F_{N}$$

where,  $F_{N}$  = natural frequency of the loop (Hz)

$\xi$  = loop damping factor

The loop signal-to-noise ratio SNR, is:

$$SNR_{L} = SNR_{if} \frac{BW_{if}}{B_{I}}$$

(8)

where, SNR<sub>if</sub> = IF signal-to-noise ratio

$BW_{if} = IF$  bandwidth

$B_{L} = loop$  equivalent noise bandwidth

In our system, for

$$BW_{if} = 0.5 \text{ x bit rate} = 100 \text{ MHz} & F_N = 1 \text{ MHz},$$

Then eq. (3) yeilds

$$SNR_{L} = SNR_{if} \left(\frac{100}{3.33}\right)$$

$$SNR_{L} = 30.0 \left(SNR_{if}\right)$$

(9)

The variance of phase jitter due to channel noise in the loop is,

$$\theta_{\rm L}^2 = 0.5/({\rm SNR_L}) \, ({\rm rad}^2),$$

(10)

and on the signal in the IF is,

$$\theta_{if}^2 = 0.5/SNR_{if} \quad (rad^2). \tag{11}$$

From eqs. (9), (10), and (11) one obtains

$$\left(\frac{\theta_{\rm L}^2}{\theta_{\rm if}^2}\right)^2 = \frac{1}{30.0} = .033$$

(12)

Equation (12) shows that for a 1 MHz loop, the reference loop jitter is negligible relative to the IF signal jitter. Performance loss with the loop jitter given by eq. (12) would be:

Loss = 10

$$\log_{10}[1 + (\frac{\theta_L^2}{\theta_{if}^2})^2]$$

= 10  $\log_{10}(1.033)$

Loss = .14 dB

From this analysis, we have concluded that a loop bandwidth of approximately one (1) MHz should be considered. Since we contemplate a digital loop filter implementation, loop filter bandwidth changes will be easy to experiment with.

Now we will describe the method whereby symbol timing is derived for the independent burst transmissions. The symbol timing function must be performed by observing the preamble and must provide around 1% of symbol time setting accuracy at the end of the preamble time.

The frequency modulation applied during the preamble, as shown in Figure 1.4-4 (a), alternates between + peak deviation and - peak deviation. The peak deviation is (15/32) SR, where SR is the symbol rate. We propose here a scheme that observes the frequency detector output during the preamble time with a correlator (probably a surface acoustic wave device) with an impulse response equivalent to that shown in Figure 1.4-4 (b). The frequency response of this correlator is passband centered around half symbol rate = 33.33 MHz with noise bandwidth of (symbol rate)/32 = 2.08 MHz.

(a) Frequency Modulation During the Preamble

(b) Correlator Impulse Response

Figure 1.4-4 Symbol Timing Waveforms

The noise out of the frequency measuring circuit has a parabolic spectral density given by:

$$N(f) = \frac{(f)^2}{2(SNR_{if})BW_{if}}$$

(13)

The spectral density at the center frequency (half symbol rate) of the correlator is, therefore:

$$N(SR/2) = \frac{(SR)^2}{8(SNR_{if})BW_{if}}$$

(14)

The noise over the 2.08 MHz noise bandwidth of the correlator is, for all practical purposes, constant at the density given by eq. (14). Therefore, the noise power out of the correlator is:

$$N_{C} = \frac{(SR)^{2}(2.08 \text{ MHz})}{8(SNR_{if})BW_{if}}$$

(15)

Since for our system,  $BW_{if} = 100 \text{ MHz}$ , we have from (15):

$$N_{C} = \frac{(SR)^{2}(2.08)}{8(SNR_{if})(100)} = \frac{.0026(SR)^{2}}{SNR_{if}}$$

(16)

The SR/2 clock signal has peak deviation = (15/32) SR or signal power out of the correlator when the preamble fills it, of:

$$S_C = (\frac{15}{32} SR)^2 / 2$$

(17)

From eqs. (16) and (17) we obtain a correlator signal-to-noise ratio (SNR $_{C}$ ), of:

$$SNR_{C} = \frac{S_{C}}{N_{C}} = \frac{(15/32)^{2}/2}{.0026} (SNR_{if}) = 42.3(SNR_{if})$$

(18)

The jitter on the SR/2 clock has variance

$$\theta_{j}^{2} = \frac{1}{2(SNR_{c})} = \frac{1}{84.5(SNR_{if})}$$

(19)

and for Eb/No = 12 dB, SNR<sub>if</sub> = 15 dB in our half bit rate IF. Since 15 dB = power ratio of 31.6, eq. (19) yeilds:

$$\theta_{j}^{2} = \frac{1}{84.5(31.6)} = .00037$$

or

$$\theta_{j} = .019$$

radians (20)

Since pi radians of the SR/2 clock represents one symbol time, T, from eq. (20) we may obtain the RMS timing jitter from the correlator as

$$t_{j} = \frac{\theta_{j}}{\pi} T = \frac{.019}{\pi} T = .62% (T)$$

Thus we meet out objective of better than 1% of T capability of jamming symbol timing phase at the end of the preamble.

This symbol timing strategy is not affected by DC offsets out of the frequency measuring circuit (since the correlator has no DC response). This procedure is also unaffected by AGC error. Thus the symbol timing is unaffected by either of the other two burst acquisition problems. Once the initial symbol timing phase is acquired, we will track it with a narrow band loop, observing the output of the frequency measuring device during the duration of the burst.

The following discussion will detail the sequence of events in acquiring access to the TDMA satellite network.

Our assumption is that the TDMA network is active when a new station desires entry onto the network. The TDMA channel has a master control station (MCT) burst interleaved with some number of other bursts from ground stations which have already gained entry on the network. Since the new station cannot even request service of the network until it acquires the MCT burst, a crucial task is to acquire the MCT burst.

As given above, the preamble correlator detects each preamble of a burst as it arrives. Upon burst detection, the 66.7 MHz symbol timing loop is jammed to the phase indicated by the next zero crossing after burst detect from the preamble correlator. After jamming the symbol phase, the loop develops a tracking signal as detailed in a previous discussion. The modem timing and control function now distributes symbol clock and timing signals required to sample the preamble-length delayed signal as well as direct the digital loop to perform burst acquisition and tracking functions as described previously. The coherent phase measurements made, within a burst interval but after the preamble, are delivered to the K=7 Viterbi decoder which performs the decoding of data as described in our proposal. By scanning the decoder output bit stream, we can detect the MCT unique word,

thereby providing our modem with the synchronized TDMA downlink 1 msec. frame timing. At this point, after no more than one (1) frame of TDMA reception, we will know all necessary information to gain access to the TDMA network.

For a fully operational TDMA satellite system, we have described the conceptual capability for our modem to perform all necessary acquisition and network synchronization functions. We have shown adequate capability to perform the following functions for independent bursts in the TDMA downlink:

- 1. Burst Detection

- 2. Symbol Timing Acquisition

- 3. Symbol Timing Tracking

- 4. Coherent Phase Acquisition

- 5. Coherent Phase Tracking

- 6. MCT Synchronization to allow synchronization of our uplink bursts into the uplink TDMA format

On the proof-of-concept (POC) modem, all functions except number 6. will be provided. Indeed, we cannot do 6. since that implies knowledge of network access protocols which are still under development.

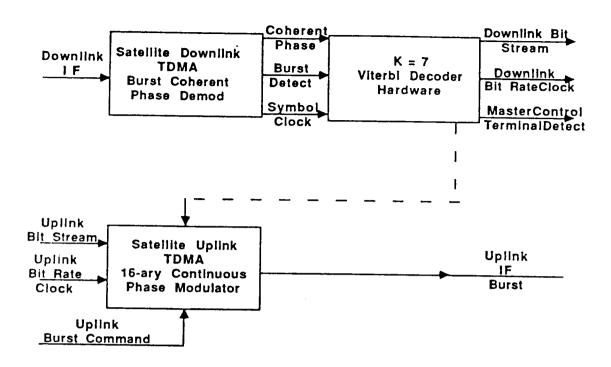

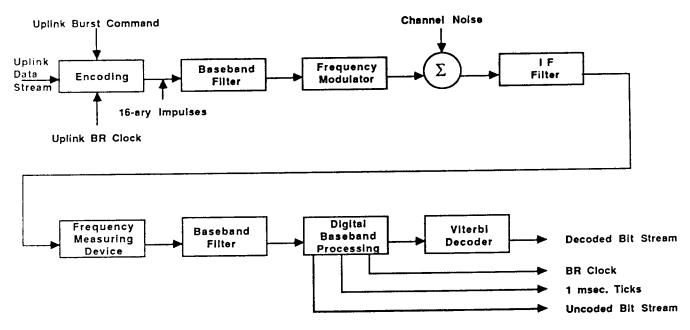

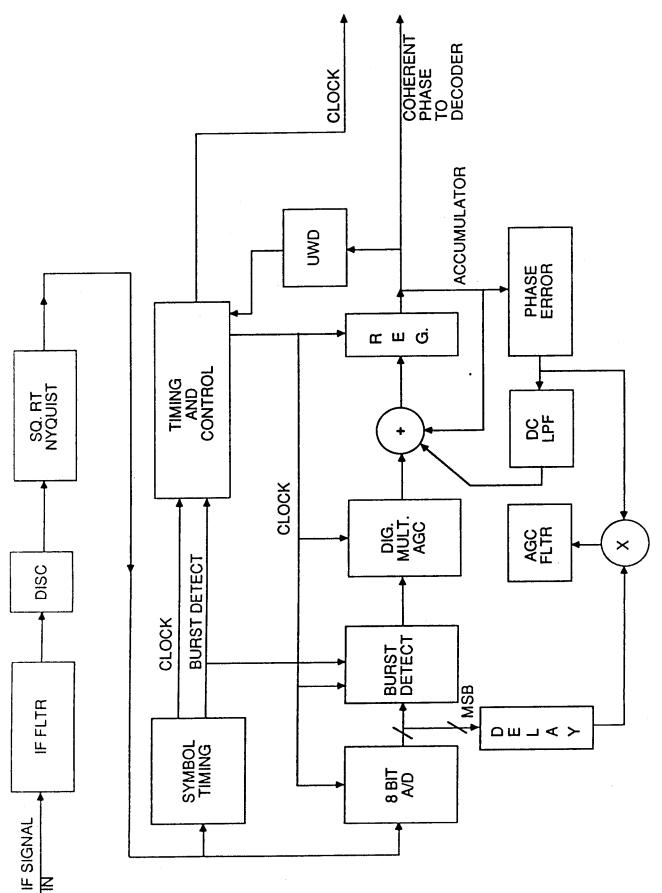

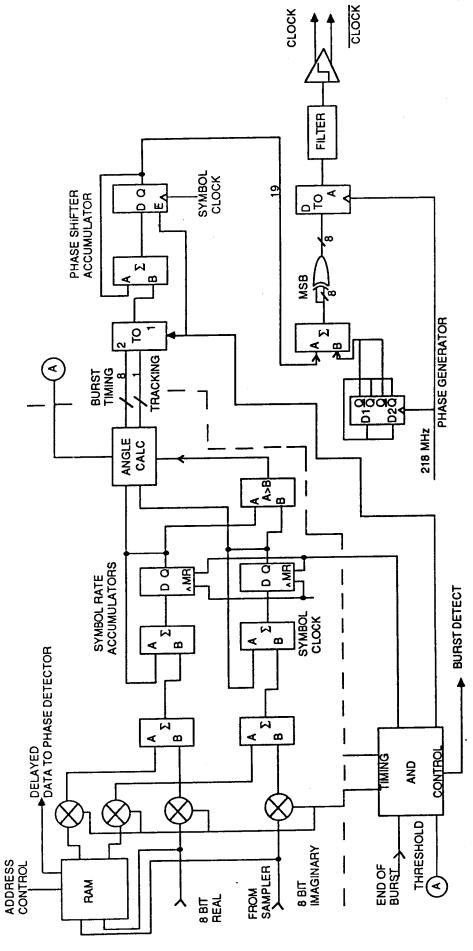

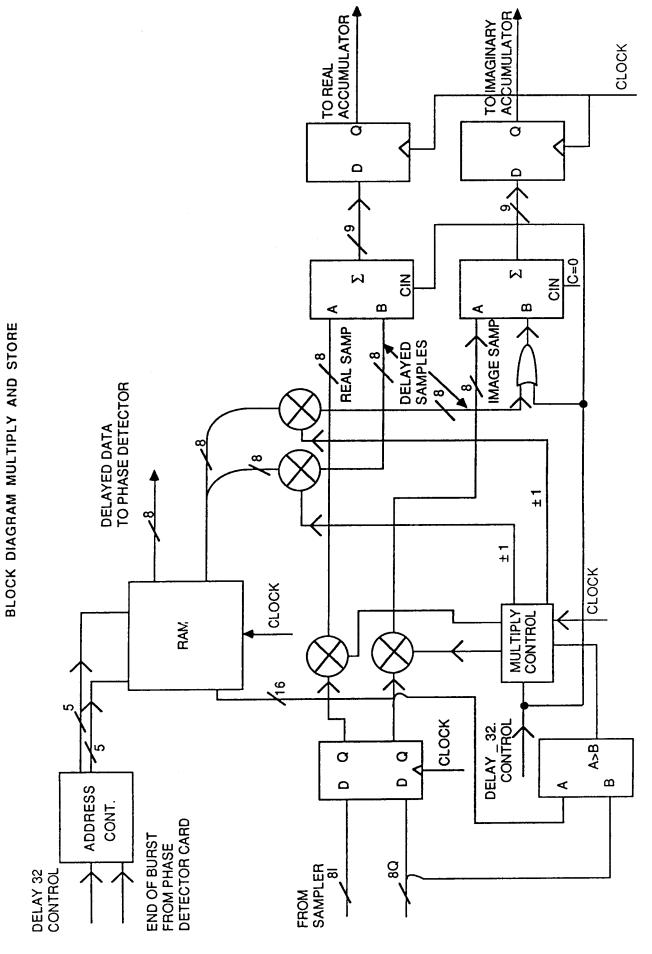

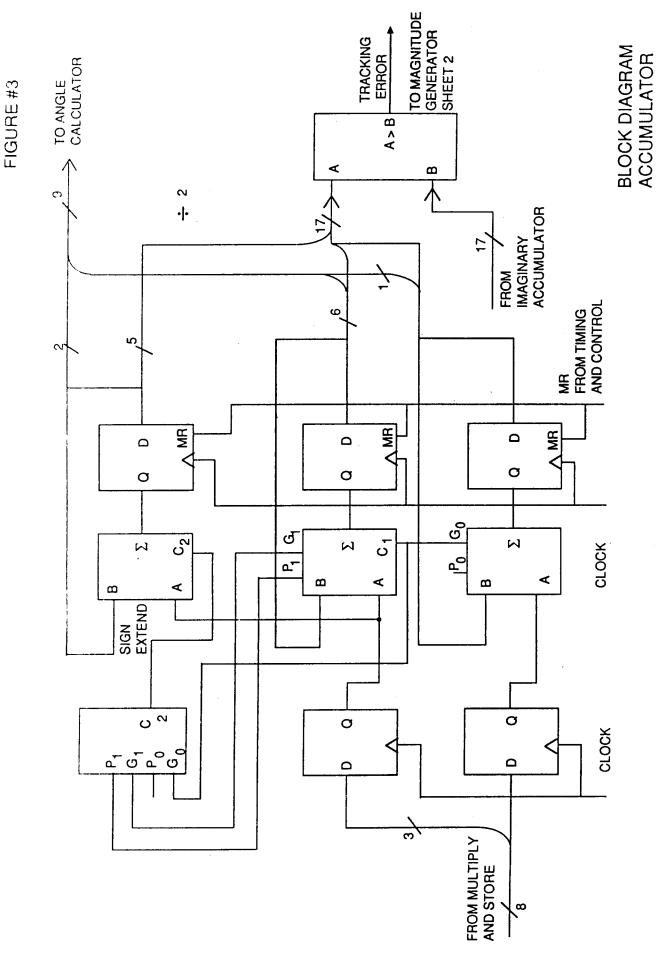

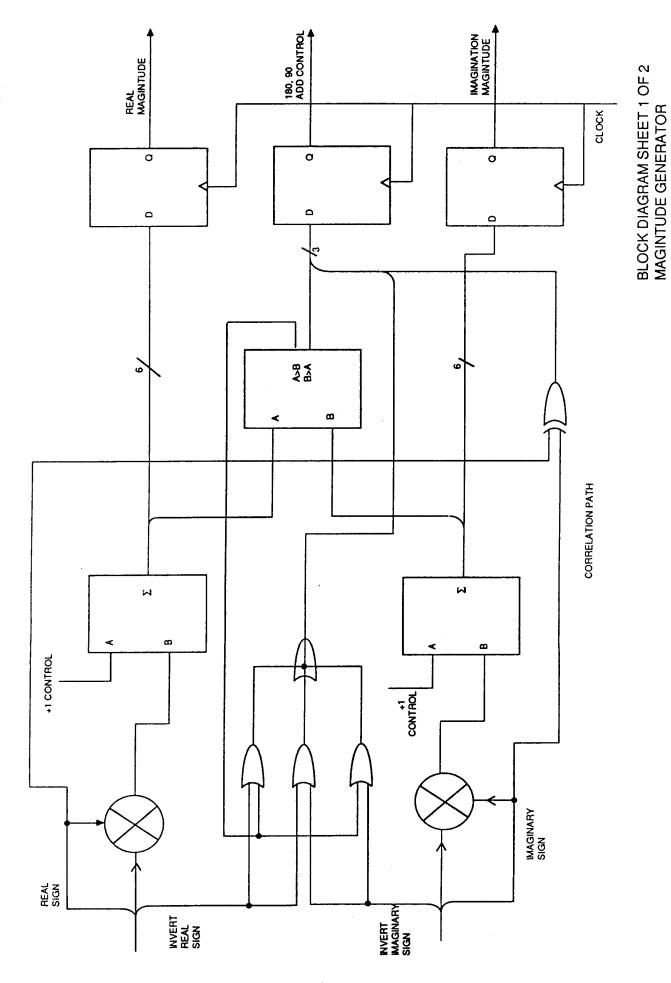

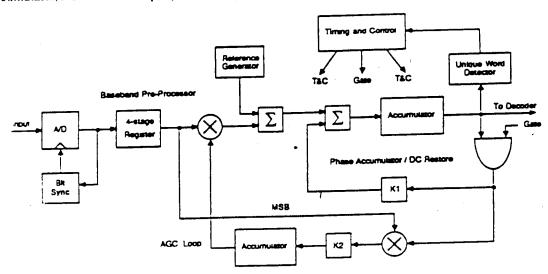

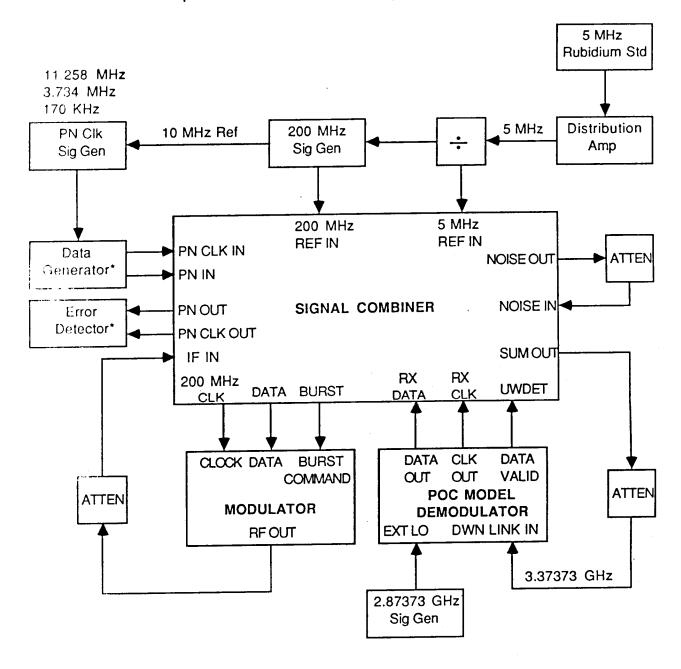

However, we will provide a modem that can interface with equipment implementing any network access assignment and control protocols. Figure 1.4-5 shows the overall block diagram for our POC modem along with its inputs and outputs which will interface with the evaluation test beds at NASA/LeRC.

Figure 1.4-5 Overall Satellite TDMA Modem Block Diagram

The dotted line for the MCT detect pulse, which is necessary in an operational modem for timing and control circuitry in the modulator to synchronize uplink bursts into the satellite, will not be provided. Rather, as we understand it, the test bed will perform that function. The test bed is assumed to provide the signal "Uplink Burst Command" to trigger transmission of an uplink burst. Other inputs to the uplink modulator from the test bed include uplink bit stream and uplink bit clock. The uplink IF signal is output from the modulator to the test bed.

On the demodulator side, downlink IF is provided from the test bed to the demodulator. Coherent phase measurements along with burst detect and symbol clock signals are provided to our K=7 Viterbi error correction decoder per our proposal. Outputs from our demodulator to the test bed are thus; downlink bit stream, downlink bit rate clock, and MCT detect.

Therefore, the test bed at NASA/LeRC can use this modem for evaluation purposes, implementing any desired TDMA network access, assignment, and control protocols.

# 2. CONCEPTUAL DESIGN OF THE DOWNLINK MODULATION HARDWARE

In this section of the task one report the conceptual design of the demodulator hardware is presented along with simulation results. Some of the detailed hardware configurations are considered to be Harris proprietary and therefore, the reader will be referred to the proprietary addendum when appropriate. In addition to the topics given above, this section of the report will also discuss issues pertaining to producibility, reliability, maintainability, recurring costs, and special test equipment.

# 2.1 Downlink Modulation System Conceptual Design

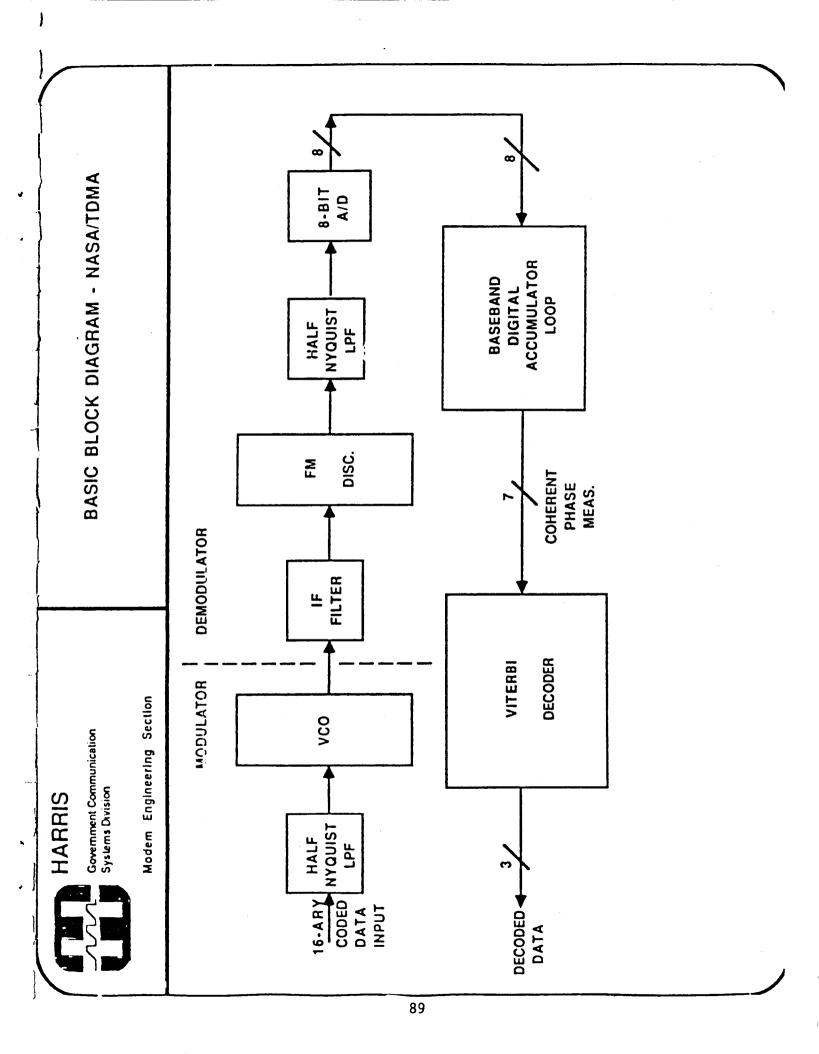

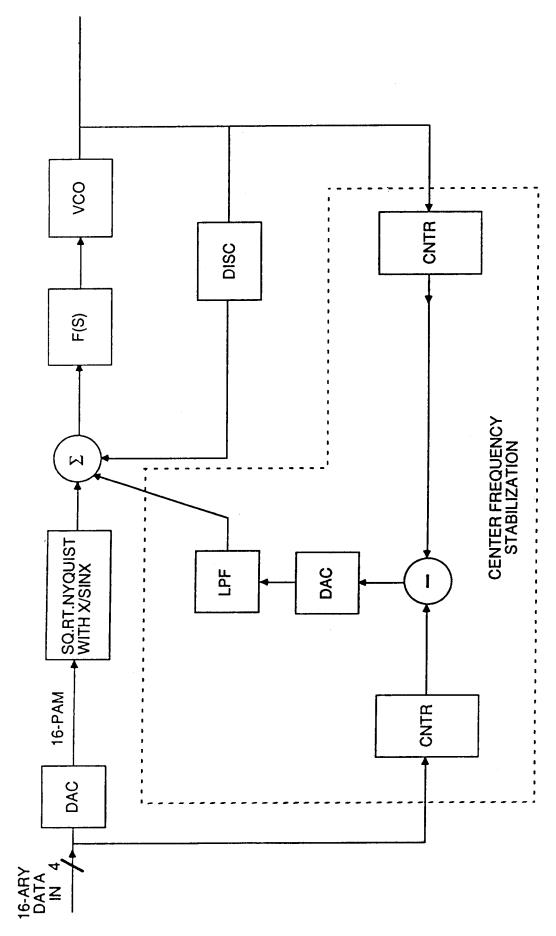

the requirements for the NASA/TDMA satellite downlink. The coded 16-CPFSK signal was to be demodulated by a coherent phase measurement receiver using a phase-locked loop (PLL) IF implementation. During our task one investigations, we have still been considering the conceptually equivalent modulation and demodulation technique, i.e. a 16-ary continuous phase frequency shift keying modulator coupled with coherent phase measurement demodulation. However, our present baseline implementation approach is quite different. Also, there are some detail differences between our present approach and the proposed approach; primarily in the area of baseband waveshaping filters at the modulator and demodulator (see Figure 1.3-3). These detail differences have some advantage over our proposed approach and are available only because of our present implementation approach.

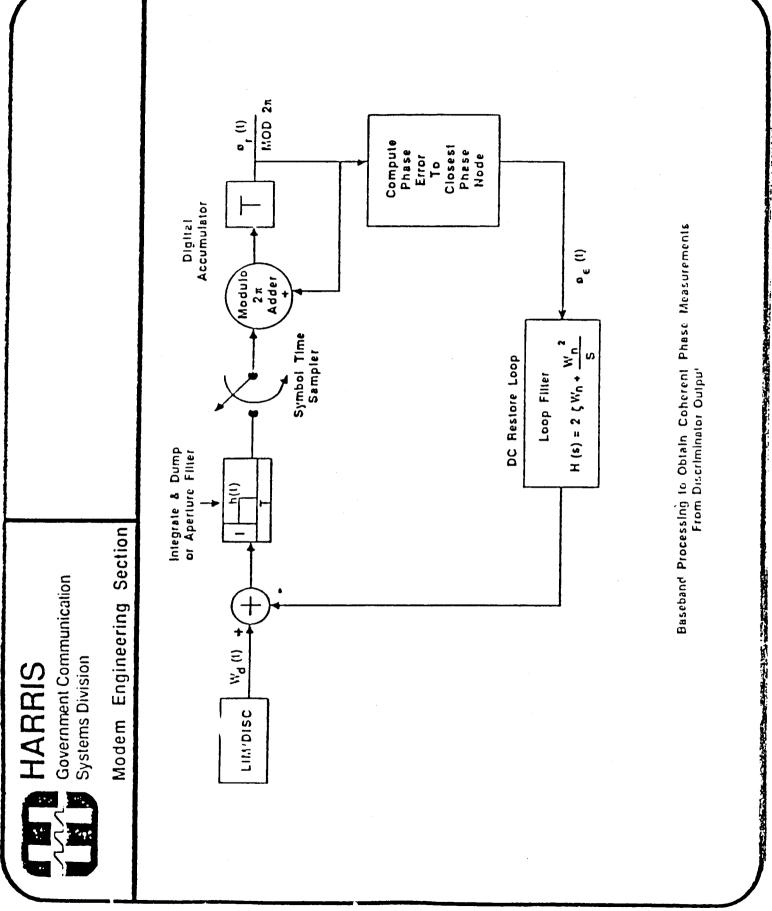

The most significant difference between our proposed implementation approach and our current baseline approach, lies in our implementation of coherent phase detection at the demodulator. Our current baseline uses a Harris-proprietary technique for coherent phase detection. Reasons for considering this approach include; (1) hardware simplification, (2) single rail processing as opposed to in-phase and quadrature (I & Q) dual-rail processing required in the proposed approach, (3) one high speed (67 Msample/sec.) A/D is required, (4) the coherent phase measurement is available directly from the single rail with no necessity for conversion from I and Q rail samples to phase as in our proposed quadrature demodulator, (5) baseband filter techniques at the demodulator, not available with the proposed approach, are applicable to the current approach, and (6) requirement for a 3 GHz IF PLL is eliminated by using our current baseline approach.

We believe that our current baseline approach offers the potential for significantly reduced hardware complexity relative to our proposed approach. We also believe that this technology is unique to Harris (We have never seen in the technical literature that our current baseline approach to obtaining coherent phase measurements is known elsewhere, and thus the need for the Harris proprietary addendum). By achieving our goals on this contract, this modem will represent a significant advance in modem technology.

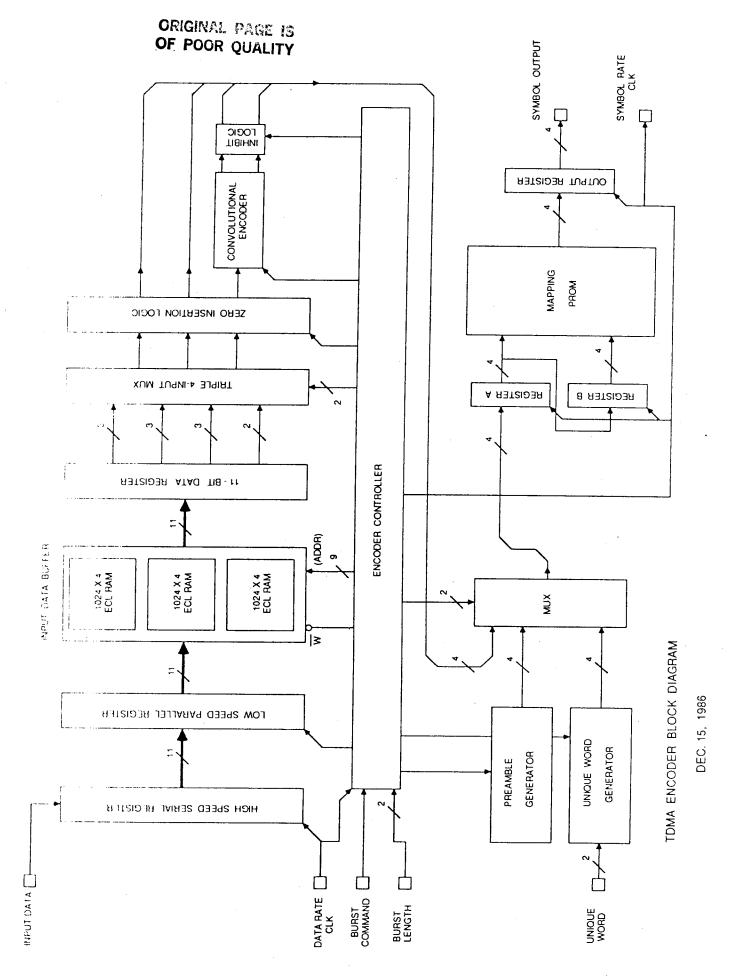

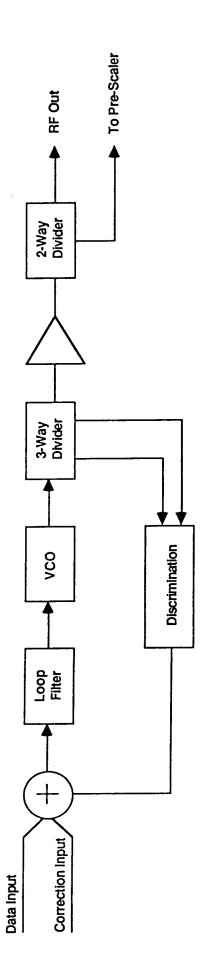

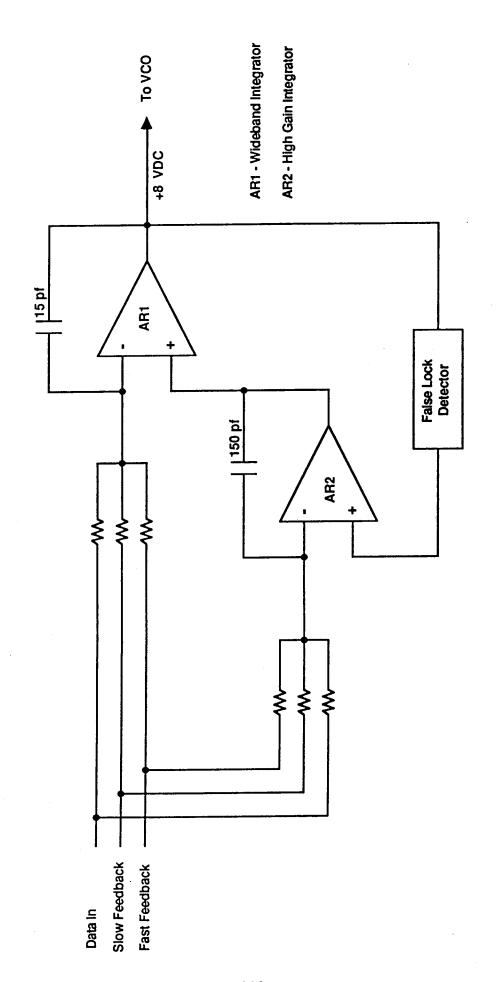

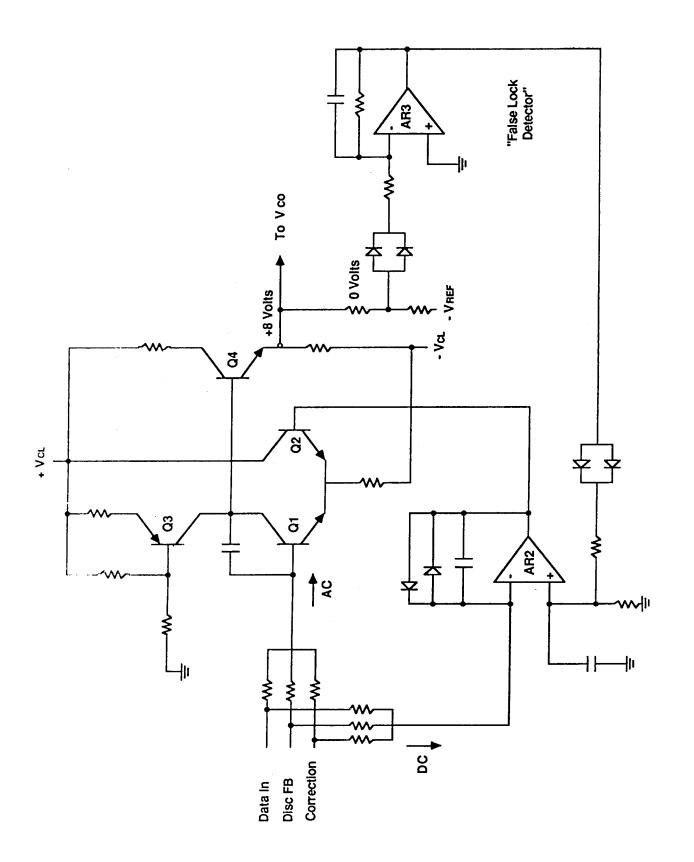

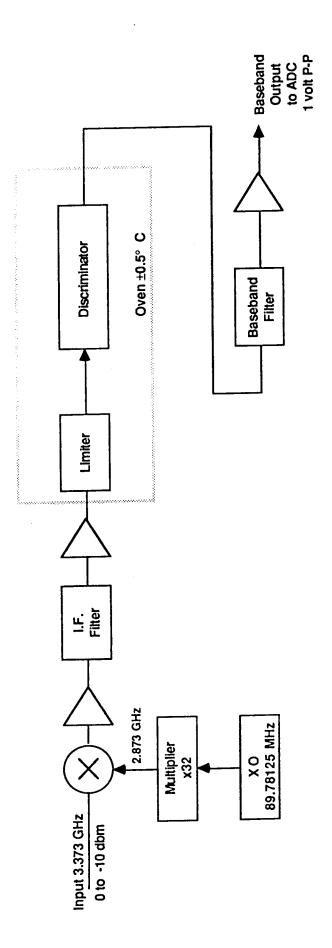

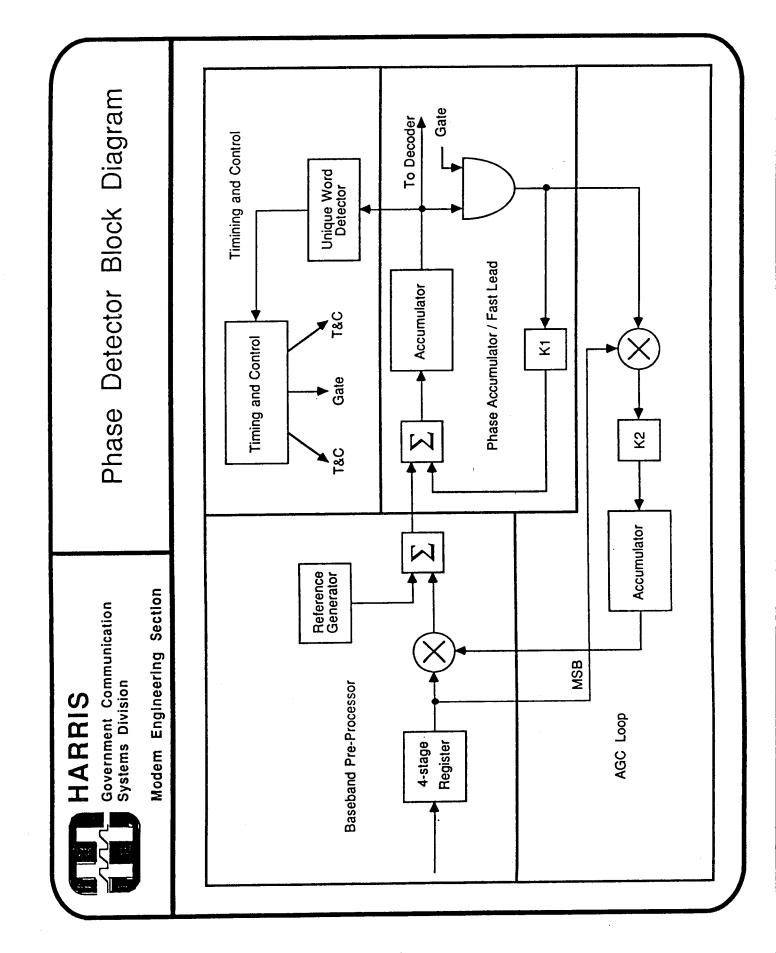

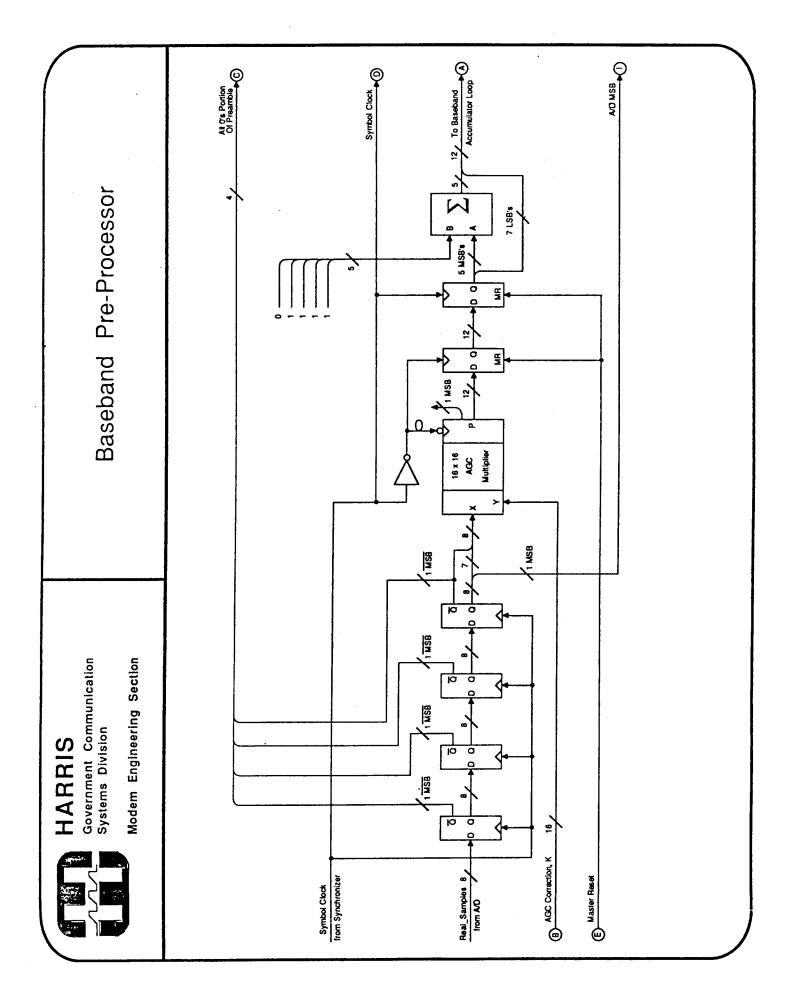

Since our current baseline modem involves a departure from prior coherent phase measurement receivers, it is necessary to give a clear conceptual picture of our technique. Figure 2.1-1 illustrates our current baseline conceptual hardware design. The input to the modulator is a data stream, a bit rate clock, and a burst command. The output from the demodulator is a demodulated data stream, a bit rate clock, and lmsec.

network access, assignment, or control protocols. The mathematical derivations of how we obtain coherent phase measurements from our current baseline approach, equivalent to an I and Q demodulator, is given in the proprietary addendum. Detailed block diagrams of the modem signal processing functions are also given in the proprietary addendum.

Figure 2.1-1 Current Baseline Conceptual Modem Hardware Block Diagram

2.2 Theoretical Performance Characteristics and Operating Conditions of the Downlink Modulation System Design Concept

In this section we present results obtained by computer simulations for the TDMA modem we have described conceptually in prior sections. These simulations were undertaken to evaluate the impact of several practical imperfections on our baseline modem. Some of these practical imperfections are not easily evaluated analytically, so the simulation results are necessary and valuable in assessing whether our unique coherent phase-measurement implementation technique leads to viable hardware.

Some of the effects we have investigated include; (1) the intersymbol interference caused by the bandlimiting IF filter, (2) effect of the A/D quantizing error in our baseband signal processing, (3) VCO modulation nonlinearity, (4) filter group delay distortion, and (5) the effect on performance of symbol timing offset.

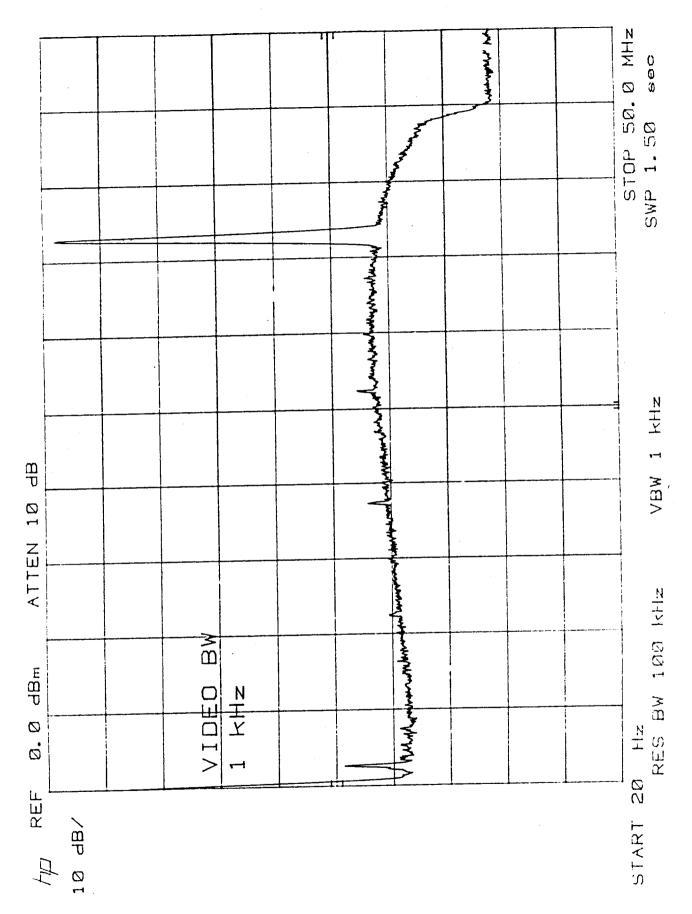

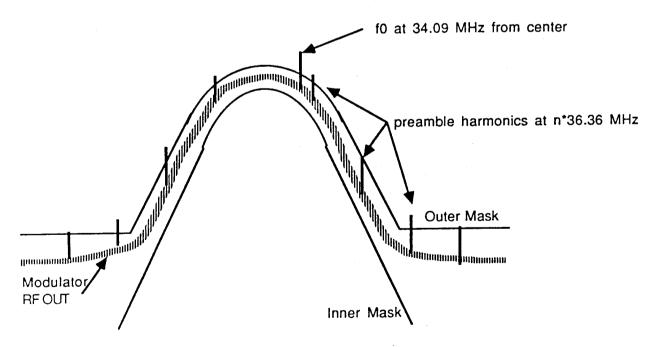

# 2.2.1 Bandwidth Efficiency

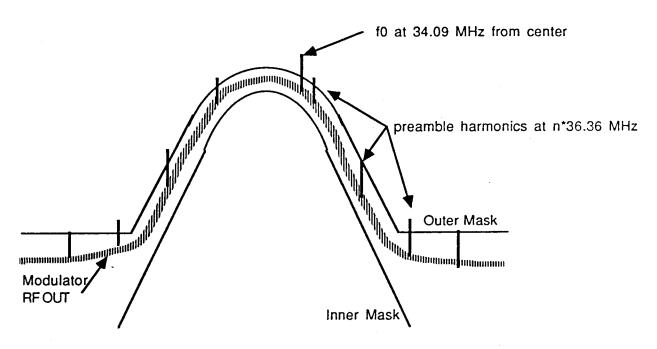

In Figure 2.2.1-1 we show the spectra produced by our modem for different choices of the modulator baseband filter. The curve for square pulse signalling corresponds to standard 16-CPFSK signalling using 16 equispaced frequencies with spacing = 1/16 symbol rate. The other curves are for various alphas on a square root Nyquist filter with raised cosine frequency transfer characteristics. The far sidelobes are significantly reduced with non-square baseband filters. The adjacent channel is located at 1.5 symbol rates from center (or .5 bit rate for our 3 information bit/symbol scheme). We are contemplating the use of an alpha = .25 baseband filter to control adjacent channel interference.

Figure 2.2.1-1 16-ary Continuous Phase FSK Modulation Spectra

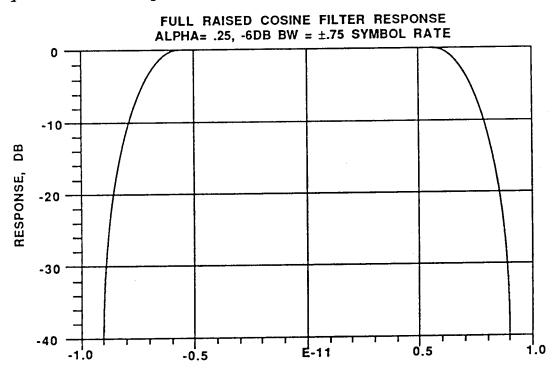

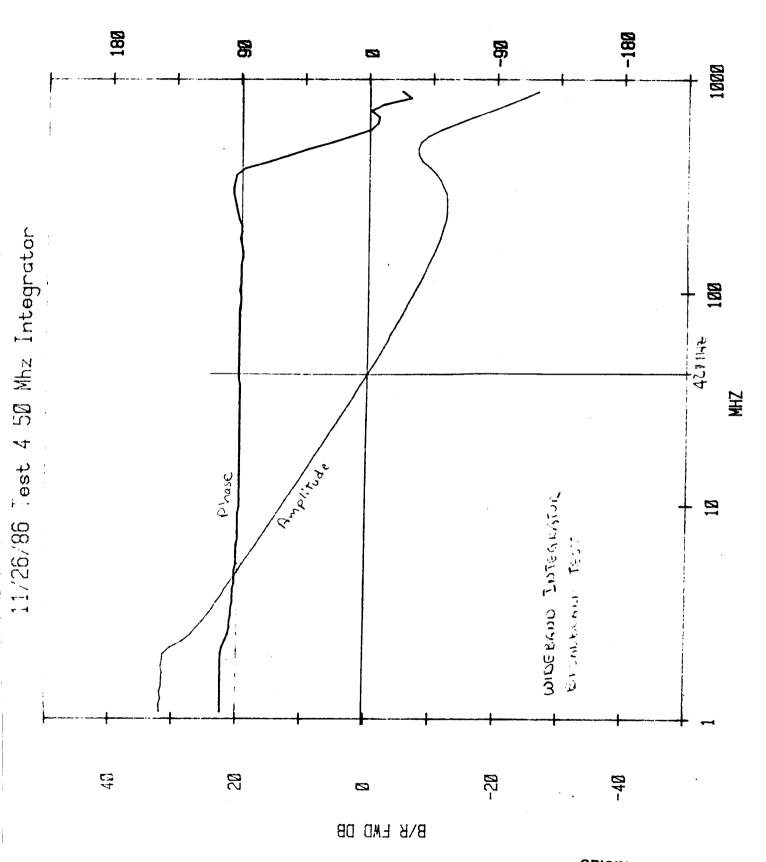

Figure 2.2.1-2 shows the IF filter characteristic we are using. This filter has a -6 dB BW = 1.5 symbol rate = .5 bit rate = 100 MHz. We are currently investigating an implementation approach that will allow the use of a SAW device for the IF filter. Such SAW filters have desirable low group delay distortion, coupled with steep skirt selectivity.

SYMBOL RATES FROM CARRIER FREQUENCY

Figure 2.2.1-2 IF Filter Characteristics

## 2.2.2 Power Efficiency

Any filter at the satellite will dissipate power by spectral truncation and insertion losses, and will thus reduce link margin since the TWT is peak limited. Since our modulation scheme is constant envelope, the TWT may be operated at peak efficiency (saturation). In addition, our modulation scheme, as previously described, requires no transmit filtering and thus there are no spectral truncation or insertion losses at the satellite. For the same number of coder states, the coded 16-PSK approach is theoretically

2 dB more power efficient than our coded 16-CPFSK approach solely on the basis of received signal-to-noise ratio. However, the 16-PSK scheme will have to use post amplifier filtering to trim the (sinx)/x spectrum to meet adjacent channel operability requirements of the SOW. IF pre-amplifier filtering is used with the 16-PSK signal, the backoff required to prevent sidelobe restoration after the nonlinear PA will be excessive. If post amplifier filtering is used, the 2 dB theoretical advantage of the coded 16-PSK approach is offset by the insertion loss of the required filter. Therefore, we believe our constant envelope coded 16-CPFSK approach, in requiring no filtering makes highly efficient use of overall link power.

# 2.2.3 Bit Error Rate Performance

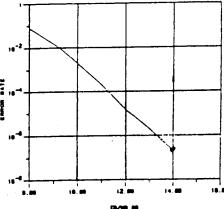

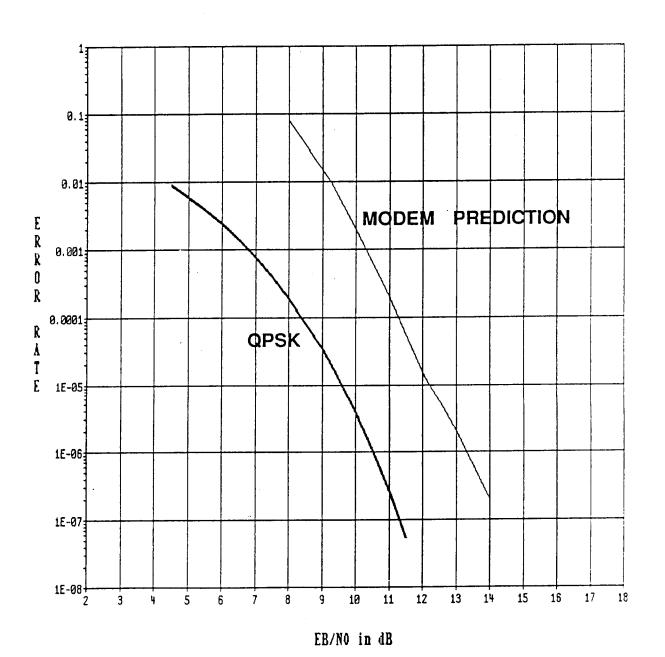

In this section of the report, bit error rate versus Eb/No will be given to illustrate the practical effects of various hardware elements, for both coded and uncoded operation.

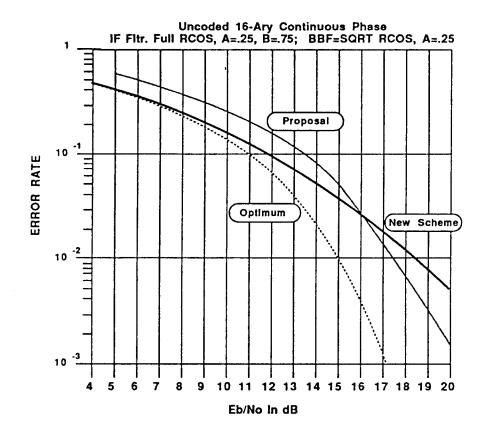

Figure 2.2.3-1 shows a comparison of the uncoded error rate curves of our proposal and our new approach using the square root of Nyquist baseband filter and the IF filter given by Figure 2.2.1-2. The proposed scheme used square pulse 16-CPFSK and experienced large intersymbol interference (ISI) due to the bandlimiting IF filter. This necessitated, in our proposed scheme, the use of ISI correction circuitry to handle up to ± 22.5° of phase error introduced by the IF filter. Because of the baseband pulse shaping filter, ISI is considerably reduced (without requiring ISI correction circuitry), and the performance curve labeled "New Scheme" in Figure 2.2.3-1 is obtained. From this work, we concluded that the ISI correction circuitry of our proposal could be eliminated, resulting in simpler hardware.

Figure 2.2.3-1 Performance Curve for the New Scheme Versus the Proposal

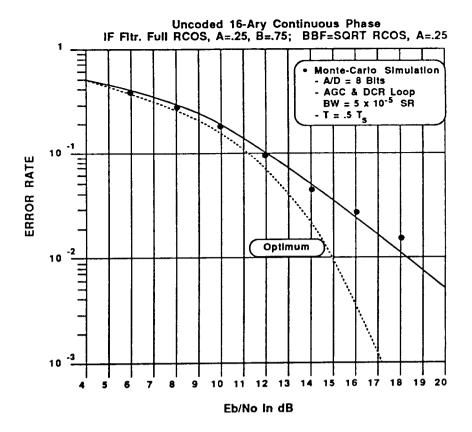

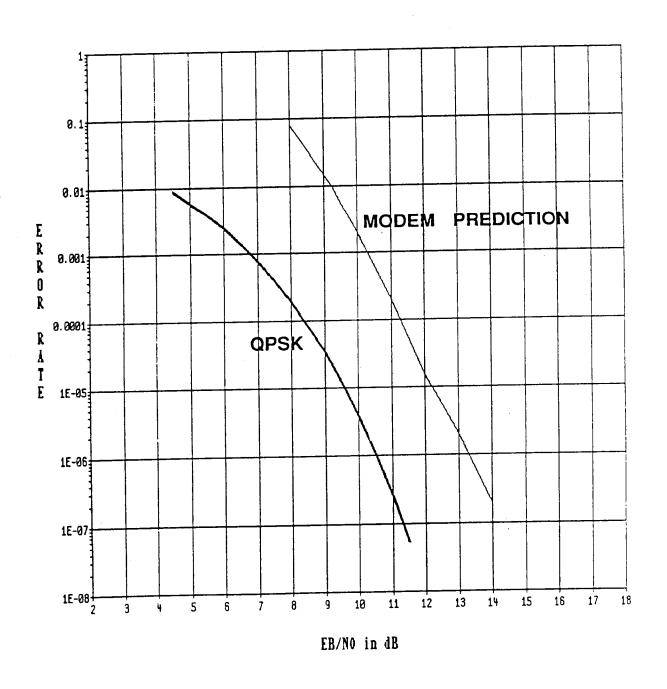

Figure 2.2.3-2 shows the result of a Monte-Carlo simulation of the uncoded error rate performance for a hardware implementation of our modem. The dotted curve is performance of an optimum Viterbi algorithm demodulator for 16-CPFSK. The solid curve is the analytical performance prediction for our modem. The dots are Monte-Carlo simulation points. Through computer modeling, the entire modulator/demodulator was simulated. Many sequences of data were sent for each value of Eb/No. Symbol errors were counted and the error rate computed by dividing the total errors by the total symbols sent. Important hardware parameters for the simulation were; (1) 8-bit A/D quantization assumed, (2) the linearity of the frequency measuring device was approximately .4%, (3) the phase jam strategy, described in section 1.4, was modeled, (4) the loops had a damping factor, zeta = .707.

Figure 2.2.3-2 Uncoded Performance Derived from a Monte-Carlo Simulation

The results given in Figure 2.2.3-2 were encouraging and indicated that our new coherent phase measurement implementation could be achieved with realistic hardware. The close comparison between analytical results and Monte-Carlo simulation results also validated the analytical prediction.

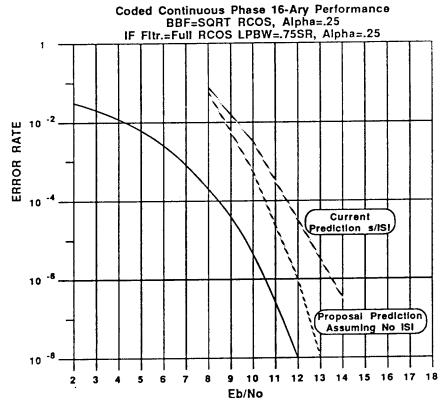

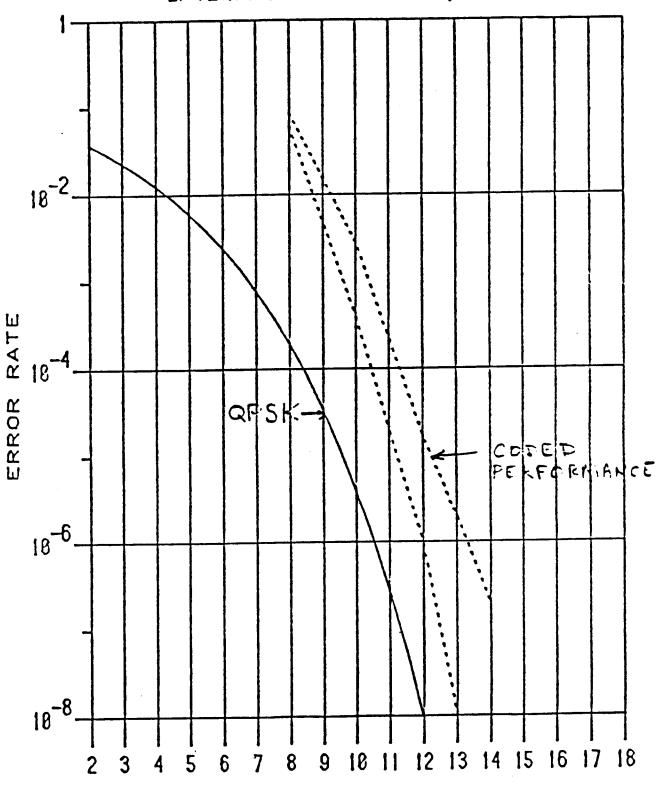

We next produced the analytical performance prediction for the coded system using a K=7 rate 1/2 convolutional code in the fashion described in our proposal. The result is shown in Figure 2.2.3-3, where our proposal prediction assuming no ISI, our current baseline system with ISI, and QPSK performances are all plotted for comparison. We note that the prediction for the current baseline is within 2.7 dB of QPSK at 5 x  $10^{-7}$  bit error rate. But it is approximately 1.4 dB worse than our proposal's prediction assuming no ISI. The loss is apparently due to the residual ISI. Perhaps some of the 1.4 dB loss relative to the proposal prediction can be recovered by careful

equalization of the baseband receiver filter. This remains under investigation.

Figure 2.2.3-3 Coded Performance Prediction

# 2.3 "Ility" Data

In this section of the task one report several subjects will be discussed that have the "ility" suffix such as; producibility (including an estimate of recurring costs), reliability, and maintainability.

# 2.3.1 Producibility - Special Features for Lowering Costs When Produced in in Quantity

There are several hardware design features of our modem that can reduce the cost of producing it when large quantities are purchased. The most notable features are; the extensive use of digital circuits in the baseband processing, the use of surface acoustic wave (SAW) technology for filtering

applications, and the use of monolithic microwave integrated circuits (MMIC) for the IF signal processing.

Digital technology has and still is evolving at an incredible pace. Because of shrinking geometries, integration at the chip level is increasing while the gate capacitance is decreasing, leading to lower propagation delays. Also, the cost of producing complex parts keeps falling due to greater percentage yeilds over time and a ever increasingly competitive market. It is for these reasons that we have strived to construct a major portion of our modem using digital technology. In the POC model we will use standard ECL parts to implement a majority of the baseband signal processing functions. However, we envision either gate array and/or custom VLSI circuits to be used in the production models, both of which have great potential for low cost when quantity purchases are made. Even VHSIC technology, which could be used to implement the K=7 Viterbi decoder, will drop significantly in quantity prices over the next several years as that technology matures (see section 2.3.2 for detailed cost estimations). Finally, the use of digital technology in implementing our modem will eliminate many adjustments that would have to be performed during the production and test cycles which are labor intensive and costly.

We are considering the use of SAW technology to implement the IF filter, the preamble correlator, and a delay line. Because SAW devices are fabricated from a mask (in much the same way as digital devices), the filters, correlators, and delay lines built using SAW technology are very repeatable from device to device. That is, the characteristics, of a filter for example, remain very consistent between various runs of the device. In addition to repeatability, once the mask for a SAW device has been designed,

the fabrication process is very automated (non labor intensive) which leads to low cost per unit if the NRE is spread over a large quantity of units.

Monolithic microwave integrated circuits (MMIC) is a young technology that is maturing quickly. Currently, companies such as Pacific Monolithics are offering circuits such as a downconvertor on a chip that has an RF input range of 3 to 6 GHz and an IF output in the range of 50 to 2000 MHz. Each chip (part# - PM-CO0601-A) contains numerous components, such as RF and IF amplifiers, a local oscillator, an LO buffer amplifier, and a double-balanced mixer. This specific device is used as an example because we are considering it's use in the POC model and because it represents what type of circuits are available now in quantities for a cost a low as \$20 per unit. Other functions are also available, including AGC amplifiers, limiting amplifiers, phase shifters, phase modulators, etc., all of which operate in the GHz regions. Since such powerful devices are currently available, it is not difficult to predict further integration levels, thus enabling even more complex MMICs to be fabricated. We anticipate that by the 1990's, the entire front-end IF chain of our modem will consist of one MMIC chip and one SAW filter on the corner of a PC board.

#### 2.3.2 An Estimate of Recurring Costs

The recurring cost estimate is based on the conceptual design, built in quantity, in a manufacturing environment. No nonrecurring engineering costs are included.

Table 2.3.2 shows three costs: first the design using present discrete components, second the design using gate arrays presently available, and third the design using 1990's technologies.

Cost data was gathered from vendor quotes, current program costs with similar complexity designs, and Harris's VHSIC operations. Gate array performance was established using current issues of VLSI magazine (esp. December, 1985), and gate array development ongoing at Harris.

Table 2.3.2

Estimation of the recurring cost of the TDMA Demod in the 1990's:

| FUNCTION          | PRESENT                 | <u>\$</u>            | GATE ARRAY PRESENT          | <u>\$</u>            | <u>1990'S</u>     | <u>\$</u>        |

|-------------------|-------------------------|----------------------|-----------------------------|----------------------|-------------------|------------------|

| Chass <b>is</b>   | 1                       | \$ 600               | Chassis                     | \$ 600               | 1 Card            | \$ 300           |

| Input RF          | 1 Card                  | \$ 2,000             | 1 Card                      | \$ 2,000             | 1 MMIC,<br>2 Saw  | \$750            |

| Bit Sync          | 1 Card                  | \$ 2,500             | 1 Saw,<br>1 VLSI(ECL, ASIC) | \$ 500               | 1 Saw,<br>1 VHSIC | \$650            |

| Phase<br>Detector | 1 Card                  | \$ 2,000             | 1 VLSI (ECL, ASIC)          | \$ 250               | Part of<br>Above  |                  |

| Decoder           | 1 Card,<br>7 VHSIC IC's | \$30,000<br>\$37,100 | 1 Card, 7 VHSIC IC's        | \$30,000<br>\$33,350 | 1 VHSIC           | \$400<br>\$2,100 |

## 2.3.3 Reliability

The reliability of our modem will be insured by several factors. The first factor to be considered is the parts that make up the whole, i.e., the components. To ensure component reliability, our preference for parts selection will be for those parts that have a proven reliable performance history, or for those parts similar to parts with a proven reliable history. In addition our preference will be toward those components that are multiple sourced. Finally, we will choose components that are capable of satisfactory performance over time and temperature, and are not stressed by the application, either thermally, electrically, or otherwise.

The second factor to be considered from a reliability standpoint is at the chassis level. First, the reliability of the overall box will be insured by a design that does not allow circuit damage due to improper control settings. Secondly, a thermal cutoff capability will be designed into the chassis. Finally, forced air circulation will be used to keep components well away from degrading or damaging temperature conditions.

# 2.3.4 Maintainability

The maintainability of our modem will be insured through thoughtful system level design considerations. Features that have already been "flagged" as important design considerations for the easy maintenance of our modem are items such as; status indicators, internal fault indicators, and easy access test points. In addition, thoughtful chassis layout in conjunction with connectorized cards will allow easy access to both cards and modules. Finally, chassis inputs and outputs will be designed for easy chassis interchange.

# 2.4 Overview of Special Test Equipment

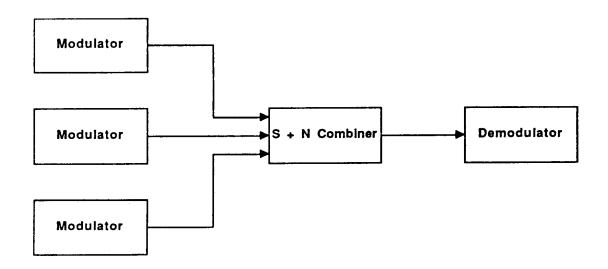

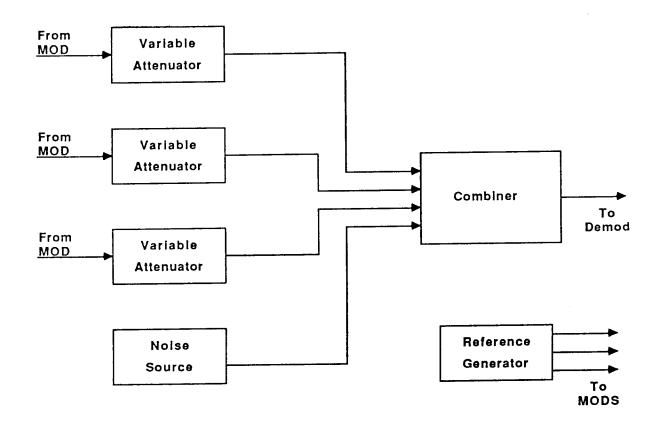

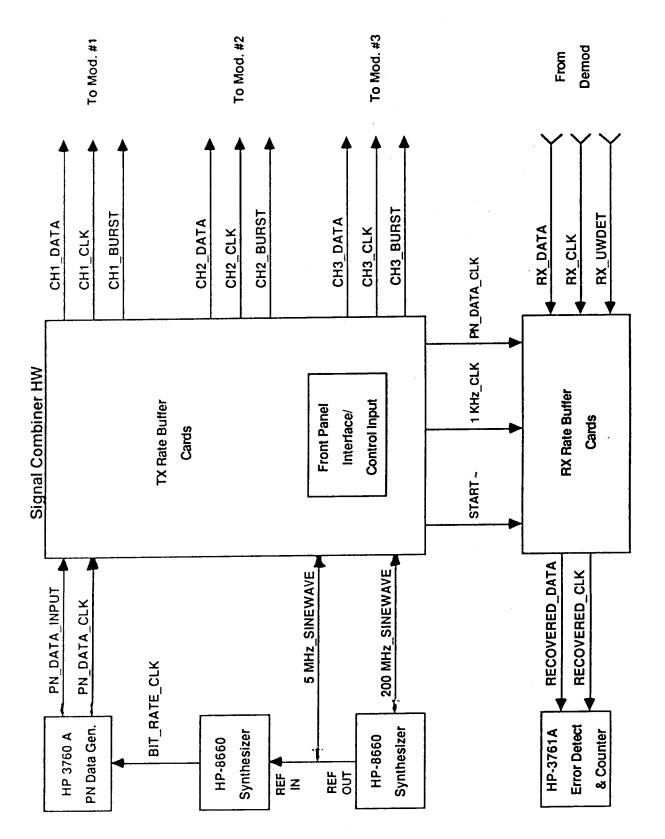

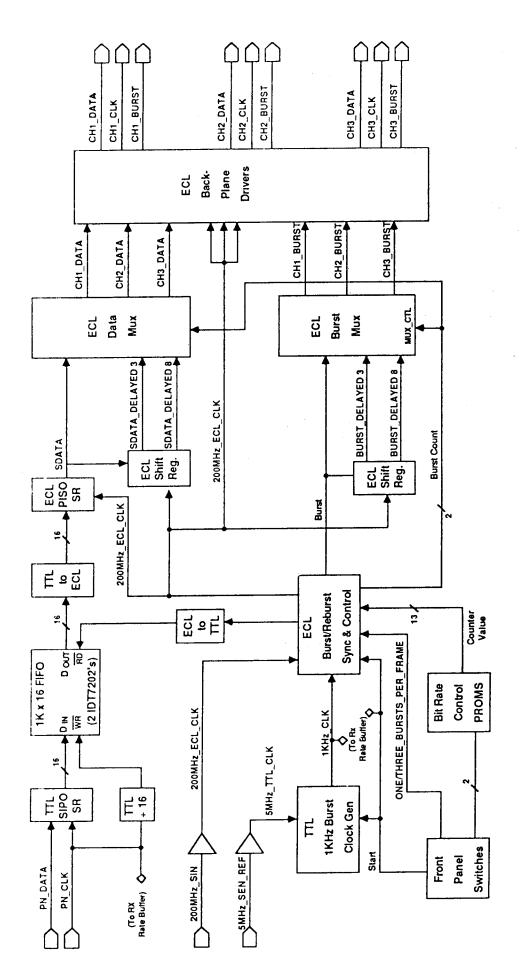

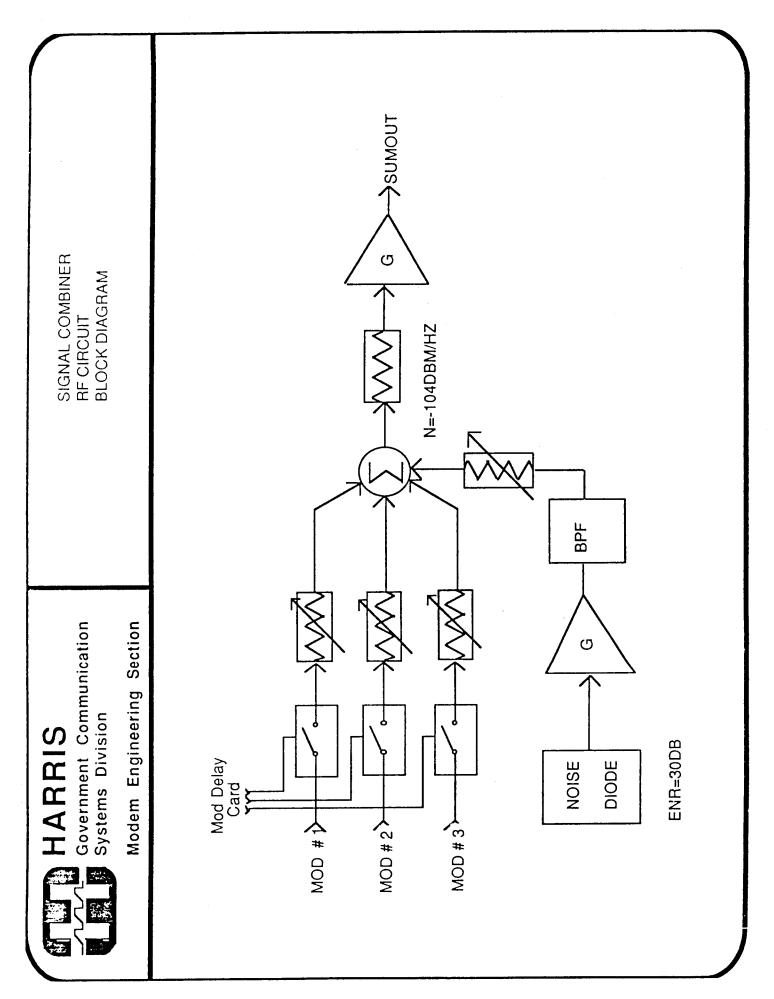

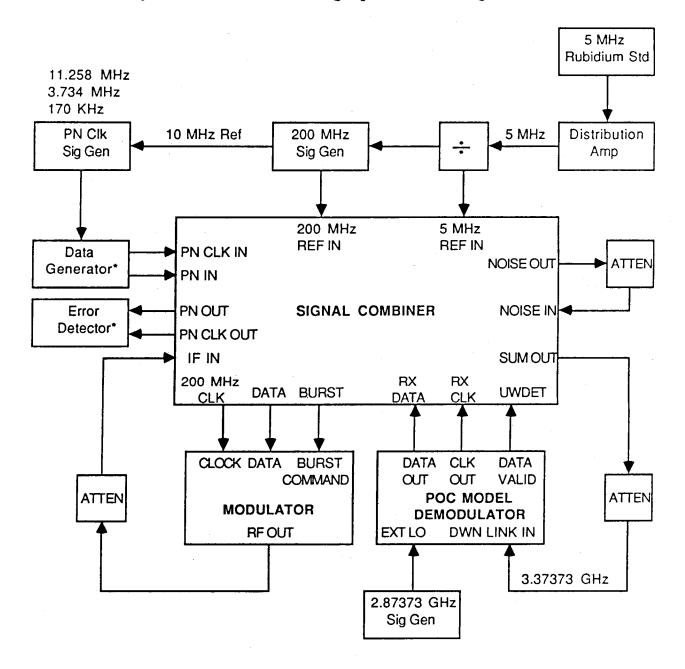

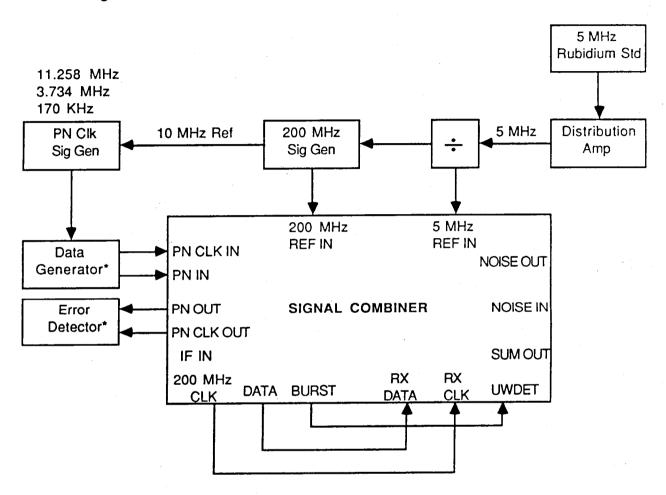

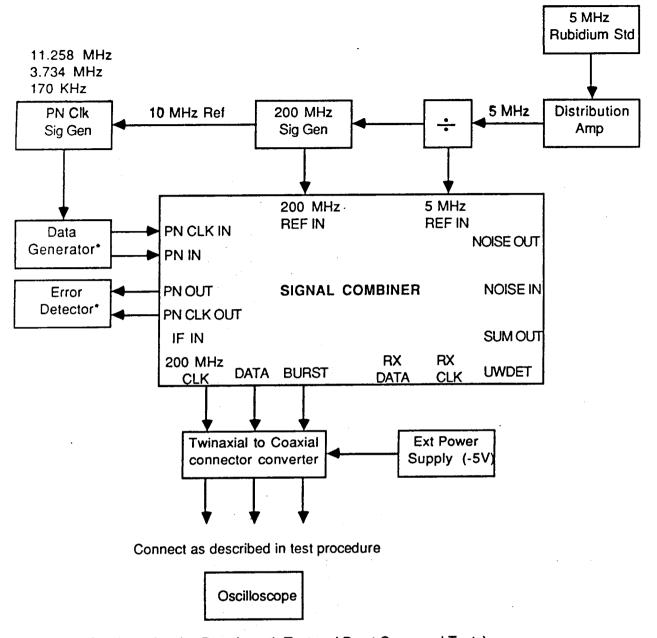

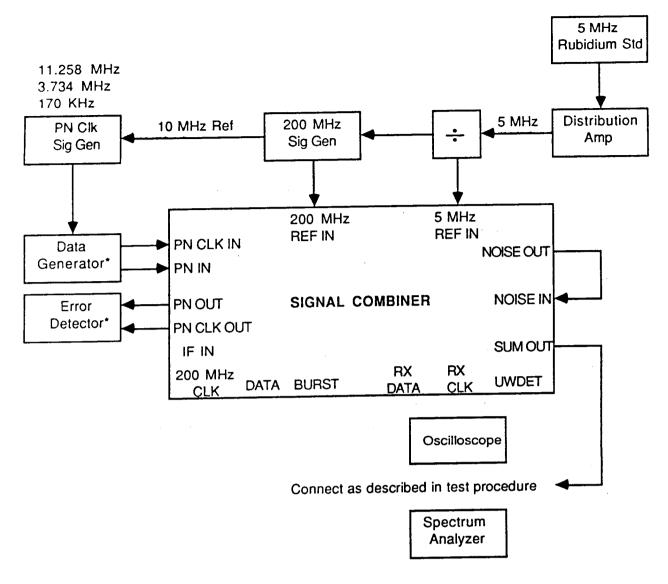

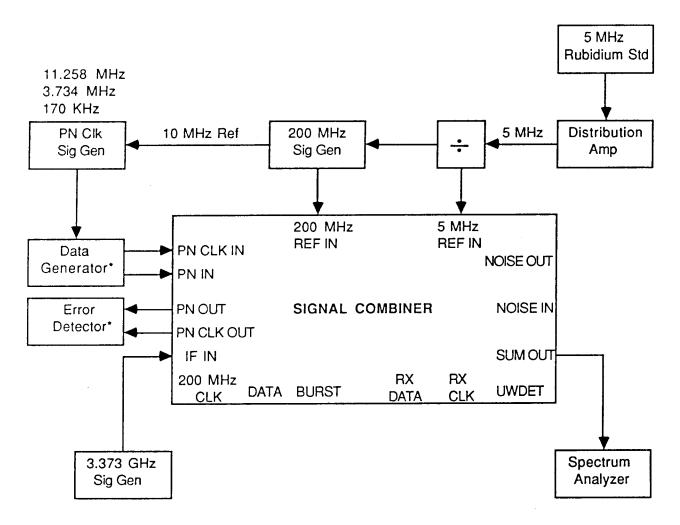

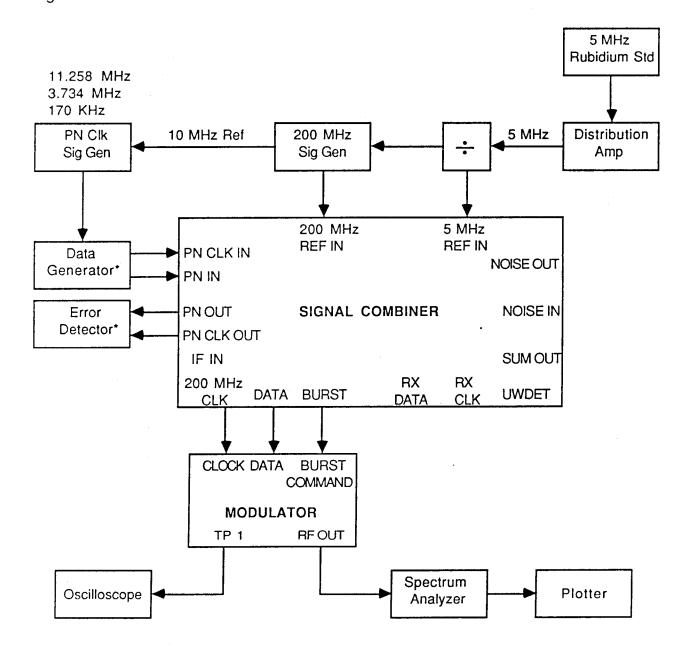

The special test equipment that will be required for testing our modem is of the type that can be designed and fabricated "in-house". Figure 2.4-1 illustrates the system level concept of a test bed. The test bed consists of three modulators, a signal-to-noise ratio combiner, and a demodulator. The three modulators may be configured as co-channel or adjacent channel modulators which in either case share a common design. They may be operated in a CW or burst mode, with a fixed burst rate and a variable burst length. Each modulator will have internal data generators, and the ability to operate with external clock, data, and uplink burst enable signals.

Figure 2.4-1 System Level Block Diagram

Figure 2.4-2 shows a block diagram of the signal to noise combiner. The signal-to-noise ratio combiner features; an internal noise source, variable signal attenuators, signal and noise combiner, burst rate and frame clocks.

FIGURE 2.4-2 Signal to Noise Combiner Block Diagram

# 3. TECHNOLOGY ASSESSMENT AND DESIGN IMPACT

In this section of the task one report we will discuss the impact of technology on the design of our modem.

# 3.1 Current Versus Future Technology

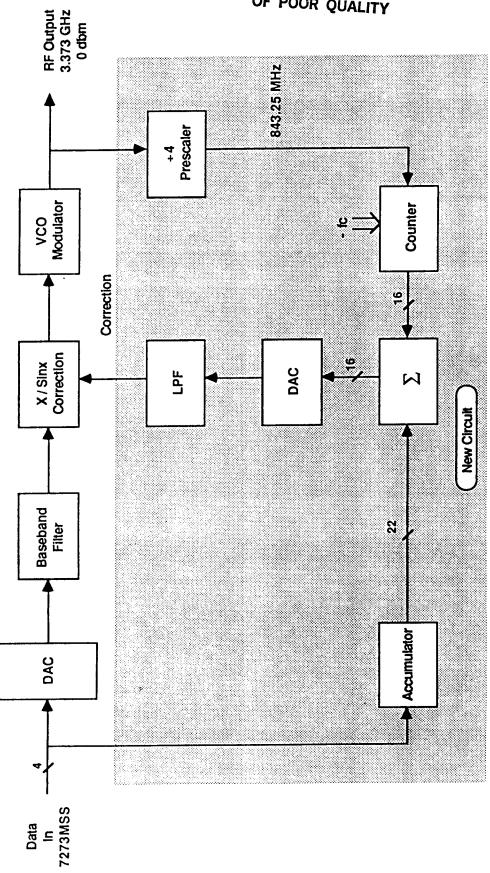

Virtually all of the circuitry required to implement our modem is available now, except for the high rate K=7 Viterbi decoder. The question is, what form, or what type of technology will be utilized in the

construction of these circuits? For example, we propose using an analog VCO to switch frequencies with no abrupt change in phase at the symbol boundaries. However, in the future it will be possible (and advantageous as discussed later in this report) to perform the frequency modulation using a direct digital synthesis technique (i.e., NCO). In addition, baseband processing circuits that are now accomplished with SSI and/or MSI ECL devices may, in the future, be implemented in either VHSIC(.5u CMOS), VLSI(ECL gate arrays), or digital GaAs circuits with a high degree of integration at the chip level, enabling many functions to be performed by one device. The improvements that are realized by the future technology may be in performance (as in the case of the NCO implementation of the VCO), in reliability (as in the case of the SSI to VLSI transition), and/or in cost. To summarize the key technologies used in the modem and their current or future implementation strategies, respectively, see Table 3.1.

Table 3.1 Current Versus Future Implementation of Key Technology Items

| TECHNOLOGY ITEM     | CURRENT IMPLEMENTATION | FUTURE IMPLEMENTATION |  |  |

|---------------------|------------------------|-----------------------|--|--|

| Frequency Modulator | Analog VCO             | Digital NCO           |  |  |

| Frequency Detector  | Bulk Analog            | MMIC/SAW              |  |  |

| IF Filter           | SAW                    | SAW                   |  |  |

| Baseband Processing | SSI & MSI ECL          | VHSIC, VLSI           |  |  |

| Viterbi Decoder     | Low Rate - SSI/MSI     | High Rate - VHSIC     |  |  |

# 3.2 Hardware Techniques which Represent an Advancement in the State-of-the-Art in Modulation Technology

There are various hardware techniques incorporated into our modem which represent an advancement of the state-of-the-art in modem technology, some of which are listed in the proprietary adendum. Others include a high speed Op Amp, high speed A/D converter, high speed D/A converter, IF input filter, and 1/2 Nyquist lowpass filter. The Op Amp represents advanced technology in that a true differential amplifier is required that has a very large bandwidth and a very short settling time. The state-of-the-art in wideband Op Amps is defined by an amplifier with a -3 dB bandwidth of DC to 200 MHz, a settling time (to .02%) of roughly 10 nsec., and a slew rate of 7000V/usec. The A/D and D/A convertors represent the state of the art in conversion technology, again because of the high speed and large bandwidth requirements of our system. The present state-of-the-art in A/D conversion is a 100 Msample 6-bit A/D. The present state-of-the-art in D/A conversion is a 100 MHz 8-bit D/A. The IF filter represents an advance in technology in that conflicting specifications, such as very steep skirt selectivity coupled with almost absolute linear phase, must be met in one filter. The 1/2 Nyquist baseband filter advances modulation technology in that it reduces the sidelobe levels of the non-filtered CPFSK spectrum at the output of the TWT. For a more thorough description of hardware techniques that represent an advancement of modulation technology, the reader is referred to the Harris proprietary adendum.

# 3.3 The Impact of Technology on System Performance

There are a few technology areas that impact the performance of our modem. That is, as the technology progresses, we will be able to take advantage of the new technology, not only to decrease the cost of our modem, but to increase (slightly) it's performance relative to the current (POC) implementation. Listed in the following paragraph are the technologies that may affect system performance. Included in this discussion is the specific area of performance affected as well as the contributor.

The linearity of the frequency detector will impact the BER versus Eb/No performance of our modem. Our goal for the frequency linearity is 1 percent. As technology progresses, linearities of less than 1% may easily be realizable. The VCO linearity may also affect the BER performance of our modem. However, as technology allows an NCO to be implemented at the frequencies of interest, linearity will be of no concern in that an NCO is inherently linear. The VCO output power variation with frequency may impact BER performance. Our goal is to keep the power variation to within .25 dB, but again, an NCO would alleviate this problem. The ability to correlate with the preamble and quickly jam the symbol timing along with the RF phase will impact acquisition. As the ultimate speed of digital technology increases, the criticality of this timing issue is diminished. The large number of interconnections required in the baseband processing section with the use of SSI and MSI technology may impact reliability. However, as the implementation transitions from SSI/MSI to VHSIC and VLSI, the number of interconnections between parts as well as the total parts count will decrease, which will increase the reliability of the modem.

# 3.4 Advantages and Disadvantages of Implementation Technologies

In this section the advantages as well as the disadvantages of the previously mentioned technology is outlined. These technology items are; the frequency measurement circuit, the VCO, the NCO, and the baseband signal processing functions.

The advantage of using a frequency measuring circuit in the implementation of the demodulator is that it reduces the overall hardware design complexity of the demodulator. Thus, by reducing circuit complexity, a cost savings is realized both in the design effort (POC) and in future production runs (EDMs and beyond). The only disadvantage to the frequency measuring approach is the possible degradation (slight) in BER performance due to nonlinearities. Although, there are methods in which to linearize a frequency measuring device, of which we are currently pursuing to ameliorate the linearity problem.

The advantage of using a VCO as the continuous phase frequency modulator is that a VCO is presently available has suitable dynamic characteristics. The disadvantage of the VCO technology is the nonlinearity of voltage to frequency conversion (goal is < 1% nonlinearity) and the long term frequency drift of the VCO. An NCO, as previously touted, is inherently linear and it's frequency stability is as good as it's reference. However, an NCO is not currently available with an output center frequency capability of 3.373 GHz, and probably will not be available for some 2 to 5 years. Hence, the only disadvantage of the NCO technology is the availability of that technology.

The baseband signal processing functions are implemented using digital technology and therefore realize all the advantages that are inherent to threshold logic. These advantages include; stability over time and

temperature, a high degree of integration at the chip level, immunity to small cross-talk and noise signals, and finally, digital circuits lend themselves to all kinds of automated processes which reduce production, test, and maintenance costs. The only disadvantage of using digital circuits to implement the baseband processing functions of our demodulator are the high processing speeds at which we must operate (the sample rate = symbol rate = 67 MHz). This leads to technology such as ECL or GaAs to accomplish the required processing under worst case conditions with margin.

#### TECHNICAL REFERENCES

- 1. J. D. Oetting, "A Comparison of Modulation Techniques for Digital Radio", IEEE Transactions on Communications, Vol. COM-27, No. 12, Dec. 1979, pp. 1752-1762.

- 2. C. R. Ryan, A. R. Hambley, and D. E. Vogt, "760 Mbps Serial MSK Microwave Modem", <u>IEEE Transactions on Communications</u>, Vol. COM-28, May 1980, pp. 771-777.

- 3. Robert C. Davis, "An Experimental 4-ary CPFSK Modem for Line-of-Sight Microwave Digital Data Transmission," EASCON 1978, pp. 674-682.

- 4. P. R. Hartman, "Digital Radio Technology: Present and Future", IEEE Communications Magazine, Vol. 19, No. 4, July 1981, pp. 10-14.

- 5. Final Technical Report, RADC-TR-79-56, "Linear Modulation Techniques for Digital Microwave," Robert C. Davis, Harris Corporation, Study for Rome Air Development Center, August 1979.

- 6. S. G. Wilson, H. A. Sleeper, II, P. J. Schottler, M. T. Lyons, "Rate 3/4 Convolutional Coding of 16-PSK: Code Design and Performance Study", IEEE Tran. of Comm., Vol. COM-32, pp. 1308-1314, Dec. 1984.

- 7. Stephen G. Wilson, Paul J. Schottler, and Harry A. Sleeper, "Rate 3/4 10-PSK Phase Codes," ICC 1982, pp. 6 F.1.1-6F.1.5.

- 8. T. A. Schonhoff, "Symbol Error Probabilities for M-ary CPFSK: Coherent and Non Coherent Detection", <u>IEEE Transactions of Communications</u>, Vol. COM-24, No. 6, June 1976, pp. 644-652.

- 9. G. David Forney, Jr., "The Viterbi Algorithm" Proceedings of the IEEE, Vol. 61, No. 3, March 1973, pp. 268-277.

- 10. M. G. Palchat, R. C. Davis, and M. B. Luntz, Harris Corporation, "Coherent Demodulation of Continuous Phase Binary FSK Signals," in Proc. Int. Telemetry Conf. (Washington, D.C., 1971).

- 11. Joe Grabowski and Robert C. Davis, "An Experimental M-QAM Modem Amplifier Linearization and Baseband Equalization Techniques," National Telesystems Conference Record, November 1982, Galveston, TX., pp. E3.2.1 E3.2.6.

# NAS3-24681

# ADVANCED MODULATION TECHNOLOGY DEVELOPMENT HIGH SPEED A/D CONVERTER BREADBOARD EVALUATION REPORT

SUBMITTED BY:

JAMES F. ROESCH, JR.

HARRIS GCSD

PREPARED FOR:

NASA LeRC

## 2.3.1 Breadboard Development Definition

- 2.3.1(a) The high speed quantizer (A/D) was a recommended breadboard item as presented at NASA LeRC during the Task II review.

- 2.3.1(b) Rationale supporting the need for breadboarding.

The high speed 8-bit flash A/D technology is very young. Only three 8-bit, 100 MHz converters are known to exist, with one of the three not yet a reality. Utilizing such new technology in such a critical function in our system, it was deemed necessary to evaluate and verify the performance of the technology relative to vendor specifications. In so doing, valuable information as to the proper utilization of the technology could be inferred for use in the detail design phase of the POC model.

2.3.1(c) A description of the objectives and approaches for breadboarding.

The objectives of the A/D breadboard phase are quite straightforward. They are:

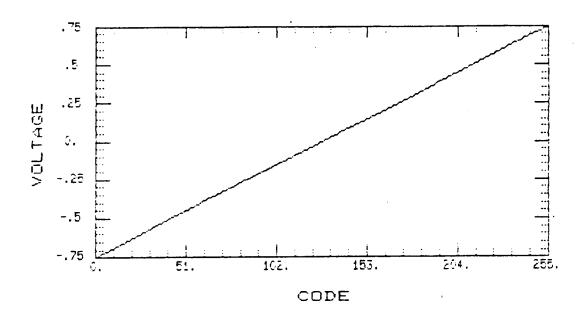

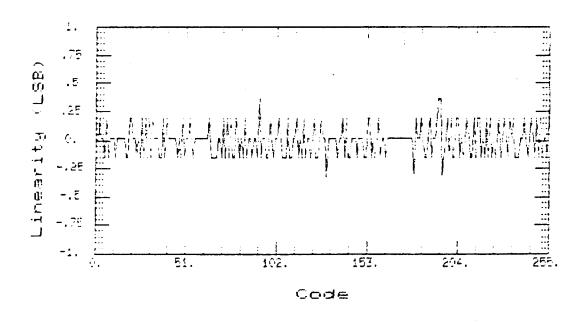

- (1) To verify accurate 8-bit resolution (1/2 LSB linearity) digitization of frequencies between DC to 50 MHz, at a sampling rate of 72.73 MHz.

- (2) To verify the input bandwidth of the device.

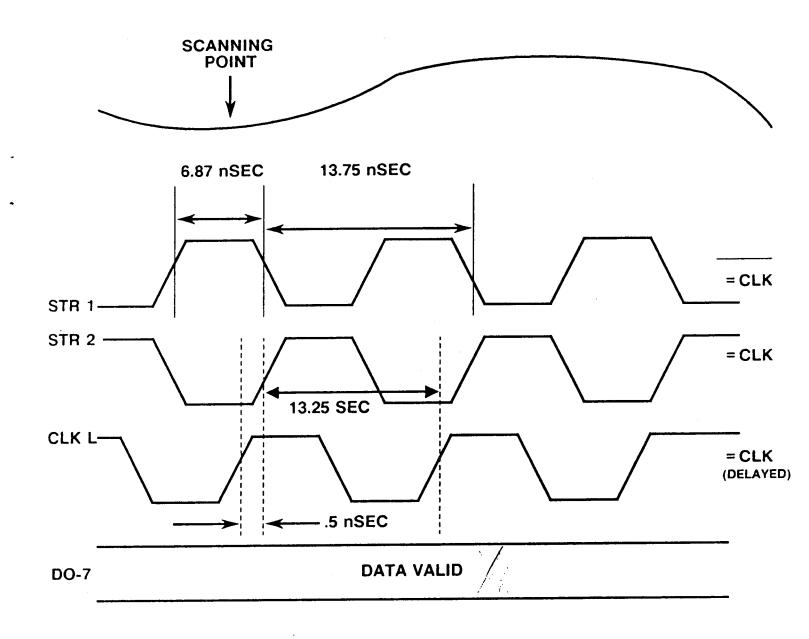

- (3) To experiment with the clocking scheme of the Siemens SDA-8010 A/D and verify accurate sampling with STR1 = CLK and STR2 = CLK.

The approach taken to verify the above objectives is also quite straightforward. All necessary hardware will be built and tests conducted, as given in Section 2.3.2, to verify the major objectives outlined above.

Tests will also be performed as necessary to verify minor objectives pursuant to the major objectives.

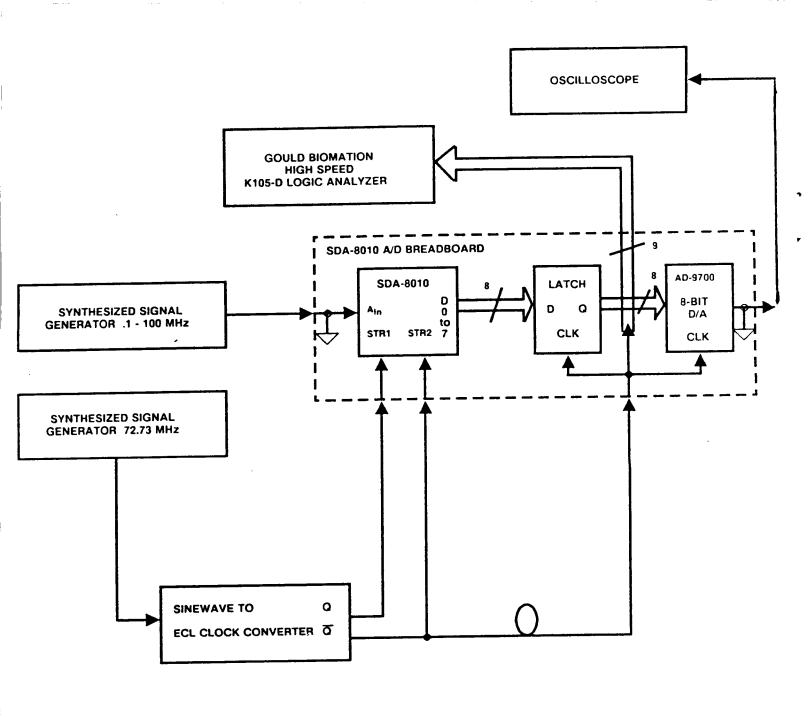

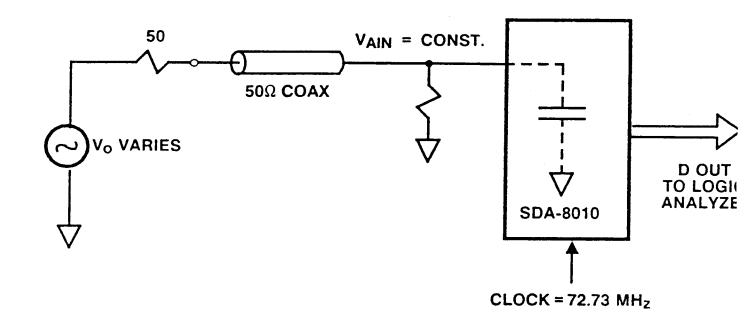

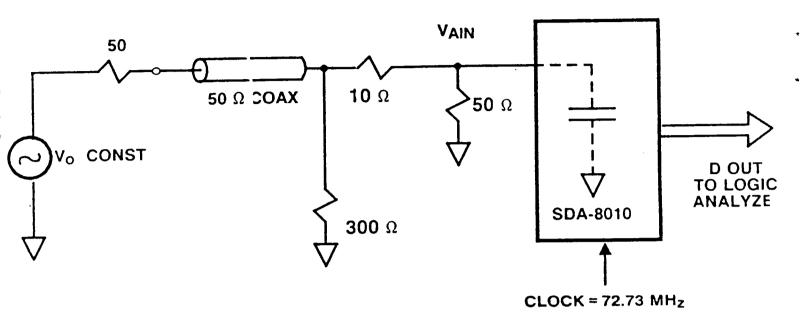

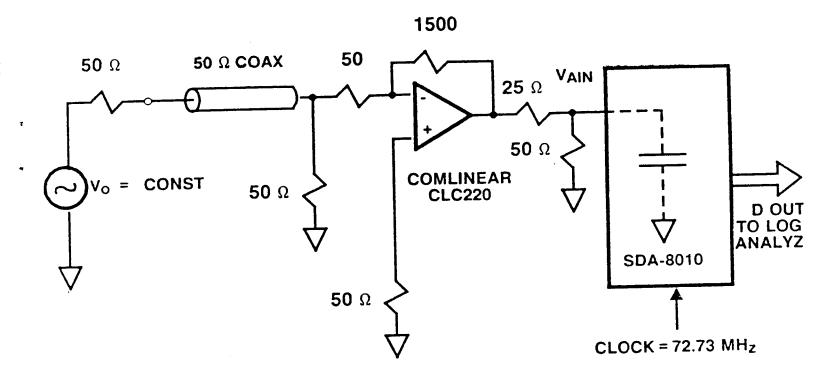

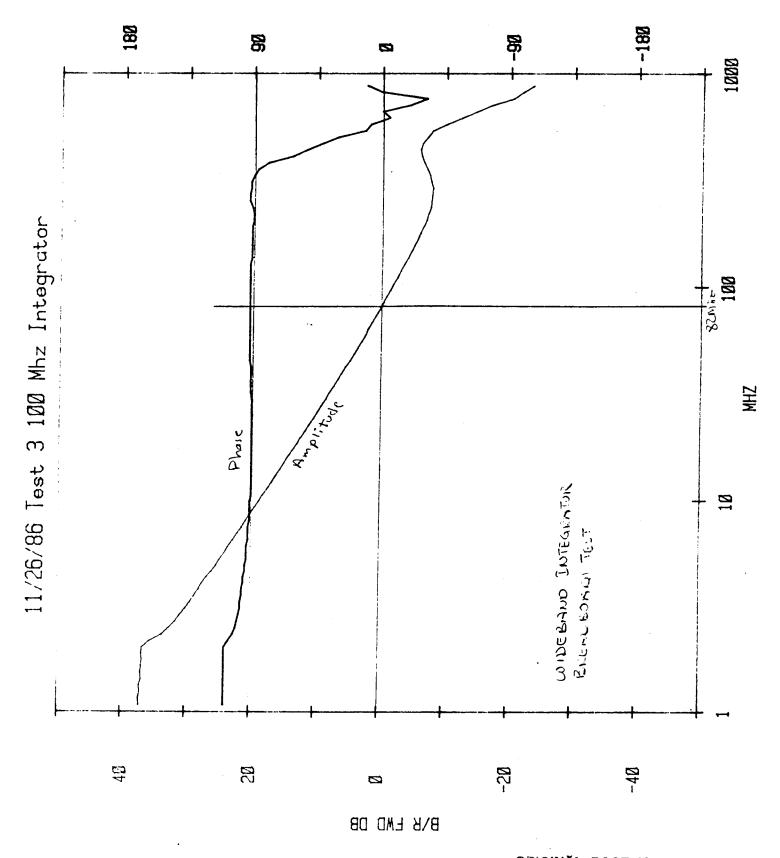

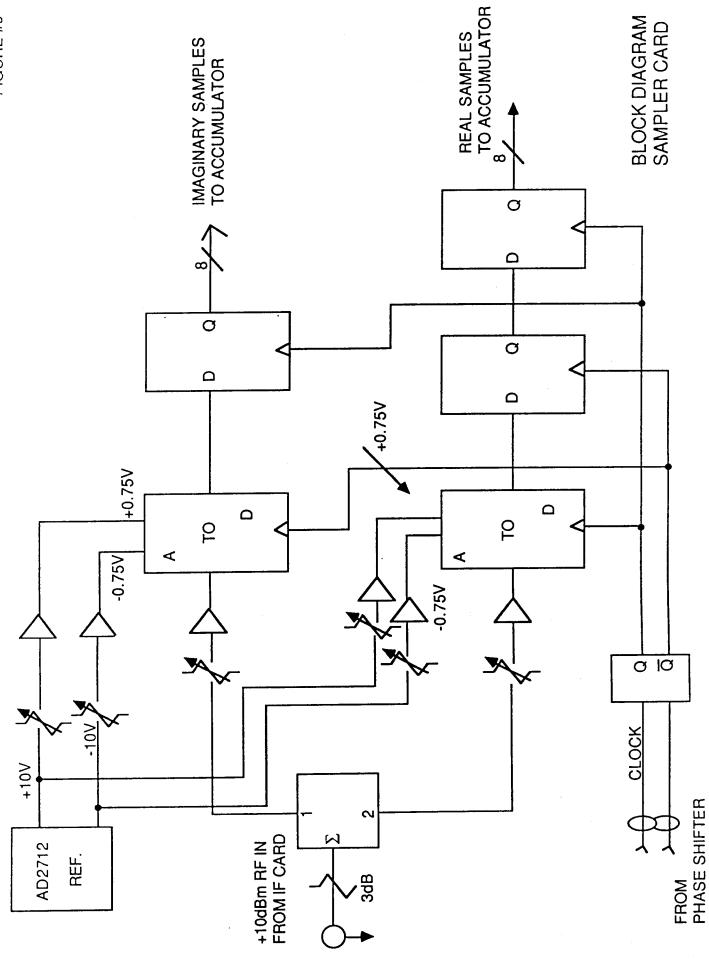

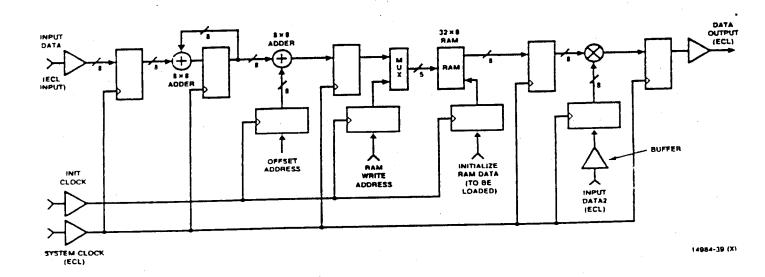

A block diagram of the test bed including the SDA-8010 A/D breadboard is given in Figure 2.3.1.

A/D/0107X

Figure 2.3.1. SDA-8010 A/D Test Bed

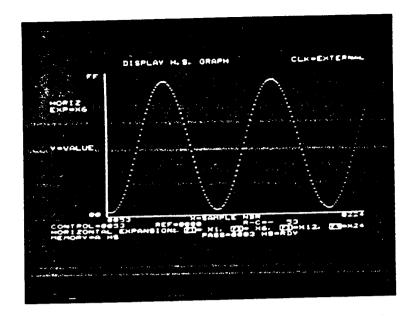

# 2.3.1(d) Functional Requirements of the SDA-8010 A/D Breadboard.