### NASA CR175070

# **Bidirectional Power Converter** Control Electronics

# **Final Report**

By: J. Mildice

### GENERAL DYNAMICS Space Systems Division

Prepared for

### NATIONAL AERONAUTICS AND SPACE ADMINISTRATION

NASA Lewis Research Center Contract NAS 3-23878

化乙酸基苯酚酸乙基乙酸医乙酸乙酸乙酸乙酸乙酯 在这边有限的情望 医外肌的过去式和过去分词 网络红色子母 重新

(NASA-CR-175070) BIDIRECTIONAL POWER N90-10175 CONVERTER CONTROL ELECTRONICS Final Report (General Dynamics Corp.) 103 p CSCL 21H

Unclas

63/20 0237142

. 1942년 1월 28일 - 1942년 1942년 1952년 1952년 1953년 1952년 1953년 1952년 195

-

# **Bidirectional Power Converter Control Electronics**

# FINAL REPORT

J.W.Mildice Program Manager

.

CR 175070

-

Final Report Contract No. NAS 3-23878

,

Final Report Contract No. NAS 3-23878

# **Table of Contents**

| <b>1.0</b> Summary                                              | . 1 |

|-----------------------------------------------------------------|-----|

| 1. General Functions                                            | . 1 |

| 2. Application Specific Functions                               | . 1 |

| 2.0 Introduction and Background                                 | . 3 |

| 3.0 Resonant Processor Operation and Control Requirements       |     |

| 3.1. "General" Functions                                        | . 5 |

| 3.1.1. Housekeeping                                             | . 5 |

| 3.1.2. Short Circuit Protection                                 | . 6 |

| 3.2. Application Specific Functions                             | . 6 |

| 3.2.1. Case 1, On-board Battery Charging from the High          |     |

| Frequency Bus                                                   | . 6 |

| 3.2.2. Case 2, Auxiliary Ground Power or AC Power Energizing    |     |

| the High Frequency Bus                                          | . 7 |

| 3.2.3. Case 3, Variable speed Motor/Generator starting/running/ |     |

| generation to and from the high frequency bus                   | . 7 |

| 3.3. Other Requirements                                         | . 8 |

| 3.3.1. Regulation                                               | . 8 |

| 3.3.2. Command Interfaces                                       | . 8 |

| 4.0 Hardware Design                                             |     |

| 4.1 Requirements Specification                                  | . 9 |

| 4.2 Predesign                                                   | . 9 |

| 4.3 Circuit Design and Development                              | 10  |

| 4.3.1 Housekeeping Module                                       | 10  |

| 4.3.2 Regulation Control                                        | 11  |

| 4.3.3. AC Output Frequency Synthesis and Control                | 12  |

| 4.3.4. High Frequency System Clock                              |     |

| 4.3.5. Digital input interfacing and storage                    | 15  |

| 4.4. Construction of Application Specific Functions             | 16  |

| 4.4.1. Case 1, On-board Battery Charging from the High          |     |

| Frequency Bus                                                   | 16  |

|                                                                 |     |

•

CR 175070

| 4.4.2. Case 2, Auxiliary Ground Power or AC Power Energizing |   | 10   |

|--------------------------------------------------------------|---|------|

| the High Frequency Bus.                                      | • | . 18 |

| 4.4.3. Case 3, Variable speed Motor/Generator starting/      |   |      |

| running/generation to and from the high frequency bus        | • | . 18 |

| 5.0 Construction and Test                                    |   |      |

|                                                              |   | 21   |

| 5.1 Initial Testing                                          |   |      |

| 5.2 High Power Compatibility Testing                         |   |      |

| 5.2.1. Power Breadboard                                      | • | . 21 |

| 5.2.2. 25 KW Testbed                                         | • | . 22 |

| 6.0 Delivery and Final Hardware Disposition                  | • | . 23 |

| 7.0 Conclusions and Recommendations                          | • | . 25 |

| 8.0 Figures                                                  | • | . 27 |

| 9.0 Tables                                                   | • | . 47 |

| <b>10.0 References</b>                                       | • | . 51 |

| Appendices                                                   | • | . 53 |

| A. Design Requirements Specification                         |   |      |

| B. Functional Block Worksheets                               |   |      |

| C. Updated Schematics                                        |   |      |

CR 175070

• •

Final Report Contract No. NAS 3-23878

. . . .

### 1.0 Summary

This program was aimed at developing a family of control circuit designs for resonant technology, power processing hardware; which were appropriate to control the SCR driven power switching stages and series resonant networks of "Mapham" (Reference 3) derived inverter/converter configurations.

In general, the primary tasks included the following:

- Analyze the basic set of functions required to control a multi-phase bidirectional resonant power system.

- Create a set of basic designs to implement those functions.

- Build and test the basic designs

- Integrate and test the control hardware into high power breadboard/testbed systems.

Application specific power processor requirements addressed both source and load interfaces, and included regulating drivers/inverters/frequency-changers to provide high frequency (20-kHz) AC from DC or low frequency AC; and bidirectional interfaces from 20-kHz AC to DC or low frequency AC loads and users. The main functions were broken into two sections and defined as follows:

1. General

- Housekeeping

- Overload Protection

- 2. Application Specific

- Case 1: On-board battery charging from the high frequency bus.

- Case 2: Auxiliary ground power energizing the high frequency bus.

- Case 3. Variable speed motor/generator starting/running/generation to and from the high frequency bus.

Final Report

CR 175070 Contract No. NAS 3-23878

The original program was to be completed in approximately twelve months, and the main tasks were completed in approximately that period. However, operational testing at that time was limited to non-real-time functional tests and to low power IRAD hardware interfaces which then existed at General Dynamics. Therefore, NASA LeRC and General Dynamics agreed to extend the final completion date twice; first to verify compatibility with the 25-kW high power IRAD hardware then in construction at General Dynamics; and then to test with the subsequent LeRC contracted 25-kW testbed equipment being completed in 1987.

CR 175070

Final Report Contract No. NAS 3-23878

### 2.0 Introduction and Background

The high-frequency power system technology addressed by this program generates its basic AC transmission link power by exciting an underdamped, series-resonant, L-C circuit. The power bus therefore becomes an integral part of the resonant link in the more or less usual resonant converter configuration, with the load interface modules forming the output stages. Therefore the power system for a vehicle is really one large, integrated, multiple-module resonant converter.

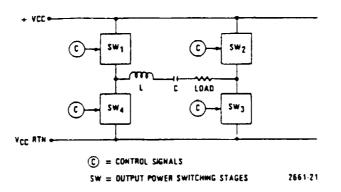

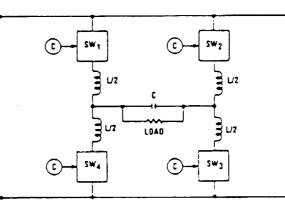

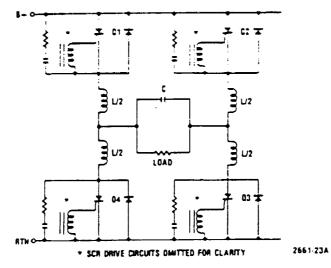

While the basic configuration is a series resonant design, it is not the familiar "Schwarz" (Reference 4) type. Alternately, it places the load (reflected through the output transformer) in parallel with the resonant capacitor in the method proposed by Neville Mapham (Reference 3). Figures 2-1 and 2-2 show the two circuit approaches.

This gives us a system driver (inverter) that is essentially a voltage source as compared to the more usual "Schwarz" current source. This has obvious advantages for a power system. The line voltage is independent of the load (on a first order basis) and is tolerant of open circuits, obvious requirements for a utility system. In addition, the output frequency is clock-controlled, and independent of variations in the resonant circuit components, which is a significant development for this class of hardware.

The basic power output hardware configuration for a single driver is shown in figure 2-3. Two or more such drivers are arranged in series, with different phase shifts between one another, to add and provide power output closed-loop regulation. The control circuits noted (c) in the above figures are the subject of this contract. CR 175070 Contract No. NAS 3-23878

·

Final Report

Page 4

#### **3.0 Resonant Processor Operation and Control Requirements**

#### 3.1. "General" Functions

#### 3.1.1. Housekeeping

Housekeeping functions are those that are associated with module operations, independent of the chosen module output character, or those that are inherently necessary to assure proper operation of the module or assembly.

The first task to be accomplished in this contract effort was to examine the operational power components of a typical driver or receiver module to find those common tasks associated with the operation of the bridge-connected power switches.

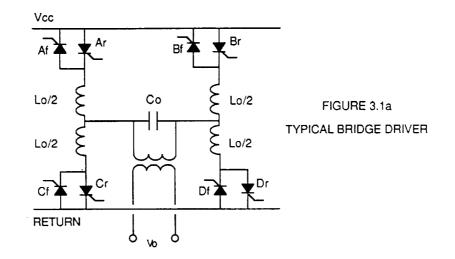

When functioning as a driver (inverter), there are four primary switch states. The component designators for the following discussion are shown in Figure 3-1a, in Chapter 8. State 1 has switches  $A_f$  and  $D_f$  turned on. The current in the output capacitor,  $C_0$  is shown in period 1 of Figure 3-1b. Since the series resonant circuit of  $L_0$  and  $C_0$  is underdamped,  $C_0$  is charged to a voltage above the power supply voltage,  $V_{CC}$ . If switches  $A_f$  and  $D_f$  are now turned on, the current shown in period 2 flows in  $C_0$ . If  $B_f$  and  $C_f$  are turned on during period 2, after a delay long enough to allow  $A_f$  and  $D_f$  to turn off, but before the current has decayed to zero, the resulting current is shown in period 3 of Figure 3-1b. It charges  $C_0$  to its maximum value (in the reverse direction) to provide the energy for period 4, when  $B_f$  and  $C_f$  are turned on. The time correlated voltage across  $C_0$  is shown in Figure 3-1c. It is obvious that if this periodic operation is continued, a continuous sinusoidal output voltage is produced at half the basic clock rate. Housekeeping functions to be performed for this operation are:

1. Alternate turn-on of the forward  $(S_f)$  switch pairs at the leading edge of the clock pulse.

Page 5

### PRECEDING PAGE BLANK NOT FILMED

GEEDING PAGE BLANK NOT FILMED

والمشتري المنهورة الأراج التي أخشتها

2. Turn-on of the appropriate reverse switches  $(S_r)$  at the zero crossings of the  $C_0$  current.

3. Detection of the  $V_{cc}$  polarity and reversal of the switch turn-on "sense" on a real time basis for AC input power operation.

4. Disabling of all switch operation for turn-off and primary control.

#### 3.1.2. Short Circuit Protection

When the output of this resonant converter topology is overloaded or shorted, the resonant circuit is no longer underdamped, and the forward current does not return to zero before it is time for the next clock pulse. If that pulse were applied, the power input would be shorted in the common "all switches on" bridge circuit failure mode. A requirements decision was made to incorporate a switch control logic input which checks to see if an appropriate reverse current has occurred, before an opposite polarity switch can be turned on. While equivalent protection could be accomplished through forced-commutation of the output switches, this choice would either complicate the power circuitry significantly or restrict the available choices for power switching components by eliminating the entire family of thyristor devices.

#### 3.2. Application Specific Functions

#### 3.2.1. Case 1, On-board Battery Charging from the High Frequency Bus

The requirement for on-board battery interface control generates the need for bidirectional operation. The basic housekeeping/short protection logic described in section 3.1 provides all the necessary control for the single-module reverse (source) mode.

When operated as a receiver (load interface), bus power is applied to the same high frequency interface (as if it were a driver) and the switches are sequenced to provide full wave rectified power at the  $V_{CC}$  terminals. Therefore, high-

frequency, polarity-determining inputs must be supplied to the logic to control switch sequencing for output polarity control. Equivalent clock signals to operate the logic are generated from the high frequency bus input.

The added control function for this case is output current regulation. To avoid the complication and power losses associated with a separate, additional DC output regulator, it was decided to use the existing switches to control power output by phase delay switching. This creates a functional requirement for an analog to digital regulator circuit that delays the clock pulses to the control logic, an amount controlled by the output current feedback.

### 3.2.2. Case 2, Auxiliary Ground Power or AC Power Energizing the High Frequency Bus.

Requirements for the housekeeping logic already would enable the circuitry to deal with AC inputs. The only consequence of simply using the AC  $V_{CC}$  equivalent would be that the output high frequency would be amplitude modulated at the AC power input frequency. A simple solution is to use a three phase source (one phase powering each of three driver modules) and add the outputs by putting them in series. With this arrangement, the high frequency signals are all in phase, adding directly, and their modulation envelopes are in the usual three phase relationship, adding to a nearly constant high frequency AC power bus output. The conventional choice to do this function would be to put a three phase rectifier-filter on the input to provide a DC Vcc. But the conventional approach would add significant losses, not found in the chosen approach.

### 3.2.3. Case 3, Variable speed Motor/Generator starting/ running/generation to and from the high frequency bus.

This application is the most complex of the specific requirements. The preceding two cases can be subsets of this most general case. Control circuitry designed to meet the requirements of case 2 will meet the generator/generation requirements of this case. The requirements for Bidirectional operation and output regulation (which can be used for low frequency motor output amplitude control) are developed in case 1. The remaining added functions are for

CR 175070 Contract No. NAS 3-23878 Final Report

frequency control of the output to the motor. They include a range of fixed frequencies, ramped frequency changes at constant rates or rates based on analog feedbacks for constant V/F control or constant torque starting.

#### 3.3. Other Requirements

#### 3.3.1. Regulation

While not specifically called out, proper system operation requires high frequency bus regulation. The regulation technique selected for this program operates by the "phasor" addition of the high frequency AC output voltages of two or more resonant inverter modules. This approach is completely consistent with the overall hardware requirements of the program which demand low losses and low output distortion.

#### 3.3.2. Command Interfaces

Today's technologies require that hardware operation and test be computer controlled. To be consistent with modern laboratory techniques, and to anticipate typical operational airborne requirements for this class of equipment, all control and data interfaces for this program are designed to be computer compatible. It was agreed that these interfaces should be designed to be compatible with normal CMOS requirements and parameters. Table 3-1 (in Chapter 9) shows the typical specifications used.

이 같은 사람이 있는 것 같은 것을 위해 주말을 수 없다.

### 4.0 Hardware Design

#### 4.1 Requirements Specification

This first phase of the program was to develop and formalize the actual circuit and operational requirements for the hardware in a requirements specification, and submitted that specification to NASA LeRC for review and approval, prior to starting on the actual hardware design and development.

That specification is included in this report as Appendix A.

#### 4.2 Predesign

The predesign stage of the program was to develop preliminary detailed circuit designs for the three application specific pieces of hardware in the program work statement; which also incorporated the general requirement provisions. These were then broken down into the lowest possible level building blocks having unique, identifiable functions, above the piece part level. Since the interfaces required CMOS parametric compatibility, the standard 4000-series CMOS logic family was chosen to implement the digital circuit topologies, and low-performance, non-critical operational amplifiers were chosen for the analog hardware implementation.

These low level functional blocks were successively combined into higher level ones, with the primary goal and limit aiming toward a set of large scale blocks that were common across all the Specific applications. Without repeating the details of all the subsequent iterations, the end result of that process identified five major, common building blocks. They are:

- Bridge/driver housekeeping and control (includes short circuit protection and input fault clearing)

- Analog regulation for the high frequency bus (combined with receiver AC and DC output regulation)

Final Report

CR 175070 Contract No. NAS 3-23878

- AC output frequency synthesis and control

- High frequency system clock

- Digital input interfacing and storage

Appendix B shows the detailed worksheets used for this process. Section 4.4 shows how these blocks are arranged for the three Application Specific Functions.

#### 4.3 Circuit Design and Development

#### 4.3.1 Housekeeping Module

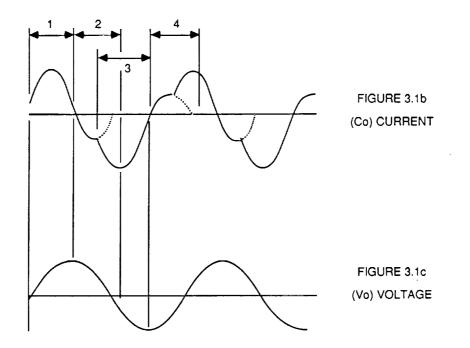

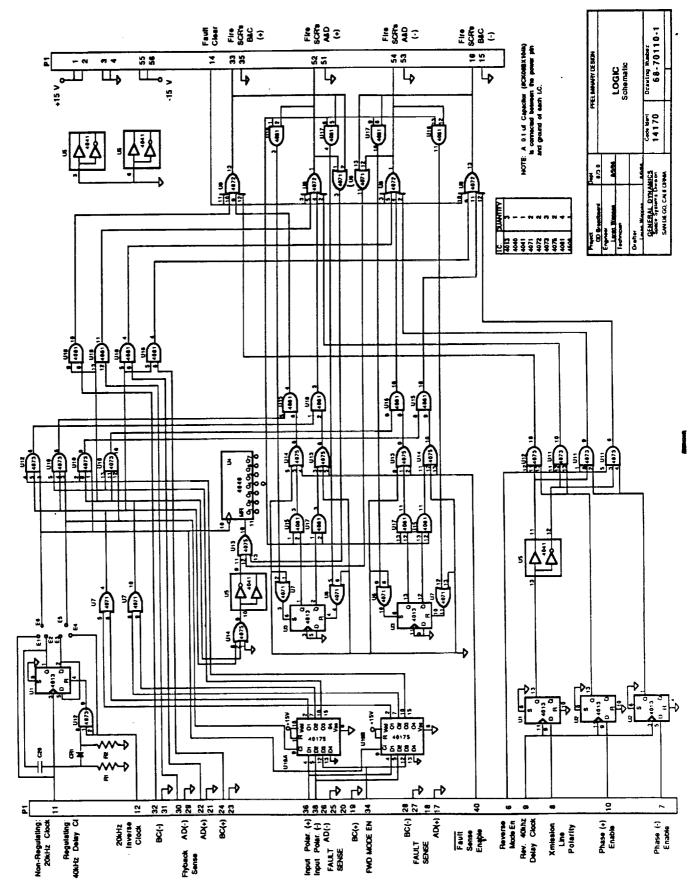

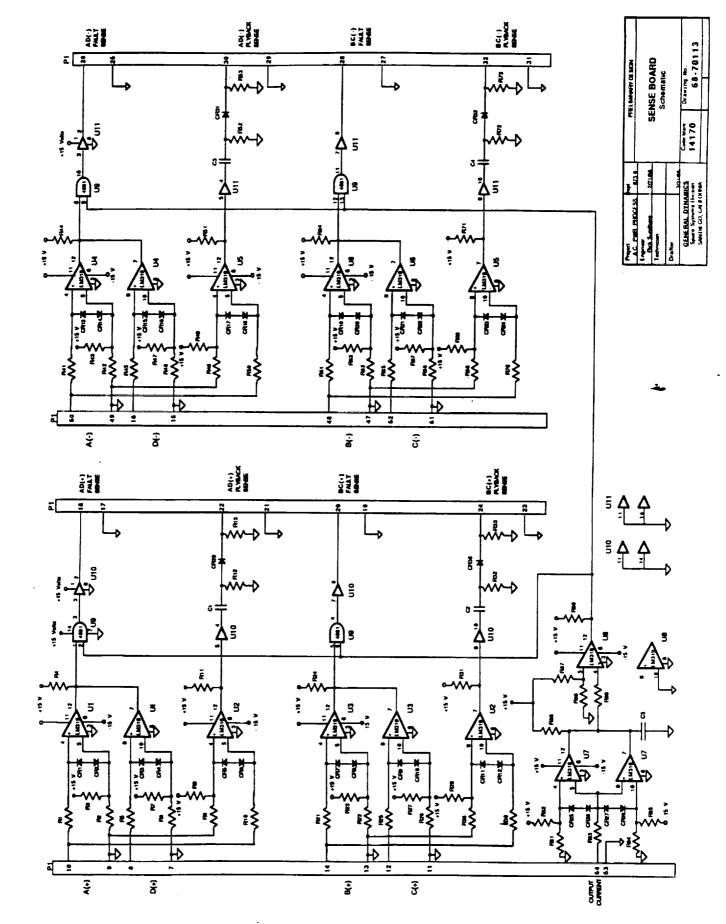

The housekeeping module is specifically designed to interface the logical functions with the control of the individual power switches in a single driver or receiver module. In addition, it became a "catch all" for those miscellaneous operations not clearly belonging somewhere else, but always required for operation. The housekeeping module appears in every application (driver or receiver) module, while multiples or subsets of the others are used, depending on the application. It performs the following detailed functions.

**Outputs:** Since the most general case of an application module has anti-parallel pairs of thyristor-family power switches in each of the four bridge driver or receiver positions, eight individual logic level command outputs are required.

Inputs: On the input side, this module processes several signals:

- Input polarity signals for low frequency AC power (V<sub>cc</sub>) inputs.

- Enable signals which determine that the bridge currents have been proper to fire the next set of thyristors.

- Zero crossing indicators for "flyback" thyristor firing.

- The primary firing signals from the system clock.

- Line fault clearing command.

**Functions:** The module acts on those input signals to provide outputs according to the following functions:

CR 175070

Final Report Contract No. NAS 3-23878

- Logically control the 40-kHz clock to provide appropriate thyristor firing signals for 20-kHz output generation.

- Invert the sense of the firing logic in response to a negative power input polarity.

- Provide "flyback" thyristor firing signals, appropriately timed with respect to the zero crossings of the primary current.

- Inhibit the outputs if the "proper current enable" signal is not received.

- Provide a zero output for line fault clearing, if commanded.

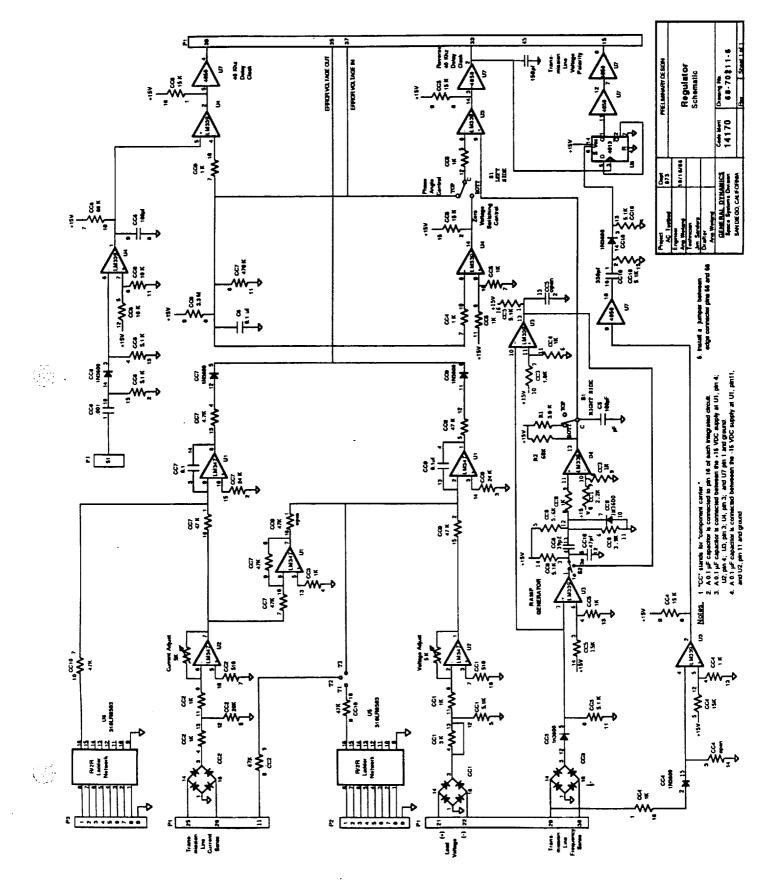

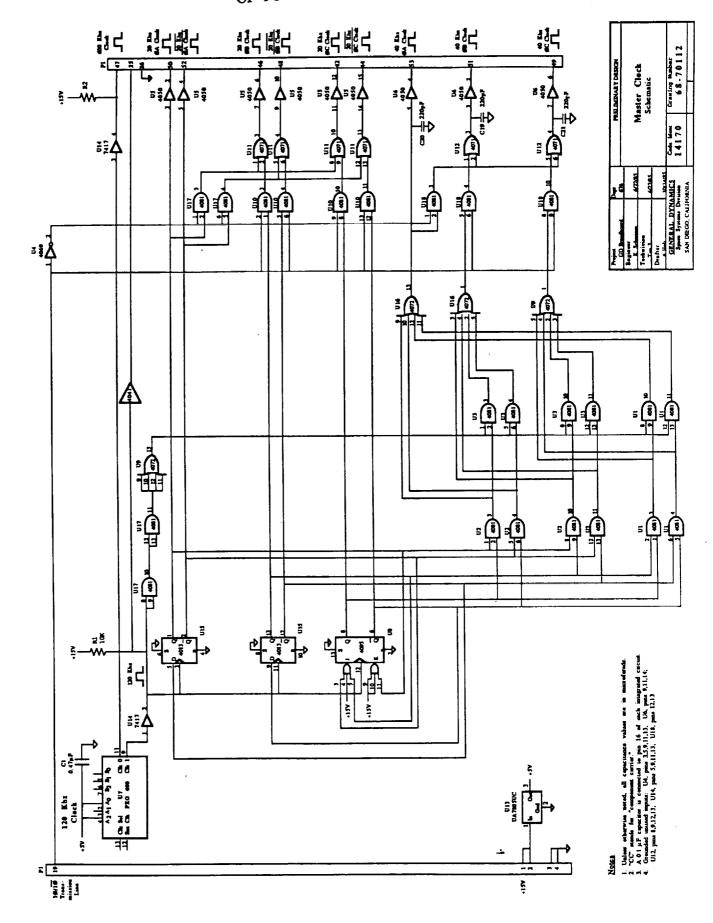

Since the digital design process to implement these functions is straight forward and not mysterious, it will not be recounted here. The final result, is documented as the module schematic, Figure 4-1.

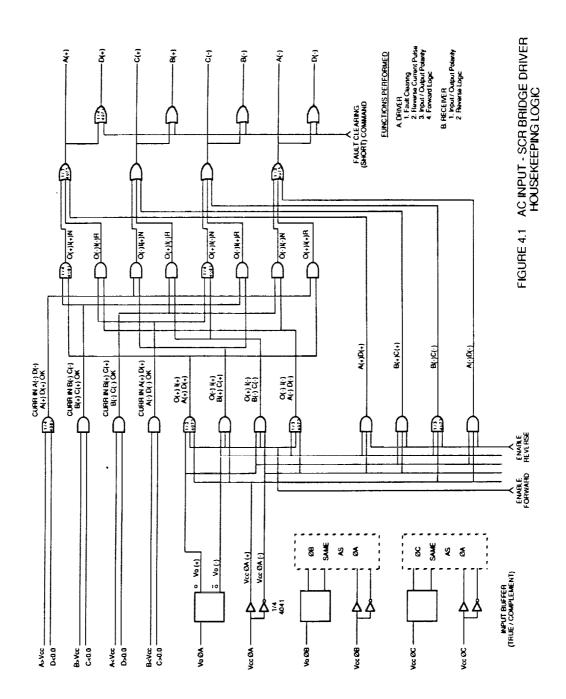

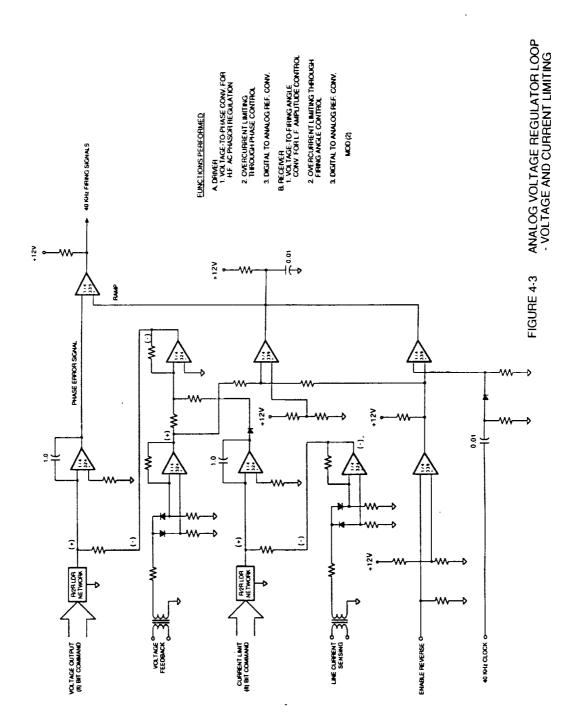

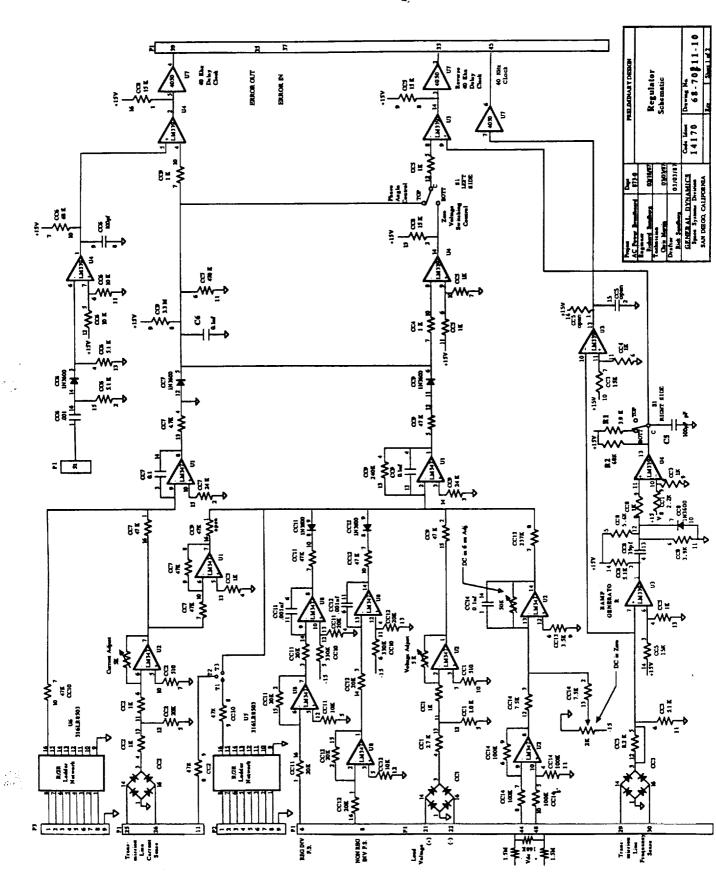

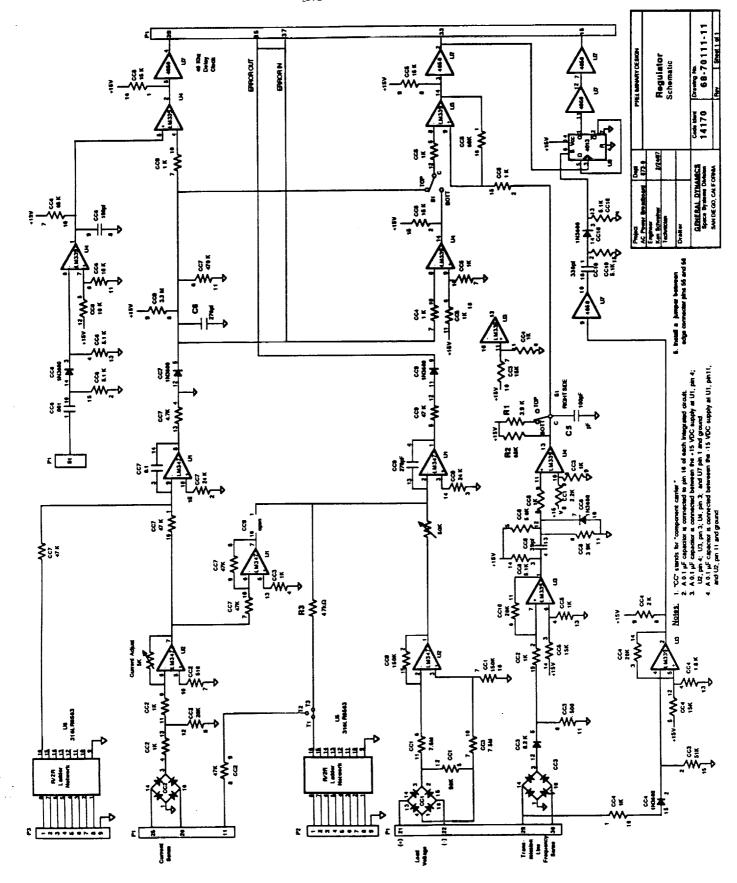

#### 4.3.2 Regulation Control

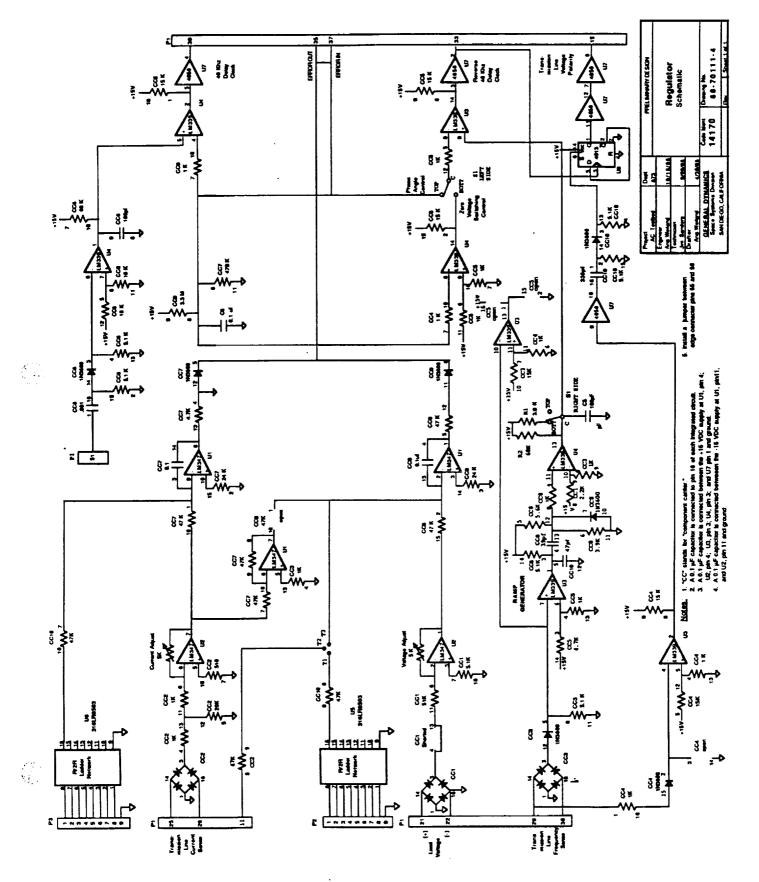

**Receiver Regulation:** Receiver modules basically provide full wave rectification, individual 20-kHz half-sine pulse steering, and output filtering to create DC or low frequency AC; as required by user loads. Regulation is accomplished in one of two ways: Pulse population, by sending or omitting full half-sine 25µsecond pulses, or phase delay regulation of each half-sine pulse. The regulation loop is a conventional first order servo loop design which samples the output voltage and compares it to a digitally-generated reference signal. Output current is also detected and used with a similar higher-gain loop to provide an overriding limit function.

**Driver Regulation:** Since the receiver loop design acts on single 20-kHz half-sine pulses, its response is also appropriate for driver regulation. The driver case only requires the phase delay output mode; to delay driver clock signals to the second of two series-connected drivers, for our AC "Phasor" regulation of the high frequency (20-kHz) power bus.

Phasor Regulation puts the outputs of two or more drivers in series, and then controls the relative phase angle between them, by controlling the clock phase. That control is based on a comparison between a digitally-generated reference signal and a feedback signal from the output voltage. The output magnitude is therefore controlled by the classical addition of two (or more) AC voltages

12.5

which are the same frequency, but different phase. The resultant is the vector addition of the two output phasors. (See Figure 4-2.) In this case, the power bus voltage and current are both sampled and compared with digitally-generated references with the same analog loop.

Because of the nearly identical operational requirements, it was possible for us to design a single analog module for both jobs, which then became the standard regulator "building block" module. Its schematic is shown as Figure 4-3.

Since the phase delay output control has unity gain and zero phase shift in the frequency domain of interest (as shown by R.D.Middlebrook,see Reference 5), and the analog portion is clearly single order, the control loop is unconditionally stable over a wide control range. The final design has a useful frequency response in the 3-kHz range with a DC gain approaching the open loop operational amplifier gain. High frequency characteristics, and therefore also transient response, are controlled by the characteristics of the resonant output network in the driver module.

#### 4.3.3. AC Output Frequency Synthesis and Control

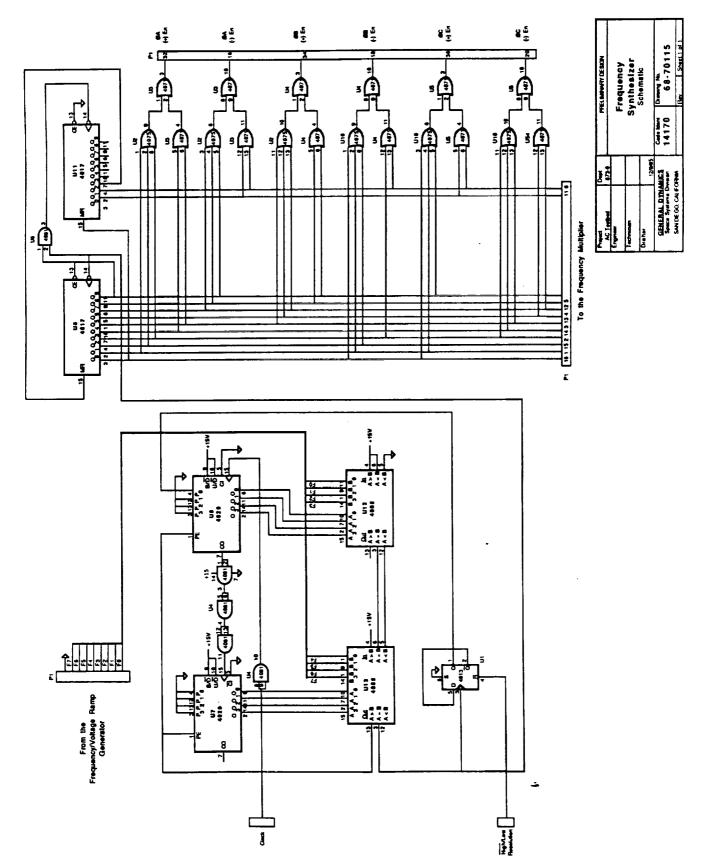

The synthesis of low frequency AC outputs to a three phase user load (typically an AC permanent magnet or induction motor) represents the most complex of the functional building blocks developed by this program. The contract requirements demand the ability to provide a wide range of output frequencies, and to change frequencies in an orderly, controlled way for motor starting and speed control. While a single module was designed, its major functions are discussed separately below for the sake of clarity.

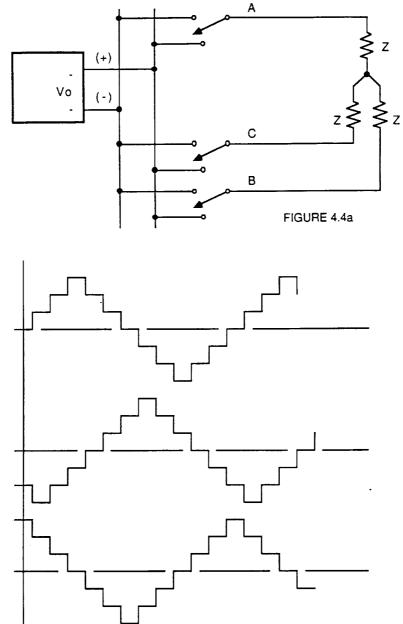

**Output Level Control:** The method used to create the various output levels without resorting to analog control uses the different impedances seen at the various inputs of the typical "Y" connected motor. Referring to Figure 4-4a, if we connect the "+" output to phase B, and the "return" to phase C, there is no current in phase A, +V/2Z in phase B, and -V/2Z in phase C, as plotted in figure 4-4b. In the next 30° period, we connect "+" to phase A and B, and "return" to phase C, the currents are as shown in the second segment of 4-4b.

Next, we connect "+" to A, open B, and "return" to C, and get +V/2Z in A and -V/2Z in C. As we alternately connect and not connect a phase, and rotate those states around the three phase positions, the complete waveform shown in Figure 4-4b is constructed. You can see that the levels approximate a sine wave and the phase relationships of the currents in the three phases of the load are appropriate to normal three phase operation. Thus, a very reasonable three phase sine construction is accomplished, with only switching, with the additional systematic advantage that the low frequency current modulation in the line is only 25% peak.

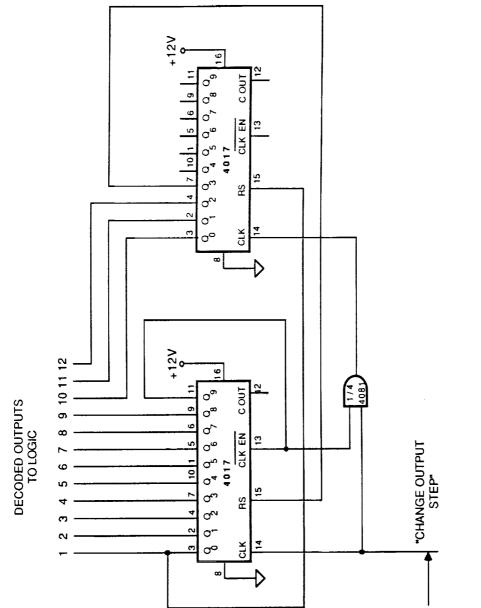

The logic to steer thyristor firing signals to the appropriate outputs is again straight forward, and shown in Figure 4-5. It simply counts through the twelve sequential output states in response to a "change output step" signal from the countdown logic.

**Frequency Control:** Steady state frequency control is accomplished by "counting down" the half-sine pulses of the 20-kHz AC power bus input and steering them to the appropriate outputs to synthesize a full cycle of the low frequency output with twelve steps or voltage levels. Therefore, the highest frequency available, while still keeping the twelve steps is:

$f_{\rm H} = 1/(25\mu \sec x \ 12) = 3.3$ -kHz

The next lower frequency would use two pulses per step and:

$f_H = 1/(25\mu \sec x 24) = 1.167$ -kHz

Since the frequency granularity is poor at or near the high frequency limits, a different method of division (using the same basic principle) was later developed, but this program and the subsequent Testbed programs with which it interfaced were not changed, since the basic technique proved the principle satisfactorily.

The actual circuitry had to be designed to count down any number of pulses, depending on the receiver output frequency required. A "comparison counter" is

al privatione de la state de la estate

CR 175070 Contract No. NAS 3-23878

> used as shown in Figure 4-6. The number of pulses per output level is inputed to a digital comparator, and each 20-kHz half-sine pulse incremented a counter. When the comparator senses an equality, the counter is reset and a "change output step" signal is sent to the "amplitude control logic".

> **Frequency Change Control:** The last function to be performed by this module is the controlled, orderly change of output frequency in response to a digital input command or analog feedback signal. In this way, motor speed changes or start up characteristics (constant torque or V/F) can be controlled. To that end, a comparison counter was also used. See Figure 4-7. The initial frequency value is loaded into an up-down counter as a preset value. The final frequency is set into the comparator. Count direction is controlled by whether the final value is higher or lower than the initial preset. The instantaneous counter value is the input to the "frequency control comparator". The "frequency change counter" is incremented by a clock whose rate is dependent on either a digitally-commanded input or an analog feedback, depending on the mode desired.

#### 4.3.4. High Frequency System Clock

To operate a single inverter/driver with a 20-kHz AC output, a train of 40-kHz clock pulses are required. One clock pulse is required for each independent output switch state change, to generate a (+) or (-) half-sine output pulse.

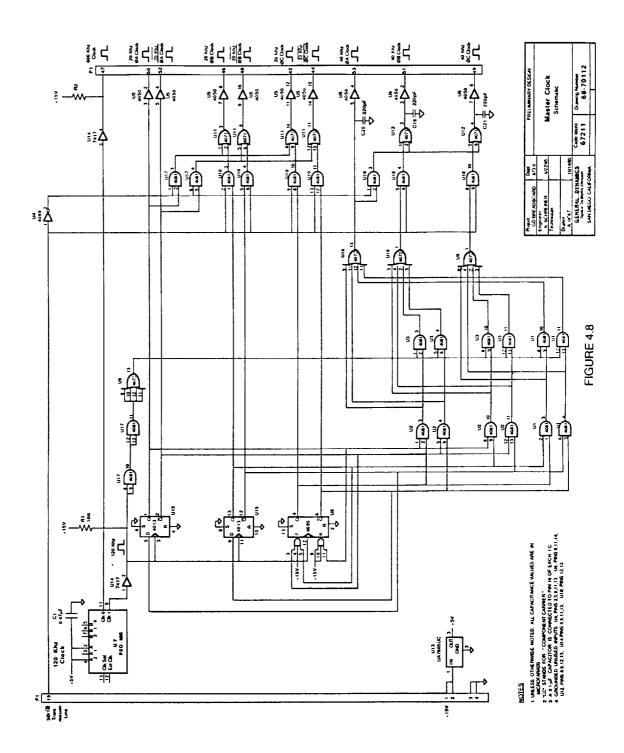

The system requirements are for single-phase or three-phase 20-kHz outputs. Therefore, three independent clock pulse trains must be synthesized, which are synchronized and phase shifted from one another to produce the required 120 electrical degree shift in the 20-kHz power outputs. We elected to provide the required set of signals totally with digital processing, to guarantee the constancy and accuracy the three related output signals.

Therefore, the basic required clock signal is 120-kHz, the lowest frequency that can be counted down to three 40-kHz pulse trains with the necessary 120° output relationship. A fully-developed flight type system would derive this higher frequency signal from a crystal controlled oscillator or use a related computer clock. Even though this program is primarily a demonstration of the

overall control functions, and that level of accuracy was not required, we used a crystal controlled 120-kHz oscillator module to make sure that frequency variations are eliminated as variables which could effect the other data taken during testing. (See Figure 4-8.)

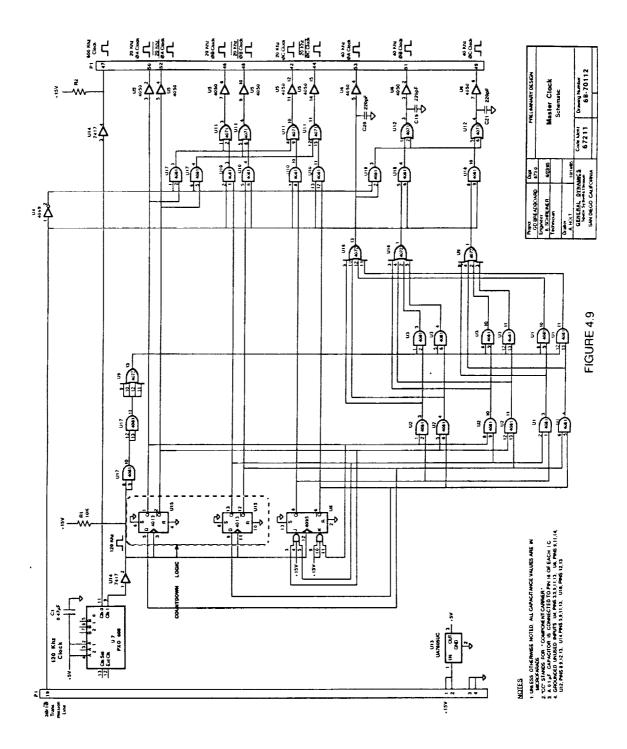

The count-down logic for the related 40-kHz outputs is of the classical type, and it is shown in Figure 4-9.

Switch S-1 is used to switch the three outputs so that they are in-phase, making the power outputs that they control into three independent single phase units, in phase with one another. In this mode the controlled modules could be connected in series or parallel for use in single phase power systems.

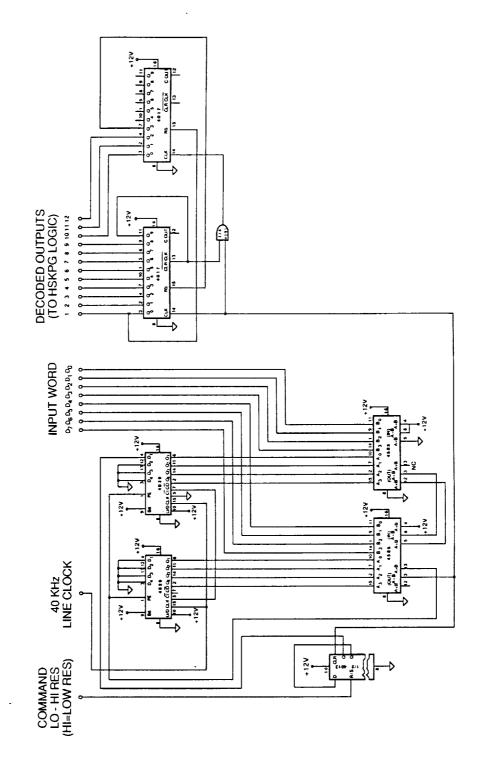

#### 4.3.5. Digital input interfacing and storage

Since the overall supervisory control of all modern systems of this type will be via computers, it is necessary to design this equipment to be compatible with digital command inputs and outputs, from a data bus.

This development is far in advance of the selection of a serial data bus technology and type for any of its anticipated missions. For control of this type of hardware, all serial data is ultimately reduced to a parallel input word, with a number of bits appropriate to the resolution and accuracy required by the application. Therefore, we elected to use a simple parallel data input to demonstrate compatibility with digital control, assuming that standard data bus to parallel output converters would be used, from the communication technology finally chosen for the individual applications.

One additional arbitrary choice was made. Since computer data is routinely stored in eight bit "bytes", and the related logic hardware is generally partitioned in "fours" and "eights", we elected to use eight bit resolution for this demonstration hardware, while making sure that the basic technology would easily expand to support higher resolutions, where they were identified and required. This decision made the granularity of some controlled functions (such as receiver output frequency) somewhat coarse, but provided the necessary

demonstration of the techniques to validate the principles, and also would allow for easy later expansion to higher resolutions.

There are four basic types of input command functions:

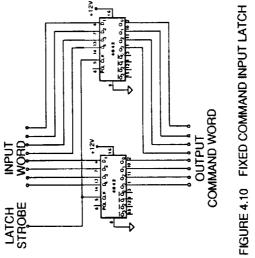

**Eight-bit digital word storage.** This was implemented with a simple eight-bit, clocked latch, from 4000-series CMOS series logic, as shown in Figure 4-10.

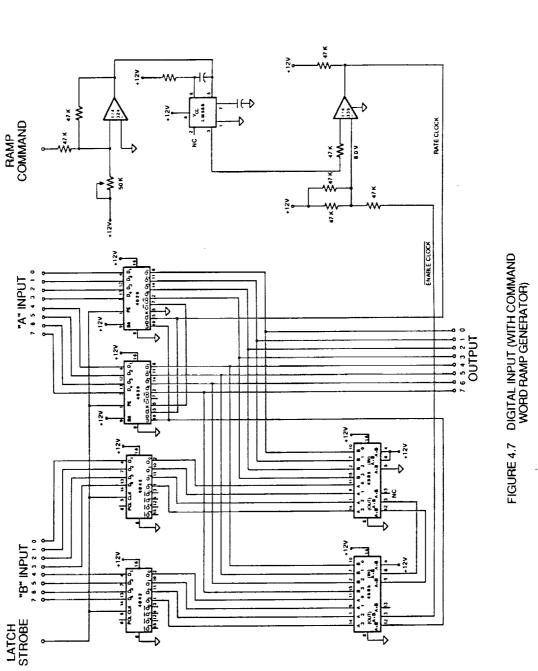

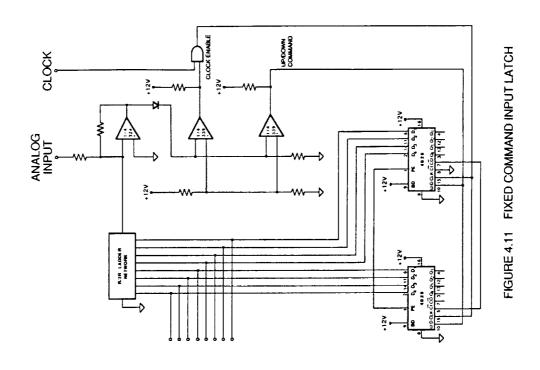

Analog loop reference signals. An eight-bit, clocked latch, with outputs connected to an R-2R ladder network, in the usual digital to analog converter manner, provides for the analog value to be summed with a feedback signal to derive the required control loop error signal. See Figure 4-11 and Section 4.3.2 for additional details.

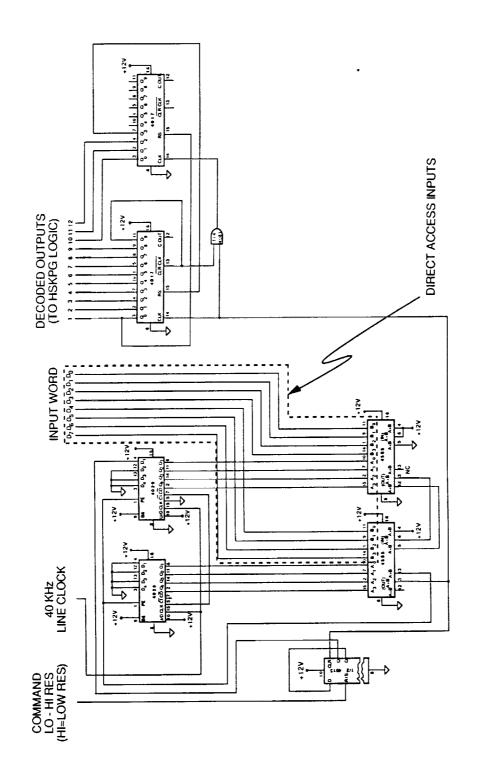

**Direct digital word storage interfaces.** Some functions already have digital input storage capability, and no additional latched storage is required. The comparison counter used in receiver frequency synthesis can be accessed directly with parallel digital inputs, which are loaded when the counters and comparator are strobed. See Figure 4-12 and Section 4.3.3 for details.

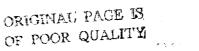

Analog data. Since some functions (ie. frequency synthesis) are digitally implemented and have inputs from analog sources, those interfaces require analog to digital conversions. The ultimate goal of the building blocks developed in this program is large scale custom or semi-custom integrated circuits. Therefore, a simple A-to-D converter function was implemented with the same series hardware selected for the other building blocks, rather than use an already developed separate A-to-D device. See Figure 4-13.

#### 4.4. Construction of Application Specific Functions

#### 4.4.1. Case 1, On-board Battery Charging from the High Frequency Bus

The requirement for on-board battery interface control generates the need for bidirectional operation. The basic housekeeping/short protection logic described

in Section 3.1 provides all the necessary control function for the single-module reverse (source) mode.

When operated as a receiver (load interface), bus power is applied to the same high frequency interface (as if it were a driver) and the switches are sequenced to provide full wave rectified power at the  $V_{CC}$  terminals. Therefore, high frequency polarity inputs must be supplied to the logic to control switch sequencing for output polarity control. Equivalent clock signals to operate the logic are generated from the high frequency bus input.

The added control function for this case is output current regulation. To avoid the complication and power losses associated with a separate, additional DC output regulator, it was decided to use the existing switches to control power output by phase delay switching. This creates a functional requirement for an analog to digital regulator circuit that either delays the clock pulses to the control logic, an amount controlled by the output current feedback.

#### **Functional Implementation**

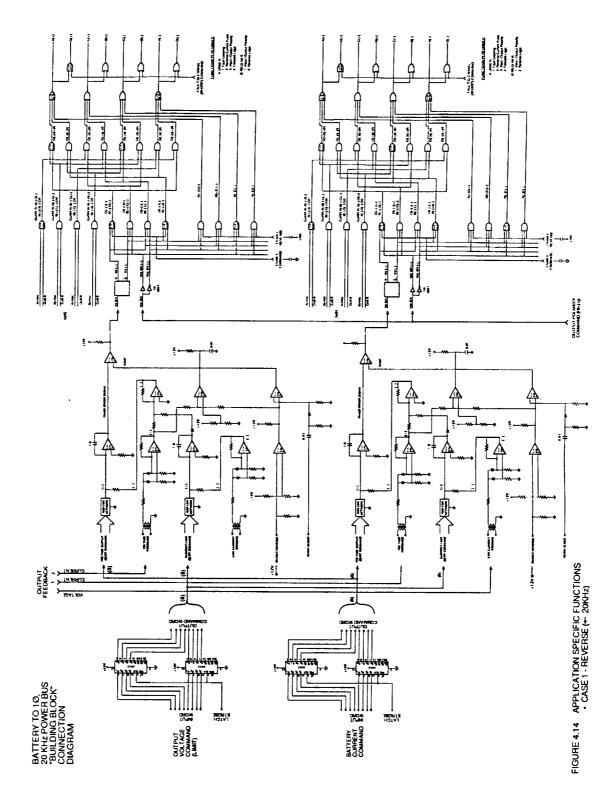

The reverse (source) mode requires two power modules for high frequency power bus regulation, using the Phasor technique. Therefore, two housekeeping blocks are required, one for each set of power outputs. Since the clock signals for one power module need to be shifted and controlled, one regulator block is required. Digital commands for output voltage magnitude and output current limiting are supplied to the analog loop references by two latch/digital-to-analog input blocks. Finally, a 40-kHz clock input is required. Figure 4-14 shows the entire configuration.

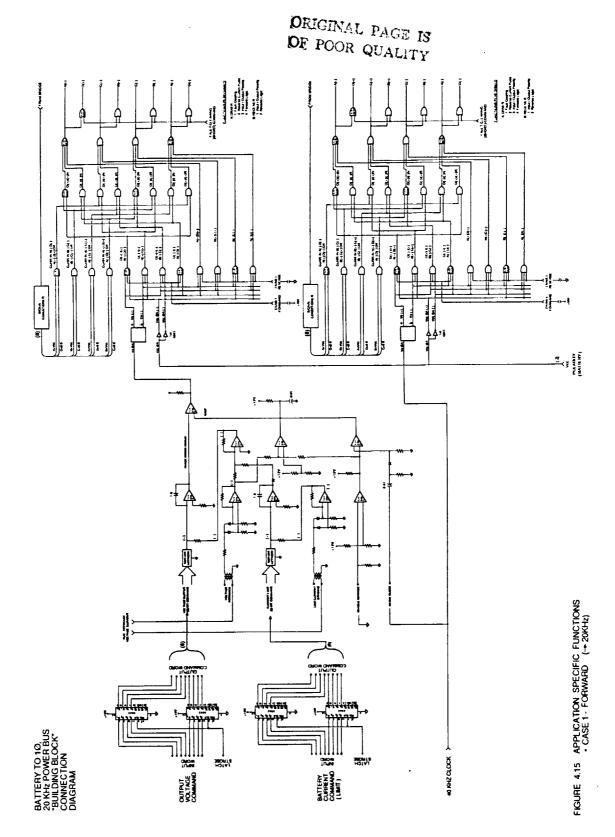

The forward (receiver) mode would only require a single power output module. However, since two are required for the source mode, their DC outputs are simply paralleled for this mode. In this case, output regulation is provided by phase of pulse population control of the rectified output, and a regulator block is required for each module, adding one to the total configuration. The same input latches provide the voltage and current references, now shared by the two regulator blocks. See Figure 4-15. This now represents the total bidirectional DC configuration.

### 4.4.2. Case 2, Auxiliary Ground Power or AC Power Energizing the High Frequency Bus.

Requirements for the housekeeping logic already would enable the circuitry to deal with AC inputs. The only consequence of simply using the AC  $V_{CC}$  equivalent would be that the output high frequency would be amplitude modulated at the AC power input frequency. A simple solution is to use a three phase source (one phase powering each of three driver modules) and add the outputs by putting them in series. With this arrangement, the high frequency signals are all in phase, adding directly, and their modulation envelopes are in the usual three phase relationship, adding to a nearly constant high frequency AC power bus output.

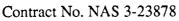

#### **Functional Implementation**

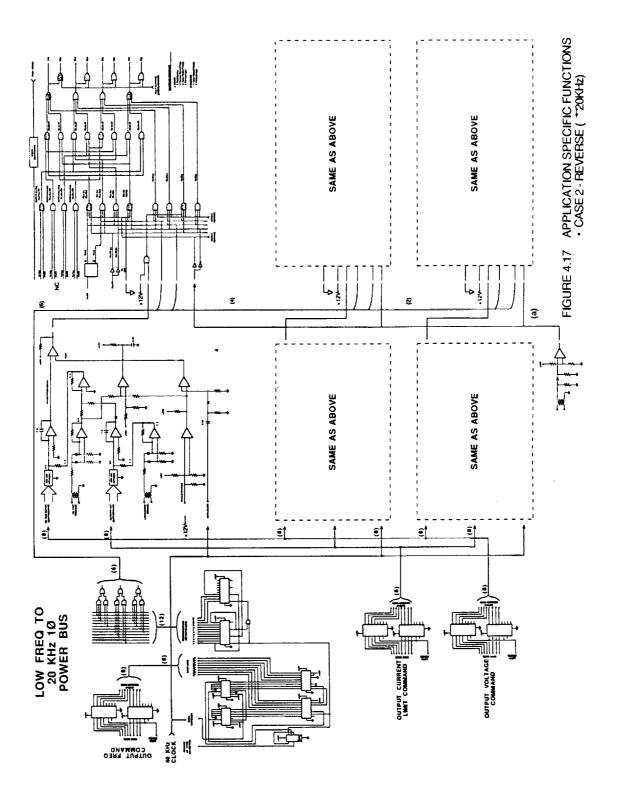

To provide the three phase output addition, three power modules are required, with their output transformers connected in series. Therefore, three housekeeping blocks are used. For regulation, the phases of the power modules are controlled; one is held fixed, the second is shifted the normal amount, and the third is shifted twice that amount, for a three-phasor regulator addition. Two regulator blocks are required, one for each shifted module. Digital commands for output voltage magnitude and output current limiting are supplied to the analog loop references by two latch/digital-to-analog input blocks. Finally, a 40-kHz clock input is required. Figure 4-16 shows thee configuration for the forward mode. Figure 4-17 shows the reverse mode.

### 4.4.3. Case 3, Variable speed Motor/Generator starting/ running/generation to and from the high frequency bus.

This application is the most complex of the specific requirements. The preceding two cases can be subsets of this most general case. Control circuitry designed to meet the requirements of case 2 will meet the generator/generation requirements of this case. The requirements for Bidirectional operation and output regulation (which can be used for low frequency motor output amplitude

control) are developed in case 1. The remaining added functions are for frequency control of the output to the motor. They include a range of fixed frequencies, ramped frequency changes at constant rates or rates based on analog feedbacks for constant V/F control or constant torque starting.

#### **Functional Implementation**

**Reverse** (source) operation is the simpler of the two operational modes for this function. It is identical to source mode operation of the AC module of Section 4.4.2. See Figure 4-16.

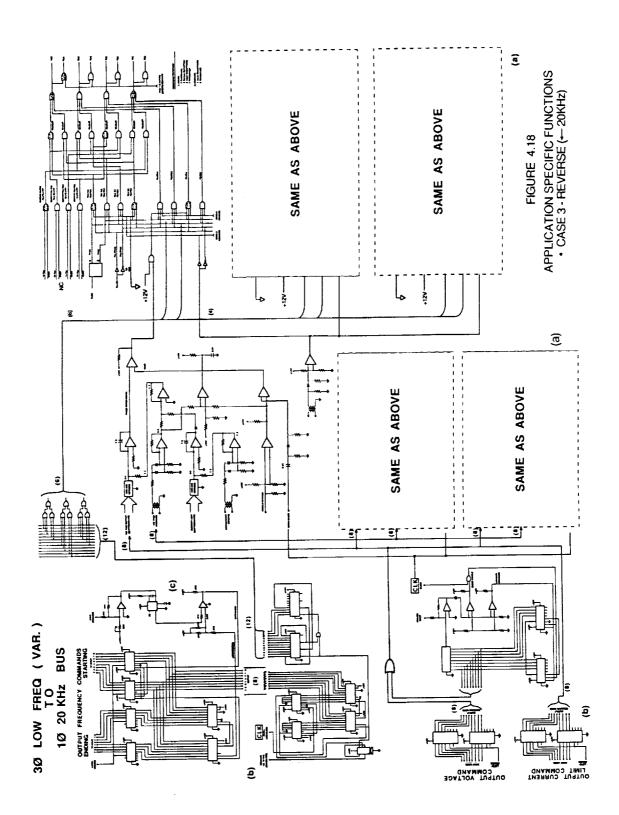

Forward (load) operation is significantly more complex. See Figure 4-18a. Three output power modules and their three housekeeping blocks are still required. Phase control or pulse population control of the rectified outputs for each motor phase is now needed, adding another regulator module, for a total of three. Shared digital commands for output voltage magnitude and output current limiting can still be supplied to the analog loop references by two latch/digitalto-analog input blocks; and the 40-kHz clock input is required.

Frequency synthesis logic blocks are added to control the sequencing of the output power switches to steer 20-kHz half-sine pulses to the appropriate motor terminals. Their detailed operation is described in Section 4.3.3. Interconnections for this operational mode are shown on Figure 4-18b. Starting and ending frequencies are stored in standard clocked latch building blocks, and the analog feedback is conditioned and scaled by an operational amplifier circuit. See Figure 4-18c.

CR 175070 Contract No. NAS 3-23878 Final Report

### **5.0** Construction and Test

#### 5.1 Initial Testing

The first step to verify proper operation and satisfaction of the requirements was to construct and test a set of "wire wrap" circuit boards, each of which would represent one of the basic building blocks. A sufficient number was constructed to separately assemble and test the three application specific functions. They were mounted in a card cage containing the appropriate interconnections. Since the outputs provided logic level signals only, they were connected to a buffered set of LED indicators, each of which represented an SCR in an application specific power processing module. The real time clock was not used for this testing, since output LED indications would have been too fast to reliably observe and judge for proper operation. Single pulses were applied instead and output states were noted and compared to a predetermined truth table.

Only minor troubleshooting was required to achieve proper operation in all cases, and meet all the requirements of the original contract.

#### 5.2 High Power Compatibility Testing

As described in the introduction, the contract was extended and modified to include tests to demonstrate compatibility; first, with General Dynamics' breadboard power hardware; and later, with LeRC's testbed power hardware. The contract included authorization and sufficient funds to provide for these compatibility tests, but not for any changes or redesigns as a result of them, and additional funding was not included in the contract changes.

#### 5.2.1. Power Breadboard

During full power, real time breadboard testing, some incompatibilities were discovered. Since the testing was performed on General Dynamics' IRAD hardware, in the midst of an IRAD development program, the determination of design changes to assure full compatibility was accomplished on that program. A full set of updated schematics is included in this report as Appendix C.

#### Page 21

#### PRECEDING PAGE BLANK NOT FILMED

Final Report

CR 175070 Contract No. NAS 3-23878

### 5.2.2. 25 KW Testbed

Changes developed during breadboard testing were incorporated into the circuit boards designed for the LeRC 25-kW Power System Testbed. Compatibility with this higher power equipment was then demonstrated during troubleshooting and checkout of that hardware, and is verified by observation of its proper operation.

CR 175070

Final Report Contract No. NAS 3-23878

### 6.0 Delivery and Final Hardware Disposition

Since the basic designs developed by this contract were ultimately incorporated into hardware which demonstrates the full set of system equipment appropriate to a Space Station power channel, it was decided that there was no need to provide additional funding to rework the original set of functional blocks, and update it to the latest configuration. Therefore, they were simply delivered in that state to satisfy the hardware delivery requirement in the contract, with the real "home" for the final designs being the 25-kW testbed hardware also delivered to LeRC.

CR 175070 Contract No. NAS 3-23878 Final Report

CR 175070

Final Report Contract No. NAS 3-23878

### 7.0 Conclusions and Recommendations

The following conclusions and recommendations are based on testing performed at the logic level outputs for this specific development, and the results of the testing using the circuit functional blocks with actual General Dynamics and NASA testbed hardware.

### 7.1 Conclusions

- 7.1.1 It is practical to develop a family of special-purpose circuit modules, that can then be used in appropriate combinations to construct the necessary functional circuits required to operate a family of direct-generation, resonant power processors.

- 7.1.2 This program proved the designs for the following circuit modules:

- Housekeeping

- Analog Control (Regulator)

- Digital Input Interfacing and Storage

- High-Frequency (20-kHz and 40-kHz) System Clock

- Receiver Output Control, including low-frequency AC Output Synthesis

- 7.1.3 These modules were used to prove the construction of the required major power processing hardware control circuits:

- Case 1: On-board battery charging from the high frequency bus (Bidirectional DC Interface)

- Case 2: Auxiliary ground power energizing the high frequency bus (Three-phase, 60-Hz, AC Source Interface)

- Variable-speed motor/generator starting/running/generation to and from the high frequency bus (Three-phase, Variable-frequency, Bidirectional AC Interface)

- 7.1.4 These modules can effectively partitioned to incorporate their functions into semi-custom integrated circuits, using gate array or PAL technology.

# PRECEDING PAGE BLANK NOT FILMED

### 7.2 Recommendations

- 7.2.1 Proceed with the development of an integrated circuit implementation to demonstrate the feasibility of that approach.

- 7.2.2 Develop additional module designs to accommodate the new families of power switching devices now becoming available. (MCT's and IGT's)

$x \in \{x_i\}$

CR 175070

# 8.0 Figures

This Chapter is a collection of the figures from the main body of this report. They are numbered in accordance with the original chapter in which their reference first appears.

Page 27

· ·

Final Report

CR 175070 Contract No. NAS 3-23878

Figure 2-1, The Schwarz configuration has the load in series with the resonant circuit.

Figure 2-2, The Mapham circuit has the load in parallel with the resonant capacitor.

Figure 2-3, Basic Inverter Power Stage

Page 28

· "我们是你是你的,我们还是你们,我们不知道,你们们还是你的你们,你们就是你不是你的事情,你不是你不是你。"

Page 29

$X_{i} = \{i,j\}$

.

. - .

Final Report

CR 175070 Contract No. NAS 3-23878

ORIGINAL PAGE IS OF POOR QUALITY

Page 30

CR 175070

CR 175070 Contract No. NAS 3-23878

÷.,

CR 175070

FIGURE 4.4b

•

CR 175070 Contract No. NAS 3-23878

٠.

Page 34

Final Report

FIGURE 4.6 LOW FREQUENCY OUTPUT SYNTHESIS MODULE

CR 175070

Page 35

1.16

1.1

${\bf v}_{\mathbf{r}} = {\bf v}_{\mathbf{r}}$

з. <sup>с</sup>.

$\mathbf{r}$

Final Report

Page 36

ومتدافعا الإجاب

ORIGINAL PAGE IS OF POOR QUALITY

Page 37

$\mathcal{L} \in \{1, \dots, n\}$

ORIGINAL FAGE IS OF POOR QUALITY

ALITY

Final Report

Final Report

FIGURE 4.12 LOW FREQUENCY OUTPUT SYNTHESIS MODULE

CR 175070 Contract No. NAS 3-23878

Page 40

Final Report

Contract No. NAS 3-23878

Page 41

CR 175070

Final Report

$(x_{i},y_{i}) \in \mathbb{R}^{n}$

.

Page 42 .

ORIGINAL PAGE IS OF POOR QUA

÷

CR 175070

Final Report

•••••

ORIGINAL PAGE IS OF PCOR QUALITY

Page 45

2,1

1.1

CR 175070

Final Report

Page 46

## 9.0 Tables

This Chapter is a collection of the tables from the main body of this report. They are numbered in accordance with the original chapter in which their reference first appears.

•.•

## Table 3-1, Control Interface Specifications (continued)

|                     | Parameter                               | Conditions                                      | Min.           | Typ.     | Max.       | Units    |

|---------------------|-----------------------------------------|-------------------------------------------------|----------------|----------|------------|----------|

| С                   | D40M                                    |                                                 |                |          |            |          |

| PHL P               | ropagation Delay Time High to Low Level | $V_{DD} = 5.0V$ $V_{DD} = 10V$                  |                | 35<br>25 | 50<br>40   | ns<br>ns |

| l <sub>PLH</sub> Pr | ropagation Delay Time Low to High Level | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |                | 35<br>25 | 65<br>40   | ns<br>ns |

| t <sub>THL</sub> Tr | ransition Time Hign to Low Level        | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |                | 65<br>35 | 125<br>70  | ns<br>ns |

| t <sub>⊤LH</sub> Tr | ransition Time Low to High Level        | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |                | 65<br>35 | 175<br>75  | ns<br>ns |

| C <sub>'N</sub> In  | put Capacitance                         | Any Input                                       | 1              | 5.0      |            | pF       |

| C                   | D40++C                                  |                                                 | <del>.</del> . |          |            |          |

| laht bu             | ropagation Delay Time High to Low Level | $V_{DD} = 5.0V$ $V_{DD} = 10V$                  |                | 35<br>25 | 80<br>55   | ns<br>ns |

| t <sub>PLH</sub> Pr | ropagation Delay Time Low to High Level | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |                | 35<br>25 | 120<br>65  | ns<br>ns |

| t <sub>⊤∺L</sub> Tr | ransition Time High to Low Level        | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |                | 65<br>35 | 200<br>115 | ns<br>ns |

| t <sub>TLH</sub> Tr | ransition Time Low to High Level        | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |                | 65<br>35 | 300<br>125 | ns<br>ns |

| C <sub>IN</sub> In  | put Capacitance                         | Any Input                                       |                | 5.0      |            | pF       |

Table 3-1, Control Interface Specifications

| /oltage an Any Pin<br>Operating Temperature R | V <sub>SS</sub> – 0.3 V to V <sub>DD</sub> + 0.3 V<br>ange<br>–55°C to +125°C<br>–40°C to +85°C | Packa<br>Opera | ige Diss<br>ting V <sub>D</sub> | peraturi<br>Sipation<br>D Rangi<br>ature (S | e            | V    | -6<br><sub>55</sub> + 3.0<br>(conds) |            | +150°C<br>500 mW<br>s + 15 V<br>300°C |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------|----------------|---------------------------------|---------------------------------------------|--------------|------|--------------------------------------|------------|---------------------------------------|

| DC Electrical Ch                              | aracteristics                                                                                   |                |                                 |                                             | Limits       |      |                                      |            |                                       |

| Parameter                                     | Conditions                                                                                      | -5:<br>Min.    | 5°C<br>Max.                     | Min.                                        | 25°C<br>Typ. | Max. | 125<br>Min.                          | °C<br>Max. | Units                                 |

| Quiescent Device                              | V <sub>DD</sub> = 5.0V                                                                          |                | 0.05                            |                                             | 0.001        | 0.05 |                                      | 3.0        | -A                                    |

| Current                                       | $V_{DD} = 10V$                                                                                  | 1              | 0.1                             |                                             | 0.001        | 0.1  |                                      | 6.0        | Aږ                                    |

| Po Quiescent Device                           | $V_{DD} = 5.0V$                                                                                 |                | 0.25                            |                                             | 0.005        | 0.25 |                                      | 15         | _w                                    |

| Dissipation/Package                           |                                                                                                 |                | 1.0                             | 1                                           | 0.01         | 1.0  | <br>                                 | 60         | _w                                    |

| Vol. Output Voltage Low                       | $V_{DD} = 5.0V$ . $V_1 = V_{DD}$ . $I_0 = 0A$                                                   | :              | 0.05                            |                                             | 0            | 0.05 |                                      | 0.05       | V                                     |

| Level                                         | $V_{DD} = 10V, V_1 = V_{DD}, I_0 = 0A$                                                          |                | 0.05                            |                                             | 0            | 0.05 | i                                    | 0.05       | V                                     |

| V <sub>CH</sub> Output Voltage Higr           | $V_{DD} = 5.0V, V_1 = V_{SS}, I_0 = 0A$                                                         | 4.95           | }                               | 4.95                                        | 5.0          |      | 4.95                                 |            | v                                     |

| Level                                         | $V_{DD} = 10V, V_1 = V_{SS}, I_C = 0A$                                                          | 9.95           |                                 | 9.95                                        | 10           |      | 9.95                                 | ĺ          | V                                     |

| V <sub>NL</sub> Noise Immunity                | $V_{DD} = 5.0V, V_{O} = 3.6V, I_{O} = 0A$                                                       | 1.5            |                                 | 1.5                                         | 2.25         |      | 1.4                                  |            | V                                     |

| (All Inputs)                                  | $V_{OD} = 10V, V_O = 7.2V, I_O = 0A$                                                            | 3.0            |                                 | 3.0                                         | 4.5          |      | 2.9                                  |            | V                                     |

| V <sub>NH</sub> Noise Immunity                | $V_{DD} = 5.0V, V_{O} = 0.95V, I_{O} = 0A$                                                      | 1.4            |                                 | 1.5                                         | 2.25         |      | 1.5                                  | ĺ          | V                                     |

| (All Inputs)                                  | $V_{DD} = 10V, V_{O} = 2.9V, I_{O} = 0A$                                                        | 2.9            |                                 | 3.0                                         | 4.5          |      | 3.0                                  |            | V .                                   |

|                                               | $V_{DD} = 5.0V, V_{D} = 0.4V, V_{I} = V_{DD}$                                                   | 0.5            |                                 | 0.40                                        | 1.0          |      | 0.28                                 |            | mA<br>mA                              |

| N-Channel (4001)                              | $V_{DD} = 10V, V_{O} = 0.5V, V_{I} = V_{DD}$                                                    | 1.1            |                                 | 0.9                                         | 2.5          |      | 0.65                                 |            | mA                                    |

|                                               | $V_{DD} = 5.0V, V_{O} = 2.5V, V_{I} = V_{SS}$                                                   | -0.62          |                                 | -0.5                                        | -2.0         |      | -0.35                                |            | mA                                    |

| P-Channel (4001)                              | $V_{DD} = 10V, V_{O} = 9.5V, V_{I} = V_{SS}$                                                    | -0.62          |                                 | -0.5                                        | -1.0         |      | -0.35                                |            | mA                                    |

| IDN Output Drive Curren                       |                                                                                                 | 0.31           |                                 | 0.25                                        | 0.5          |      | 0.175                                |            | mA<br>mA                              |

| N-Channel (4011)                              | $V_{DD} = 10V, V_{O} = 0.5V, V_{I} = V_{DD}$                                                    | 0.63           |                                 | 0.5                                         | 0.6          |      |                                      |            |                                       |

| I <sub>D</sub> P Output Drive Curren          |                                                                                                 | -0.31          |                                 | -0.25                                       | -0.5         |      | -0.175                               |            | mA<br>mA                              |

| P-Channel (4011)                              | $V_{DD} = 10V, V_{O} = 9.5V, V_{I} = V_{SS}$                                                    | -0.75          |                                 | 0.0                                         | 10           |      | -0.4                                 |            | pA                                    |

| I <sub>I</sub> Input Current                  |                                                                                                 |                | 1                               |                                             |              | 1    |                                      | I          | 1 PA                                  |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

•

Final Report

Page 50

$|q_{i}| = 1 + \epsilon$

• • •

•

and the second second

#### **10.0 References**

- 1."Study of Power Management Technology for Orbital Multi-100kWe Applications"; Final Report, NASA CR 159834; J.W.Mildice, General Dynamics, Convair Division

- "Study of Multi-Megawatt Technology Needs for Photovoltaic Space Power Systems"; Final Report, NAS 3-21951; D.M.Peterson, General Dynamics, Convair Division

- 3. "An SCR Inverter with Good Regulation Sine-Wave Output"; Neville Mapham, IEEE Transactions on Industry and General Applications; IGA-3, No. 2, Apr-May, 1967

- 4. "Bidirectional Four Quadrant (BD4Q) Power Converter Development", Final Report, NASA CR 159660, F.C.Schwarz, Power Electronics Assoc. Inc.

- 5. "Predicting Modulator Phase Lag in PWM Converter Feedback Loops", R. D. Middlebrook, Powercon 8, April 27-30, 1981

- 6. "Controllable Four-Quadrant AC to DC and AC Converter Employing an Integral High Frequency Series Resonant Link"; U.S.Patent 4,096,557, June, 1978

- 7. "A Practical Resonant Converter Using High Speed Power Darlington Transistors"; Suridar R. Babu, General Electric Co., Auburn, NY, PCI March, 1982 Proceedings, pp 122-141

- "Advances in Series Resonant Inverter Technology and Its Effect on Spacecraft Employing Electric Propulsion"; R.R.Robson, Hughes Research Labs, Malibu, CA, presented at AIA/UASS/OGLR 16th International Electric Propulsion Conference, November, 1982.

#### PRECEDING PAGE BLANK NOT FILMED

Page 51

. . . .

. . .

المرجوع فيتحدث وتركب المرجع والمرجع وا

\_\_\_\_

.,

...

Final Report

## Appendices

| A. Design Requirements Specification | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 35 |

|--------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| B. Functional Block Worksheets       | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 37 |

| C. Updated Schematics                | • | • |   |   |   |   |   |   |   |   | • |   |   | • |   |   |   |   | 39 |

# PRECEDING PAGE BLANK NOT FILMED

Page 53

•

. .

٠,

and a state of

Final Report

CR 175070

#### Appendix A

## **Functional Requirements Specification**

This appendix is a copy of the detailed Functional Requirements Specification, which was written to provide a set of requirements to which the hardware could actually be designed. It was approved by NASA LeRC prior to the hardware design phase of the program.

#### PRECEDING PAGE BLANK NOT FILMED

15

Final Report

÷.,

## DESIGN REQUIREMENTS SPECIFICATION

the second se

#### Bi-Directional Power Control Electronics Unit

NASA Contract: NAS 3-23878

#### 1.0 GENERAL

This controller is a device which provides the interface and control functions between the power handling devices and the supervisory system computer outputs for bi-directional power conversion between DC or low-frequency AC and the high-frequency AC power transmission bus. While the basic design is for computer control through parallel digital words, the hardware delivered on this contract shall be capable of operation from set-points commanded by manual inputs from the unit control panel.

- 1.1 The overall system actions performed by the integrated computer (or manual control) - controller - power switch combination are supplied by a family of modules, having the following characteristics:

- 1.1.1 Generator Intertace Takes variable, low frequency, engine-driven generator power and transforms it to controlled, high-fixed-frequency, AC distribution bus power.

- 1.1.2 Motor Interface Provides variable frequency, variable voltage start, and run power to AC three-phase actuator and/or synchronous (PM) and induction starting motors for airborne functions, from the high-frequency AC distribution bus.

- 1.1.3 Battery Interface Acts as a battery charger to interface the battery system with the high-frequency AC distribution busses. In its source mode, it converts battery power to high-frequency AC distribution bus power. The combination acts as the source for an uninterruptable power system.

- 1.1.4 Ground Power Interface Provides power in either direction between the high-frequency AC distribution system and a three-phase AC ground power supply operating at 60 or 400 Hz.

#### 2.0 APPLICABLE DOCUMENTS

The following documents, to the extent specified herein, shall apply to the design, construction, and documentation of this controller.

2.1 Contract NAS 3-23878

- 2.2 MIL-STD-746A, for EMI design considerations

- 2.3 MIL-HNDBK-217B, for reliability and failure rate considerations, to evaluate selective design component redundancy.

- 2.4 GDC-ACW67-006, Report Writer's Guide; for reports and documentation

- 2.5 Division Standard Practice C90 Series; for hardware construction and documentation

#### 3.0 FUNCTIONAL/OPERATIONAL DISCRIPTIONS

This unit acts as a "smart" electronic interface/controller between the electrical power system Mode Commands and the high power hardware in the system and performs the following specific functions:

. . . **.** .

- 3.1 Commanded Functions in response to a digital word input simulated by a manually entered set-point from the control panel.

- 3.1.1 Dutput Amplitude Control This is the basic steady-state output voltage or power. A D to A converter provides an analog output reference signal to be used by the output regulator. It is maintained with no further inputs until commanded to change.

- 3.1.2 Mode Control Controls the basic nature of the three module types; determines whether they take power from the high-frequency AC distribution bus or supply power to it.

- 3.1.3 Time-varying Outputs The motor/generator interface module shall be capable of accepting inputs to command variable motor/generator frequency or voltage and their rate of change. It can command a constant V/F ratio or current limit for motor starting.

- 3.1.4 Output Frequency Setting of a steady-state output frequency for the motor interface to control motor speed.

- 3.1.5 Overload Limits Output current and/or voltage, above and/or below which fault isolation action is required.

- 3.2 Data Functions

engelege (\* 1977) en er er

Nr. 199

The following list of data measurement points shall be provided on the front panel of the unit. Values provided are nominals.

1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -

Condition associated SEE reasonant data and

3.2.1 High trequency bus: Frequency = 20.0 kHz Voltage = 440/460 VRMS AC (LL) Current = TBD Phase Angle = TBD Single-phase

3.2.2 Battery Charger Input/Output: Voltage = 140/280 VDC

Current = 180 Current or Voltage +eedback mode +lag 3.2.3 Auxiliary bround Power Input/Output: Voltage = 440/460 VRMS AC (LL)  $Current = \Gamma BD$ Frequency = 60 HzThree-phase 3.2.4 Variable-speed Motor/Generator Input: Voltage = variable, 300-450 VAC RMS Current = TBD Frequency = variable, range TBD Phase Angle = TBDThree-phase or Six-phase 3.2.5 Variable-speed Motor/Generator Output: Voltage = variable, range TBD Current = variable, range TBD Phase Angle = TBD Frequency = variable, range 0 to 600 Hz, (current limited); range 600 to 1200 Hz, (voltage limited) Three-phase or Six-phase

- 3.2.6 Starter/Generator shaft speed: Output perameters consistant with Table 4-1 Frequency = variable, range TBD

- 3.2.7 Status Flags; Dutput perameters consistant with lable 4-1: Current over limit Voltage over limit Voltage under limit Energy flow direction Fault status

- 3.2.8 Current sink for reflex battery charger: Characteristics and applicability FBD

#### 3.3 Other Functions

Motor start/run

3.3.1 Overload Limits - There are two levels of over current protection provided. The first raises an overload flag to the system controller advising of an out-of-spec condition that is not of immediate danger to the hardware. The second automatically turns the overloaded module off to protect itself.

3.3.2 Output Switch timing - shall be such that either/both

transistors and thyristors can be used as the main power switch elements.

1. **1.** . . .

.

·.

•

4.0 ELECTRONIC INTERFACE - DETAILED SPECIFICATIONS

4.1 Fower Supply Inputs:

- 4.1.1 Operating Voltage: 10.0 VDC to 14.0 VDC

- 4.1.2 Maximum Supply Voltage: 5.0 VDC to 17.0 VDC (for non-spec operation)

- 4.1.3 Damage Limits: (-)0.5 VDC to (+)20.0 VDC

- 4.1.4 Current: 1.0 amp, maximum, steady-state average

4.2 Control Interfaces

- 4.2.1 Set Point Control "Dip" switches, with BCD encoded outputs, to simulate computer control inputs.

- 4.2.2 Command Organization Eight bit parallel data, plus strobe.

- 4.2.3 Electrical Characteristics as specified in table 4-1.

- 4.3 Control Outputs All power control outputs are discrete commands, used to operate switched components, and have the characteristics specified in Table 4-1

- 4.4 Instrumentation Interface All signals shall be preconditioned to the following limits:

- 4.4.1 Analog Inputs: Input Voltage = 0.0 to 10.0 VDC Input Current = 0.0 to 25.0 mA DC Other characteristics in accordance with Table 4-1.

- 4.4.2 Discrete Inputs: In accordance with Table 4-1.

ORIGINAL FAGE IS OF POOR QUALITY

#### Table 4-1, Control Interface Specifications

1

٠,

| /olta<br>Operi   | ge an Any Pin<br>ating Temperature Rar<br>Electrical Cha | -55°C to -125°C<br>-40°C to -85°C                                                             | Packa<br>Opera | ge Diss<br>ting V <sub>D</sub> : | perature<br>lipation<br><sub>D</sub> Range<br>ature (Si | <u> </u>            | Vs   | s + 3.0 \    | Ę    | - 150°C<br>500 mW<br>s + 15 \<br>300°C |

|------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------|----------------------------------|---------------------------------------------------------|---------------------|------|--------------|------|----------------------------------------|

|                  | Electrical ona                                           |                                                                                               | i              |                                  | <del></del>                                             | Limits              |      |              |      |                                        |

|                  | Parameter                                                | Conditions                                                                                    | -55            | 5°C                              |                                                         | 25°C                |      | 125          | °C   | Units                                  |

|                  |                                                          |                                                                                               | Min.           | Max.                             | Min.                                                    | Тур.                | Max. | Min.         | Max. | ļ                                      |

| <br>1            | Quiescent Device                                         | V <sub>DD</sub> = 5.0V                                                                        |                | 0.05                             |                                                         | 0.001               | 0.05 |              | 3.0  | A.                                     |

| 'L               | Current                                                  | $V_{DD} = 10V$                                                                                |                | 0.1                              |                                                         | 0.001               | 0.1  |              | 6.0  | ∆رت<br>بير                             |

| Pa               | Quiescent Device                                         | V <sub>2D</sub> = 5.0V                                                                        |                | 0.25                             |                                                         | 0.005               | 0.25 |              | 15   | W<br>W                                 |

| . 0              | Dissidation Package                                      |                                                                                               |                | 1.0                              |                                                         | 0.01                | 1.0  |              | 60   | W                                      |

| Vai              | Output Voltage Low                                       | $V_{DD} = 5.0V$ , $V_1 = V_{DD}$ , $I_0 = 0A$                                                 |                | 0.05                             |                                                         | 0                   | 0.05 |              | 0.05 |                                        |

|                  | Level                                                    | $V_{DD} = 10V, V_1 = V_{DD}, I_0 = 0A$                                                        |                | 0.05                             |                                                         | 0                   | 0.05 |              | 0.05 |                                        |

| Vch              | Output Voltage High                                      | $V_{DD} = 5.0V$ . $V_1 = V_{SS}$ , $I_D = 0A$                                                 | 4.95           |                                  | 4.95                                                    | 5.0                 | 1    | 4.95<br>9.95 |      | v                                      |

|                  | Level                                                    | $V_{DD} = 10V. V_1 = V_{SS}, I_C = 0A$                                                        | 9.95           |                                  | 9.95                                                    | 10                  |      | 9.50         |      |                                        |

| V <sub>NL</sub>  | Noise Immunity                                           | $V_{DD} = 5.0V, V_C = 3.6V. I_0 = 0A$                                                         | 1.5            |                                  | 1.5<br>3.0                                              | 2.25                |      | 2.9          |      |                                        |

|                  | (All inputs)                                             | $V_{DD} = 10V, V_0 = 7.2V, I_0 = 0A$                                                          | 3.0            |                                  |                                                         | 4.5<br>2.25         |      | 1.5          |      |                                        |

| V <sub>N</sub> L | Noise immunity                                           | $V_{DD} = 5.0V$ . $V_{C} = 0.95V$ . $I_{C} = 0.4$                                             | 1.4            |                                  | 1.5<br>3.0                                              | ت <i>د.د</i><br>ع.د |      | 3.0          |      | v                                      |

|                  | (A.) Incuts.                                             | $V_{DD} = 10V, V_{D} = 2.9V, I_{D} = 3A$                                                      | 1 -            |                                  | 2.42                                                    | 1.0                 |      | 0.25         |      |                                        |

| ιcΝ              | Cutput Drive Current                                     | $V_{20} = 5.0V, V_{2} = 0.4V, V = V_{20}$                                                     | 0.5<br>1,1     |                                  | 0.5                                                     | 2.5                 |      | 2.65         | ļ    |                                        |

|                  | N-Onannel (4001)                                         | $V_{00} = 10V V_0 = 0.5V V_1 = V_{00}$                                                        | -0.62          |                                  | -0.5                                                    | -2.0                |      | -0.35        |      | m A                                    |

| ' <b>5</b> 2     | Output Drive Current<br>P-Channel (4001)                 | $V_{DD} = 5.0V, V_D = 2.5V, V_i = V_{SS}$<br>$V_{DD} = 10V, V_D = 9.5V, V_I = V_{SS}$         | -0.62          | 1                                | -0.5                                                    | -1.0                |      | -0.35        |      | mA                                     |

|                  |                                                          |                                                                                               | 0.31           |                                  | 0.25                                                    | 0.5                 |      | 0.175        |      | mA                                     |

| I <sub>D</sub> N | Output Drive Current<br>N-Channel (4011)                 | $V_{DD} = 5.0V, V_{O} = 0.4V, V_{I} = V_{DD}$<br>$V_{DD} = 10V, V_{O} = 0.5V, V_{I} = V_{DD}$ | 0.63           |                                  | 0.5                                                     | 0.6                 |      | 0.35         |      | mA                                     |

|                  |                                                          | $V_{DD} = 10V, V_0 = 0.5V, V_1 = V_{SS}$<br>$V_{DD} = 5.0V, V_0 = 2.5V, V_1 = V_{SS}$         | -0.31          |                                  | -0.25                                                   | -0.5                |      | -0.175       |      | mA                                     |

| IDP              | P-Channel (4011)                                         | $V_{DD} = 3.0V, V_0 = 2.5V, V_1 = V_{SS}$<br>$V_{DD} = 10V, V_0 = 9.5V, V_1 = V_{SS}$         | -0.75          |                                  | -0.6                                                    | -1.2                |      | -0.4         |      | m A                                    |

|                  |                                                          |                                                                                               | 1              | 1                                | 1                                                       | 1                   | 1    | 1            | 1    | A DA                                   |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

| Table 4-1, Control Interface | Specifications | (continued) |

|------------------------------|----------------|-------------|

|------------------------------|----------------|-------------|

.

|                   | Parameter                                | Conditions                                      | Min. | Тур.     | Max.       | Units    |

|-------------------|------------------------------------------|-------------------------------------------------|------|----------|------------|----------|

|                   | CD40++M                                  |                                                 |      |          |            |          |

| PHL               | Propagation Delay Time High to Low Level | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |      | 35<br>25 | 50<br>40   | ns<br>ns |

| lpLH              | Propagation Delay Time Low to High Level | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |      | 35<br>25 | 65<br>40   | ns<br>ns |

| t <sub>THL</sub>  | Transition Time Hign to Low Level        | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |      | 65<br>35 | 125<br>70  | ns<br>ns |

| t <del>т</del> шн | Transition Time Low to High Level        | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |      | 65<br>35 | 175<br>75  | ns<br>ns |

| C <sub>'N</sub>   | Input Capacitance                        | Any Input                                       |      | 5.0      |            | pF       |

|                   | CD40++C                                  |                                                 |      |          |            |          |

| ¦эн∟              | Propagation Delay Time High to Low Level | $V_{DD} = 5.0V$<br>$V_{DD} = 10V$               |      | 35<br>25 | 80<br>55   | ns<br>ns |

| t <u>pi u</u>     | Propagation Delay Time Low to High Level | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |      | 35<br>25 | 120<br>65  | ns<br>ns |

| t <sub>THL</sub>  | Transition Time High to Low Level        | V <sub>DD</sub> = 5.0V<br>V <sub>DD</sub> = 10V |      | 65<br>35 | 200<br>115 | ns<br>ns |