# NASA Contractor Report 182006

# IAPSA II Small-Scale System Specification

G. C. Cohen Boeing Advanced Systems Seattle, Washington

T. C. Torkelson Boeing Advanced Systems Seattle, Washington

NASA Contract NAS1-18099 March 1990

# NASA

National Aeronautics and Space Administration

Langley Research Center Hampton, Virginia 23665

(NAPA-CP-162006) IAPSA 2 SMALL-SCALE SYSTEM SPECIFICATION Final Report (Poeing Advanced Systems Co.) 316 P N90-24105

Unclus 63/36 0287444 •

#### PREFACE

This report describes the IAPSA II Small-Scale System Specification. This work was supported under NASA contract NAS1-10899, Integrated Airframe/Propulsion Control System Architecture (IAPSA II).

The NASA technical monitor for this work is Daniel L. Palumbo, of the NASA Langley Research Center, Hampton, Virginia.

The work was accomplished by the Flight Controls Technology organization of Boeing Advanced Systems in Seattle, Washington. Personnel responsible for the work performed include:

| D. Gangsaas      | Responsible Manager        |

|------------------|----------------------------|

| T. M. Richardson | Program Manager            |

| G. C. Cohen      | Principal Investigator     |

| T. C. Torkelson  | Flight Controls Technology |

ii

TABLE OF CONTENTS

|     |              |         |                                                  | PAGE |  |  |  |  |  |  |

|-----|--------------|---------|--------------------------------------------------|------|--|--|--|--|--|--|

| 1.0 | SUMMAR       | RΥ      |                                                  | 1    |  |  |  |  |  |  |

| 2.0 | INTRODUCTION |         |                                                  |      |  |  |  |  |  |  |

| 3.0 | DISCUSSION   |         |                                                  |      |  |  |  |  |  |  |

|     | 3.1          | General | Simulation Host Hardware Description             | 9    |  |  |  |  |  |  |

|     |              | 3.1.1   | VMEbus CPU Card                                  | 9    |  |  |  |  |  |  |

|     |              | 3.1.2   | Bulk VMEbus Memory                               | 9    |  |  |  |  |  |  |

|     |              | 3.1.3   | VME-MicroVAX Interface                           | 9    |  |  |  |  |  |  |

|     |              | 3.1.4   | DIU Simulators                                   | 13   |  |  |  |  |  |  |

|     |              | 3.1.5   | I/O Network Fault Insertion                      | 15   |  |  |  |  |  |  |

|     |              | 3.1.6   | Experiment Control and Experiment Bus            | 15   |  |  |  |  |  |  |

|     |              | 3.1.7   | VMEbus Experiment Time and Fault Insertion Delay | 16   |  |  |  |  |  |  |

|     | 3.2          | Develop | ment Support Hardware                            | 16   |  |  |  |  |  |  |

|     |              | 3.2.1   | Development Host Computer                        | 16   |  |  |  |  |  |  |

|     |              | 3.2.2   | Terminal Server                                  | 16   |  |  |  |  |  |  |

|     |              | 3.2.3   | Line Printer                                     | 17   |  |  |  |  |  |  |

|     |              | 3.2.4   | Logic Analyzer                                   | 17   |  |  |  |  |  |  |

|     |              | 3.2.5   | Microprocessor Emulators                         | 17   |  |  |  |  |  |  |

|     | 3.3          | General | Software Description                             | 17   |  |  |  |  |  |  |

|     |              | 3.3.1   | Experiment Software Interaction                  | 17   |  |  |  |  |  |  |

|     |              | 3.3.2   | Experiment Host Software                         | 19   |  |  |  |  |  |  |

|     |              | 3.3.3   | Simulation Host Software                         | 20   |  |  |  |  |  |  |

|     |              | 3.3.4   | DIU Simulator Software                           | 21   |  |  |  |  |  |  |

|     |              | 3.3.5   | AIPS FTP Software                                | 21   |  |  |  |  |  |  |

|     |              | 3.3.6   | Development Host Support Software                | 21   |  |  |  |  |  |  |

|     | 3.4          | Hardwar | e Modifications to AIPS Building Blocks          | 22   |  |  |  |  |  |  |

----

¥

RAGE 11 INTENTIONALLY BLANK

iii

# TABLE OF CONTENTS (Continued)

PAGE

| 3.5         | Simulation Host Hardware Details |                                             |            |  |  |

|-------------|----------------------------------|---------------------------------------------|------------|--|--|

|             | 3.5.1                            | VMEbus System Configuration                 | 22         |  |  |

|             | 3.5.2                            | Experiment Host - Simulation Host Interface | 24         |  |  |

|             | 3.5.3                            | VMEbus Backplane Modifications              | 33         |  |  |

|             | 3.5.4                            | DIU Simulator                               | 35         |  |  |

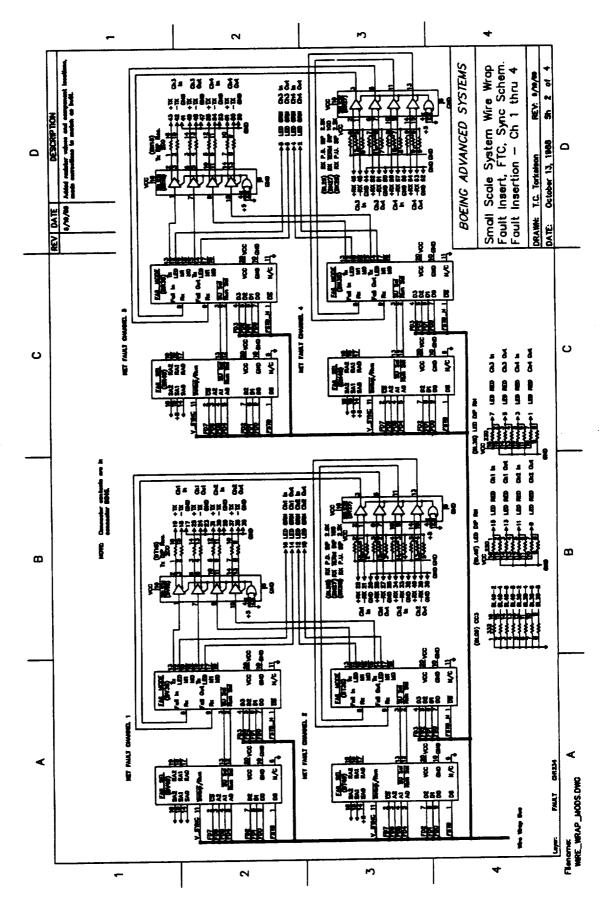

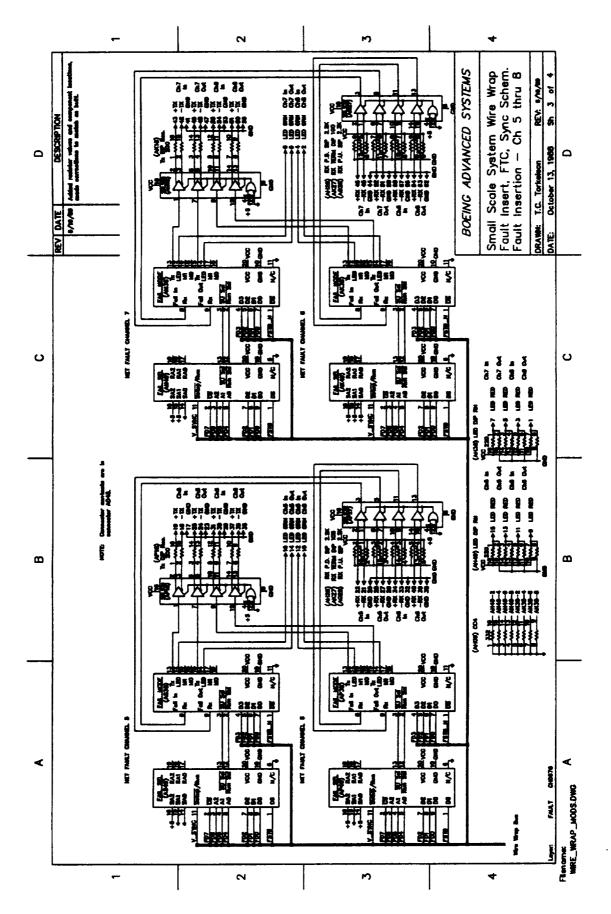

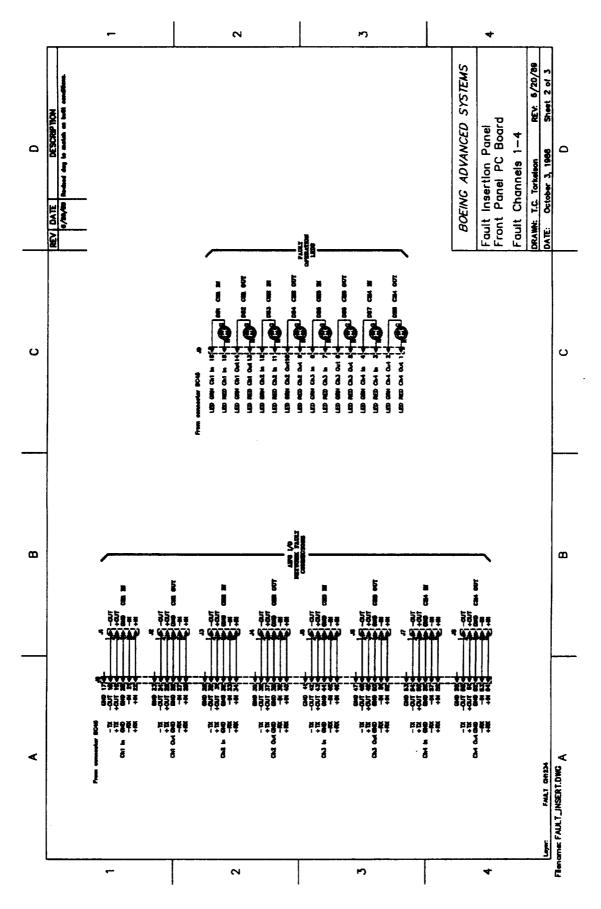

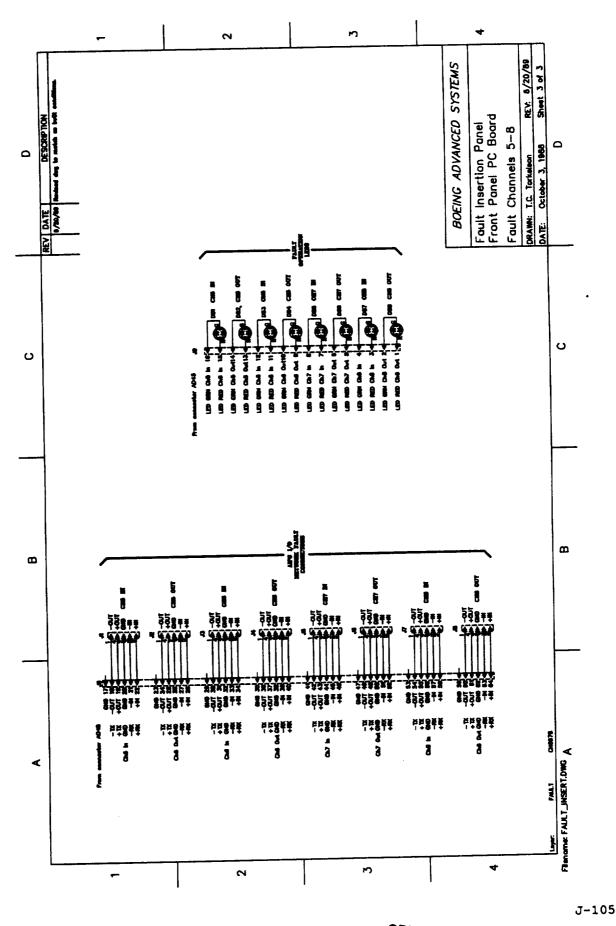

|             | 3.5.5                            | I/O Network Fault Inserter                  | 48         |  |  |

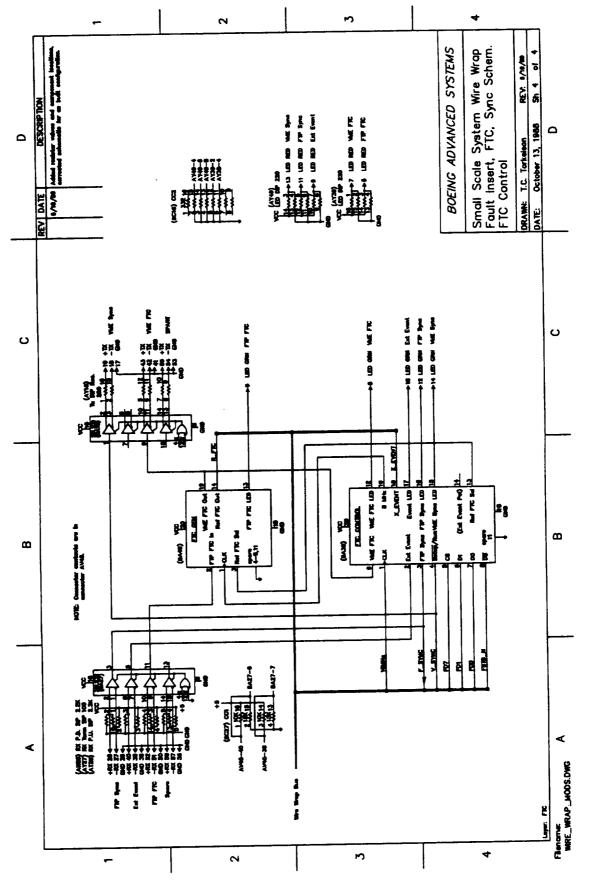

|             | 3.5.6                            | Miscellaneous Wire Wrap Board Functions     | 52         |  |  |

|             | 3.5.7                            | VMEbus Computer Timekeeping                 | 54         |  |  |

| 3.6         | Softwar                          | e Details                                   | 54         |  |  |

|             | 3.6.1                            | AIPS FTP System Services                    | 54         |  |  |

|             | 3.6.2                            | AIPS FTP Pseudoapplications                 | 55         |  |  |

|             | 3.6.3                            | VME System Kernel and Utilities             | 55         |  |  |

|             | 3.6.4                            | DIU Kernel                                  | 56         |  |  |

|             | 3.6.5                            | DIU Simulator                               | 56         |  |  |

|             | 3.6.6                            | I/O Network Probe                           | 58         |  |  |

|             | 3.6.7                            | DIU Data Formatting                         | 59         |  |  |

|             | 3.6.8                            | Fault Insertion Control                     | 59         |  |  |

|             | 3.6.9                            | VME Experiment Control                      | 59         |  |  |

|             | 3.6.10                           | MicroVAX Interface Software                 | 60         |  |  |

|             | 3.6.11                           | Experiment Control Command Files            | 60         |  |  |

| REFERENCES  |                                  |                                             | 62         |  |  |

| APPENDIX A: | SMALL-SC                         | ALE SYSTEM EXPERIMENT SYNCHRONIZATION       | A-1        |  |  |

| APPENDIX B: |                                  | NETWORK INTERFACE REQUIREMENTS              | B-1        |  |  |

| APPENDIX C: |                                  | ALE SYSTEM DIU SIMULATOR                    | Б-1<br>С-1 |  |  |

|             |                                  |                                             |            |  |  |

,

# TABLE OF CONTENTS (Continued)

|                                                                  | PAGB                        |

|------------------------------------------------------------------|-----------------------------|

| APPENDIX D: SMALL-SCALE SYSTEM NETWORK<br>INSERTION REQUIREMENTS | C FAULT D-1                 |

| APPENDIX E: SMALL-SCALE SYSTEM NETWORK                           | C/DIU CONFIGURATION E-1     |

| APPENDIX F: SMALL-SCALE SYSTEM I/O NET                           | TWORK TRANSACTIONS F-1      |

| APPENDIX G: EXPERIMENT BUS DESCRIPTION                           | N G-1                       |

| APPENDIX H: VULTURE PROGRAM DETAILS                              | H-1                         |

| APPENDIX I: SOFTWARE TAPE LISTING                                | I-1                         |

| APPENDIX J: DOCUMENTATION PACKAGES                               | J-1                         |

| Documentation Package A: VMEbus Simula<br>Configuration          | ation Computer J-1          |

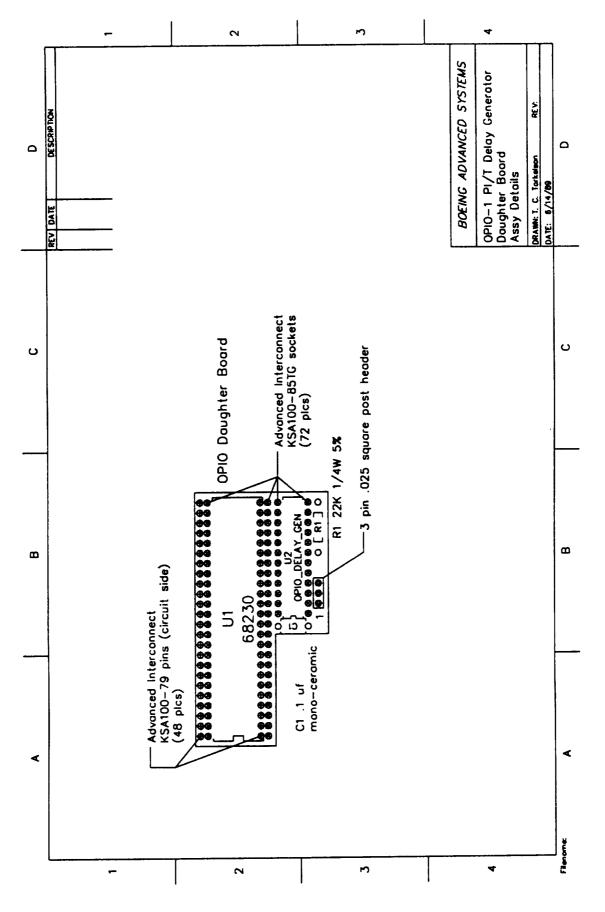

| Documentation Package B: OPIO-1 Paral<br>Interface Mod           |                             |

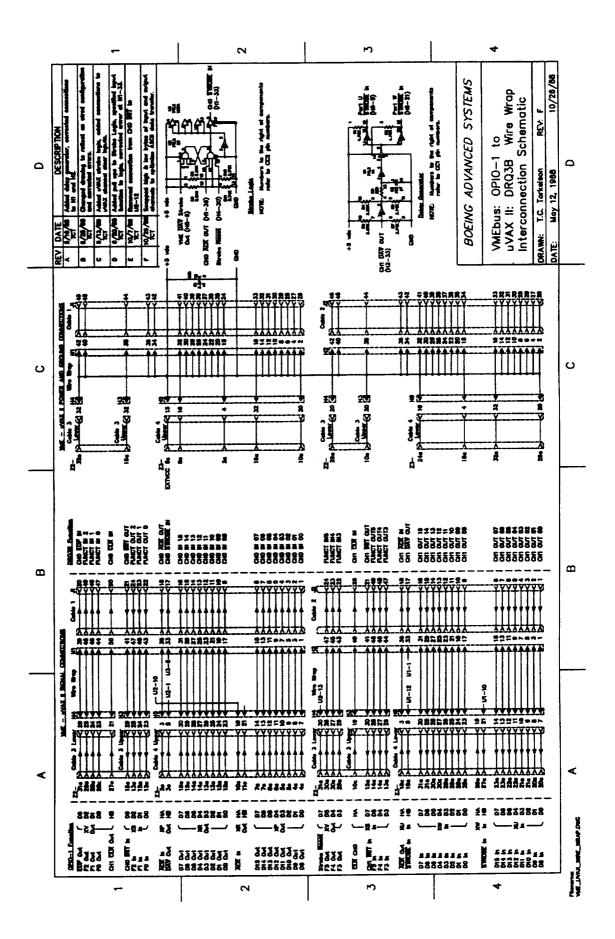

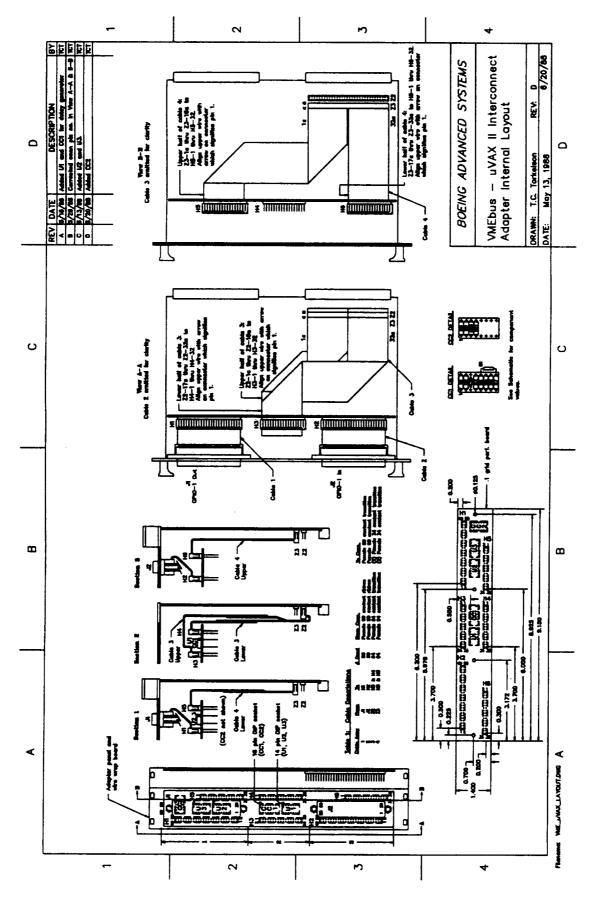

| Documentation Package C: VMEbus-Micro<br>Parallel Inte           | VAX J-23<br>erface Adapter  |

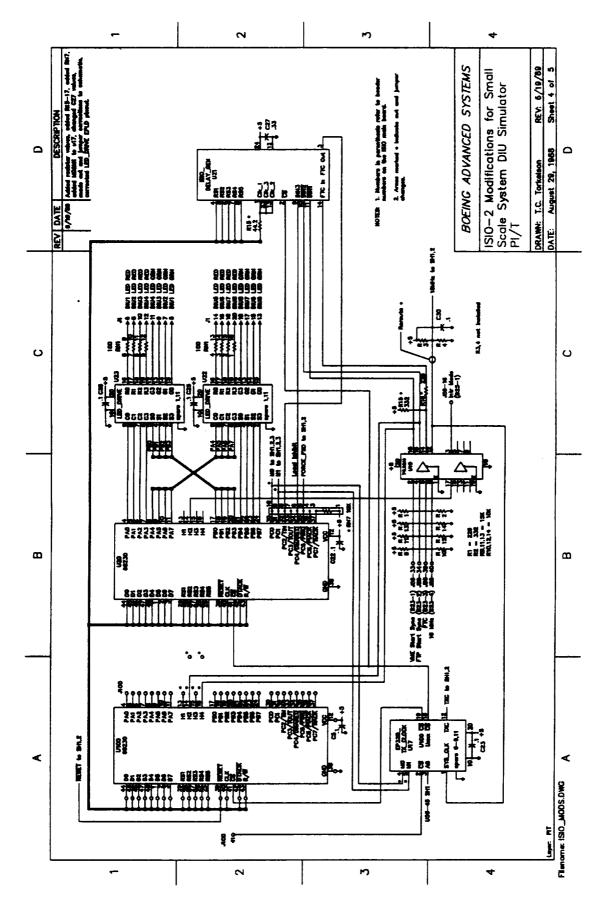

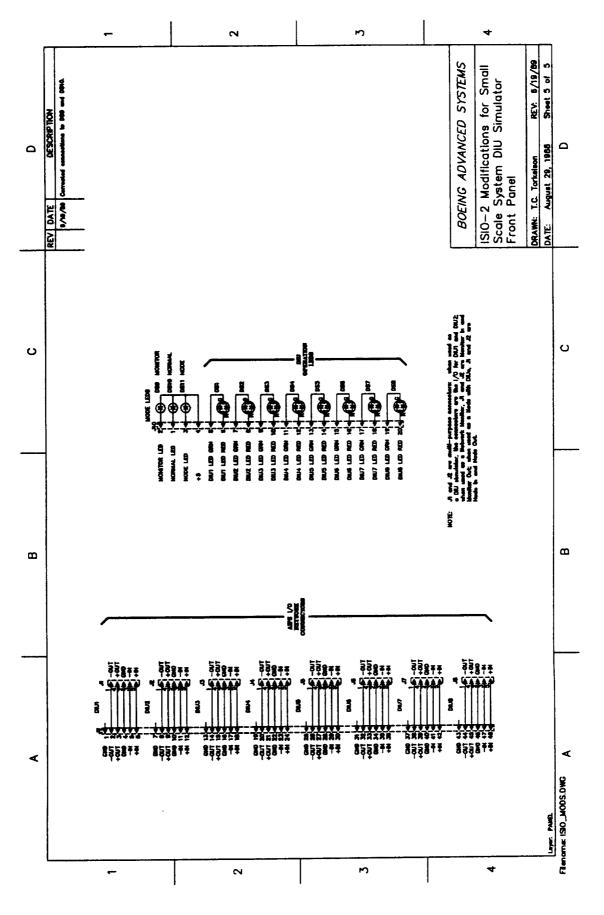

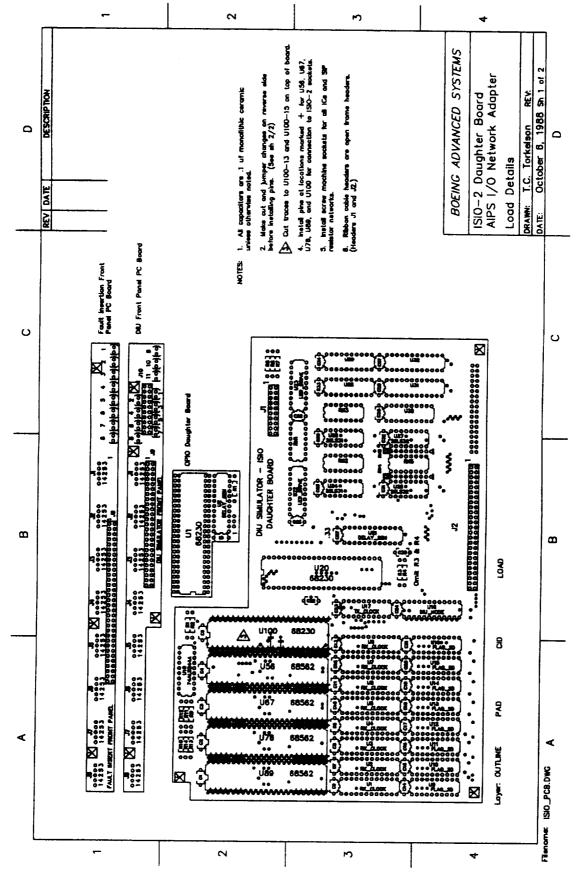

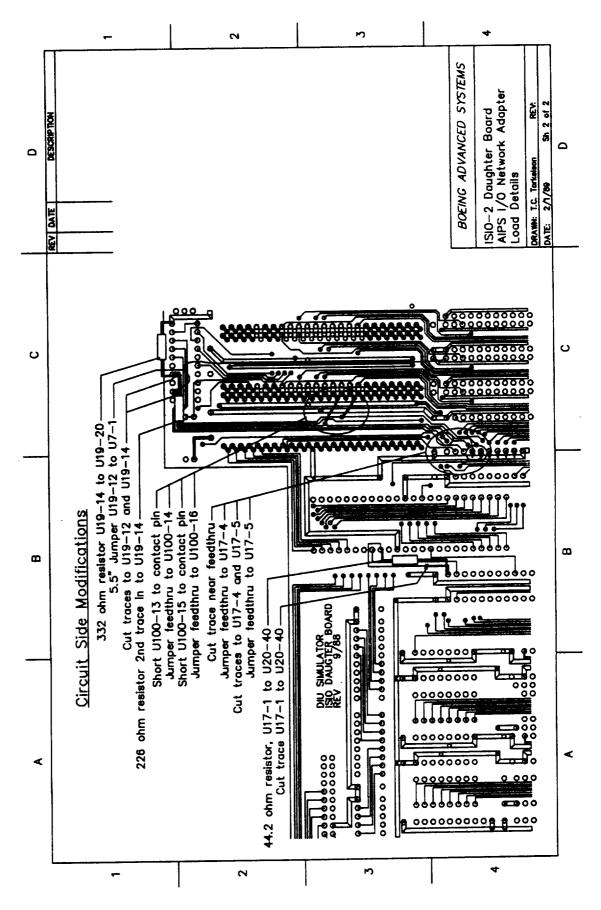

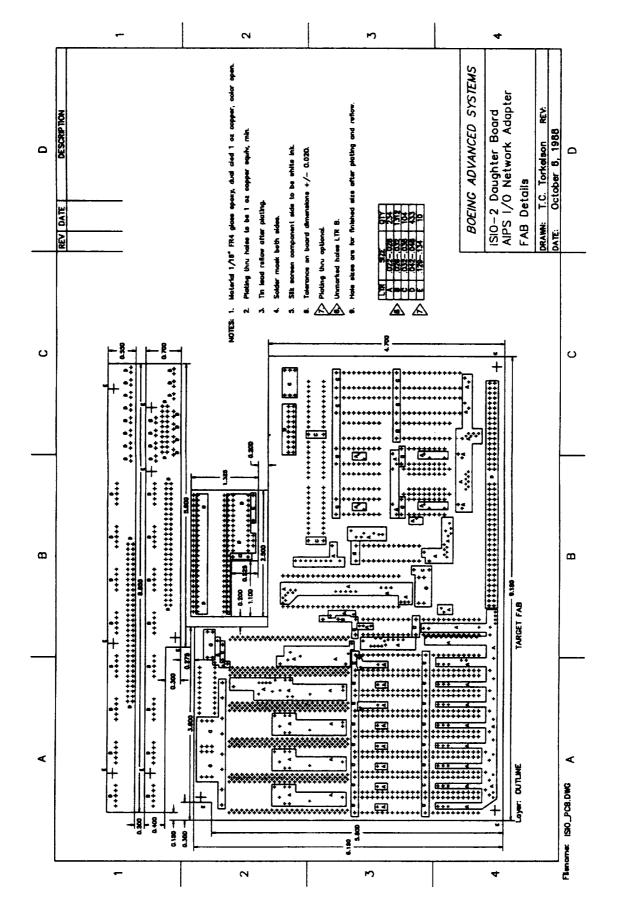

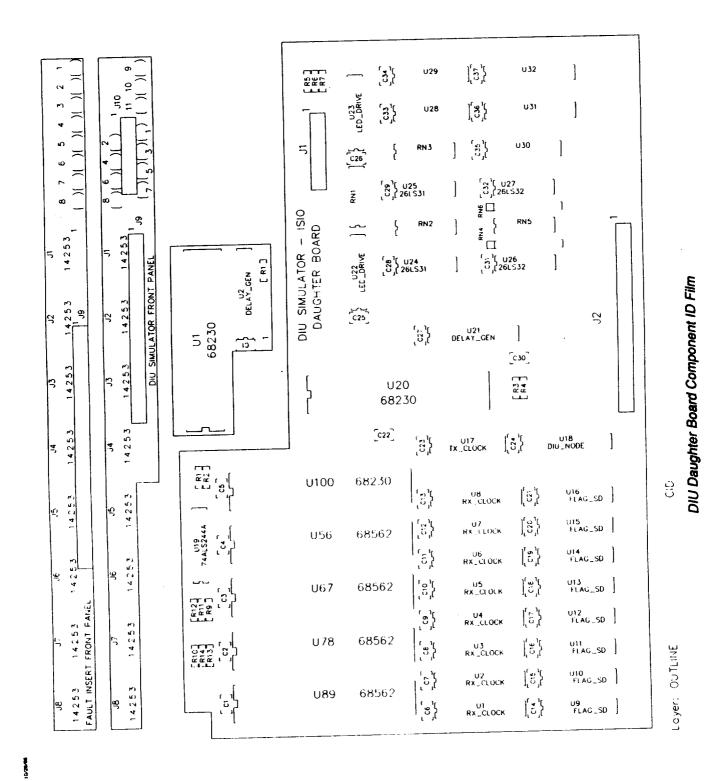

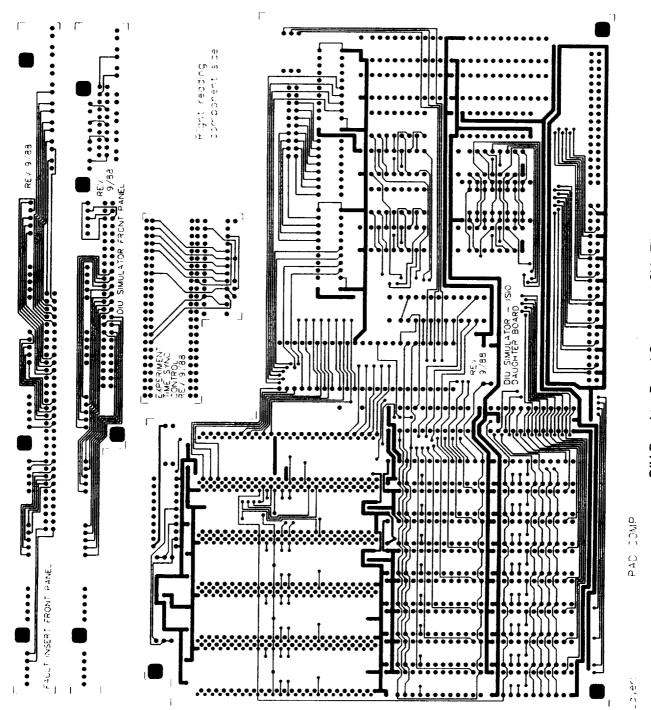

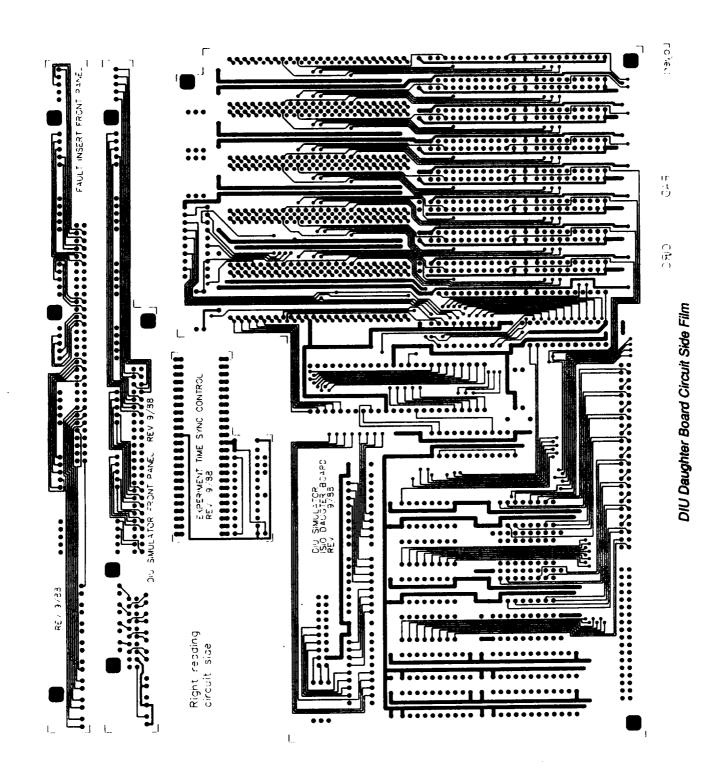

| Documentation Package D: ISIO-2/DIU<br>Simulator Dat             | J-29<br>ughter Board        |

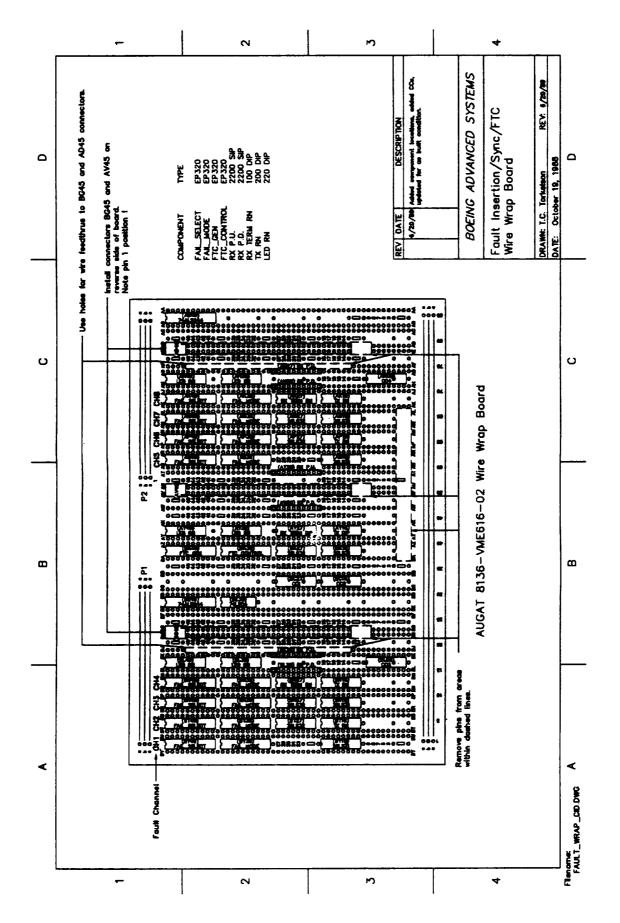

| Documentation Package E: Fault Insert<br>and Control             | ion J-97<br>Wire Wrap Board |

۰<sub>4</sub>

v

## LIST OF FIGURES

| FIGURE |                                                                              | PAGE |

|--------|------------------------------------------------------------------------------|------|

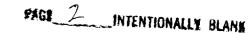

| 2.0-1  | Experiment Test Configuration                                                | 4    |

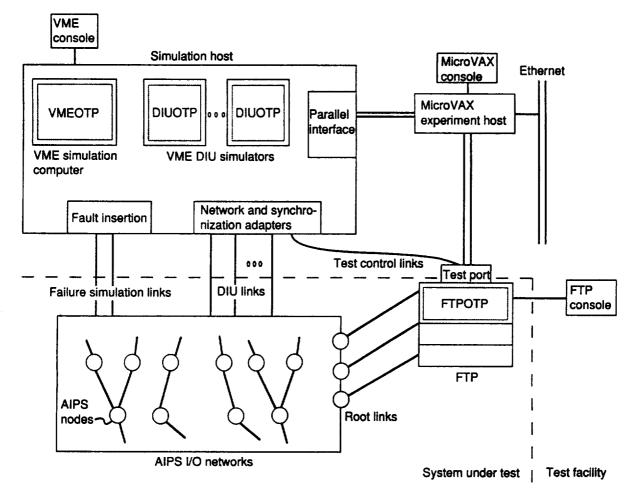

| 2.0-2  | Small-Scale System Block Diagram                                             | 5    |

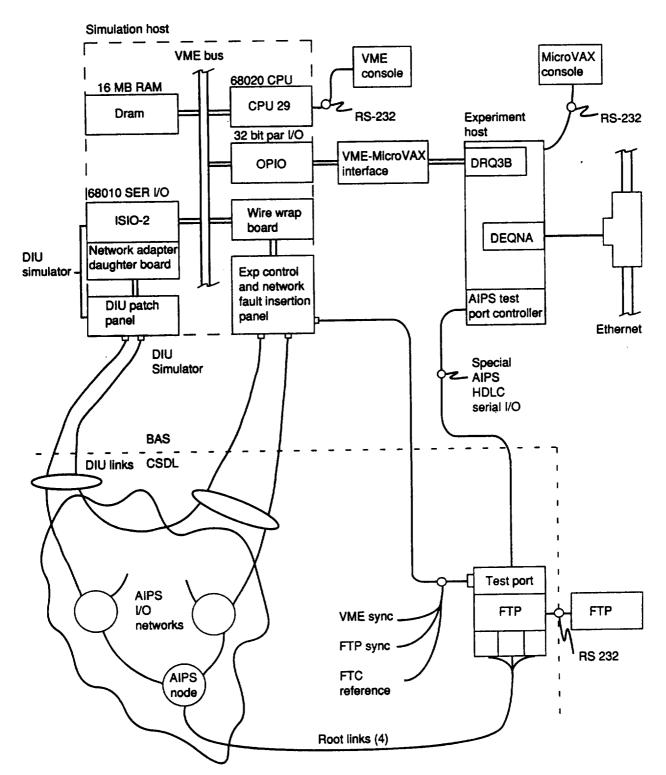

| 3.1-1  | CPU-29 and Memory Block Diagram                                              | 10   |

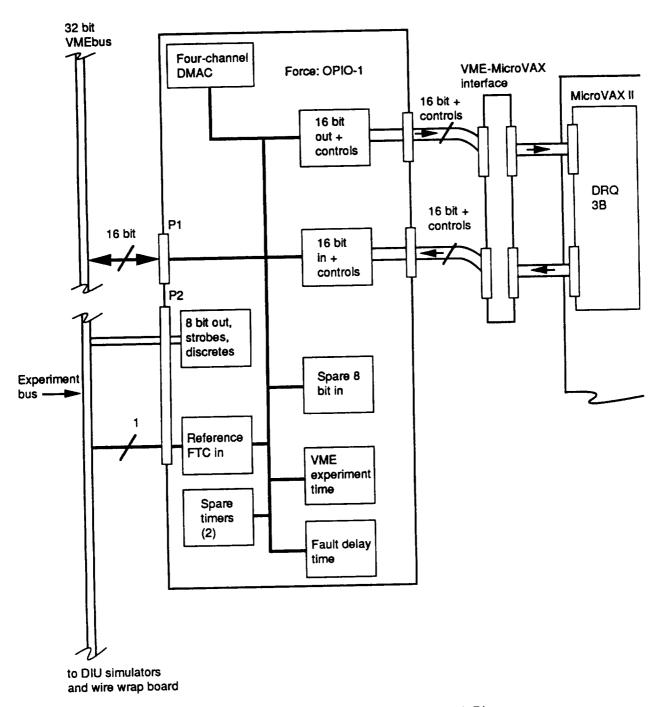

| 3.1-2  | OPIO-1 and MicroVAX Interface Block Diagram                                  | 11   |

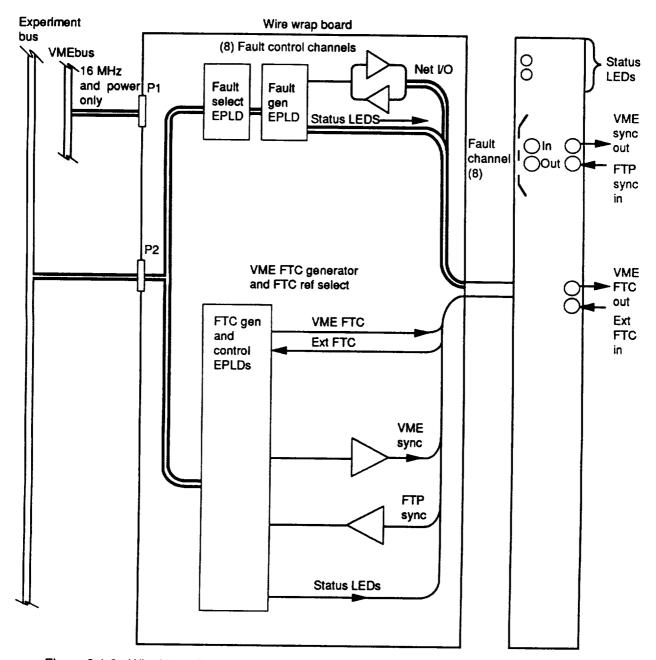

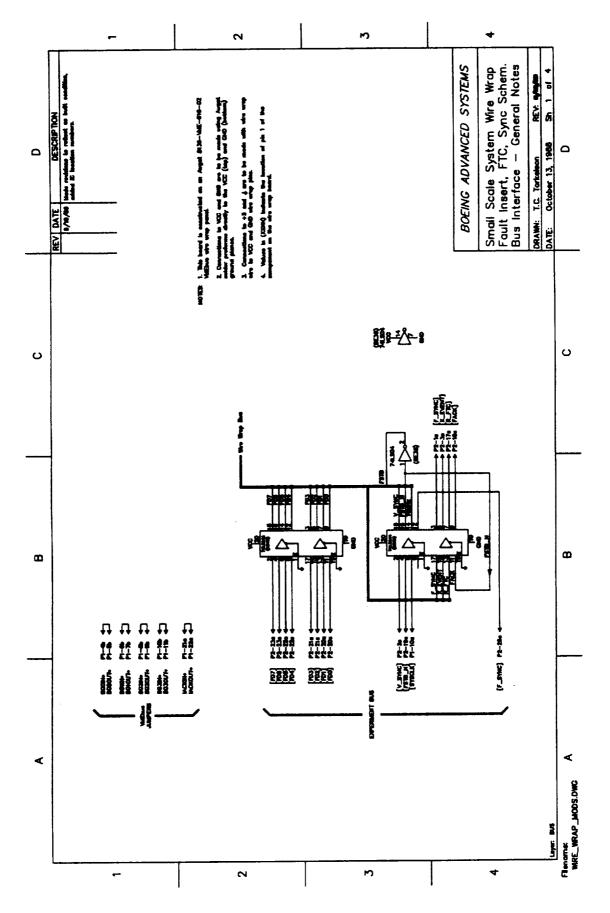

| 3.1-3  | Wire Wrap Board-Network Fault Insertion/<br>Experiment Control Block Diagram | 12   |

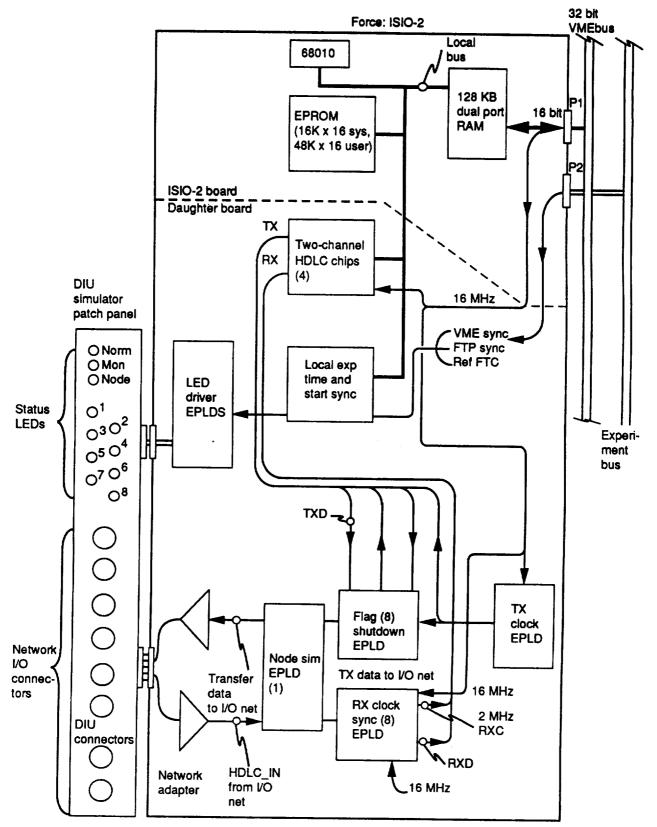

| 3.1-4  | DIU Simulator Block Diagram                                                  | 14   |

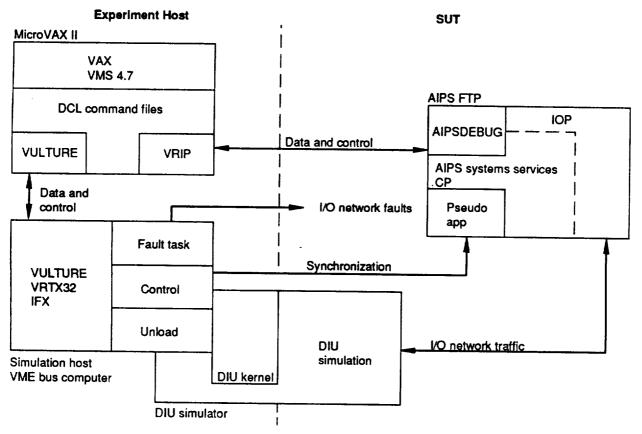

| 3.3-1  | Small-Scale System Software Block Diagram                                    | 18   |

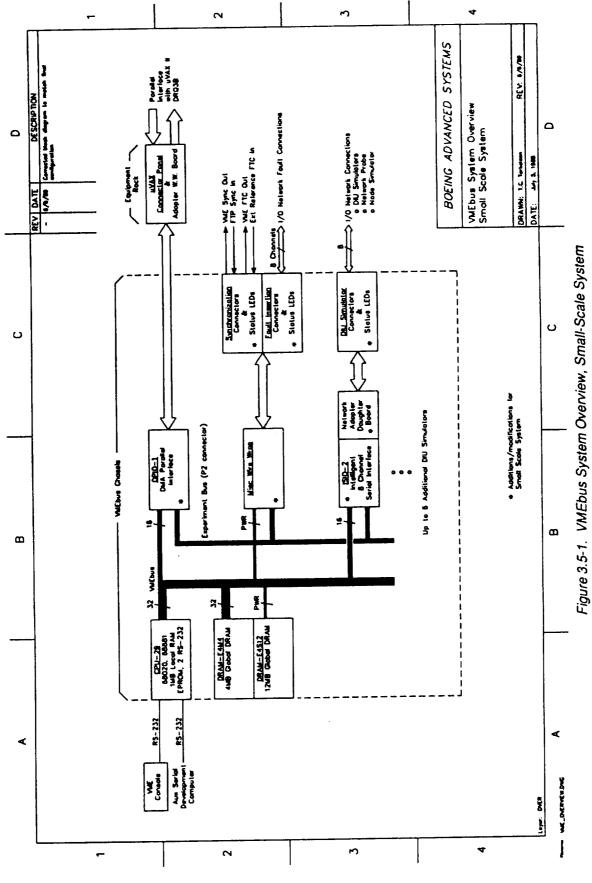

| 3.5-1  | VMEbus System Overview, Small-Scale System                                   | 23   |

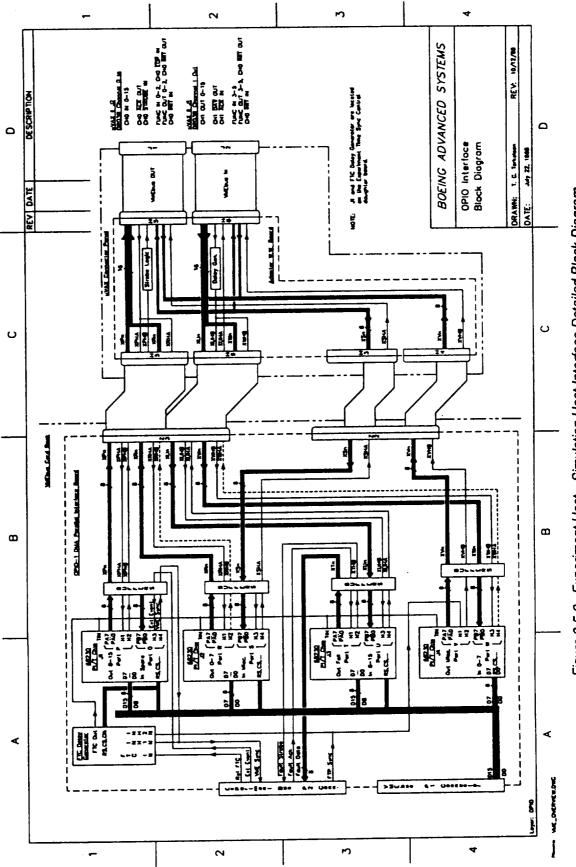

| 3.5-2  | Experiment Host-Simulation Host Interface Detailed<br>Block Diagram          | 25   |

| 3.5-3  | VMEbus and MicroVAX Byte Stacking Order                                      | 28   |

| 3.5-4  | Data Transfer Without Hardware Byte Swapping                                 | 30   |

| 3.5-5  | Data Transfer With Hardware Byte Swapping                                    | 30   |

| 3.5-6  | Experiment Host to Simulation Host Transfer                                  | 31   |

| 3.5-7  | Simulation Host to Experiment Host Transfer                                  | 34   |

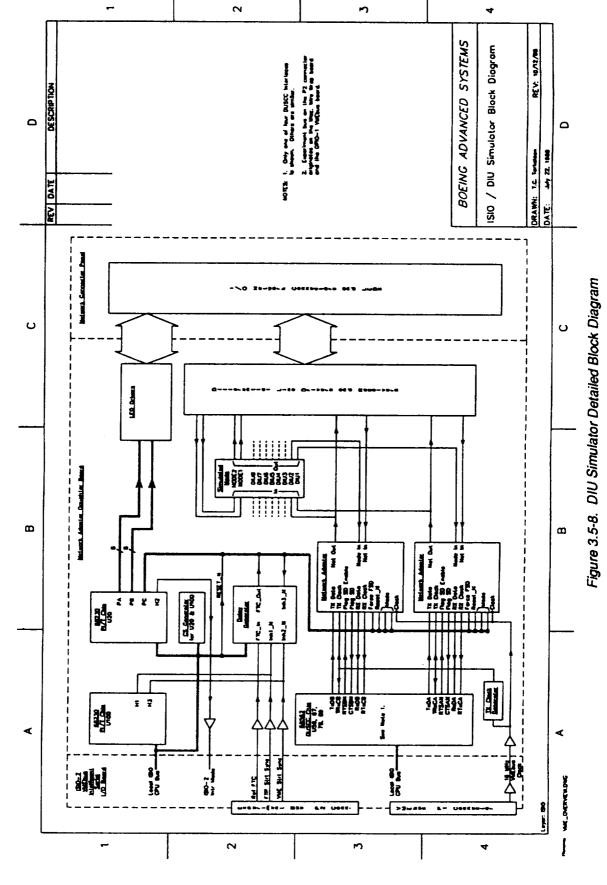

| 3.5-8  | DIU Simulator Detailed Block Diagram                                         | 36   |

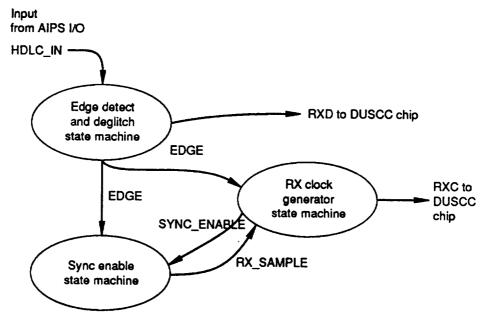

| 3.5-9  | Block Diagram RX Clock EPLD                                                  | 38   |

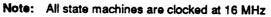

| 3.5-10 | HDLC Input Edge Detect and Deglitch State Machine                            | 40   |

| 3.5-11 | RX Clock EPLD Timing Diagram                                                 | 41   |

| 3.5-12 | Sync Enable State Machine                                                    | 42   |

| 3.5-13 | RX Clock Generator State Machine                                             | 43   |

| 3.5-14 | Flag Shutdown State Machine                                                  | 45   |

| 3.5-15 | Fault Insertion, Control Interface Detailed<br>Block Diagram                 | 49   |

| 3.5-16 | Network Fault EPLD Block Diagram                                             | 50   |

#### 1.0 SUMMARY

This document presents the specifications used to implement hardware and software for those portions of the IAPSA II small-scale system supplied by Boeing. Portions of the system provided by the Charles Stark Draper Laboratory (CSDL) are not included.

A small-scale system was implemented to embody the essential characteristics of a flight-critical system modeled earlier in the IAPSA-II contract. It was used to investigate the critical issues identified by those efforts in both normal and faulted operation.

The system under test was composed of existing proof-of-concept AIPS building-block hardware and software plus simulated device interface units (DIU). The entire system was controlled from a MicroVAX II experiment host computer.

Commercially available VMEbus building-block hardware and software were used to create the simulation host and DIUs. Hardware used to inject faults into the system I/O networks was built on a VMEbus wire wrap card and controlled by an off-the-shelf VMEbus parallel I/O card.

Pseudoapplication Ada software was used to simulate the computational loading of the FTP processors. Dummy data representing the total volume of flight control traffic was sent over the I/O network. DIU dummy response data were sent over the I/O network to answer dummy command data.

The revision level of these specifications reflects the system delivered to NASA Langley Airlab for testing.

# 2.0 INTRODUCTION

This document presents the details necessary to implement the small-scale system experiment test configuration shown in figure 2.0-1. Off-theshelf components were used wherever possible to minimize development cost. All discussions pertain to the small-scale system used for experimentation at NASA Langley facilities.

A brief description of off-the-shelf components is provided to help understand system operation. More detailed information on building blocks may be found in manufacturers' specifications and operation manuals, referenced at the end of this document.

The discussion section that follows focuses on the details of modifications to the standard building blocks and on implementation of custom interfaces.

Specifications in the appendixes were derived from meetings and telephone conversations with CSDL personnel, Advanced Information Processing System (AIPS) schematics, Ada software templates supplied by CSDL, preliminary AIPS documentation, and discoveries made during integration testing at CSDL.

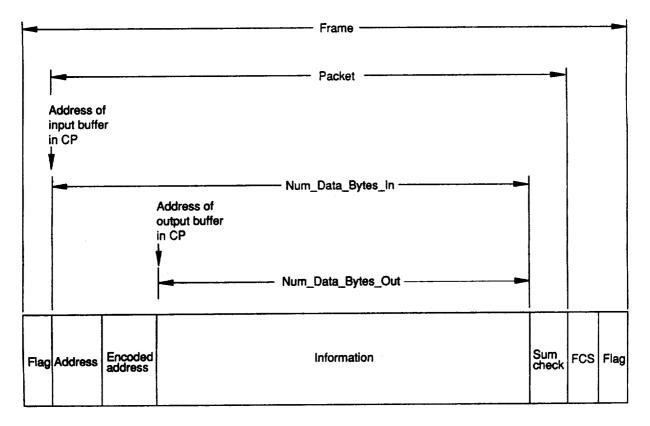

System Under Test Description. The FTP shown in figures 2.0-1 and 2.0-2 is a triplex, bit synchronous 68010-based AIPS building block. Each of its three channels has a computational processor (CP), an input/output processor (IOP), local memory, shared memory (SM), one or more input/output sequencers (IOS) to connect the fault-tolerant processor (FTP) to I/O networks, and a test port to allow control of the FTP by the experiment host computer.

The I/O network connected the FTP to DIUs via a circuit-switched network rich in redundant interconnections, enabling reconfiguration around network faults.

3

PRECEDING PAGE BLANK NOT FILMED

Figure 2.0-1. Experiment Test Configuration

Figure 2.0-2. Small-Scale System Block Diagram

Ada pseudoapplication software was run on the FTP under the control of AIPS system services.

The AIPS system building blocks used in the small-scale system were proof-of-concept components that were still in development and for which no firm specifications existed. Without CSDL's close assistance and cooperation, integration of the small-scale system would not have been possible.

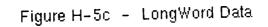

Simulation Host Description. The test facility depicted in figures 2.0-1 and 2.0-2 was designed to support generic, general-purpose test systems that require special interfaces in hardware-in-the-loop simulation environments. It is VMEbus-based and uses standard VMEbus boards obtained from Force Computers, Inc. The base-level test system configuration includes a CPU card, bulk memory, seven intelligent serial interface cards, and a high-speed parallel interface between the simulation host and the experiment host.

Figure 2.0-2 shows the base-level test system after the addition of modifications to support small-scale system hardware-in-the-loop requirements. The upper half of the simulation host block is the base configuration of the general-purpose test system, including the bulk memory, CPU, and interface to the experiment host. The lower half of the simulation host block represents the additions and modifications required to create DIU simulators and special interfaces for the small-scale system. Daughter boards were designed and built for the serial interface cards; a custom wire wrap board was built; and modifications were made to the parallel interface board.

The configurations of each of the main components of the test system are described in greater detail in the discussion section that follows.

**Experiment Host Description.** The experiment host shown in figure 2.0-2 was a Digital Equipment Corporation (DEC) MicroVAX II computer with 10 MB

of memory, two RD-53 70-MB hard disks, a TK-50 93-MB cassette tape, a DEQNA Ethernet controller, and a DRQ3B parallel, DMA interface card. An AIPS test port controller card was installed to control the AIPS FTP from the experiment host.

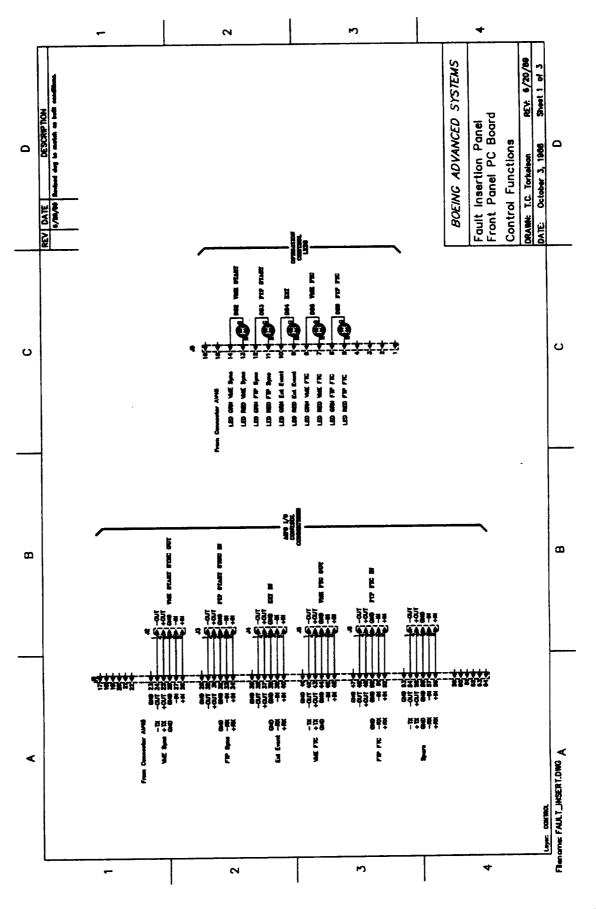

Small-Scale System Software Operation. Figure 2.0-1 shows major software elements: VME Operational Test Program (VMEOTP) and DIU Operational Test Program (DIUOTP) in the simulation host, and FTP Operational Test Program (FTPOTP) in the AIPS FTP. The interaction of these software elements is described later in this document.

Section 6.0 of reference 1 is a discussion of small-scale system testing that presents additional information concerning the configuration of the system and the use of the the experiment test configuration. .

.

e#

¥

-

#### 3.0 DISCUSSION

#### 3.1 GENERAL SIMULATION HOST HARDWARE DESCRIPTION

#### 3.1.1 VMEbus CPU Card

As shown in figure 3.1-1, the CPU-29 contains 128K x 32 bit (1 MB) highspeed static ram, 128K x 32 bits of EPROM, a real-time clock, and two serial I/O ports controlled over a local bus by a Motorola 68020 microprocessor/68881 math coprocessor combination operating at 16.7 MHz. The VMEbus interface is controlled by the 68020 when it gains access to the VMEbus as a bus master. None of the resources on the CPU-29 are accessible to other VMEbus masters.

#### 3.1.2 Bulk VMBbus Memory

The VMEbus DRAM-Exxx bulk memory system shown in figure 3.1-2 has 16 MB of 32-bit-wide dynamic memory. The dynamic ram is slower than the CPU-29 local static RAM but provides relatively low-cost, fast bulk storage for experiment programs and data. The DRAM storage system consists of two cards; the master DRAM controller card has 4 MB of memory and the VMEbus interface; and the slave card, holding 12 MB of memory, connects to the master over a private intercard bus.

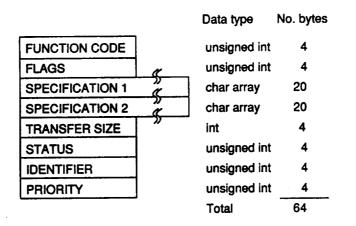

## 3.1.3 VME-MicroVAX Interface

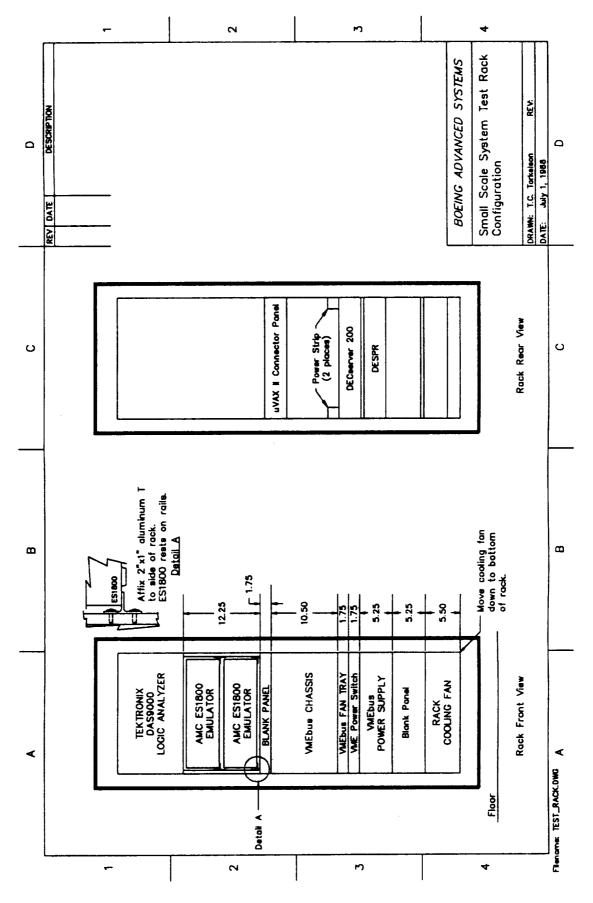

The OPIO-1 card is used for several purposes, as shown in figures 3.1-2 and 3.1-3. This card has four Motorola 68230 programmable interface/timer (PI/T) chips and a Hitachi 68450 four-channel direct memory access (DMA) controller. The PI/T chips provide a total of 32 bits of input, 32 bits of output, 16 handshake lines, and four 24-bit timers. The DMA controller was not used in the small-scale system.

PRECEDING PAGE BLANK NOT FILMED

PAGE 8 INTENTIONALLY BLANK

Figure 3.1-1. CPU-29 and Memory Block Diagram

\*

Figure 3.1-3. Wire Wrap Board—Network Fault Insertion/Experiment Control Block Diagram

As illustrated in the upper half of figure 3.1-2, half of the OPIO-1 I/O capability is used for a high-speed 16-bit parallel communications link between the simulation host and the experiment host. The interface is used to download VMEbus programs, to control the simulation host from the experiment host during experiments, and to upload VMEbus experiment data after experiments. Data transfer rates are on the order of 500 KB per second.

Additional functions monitored or controlled using the OPIO-1 card are discussed in sections 3.1.5, 3.1.6, and 3.1.7 below.

#### 3.1.4 DIU Simulators

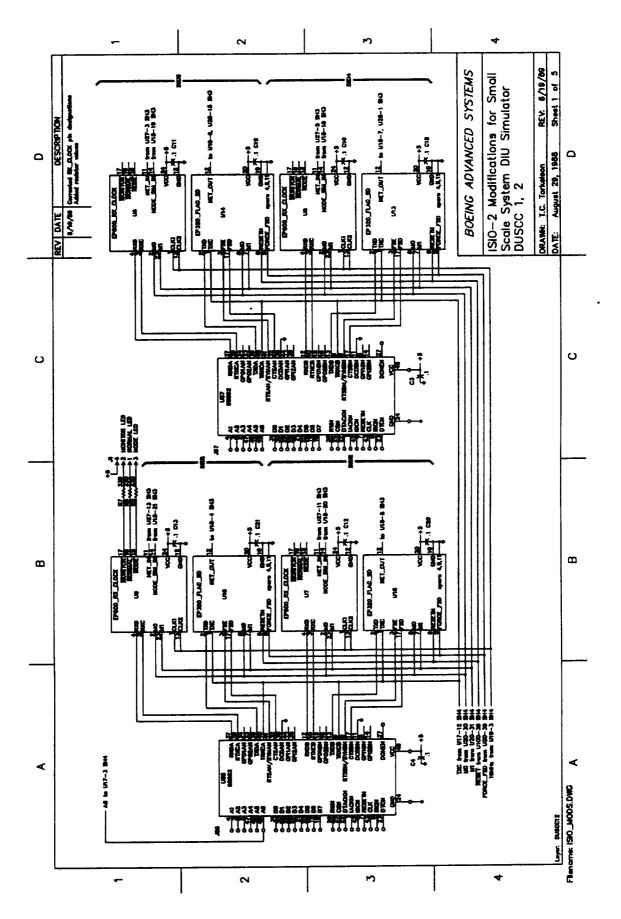

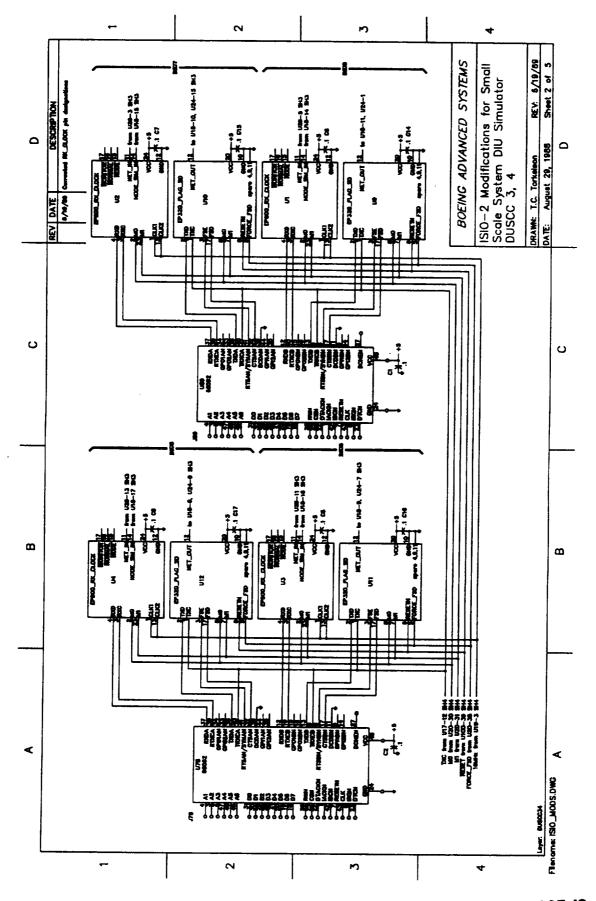

Figure 3.1-4 shows a block diagram of the AIPS-compatible DIU simulators based on modified Force Computer ISIO-2 boards from the base-level simulation host. These boards are intelligent peripheral boards: each board has a local 10 MHz Motorola 68010 microprocessor, 128 KB of local/VMEbus dual-ported high-speed static RAM and eight channels of high-speed serial interface capable of supporting the hierarchical data link control (HDLC) protocol at up to 4 MHz.

Local ISIO-2 resources are not directly available to the VMEbus, and the VMEbus is not directly accessible to the local ISIO-2 CPU; all communications in the small-scale system between the ISIO-2 and the VMEbus were via the dual-port ram.

A daughter board and AIPS I/O connectors were added to the existing boards to implement the special AIPS I/O requirements for clock synchronization and flag shutdown. An additional Motorola 68230 PI/T chip provided status, timekeeping, and synchronization functions. The experiment bus (see below) was routed to each of the DIU simulator cards to synchronize the simulators with the VMEbus and AIPS FTP.

The small-scale system used one complete I/O network and one partial network. The design of the ISIO-2 daughter boards enables each simulator

(n) indicates number of replications

Figure 3.1-4. DIU Simulator Block Diagram

board to act either as eight independent DIUs with individual I/O connectors or as eight independent DIUs sharing a single I/O connector. Each DIU simulator board can also be used as a network probe to view all activity on an I/O network for debugging purposes.

# 3.1.5 I/O Network Fault Insertion

Figure 3.1-3 is a block diagram of the wire wrap card. The top portion of the block diagram shows the network fault insertion channels. Each channel consists of an in and out connector, which are used to break a link in the I/O network. Eight physical fault channels are present on the card. Each of the channels can be mapped to a logical channel for fault control purposes. Failing a logical channel causes all physical channels mapped to that logical channel to fail simultaneously to the same fault condition.

The fault channels support three different modes: normal, in which inputs are routed directly to outputs; passive, in which outputs are failed to a low state; and active, in which outputs are failed to a high state. The state of each fault channel in and out connector output is indicated by a bi-color LED: green for normal; off for passive; and red for active. Small-scale system faults were identically applied to both in and out connectors.

# 3.1.6 Experiment Control and Experiment Bus

The wire wrap card shown in figure 3.1-3 was also used to interface the simulation host to the AIPS FTP to control experiment synchronization and timing. The VME sync output was used to signal the FTP when the simulation host was ready to proceed; the FTP sync input was used to synchronize all experiment time keeping functions in the simulation host. The state of the the sync signals is indicated by bi-color LEDs: red for stop and green for run.

A common timebase is used for all experiment timekeeping in the simulation host. Two timebase options are provided: either the FTC generated by the VMEbus wire wrap card or an external FTC can be used. The small-scale system used an external FTC provided by the FTP so that experiment timekeeping in the FTP and the simulation host would correlate.

Timebase, synchronization, and control signals are routed to each DIU simulator and the wire wrap board from the OPIO-1 card via spare pins in the VMEbus P2 connector, which form the experiment bus.

# 3.1.7 VMEbus Experiment Time and Fault Insertion Delay

The OPIO-1 card shown in figure 3.1-2 was modified to add a clock control daughter board that synchronizes VMEbus timing signals with all DIU simulators and the external system under test. One of the OPIO-1 PI/T timers is the source of VMEbus experiment timekeeping; another is used as a delay timer for controlling fault insertion timing. Two spare timers remain on the OPIO-1.

# 3.2 DEVELOPMENT SUPPORT HARDWARE

# 3.2.1 Development Host Computer

All software and hardware were designed using software tools installed on a DEC VAXstation 2000. The VAXstation was equipped with 6 MB of RAM, an internal RD-53 70-MB hard disk, an external RD-54 150-MB hard disk, and an external TK-50 tape drive.

### 3.2.2 Terminal Server

A DECserver 200 was included in the development support hardware to allow flexible access to serial devices. Using the terminal server in the development system allows serial port access to the simulation host computer from local CRTs or the VAXstation; use of a single serial

printer for both experiment host and development host; access to emulators from CRTs or development host; and access to either the development or experiment host computer from local CRTs.

## 3.2.3 Line Printer

A Mannesmann Tally MT660 line printer provided both text and graphics output for the VAXstation and the experiment host computer.

## 3.2.4 Logic Analyzer

A Tektronix DAS 9200 logic analyzer with two 92A90 modules, a 92A16 module, a 68010 PGA adapter pod plus software, a 68020 adapter pod plus software, and a parallel graphics printer were used to aid in hardware and software debugging and performance evaluation. The logic analyzer was also used to view activity on the AIPS I/O network.

# 3.2.5 Microprocessor Emulators

Applied Microsystems emulators equipped with C source level debugging software were available for debugging hardware and software problems in both the Motorola 68010-based ISIO card and the Motorola 68020-based CPU-29 card.

# 3.3 GENERAL SOFTWARE DESCRIPTION

The major software development efforts were the implementation of DIU simulator software, creation of FTP pseudoapplications, and production of experiment control programs.

# 3.3.1 Experiment Software Interaction

Figure 3.3-1 is a block diagram of small-scale system software as it was used during an experiment run.

Figure 3.3-1. Small-Scale System Software Block Diagram

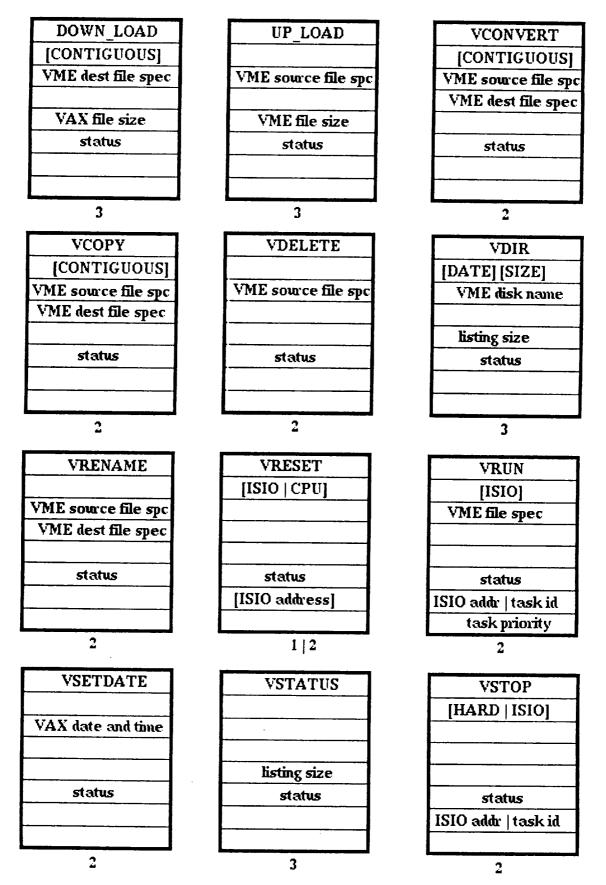

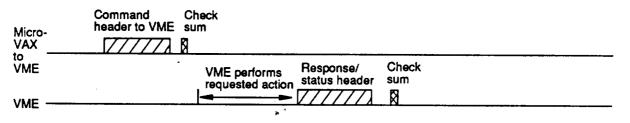

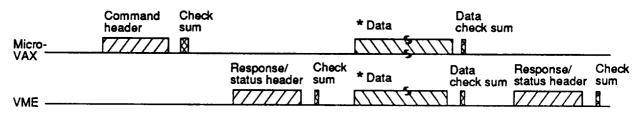

Experiments were controlled by DCL command files running in the experiment host. Experiment control commands were routed to the AIPS FTP using the VRIP/AIPSDEBUG interface and routed to the simulation host using the VME Ultimate User Environment (VULTURE) interface. The VRIP/AIPSDEBUG interface was used to start initialization programs in the ftp, activating aips systems services and pseudoapplication programs. VULTURE commands to the simulation host loaded DIU software in simulator boards and started the VMEbus computer control, fault task, and unload programs. The simulation host control program was used to synchronize operation of the FTP pseudoapplication, the fault task, and the DIU simulation program.

Upon completion of an experiment run, the unload program in the simulation host removed and reformatted data from the DIU simulator for uploading to the experiment host disk using VULTURE commands. VRIP/AIPSDEBUG commands were used to remove experiment application data from the FTP for storage on the experiment host disk.

#### 3.3.2 Experiment Host Software

The experiment host MicroVAX II ran version 4.7 of the VAX VMS operating system.

Software in the experiment host was responsible for controlling the overall operation of both the simulation host and the FTP. The main experiment control programs were DEC DCL command files. The simulation host was controlled using the VULTURE commands; the FTP was controlled using VRIP/AIPSDEBUG commands.

All executable programs for the simulation host and the FTP were stored on disk in the experiment host. These programs were downloaded to their appropriate target machines using either VULTURE or VRIP/AIPSDEBUG.

Upon completion of experiment runs, data were uploaded from the simulation host and the FTP to disk files on the experiment host, where they were transferred to magnetic tape for archiving.

Experiment host resident analysis software was used to perform preliminary analysis on collected data. The direction of experimentation was guided by the ability to perform timely data analysis.

## 3.3.3 Simulation Host Software

A portion of the software in the simulation host is located in EPROM to control the operation of the simulation host at power up. The EPROMS contain Ready Systems VRTX-32 and IFX, a board support package to adapt VRTX-32 and IFX to the CPU-29; VMEPROM, which is shipped with the CPU-29, the VMEbus resident portion of the VULTURE program; and a sharable copy of Ready Systems Real Time C library.

A portion of simulation host RAM is configured as two RAM disks: DRAM: which is located in the DRAM-E4XXX boards, and SRAM:, which is in CPU-29 static RAM. All files in these two RAM disks obey MS-DOS file-naming conventions. Files in the RAM disks can be either contiguous or noncontiguous.

Programs downloaded from the experiment host to the simulation host can reside on either of the two RAM disks. Executable programs are required to be in contiguous files in RAM disk. Optimum performance of CPU-29 targetted programs is obtained when they reside on the SRAM: disk. CPU-29 programs will also run on DRAM: disk but with slightly reduced performance. When a CPU-29 program is started using the VULTURE VRUN command, the program executes the image of the program in the contiguous ram disk file.

Data collected by the simulation host during an experiment run were stored in noncontiguous files in the DRAM: disk and later uploaded to disk files in the MicroVAX II experiment host.

Repeated creation and deletion of RAM disk files may cause disk fragmentation; no attempt is made to repack memory. No fragmentation problems were encountered during operation with the small-scale system.

# 3.3.4 DIU Simulator Software

Executable versions of DIU simulator software were stored on disk in the experiment host. They were downloaded from the experiment host to contiguous RAM disk files in the DRAM: disk in the simulation host. At the start of an experiment run, the DIU simulator software was loaded from the DRAM: disk into the active DIU simulator boards.

The ISIO-2 DUSCC chip initialization portion of firmware, supplied by Force Computers in EPROM on the ISIO-2 boards, was modified to prevent a hardware conflict for the DUSCC chip serial clock source.

A DIU simulator control kernel was developed to supply synchronization and system-level functions for the DIU simulator software. The kernel software must be loaded before any DIU software can be run.

DIU simulator software was configured to respond to specific AIPS I/O network addresses. See appendix E and software tape for more details.

## 3.3.5 AIPS FTP Software

The pseudoapplication programs run in the AIPS FTP were based on Ada code templates provided by CSDL. The code templates were modified to meet small-scale system testing requirements of reference 1.

Some modifications of the AIPS runtime software were made to support the testing requirements of reference 1.

Pseudoapplication software is discussed in reference 1. Listings are found in the software tape.

#### 3.3.6 Development Host Support Software

The VAXstation 2000 development host computer system was supplied with software packages to support both hardware and software design. All the software ran under version 4.7 of the VAX VMS operating system.

Software included DEC Ada to support the data analysis program, DEC C to support the VAX portion of the VULTURE interface, and DEC FORTRAN to support recompilation the VRIP interface for the MicroVAX II.

Third-party software included Autodesk AutoCAD for documentation and ISIO daughter board layout, Data I/O Abel to support the design and production of EPLDs for small-scale system (SSS) custom hardware, Verdix 68010 Ada for compilation of FTP pseudoapplications, and Microtec C and Assembler to support VMEbus CPU and DIU simulation software.

# 3.4 HARDWARE MODIFICATIONS TO AIPS BUILDING BLOCKS

To provide a common timebase in both the FTP and the simulation host, the test port controllers for all three channels of the SSS FTP were modified to provide a differential driver ftc output. Only the Channel A connector panel at the rear of the FTP was modified to connect the differential FTC output to one of the spare connectors. This signal was used by the simulation host for all of its local experiment timekeeping functions.

No other modifications were required to AIPS hardware building blocks.

# 3.5 SIMULATION HOST HARDWARE DETAILS

# 3.5.1 VMEbus System Configuration

Figures in documentation package A show the allocation of cards and special interfaces in the slots of the VMEbus card cage. All slots are used when all seven DIU simulator boards are installed. The small-scale system can operate with four DIU simulators boards when no simulator boards are required for network I/O debugging.

Figure 3.5-1 is a detailed block diagram of the VMEbus system simulation host configured for use in the small-scale system.

23

ORIGINAL PAGE IS OF POOR QUALITY

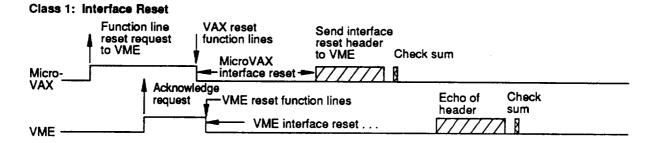

#### 3.5.2 Experiment Host - Simulation Host Interface

Figure 3.5-2 is a detailed block diagram of the interface between the VMEbus simulation host OPIO-1 card and the MicroVAX II experiment host DRQ3B card. The MicroVAX connector panel shown serves four functions: to cross-connect the VMEbus and MicroVAX II data lines for correct transfer of ASCII data; to provide miscellaneous function lines for cross-system signaling; to buffer board I/O signals; and to condition the handshake lines of the two interface cards to ensure correct data transfers.

See documentation package B for OPIO-1 layout and schematics.

DRQ3B inputs and outputs are 74S series TTL terminated with 330/220 pull up/down resistors. Inputs must be driven from devices with 22 mA pull-down capabilities. (See ref. 2 for additional DRQ3B information.)

The OPIO-1 card uses high-speed opto-isolators on all input and output lines. The output of the opto-isolators is insufficient to drive the DRQ3B, and there is no real need for output isolation. The output optoisolators were removed and jumpers inserted to directly connect the output of the opto-isolator driver chips to the DRQ3B inputs.

It was desirable to leave the inputs to the OPIO-1 opto-isolated to minimize the possibility of damaging the inputs to the MC68230 parallel interface timer (PI/T) chips. The output from the DRQ3B does not pull up high enough at logic 1 out to guarantee that the opto-isolators will shut off. To solve this problem, the input LEDs of the opto-isolators were run from a supply one diode drop below 5V. This was adequate to guarantee that the isolators will be shut off at DRQ3B logic 1 out.

Documentation package C contains the drawings used to produce the wire wrap interface and connector panel for the VME-MicroVAX interface.

Figure 3.5-2. Experiment Host-Simulation Host Interface Detailed Block Diagram

ORIGINAL PAGE IS OF POOR QUALITY

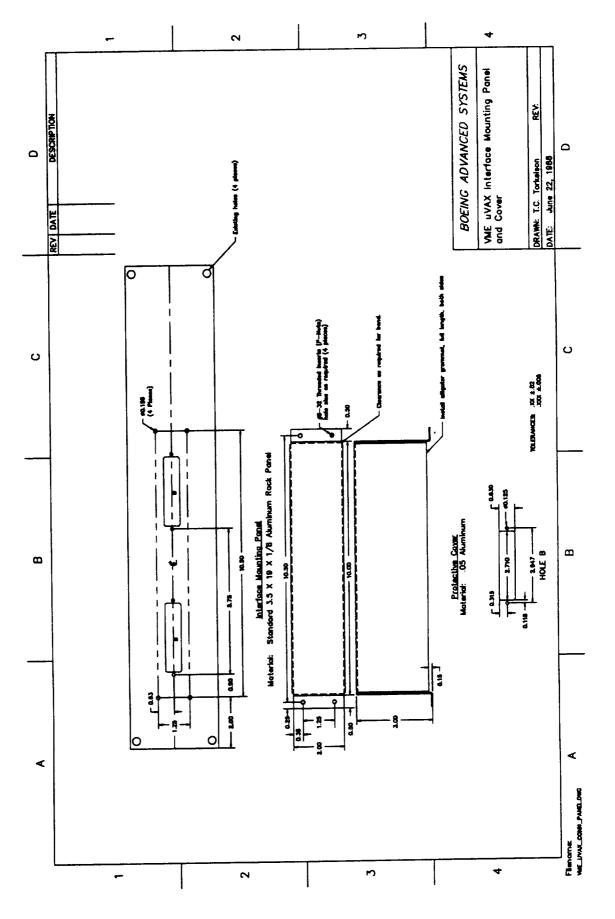

Documentation package C illustrates the interface panel design used for the SSS. The only deviation from this design was that a standard rack width U chassis with side panels was used for shielding the interface board instead of the protective cover shown.

The protective cover shown is preferable because it is permanently affixed to the connector panel. The U chassis is secured with the same screws that hold the connector panel to the equipment rack, raising the possibility of damage to the interface wire wrap board or ribbon cables during installation.

The ribbon cables that connect the wire wrap board to the VMEbus OPIO-1 card are held in place with the edge of the side panels attached to the U chassis. The exposed edges of the side panels are covered with alligator grommet to prevent insulation damage to the ribbon cables.

Documentation package C shows the placement of components on the wire wrap interface board and illustrates the routing of cables from the OPIO-1 to the interface board for an installation in which the interface connector panel is mounted in the VMEbus chassis. No spare slots were available in the small-scale system VMEbus chassis for a connector panel, so the interface board was mounted at the rear of the equipment rack, with the ribbon cables routed up through the top of the card cage to the adapter in the back of the equipment rack.

Documentation package C is a schematic for the wire wrap adapter. The left side of the schematic shows the connections and function names for the VMEbus OPIO-1 board; the connections and function names on the right side of the schematic are for the Micro VAX II DRQ3B interface.

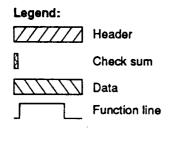

Data Representation and Effect on Data Transfer Interface. Close inspection of the interface wire wrap interconnection schematic reveals that the upper and lower data bytes of the interface lines between the MicroVAX and the VME system are reversed. An explanation of this apparent inconsistency is necessary both to understand the design of the hardware interface and to appreciate the subtleties encountered when attempting to transfer data between a Motorola 68020-based VMEbus system and a DEC VAX system.

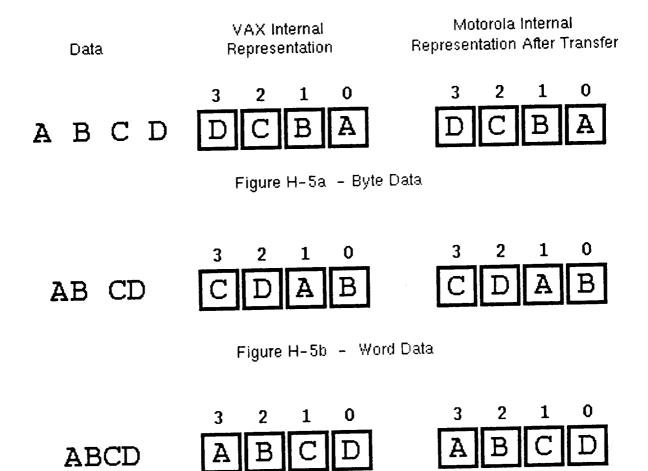

The underlying reason for byte swapping the interconnections was a difference in the byte stacking order in the 68020 VMEbus and MicroVAX systems. The VMEbus system is based on a Motorola 68020 microprocessor. The 68020 byte stacking order is reversed from that of the MicroVAX system except for byte data. (The MicroVAX byte stacking order is the same as that used by Intel systems.)

Figure 3.5-3 shows the byte stacking orders of three types of arrays as stored in the two systems. The array data types are long (32 bit), short (16 bit), and char (8 bit). The examples are shown as hexadecimal bytes arranged from lowest address to highest address. The partial C source code to generate these representations is also shown.

For data to retain the same value in both systems, the byte stacking order must be translated when transferring data. To translate the byte stacking order it is necessary to know the type of data being transferred. For systems that use data structures composed of mixed types it is impossible to perform byte stacking order translation without having access to the definition of every specific data structure being transferred.

The solution chosen for this problem was to use C library functions to convert all binary data to ASCII before transfer between the two systems. This has the disadvantage that up to twice as much data storage may be required, and additional time is required to convert binary data to ASCII. Note that data may still be collected in any desired format during real-time operations as long as it is converted to ASCII before transfer to the MicroVAX.

```

Partial C code used to generate arrays.

/* array allocation */

unsigned char array 1[8];

unsigned short array 2[4];

unsigned long array 4[2];

/* assign values to unsigned character array */

array 1[0] = 0x11;

array[1] = 0x22;

array^{-1}[2] = 0x33;

array[1[3] = 0x44;

\operatorname{array}[1[4] = 0xAA;

array 1[5] = 0xBB;

array 1[6] = 0xCC;

array 1[7] = 0xDD;

/* assign values to unsigned short array */

array_2[0] = 0x1122;

array^{2}[1] = 0x3344;

array^{2}[2] = 0xAABB;

array 2[3] = 0xCCDD;

/* assign values to unsigned long array */

array_{4[0]} = 0x11223344;

array_4[1] = 0xAABBCCDD;

```

The above code generates the following data arrays in the VMEbus and uVAX systems.

|          |    | 1   | /MEI | ous |    |                        |    |    |    |    | - u' | VAX |    |    |    |

|----------|----|-----|------|-----|----|------------------------|----|----|----|----|------|-----|----|----|----|

| 0        | 1  | 2   | 3    | - 4 | 5  | 6                      | 7  | 0  | 1  | 2  | 3    | 4   | 5  | 6  | 7  |

| <br>char | aı | ray | 7    |     |    |                        |    |    |    |    |      |     |    | -  |    |

| 11       | 22 | 33  | 44   | AA  | BB | $\mathbf{C}\mathbf{C}$ | DD | 11 | 22 | 33 | 44   | AA  | BB | сс | DD |

| <br>word |    |     |      |     |    |                        |    |    |    |    |      |     |    |    |    |

| 22       | 11 | 44  | 33   | BB  | AA | DD                     | СС | 11 | 22 | 33 | 44   | AA  | BB | сс | DD |

| <br>long |    |     |      |     |    |                        |    |    |    |    |      |     |    |    |    |

| 44       | 33 | 22  | 11   | DD  | СС | BB                     | AA | 11 | 22 | 33 | 44   | AA  | BB | сс | DD |

Figure 3.5-3. VMEbus and MicroVAX Byte Stacking Order

Figure 3.5-3 shows that ASCII data is stacked in the same order in both the VMEbus and MicroVAX systems, implying that there is no reason to swap the upper and lower bytes in hardware. The physical interfaces, however, treat all transferred data as word (16 bit) data. When the VMEbus system transfers word data, the most significant byte located at address 0 is sent to bits 8 through 15 of the interface; the least significant byte from address 1 is sent to bits 0 thru 7. Because the data being sent are actually ASCII, the bytes are swapped by the VMEbus system. Swapping the high and low byte lines corrects the problem.

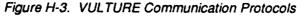

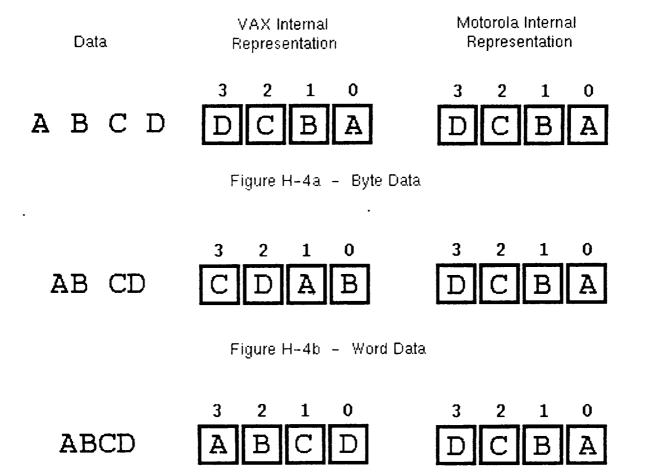

Figures 3.5-4 and 3.5-5 illustrate the transfer of different types of data using both unswapped and swapped lines.

The limitations of this solution have not affected VMEbus system performance adversely enough to require an alternative solution.

Experiment Host to Simulation Host Transfer Protocol. See figure 3.5-6 for typical interface handshake waveforms. Port B of OPIO-1 PI/T devices J3 and J4 serve as the 16-bit VMEbus input port. They are both configured to operate as double-buffered input devices with interlocked input handshakes. (PI/T Port B is set up to operate mode 0, submode 00, double-buffered input, interlocked input handshake protocol.) The input !STROBE is received by both PI/Ts on their H3 pins. The PI/T !ACK output originates on the H4 pin PI/T J3. (A PI/T !ACK output is also available from pin H4 on PI/T J4, but is not used.)

The two handshake protocols have no logical conflicts; however, handshake timing must be modified because of VMEbus PI/T data setup timing requirements. DRQ3B !DAV Out is set low a minimum of 65 ns after data are stable on the out nn lines. At least 100 ns of data setup must be allowed before an input !STROBE is applied to the PI/T chip. To meet the setup time requirements, a delay of approximately 100 ns is placed between the DRQ3B !DAV output and the PI/T input !STROBE, leaving at least a 65 ns margin. The delay is implemented using an RC delay and 74LS14 Schmitt input inverters. (See U1 and associated components in the schematic in documentation package C.)

----- VMEbus ----------- uVAX -----0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 -- char array -- incorrectly transferred 11 22 33 44 AA BB CC DD 22 11 44 33 BB AA DD CC 1 +--- bits 0-7 ---- bits 0-7 ---+ | +----- bits 8-15 ----- bits 8-15 ----+ \*\* word array -- CORRECTLY TRANSFERRED 22 11 44 33 BB AA DD CC 11 22 33 44 AA BB CC DD +--- bits 0-7 ---- bits 0-7 ---+ +----- bits 8-15 ----- bits 8-15 ----+ -- long array -- incorrectly transferred 44 33 22 11 DD CC BB AA 33 44 11 22 CC DD AA BB +--- bits 0-7 ---- bits 0-7 ---+ | +----- bits 8-15 ----- bits 8-15 ----+

----- VMEbus ---------- uVAX -----0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 \*\* char array -- CORRECTLY TRANSFERRED 11 22 33 44 AA BB CC DD 11 22 33 44 AA BB CC DD +--- bits 0-7 ---- bits 8-15 -- |--+ +----- bits 8-15 ----- bits 0-7 ---+ -- word array -- incorrectly transferred 22 11 44 33 BB AA DD CC 22 11 44 33 BB AA DD CC 1 - [ +--- bits 0-7 ---- bits 8-15 --|--+ +---- bits 8-15 ---- bits 0-7 ---+ -- long array -- incorrectly transferred 44 33 22 11 DD CC BB AA 44 33 22 11 DD CC BB AA 1 1 +--- bits 0-7 ---- bits 8-15 -- |--+ +----- bits 8-15 ----- bits 0-7 ---+

Figure 3.5-5. Data Transfer With Hardware Byte Swapping

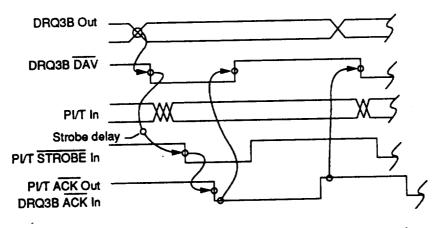

Figure 3.5-6. Experiment Host to Simulation Host Transfer

Note: symbols such as !ACK signify inverted polarity logic.

7The modified MicroVAX to VME transfer operates as follows (see fig. 3.5-6).

- a. Data are placed on the DRQ3B Out lines and the DRQ3B !DAV Out is pulled low.

- b. After a 100-ns delay, the DRQ3B !DAV Out appears at PI/T !STROBE in, latching data in the PI/T input buffer.

- c. After data are latched by the PI/T, PI/T !ACK Out is pulled low.

- d. On receiving DRQ3B !ACK In low, DRQ3B !DAV Out returns high.

- e. If more space is available in PI/T input buffers, PI/T !ACK Out returns high and the next data transfer cycle begins. If the PI/T input buffers are full, PI/T !ACK remains low until the VMEbus computer removes data from the PI/T input buffer, at which time PI/T !ACK returns high and another data transfer cycle begins.

#### Notes:

- a. PI/T !ACK Out timing is referenced to the falling edge of PI/T !STROBE In, not the rising edge.

- b. PI/T !ACK out will return high regardless of the state of PI/T !STROBE In.

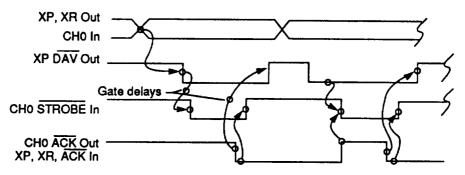

Simulation Host to Experiment Host Transfer Protocol. Without modification, the PI/T to DRQ3B transfer handshake protocol does not work. A logical conflict exists, caused by different interpretations of the meaning of the !ACK signal. The DRQ3B uses the !ACK line to first signify receipt of data at the falling edge and then to signify ready for next transfer on the rising edge. The PI/T, however, interprets the falling edge of the !ACK line to mean data accepted and ready for next transfer.

Without modification, the PI/T begins its next data transfer before the DRQ3B !ACK Out line has returned high. Because the DRQ3B !ACK Out line is still low, the DRQ3B ignores the !STROBE signal and does not produce an !ACK Out handshake for the PI/T. This both causes the data being transferred to be lost and the interface to hang up while the PI/T waits forever for the DRQ3B !ACK Out handshake.

A NAND R-S latch formed from gates in U2 resolves the conflict. The output of the latch is buffered by U3 to provide adequate drive capability for the DRQ3B input.

The operation of the modified interface is as follows (see fig. 3.5-7).

Note: Symbols such as !ACK signify inverted polarity logic.

- a. Data are placed on PI/T Out lines and PI/T !DAV Out goes low.

- b. On DRQ3B !STROBE In low, data on DRQ3B In lines are read and DRQ3B !ACK Out goes low, keeping !STROBE In low in the U2 latch.

- c. The rising edge of PI/T !ACK In causes PI/T !DAV Out to return high and the PI/T starts another output transfer cycle.

- d. Data are placed on PI/T Out lines and PI/T !DAV Out goes low; however, because DRQ3B !ACK Out is still low, DRQ3B !STROBE In remains high.

- e. When DRQ3B !ACK Out finally returns high, DRQ3B !STROBE immediately goes low and a new data transfer cycle begins.

## 3.5.3 VMEbus Backplane Modifications

Jumpers were installed between P1a-21 and P1a-22 to maintain the continuity of the I!ACKIN\* I!ACKOUT\* daisy chain for unused VMEbus connector positions at slots 5, 6, 9, 11, 13, 15, 17, and 19.

Figure 3.5-7. Simulation Host to Experiment Host Transfer

A 64-conductor ribbon cable with special connectors was fabricated to connect the experiment bus described in appendix G from VMEbus chassis slot 4 P2 connector to P2 connectors in slots 7, 8, 10, 12, 14, 16, 18, and 20. The uncommitted pins of the P2 connectors are used. (See documentation package A.)

#### 3.5.4 DIU Simulator

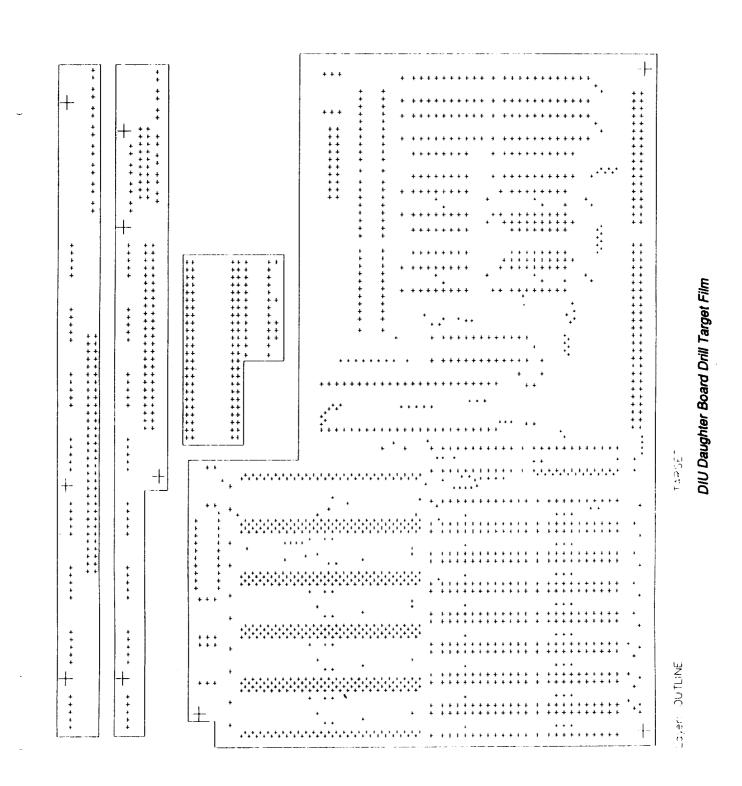

Figure 3.5-8 is a block diagram showing additions made to Force ISIO-2 VMEbus cards to adapt them to the interface requirements of the AIPS I/O network as described in appendix B. The additions reside on a double sided daughter board that plugs into five IC sockets on the ISIO-2 card. All power and signal connections between the daughter board and the ISIO-2 board are made via these five IC sockets.

The major additions and modifications required to adapt the ISIO-2 card to DIU simulator service were:

- a. Operation of DUSCC chips with external 2 MHz receive and transmit clocks and isolation of DUSCC I/O lines from the ISIO-2 board.

- Addition of AIPS I/O network compatible differential line drivers, receivers, and termination resistors.

- c. Addition of external receive clock synchronization circuitry.

- d. Addition of transmitter output flag shutdown circuitry.

- e. Addition of a 2-MHz transmitter clock generator.

- f. Addition of a second 68230 PI/T chip and address decoder for timekeeping, daughter board control, and vectored interrupt selection.

36

-

The daughter board and its components are described in detail in this section.

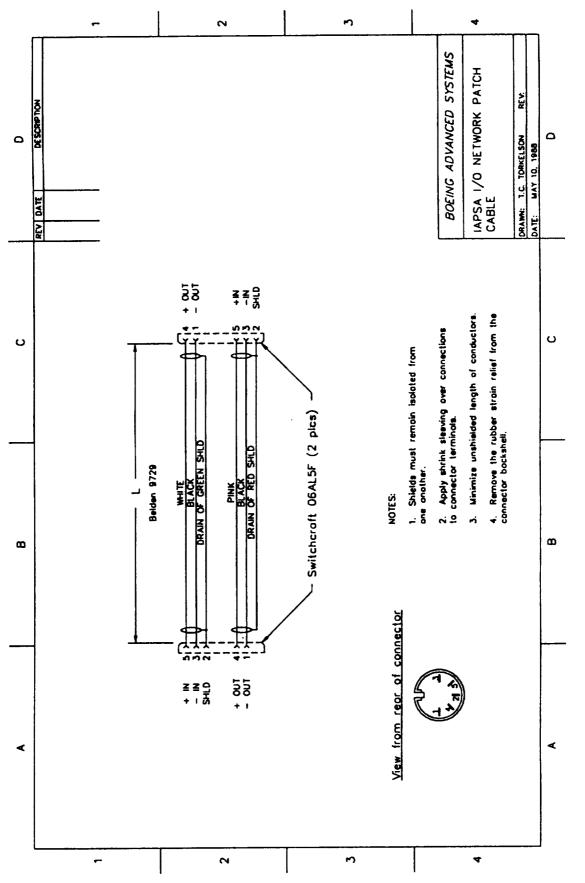

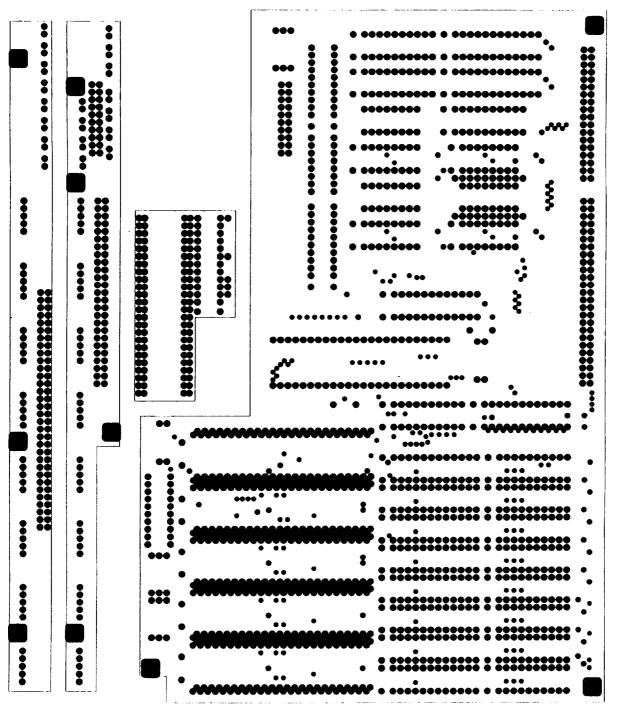

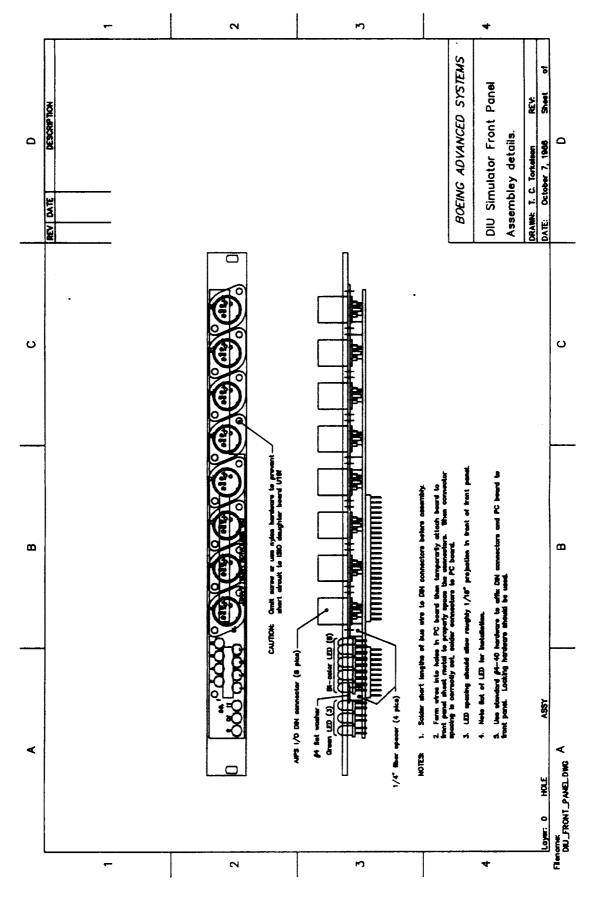

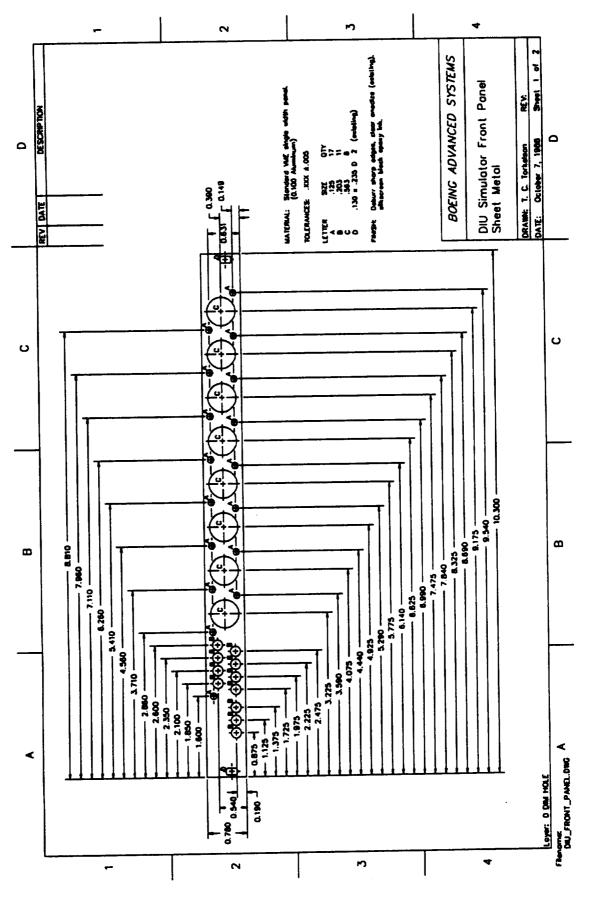

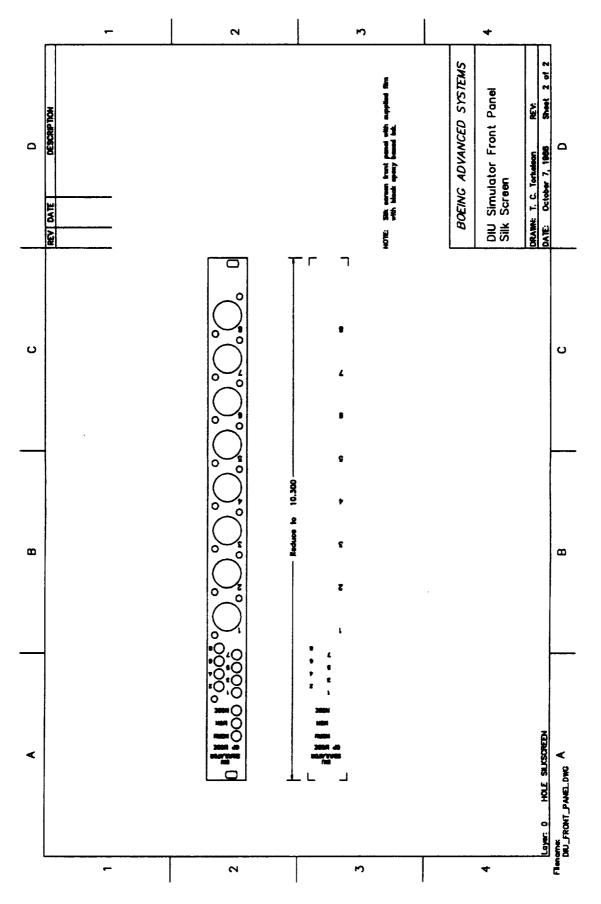

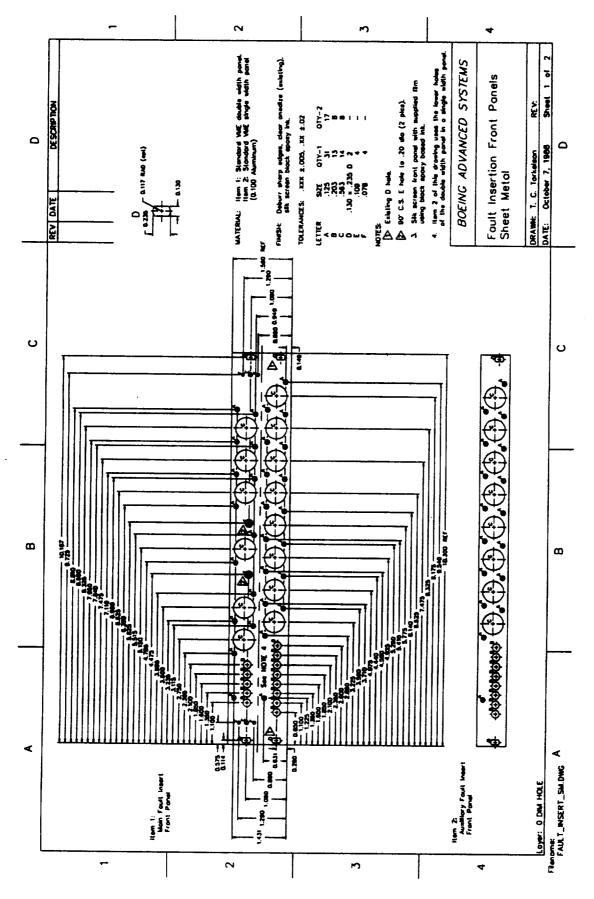

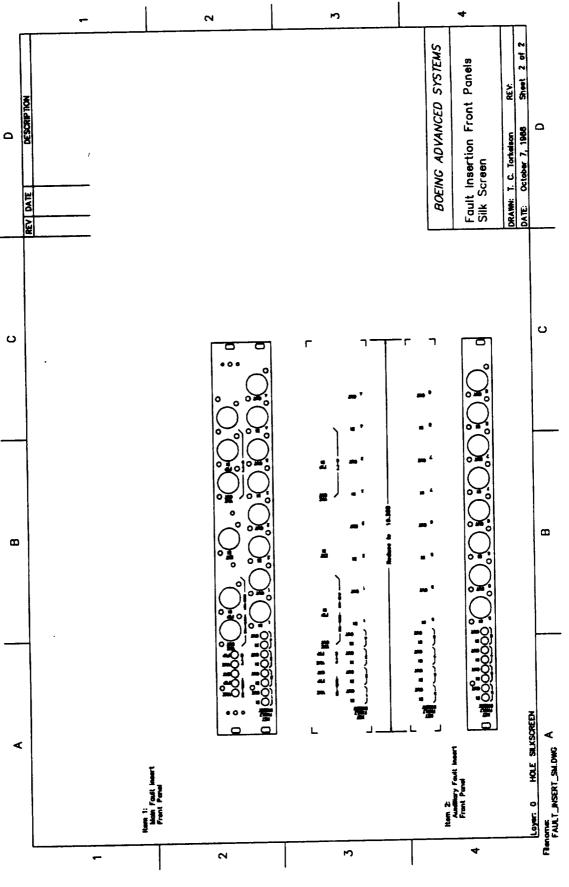

Network Connector Panel. The DIU interface to the AIPS I/O network is via DIN audio connectors mounted on the I/O network connector panel. Fabrication details for the sheet metal and silkscreen of the DIU simulator front panel are in documentation package D.

DIU I/O connectors and status LEDs are soldered to a small PC board located behind the panel. Two ribbon cables connect this PC board to the ISIO daughter board: a 50-conductor ribbon cable is used exclusively for I/O connections, and a 20-conductor ribbon cable is used for status LEDs.

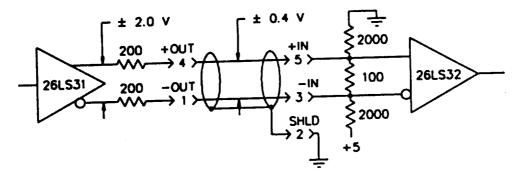

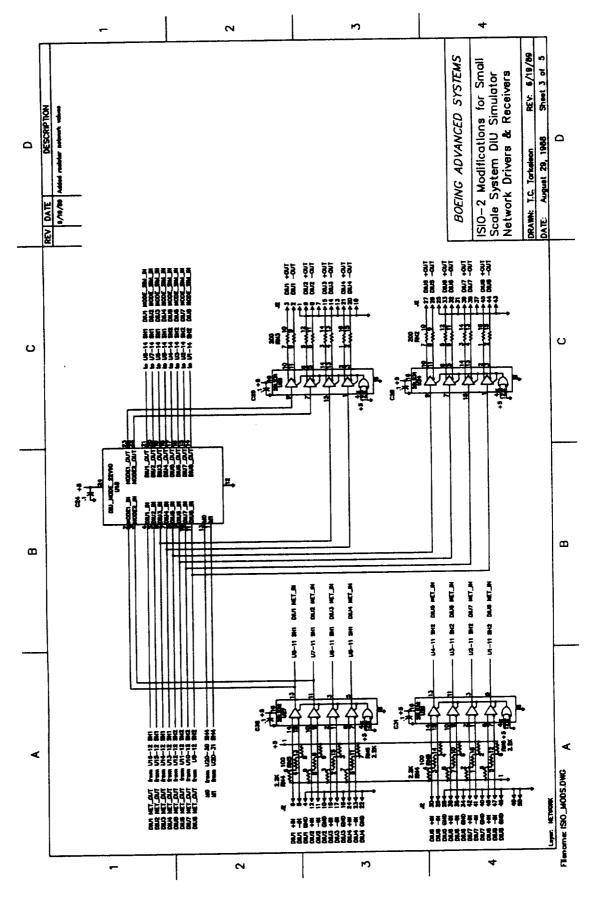

Differential Drivers and Receivers. Differential drivers, receivers, isolation resistors, and termination resistors are located on the daughter board. Components used are in accordance with appendix B to ensure DIU I/O interface compatability with AIPS I/O network requirements.

**RX Clock Generator EPLD.** Data sent over the AIPS I/O network are transmitted at 2 Mb per second. To receive these data each DIU simulator channel must independently regenerate a clock synchronized to its incoming data. Clock stability and synchronization requirements are specified in appendix B.

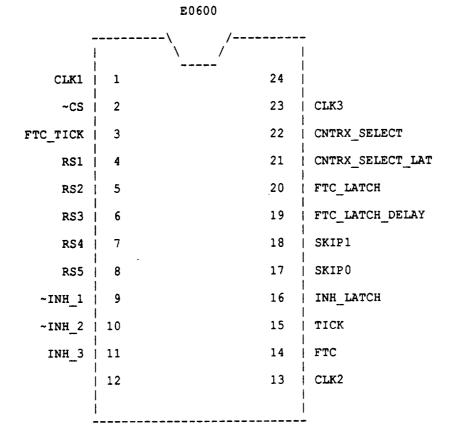

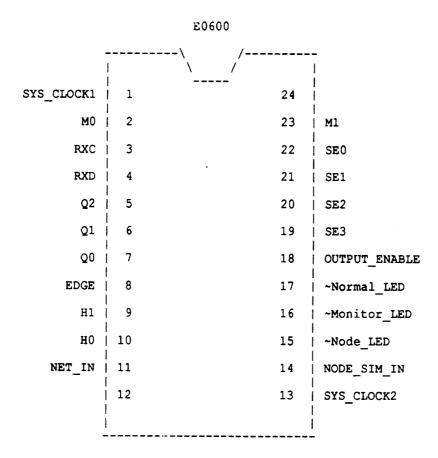

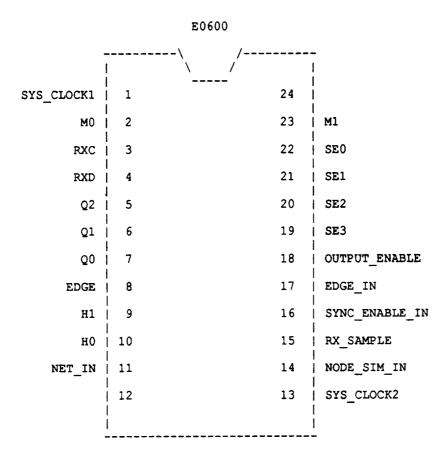

An Altera EP600 erasable programmable logic device (EPLD) was designed to use three interdependent state machines to synchronize the DIU clock to incoming RX data, meet the clock timing requirements of the DUSCC chip, and to provide deglitching of the received data. All three state machines are driven by the same 16-MHz system clock. Figure 3.5-9 shows their interdependence.

Each RX clock EPLD also provides three outputs capable of driving the mode LEDs on the network interconnection panel. See documentation package for listings of EP600\_RX\_CLOCK files.

Figure 3.5-9. Block Diagram RX Clock EPLD

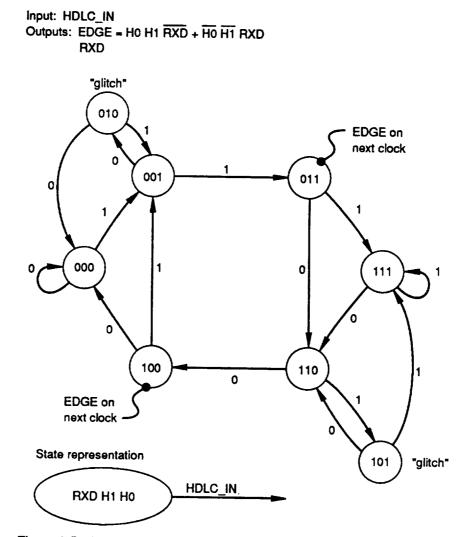

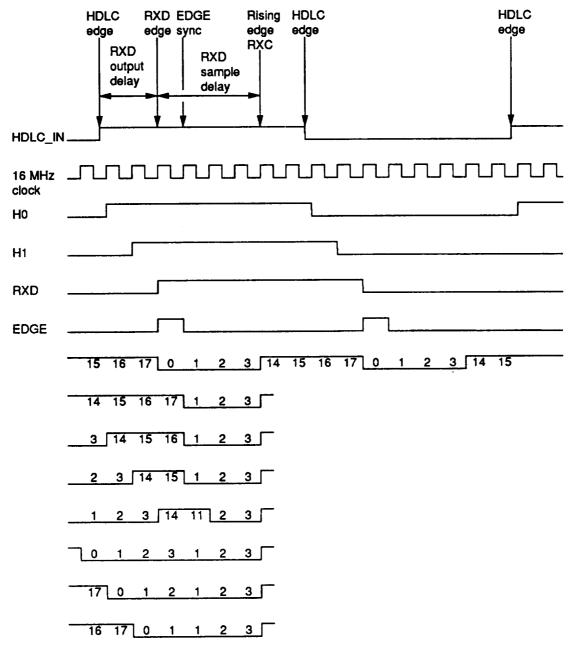

The HDLC\_IN signal from the I/O network is conditioned by the edge detect and deglitch state machine. The state transition diagram in figure 3.5-10 shows that only input logic levels that remain for longer than one clock cycle will be passed to the RXD output. Single clock cycle duration inputs that place the state machine in either state 010 or 101 are ignored. Edge detection occurs whenever the RXD output changes from 0 to 1 or 1 to 0. Both the RXD and EDGE outputs are delayed two to three clock cycles from HDLC\_IN. The rising edge of the RXC signal sent to the DUSCC chip is synchronized with this delay, ensuring correct operation as shown in the timing diagram in figure 3.5-11.

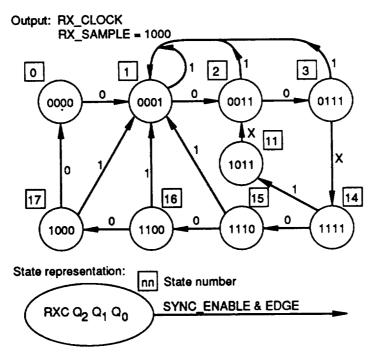

According to AIPS I/O requirements in appendix B, the RX clock signal must not be synchronized until edges have been absent from the I/O network for at least eight RXC periods. The sync enable state machine shown in figure 3.5-12 is used to prevent erroneous synchronization. The state of EDGE is tested at the falling edge of each RXC (RX\_SAMPLE). If no edge is present, the state machine advances to the next state until no edges have been detected for eight RX samples. The state machine stays in state 1000 until an edge is detected. Any edge occurring before reaching state 1000, regardless of RX\_SAMPLE, resets the sync enable state machine to state 0000.

The RX clock generator state machine design guarantees that the RXD signal from the first state machine is sampled halfway between transitions. DUSCC chip input timing restrictions require that the minimum pulse width of the RXC output be at least 100 ns. The RXD output to the DUSCC chip receive input is sampled on the rising edge RXC. The state transition diagram of figure 3.5-13 and the timing diagram in figure 3.5-11 illustrate its operation. State 11 ensures that the clock generator meets DUSCC chip timing specifications.

The clock generator will not synchronize to an HDLC\_IN edge unless the SYNC\_ENABLE signal is present. Because incoming data transitions are not initially synchronized to the state machine internal RXC output, the RX

Figure 3.5-10. HDLC Input Edge Detect and Deglitch State Machine

Figure 3.5-11. RX Clock EPLD Timing Diagram

Inputs: EDGE, RX\_SAMPLE Output: SYNC\_ENABLE = SE3

State representation

SE3..SE0 Е Ε Ε Ε Ε E Ε E NE NE NE NE NE NE NE NE 0011 0100 0101 0000 0001 0010 0110 0111 1000

#### Notes:

- 1. SYNC\_ENABLE is true at state 8 only.

- 2. NE = no edge was present at RX\_SAMPLE of HDLC clock.

- 3. E = edge detected.

- 4. EDGE comes from edge detect and deglitch state machine.

- 5. RX sample comes from RX clock generator state machine.

Figure 3.5-12. Sync Enable State Machine

# Inputs: EDGE, SYNC\_ENABLE

## Notes:

- 1. SYNC\_ENABLE comes from the sync enable state machine.

- 2. EDGE comes from the HDLC input edge detect and deglitch state machine.

- 3. X means don't care.

Figure 3.5-13. RX Clock Generator State Machine

clock state at the input synchronizing edge cannot be predicted. The timing diagram in figure 3.5-11 shows the action of the state machine for all possible HDLC IN edge/RX clock state conditions.

TX Clock EPLD. An Altera EP320 EPLD implements a state machine used to generate a common transmit clock for all the DUSCC chips and flag shutdown EPLDs on the ISIO daughter board. The DUSCC chip outputs TX data on the falling edge of the external transmit clock. The output delay from the falling edge of the clock is too long to guarantee adequate data setup time for the flag shutdown EPLD, which samples the TX data output on the rising edge of the TX clock. To allow adequate data setup time for the flag shutdown EPLD and still meet DUSCC chip external clock specification, the transmit clock is high for 125 ns and low for 375 ns. This allows maximum setup time in the flag shutdown EPLD while still meeting DUSCC chip requirements.

This EPLD also generates chip select signals for both the existing ISI0-2 68230 PI/T chip (U100) and the new PI/T chip (U20) added to the daughter board.

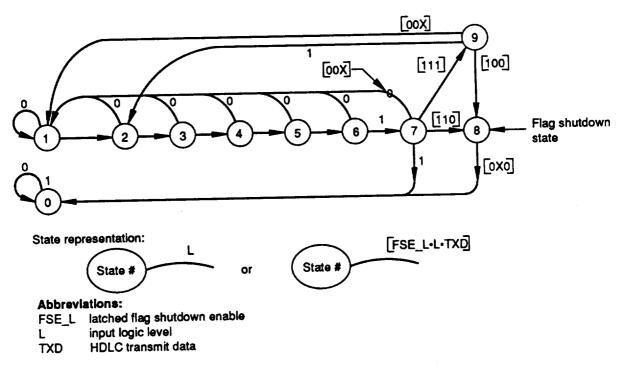

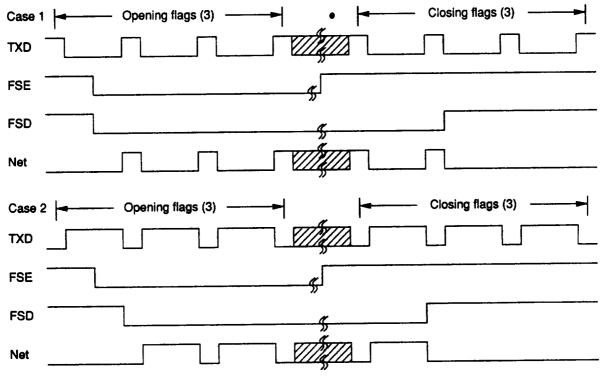

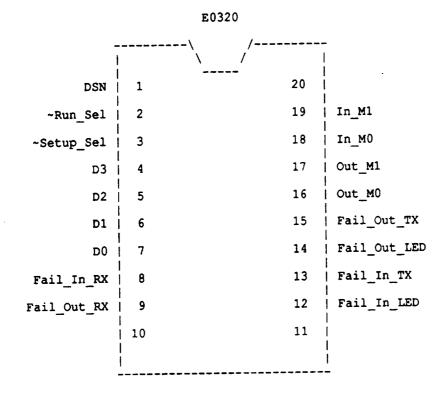

Flag Shutdown EPLD. One of the requirements of appendix B is that I/O network lines be left in a logic low state, called flag shutdown. Flag shutdown must be synchronized with data sent from the ISIO DUSCC chips to prevent spurious data from appearing on the I/O network. Because of the high output data rate, it is not possible to control the DUSCC chip accurately enough to guarantee these requirements without additional hardware.

The flag shutdown EPLD uses an Altera EP320. The state machine in the EPLD detects HDLC flags in the transmitted output data stream. When the flag shutdown enable (FSE) input is high, the state machine searches for an output flag that meets shutdown requirements. When the FSE input is low, the state machine searches for the conditions necessary to reconnect the DUSCC chip output to the I/O network. Figure 3.5-14 shows a state transition diagram for this state machine.

The flag shutdown EPLD also ensures that its associated DUSCC chip transmitter output is not connected to the I/O network at power up. Two inputs ensure that this does not happen: !SYS\_RESET is brought low whenever the VMEbus RESET signal is active; FORCE\_FSD is connected to an output of the additional PI/T, which always is pulled high at system reset. The local ISIO-2 68010 CPU must program the FORCE\_FSD line low before the flag shutdown enable input can be recognized by the EPLD.

Before FORCE\_FSD is pulled low, the TX\_CLOCK input must be present to the flag shutdown EPLD to ensure that the EPLD remains in the flag shutdown state. Failure to follow this sequence will cause the DUSCC transmitter output to be connected to the I/O network on initial power-up, potentially corrupting the entire I/O network.

LED Driver EPLD. Several bi-color (red/green) LEDs are provided on the network interconnection panel to provide status information concerning operation of the DIU simulator. Two of these EPLDs are provided to control the eight-channel status LEDs. See LED\_DRIVER EPLD listings for details.

**Simulated Node EPLD.** A Cypress Semiconductor 22V10 EPLD is used to condition DUSCC chip inputs and outputs to support the required operating modes of the DIU simulator.

Normal mode directly connects the inputs and outputs of each DIU simulator channel to its appropriate differential driver/receiver and I/O connector.

The partially simulated network of the small-scale system required a full complement of DIU simulators, but with reduced interconnection capabilities. To meet this requirement, the node mode of the 22V10 mixes data in a way similar to an AIPS node; each DUSCC input channel receives the output of all other DUSCC channels on the board plus input signals from the active I/0 connectors. In probe mode, the 22V10 disables transmitter output to the two active I/O connectors. It also combines input and output data that appear on the active I/O connector input and output pins, enabling one DUSCC chip to monitor all data on the I/O network. (This mode of operation is used only for troubleshooting I/O network problems and is not used during experiments.)

**Delay Generator.** Experiment timekeeping in the DIU simulators is performed by the 24-bit timer in the added PI/T. The input timebase is the reference fault-tolerant clock (FTC) signal on the P2 connector experiment bus.

When a PI/T timer is read by the local CPU, the three bytes of the 24-bit timer must be read individually. There is no way to snapshot the value in all three bytes of the timer with a single operation. This can lead to rollover errors caused by reading the timer while its value is changing. Four consecutive bytes are allocated to the timer in the PI/T, allowing use of the 68010 MOVEP.L instruction to obtain all timer bytes with a single, noninterruptible instruction, the rollover problem is still present, however. The first byte read by the MOVEP.L instruction is a dummy byte, which always returns a value of 0.

A delay generator EPLD using an Altera EP600 was designed that monitors the dummy read address of the timer. When a dummy byte read access is detected, the input FTC is disabled for the four read cycles of the MOVEP.L instruction necessary to obtain the dummy byte and three timer bytes. Any FTC pulse that occurs during the disable period is made up with an extra clock pulse at the end of the last read cycle. This guarantees that the timer bytes will never be read while they are changing and that no input FTC pulses will ever be missed.

External timer input restrictions for the PI/T limit its clock period to eight times the PI/T clock period. The ISIO-2 board PI/T chips use a 7.3728 MHz clock, limiting the external timer input to 1.09 µs. Because the delay generator chip may insert an extra clock pulse after a timer

read cycle, the input period must be greater than the duration of the four read cycles generated by the MOVEP.L instruction + 1.09  $\mu$ s. For the ISIO-2 board, this restricts the external timer input period to 3.26  $\mu$ s or longer. The AIPS FTC period is between 4 and 4.25  $\mu$ s, which meets these restrictions.

The delay generator EPLD also synchronizes the start of timekeeping in the DIU simulator. Inputs are provided that inhibit the FTC until the local inhibit signal is removed and both the VME sync and FTP sync signals from the experiment bus are at the RUN state.

#### 3.5.5 I/O Network Fault Inserter

Additional details of fault inserter construction are located in the documentation for the wire wrap board in documentation package E.

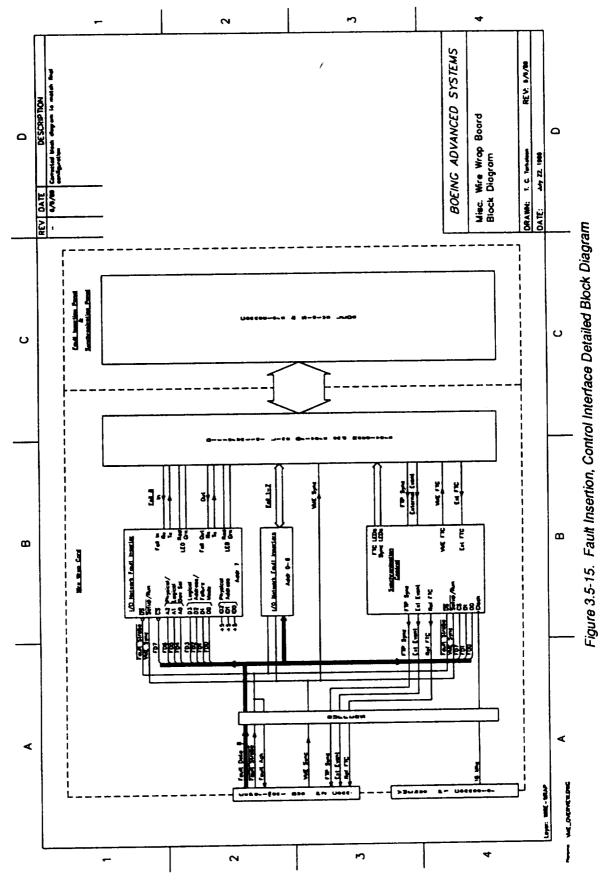

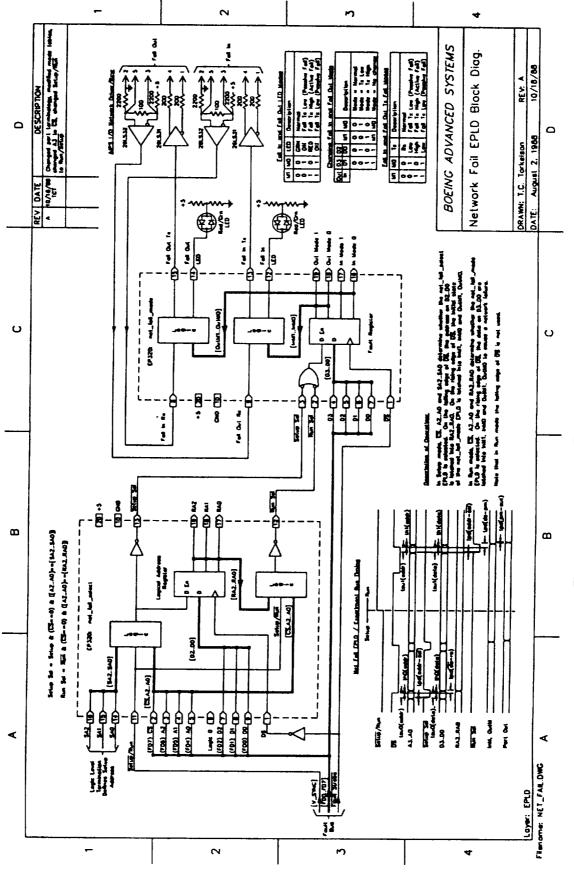

The eight network fault insertion channels are located on the VMEbus wire wrap board and are controlled by signals from the experiment bus described in appendix G. Figure 3.5-15 shows an overall block diagram of the wire wrap board. Figure 3.5-16 shows the design of a network fault insertion channel in greater detail.

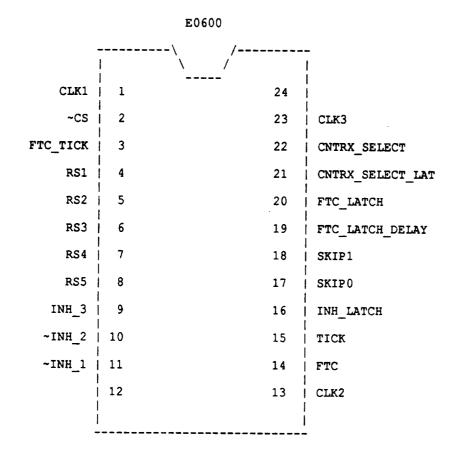

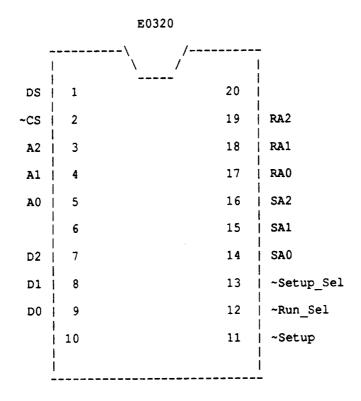

Two Altera EP320 EPLDs are used for each fault insertion channel. The NET\_FAIL\_SELECT EPLD contains a 3-bit logical address register used to map the physical channel address to a logical address. The NET\_FAIL\_MODE EPLD contains a 4-bit fault register that controls the in and out faults. Channel physical addresses are hard-wired to the SAO-SA2 inputs of the NET FAIL SELECT EPLD.

To initialize a physical fault insertion channel, its logical address register and fault register must be programmed. This can only occur while the V-SYNC line is low (simulation host VME sync line in STOP state).

ORIGINAL PAGE 13 OF POOR QUALITY

Figure 3.5-16. Network Fault EPLD Block Diagram

ORIGINAL PAGE IS OF POOR QUALITY

Initialization proceeds as follows:

- a. With Fault\_Strobe high, the fault bus is set to select the desired physical to logical address mapping: FD7 low, FD4-6 specifies the physical channel address, and FD0-2 specifies the logical address.

- b. The Fault\_Strobe is brought low to store the logical address in the logical address register of the NET\_FAIL\_SELECT EPLD.

- c. The initial condition for the NET\_FAIL\_MODE EPLD is placed on FDO-3 while the Fault\_Strobe is still low. The state of FD4-7 remains unchanged.

- d. The Fault\_Strobe is brought high, storing the initial fault condition in the fault register of the NET\_FAIL\_MODE EPLD. Note that the initial fault condition is written to a physical address, not a logical address.

When the simulation computer enters the run state, the V\_SYNC line in the experiment bus goes high. This changes the fault insertion system from physical to logical address control.

To cause a fault to a logical address the following actions occur:

- a. The fault bus is set to select the desired logical address and fault condition: FD7 low, FD4-6 specifies the logical address, and FD0-3 specifies the desired fault condition.

- b. The rising edge of the Fault\_Strobe stores the fault condition in the fault registers of all channels programmed to the selected logical address, causing the fault.

Note that the fault bus can be set up with Fault\_Strobe at either a high or low level and that only the rising edge of the Fault\_Strobe has any effect. In practice the Fault\_Strobe is always left high when the fault bus is not in use.

## 3.5.6 Miscellaneous Wire Wrap Board Functions

Detailed documentation of the wire wrap board is found in documentation package E.

The miscellaneous wire wrap board functions are implemented with two Altera EP320 EPLDs (FTC\_GEN and FTC\_CONTROL) and AIPS I/O compatible differential line drivers, receivers, and terminators.

**VME FTC Generation.** The FTC\_GEN EPLD is primarily used to generate a 4.125 µsec period FTC that can be used for the timebase of the simulation host. This clock source is available on the front panel of the wire wrap board. A bi-level LED indicates amber when the clock is operating correctly. The output of the VME FTC is high for 2.0 µs and low for 2.125 µs to match the normal operation of the AIPS FTP FTC.

VME Sync. VME sync is generated by PI/T J1 H4 output on the OPIO-1 board and routed to the wire wrap board in the experiment bus. It is converted to a differential output signal that meets the AIPS I/O network requirements of appendix B and routed to an AIPS I/O connector the front panel of the wire wrap board. The FTC\_CONTROL EPLD drives a bi-color LED on the front panel that indicates the state of the VME sync signal: red for V STOP, green for V RUN.

**FTP Sync.** The FTP Sync signal originates on an AIPS I/O connector on the front panel of the wire wrap board. AIPS I/O network-compatible differential driver and termination resistors convert it to an experiment bus level signal. The FTC-CONTROL EPLD drives a bi-color LED on the front panel that indicates the state of the FTP Sync signal: red for F\_STOP, green for F RUN.

Reference FTC Select. The FTC\_CONTROL EPLD is used to select the source of the reference FTC used for the experiment timebase in the simulation host. Either the VME-generated FTC or an external FTC can be selected. As with fault insertion setup, the reference FTC source can only be selected when the V\_SYNC line is low.

To select the FTC source and external event polarity in the FTC\_CONTROL EPLD:

- a. With FSTB\_N high, set FD7 high and set FD0 low to select the internal FTC or FD0 high to select the external reference. Set FD1 to the desired external event polarity (see below).

- b. Cycle FSTB\_N low, then high, while keeping the FDO and FD7 values stable.

Two LEDs on the wire wrap front panel indicate the clock reference selection. The VME FTC bi-color LED, driven from the FTC\_CONTROL EPLD is illuminated when the VME FTC is selected. The EXT FTC bi-color LED, driven from the FTC\_GEN EPLD, is illuminated when the external FTC is selected. The appropriate LED is amber when the selected FTC is functioning correctly and red or green when the selected FTC is stuck at logic high or logic low.

External Event Detection. AIPS I/O external event input is provided on the wire wrap board front panel. The active polarity of the event is programmable as described for FTC source selection, above. The logic level of the external event input on the experiment bus is inverted if FD1 is low at programming and non-inverted if FD1 is high. The external event bi-color LED reflects the logic level of the external event signal on the experiment bus. The LED is green for logic low and red for logic high.

The external event signal on the experiment bus is routed to PI/T J1 H3 on the OPIO-1 board.

The external event input was not used in the small-scale system.

# 3.5.7 VMBbus Computer Timekeeping

The master experiment clock used by the VMEbus system is the timer in PI/T J1 on the OPIO-1 board. A small daughter board adds a delay generator EPLD to control the action of the external timer input. Its output is bused to all other PI/T chip external timer inputs on the OPIO-1 board. The OPIO delay generator operates the same as the DIU simulator delay generator.

The timer in PI/T J3 is used for the fault injection delay timer.

## 3.6 SOFTWARE DETAILS

# 3.6.1 AIPS FTP System Services

AIPS system services were modified by CSDL to support the special requirements of small-scale system testing discussed in reference 1. Modifications included adding the means to:

- a. Control the time phasing of FDIR execution in both the CP and IOP with respect to experiment start reference time.

- b. Disable background self-test routines.

- c. Select the amount of RAM included in the exhaustive RAM background self-test.

- d. Disable I/O network spare link testing.

- e. Selectively control the start of the CRT display tasks.

## 3.6.2 AIPS FTP Pseudoapplications

Requirements for pseudoapplication software is discussed in reference 1. Listings of pseudoapplications are included on the software tape (see appendix I).

## 3.6.3 VMB System Kernel and Utilities

The VMEbus CPU-29 uses silicon software components from Ready Systems. The Ready Systems concept is that additional functions in EPROM can be added to a core operating system kernel (VRTX32) as required with very little need for custom configuration. The components can be verified to operate correctly independent of the hardware platform on which they will ultimately reside.

The Ready Systems silicon software components installed in EPROM include VRTX32, IFX, and RTscope. A board support package (BSP) from Ready Systems was modified to support the specific requirements of the general purpose test system. The Ready Systems Real Time C (RTC) library, although not a software component, was also placed in EPROM. The RTC library is a sharable library; its inclusion in EPROM allows smaller load modules to be developed for the CPU-29.

The IFX extension to VRTX32 provides MS-DOS compatible RAM disks and allows multiple user tasks to share physical devices such as the simulation host console. Each task can send messages to the console to log its progress.

Further information on the Ready Systems products used can be found in references 3 through 13.

To interface the VMEbus simulation system with the MicroVAX experiment host computer system, the VULTURE program was written. Portions of the VULTURE program reside in both the VMEbus system and the MicroVAX system. Appendix H presents a detailed discussion of this program.

Noncopyrighted portions of the VME system kernel and utilities are included in the software tape (see appendix I).

## 3.6.4 DIU Kernel

The ISIO-2 board from Force Computers comes with a small operating system kernel that was not adequate for the operation of the DIU simulators for the small-scale system. The firmware operating system was only used to load the DIU kernel, at which point the onboard ISIO-2 firmware was disabled and DIU simulator software was loaded. All kernel functions are implemented as TRAP instructions. User access to kernel functions is via macros that complete the setup for the traps. COMMAND\_KERNEL.INC on the software tape discusses the operation of the specific macros.

All DIU kernel operation is polled; no interrupts are used. This allows minimum latency for user programs that use interrupts and kernel functions.

The kernel operates in supervisor mode; user programs may operate in either supervisor or user mode.

#### 3.6.5 DIU Simulator

The core source files for creating DIU simulator software are DIU\_INIT, DIU\_START, and DIU\_SVC. These files are linked with NxDIUy files that define unique DIU configurations. Four unique DIU configurations were created for the small-scale system and reside in absolute files N1DIU1.ABS, N1DIU2.ABS, N2DIU1.ABS, and N2DIU2.ABS.

The NxDIUy.SRC files are created by a DEC C program called MAKE\_FRAME\_FILES that takes frame definitions from FRAME\_DATA.C, DIU.H, and unique DIU definition NxDIUy.DEF files to create the source files. The source files are assembled using the Microtec Assembler on the development host to produce linkable DIU configuration files for inclusion with the core DIU files. If modification of transaction definitions or timeouts is required, the FRAME\_DATA.C file is modified, recompiled, and MAKE\_FRAME\_FILES is re-linked.

To modify the allocation of DIU addresses to simulator board absolute files the NxDIUy.DEF files are modified, and the DCL command file MAKE\_TABLES.COM is used to create the source and object files. Command file LINK\_DIU.COM creates the new DIU absolute files.

The new absolute files are copied to the experiment host computer for loading in the simulation host and DIU simulators.

The new set of DIU absolute format files must be converted to executable form in the simulation host and saved on the experiment host hard disk as follows:

- a. DOWN\_LOAD NxDIUy.ABS NxDIUy.ABS downloads the absolute file to the DRAM: disk in the simulation host.

- b. VCONVERT NxDIUy.ABS NxDIUy.EXE converts the Motorola S record format absolute file to an executable image file. Note that the VCONVERT command automatically makes the executable image file a contiguous file.

- c. UP\_LOAD NxDIUy.EXE NxDIUy.EXE saves the executable image in the experiment host.

DIU simulator software uses a double buffering scheme in the ISIO-2 dual port RAM to collect data during experiment runs. Each buffer is capable of holding 46 kB of data. A handshake scheme with the VMEbus computer was established to allow control of the buffers and to notify the VMEbus computer when a buffer was full. Software locks prevent data corruption in either buffer while allowing real-time buffer flushing by the VMEbus CPU and buffer filling and swapping by the ISIO-2 CPU. Small scale system tests were short enough in duration that the DIU simulator buffers did not overflow during normal operation and were unloaded at the completion of each experiment run.

The DIU\_START module controls the sequencing of operations of the DIU simulator during an experiment. It is responsible for calling subroutines in the DIU\_INIT file which set up peripheral chips, initialize interrupts, disable interrupts, etc. The DIU\_START module also signals the VMEbus CPU to perform a final buffer flush at the end of an experiment run before returning DIU simulator operation to the DIU kernel. The DIU simulator software is interrupt driven during experiment operation. Interrupt service routines in the DIU\_SVC module are used to remove data from the DUSCC chip FIFOs when a frame passes address screening. The DIU\_SVC module also validates a received frame, prepares an appropriate response, logs data and errors, and controls the eight channel LEDs on the front panel.

## 3.6.6 I/O Network Probe

I/O network probe software used all the core DIU simulator routines, replacing DIU\_SVC with FAST\_PROBE\_SVC. No address screening is used in the probe; all data received is logged in the double buffer scheme. Because of the amount of data collected by the probe, the VMEbus CPU is required to flush buffers in real time.

The turn around time of some of the network transactions is so fast that the probe software may not have time to recover and may erroneously record bad data. The validity of probe data can be determined by comparing DIU simulator and probe data and by the selected probe location in the network.

Operation of the probe during small scale system integration showed that the buffers could hold a maximum of 30 seconds of data before overflow occurred. The VMEbus CPU polled each probe every 500 msec to ensure that its buffers were promptly flushed.

#### 3.6.7 DIU Data Formatting

Data from DIU simulators was recorded in the ISIO-2 dual port RAM in binary form to maximize storage capacity. When data are removed from the dual port RAM, the VMEbus CPU program first removes the binary format data to a temporary binary file in DRAM: disk. At the completion of an experiment, the temporary file is then converted to an ASCII data file in the DRAM: disk. Only the DIU simulator data fields required by the data analysis program are saved.

The UNLOAD program operates slightly differently on probe data. It is used in real time during an experiment to remove data from the ISIO-2 probe buffers. Post experiment formatting saves all data for later use.

# 3.6.8 Fault Insertion Control

The fault insertion control program, FAULT, is an optional program for use only during experiments requiring I/O network fault insertion. It runs autonomously after it is loaded and started on the VMEbus CPU. It requires that a FAULT.DAT file be present on the DRAM: disk which defines the data required to initialize each fault channel, perform physical to logical mapping, set up a time delay to the fault, and define the fault condition.

# 3.6.9 VME Experiment Control

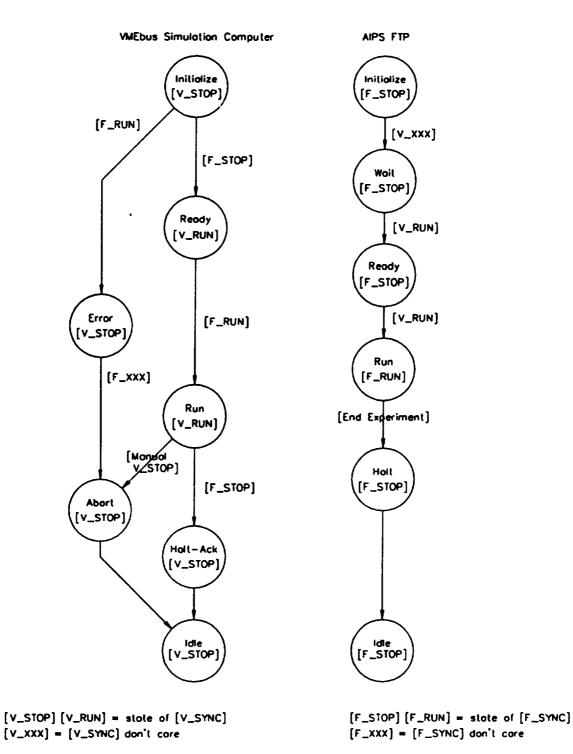

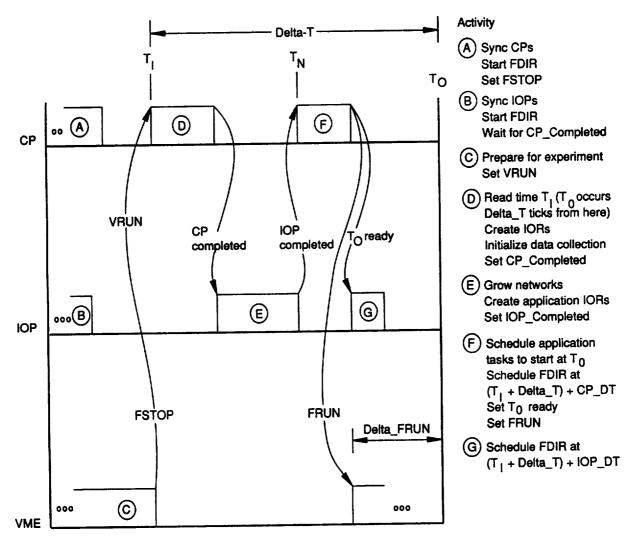

A master simulation host experiment control program (CONTROL) was used to sequence the simulation host through experiment synchronization handshakes discussed in appendix A. The CONTROL program uses a CONTROL.DAT file in the simulation host DRAM: disk to determine which DIU simulators are active. This file must agree with the actual use of DIU simulators controlled by the experiment control command files.

The CONTROL program controls the VME Sync output to the FTP. It also

moni.ors the FTP Sync input. The program can be aborted at any time it is active by manually cycling the VME Sync output using VGO and VNO commands.

### 3.6.10 MicroVAX Interface Software

The MicroVAX interface to the VMEbus simulation computer is controlled by VULTURE software which resides in both the VMEbus computer and on disk in the micro vax. Appendix H discusses this software in detail.

The DRQ3B interface to the VMEbus system is controlled by a DEC supplied driver. DEC C programs were written to interface VULTURE protocol to the DRQ3B driver.

Details on the operation of the VRIP interface which is used to control the FTP are available from CSDL.

#### 3.6.11 Experiment Control Command Files

All experiment operation was controlled from the experiment host. When the experimenter logged in, the account which was active set up several VRIP related aliases. The first operation was to initialize the VRIP interface, providing access to the FTP in the system under test.

Following successful initialization of the VRIP system, the experimenter then set up the environment for data collection, executable image loading, and simulation computer control.

Several classes of DEC DCL command files were used:

- a. VRIP initialization control files were supplied by CSDL and are used to set up the interface and screen for FTP control.

- b. Definition command files created symbols which accessed command files. VULTURE.COM and SYMBOLS.COM set up the experiment environment.

- c. Simulation computer loading was controlled by VME\_LOAD\_EXE.COM.

- d. FTP computer loading was controlled by LD\_xx.COM files in experiment directories.

- e. FTP program patch files were used to correct problems in FTP IOP programs caused by the VRTX Ada compiler.

- f. FTP experiment setup command files defined unique experiment parameters.

- g. Program execution was controlled by the RUN\_EXP command file. It accessed other command files which loaded DIUs and extracted data from both the simulation computer and the FTP.

- h. FTP data collection was controlled by the GET\_FTP command file. The command file used the known configuration of FTP memory to extract experiment data without additional operator input.

- j. Simulation computer data collection was controlled by the UNL\_DIU command file. It controlled the post experiment operation of the UNLOAD programs.

It was not possible to totally automate the control of small scale system testing because of the need to manually record the FTP logs.

#### REFERENCES

- G. C. Cohen, et al., Design of an Integrated Airframe/ Propulsion Control System Architecture, NASA CR-182004, March 1990.

- 2. DRQ3B Parallel DMA I/O Module User's Guide, DEC order number EK-47AA-UG-001.