9DL

## **VIRCINIA POWER ELECTRONICS CENTER**

22

G

A T

Å

T L

C H THE BRADLEY DEPARTMENT OF ELECTRICAL ENGINEERING

# SPACE PLATFORM POWER SYSTEM HARDWARE TESTBED

## FINAL REPORT

300

PREPARED FOR NASA GODDARD SPACE FLIGHT CENTER GREENBELT, MD Contract No. NAG 5-1232

> D. Sable, A. Patil, T. Sizemore, S. Deuty J. Noon, B.H. Cho, and E.C. Lee

June 21, 1991

VPEC IS A TECHNOLOGY DEVELOPMENT CENTER OF THE VIRGINIA CENTER FOR INNOVATIVE TECHNOLOGY

VIRGINIA POLYTECHNIC INSTITUTE AND STATE UNIVERSITY

BLACKSBURG, VA. 24061-0111 (703) 231-4536

## SPACE PLATFORM POWER SYSTEM HARDWARE TESTBED

## FINAL REPORT

Prepared For NASA Goddard Space Flight Center Greenbelt, MD Contract No. NAG 5-1232

Prepared By D. Sable, A. Patil, T. Sizemore, S. Deuty, J. Noon, B.H. Cho, and F.C. Lee

June 21, 1991

## FINAL REPORT

## SPACE PLATFORM POWER SYSTEM HARDWARE TESTBED

## TABLE OF CONTENTS

|                                                        | Page |

|--------------------------------------------------------|------|

| 1.0 INTRODUCTION                                       | 1    |

| 2.0 MULTI-MODULE BOOST CONVERTER DESIGN                | 2    |

| 2.1 MAGNETICS DESIGN                                   | 2    |

| 2.1.1 METGLAS Material                                 | 2    |

| 2.1.2 MPP Material                                     | 7    |

| 2.2 OUTPUT FILTER DESIGN                               | 9    |

| 2.3 DISCRETE PWM DESIGN                                | 14   |

| 2.4 PROTECTION CIRCUIT DESIGN                          | 15   |

| 2.5 CONTROL LOOP DESIGN                                | 19   |

| 2.5.1 Small Signal Characteristics                     | 19   |

| 2.5.1.1 Continuous Mode of Operation                   | 20   |

| 2.5.1.1.1 PSPICE Modelling                             | 20   |

| 2.5.1.1.2 Control-to-Output Transfer Function Analysis | 22   |

| 2.5.1.1.3 Output Impedance Analysis                    | 24   |

| 2.5.1.2 Discontinuous Mode of Operation                | 26   |

| 2.5.1.2.1 PSPICE Modelling                             | 26   |

| 2.5.1.2.2 Loop Gain Stability Analysis                 | 26   |

| 2.5.1.2.3 Output Impedance Analysis                    | 30   |

| 2.5.2 Current Sense Design                             | 30   |

| 2.5.3 External Ramp Design                             | 32   |

| 2.5.4 Voltage Loop Design                              | 33   |

| 2.6 THEORETICAL AND EXPERIMENTAL RESULTS               | 33   |

| 2.6.1 Small-Signal Loop Gain and Output Impedance                | 36  |

|------------------------------------------------------------------|-----|

| 2.6.2 Large-Signal Step Load Response                            | 39  |

| 2.6.3 EMI Characteristics                                        | 39  |

| 2.6.3.1 Output Voltage Ripple                                    | 43  |

| 2.6.3.2 Input Current Ripple and Module Current Sharing          | 43  |

| 3.0 VOLTAGE-FED, PUSH-PULL, AUTOTRANSFORMER DESIGN               | 50  |

| 3.1 INTRODUCTION                                                 | 51  |

| 3.1.1 Voltage-Fed, Push-Pull Autotransformer (VFPPAT)            | 55  |

| 3.1.2 Summary                                                    | 58  |

| 3.2 VFPPAT POWER STAGE DESIGN                                    | 59  |

| 3.2.1 General Power Stage Analysis                               | 59  |

| 3.2.2 Power Stage Component Selection                            | 64  |

| 3.2.2.1 Inductor                                                 | 64  |

| 3.2.2.2 MOSFET Switch Transistors                                | 72  |

| 3.2.2.3 Rectifier Diodes                                         | 75  |

| 3.2.2.4 Output Capacitor                                         | 76  |

| 3.2.2.5 Input Capacitor                                          | 77  |

| 3.2.3 Summary                                                    | 78  |

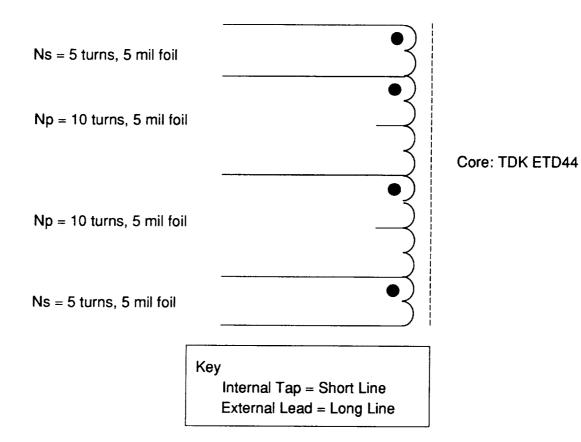

| 3.3 POWER STAGE MAGNETICS                                        | 79  |

| 3.3.1 Autotransformer                                            | 79  |

| 3.3.1.1 Core Design                                              | 79  |

| 3.3.1.2 Windings Design                                          | 85  |

| 3.3.1.3 Autotransformer Measured and Performance Testing Results | 89  |

| 3.3.2 Inductor                                                   | 92  |

| 3.3.3 Summary                                                    | 97  |

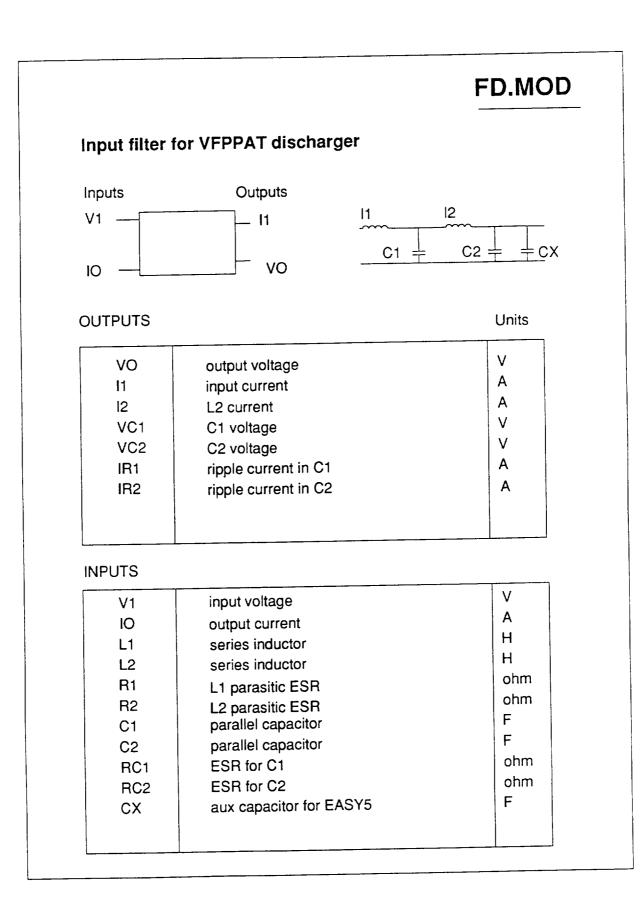

| 3.4 INPUT FILTER                                                 | 100 |

| 3.4.1 Input Filter Design                                        | 100 |

| 3.4.1.1 Component Values                                         | 104 |

| 3.4.1.2 Component Selection                             | 105 |  |

|---------------------------------------------------------|-----|--|

| 3.4.2 Input Filter Performance                          | 108 |  |

| 3.4.3 Summary                                           | 111 |  |

| 3.5 CONTROL BOARD DESIGN OPTIMIZATION                   | 113 |  |

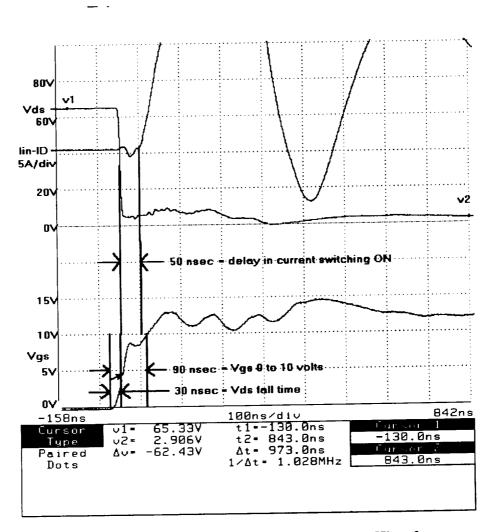

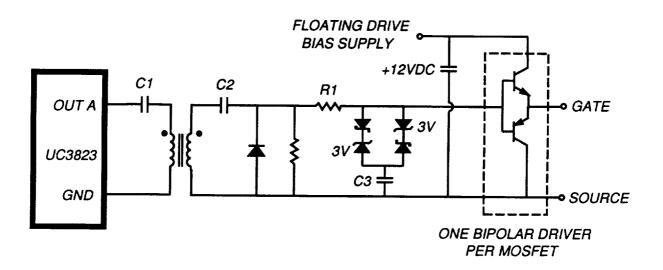

| 3.5.1 Design of PWM and MOSFET Gate Drive Circuitry     | 115 |  |

| 3.5.2 Current-Injection Control (CIC) Loop              | 117 |  |

| 3.5.3 Voltage Loop Design and Optimization              | 122 |  |

| 3.5.4 Measured Small-Signal Performance                 | 126 |  |

| 3.5.5 Measured Large-Signal Performance                 | 134 |  |

| 3.5.6 EASY5 Model Analysis and Results                  | 139 |  |

| 3.5.7 Summary                                           | 146 |  |

| 3.6 POWER STAGE PERFORMANCE                             | 147 |  |

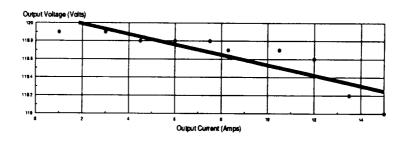

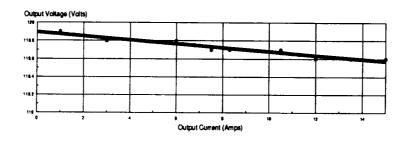

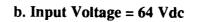

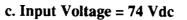

| 3.6.1 Regulation                                        | 147 |  |

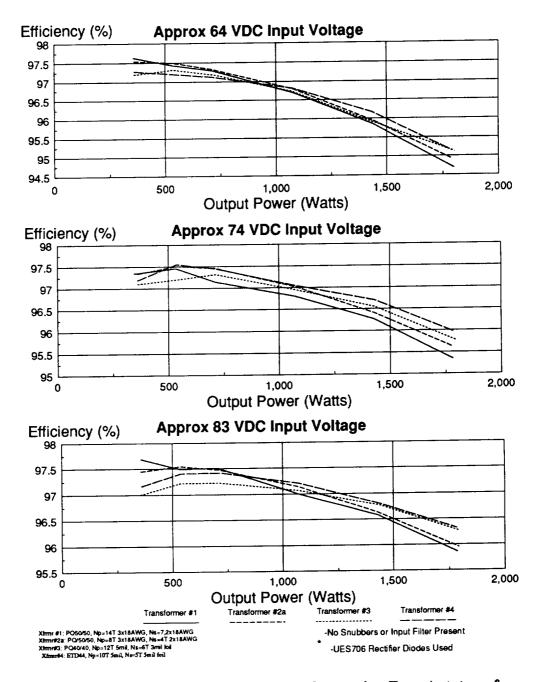

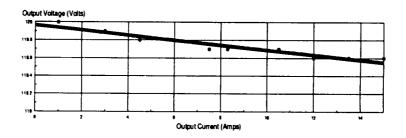

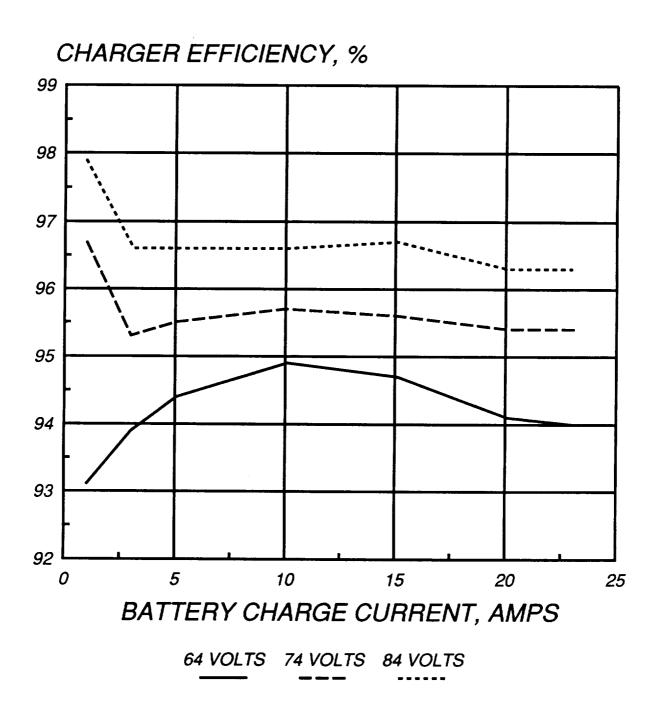

| 3.6.2 Efficiency                                        | 149 |  |

| 3.6.2.1 Efficiency at the Terminals                     | 149 |  |

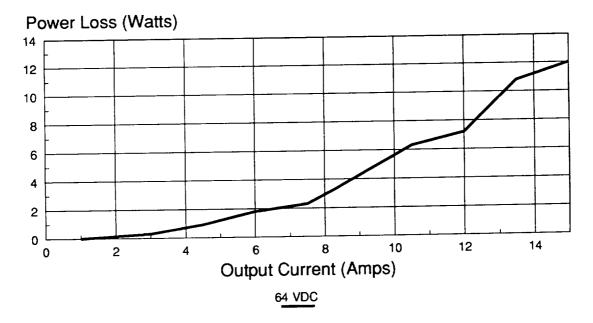

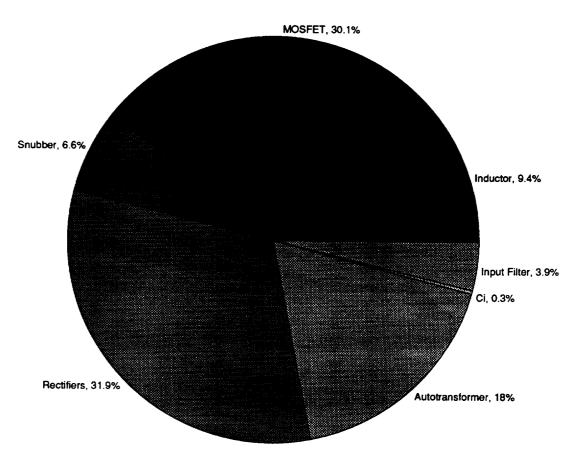

| 3.6.2.2 Power Dissipation in the Power Stage Components | 152 |  |

| 3.6.3 Summary                                           | 162 |  |

| 3.7 SUMMARY                                             | 162 |  |

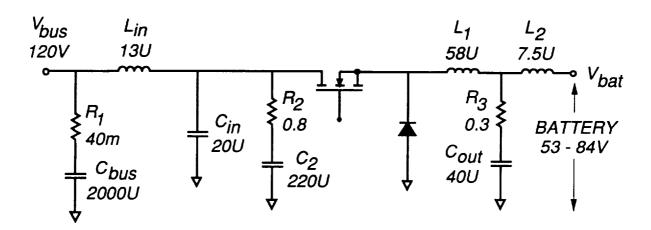

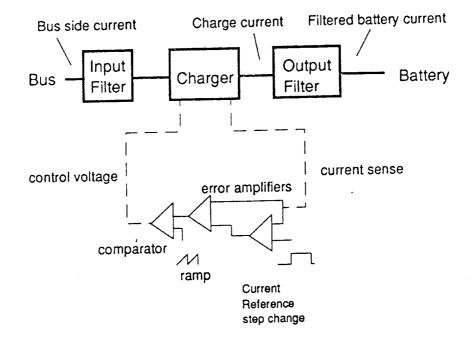

| 4.0 BATTERY CHARGER DESIGN                              | 167 |  |

| 4.1 DESIGN SPECIFICATIONS AND TRADEOFFS                 | 167 |  |

| 4.2 POWER STAGE DESIGN                                  | 169 |  |

| 4.2.1 Power Switches                                    | 169 |  |

| 4.2.2 Drive Circuit                                     | 171 |  |

| 4.2.3 Input Filter                                      | 173 |  |

| 4.2.4 Output Filter                                     | 174 |  |

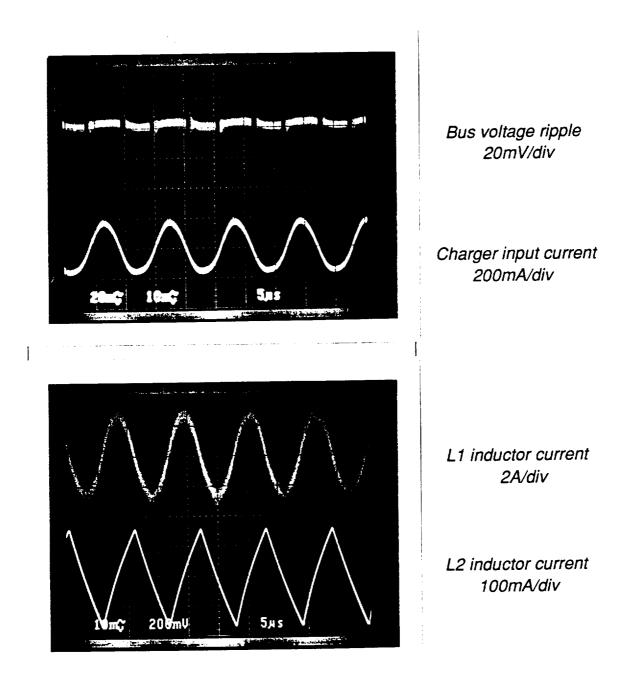

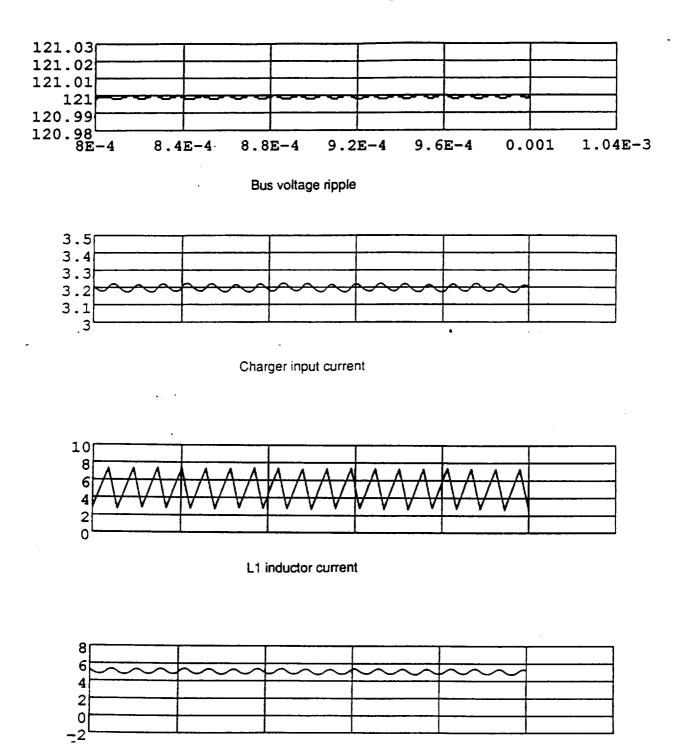

| 4.2.5 Power Stage Performance                           | 175 |  |

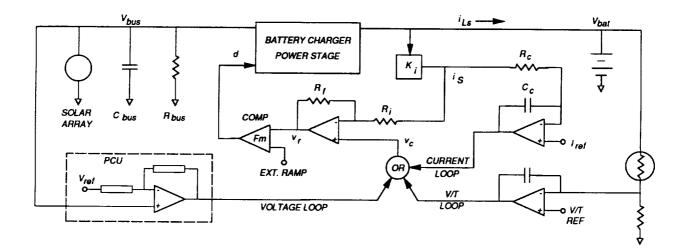

| 4.3 CONTROL SYSTEM MODELLING                            | 179 |  |

| 4.3.1 Control System Configuration                      | 179 |  |

-----

| 4.3.2 Power Stage Modelling                                | 179 |

|------------------------------------------------------------|-----|

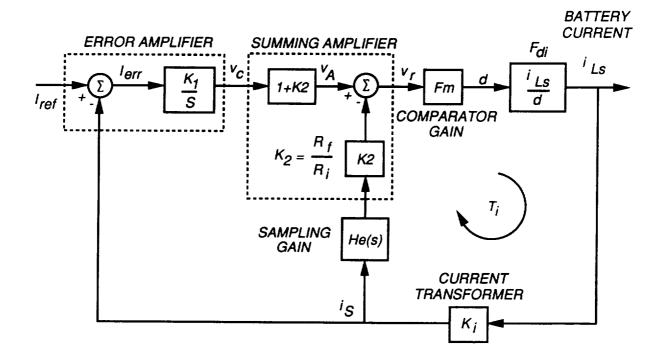

| 4.3.3 Current Mode Control Modelling                       | 182 |

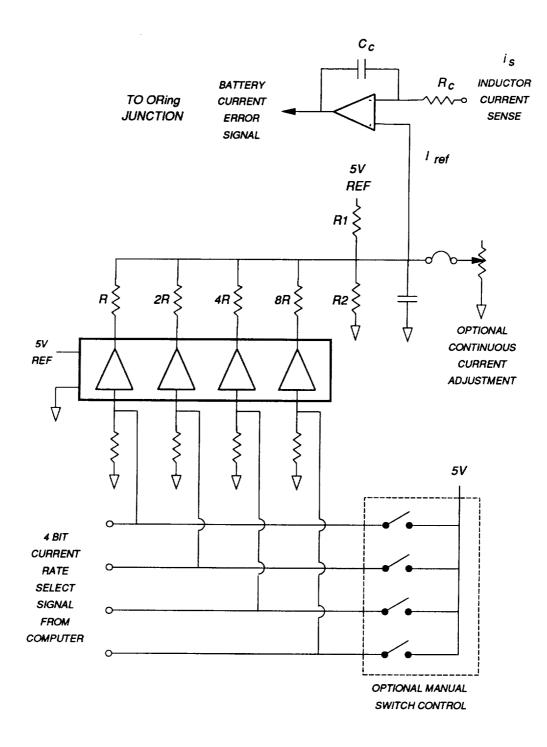

| 4.4 CURRENT REGULATION MODE                                | 183 |

| 4.4.1 Current Sensing and Control                          | 183 |

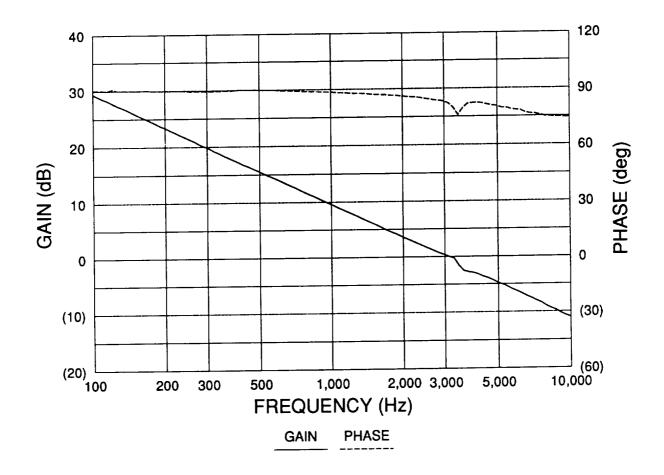

| 4.4.2 Current Loop Design                                  | 190 |

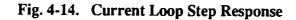

| 4.4.3 Transient Response                                   | 191 |

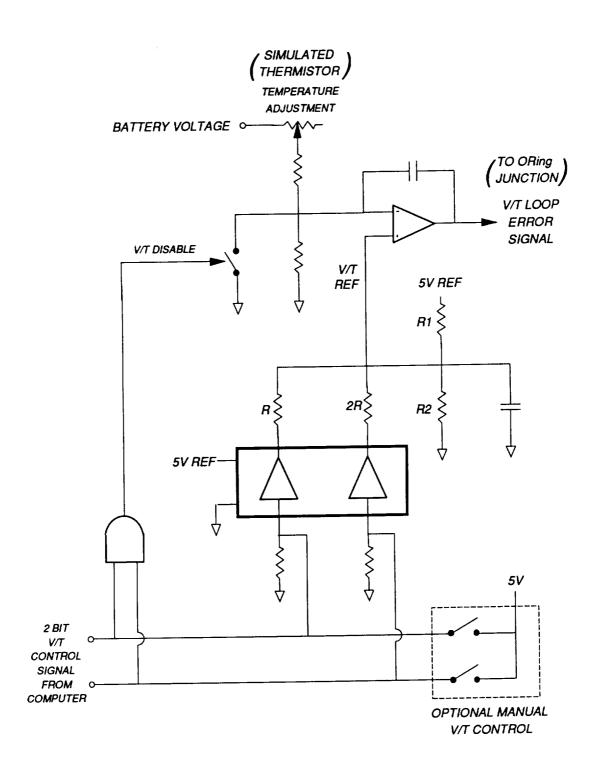

| 4.5 VOLTAGE REGULATION MODE                                | 196 |

| 4.5.1 Bus Voltage Control                                  | 196 |

| 4.5.2 Power Stage Transfer Functions                       | 197 |

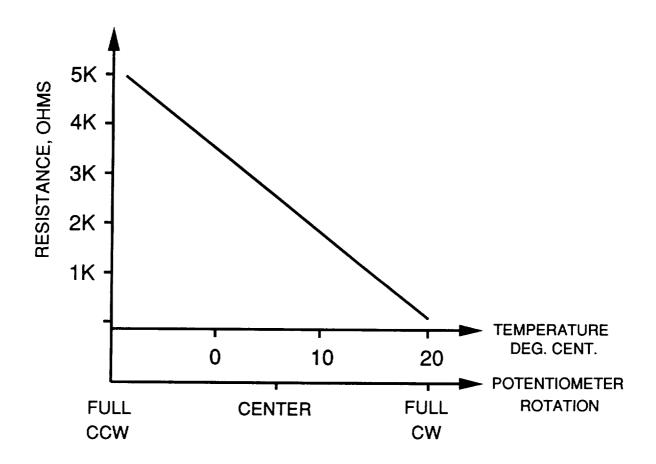

| 4.5.3 Feedback Loop Design                                 | 200 |

| 4.5.4 Voltage Loop Performance                             | 205 |

| 4.6 MODE TRANSITION SIMULATION                             | 210 |

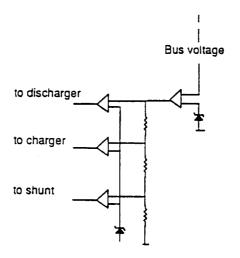

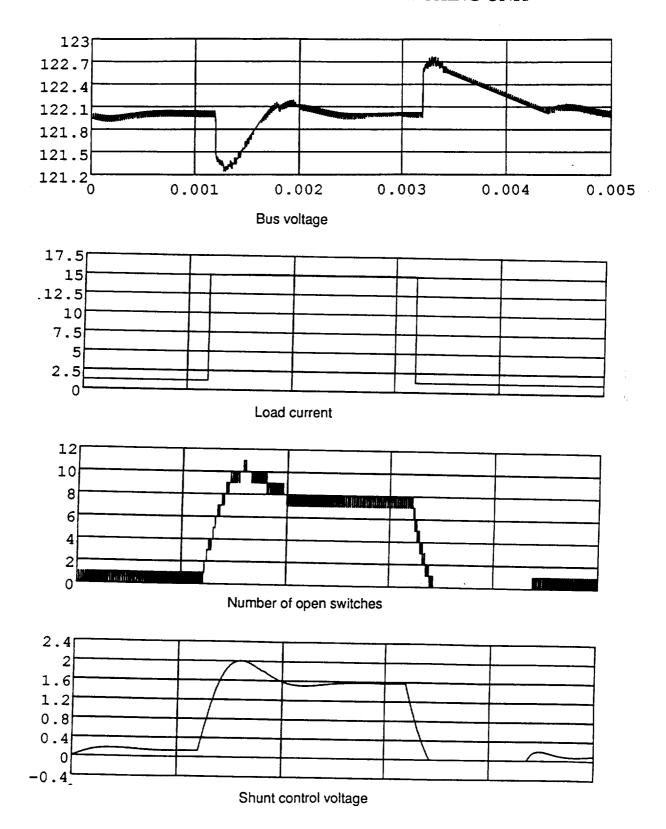

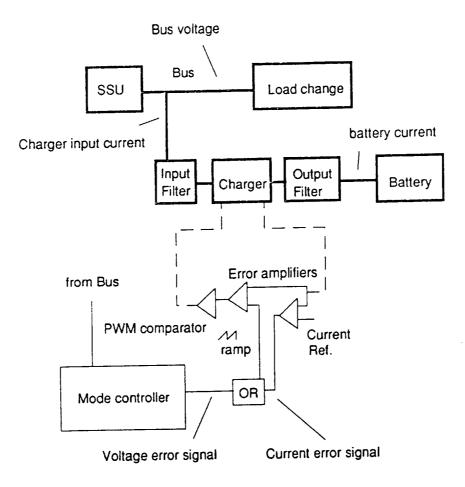

| 5.0 MODE CONTROLLER                                        | 216 |

| 5.1 CONTROLLER CIRCUIT DESIGN                              | 215 |

| 5.2 THEORETICAL AND EXPERIMENTAL RESULTS                   | 215 |

| 5.2.1 Effects of Cable                                     | 215 |

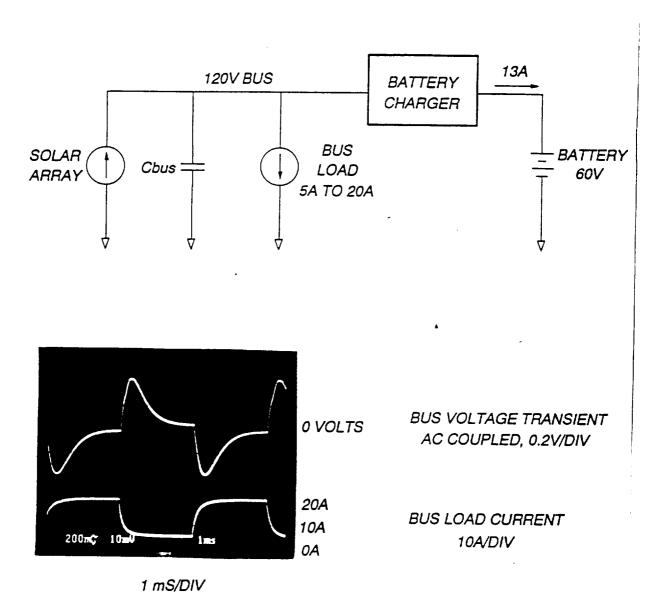

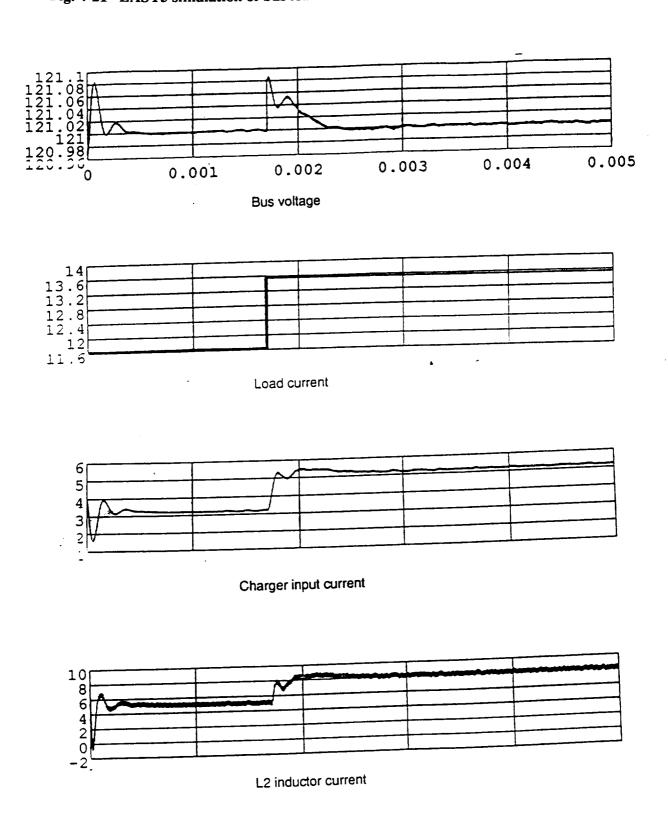

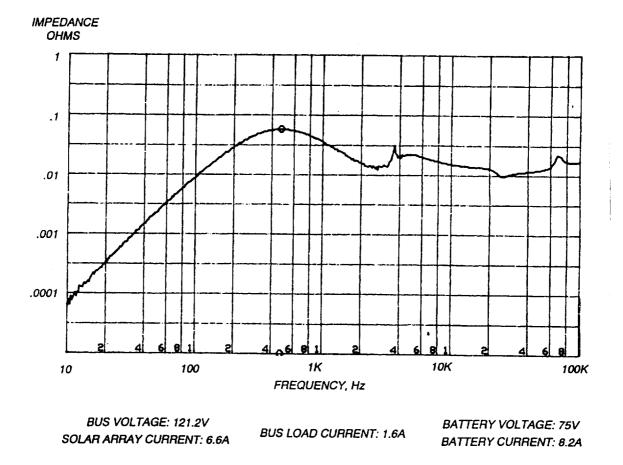

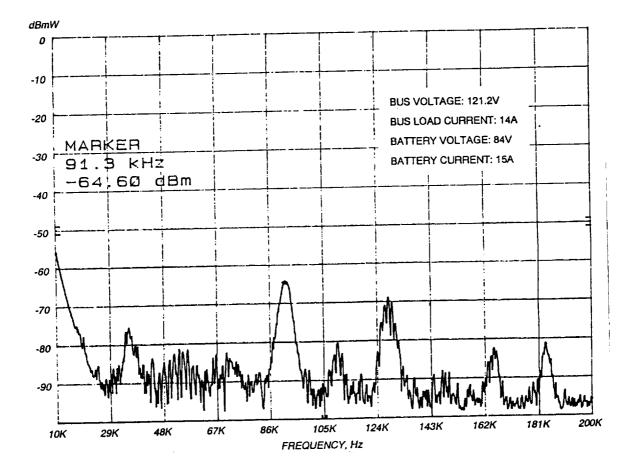

| 5.2.2 Large-Signal Dynamics                                | 218 |

| 6.0 OTHER TOPOLOGIES                                       | 224 |

| 6.1 BIDIRECTIONAL CHARGER/DISCHARGER                       | 224 |

| 6.2 ZERO-RIPPLE CHARGER/DISCHARGER                         | 224 |

| 6.3 MULTI-MODULE CHARGER                                   | 227 |

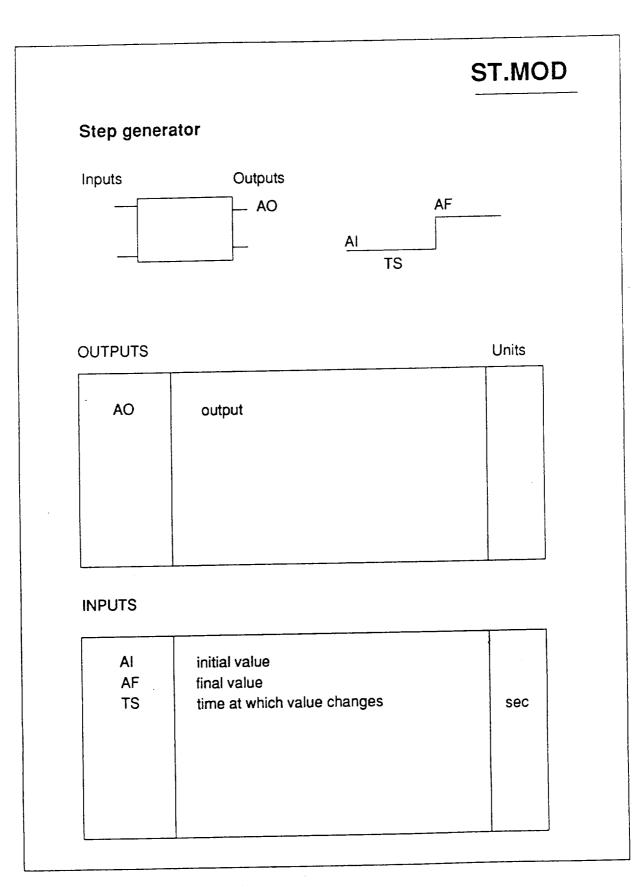

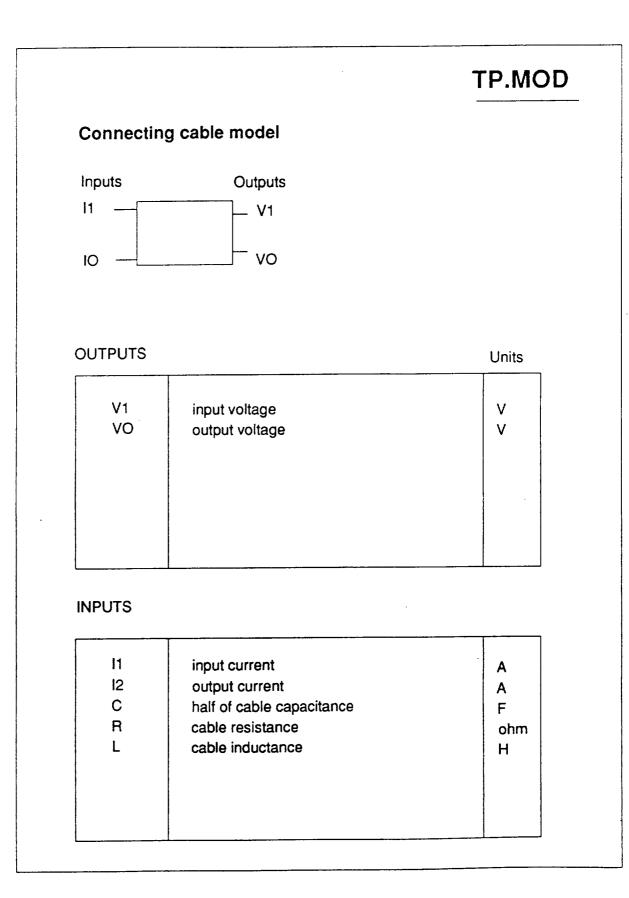

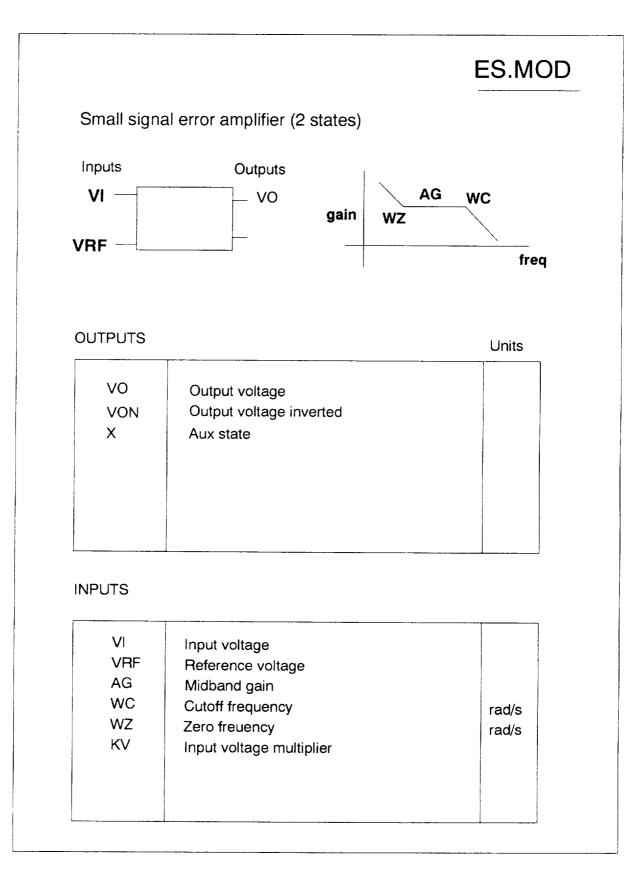

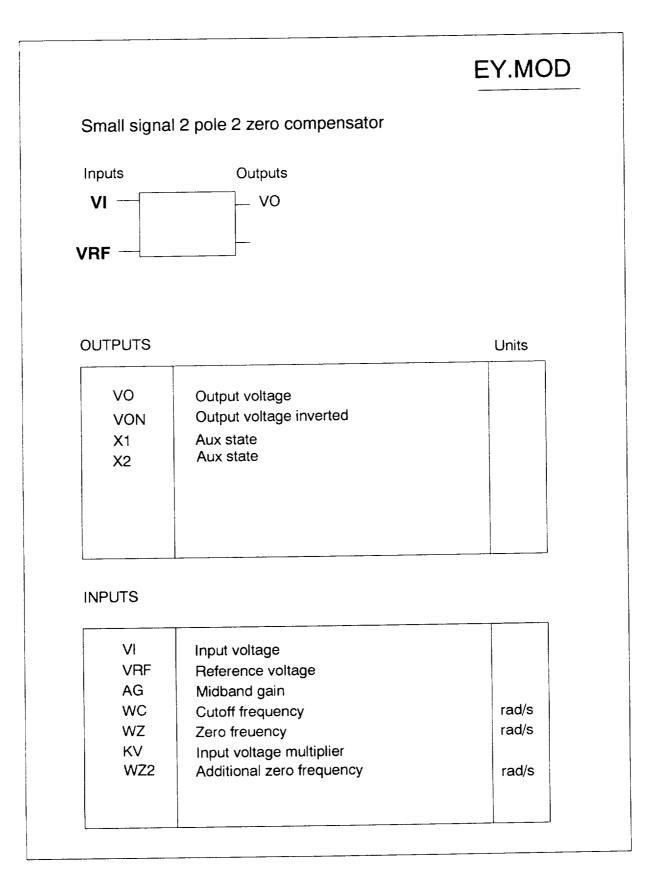

| 7.0 EASY5 COMPONENT AND SYSTEM MODELS                      | 230 |

| 7.1 INTRODUCTION                                           | 231 |

| 7.2 COMPONENT MODEL FILES                                  | 231 |

| 7.3 SYBSYSTEM AND SYSTEM MODEL FILES                       | 232 |

| 7.4 ANALYSIS FILES                                         | 232 |

| 7.5 SWITCH STATES, NONLINEARILTIES AND INTEGRATION METHODS | 233 |

| 7.6 ABNORMAL COMP. VALUES, TIME-CONSTANTS, AND TINC        | 234 |

|                                                            |     |

| 7.7 CONVERTER MODELING                          | 235 |

|-------------------------------------------------|-----|

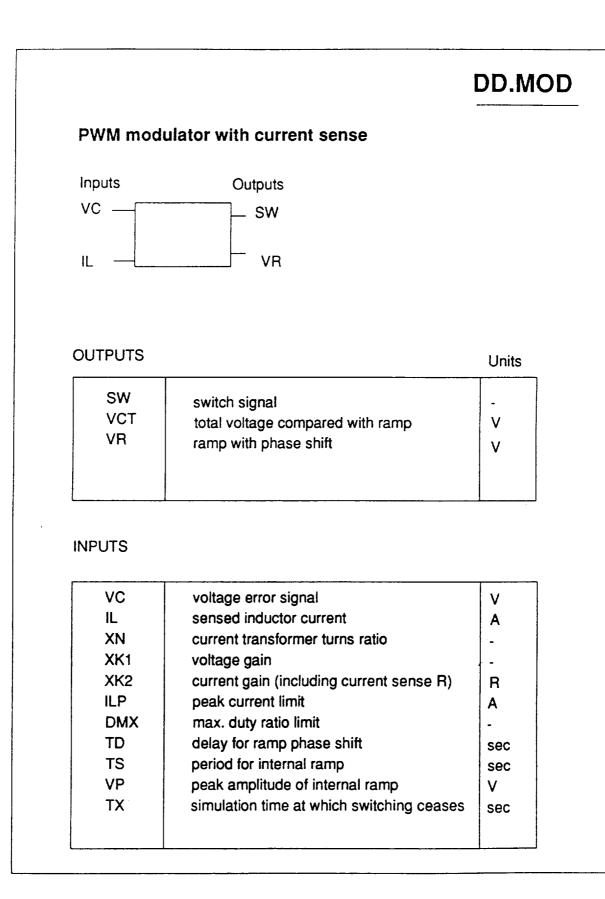

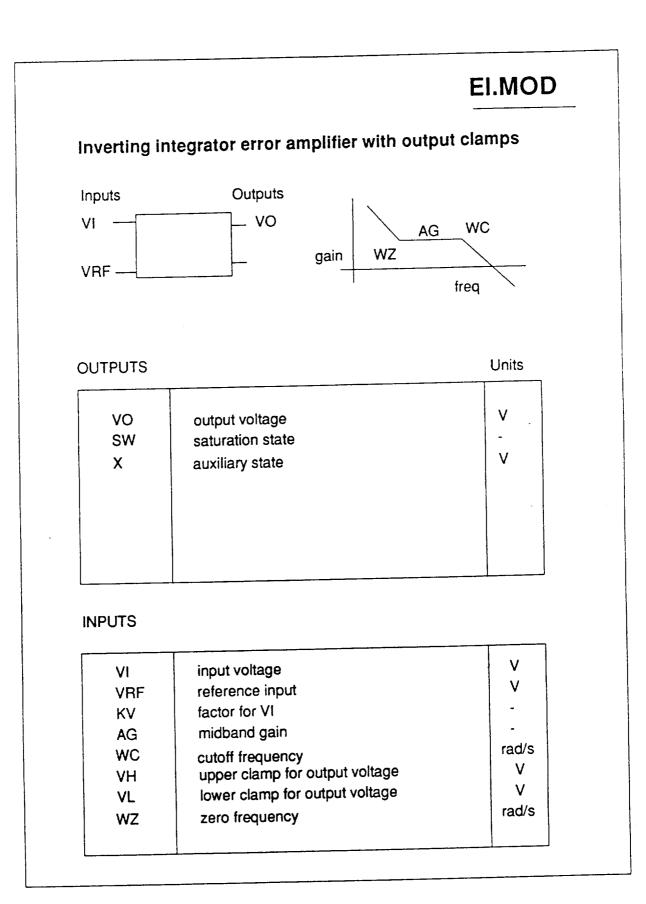

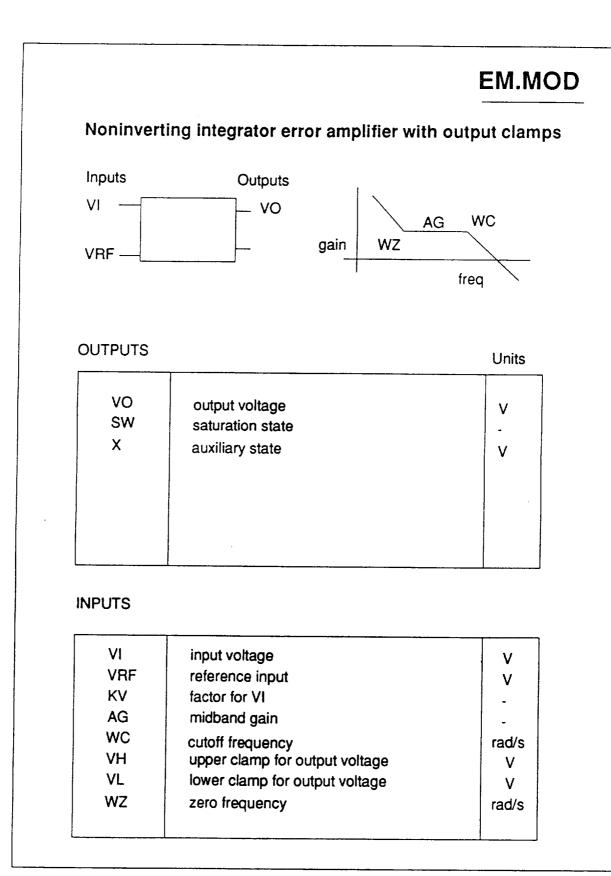

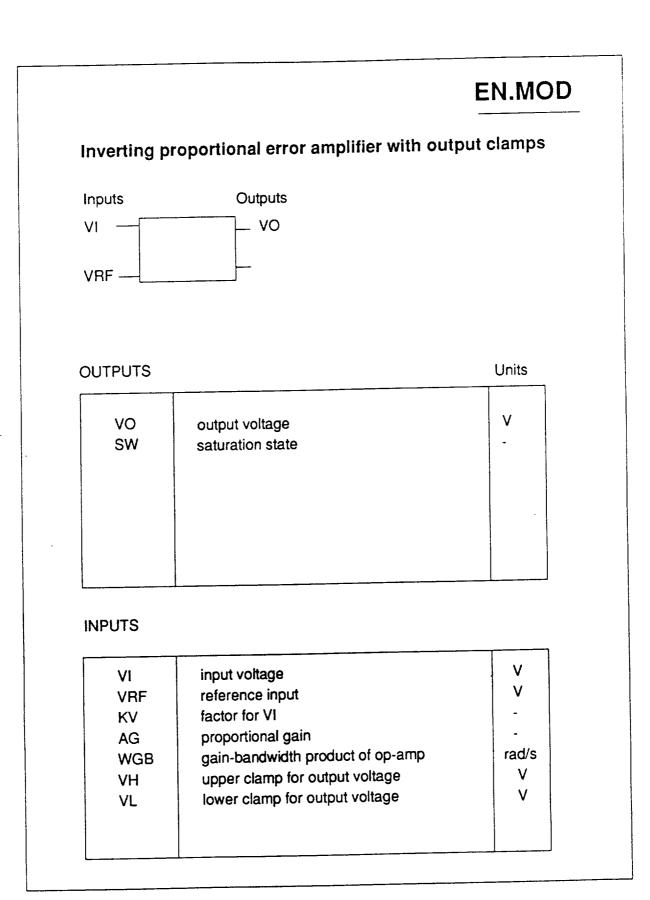

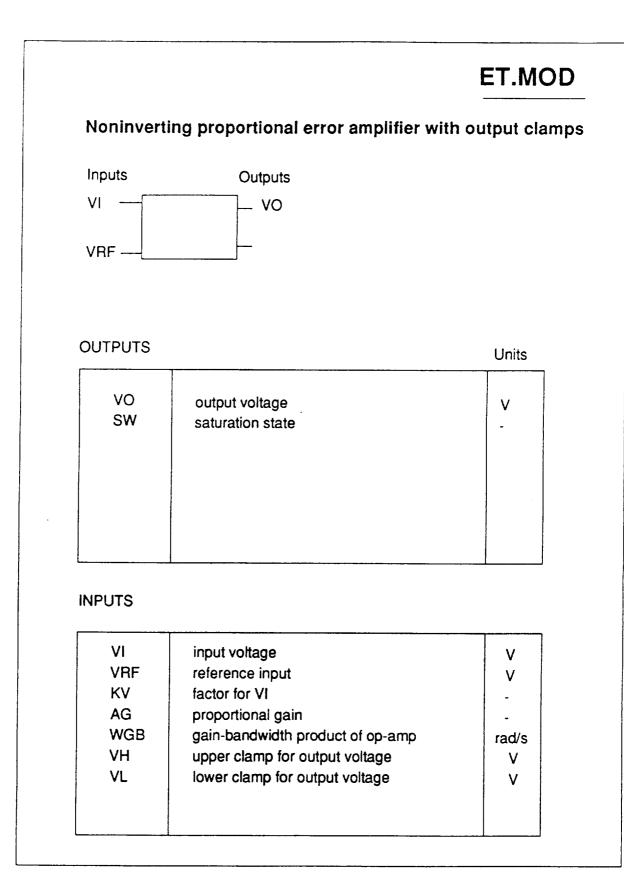

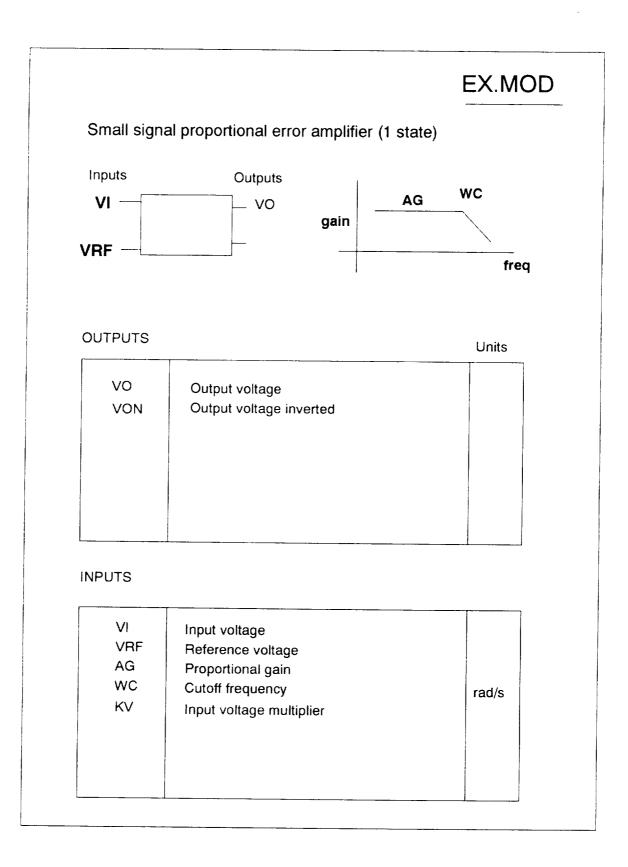

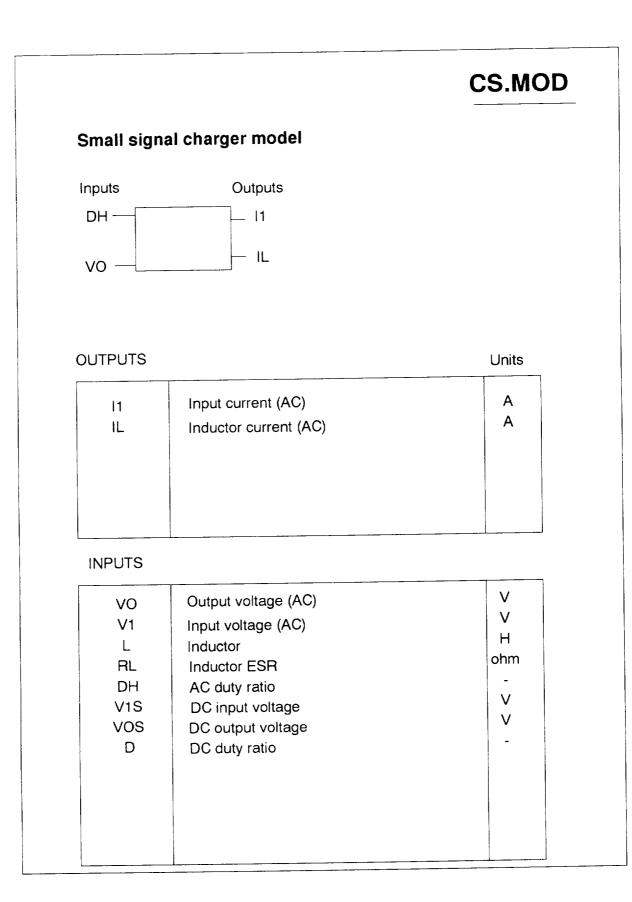

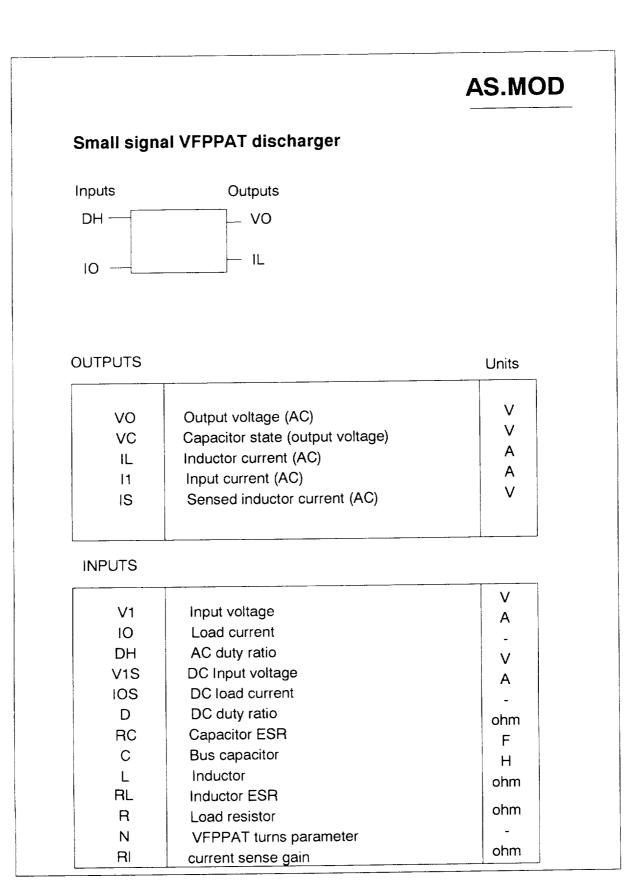

| 7.8 ERROR AMPLIFIER MODELING                    | 237 |

| 7.9 CONNECTING CABLE MODELING                   | 240 |

| 7.10 SMALL SIGNAL MODELS                        | 241 |

| 7.11 ADDITIONAL SIMULATIONS                     | 246 |

| 8.0 CONCLUSIONS                                 | 260 |

| APPENDIX                                        | 263 |

| DESCRIPTIVE LIST OF SUBSYSTEM AND SYSTEM MODELS | 264 |

| ANALYSIS FILES                                  | 284 |

| COMPONENT MODELS                                | 318 |

# SPACE PLATFORM POWER SYSTEM HARDWARE TESTBED - FINAL REPORT

## **1.0 INTRODUCTION**

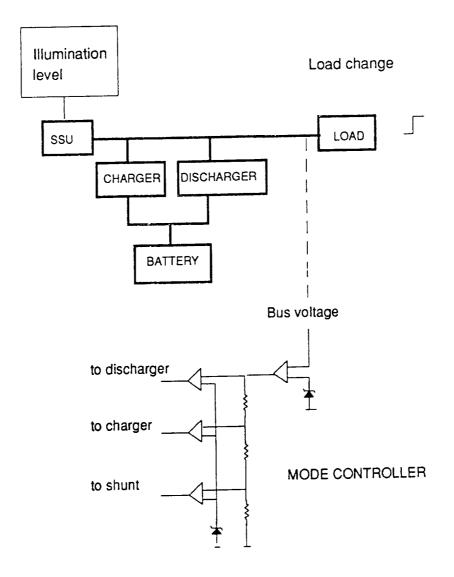

This final report covers work performed under NASA contract NAG 5-1232 from September 1990 to April 1991 on the design, development, and test of a power system suitable for use in the NASA Space Platform. The scope of the work includes the design of a multi-module, multi-phase boost regulator and a voltage-fed, push-pull autotransformer converter for the battery discharger. A buck converter was designed for the charge regulator. Also included is the associated mode control electronics for the charger and discharger, as well as continued development of a comprehensive modelling and simulation tool for the system.

Chapter 2 discusses the design of multi-module boost converter for use as a battery discharger. Chapter 3 discusses an alternative battery discharger design using a voltage-fed, push-pull autotransformer converter and has been submitted by Scott Deuty as his Masters' Thesis. Chapter 4 discusses the design of the charge regulator using a simple buck converter. Chapter 5 discusses the design of the mode controller and effects of locating the bus filter capacitor bank 20 feet away from the power ORU. Chapter 6 includes a brief discussion of some alternative topologies for battery charging and discharging. Chapter 7 describes the power system modelling.

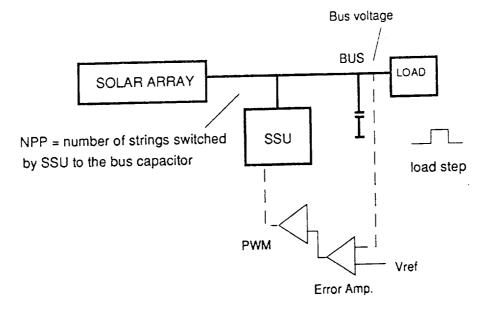

## 2.0 MULTI-MODULE BOOST CONVERTER DESIGN

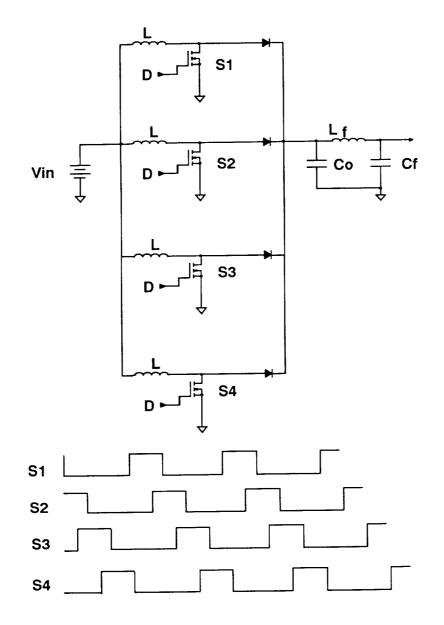

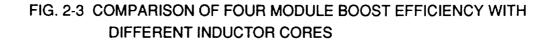

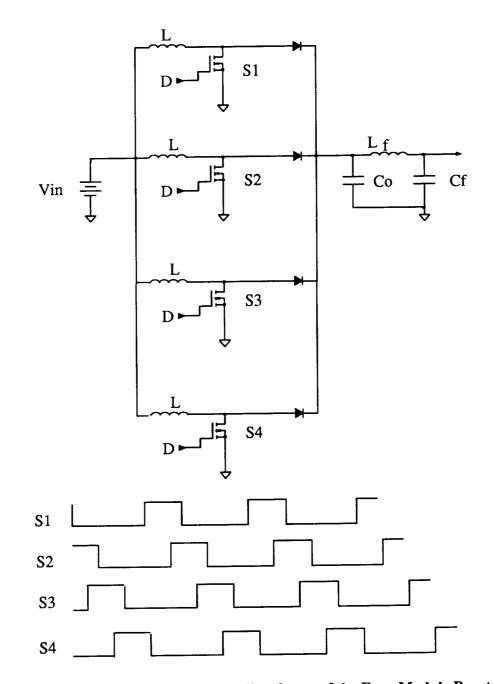

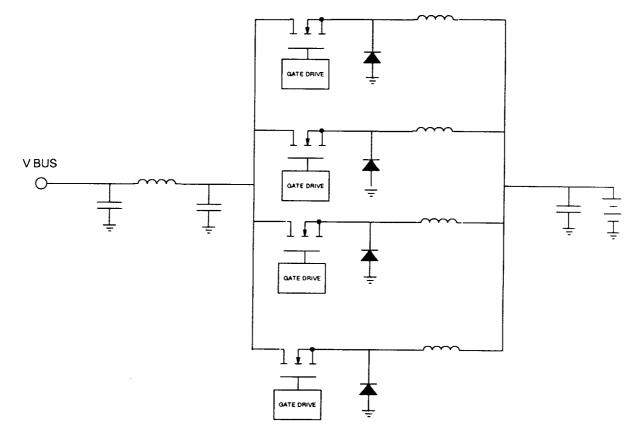

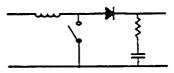

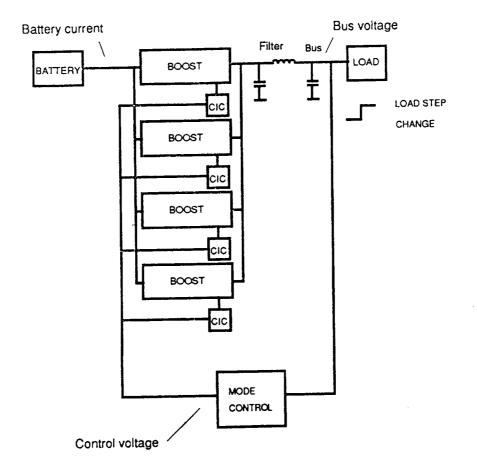

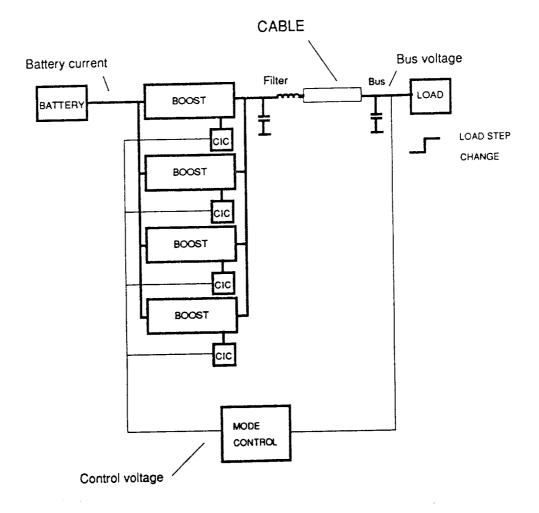

A four module, multi-phase boost converter, shown in Fig. 2-1, was analyzed [1] as a candidate topology for the Space Platform battery discharger. Nonlinear design optimization techniques were employed in order to determine the optimum switching frequency of a 95%, 96%, and 97% efficient design. The results of the analysis indicated that a 97% efficient design operating a 45 kHz was feasible with moderate component sizes. This chapter shall detail the design and test of a four module, multi-phase boost converter for the Space Platform battery discharger. Included is a discussion of the magnetics design, the output filter design, the pulse-width-modulator (PWM) design, the protection circuitry, the control loop, and the theoretical and experimental results.

### 2.1 Magnetics Design

The original analysis called for a METGLAS 2605S-C material gapped cut C-core with foil windings to be employed for the boost inductor. This was selected for its high saturation flux density, low loss, and high window utilization factor. Two cut cores were designed for the application. After experiencing higher than expected losses, two Molypermalloy Powder (MPP) torroid cores were designed and tested. All cores were designed with the aid of a data-base driven electronic spreadsheet. Included is a discussion of the different inductor designs and their test results.

#### 2.1.1 METGLAS Material

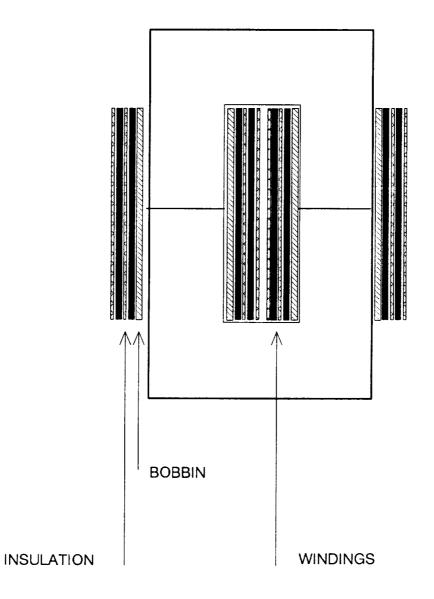

Fig. 2-2 shows a representation of a cut-core design with foil windings. Two foil lengths are insulated with kapton tape and wound around separate bobbins. A short piece of wire is soldered to connect the two foil forms. A fiberglass material is placed into both bobbins to

FIG. 2-1 FOUR MODULE, MULTI-PHASE BOOST CONVERTER

FIG. 2-2 CUT-CORE INDUCTOR WITH FOIL WINDINGS

serve as the air gap. The two halves of the cut-core are placed into the bobbins with the gap sandwiched in between.

One way to for design a cut-core inductor having an inductance, L, a peak current,  $I_{pk}$ , and an RMS current,  $I_{rms}$ , is to calculate the power handling capability as the window area, cross sectional area product given below:

$$W_a A_c = \frac{I_{rms} I_{pk} I_c}{0.75 K_u B_{max} I} \quad (m^4)$$

(2.1)

The window utilization,  $K_{\mu}$ , for a foil-wound cut-core can be very high, sometimes over 45%. The constant 0.75 comes from the stack factor of METGLAS material. The saturation flux density,  $B_{\text{max}}$ , of the METGLAS material is 1.4 Tesla. The current density, J, can vary between  $3 \times 10^6$  to  $3 \times 10^7$  A/m<sup>2</sup> and involves a trade-off between efficiency and weight. Based on the results of the optimization study, a low current density of about  $3 \times 10^6$  A/m<sup>2</sup> is optimum. Once a core is selected having the necessary power handling capability, the number of turns, N, is designed to fill the window area. The air gap length,  $l_g$ , is then designed to yield the proper inductance. This is given by (air gap length in mils):

$$l_g = \frac{0.4\pi N^2 (A_c \times 0.75) \times 0.1}{L \times 2.54}$$

(2.2)

Inductor core loss for METGLAS material is a function of the core volume,  $CV_L$ , the AC flux,  $B_{ac}$ , and the switching frequency,  $F_s$ . It is estimated from the manufacturers data sheets as:

$$P_{fe} = 3.42 \times 10^{-4} C V_L B_{ac} {}^{2.04} F_s {}^{2.23}$$

(2.3)

One further significant loss mechanism is eddy current loss induced in the plane of the laminations by the fringing flux around the air gap. Very little information has been published about gap loss, yet it is a significant component of the inductor loss. Using silicon steel cut cores at 60 Hz and 400 Hz, Lee and Stephens [2] offered the following empirical formula for gap loss:

$$P_{gap} = .039 \times l_g F_s C_{wid} B_{ac}^{-2} \tag{2.4}$$

where  $C_{wid}$  is the width of the core in the plane of the laminations. This formula was found to be highly useful in determining the gap loss of METGLAS cut-cores in the frequency range of 40 kHz to 100 kHz.

The chosen inductance value was the subject of extensive optimization. Power supply designers will often select an inductance that maintains continuous inductor current at the minimum load condition. This avoids large changes in the converter dynamic characteristics when crossing the boundary between continuous and discontinuous modes. This was not a design criteria for the four module boost converter. Since the converter must operate down to no load, even an infinite inductance cannot maintain continuous inductor current. The four module boost inductors were designed to optimize efficiency and weight only.

A smaller inductance will obviously yield a lighter weight inductor. However, the smaller the inductance value, the higher the AC flux in the inductor resulting in higher core loss and gap loss. A inductance value of approximately 270  $\mu$ H was selected as a compromise between size and efficiency. This brings the boost converter into discontinuous inductor current mode at a power level of 300 W, one sixth of the peak power. This is a very close to a conventional design.

Specifications called for a design able to regulate 1800 W down to an input voltage of 53 V. This requires an inductor with a saturating current greater than 12 A. The cut-core design used an MC1490-1b core with 45 turns of 7 mil by 1.1 inch foil. A 20 mil airgap yielded a 250  $\mu$ H inductor saturating a 15  $\Lambda$ . The total weight for the four inductors is 780 grams.

The inductor gap loss led to higher than expected total losses for the cut-core inductors. This prompted the design of an alternative inductor.

#### 2.1.2 MPP Material

Molypermalloy Powder (MPP) cores contain a distributed airgap within a torroid geometry. MPP cores have less than half the saturating flux density of the METGLAS material. Also, the torroidal shape cannot yield as high a window utilization factor. Obtaining the same inductance and saturating current as a METGLAS cut-core will result in an MPP core with larger size and weight. MPP cores, however, have lower core loss and do not have a gap loss. The lower permeability MPP cores have very low losses. Ironically, to obtain lower effective permeability with the cut-cores requires a larger air gap and thus higher losses. Thus a smaller inductance can be used to obtain the same efficiency with an MPP core as with a METGLAS core.

An inductance of 75  $\mu$ H was selected for the MPP core. This brought the converter into discontinuous mode at power levels below 1200 W which is two thirds of the peak power level. This is much higher than a conventional design. Two 75  $\mu$ H, MPP inductors were designed. The first used a 55083, 60  $\mu$ , core with 31 turns of #12 AWG wire. The total weight of the four inductors was 590 grams. The second used a 55550, 26  $\mu$ , core with 52 turns of #16 AWG wire. This has a total weight of 308 grams.

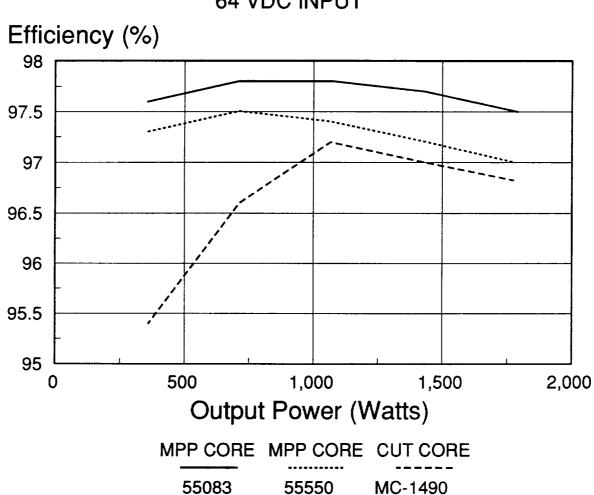

Fig. 2-3 shows a comparison of the four module boost experimental efficiency with the different inductor designs. Both designs with the MPP cores exceed 97% efficiency over the load range from 300 W to 1800 W. The cut-core design drops in efficiency at lighter loads due to the higher eddy current losses. Both MPP core designs have a lighter weight than the cut-core design.

The final design selected was the 55550 core. It was felt that the lighter weight was worth the small drop in efficiency from the 55083 core.

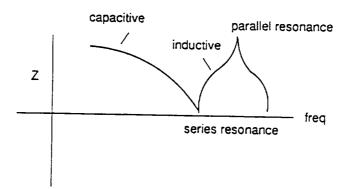

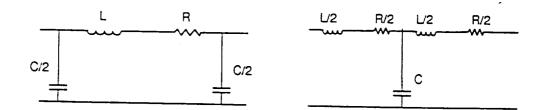

## **2.2 OUTPUT FILTER DESIGN**

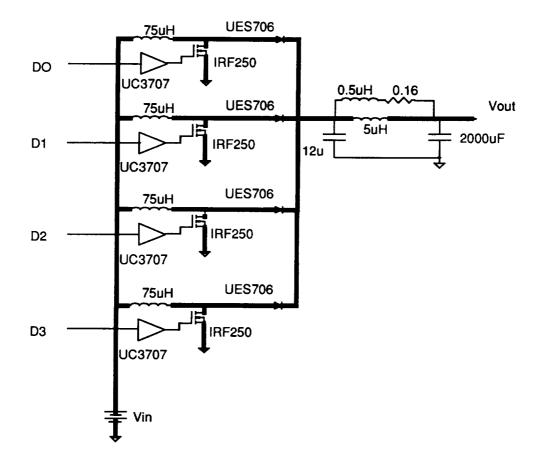

Fig. 2-4 shows the four module boost power stage. The four modules feed into a common first stage capacitor and secondary filter. The bus capacitor serves as the second stage capacitor. If the modules are not multiphased, the RMS current in the first stage capacitor is given by:

$$I_{Corms} = \frac{I_o}{(1-D)} \sqrt{D(1-D)}$$

(2.5)

A substantial reduction in the RMS ripple current in the first stage capacitor is achieved by phasing the modules by 90 degrees. Then the RMS ripple current in the output capacitor is given by:

$$I_{Corms} = \frac{I_o}{(1-D)} \sqrt{D(1/4-D)} \quad 0 \le D \le 0.25$$

(2.6)

$$= \frac{I_o}{(1-D)} \sqrt{-D^2 + 3/4D - 1/8} \quad 0.25 \le D \le 0.5$$

(2.7)

$$=\frac{I_o}{(1-D)}\sqrt{-D^2+5/4D-3/8} \quad 0.5 \le D \le 0.75$$

(2.8)

Fig. 2-5 compares the ripple current in the output capacitor for an 1800 W, 120 V boost converter where the input voltage varies between 60 V and 90 V. With multiphasing, the peak

FIG. 2-4 MULTI-MODULE BOOST POWER STAGE

FIG. 2-5 COMPARISON OF CAPACITOR RIPPLE CURRENT

ripple current occurs at the 60 V input voltage and is 15 A. With multiphasing, the peak ripple current occurs at an input voltage of 72 V and is only 3.8 A. This can significantly reduce the size of the output filter.

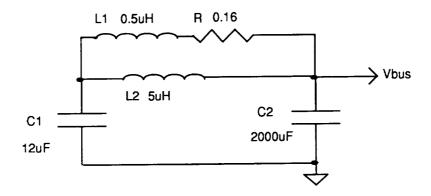

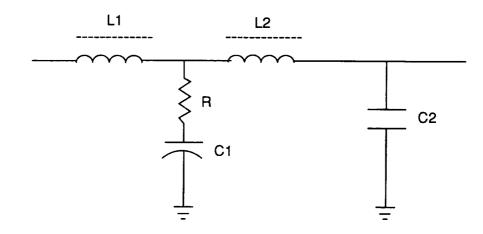

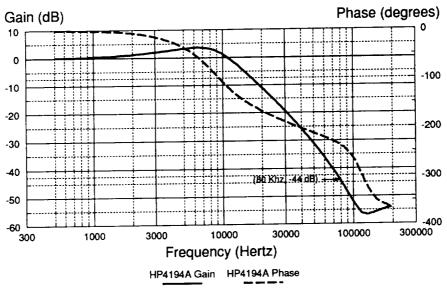

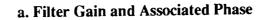

Fig. 2-6 shows a schematic of the damped secondary output filter. Under the following conditions:

1)

$$L_2 >> L_1$$

2)  $\frac{L_1}{R} >> RC_1$

Then the resonant frequency and Q of the filter are given by:

$$\omega_o = \frac{1}{\sqrt{L_1 C_1}} \tag{2.9}$$

$$Q = \frac{1}{\omega_o C_1 R} \tag{2.10}$$

The advantage of this configuration is that the secondary resonance is independent of the bus capacitance and load capacitance. The first stage capacitor bank,  $C_1$ , is comprised of 12  $\mu$ F of polypropylene capacitors sized to handle the RMS ripple current.  $L_1$  is selected as 0.5  $\mu$ H to place the resonance at about 60 kHz, a third of the 180 kHz ripple frequency.  $L_2$  is selected as 5.0  $\mu$ H to be 10 times larger than  $L_1$ . The resistor, R, is design to be 0.15  $\Omega$  in order to make the Q slightly greater than 1 to avoid peaking in the loop gain. The bus capacitor is approximately 2000  $\mu$ F of aluminum capacitors. Although aluminum capacitors are not approved for flight use, they are electrically similar to the wet slug (CLR35) type capacitors which are flight approved. Upon advice from NASA, VPEC constructed the bus filter from aluminum capacitors to minimize costs.

## FIG. 2-6 DAMPED SECONDARY OUTPUT FILTER

## **2.3 DISCRETE PWM DESIGN**

Several PWM integrated circuits are available for use in spacecraft applications, including some that support current-mode control. However, there are several problems with using a PWM integrated circuit in this application. With four modules operating out of phase an external oscillator will be needed to synchronize the PWM's. Hence the internal oscillator will be unused. Also, the comparator input of all PWM integrated circuits has only a small linear range, usually only about 2 V. When using current-injection-control over a wide load range, severe limitations are placed on the current sense gain just to ensure that the signal will be within the linear range of the comparator. This necessitates a small current sense gain making the PWM sensitive to noise. A large offset variation in the ramp bias voltage exists between different IC's. It is desirable that the PWM ramp bias voltage of the four modules be a common voltage. This helps reduce the error in current-sharing between modules. In order to maximize the small-signal benefit of current-injection-control, one needs precise control over the slope of the external ramp. The ramp slope of all PWM integrated circuits cannot be controlled without also changing the switching frequency. Finally, a maximum duty cycle limit of 75% is desirable for each module. PWM integrated circuits are not easily programmed with such a low duty cycle limit.

A discrete four phase pulse-width-modulator circuit is designed with the following features:

- 1) 10 V linear range on the PWM comparator,

- 2) easy interface to a CIC signal,

- 3) common bias voltage to reduce variations in the duty cycle,

- 4) precise 75% maximum duty cycle limit,

- 5) easy control of the external ramp slope without affecting the operating frequency, and

- 6) latching mechanism to eliminate chattering.

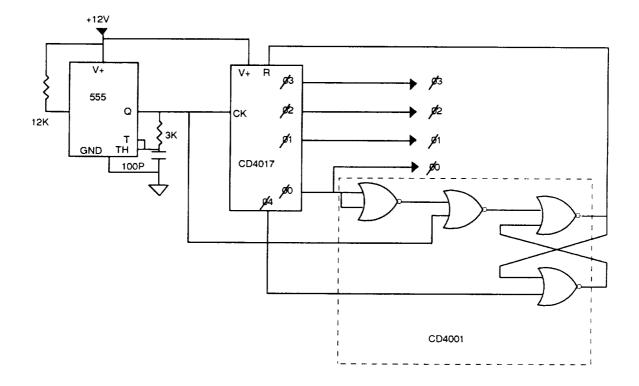

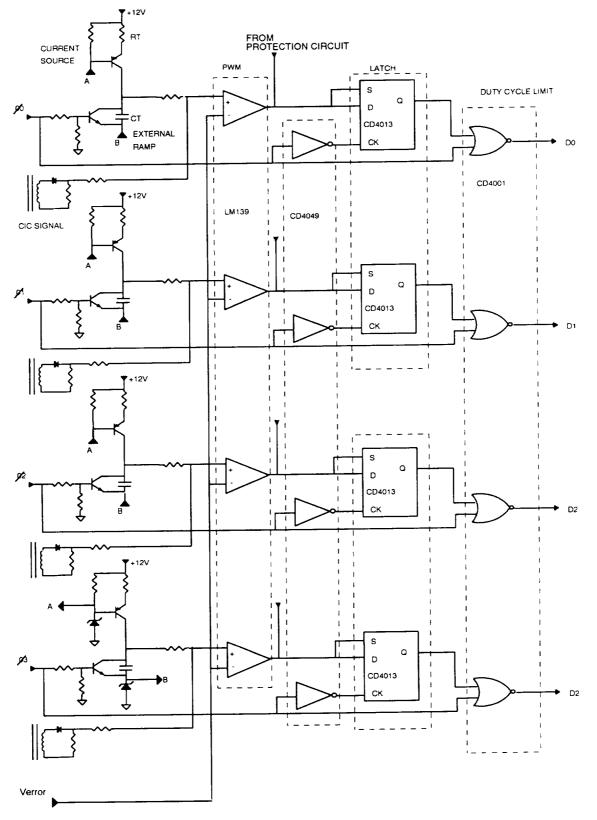

Fig. 2-7 shows a schematic of the four phase clock generator. A CMOS 555 timer outputs a 180 kHz square wave to a CD4017 Johnson counter. A set/reset latch divides the 180 kHz into four phases of 45 kHz, each having a 25% duty cycle. Fig. 2-8 shows the discrete four phase pulse-width-modulator. A high signal on the phase signal shorts the ramp capacitor and turns off the duty cycle output. When the phase signal goes high, the ramp capacitor is charged with a constant current source determined by the common zener voltage Va and resistor Rt. The D flip-flop is also clocked into the active low state, turning on the duty cycle output. When the summed ramp signal and CIC signal reaches the error signal, the comparator output goes high, seting the D flip-flop. Repetitive switching of the comparator will not effect the flip flop state until the next cycle.

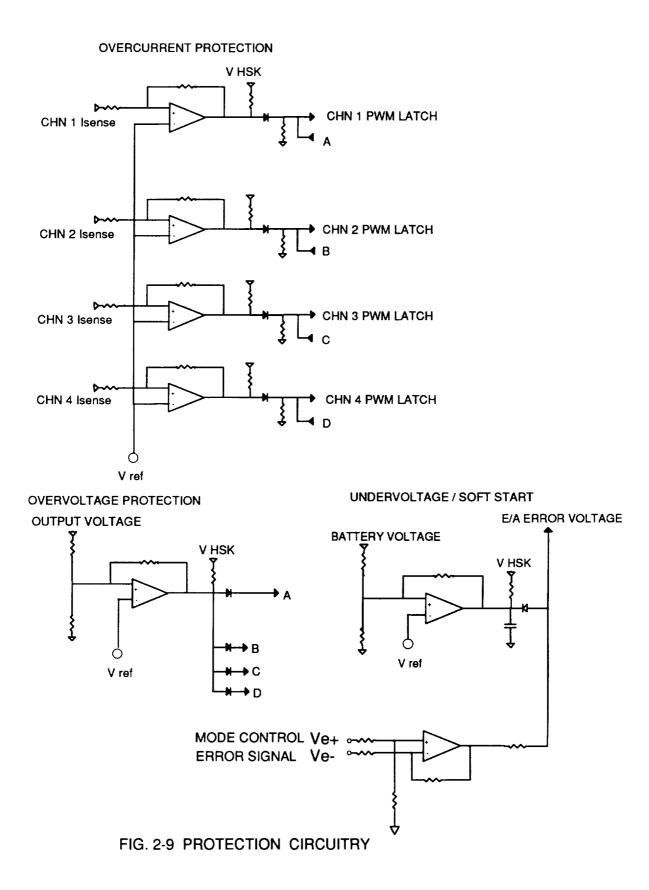

## 2.4 PROTECTION CIRCUIT DESIGN

The four module boost converter contains undervoltage, overvoltage, overcurrent and soft-start protection circuitry. A schematic is shown in Fig. 2-9. The switch current in each channel is sensed and compared with a reference. The output of the comparator is logically ored with the PWM comparator output for each of the four channels.

To protect against an open mode control signal, the four module boost converter also has overvoltage protection. Output voltage is sensed at the output of the ORU and is compared with the reference. If the output voltage exceeds 130 V, the comparator output goes high forcing each of the PWM outputs low. There is a two volt hysteresis.

For smooth starting, battery voltage is sensed and compared with the reference. At battery voltages below 50 V, the comparator output is low, which holds down the error signal, keeping all channels off. When the battery voltage exceeds 50 V, the error signal is slowly increased through the soft start capacitor until it is back-biased.

FIG. 2-7 FOUR PHASE CLOCK GENERATOR

FIG. 2-8 DISCRETE FOUR PHASE PWM

## **2.5 CONTROL LOOP DESIGN**

The four module boost battery discharger employs current-mode control in order to ensure current sharing between modules, to improve the dynamic characteristics, and to provide a means for overcurrent protection. Recent analysis of current-mode control [3] has shown that the relative slopes of the current sense waveform and the external ramp waveform have a powerful impact on the control-to-output small-signal characteristics of a power converter. Current-mode control introduces a double pole at one-half of the switching frequency. The Q of this double pole is determined by the external ramp slope. With no external ramp and operation above 50% duty cycle, the Q becomes negative, causing the system to experience a subharmonic oscillation. The discrete PWM of the four module boost converter is specifically designed in order to allow high flexibility in selecting the external ramp slope and the current sense gain.

The four module boost converter operates in the discontinuous inductor current mode at power levels below 1200 W. This is unusually high for an 1800 W power converter, but was selected to keep the inductor weight to a minimum. Recent analysis of current-mode control in the discontinuous mode [4,5] has shown that the dynamic performance of converters which operate in continuous and discontinuous modes of operation can be greatly enhanced with currentmode control.

Included is a discussion of the small-signal characteristics of the four module boost converter in both the continuous and the discontinuous modes of operation. A simple PSPICE model is presented incorporating the current-controlled model of the PWM switch [6].

## 2.5.1 Small Signal Characteristics

There are two primary considerations in the small signal characteristics of the four module boost converter. The system should be stable over all line and load conditions, and the system should meet output impedance specifications over all line and load conditions. Audio susceptibility is not a prime consideration since the input voltage is a battery and is not subject to AC perturbations. Output impedance is important for several reasons. A low output impedance will better reject load-induced voltage ripple from the bus. Also, transient response peaking is minimized by minimizing the output impedance over a broad range of frequencies. Finally, a low output impedance will allow the converter to handle a wider variety of complex loads without stability problems.

Included is a discussion of the loop gain stability analysis and output impedance analysis for the continuous and discontinuous mode four module boost converter.

#### 2.5.1.1 Continuous Mode of Operation

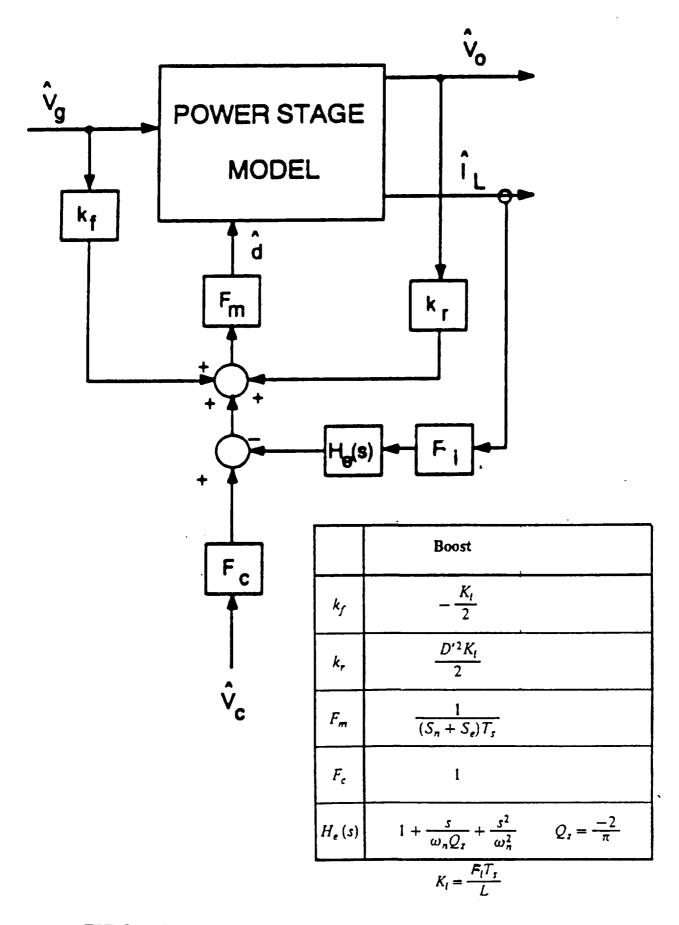

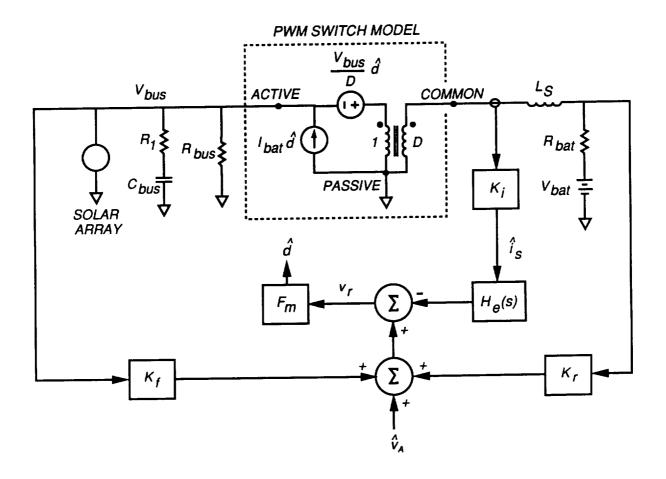

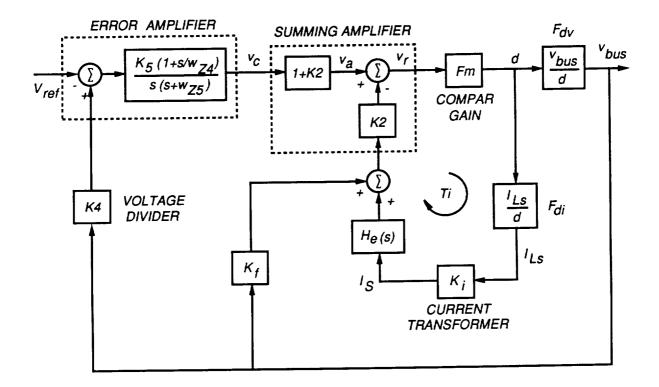

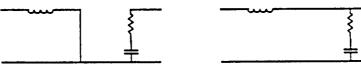

Fig. 2-10 shows a block diagram of a single module, continuous mode, current-injection controlled power converter. The power stage model comes from the well-known state-space averaged model [7]. The block Kf accounts for the feedforward effect of the input voltage on the slope of the current sense waveform. The block Kr accounts for the feedback effect of the output voltage of the slope of the current sense waveform. The block He(s) forms a pair of complex right half plane zeroes at one-half the switching frequency to account for the sampling nature of the system. This new model predicts the second order effects of current-mode control, including the subharmonic oscillation at duty cycles above 50%.

The four module boost regulator can be analyzed as an effective single module system using an effective power stage inductance of one-fourth the inductance in each module [8]. This greatly simplifies the design of feedback controller.

#### 2.5.1.1.1 PSPICE Modelling

FIG. 2-10 Block Diagram Of CIC Converter

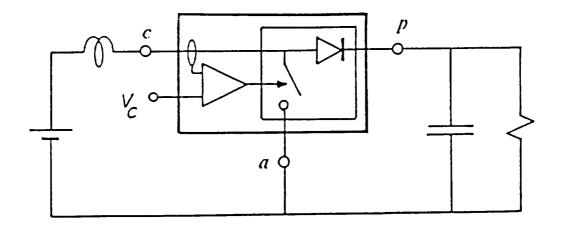

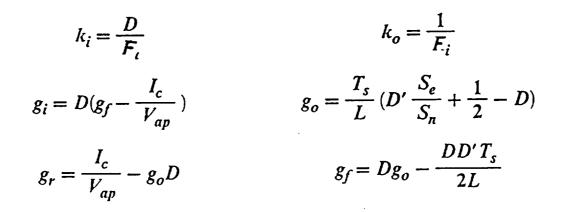

While the new model of current-mode control is effective for design and analysis, it is cumbersome to use in a circuit analysis program such as PSPICE. The current-controlled model of the PWM switch [6] is a simple means of implementing the new current-mode model in PSPICE. Fig. 2-11 shows how the switch, diode, current sense network, and external ramp can be effectively replaced with a linear network for easy modelling.

#### 2.5.1.1.2 Control-to-Output Transfer Function Analysis

The control-to-output transfer function of the four module boost regulator with each of the current loops closed can be approximated as the product of three transfer functions:

$$\frac{\hat{v}_o}{\hat{d}} \cong F_p(s)F_h(s)F_o(s) \tag{2.11}$$

$F_p(s)$  is the power stage transfer function and is given by:

$$F_p(s) = \frac{R_L/2}{F_i/4} \quad \frac{(1 - s/\omega_a)(1 + sC_{bus}R_c)}{(1 + 2sC_{bus}R_L)} \tag{2.12}$$

where  $\omega_a$  is a right-half-plane zero and is given by:

$$\omega_a = \frac{D'^2 R_L}{L/4} \tag{2.13}$$

$F_h(s)$  is the double pole introduced by the current loop and is approximated as:

# FIG. 2-11 Current-Controlled Model of The PWM Switch

$$F_h(s) \cong \frac{1}{1 + \frac{s}{\omega_n Q_i} + \frac{s^2}{\omega_n^2}}$$

(2.14)

where

$$Q_i = \frac{1}{\pi (m_c D' - 0.5)} \tag{2.15}$$

and

$$m_c = 1 + \frac{S_e}{S_n} \tag{2.16}$$

$F_o(s)$  is the double pole of the secondary output filter defined previously.

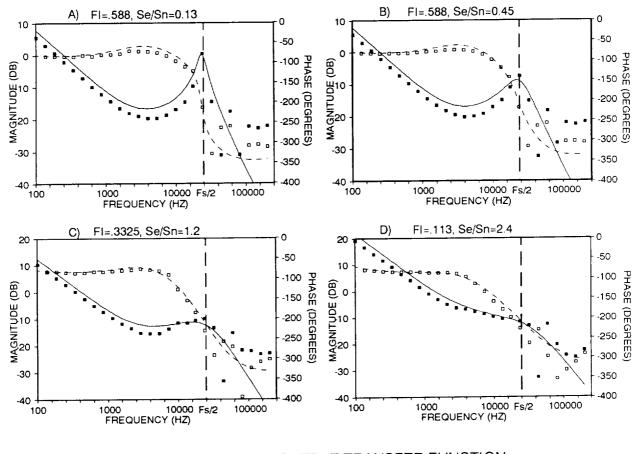

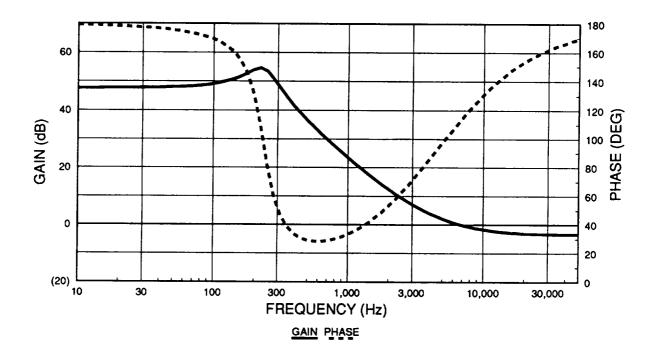

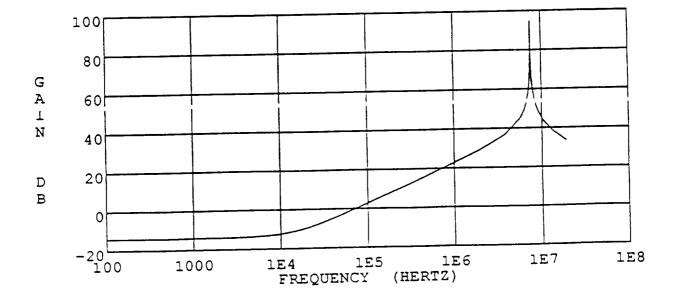

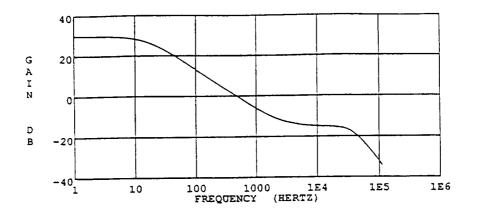

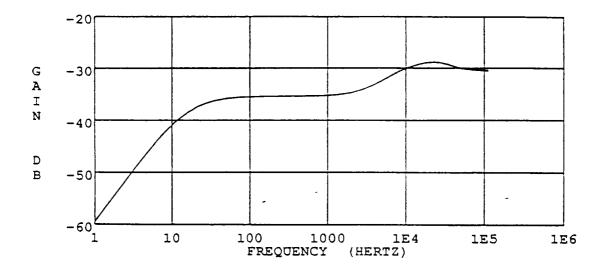

Fig. 2-12 shows the theoretical and experimental control-to-output transfer of the four module boost converter for increasing values of the external ramp slope. It is seen how the Q of the double pole at one-half of switching frequency is effectively damped for increasing external ramp slope.

#### 2.5.1.1.3 Output Impedance Analysis

The output impedance of the four module boost regulator with each of the current loops closed can be approximated as:

FIG. 2-12 CONTROL-TO-OUTPUT TRANSFER FUNCTION CURRENT LOOP CLOSED

$$\frac{\hat{v}_o}{\hat{i}_o} = \frac{R_L}{2} \frac{(1 + sC_{bus}R_c)}{(1 + 2s/R_L)}$$

(2.17)

Current-mode control raises the low frequency output impedance of the converter, causing the converter to behave as a current source. However, the resonant peaking in the output impedance, which is characteristic of single-loop control, is no longer apparent.

#### 2.5.1.2 Discontinuous Mode of Operation

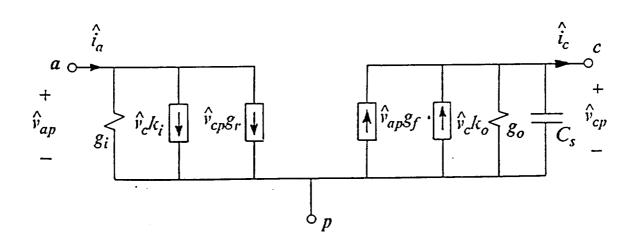

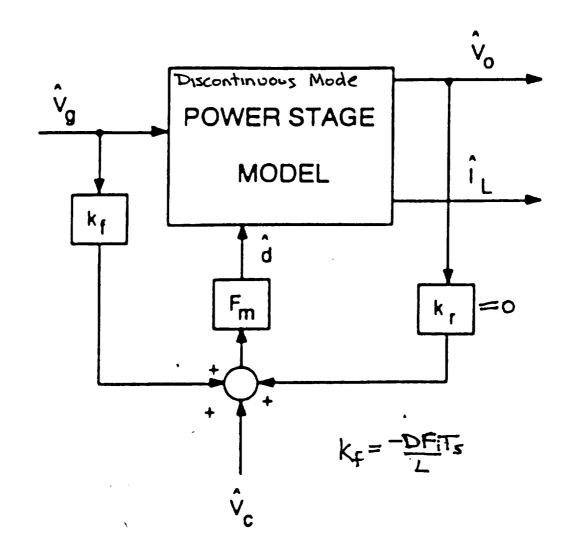

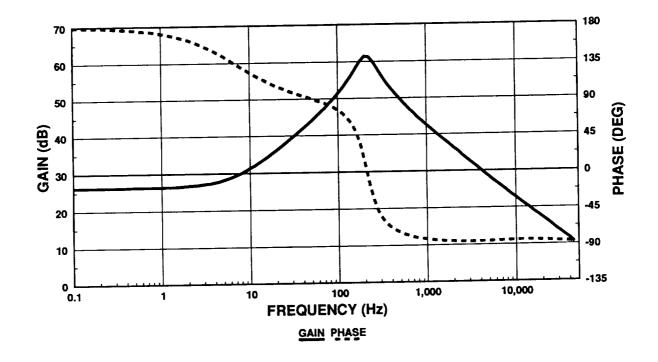

A new model of current-mode control has also been formulated for the discontinuous mode of operation [4]. There the inductor current ceases to be a state with memory from cycle to cycle. At the start of each switching cycle, the inductor current always starts from zero. The state of the inductor current can be inferred by knowledge of the input voltage and inductance only. Hence the model of current-mode control in the discontinuous mode of operation does not contain a current loop. It only contains a feedforward gain input voltage. Fig. 2-13 shows the model of current mode control for discontinuous mode of operation. Since there is no input filter, and audio susceptibility is not a concern, the feedforward term can be ignored. Hence the discontinuous mode model for current-mode control is almost identical to the discontinuous mode model for single-loop control. The only difference is in the modulator gain, which is a function of the current sense slope.

#### 2.5.1.2.1 PSPICE Modelling

The discontinuous mode model of the PWM switch [9] is employed to form the PSPICE model of the four module boost converter.

#### 2.5.1.2.2 Loop Gain Stability Analysis

# FIG. 2-13 Discontinuous Mode CIC Model

When using single-loop control, the control-to-output transfer function of a boost regulator in the continuous mode of operation contains a double pole at the resonant frequency, a righthalf-plane zero, and an ESR zero. In the discontinuous mode, the double pole splits into a low frequency pole and a very high frequency pole, the right-half-plane zero moves to a high frequency, and the ESR zero remains the same.

Unlike current-mode control in the continuous mode of operation, the control-to-output transfer function in the discontinuous mode is dependent on the modulator gain,  $F_m$ . The control-to-output transfer function of the four module boost regulator with each of the current loops closed in the discontinuous mode can be approximated as:

$$\frac{\hat{v}_o}{\hat{v}_c} = \frac{H_d F_m (1 + s/\omega_{zc})(1 - s/\omega_{a1})}{\Delta_1}$$

(2.18)

where:

$$H_d = \frac{2V_o(M-1)}{D(2M-1)}$$

(2.19)

M is the voltage conversion ratio,  $V_o/V_i$ , of the four module boost converter in the discontinuous mode of operation and is given by:

$$M = \frac{1 + \sqrt{1 + \frac{2D^2}{\tau_L}}}{(2.20)}$$

where  $\tau_L$  is the effective inductor time constant and is given by:

$$\tau_L = \frac{L/4F_s}{R_L} \tag{2.21}$$

$\omega_{a1}$  is the right-half-plane zero and is given by:

$$\omega_{a1} = \frac{R_L}{M^2 L/4} \tag{2.22}$$

$\Delta_1$  represents the double complex pole denominator that splits into two real poles, one at a low frequency and one at a high frequency.

$$\Delta_1 = (1 + s/\omega_{p1})(1 + s/\omega_{p2}) \tag{2.23}$$

where  $\omega_{p1}$  is the low frequency pole and is given by:

$$\omega_{p1} = \frac{1}{R_L C} \frac{2M - 1}{M - 1}$$

(2.24)

$\omega_{p2}$  is the high frequency pole and is given by:

$$\omega_{p2} = 2F_s \left(\frac{1 - 1/M}{D}\right)^2 \tag{2.25}$$

The right-half-plane zero,  $\omega_{a1}$ , and the high frequency pole,  $\omega_{p2}$ , are beyond twice the switching frequency. However, since they both result in additional phase lag, their effect can be seen in the loop gain at one-fifth of the switching frequency.

#### 2.5.1.2.3 Output Impedance Analysis

The open loop output impedance in the discontinuous mode of operation is given by:

$$\frac{\hat{v}_o}{\hat{i}_o} = \frac{R_L(M-1)}{(2M-1)} \frac{(1+s/\omega_{zc})}{(1+\omega_{p1})}$$

Unlike single-loop control, the output impedance in the discontinuous mode of operation is very similar to the output impedance in the continuous mode of operation. This provides a smooth transition in the dynamic characteristics when crossing that boundary. It also greatly improves the no-load to full-load transient response.

#### 2.5.2 Current Sense Design

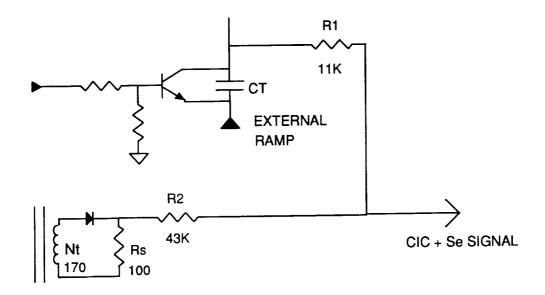

Switch current is sensed in each module with a current transformer and half-wave rectifier and load resistor as shown in Fig. 2-14. The transformer contains 170 turns of #28 AWG wire around a 58076-1 supermalloy tape wound core. This is chosen for its low magnetizing current. A sense resistor of  $100\Omega$  is selected, The gain of the current sense,  $F_i$ , is given by:

$$F_i = \frac{R_s}{N_i} \times \frac{R_1}{R_1 + R_2} = 0.12$$

(2.26)

The slope of the sensed switch current,  $S_n$ , is given by:

SWITCH CURRENT SENSE

FIG. 2-14 CURRENT SENSE CIRCUIT

$$S_n = \frac{V_i F_i}{L} \tag{2.27}$$

The minimum slope to the current sense signal occurs at the minimum line voltage where the slope is approximately  $8.6 \times 10^4$  V/s.

#### 2.5.3 External Ramp Design

As previously described, the external ramp slope has a powerful impact on the peaking of the double pole at one-half of the switching frequency when operating in the continuous mode of operation. As shown in Fig. 2-12d, a large external ramp can cause the double pole to split into two real poles where one goes towards the origin and the other goes towards infinity. If selected properly, the lower frequency pole can cancel the power stage ESR zero, thus minimizing the phase lag in the control-to-output transfer function. This can be useful in optimizing the converter in the continuous mode of operation.

However, the external ramp slope also plays a significant but somewhat different role in the discontinuous mode of operation. There is no double pole at one-half of the switching frequency in the discontinuous mode. However, unlike the continuous mode, the control-to-output transfer function in the discontinuous mode of operation is a function of the modulator gain,  $F_m$ . The modulator gain is given by:

$$F_m = \frac{1}{(S_e + S_n)T_s}$$

(2.28)

A larger external ramp slope,  $S_e$ , relative to the sensed inductor slope,  $S_n$ , causes a reduction in the modulator gain. This will reduce the control-to-output transfer function gain in the discontinuous mode only, with a corresponding reduction in the loop gain. This can greatly increase the discontinuous mode output impedance. To optimize the external ramp slope for both the continuous and discontinuous modes requires as little slope as possible to avoid peaking in the loop gain in the continuous mode. This will result in the smallest loop gain reduction in the discontinuous mode. From Eq. (2.15), the maximum Q of the double pole at half the switching frequency in the continuous mode occurs at the minimum line voltage and is given by:

$$Q_{imax} = \frac{1}{\pi (D'_{\min}(1 + S_e/S_{nmin}) - 0.5)}$$

(2.29)

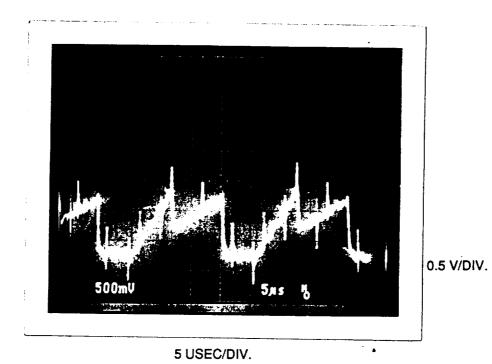

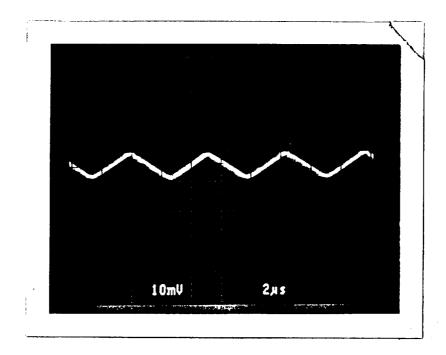

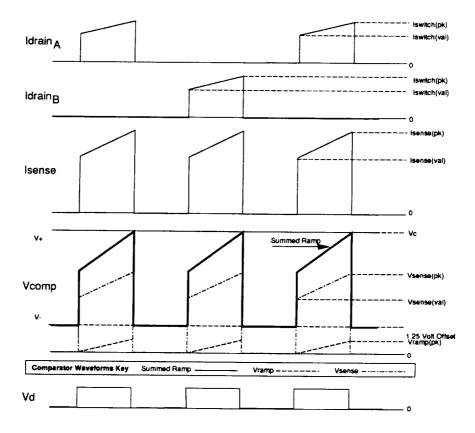

The system is designed so that the maximum Q = 1.2 at an input voltage of 53 V. This yields an external ramp slope of  $6.25 \times 10^4$  Fig. 2-15 shows a photograph of the summed external ramp signal with the current sense signal.

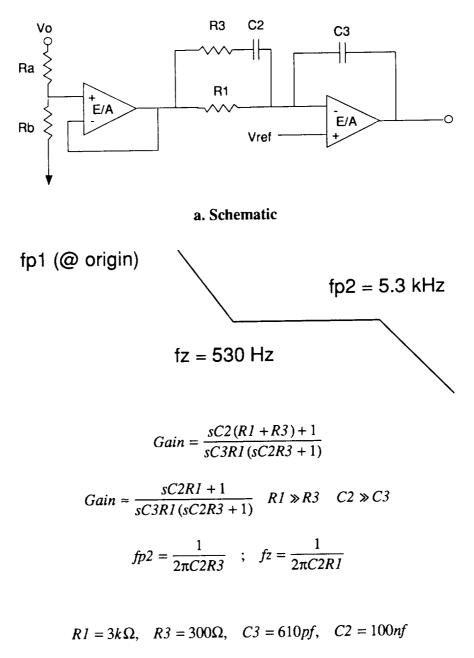

#### 2.5.4 Voltage Loop Design

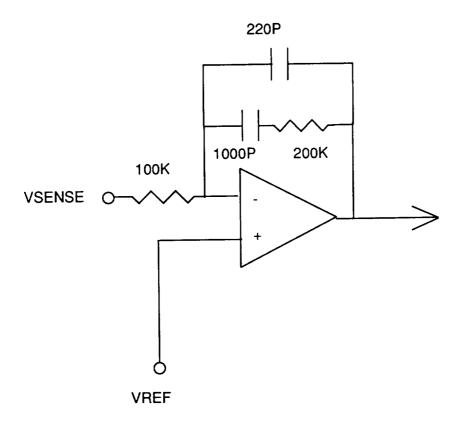

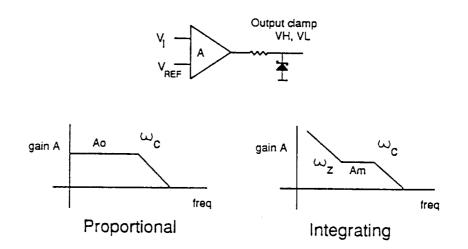

The voltage loop feedback compensation network is shown in Fig. 2-16. This operation amplifier connection contains two poles and one zero. The first pole is placed at the origin in order to obtain tight DC regulation. The second pole is placed to cancel the ESR zero. The zero is placed in order to obtain the necessary phase boost in the loop gain. Finally, the integrator gain is selected in order to cross-over 0 db in the loop gain with acceptable phase margin.

### 2.6 THEORETICAL AND EXPERIMENTAL RESULTS

FIG. 2-15 PHOTOGRAPH OF SUMMED EXTERNAL RAMP WITH CURRENT

SENSE SIGNAL

١

FIG. 2-16 VOLTAGE LOOP COMPENSATION

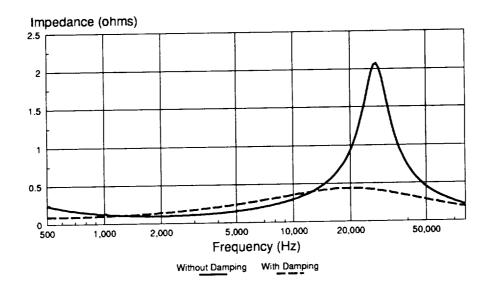

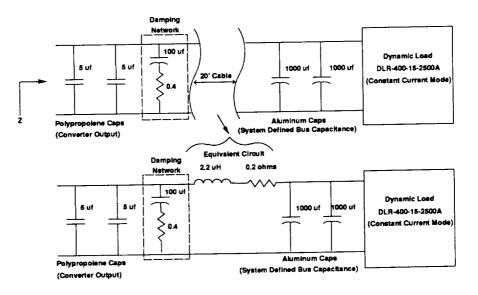

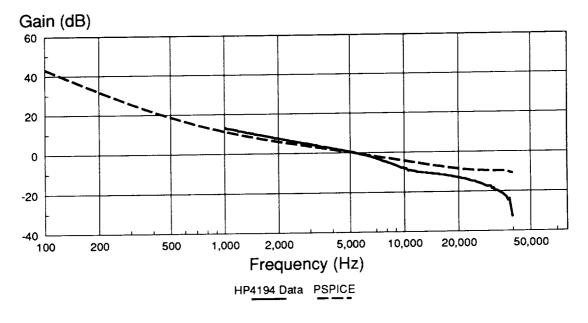

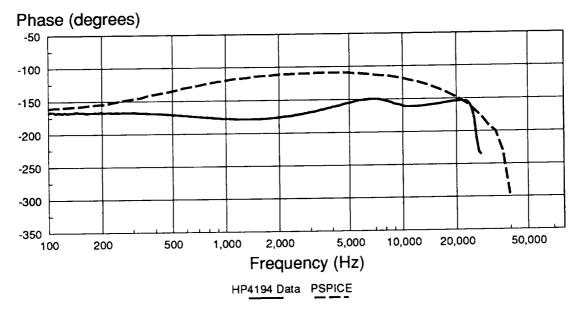

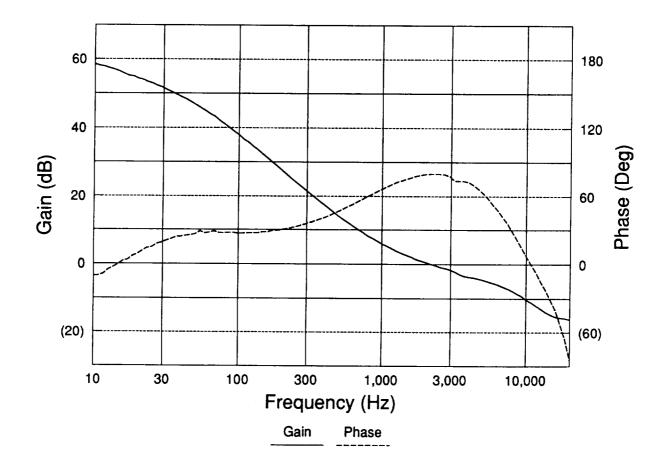

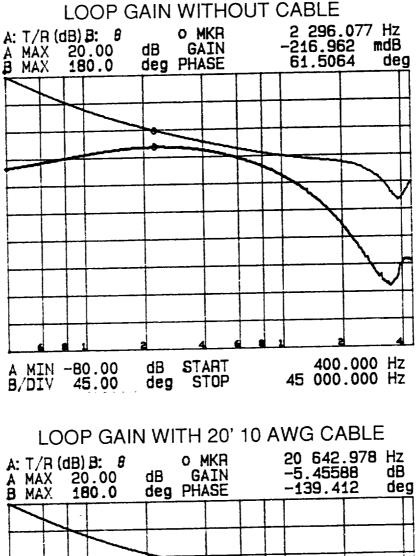

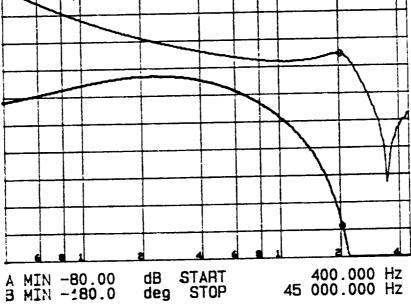

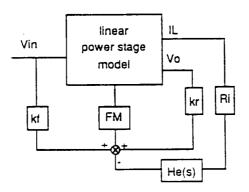

The small-signal and large-signal characteristics of the four module boost regulator were evaluated both theoretically and experimentally. Small-signal measurements include loop gain stability and output impedance over a wide range of load conditions. These measurements were performed prior to and after placement of a 20 foot cable from the discharger output to the bus capacitor. Large-signal measurements include the load transient response going from no load to max load and max load to no load, as well as the EMI characteristics.

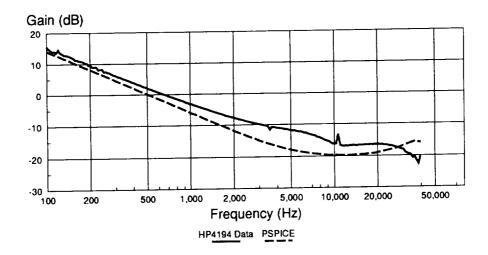

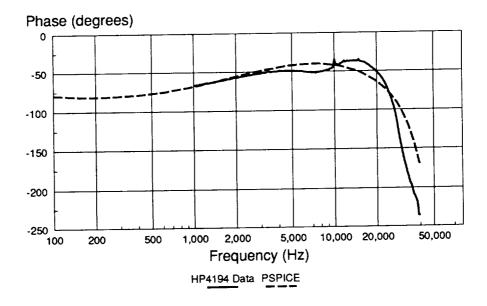

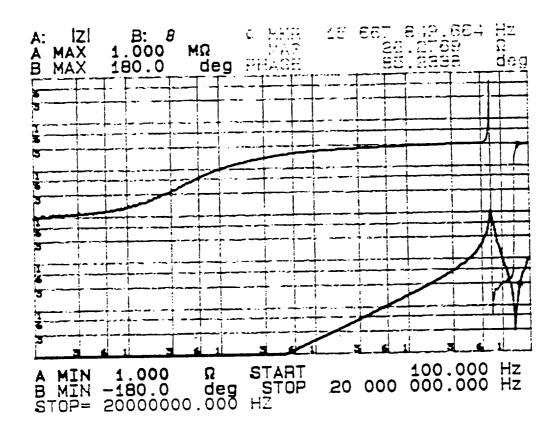

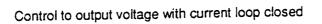

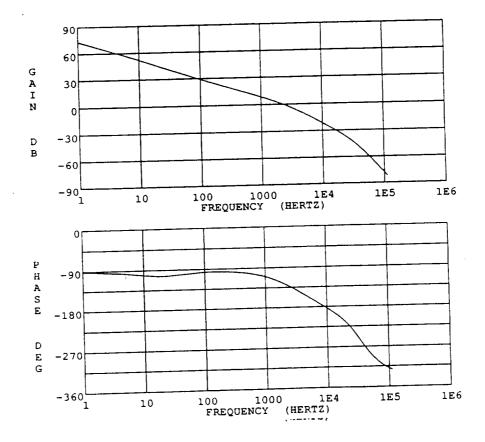

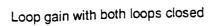

#### 2.6.1 Small-Signal Loop Gain and Output Impedance

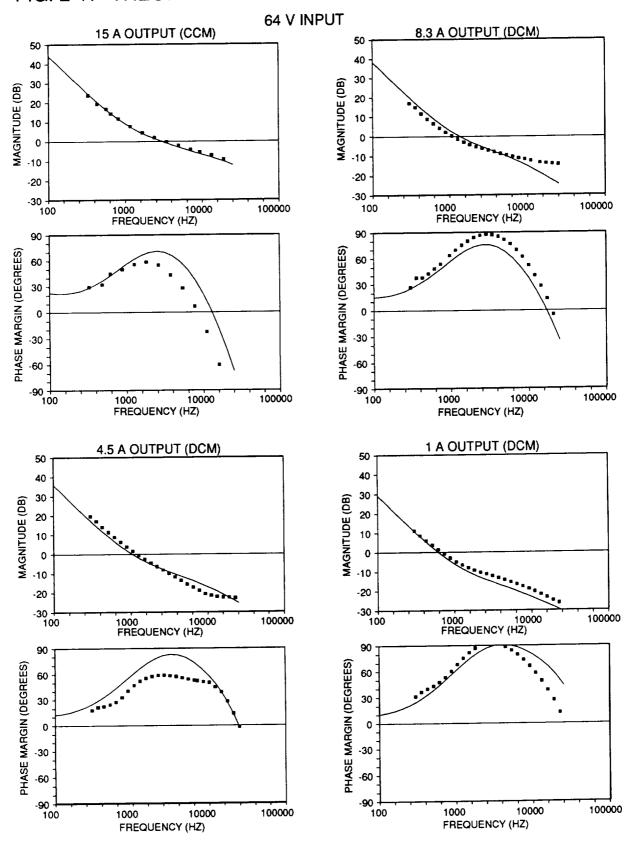

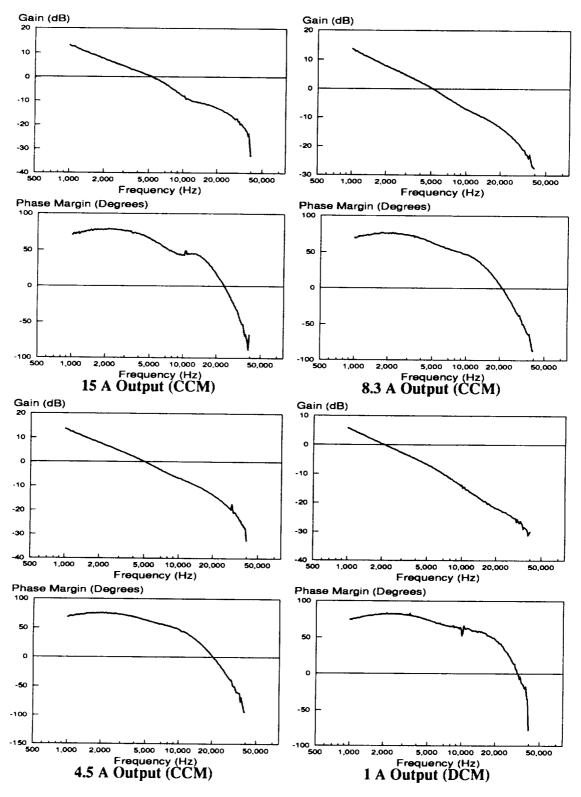

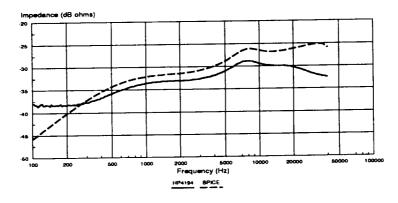

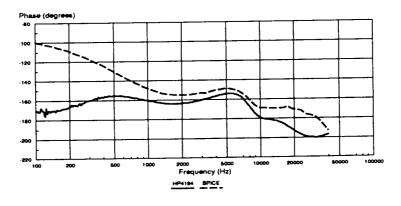

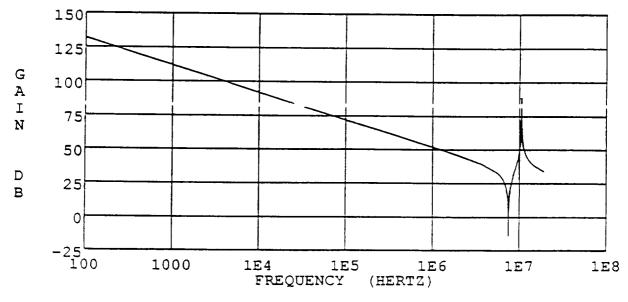

Loop gain stability was measured by injecting a transformer-coupled AC signal into the loop. Fig. 2-17 shows the four module boost converter theoretical and experimental loop gain bode plot at four different load conditions: 15 A, 8.3 A, 4.5 A, and 1 A. The input voltage is 64 V. The solid line is the theoretical prediction, and the dots are the experimental measurement. There is excellent agreement between the prediction and measurement. The converter is in the discontinuous mode of operation for all the measurements except the 15 A load condition. The 0 db cross-over frequency ranges from about 4 kHz at the 15 A load condition to 800 Hz at the 1 A load condition. The worst case phase margin occurs at the 1 A load condition and is 45 degrees. T<sup>i</sup> worst case gain margin occurs at the 15 A load condition and is about 10 db.

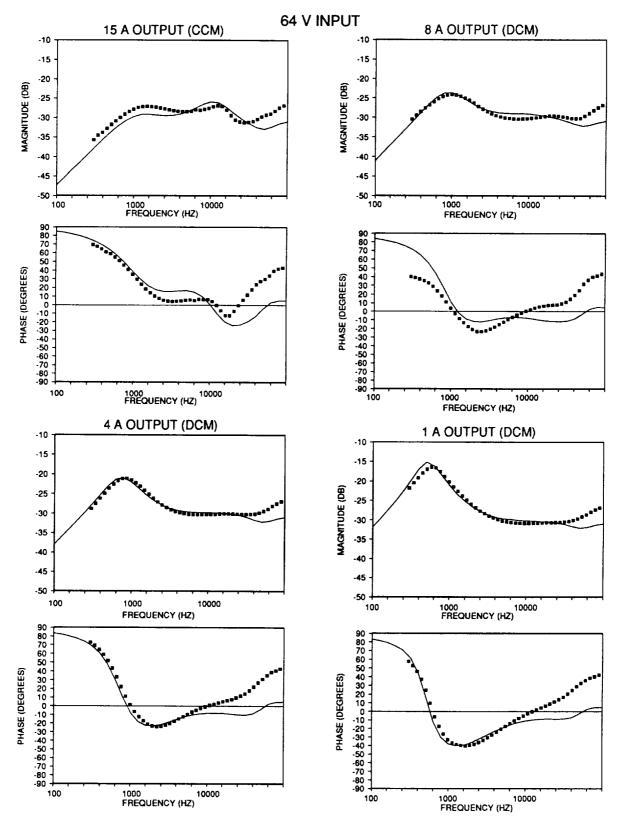

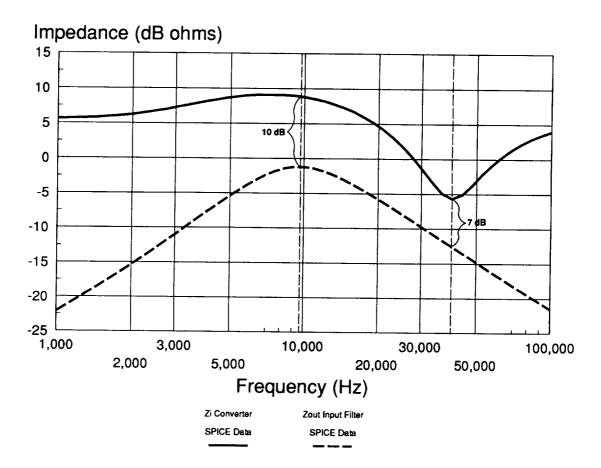

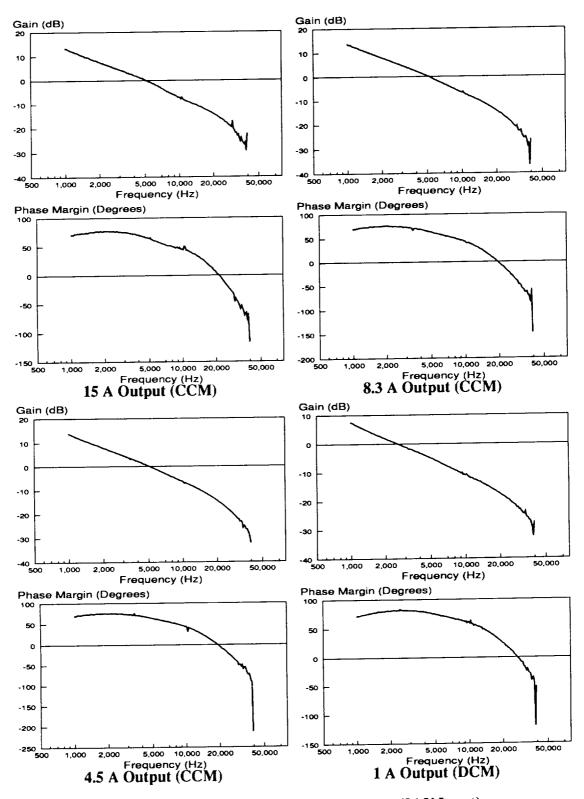

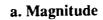

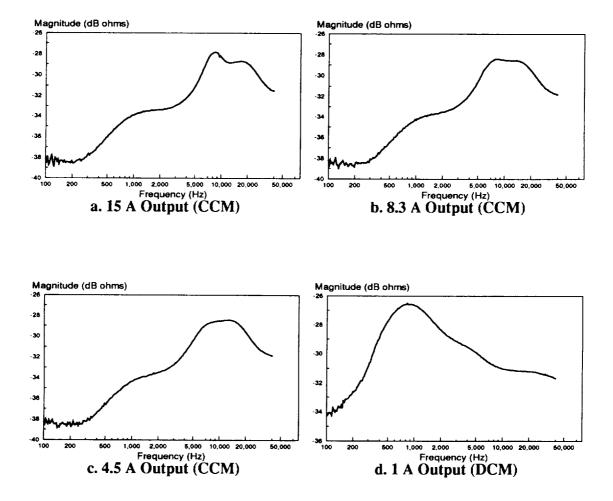

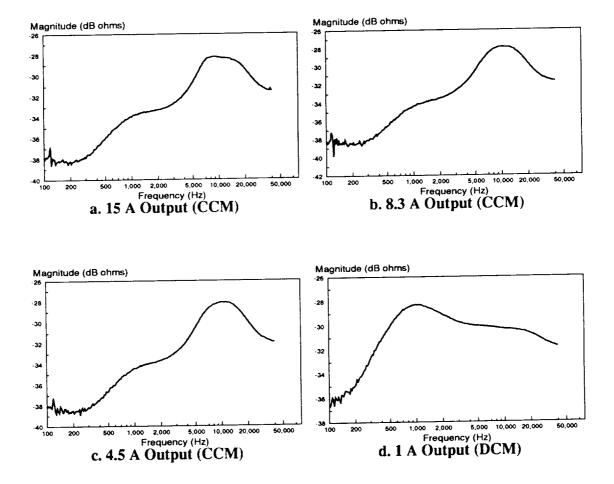

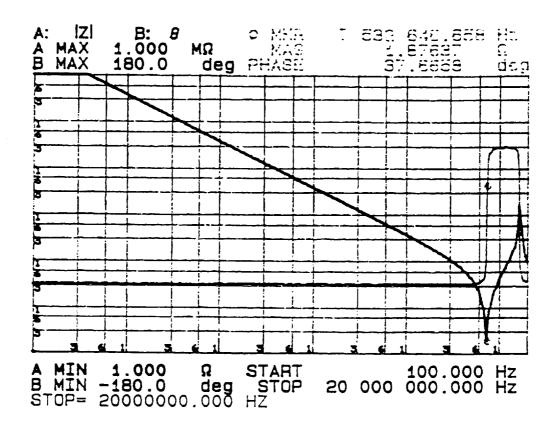

Output impedance was measured by injecting a sinusoidal current load disturbance on the four module boost converter output. Fig. 2-18 shows the theoretical and experimental output impedance under the same conditions. The output impedance is plotted on a log scale referenced to db ohms (0 db = 1  $\Omega$ , -20 db = 0.1  $\Omega$ ). The phase of the output impedance is also presented because of its importance in evaluating the system stability when the converter is powering the complex loads of the spacecraft. There is excellent agreement between the theory and prediction. The peak output impedance at the 15 A load condition is about -26 db = 50  $m\Omega$ . At a 1A load, the output impedance peaks at about -15 db = 178  $m\Omega$ .

FIG. 2-17 THEORETETICAL AND EXPERIMENTAL LOOP GAIN

FIG. 2-18 THEORETICAL AND EXPERIMENTAL OUTPUT IMPEDANCE

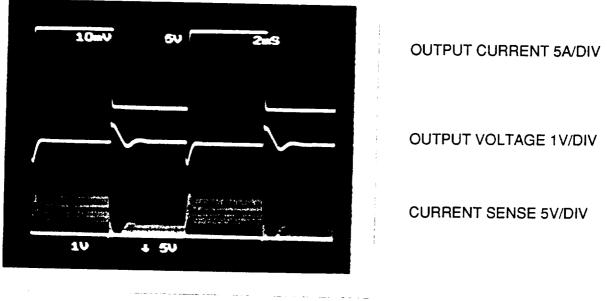

### 2.6.2 Large-Signal Step Load Response

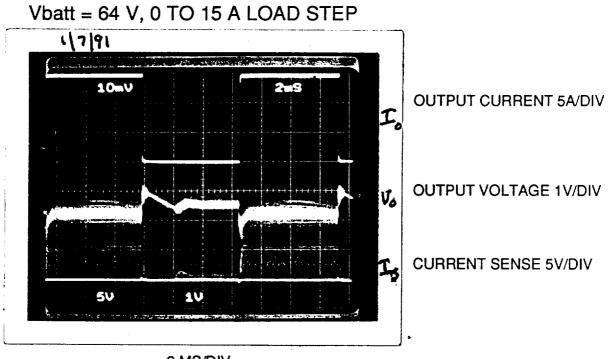

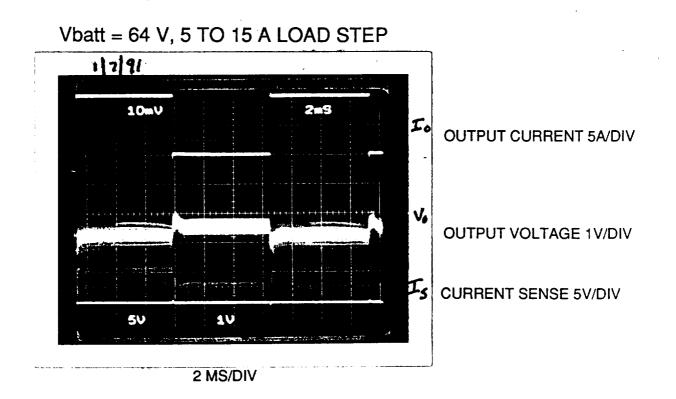

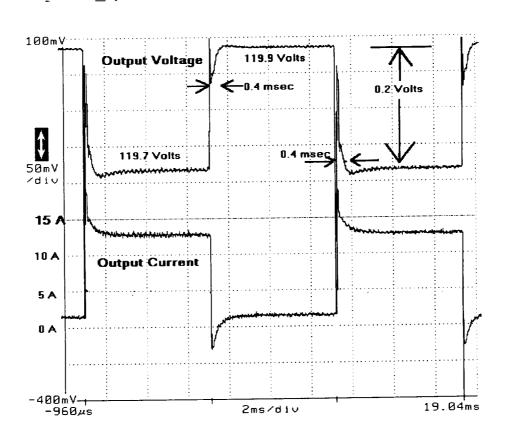

The four module boost converter was excited with a no-load to full load instantaneous step. This is much worst than the worst case transient that appears on the spacecraft bus. Fig. 2-19 shows two photographs of a large transient load. The top photograph shows a load step going from 15 A to 1.2 A back to 15 A. The top trace shows the current step at 5 A/Div. The second trace shows the output voltage at 1 V/Div., AC coupled. The third trace shows the switch current sense waveform of one of the four modules at 5 V/Div. When going from 15 A to 1.2 A, the output voltage experiences a positive peaking of about 1 V. At that point, the current sense waveform goes to zero, indicating that there is no switching being performed. The output voltage droops to the regulation point (about 2 msec later), switching commences again with a minor overshoot in the current sense waveform. Following is an instantaneous load transient back to 15 A. The output voltage peaks down about 1 V and responds back to the regulation point within 800  $\mu$ sec. The transient response time is determined by the zero in the voltage compensation.

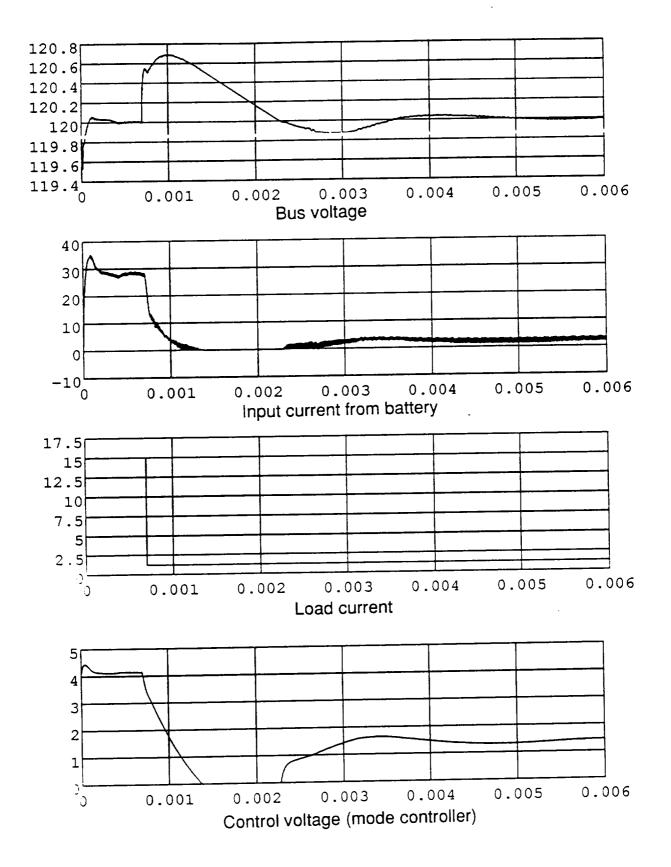

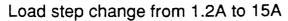

This transient response is compared against a simulation under the same conditions. Fig. 2-20 shows the simulated 15 A to 1.2 A transient response. The bus voltage response and current sense response are in excellent agreement with the experimental result.

The second photograph of Fig. 2-21 shows a transient from  $15 \wedge to 5 \wedge to 5 \wedge to 15 \wedge to 15$

#### 2.6.3 EMI Characteristics

# TRANSIENT RESPONSE (NO CABLE LENGTH)

2 MS/DIV

Load step change from 15A to 1.2A

42

The EMI characteristics that were measured include the output voltage ripple and the input current ripple (conducted emmissions).

### 2.6.3.1 Output Voltage Ripple

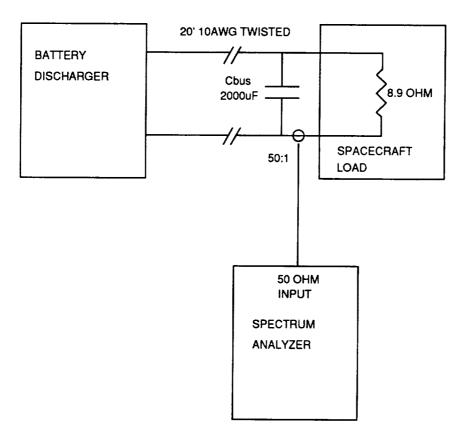

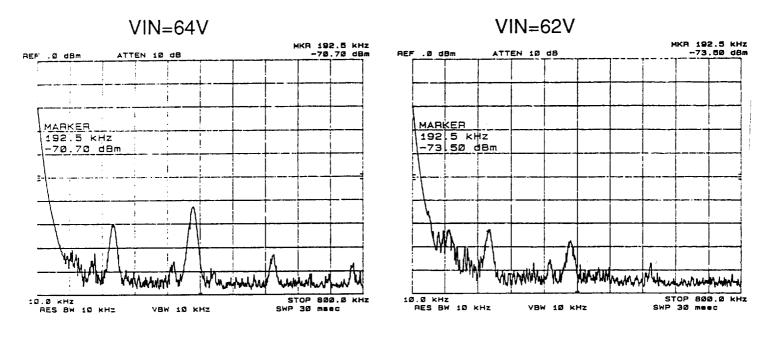

Output voltage ripple was difficult to measure with an oscilloscope due to noise pickup and test equipment grounding. An attempt was made to measure the spectrum of the output noise by an isolated current measurement. This test set-up is shown in Fig. 2-22. Fig. 2-23 shows the results of the output EMI measurement at different line voltages. The upper left plot is taken at a line voltage of 64 V. The first peak occurs at the ripple frequency of 192 kHz and reaches -71 dbm, which corresponds to 5.6 mV  $\Lambda$ C. The second peak occurs at the second harmonic and reaches -62 dbm. When the input voltage is reduced to 62 V, there is a large drop in the output EMI. This is because the duty cycle is 50% resulting in almost perfect cancellation of the ripple current. The lack of any significant component at a subharmonic of the ripple frequency indicates that the current sharing between the four modules is performing very well.

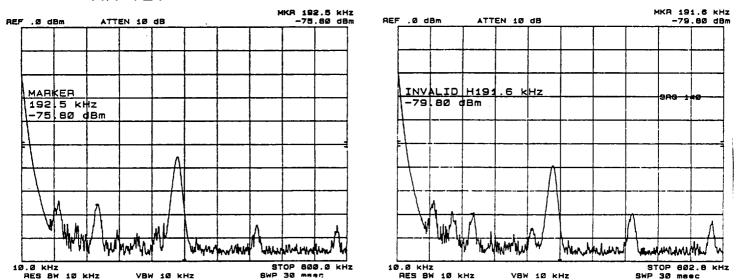

Fig. 2-24 shows a simulation result of the output voltage ripple, including the effect of one failed module. The top four traces show the phased inductor currents. The bottom trace shows the output voltage ripple. With all modules active, the ripple is barely noticeable on the output. When one module fails, the phasing of the remaining modules is not longer symmetrical. The ripple increases many times to over 300 mV peak-to-peak. This demonstrates the advantage of symmetrical phasing of the boost regulator modules.

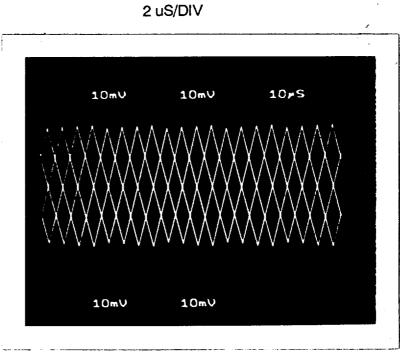

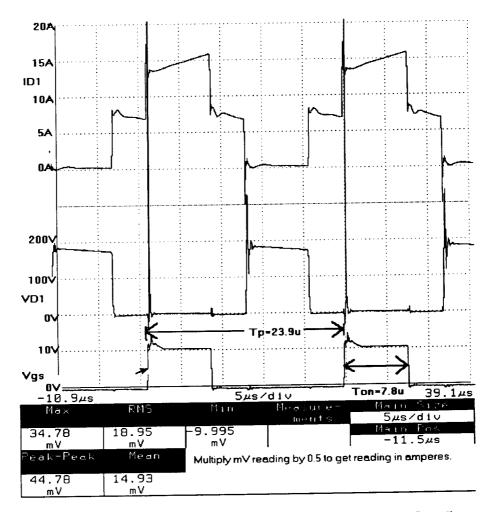

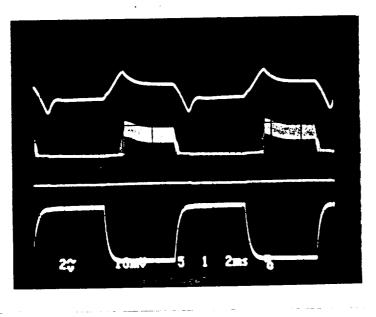

# 2.6.3.2 Input Current Ripple and Module Current Sharing

Fig. 2-25 shows a photograph of the battery input current. The peak-to-peak current ripple is approximately 20 mA. This is despite the fact that each individual module has a current ripple of over 10 A peak-to-peak, yet there is no input filter. The time scale on the photograph is 2

Vrms = \(\sqrt{10^(Xdbm/10)^1mW/50^8.9^500}\)

-60 dBM = 20mVAC

FIG. 2-22 EMI TEST SET-UP

# OUTPUT EMI MEASUREMENT

.

VIN=80V

VIN=72V

.

Effect of disabling one boost module

46

# FOUR MODULE BOOST BREADBOARD WAVEFORMS

INPUT CURRENT MAX. LOAD 20 mA/DIV

INDUCTOR CURRENTS

2.0 A/DIV

$\mu$ sec per division, indicating that the fundamental frequency of the waveform is about 180 kHz. Successive peaks have equal amplitude, indicating that the current sharing between modules is very good. The lower photograph shows the four inductor currents.

### **CHAPTER 2 REFERENCES**

- [1] D.M. Sable, B.H. Cho and F.C. Lee, "Use of Nonlinear Design Optimization Techniques in the Comparison of Battery Discharger Topologies for the Space Platform," IECEC, August, 1990.

- [2] R. Lee and D.S. Stephens, "Gap Loss in Current-Limiting Transformers," Electromechanical Design, April, 1973, pp. 24-26.

- [3] R. B. Ridley, "A New, Continuous-Time Model for Current-Mode Control," Power Conversion and Intelligent Motion Conference, October, 1989.

- [4] R. B. Ridley, "A New, Continuous-Time Model for Current-Mode Control with Constant On-Time, Constant Off-Time, and Discontinuous Conduction Mode," IEEE PESC, 1990.

- [5] D.M. Sable, B.H. Cho and R.B. Ridley, "Comparison of Performance of Single-Loop Control and Current-Injection Control for Power Converters Which Operate in both Continuous and Discontinuous Modes of Operation," IEEE PESC, June, 1990.

- [6] V. Vorperian, "Analysis of Current-mode Controlled PWM Converters Using the Model of the Current-Controlled PWM Switch," PCIM, October, 1990.

- [7] R.D. Middlebrook and S. Cuk, "A General Unified Approach to Modeling Switching-Converter Power Stages," IEEE PESC, 1976.

- [8] R.B. Ridley, "Small Signal Analysis of Parallel Converters," M.S. Thesis, VPI&SU, 1986.

- [9] V. Vorperian, "Simplified Analysis of PWM Converters Using the Model of the PWM Switch: Parts I and II," IEEE Transactions on Aerospace and Electronic Systems, March 1990, Vol. 26, No. 2.

# 3. VOLTAGE-FED, PUSH-PULL, AUTO-TRANSFORMER DESIGN

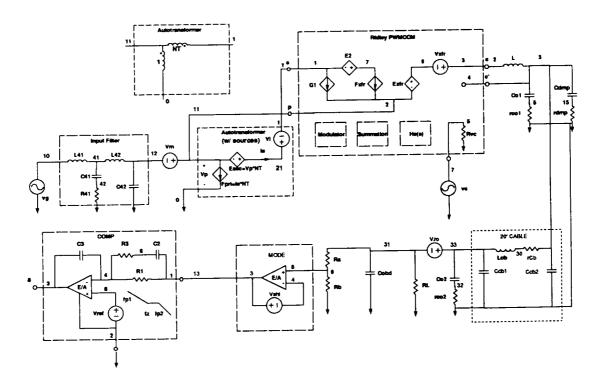

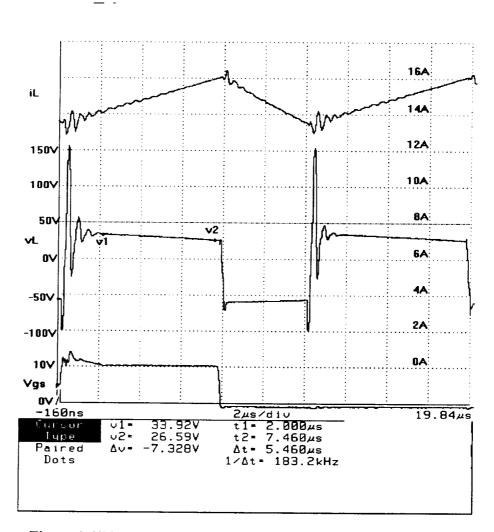

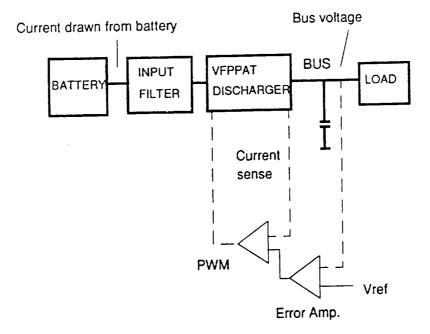

The voltage-fed, push-pull, autotransformer (VFPPAT) battery charger topology design and analysis are presented. The final breadboard stage of the VFPPAT topology was not integrated into the system as was the four-module, boost converter. However, the control loop has a provision for integrating the mode controller (Section 3.5) and analysis was performed with the 20', #8 AWG cable in place.

## **3.1 INTRODUCTION**

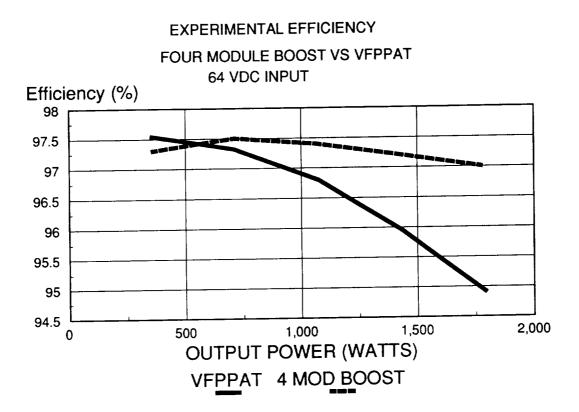

The specifications for the battery discharger studied are given in Table 3-1. The main focus of [1] was to optimize the battery discharger for efficiency, weight and dynamic characteristics by using a computer-based electronic spreadsheet program to figure the power loss of each converter. By plotting weight vs. frequency for curves representing efficiencies of 95%, 96%, and 97%, an optimal topology was determined. The results show that the multi-module boost converter is an optimal battery discharger topology in terms of efficiency. The VFPPAT topology was a viable option for the battery discharger. A project research grant from NASA was awarded to the VPEC to further investigate the findings of [1].

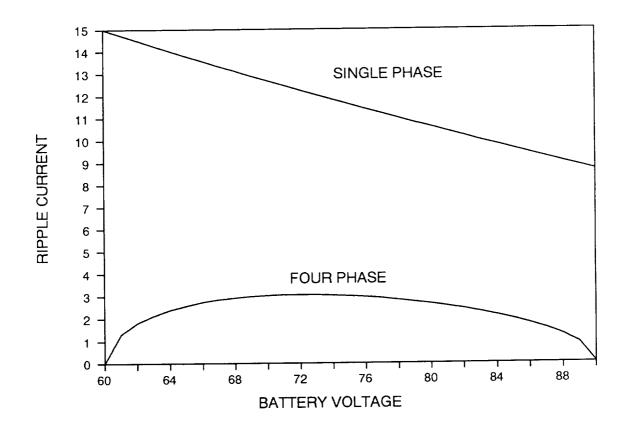

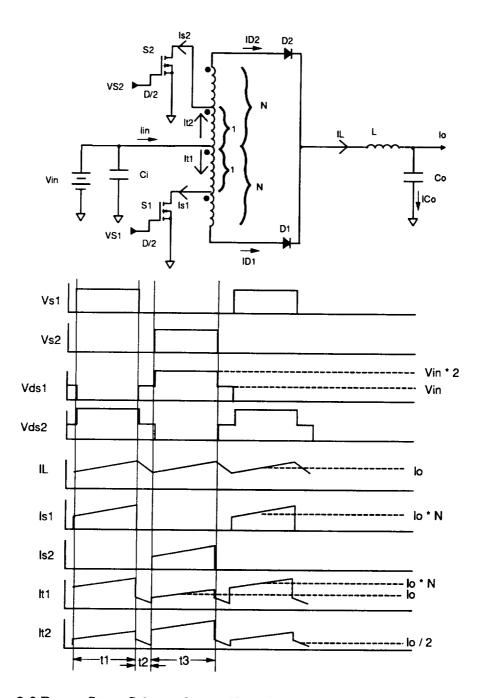

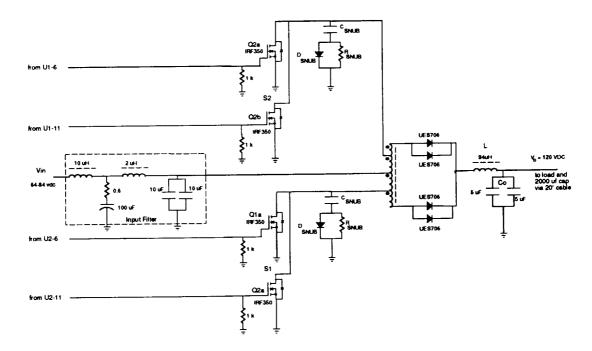

Two power converter topologies were considered for the research program of the battery discharger for the Space Platform. These include a four-module boost converter (FMBC) shown in Figure 3-2, and a VFPPAT shown in Figure 3-3. This section reports on the optimization of the design, methods of the build and analysis of the test results of the VFPPAT topology. First, however, a brief comparison of the two topologies is presented.

| Parameter                                | Specification         |

|------------------------------------------|-----------------------|

| Input Voltage Range                      |                       |

| Optimal Performance Range                | 64 Vdc to 84 Vdc      |

| Regulation Range                         | 53 Vdc to 84 Vdc      |

| Output Voltage Range                     | 120 Vdc <u>+</u> 4%   |

| Output Voltage Ripple                    | 200mV peak-to-peak    |

| Output Power Range                       | 0 W to 1800 W         |

| Output Current Range                     | 0 Amps to 15 Amps     |

| Input Current Ripple                     | 250 mA peak-to-peak   |

| Switching Frequency                      | 40 kHz                |

| Efficiency Goal                          |                       |

| (low line = 64 Vdc, high load = 15 Amps) | 96 %                  |

| Transient Performance                    |                       |

| Output Voltage Peaking Range             | 115.2 Vdc - 124.8 Vdc |

| Output Settling Time                     | 10 msec               |

## Table 3-1 Battery Discharger Design Specifications

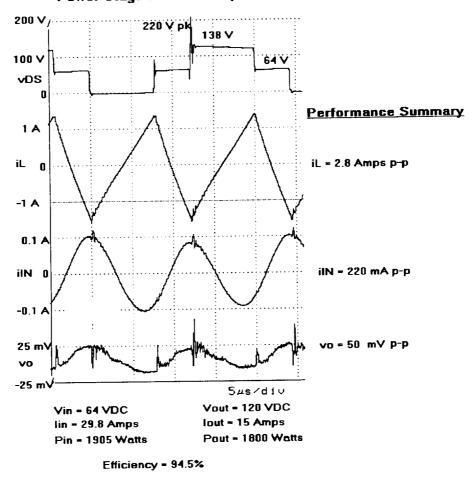

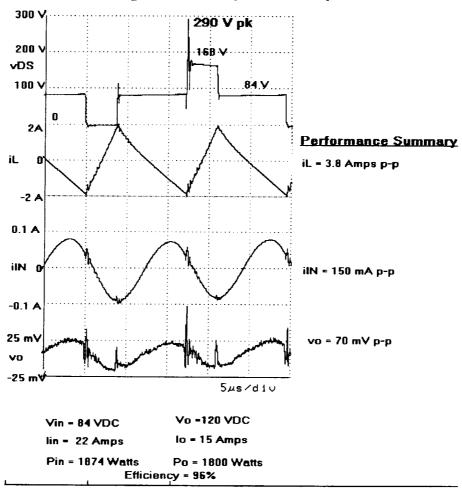

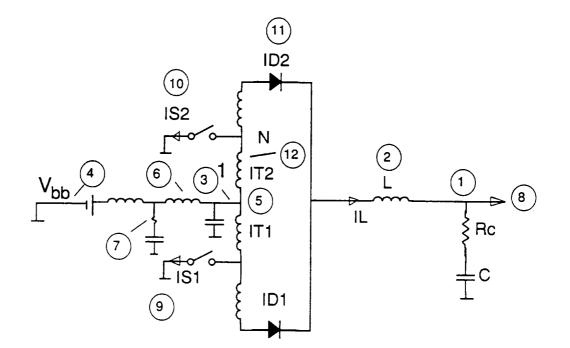

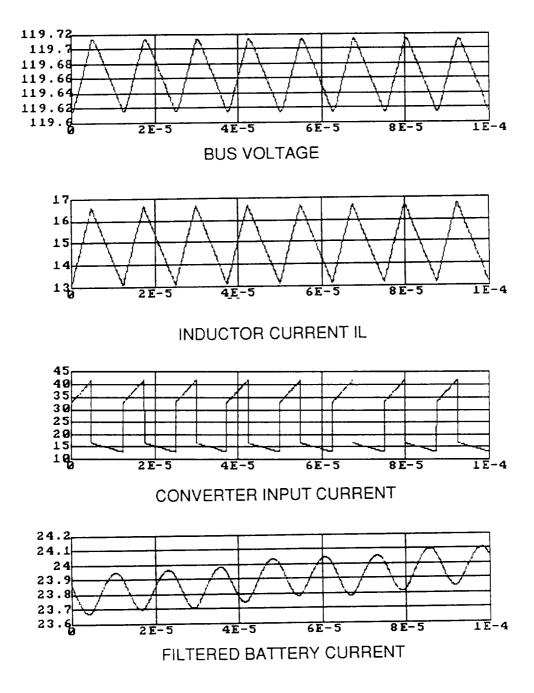

Figure 3-1 Power Stage Schematic and Waveforms of the Four Module Boost Con-

verter

Figure 3-2 Power Stage Schematic and Waveforms of the Voltage-Fed, Push-Pull Autotransformer Converter

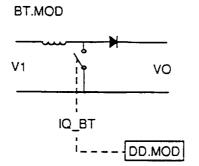

## 3.1.1 Voltage-Fed, Push-Pull Autotransformer (VFPPAT)

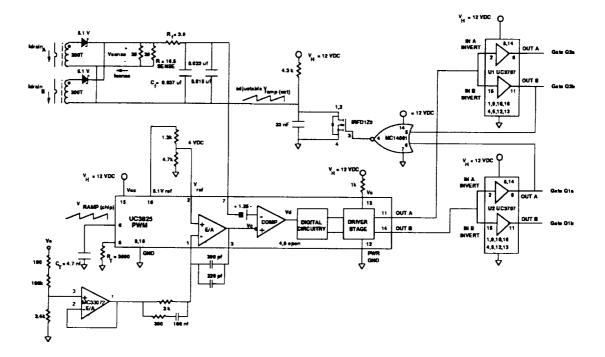

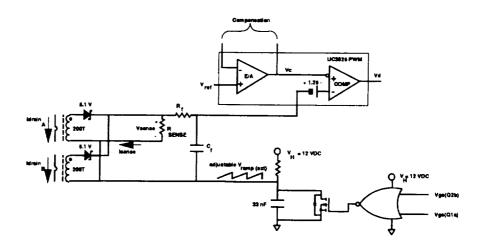

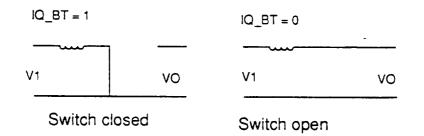

The VFPPAT presents several advantages. The push-pull operation along with the non-isolated nature of the autotransformer allows for a single PWM chip to be used to directly drive the MOSFETs (whose source terminals connect to the same ground as the input, output, and PWM reference). Because the push-pull operation requires only two switches operating 180° out of phase, a PWM IC (such as the UC1825) can be used; this is not the case for the FMBC with its four-phase PWM. The presence of the inductor on the output of this buck-derived converter allows for a continuous output current to flow over most of the power range. Peak-to-peak ripple current is less than for a boost converter, thus eliminating the need for an additional output filter stage.

Many of the disadvantages of the VFPPAT result from its buck-derived nature. A discontinuous input current will require filtering to meet the ripple current specification. In addition, this high current ripple will not allow an input capacitor with a high equivalent series resistance (ESR) value. By using low ESR, polypropolene capacitors, the capacitor ripple current rating will not be exceeded. Any imbalance in the transformer may cause "flux walking" to occur. This problem may damage the switching devices by allowing the transformer to saturate and pass large current through the drain. The use of current-injection control (CIC) insures flux walking does not occur by level detecting both the dc and ac portions of the transistor drain current.

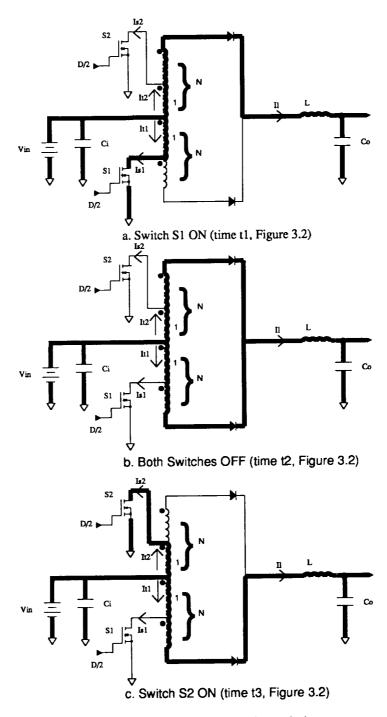

Figure 3-2 shows the tapped version of the VFPPAT along with the resulting waveforms. These waveforms illustrate the push-pull nature of the converter. Figure 3-3 uses thick lines to show that each time a switch is gated ON, the diode connected to the opposing winding conducts. This provides a voltage of Vin to each primary on every other gating of the switch, and a primary voltage of zero when both switches are OFF.

55

Because the switch transistors are operated 180° out of phase, the primary voltage is constantly reversed due to the polarity of the primaries, and complete flux balance will take place provided the circuit and waveforms are completely symmetrical.

Figure 3-3 VFPPAT Conduction Modes

By noting the applied voltages for times t1, t2, and t3, the voltage across the inductor can be found as shown in Eqs. 3.1 and 3.2. Where N is the turns ratio of one primary plus secondary (as shown in Figures 3-2 and 3-3).

$$VL_{ON} = (N+1) \times Vin - Vo$$

(either switch ON), and (3.1)

$$VL_{OFF} = Vin - Vo$$

(both switches OFF). (3.2)

For steady state operation the flux for the ON-time of the inductor must equal the flux for the OFF-time. This phenomenon known as flux balance uses the switching period Ts and the duty cycle at the inductor D (Note that the duty cycle of each switch is D/2) multiplied by the inductor voltage. Using the flux balance relationship the gain is found in equation 3.3.

Flux Balance:

$$\Delta \Phi_{ON} = VL_{ON} \times D \times Ts = \Delta \Phi_{OFF} = VL_{OFF} \times (1 - D) \times Ts$$

$$Gain = M = (Vo/Vin) = N \times D + 1$$

(3.3)

### 3.1.2 Summary

The results of the trade-off study [1] determined that the FMBC and VFPPAT topologies would provide the efficiency and size needed for the Space Platform battery discharger. Of these two topologies, the VFPPAT provides a challenge to optimize the design such that the resulting efficiency and performance is comparable to that of the FMBC. The VFPPAT can be designed in a manner which may make it more reliable than the FMBC. Finally, by investigating all areas of the power stage of the VFPPAT, a valuable lesson in optimizing the performance of high power converter operation can be learned.

# 3.2 VFPPAT POWER STAGE DESIGN AND PARAM-ETER VALUE SELECTION

Establishment of the parameter values of the circuit components to meet the design specifications is performed along with choice of each component in accordance with the approved parts list [2]. The autotransformer turns ratio and inductor value are chosen first, and the resulting voltage and current levels are used to determined the remaining power stage components.

A limited number of flight approved semiconductors causes the design to rely on optimization of the power stage magnetics for achievement of the best efficiency. Therefore the semiconductors are chosen and the values of the magnetic components are determined in this section, and the magnetics design is detailed in Section 3.3.

### 3.2.1 General Power Stage Analysis

The design of the power stage is begun by calculating the maximum duty cycle and then choosing a value for the autotransformer turns ratio. The resulting voltage levels are then calculated.

#### Autotransformer Turns Ratio and Converter Duty Cycle Range

The establishment of the gain equation along with the input specifications listed in Table 3-1 allows the design stage to begin. By noting that the input voltage regulation range from Table 3-1 is 53-84 Vdc and the output voltage is 120 Vdc, both the duty ratio D and the turns ratio N (Fig. 3-2) can be chosen. The choice of D is based on the maximum duty cycle a typical PWM IC can produce at the switch (D/2). This value reaches a theoretical maximum of 50% for the chosen UC1825 PWM. However, when variables such as rise and fall times are considered, this value can safely be assumed to be a maximum of 45%. The maximum duty cycle will occur at low line (53 Vdc). By using the gain Eq. 3.3 The minimum turns ratio is determined as follows:

$$N_{\min} = \frac{(Vo/Vin_{\min}) - 1}{D_{\max}} = \frac{(120V/53V) - 1}{0.9} = 1.405$$

Because this is a minimum value, N=1.5 was selected to accommodate for any drops in the semiconductors or other components. Also, 1.5 is favorable for winding the autotransformer because it allows for an integer number of turns to be wound for a complete set of conductors for all primaries and secondaries. The design then simply taps two series windings for a primary (autotransformer winding ratio of 1 in Fig. 3-2) and taps a third winding for the secondary giving a total of N=1.5.

The establishment of a turns ratio allows the duty cycle range of the converter to be calculated. This ratio is found by using Eq. 3.3 as follows:

$$Dmin = \frac{(Vo - Vin_{\max} + Vde)}{((Vi_{\max} - Vqe) \times (N+1) - Vi_{\max})} = \frac{(120V - 84V + 1.5)}{((84V - 1.65V) \times (1.5+1) - 84V)} = 0.31, \text{ and}$$

$$Dmax = \frac{(Vo - Vin_{\min} + Vde)}{((Vi_{\min} - Vqe) \times (N+1) - Vi_{\min})} = \frac{(120V - 53V + 1.5)}{((53V - 1.65V) \times (1.5+1) - 53V)} = 0.91,$$

where the voltage drops are assumed to be:

Vqe = estimated primary voltage drop = 1.65 V, and

Vde = estimated secondary voltage drop = 1.50 V.

The duty cycles calculated are twice the duty cycle seen by the switch. Therefore the duty cycles seen at the switch are as follows:

$$Dswitch_{min} = \frac{D_{min}}{2} = \frac{0.31}{2} = 0.155$$

, and

$Dswitch_{max} = \frac{D_{max}}{2} = \frac{0.91}{2} = 0.455.$

The maximum duty cycle of 0.46 is attainable with the UC1825 IC chosen for this design. This value is achieved using the dead-time capacitor calculation specified by the manufacturer's data sheet, and it is calculated in Section 3.5.

#### **Power Stage Voltage Levels**

Voltage levels experienced by the power stage components can be determined by using Kirchoff's Voltage Law and Fig. 3-2. The voltage of the switch is equal to the input voltage or twice the input voltage when the opposing switch is OFF or ON, respectively and is given by Eq. 3.4:

$$Vds_{(opposing switch ON)} = 2Vin$$

, and (3.4*a*)

$$Vds_{(opposing switch OFF)} = Vin.$$

(3.4b)

Autotransformer primary voltage levels are equal to Vin when either switch is ON and zero when the switches are OFF as given by Eq. 3.5:

$$V prim_{(either switch ON)} = Vin$$

, and (3.5*a*)

$$Vprim_{(either switch OFF)} = 0. \tag{3.5b}$$

Autotransformer secondary voltages are equal to the primary voltages through the turns ratio as shown in Eq. 3.6:

$$Vsec_{(either switch ON)} = Vprim \times (N-1) = Vin \times (N-1) = 0.5Vin, \text{ and}$$

(3.6*a*)

$$Vsec_{(either switch OFF)} = \frac{Vprim}{(N-1)} = 0.$$

(3.6b)

The voltage experienced by the inductor is established next (Eq. 3.7):

$$VL_{(switch ON)} = (N+1) \times Vin - Vo = 2.5Vin - Vo, \text{ and}$$

(3.7*a*)

$$VL_{(switch \ OFF)} = Vin - Vo. \tag{3.7b}$$

The reverse voltage on the diode occurs only when the adjacent switch is conducting as found using Eq. 3.8:

$$Vrr = (VL + Vo) - Vin \times (N+1) = 2N \times Vin.$$

(3.8)

Finally, the voltage levels of the input and output capacitors are simply the input and output voltage, respectively, as shown in Eqs. 3.9 and 3.10:

$$VCi = Vin$$

, and (3.9)

$$VCo = Vo. \tag{3.10}$$

The resulting component voltage levels for low line and high line input voltages are shown in Table 3-2.

| Voltage Designation                                          | Voltage Level<br>Low Line (Vin = 53 Vdc) | Voltage Level<br>High Line (Vin = 84 Vdc) |

|--------------------------------------------------------------|------------------------------------------|-------------------------------------------|

| $Vds_{(opposing \ switch \ ON)}$                             | 106.0 V                                  | 168.0 V                                   |

| Vprim <sub>(either switch ON)</sub>                          | 53.0 V                                   | 84.0 V                                    |

| $\operatorname{Vsec}_{(\operatorname{opposing switch OFF})}$ | 26.5 V                                   | 42.0 V                                    |

| $\mathrm{VL}_{(either switch ON)}$                           | 12.5 V                                   | 90.0 V                                    |

| Vrr                                                          | 159.0 V                                  | 252.0 V                                   |

| VCi                                                          | 53.0 V                                   | 84.0 V                                    |

| VCo                                                          | 120.0 V                                  | 120.0 V                                   |

| Table 3-2 Maximum V | oltages Levels of Power Stag | e Components |

|---------------------|------------------------------|--------------|

|---------------------|------------------------------|--------------|

#### **3.2.2 Power Stage Component Selection**

Now that the voltage levels are known, the inductor value is determined, and the resulting peak current and root-mean-square (rms) current levels are then found. Based on these levels, the input and output capacitors and the semiconductor devices to be used for the switches and rectifiers are chosen.

#### **3.2.2.1 Inductor**

#### **Inductor Value**

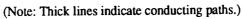

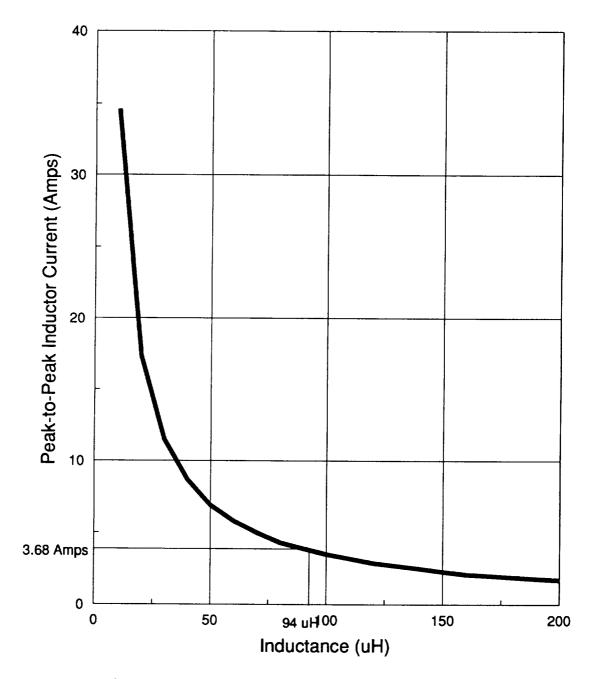

The choice of an inductor value for the VFPPAT is related to many factors such as: ripple current, power loss, power level at which discontinuous operation begins, size, and weight. An optimization program was conducted [1] and the resulting value of 94 uH was chosen for optimal efficiency. The following discussion illustrates how the inductor value affects the output ripple current (for other factors in the optimization refer to [1]).

The presence of the inductor on the output of the converter is advantageous only if the peak-to-peak inductor current level can be kept to a minimum, thereby reducing the output ripple current and the ripple voltage produced by the capacitor ESR. The peak-to-peak inductor current is most affected by the applied voltage VL, and by the duty cycle value (which was shown to be a function of the input voltage level in Eq. 3.1). Eq. 3.11 shows the peak-to-peak inductor current relationship to the voltage across the inductor:

$$\Delta IL = \frac{VL \times D}{2f \times L}.$$

(3.11)

The peak-to-peak inductor current will be greatest at high input voltage, where the applied inductor voltage will be 90 V as shown in Table 3-2. A plot of the  $\Delta$ IL versus

inductor values illustrates this relationship and provides insight into the optimized inductor value (Fig. 3-4). The inductor value of 94 uH chosen produces a relatively low peakto-peak inductor current of 3.68 A which allows for a minimal output voltage ripple. This choice of inductance value will produce a respectable sized inductor with minimal gap loss as will be shown in the power loss analysis (Section 3.6).

$$\Delta IL = \frac{90V \times 0.31}{2 \times 40kHz \times 94uH} = 3.68 A \ peak - to - peak$$

Figure 3-4 Peak-to-Peak Inductor Current vs. Inductance

#### Inductor Current

Now that the inductor value is determined, the peak and rms current levels are developed and values are presented. Because the load range has a minimum level of 0 A, the inductor current will have to become discontinuous at an output level between the specified 0 and 15 A. The output current level at which discontinuity occurs is half of the 3.68 A determined for Vin=84 Vdc earlier. Therefore discontinuous inductor current was chosen in [1] and occurs at 1.84 A dc load current or 216 W output power for Vin=84 Vdc. Maximum peak inductor current will occur at maximum load current as shown in Eq. 3.12:

$$ILpk = Iload_{\max} + \frac{(\Delta IL_{\max})}{2} = 15A + \frac{(3.68A)}{2} = 16.84A.$$

(3.12)

#### **Remaining Power Stage Current Levels**

As shown in Fig 3-2, the primary of the autotransformer will experience three different waveform levels depending on whether the adjacent MOSFET switch is in the ON state, the opposite MOSFET is in the ON state, or both MOSFETs are OFF, as shown in Eq. 3.13. The peak primary current from Fig. 3-2 is the autotransformer turns ratio multiplied by the inductor current:

$$ItI_{(SI ON)} = N \times IL = IsI, \text{ and}$$

(3.13*a*)

$$It_{(S2 \ ON)} = IL$$

, and (3.13b)

$$It1_{(SI \text{ and } S2 \text{ } OFF)} = \frac{IL}{2}.$$

(3.13c)

Similarly, the diode currents will conduct the inductor current when the opposite switch is ON, no current when the adjacent switch is ON, and half the inductor current if both switches are ON, as shown in Eq. 3.14. Note that the secondary currents of the autotransformer are equal to the diode currents which are developed below:

$$IDI_{(SI ON)} = IL$$

, and (3.14*a*)

$$IDI_{(S2 \ ON)} = 0$$

, and (3.14b)

$$IDI_{(SI \text{ and } S2 \text{ } OFF)} = \frac{IL}{2}.$$

(3.14c)

The input current is the sum of the two primary currents (It1 and It2), and the capacitor current is the input current without the dc level, as shown in Eq. 3.15:

$$ICi_{(either \ switch \ ON)} = (It1 + It2) - \frac{((N+2) \times Io)}{2}$$

, and (3.15a)

$$ICi_{(both switches OFF)} = IL - \frac{((N+2) - Io)}{2}.$$

(3.15b)

The output capacitor will experience the peak-to-peak inductor current (ie. the ac portion of the inductor current) as shown in Eq. 3.16:

$$ICo = \Delta IL.$$

(3.16)

The peak current level values are presented in Table 3-3.

| Current Designation        | Maximum Current Value<br>Low Line (Vin = 53 Vdc) | Maximum Current Value<br>High Line (Vin = 84 Vdc) |

|----------------------------|--------------------------------------------------|---------------------------------------------------|

| Isw <sub>peak</sub>        | 23.6 A                                           | 25.3 A                                            |

| Iprim <sub>peak</sub>      | 23.6 A                                           | 25.3 A                                            |

| $Isec_{peak} = ID1_{peak}$ | 15.8 A                                           | 16.8 A                                            |

| IL <sub>peak</sub>         | 15.8 A                                           | 16.8 A                                            |

| ICo <sub>peak</sub>        | 0.8 A                                            | 1.8 A                                             |

| Iin <sub>peak</sub>        | 42.1 A                                           | 39.4 A                                            |

| ICi <sub>peak</sub>        | 15.9 A                                           | 13.1 A                                            |

| Table 3-3 Peak | Current | Values of Powe | r Stage Components |

|----------------|---------|----------------|--------------------|

|----------------|---------|----------------|--------------------|

The rms current levels are based on the peak current levels which were developed in the previous section. The waveforms and time periods mentioned are illustrated in Fig. 3-2. Starting with the transformer the rms currents are shown in Eqs. 3.17 and 3.18:

$$Itprim_{rms} = \sqrt{\frac{1}{T}} \left( \int^{t} (ItI(t))^2 dt + 2 \int^{t^2} (ItI(t))^2 dt + \int^{t^3} (It(t))^2 dt \right), \text{ and } (3.17)$$

$$Itsec_{rms} = \sqrt{\frac{1}{T} \left( 2 \int^{t^2} (IDI(t))^2 dt + \int^{t^2} (IDI(t))^2 dt \right)}.$$

(3.18)

The rms current level as experienced by either switch is shown in Eq. 3.19:

$$IsI_{rms} = Is2_{rms} = \sqrt{\frac{1}{T} \left( \int^{tl} (ItI(t))^2 dt \right)}.$$

(3.19)

The rms current level of the output inductor is found using Eq. 3.20:

$$IL_{rms} = \sqrt{\frac{2}{T} \left( \int^{tl} (IL(t))^2 dt + \int^{t2} (IL(t))^2 dt \right)}.$$

(3.20)

The output capacitor rms current is shown by Eq. 3.21:

$$ICo_{rms} = \sqrt{\frac{2}{T} \left( \int^{tl} (IL(t) - Io)^2 dt + \int^{t2} (IL(t) - Io)^2 dt \right)}.$$

(3.21)

Finally, the input capacitor current can be found using Eq. 3.22:

$$ICi_{rms} = \sqrt{\frac{2}{T} \left( \int^{tl} (Itl(t) + It2(t))^2 dt + \int^{t2} (Itl(t) + It2(t))^2 dt \right)}.$$

(3.22)

A summary of the expected power stage rms current levels is presented in Table 3-4.

| Current Designation      | Maximum Current Level<br>Low Line (Vin = 53 Vdc) | Maximum Current Level<br>High Line (Vin = 84 Vdc) |

|--------------------------|--------------------------------------------------|---------------------------------------------------|

| Isw <sub>rms</sub>       | 15.2 A rms                                       | 8.9 A rms                                         |

| Iprim <sub>rms</sub>     | 18.3 A rms                                       | 11.1 A rms                                        |

| $Isec_{rms} = ID1_{rms}$ | 10.2 A rms                                       | 6.7 A rms                                         |

| IL <sub>ms</sub>         | 15.0 A rms                                       | 14.9 A rms                                        |

| ICo <sub>rns</sub>       | 0.5 A rms                                        | 1.2 A rms                                         |

| Iin <sub>ms</sub>        | 36.1 A ms                                        | 24.4 A rms                                        |

| IC <sub>irms</sub>       | 11.2 A rms                                       | 11.6 A rms                                        |

| Table 3-4 RMS | Current | Values of Power | • Stage Components |

|---------------|---------|-----------------|--------------------|

|---------------|---------|-----------------|--------------------|

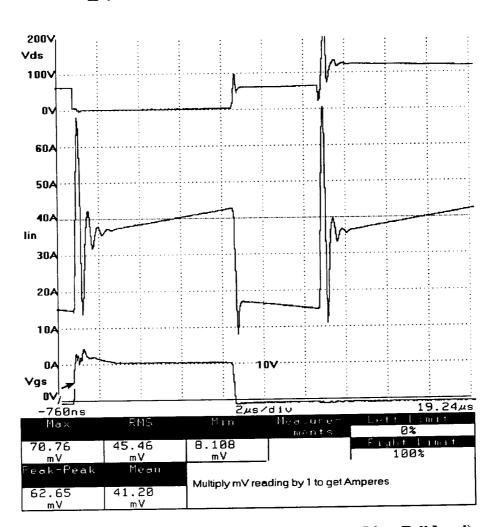

## **3.2.2.2 MOSFET Switch Transistors**

The switching transistor will experience the following maximum voltage and current levels (from Tables 3-2, 3-3, and 3-4):

$$Vds_{max} = 168.0 V$$

,

$Isw(pk)_{max} = 25.3 A peak$ , and

$Isw(rms)_{max} = 15.2 A rms$ .

MOSFET switch transistors are approved for flight by NASA and will be used because implementation is easier and performance is better than for bipolar switch transistors. The MOSFET chosen for this design is the IRF350; an approved part. The data for this device is listed in Table 3-5.

| Parameter                                                         | Value                                                              |

|-------------------------------------------------------------------|--------------------------------------------------------------------|

| Vds <sub>max</sub>                                                | 400 V                                                              |

| Id <sub>max</sub> (T <sub>C</sub> = 25° C)                        | 15 A Continuous                                                    |

| $Id_{max} (T_c = 50^{\circ} C)$                                   | 11.6 A Continuous                                                  |

| Id <sub>max</sub> (T <sub>c</sub> =100° C)                        | 9 A Continuous                                                     |

| Id <sub>max</sub>                                                 | 60 A (Repetitive Pulse)                                            |

| Pd <sub>max</sub> (T <sub>c</sub> =87° C, T <sub>j</sub> =105° C) | 72 W                                                               |

| Rds <sub>on</sub>                                                 | $0.34 \ \Omega \ (Id_{pk}=20 \text{ A}, \text{ Vgs}=15 \text{ V})$ |

| Ciss <sub>max</sub> (Vgs=0V, Vds=50V, f=1MHz)                     | 2000 pf                                                            |

| Coss <sub>max</sub> (Vgs=0V, Vds=50V, f=1MHz)                     | 200 pf                                                             |

| Crss <sub>max</sub> (Vgs=0V, Vds=50V, f=1MHz)                     | 50 pf                                                              |

| Vgs <sub>max</sub>                                                | <u>+</u> 20 V                                                      |

# Table 3-5 IRF350 MOSFET Switch Transistor Parameters

The derating guideline [2] requires the rated maximum transistor values be reduced to the following levels:

$$Vds_{(\max(derated))} = 75\% \times Vds_{\max} = 0.75 \times 400V = 300V,$$

$$Id_{(\max(derated))} = 75\% \times Id_{\max} = 0.75 \times 11.8A = 8.7A (T_C = 50^{\circ} C),$$

$$Pd_{(\max(derated))} = 60\% \times Pd_{\max} = 0.6 \times 72W = 43.2W (T_j = 105^{\circ} C), \text{ and}$$

$$Tj_{(\max(derated))} = 60\% \times Tj_{\max} = 0.6 \times 150^{\circ}C = 90^{\circ} C.$$

Each switch requires the use of two IRF350 MOSFETs in parallel for each switch. This will allow the derated continuous drain current requirement to be met by having each switch pass a drain current of 7.6 As rms, and, it will reduce the total ON resistance of the one switch leg to one-half of the 0.34  $\Omega$  exhibited by the IRF350. This lowering of the switch ON resistance will reduce conduction loss.

The 400 Vdrain-to-source voltage rating (which is derated to 300 V) is the main reason for choosing this device, because it will allow the 168 V applied level to exist with some overshoot. Otherwise, a smaller device would be specified to reduce the parasitic capacitances and the ON resistance of the drain.

Paralleling MOSFETs is not without its problems, however. The output capacitance (Coss) is doubled when MOSFETs are paralleled, and problems can develop due to using devices with unequal parasitics, resulting in unsynchronized switching and/or unequal sharing of drain current. These problems have been solved through the use of a reliable drive scheme (Section 3.5) and careful circuit layout to reduce and equate parasitics.

The expected power dissipation due to conduction is:

$$PQI_{ON}(\max) = Id^2 \times Rd_{ON} = \frac{(15.2 \ A \ rms)^2}{2} \times 0.34\Omega = 19.6 \ W.$$

The power dissipation of the device when it is ON should compare favorably with the derated 43.2 W at  $Tj=105^{\circ}$  C when the switching losses are added (provided proper heat sinking is implemented).

### **3.2.2.3 Rectifier Diodes**

Rectifier diodes are subject to the following voltage and current levels (from Tables 3-2, 3-3, and 3-4):

$$Vrr_{max} = 252.0 V$$

,

IDpk<sub>max</sub> = 16.8 A peak, and

IDrms<sub>max</sub> = 10.2 A rms.

A check of the approved parts list [2] shows that no diodes can meet the required derated voltage and current levels. Initially the design was to use two 1N5816 diodes ( $Vrr_{max}$ = 150 V) in series to handle the 252 V reverse voltage. This set of two diodes was to be paralleled so that each string would conduct half of the 10.2 A rms rectifier current (Iavgmax = 20 A). NASA determined that a failure of one of the series diodes could go undetected and was difficult to test for.

The next design chosen used UES706 diodes as a viable replacement. These diodes are rated for a reverse voltage of 400 V peak (which is derated to 325 V), an average forward current of 20 A each (which is derated to 60% provided the junction temperature stays below  $T_D$ ), and a peak forward current of 300 A for 8.3 msec. The temperature  $T_D$  is found from the derating guideline [2] to be:

$$T_{D} = T_{(j(derated))} - (Derating Factor) \times (T_{(j(max))} - T_{M}),$$

$$T_{D} = 60\% \times 105^{\circ} C - 60\% \times (105^{\circ} C - 90^{\circ} C) = 54^{\circ} C.$$

The maximum temperature of the case should remain around 50° C, which is the heat sink temperature. Therefore the junction temperature will be more than 54 ° C, and the diodes will have to be paralleled to meet the current specification. Paralleling the diodes will reduce the power loss due to the forward voltage drop. These rectifiers will not have to be put in series to meet the applied reverse voltage. However, ringing will have to be kept to less than a 325 V peak. The UES706 diodes are available in a D0-4 package and must meet final approval for space flight. The number of these diodes required will be half of the number of 1N5816 diodes, therefore increasing mean time between failure (MTBF) and reliability.

#### 3.2.2.4 Output Capacitor

The output capacitance value for the 120 V bus has been determined by NASA to be 2000 uf. However, fifteen to twenty-five feet of twisted, shielded, #10 AWG wire is between the converter and the output capacitor bank, making it necessary to have some capacitance placed at the converter output. The value chosen for the output capacitor was 10 uf. This value is low enough not to alter the final capacitance of the capacitor bank when the converters are paralleled, and high enough to support transients at the converter outputs.

For the test circuit, the output capacitor value of 10 uf was implemented using two 5 uf polypropolene capacitors with the following information:

| Part number                                    | = CFR13ALC505 |

|------------------------------------------------|---------------|

| Voltage rating                                 | = 200 Vdc     |

| ESR value                                      | = 0.011 Ω     |

| Maximum ripple current (T <sub>c</sub> =85° C) | = 8.5 A rms.  |

These parts meet the applied rms current of 0.6 A each (Table 3-4) and can be used for the 120 V output provided the derating is not less than 50%. Note that although these capacitors were chosen for breadboard testing, their size is rather large when compared to other approved styles such as the M39006 series. The choice of another style for flight use may reduce the size and must have an ESR value and rms current rating compatible with the applied 1.2 A rms current.

# 3.2.2.5 Input Capacitor

The input capacitor has two restrictions placed on it by this topology. The rms input current is a maximum 11.6 A (Table 3-4), and the converter input impedance will need to see a rather low impedance from the input capacitor. For these reasons the input capacitor was chosen at 20 uf; it is composed of two 10 uf polypropolene capacitors in parallel. The information for these capacitors is as follows:

| Part Number                                   | = CFR14LLC106      |

|-----------------------------------------------|--------------------|

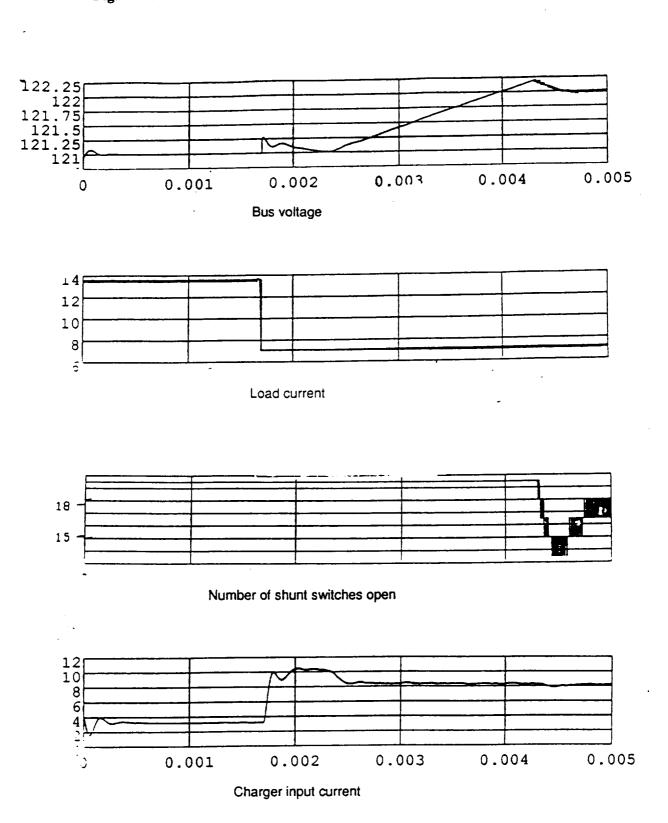

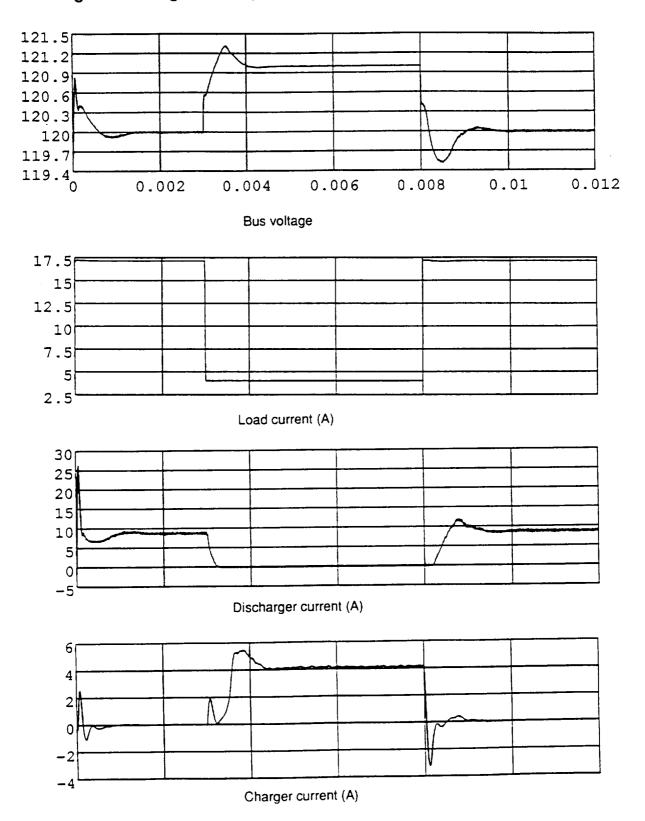

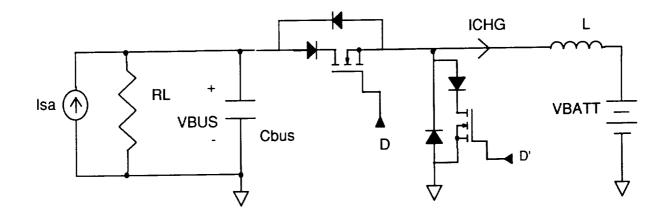

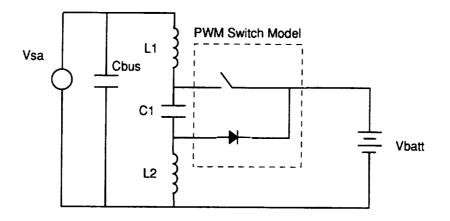

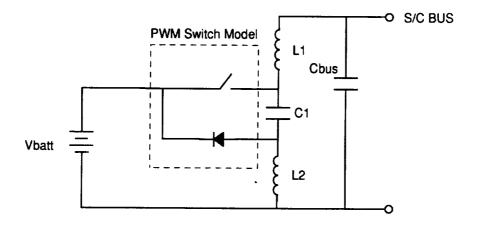

| Voltage Rating                                | = 200 Vdc          |